# CC1020 ナローバンド・システム用のシングル・チップ 低消費電力RFトランシーバ

## 特 長

- シングル・チップUHF RFトランシーバ

- 周波数範囲：402MHz ~ 470MHzおよび804MHz ~ 940MHz

- 高感度：-118dBm/12.5kHzチャネル

- プログラマブルな出力電力

- 低消費電流：Rx 19.9mA

- 低電源電圧：2.3V - 3.6V

- 外付けIFフィルタ不要

- 低IF周波数レシーバ

- わずかな外付け素子

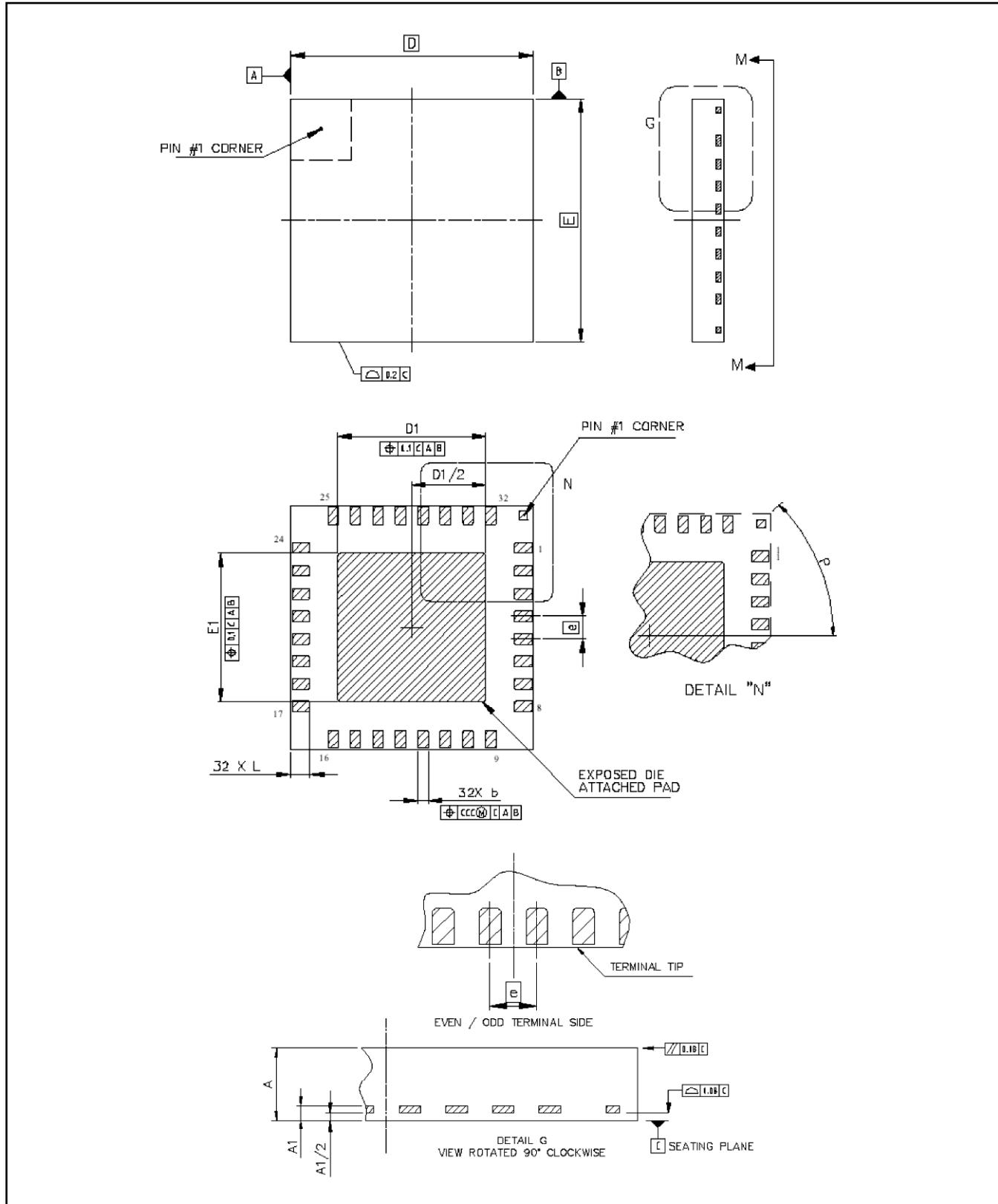

- 小型なQFN32パッケージ

- 鉛フリーのパッケージ

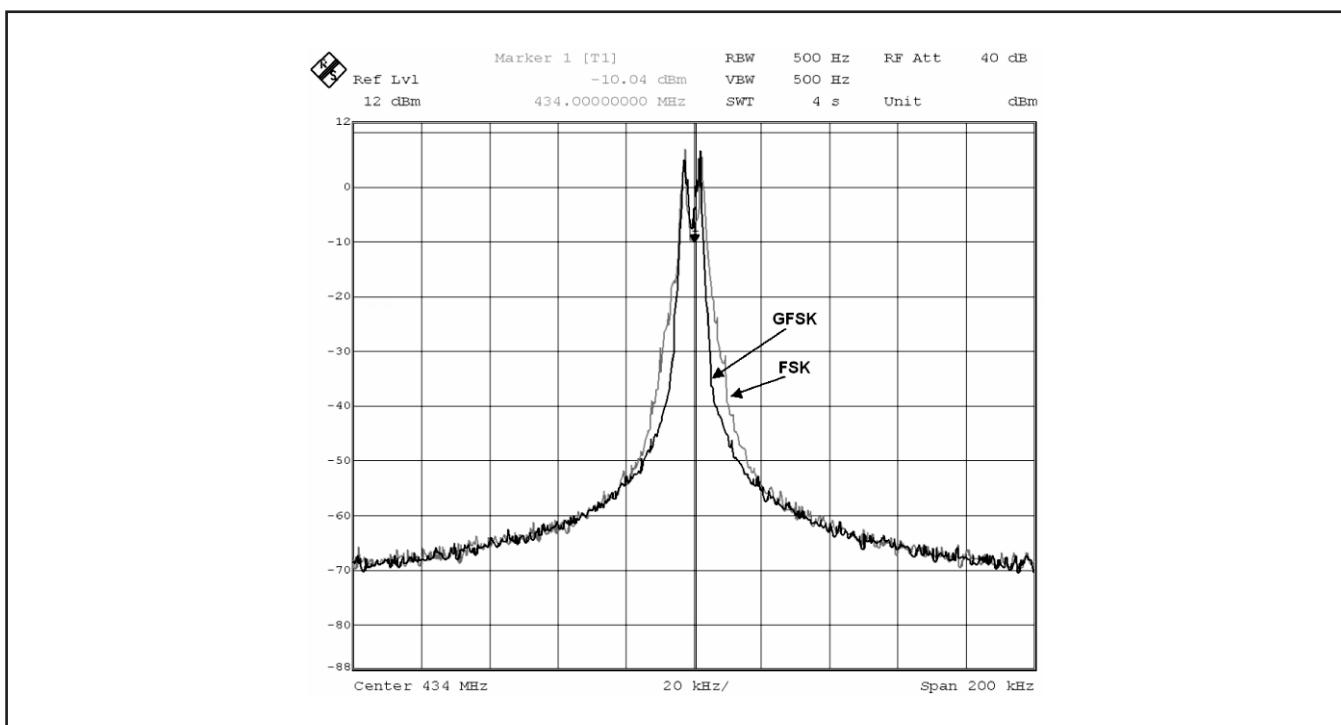

- デジタルRSSIおよびキャリア検知表示

- 最大データ・レート：153.6kBaud

- OOK、FSKおよびGFSKデータ変調

- ビット・シンクロナイザ内蔵

- 干渉波除去ミキサ

- プログラマブルな周波数およびAFCにより、水晶発振器の温度ドリフトがTCXOなしで補償可能

- 周波数ホッピング・システムに適合

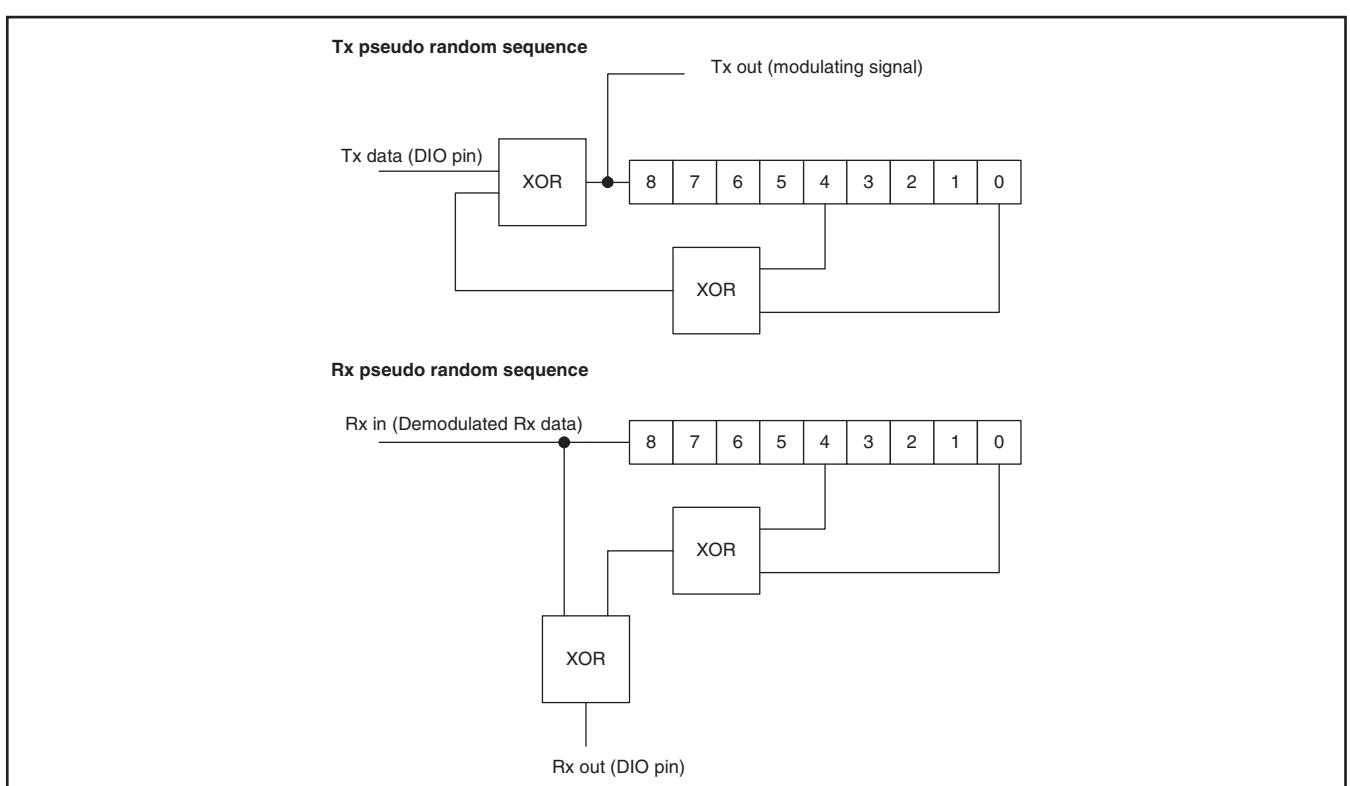

- EN 300 220、FCC CFR47パート15およびARIB STD T-67に準拠したシステムに適する

- 開発用キット完備

- CC1020の設定データを生成する、使いやすいソフトウェア

## アプリケーション

- 12.5kHzおよび25kHzの狭チャネル間隔のナローバンド低消費電力UHFワイヤレス・データ・トランスマッタ/レシーバ

- 402/424/426/429/433/447/449/469/868および915MHzのISM/SDR帯域システム

## ● AMR(自動検針)

- ワイヤレスのアラーム/セキュリティ・システム

- ホーム・オートメーション

- 低消費電力の遠隔計測

## 概 要

CC1020は、非常に低消費電力・低電圧のワイヤレス・アプリケーション向けに設計されたシングル・チップUHFトランシーバです。本デバイスは、402, 424, 426, 429, 433, 447, 449, 469, 868、および915MHzの周波数帯域のISM（産業、科学および医用）およびSDR（短距離無線装置）を主な目的としています。しかし、402 ~ 470および804 ~ 940MHzの範囲における他の周波数の多チャネル動作にも、容易にプログラミングすることができます。

CC1020は、ARIB STD T-67およびEN 300 220に準拠した、チャネル間隔12.5あるいは25kHzのナローバンド・システムに最適です。

CC1020の主な動作パラメータは、シリアルバスでプログラミングできます。そのため、CC1020はトランシーバとして柔軟かつ容易に使用できます。

一般的なシステムでは、CC1020は1個のマイクロコントローラと数個の外付け受動素子とともに使用されます。

CC1020はChipconの0.35μmのCMOSのSmartRF®-02テクノロジーで設計されています。

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 内 容

|                                      |    |

|--------------------------------------|----|

| 1. 略語 .....                          | 4  |

| 2. 絶対最大定格 .....                      | 5  |

| 3. 動作条件 .....                        | 5  |

| 4. 電気的仕様 .....                       | 5  |

| 4.1. RF送信部 .....                     | 6  |

| 4.2. RF受信部 .....                     | 8  |

| 4.3. RSSI/キャリア検知部 .....              | 11 |

| 4.4. IF部 .....                       | 11 |

| 4.5. 水晶発振器部 .....                    | 12 |

| 4.6. 周波数シンセサイザ部 .....                | 13 |

| 4.7. デジタル入出力 .....                   | 14 |

| 4.8. 消費電流 .....                      | 15 |

| 5. 端子配置 .....                        | 15 |

| 6. 回路解説 .....                        | 17 |

| 7. アプリケーション回路 .....                  | 18 |

| 8. 設定の概要 .....                       | 21 |

| 8.1. 設定用ソフトウェア .....                 | 21 |

| 9. マイクロコントローラ・インターフェイス .....         | 22 |

| 9.1. 4線式シリアル設定インターフェイス .....         | 23 |

| 9.2. 信号インターフェイス .....                | 25 |

| 10. データ・レートのプログラミング .....            | 27 |

| 11. 周波数のプログラミング .....                | 28 |

| 11.1. ディザリング .....                   | 29 |

| 12. レシーバ .....                       | 29 |

| 12.1. IF周波数 .....                    | 29 |

| 12.2. レシーバ・チャネル・フィルタ帯域幅 .....        | 30 |

| 12.3. 復調器、ビット・シンクロナイザおよびデータ決定 .....  | 31 |

| 12.4. レシーバ感度 対 データ・レートおよび周波数間隔 ..... | 32 |

| 12.5. RSSI .....                     | 32 |

| 12.6. 干渉波除去キャリブレーション .....           | 34 |

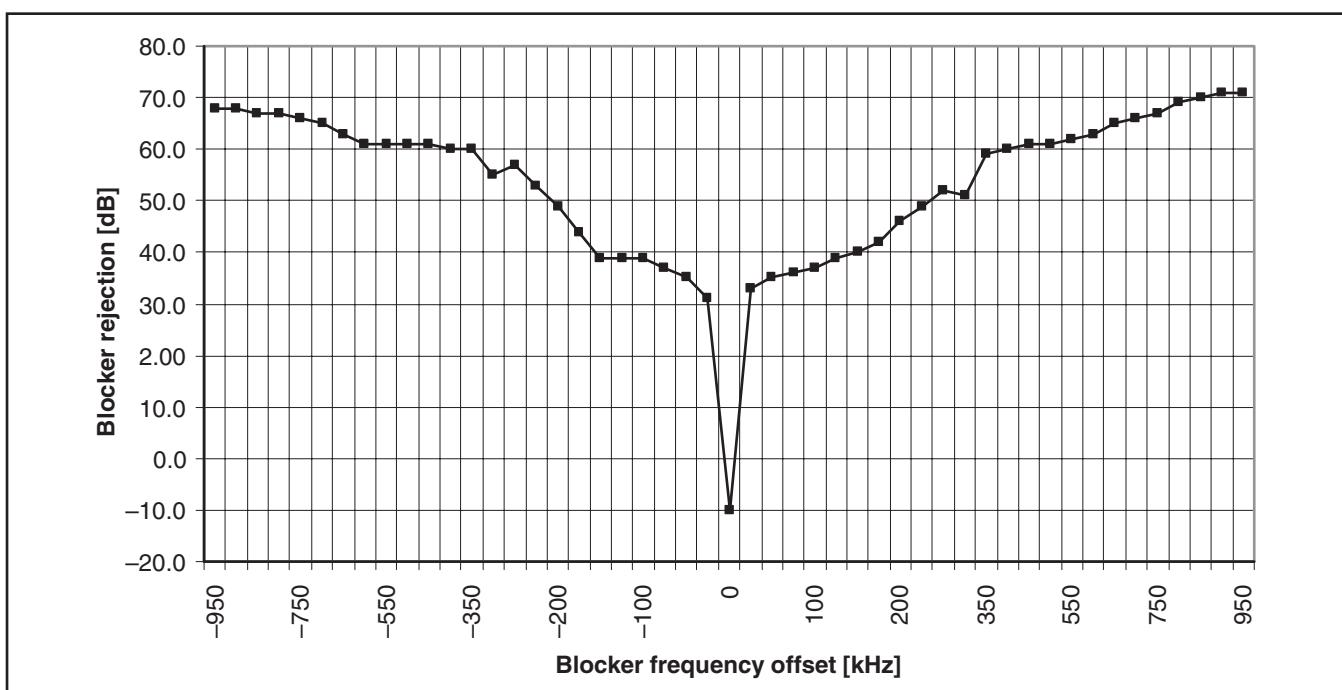

| 12.7. ブロッキングおよび選択性 .....             | 35 |

| 12.8. リニアIFチェインおよびAGCの設定 .....       | 36 |

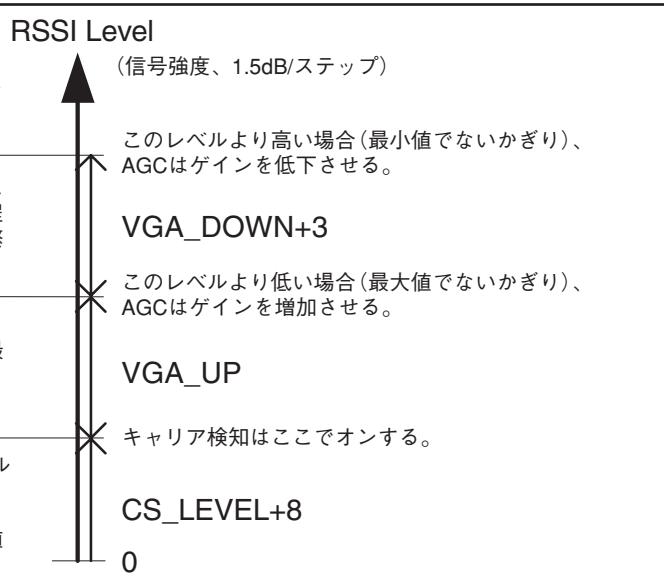

| 12.9. AGC設定 .....                    | 37 |

| 12.10. プリアンブル長およびシンク・ワード .....       | 37 |

| 12.11. キャリア検知 .....                  | 37 |

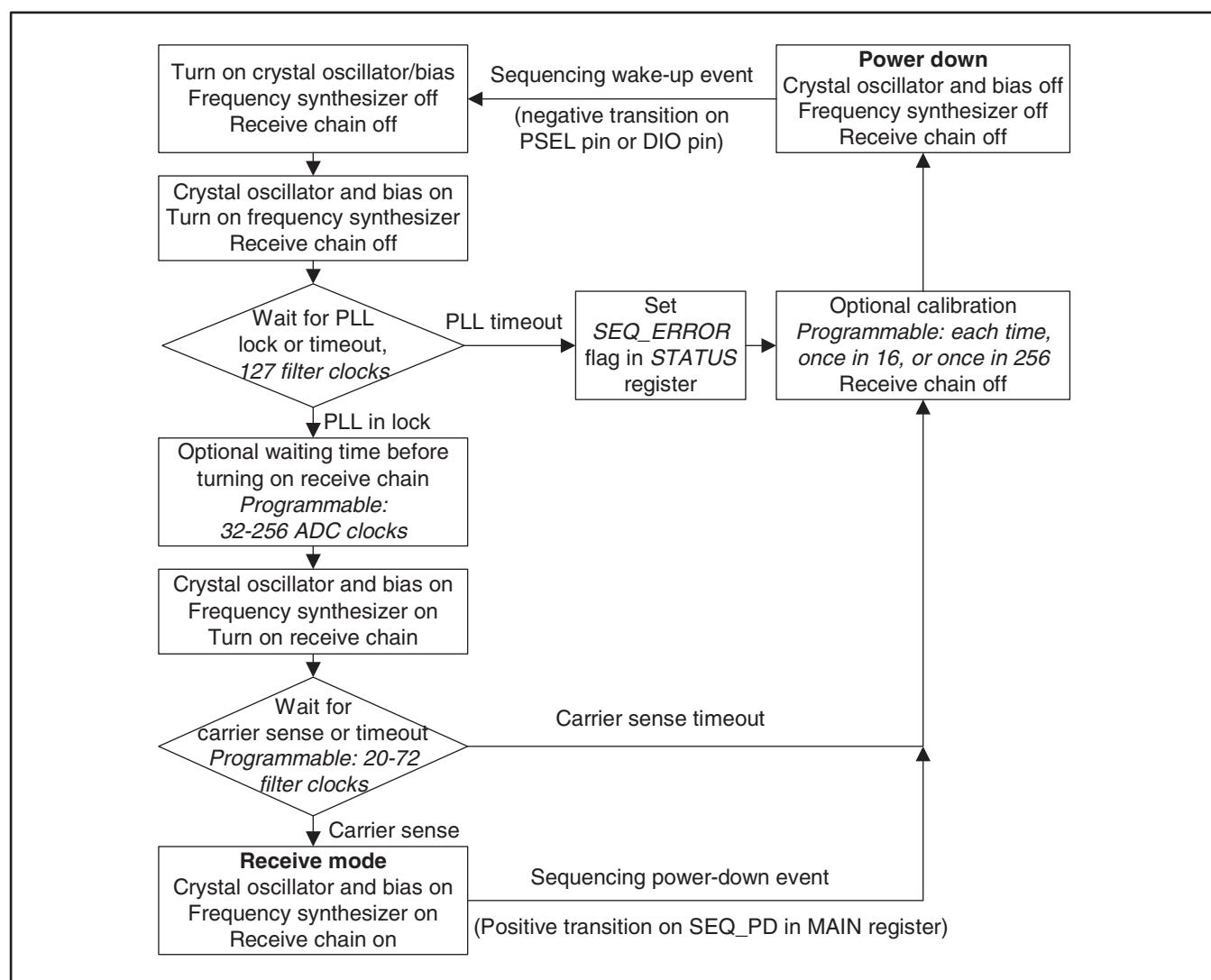

| 12.12. 自動パワーアップ・シーケンス .....          | 37 |

| 12.13. 自動周波数制御 (AFC) .....           | 38 |

| 12.14. デジタルFM .....                  | 39 |

|                                   |    |

|-----------------------------------|----|

| 13. トランスマッタ                       | 39 |

| 13.1. FSK変調フォーマット                 | 39 |

| 13.2. 出力電力プログラミング                 | 41 |

| 13.3. TXデータ・レイテンシ                 | 42 |

| 13.4. スプリアスおよび変調帯域幅の低減            | 42 |

| 14. 入出力整合およびフィルタリング               | 42 |

| 15. 周波数シンセサイザ                     | 46 |

| 15.1. VCO、チャージポンプおよびPLLループ・フィルタ   | 46 |

| 15.2. VCOおよびPLLセルフ・キャリブレーション      | 47 |

| 15.3. PLLターンオン時間 対 ループ・フィルタ帯域幅    | 48 |

| 15.4. PLLロック時間 対 ループ・フィルタ帯域幅      | 49 |

| 16. VCOおよびLNAの電流制御                | 49 |

| 17. パワー・マネージメント                   | 50 |

| 18. オン-オフ変調 (OOK)                 | 53 |

| 19. 水晶発振器                         | 54 |

| 20. 内蔵テスト・パターン・ジェネレータ             | 55 |

| 21. DCLK端子の割込み                    | 55 |

| 21.1. PLLロックの割込み                  | 55 |

| 21.2. 受信信号キャリア検知の割込み              | 55 |

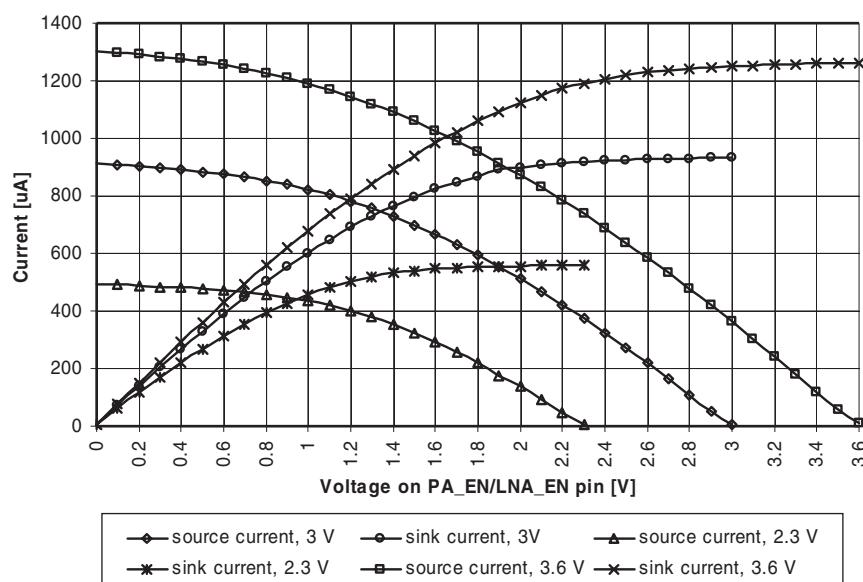

| 22. PA_ENおよびLNA_ENデジタル出力端子        | 56 |

| 22.1. 外部LNAあるいはPAとのインターフェイス       | 56 |

| 22.2. 汎用出力制御端子                    | 56 |

| 22.3. PA_ENおよびLNA_EN端子のドライブ       | 56 |

| 23. システムの考察およびガイドライン              | 57 |

| 24. 推奨PCBレイアウト                    | 58 |

| 25. アンテナの考察                       | 58 |

| 26. 設定レジスタ                        | 59 |

| 26.1. CC1020のレジスタの概要              | 60 |

| 27. パッケージの内容 (QFN32)              | 80 |

| 27.1. パッケージのマーキング                 | 81 |

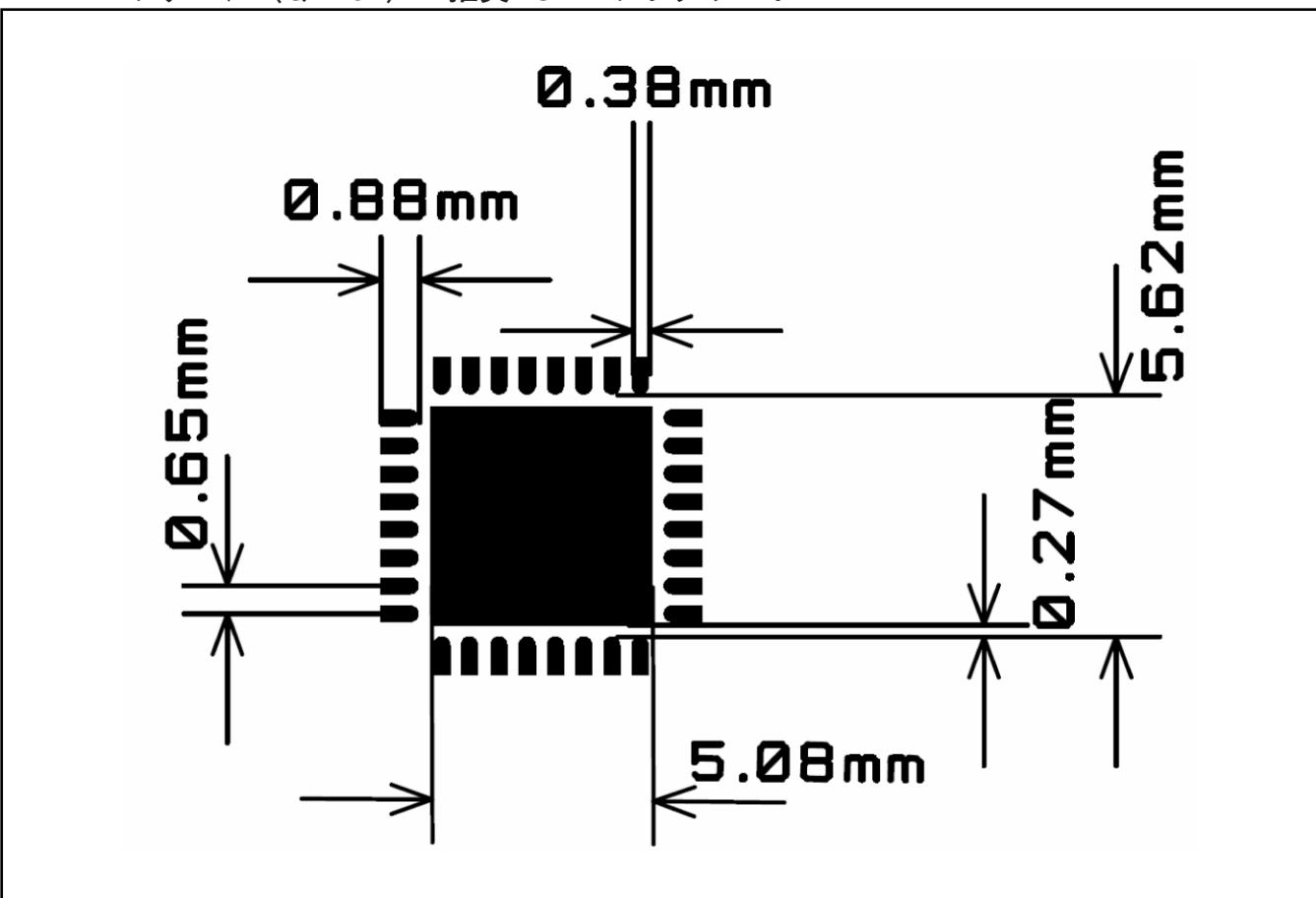

| 27.2. パッケージ (QFN32) の推奨PCBフットプリント | 81 |

| 27.3. パッケージの熱的特性                  | 82 |

| 27.4. 半田付けに関する情報                  | 82 |

| 27.5. プラスチック・チューブの仕様              | 82 |

| 27.6. キャリア・テープおよびリールの仕様           | 82 |

| 28. 発注情報                          | 82 |

| 29. 一般情報                          | 83 |

| 30. アドレス情報                        | 85 |

## 1. 略語

|      |                                                       |

|------|-------------------------------------------------------|

| ACP  | 隣接チャネル漏洩電力 (Adjacent Channel Power)                   |

| ACR  | 隣接チャネル除去 (Adjacent Channel Rejection)                 |

| ADC  | AD コンバータ (Analog-to-Digital Converter)                |

| AFC  | 自動周波数制御 (Automatic Frequency Control)                 |

| AGC  | 自動ゲイン制御 (Automatic Gain Control)                      |

| AMR  | 自動検針 (Automatic Meter Reading)                        |

| ASK  | 振幅偏移変調 (Amplitude Shift Keying)                       |

| BER  | ビット誤り率 (Bit Error Rate)                               |

| BOM  | 部品表 (Bill Of Materials)                               |

| bps  | ビット/秒 (bits per second)                               |

| BT   | 帯域幅時間積—GFSKで使用 (Bandwidth-Time product)               |

| ChBW | レシーバ・チャネル・フィルタ帯域幅 (Receiver Channel Filter Bandwidth) |

| CW   | 連続波 (Continuous Wave)                                 |

| DAC  | DA コンバータ (Digital-to-Analog Converter)                |

| DNM  | 実装禁止 (Do Not Mount)                                   |

| ESR  | 等価直列抵抗 (Equivalent Series Resistance)                 |

| FHSS | 周波数ホッピング・スペクトラム拡散 (Frequency Hopping Spread Spectrum) |

| FM   | 周波数変調 (Frequency Modulation)                          |

| FS   | 周波数シンセサイザ (Frequency Synthesizer)                     |

| FSK  | 周波数偏移変調 (Frequency Shift Keying)                      |

| GFSK | ガウス周波数偏移変調 (Gaussian Frequency Shift Keying)          |

| IC   | 集積回路 (Integrated Circuit)                             |

| IF   | 中間周波数 (Intermediate Frequency)                        |

| IP3  | 3次インターセプト・ポイント (Third Order Intercept Point)          |

| ISM  | 産業・科学・医用 (Industrial Scientific Medical)              |

| kbps | キロ・ビット/秒 (kilo bits per second)                       |

| LNA  | 低雑音アンプ (Low Noise Amplifier)                          |

| LO   | ローカル・オシレータ (Local Oscillator - 受信モード)                 |

| MCU  | マイクロ・コントローラ・ユニット (Micro Controller Unit)              |

| NRZ  | ノン・リターン・ツー・ゼロ (Non Return to Zero)                    |

| OOK  | オン-オフ変調 (On-Off Keying)                               |

| PA   | パワー・アンプ (Power Amplifier)                             |

| PD   | 位相判別器/パワーダウン (Phase Detector / Power Down)            |

| PER  | パケット誤り率 (Packet Error Rate)                           |

| PCB  | プリント回路基板 (Printed Circuit Board)                      |

| PN9  | 擬似ランダム・ビット・シーケンス-9ビット (Pseudo-random Bit Sequence)    |

| PLL  | 位相同期回路 (Phase Locked Loop)                            |

| PSEL | プログラム選択 (Program Select)                              |

| RF   | 高周波 (Radio Frequency)                                 |

| RSSI | 受信信号強度表示 (Received Signal Strength Indicator)         |

| RX   | 受信 - モード (Receive)                                    |

| SBW  | 信号帯域幅 (Signal Bandwidth)                              |

| SPI  | シリアル・ペリフェラル・インターフェイス (Serial Peripheral Interface)    |

| SRD  | 短距離無線装置 (Short Range Device)                          |

| TBD  | 未定 (To Be Decided/Defined)                            |

| T/R  | 送信/受信-スイッチ (Transmit/Receive)                         |

| TX   | 送信 - モード (Transmit)                                   |

| UHF  | 超高周波数 (Ultra High Frequency)                          |

| VCO  | 電圧制御発振器 (Voltage Controlled Oscillator)               |

| VGA  | 可変ゲインアンプ (Variable Gain Amplifier)                    |

| XOSC | 水晶発振器 (Crystal oscillator)                            |

| XTAL | 水晶振動子 (Crystal)                                       |

## 2. 絶対最大定格

表1に示す絶対最大定格を超えてはなりません。これらの制限値を超えたストレスをすこしでも加えると、デバイスは永久破壊することがあります。

## 3. 動作条件

CC1020の動作条件を表2に示します。

## 4. 電気的仕様

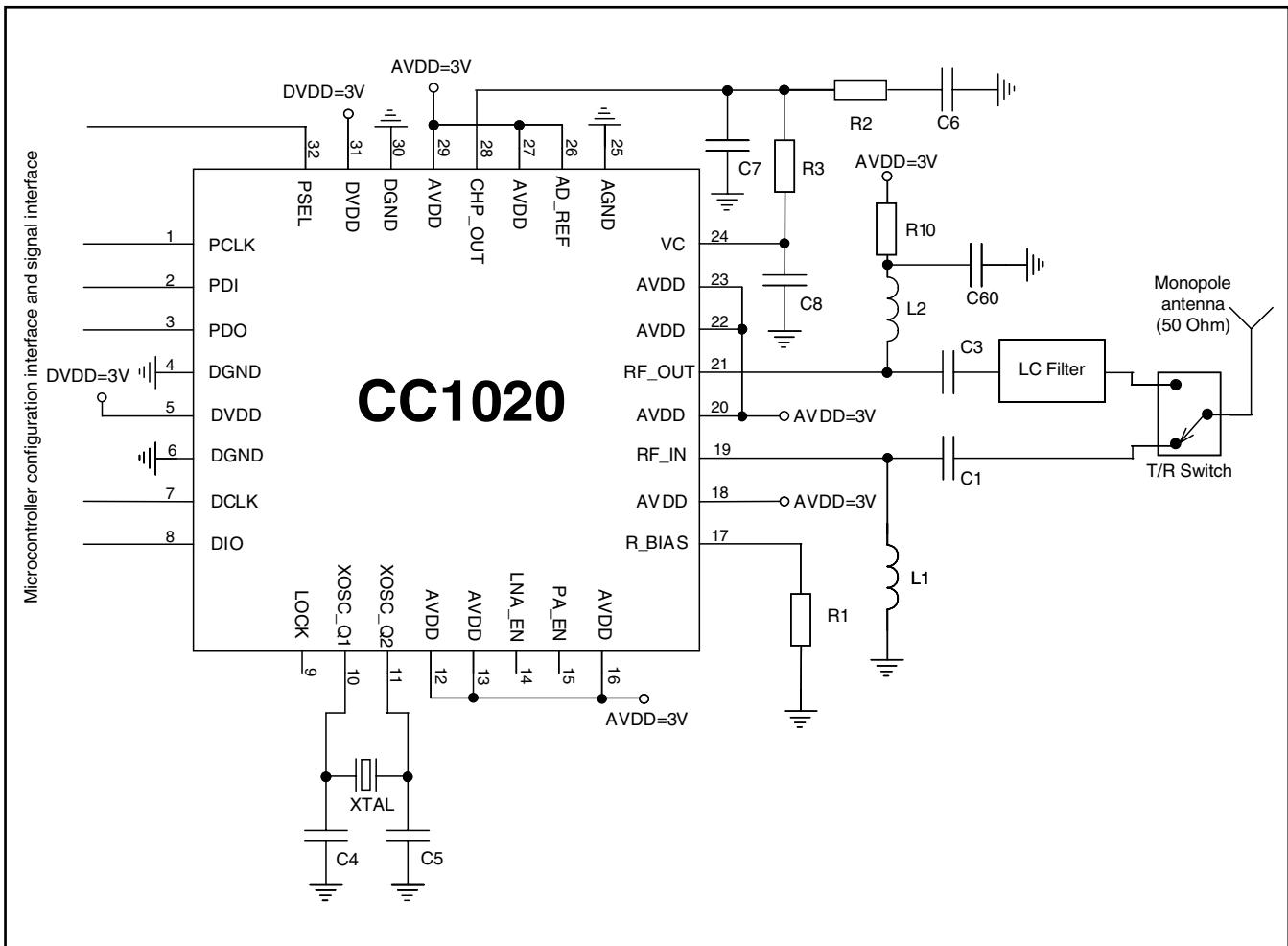

表3から表10にCC1020の電気的仕様を示します。測定はすべて、2層PCBのCC1020EMXリファレンス・デザインを使用して行いました。これは図3に示すものと同じ試験回路です。特記なき場合は、温度 = 25°C, 電源電圧 = AVDD = DVDD = 3.0V, 水晶発振周波数 = 14.7456MHzです。

868MHzでの電気的仕様は、902~928MHzの周波数範囲でも適用されます。

## 静電気放電対策

これらのデバイスは、限定的なESD（静電破壊）保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

| パラメータ          | Min  | Max              | 単位       | 条件                                  |

|----------------|------|------------------|----------|-------------------------------------|

| 電源電圧、VDD       | -0.3 | 5.0              | V        | 電源端子はすべて同一の電圧であること。                 |

| 電圧、他のピン        | -0.3 | VDD+0.3, max 5.0 | V        |                                     |

| RF入力レベル        |      | 10               | dBm      |                                     |

| 保存温度範囲         | -50  | 150              | °C       |                                     |

| パッケージ温度        |      | 260              | °C       | IPC/JEDEC J-STD_020C <sup>(1)</sup> |

| 保存湿度、結露しないこと   | 5    | 85               | %        |                                     |

| ESD<br>(人体モデル) |      | ±1<br>±0.4       | kV<br>kV | RFパッドを除く<br>RFパッド                   |

注：(1) 半田リフローのピーク温度(パッケージ本体温度)は、「IPC/JEDEC J-STD\_020C Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices」に基づき規定されています。

表 1. 絶対最大定格

| パラメータ    | Min        | Typ | Max        | 単位         | 条件/注                                                                                                |

|----------|------------|-----|------------|------------|-----------------------------------------------------------------------------------------------------|

| RF周波数レンジ | 402<br>804 |     | 470<br>940 | MHz<br>MHz | < 300Hzステップ・プログラマブル<br>< 600Hzステップ・プログラマブル                                                          |

| 推奨動作温度範囲 | -40        |     | 85         | °C         |                                                                                                     |

| 電源電圧     | 2.3        | 3.0 | 3.6        | V          | デジタル(DVDD)とアナログ(AVDD)の電源には、同一の電圧値を使用します。<br>ARIB STD T-67の選択度および出力電力許容条件を満たすため、3.0±0.1Vの電源電圧を推奨します。 |

表 2. 動作条件

## 4.1. RF送信部

| パラメータ                | Min    | Typ | Max        | 単位         | 条件/注                                                                                                                                                      |

|----------------------|--------|-----|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 送信データ・レート            | 0.45   |     | 153.6      | kBaud      | データレートはプログラマブルです。詳細は10節を参照。<br>NRZやマンチェスター符号化方式を使用できます。153.6kbpsは、NRZ方式では153.6kbpsに、マンチェスター符号化方式では76.8kbpsに相当します。詳細は9.2節を参照。<br>OOKの最小データ・レートは2.4 kbpsです。 |

| バイナリFSK間隔            | 0<br>0 |     | 108<br>216 | kHz<br>kHz | 402~470MHzの範囲。<br>804~940MHzの範囲。<br>108/216kHzは1.84MHz基準周波数時の保証最大間隔です。基準周波数を高くすると、周波数間隔を広くできます。                                                           |

| 出力                   |        |     |            |            | 50Ω不平衡負荷のとき。                                                                                                                                              |

| 433 MHz              |        |     | -20 ~ +10  | dBm        |                                                                                                                                                           |

| 868 MHz              |        |     | -20 ~ +5   | dBm        | 出力電力はプログラマブルであり、いかなる条件下でも433/868MHz時で+10dBm/+5dBmを超えるプログラミングをしてはなりません(CC1020エラーテ・ノート003参照)。詳細は14節を参照。                                                     |

| 出力許容誤差               |        |     | -4<br>+3   | dB<br>dB   | 最大出力電力時<br>2.3V, +85°Cにて。<br>3.6V, -40°Cにて。                                                                                                               |

| 高調波、CW輻射             |        |     |            |            |                                                                                                                                                           |

| 第2高調波, 433MHz,+10dBm |        |     | -50        | dBc        | 高調波はEN 300 200により等価等方輻射電力(EIRP)値で測定。アンテナ(RW Badland社製SMAFF433とSMAFF868)は、高調波を減衰します。                                                                       |

| 第3高調波, 433MHz,+10dBm |        |     | -50        | dBc        |                                                                                                                                                           |

| 第2高調波, 868MHz,+5dBm  |        |     | -50        | dBc        |                                                                                                                                                           |

| 第3高調波, 868MHz,+5dBm  |        |     | -50        | dBc        |                                                                                                                                                           |

| 隣接チャネル漏洩電力(GFSK)     |        |     |            |            |                                                                                                                                                           |

| 433MHz、12.5kHz間隔     |        |     | -46        | dBc        | 12.5kHzチャネル間隔の隣接チャネル漏洩電力(ACP)は、±4.25kHz帯域幅および±12.5kHzオフセットで測定。<br>変調: 2.4kBaud、NRZ PN9シーケンス、±2.025kHz周波数偏差。                                               |

| 433MHz、25kHz間隔       |        |     | -52        | dBc        |                                                                                                                                                           |

| 868MHz、25kHz間隔       |        |     | -49        | dBc        | 25kHzチャネル間隔のACPは、±8.5kHz帯域幅および±25kHzオフセットで測定。<br>変調: 4.8kBaud、NRZ PN9シーケンス、±2.475kHz周波数偏差。                                                                |

| パラメータ                                 | Min | Typ      | Max | 単位  | 条件/注                                                                                                                                                                                         |

|---------------------------------------|-----|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 占有帯域幅(99.5%,GFSK)                     |     |          |     |     | 全体平均電力の99.5%の帯域幅。                                                                                                                                                                            |

| 433MHz、12.5kHz間隔                      |     | 7.5      |     | kHz | 12.5kHzチャネル間隔の変調：2.4kBaud、NRZ PN9シーケンス、±2.025kHz周波数偏差。                                                                                                                                       |

| 433MHz、25kHz間隔                        |     | 9.6      |     | kHz | 25kHzチャネル間隔の変調：4.8kBaud、NRZ PN9シーケンス、±2.475kHz周波数偏差。                                                                                                                                         |

| 868MHz、25kHz間隔                        |     | 9.6      |     | kHz | 25kHzチャネル間隔の変調：4.8kBaud、NRZ PN9シーケンス、±2.475kHz周波数偏差。                                                                                                                                         |

| 変調帯域幅、868MHz                          |     | 48       |     | kHz | 変調の電力エンベロープが36dBm時の帯域幅。スペクトラム・アナライザのRBW =1kHz。                                                                                                                                               |

| 19.2bps、±9.9kHz周波数偏移                  |     | 106      |     | kHz |                                                                                                                                                                                              |

| 39.4bps、±19.8kHz周波数偏移                 |     |          |     |     |                                                                                                                                                                                              |

| スプリアス、CW輻射                            |     |          |     |     | 最大出力+10/+5dBm、433/868MHz時。                                                                                                                                                                   |

| 47-74,87.5-118,<br>174-230,470-862MHz |     |          |     | dBm | EN 300 220, FCC CFR47パート15およびARIB STD T-67に準拠するために、外付け(アンテナ)フィルタを図25のアプリケーション回路のように使用し、個々の設計を調整して帯域外スプリアス発射レベルを低減する必要があります。                                                                  |

| 9kHz ~ 1GHz                           |     |          | -54 | dBm |                                                                                                                                                                                              |

| 1 ~ 4GHz                              |     |          | -36 | dBm |                                                                                                                                                                                              |

|                                       |     |          | -30 | dBm | スプリアス発射はEN 300 200によりEIRP値で測定できます。アンテナ(RW Badland社製SMAFF433とSMAFF868)は、スプリアス発射高調波を減衰する役割をします。                                                                                                |

|                                       |     |          |     |     | 外部PAを使用して出力電力が増加する場合、ヨーロッパにおける周波数帯域868MHzの動作では、フィルタを使用して862MHzを下回るスペクトルを減衰させる必要があります。アプリケーションノートの『AN036 CC1020/1021スプリアス発射』では、REF_DIVを1から7に増加して、862MHzに近いTXモードのスプリアス発射を減衰するソリューションが議論されています。 |

| 最適負荷インピーダンス                           |     |          |     |     | 送信モード。整合の詳細については14節を参照。                                                                                                                                                                      |

| 433MHz                                |     | 54 + j44 |     | Ω   |                                                                                                                                                                                              |

| 868MHz                                |     | 15 + j24 |     | Ω   |                                                                                                                                                                                              |

| 915MHz                                |     | 20 + j35 |     | Ω   |                                                                                                                                                                                              |

表3. RF送信パラメータ

## 4.2. RF受信部

| パラメータ                                                        | Min | Typ                                        | Max | 単位                                         | 条件/注                                                                                                                                                        |

|--------------------------------------------------------------|-----|--------------------------------------------|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 受信感度、433MHz、FSK<br><br>12.5kHzチャネル間隔、選択度最適化、周波数偏移±2.025kHz   |     | -114                                       |     | dBm                                        | 感度はBER = 10 <sup>-3</sup> のPN9シーケンスで測定。<br><br>12.5kHzチャネル間隔：2.4kBaud、マンチェスター符号データ。                                                                         |

| 12.5kHzチャネル間隔、選択度最適化、周波数偏移±2.025kHz                          |     | -118                                       |     | dBm                                        |                                                                                                                                                             |

| 25kHzチャネル間隔                                                  |     | -112                                       |     | dBm                                        | 25kHzチャネル間隔：4.8kBaud、NRZ符号データ、±2.475kHz周波数偏差                                                                                                                |

| 500kHzチャネル間隔                                                 |     | -96                                        |     | dBm                                        | 500kHzチャネル間隔：153.6kBaud、NRZ符号データ、±72kHz周波数偏差                                                                                                                |

| 受信感度、868MHz、FSK<br><br>12.5kHzチャネル間隔、選択度最適化、周波数偏移±2.475kHz   |     | -116                                       |     | dBm                                        | その他のデータ・レートにおける標準的な感度の値は、表19および表20を参照。                                                                                                                      |

| 25kHzチャネル間隔                                                  |     | -111                                       |     | dBm                                        |                                                                                                                                                             |

| 500kHzチャネル間隔                                                 |     | -94                                        |     | dBm                                        |                                                                                                                                                             |

| 受信感度、433MHz、OOK<br><br>2.4kBaud<br>153.6kBaud                |     | -116<br>-81                                |     | dBm<br>dBm                                 | 感度はBER = 10 <sup>-3</sup> のPN9シーケンスで測定。<br><br>マンチェスター符号データ。                                                                                                |

| 受信感度、868MHz、OOK<br><br>2.4kBaud<br>153.6kBaud                |     | -107<br>-87                                |     | dBm<br>dBm                                 | その他のデータ・レートにおける標準的な感度の値は、表27を参照。                                                                                                                            |

| 飽和レベル(最大入力レベル)<br>FSK、OOK                                    |     | 10                                         |     | dBm                                        | FSK：マンチェスター/NRZ符号データ<br>OOK：マンチェスター符号データ。<br>BER = 10 <sup>-3</sup> 。                                                                                       |

| システム雑音帯域幅                                                    |     | 9.6<br>to<br>307.2                         |     | kHz                                        | レシーバ・チャネル・フィルタの6dB帯域幅は、9.6kHzから307.2kHzでプログラマブルです。詳細は12.2節を参照。                                                                                              |

| 総合雑音指数、カスケード接続<br>433 and 868MHz                             |     | 7                                          |     | dB                                         | NRZ符号データ                                                                                                                                                    |

| 三次インターフェト・ポイント<br><br>433MHz、12.5kHz間隔<br><br>868MHz、25kHz間隔 |     | -23<br>-18<br>-16<br><br>-18<br>-15<br>-13 |     | dBm<br>dBm<br>dBm<br><br>dBm<br>dBm<br>dBm | ツー・トーン試験(+10MHz/+20MHz)<br><br>LNA2 maximum gain<br>LNA2 medium gain<br>LNA2 minimum gain<br><br>LNA2 maximum gain<br>LNA2 medium gain<br>LNA2 minimum gain |

| パラメータ                                                                               | Min | Typ                              | Max | 単位                   | 条件/注                                                                                                                              |

|-------------------------------------------------------------------------------------|-----|----------------------------------|-----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 共通チャネル除去、FSK、OOK<br>433MHz、12.5kHz間隔<br>433MHz、25kHz間隔<br>868MHz、25kHz間隔            |     | -11                              |     | dB                   | 感知レベルより3dB高い信号、動作周波数でのFM妨害波(1kHz正弦波、±2.5kHz周波数偏差)、BER = 10 <sup>-3</sup>                                                          |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

| 隣接チャネル除去(ACR)<br>433MHz、12.5kHz間隔<br>433MHz、25kHz間隔<br>868MHz、25kHz間隔               |     | 32                               |     | dB                   | 感知レベルより3dB高い信号、隣接チャネルでのFM妨害波(1kHz正弦波、±2.5kHz周波数偏差)、BER = 10 <sup>-3</sup>                                                         |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

| 干渉波チャネル除去<br>433/868MHz<br>I/Q ゲイン/位相キャリブレーション無し<br>I/Q ゲイン/位相キャリブレーション有り           |     | 26/31                            |     | dB                   | 感知レベルより3dB高い信号、干渉波周波数でのCW妨害波(1kHz正弦波、±2.5kHz周波数偏差)、BER = 10 <sup>-3</sup>                                                         |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

| 選択性*<br>433MHz、12.5kHz間隔<br>433MHz、25kHz間隔<br>868MHz、25kHz間隔<br>(*隣接スプリアス応答除去)      |     | 41                               |     | dB                   | 感知レベルより3dB高い信号。CW妨害波が12.5kHz/25kHzのステップで±1MHzまで所要のチャネルからスイープされ、BER = 10 <sup>-3</sup> 。隣接チャネルと干渉波チャネルは除外。                         |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

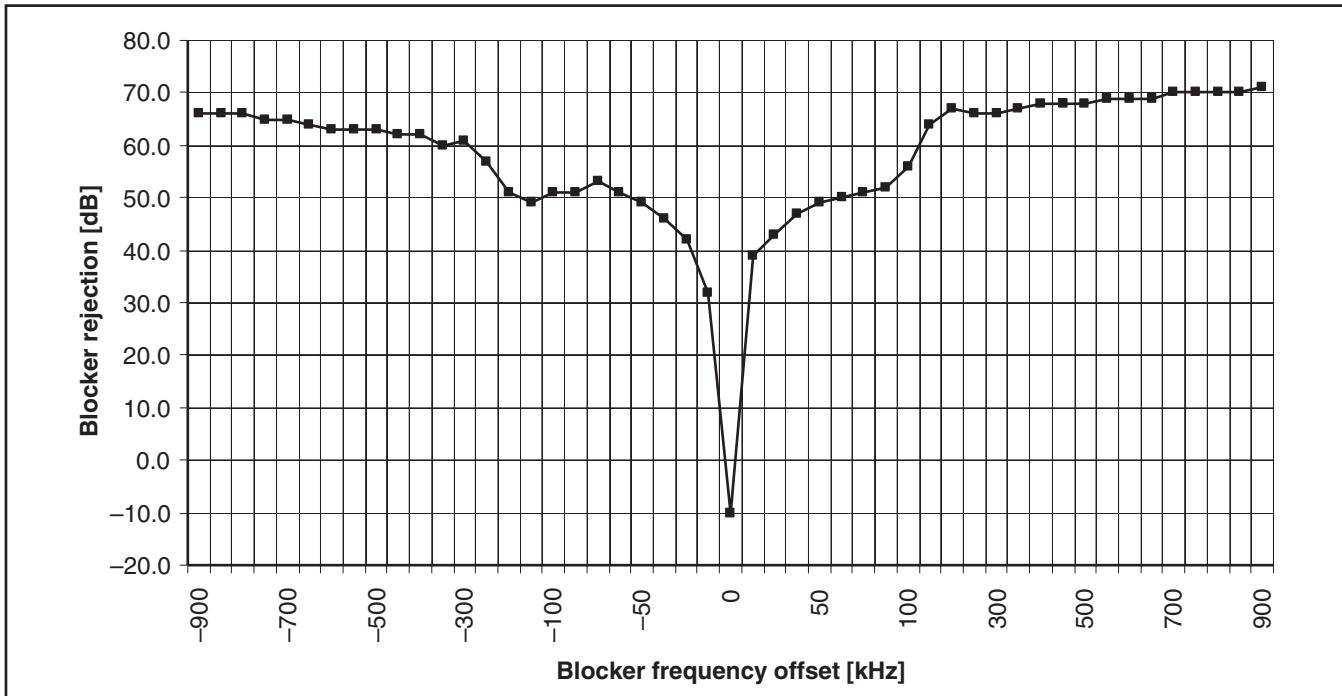

| ブロッキング/感度抑圧*<br>433/868 MHz<br>±1MHz<br>±2MHz<br>±5MHz<br>±10MHz<br>(*帯域外スプリアス応答除去) |     | 50/57<br>64/71<br>64/71<br>75/78 |     | dB<br>dB<br>dB<br>dB | 感知レベルより3dB高い信号。±1,2,5および10MHzオフセットのCW妨害波。BER = 10 <sup>-3</sup> 、433/868MHzで12.5kHz/25kHzのチャネル間隔。<br><br>EN 300 220の2分類レシーバ条件に準拠。 |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

| 干渉波周波数抑圧<br>433/868 MHz<br>I/Q ゲイン/位相キャリブレーション無し<br>I/Q ゲイン/位相キャリブレーション有り           |     | 36/41                            |     | dB                   | 干渉波周波数での信号の感度と、所要チャネルにおける感度との比。干渉波周波数はRF_21F。信号源は2.4kbps、マンチェスター符号データ、±2.025kHz周波数偏差、BER = 10 <sup>-3</sup> の信号レベル。               |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

|                                                                                     |     |                                  |     |                      |                                                                                                                                   |

| スプリアス受信                                                                             |     |                                  | 40  | dB                   | 不要周波数の感度と、所要チャネルにおける感度との比。信号源は2.4kbps、マンチェスター符号データ、±2.025kHz周波数偏差、100MHz～2GHzの周波数範囲でスイープ、BER = 10 <sup>-3</sup> の信号レベル。           |

| パラメータ                                           | Min | Typ                  | Max  | 単位                   | 条件/注                                                                                  |

|-------------------------------------------------|-----|----------------------|------|----------------------|---------------------------------------------------------------------------------------|

| 相互変調除去(1)<br>433MHz、12.5kHz間隔<br>868MHz、25kHz間隔 |     | 30<br>30             |      | dB<br>dB             | 感知レベルより3dB高い信号。+2Chと+4Chの2つのCW妨害波。ここで、Chは12.5kHzあるいは25kHzのチャネル間隔。<br>BER = $10^{-2}$  |

| 相互変調除去(2)<br>433MHz、12.5kHz間隔<br>868MHz、25kHz間隔 |     | 56<br>55             |      | dB<br>dB             |                                                                                       |

| LO漏洩電力、433/868MHz                               |     | <-80/-66             |      | dBm                  |                                                                                       |

| VCO漏洩電力                                         |     | -64                  |      | dBm                  | VCO周波数は1608~1880MHzの範囲。                                                               |

| スプリアス、CW輻射<br>9kHz~1GHz<br>1~4GHz               |     | <-60<br><-60         |      | dBm<br>dBm           | EN 300 220, FCC CFR47パート15およびARIB STD T-67に準拠。<br>スプリアスは、EN 300 220によるEIRP値として測定できます。 |

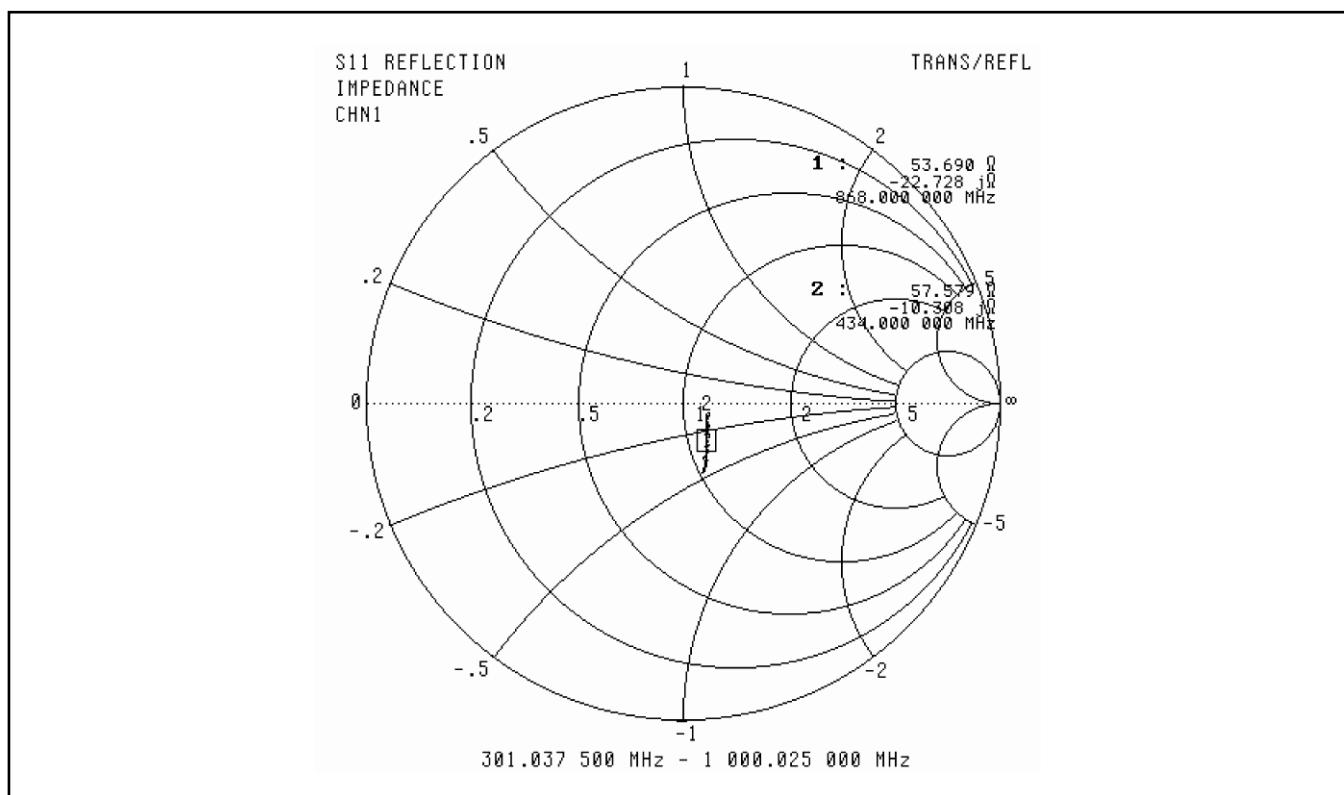

| 入力インピーダンス<br>433MHz<br>868MHz                   |     | 58 + j10<br>54 + j22 |      | $\Omega$<br>$\Omega$ | 受信モード。詳細は14節を参照。                                                                      |

| 入力インピーダンス整合、S11パラメータ<br>433MHz<br>868MHz        |     | -14<br>-12           |      | dB<br>dB             | アプリケーション回路の整合回路網を使用。詳細は14節を参照。                                                        |

| 入力インピーダンス整合<br>433MHz<br>868MHz                 |     | 39 + j14<br>32 + j10 |      | $\Omega$<br>$\Omega$ | アプリケーション回路の整合回路網を使用。詳細は14節を参照。                                                        |

| ビット同期オフセット                                      |     |                      | 8000 | ppm                  | 最大ビット・レート・オフセット。ビット同期回路により6dBの低下を許容。同期モードのみ。                                          |

| データ・レイテンシ<br>NRZモード<br>マンチェスター・モード              |     | 4<br>8               |      | Baud<br>Baud         | データがトランスマッタのDIO端子に入力されてから、レシーバのDIO端子に出力されるまでの時間。                                      |

表4. RF受信パラメータ

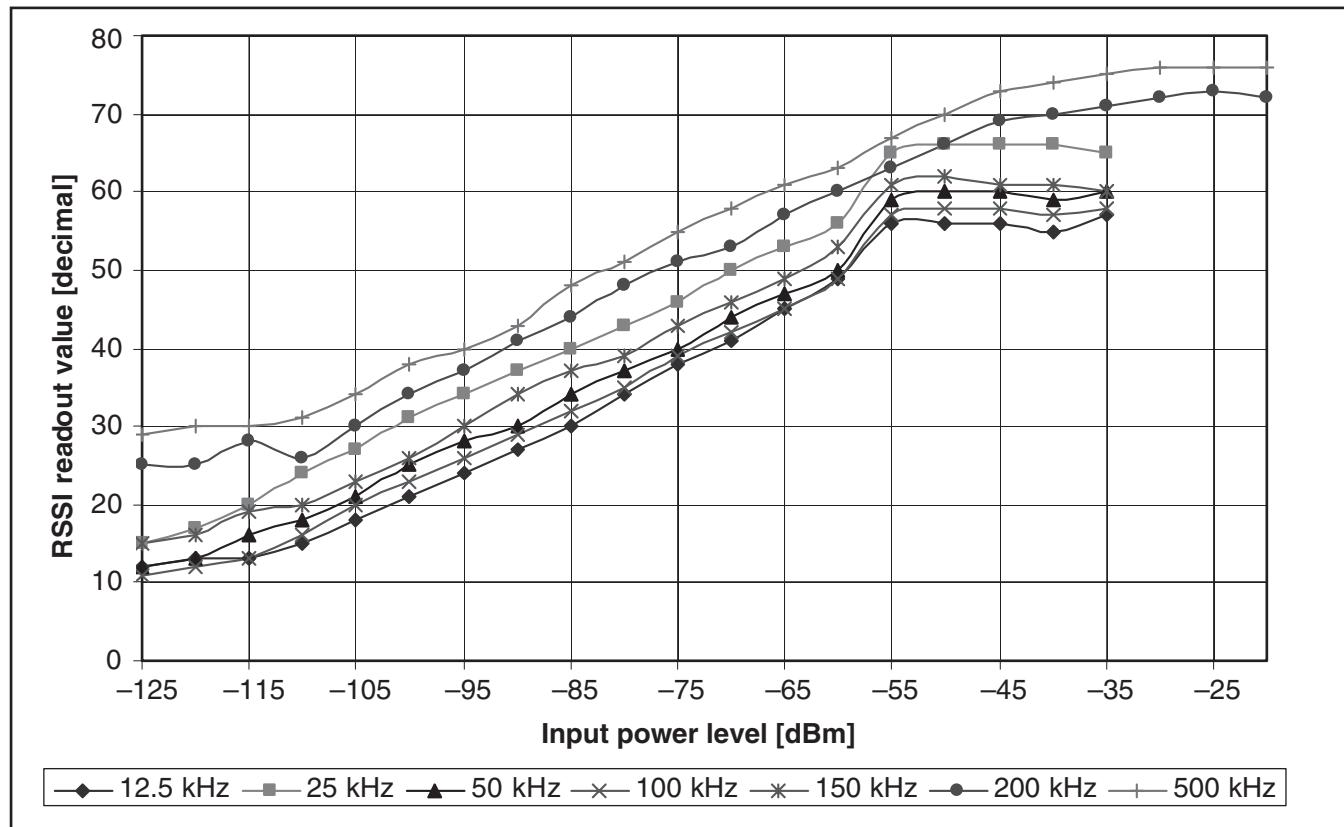

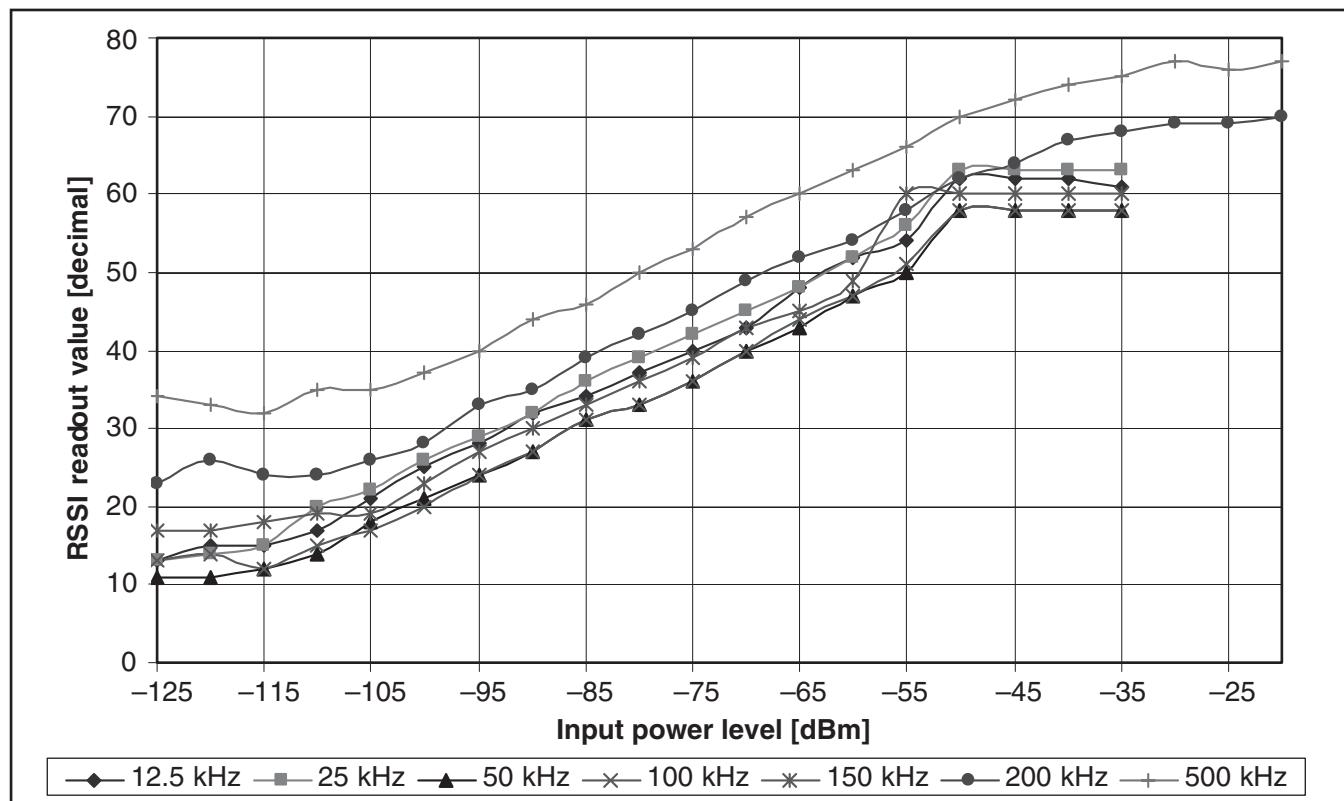

#### 4.3. RSSI/キャリア検知部

| パラメータ                              | Min | Typ     | Max | 単位      | 条件/注                                                       |

|------------------------------------|-----|---------|-----|---------|------------------------------------------------------------|

| RSSI ダイナミック・レンジ                    |     | 55      |     | dB      | チャネル間隔12.5/25kHz。                                          |

| RSSI 精度                            |     | $\pm 3$ |     | dB      | 詳細は12.5節を参照。                                               |

| RSSI リニアリティ                        |     | $\pm 1$ |     | dB      |                                                            |

| RSSI安定時間<br>2.4kBaud、12.5kHzチャネル間隔 |     | 3.8     |     | ms      | RSSI安定時間が短いと、トレードオフでRSSI精度が低下します。詳細は12.5節を参照。              |

| 4.8kBaud、25kHzチャネル間隔               |     | 1.9     |     | ms      | また、RSSI安定時間が短いとレシーバ・チャネル・フィルタ帯域幅が増加し、トレードオフで感度と選択度が低下します。  |

| 153.6kBaud、500kHzチャネル間隔            |     | 140     |     | $\mu s$ |                                                            |

| キャリア検知 プログラマブル範囲                   |     | 40      |     | dB      | 精度はRSSIと同様。                                                |

| 隣接チャネル・キャリア<br>12.5kHzチャネル間隔       |     | -72     |     | dBm     | キャリア検知レベルー110dBm、隣接チャネルにFM妨害波(1kHz正弦波、 $\pm 2.5$ kHz偏差)。   |

| 25kHzチャネル間隔                        |     | -72     |     | dBm     | 隣接チャネル・キャリア検知は、隣接チャネルに信号を印加し、キャリア検知レベルが表示されるチャネルを観察して測定する。 |

| スプリアス・キャリア 検知                      |     | -70     |     | dBm     | キャリア検知レベルー110dBm、100MHz～2GHz。隣接チャネルとイメージ・チャネルは除外。          |

表 5. RSSI/キャリア検知パラメータ

#### 4.4. IF部

| パラメータ             | Min | Typ                | Max | 単位  | 条件/注                                                    |

|-------------------|-----|--------------------|-----|-----|---------------------------------------------------------|

| IF周波数             |     | 307.2              |     | kHz | 詳細は12.1節参照。                                             |

| デジタル・チャネル・フィルタ帯域幅 |     | 9.6<br>to<br>307.2 |     | kHz | 6dB帯域幅のチャネル・フィルタは、9.6kHz～307.2kHzでプログラマブルです。詳細は12.2節参照。 |

| AFC分解能            |     | 150                |     | Hz  | 2.4kbpsのとき。<br>ビット・レートkbps/16で与えられます。詳細は12.13節参照。       |

表 6. IF部パラメータ

## 4.5. 水晶発振器部

| パラメータ                   | Min            | Typ                                         | Max            | 単位                               | 条件/注                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|----------------|---------------------------------------------|----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 水晶発振周波数                 | 4.9152         | 14.7456                                     | 19.6608        | MHz                              | 推奨周波数14.7456MHz。<br>詳細は19節参照。                                                                                                                                                                                                                                                                                                                                          |

| 必要基準周波数精度               |                | +/-5.7<br>+/-2.8<br><br>+/-4                |                | ppm<br>ppm<br><br>ppm            | 433MHz (EN 300 220)<br>868MHz (EN 300 220)<br>433/868MHzにて25kHzチャネル間隔で<br>EN 300 220に準拠するには、 $\pm 5.7 \pm 2.8$ ppm<br>より小であることが必要です。<br><br>日本の12.5kHzチャネル間隔規則 (ARIB<br>STD T-67) に準拠するには、 $\pm 4$ ppmより<br>小であることが必要です。<br><br>注記：<br>基準周波数精度(初期許容)およびドリフト(エイジングと温度に依存)により、送信周波数精度が定まります。<br><br>水晶発振器の温度補償は、微小ステップ<br>のPLL周波数のプログラミングおよびAFC<br>機能で行われます。詳細は12.13節参照。 |

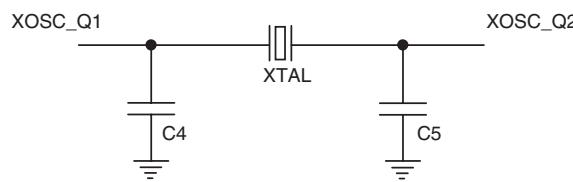

| 水晶振動子使用法                |                | 並列共振                                        |                |                                  | C4とC5は負荷容量です。<br>詳細は19節参照。                                                                                                                                                                                                                                                                                                                                             |

| 水晶振動子負荷容量               | 12<br>12<br>12 | 22<br>16<br>16                              | 30<br>30<br>16 | pF<br>pF<br>pF                   | 4.9~6MHz、22pF推奨<br>6~8MHz、16pF推奨<br>8~19.6MHz、16pF推奨                                                                                                                                                                                                                                                                                                                   |

| 水晶発振器スタートアップ時間          |                | 1.55<br>1.0<br>0.90<br>0.95<br>0.60<br>0.63 |                | ms<br>ms<br>ms<br>ms<br>ms<br>ms | 4.9152MHz、12pF負荷<br>7.3728MHz、12pF負荷<br>9.8304MHz、12pF負荷<br>14.7456MHz、16pF負荷<br>17.2032MHz、12pF負荷<br>19.6608MHz、12pF負荷                                                                                                                                                                                                                                                |

| 外部クロック信号、<br>正弦波        |                | 300                                         |                | mVpp                             | 外部クロック信号は、DCカットコンデンサ (10nF) を用いてXOSC_Q1に接続します。<br>低振幅や水晶を外部クロック信号に使用する場合、INTERFACEレジスタの<br>XOSC_BYPASS = 0に設定します。                                                                                                                                                                                                                                                      |

| 外部クロック信号、<br>デジタル外部クロック |                | 0 ~ VDD                                     |                | V                                | 外部クロック信号はXOSC_Q1に接続します。<br>DCカットコンデンサは使用しません。全振幅デジタル外部クロックを使用する場合、INTERFACEレジスタの<br>XOSC_BYPASS = 1に設定します。                                                                                                                                                                                                                                                             |

表 7. IF部パラメータ

## 4.6. 周波数シンセサイザ部

| パラメータ                                                                                                  | Min | Typ                                 | Max | 単位             | 条件/注                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------|-----|-------------------------------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 位相ノイズ、402~470MHz<br>12.5kHzチャネル間隔                                                                      |     | -90<br>-100<br>-105<br>-110<br>-114 |     | dBc/Hz         | 無変調キャリア<br>キャリアから<br>12.5kHzでのオフセット<br>25kHzでのオフセット<br>50kHzでのオフセット<br>100kHzでのオフセット<br>1MHzでのオフセット<br><br>表13のループ・フィルタ部品を使用して測定。PLLループ・フィルタの帯域幅が大きいほど、位相ノイズは大きくなります。 |

| 位相ノイズ、804~940MHz<br>25kHzチャネル間隔                                                                        |     | -85<br>-95<br>-101<br>-109<br>-118  |     | dBc/Hz         | 無変調キャリア<br>キャリアから<br>12.5kHzでのオフセット<br>25kHzでのオフセット<br>50kHzでのオフセット<br>100kHzでのオフセット<br>1MHzでのオフセット<br><br>表13のループ・フィルタ部品を使用して測定。PLLループ・フィルタの帯域が大きいほど、位相ノイズは大きくなります。  |

| PLLループ帯域幅<br>433MHz 12.5kHzチャネル間隔<br>868MHz 25kHzチャネル間隔                                                |     | 2.7                                 |     | kHz            | PLLおよびVCOのキャリブレーション後。<br>PLLループ帯域幅はプログラマブルです。                                                                                                                         |

| PLLロック時間(RX/TX切替時間)<br>433MHz 12.5kHzチャネル間隔<br>868MHz 25kHzチャネル間隔<br>500kHzチャネル間隔                      |     | 900<br>640<br>14                    |     | us             | チャネル間隔の±10%以内のRF周波数まで307.2kHzの周波数ステップ。ループ・フィルタ部品定数およびPLL_BWレジスタの設定に依存します。詳細は表26参照。                                                                                    |

| PLLターンオン時間。パワーダウン・モードで水晶発信器が発振した状態からの時間。<br>433MHz 12.5kHzチャネル間隔<br>868MHz 25kHzチャネル間隔<br>500kHzチャネル間隔 |     | 3.2<br>2.5<br>700                   |     | ms<br>ms<br>us | レジスタ書き込みから、チャネル間隔の±10%以内のRF周波数になるまでの時間。<br>ループ・フィルタ部品定数およびPLL_BWレジスタの設定に依存します。詳細は表25参照。                                                                               |

表8. 周波数シンセサイザのパラメータ

## 4.7. デジタル入出力

| パラメータ                                        | Min         | Typ                                                              | Max         | 単位                                               | 条件/注                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|-------------|------------------------------------------------------------------|-------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ロジック “0” 入力電圧                                | 0           |                                                                  | 0.3*<br>VDD | V                                                |                                                                                                                                                                                                                                                                                            |

| ロジック “1” 入力電圧                                | 0.7*<br>VDD |                                                                  | VDD         | V                                                |                                                                                                                                                                                                                                                                                            |

| ロジック “0” 出力電圧                                | 0           |                                                                  | 0.4         | V                                                | 出力電流=-2.0mA、電源電圧=3.0V                                                                                                                                                                                                                                                                      |

| ロジック “1” 出力電圧                                | 2.5         |                                                                  | VDD         | V                                                | 出力電流=2.0mA、電源電圧=3.0V                                                                                                                                                                                                                                                                       |

| ロジック “0” 入力電流                                | NA          |                                                                  | 1           | μA                                               | 入力信号はGND。<br><br>PSEL端子には内部プルアップ抵抗があり、<br>設定の間の電流は-350μA。                                                                                                                                                                                                                                  |

| ロジック “1” 入力電流                                | NA          |                                                                  | 1           | μA                                               | 入力信号はVDD。                                                                                                                                                                                                                                                                                  |

| DIOセットアップ・タイム                                | 20          |                                                                  |             | ns                                               | TXモード。DCLKの立ち上りエッジの前<br>に必要なDIOの最小時間。データはDCLK<br>の立ち下りエッジでセットします。                                                                                                                                                                                                                          |

| DIOホールド・タイム                                  | 10          |                                                                  |             | ns                                               | TXモード。DCLKの立ち上りエッジの後<br>に必要なDIOの最小時間。データはDCLK<br>の立ち下りエッジでセットします。                                                                                                                                                                                                                          |

| シリアル・インターフェイス<br>(PCLK,PDI,PDO,PSEL) タイミング仕様 |             |                                                                  |             |                                                  | 詳細は表14を参照。                                                                                                                                                                                                                                                                                 |

| ピンドライブ、LNA_EN、PA_EN                          |             | 0.90<br>0.87<br>0.81<br>0.69<br><br>0.93<br>0.92<br>0.89<br>0.79 |             | mA<br>mA<br>mA<br>mA<br><br>mA<br>mA<br>mA<br>mA | ソース電流<br>0 V on LNA_EN, PA_EN pins<br>0.5 V on LNA_EN, PA_EN pins<br>1.0 V on LNA_EN, PA_EN pins<br>1.5 V on LNA_EN, PA_EN pins<br><br>シンク電流<br>3.0 V on LNA_EN, PA_EN pins<br>2.5 V on LNA_EN, PA_EN pins<br>2.0 V on LNA_EN, PA_EN pins<br>1.5 V on LNA_EN, PA_EN pins<br><br>詳細は図35を参照。 |

表9. デジタル入出力パラメータ

## 4.8. 消費電流

| パラメータ                   | Min | Typ       | Max | 単位            | 条件/注                  |

|-------------------------|-----|-----------|-----|---------------|-----------------------|

| パワーダウン・モード              |     | 0.2       | 1.8 | $\mu\text{A}$ | 内部発振器オフ。              |

| 消費電流、受信モード、433および868MHz |     | 19.9      |     | mA            |                       |

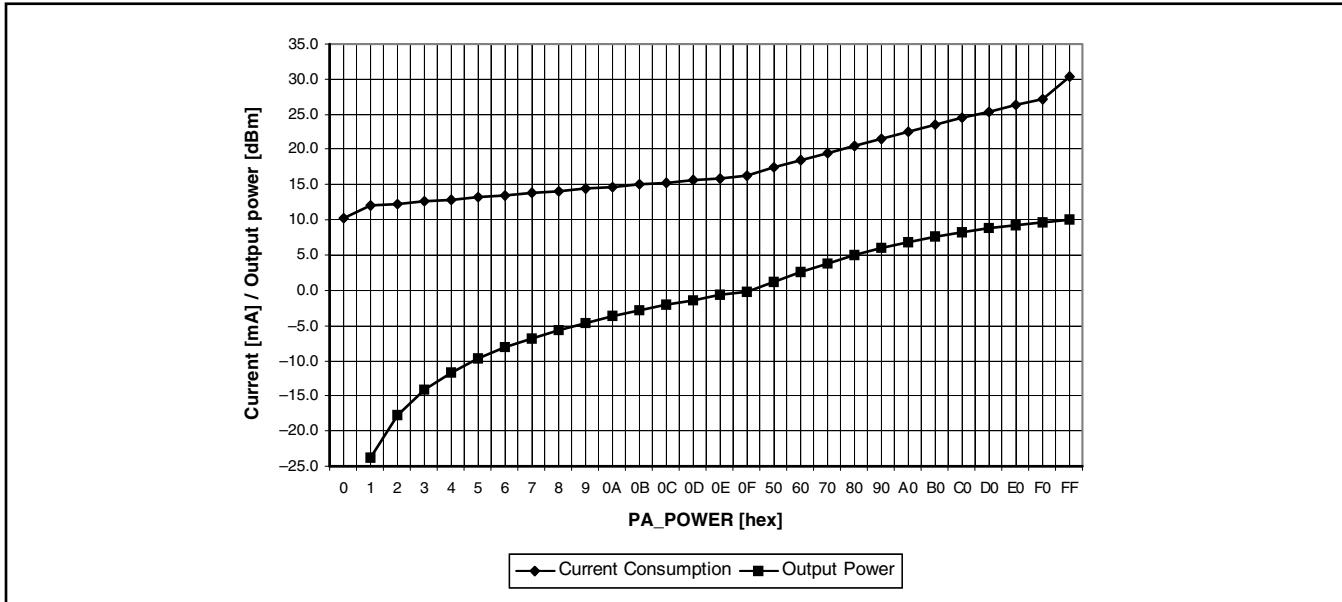

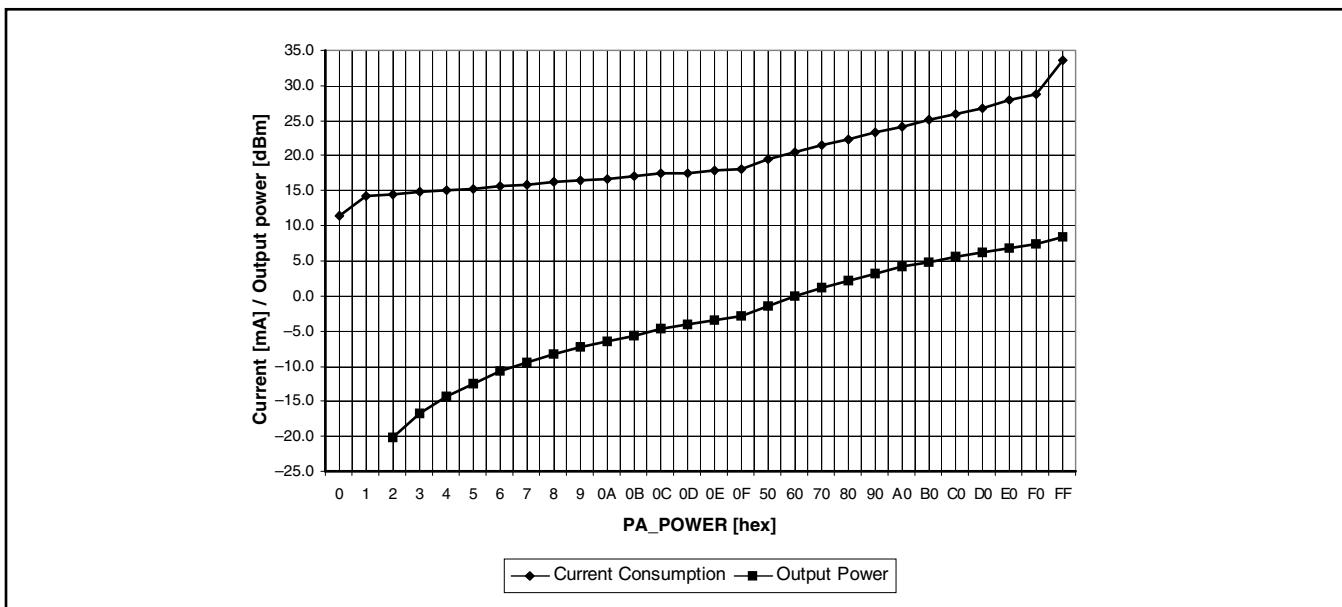

| 消費電流、送信モード、433/868MHz : |     |           |     |               |                       |

| P = -20dBm              |     | 12.3/14.5 |     | mA            | 出力電力は50Ωシングルエンド負荷に供給。 |

| P = -5dBm               |     | 14.4/17.0 |     | mA            |                       |

| P = 0dBm                |     | 16.2/20.5 |     | mA            | 詳細は13.2節を参照。          |

| P = +5dBm               |     | 20.5/25.1 |     | mA            |                       |

| P = +10dBm (433MHzのみ)   |     | 27.1      |     | mA            |                       |

| 消費電流、水晶発振器              |     | 77        |     | $\mu\text{A}$ | 14.7456 MHz、水晶負荷16 pF |

| 消費電流、水晶発振器/バイアス         |     | 500       |     | $\mu\text{A}$ | 14.7456 MHz、水晶負荷16 pF |

| 消費電流、水晶発振器、バイアス/シンセサイザ  |     | 7.5       |     | mA            | 14.7456 MHz、水晶負荷16 pF |

表 10. 消費電流

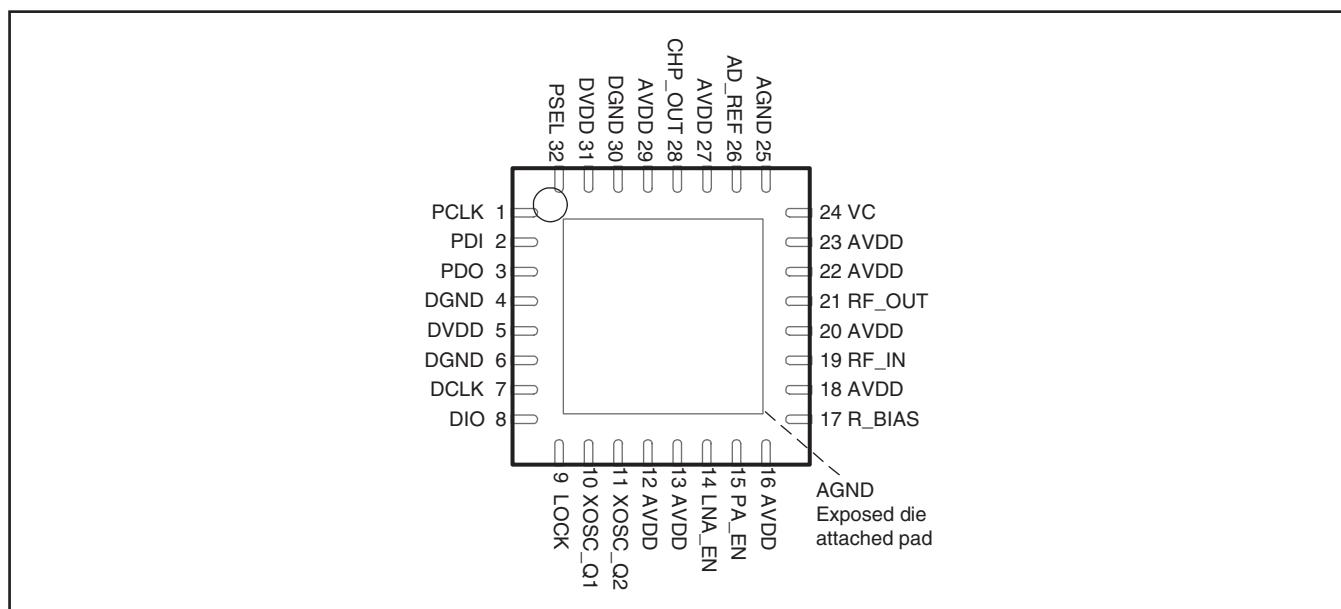

## 5. 端子配置

表11にCC1020の端子の概要を示します。

CC1020はQFN32パッケージ(詳細は27節を参照)で供給しています。

図 1. CC1020パッケージ(トップ・ビュー)

| ピン番号 | ピン名     | ピン・タイプ               | 説明                                                                                  |

|------|---------|----------------------|-------------------------------------------------------------------------------------|

| -    | AGND    | Ground (analog)      | チップに接続する露出パッド。これは全アナログ部のグランドであり、しっかりしたグランド面に半田付けする必要があります。                          |

| 1    | PCLK    | Digital input        | SPI設定インターフェイスのプログラミング・クロック。                                                         |

| 2    | PDI     | Digital input        | SPI設定インターフェイスのプログラミング・データ入力。                                                        |

| 3    | PDO     | Digital output       | SPI設定インターフェイスのプログラミング・データ出力。                                                        |

| 4    | DGND    | Ground (digital)     | デジタル部とデジタルI/O部のグランド(0V)。                                                            |

| 5    | DVDD    | Power (digital)      | デジタル部とデジタルI/O部の電源(標準3V)。                                                            |

| 6    | DGND    | Ground (digital)     | デジタル部(サブストレート)のグランド(0V)。                                                            |

| 7    | DCLK    | Digital output       | 送受信モードのデータ入力用クロック。非同期モードにおいて受信データの出力にも使用できます。                                       |

| 8    | DIO     | Digital input/output | 送信モードのデータ入力および受信モードのデータ出力。<br>受信モードにおけるパワー・アップ・シーケンスの開始にも使用できます。                    |

| 9    | LOCK    | Digital output       | PLLロックを示し、負論理。PLLがロックすると出力します。本端子は、汎用デジタル出力や同期NRZ/マンチェスター・モードにおける受信データ出力としても使用できます。 |

| 10   | XOSC_Q1 | Analog input         | 水晶振動子あるいは外部クロック入力。                                                                  |

| 11   | XOSC_Q2 | Analog output        | 水晶振動子。                                                                              |

| 12   | AVDD    | Power (analog)       | 水晶発振器の電源(標準3V)。                                                                     |

| 13   | AVDD    | Power (analog)       | IF VGAの電源(標準3V)。                                                                    |

| 14   | LNA_EN  | Digital output       | 汎用デジタル出力。高感度が必要な場合の外部LNAの制御に使用できます。                                                 |

| 15   | PA_EN   | Digital output       | 汎用デジタル出力。高出力が必要な場合の外部PAの制御に使用できます。                                                  |

| 16   | AVDD    | Power (analog)       | バイアス発生回路およびアンチ・エイリアシング用フィルタの電源(標準3V)。                                               |

| 17   | R_BIAS  | Analog output        | 外付け高精度バイアス抵抗(82kΩ, ±1%)を接続。                                                         |

| 18   | AVDD    | Power (analog)       | LNA入力段の電源(標準3V)。                                                                    |

| 19   | RF_IN   | RF Input             | アンテナ(外付け、AC結合)からのRF信号入力。                                                            |

| 20   | AVDD    | Power (analog)       | LNAの電源(標準3V)。                                                                       |

| 21   | RF_OUT  | RF output            | アンテナRF信号出力。                                                                         |

| 22   | AVDD    | Power (analog)       | LOパッファ、ミキサ、プリスケーラ、初段PAの電源(標準3V)。                                                    |

| 23   | AVDD    | Power (analog)       | VCOの電源(標準3V)。                                                                       |

| 24   | VC      | Analog input         | 外部ループ・フィルタからのVCO制御電圧入力。                                                             |

| 25   | AGND    | Ground (analog)      | アナログ部(ガード)のグランド(0V)。                                                                |

| 26   | AD_REF  | Power (analog)       | ADCの3V基準電圧入力。                                                                       |

| 27   | AVDD    | Power (analog)       | チャージポンプおよび位相判別器の電源(標準3V)。                                                           |

| 28   | CHP_OUT | Analog output        | 外部ループ・フィルタへのPLLチャージポンプ出力。                                                           |

| 29   | AVDD    | Power (analog)       | ADCの電源(標準3V)。                                                                       |

| 30   | DGND    | Ground (digital)     | デジタル部(ガード)のグランド(0V)。                                                                |

| 31   | DVDD    | Power (digital)      | デジタル部の電源(標準3V)。                                                                     |

| 32   | PSEL    | Digital input        | 設定インターフェイスのプログラミング・チップ・セレクト、負論理。内部プルアップ抵抗あり。                                        |

表 11. 端子配置の概要

#### 注記：

DCLK, DIOおよびLOCKは、パワーダウン時(MAINレジスタのBIAS\_PD = 1)の場合、高インピーダンス(3ステート)です。

チップの露出パッドは、チップの主なグランド接続なので、しっかりしたアナログ面に半田付けする必要があります。

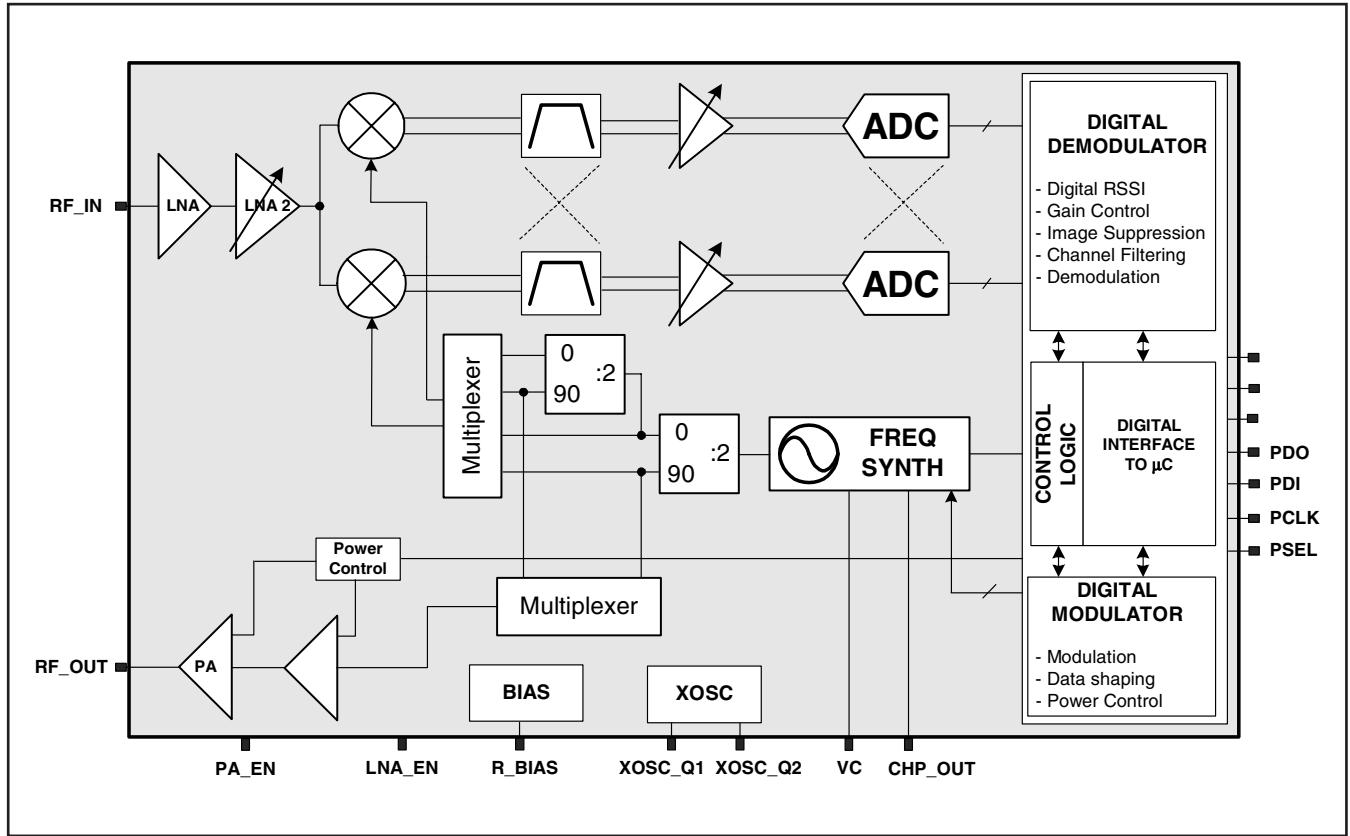

## 6. 回路解説

図2. CC1020の概略ブロック図

CC1020の概略ブロック図を図2に示します。ここでは信号端子のみを示しています。

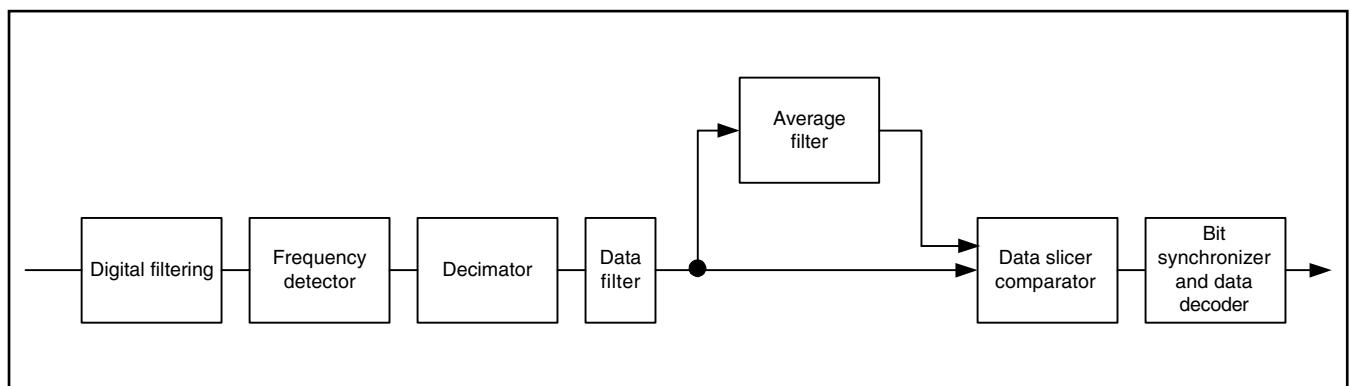

CC1020は低周波数IFレシーバを特長としています。受信されたRF信号は低雑音アンプ(LNA1およびLNA2)で増幅され、中間周波数(IF)へ直交(I/Q)ダウンコンバートされます。IFではI/Q信号が複素フィルタリングおよび増幅され、次にADCでデジタル化されます。自動ゲイン制御、チャネルの微調フィルタリング、復調およびビット同期はデジタルで行われます。CC1020はデジタル復調データをDIO端子に出力します。同期データ・クロックがDCLK端子で得られます。RSSIはデジタル・フォーマットで得られ、シリアル・インターフェイスで読み取ることができます。また、RSSIにはキャリア検知表示としての機能もあります。

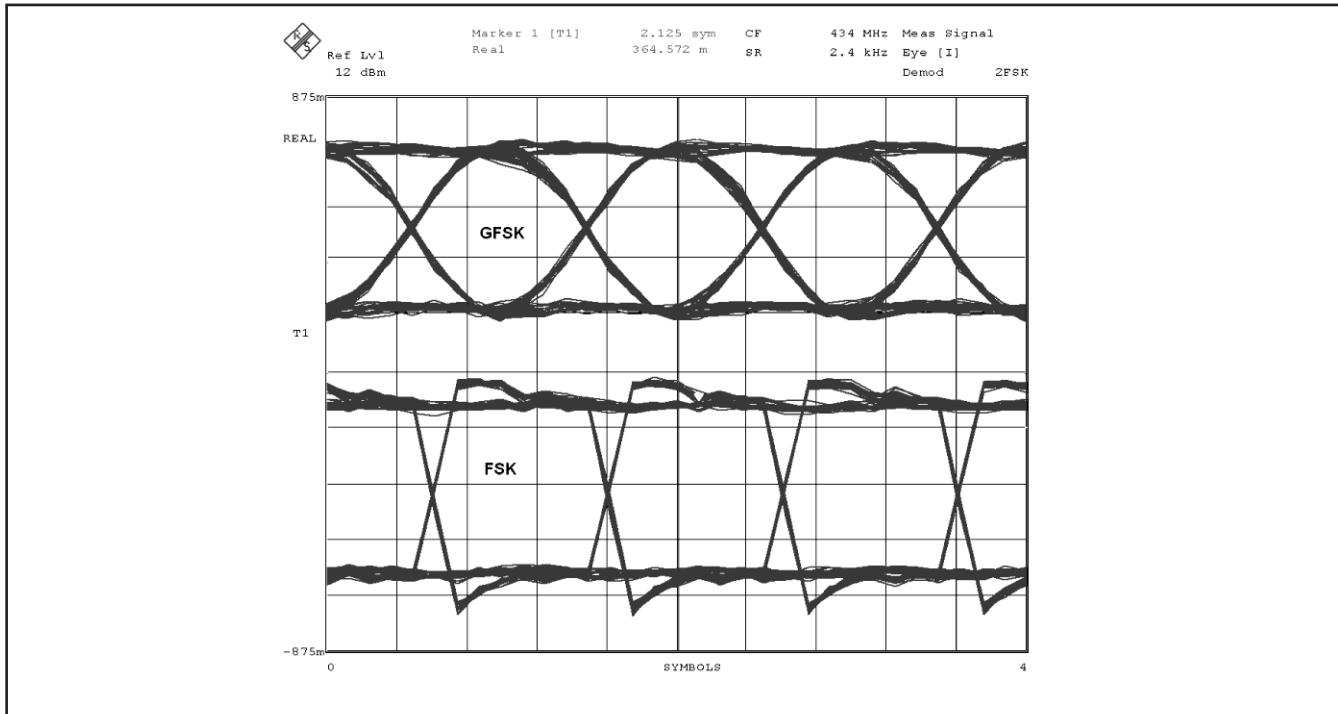

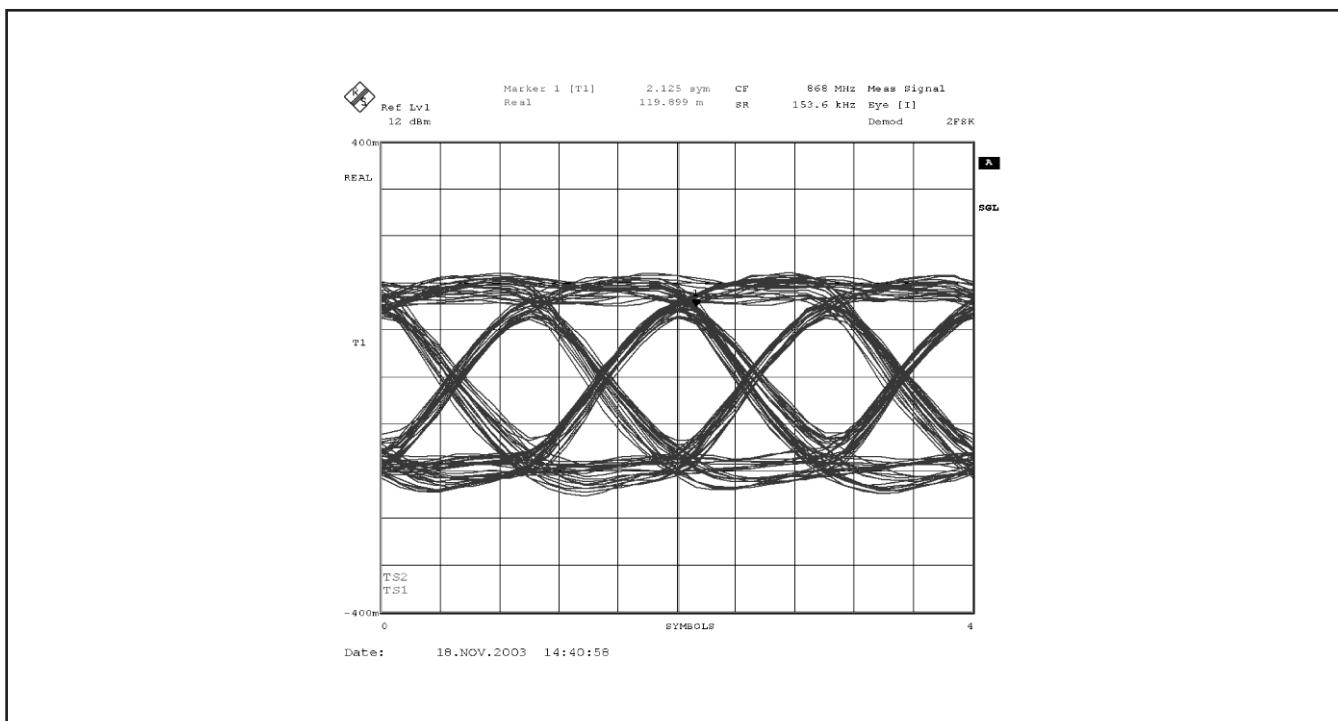

送信モードでは、シンセサイズされたRF周波数がパワーアンプ(PA)に直接供給されます。RF出力は、DIO端子に入力されるデジタルのビット・ストリームでFSK(周波数偏移変調)されます。オプションとして、ガウスFSK(GFSK)を行うガウス・フィルタが使用できます。

周波数シンセサイザには、完全なオン・チップLC VCOおよび90°位相スプリッタがあり、受信モード時にLO\_IおよびLO\_Q信号をダウン・コンバート・ミキサに供給します。VCOは1.608~1.880GHzの周波数範囲で動作します。CHP\_OUT端子はチャージポンプ出力であり、VCは内蔵されたVCOの制御端子です。外部ループ・フィルタは、これらの端子間に接続します。水晶はXOSC\_Q1とXOSC\_Q2の端子間に接続します。PLLからロック信号が得られます。

4線式のSPIシリアル・インターフェイスが設定に使用されます。

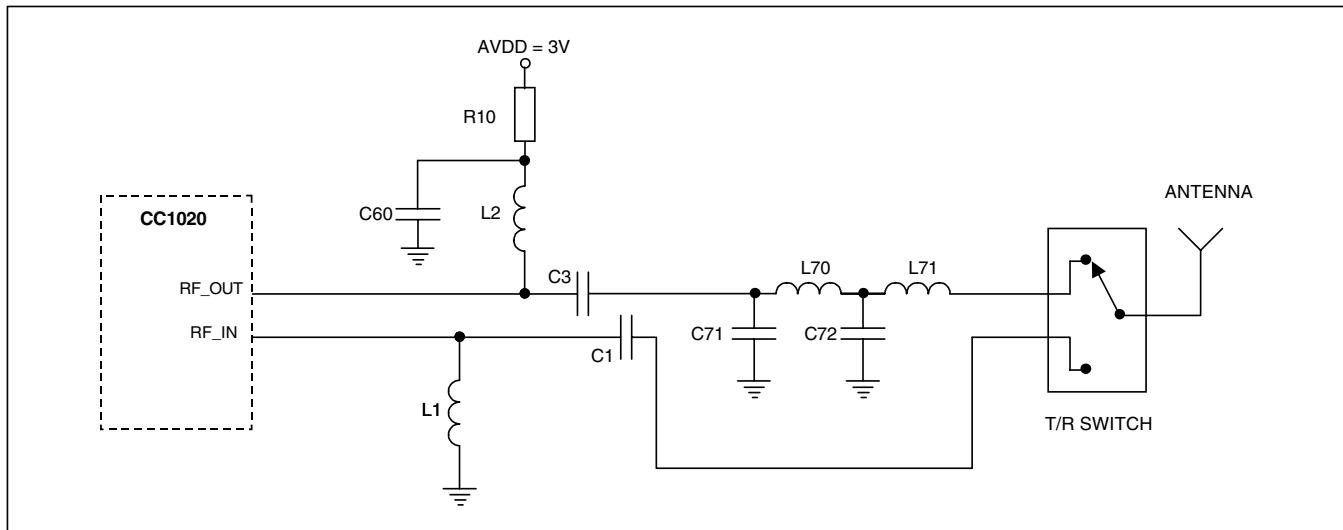

## 7. アプリケーション回路

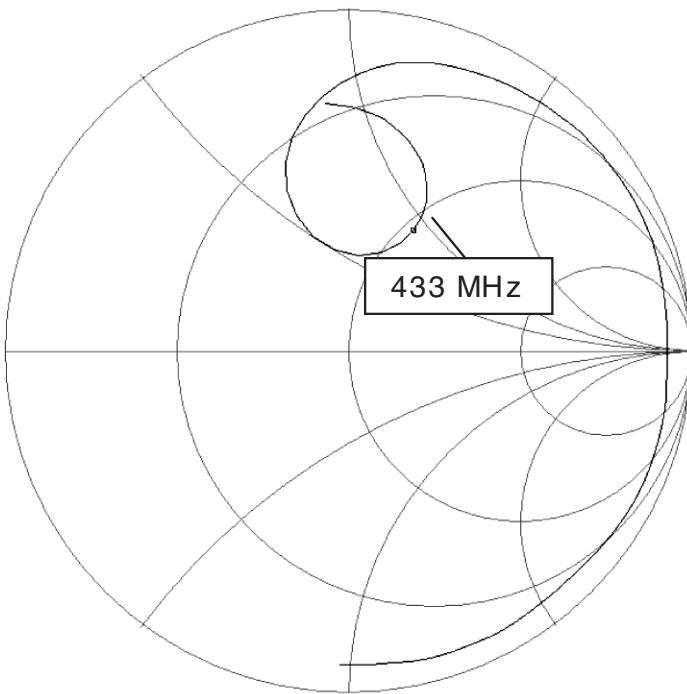

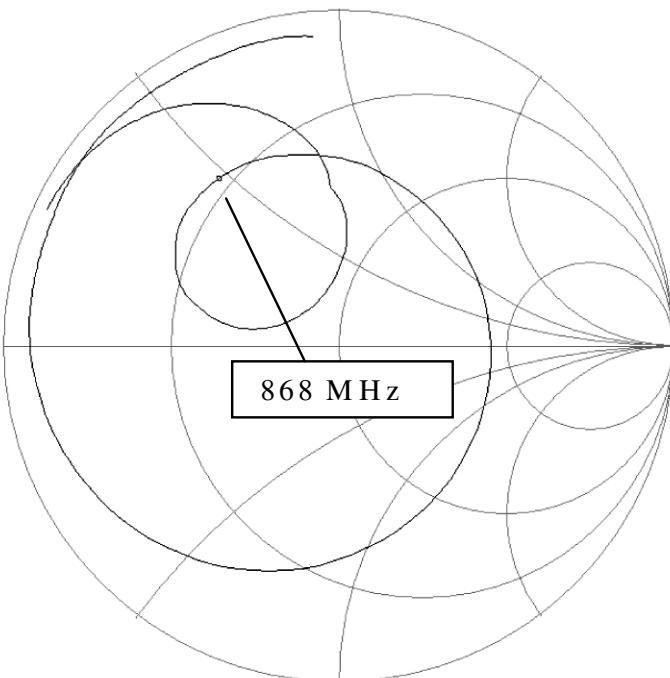

CC1020を動作させるには、非常にわずかな外付け部品しか必要ありません。推奨アプリケーション回路を図3に示します。外付け部品について表12に示し、その定数について表13に示します。

### 入出力整合

L1とC1はレシーバの入力整合に使用されます。L1はバイアスを与えるDCチョークでもあります。L2とC3によりトランスマッタを50Ωに整合します。CC1020の内部回路は、送受信の両モードで入出力を相互に接続でき、かつ50Ωに整合がとれるようになっています。しかし、最適な特性を得るために外付けのT/Rスイッチを使用することを推奨します。詳細は14節をご覧ください。整合回路網の部品定数は、SmartRF® Studioソフトウェアを使用すると容易に得られます。

### バイアス抵抗

高精度のバイアス抵抗R1は、バイアス電流を正確に設定するために使用されます。

### PLLループ・フィルタ

ループ・フィルタは、2個の抵抗(R2, R3)と3個のコンデンサ(C6–C8)からなります。C7とC8は、広ループ帯域幅が必要なアプリケーションでは省略可能です。表13に示す定数は、最大

4.8kBaudのデータ・レートまで使用できます。それより高データ・レートの部品定数は、SmartRF® Studioソフトウェアを使用すると容易に得られます。

### 水晶振動子

1個の外付け水晶振動子と2個の負荷コンデンサ(C4, C5)が水晶発振器に使用されます。詳細は19節をご覧ください。

### 他のフィルタ

特定のアプリケーションにおける特性を向上させるため、他の外付け部品(RF LCやSAWフィルタ)が使用できます。より詳しい情報は14節をご覧ください。

### 電源のデカップリングおよびフィルタリング

電源はデカップリングおよびフィルタリングする必要があります(アプリケーション回路には示していません)。デカップリング用コンデンサおよび電源フィルタリングの配置と定数は、ナローバンド・アプリケーションの最適特性を得るために非常に重要です。そのため、TIは極力従うべきリファレンス・デザインを提供しております。

| 参照   | 説明                                |

|------|-----------------------------------|

| C1   | LNA入力整合およびDC阻止、14節参照。             |

| C3   | PA出力整合およびDC阻止、14節参照。              |

| C4   | 水晶振動子負荷コンデンサ、19節参照。               |

| C5   | 水晶振動子負荷コンデンサ、19節参照。               |

| C6   | PLLループ・フィルタ・コンデンサ。                |

| C7   | PLLループ・フィルタ・コンデンサ(広ループ帯域幅では省略可能)。 |

| C8   | PLLループ・フィルタ・コンデンサ(広ループ帯域幅では省略可能)。 |

| C60  | デカップリング用コンデンサ。                    |

| L1   | LNA整合およびDCバイアス(グランド)、14節参照。       |

| L2   | PA整合およびDCバイアス(電源電圧)、14節参照。        |

| R1   | 基準電流源用の高精度抵抗。                     |

| R2   | PLLループ・フィルタ抵抗。                    |

| R3   | PLLループ・フィルタ抵抗。                    |

| R10  | PA出力整合、14節参照。                     |

| XTAL | 水晶振動子、19節参照。                      |

表 12. 外付け部品の概要(電源デカップリング用コンデンサは除く)

図3. 標準的なアプリケーションおよび試験回路(電源デカップリング用コンデンサは除く)

| Item | 433 MHz                            | 868 MHz                            | 915 MHz                            |

|------|------------------------------------|------------------------------------|------------------------------------|

| C1   | 10 pF, 5%, NPO, 0402               | 47 pF, 5%, NPO, 0402               | 47 pF, 5%, NPO, 0402               |

| C3   | 5.6 pF, 5%, NPO, 0402              | 10 pF, 5%, NPO, 0402               | 10 pF, 5%, NPO, 0402               |

| C4   | 22 pF, 5%, NPO, 0402               | 22 pF, 5%, NPO, 0402               | 22 pF, 5%, NPO, 0402               |

| C5   | 12 pF, 5%, NPO, 0402               | 12 pF, 5%, NPO, 0402               | 12 pF, 5%, NPO, 0402               |

| C6   | 220 nF, 10%, X7R, 0603             | 100 nF, 10%, X7R, 0603             | 100 nF, 10%, X7R, 0603             |

| C7   | 8.2 nF, 10%, X7R, 0402             | 3.9 nF, 10%, X7R, 0402             | 3.9 nF, 10%, X7R, 0402             |

| C8   | 2.2 nF, 10%, X7R, 0402             | 1.0 nF, 10%, X7R, 0402             | 1.0 nF, 10%, X7R, 0402             |

| C60  | 220 pF, 5%, NPO, 0402              | 220 pF, 5%, NPO, 0402              | 220 pF, 5%, NPO, 0402              |

| L1   | 33 nH, 5%, 0402                    | 82 nH, 5%, 0402                    | 82 nH, 5%, 0402                    |

| L2   | 22 nH, 5%, 0402                    | 3.6 nH, 5%, 0402                   | 3.6 nH, 5%, 0402                   |

| R1   | 82 kΩ, 1%, 0402                    | 82 kΩ, 1%, 0402                    | 82 kΩ, 1%, 0402                    |

| R2   | 1.5 kΩ, 5%, 0402                   | 2.2 kΩ, 5%, 0402                   | 2.2 kΩ, 5%, 0402                   |

| R3   | 4.7 kΩ, 5%, 0402                   | 6.8 kΩ, 5%, 0402                   | 6.8 kΩ, 5%, 0402                   |

| R10  | 82 Ω, 5%, 0402                     | 82 Ω, 5%, 0402                     | 82 Ω, 5%, 0402                     |

| XTAL | 14.7456 MHz crystal,<br>16 pF load | 14.7456 MHz crystal,<br>16 pF load | 14.7456 MHz crystal,<br>16 pF load |

注記：網掛けした項目は周波数により定数が変化します。433MHz、12.5kHzチャネル間隔については、より低帯域幅のループ・フィルタを使用して隣接および代替チャネル除去特性を改善します。

表13. アプリケーション回路(図3)の部品表

注記：

表13のPLLループ・フィルタの部品定数(R2, R3, C6-C8)は、最大4.8kBaudのデータ・レートまで使用できます。その他のデータ・レートについては、SmartRF® Studioソフトウェアが15.1節の方程式を使用して部品定数を与えてくれ

ます。CC1020EMXリファレンス・デザインでは、村田製作所のLQG15HSシリーズ・コイルが使用されています。スイッチはM/A-COM製のSW-456です。

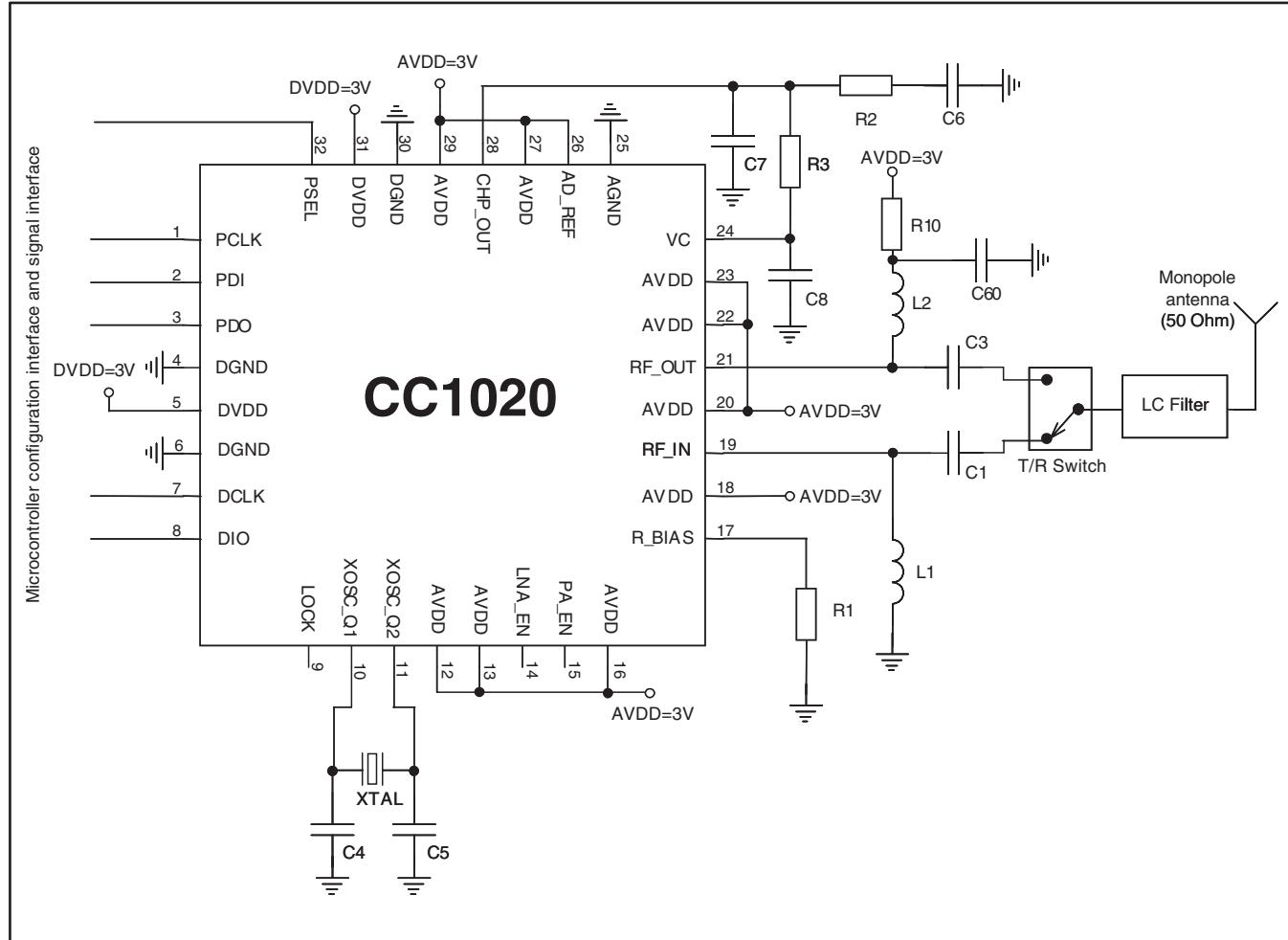

図3のLCフィルタは送信回路にのみ挿入されています。このフィルタは、送信系統の高調波とスプリアスを低減するとともに、受信選択度も向上します。しかし、LCフィルタの挿入損失により、感度がわずかに低下します。

信号の高調波とスプリアスを低減するとともに、受信選択度も向上します。しかし、LCフィルタの挿入損失により、感度がわずかに低下します。

図4. LCフィルタの挿入場所を変更したアプリケーション回路(電源デカッピング用コンデンサは除く)

## 8. 設定の概要

CC1020は様々なアプリケーションために、その構成と特性をアプリケーションに最適に設定することができます。構成レジスタの設定により、以下の主要なパラメータをプログラミングできます。

- 受信/送信モード

- RF出力パワー

- 周波数シンセサイザの主要パラメータ：

- RF出力周波数

- FSK周波数間隔

- 水晶発振器の基準周波数

- パワーダウン/パワーアップ・モード

- 水晶発振器のパワーアップ/パワーダウン

- データ・レートおよびデータ・フォーマット (NRZ, マンチェスター符号やUARTインターフェイス)

- シンセサイザ・ロック表示モード

- デジタルRSSIおよびキャリア検知

- FSK/GFSK/OOK変調

### 8.1. 設定用ソフトウェア

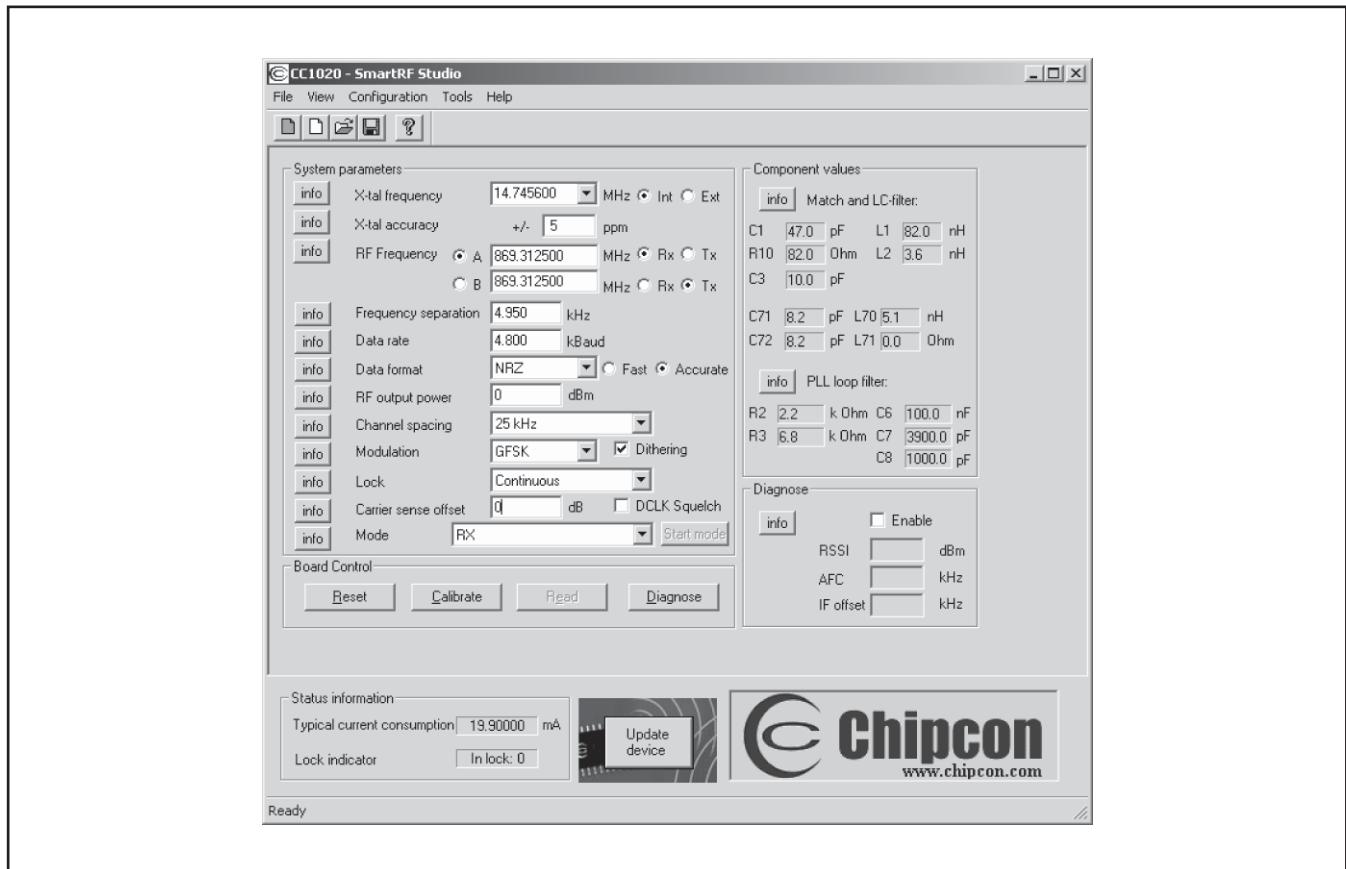

TIはCC1020のユーザーにソフトウェア・プログラムSmartRF® Studio (Windowsインターフェイス) を提供しています。このソフトウェアは、ユーザーによる様々なパラメータの選択に基づいて、必要なCC1020の設定データをすべて生成します。これらの16進数は、CC1020の設定に関してマイクロコントローラに必要な入力になります。さらに、このソフトウェアにより出入力整合回路、PLLループ・フィルタおよびLCフィルタの部品定数がユーザーに与えられます。

図5にCC1020設定ソフトウェアのユーザー・インターフェイス画面を示します。

図 5. SmartRF® Studioユーザ・インターフェイス

## 9. マイクロコントローラ・インターフェイス

標準システムの場合、CC1020はマイクロコントローラと接続して使用します。このマイクロコントローラは下記のことが必要です。

- CC1020のモードをプログラミングするための、設定用4線式シリアル・インターフェイス(PDI, PDO, PCLKおよびPSEL)。

- データ信号のための、双方向同期インターフェイス(DIO, DCLK)。

- データの符号化/復号化。

- LOCK端子を経由して周波数ロック状態、キャリア検知状態、その他の状態情報を監視する。

- 4線式シリアル・インターフェイスを経由して、デジタルRSSI値やその他の状態情報を読み込む。

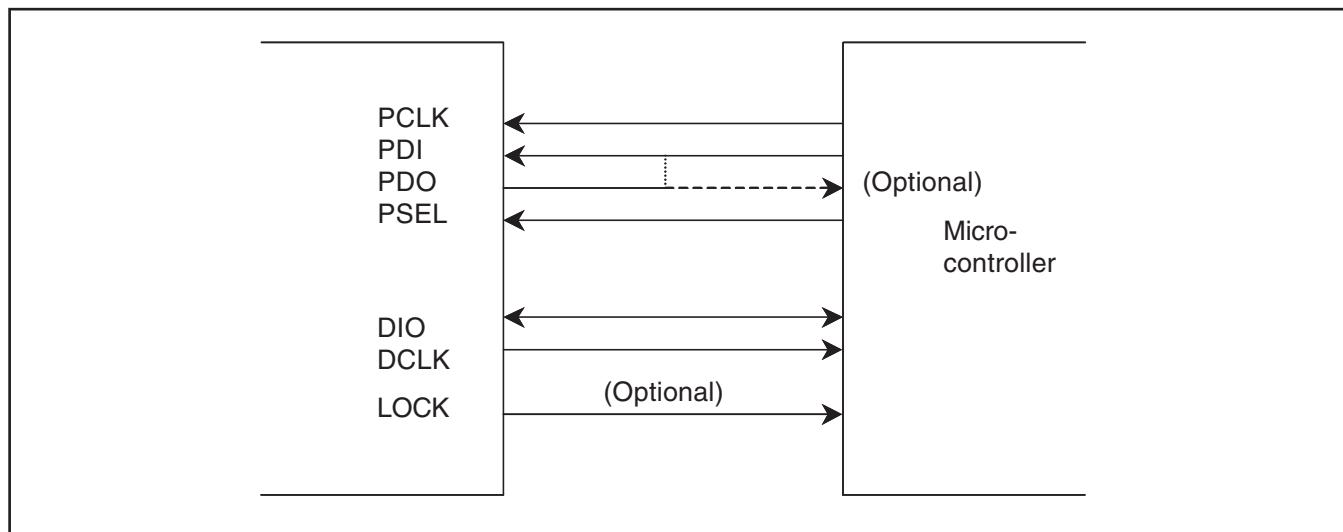

### 設定インターフェイス

図6にマイクロコントローラとのインターフェイスを示します。マイクロコントローラは、設定インターフェイスに3あるいは4本のI/O端子(PDI, PDO, PCLKおよびPSEL)を使用します。PDOはマイクロコントローラの入力に接続します。PDI, PCLKおよびPSELは、マイクロコントローラの出力に接続する必要があります。PDI, PDOを相互に接続し、マイクロコントローラの端子が双方向ならば、I/O端子を1本節約できます。

また、PDI, PDOおよびPCLKに接続したマイクロコントローラの端子は、設定インターフェイスに使用されていないとき他の目的に使用できます。PSEL(アクティブ高)がアクティブでない場合、PDI, PDOおよびPCLKは高インピーダンス入力になります。

PSELには内部プルアップ抵抗があり、それを流れる電流を防止するため、パワーダウン・モードの間はオープンまたは、ハイレベルに設定します。

### 信号インターフェイス

双方向端子は一般にデータ(DIO)の送受信に使用します。データのタイミングを与えるDCLKは、マイクロコントローラの入力に接続します。

オプションとして、受信モード時のデータ出力は別の端子に出力できます。詳細については9.2節をご覧ください。

### PLLロック信号

オプションで、マイクロコントローラの1端子をLOCK信号の監視に使用できます。この信号は、PLLがロックするとローのロジックレベルになります。また、キャリア検知や他の内部テスト信号の監視にも使用できます。

図6. マイクロコントローラ・インターフェイス

## 9.1 設定用4線式シリアル・インターフェイス

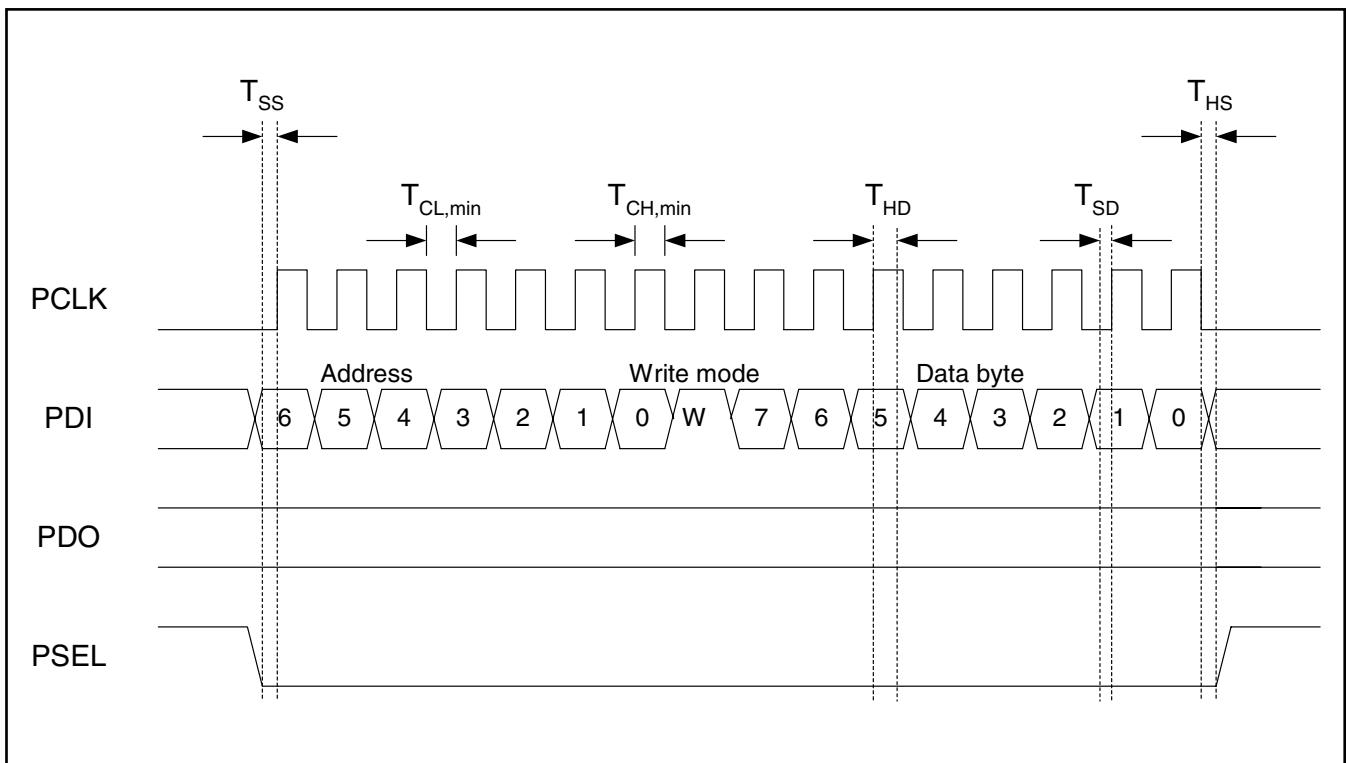

CC1020の設定は、SPI互換の4線式インターフェイス(PDI, PDO, PCLKおよびPSEL)にスレーブ接続して行います。各々7ビットでアドレスされる8ビットの設定レジスタがあり、リード/ライト(R/W)ビットにより、リードあるいはライト動作を開始します。CC1020の全てを設定するには、それぞれ16ビット(7アドレス・ビット、R/Wビットおよび8データ・ビット)からなるデータ・フレームを33個送信する必要があります。全ての設定に必要な時間はPCLK周波数に依存します。10MHzのPCLKの場合、フル設定は53μs以下で終了します。デバイスをパワーダウン・モードに設定するに必要なのは、1フレームの送信と2μs以下の時間だけです。また、レジスタはすべて読み取り可能です。

各ライト・サイクルの間、16ビットがPDIラインに送信されます。各データ・フレームの上位7ビット(A6:0)はアドレス・ビットです。A6はアドレスのMSB(最上位ビット)であり、最初のビットとして送信されます。次のビットはR/Wビット("High"がライト、"Low"がリード)です。その後にデータ8ビット(D7:0)が伝送されます。アドレスとデータの伝送の間、PSEL(プログラム・セレクト)は"Low"に保つ必要があります。図7をご覧ください。

プログラミング・タイミングを図7に示します、表14とともに参照してください。PDIのデータはPCLKの立ち上りエッジでクロックされます。マイクロコントローラでは、データをPCLKの立ち下りエッジでセットするようにします。データ8ビットの最終ビットD0がロードされると、データ・ワードが内部の設定レジスタにロードされます。

設定データはプログラミングされたパワーダウン・モードでは保持されますが、電源の供給が絶たれた場合、保持されません。設定レジスタは任意の順番でプログラミングできます。

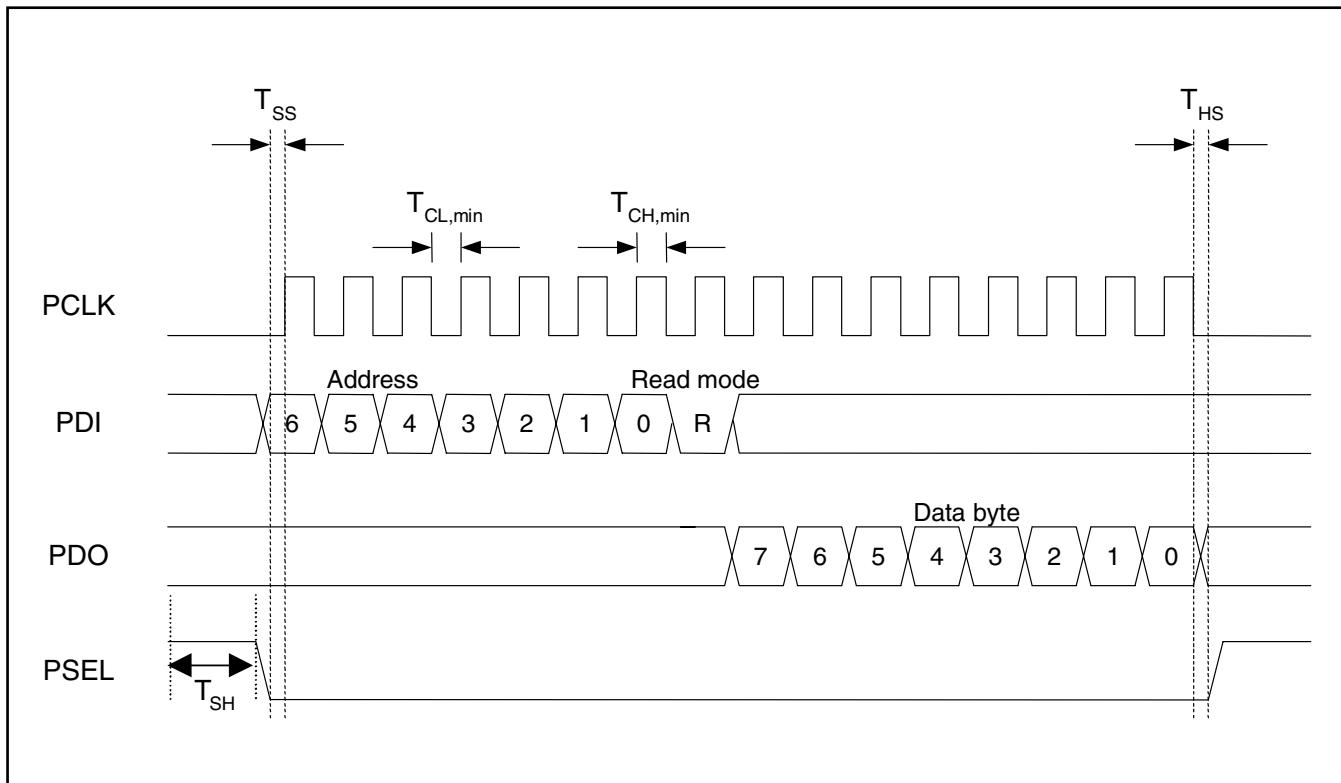

設定レジスタの内容は、同じ設定インターフェイスでマイクロコントローラからリードできます。7ビットのアドレス・ビットを最初に送信し、次にR/Wビットを"Low"にしてデータの読み取りを開始します。すると、CC1020はアドレスされたレジスタからデータを返します。PDOがデータ出力として使用されるので、 PDOはマイクロコントローラで入力として設定する必要があります。また、 PDOはPCLKの立ち下りエッジでセットされるため、立ち上りエッジでサンプリングされるようになります。図8にリード動作を示します。

リード/ライト動作でない期間は、PSELは"High"に設定しなければなりません。

図7. 設定レジスタのライト動作

図 8. 設定レジスタのリード動作

| Parameter                | Symbol       | Min | Max | Unit | Conditions                              |

|--------------------------|--------------|-----|-----|------|-----------------------------------------|

| PCLK, clock frequency    | $f_{PCLK}$   |     | 10  | MHz  |                                         |

| PCLK low pulse duration  | $T_{CL,min}$ | 50  |     | ns   | PCLKに必要な“L”レベルの最短時間。                    |

| PCLK high pulse duration | $T_{CH,min}$ | 50  |     | ns   | PCLKに必要な“H”レベルの最短時間。                    |

| PSEL setup time          | $T_{SS}$     | 25  |     | ns   | PCLKの立ち上りエッジ前に必要なPSELの“L”レベルの最短時間。      |

| PSEL hold time           | $T_{HS}$     | 25  |     | ns   | PCLKの立ち下りエッジ後に必要なPSELの“L”レベルの最短時間。      |

| PSEL high time           | $T_{SH}$     | 50  |     | ns   | PSELに必要な“H”レベルの最短時間。                    |

| PDI setup time           | $T_{SD}$     | 25  |     | ns   | PDIにおけるデータの、PCLKの立ち上りエッジ前に必要なレディの最短時間。  |

| PDI hold time            | $T_{HD}$     | 25  |     | ns   | PDIにおけるデータの、PCLKの立ち上りエッジ後に必要なホールドの最短時間。 |

| Rise time                | $T_{rise}$   |     | 100 | ns   | PCLKとPSELの最長立ち上り時間。                     |

| Fall time                | $T_{fall}$   |     | 100 | ns   | PCLKとPSELの最長立ち下り時間。                     |

注記：セットアップ・タイムとホールド・タイムは、VDDの50%を基準にしています。立ち上りと立ち下り時間は、それぞれVDDの10%と90%を基準にしています。本表は最大負荷が20pFまで有効です。

表 14. シリアル・インターフェイスのタイミング仕様

## 9.2. 信号インターフェイス

CC1020は、NRZ(ノン・リターン・ツー・ゼロ)データあるいはマンチェスター符号(バイフェーズレベルとして知られる)データを使用できます。また、CC1020は復調器からのデータと同期したデータ・クロック、DCLKを出力することもできます。データ・フォーマットは、MODEMレジスタのDATA\_FORMAT[1:0]ビットで制御されます。

CC1020では、以下の3種類のデータ・フォーマットが設定できます。

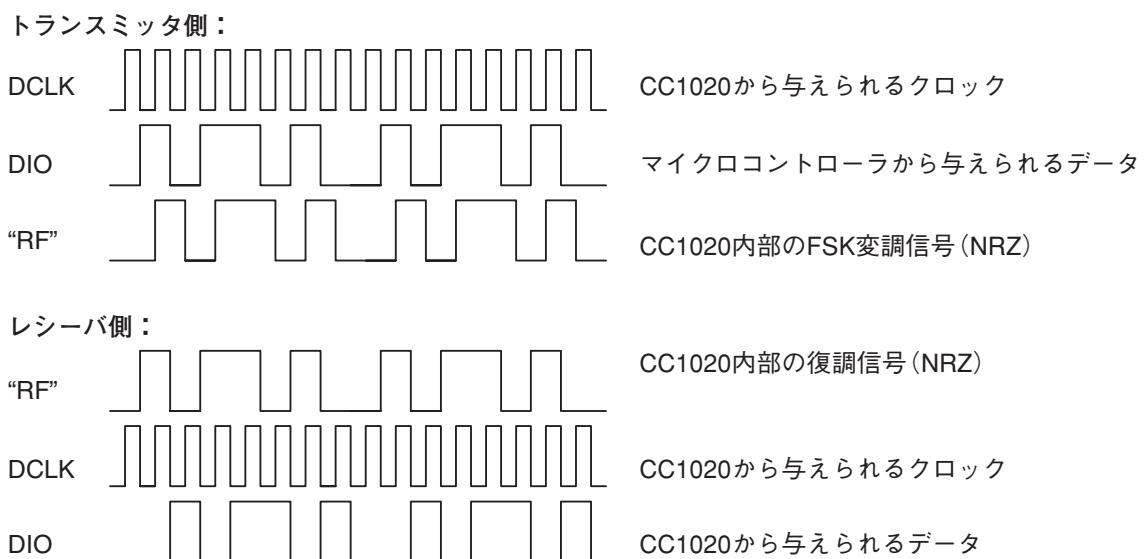

### 同期NRZモード

送信モード時、CC1020はDCLKにデータ・クロックを出力し、DIOをデータ入力として使用します。データはDCLKの立ち上がりエッジでクロックに同期して入力します。CC1020はデータを符号化せずにRF信号を変調します。

受信モードではCC1020は受信データから同期クロックを作成し、DCLKに受信データ・クロックを、DIOにデータを出力します。このデータは、DCLKの立ち上がりエッジに同期してインターフェイス回路に送ります。図9をご覧ください。

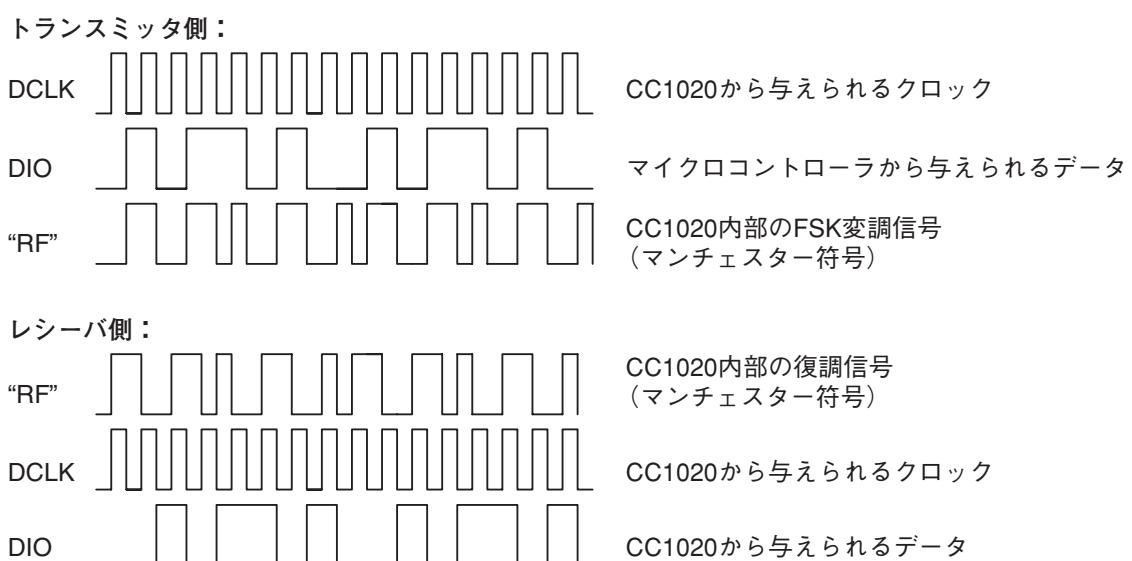

### 同期マンチェスター符号モード

送信モード時にCC1020はDCLKにデータ・クロックを出力し、DIOをデータ入力として使用します。データはDCLKの立ち上がりエッジでクロック同期して入力し、データをNRZフォーマットにします。次に、データはマンチェスター符号でRF信号を変調します。符号化はCC1020で行われ、これにより実効的なビット・レートはBaudレートの半分になります。たとえば、4.8kBaudのマンチェスター符号データは、2.4kbpsに相当します。

受信モードではCC1020は受信データから同期クロックを作成し、DCLKに受信データ・クロックを、DIOにデータを出力します。またCC1020は復号を行い、NRZデータがDIOに出力されます。このデータは、DCLKの立ち上がりエッジにクロック同期してインターフェイス回路に送ります。以上について図10をご覧ください。

同期NRZまたはマンチェスター・モードでは、キャリア検知信号あるいはPLLロック信号でゲートされないかぎり、DCLK信号は送受信モードにおいて連続的に出力されます。より詳細については、21節および21.2節を参照してください。

INTERFACEレジスタのビットSEP\_DI\_DO = 0の場合、DIO端子は受信モードでデータ出力、送信モードでデータ入力になります。

オプションとして、データ出力は他の端子に出力できます。これを行うには、INTERFACEレジスタのビットSEP\_DI\_DO = 1と設定します。すると、LOCK端子のその他の使用方法より優先されて、同期モードにてLOCK端子をデータ出力として使用できます。

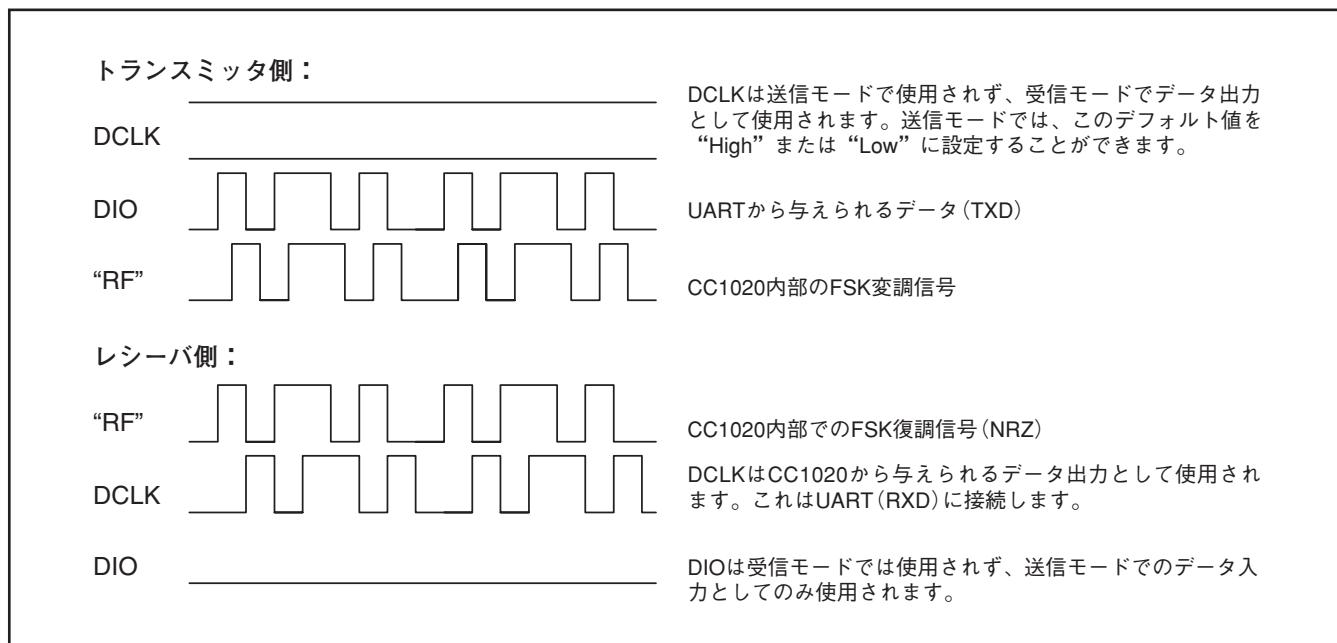

### トランスペアレント非同期UARTモード

送信モードでDIOがデータ入力として使用されます。データは同期化あるいは符号化せずにRF信号を変調します。

受信モードでは、復調器からのデータの原信号が出力(DIO)に送られます。CC1020では信号の同期化も復号も行われず、インターフェイス回路でも行いません。

INTERFACEレジスタのビットSEP\_DI\_DO = 0の場合、DIO端子は受信モードでデータ出力に、送信モードでデータ入力になります。DCLK端子はアクティブにならず、DATA\_FORMAT[0]により“High”または“Low”レベルに設定できます。

INTERFACEレジスタのビットSEP\_DI\_DO = 1の場合、DCLK端子は受信モードでデータ出力であり、DIO端子は送信モードでデータ入力になります。送信モードではDCLK端子はアクティブにならず、DATA\_FORMAT[0]により“H”または“L”レベルに設定できます。以上については図11をご覧ください。

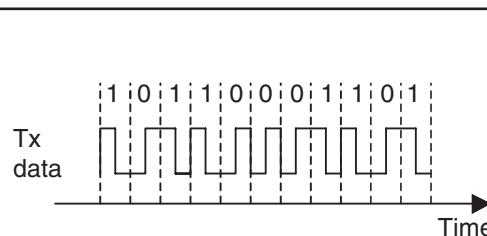

### マンチェスター符号化および復号化

同期マンチェスター符号モードでは、CC1020はデータの変調にマンチェスター符号を使用します。また、CC1020はデータの復号化と同期化も行います。マンチェスター符号は遷移をベースにしており、“0”は“Low”から“High”的遷移として、“1”は“High”から“Low”的遷移として符号化されます。これについては図12をご覧ください。

マンチェスター符号では、一定のDC成分が信号にあることが保証されます。このDC成分はある種のFSK復調器に必要になります。このモードを使用すると、CC400/CC900設計との互換性も保証されます。

図 9. 同期NRZモード (SEP\_DL\_DO = 0)

図 10. 同期マンチェスター符号モード (SEP\_DL\_DO = 0)

図 11. トランスペアレント非同期UARTモード (SEP\_DI\_DO = 1)

図 12. マンチェスター符号化

## 10. データ・レートのプログラミング

データ・レート (ビット・レート) はプログラマブルであり、水晶発振周波数とCLOCKレジスタ (CLOCK\_AおよびCLOCK\_B) のプログラミングにより定まります。

ビット・レート (B.R.) は次式で与えられます。

$$B.R. = \frac{f_{XOSC}}{8 \cdot (REF\_DIV+1) \cdot DIV1 \cdot DIV2}$$

ここで、DIV1およびDIV2はMCLK\_DIV1およびMCLK\_DIV2によって与えられる値です。

いくつかの可能なデータ・レートを同期モード時の水晶発振周波数の関数として表17に示します。非同期トランスペアレントUARTモードでは、最大153.6kBaudまでのデータ・レートが使用できます。

| MCLK_DIV2[1:0] | DIV2 |

|----------------|------|

| 00             | 1    |

| 01             | 2    |

| 10             | 4    |

| 11             | 8    |

表 15. MCLK\_DIV2の設定によるDIV2

| MCLK_DIV1[2:0] | DIV1 |

|----------------|------|

| 000            | 2.5  |

| 001            | 3    |

| 010            | 4    |

| 011            | 7.5  |

| 100            | 12.5 |

| 101            | 40   |

| 110            | 48   |

| 111            | 64   |

表 16. MCLK\_DIV1の設定によるDIV1

| Data rate<br>[kBaud] | Crystal frequency [MHz] |        |        |        |         |         |         |

|----------------------|-------------------------|--------|--------|--------|---------|---------|---------|

|                      | 4.9152                  | 7.3728 | 9.8304 | 12.288 | 14.7456 | 17.2032 | 19.6608 |

| 0.45                 |                         | X      |        |        | X       |         |         |

| 0.5                  |                         |        |        | X      |         |         |         |

| 0.6                  | X                       | X      | X      | X      | X       | X       |         |

| 0.9                  |                         | X      |        |        | X       |         |         |

| 1                    |                         |        |        | X      |         |         |         |

| 1.2                  | X                       | X      | X      | X      | X       | X       | X       |

| 1.8                  |                         | X      |        |        | X       |         |         |

| 2                    |                         |        |        | X      |         |         |         |

| 2.4                  | X                       | X      | X      | X      | X       | X       | X       |

| 3.6                  |                         | X      |        |        | X       |         |         |

| 4                    |                         |        |        | X      |         |         |         |

| 4.096                |                         |        | X      |        |         |         | X       |

| 4.8                  | X                       | X      | X      | X      | X       | X       | X       |

| 7.2                  |                         | X      |        |        | X       |         |         |

| 8                    |                         |        |        | X      |         |         |         |

| 8.192                |                         |        | X      |        |         |         | X       |

| 9.6                  | X                       | X      | X      | X      | X       | X       | X       |

| 14.4                 |                         | X      |        |        | X       |         |         |

| 16                   |                         |        |        | X      |         |         |         |

| 16.384               |                         |        | X      |        |         |         | X       |

| 19.2                 | X                       | X      | X      | X      | X       | X       | X       |

| 28.8                 |                         | X      |        |        | X       |         |         |

| 32                   |                         |        |        | X      |         |         |         |

| 32.768               |                         |        | X      |        |         |         | X       |

| 38.4                 | X                       | X      | X      | X      | X       | X       | X       |

| 57.6                 |                         | X      |        |        | X       |         |         |

| 64                   |                         |        |        | X      |         |         |         |

| 65.536               |                         |        |        |        |         |         | X       |

| 76.8                 | X                       | X      | X      | X      | X       | X       | X       |

| 115.2                |                         | X      |        |        | X       |         |         |

| 128                  |                         |        |        | X      |         |         |         |

| 153.6                |                         | X      |        | X      | X       | X       | X       |

表 17. いくつかの可能なデータレート 対 水晶発振周波数

## 11. 周波数のプログラミング

設定レジスタにおける周波数ワードをプログラミングすると、動作周波数が設定されます。周波数ワード・レジスタにはFREQ\_AおよびFREQ\_Bの2種類があり、異なる2つの周波数をプログラミングすることができます。RXとTXの両モード間を非常に高速に切り換えられるように、一方の周波数ワードはRX(局部発振周波数)に使用でき、他方はTX(送信キャリア周波数)に使用できます。また、この2つの周波数はRX(あるいはTX)の異なる2個のチャネルに使用することもできます。MAINレジスタのF\_REGビットにより、周波数ワードAあるいはBが選択されます。

周波数ワードは、FREQ\_AワードについてはFREQ\_2A : FREQ\_1A : FREQ\_0Aにあり、FREQ\_BワードについてはFREQ\_2B : FREQ\_1B : FREQ\_0Bにあります。FREQ\_0レジスタのLSBは、11.1節のディザリングをイネーブルするために使用されます。

PLL出力周波数は次式で与えられます。

周波数帯域が402~470MHzでは、

$$f_c = f_{ref} \cdot \left( \frac{3}{4} + \frac{\text{FREQ} + 0.5 \cdot \text{DITHER}}{32768} \right)$$

また、周波数帯域が804~940MHzでは、

$$f_c = f_{ref} \cdot \left( \frac{3}{4} + \frac{\text{FREQ} + 0.5 \cdot \text{DITHER}}{32768} \right)$$

ANALOGレジスタのBANDSELECTビットにより、使用する周波数帯域が制御されます。

BANDSELECT = 0ならば402~470MHzであり、BANDSELECT = 1ならば804~940MHzになります。

基準周波数は、水晶発振器のクロック周波数をREF\_DIV (CLOCK\_AあるいはCLOCK\_Bレジスタの3ビット) の数字1～7で分周したものであり、次式で与えられます。

$$f_{ref} = \frac{f_{xosc}}{REF\_DIV + 1}$$

FSK周波数偏移はDEVIATIONレジスタでプログラミングされます。偏移プログラミングは仮数(TXDEV\_M[3:0])と指数(TXDEV\_X[2:0])に分かれます。

一般にREF\_DEVはできるだけ低くしますが、次の条件を満たす必要があります。

周波数帯域が402～470MHzでは、

$$9.8304 \geq f_{ref} > \frac{f_c}{256} [\text{MHz}]$$

また、周波数帯域が804～940MHzでは、

$$9.8304 \geq f_{ref} > \frac{f_c}{512} [\text{MHz}]$$

上記のPLL出力周波数の式により、送信モードでのキャリア周波数( $f_c$ 中心周波数)が与えられます。2つのFSK変調周波数は次式で与えられます。

$$f_0 = f_c - f_{dev}$$

$$f_1 = f_c + f_{dev}$$

ここで、 $f_{dev}$ はDEVIATIONレジスタで設定され、周波数帯域が402～470MHzでは、

$$f_{dev} = f_{ref} \cdot TXDEV\_M \cdot 2^{(TXDEV\_X-16)}$$

周波数帯域が804～940MHzでは、

$$f_{dev} = f_{ref} \cdot TXDEV\_M \cdot 2^{(TXDEV\_X-15)}$$

OOK(オン・オフ変調)はTXDEV\_M[3:0] = 0000のとき使用されます。

DEVIATIONレジスタのTX\_SHAPINGビットにより、変調信号のガウス整形が制御されます。

受信モードでは、周波数はLO周波数にプログラミングする必要があります。下側のLO注入が使用されるので、

$$f_{LO} = f_c - f_{IF}$$

ここで、 $f_{IF}$ はIF周波数(理想的には307.2kHz)です。

## 11.1. ディザリング

スプリアス信号は、PLLの分周比に依存するいくつかの周波数で発生します。これらのスパー強度を低減する一般的な手法は、周波数分周器の制御でディザリング信号を使用することです。ディザリングはFREQ\_0レジスタのDITHERビットを設定すると有効になります。できるだけ最適な特性を得るため、ディザリングを行うことを推奨します。

## 12. レシーバ

### 12.1. IF周波数

IF周波数は水晶発振周波数から次式のように得られます。

$$f_{IF} = \frac{f_{xoscx}}{8 \cdot (\text{ADC\_DIV}[2:0]+1)}$$

ここで、ADC\_DIV[2:0]はMODEMレジスタで設定されます。

ミキサの後に続くアナログ・フィルタは、広帯域およびアンチ・エイリアシングのフィルタリングに使用され、1MHz以上のオフセットのブロッキング特性に重要です。このフィルタは固定値であり、IF周波数の名目値である307.2kHzを中心としています。また、このアナログ・フィルタの帯域幅は約160kHzです。

300～320kHz以内のIF周波数を与える水晶発振周波数を使用すると、アナログ・フィルタが使用できます(周波数偏差が小さく、データ・レートが低いとして)。

しかし、オフセットが名目値のIF周波数より大きいと、信号の非対称なフィルタリング(群遅延変動および様々な減衰)となり、感度および選択性が低下することになります。より詳細については、アプリケーション・ノート『AN022水晶発振周波数の選択』を参照してください。

300～320kHz以外のIF周波数および高周波数偏移と高データ・レート(一般に76.8kbps以上)については、FILTERレジスタのFILTER\_BYPASS = 1と設定して、アナログ・フィルタをバイパスする必要があります。この場合、1MHz以上のオフセットのブロッキング特性が低下します。

IF周波数は常にADCクロック周波数の4分の1です。したがって、ADCクロック周波数は可能な限り1.2288MHzに近くします。

## 12.2. レシーバ・チャネル・フィルタ帯域幅

種々のチャネル間隔条件に対応するため、レシーバ・チャネル・フィルタ帯域幅はプログラマブルであり、9.6kHzから307.2kHzまでプログラミングできます。

最小レシーバ・チャネル・フィルタ帯域幅はビット・レート、周波数分離および水晶発振周波数許容誤差に依存します。

信号の帯域幅は、可能なレシーバ・チャネル・フィルタ帯域幅より小さくする必要があります。信号帯域幅(SBW)は次式(Carsonの法則)で近似できます。

$$SBW = 2 \cdot fm + 2 \cdot \text{周波数偏移}$$

ここで、 $fm$ は変調信号です。マンチェスター符号モードでは、最大変調信号は連続した0(または1)のシーケンスを送信する場合に発生します。NRZモードでは、最大変調信号は0-1-0シーケンスの送信で発生します。すると、マンチェスターとNRZの両モードとともに、 $2 \cdot fm$ はプログラミング設定されたビット・レートに等しくなります。したがって、SBWの式は次のように書き換えられます。

$$SBW = \text{ビット・レート} + \text{周波数間隔}$$

さらに、トランスマッタとレシーバの周波数オフセットについても考察しなければなりません。トランスマッタとレシーバで等しい周波数誤差(同型の水晶振動子)があるとして、合計の周波数誤差は、

$$f_{\text{error}} = \pm 2 \cdot XTAL\_ppm \cdot f_{\text{RF}}$$

ここで $XTAL\_ppm$ は、初期公差、温度ドリフト、負荷および経年変化を含む水晶振動子の総合精度です。また、 $f_{\text{RF}}$ はRFの動作周波数です。

したがって、最小レシーバ・チャネル・フィルタ帯域幅(ChBW)は、次式のように見積もることができます。

$$ChBW > SBW + 2 \cdot f_{\text{error}}$$

FILTERレジスタのDEC\_DIV[4:0]ビットにより、レシーバ・チャネル・フィルタ帯域幅が制御されます。6dB帯域幅は次式で与えられます。

$$ChBW = 307.2 / (DEC\_DIV + 1) [\text{kHz}]$$

ここで、IF周波数は307.2kHzに設定されています。

SmartRF® Studioでは、ユーザはチャネル間隔を規定し、チャネル・フィルタ帯域幅を表18にしたがって設定します。

チャネル間隔が12.5および25kHzのナローバンド・システムについては、チャネル・フィルタ帯域幅がそれぞれ12.288kHzおよび19.2kHzでARIB STD T-67およびEN 300 220に準拠します。

広帯域システム(チャネル間隔が50kHz以上)については、表18と異なるチャネル・フィルタ帯域幅が使用できます。

選択度および感度には周波数許容値とトレードオフの関係があります。大きな周波数ドリフトが予想されるアプリケーションでは、チャネル・フィルタ帯域幅は大きくできますが、隣接チャネル除去(ACR)および感度は低下します。

| Channel spacing<br>[kHz] | Filter bandwidth<br>[kHz] | FILTER.DEC_DIV<br>[4:0]<br>[decimal(binary)] |

|--------------------------|---------------------------|----------------------------------------------|

| 12.5                     | 12.288                    | 24 (11000b)                                  |

| 25                       | 19.2                      | 15 (01111b)                                  |

| 50                       | 25.6                      | 11 (01011b)                                  |

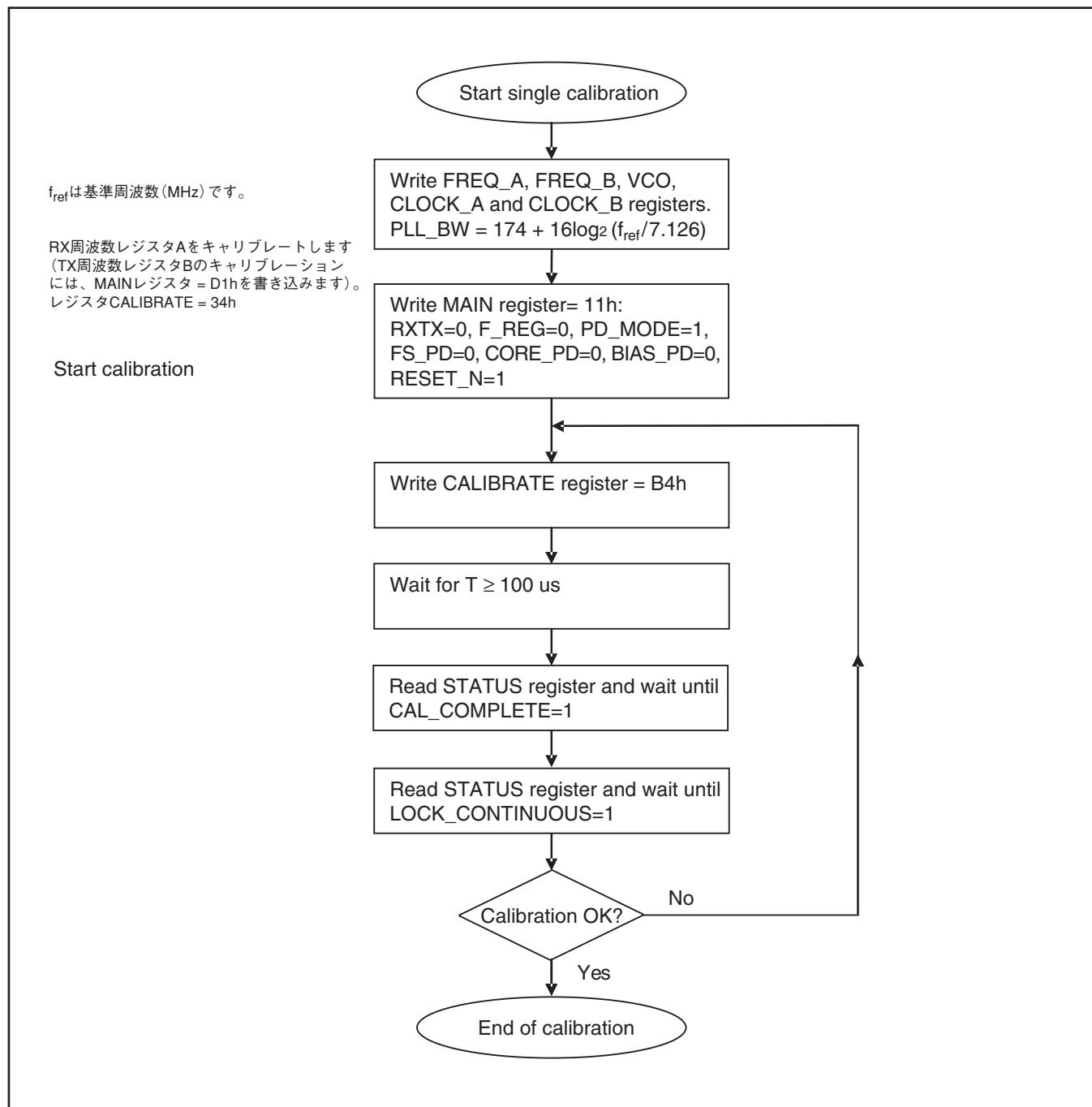

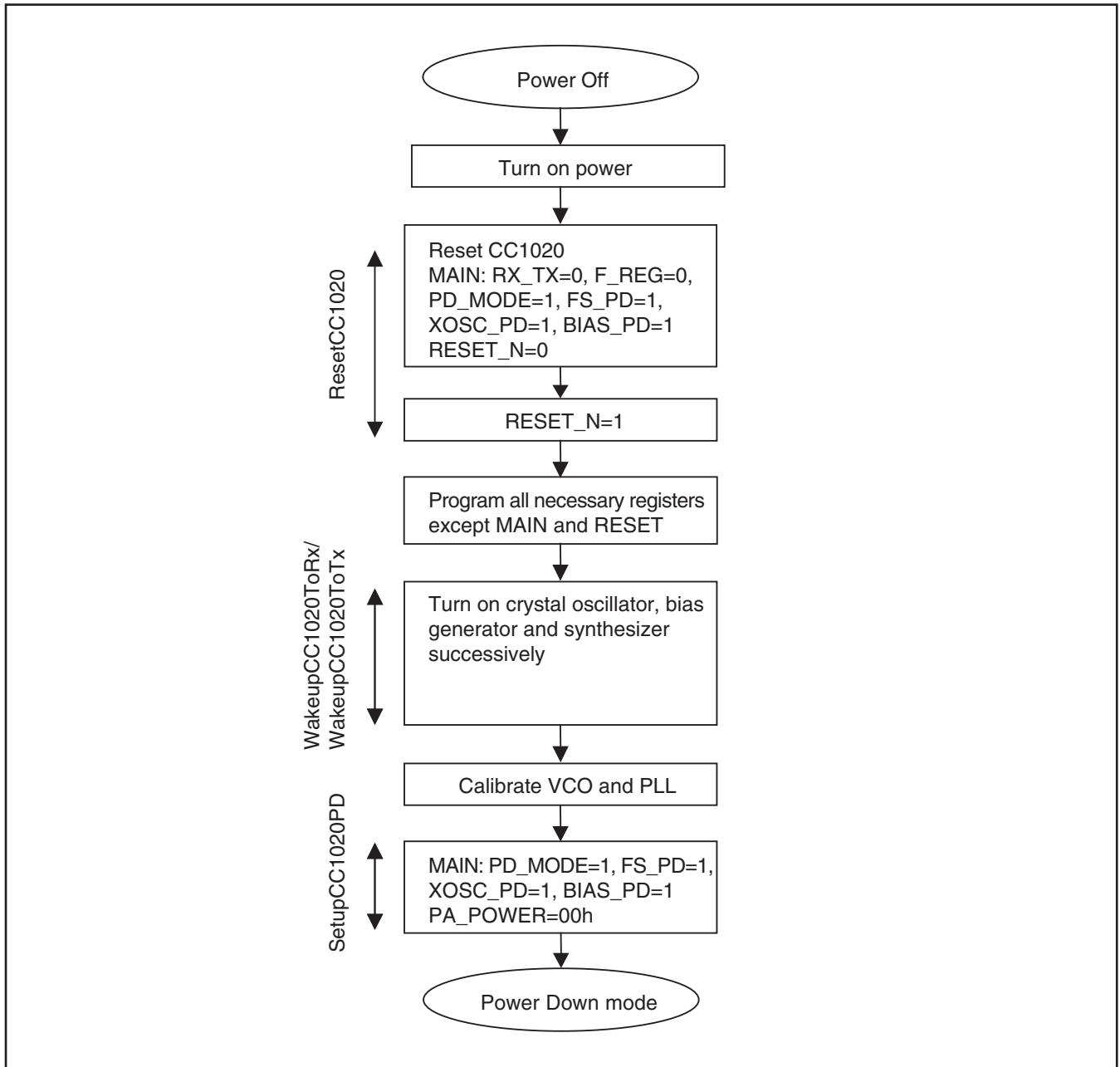

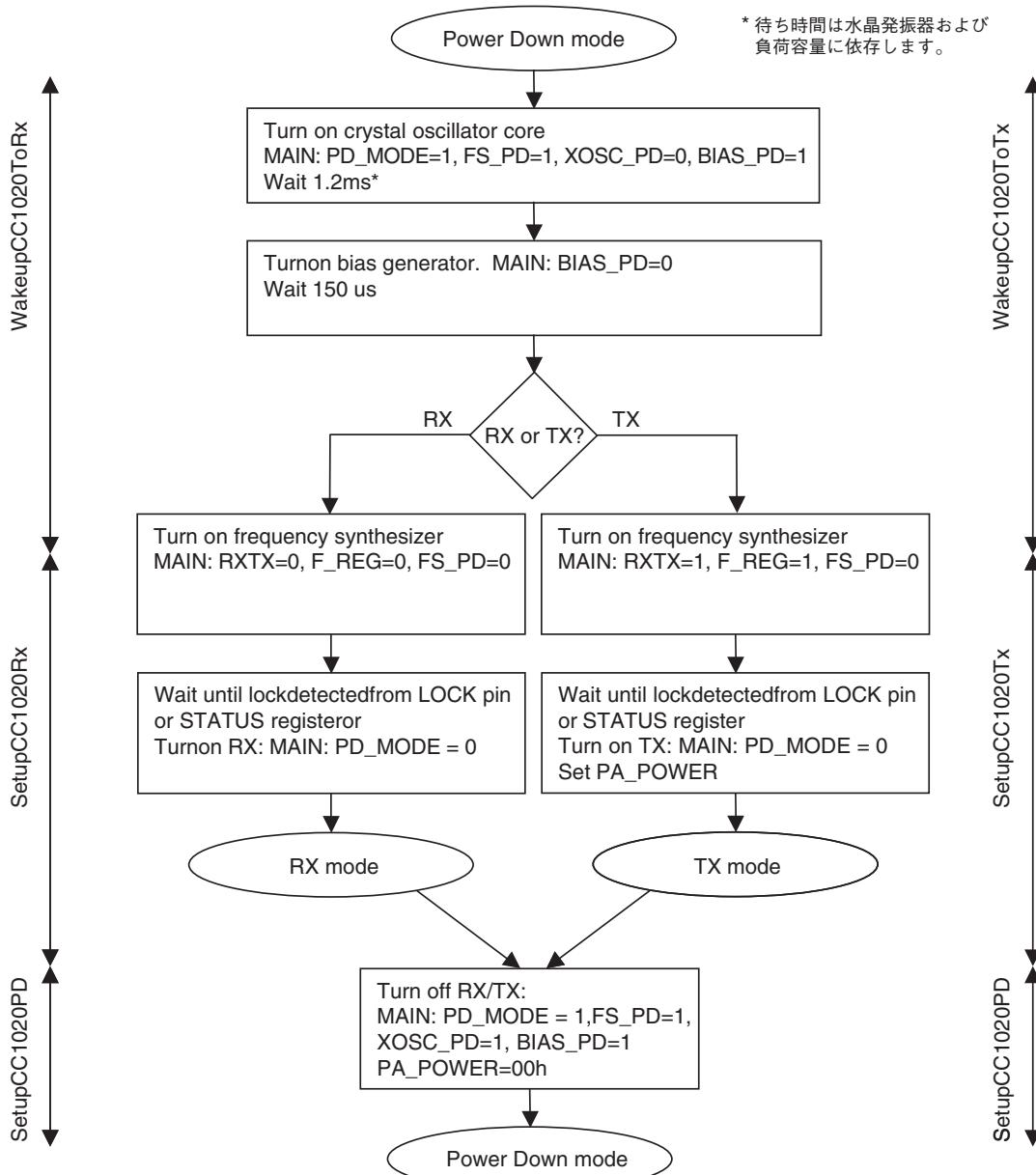

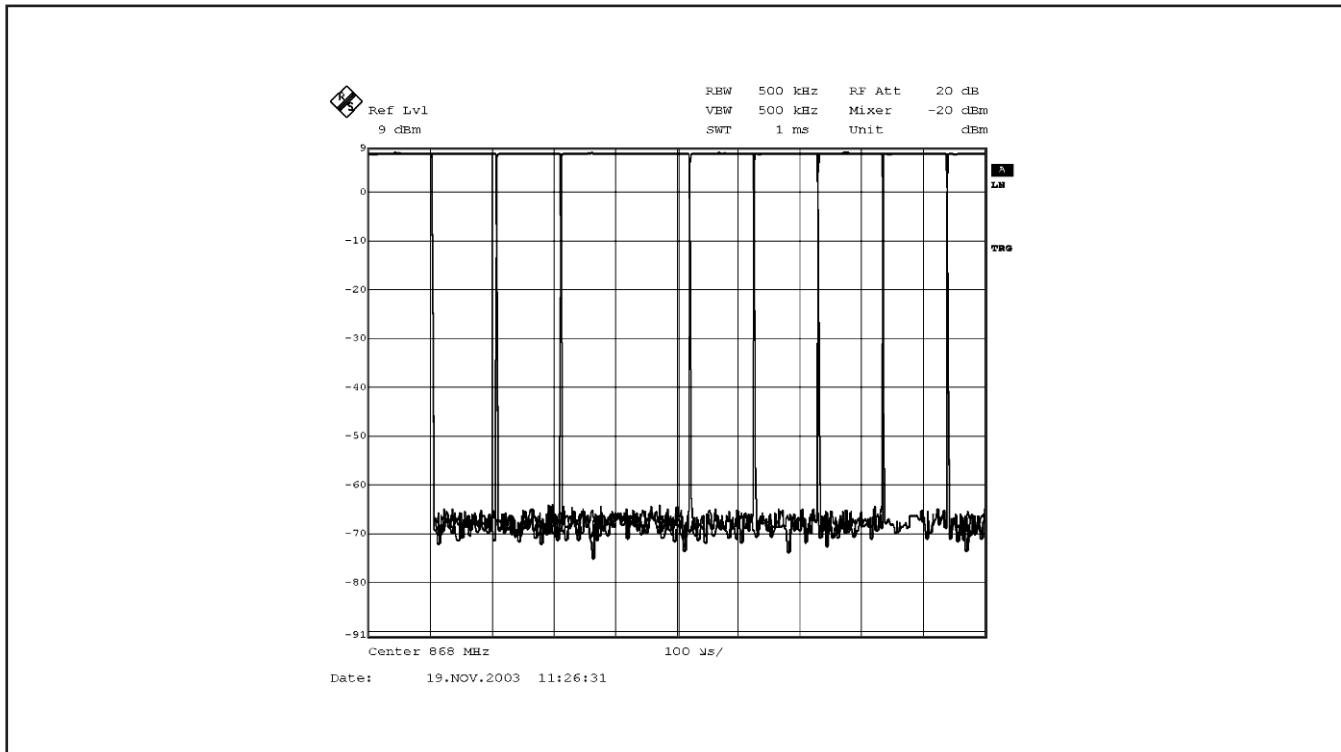

| 100                      | 51.2                      | 5 (00101b)                                   |