BQ79616-Q1, BQ79614-Q1, BQ79612-Q1

# JAJSL83D - AUGUST 2020 - REVISED SEPTEMBER 2022

# BQ79616-Q1、BQ79614-Q1、BQ79612-Q1 機能安全準拠、車載用、16S/14S/12S、 バッテリ・モニタ / バランサおよび統合型ハードウェア・プロテクタ

# 1 特長

- 車載アプリケーション認定済み

- 下記内容で AEC-Q100 認定済み:

- デバイス温度グレード 1:-40°C~+125°Cの動作時 周用温度範囲

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4B

- 機能安全準拠

- 機能安全アプリケーション向けに開発

- ISO 26262 システムの設計に役立つ資料

- ASIL Dまでの決定論的対応能力

- ASIL Dまでのハードウェア機能

- ±1.5mV の ADC 精度

- ピン・パッケージおよびソフトウェア互換のデバイス・フ アミリ

- スタッカブル・モニタ 16S (BQ79616-Q1、 BQ79656-Q1), 14S (BQ79614-Q1, BQ79654-Q1), 12S (BQ79612-Q1, BQ79652-Q1)

- スタンドアロン・モニタ 48V システム (BQ75614-Q1)

- 電圧、温度、診断用の冗長化パスを内蔵

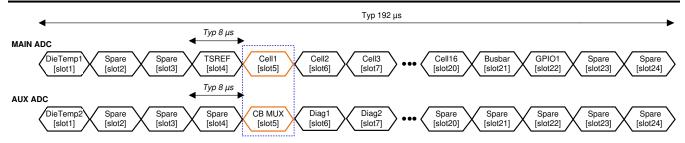

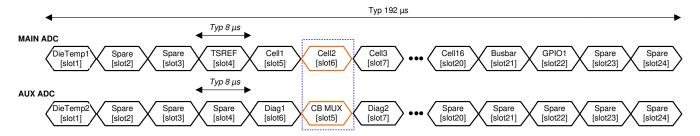

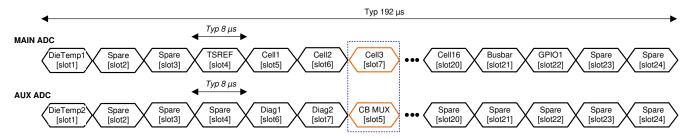

- すべてのセル・チャネルについて 128µs 以内にセル 電圧を高精度で測定

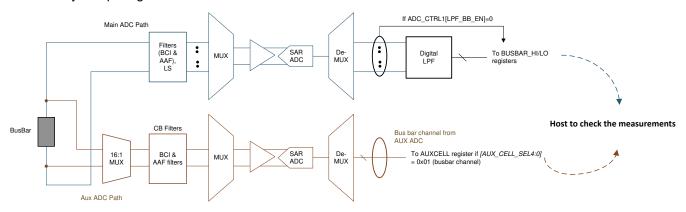

- 構成可能なポスト ADC デジタル・ローパス・フィルタを 内蔵

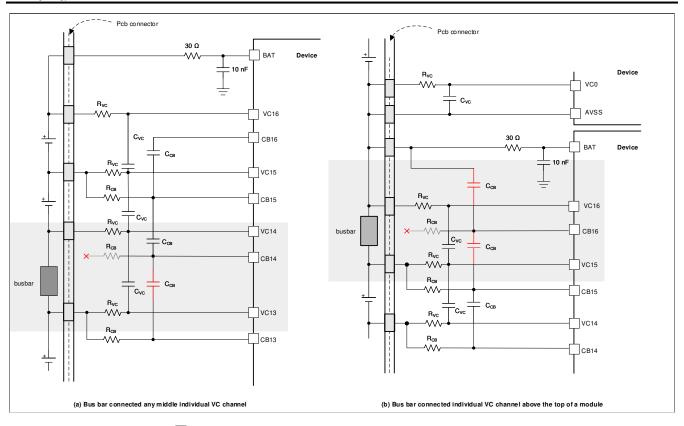

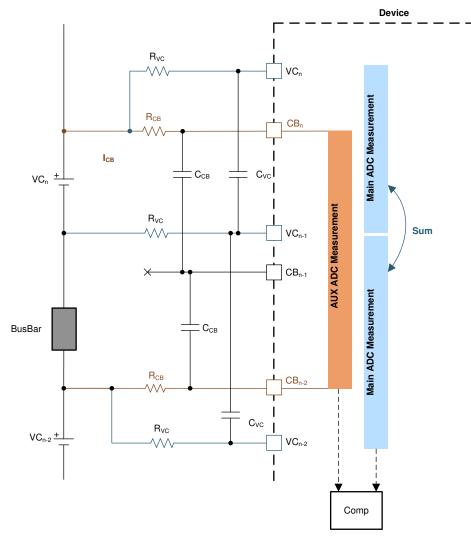

- バス・バーの接続と測定をサポート

- POR と同様のデバイス・リセットをエミュレートするホス ト制御のハードウェア・リセットを内蔵

- 内部セル平衡化をサポート

- 240mA の平衡化電流

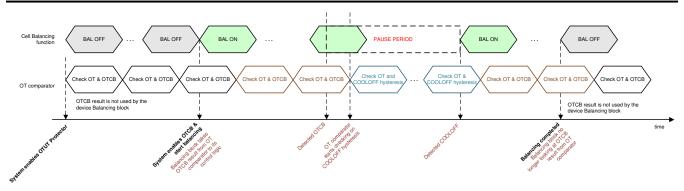

- 自動中断および再開制御付きの平衡化熱管理機

- 絶縁型差動デイジー・チェーン通信 (リング・アーキテ クチャにも対応可能)

- 通信ラインによる組み込みフォルト信号およびハートビ

- UART/SPI ホスト・インターフェイス / 通信ブリッジ・デ バイス BQ79600-Q1

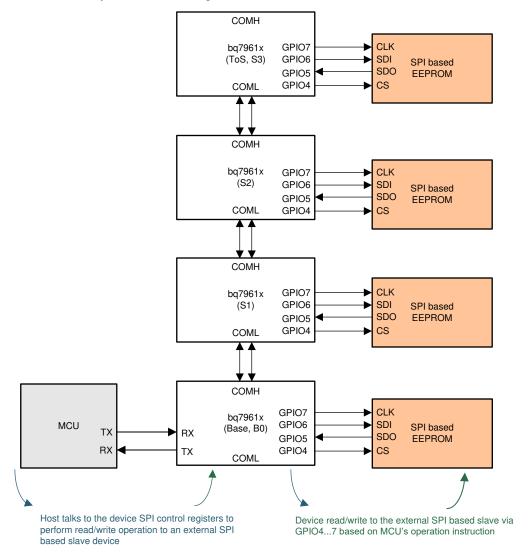

- **SPI** マスタを内蔵

# 2 アプリケーション

- ハイブリッドおよび電動パワートレイン・システムのバッ テリ管理システム (BMS)

- バッテリ管理システムを搭載したエネルギー貯蔵バッテ リ・パック

## 3 概要

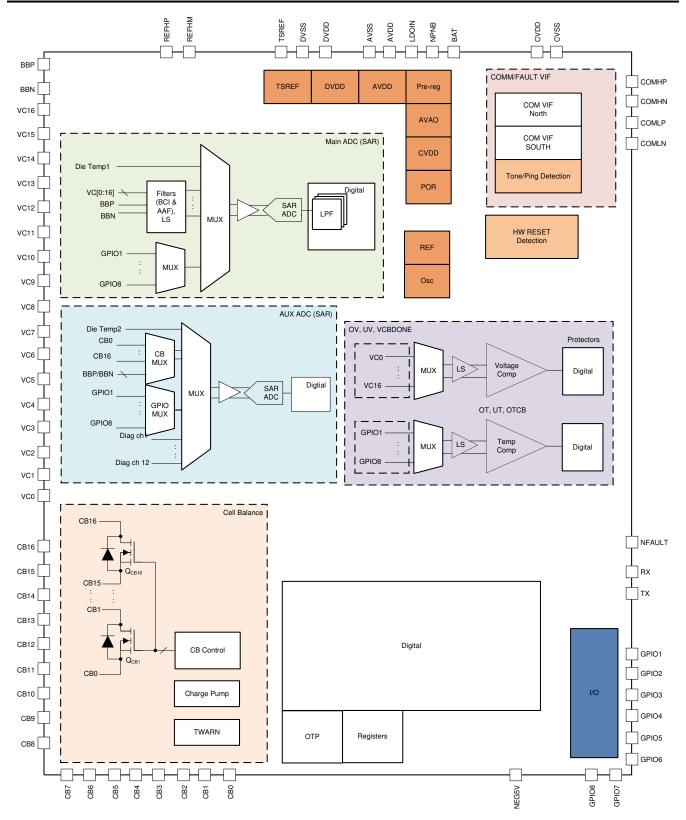

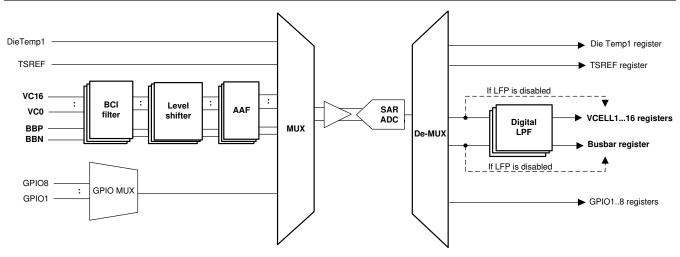

BQ79612-Q1 、BQ79614-Q1 、BQ79616-Q1 は、 HEV/EV の高電圧バッテリ管理システムで 12S、14S、 168 の各バッテリ・モジュールの高精度セル電圧測定を 200µs 未満で実現します。このモニタ・ファミリは、同じパッ ケージ・タイプでさまざまなチャネル・オプションを提供し、 ピン互換性を実現しているほか、確立されたソフトウェアと ハードウェアをあらゆるプラットフォームで再利用できま す。内蔵のフロントエンド・フィルタにより、単純な低電圧定 格の差動 RC フィルタをシステムのセル入力チャネルに 実装できます。内蔵ポスト ADC ローパス・フィルタにより、 フィルタ処理された (DC と同様の) 電圧を測定できるた め、充電状態 (SOC) をより的確に計算できます。このデ バイスは、温度監視機能を備えた自律的な内部セル平衡 化をサポートしており、平衡化を自動的に中断および再開 することで過熱状態を防止します。

#### 制品情報

|                     | ₹XHH IFI TX   |                 |

|---------------------|---------------|-----------------|

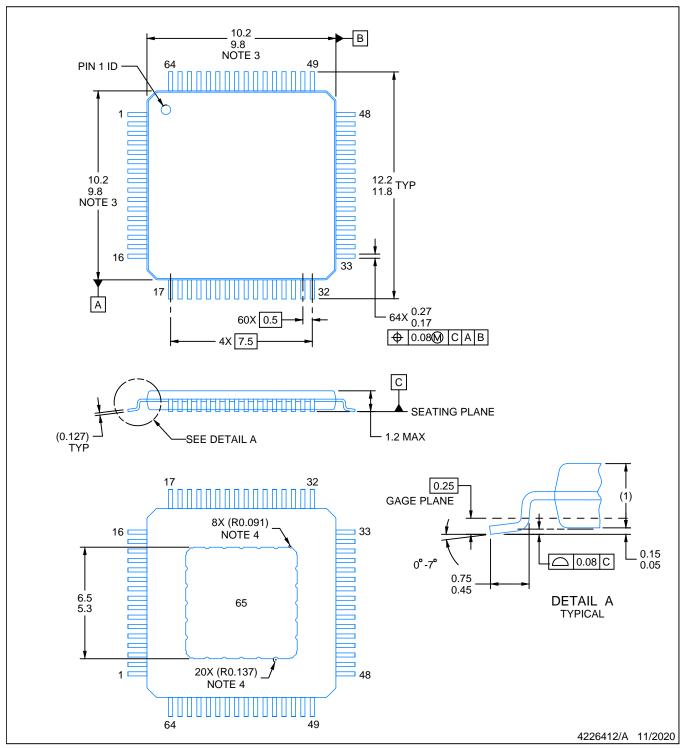

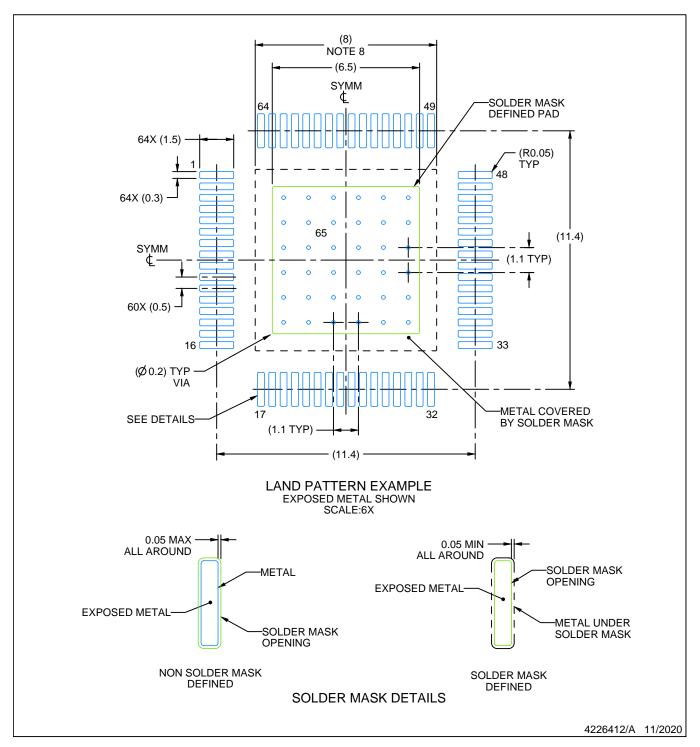

| 部品番号 <sup>(1)</sup> | パッケージ         | 本体サイズ (公称)      |

| BQ79612-Q1          |               |                 |

| BQ79614-Q1          | HTQFP (64 ピン) | 10.00mm×10.00mm |

| BQ79616-Q1          |               |                 |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

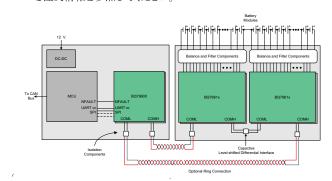

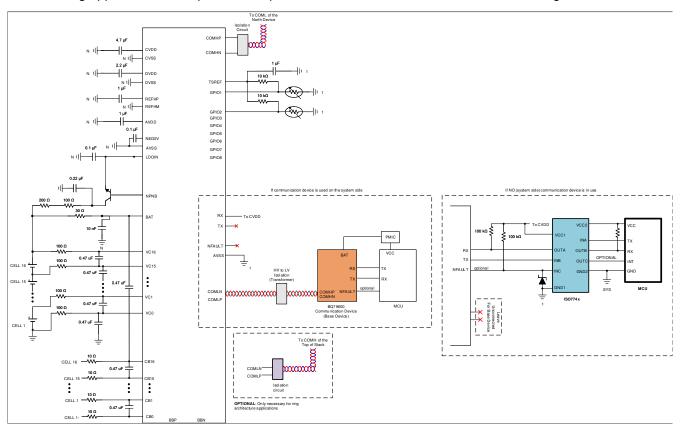

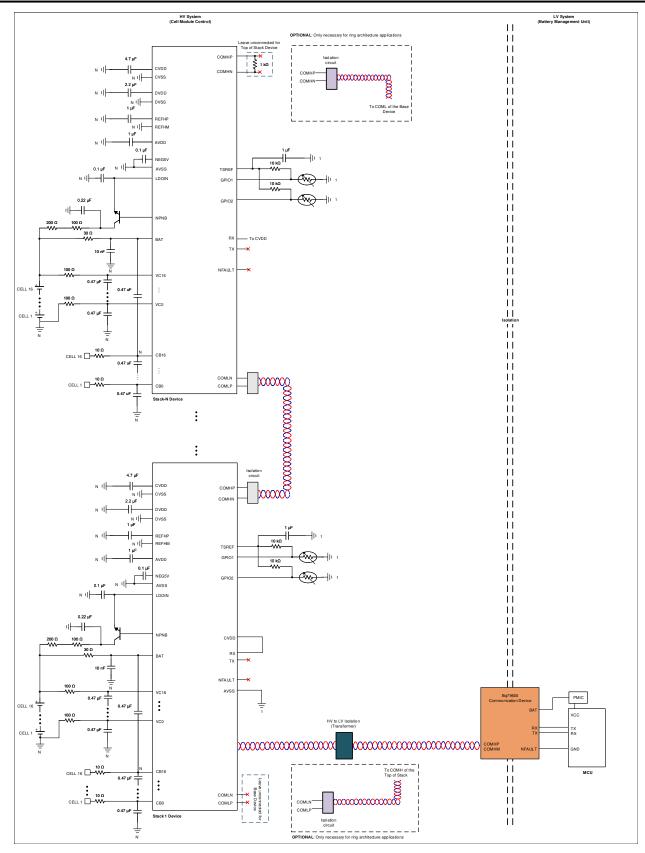

単純化したシステム図

# **Table of Contents**

| 1 特長                                 | 1 | 9.4 Device Functional Modes                    | 103               |

|--------------------------------------|---|------------------------------------------------|-------------------|

| 2 アプリケーション                           |   | 9.5 Register Maps                              | 112               |

| 3 概要                                 |   | 10 Application and Implementation              | 19                |

| 4 Revision History                   |   | 10.1 Application Information                   | 19 <sup>2</sup>   |

| 5 概要 (続き)                            |   | 10.2 Typical Applications                      | 191               |

| 6 Device Comparison Table            |   | 11 Power Supply Recommendations                | 203               |

| 7 Pin Configuration and Functions    |   | 12 Layout                                      | 204               |

| 8 Specifications                     |   | 12.1 Layout Guidelines                         | 204               |

| 8.1 Absolute Maximum Ratings         |   | 12.2 Layout Example                            | 207               |

| 8.2 ESD Ratings                      |   | 13 Device and Documentation Support            | <mark>21</mark> ′ |

| 8.3 Recommended Operating Conditions |   | 13.1 Device Support                            | <mark>21</mark> ′ |

| 8.4 Thermal Information              |   | 13.2 Receiving Notification of Documentation L | Jpdates 21        |

| 8.5 Electrical Characteristics       |   | 13.3 サポート・リソース                                 | 21 <sup>2</sup>   |

| 8.6 Timing Requirements              |   | 13.4 Trademarks                                | 21 <sup>2</sup>   |

| 8.7 Typical Characteristics          |   | 13.5 Electrostatic Discharge Caution           | <mark>21</mark>   |

| 9 Detailed Description               |   | 13.6 Glossary                                  |                   |

| 9.1 Overview                         |   | 14 Mechanical, Packaging, and Orderable        |                   |

| 9.2 Functional Block Diagram         |   | Information                                    | 212               |

| 9.3 Feature Description              |   |                                                |                   |

|                                      |   |                                                |                   |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision C (June 2021) to Revision D (September 2022)                                                    | Page             |

|---|----------------------------------------------------------------------------------------------------------------------|------------------|

| • | 制限付きから公開に変更                                                                                                          | 1                |

| • | Additional supply current when TSREF is enabled                                                                      | 12               |

| • | DVDD output voltage                                                                                                  | 1 <mark>2</mark> |

| • | NEG5V pin voltage                                                                                                    | 12               |

| • | Diagnostic measurements resolution                                                                                   | 12               |

| • | Added paragraph to セクション 9.3.1.2                                                                                     | 24               |

| • | Changed 380µs to 1.35ms in セクション 9.3.1.6                                                                             | 2 <mark>5</mark> |

| • | Added Note to セクション 9.3.2.1.3.1                                                                                      | 30               |

| • | Deleted as in the Main ADC path and added Note to セクション 9.3.2.2.1.1                                                  | 32               |

| • | Changed text in セクション 9.3.2.3                                                                                        | 36               |

| • | Changed latch to load in セクション 9.3.3.3.3                                                                             | 42               |

| • | Added text to セクション 9.3.5                                                                                            | 48               |

| • | Changed above to below in 🗵 9-23                                                                                     | 49               |

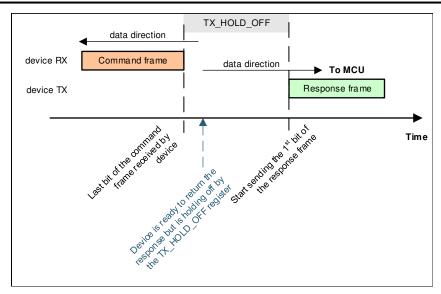

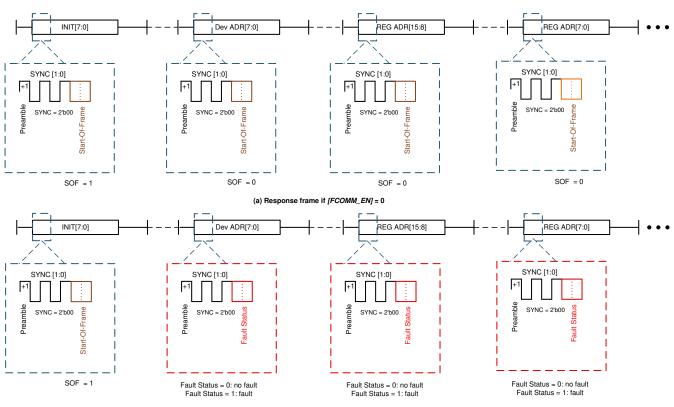

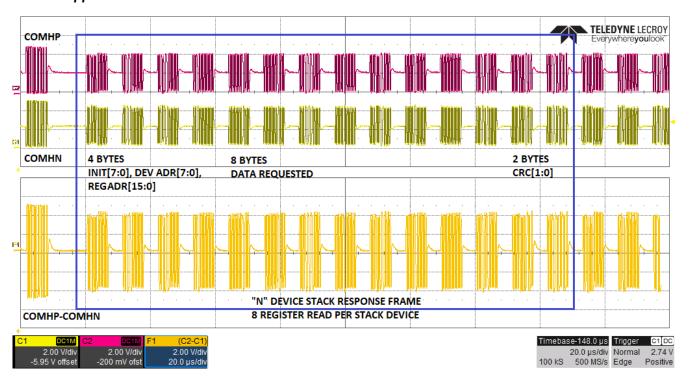

| • | Changed ☑ 9-25 to show response frame start time is after TX_HOLF_OFF expiration time                                | 50               |

| • | Changed Read to Write in 表 9-9                                                                                       | 52               |

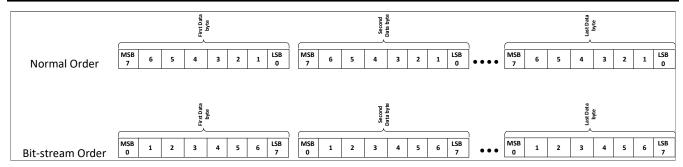

| • | Changed 🗵 9-27 to the correct bit-width per byte                                                                     | 54               |

| • | Added $t_{proq-otp}$ = 100ms and During this time no data communications is allowed to step 4 in $\frac{1}{5}$ 9-26. | 80               |

| • | Changed BQ79606-Q1 to BQ7961X-Q1 in セクション 9.3.6.4                                                                    |                  |

| • | Deleted Rcb resistor in ⊠ 9-56                                                                                       |                  |

| • | Multiple bits in セクション 9.5.4.3.11 updated with Bit is self-cleared and added text                                    | 129              |

| • | Changed bit setting 11 to Reserved in セクション 9.5.4.5.1                                                                |                  |

| • | Changed bit 6 to Reserved and changed bit 5 to 0 = Dynamic Alignment in セクション 9.5.4.5.8                              |                  |

| • | Added sourced from TSREF regulator voltage and Default Reset setting 4% to COOLOFF[2:0] and so                       |                  |

|   | from TSREF regulator voltage and Default Reset setting 24% to OTCB_THR[3:0] in セクション 9.5.4.7.                        |                  |

| • | Added This bit is self clearing to BAL_TIME_GO in セクション 9.5.4.7.8                                                    |                  |

| • | Added sourced from TSREF regulator voltage, and Default Reset setting 80% to UT_THR[2:0] and so                      |                  |

|   | from TSREF regulator voltage. and Default Reset setting 39% to OT THR[4:0] in セクション 9.5.4.8.5.                       |                  |

### www.tij.co.jp

| ・ Added Note to UART_MIRROR_EN in セクション 9.5.4.14.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • Updated correct register name                | s in セクション 9.5.4.13.3                     | 170      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|----------|

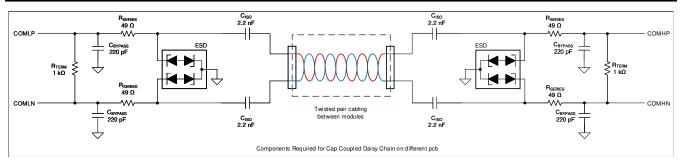

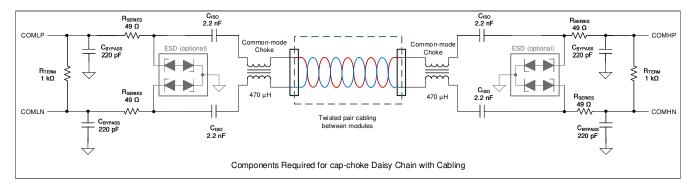

| ・ Changed cap value to 2.2 µF and fixed isolator pinout in 図 10-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                                           |          |

| ・ Changed content, 図 10-7, 図 10-8, and 図 10-9 in セクション 10.2.1.2.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |                                           |          |

| ・ Changed cap values to 2.2 µF in 図 10-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |                                           |          |

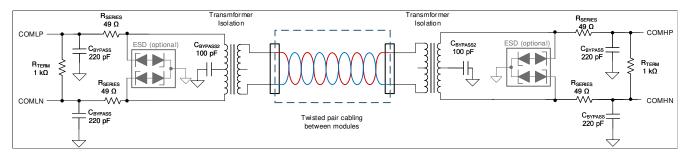

| Changes from Revision B (April 2021) to Revision C (June 2021)  BQ79614-Q1 と BQ79612-Q1 を「製品プレビュー」から「量産データ」に変更  Added (2) (3)  Added (2)  Added (3)  Added (3)  Changed CUST_CRC_LO reset value from 0x73 to 0xF3 in セクション 9.5.4.5.7  Added content to MAIN_MODE[1:0] description in セクション 9.5.4.5.7  Added Content to AUX_MODE[1:0] description in セクション 9.5.4.5.9  Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1  Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-5  Changes from Revision * (August 2020) to Revision A (December 2020)                                                                                                                                                                      |                                                |                                           |          |

| ・ BQ79614-Q1 と BQ79612-Q1 を「製品プレビュー」から「量産データ」に変更 1  Changes from Revision A (December 2020) to Revision B (April 2021) Page ・ Added (2) (3) 11 ・ Added (2) 11 ・ Added (3) 11 ・ Added (3) 11 ・ Added MAIN_ADC_CAL1, MAIN_ADC_CAL2 register to セクション 9.3.2.1.3.1 30 ・ Changed CUST_CRC_LO reset value from 0x73 to 0xF3 in セクション 9.5.1 112 ・ Added content to MAIN_MODE[1:0] description in セクション 9.5.4.5.7 136 ・ Added content to AUX_MODE[1:0] description in セクション 9.5.4.5.9 136 ・ Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1 168 ・ Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4 197 ・ Changed content for Transformer description and added content to ESD diode (optional) description in 表 10-5 197 |                                                |                                           |          |

| Changes from Revision A (December 2020) to Revision B (April 2021)  • Added (2) (3) (11)  • Added (3) (11)  • Added (3) (11)  • Added MAIN_ADC_CAL1, MAIN_ADC_CAL2 register to セクション 9.3.2.1.3.1 (11)  • Changed CUST_CRC_LO reset value from 0x73 to 0xF3 in セクション 9.5.1 (11)  • Added content to MAIN_MODE[1:0] description in セクション 9.5.4.5.7 (13)  • Added content to AUX_MODE[1:0] description in セクション 9.5.4.5.9 (13)  • Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1 (16)  • Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4 (19)  • Changes from Revision * (August 2020) to Revision A (December 2020)                                                                                              | Changes from Revision B (April                 | 2021) to Revision C (June 2021)           | Page     |

| * Added (2) (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • BQ79614-Q1 ≥ BQ79612-Q1                      | を「製品プレビュー」から「量産データ」に変更                    | 1        |

| * Added (2) (3) 11 * Added (2) 11 * Added (3) 11 * Added (3) 11 * Added MAIN_ADC_CAL1, MAIN_ADC_CAL2 register to セクション 9.3.2.1.3.1 11 * Added CUST_CRC_LO reset value from 0x73 to 0xF3 in セクション 9.5.1 112 * Added content to MAIN_MODE[1:0] description in セクション 9.5.4.5.7 136 * Added content to AUX_MODE[1:0] description in セクション 9.5.4.5.9 136 * Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1 168 * Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4 197 * Changed content for Transformer description and added content to ESD diode (optional) description in 表 10-5 197  Changes from Revision * (August 2020) to Revision A (December 2020)                                                          | Changes from Revision A (Dece                  | ember 2020) to Revision B (April 2021)    | Page     |

| ・ Added <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |                                           | 11       |

| ・ Added (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |                                           |          |

| <ul> <li>Changed CUST_CRC_LO reset value from 0x73 to 0xF3 in セクション 9.5.1</li> <li>Added content to MAIN_MODE[1:0] description in セクション 9.5.4.5.7</li> <li>Added content to AUX_MODE[1:0] description in セクション 9.5.4.5.9</li> <li>Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1</li> <li>Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4</li> <li>Changed content for Transformer description and added content to ESD diode (optional) description in 表 10-5</li> <li>Changes from Revision * (August 2020) to Revision A (December 2020)</li> </ul>                                                                                                                                                         |                                                |                                           |          |

| <ul> <li>Added content to MAIN_MODE[1:0] description in セクション 9.5.4.5.7</li> <li>Added content to AUX_MODE[1:0] description in セクション 9.5.4.5.9</li> <li>Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1</li> <li>Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4</li> <li>Changed content for Transformer description and added content to ESD diode (optional) description in 表 10-5</li> <li>Changes from Revision * (August 2020) to Revision A (December 2020)</li> </ul>                                                                                                                                                                                                                                   | • Added MAIN_ADC_CAL1, MA                      | IN_ADC_CAL2 register to セクション 9.3.2.1.3.1 | 30       |

| <ul> <li>Added content to AUX_MODE[1:0] description in セクション 9.5.4.5.9</li> <li>Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1</li> <li>Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4</li> <li>Changed content for Transformer description and added content to ESD diode (optional) description in 表 10-5</li> <li>Changes from Revision * (August 2020) to Revision A (December 2020)</li> </ul>                                                                                                                                                                                                                                                                                                           | <ul> <li>Changed CUST_CRC_LO rese</li> </ul>   | et value from 0x73 to 0xF3 in セクション 9.5.1 | 112      |

| <ul> <li>Changed From: This bit is set if [MSK_COMP] = 1 To: This bit is set if [MSK_COMP] = 0 for FAULT_COMP_ADC = in セクション 9.5.4.13.1</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>Added content to MAIN_MODE</li> </ul> | 트[1:0] description in セクション 9.5.4.5.7     | 136      |

| FAULT_COMP_ADC = in セクション 9.5.4.13.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |                                           |          |

| Added content to Common-mode choke and ESD diode (optional) descriptions in 表 10-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                           |          |

| Changed content for Transformer description and added content to ESD diode (optional) description in 表 10-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |                                           |          |

| 10-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |                                           |          |

| Changes from Revision * (August 2020) to Revision A (December 2020) Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |                                           |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                           |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                           | <u> </u> |

# 5 概要 (続き)

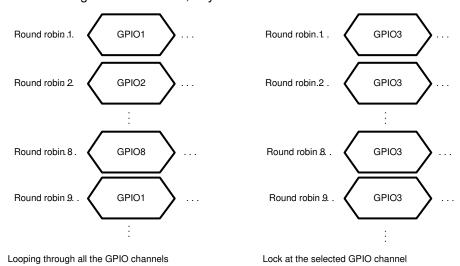

絶縁型双方向デイジー・チェーン・ポートを内蔵することでコンデンサ絶縁と変圧器絶縁の両方をサポートしているため、 xEV パワートレイン・システムで一般的に使用される集中または分散アーキテクチャ用の最も効率の高い部品を使用できます。このデバイスは、外部サーミスタ測定に使用できる8つの GPIO (補助入力)も備えています。

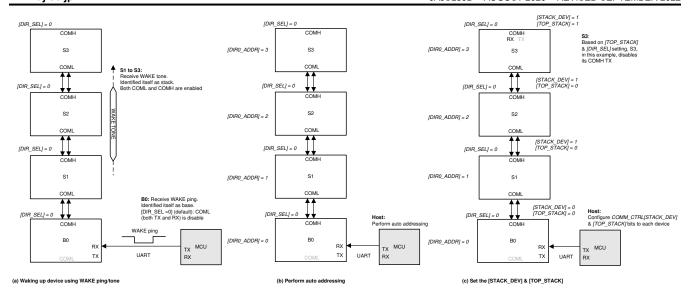

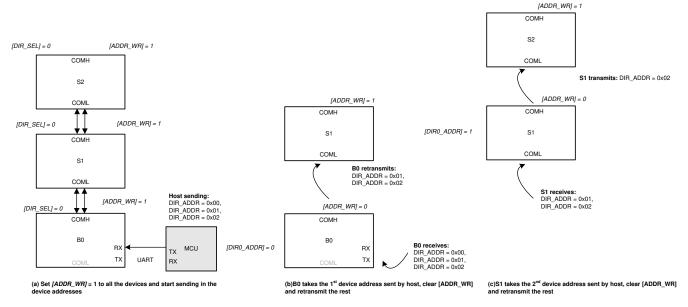

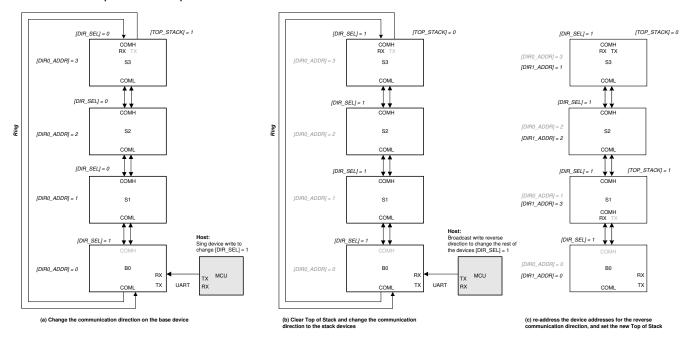

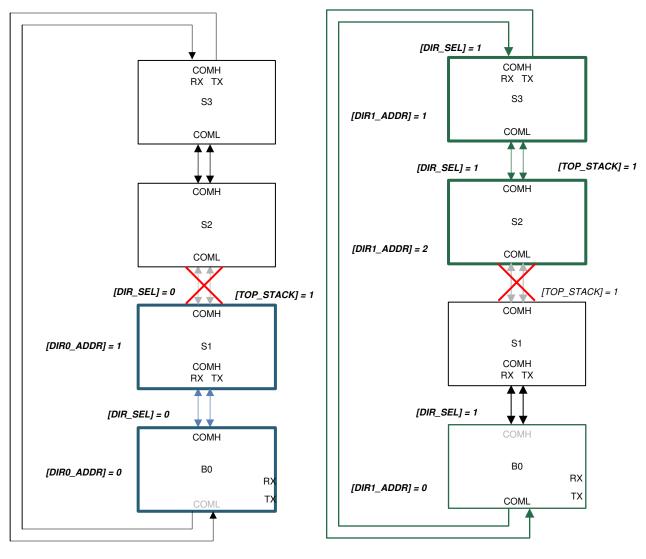

BQ7961x-Q1 ファミリのデバイス へのホスト通信は、本デバイスの専用 UART インターフェイスまたは通信ブリッジ・デバイス BQ79600 経由で接続できます。さらに、絶縁型差動デイジー・チェーン通信インターフェイスにより、ホストは単一のインターフェイスを介してバッテリ・スタック全体と通信できます。通信ラインが切断された場合、デイジー・チェーン通信インターフェイスはリング・アーキテクチャに構成でき、ホストはスタックのどちらの端にあるデバイスとも通信できます。

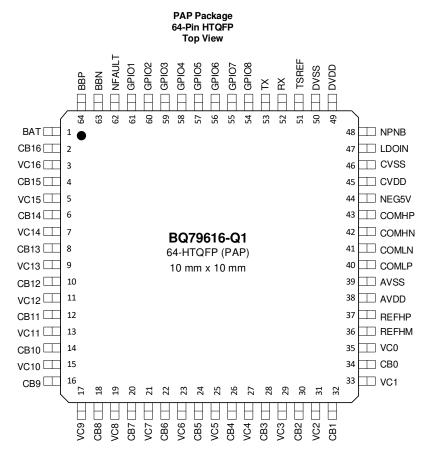

# **6 Device Comparison Table**

| DEVICE     | STATUS          | DESCRIPTION                        |

|------------|-----------------|------------------------------------|

| BQ79616-Q1 | Production Data | Supports 6S to 16S battery modules |

| BQ79614-Q1 | Production Data | Supports 6S to 14S battery modules |

| BQ79612-Q1 | Production Data | Supports 6S to 12S battery modules |

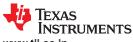

# 7 Pin Configuration and Functions

### 表 7-1. Pin Functions

|         | PIN     |         |     |      |                                                                                                                                                                                                                                     |

|---------|---------|---------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | NAME    |         | N.  | TYPE | DESCRIPTION                                                                                                                                                                                                                         |

| BQ79616 | BQ79614 | BQ79612 | No. |      |                                                                                                                                                                                                                                     |

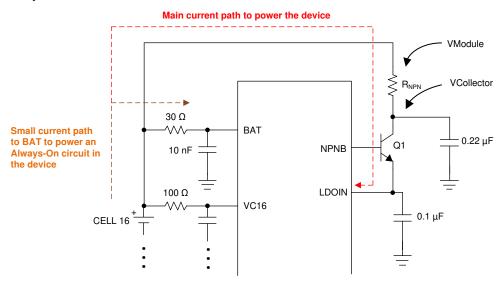

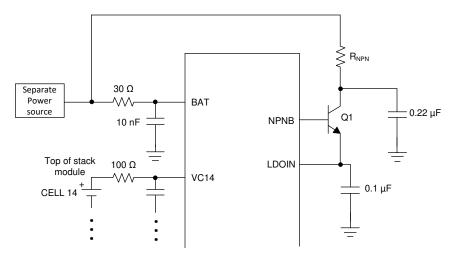

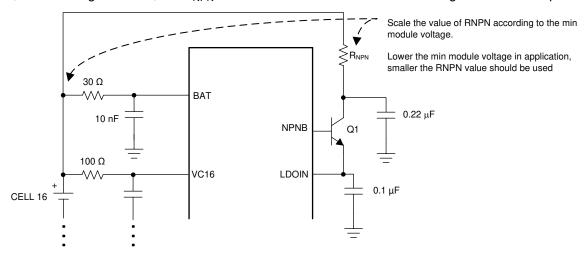

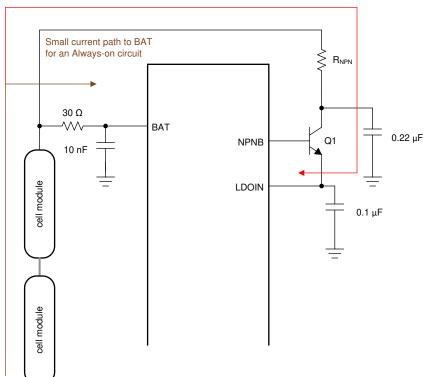

| BAT     | BAT     | BAT     | 1   | Р    | Power supply input and top of module measurement input. Connect to the top cell of the battery module.                                                                                                                              |

| NPNB    | NPNB    | NPNB    | 48  | Р    | Connect to the base of an external NPN transistor.                                                                                                                                                                                  |

| LDOIN   | LDOIN   | LDOIN   | 47  | Р    | 6-V preregulated analog power supply input/sense pin. Connect to the emitter of the external NPN transistor and connect a 0.1-µF decoupling capacitor to CVSS.                                                                      |

| AVDD    | AVDD    | AVDD    | 38  | Р    | 5-V regulated output. AVDD supplies the internal analog circuits. Bypass AVDD with a capacitor to AVSS.                                                                                                                             |

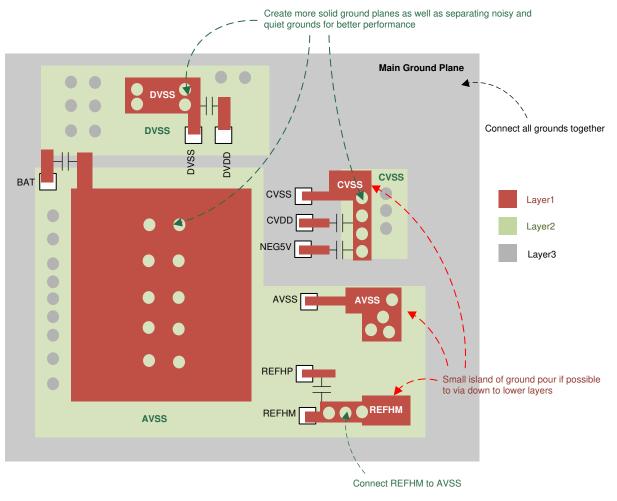

| AVSS    | AVSS    | AVSS    | 39  | GND  | Analog ground. Ground connection for internal analog circuits. Connect DVSS, CVSS, REFHM, and AVSS externally.                                                                                                                      |

| NEG5V   | NEG5V   | NEG5V   | 44  | Р    | Negative 5-V charge pump used for daisy chain and Main ADC. Connect with a capacitor to CVSS.                                                                                                                                       |

| DVDD    | DVDD    | DVDD    | 49  | Р    | 1.8-V regulated output. DVDD supplies the internal digital circuits. Bypass DVDD with a capacitor to DVSS.                                                                                                                          |

| DVSS    | DVSS    | DVSS    | 50  | GND  | Digital ground. Ground connection for internal digital logics. Connect DVSS, CVSS, REFHM, and AVSS externally.                                                                                                                      |

| CVDD    | CVDD    | CVDD    | 45  | Р    | 5-V daisy chain communication and I/Os power supply. CVDD supplies the stack daisy chain communication transceiver circuit and the I/O pins. This power supply also supports an additional 10-mA external load in ACTIVE and SLEEP. |

| CVSS    | cvss    | CVSS    | 46  | GND  | Daisy chain communication ground. Ground connection for internal daisy chain transceivers. Connect DVSS, CVSS, REFHM, and AVSS externally.                                                                                          |

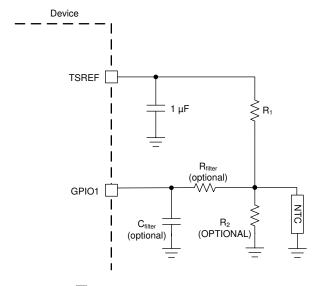

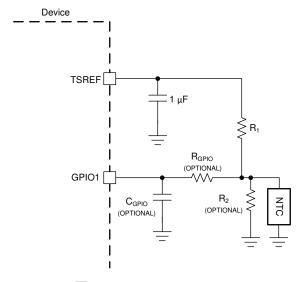

| TSREF   | TSREF   | TSREF   | 51  | Р    | 5-V bias voltage for NTC thermistor. Connect TSREF to the top of the NTC resistor divider network to the GPIOs when they are configured for NTC temperature monitoring. Bypass TSREF with a capacitor to CVSS.                      |

| REFHP   | REFHP   | REFHP   | 37  | Р    | Precision reference output pin. Bypass with a capacitor to REFHM.                                                                                                                                                                   |

| REFHM   | REFHM   | REFHM   | 36  | GND  | Precision reference ground. Ground connection for the internal precision reference. Connect DVSS, CVSS, REFHM, and AVSS externally.                                                                                                 |

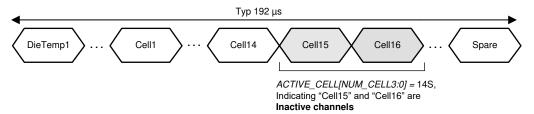

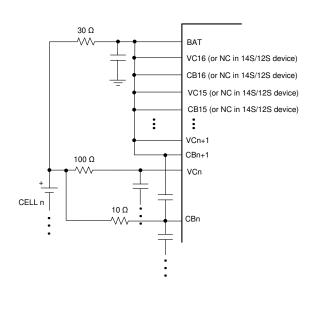

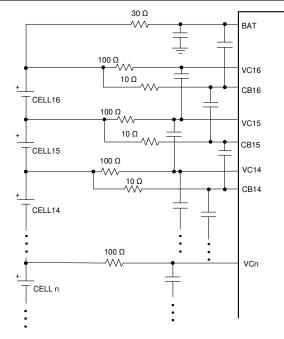

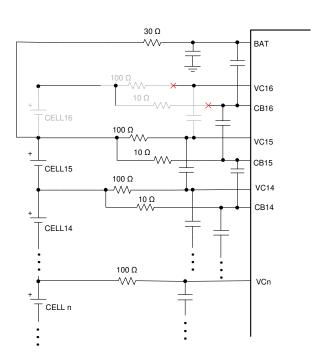

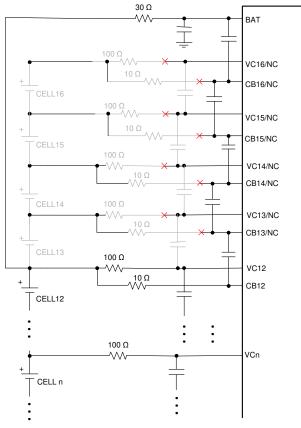

| VC16    | NC      | NC      | 3   | I    | Cell voltage sense input. Connect to the positive terminal of cell 16. Connect a differential RC filter to VC15. Tie unused NC pins in BQ79614 and BQ79612 to BAT pin as explained in Cell Connections.                             |

| VC15    | NC      | NC      | 5   | I    | Cell voltage sense input. Connect to the positive terminal of cell 15. Connect a differential RC filter to VC14.Tie unused NC pins in BQ79614 and BQ79612 to BAT pin as explained in Cell Connections.                              |

| VC14    | VC14    | NC      | 7   | I    | Cell voltage sense input. Connect to the positive terminal of cell 14. Connect a differential RC filter to VC13. Tie unused NC pins in BQ79612 to BAT pin as explained in Cell Connections.                                         |

| VC13    | VC13    | NC      | 9   | I    | Cell voltage sense input. Connect to the positive terminal of cell 13. Connect a differential RC filter to VC12. Tie unused NC pins in BQ79612 to BAT pin as explained in Cell Connections.                                         |

| VC12    | VC12    | VC12    | 11  | I    | Cell voltage sense input. Connect to the positive terminal of cell 12. Connect a differential RC filter to VC11.                                                                                                                    |

| VC11    | VC11    | VC11    | 13  | I    | Cell voltage sense input. Connect to the positive terminal of cell 11. Connect a differential RC filter to VC10.                                                                                                                    |

| VC10    | VC10    | VC10    | 15  | I    | Cell voltage sense input. Connect to the positive terminal of cell 10. Connect a differential RC filter to VC9.                                                                                                                     |

| VC9     | VC9     | VC9     | 17  | I    | Cell voltage sense input. Connect to the positive terminal of cell 9. Connect a differential RC filter to VC8.                                                                                                                      |

| VC8     | VC8     | VC8     | 19  | I    | Cell voltage sense input. Connect to the positive terminal of cell 8. Connect a differential RC filter to VC7.                                                                                                                      |

| VC7     | VC7     | VC7     | 21  | I    | Cell voltage sense input. Connect to the positive terminal of cell 7. Connect a differential RC filter to VC6.                                                                                                                      |

| VC6     | VC6     | VC6     | 23  | I    | Cell voltage sense input. Connect to the positive terminal of cell 6. Connect a differential RC filter to VC5.                                                                                                                      |

| VC5     | VC5     | VC5     | 25  | I    | Cell voltage sense input. Connect to the positive terminal of cell 5. Connect a differential RC filter to VC4.                                                                                                                      |

| VC4     | VC4     | VC4     | 27  | I    | Cell voltage sense input. Connect to the positive terminal of cell 4. Connect a differential RC filter to VC3.                                                                                                                      |

| VC3     | VC3     | VC3     | 29  | I    | Cell voltage sense input. Connect to the positive terminal of cell 3. Connect a differential RC filter to VC2.                                                                                                                      |

# 表 7-1. Pin Functions (continued)

| PIN     |         |         |     | 22 7-1. First unctions (continueu) |                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------|---------|---------|-----|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | NAME    |         |     | TYPE                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |

| BQ79616 | BQ79614 | BQ79612 | No. |                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |

| VC2     | VC2     | VC2     | 31  | I                                  | Cell voltage sense input. Connect to the positive terminal of cell 2. Connect a differential RC filter to VC1.                                                                                                                                                                                                                                                              |  |

| VC1     | VC1     | VC1     | 33  | I                                  | Cell voltage sense input. Connect to the positive terminal of cell 1. Connect a differential RC filter to VC0.                                                                                                                                                                                                                                                              |  |

| VC0     | VC0     | VC0     | 35  | I                                  | Cell voltage sense input. Connect to the negative terminal of cell 1. Connect a differential RC filter to AVSS.                                                                                                                                                                                                                                                             |  |

| CB16    | NC      | NC      | 2   | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 16 with a differential RC filter to CB15. The filter resistor also sets the internal balance current. Tie unused CB16 pin via RC to BAT pin and tie unused NC pins in BQ79614 and BQ79612 to BAT pin as explained in Cell Connections. |  |

| CB15    | NC      | NC      | 4   | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 15 with a differential RC filter to CB14. The filter resistor also sets the internal balance current. Tie unused NC pins in BQ79614 and BQ79612 to BAT pin as explained in Cell Connections.                                           |  |

| CB14    | CB14    | NC      | 6   | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 14 with a differential RC filter to CB13. The filter resistor also sets the internal balance current. Tie unused NC pins in BQ79612 to BAT pin as explained in Cell Connections.                                                       |  |

| CB13    | CB13    | NC      | 8   | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 13 with a differential RC filter to CB12. The filter resistor also sets the internal balance current. Tie unused NC pins in BQ79612 to BAT pin as explained in Cell Connections.                                                       |  |

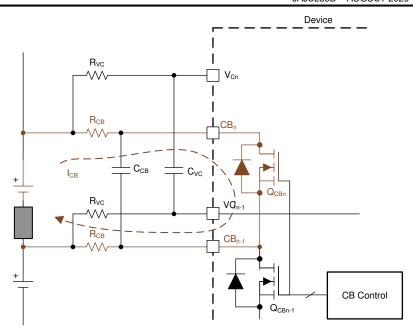

| CB12    | CB12    | CB12    | 10  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 12 with a differential RC filter to CB11. The filter resistor also sets the internal balance current.                                                                                                                                  |  |

| CB11    | CB11    | CB11    | 12  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 11 with a differential RC filter to CB10. The filter resistor also sets the internal balance current.                                                                                                                                  |  |

| CB10    | CB10    | CB10    | 14  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 10 with a differential RC filter to CB9. The filter resistor also sets the internal balance current.                                                                                                                                   |  |

| СВ9     | CB9     | CB9     | 16  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 9 with a differential RC filter to CB8. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB8     | CB8     | CB8     | 18  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 8 with a differential RC filter to CB7. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB7     | CB7     | CB7     | 20  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 7 with a differential RC filter to CB6. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB6     | CB6     | CB6     | 22  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 6 with a differential RC filter to CB5. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB5     | CB5     | CB5     | 24  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 5 with a differential RC filter to CB4. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB4     | CB4     | CB4     | 26  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 4 with a differential RC filter to CB3. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB3     | CB3     | CB3     | 28  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 3 with a differential RC filter to CB2. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB2     | CB2     | CB2     | 30  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 2 with a differential RC filter to CB1. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB1     | CB1     | CB1     | 32  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect this pin to the positive terminal of cell 1 with a differential RC filter to CB0. The filter resistor also sets the internal balance current.                                                                                                                                    |  |

| CB0     | CB0     | CB0     | 34  | I/O                                | Cell balance connection. This pin is connected to the internal cell balancing FET. Connect to the negative terminal of cell 1 with differential RC filter to AVSS. The filter resistor also sets the internal balance current.                                                                                                                                              |  |

### 表 7-1. Pin Functions (continued)

|         | Р       | IN      |     |      |                                                                                                                                                                                                                 |  |

|---------|---------|---------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | NAME    |         | No. | TYPE | DESCRIPTION                                                                                                                                                                                                     |  |

| BQ79616 | BQ79614 | BQ79612 | NO. |      |                                                                                                                                                                                                                 |  |

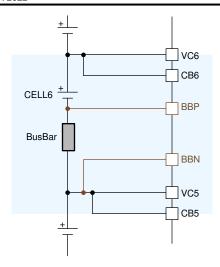

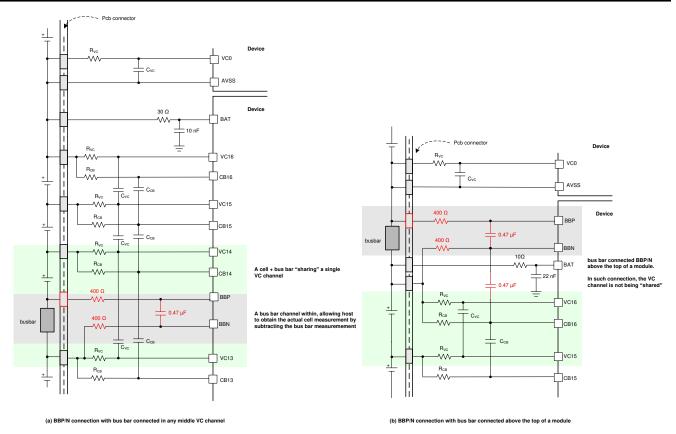

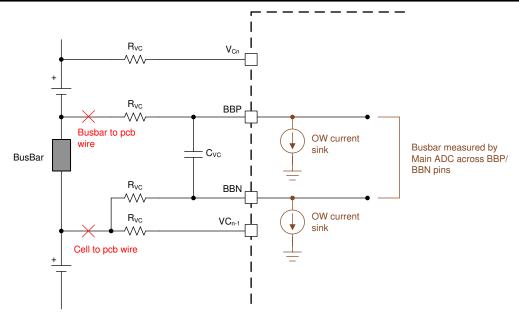

| ВВР     | BBP     | BBP     | 64  | I    | Bus bar connection. With BBP and BBN connecting to each end of a bus bar, this channel provides a differential input to the ADC measurement with a 5x gain.                                                     |  |

| BBN     | BBN     | BBN     | 63  | 1    | Bus bar connection. With BBP and BBN connecting to each end of a bus bar, this channel provides a differential input to the ADC measurement with a 5x gain.                                                     |  |

| RX      | RX      | RX      | 52  | 1    | UART receiver input. Pull up to CVDD with an external resistor and connect the device RX to the TX output of the host MCU. If unused (for example, for stack devices), connect RX to CVDD.                      |  |

| TX      | TX      | TX      | 53  | 0    | UART transmitter output. Connect device TX to RX input of the host MCU and will be pulled up from the host side. If unused (for example, for stack devices), leave it floating.                                 |  |

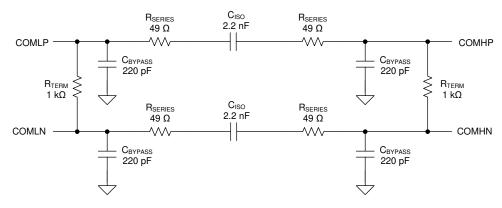

| COMHP   | COMHP   | COMHP   | 43  | I/O  | Vertical bidirectional communication interface for daisy chain connection. High side (north                                                                                                                     |  |

| COMHN   | COMHN   | COMHN   | 42  | I/O  | side) differential I/O. Will connect to the low side (south side) COMLP and COMLN of the lower adjacent device in the daisy chain configuration. If unused, connect COMHP and COMHN with a $1k\Omega$ resistor. |  |

| COMLP   | COMLP   | COMLP   | 40  | I/O  | Vertical bidirectional communication interface for daisy chain connection. Low side (south                                                                                                                      |  |

| COMLN   | COMLN   | COMLN   | 41  | I/O  | side) differential I/O. Will connect to the high side (north side) COMHP and COMHN of the upper adjacent device in the daisy chain configuration. If unused, connect COMLP and COMLN with a 1kΩ resistor.       |  |

| NFAULT  | NFAULT  | NFAULT  | 62  | 0    | Fault indication output. Active low. If used on the base device, pull up NFAULT to CVDD with a pullup resistor and connect NFAULT to host MCU GPIO. If unused, leave it unconnected.                            |  |

| GPIO1   | GPIO1   | GPIO1   | 61  | I/O  | General purpose input/output, configuration options are:                                                                                                                                                        |  |

| GPIO2   | GPIO2   | GPIO2   | 60  | I/O  | For external NTC thermistor connection, connect NTC thermistor to the pin and pull up                                                                                                                           |  |

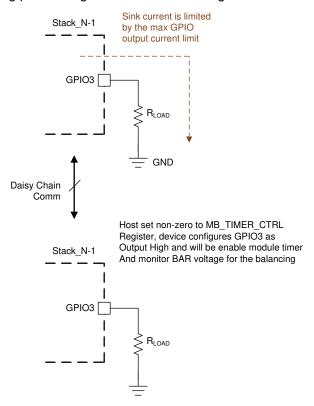

| GPIO3   | GPIO3   | GPIO3   | 59  | I/O  | to TSREF. Used as input to ADC and OT and UT hardware comparators.                                                                                                                                              |  |

| GPIO4   | GPIO4   | GPIO4   | 58  | I/O  | For external DC voltage measurement, configured as input to ADC.                                                                                                                                                |  |

| GPIO5   | GPIO5   | GPIO5   | 57  | I/O  | Generic digital input/output.                                                                                                                                                                                   |  |

| GPIO6   | GPIO6   | GPIO6   | 56  | I/O  | Use as I/O for SPI master.                                                                                                                                                                                      |  |

| GPIO7   | GPIO7   | GPIO7   | 55  | I/O  |                                                                                                                                                                                                                 |  |

| GPIO8   | GPIO8   | GPIO8   | 54  | I/O  |                                                                                                                                                                                                                 |  |

# 8 Specifications

# 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                       |                                                                           | MIN  | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------------|------|------|------|

| Input Voltage         | BAT, VC* (except VC0), CB* (except CB0), NFAULT, BBP, BBN to AVSS (2) (3) | -0.3 | 100  | V    |

|                       | CB0, VC0 to AVSS                                                          | -0.3 | 5.5  | V    |

|                       | VCn to VCn-1, n = 1 to 16 (2)                                             | -80  | 80   | V    |

|                       | CBn to CBn-1, n = 1 to 16 (3)                                             | -0.3 | 16   | V    |

|                       | BBP to BBN                                                                | -80  | 80   | V    |

|                       | LDOIN to AVSS                                                             | -0.3 | 9    | V    |

|                       | NPNB to AVSS                                                              | -0.3 | 10   | V    |

|                       | AVDD to AVSS                                                              | -0.3 | 5.5  | V    |

|                       | DVDD to DVSS                                                              | -0.3 | 1.98 | V    |

|                       | CVDD to CVSS                                                              | -0.3 | 6    | V    |

|                       | TSREF to AVSS                                                             | -0.3 | 5.5  | V    |

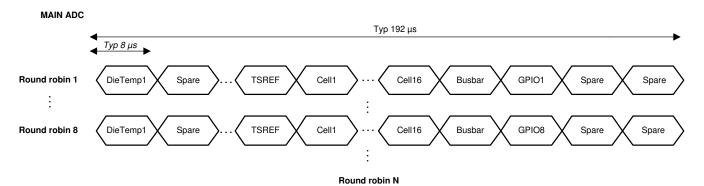

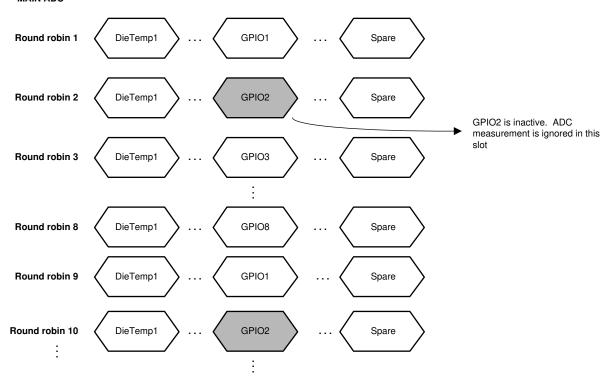

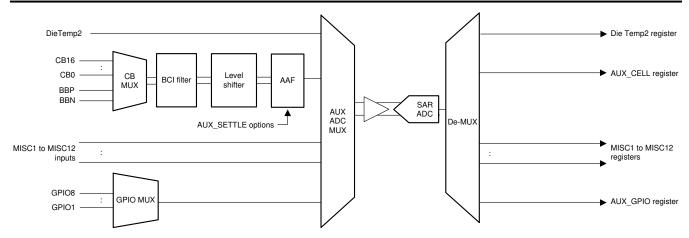

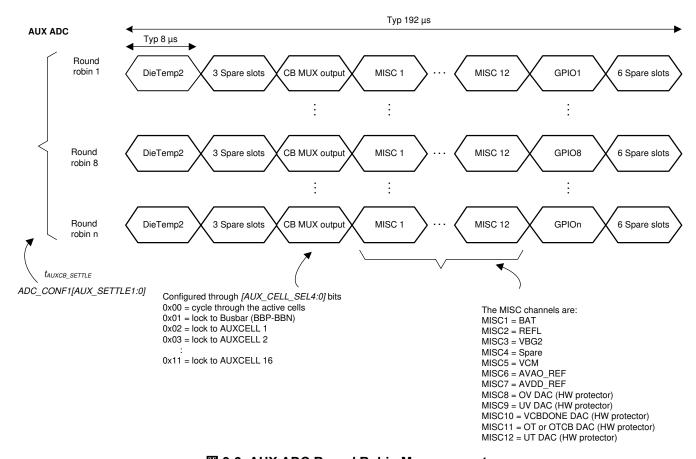

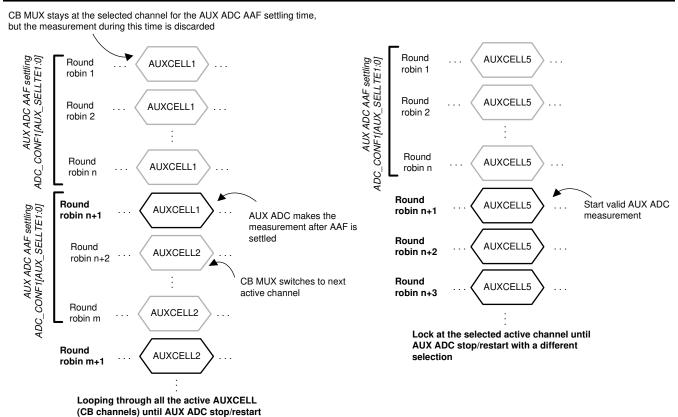

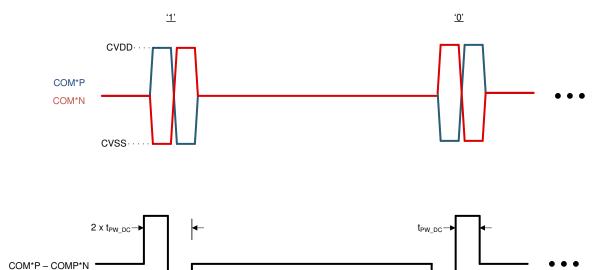

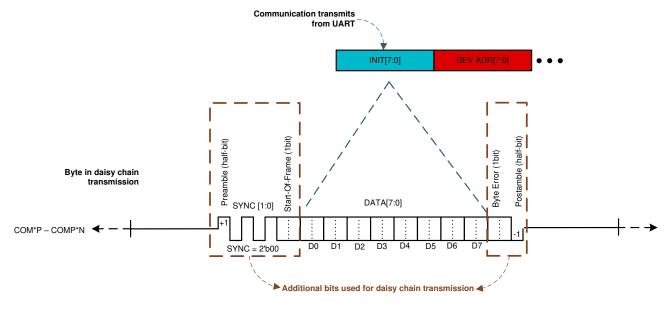

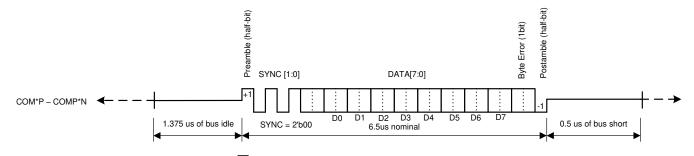

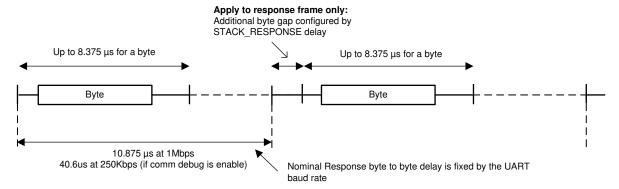

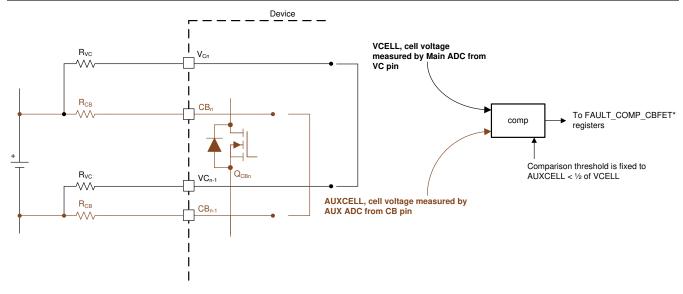

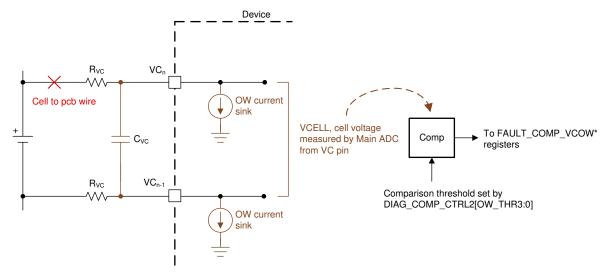

|                       | REFHP to REFHM                                                            | -0.3 | 5.5  | V    |

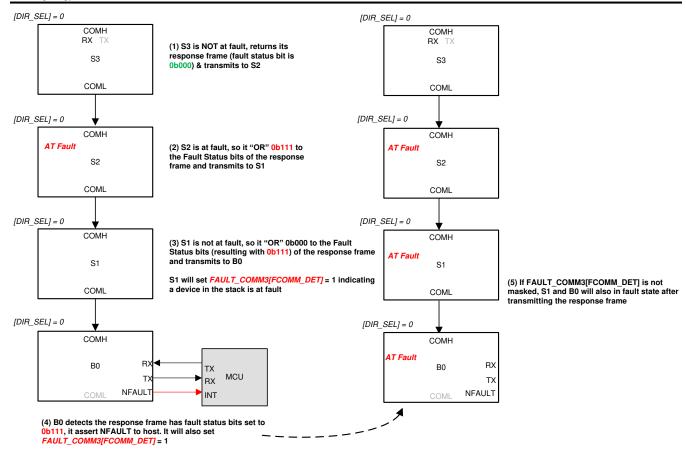

|                       | NEG5V to AVSS                                                             | -5.5 | 0    | V    |

|                       | TX, RX to AVSS                                                            | -0.3 | 6    | V    |

|                       | COMHP, COMHN, COMLP, COMLN to CVSS                                        | -20  | 20   | V    |

|                       | COMHP to COMHN, COMLP to COMLN                                            | -5.5 | 5.5  | V    |

|                       | GPIO* to AVSS                                                             | -0.3 | 5.5  | V    |

| CB* current           | Max of 8 cell in balancing at 75°C ambient                                |      | 240  | mA   |

| I/O current           | GPIO*, RX, TX current                                                     |      | 10   | mA   |

| T <sub>OTP_PROG</sub> | Device will not start OTP programming above this temperature              |      | 55   | °C   |

| T <sub>A</sub>        | Ambient temperature                                                       | -40  | 130  | °C   |

| T <sub>J</sub>        | Junction temperature                                                      | -40  | 150  | °C   |

| T <sub>stg</sub>      | Storage temperature                                                       | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                         |                                      |                                            | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------|--------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per AEC Q100 | 0-002 <sup>(1)</sup>                       | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC  | All Pins                                   | ±500  | V    |

|                    | J 9 -                   | Q100-011                             | Other pins (1, 16, 17, 32, 33, 48, 49, 64) | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                                              | MIN | NOM MAX | UNIT |

|-----------------------|--------------------------------------------------------------|-----|---------|------|

| V <sub>BAT_RANG</sub> | Total module voltage, full functionality, no OTP programming | 9   | 80      | V    |

<sup>(2)</sup> VC pin voltage has to meet criteria of both VCn to AVSS as well as VCn to VCn-1.

<sup>(3)</sup> CB pin voltage has to meet criteria of both CBn to AVSS as well as CBn to CBn-1.

# 8.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                                |                                                                 | MIN  | NOM MAX | UNIT |

|--------------------------------|-----------------------------------------------------------------|------|---------|------|

| V <sub>BAT_OTP_R</sub><br>ANGE | Total module voltage, full functionality, OTP programming allow | 11   | 80      | V    |

| V <sub>CELL_RAN</sub><br>GE    | $VC_n$ - $VC_{n-1}$ , where n = 2 to 16                         | -1   | 5       | V    |

|                                | VC1 - VC0                                                       | 0    | 5       | V    |

|                                | VC0, CB0 to AVSS                                                | -0.3 | 5       | V    |

|                                | VC1, VC2, CB1, CB2 to AVSS                                      | -0.3 | 80      | V    |

|                                | VCn, CBn to AVSS, where n = 3 to 16                             | 3    | 80      | V    |

| V <sub>BB_RANGE</sub>          | $V_{BBP}$ - $V_{BBN}$                                           | -600 | 800     | mV   |

| V <sub>CB_RANGE</sub>          | $CB_n$ - $CB_{n-1}$ , where n = 1 to 16                         | 0    | 5       | V    |

| V <sub>IO_RANGE</sub>          | RX, TX, NFAULT                                                  | 0    | CVDD    | V    |

| V <sub>GPIO_RAN</sub><br>GE    | GPIO <sub>n</sub> input, where n = 1 to 8                       | 0.2  | 4.8     | V    |

| I <sub>IO</sub>                | GPIO <sub>n</sub> , RX, TX, where n = 1 to 8                    |      | 5       | mA   |

| T <sub>A</sub>                 | Operation temperature                                           | -40  | 125     | °C   |

### 8.4 Thermal Information

|                       |                                              | BQ7961x-Q1  |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC                               | PAP (HTQFP) | UNIT |

|                       |                                              | 64 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 21.6        | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 8.7         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.9         | °C/W |

| ΨЈΤ                   | Junction-to-top characterization parameter   | 0.1         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 7.8         | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.1         | °C/W |

# 8.5 Electrical Characteristics

|                         | PARAMETER                                                  | TEST CONDITIONS                                                                        | MIN | TYP | MAX | UNIT |

|-------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|------|

| THERMAL SHU             | TDOWN                                                      |                                                                                        |     |     | '   |      |

| T <sub>SHUT</sub>       | Thermal shutdown (rising direction)                        |                                                                                        | 130 | 137 | 152 | °C   |

| T <sub>SHUT_FALL</sub>  | Thermal shutdown (falling direction)                       |                                                                                        | 112 |     | 129 | °C   |

| T <sub>SHUT_HYS</sub>   | Thermal shutdown (rising - falling direction)              |                                                                                        |     | 20  |     | °C   |

| T <sub>WARN_RANGE</sub> | Thermal warning Threshold (rising direction)               |                                                                                        | 85  |     | 115 | °C   |

| T <sub>WARN_HYS</sub>   | Thermal warning hysteresis (falling direction)             |                                                                                        |     | 10  |     | °C   |

| T <sub>WARN_ACC</sub>   | Thermal warning accuracy (+/-)                             |                                                                                        |     | 5   |     | °C   |

| SUPPLY CURRE            | ENTS                                                       |                                                                                        | •   |     | ,   |      |

| I <sub>SHDN</sub>       | Supply current in SHUTDOWN mode                            | Sum of both I <sub>BAT</sub> and I <sub>LDOIN</sub>                                    |     | 16  | 23  | μA   |

| 1                       | Baseline supply current in SLEEP                           | Sum of both I <sub>BAT</sub> and I <sub>LDOIN</sub><br>T <sub>A</sub> = -20°C to 65°C  |     | 120 | 160 | μΑ   |

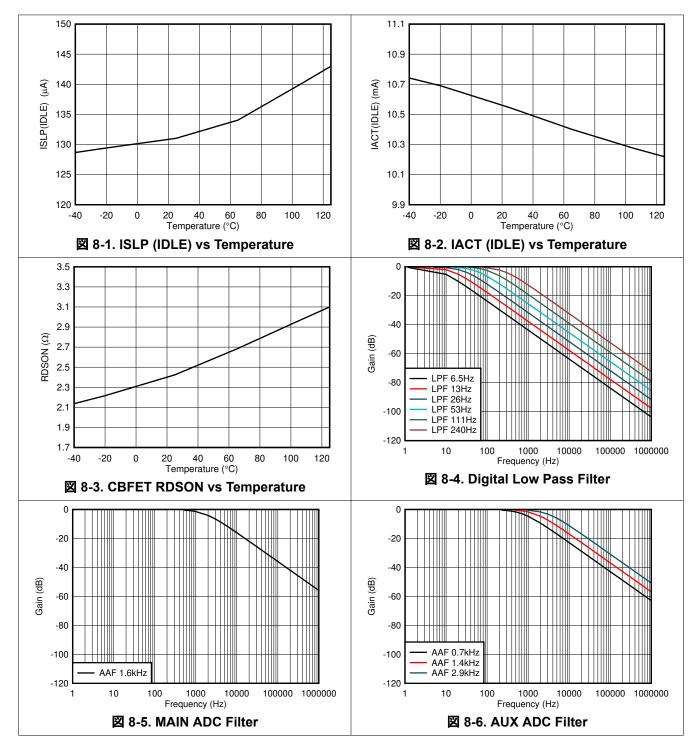

| ISLP(IDLE)              | mode. No fault, no protector comparator, no cell balancing | Sum of both I <sub>BAT</sub> and I <sub>LDOIN</sub><br>T <sub>A</sub> = -40°C to 125°C |     |     | 220 | μΑ   |

|                          | PARAMETER                                                                        | TEST CONDITIONS                                                                                                            | MIN  | TYP  | MAX  | UNIT |

|--------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>ACT(IDLE)</sub>   | Baseline supply current in ACTIVE mode                                           | Sum of both I <sub>BAT</sub> and I <sub>LDOIN</sub> No fault, no communication, no protector comparator, no cell balancing |      | 10.4 | 11.6 | mA   |

| I <sub>CB_EN</sub>       | Additional supply current when cell balancing is on                              | At least 1 cell balancing FET is on, OT <sub>CB</sub> is enabled. Other functions are inactive                             |      | 1    | 1.5  | mA   |

| I <sub>PROTCOMP</sub>    | Additional supply current when protector comparator is on                        | Either OV/UV/OT/UT protector is enabled. Other functions are inactive                                                      |      | 20   | 60   | μΑ   |

| I <sub>TSREF</sub>       |                                                                                  | SLEEP Mode, no load on TSREF pin                                                                                           |      | 100  |      | μΑ   |

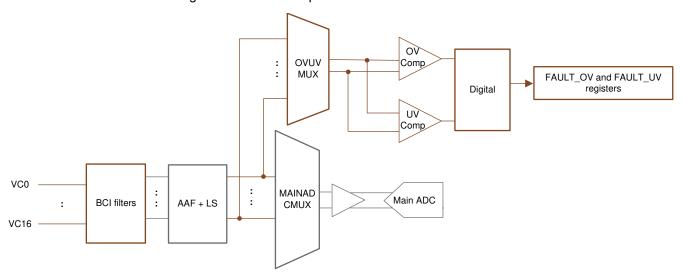

| I <sub>ADC</sub>         | Additional supply current when ADC is                                            | One ADC on, and conversion is in progress. Other functions are inactive                                                    |      | 0.4  | 0.6  | mA   |

| ADC                      | enabled                                                                          | 2 ADCs on, and conversion is in progress. Other functions are inactive                                                     |      | 0.6  | 0.9  | mA   |

|                          |                                                                                  | ACTIVE Mode                                                                                                                |      | 150  |      | μΑ   |

| I <sub>BAT</sub>         | Supply current goes into BAT pin                                                 | SLEEP Mode                                                                                                                 |      | 25   |      | μΑ   |

|                          |                                                                                  | SHUTDOWN Mode                                                                                                              |      | 5    |      | μΑ   |

| Ісомт                    | Additional supply current during daisy-<br>chain broadcast read of 128-byte data | Use transformer isolation for daisy-<br>chain interface                                                                    |      | 10   |      | mA   |

| Ісомс                    | Additional supply current during daisy-<br>chain broadcast read of 128-byte data | Use capacitor or capacitor and choke isolation for daisy-chain interface                                                   |      | 10   |      | mA   |

| I <sub>OW_SINK</sub>     | Sink current for open wire test, applies to VC1 to VC16 and CB1 to CB 16         |                                                                                                                            | 380  | 500  | 600  | μΑ   |

| I <sub>OW_SOURCE</sub>   | Source current for open wire test, applies to VC0 and CB0                        |                                                                                                                            | 380  | 500  | 600  | μΑ   |

| I <sub>LEAK</sub>        | Leakage current on VC, CB pins                                                   | VC, CB pins with ADC off.                                                                                                  |      |      | 0.1  | μΑ   |

| Supplies (LDOII          | N)                                                                               |                                                                                                                            |      |      |      |      |

| $V_{LDOIN}$              | LDOIN voltage                                                                    | No OTP programming                                                                                                         | 5.9  | 6    | 6.1  | V    |

|                          |                                                                                  | OTP programming                                                                                                            | 7.9  | 8    | 8.1  | V    |

| Supplies (CVDD           | <u>)</u>                                                                         |                                                                                                                            |      |      |      |      |

|                          |                                                                                  | ACTIVE and SLEEP mode                                                                                                      | 4.9  | 5    | 5.1  | V    |

| $V_{CVDD}$               | CVDD output voltage                                                              | SHUTDOWN mode, no external lload                                                                                           | 3.95 |      | 6    | V    |

|                          |                                                                                  | SHUTDOWN mode, max external lload = 5mA                                                                                    | 3.4  |      | 5.5  | V    |

| V <sub>CVDD_LDRG</sub>   | CVDD load regulation                                                             | ACTIVE/SLEEP mode, max external lload = 10mA                                                                               | -30  |      | 30   | mV   |

| V <sub>CVDD_OV</sub>     | CVDD OV threshold                                                                | ACTIVE/SLEEP mode, max external lload = 10mA                                                                               | 5.3  | 5.5  | 5.7  | V    |

| V <sub>CVDD_OVHYS</sub>  | CVDD OV Hystersis                                                                | ACTIVE/SLEEP mode, max external lload = 10mA                                                                               | 130  | 150  | 170  | mV   |

|                          |                                                                                  | SHUTDOWN mode                                                                                                              |      | 3.5  |      | V    |

| V <sub>CVDD_UV</sub>     | CVDD UV threshold                                                                | ACTIVE/SLEEP mode, max external lload = 10mA                                                                               | 4.3  | 4.45 | 4.65 | V    |

| V <sub>CVDD_UVHYS</sub>  | CVDD UV Hystersis                                                                |                                                                                                                            |      | 260  |      | mV   |

| V <sub>CVDD_ILIMIT</sub> | CVDD current limit                                                               | ACTIVE, SLEEP                                                                                                              | 35   | 60   | 85   | mA   |

| Supplies (AVDD           | 9)                                                                               |                                                                                                                            |      |      |      |      |

| $V_{AVDD}$               | AVDD output voltage                                                              | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                                                                                   | 4.85 | 5    | 5.21 | V    |

| V <sub>AVDD_OV</sub>     | AVDD OV threshold                                                                | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                                                                                   | 5.25 | 5.5  | 5.7  | V    |

| V <sub>AVDD_OVHYS</sub>  | AVDD OV Hystersis                                                                | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                                                                                   | 135  | 155  | 165  | mV   |

| $V_{AVDD\_UV}$           | AVDD UV threshold                                                                | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                                                                                   | 4.25 | 4.45 | 4.6  | V    |

|                               | PARAMETER                                                 | TEST CONDITIONS                                                   | MIN   | TYP    | MAX   | UNIT   |

|-------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|-------|--------|-------|--------|

| V <sub>AVDD_UVHYS</sub>       | AVDD UV Hystersis                                         | C <sub>SUPPLIES</sub> = 1μF, ACTIVE mode                          | 235   | 340    | 430   | mV     |

| V <sub>AVDD_ILIMIT</sub>      | AVDD current limit                                        | C <sub>SUPPLIES</sub> = 1µF                                       | 10    | 30     | 50    | mA     |

| Supplies (DVDD)               |                                                           |                                                                   |       |        |       |        |

| $V_{DVDD}$                    |                                                           | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                          | 1.72  | 1.8    | 1.88  | V      |

| V <sub>DVDD_OV</sub>          | DVDD OV threshold                                         | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                          | 1.95  | 2.1    | 2.3   | V      |

| V <sub>DVDD_OVHYS</sub>       | DVDD OV Hystersis                                         | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                          | 40    | 65     | 120   | mV     |

| $V_{DVDD\_UV}$                | DVDD UV threshold                                         | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                          | 1.623 | 1.65   | 1.71  | V      |

| V <sub>DVDD_UVHYS</sub>       | DVDD UV Hystersis                                         | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                          | 15    | 50     | 73    | mV     |

| V <sub>DVDD_ILIMIT</sub>      | DVDD current limit                                        |                                                                   | 13    | 30     | 53    | mA     |

| Supplies (TSREF)              |                                                           |                                                                   |       |        |       |        |

| V <sub>TSREF</sub>            | TSREF output voltage                                      | C <sub>SUPPLIES</sub> = 1µF, ACTIVE mode                          | 4.975 | 5      | 5.025 | V      |

| V <sub>TSREF_LDRG</sub>       | TSREF load regulation                                     | I <sub>load</sub> = 4mA, C <sub>SUPPLIES</sub> = 1μF, ACTIVE mode | -30   |        | 30    | mV     |

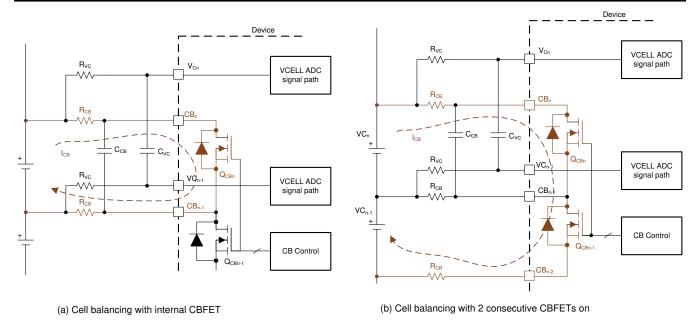

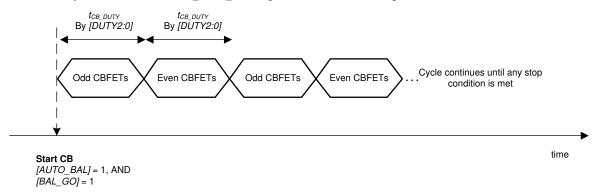

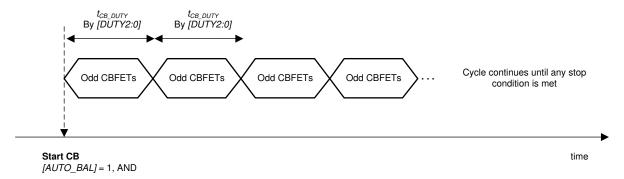

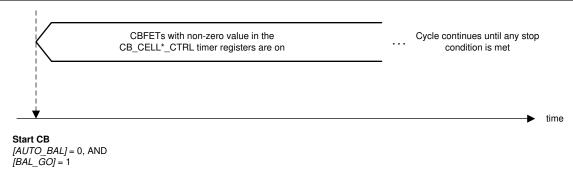

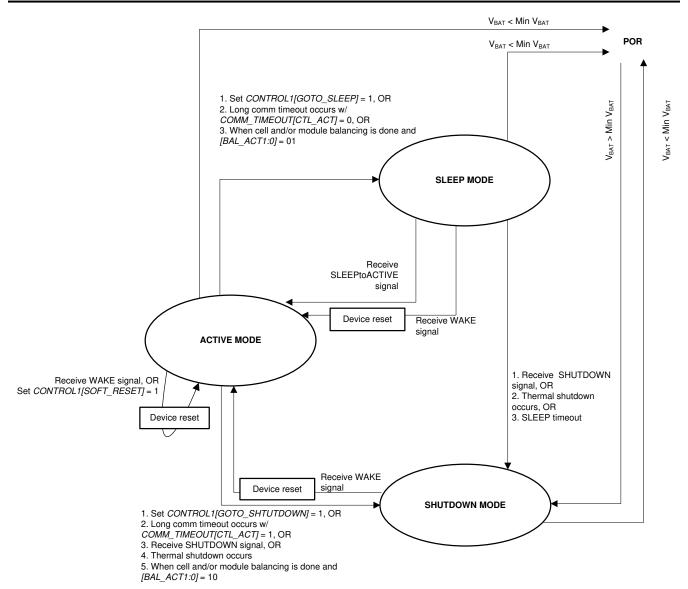

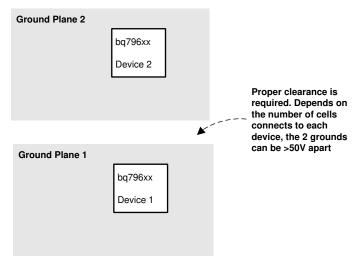

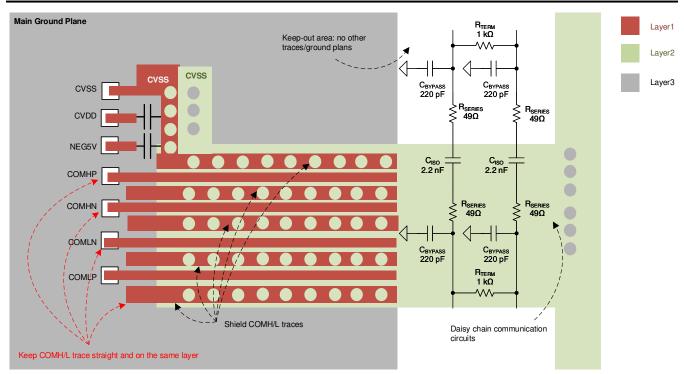

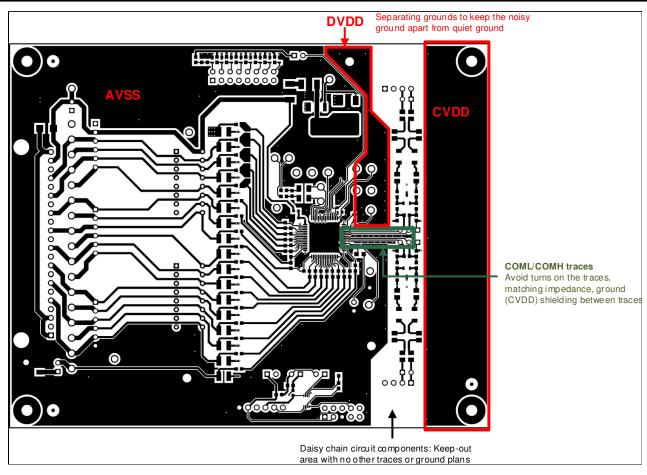

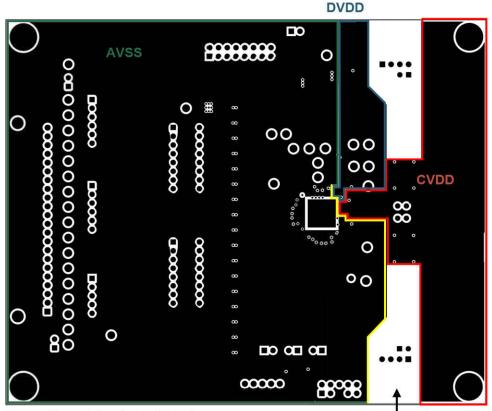

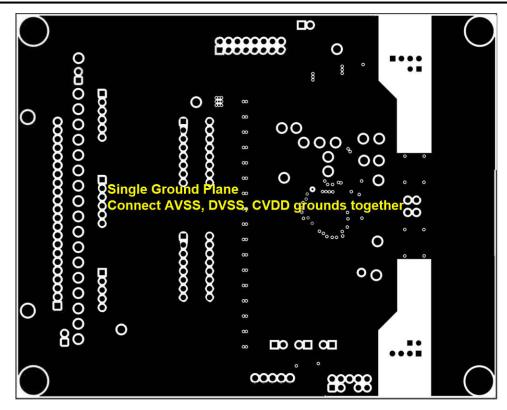

| V <sub>TSREF_OV</sub>         | TSREF OV threshold                                        | I <sub>load</sub> = 4mA, C <sub>SUPPLIES</sub> = 1μF, ACTIVE mode | 5.2   | 5.6    | 5.8   | V      |