**BQ76905**

# BQ76905 リチウムイオン、リチウムポリマ、LiFePO₄ (LFP)、および LTO バッ テリパック向け、2直列~5直列、高精度バッテリモニタ/プロテクタ

## 1 特長

- 2 直列~5 直列セルのバッテリ監視が可能

- NFET 保護用のローサイドドライバを内蔵 (オプション の自律回復機能付き)

- 電圧、温度、電流、内部診断を含む包括的な保護スイ

- 16 ビット デルタシグマ型電圧 ADC

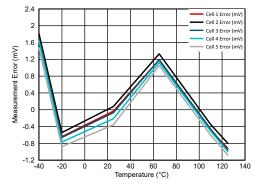

- 高精度のセル電圧測定:4mV (代表値)

- 専用の同時 16 および 24 ビット デルタシグマ クーロ ン カウンタ ADC

- 入力オフセット誤差が小さい高精度電流測定

- 広範囲電流アプリケーション (検出抵抗の両端で ±200mV の測定範囲)

- タイマ付き、48 ビット蓄積電荷積分器

- ホスト制御セル バランシング

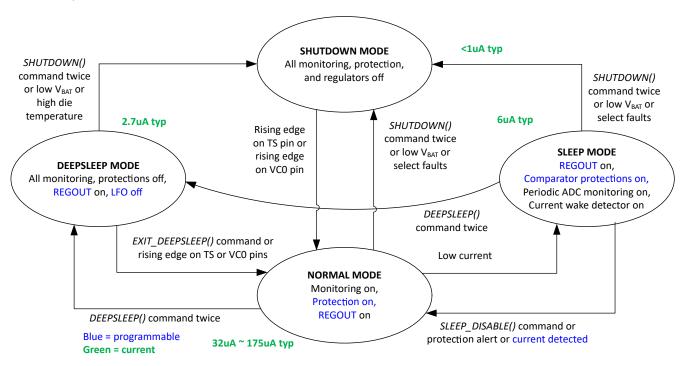

- 複数の電力モード (一般的なバッテリ・パックの動作範 囲の条件)

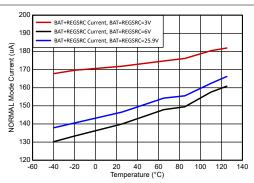

- 通常モード:32µA~175µA

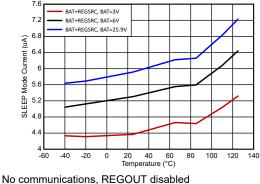

- スリープ・モード:6μA

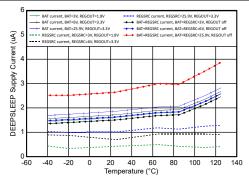

- DEEPSLEEP モード: 2.7µA

- シャットダウン・モード:1µA 未満

- 45V の高電圧耐性 (セル接続および他の一部のピン)

- 内部センサと外部サーミスタを使用した温度検出をサ

- テキサス・インスツルメンツによりプログラム済みのデバ イス設定用ワンタイム プログラマブル (OTP) メモリを内

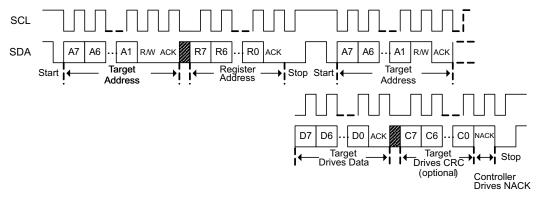

- 400kHz l<sup>2</sup>C シリアル通信 (オプションの CRC サポー

- 外部システムで使用するためのプログラム可能な LDO

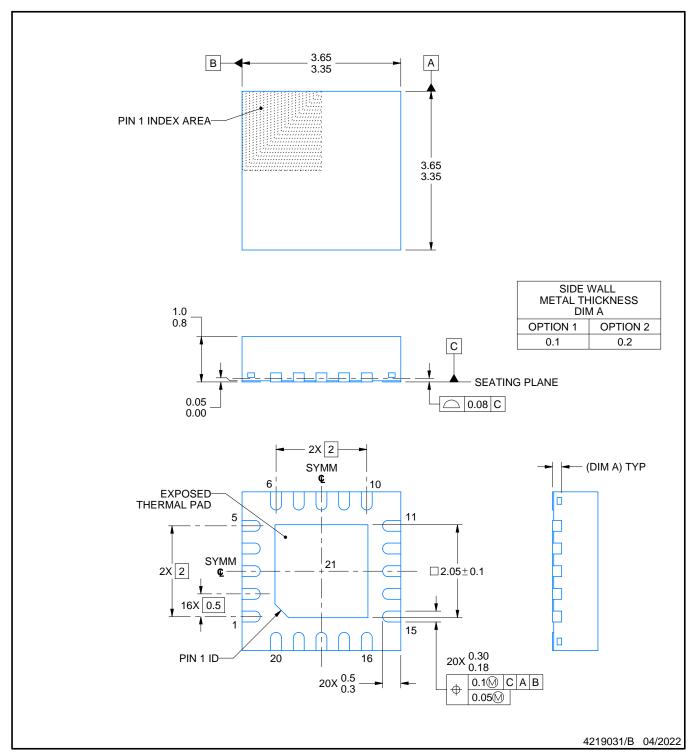

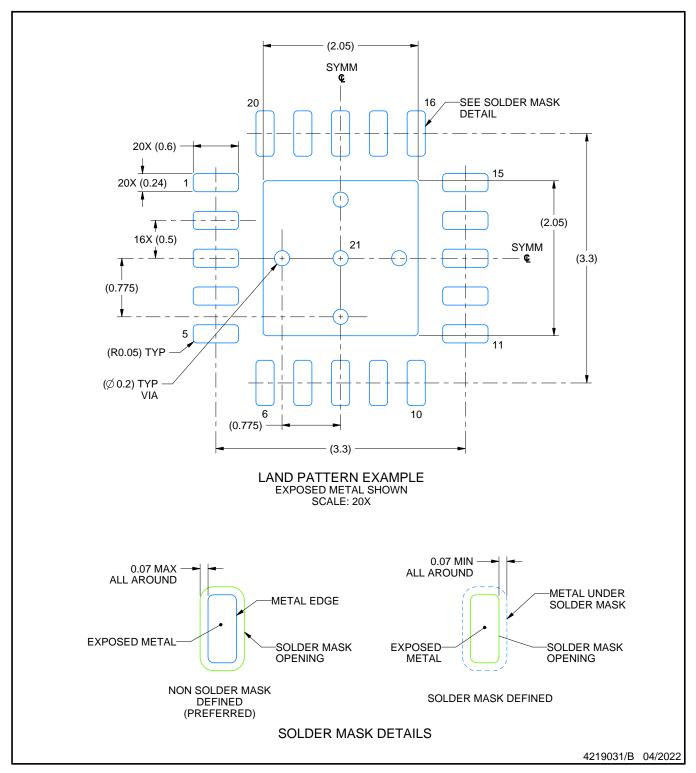

- 20 ピン QFN (RGR) パッケージ

# 2 アプリケーション

- コードレス電動工具および園芸用具

- 掃除機

- 非軍事用ドローン

- その他産業用バッテリパック(2直列~5直列)

## 3 概要

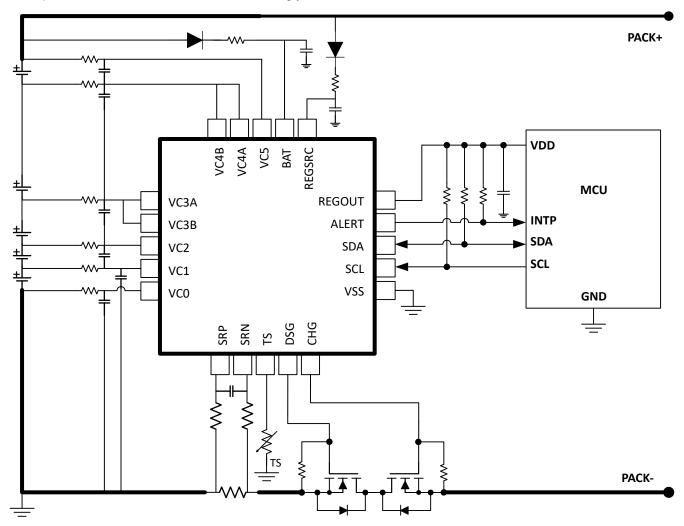

テキサス・インスツルメンツの BQ76905 は、2 直列~5 直 列のリチウムイオン、リチウムポリマ、LiFePO<sub>4</sub> (LFP)、およ び LTO バッテリパック向けの高集積高精度バッテリモニ タ/プロテクタです。各デバイスは高精度の監視システ ム、高度に構成可能な保護サブシステム、ホスト制御のセ ル バランシング機能を内蔵しています。ローサイド保護 NFETドライバ、外部システム用のプログラム可能な LDO、およびオプションの CRC で最大 400kHz の動作 をサポートする I2C ホスト通信インターフェイスが統合され ています。BQ76905 は、20 ピン QFN パッケージで供給 されます。

### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ (公称<br>値)                |

|---------|----------------------|------------------------------------|

| BQ76905 | RGR (20 ピン QFN)      | 3.5mm × 3.5mm ×<br>0.9mm、0.5mm ピッチ |

#### 巻末の注文情報を参照してください。

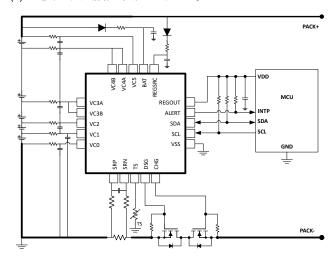

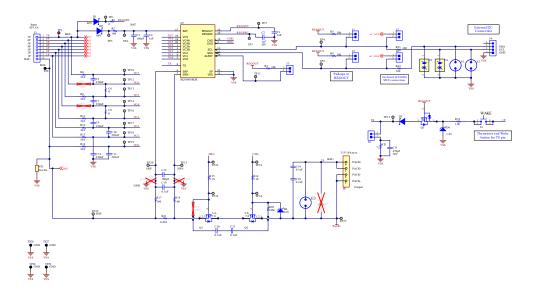

図 3-1. 概略回路図

# **Table of Contents**

| 1 | 特長1                                                          | 7.4.9 Low Freque                 |

|---|--------------------------------------------------------------|----------------------------------|

|   | アプリケーション1                                                    | 7.4.10 I <sup>2</sup> C Serial ( |

|   | 概要1                                                          | 7.5 Measurement S                |

|   | Device Comparison Table3                                     | 7.5.1 Voltage Mea                |

|   | Pin Configuration and Functions3                             | 7.5.2 Current Mea                |

|   | Specifications5                                              | 7.5.3 Internal Tem               |

| • | 6.1 Absolute Maximum Ratings5                                | 7.5.4 Thermistor                 |

|   | 6.2 ESD Ratings5                                             | 7.5.5 Factory Trim               |

|   | 6.3 Recommended Operating Conditions6                        | 7.6 Protection Subs              |

|   | 6.4 Thermal Information7                                     | 7.6.1 Protections                |

|   | 6.5 Supply Current7                                          | 7.6.2 Primary Pro                |

|   | 6.6 Digital I/O                                              | 7.6.3 CHG Detect                 |

|   | 6.7 REGOUT LDO8                                              | 7.6.4 Cell Open-V                |

|   | 6.8 Voltage References8                                      | 7.6.5 Diagnostic 0               |

|   | 6.9 Coulomb Counter9                                         | 7.7 Cell Balancing               |

|   | 6.10 Coulomb Counter Digital Filter9                         | 7.8 Device Operatio              |

|   | 6.11 Current Wake Detector11                                 | 7.8.1 Overview of                |

|   | 6.12 Analog-to-Digital Converter                             | 7.8.2 NORMAL M                   |

|   | 6.13 Cell Balancing                                          | 7.8.3 SLEEP Mod                  |

|   | 6.14 Internal Temperature Sensor                             | 7.8.4 DEEPSLEE                   |

|   | 6.15 Thermistor Measurement                                  | 7.8.5 SHUTDOWI                   |

|   | 6.16 Hardware Overtemperature Detector                       | 7.8.6 CONFIG_UI                  |

|   | 6.17 Internal Oscillator                                     | 8 Application and Im             |

|   | 6.18 Charge and Discharge FET Drivers                        | 8.1 Application Infor            |

|   | 6.19 Comparator-Based Protection Subsystem17                 | 8.2 Typical Applicati            |

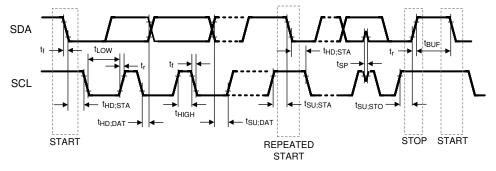

|   | 6.20 Timing Requirements—I <sup>2</sup> C Interface, 100-kHz | 8.2.1 Design Req                 |

|   | Mode                                                         | 8.2.2 Detailed Des               |

|   | 6.21 Timing Requirements—I <sup>2</sup> C Interface, 400-kHz | 8.2.3 Application I              |

|   | Mode                                                         | 8.2.4 Random Ce                  |

|   | 6.22 Timing Diagram20                                        | 8.2.5 Startup Timi               |

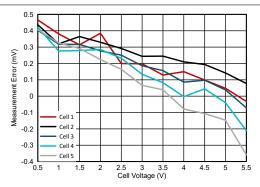

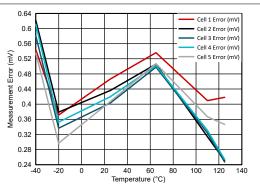

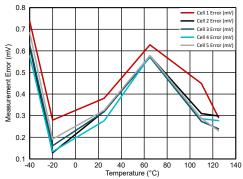

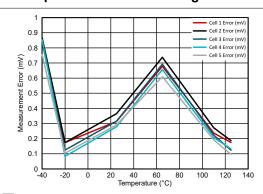

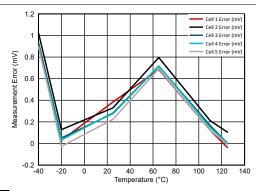

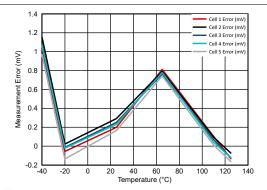

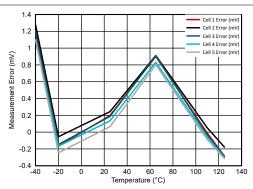

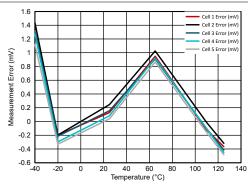

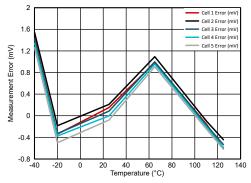

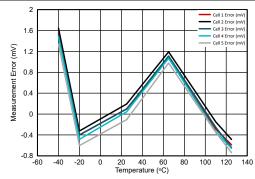

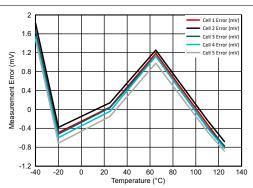

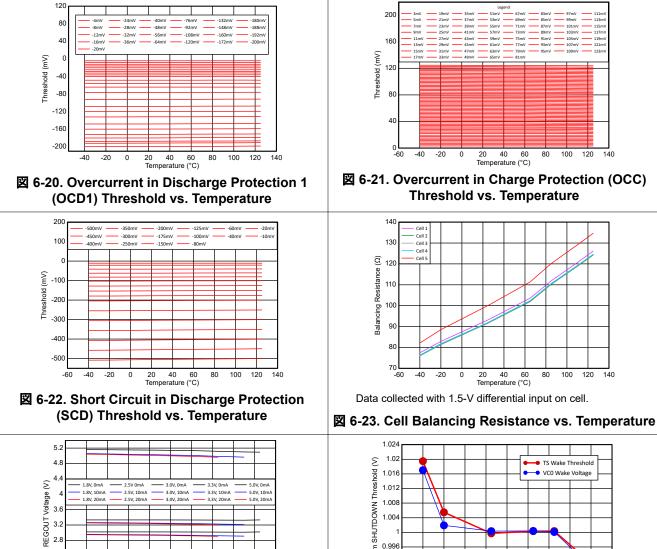

|   | 6.23 Typical Characteristics21                               | 8.2.6 FET Driver                 |

| 7 | Detailed Description                                         | 8.2.7 Usage of Ur                |

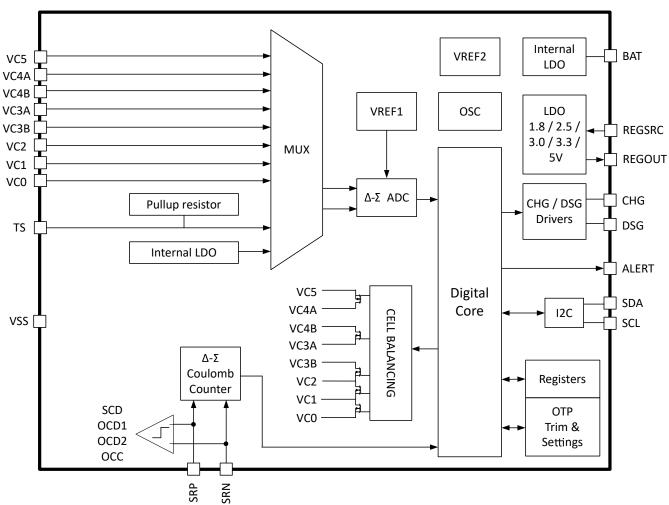

| • | 7.1 Overview                                                 | 8.3 Power Supply R               |

|   | 7.2 Functional Block Diagram                                 | 8.4 Layout                       |

|   | 7.3 Device Configuration                                     | 8.4.1 Layout Guid                |

|   | 7.3.1 Commands and Subcommands                               | 8.4.2 Layout Exar                |

|   | 7.3.2 Configuration Using OTP or Registers27                 | 9 Device and Docum               |

|   | 7.3.3 Device Security                                        | 9.1 Documentation                |

|   | 7.4 Device Hardware Features                                 | 9.1.1 Related Dod                |

|   | 7.4.1 Voltage ADC                                            | 9.2 ドキュメントの更新                    |

|   | 7.4.2 Coulomb Counter and Digital Filters28                  | 9.3 サポート・リソース                    |

|   | 7.4.3 Protection FET Drivers                                 | 9.4 Trademarks                   |

|   | 7.4.4 Voltage References                                     | 9.5 静電気放電に関 <sup>*</sup>         |

|   | 7.4.5 Multiplexer                                            | 9.6 用語集                          |

|   | 7.4.6 LDOs. 29                                               | 10 Revision History              |

|   | 7.4.7 Standalone Versus Host Interface                       | 11 Mechanical, Packa             |

|   | 7.4.7 Standardie Versus Host Interface                       | Information                      |

|   | 7.1.07.4EERT 1 111 Operation                                 | 111101111ati011                  |

| 7.4.9 Low Frequency Oscillator                          | .30                      |

|---------------------------------------------------------|--------------------------|

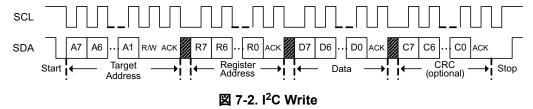

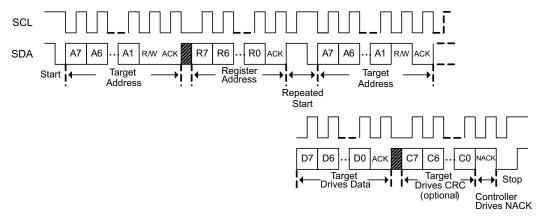

| 7.4.10 I <sup>2</sup> C Serial Communications Interface | . 30                     |

| 7.5 Measurement Subsystem                               | . 32                     |

| 7.5.1 Voltage Measurement                               | . 32                     |

| 7.5.2 Current Measurement and Charge Integration.       | .33                      |

| 7.5.3 Internal Temperature Measurement                  |                          |

| 7.5.4 Thermistor Temperature Measurement                | . 34                     |

| 7.5.5 Factory Trim and Calibration                      | . 35                     |

| 7.6 Protection Subsystem                                | .35                      |

| 7.6.1 Protections Overview                              | . 35                     |

| 7.6.2 Primary Protections                               |                          |

| 7.6.3 CHG Detector                                      | .36                      |

| 7.6.4 Cell Open-Wire Protection                         |                          |

| 7.6.5 Diagnostic Checks                                 |                          |

| 7.7 Cell Balancing                                      | . 37                     |

| 7.8 Device Operational Modes                            |                          |

| 7.8.1 Overview of Operational Modes                     | . 38                     |

| 7.8.2 NORMAL Mode                                       | .38                      |

| 7.8.3 SLEEP Mode                                        | .39                      |

| 7.8.4 DEEPSLEEP Mode                                    |                          |

| 7.8.5 SHUTDOWN Mode                                     |                          |

| 7.8.6 CONFIG_UPDATE Mode                                | .40                      |

| 8 Application and Implementation                        | .41                      |

| 8.2 Typical Application                                 | . <del>4</del> 1<br>. 11 |

| 8.2.1 Design Requirements                               |                          |

| 8.2.2 Detailed Design Procedure                         |                          |

| 8.2.3 Application Performance Plot                      |                          |

| 8.2.4 Random Cell Connection Support                    | 46                       |

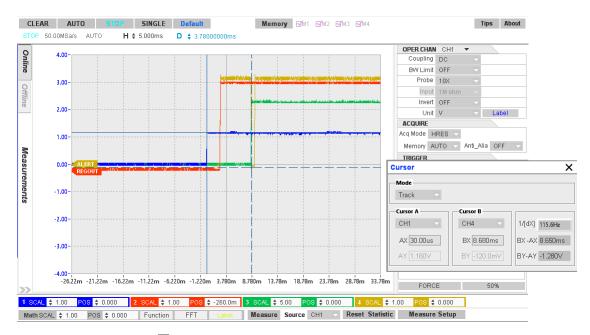

| 8.2.5 Startup Timing                                    | .47                      |

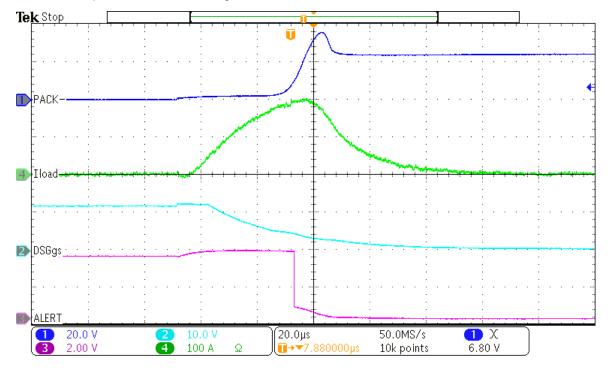

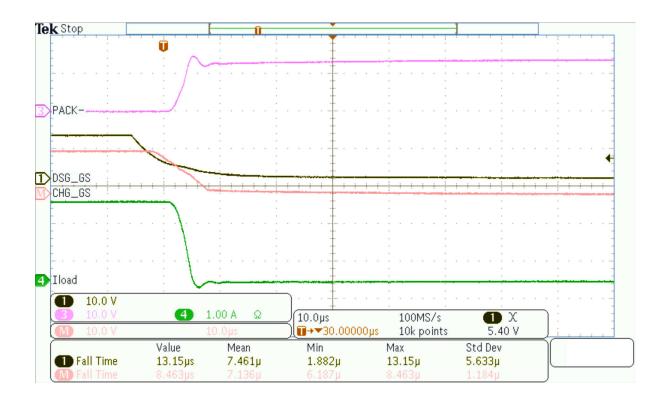

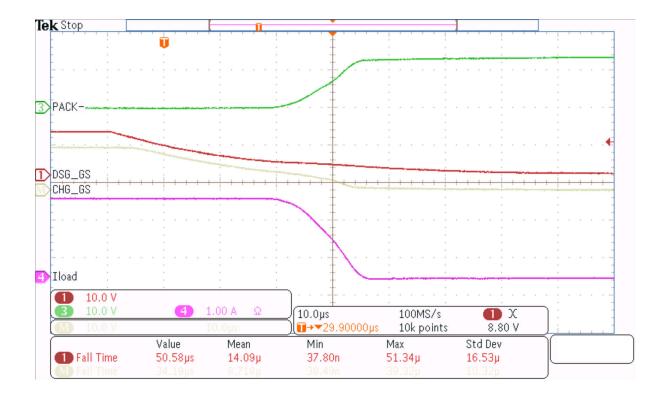

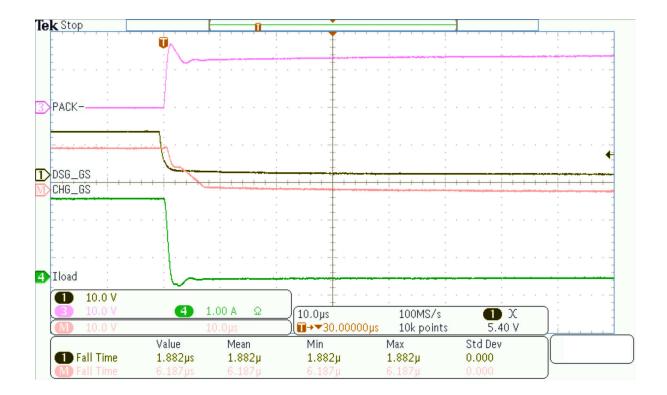

| 8.2.6 FET Driver Turn-Off                               | 48                       |

| 8.2.7 Usage of Unused Pins                              | .51                      |

| 8.3 Power Supply Recommendations                        |                          |

| 8.4 Layout                                              |                          |

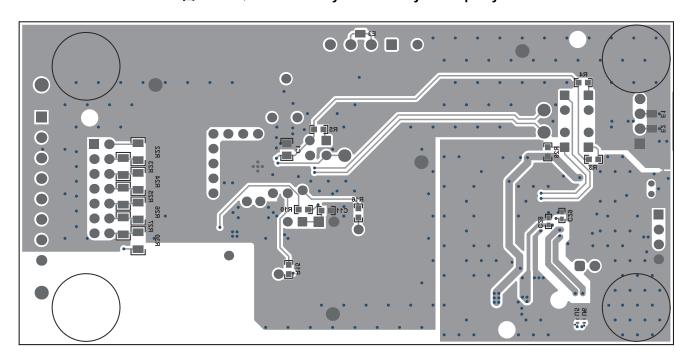

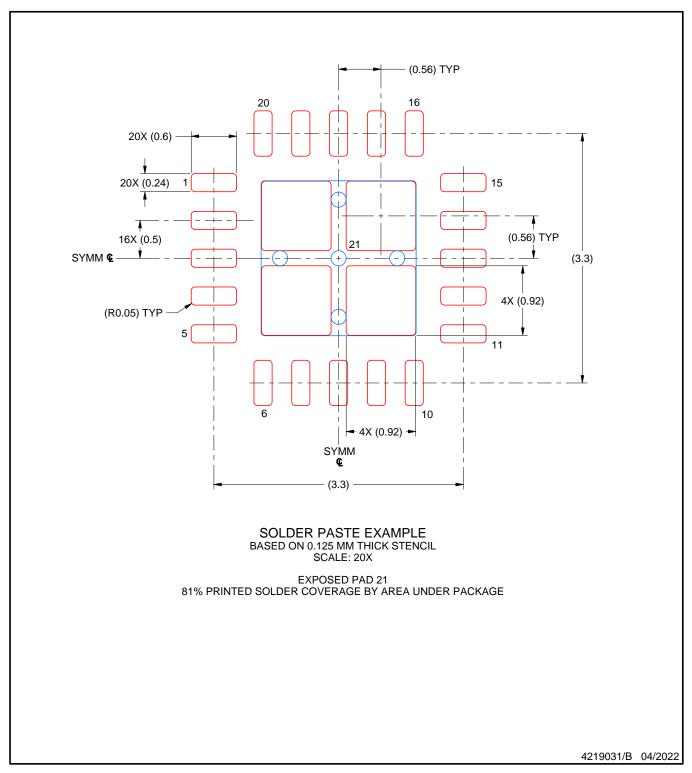

| 8.4.1 Layout Guidelines                                 | .52                      |

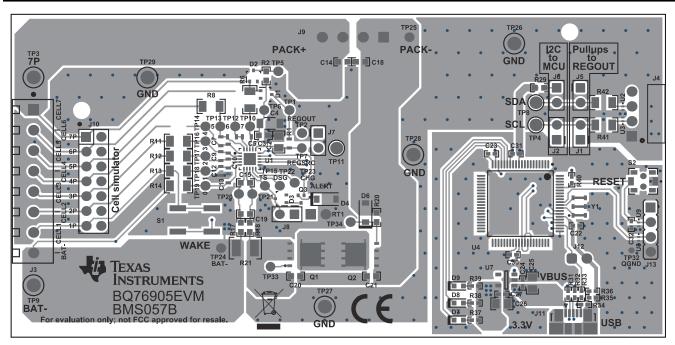

| 8.4.2 Layout Example                                    | .52                      |

| 9 Device and Documentation Support                      |                          |

| 9.1 Documentation Support                               | . 54                     |

| 9.1.1 Related Documentation                             | .54                      |

| 9.2ドキュメントの更新通知を受け取る方法                                   | . 54                     |

| 9.3 サポート・リソース                                           | . 54                     |

| 9.4 Trademarks                                          | .54                      |

| 9.5 静電気放電に関する注意事項                                       |                          |

| 9.6 用語集                                                 |                          |

| 10 Revision History                                     | . 54                     |

| 11 Mechanical, Packaging, and Orderable                 |                          |

| Information                                             | . 55                     |

# **4 Device Comparison Table**

| BQ76905 DEVICE FAMILY                                                |   |     |                |  |  |

|----------------------------------------------------------------------|---|-----|----------------|--|--|

| PART NUMBER SETTINGS PROGRAMMABLE CELL COUNT SUPPORTED REGOUT STATUS |   |     |                |  |  |

| BQ76905                                                              | Y | 2–5 | Enabled, 3.3 V |  |  |

| BQ76905xy <sup>(1)</sup>                                             | Y | 2–5 | Enabled, 3.3 V |  |  |

(1) PRODUCT PREVIEW

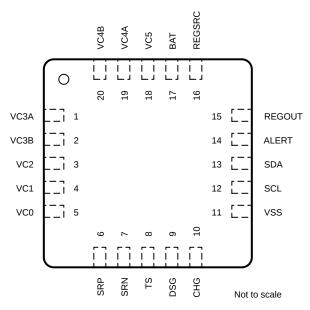

# **5 Pin Configuration and Functions**

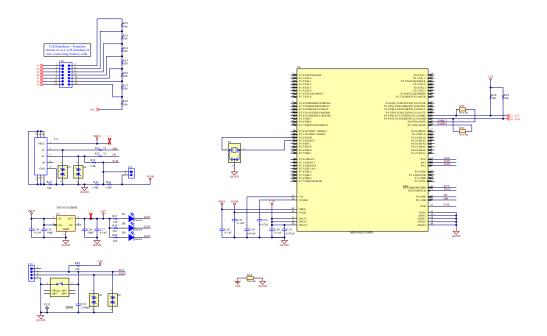

図 5-1. BQ76905 Pinout

表 5-1. Pin Functions

|     | PIN  | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                       |  |

|-----|------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME |     | ITPE | DESCRIPTION                                                                                                                                                                                                                                       |  |

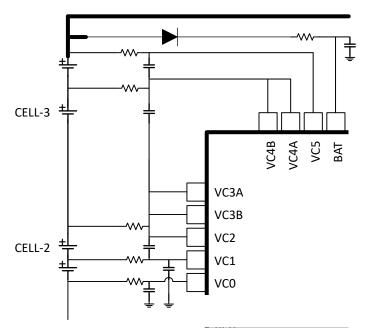

| 1   | VC3A | ı   | IA   | Sense voltage input pin for the negative terminal of the fourth cell from the bottom of the stack, and return balance current for the fourth cell from the bottom of the stack                                                                    |  |

| 2   | VC3B | ı   | IA   | Sense voltage input pin for the third cell from the bottom of the stack, and balance current input for the third cell from the bottom of the stack.                                                                                               |  |

| 1   | VC2  | ı   | IA   | Sense voltage input pin for the second cell from the bottom of the stack, balance current input for the second cell from the bottom of the stack, and return balance current for the third cell from the bottom of the stack                      |  |

| 2   | VC1  | ı   | IA   | Sense voltage input pin for the first cell from the bottom of the stack, balance current input for the first cell from the bottom of the stack, and return balance current for the second cell from the bottom of the stack                       |  |

| 3   | VC0  | ı   | IA   | Sense voltage input pin for the negative terminal of the first cell from the bottom of the stack, and return balance current for the first cell from the bottom of the stack                                                                      |  |

| 6   | SRP  | ı   | IA   | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRP is the top of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN.    |  |

| 7   | SRN  | 1   | IA   | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRN is the bottom of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN. |  |

| 8   | TS   | I/O | I/OA | Thermistor or general-purpose ADC input and functions as wakeup from SHUTDOWN                                                                                                                                                                     |  |

| 9   | DSG  | 0   | OA   | NMOS Discharge FET drive output pin                                                                                                                                                                                                               |  |

| 10  | CHG  | 0   | OA   | NMOS Charge FET drive output pin                                                                                                                                                                                                                  |  |

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

3

# 表 5-1. Pin Functions (続き)

|     | PIN    | I/O | TYPE | DESCRIPTION                                                                                                                                                                            |  |

|-----|--------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME   |     | ITPE | DESCRIPTION                                                                                                                                                                            |  |

| 11  | VSS    | T — | Р    | Device ground                                                                                                                                                                          |  |

| 12  | SCL    | I/O | I/OD | I <sup>2</sup> C serial communication bus clock                                                                                                                                        |  |

| 13  | SDA    | I/O | I/OD | I <sup>2</sup> C serial communication bus data                                                                                                                                         |  |

| 14  | ALERT  | 0   | OD   | Digital interrupt output pin                                                                                                                                                           |  |

| 15  | REGOUT | 0   | OA   | LDO output, which can be programmed for 1.8 V, 2.5 V, 3.0 V, 3.3 V, or 5.0 V                                                                                                           |  |

| 16  | REGSRC | I   | IA   | Input pin for REGOUT LDO, also functions as supply for the CHG and DSG FET drivers                                                                                                     |  |

| 17  | BAT    | I   | Р    | Primary power supply input pin                                                                                                                                                         |  |

| 18  | VC5    | ı   | IA   | Sense voltage input pin for the fifth cell from the bottom of the stack, balance current input for the fifth cell from the bottom of the stack, and the top-of-stack measurement point |  |

| 19  | VC4A   | I   | IA   | Sense voltage input pin for negative terminal of the fifth cell from the bottom of the stack, and return balance current for the fifth cell from the bottom of the stack               |  |

| 20  | VC4B   | ı   | IA   | Sense voltage input pin for the fourth cell from the bottom of the stack, and balance current input for the fourth cell from the bottom of the stack                                   |  |

English Data Sheet: SLUSE97

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| DESCRIPTION                                                    | PINS                        | MIN                                | MAX    | UNIT |

|----------------------------------------------------------------|-----------------------------|------------------------------------|--------|------|

| Supply voltage range, V <sub>IN(DC)</sub> (2)                  | BAT, REGSRC                 | VSS-0.3                            | VSS+40 | V    |

| Short duration input voltage range, V <sub>IN(short)</sub> (2) | VC1 – VC5, BAT, REGSRC, CHG |                                    | VSS+45 | V    |

| DC input voltage range, V <sub>IN(DC)</sub>                    | ALERT, SCL, SDA             | VSS-0.3                            | VSS+6  | V    |

| DC input voltage range, V <sub>IN(DC)</sub>                    | TS                          | VSS-0.3                            | 2.1    | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | SRP, SRN                    | VSS-0.3                            | 2.1    | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC5                         | Maximum of VSS-0.3<br>and VC4A-0.3 | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC4A                        | Maximum of VSS-0.3<br>and VC4B-0.3 | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC4B                        | Maximum of VSS-0.3<br>and VC3A-0.3 | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC3A                        | Maximum of VSS-0.3<br>and VC3B-0.3 | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC3B                        | Maximum of VSS-0.3<br>and VC2-0.3  | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC2                         | Maximum of VSS-0.3<br>and VC1-0.3  | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | VC1                         | Maximum of VSS-0.3 and VC0-0.3     | VSS+40 | V    |

| DC input voltage range, V <sub>IN(DC)</sub>                    | VC0                         | VSS-0.3                            | VSS+6  | V    |

| DC input voltage range, V <sub>IN(DC)</sub> (2)                | CHG                         | VSS-30                             | VSS+40 | V    |

| Output voltage range, V <sub>O</sub>                           | DSG                         | VSS-0.3                            | VSS+20 | V    |

| Output voltage range, V <sub>O</sub>                           | REGOUT                      | VSS-0.3                            | VSS+6  | V    |

| Maximum cell balancing current, each cell                      | VC0 – VC5                   |                                    | 50     | mA   |

| Junction temperature, T <sub>J</sub>                           |                             | -65                                | 150    | °C   |

| Storage temperature, T <sub>STG</sub>                          |                             | -65                                | 150    | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

5

English Data Sheet: SLUSE97

<sup>(2)</sup> Stresses applied above V<sub>IN(DC)</sub> and below V<sub>IN(SHORT)</sub> should be limited to less than 100 hours over the lifetime of the device. These stresses may occur during brief transient events but DC voltages in this range should not be applied.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

|                        | PARAMETER                                                   | TEST CONDITIONS                             | MIN                                             | TYP MAX                                   | UNIT |

|------------------------|-------------------------------------------------------------|---------------------------------------------|-------------------------------------------------|-------------------------------------------|------|

| V <sub>BAT</sub>       | Supply voltage                                              | Voltage on BAT pin (normal operation)       | 3                                               | 27.5                                      | V    |

| V <sub>BAT(UVLO)</sub> | Under voltage lockout level                                 | Falling voltage on BAT causing device reset |                                                 | 2.5                                       | V    |

| V <sub>WAKEONTS</sub>  | Wake on TS voltage                                          | Voltage on BAT pin in valid range           | 0.65                                            | 1.2                                       | V    |

| V <sub>WAKEONVC0</sub> | Wake on VC0 voltage                                         | Voltage on BAT pin in valid range           | 0.65                                            | 1.2                                       | V    |

| V <sub>IN</sub>        | Input voltage range                                         | ALERT, SCL, SDA                             | 0                                               | 5.5                                       | V    |

| V <sub>IN</sub>        | Input voltage range (with ADC measurements)                 | TS                                          | -0.2                                            | 1.8                                       | V    |

| V <sub>IN</sub>        | Input voltage range                                         | SRP, SRN, SRP-SRN (while measuring current) | -0.2                                            | 0.2                                       | V    |

| V <sub>IN</sub>        | Input voltage range                                         | SRP, SRN (without measuring current)        | -0.2                                            | 1.8                                       | V    |

| V <sub>IN</sub>        | Input voltage range <sup>(3)</sup>                          | V <sub>VC0</sub>                            | -0.2                                            | 3.0                                       | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC1</sub>                            | maximum of $V_{VC0} - 0.2$ or $VSS - 0.2$       | V <sub>VC0</sub> + 5.5                    | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC2</sub>                            | maximum of $V_{VC1} - 0.2$ or $VSS - 0.2$       | minimum of $V_{VC1}$ + 5.5 or VSS + 27.5  | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC3B</sub>                           | maximum of $V_{VC2} - 0.2$ or $VSS - 0.2$       | minimum of $V_{VC2}$ + 5.5 or VSS + 27.5  | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC3A</sub>                           | maximum of $V_{VC3B} - 0.2$ or $VSS - 0.2$      | minimum of $V_{VC3B}$ + 0.1 or VSS + 27.5 | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC4B</sub>                           | maximum of V <sub>VC3A</sub> – 0.2 or VSS + 2.0 | minimum of $V_{VC3A}$ + 5.5 or VSS + 27.5 | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC4A</sub>                           | maximum of V <sub>VC4B</sub> – 0.2 or VSS + 2.0 | minimum of $V_{VC4B}$ + 0.1 or VSS + 27.5 | V    |

| V <sub>IN</sub>        | Input voltage range                                         | V <sub>VC5</sub>                            | maximum of V <sub>VC4A</sub> – 0.2 or VSS + 2.0 | minimum of $V_{VC4A}$ + 5.5 or VSS + 27.5 | V    |

| Vo                     | Output voltage range                                        | CHG                                         | -25                                             | 27.5                                      | V    |

| Vo                     | Output voltage range                                        | DSG                                         | -0.2                                            | 14                                        | V    |

| I <sub>CB</sub>        | Cell balancing current (internal, per cell) <sup>(3)</sup>  |                                             | 0                                               | 50                                        | mA   |

| R <sub>C</sub>         | External cell input resistance <sup>(2) (3)</sup>           |                                             | 10                                              | 1000                                      | Ω    |

| C <sub>C</sub>         | External cell input capacitance <sup>(2) (3)</sup>          |                                             | 0.1                                             | 10                                        | μF   |

| R <sub>f</sub>         | External supply filter resistance (BAT pin) <sup>(3)</sup>  |                                             | 50                                              | 1000                                      | Ω    |

| C <sub>f</sub>         | External supply filter capacitance (BAT pin) <sup>(3)</sup> |                                             | 1                                               | 40                                        | μF   |

| R <sub>filt</sub>      | Sense resistor filter resistance <sup>(3)</sup>             |                                             |                                                 | 100 200                                   | Ω    |

| C <sub>REGSRC</sub>    | REGSRC capacitance <sup>(3)</sup>                           |                                             | 1                                               |                                           | μF   |

Copyright © 2023 Texas Instruments Incorporated

6

## 6.3 Recommended Operating Conditions (続き)

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = 18.5 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}\text{C}$  to 110°C and  $V_{BAT} = 3 \text{ V}$  to 27.5 V (unless otherwise noted)

|                  | PARAMETER                                            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------------------------|-----------------|-----|-----|-----|------|

| R <sub>TS</sub>  | External thermistor nominal resistance at 25°C       |                 |     | 10  |     | kΩ   |

| T <sub>OPR</sub> | Junction temperature during operation <sup>(1)</sup> |                 | -40 |     | 110 | °C   |

- (1) Power dissipated within device should be limited to ensure junction temperature remains within specification during operation.

- (2) External cell input resistance times external input capacitance should be limited to 200 µs or below.

- (3) Specified by design

### **6.4 Thermal Information**

|                          |                                              | BQ76905   |      |

|--------------------------|----------------------------------------------|-----------|------|

|                          | THERMAL METRIC <sup>(1)</sup>                | RGR (QFN) | UNIT |

|                          |                                              | 20 PINS   |      |

| R <sub>0JA</sub>         | Junction-to-ambient thermal resistance       | 47.2      | °C/W |

| R <sub>0JC(top)</sub>    | Junction-to-case (top) thermal resistance    | 47.9      | °C/W |

| R <sub>0JC(bottom)</sub> | Junction-to-case (bottom) thermal resistance | 8.3       | °C/W |

| R <sub>θJB</sub>         | Junction-to-board thermal resistance         | 23.4      | °C/W |

| $\Psi_{JT}$              | Junction-to-top characterization parameter   | 1.4       | °C/W |

| $\Psi_{JB}$              | Junction-to-board characterization parameter | 23.4      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

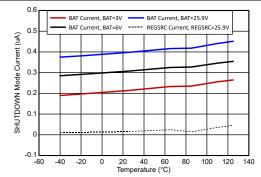

## 6.5 Supply Current

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $110^{\circ}C$  and  $V_{BAT} = 3$  V to 27.5 V (unless otherwise noted)

| P                      | ARAMETER       | TEST CONDITIONS                                                                                                                                                                                                             | MIN | TYP | MAX | UNIT |

|------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| INORMAL                | Normal Mode    | Regular measurements and protections active, REGOUT = 3.3 V with no load, CHG = ON, DSG = ON, Settings:Configuration:Power Config[IADCSPEED] = 0x0, Settings:Configuration:Power Config[CVADCSPEED] = 0x0, no communication |     | 146 |     | μА   |

| I <sub>SLEEP</sub>     | SLEEP Mode     | Periodic protections and monitoring, no pack current, REGOUT = OFF, CHG = OFF, DSG = ON, no communication, <b>Power:Sleep:Voltage Time</b> = 5 s                                                                            |     | 5.9 |     | μΑ   |

| I <sub>DEEPSLEEP</sub> | DEEPSLEEP Mode | No monitoring or protections, REGOUT = 3.3 V with no load, LFO = OFF, no communication                                                                                                                                      |     | 2.9 |     | μΑ   |

| I <sub>SHUTDOWN</sub>  | SHUTDOWN Mode  | All blocks powered down, no monitoring or protections, no communication                                                                                                                                                     |     | 1   | 2   | μΑ   |

## 6.6 Digital I/O

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = 18.5 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}\text{C}$  to 110°C and  $V_{BAT} = 3 \text{ V}$  to 27.5 V (unless otherwise noted)

| PARAMETER       |                  | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-----------------|------------------|-----------------|------|-----|------|------|

| V <sub>IH</sub> | High-level input | SCL, SDA        | 1.23 |     | 5.5  | V    |

| V <sub>IL</sub> | Low-level input  | SCL, SDA        |      |     | 0.53 | V    |

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ) を送信

## 6.6 Digital I/O (続き)

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $110^{\circ}C$  and  $V_{BAT} = 3$  V to 27.5 V (unless otherwise noted)

|                  | PARAMETER                        | TEST CONDITIONS                                                             | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OL</sub>  | Output voltage low               | ALERT, SCL, SDA, V <sub>BAT</sub> ≥ 3 V, I <sub>OL</sub> = 5 mA, 10-pF load |     |     | 0.4 | V    |

| C <sub>IN</sub>  | Input capacitance <sup>(1)</sup> | ALERT, SCL, SDA                                                             |     | 2   |     | pF   |

| I <sub>LKG</sub> | Input leakage current            | ALERT, SCL, SDA, device in<br>SHUTDOWN mode                                 |     |     | 1   | μΑ   |

<sup>(1)</sup> Specified by design

### **6.7 REGOUT LDO**

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = 18.5 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}\text{C}$  to 110°C and  $V_{BAT} = 3 \text{ V}$  to 27.5 V (unless otherwise noted)

| ,                           | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                                                                | MIN  | TYP     | MAX  | UNIT   |

|-----------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|--------|

| V <sub>REGOUT_1.8_LOW</sub> | Regulator voltage (nominal 1.8-V setting)                | V <sub>BAT</sub> , V <sub>REGSRC</sub> = 3.0 V,<br>I <sub>REGOUT</sub> = 10 mA                                                                                                                                 | 1.62 | 1.8     | 1.92 | V      |

| V <sub>REGOUT_1.8</sub>     | Regulator voltage (nominal 1.8-V setting) <sup>(1)</sup> | $V_{BAT} \ge 3.0 \text{ V}, V_{REGSRC} \ge 3.8 \text{ V},$<br>$I_{REGOUT} = 0 \text{ mA to } 20 \text{ mA}$                                                                                                    | 1.62 | 1.8     | 1.92 | V      |

| V <sub>REGOUT_2.5_LOW</sub> | Regulator voltage (nominal 2.5-V setting) <sup>(1)</sup> | $V_{BAT}$ , $V_{REGSRC}$ = 3.0 V,<br>$I_{REGOUT}$ = 10 mA                                                                                                                                                      | 2.25 | 2.5     | 2.75 | V      |

| V <sub>REGOUT_2.5</sub>     | Regulator voltage (nominal 2.5-V setting) <sup>(1)</sup> | $V_{BAT} \ge 3.0 \text{ V}, V_{REGSRC} \ge 3.8 \text{ V},$<br>$I_{REGOUT} = 0 \text{ mA to } 20 \text{ mA}$                                                                                                    | 2.25 | 2.5     | 2.75 | V      |

| V <sub>REGOUT_3.0</sub>     | Regulator voltage (nominal 3.0-V setting) <sup>(1)</sup> | $V_{BAT} \ge 3.0 \text{ V}, V_{REGSRC} \ge 3.8 \text{ V},$<br>$I_{REGOUT} = 0 \text{ mA to } 20 \text{ mA}$                                                                                                    | 2.7  | 3.0     | 3.3  | V      |

| V <sub>REGOUT_3.3</sub>     | Regulator voltage (nominal 3.3-V setting) <sup>(1)</sup> | $V_{BAT} \ge 3.0 \text{ V}, V_{REGSRC} \ge 4.2 \text{ V},$<br>$I_{REGOUT} = 0 \text{ mA to } 20 \text{ mA}$                                                                                                    | 3    | 3.3     | 3.6  | V      |

| V <sub>REGOUT_5.0</sub>     | Regulator voltage (nominal 5.0-V setting) <sup>(1)</sup> | $V_{BAT} \ge 3.0 \text{ V}, V_{REGSRC} \ge 5.5 \text{ V},$<br>$I_{REGOUT} = 0 \text{ mA to } 20 \text{ mA}$                                                                                                    | 4.5  | 5.0     | 5.5  | V      |

| $\Delta V_{O(TEMP)}$        | Regulator output over temperature                        | $\Delta V_{REGOUT}$ vs ( $V_{REGOUT}$ at 25°C, $I_{REGOUT}$ = 20 mA, $V_{BAT}$ = 5.5 V, $V_{REGOUT}$ set to nominal 3.3-V setting)                                                                             |      | ±0.015% |      | % / °C |

| $\Delta V_{O(LINE)}$        | Line regulation <sup>(1)</sup>                           | ΔV <sub>REGOUT</sub> vs (V <sub>REGOUT</sub> at 25°C, V <sub>BAT</sub> = 4.2 V, I <sub>REGOUT</sub> = 5 mA), as V <sub>BAT</sub> varies from 4.2 V to 27.5 V, V <sub>REGOUT</sub> set to nominal 3.3-V setting | -1%  |         | 1%   |        |

| I <sub>SC</sub>             | Regulator short-circuit current limit                    | V <sub>REGOUT</sub> = 0 V                                                                                                                                                                                      | 23   |         | 50   | mA     |

| C <sub>EXT</sub>            | External capacitor REGOUT to VSS <sup>(2)</sup>          |                                                                                                                                                                                                                | 1    |         |      | μF     |

<sup>(1)</sup> Specified by a combination of characterization and production test

## 6.8 Voltage References

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

| PARAMETER                |                                      | TEST CONDITIONS                 | MIN    | TYP    | MAX    | UNIT   |  |

|--------------------------|--------------------------------------|---------------------------------|--------|--------|--------|--------|--|

| VOLTAGE REFERENCE 1      |                                      |                                 |        |        |        |        |  |

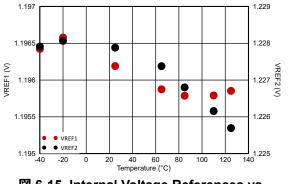

| V <sub>(REF1)</sub>      | Internal reference voltage (1)       | T <sub>A</sub> = 25°C           | 1.1955 | 1.1962 | 1.1969 | V      |  |

| V <sub>(REF1DRIFT)</sub> | Internal reference voltage drift (1) | T <sub>A</sub> = -40°C to 110°C |        | ±29    |        | PPM/°C |  |

資料に関するフィードバック (ご意見やお問い合わせ) を送信 Product Folder Links: BQ76905 Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> Specified by design

## 6.8 Voltage References (続き)

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}C$  to  $110^{\circ}C$  and  $V_{BAT} = 3 \text{ V}$  to 27.5 V (unless otherwise noted)

| PARAMETER                |                                                 | TEST CONDITIONS         | MIN   | TYP   | MAX   | UNIT   |

|--------------------------|-------------------------------------------------|-------------------------|-------|-------|-------|--------|

| VOLTAGE RE               | FERENCE 2                                       |                         |       |       |       |        |

| V <sub>(REF2)</sub>      | Internal reference voltage (2)                  | T <sub>A</sub> = 25°C   | 1.226 | 1.227 | 1.229 | V      |

| V <sub>(REF2DRIFT)</sub> | Internal reference voltage drift <sup>(2)</sup> | $T_A = -40$ °C to 110°C |       | ±52   |       | PPM/°C |

<sup>(1)</sup> V<sub>(REF1)</sub> is used for the ADC reference. Its effective value is determined through indirect measurement using the ADC.

#### 6.9 Coulomb Counter

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to 110°C and  $V_{BAT} = 3$  V to 27.5 V (unless otherwise noted)

| PARAMETER                   |                                                     | TEST CONDITIONS                                                                                                                                                                  | MIN    | TYP    | MAX    | UNIT                        |

|-----------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-----------------------------|

| V <sub>(CC_IN)</sub>        | Input voltage range for measurements <sup>(3)</sup> | V <sub>SRP</sub> – V <sub>SRN</sub>                                                                                                                                              | -0.2   |        | 0.2    | V                           |

| V <sub>(CC_IN)</sub>        | Input voltage range for measurements <sup>(3)</sup> | V <sub>SRP</sub> , V <sub>SRN</sub>                                                                                                                                              | -0.2   |        | 0.2    | V                           |

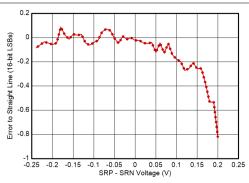

| B <sub>(CM_INL)</sub>       | Integral nonlinearity <sup>(2)</sup>                | 16-bit, best fit straight line over input voltage range of –200 mV to 0 mV, using <i>Current()</i> command data with <i>Curr Gain</i> = 32, such that 1-LSB ≈ 7.52 µV, at 25°C   |        | ±0.42  | ±1.23  | LSB <sup>(1)</sup>          |

| B <sub>(CM_INL)</sub>       | Integral nonlinearity <sup>(2)</sup>                | 16-bit, best fit straight line over input voltage range of –200 mV to 100 mV, using <i>Current()</i> command data with <i>Curr Gain</i> = 32, such that 1-LSB ≈ 7.52 µV, at 25°C |        | ±0.86  | ±3.2   | LSB <sup>(1)</sup>          |

| V <sub>(CM_OFF)</sub>       | Offset error                                        | 16-bit, uncalibrated, using <i>Current()</i> command data with <i>Curr Gain</i> = 32, such that 1-LSB ≈ 7.52 μV                                                                  | -1.37  | 0.033  | 1.49   | μV                          |

| V <sub>(CM_OFF_DRIFT)</sub> | Offset error drift <sup>(2)</sup>                   | 16-bit, uncalibrated, using <i>Current()</i> command data with <i>Curr Gain</i> = 32, such that 1-LSB ≈ 7.52 μV                                                                  | -0.032 |        | 0.032  | μV/°C                       |

| B <sub>(CM_GAIN)</sub>      | Gain <sup>(2)</sup>                                 | Using 16-bit data from <i>Current()</i> command, with <i>Curr Gain</i> = 32, V <sub>SRP</sub> – V <sub>SRN</sub> = ±0.2V                                                         | 131949 | 132910 | 133981 | LSB/V <sup>(1)</sup>        |

| B <sub>(CM_GAIN)</sub>      | Gain drift (2)                                      | Using 16-bit data from <i>Current()</i> command, with <i>Curr Gain</i> = 32, V <sub>SRP</sub> – V <sub>SRN</sub> = ±0.2V                                                         | -19    | 0.72   | 16     | LSB/V/<br>°C <sup>(1)</sup> |

| R <sub>(CM_IN)</sub>        | Effective input resistance <sup>(3)</sup> (4)       |                                                                                                                                                                                  | 2      |        |        | МΩ                          |

<sup>(1) 1</sup> LSB =  $V_{REF2}$  / (5 × 2<sup>N-1</sup>) ≈ 1.227 / (5 × 2<sup>15</sup>) = 7.49  $\mu$ V

### 6.10 Coulomb Counter Digital Filter

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = 18.5 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}\text{C}$  to 110°C and  $V_{BAT} = 3 \text{ V}$  to 27.5 V (unless otherwise noted)

| to 21.0 V (unless otherwise noted)     |                                         |                                                                                            |      |     |     |      |  |  |  |

|----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------|------|-----|-----|------|--|--|--|

| PARAMETER                              |                                         | TEST CONDITIONS                                                                            | MIN  | TYP | MAX | UNIT |  |  |  |

| CC1 Charge Integration Digital Filter  |                                         |                                                                                            |      |     |     |      |  |  |  |

| t <sub>(CC1_CONV)</sub>                | Conversion-time                         | Single conversion                                                                          |      | 250 |     | ms   |  |  |  |

| B <sub>(CC1_RSL)</sub>                 | Effective resolution <sup>(1) (2)</sup> | Single conversion, DC inputs from $-$ 200 mV to 0 mV across $V_{SRP} - V_{SRN}$ , at 25°C. | 15.5 |     |     | bits |  |  |  |

| CC2 Current Measurement Digital Filter |                                         |                                                                                            |      |     |     |      |  |  |  |

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

9

English Data Sheet: SLUSE97

<sup>(2)</sup>  $V_{(REF2)}$  is used for the coulomb counter, LDOs, and comparator protection subsystem.

<sup>(2)</sup> Specified by characterization

<sup>(3)</sup> Specified by design

<sup>(4)</sup> Average effective differential input resistance with device operating in NORMAL mode, 0.1-V differential input applied

# 6.10 Coulomb Counter Digital Filter (続き)

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

| PARAMETER                        |                                                                            | TEST CONDITIONS                                                                                                                                     | MIN TYP |      | MAX | UNIT |

|----------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----|------|

| t(CM_CONV)                       | Conversion-time in slow mode                                               | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x0                                                       |         | 2.93 |     | ms   |

| t(CM_CONV_MEDSLOW)               | Conversion-time in medium slow mode                                        | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x1                                                       |         | 1.46 |     | ms   |

| t(CM_CONV_MEDFAST)               | Conversion-time in medium fast mode                                        | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x2                                                       |         | 732  |     | μs   |

| t(CM_CONV_FAST)                  | Conversion-time in fast mode                                               | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x3                                                       |         | 366  |     | μs   |

| B <sub>(CM_RES)</sub>            | Effective resolution in slow mode <sup>(1)</sup> (2)                       | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x0                                                       | 15.5    | 16   |     | bits |

| B <sub>(CM_RES_MEDSLOW)</sub>    | Effective resolution in medium slow mode <sup>(1)</sup>                    | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x1                                                       |         | 15.7 |     | bits |

| B <sub>(CM_RES_MEDFAST)</sub>    | Effective resolution in medium fast mode <sup>(1)</sup>                    | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x2                                                       |         | 14.9 |     | bits |

| B <sub>(CM_RES_FAST)</sub>       | Effective resolution in fast mode <sup>(1)</sup>                           | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] = 0x3                                                       |         | 12.9 |     | bits |

| B <sub>(CM_LP_RES)</sub>         | Effective resolution in slow mode and low power mode <sup>(1)</sup> (2)    | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] =<br>0x0, Settings:Configuration:DA<br>Config[CCMODE] = 0x2 | 15.5    | 16   |     | bits |

| B <sub>(CM_LP_RES_MEDSLOW)</sub> | Effective resolution in medium slow mode and low power mode <sup>(1)</sup> | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] =<br>0x1, Settings:Configuration:DA<br>Config[CCMODE] = 0x2 |         | 15.7 |     | bits |

| B <sub>(CM_LP_RES_MEDFAST)</sub> | Effective resolution in medium fast mode and low power mode <sup>(1)</sup> | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] =<br>0x2, Settings:Configuration:DA<br>Config[CCMODE] = 0x2 |         | 14.9 |     | bits |

| B <sub>(CM_LP_RES_FAST)</sub>    | Effective resolution in fast mode and low power mode <sup>(1)</sup>        | Single conversion, in NORMAL mode,<br>Settings:Configuration:Power<br>Config[IADCSPEED] =<br>0x3, Settings:Configuration:DA<br>Config[CCMODE] = 0x2 |         | 12.9 |     | bits |

<sup>(1)</sup> Effective resolution is defined as the resolution such that the data exhibits 1-sigma variation within ±1-LSB.

Copyright © 2023 Texas Instruments Incorporated

10

<sup>(2)</sup> Specified by characterization

# **6.11 Current Wake Detector**

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

|                       | PARAMETER                                                                                                                           | TEST CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 1, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 186  | 271  | 355  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 2, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 670  | 794  | 921  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 3, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 1145 | 1317 | 1503 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 4, positive threshold (charging current) (1)             | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 1594 | 1838 | 2089 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 5, positive threshold (charging current) (1)             | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 2056 | 2364 | 2676 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 6, positive threshold (charging current) (1)             | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 2516 | 2890 | 3276 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 7, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 3000 | 3419 | 3851 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 8, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 3460 | 3942 | 4443 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 9, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 3893 | 4466 | 5045 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 10, positive threshold (charging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise  | 4386 | 4994 | 5627 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 1, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 88   | 275  | 462  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 2, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 581  | 794  | 978  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 3, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 1050 | 1317 | 1537 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 4, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 1527 | 1836 | 2106 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 5, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 1974 | 2360 | 2711 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 6, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 2483 | 2885 | 3290 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 7, positive threshold (charging current) <sup>(1)</sup>  | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | 2897 | 3412 | 3885 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 8, positive threshold (charging current) (1)             | $T_A = -40$ °C to 110°C. Measured using averaged data to remove effects of noise         | 3357 | 3933 | 4498 | μV   |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

Product Folder Links: BQ76905

English Data Sheet: SLUSE97

# 6.11 Current Wake Detector (続き)

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

|                       | PARAMETER                                                                                                                             | TEST CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNIT |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 9, positive threshold (charging current) <sup>(1)</sup>    | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise. | 3793  | 4458  | 5062  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 10, positive threshold (charging current) <sup>(1)</sup>   | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise. | 4261  | 4986  | 5654  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 1, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -719  | -635  | -546  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 2, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -1234 | -1118 | -1005 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 3, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -1736 | -1605 | -1469 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 4, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -2262 | -2088 | -1917 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 5, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -2794 | -2579 | -2354 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 6, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -3324 | -3067 | -2805 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 7, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -3849 | -3552 | -3245 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 8, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -4369 | -4037 | -3704 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 9, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -4913 | -4527 | -4129 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 10, negative threshold (discharging current) (1)           | T <sub>A</sub> = -20°C to 65°C. Measured using averaged data to remove effects of noise   | -5425 | -5012 | -4577 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 1, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise  | -862  | -630  | -369  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 2, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise  | -1340 | -1113 | -865  | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 3, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise  | -1887 | -1600 | -1284 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 4, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise  | -2387 | -2087 | -1765 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 5, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise  | -2949 | -2575 | -2179 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 6, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise  | -3487 | -3064 | -2622 | μV   |

Copyright © 2023 Texas Instruments Incorporated

12

# 6.11 Current Wake Detector (続き)

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

|                       | PARAMETER                                                                                                                             | TEST CONDITIONS                                                                          | MIN   | TYP   | MAX   | UNIT |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 7, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | -3991 | -3548 | -3083 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 8, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | -4599 | -4033 | -3420 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 9, negative threshold (discharging current) <sup>(1)</sup> | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | -5067 | -4521 | -3918 | μV   |

| V <sub>WAKE_THR</sub> | Wakeup voltage threshold (V <sub>SRP</sub> – V <sub>SRN</sub> ), setting = 10, negative threshold (discharging current) (1)           | T <sub>A</sub> = -40°C to 110°C. Measured using averaged data to remove effects of noise | -5580 | -5011 | -4415 | μV   |

| t <sub>WAKE</sub>     | Measurement interval                                                                                                                  |                                                                                          |       | 2.44  |       | ms   |

<sup>(1)</sup> Specified by a combination of characterization and production test

# 6.12 Analog-to-Digital Converter

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

| PARAI                       | METER                                                                               | TEST CONDITIONS                                                                                                                                                                    | MIN   | TYP   | MAX   | UNIT               |

|-----------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| V <sub>(ADC_IN_CELLS)</sub> | Input voltage range<br>(differential cell input<br>mode) <sup>(2) (4)</sup>         | Internal reference (Vref = V <sub>REF1</sub> )                                                                                                                                     | -0.2  |       | 5.5   | V                  |

| V <sub>(ADC_IN)</sub>       | Input voltage ran ge<br>(ADCIN measurement<br>mode) <sup>(2)</sup> (6)              | Internal reference (Vref = V <sub>REF1</sub> ,<br><b>Settings:Configuration:DA</b><br><b>Config[TSMODE]</b> = 1), applicable to ADCIN<br>measurements using the TS pin             | -0.2  |       | 1.8   | V                  |

| V <sub>(ADC_IN_TS)</sub>    | Input voltage range<br>(external thermistor<br>measurement mode)<br>(2) (5)         | Regulator reference (Vref = V <sub>REG18</sub> ,<br><b>Settings:Configuration:DA</b><br><b>Config[TSMODE]</b> = 0), applicable to external thermistor measurement using the TS pin | -0.2  |       | 1.8   | V                  |

| V <sub>(ADC_IN_DIV)</sub>   | Input voltage range<br>(divider measurement<br>mode) <sup>(2)</sup> (7)             | Internal reference (Vref = V <sub>REF1</sub> ), applicable to divider measurements using the VC5 pin relative to VSS.                                                              | 2.0   |       | 27.5  | V                  |

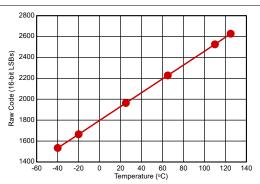

| B <sub>(ADC_OFF_CELL)</sub> | Differential cell offset error                                                      | 16-bit, uncalibrated, with VC5 - VC4A = 0 V, VC4A = 27 V, using raw ADC codes                                                                                                      |       | 2.4   |       | LSB (4)            |

| D                           | Differential cell offset                                                            | 16-bit, uncalibrated, with VC5 - VC4A = 0 V,<br>VC4A = 27 V, using raw ADC codes, over<br>-20°C to +65°C                                                                           | -0.26 |       | 0.26  | LSB/°C (4)         |

| B(ADC_OFF_DRIFT_CELL)       | error drift <sup>(3)</sup>                                                          | 16-bit, uncalibrated, with VC5 - VC4A = 0 V,<br>VC4A = 27 V, using raw ADC codes, over<br>-40°C to +110°C                                                                          | -0.41 |       | 0.41  | LSB/°C (4)         |

| B <sub>(ADC_OFF)</sub>      | ADCIN offset error                                                                  | 16-bit, uncalibrated, using ADCIN mode on TS pin                                                                                                                                   |       | -0.5  |       | LSB <sup>(6)</sup> |

| B <sub>(ADC_OFF_DIV)</sub>  | Divider offset error                                                                | 16-bit, uncalibrated, using divider mode on VC5                                                                                                                                    |       | -3.7  |       | LSB <sup>(7)</sup> |

| G <sub>(ADC_TS_REG18)</sub> | Gain of ADC TS pin<br>measurement using<br>Vref = V <sub>REG18</sub> <sup>(9)</sup> | Reported digital code = $G_{(ADC\_TS\_REG18)} \times V_{TS} / V_{REG18}$ . 16-bit, uncalibrated, using TS pin, input range from 0.1 V to 1.8 V.                                    | 19083 | 19405 | 19750 | N/A <sup>(5)</sup> |

| G <sub>(ADC_TS_ADCIN)</sub> | Gain of ADC TS pin<br>measurement using<br>Vref = V <sub>REF1</sub> <sup>(9)</sup>  | Reported digital code = $G_{(ADC\_TS\_ADCIN)} \times V_{TS}$ . 16-bit, uncalibrated, using $\overline{T}S$ pin, input range from 0.1 V to 1.8 V.                                   | 15768 | 16027 | 16261 | LSB/V (6)          |

Product Folder Links: BQ76905

資料に関するフィードバック(ご意見やお問い合わせ)を送信

13

English Data Sheet: SLUSE97

# 6.12 Analog-to-Digital Converter (続き)

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 18.5 V, min/max values stated where  $T_A$  = -40°C to 110°C and  $V_{BAT}$  = 3 V to 27.5 V (unless otherwise noted)

| PARA                           | METER                                                              | TEST CONDITIONS                                                                                                                                         | MIN   | TYP  | MAX  | UNIT                        |

|--------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-----------------------------|

| $G_{(ADC\_CELL\_RAW)}$         | Raw gain of ADC cell<br>voltage measurement                        | Gain measured 16-bit, over input voltage range 1.0 V to 5.0 V, differential cell input mode on VC5 - VC4A, uncalibrated, using raw ADC codes.           | 5458  | 5479 | 5502 | LSB/V (4)                   |

| Bung our priet                 | Gain drift <sup>(3)</sup>                                          | Gain measured 16-bit using Cell 5, VC5 - VC4A = 4.5 V. VC5 = 23 V, uncalibrated, using raw ADC codes, over -20°C to +65°C                               | -0.17 |      | 0.23 | LSB/V/<br>°C <sup>(4)</sup> |

| B <sub>(ADC_GAIN_DRIFT)</sub>  | Gain diffe.                                                        | Gain measured 16-bit using Cell 5, VC5 - VC4A = 4.5 V. VC4A = 23 V, uncalibrated, using raw ADC codes, over -40°C to +110°C                             | -0.32 |      | 0.23 | LSB/V/<br>°C <sup>(4)</sup> |

| R <sub>(ADC_IN_CELL)</sub>     | Effective input resistance <sup>(8)</sup>                          | Differential cell input mode on VC5 - VC4A                                                                                                              |       | 4    |      | МΩ                          |

| R <sub>(ADC_IN_TOS)</sub>      | Effective input resistance                                         | Divider measurement on VC5 pin (only active while the pin is being measured)                                                                            |       | 600  |      | kΩ                          |

| I <sub>(LEAKAGE)</sub>         | Pin leakage current <sup>(3)</sup>                                 | Input current per pin into VC1 $\sim$ VC5, BAT, REGSRC, with no conversions, stack biased with 5 V / cell, $V_{BAT}$ = 27.5 V, device in SHUTDOWN mode. |       |      | 2    | μА                          |

| B <sub>(ADC_RES_SLOW)</sub>    | Effective resolution with slow speed setting <sup>(1)</sup> (3)    | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] = 0x0, using TS input in ADCIN mode.                                 | 14    | 16   |      | bits                        |

| B <sub>(ADC_RES_MEDSLOW)</sub> | Effective resolution with medium slow speed setting <sup>(1)</sup> | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] = 0x1, using TS input in ADCIN mode.                                 |       | 15.5 |      | bits                        |

| B <sub>(ADC_RES_MEDFAST)</sub> | Effective resolution with medium fast speed setting <sup>(1)</sup> | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] = 0x2, using TS input in ADCIN mode.                                 |       | 14.5 |      | bits                        |

| B <sub>(ADC_RES_FAST)</sub>    | Effective resolution with fast speed setting <sup>(1)</sup>        | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] = 0x3, using TS input in ADCIN mode.                                 |       | 12   |      | bits                        |

| t(ADC_CONV_SLOW)               | Conversion-time                                                    | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] and [IADCSPEED] = 0x0                                                |       | 2.93 |      | ms                          |

| t(ADC_CONV_MEDSLOW)            | Conversion-time in medium slow mode                                | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] and [IADCSPEED] = 0x1                                                |       | 1.46 |      | ms                          |

| t(ADC_CONV_MEDFAST)            | Conversion-time in medium fast mode                                | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] and [IADCSPEED] = 0x2                                                |       | 732  |      | μs                          |

| t(ADC_CONV_FAST)               | Conversion-time in fast mode                                       | Single conversion, in NORMAL mode, Settings:Configuration:Power Config[CVADCSPEED] and [IADCSPEED] = 0x3                                                |       | 366  |      | μs                          |

Copyright © 2023 Texas Instruments Incorporated

14

## 6.12 Analog-to-Digital Converter (続き)

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $110^{\circ}C$  and  $V_{BAT} = 3$  V to 27.5 V (unless otherwise noted)