🕳 Order

Now

bq51003

JAJSEG4C – DECEMBER 2013 – REVISED JULY 2018

Support &

Community

20

# bq51003 Qi (WPC v1.2)に準拠した高集積ワイヤレス給電レシーバ

Technical

Documents

# 1 特長

- 高集積ワイヤレス給電レシーバ・ソリューション

2.5W給電用に最適化

- 全体ピークAC-DC効率: 93%

- 完全な同期整流回路

- WPC v1.2準拠の通信制御

- 出力電圧調整

- RXコイルと出力の間に必要な唯一のIC

- Wireless Power Consortium (WPC) v1.2準拠(FOD イネーブル)の高精度電流センス

- 整流回路の動的制御により負荷過渡応答を向上

- 動的効率スケーリングにより広範囲の出力電力で 性能を最適化

- 適応型の通信制限により安定した通信を実現

- 最大20Vの入力をサポート

- 低消費電力の整流回路による過電圧クランプ (V<sub>RECT-OVP</sub>=15V)

- ・ サーマル・シャットダウン

- 温度監視、充電完了、フォルト・ホスト制御用の 多機能NTC/制御ピン

- 2 アプリケーション

- WPC準拠レシーバ

- 携帯電話、スマートフォン

- ヘッドセット

ΔÀ

- デジタル・カメラ

- ポータブル・メディア・プレーヤ

- ハンドヘルド機器

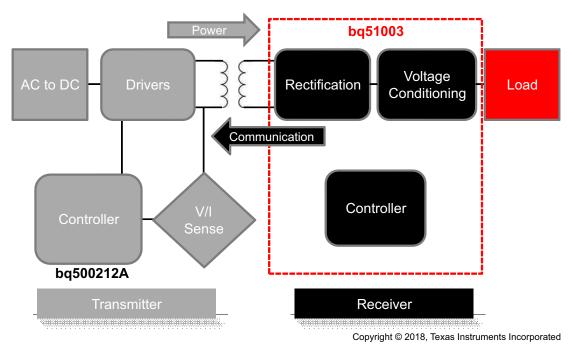

# 3 概要

Tools &

Software

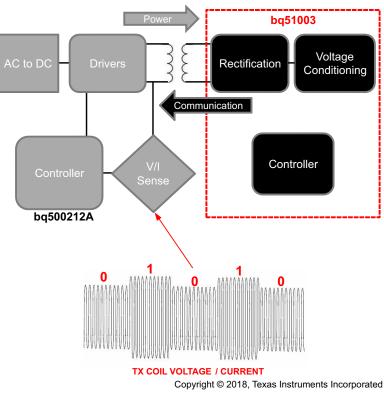

bq51003は最大2.5Wの給電用に最適化された、携帯機 器向けの先進的な高集積ワイヤレス給電レシーバIC です。AC/DC電力変換を実現し、Qi v1.2通信プロトコル への準拠に必要なデジタル制御を内蔵しています。 bq500212Aトランスミッタ・コントローラとの組み合わせによ り、ワイヤレス給電ソリューション用の完全な非接触電力伝 送システムを実現します。誘電式近距離電力伝送の採用 により、携帯機器に組み込まれたレシーバ・コイルが、相 互結合したインダクタを介して、トランスミッタ・コイルにより 伝送される電力を受け取ります。レシーバ・コイルからの AC信号は整流および制御され、接続先のシステムの電源 として使用されます。2次側からトランスミッタへのグローバ ル・フィードバックを確立することで、後方散乱変調により 電力伝送プロセスを安定化できます。このフィードバック は、最大2.5Wの給電に対応するQi v1.2通信プロトコルに より確立されます。

bq51003は、低インピーダンスの同期整流回路、低ドロッ プアウト・レギュレータ、デジタル制御、高精度の電圧/電 流ループを内蔵しています。

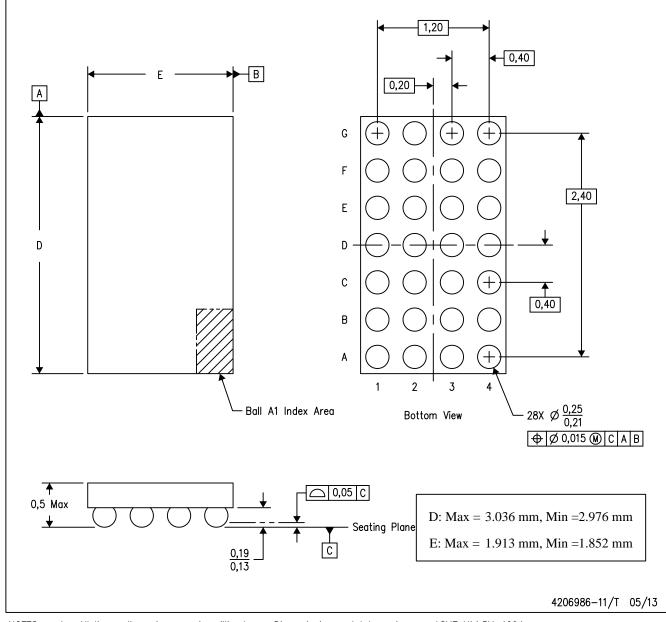

製品情報<sup>(1)</sup>

| 型番      | パッケージ      | 本体サイズ(公称)     |

|---------|------------|---------------|

| bq51003 | DSBGA (28) | 1.90mm×3.00mm |

|         |            |               |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

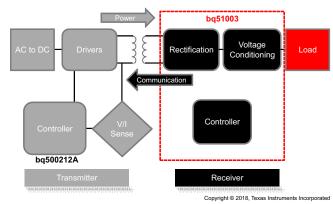

#### Wireless Power Consortium (WPCまたはQi)電磁誘 導給電システム

# 目次

| 1 | 特長   |                                    |

|---|------|------------------------------------|

| 2 | アプ   | リケーション1                            |

| 3 | 概要   |                                    |

| 4 | 改訂   | '履歴2                               |

| 5 | Dev  | ice Comparison Table 3             |

| 6 | Pin  | Configuration and Functions 4      |

| 7 | Spe  | cifications6                       |

|   | 7.1  | Absolute Maximum Ratings 6         |

|   | 7.2  | ESD Ratings 6                      |

|   | 7.3  | Recommended Operating Conditions 6 |

|   | 7.4  | Thermal Information7               |

|   | 7.5  | Electrical Characteristics7        |

|   | 7.6  | Typical Characteristics 9          |

| 8 | Deta | ailed Description 12               |

|   | 8.1  | Overview 12                        |

|   | 8.2  | Functional Block Diagram 13        |

|   | 8.3  | Feature Description 13             |

|    | 8.4  | Device Functional Modes     | 26   |

|----|------|-----------------------------|------|

| 9  | App  | lication and Implementation | 27   |

|    | 9.1  | Application Information     | 27   |

|    | 9.2  | Typical Applications        | 27   |

| 10 | Pow  | er Supply Recommendations   | 34   |

| 11 | Laye | out                         | 34   |

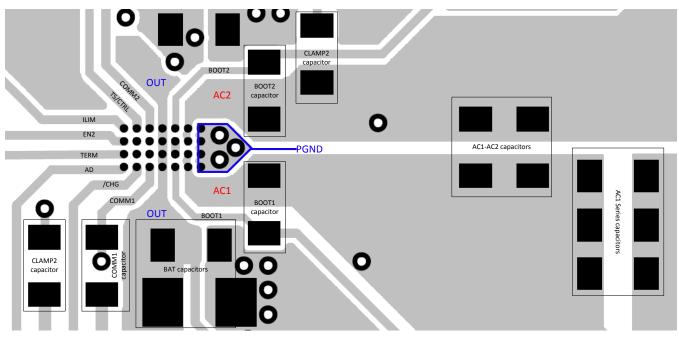

|    | 11.1 |                             |      |

|    | 11.2 | Layout Example              | 34   |

| 12 | デバ   | イスおよびドキュメントのサポート            | 35   |

|    | 12.1 | デバイス・サポート                   | 35   |

|    | 12.2 | ドキュメントの更新通知を受け取る方法          | . 35 |

|    | 12.3 | コミュニティ・リソース                 | 35   |

|    | 12.4 | 商標                          | 35   |

|    | 12.5 | 静電気放電に関する注意事項               | 35   |

|    | 12.6 | Glossary                    | 35   |

| 13 | メカニ  | ニカル、パッケージ、および注文情報           | 35   |

|    |      |                             |      |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Revision B (March 2017) から Revision C に変更

| • | 「bq500210との組み合わせにより」を「bq500212Aとの組み合わせにより」に変更(「概要」)                                 | 1  |

|---|-------------------------------------------------------------------------------------|----|

| • | Wireless Power Consortium (WPCまたはQi)電磁誘導給電システムの画像でbq500210をbq500212Aに変更             | 1  |

| • | Changed the Device Comparison Table                                                 | 3  |

| • | Changed bq500210 To: bq500212A in the Figure 17                                     | 12 |

| • | Changed "No Response" To: "EPT 0x00, Unknown" in the EPT column of Table 4          | 17 |

| • | Changed "Termination" To: " EPT 0x01, Charge Complete" in the EPT column of Table 4 | 17 |

| • | Added row "Unknown" to Table 5                                                      | 18 |

| • | Changed the condition of row "Charge Complete" in Table 5                           | 18 |

| • | Changed bq500210 To: bq500212A in the Figure 22                                     | 20 |

| • | Changed the 3-State Driver Recommendations for the TS-CTRL Pin section              | 25 |

|   |                                                                                     | _  |

#### Revision A (June 2016) から Revision B に変更

| • ドキュメント全体でWPC v1.1からWPC v1.2に変更1 |

|-----------------------------------|

|-----------------------------------|

# 2013年12月発行のものから更新

| • | 「ESD定格」の表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に  |

|---|------------------------------------------------------------------|

|   | 関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケー |

|   | ジ、および注文情報」セクションを追加。 1                                            |

| • | 注文信報の表および「                                                       |

パッケージ概要」セクションを削除、このデータシートの末尾にあるパッケージ注文情報を参照......

www.tij.co.jp

# Page

Page

Page

# 5 Device Comparison Table

| DEVICE              | FUNCTION                           | V <sub>OUT</sub> (V <sub>BAT-REG</sub> ) | MAXIMUM P <sub>OUT</sub> | I <sup>2</sup> C |

|---------------------|------------------------------------|------------------------------------------|--------------------------|------------------|

| bq51003             | Wireless Receiver                  | 5 V                                      | 2.5 W                    | No               |

| bq51013B            | Wireless Receiver                  | 5 V                                      | 5 W                      | No               |

| bq51010B            | Wireless Receiver                  | 7 V                                      | 5 W                      | No               |

| bq51020             | Wireless Receiver                  | 4.5 to 8 V                               | 5 W                      | No               |

| bq51021             | Wireless Receiver                  | 4.5 to 8 V                               | 5 W                      | Yes              |

| bq51221,<br>bq51222 | Dual Mode Wireless Receiver        | 4.5 to 8 V                               | 5 W                      | Yes              |

| bq51050B            | Wiress Receiver and Direct Charger | 4.2 V                                    | 5 W                      | No               |

| bq51051B            | Wiress Receiver and Direct Charger | 4.35 V                                   | 5 W                      | No               |

| bq51052B            | Wiress Receiver and Direct Charger | 4.4 V                                    | 5 W                      | No               |

# Table 1. Available Options

| DEVICE  | FUNCTION            | WPC<br>VERSION | V <sub>RECT-OVP</sub> | V <sub>OUT-(REG)</sub> | OVER<br>CURRENT<br>SHUTDOWN | AD-OVP   | TERMINATION | COMMUNICATION<br>CURRENT LIMIT <sup>(1)(2)</sup> |

|---------|---------------------|----------------|-----------------------|------------------------|-----------------------------|----------|-------------|--------------------------------------------------|

| bq51003 | 5-V Power<br>Supply | v1.2           | 15 V                  | 5 V                    | Disabled                    | Disabled | Disabled    | Adaptive + 1 s Hold-Off                          |

(1)

Enabled if EN2 is low and disabled if EN2 is high Communication current limit is disabled for 1 second at start-up (2)

TEXAS INSTRUMENTS

www.ti.com

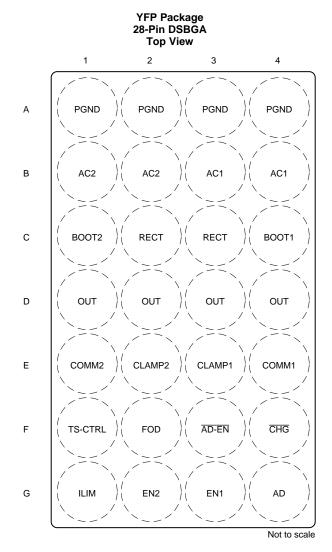

# 6 Pin Configuration and Functions

# **Pin Functions**

| PIN               |         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.               | NAME    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| B3, B4            | AC1     | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| B1, B2            | AC2     | I   | AC input from receiver coil antenna.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| G4                | AD      | I   | Connect this pin to the wired adapter input. When a voltage is applied to this pin wireless charging is disabled and $\overline{AD}_EN$ is driven low. Connect to GND through a 1 $\mu$ F capacitor. If unused, capacitor is not required and should be grounded directly.                                                                                                                                                                                                                                                                  |  |

| F3                | AD-EN   | о   | Push-pull driver for external PFET connecting AD and OUT. This node is pulled to the higher of OUT and AD when turning off the external FET. This voltage tracks approximately 4 V below AD when voltage is present at AD and provides a regulated $V_{GS}$ bias for the external FET. Float this pin if unused.                                                                                                                                                                                                                            |  |

| C4                | BOOT1   | 0   | Bootstrap capacitors for driving the high-side FETs of the synchronous rectifier. Connect a 10 nF                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| C1                | BOOT2   | 0   | ceramic capacitor from BOOT1 to AC1 and from BOOT2 to AC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| F4                | CHG     | 0   | Open-drain output – Active when the output of the wireless power supply is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| E3                | CLAMP1  | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| E2                | CLAMP2  | 0   | Open drain FETs which are utilized for a non-power dissipative over-voltage AC clamp protection. When the RECT voltage goes above 15 V, both switches will be turned on and the capacitors will act as a low impedance to protect the IC from damage. If used, CLAMP1 is required to be connected to AC1, and CLAMP2 is required to be connected to AC2 through $0.47$ -µF capacitors.                                                                                                                                                      |  |

| E4                | COMM1   | 0   | Dpen-drain output used to communicate with primary by varying reflected impedance. Connect CON                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| E1                | COMM2   | ο   | through a capacitor to either AC1 or AC2 for capacitive load modulation (COMM2 must be connected to the alternate AC1 or AC2 pin). For resistive modulation connect COMM1 and COMM2 to RECT through a single resistor; connect through separate capacitors for capacitive load modulation.                                                                                                                                                                                                                                                  |  |

| G3                | EN1     | I   | Inputs that allow user to enable/disable wireless and wired charging <en1 en2="">:</en1>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| G2                | EN2     | I   | <ul> <li>&lt;00&gt; Wireless charging is enabled</li> <li>&lt;01&gt; Dynamic communication current limit disabled</li> <li>&lt;10&gt; Wireless charging disabled</li> <li>&lt;11&gt; Wireless charging disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                 |  |

| F2                | FOD     | I   | Input for the recieved power measurement. Connect to GND with a R <sub>FOD</sub> resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| G1                | ILIM    | I/O | Programming pin for the over current limit. Connect external resistor to VSS. Size R <sub>ILIM</sub> with the following equation: R <sub>ILIM</sub> = 262 / I <sub>MAX</sub> where I <sub>MAX</sub> is the expected maximum output current of the wireless power supply. The hardware current limit (I <sub>ILIM</sub> ) will be 20% greater than I <sub>MAX</sub> or 1.2 x I <sub>MAX</sub> . If the supply is meant to operate in current limit use R <sub>ILIM</sub> = 314 / I <sub>ILIM</sub> R <sub>ILIM</sub> = R1 + R <sub>FOD</sub> |  |

| D1, D2,<br>D3, D4 | OUT     | Ο   | Output pin, delivers power to the load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| A1, A2,<br>A3, A4 | PGND    |     | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| C2, C3            | RECT    | 0   | Filter capacitor for the internal synchronous rectifier. Connect a ceramic capacitor to PGND. Depending on the power levels, the value may be 4.7 $\mu F$ to 22 $\mu F.$                                                                                                                                                                                                                                                                                                                                                                    |  |

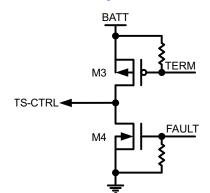

| F1                | TS-CTRL | I   | Must be connected to ground through a resistor. If an NTC function is not desired connect to GND with a 10-k $\Omega$ resistor. As a CTRL pin pull to ground to send end power transfer (EPT) fault to the transmitter or pullup to an internal rail (i.e. 1.8 V) to send EPT termination to the transmitter. Note that a 3-state driver should be used to interface this pin (see 3-State Driver Recommendations for the TS-CTRL Pin for further description).                                                                             |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                       |                                              | MIN  | MAX | UNIT   |  |

|---------------------------------------|----------------------------------------------|------|-----|--------|--|

|                                       | AC1, AC2                                     | -0.8 | 20  |        |  |

|                                       | RECT, COMM1, COMM2, OUT, CHG, CLAMP1, CLAMP2 | -0.3 | 20  |        |  |

| Input voltage                         | AD, AD-EN                                    | -0.3 | 30  | V      |  |

|                                       | BOOT1, BOOT2                                 | -0.3 | 26  |        |  |

|                                       | EN1, EN2, FOD, TS-CTRL, ILIM                 | -0.3 | 7   |        |  |

| Input current                         | AC1, AC2                                     |      | 1   | A(RMS) |  |

| Output current                        | OUT                                          |      | 525 | mA     |  |

| Output sink current                   | CHG                                          |      | 15  | mA     |  |

|                                       | COMM1, COMM2                                 |      | 1   | А      |  |

| Junction temperature, T <sub>J</sub>  |                                              | -40  | 150 | °C     |  |

| Storage temperature, T <sub>stg</sub> |                                              | 65   | 150 | °C     |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the VSS terminal, unless otherwise noted.

# 7.2 ESD Ratings

|                    |                                        |                                                                                | VALUE | UNIT |

|--------------------|----------------------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electroptotic discharge <sup>(1)</sup> | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(2)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge <sup>(1)</sup> | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(3)</sup> | ±500  | v    |

100 pF, 1.5 kΩ (1)

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

(3)

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                      |       | MIN | MAX | UNIT |

|--------------------|----------------------|-------|-----|-----|------|

| V <sub>IN</sub>    | Input voltage        | RECT  | 4   | 10  | V    |

| I <sub>IN</sub>    | Input current        | RECT  |     | 500 | mA   |

| I <sub>OUT</sub>   | Output current       | OUT   |     | 500 | mA   |

| I <sub>AD-EN</sub> | Sink current         | AD-EN |     | 1   | mA   |

| I <sub>COMM</sub>  | COMM sink current    | СОММ  |     | 500 | mA   |

| TJ                 | Junction temperature |       | 0   | 125 | °C   |

# 7.4 Thermal Information

|                       |                                              | bq51003     |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFP (DSBGA) | UNIT |

|                       |                                              | 28 PINS     |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 58.9        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.2         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.1         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.4         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 8.9         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | _           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

over operating free-air temperature range, 0°C to 125°C (unless otherwise noted)

| PARAMETER             |                                                                                                                          | TEST CONDITIONS                                                                                                  | MIN  | TYP                  | MAX  | UNIT |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|----------------------|------|------|

| UVLO                  | Undervoltage lockout                                                                                                     | $V_{RECT}$ : 0 V $\rightarrow$ 3 V                                                                               | 2.6  | 2.7                  | 2.8  | V    |

| <i>\</i> /            | Hysteresis on UVLO                                                                                                       | $V_{RECT}$ : 3 V $\rightarrow$ 2 V                                                                               |      | 250                  |      | mV   |

| V <sub>HYS</sub>      | Hysteresis on OVP                                                                                                        | $V_{RECT}$ : 16 V $\rightarrow$ 5 V                                                                              |      | 150                  |      | mV   |

| V <sub>RECT-OVP</sub> | Input overvoltage threshold                                                                                              | $V_{RECT}$ : 5 V $\rightarrow$ 16 V                                                                              | 14.5 | 15                   | 15.5 | V    |

|                       | Dynamic V <sub>RECT</sub> threshold 1                                                                                    | $I_{LOAD} < 0.1 \text{ x } I_{IMAX} (I_{LOAD} \text{ rising})$                                                   |      | 7.08                 |      |      |

|                       | Dynamic V <sub>RECT</sub> threshold 2                                                                                    | 0.1 x I <sub>IMAX</sub> < I <sub>LOAD</sub> < 0.2 x I <sub>IMAX</sub><br>(I <sub>LOAD</sub> rising)              |      | 6.28                 |      | V    |

| V <sub>RECT-REG</sub> | Dynamic V <sub>RECT</sub> threshold 3                                                                                    | $0.2 	ext{ x } I_{\text{IMAX}} < I_{\text{LOAD}} < 0.4 	ext{ x } I_{\text{IMAX}}$<br>( $I_{\text{LOAD}}$ rising) |      | 5.53                 |      | v    |

|                       | Dynamic V <sub>RECT</sub> threshold 4                                                                                    | $I_{LOAD} > 0.4 \text{ x } I_{IMAX} (I_{LOAD} \text{ rising})$                                                   |      | 5.11                 |      |      |

|                       | V <sub>RECT</sub> TRACKING                                                                                               | In current limit voltage above<br>V <sub>OUT</sub>                                                               | ,    | V <sub>O</sub> +0.25 |      |      |

| I <sub>LOAD</sub>     | $I_{\text{LOAD}}$ hysteresis for dynamic $V_{\text{RECT}}$ thresholds as a % of $I_{\text{ILIM}}$                        | I <sub>LOAD</sub> falling                                                                                        |      | 4%                   |      |      |

| V <sub>RECT-DPM</sub> | Rectifier undervoltage protection, restricts<br>I <sub>OUT</sub> at V <sub>RECT-DPM</sub>                                |                                                                                                                  | 3    | 3.1                  | 3.2  | V    |

| V <sub>RECT-REV</sub> | Rectifier reverse voltage protection at the<br>output                                                                    | $V_{RECT-REV} = V_{OUT} - V_{RECT},$<br>$V_{OUT} = 10 V$                                                         |      | 8                    | 9    | V    |

| QUIESCENT             | CURRENT                                                                                                                  |                                                                                                                  |      |                      |      |      |

|                       | Active chip quipecent current concumption                                                                                | $I_{LOAD} = 0 \text{ mA}, 0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}$                      |      | 8                    | 10   | mA   |

| I <sub>RECT</sub>     | Active chip quiescent current consumption<br>from RECT                                                                   | $I_{LOAD} = 300 \text{ mA},$<br>$0^{\circ}C \le T_{J} \le 85^{\circ}C$                                           |      | 2                    | 3    | mA   |

| I <sub>OUT</sub>      | Quiescent current at the output when<br>wireless power is disabled (Standby)                                             | $V_{OUT} = 5 \text{ V}, 0^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                                      |      | 20                   | 35   | μA   |

|                       | CIRCUIT                                                                                                                  |                                                                                                                  |      |                      |      |      |

| R <sub>ILIM</sub>     | Highest value of $I_{LIM}$ resistor considered a fault (short). Monitored for $I_{OUT}$ > 100 mA                         | $R_{ILIM}$ : 200 $\Omega \rightarrow 50 \Omega$ . $I_{OUT}$<br>latches off, cycle power to reset                 |      |                      | 120  | Ω    |

| t <sub>DGL</sub>      | Deglitch time transition from ${\rm I}_{\rm LIM}$ short to ${\rm I}_{\rm OUT}$ disable                                   |                                                                                                                  |      | 1                    |      | ms   |

| I <sub>LIM_SC</sub>   | $I_{\text{LIM-SHORT,OK}}$ enables the $I_{\text{LIM}}$ short comparator when $I_{\text{OUT}}$ is greater than this value | $I_{LOAD}$ : 0 mA $\rightarrow$ 200 mA                                                                           | 120  | 145                  | 165  | mA   |

|                       | Hysteresis for ILIM-SHORT, OK comparator                                                                                 | $I_{LOAD}$ : 0 mA $\rightarrow$ 200 mA                                                                           |      | 30                   |      | mA   |

| I <sub>OUT</sub>      | Maximum output current limit, CL                                                                                         | Maximum $I_{\text{LOAD}}$ that will be delivered for 1 ms when $I_{\text{LIM}}$ is shorted                       |      |                      | 2.45 | A    |

STRUMENTS

Texas

# **Electrical Characteristics (continued)**

over operating free-air temperature range, 0°C to 125°C (unless otherwise noted)

|                      | PARAMETER                                                                                                                             | TEST CONDITIONS                                                                                                                                                    | MIN  | TYP                 | MAX  | UNIT                       |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|----------------------------|--|

| OUTPUT               |                                                                                                                                       | ·                                                                                                                                                                  |      |                     |      |                            |  |

| \ <i>\</i>           | Developed a developed and to be                                                                                                       | $I_{LOAD} = 500 \text{ mA}$                                                                                                                                        | 4.96 | 5                   | 5.04 |                            |  |

| V <sub>OUT-REG</sub> | Regulated output voltage                                                                                                              | I <sub>LOAD</sub> = 10 mA                                                                                                                                          | 4.97 | 5.01                | 5.05 | V                          |  |

| K <sub>ILIM</sub>    | Current programming factor for hardware protection                                                                                    | $\label{eq:klim} \begin{array}{c} R_{LIM} = K_{ILIM} \ / \ I_{ILIM}, \ where \ I_{ILIM} \ is \\ the hardware \ current \ limit. \\ I_{OUT} = 500 \ mA \end{array}$ | 303  | 314                 | 321  | AΩ                         |  |

| K <sub>IMAX</sub>    | Current programming factor for the nominal operating current                                                                          | $      I_{IMAX} = K_{IMAX} / R_{LIM} \text{ where } I_{MAX} $ is the maximum normal operating current.<br>I_{OUT} = 500 mA                                         |      | 262                 |      | AΩ                         |  |

| I <sub>OUT</sub>     | Current limit programming range                                                                                                       |                                                                                                                                                                    |      |                     | 750  | mA                         |  |

|                      | Current limit during W/DC communication                                                                                               | I <sub>OUT</sub> > 300 mA                                                                                                                                          | la   | <sub>DUT</sub> + 50 |      | mA                         |  |

| COMM                 | Current limit during WPC communication                                                                                                | I <sub>OUT</sub> < 300 mA                                                                                                                                          | 343  | 378                 | 425  | mA                         |  |

| t <sub>HOLD</sub>    | Holdoff time for the communication current limit during start-up                                                                      |                                                                                                                                                                    |      | 1                   |      | S                          |  |

| TS / CTRL            |                                                                                                                                       |                                                                                                                                                                    |      |                     |      |                            |  |

| V <sub>TS</sub>      | Internal TS bias voltage                                                                                                              | I <sub>TS-Bias</sub> < 100 μA (periodically driven see t <sub>TS-CTRL)</sub>                                                                                       | 2    | 2.2                 | 2.4  | V                          |  |

| M                    | Rising threshold                                                                                                                      | $V_{TS}: 50\% \rightarrow 60\%$                                                                                                                                    | 56.5 | 58.7                | 60.8 |                            |  |

| V <sub>COLD</sub>    | Falling hysteresis                                                                                                                    | $V_{TS}: 60\% \rightarrow 50\%$                                                                                                                                    |      | 2                   |      | 0/1/                       |  |

|                      | Falling threshold                                                                                                                     | $V_{TS}$ : 20% $\rightarrow$ 15%                                                                                                                                   | 18.5 | 19.6                | 20.7 | 20.7 <sup>%V</sup> TS-Bias |  |

| V <sub>HOT</sub>     | Rising hysteresis                                                                                                                     | $V_{TS}$ : 15% $\rightarrow$ 20%                                                                                                                                   |      | 3                   |      |                            |  |

| V <sub>CTRL</sub>    | CTRL pin threshold for a high                                                                                                         | $V_{\text{TS-CTRL}}$ : 50 $\rightarrow$ 150 mV                                                                                                                     | 80   | 100                 | 130  | mV                         |  |

|                      | CTRL pin threshold for a low                                                                                                          | $V_{TS-CTRL}$ : 150 $\rightarrow$ 50 mV                                                                                                                            | 50   | 80                  | 100  |                            |  |

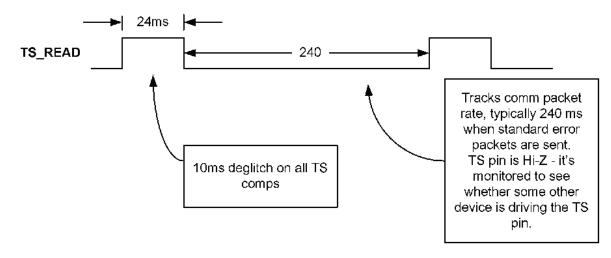

| t <sub>TS-CTRL</sub> | Time V <sub>TS</sub> -Bias is active when TS measurements occur                                                                       | Synchronous to the communication period                                                                                                                            |      | 24                  |      | ms                         |  |

| t <sub>TS</sub>      | Deglitch time for all TS comparators                                                                                                  |                                                                                                                                                                    |      | 10                  |      | ms                         |  |

| R <sub>TS</sub>      | Pullup resistor for the NTC network. Pulled up to the voltage bias.                                                                   |                                                                                                                                                                    | 18   | 20                  | 22   | kΩ                         |  |

| THERMAL F            | ROTECTION                                                                                                                             |                                                                                                                                                                    |      |                     |      |                            |  |

| Ŧ                    | Thermal shutdown temperature                                                                                                          |                                                                                                                                                                    |      | 155                 |      | °C                         |  |

| TJ                   | Thermal shutdown hysteresis                                                                                                           |                                                                                                                                                                    |      | 20                  |      | C                          |  |

| OUTPUT LO            | GIC LEVELS ON CHG                                                                                                                     |                                                                                                                                                                    |      |                     |      |                            |  |

| V <sub>OL</sub>      | Open-drain CHG pin                                                                                                                    | I <sub>SINK</sub> = 5 mA                                                                                                                                           |      |                     | 500  | mV                         |  |

| I <sub>OFF</sub>     | CHG leakage current when disabled                                                                                                     | $V_{\overline{CHG}} = 20 V$                                                                                                                                        |      |                     | 1    | μA                         |  |

| COMM PIN             |                                                                                                                                       |                                                                                                                                                                    |      |                     |      |                            |  |

| R <sub>DS(ON)</sub>  | COMM1 and COMM2                                                                                                                       | V <sub>RECT</sub> = 2.6 V                                                                                                                                          |      | 1.5                 |      | Ω                          |  |

| f <sub>COMM</sub>    | Signaling frequency on COMM pin                                                                                                       |                                                                                                                                                                    |      | 2                   |      | Kbps                       |  |

| I <sub>OFF</sub>     | Comm pin leakage current                                                                                                              | $V_{COMM1} = 20 \text{ V}, V_{COMM2} = 20 \text{ V}$                                                                                                               |      |                     | 1    | μA                         |  |

| CLAMP PIN            |                                                                                                                                       |                                                                                                                                                                    |      |                     |      |                            |  |

| R <sub>DS(ON)</sub>  | CLAMP1 and CLAMP2                                                                                                                     |                                                                                                                                                                    |      | 0.8                 |      | Ω                          |  |

| ADAPTER E            | NABLE                                                                                                                                 |                                                                                                                                                                    |      |                     |      |                            |  |

|                      | $V_{\text{AD}}$ rising threshold voltage. EN-UVLO                                                                                     | $V_{AD} \ 0 \ V \rightarrow 5 \ V$                                                                                                                                 | 3.5  | 3.6                 | 3.8  | V                          |  |

| V <sub>AD-EN</sub>   | V <sub>AD-EN</sub> hysteresis, EN-HYS                                                                                                 | $V_{AD} \: 5 \: V \to 0 \: V$                                                                                                                                      |      | 400                 |      | mV                         |  |

| I <sub>AD</sub>      | Input leakage current                                                                                                                 | $V_{RECT} = 0 V, V_{AD} = 5 V$                                                                                                                                     |      |                     | 60   | μΑ                         |  |

| R <sub>AD</sub>      | Pullup resistance from $\overline{\text{AD-EN}}$ to OUT when adapter mode is disabled and V <sub>OUT</sub> > V <sub>AD</sub> , EN-OUT | V <sub>AD</sub> = 0 V, V <sub>OUT</sub> = 5 V                                                                                                                      |      | 200                 | 350  | Ω                          |  |

| V <sub>AD</sub>      | Voltage difference between $V_{AD}$ and $V_{\overline{AD-EN}}$ when adapter mode is enabled, EN-ON                                    | $V_{AD} = 5 \text{ V}, 0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}$                                                                           | 3    | 4.5                 | 5    | V                          |  |

# **Electrical Characteristics (continued)**

over operating free-air temperature range, 0°C to 125°C (unless otherwise noted)

|                                                                                           | PARAMETER                                                                                 | TEST CONDITIONS                          | MIN   | TYP | MAX  | UNIT |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------|-------|-----|------|------|

| SYNCHRONO                                                                                 | US RECTIFIER                                                                              |                                          |       |     |      |      |

| 1                                                                                         | I <sub>OUT</sub> at which the synchronous rectifier enters half synchronous mode, SYNC_EN | $I_{LOAD}$ : 200 mA $\rightarrow$ 0 mA   | 80    | 100 | 130  | mA   |

| IOUT                                                                                      | Hysteresis for I <sub>OUT,RECT-EN</sub> (full-synchronous mode enabled)                   | $I_{LOAD}$ : 0 mA $\rightarrow$ 200 mA   |       | 25  |      | mA   |

| V <sub>HS-DIODE</sub> High-side diode drop when the rectifier is in half synchronous mode |                                                                                           | $I_{AC-VRECT}$ = 250 mA and $T_J$ = 25°C |       | 0.7 |      | V    |

| EN1 AND EN                                                                                | 2                                                                                         |                                          |       |     |      |      |

| V <sub>IL</sub>                                                                           | Input low threshold for EN1 and EN2                                                       |                                          |       |     | 0.4  | V    |

| VIH                                                                                       | Input high threshold for EN1 and EN2                                                      |                                          | 1.3   |     |      | V    |

| R <sub>PD</sub>                                                                           | EN1 and EN2 pull down resistance                                                          |                                          |       | 200 |      | kΩ   |

| ADC (WPC R                                                                                | elated Measurements and Coefficients)                                                     |                                          |       |     |      |      |

| IOUT SENSE                                                                                | Accuracy of the current sense over the load range                                         | I <sub>OUT</sub> = 300 mA - 500 mA       | -1.5% | 0%  | 0.9% |      |

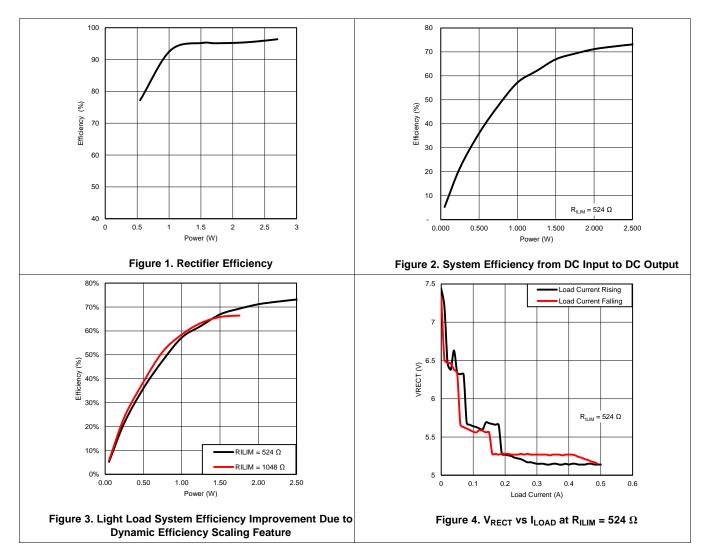

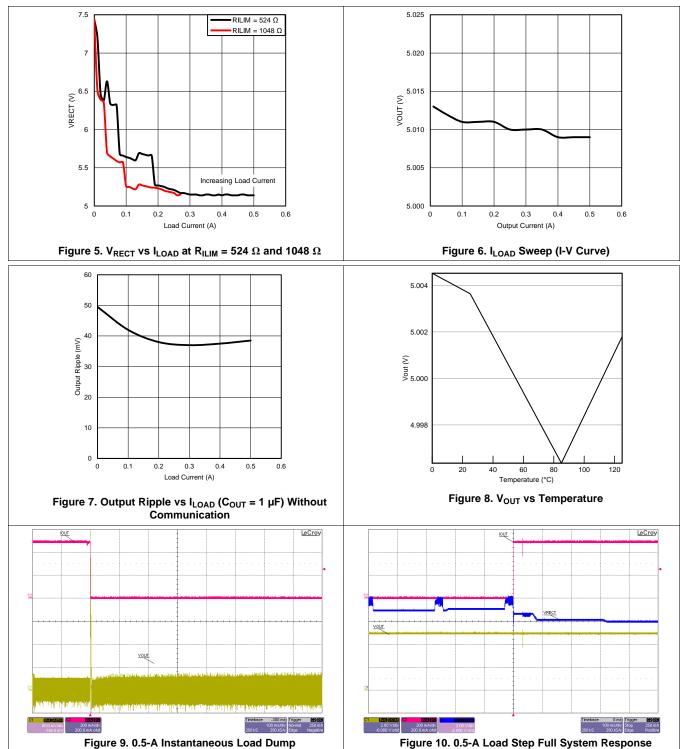

# 7.6 Typical Characteristics

# **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

# 8 Detailed Description

# 8.1 Overview

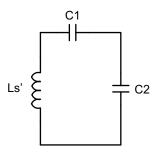

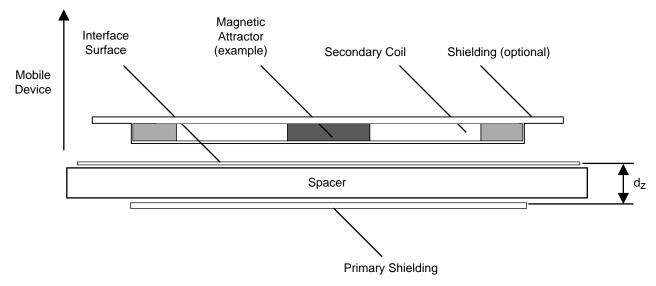

The principle of wireless power transfer is simply an open-cored transformer consisting of transmitter and receiver coils. The transmitter coil and electronics are typically built into a charger pad, and the receiver coil and electronics are typically built into a portable device such as a cell phone. When the receiver coil is positioned on the transmitter coil, magnetic coupling occurs when the transmitter coil is driven. The flux is coupled into the secondary coil, which induces a voltage and current flows. The secondary voltage is rectified, and power can be transferred effectively to a load wirelessly. Power transfer can be managed through any of the various closed-loop control schemes.

#### 8.1.1 A Brief Description of the Wireless System

A wireless system consists of a charging pad (transmitter or primary) and the secondary-side equipment (receiver or secondary). There is a coil in the charging pad and in the secondary equipment which are magnetically coupled to each other when the secondary is placed on the primary. Power is then transferred from the transmitter to the receiver through coupled inductors (for example, an air-core transformer). Controlling the amount of power transferred is achieved by sending feedback (error signal) communication to the primary (that is, to increase or decrease power).

The receiver communicates with the transmitter by changing the load seen by the transmitter. This load variation results in a change in the transmitter coil current, which is measured and interpreted by a processor in the charging pad. Communication is done through digital-packets which are transferred from the receiver to the transmitter. Differential Biphase encoding is used for the packets. The bit rate is 2-kbps.

Various types of communication packets have been defined. These include identification and authentication packets, error packets, control packets, end power packets, and power usage packets.

The transmitter coil stays powered off most of the time. It occasionally wakes up to see if a receiver is present. When a receiver authenticates itself to the transmitter, the transmiter will remain powered on. The receiver maintains full control over the power transfer using communication packets.

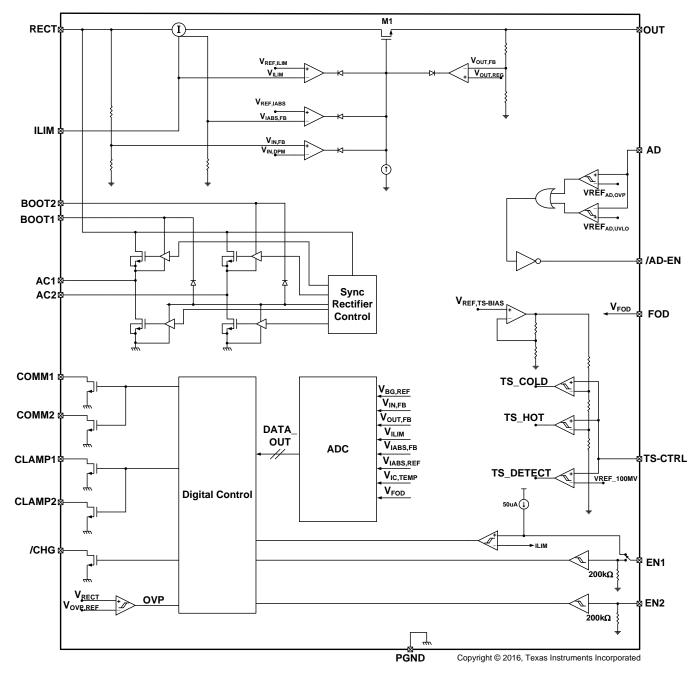

#### 8.2 Functional Block Diagram

# 8.3 Feature Description

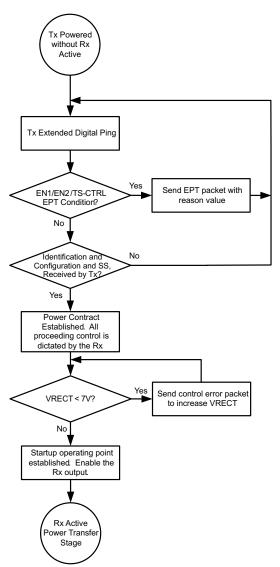

#### 8.3.1 Details of a Qi Wireless Power System and bq51003 Power Transfer Flow Diagrams

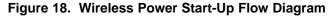

The bq51003 integrates a fully compliant WPC v1.2 communication algorithm to streamline receiver designs (no extra software development required). Other unique algorithms such as Dynamic Rectifier Control are also integrated to provide best-in-class system performance. This section provides a high-level overview of these features by illustrating the wireless power transfer flow diagram from start-up to active operation.

#### Feature Description (continued)

During start-up operation, the wireless power receiver must comply with proper handshaking to be granted a power contract from the Tx. The Tx initiates the hand shake by providing an extended digital ping. If an Rx is present on the Tx surface, the Rx then provides the signal strength, configuration, and identification packets to the Tx (see volume 1 of the WPC specification for details on each packet). These are the first three packets sent to the Tx. The only exception is if there is a true shutdown condition on the EN1/EN2, AD, or TS-CTRL pins where the Rx will shut down the Tx immediately. See Table 5 for details. Once the Tx has successfully received the signal strength, configuration, and identification packets, the Rx will be granted a power contract and is then allowed to control the operating point of the power transfer. With the use of the bq51003 Dynamic Rectifier Control algorithm, the Rx will inform the Tx to adjust the rectifier voltage above 7 V prior to enabling the output supply. This method enhances the transient performance during system start-up. See Figure 18 for the start-up flow diagram details.

#### Feature Description (continued)

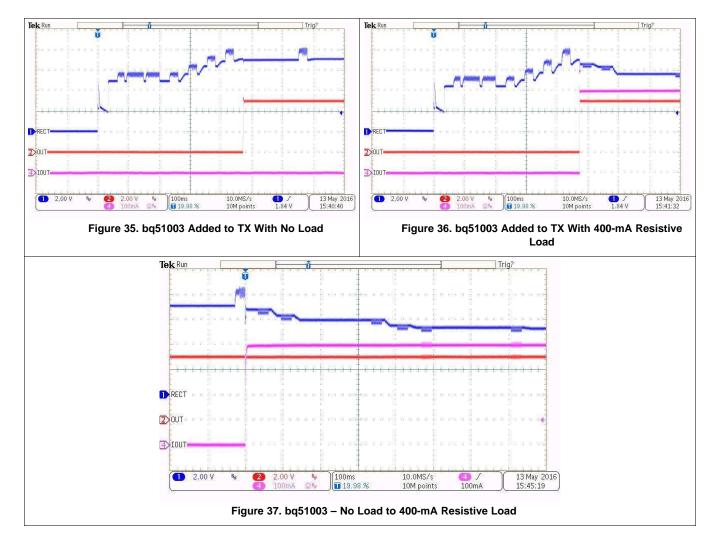

Once the start-up procedure has been established, the Rx will enter the active power transfer stage. This is considered the *main loop* of operation. The Dynamic Rectifier Control algorithm will determine the rectifier voltage target based on a percentage of the maximum output current level setting (set by  $K_{IMAX}$  and the ILIM resistance to GND). The Rx will send control error packets to converge on these targets. As the output current changes, the rectifier voltage target will dynamically change. As a note, the feedback loop of the WPC system is relatively slow where it can take up to 90 ms to converge on a new rectifier voltage target. It should be understood that the instantaneous transient response of the system is open loop and dependent on the Rx coil output impedance at that operating point. The *main loop* will also determine if any conditions in Table 5 are true to discontinue power transfer. See Figure 19 which illustrates the active power transfer loop.

Figure 19. Active Power Transfer Flow Diagram

Another requirement of the WPC v1.2 specification is to send the measured received power. This task is enabled on the IC by measuring the voltage on the FOD pin which is proportional to the output current and can be scaled based on the choice of the resitor to ground on the FOD pin.

## Feature Description (continued)

#### 8.3.2 Dynamic Rectifier Control

The Dynamic Rectifier Control algorithm offers the end system designer optimal transient response for a given max output current setting. This is achieved by providing enough voltage headroom across the internal regulator at light loads to maintain regulation during a load transient. The WPC system has a relatively slow global feedback loop where it can take more than 90 ms to converge on a new rectifier voltage target. Therefore, the transient response is dependent on the loosely coupled transformers output impedance profile. The Dynamic Rectifier Control allows for a 2-V change in rectified voltage before the transient response will be observed at the output of the internal regulator (output of the bq51003).

#### 8.3.3 Dynamic Efficiency Scaling

The Dynamic Efficiency Scaling feature allows for the loss characteristics of the bq51003 to be scaled based on the maximum expected output power in the end application. This effectively optimizes the efficiency for each application. This feature is achieved by scaling the loss of the internal LDO based on a percentage of the maximum output current. Note that the maximum output current is set by the  $K_{IMAX}$  term and the  $R_{ILIM}$  resistance (where  $R_{ILIM} = K_{IMAX} / I_{MAX}$ ). The flow diagram show in Figure 19 illustrates how the rectifier is dynamically controlled (*Dynamic Rectifier Control*) based on a fixed percentage of the I<sub>MAX</sub> setting. Table 2 summarizes how the rectifier behavior is dynamically adjusted based on two different  $R_{ILIM}$  settings.

| , , , ,                      |                                                         |                                                        |                   |  |  |  |

|------------------------------|---------------------------------------------------------|--------------------------------------------------------|-------------------|--|--|--|

| OUTPUT CURRENT<br>PERCENTAGE | R <sub>ILIM</sub> = 1116 Ω<br>I <sub>MAX</sub> = 250 mA | R <sub>ILIM</sub> = 488 Ω<br>I <sub>MAX</sub> = 500 mA | V <sub>RECT</sub> |  |  |  |

| 0 to 10%                     | 0 A to 0.025 A                                          | 0 A to 0.05 A                                          | 7.08 V            |  |  |  |

| 10 to 20%                    | 0.025 A to 0.050 A                                      | 0.050 A to 0.100 A                                     | 6.28 V            |  |  |  |

| 20 to 40%                    | 0.050 A to 0.100 A                                      | 0.100 A to 0.200 A                                     | 5.53 V            |  |  |  |

| >40%                         | > 0.100 A                                               | > 0.200 A                                              | 5.11 V            |  |  |  |

| Table 2. Dynamic Efficiency | / Scaling |

|-----------------------------|-----------|

|-----------------------------|-----------|

Figure 5 illustrates the shift in the *Dynamic Rectifier Control* behavior based on the two different  $R_{ILIM}$  settings. With the rectifier voltage ( $V_{RECT}$ ) being the input to the internal LDO, this adjustment in the *Dynamic Rectifier Control* thresholds will dynamically adjust the power dissipation across the LDO where:

$$P_{DIS} = (V_{RECT} - V_{OUT}) \times I_{OUT}$$

(1)

(2)

Figure 3 illustrates how the system efficiency is improved due to the *Dynamic Efficiency Scaling* feature. Note that this feature balances efficiency with optimal system transient response.

#### 8.3.4 R<sub>ILIM</sub> Calculations

The bq51003 includes a means of providing hardware overcurrent protection by means of an analog current regulation loop. The hardware current limit provides an extra level of safety by clamping the maximum allowable output current (that is, a current compliance). The  $R_{ILIM}$  resistor size also sets the thresholds for the dynamic rectifier levels and thus providing efficiency tuning per each application's maximum system current. The calculation for the total  $R_{ILIM}$  resistance is as follows:

$$R_{ILIM} = \frac{262}{I_{MAX}}$$

$$I_{ILIM} = 1.2 \times I_{MAX} = \frac{314}{R_{ILIM}}$$

$$R_{ILIM} = R_1 + R_{FOD}$$

where

- I<sub>MAX</sub> is the expected maximum output current during normal operation

- I<sub>ILIM</sub> is the hardware over current limit

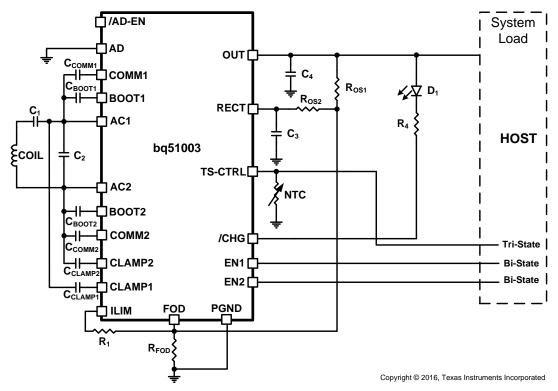

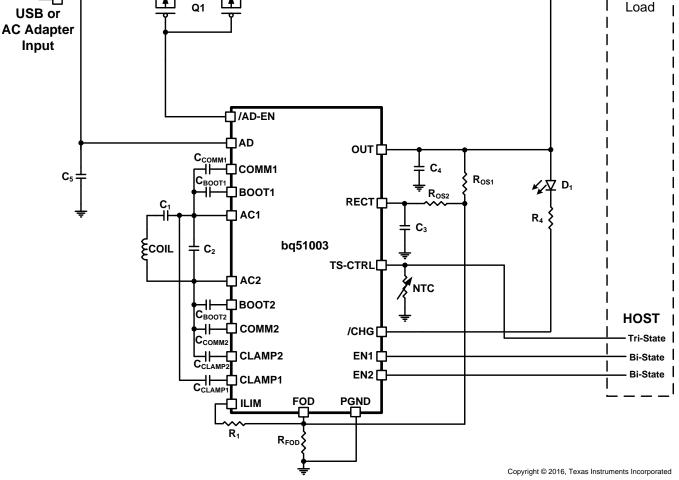

When referring to the application diagram shown in Figure 32,  $R_{ILIM}$  is the sum of  $R_{FOD}$  and the  $R_1$  resistance (that is, the total resistance from the ILIM pin to GND).

#### 8.3.5 Input Overvoltage

If the input voltage suddenly increases in potential (that is, due to a change in position of the equipment on the charging pad), the voltage-control loop inside the bq51003 becomes active, and prevents the output from going beyond  $V_{OUT-REG}$ . The receiver then starts sending back error packets to the transmitter every 30 ms until the input voltage comes back to the  $V_{RECT-REG}$  target, and then maintains the error communication every 250 ms.

If the input voltage increases in potential beyond  $V_{RECT-OVP}$ , the IC switches off the LDO and communicates to the primary to bring the voltage back to  $V_{RECT-REG}$ . In addition, a proprietary voltage protection circuit is activated by means of  $C_{CLAMP1}$  and  $C_{CLAMP2}$  that protects the IC from voltages beyond the maximum rating of the IC (that is, 20 V).

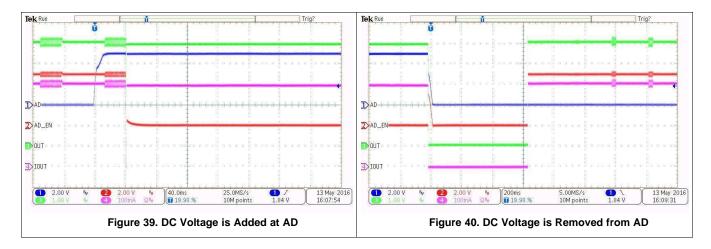

### 8.3.6 Adapter Enable Functionality and EN1/EN2 Control

Figure 38 is an example application that shows the bq51003 used as a wireless power receiver that can power multiplex between wired or wireless power for the down-system electronics. In the default operating mode pins EN1 and EN2 are low, which activates the adapter enable functionality. In this mode, if an adapter is not present the AD pin will be low, and AD-EN pin will be pulled to the higher of the OUT and AD pins so that the PMOS between OUT and AD will be turned off. If an adapter is plugged in and the voltage at the AD pin goes above 3.6 V then wireless charging is disabled and the AD-EN pin will be pulled approximately 4 V below the AD pin to connect AD to the secondary charger. The difference between AD and AD-EN is regulated to a maximum of 7 V to ensure the V<sub>GS</sub> of the external PMOS is protected.

The EN1 and EN2 pins include internal 200-k $\Omega$  pulldown resistors, so that if these pins are not connected bq51003 defaults to AD-EN control mode. However, these pins can be pulled high to enable other operating modes as described in Table 3:

| EN1 | EN2 | RESULT                                                                                                                                                                                                        |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Adapter control enabled. If adapter is present then secondary charger is powered by adapter, otherwise wireless charging is enabled when wireless power is available. Communication current limit is enabled. |

| 0   | 1   | Disables communication current limit.                                                                                                                                                                         |

| 1   | 0   | AD-EN is pulled low, whether or not adapter voltage is present. This feature can be used, for example, for USB OTG applications.                                                                              |

| 1   | 1   | Adapter and wireless charging are disabled, that is, power will never be delivered by the OUT pin in this mode.                                                                                               |

#### Table 3. Adapter Enable Functionality

#### Table 4. EN1/EN2 Control

| EN1 | EN2 | WIRELESS POWER          | WIRED POWER             | OTG MODE               | ADAPTIVE<br>COMMUNICATION LIMIT | EPT                          |

|-----|-----|-------------------------|-------------------------|------------------------|---------------------------------|------------------------------|

| 0   | 0   | Enabled                 | Priority <sup>(1)</sup> | Disabled               | Enabled                         | Not Sent to Tx               |

| 0   | 1   | Priority <sup>(1)</sup> | Enabled                 | Disabled               | Disabled                        | Not Sent to Tx               |

| 1   | 0   | Disabled                | Enabled                 | Enabled <sup>(2)</sup> | N/A                             | EPT 0x00, Unknown            |

| 1   | 1   | Disabled                | Disabled                | Disabled               | N/A                             | EPT 0x01, Charge<br>Complete |

(1) If both wired and wireless power are present, wired power is given priority.

(2) Allows for a boost-back supply to be driven from the output terminal of the Rx to the adapter port through the external back-to-back PMOS FET.

As described in Table 4, pulling EN2 high disables the adapter mode and only allows wireless charging. In this mode the adapter voltage will always be blocked from the OUT pin. An application example where this mode is useful is when USB power is present at AD, but the USB is in suspend mode so that no power can be taken from the USB supply. Pulling EN1 high enables the off-chip PMOS regardless of the presence of a voltage. This function can be used in USB OTG mode to allow a charger connected to the OUT pin to power the AD pin. Finally, pulling both EN1 and EN2 high disables both wired and wireless charging.

# NOTE

It is required to connect a back-to-back PMOS between AD and OUT so that voltage is blocked in both directions. Also, when AD mode is enabled no load can be pulled from the RECT pin as this could cause an internal device overvoltage in bq51003.

## 8.3.7 End Power Transfer Packet (WPC Header 0x02)

The WPC allows for a special command for the receiver to terminate power transfer from the transmitter termed End Power Transfer (EPT) packet. Table 5 specifies the v1.2 reasons column and their corresponding data field value. The condition column corresponds to the methodology used by bq51003 to send equivalent message.

| MESSAGE VALUE       |      | CONDITION                                              |  |  |  |

|---------------------|------|--------------------------------------------------------|--|--|--|

| Unknown             | 0x00 | TS-CTRL = 1, or ,EN1 EN2> = <10> or AD > $V_{AD_{EN}}$ |  |  |  |

| Charge Complete     | 0x01 | <en1 en2=""> = &lt;11&gt;</en1>                        |  |  |  |

| Internal Fault 0x02 |      | $T_{\rm J}$ > 150°C or $R_{\rm ILIM}$ < 100 $\Omega$   |  |  |  |

| Over Temperature    | 0x03 | TS < $V_{HOT}$ , TS > $V_{COLD}$ , or TS-CTRL < 100 mV |  |  |  |

| Over Voltage        | 0x04 | Not Sent                                               |  |  |  |

| Over Current        | 0x05 | NOT USED                                               |  |  |  |

| Battery Failure     | 0x06 | Not Sent                                               |  |  |  |

| Reconfigure         | 0x07 | Not Sent                                               |  |  |  |

| No Response 0x08    |      | V <sub>RECT</sub> target does not converge             |  |  |  |

| Table 4 | 5 End   | Power | Transfer  | Packet |

|---------|---------|-------|-----------|--------|

|         | ). LIIU | FOWEI | ITALISICI | Γαυκει |

#### 8.3.8 Status Outputs

The bq51003 has one status output,  $\overline{CHG}$ . This output is an open-drain NMOS device that is rated to 20 V. The open-drain FET connected to the  $\overline{CHG}$  pin will be turned on whenever the output of the power supply is enabled. Note that the output of the power supply will not be enabled if the V<sub>RECT-REG</sub> does not converge at the no-load target voltage.

#### 8.3.9 WPC Communication Scheme

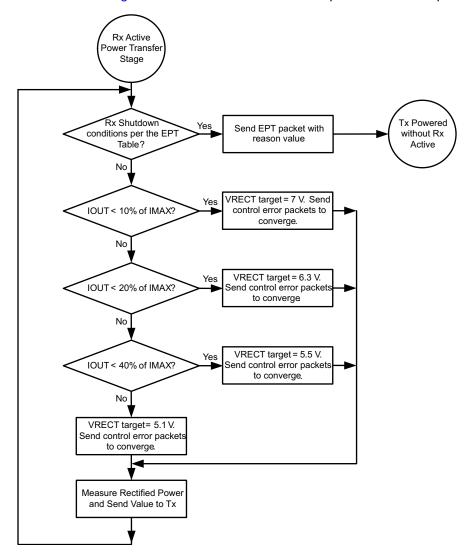

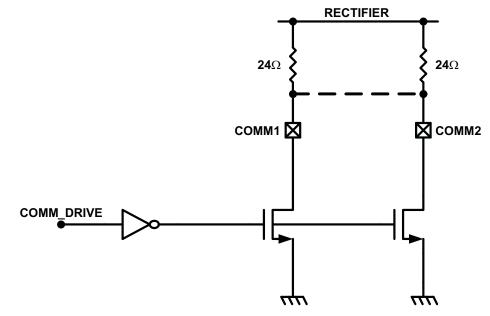

The WPC communication uses a modulation technique termed *backscatter modulation* where the receiver coil is dynamically loaded to provide amplitude modulation of the transmitter's coil voltage and current. This scheme is possible due to the fundamental behavior between two loosely coupled inductors (that is, between the Tx and Rx coil). This type of modulation can be accomplished by switching in and out a resistor at the output of the rectifier, or by switching in and out a capacitor across the AC1/AC2 net. Figure 20 shows how to implement resistive modulation.

Figure 20. Resistive Modulation

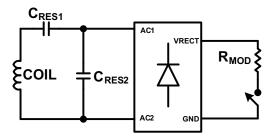

Figure 21 shows how to implement capacitive modulation.

Figure 21. Capacitive Modulation

TEXAS INSTRUMENTS

www.ti.com

The amplitude change in Tx coil voltage or current can be detected by the transmitters decoder. Figure 22 shows the resulting signal observed by the Tx.

Figure 22. TX Coil Voltage and Current

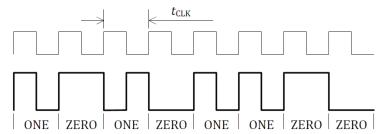

The WPC protocol uses a differential biphase encoding scheme to modulate the data bits onto the Tx coil voltage and current. Each data bit is aligned at a full period of 0.5 ms ( $t_{CLK}$ ) or 2 kHz. An encoded ONE results in two transitions during the bit period and an encoded ZERO results in a single transition. See Figure 23 for an example of the differential biphase encoding.

Figure 23. Differential Biphase Encoding Scheme (WPC Volume 1: Low Power, Part 1 Interface Definition)

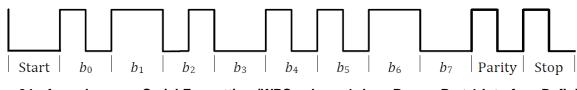

The bits are sent LSB first and use an 11-bit asynchronous serial format for each portion of the packet. This includes one start bit, n-data bytes, a parity bit, and a single stop bit. The start bit is always ZERO and the parity bit is odd. The stop bit is always ONE. Figure 24 shows the details of the asynchronous serial format.

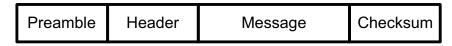

Each packet format is organized as shown in Figure 25.

Figure 25. Packet Format (WPC Volume 1: Low Power, Part 1 Interface Definition)

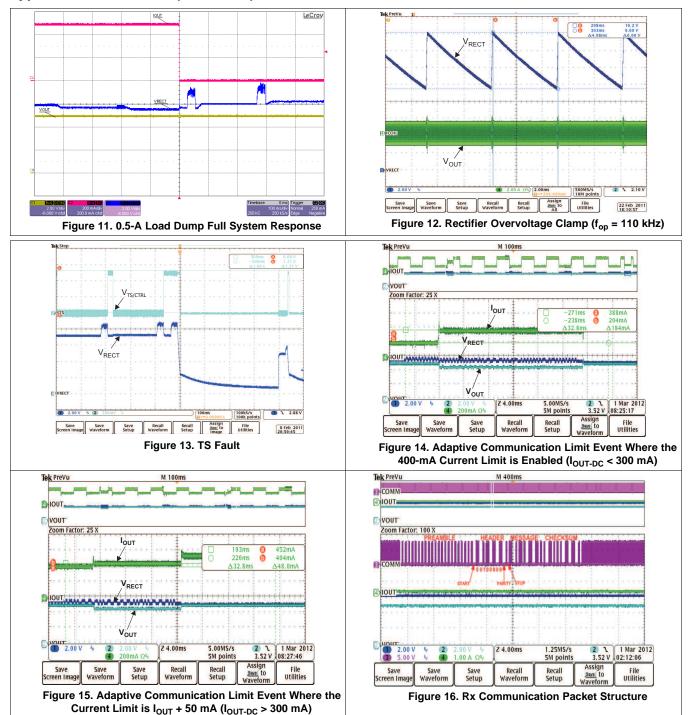

Figure 16 shows an example waveform of the receiver sending a rectified power packet (header 0x04).

#### 8.3.10 Communication Modulator

The bq51003 provides two identical, integrated communication FETs which are connected to the pins COMM1 and COMM2. These FETs are used for modulating the secondary load current which allows bq51003 to communicate error control and configuration information to the transmitter. Figure 26 shows how the COMM pins can be used for resistive load modulation. Each COMM pin can handle at most a 24- $\Omega$  communication resistor. Therefore, if a COMM resistor between 12  $\Omega$  and 24  $\Omega$  is required COMM1 and COMM2 pins must be connected in parallel. The bq51003 does not support a COMM resistor less than 12  $\Omega$ .

Figure 26. Resistive Load Modulation

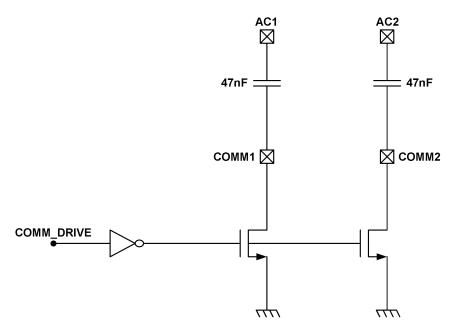

In addition to resistive load modulation, the bq51003 is also capable of capacitive load modulation as shown in Figure 27. In this case, a capacitor is connected from COMM1 to AC1 and from COMM2 to AC2. When the COMM switches are closed there is effectively a 22-nF capacitor connected between AC1 and AC2. Connecting a capacitor in between AC1 and AC2 modulates the impedance seen by the coil, which will be reflected in the primary as a change in current.

Figure 27. Capacitive Load Modulation

# 8.3.11 Adaptive Communication Limit

The Qi communication channel is established through backscatter modulation as described in the previous sections. This type of modulation takes advantage of the loosely coupled inductor relationship between the Rx and Tx coil. Essentially the switching in-and-out of the communication capacitor or resistor adds a transient load to the Rx coil to modulate the Tx coil voltage and current waveform (amplitude modulation). The consequence of this technique is that a load transient (load current noise) from the mobile device has the same signature. To provide noise immunity to the communication channel, the output load transients must be isolated from the Rx coil. The proprietary feature *Adaptive Communication Limit* achieves this by dynamically adjusting the current limit of the regulator. When the regulator is put in current limit, any load transients will be offloaded to the battery in the system.

Note that this requires the battery charger IC to have input voltage regulation (weak adapter mode). The output of the Rx appears as a weak supply if a transient occurs above the current limit of the regulator.

The Adaptive Communication Limit feature has two current limit modes and is detailed in Table 6:

| Ι <sub>Ουτ</sub> | COMMUNICATION CURRENT LIMIT |

|------------------|-----------------------------|

| < 300 mA         | Fixed 400 mA                |

| > 300 mA         | I <sub>OUT</sub> + 50 mA    |

#### **Table 6. Adaptive Communication Limit**

# 8.3.12 Synchronous Rectification

The bq51003 provides an integrated, self-driven synchronous rectifier that enables high-efficiency AC to DC power conversion. The rectifier consists of an all NMOS H-Bridge driver where the backgates of the diodes are configured to be the rectifier when the synchronous rectifier is disabled. During the initial start-up of the WPC system the synchronous rectifier is not enabled. At this operating point, the DC rectifier voltage is provided by the diode rectifier. Once  $V_{RECT}$  is greater than UVLO, half-synchronous mode will be enabled until the load current surpasses 120 mA. Above 120 mA the full synchronous rectifier stays enabled until the load current drops back below 100 mA where half-synchronous mode is enabled instead.

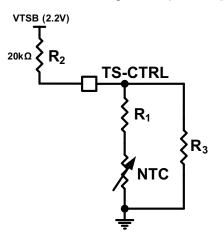

#### 8.3.13 Temperature Sense Resistor Network (TS)

bq51003 includes a ratiometric external temperature sense function. The temperature sense function has two ratiometric thresholds which represent a hot and cold condition. TI recommends an external temperature sensor to provide safe operating conditions for the receiver product. This pin is best used for monitoring the surface that can be exposed to the end user (that is, place the NTC resistor closest to the user).

Figure 28 allows for any NTC resistor to be used with the given  $V_{HOT}$  and  $V_{COLD}$  thresholds.

The resistors  $R_1$  and  $R_3$  can be solved by resolving the system of equations at the desired temperature thresholds (see Equation 3 and Equation 4).

$$%V_{\text{COLD}} = \frac{\left(\frac{R_{3}(R_{\text{NTC}}|_{\text{TCOLD}} + R_{1})}{R_{3} + (R_{\text{NTC}}|_{\text{TCOLD}} + R_{1})}\right)}{\left(\frac{R_{3}(R_{\text{NTC}}|_{\text{TCOLD}} + R_{1})}{R_{3} + (R_{\text{NTC}}|_{\text{TCOLD}} + R_{1})}\right) + R2} \times 100$$

%V\_{HOT} =  $\frac{\left(\frac{R_{3}(R_{\text{NTC}}|_{\text{TCOLD}} + R_{1})}{R_{3} + (R_{\text{NTC}}|_{\text{THOT}} + R_{1})}\right)}{\left(\frac{R_{3}(R_{\text{NTC}}|_{\text{THOT}} + R_{1})}{R_{3} + (R_{\text{NTC}}|_{\text{THOT}} + R_{1})}\right) + R2} \times 100$

R\_{\text{NTC}}|\_{\text{TCOLD}} = R\_{0}e^{\beta\left(\frac{1}{T}\text{TCOLD}^{-1}\text{T}\_{0}\right)}}{R\_{\text{NTC}}|\_{\text{THOT}} = R\_{0}e^{\beta\left(\frac{1}{T}\text{THOT}} - \frac{1}{T}\_{0}\right)}

where

- T<sub>COLD</sub> and T<sub>HOT</sub> are the desired temperature thresholds in degrees Kelvin

- R<sub>o</sub> is the nominal resistance

- and  $\beta$  is the temperature coefficient of the NTC resistor

- R<sub>0</sub> is fixed at 20 kΩ

An example solution is provided:

- R1 = 4.23 kΩ

- R3 = 66.8 kΩ

where the chosen parameters are:

• %V<sub>HOT</sub> = 19.6%

(3)

(4)

**bq51003** JAJSEG4C – DECEMBER 2013 – REVISED JULY 2018

www.ti.com

- %V<sub>COLD</sub> = 58.7%

- $T_{COLD} = -10^{\circ}C$

- T<sub>HOT</sub> = 100°C

- β = 3380

- R<sub>0</sub> = 10 kΩ

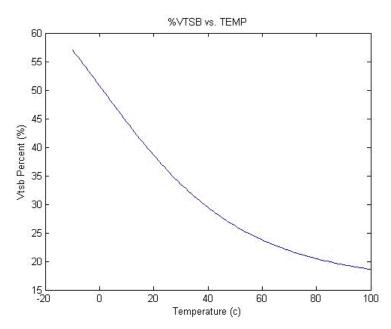

Figure 29 shows the plot of the percent  $V_{TSB}$  vs temperature.

Figure 29. Example Solution for an NTC resistor with  $R_0 = 10 \text{ k}\Omega$  and  $\beta = 4500$

Figure 30 illustrates the periodic biasing scheme used for measuring the TS state. The TS\_READ signal enables the TS bias voltage for 24 ms. During this period the TS comparators are read (each comparator has a 10-ms deglitch) and appropriate action is taken based on the temperature measurement. After this 24-ms period has elapsed, the TS\_READ signal goes low, which causes the TS-Bias pin to become high impedance. During the next 35 ms (priority packet period) or 235 ms (standard packet period), the TS voltage is monitored and compared to 100 mV. If the TS voltage is greater than 100 mV then a secondary device is driving the TS-CTRL pin and a CTRL = '1' is detected.