BQ28Z610-R1

JAJSII1B - JANUARY 2020 - REVISED JANUARY 2022

# BQ28Z610-R1 Impedance Track™ バッテリ残量計および保護ソリューション、 1~2個の直列セルのリチウムイオン・バッテリ・パック用

## 1 特長

**TEXAS**

Instruments

- 専用のマスタ・モード I<sup>2</sup>C インターフェイスを使った自 律的なバッテリ充電制御

- 内部バイパス付きのセル・バランス機能により、バッテリ の状態を最適化

- N-CH FET ドライブのハイサイド保護により、フォルト状 況でもシリアル・バス通信が可能

- 電圧、電流、温度について保護レベルをプログラム可

- 2 つの独立した ADC を持つアナログ・フロント・エンド

- 電流と電圧の同時サンプリングに対応

- 入力オフセット誤差 1µV 未満 (標準値) の高精度 クーロン・カウンタ

- 最低 1mΩ の電流センス抵抗をサポートし、1mA の電 流測定が可能

- Windows® のバッテリ・トリップ・ポイント (BTP) 機能の 統合をサポート

- SHA-1 認証レスポンダによるバッテリ・パックのセキュリ ティ強化

- 400kHz の I<sup>2</sup>C バス通信インターフェイスによる高速な プログラミングとデータ・アクセス

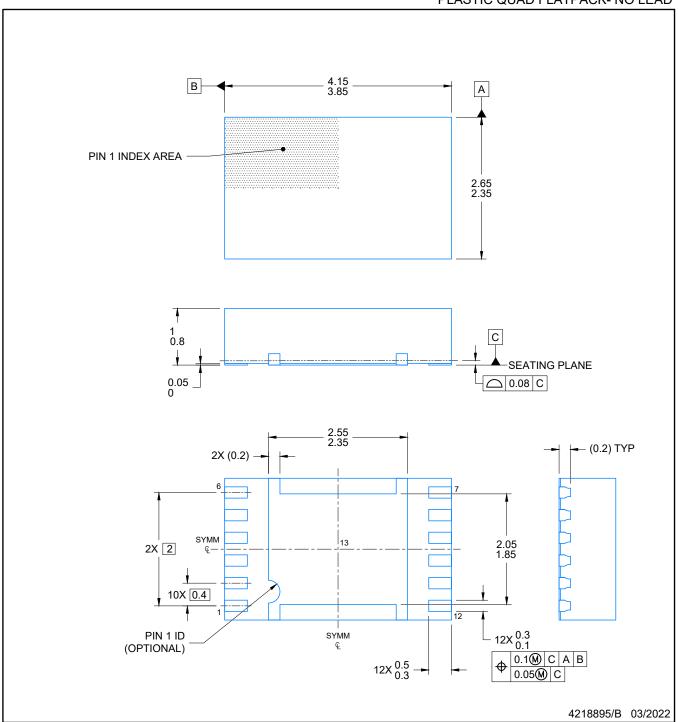

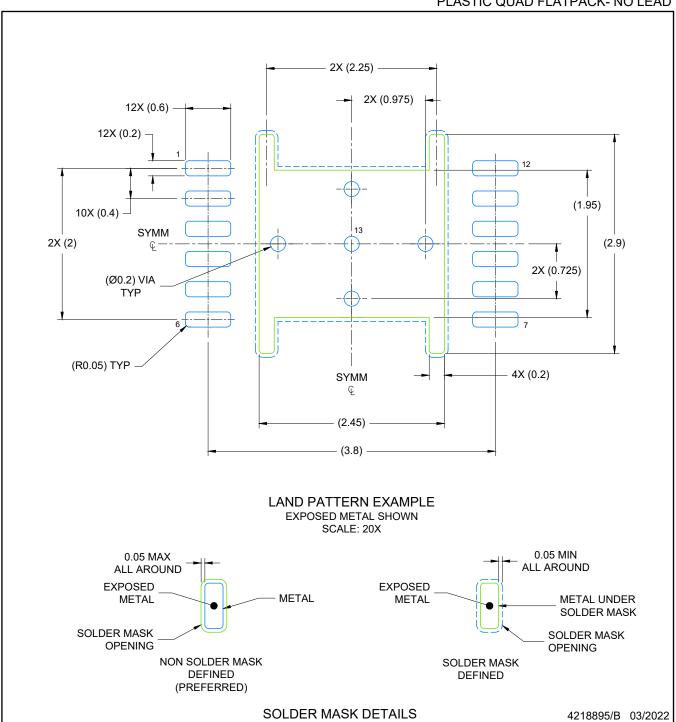

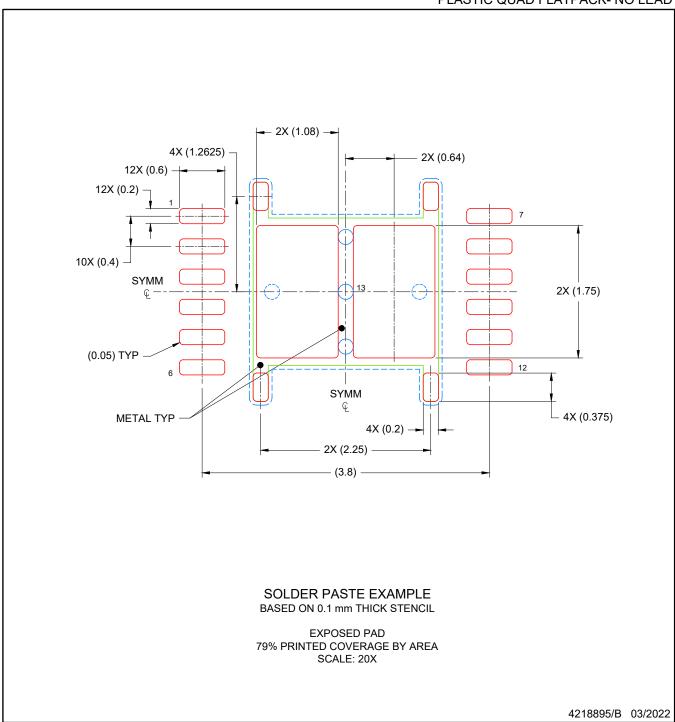

- 小型の 12 ピン VSON パッケージ (DRZ)

# 2 アプリケーション

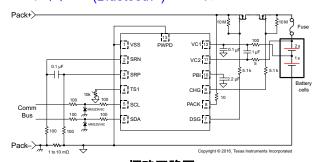

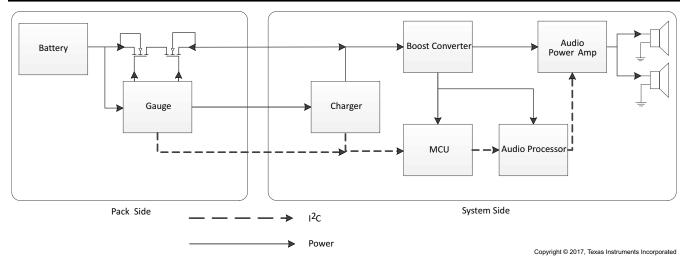

- タブレット・コンピュータ

- 携帯およびウェアラブルの健康機器

- 携帯用オーディオ・デバイス

- ワイヤレス (Bluetooth®) スピーカー

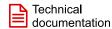

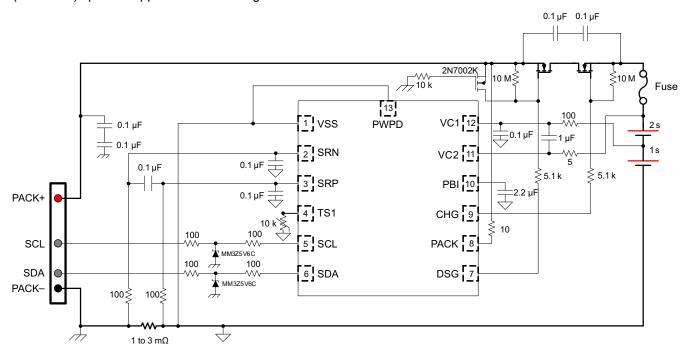

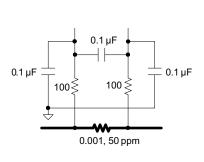

概略回路図

## 3 概要

テキサス・インスツルメンツの BQ28Z610-R1 デバイスは、 高度に統合された高精度の1シリーズ~2シリーズ・セル 用バッテリ残量計および保護ソリューションであり、自律的 な充電制御とセル・バランスを実現します。

BQ28Z610-R1 デバイスは、充電電流および電圧情報の マスタ・モード I2C ブロードキャストによって自律的に充電 を制御できるため、システムのホスト・コントローラに通常生 じるソフトウェアのオーバーヘッドを解消できます。

BQ28Z610-R1 は、フラッシュ・プログラマブル・カスタム RISC (Reduced Instruction Set CPU)、安全保護機能、 1~2 シリーズ・セル・リチウムイオンおよびリチウムポリマ ー・バッテリ・パック認証機能を備えた完全統合型パック・ ベース・ソリューションです。

BQ28Z610-R1 バッテリ残量計は I<sup>2</sup>C 互換のインターフェ イスで通信を行い、超低消費電力かつ高速の TI BQBMP プロセッサ、高精度のアナログ測定機能、内蔵のフラッシ ュ・メモリ、ペリフェラルおよび通信ポートのアレイ、N-CH FETドライブ、SHA-1認証変換レスポンダを組み合わせ た、完全な高性能バッテリ管理ソリューションです。

### 製品情報

|             | WENN IN TA |             |

|-------------|------------|-------------|

| 部品番号(1)     | パッケージ      | 本体サイズ (公称)  |

| BQ28Z610-R1 | VSON (12)  | 4mm × 2.5mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

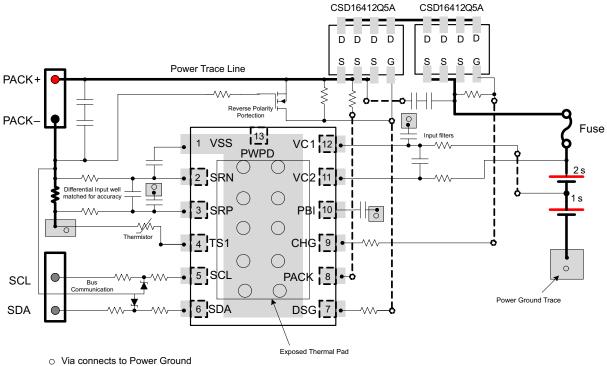

ワイヤレス (Bluetooth®) スピーカー・アプリケーショ ンの ブロック図

# **Table of Contents**

| 特長                                                               | 1  | 7.23 Current Protection Thresholds                   | 10             |

|------------------------------------------------------------------|----|------------------------------------------------------|----------------|

| ! アプリケーション                                                       |    | 7.24 Current Protection Timing                       |                |

| 3 概要                                                             |    | 7.25 N-CH FET Drive (CHG, DSG)                       |                |

| Revision History                                                 |    | 7.26 I <sup>2</sup> C Interface I/O                  |                |

| 5 概要 (続き)                                                        |    | 7.27 I <sup>2</sup> C Interface Timing               |                |

| の                                                                |    | 7.28 Typical Characteristics                         |                |

|                                                                  |    | 8 Detailed Description                               |                |

| 7 Specifications                                                 |    | 8.1 Overview                                         |                |

|                                                                  |    | 8.2 Functional Block Diagram                         |                |

| 7.2 ESD Ratings 7.3 Recommended Operating Conditions             |    | 8.3 Feature Description                              |                |

| 7.4 Thermal Information                                          |    | 8.4 Device Functional Modes                          | 2 <sup>2</sup> |

|                                                                  |    | 9 Applications and Implementation                    |                |

| 7.5 Supply Current                                               |    | 9.1 Application Information                          |                |

| 7.6 Power Supply Control7.7 Low-Voltage General Purpose I/O, TS1 |    | 9.2 Typical Applications                             |                |

|                                                                  |    | 10 Power Supply Recommendations                      |                |

| 7.8 Power-On Reset (POR)<br>7.9 Internal 1.8-V LDO               |    | 11 Layout                                            |                |

|                                                                  |    | 11.1 Layout Guidelines                               |                |

| 7.10 Current Wake Comparator7.11 Coulomb Counter                 |    | 11.2 Layout Example                                  |                |

|                                                                  |    | 12 Device and Documentation Support                  |                |

| 7.12 ADC Multipleyer                                             |    | 12.1 Third-Party Products Disclaimer                 |                |

| 7.13 ADC Multiplexer                                             |    | 12.2 Documentation Support                           |                |

| 7.14 Cell Balancing Support                                      |    | 12.3 Receiving Notification of Documentation Updates |                |

| 7.15 Internal Temperature Sensor                                 |    | 12.4 サポート・リソース                                       |                |

| 7.16 NTC Thermistor Measurement Support                          |    | 12.5 Trademarks                                      |                |

| 7.17 High-Frequency Oscillator                                   |    | 12.6 Electrostatic Discharge Caution                 |                |

| 7.18 Low-Frequency Oscillator                                    |    | 12.7 Glossary                                        |                |

| 7.19 Voltage Reference 1                                         |    | 13 Mechanical, Packaging, and Orderable              |                |

| 7.20 Voltage Reference 2                                         |    | Information                                          | . 29           |

| 7.21 Instruction Flash                                           |    |                                                      |                |

| 7.22 Data Flash                                                  | 10 |                                                      |                |

# **4 Revision History**

| Changes from Revision A (February 2020) to Revision B (January 2022)  | Page |

|-----------------------------------------------------------------------|------|

| Changed Absolute Maximum Ratings                                      | 4    |

|                                                                       |      |

| Changes from Revision * (February 2020) to Revision A (February 2020) | Page |

# 5 概要 (続き)

BQ28Z610-R1 デバイスは、バッテリの放電中の過電流、充電中の短絡、放電保護中の短絡、さらには N チャネル FET の FET 保護、内部 AFE ウォッチドッグ、セル・バランスなど、多くのバッテリ / システム安全機能を備えています。ファームウェアにより、過電圧、低電圧、過熱、その他に対する保護を含めより多くの機能を本デバイスは提供できます。

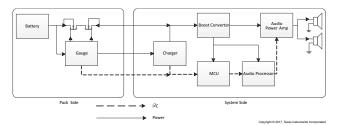

# **6 Pin Configuration and Functions**

図 6-1. DRZ Package 12-Pin VSON Top View

表 6-1. Pin Functions

| PIN NUMBER                                                                                | PIN NAME                                                                                                                                                              | TYPE             | DESCRIPTION                                                                                                                                                           |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                         | VSS                                                                                                                                                                   | P <sup>(1)</sup> | Device ground                                                                                                                                                         |

| 2                                                                                         | SRN                                                                                                                                                                   | Al               | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN where SRP is the top of the sense resistor. |

| 3                                                                                         | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN where SRP is the top of the sense resistor. |                  |                                                                                                                                                                       |

| 4   151   Al                                                                              |                                                                                                                                                                       |                  | Temperature input for ADC to the oversampled ADC channel, and optional Battery Trip Point (BTP) output                                                                |

| 5 SCL I/O Serial Clock for I <sup>2</sup> C interface; requires external pullup when used |                                                                                                                                                                       |                  | Serial Clock for I <sup>2</sup> C interface; requires external pullup when used                                                                                       |

| 6                                                                                         | SDA                                                                                                                                                                   | I/O              | Serial Data for I <sup>2</sup> C interface; requires external pullup                                                                                                  |

| 7                                                                                         | DSG                                                                                                                                                                   | 0                | N-CH FET drive output pin                                                                                                                                             |

| 8                                                                                         | PACK                                                                                                                                                                  | AI, P            | Pack sense input pin                                                                                                                                                  |

| 9                                                                                         | CHG                                                                                                                                                                   | 0                | N-CH FET drive output pin                                                                                                                                             |

| 10                                                                                        | PBI                                                                                                                                                                   | Р                | Power supply backup input pin                                                                                                                                         |

| 11 VC2 AI, P                                                                              |                                                                                                                                                                       | AI, P            | Sense voltage input pin for most positive cell, balance current input for most positive cell. Primary power supply input and battery stack measurement input (BAT)    |

| 12                                                                                        | VC1                                                                                                                                                                   | Al               | Sense voltage input pin for least positive cell, balance current input for least positive cell                                                                        |

|                                                                                           | PWPD                                                                                                                                                                  | _                | Exposed Pad, electrically connected to VSS (external trace)                                                                                                           |

(1) P = Power Connection, O = Digital Output, AI = Analog Input, I = Digital Input, I/O = Digital Input/Output

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)

|                                             |                     | MIN       | MAX                      | UNIT |

|---------------------------------------------|---------------------|-----------|--------------------------|------|

| Supply voltage range, V <sub>CC</sub>       | VC2, PBI            | -0.3      | 30                       | V    |

|                                             | PACK                | -0.3      | 30                       | V    |

|                                             | TS                  | -0.3      | V <sub>REG</sub> + 0.3   | V    |

|                                             | SRP, SRN            | -0.3      | V <sub>REG</sub> + 0.3   | V    |

| Input voltage range, V <sub>IN</sub>        | VC2                 | VC1 – 0.3 | VC1 + 8.5 or<br>VSS + 30 | V    |

|                                             | VC1                 | VSS - 0.3 | VSS + 8.5 or<br>VSS + 30 | V    |

| Communication Interface                     | SDA, SCL            | -0.3      | 6                        | V    |

| Output voltage range, V <sub>O</sub>        | CHG, DSG            | -0.3      | 32                       | V    |

| Maximum VSS current, I <sub>SS</sub>        |                     |           | ±50                      | mA   |

| Functional Temperature, T <sub>FUNC</sub>   |                     | -40       | 110                      | °C   |

| Lead temperature (soldering, 10 s),         | T <sub>SOLDER</sub> |           | ±300                     | °C   |

| Storage temperature range, T <sub>STG</sub> |                     | -65       | 150                      | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 7.2 ESD Ratings

|                    |                                                                                 | VALUE | UNIT |

|--------------------|---------------------------------------------------------------------------------|-------|------|

|                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | v    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PARAMETER               |                             | TEST CONDITION                                               | MIN              | NOM  | MAX                  | UNIT |

|-------------------------|-----------------------------|--------------------------------------------------------------|------------------|------|----------------------|------|

| V <sub>CC</sub>         | Supply voltage              | VC2, PBI                                                     | 2.2              |      | 26                   | V    |

| V <sub>SHUTDOWN</sub> - | Shutdown voltage            | V <sub>PACK</sub> < V <sub>SHUTDOWN</sub> -                  | 1.8              | 2.0  | 2.2                  | V    |

| V <sub>SHUTDOWN+</sub>  | Start-up voltage            | V <sub>PACK</sub> > V <sub>SHUTDOWN</sub> + V <sub>HYS</sub> | 2.05             | 2.25 | 2.45                 | V    |

| V <sub>HYS</sub>        | Shutdown voltage hysteresis | V <sub>SHUTDOWN+</sub> – V <sub>SHUTDOWN</sub>               |                  | 250  |                      | mV   |

|                         |                             | SDA, SCL                                                     |                  |      | 5.5                  |      |

|                         |                             | TS1                                                          |                  |      | $V_{REG}$            | v    |

| \ <u>\</u>              | Input voltage range         | SRP, SRN                                                     | -0.2             |      | 0.2                  |      |

| V <sub>IN</sub>         | input voitage range         | VC2                                                          | V <sub>VC1</sub> |      | V <sub>VC1</sub> + 5 |      |

|                         |                             | VC1                                                          | V <sub>VSS</sub> |      | V <sub>VSS</sub> + 5 |      |

|                         |                             | PACK                                                         |                  |      | 26                   |      |

| Vo                      | Output voltage range        | CHG, DSG                                                     |                  |      | 26                   | V    |

| C <sub>PBI</sub>        | External PBI capacitor      |                                                              | 2.2              |      |                      | μF   |

| T <sub>OPR</sub>        | Operating temperature       |                                                              | -40              |      | 85                   | °C   |

Submit Document Feedback

#### 7.4 Thermal Information

|                          |                                              | BQ28Z610-R1 |        |

|--------------------------|----------------------------------------------|-------------|--------|

|                          | THERMAL METRIC <sup>(1)</sup>                | DRZ         | UNIT   |

|                          |                                              | 12 PINS     |        |

| R <sub>0JA, High K</sub> | Junction-to-ambient thermal resistance       | 186.4       |        |

| R <sub>0</sub> JC(top)   | Junction-to-case(top) thermal resistance     | 90.4        |        |

| $R_{\theta JB}$          | Junction-to-board thermal resistance         | 110.7       | °C/W   |

| ΨЈТ                      | Junction-to-top characterization parameter   | 96.7        | - C/VV |

| ΨЈВ                      | Junction-to-board characterization parameter | 90          |        |

| $R_{\theta JC(bottom)}$  | Junction-to-case(bottom) thermal resistance  | n/a         |        |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics Application Report (SPRA953).

# 7.5 Supply Current

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER               |               | TEST CONDITION                                | MIN | TYP | MAX | UNIT |

|-------------------------|---------------|-----------------------------------------------|-----|-----|-----|------|

| I <sub>NORMAL</sub> (1) | NORMAL mode   | CHG = ON, DSG = ON, No Flash Write            |     | 250 |     | μA   |

| I <sub>SLEEP</sub> (1)  | SLEEP mode    | CHG = OFF, DSG = OFF, No Communication on Bus |     | 100 |     |      |

| I <sub>SHUTDOWN</sub>   | SHUTDOWN mode |                                               |     | 0.5 | 2   | μA   |

<sup>(1)</sup> Dependent on the use of the correct firmware (FW) configuration

# 7.6 Power Supply Control

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PAI                       | RAMETER                        | TEST CONDITION                                                | MIN | TYP  | MAX | UNIT |

|---------------------------|--------------------------------|---------------------------------------------------------------|-----|------|-----|------|

| V <sub>SWITCHOVER</sub> - | VC2 to PACK switchover voltage | V <sub>VC2</sub> < V <sub>SWITCHOVER</sub> -                  | 2.0 | 2.1  | 2.2 | V    |

| V <sub>SWITCHOVER+</sub>  | PACK to VC2 switchover voltage | V <sub>VC2</sub> > V <sub>SWITCHOVER</sub> + V <sub>HYS</sub> | 3.0 | 3.1  | 3.2 | V    |

| V <sub>HYS</sub>          | Switchover voltage hysteresis  | V <sub>SWITCHOVER+</sub> – V <sub>SWITCHOVER</sub>            |     | 1000 |     | mV   |

|                           |                                | VC2 pin, VC2 = 0 V, PACK = 25 V                               |     |      | 1   | μA   |

| luco                      | Input Leakage                  | PACK pin, VC2 = 25 V, PACK = 0 V                              |     |      | 1   |      |

| I <sub>LKG</sub>          | current                        | VC2 and PACK pins, VC2 = 0 V, PACK = 0 V, PBI = 25 V          |     |      | 1   |      |

| R <sub>PACK(PD)</sub>     | Internal pulldown resistance   | PACK                                                          | 30  | 40   | 50  | kΩ   |

# 7.7 Low-Voltage General Purpose I/O, TS1

Typical values stated where  $T_A$  = 25°C and VCC = 7.2 V, Min/Max values stated where  $T_A$  = -40°C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

|                 | PARAMETER           | TEST CONDITION            | MIN                     | TYP | MAX                     | UNIT |

|-----------------|---------------------|---------------------------|-------------------------|-----|-------------------------|------|

| V <sub>IH</sub> | High-level input    |                           | 0.65 x V <sub>REG</sub> |     |                         | V    |

| V <sub>IL</sub> | Low-level input     |                           |                         |     | 0.35 x V <sub>REG</sub> | V    |

| V <sub>OH</sub> | Output voltage high | I <sub>OH</sub> = -1.0 mA | 0.75 x V <sub>REG</sub> |     |                         | V    |

| V <sub>OL</sub> | Output voltage low  | I <sub>OL</sub> = 1.0 mA  |                         |     | 0.2 x V <sub>REG</sub>  | V    |

| C <sub>IN</sub> | Input capacitance   |                           |                         | 5   |                         | pF   |

### 7.7 Low-Voltage General Purpose I/O, TS1 (continued)

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER                             |   | TEST CONDITION | MIN | TYP | MAX | UNIT |

|---------------------------------------|---|----------------|-----|-----|-----|------|

| I <sub>LKG</sub> Input leakag current | ; |                |     |     | 1   | μΑ   |

# 7.8 Power-On Reset (POR)

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

|                    | PARAMETER                    | TEST CONDITION                           | MIN  | TYP  | MAX  | UNIT |

|--------------------|------------------------------|------------------------------------------|------|------|------|------|

| V <sub>REGIT</sub> | Negative-going voltage input | V <sub>REG</sub>                         | 1.51 | 1.55 | 1.59 | V    |

| V <sub>HYS</sub>   | Power-on reset hysteresis    | V <sub>REGIT+</sub> – V <sub>REGIT</sub> | 70   | 100  | 130  | mV   |

| t <sub>RST</sub>   | Power-on reset time          |                                          | 200  | 300  | 400  | μs   |

#### 7.9 Internal 1.8-V LDO

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

|                      | PARAMETER                               | TEST CONDITION                                                                                 | MIN    | TYP    | MAX  | UNIT |

|----------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|--------|--------|------|------|

| V <sub>REG</sub>     | Regulator voltage                       |                                                                                                | 1.6    | 1.8    | 2.0  | V    |

| $\Delta V_{O(TEMP)}$ | Regulator output over temperature       | $\Delta V_{REG}/\Delta T_A$ , $I_{REG}$ = 10 mA                                                |        | ±0.25% |      |      |

| $\Delta V_{O(LINE)}$ | Line regulation                         | $\Delta V_{REG}/\Delta V_{BAT}$ , $V_{BAT}$ = 10 mA                                            | -0 .6% |        | 0.5% |      |

| $\Delta V_{O(LOAD)}$ | Load regulation                         | $\Delta V_{REG}/\Delta I_{REG}$ , $I_{REG}$ = 0 mA to 10 mA                                    | -1.5%  |        | 1.5% |      |

| I <sub>REG</sub>     | Regulator output current limit          | $V_{REG} = 0.9 \text{ x } V_{REG(NOM)}, V_{IN} > 2.2 \text{ V}$                                | 20     |        |      | mA   |

| I <sub>SC</sub>      | Regulator short-circuit current limit   | V <sub>REG</sub> = 0 x V <sub>REG(NOM)</sub>                                                   | 25     | 40     | 50   | mA   |

| PSRR <sub>REG</sub>  | Power supply rejection ratio            | $\Delta V_{BAT}/\Delta V_{REG}$ , I <sub>REG</sub> = 10 mA, V <sub>IN</sub> > 2.5 V, f = 10 Hz |        | 40     |      | dB   |

| V <sub>SLEW</sub>    | Slew rate enhancement voltage threshold | V <sub>REG</sub>                                                                               | 1.58   | 1.65   |      | V    |

### 7.10 Current Wake Comparator

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER                | 2                                               | TEST CONDITION                                                                          | MIN  | TYP    | MAX  | UNIT |

|--------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|------|--------|------|------|

|                          |                                                 | V <sub>WAKE</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> WAKE_CONTROL[WK1, WK0]<br>= 0,0 | ±0.3 | ±0.625 | ±0.9 | mV   |

| V                        | Wake voltage                                    | V <sub>WAKE</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> WAKE_CONTROL[WK1, WK0]<br>= 0,1 | ±0.6 | ±1.25  | ±1.8 | mV   |

| V <sub>WAKE</sub>        | threshold                                       | V <sub>WAKE</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> WAKE_CONTROL[WK1, WK0]<br>= 1,0 | ±1.2 | ±2.5   | ±3.6 | mV   |

|                          |                                                 | V <sub>WAKE</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> WAKE_CONTROL[WK1, WK0]<br>= 1,1 | ±2.4 | ±5.0   | ±7.2 | mV   |

| V <sub>WAKE(DRIFT)</sub> | Temperature drift of V <sub>WAKE</sub> accuracy |                                                                                         |      | 0.5%   |      | °C   |

| t <sub>WAKE</sub>        | Time from application of current to wake        |                                                                                         |      | 0.25   | 0.5  | ms   |

Submit Document Feedback

### 7.10 Current Wake Comparator (continued)

Typical values stated where  $T_A$  = 25°C and VCC = 7.2 V, Min/Max values stated where  $T_A$  = -40°C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETE              | R                               | TEST CONDITION                                                        | MIN | TYP | MAX | UNIT |

|-----------------------|---------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>WAKE(SU)</sub> | Wake up comparator startup time | [WKCHGEN] = 0 and [WKDSGEN] = 0 to<br>[WKCHGEN] = 1 and [WKDSGEN] = 1 |     | 250 | 640 | μs   |

#### 7.11 Coulomb Counter

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER                  | TEST CONDITION                            | MIN                    | TYP  | MAX                    | UNIT   |

|----------------------------|-------------------------------------------|------------------------|------|------------------------|--------|

| Input voltage range        |                                           | -100                   |      | 100                    | mV     |

| Full scale range           |                                           | -V <sub>REF1</sub> /10 |      | +V <sub>REF1</sub> /10 | mV     |

| Differential nonlinearity  | 16-bit, no missing codes                  |                        |      | ±1                     | LSB    |

| Integral nonlinearity      | 16-bit, best fit over input voltage range |                        | ±5.2 | ±22.3                  | LSB    |

| Offset error               | 16-bit, post-calibration                  |                        | ±1.3 | ±2.6                   | LSB    |

| Offset error drift         | 15-bit + sign, post-calibration           |                        | 0.04 | 0.07                   | LSB/°C |

| Gain error                 | 15-bit + sign, over input voltage range   |                        | ±131 | ±492                   | LSB    |

| Gain error drift           | 15-bit + sign, over input voltage range   |                        | 4.3  | 9.8                    | LSB/°C |

| Effective input resistance |                                           | 2.5                    |      |                        | ΜΩ     |

# 7.12 ADC Digital Filter

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER            | TEST CONDITION                                 | MIN | TYP   | MAX | UNIT |

|----------------------|------------------------------------------------|-----|-------|-----|------|

|                      | ADCTL[SPEED1, SPEED0] = 0, 0                   |     | 31.25 |     |      |

|                      | ADCTL[SPEED1, SPEED0] = 0, 1                   |     | 15.63 |     |      |

| CONV                 | ADCTL[SPEED1, SPEED0] = 1, 0                   |     | 7.81  |     | ms   |

|                      | ADCTL[SPEED1, SPEED0] = 1, 1                   |     | 1.95  |     |      |

| Resolution           | No missing codes, ADCTL[SPEED1, SPEED0] = 0, 0 |     | 16    |     | Bits |

|                      | With sign, ADCTL[SPEED1, SPEED0] = 0, 0        | 14  | 15    |     |      |

| Effective resolution | With sign, ADCTL[SPEED1, SPEED0] = 0, 1        | 13  | 14    |     | Bits |

| Lifective resolution | With sign, ADCTL[SPEED1, SPEED0] = 1, 0        | 11  | 12    |     | טונס |

|                      | With sign, ADCTL[SPEED1, SPEED0] = 1, 1        | 9   | 10    |     |      |

### 7.13 ADC Multiplexer

Typical values stated where  $T_A$  = 25°C and VCC = 7.2 V, Min/Max values stated where  $T_A$  = -40°C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAM           | METER               | TEST CONDITION       | MIN    | TYP    | MAX                     | UNIT |

|-----------------|---------------------|----------------------|--------|--------|-------------------------|------|

| K Scaling fac   |                     | VC1-VSS, VC2-VC1     | 0.1980 | 0.2000 | 0.2020                  |      |

|                 | Scaling factor      | VC2-VSS, PACK-VSS    | 0.0485 | 0.050  | 0.051                   | _    |

|                 |                     | V <sub>REF1</sub> /2 | 0.490  | 0.500  | 0.510                   |      |

| V <sub>IN</sub> |                     | VC2-VSS, PACK-VSS    | -0.2   |        | 20                      |      |

|                 | Input voltage range | TS1                  | -0.2   |        | 0.8 × V <sub>REF1</sub> | V    |

|                 |                     | TS1                  | -0.2   |        | 0.8 × V <sub>REG</sub>  |      |

# 7.13 ADC Multiplexer (continued)

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| P  | ARAMETER                 | TEST CONDITION                                                              | MIN | TYP | MAX | UNIT |

|----|--------------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|

| IL | ko Innut leakade current | VC1, VC2 cell balancing off, cell detach detection off, ADC multiplexer off |     |     | 1   | μA   |

# 7.14 Cell Balancing Support

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAM           | ETER                             | TEST CONDITION                                                             | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------|----------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>CB</sub> | Internal cell balance resistance | R <sub>DS(ON)</sub> for internal FET switch at 2 V < V <sub>DS</sub> < 4 V |     |     | 200 | Ω    |

### 7.15 Internal Temperature Sensor

Typical values stated where  $T_A = 25^{\circ}$ C and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}$ C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAME            | TER                  | TEST CONDITION                                         | MIN   | TYP   | MAX   | UNIT    |

|-------------------|----------------------|--------------------------------------------------------|-------|-------|-------|---------|

| V <sub>TEMP</sub> | Internal temperature | V <sub>TEMPP</sub>                                     | -1.9  | -2.0  | -2.1  | mV/°C   |

|                   | sensor voltage drift | V <sub>TEMPP</sub> – V <sub>TEMPN</sub> <sup>(1)</sup> | 0.177 | 0.178 | 0.179 | 11107 C |

<sup>(1)</sup> Assured by design

# 7.16 NTC Thermistor Measurement Support

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETEI               | R                                 | TEST CONDITION | MIN  | TYP  | MAX  | UNIT   |

|-------------------------|-----------------------------------|----------------|------|------|------|--------|

| R <sub>NTC(PU)</sub>    | Internal pull-up resistance       | TS1            | 14.4 | 18   | 21.6 | kΩ     |

| R <sub>NTC(DRIFT)</sub> | Resistance drift over temperature | TS1            | -360 | -280 | -200 | PPM/°C |

# 7.17 High-Frequency Oscillator

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMET               | ER                  | TEST CONDITION                                                                                   | MIN   | TYP    | MAX  | UNIT |

|-----------------------|---------------------|--------------------------------------------------------------------------------------------------|-------|--------|------|------|

| f <sub>HFO</sub>      | Operating frequency |                                                                                                  |       | 16.78  |      | MHz  |

| f <sub>HFO(ERR)</sub> | Eroguenov error     | $T_A = -20$ °C to 70°C, includes frequency drift                                                 | -2.5% | ±0.25% | 2.5% |      |

|                       | Frequency error     | T <sub>A</sub> = -40°C to 85°C, includes frequency drift                                         | -3.5% | ±0.25% | 3.5% |      |

| t <sub>HFO(SU)</sub>  | Start-up time       | T <sub>A</sub> = -20°C to 85°C, Oscillator frequency within +/-3% of nominal, CLKCTL[HFRAMP] = 1 |       |        | 4    | ms   |

|                       |                     | Oscillator frequency within +/–3% of nominal, CLKCTL[HFRAMP] = 0                                 |       |        | 100  | μs   |

### 7.18 Low-Frequency Oscillator

Submit Document Feedback

Typical values stated where  $T_A = 25^{\circ}$ C and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}$ C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAM     | METER               | TEST CONDITION | MIN | TYP     | MAX | UNIT |

|-----------|---------------------|----------------|-----|---------|-----|------|

| $f_{LFO}$ | Operating frequency |                |     | 262.144 |     | kHz  |

Product Folder Links: BQ28Z610-R1

### www.tij.co.jp

### 7.18 Low-Frequency Oscillator (continued)

Typical values stated where  $T_A = 25$ °C and VCC = 7.2 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETI                | ER                                    | TEST CONDITION                                           | MIN   | TYP    | MAX  | UNIT |

|-------------------------|---------------------------------------|----------------------------------------------------------|-------|--------|------|------|

| f <sub>LFO(LP)</sub>    | Operating frequency in low power mode |                                                          |       | 247    |      | kHz  |

| f                       | Fraguency arror                       | T <sub>A</sub> = -20°C to 70°C, includes frequency drift | -1.5% | ±0.25% | 1.5% |      |

| f <sub>LFO(ERR)</sub>   | Frequency error                       | T <sub>A</sub> = -40°C to 85°C, includes frequency drift | -2.5% | ±0.25% | 2.5% |      |

| f <sub>LFO(LPERR)</sub> | Frequency error in low power mode     |                                                          | -5%   |        | 5%   |      |

| f <sub>LFO(FAIL)</sub>  | Failure detection frequency           |                                                          | 30    | 80     | 100  | kHz  |

# 7.19 Voltage Reference 1

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER                | र                          | TEST CONDITION                             | MIN   | TYP   | MAX   | UNIT     |

|--------------------------|----------------------------|--------------------------------------------|-------|-------|-------|----------|

| V <sub>REF1</sub>        | Internal reference voltage | T <sub>A</sub> = 25°C, after trim          | 1.215 | 1.220 | 1.225 | V        |

| V                        | Internal reference         | T <sub>A</sub> = 0°C to 60°C, after trim   |       | ±50   |       | PPM/°C   |

| V <sub>REF1(DRIFT)</sub> | voltage drift              | T <sub>A</sub> = -40°C to 85°C, after trim |       | ±80   |       | PPINI/ C |

# 7.20 Voltage Reference 2

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER                |                            | TEST CONDITION                             | MIN   | TYP   | MAX   | UNIT     |

|--------------------------|----------------------------|--------------------------------------------|-------|-------|-------|----------|

| V <sub>REF2</sub>        | Internal reference voltage | T <sub>A</sub> = 25°C, after trim          | 1.215 | 1.220 | 1.225 | V        |

| V <sub>REF2(DRIFT)</sub> | Internal reference         | T <sub>A</sub> = 0°C to 60°C, after trim   |       | ±50   |       | PPM/°C   |

|                          | voltage drift              | T <sub>A</sub> = -40°C to 85°C, after trim |       | ±80   |       | FFIVI/ C |

#### 7.21 Instruction Flash

Typical values stated where  $T_A = 25^{\circ}$ C and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}$ C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETE                | R                              | TEST CONDITION                                       | MIN  | TYP | MAX | UNIT   |

|-------------------------|--------------------------------|------------------------------------------------------|------|-----|-----|--------|

|                         | Data retention                 |                                                      | 10   |     |     | Years  |

|                         | Flash programming write cycles |                                                      | 1000 |     |     | Cycles |

| t <sub>PROGWORD</sub>   | Word programming time          | T <sub>A</sub> = -40°C to 85°C                       |      |     | 40  | μs     |

| t <sub>MASSERASE</sub>  | Mass-erase time                | $T_A = -40$ °C to 85°C                               |      |     | 40  | ms     |

| t <sub>PAGEERASE</sub>  | Page-erase time                | $T_A = -40^{\circ} \text{C to } 85^{\circ} \text{C}$ |      |     | 40  | ms     |

| I <sub>FLASHREAD</sub>  | Flash-read current             | $T_A = -40^{\circ} C \text{ to } 85^{\circ} C$       |      |     | 2   | mA     |

| I <sub>FLASHWRITE</sub> | Flash-write current            | $T_A = -40$ °C to 85°C                               |      |     | 5   | mA     |

| I <sub>FLASHERASE</sub> | Flash-erase current            | $T_A = -40$ °C to 85°C                               |      |     | 15  | mA     |

#### 7.22 Data Flash

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETE                | R                              | TEST CONDITION                 | MIN   | TYP | MAX | UNIT   |

|-------------------------|--------------------------------|--------------------------------|-------|-----|-----|--------|

|                         | Data retention                 |                                | 10    |     |     | Years  |

|                         | Flash programming write cycles |                                | 20000 |     |     | Cycles |

| t <sub>PROGWORD</sub>   | Word programming time          | T <sub>A</sub> = -40°C to 85°C |       |     | 40  | μs     |

| t <sub>MASSERASE</sub>  | Mass-erase time                | $T_A = -40$ °C to 85°C         |       |     | 40  | ms     |

| t <sub>PAGEERASE</sub>  | Page-erase time                | $T_A = -40$ °C to 85°C         |       |     | 40  | ms     |

| I <sub>FLASHREAD</sub>  | Flash-read current             | $T_A = -40$ °C to 85°C         |       |     | 1   | mA     |

| I <sub>FLASHWRITE</sub> | Flash-write current            | $T_A = -40$ °C to 85°C         |       |     | 5   | mA     |

| I <sub>FLASHERASE</sub> | Flash-erase current            | $T_A = -40$ °C to 85°C         |       |     | 15  | mA     |

### 7.23 Current Protection Thresholds

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAME             | ETER                                         | TEST CONDITION                                                                            | MIN   | TYP   | MAX  | UNIT |

|--------------------|----------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|------|------|

| V                  | OCD detection threshold                      | V <sub>OCD</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 1  | -16.6 |       | -100 | mV   |

| V <sub>OCD</sub>   | voltage range                                | V <sub>OCD</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 0  | -8.3  |       | -50  | 1110 |

| ΔV <sub>OCD</sub>  | OCD detection threshold                      | V <sub>OCD</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 1  |       | -5.56 |      | mV   |

|                    | voltage program step                         | $V_{OCD} = V_{SRP} - V_{SRN}$ ,<br>PROTECTION_CONTROL[RSNS] = 0                           |       | -2.78 |      | IIIV |

| $\Delta V_{SCC}$   | SCC detection threshold                      | V <sub>SCC</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 1  | 44.4  |       | 200  | mV   |

|                    | voltage range                                | V <sub>SCC</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 0  | 22.2  |       | 100  | IIIV |

| $\Delta V_{SCC}$   | SCC detection threshold voltage program step | V <sub>SCC</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 1  |       | 22.2  |      | mV   |

|                    |                                              | V <sub>SCC</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 0  |       | 11.1  |      | IIIV |

| \/                 | SCD1 detection threshold                     | V <sub>SCD1</sub> = V <sub>SRP</sub> – V <sub>SRN,</sub><br>PROTECTION_CONTROL[RSNS] = 1  | -44.4 |       | -200 | mV   |

| V <sub>SCD1</sub>  | voltage range                                | V <sub>SCD1</sub> = V <sub>SRP</sub> - V <sub>SRN,</sub><br>PROTECTION_CONTROL[RSNS] = 0  | -22.2 |       | -100 | IIIV |

| ۸۱/                | SCD1 detection threshold                     | V <sub>SCD1</sub> = V <sub>SRP</sub> – V <sub>SRN,</sub><br>PROTECTION_CONTROL[RSNS] = 1  |       | -22.2 |      | mV   |

| ΔV <sub>SCD1</sub> | voltage program step                         | V <sub>SCD1</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 0 |       | -11.1 |      | 1110 |

| \/                 | SCD2 detection threshold                     | V <sub>SCD2</sub> = V <sub>SRP</sub> - V <sub>SRN,</sub><br>PROTECTION_CONTROL[RSNS] = 1  | -44.4 |       | -200 | mV   |

| V <sub>SCD2</sub>  | voltage range                                | V <sub>SCD2</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 0 | -22.2 |       | -100 | IIIV |

| ۸۱/                | SCD2 detection threshold                     | V <sub>SCD2</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 1 |       | -22.2 |      | mV   |

| ΔV <sub>SCD2</sub> | voltage program step                         | V <sub>SCD2</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> ,<br>PROTECTION_CONTROL[RSNS] = 0 |       | -11.1 |      | 1111 |

Submit Document Feedback

# 7.24 Current Protection Timing

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAME              | TER                                    | TEST CONDITION                                                                                    | MIN  | NOM  | MAX  | UNIT |

|---------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>OCD</sub>    | OCD detection delay time               |                                                                                                   | 1    | ,    | 31   | ms   |

| $\Delta t_{OCD}$    | OCD detection delay time program step  |                                                                                                   |      | 2    |      | ms   |

| t <sub>scc</sub>    | SCC detection delay time               |                                                                                                   | 0    |      | 915  | μs   |

| Δt <sub>SCC</sub>   | SCC detection delay time program step  |                                                                                                   |      | 61   |      | μs   |

|                     | SCD1 detection delay time              | PROTECTION_CONTROL[SCDDx2] = 0                                                                    | 0    |      | 915  |      |

| t <sub>SCD1</sub>   |                                        | PROTECTION_CONTROL[SCDDx2] = 1                                                                    | 0    |      | 1850 | μs   |

| Λ+                  | SCD1 detection delay time program step | PROTECTION_CONTROL[SCDDx2] = 0                                                                    |      | 61   |      |      |

| ∆t <sub>SCD1</sub>  |                                        | PROTECTION_CONTROL[SCDDx2] = 1                                                                    |      | 121  |      | μs   |

| 4                   | SCD2 detection delay                   | PROTECTION_CONTROL[SCDDx2] = 0                                                                    | 0    |      | 458  |      |

| t <sub>SCD2</sub>   | time                                   | PROTECTION_CONTROL[SCDDx2] = 1                                                                    | 0    |      | 915  | μs   |

| ۸٠                  | SCD2 detection delay                   | PROTECTION_CONTROL[SCDDx2] = 0                                                                    |      | 30.5 |      |      |

| ∆t <sub>SCD2</sub>  | time program step                      | PROTECTION_CONTROL[SCDDx2] = 1                                                                    |      | 61   |      | μs   |

| t <sub>DETECT</sub> | Current fault detect time              | $V_{SRP} - V_{SRN} = V_T - 3$ mV for OCD, SCD1, and SC2, $V_{SRP} - V_{SRN} = V_T + 3$ mV for SCC |      |      | 160  | μs   |

| t <sub>ACC</sub>    | Current fault delay time accuracy      | Max delay setting                                                                                 | -10% |      | 10%  |      |

# 7.25 N-CH FET Drive (CHG, DSG)

Typical values stated where  $T_A$  = 25°C and VCC = 7.2 V, Min/Max values stated where  $T_A$  = -40°C to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAMETER             |                                       | TEST CONDITION                                                                                                                                                   | MIN   | TYP   | MAX   | UNIT |

|-----------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                       | Output voltage ratio                  | Ratio DSG = $(V_{DSG} - V_{VC2})/V_{VC2}$ , 2.2 V < $V_{VC2}$ < 4.07 V, 10 M $\Omega$ between PACK and DSG                                                       | 2.133 | 2.333 | 2.467 |      |

|                       |                                       | Ratio CHG = $(V_{CHG} - V_{VC2})/V_{VC2}$ , 2.2 V < $V_{VC2}$ < 4.07 V, 10 M $\Omega$ between BAT and CHG                                                        | 2.133 | 2.333 | 2.467 | _    |

| V <sub>(FETON)</sub>  | Output voltage,                       | $V_{DSG(ON)}$ = $V_{DSG}$ – $V_{VC2}$ , 4.07 V ≤ $V_{VC2}$ ≤ 18 V, 10 MΩ between PACK and DSG                                                                    | 8.75  | 9.5   | 10.25 | V    |

|                       | CHG and DSG on                        | $V_{CHG(ON)} = V_{CHG} - V_{VC2}, 4.07 \text{ V} \le V_{VC2} \le 18 \text{ V}, 10 \text{ M}\Omega$ between VC2 and CHG                                           | 8.75  | 9.5   | 10.25 | V    |

| V <sub>(FETOFF)</sub> | Output voltage,<br>F) CHG and DSG off | $V_{DSG(OFF)}$ = $V_{DSG}$ – $V_{PACK}$ , 10 M $\Omega$ between PACK and DSG                                                                                     | -0.4  |       | 0.4   | V    |

| , ,                   |                                       | $V_{\text{CHG(OFF)}}$ = $V_{\text{CHG}} - V_{\text{BAT}}$ , 10 M $\Omega$ between VC2 and CHG                                                                    | -0.4  |       | 0.4   |      |

| 4_                    | <b>5</b>                              | $V_{DSG}$ from 0% to 35% $V_{DSG~(ON)(TYP)}$ , $V_{BAT}$ ≥ 2.2 V, $C_L$ = 4.7 nF between DSG and PACK, 5.1 kΩ between DSG and $C_L$ , 10 MΩ between PACK and DSG |       | 200   | 500   | 116  |

| t <sub>R</sub>        | Rise time                             | $V_{CHG}$ from 0% to 35% $V_{CHG~(ON)(TYP)}$ , $V_{VC2}$ ≥ 2.2 V, $C_L$ = 4.7 nF between CHG and VC2, 5.1 kΩ between CHG and $C_L$ , 10 MΩ between VC2 and CHG   |       | 200   | 500   | μs   |

| t <sub>F</sub>        | Fall time                             | $V_{DSG}$ from $V_{DSG(ON)(TYP)}$ to 1 V, $V_{VC2}$ ≥ 2.2 V, $C_L$ = 4.7 nF between DSG and PACK, 5.1 kΩ between DSG and $C_L$ , 10 MΩ between PACK and DSG      |       | 40    | 300   | 116  |

|                       | Fall time                             | $V_{CHG}$ from $V_{CHG(ON)(TYP)}$ to 1 V, $V_{VC2}$ ≥ 2.2 V, $C_L$ = 4.7 nF between CHG and VC2, 5.1 kΩ between CHG and $C_L$ , 10 MΩ between VC2 and CHG        |       | 40    | 200   | μs   |

# 7.26 I<sup>2</sup>C Interface I/O

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}\text{C}$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| PARAME           | TER                   | TEST CONDITION                                             | MIN                    | TYP | MAX                    | UNIT |

|------------------|-----------------------|------------------------------------------------------------|------------------------|-----|------------------------|------|

| V <sub>IH</sub>  | Input voltage high    | SCL, SDA (STANDARD and FAST modes)                         | 0.7 × V <sub>REG</sub> |     |                        | V    |

| V <sub>IL</sub>  | Input voltage low     | SCL, SDA (STANDARD and FAST modes)                         | -0.5                   |     | 0.3 × V <sub>REG</sub> | V    |

| V <sub>OL</sub>  | Output low voltage    | SCL, SDA, I <sub>OL</sub> = 1 mA (STANDARD and FAST modes) |                        |     | 0.2 × V <sub>REG</sub> | V    |

| C <sub>IN</sub>  | Input capacitance     |                                                            |                        |     | 10                     | pF   |

| I <sub>LKG</sub> | Input leakage current |                                                            |                        | 1   |                        | μА   |

| R <sub>PD</sub>  | Pull-down resistance  |                                                            |                        | 3.3 |                        | kΩ   |

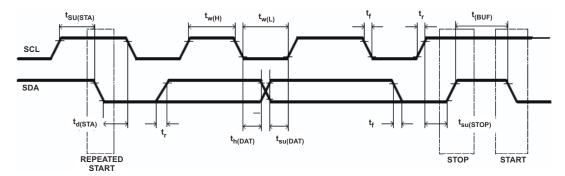

# 7.27 I<sup>2</sup>C Interface Timing

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 7.2 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 7.6 V (unless otherwise noted)

| P                      | ARAMETER                                   | TEST CONDITION                 | MIN | NOM | MAX | UNIT |

|------------------------|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| t <sub>R</sub>         | Clock rise time                            | 10% to 90%                     |     |     | 300 | ns   |

| t <sub>F</sub>         | Clock fall time                            | 90% to 10%                     |     |     | 300 | ns   |

| t <sub>HIGH</sub>      | Clock high period                          |                                | 600 |     |     | ns   |

| $t_{LOW}$              | Clock low period                           |                                | 1.3 |     |     | μs   |

| t <sub>SU(START)</sub> | Repeated start setup time                  |                                | 600 |     |     | ns   |

| t <sub>d(START)</sub>  | Start for first falling edge to SCL        |                                | 600 |     |     | ns   |

| t <sub>SU(DATA)</sub>  | Data setup time                            |                                | 100 |     |     | ns   |

| t <sub>HD(DATA)</sub>  | Data hold time                             |                                | 0   |     |     | μs   |

| t <sub>SU(STOP)</sub>  | Stop setup time                            |                                | 600 |     |     | ns   |

| t <sub>BUF</sub>       | Bus free time<br>between stop and<br>start |                                | 1.3 |     |     | μs   |

| f <sub>SW</sub>        | Clock operating frequency                  | SLAVE mode, SCL 50% duty cycle |     |     | 400 | kHz  |

図 7-1. I<sup>2</sup>C Timing

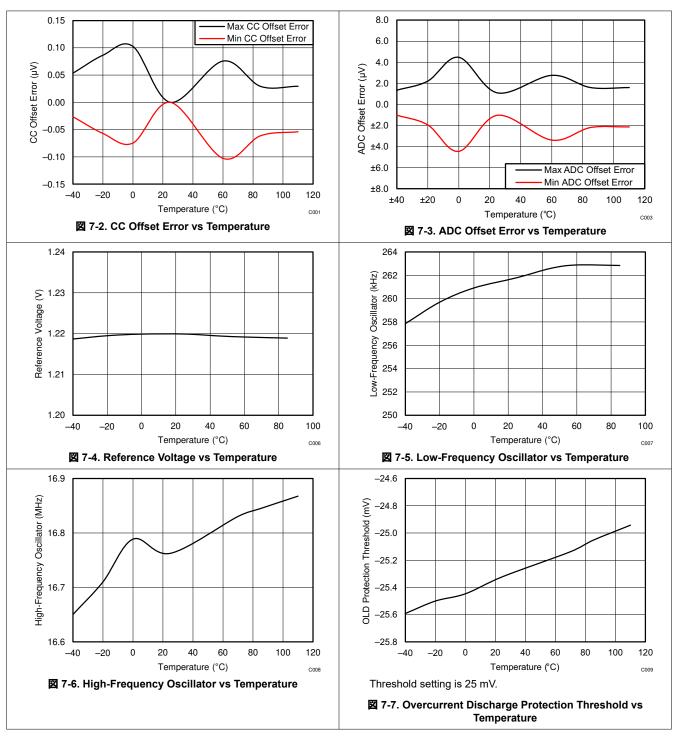

# 7.28 Typical Characteristics

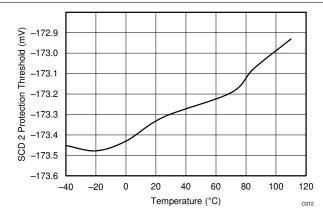

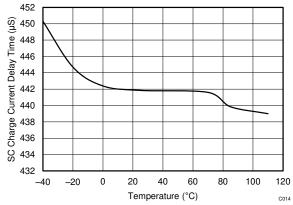

# 7.28 Typical Characteristics (continued)

Threshold setting is 88.8 mV.

図 7-8. Short Circuit Charge Protection Threshold vs Temperature

Threshold setting is -177.7 mV.

図 7-10. Short Circuit Discharge 2 Protection Threshold vs Temperature

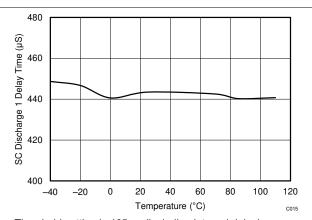

Threshold setting is 465 µs.

図 7-12. Short Circuit Charge Current Delay Time vs Temperature

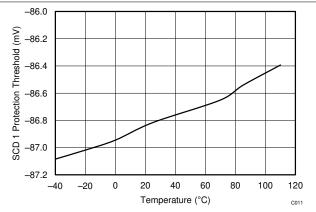

Threshold setting is -88.8 mV.

図 7-9. Short Circuit Discharge 1 Protection Threshold vs Temperature

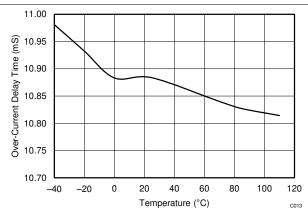

Threshold setting is 11 ms.

図 7-11. Overcurrent Delay Time vs Temperature

Threshold setting is 465 µs (including internal delay).

図 7-13. Short Circuit Discharge 1 Delay Time vs Temperature

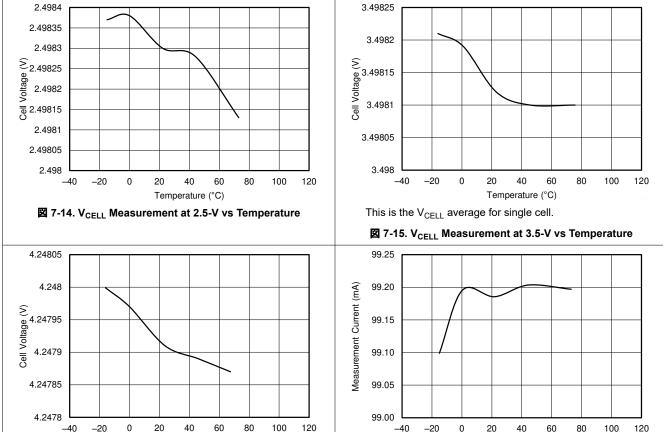

# 7.28 Typical Characteristics (continued)

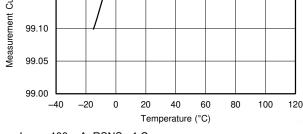

This is the  $V_{\text{CELL}}$  average for single cell.

☑ 7-16. V<sub>CELL</sub> Measurement at 4.25-V vs Temperature

Temperature (°C)

$I_{SET}$  = 100 mA, RSNS= 1  $\Omega$

☑ 7-17. I Measured vs Temperature

# 8 Detailed Description

### 8.1 Overview

The BQ28Z610-R1 gas gauge is a fully integrated battery manager that employs flash-based firmware and integrated hardware protection to provide a complete solution for battery-stack architectures composed of 1- to 2-series cells. The BQ28Z610-R1 device interfaces with a host system via an  $I^2C$  protocol. High-performance, integrated analog peripherals enable support for a sense resistor down to 1 m $\Omega$  and simultaneous current/ voltage data conversion for instant power calculations. The following sections detail all of the major component blocks included as part of the BQ28Z610-R1 device.

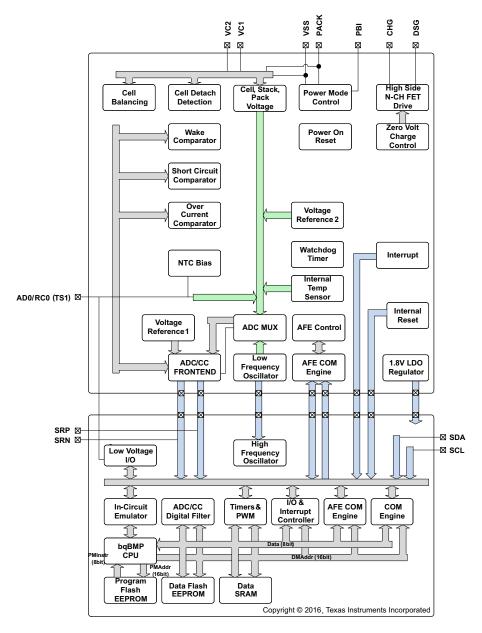

## 8.2 Functional Block Diagram

The *Functional Block Diagram* depicts the analog (AFE) and digital (AGG) peripheral content in the BQ28Z610-R1 device.

Submit Document Feedback

### 8.3 Feature Description

#### 8.3.1 Battery Parameter Measurements

The BQ28Z610-R1 device measures cell voltage and current simultaneously, and measures temperature to calculate the information related to remaining capacity, full charge capacity, state-of-health, and other gauging parameters.

#### 8.3.1.1 BQ28Z610-R1 Processor

The BQ28Z610-R1 device uses a custom TI-proprietary processor design that features a Harvard architecture and operates at frequencies up to 4.2 MHz. Using an adaptive, three-stage instruction pipeline, the BQ28Z610-R1 processor supports variable instruction length of 8, 16, or 24 bits.

### 8.3.2 Coulomb Counter (CC)

The first ADC is an integrating converter designed specifically for coulomb counting. The converter resolution is a function of its full-scale range and number of bits, yielding a 3.74-µV resolution.

### 8.3.3 CC Digital Filter

The CC digital filter generates a 16-bit conversion value from the delta-sigma CC front-end. Its FIR filter uses the LFO clock output, which allows it to stop the HFO clock during conversions. New conversions are available every 250 ms while CCTL[CC\_ON] = 1. Proper use of this peripheral requires turning on the CC modulator in the AFE.

# 8.3.4 ADC Multiplexer

The ADC multiplexer provides selectable connections to the VCx inputs, TS1 inputs, internal temperature sensor, internal reference voltages, internal 1.8-V regulator, PACK input, and VSS ground reference input. In addition, the multiplexer can independently enable the TS1 input connection to the internal thermistor biasing circuitry, and enables the user to short the multiplexer inputs for test and calibration purposes.

#### 8.3.5 Analog-to-Digital Converter (ADC)

The second ADC is a 16-bit delta-sigma converter designed for general-purpose measurements. The ADC automatically scales the input voltage range during sampling based on channel selection. The converter resolution is a function of its full-scale range and number of bits, yielding a 38-µV resolution. The default conversion time of the ADC is 31.25 ms, but is user-configurable down to 1.95 ms. Decreasing the conversion time presents a tradeoff between conversion speed and accuracy, as the resolution decreases for faster conversion times.

#### 8.3.6 ADC Digital Filter

The ADC digital filter generates a 24-bit conversion result from the delta-sigma ADC front end. Its FIR filter uses the LFO clock, which allows it to stop the HFO clock during conversions. The ADC digital filter is capable of providing two 24-bit results: one result from the delta-sigma ADC front-end and a second synchronous result from the delta-sigma CC front-end.

#### 8.3.7 Internal Temperature Sensor

An internal temperature sensor is available on the BQ28Z610-R1 device to reduce the cost, power, and size of the external components necessary to measure temperature. It is available for connection to the ADC using the multiplexer, and is ideal for quickly determining pack temperature under a variety of operating conditions.

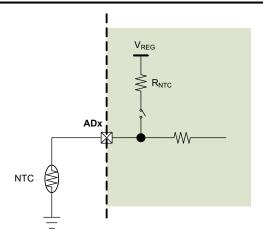

### 8.3.8 External Temperature Sensor Support

The TS1 input is enabled with an internal  $18-k\Omega$  (Typ.) linearization pull-up resistor to support the use of a  $10-k\Omega$  ( $25^{\circ}$ C) NTC external thermistor, such as the Semitec 103AT-2. The NTC thermistor should be connected between VSS and the individual TS1 pin. The analog measurement is then taken via the ADC through its input multiplexer. If a different thermistor type is required, then changes to configurations may be required.

図 8-1. External Thermistor Biasing

#### 8.3.9 Power Supply Control

The BQ28Z610-R1 device manages its supply voltage dynamically according to operating conditions. When  $V_{VC2} > V_{SWITCHOVER-} + V_{HYS}$ , the AFE connects an internal switch to BAT and uses this pin to supply power to its internal 1.8-V LDO, which subsequently powers all device logic and flash operations. Once VC2 decreases to  $V_{VC2} < V_{SWITCHOVER-}$ , the AFE disconnects its internal switch from VC2 and connects another switch to PACK, allowing sourcing of power from a charger (if present). An external capacitor connected to PBI provides a momentary supply voltage to help guard against system brownouts due to transient short-circuit or overload events that pull VC2 below  $V_{SWITCHOVER-}$ .

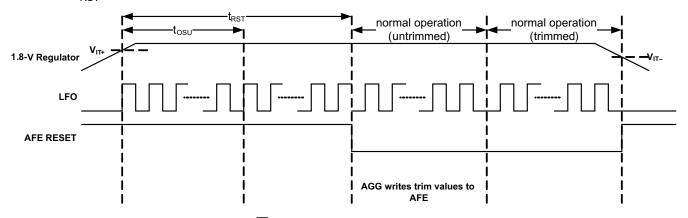

#### 8.3.10 Power-On Reset

In the event of a power-cycle, the BQ28Z610-R1 AFE holds its internal RESET output pin high for  $t_{RST}$  duration to allow its internal 1.8-V LDO and LFO to stabilize before running the AGG. The AFE enters power-on reset when the voltage at  $V_{REG}$  falls below  $V_{REGIT-}$  and exits reset when  $V_{REG}$  rises above  $V_{REGIT-} + V_{HYS}$  for  $t_{RST}$  time. After  $t_{RST}$ , the BQ28Z610-R1 AGG will write its trim values to the AFE.

図 8-2. POR Timing Diagram

#### 8.3.11 Bus Communication Interface

The BQ28Z610-R1 device has an I<sup>2</sup>C bus communication interface. This device has the option to broadcast information to a smart charger to provide key information to adjust the charging current and charging voltage based on the temperature or individual cell voltages.

Submit Document Feedback

#### CAUTION

If the device is configured as a single-master architecture (an application processor) and an occasional NACK is detected in the operation, the master can resend the transaction. However, in a multi-master architecture, an incorrect ACK leading to accidental loss of bus arbitration can cause a master to wait incorrectly for another master to clear the bus. If this master does not get a bus-free signal, then it must have in place a method to look for the bus and assume it is free after some period of time. Also, if possible, set the clock speed to be 100 kHz or less to significantly reduce the issue described above for multi-mode operation.

#### 8.3.12 I<sup>2</sup>C Timeout

The  $I^2C$  engine will release both SDA and SCL if the  $I^2C$  bus is held low for  $\sim$ 2 seconds. If the BQ28Z610-R1 device were holding the lines, releasing them frees the master to drive the lines. Note: that the low time setting can be under firmware control but the HW default is 2 seconds.

#### 8.3.13 Cell Balancing Support

The integrated cell balancing FETs included in the BQ28Z610-R1 device enable the AFE to bypass cell current around a given cell or numerous cells to effectively balance the entire battery stack. External series resistors placed between the cell connections and the VCx input pins set the balancing current magnitude. The cell balancing circuitry can be enabled or disabled via the *CELL\_BAL\_DET[CB2, CB1]* control register. Series input resistors between 100  $\Omega$  and 1 k $\Omega$  are recommended for effective cell balancing.

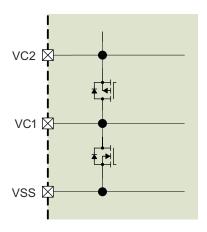

図 8-3. Internal Cell Balancing

#### 8.3.14 N-Channel Protection FET Drive

The BQ28Z610-R1 device controls two external N-Channel MOSFETs in a back-to-back configuration for battery protection. The charge (CHG) and discharge (DSG) FETs are automatically disabled if a safety fault (AOLD, ASSC, ASCD, SOV) is detected, and can also be manually turned off using **AFE\_CONTROL[CHGEN, DSGEN]** = 0, 0. When the gate drive is disabled, an internal circuit discharges CHG to VC2 and DSG to PACK.

#### 8.3.15 Low Frequency Oscillator

The BQ28Z610-R1 AFE includes a low frequency oscillator (LFO) running at 262.144 kHz. The AFE monitors the LFO frequency and indicates a failure via *LATCH\_STATUS[LFO]* if the output frequency is much lower than normal.

#### 8.3.16 High Frequency Oscillator

The BQ28Z610-R1 AGG includes a high frequency oscillator (HFO) running at 16.78 MHz. It is synthesized from the LFO output and scaled down to 8.388 MHz with 50% duty cycle.

#### 8.3.17 1.8-V Low Dropout Regulator

The BQ28Z610-R1 AFE contains an integrated 1.8-V LDO that provides regulated supply voltage for the device CPU and internal digital logic.

#### 8.3.18 Internal Voltage References

The BQ28Z610-R1 AFE provides two internal voltage references with  $V_{REF1}$ , used by the ADC and CC, while  $V_{REF2}$  is used by the LDO, LFO, current wake comparator, and OCD/SCC/SCD1/SCD2 current protection circuitry.

### 8.3.19 Overcurrent in Discharge Protection

The overcurrent in discharge (OCD) function detects abnormally high current in the discharge direction. The overload in discharge threshold and delay time are configurable via the OCD\_CONTROL register. The thresholds and timing can be fine-tuned even further based on a sense resistor with lower resistance or wider tolerance via the PROTECTION\_CONTROL register. The detection circuit also incorporates a filtered delay before disabling the CHG and DSG FETs. When an OCD event occurs, the **LATCH\_STATUS[OCD]** bit is set to 1 and is latched until it is cleared and the fault condition has been removed.

### 8.3.20 Short-Circuit Current in Charge Protection

The short-circuit current in charge (SCC) function detects catastrophic current conditions in the charge direction. The short-circuit in charge threshold and delay time are configurable via the SCC\_CONTROL register. The thresholds and timing can be fine-tuned even further based on a sense resistor with lower resistance or wider tolerance via the PROTECTION\_CONTROL register. The detection circuit also incorporates a blanking delay before disabling the CHG and DSG FETs. When an SCC event occurs, the **LATCH\_STATUS[SCC]** bit is set to 1 and is latched until it is cleared and the fault condition has been removed.

### 8.3.21 Short-Circuit Current in Discharge 1 and 2 Protection

The short-circuit current in discharge (SCD) function detects catastrophic current conditions in the discharge direction. The short-circuit in discharge thresholds and delay times are configurable via the SCD1\_CONTROL and SCD2\_CONTROL registers. The thresholds and timing can be fine-tuned even further based on a sense resistor with lower resistance or wider tolerance via the PROTECTION\_CONTROL register. The detection circuit also incorporates a blanking delay before disabling the CHG and DSG FETs. When an SCD event occurs, the *LATCH\_STATUS[SCD1]* or *LATCH\_STATUS[SCD2]* bit is set to 1 and is latched until it is cleared and the fault condition has been removed.

#### 8.3.22 Primary Protection Features

The BQ28Z610-R1 gas gauge supports the following battery and system level protection features, which can be configured using firmware:

- Cell Undervoltage Protection

- Cell Overvoltage Protection

- Overcurrent in CHARGE Mode Protection

- Overcurrent in DISCHARGE Mode Protection

- Overload in DISCHARGE Mode Protection

- Short Circuit in CHARGE Mode Protection

- Overtemperature in CHARGE Mode Protection

- Overtemperature in DISCHARGE Mode Protection

- · Precharge Timeout Protection

- Fast Charge Timeout Protection

#### 8.3.23 Gas Gauging

This device uses the Impedance Track™ technology to measure and determine the available charge in battery cells. The accuracy achieved using this method is better than 1% error over the lifetime of the battery. There is no full charge/discharge learning cycle required. See the *Theory and Implementation of Impedance Track Battery Fuel-Gauging Algorithm Application Report* for further details.

#### 8.3.24 Charge Control Features

This device supports charge control features, such as:

- Reports charging voltage and charging current based on the active temperature range—JEITA temperature ranges T1, T2, T3, T4, T5, and T6

- Provides more complex charging profiles, including sub-ranges within a standard temperature range

- Reports the appropriate charging current required for constant current charging and the appropriate charging voltage needed for constant voltage charging to a smart charger, using the bus communication interface

- Selects the chemical state-of-charge of each battery cell using the Impedance Track method, and reduces the voltage difference between cells when cell balancing multiple cells in a series

- Provides pre-charging/zero-volt charging

- · Employs charge inhibit and charge suspend if battery pack temperature is out of programmed range

- · Reports charging faults and indicates charge status via charge and discharge alarms

#### 8.3.25 Authentication

This device supports security by:

- · Authentication by the host using the SHA-1 method

- The gas gauge requires SHA-1 authentication before the device can be unsealed or allow full access.

#### **8.4 Device Functional Modes**

This device supports three modes, but the current consumption varies, based on firmware control of certain functions and modes of operation:

- NORMAL mode: In this mode, the device performs measurements, calculations, protections, and data

updates every 250-ms intervals. Between these intervals, the device is operating in a reduced power stage to

minimize total average current consumption.

- SLEEP mode: In this mode, the device performs measurements, calculations, protections, and data updates in adjustable time intervals. Between these intervals, the device is operating in a reduced power stage to minimize total average current consumption.

- SHUTDOWN mode: The device is completely disabled.

# 8.4.1 Lifetime Logging Features

The device supports data logging of several key parameters for warranty and analysis:

- · Maximum and minimum cell temperature

- Maximum current in CHARGE or DISCHARGE mode

- · Maximum and minimum cell voltages

#### 8.4.2 Configuration

The device supports accurate data measurements and data logging of several key parameters.

#### 8.4.2.1 Coulomb Counting

The device uses an integrating delta-sigma analog-to-digital converter (ADC) for current measurement. The ADC measures charge/discharge flow of the battery by measuring the voltage across a very small external sense resistor. The integrating ADC measures a bipolar signal from a range of -100 mV to 100 mV, with a positive value when  $V_{(SRP)} - V_{(SRN)}$ , indicating charge current and a negative value indicating discharge current. The integration method uses a continuous timer and internal counter, which has a rate of 0.65 nVh.

#### 8.4.2.2 Cell Voltage Measurements

The BQ28Z610-R1 measures the individual cell voltages at 250-ms intervals using an ADC. This measured value is internally scaled for the ADC and is calibrated to reduce any errors due to offsets. This data is also used for calculating the impedance of the individual cell for Impedance Track gas gauging.

#### 8.4.2.3 Current Measurements

The current measurement is performed by measuring the voltage drop across the external sense resistor (1 m $\Omega$  to 3 m $\Omega$ ) and the polarity of the differential voltage determines if the cell is in the CHARGE or DISCHARGE mode.

#### 8.4.2.4 Auto Calibration

The auto-calibration feature helps to cancel any voltage offset across the SRP and SRN pins for accurate measurement of the cell voltage, charge/discharge current, and thermistor temperature. The auto-calibration is performed when there is no communication activity for a minimum of 5 s on the bus lines.

#### 8.4.2.5 Temperature Measurements

This device has an internal sensor for on-die temperature measurements, and the ability to support external temperature measurements via the external NTC on the TS1 pin. These two measurements are individually enabled and configured.

Product Folder Links: BQ28Z610-R1

# 9 Applications and Implementation

#### Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

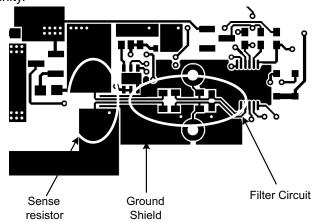

### 9.1 Application Information