# BQ25960 I<sup>2</sup>C 制御、バイパス・モードおよびデュアル入力選択機能搭載、 ーセル 8A スイッチト・キャパシタ・パラレル・バッテリ・チャージャ

#### 1 特長

- 8A の高速充電をサポートするピーク効率 98.1% のス イッチト・キャパシタ・パラレル充電器

- 最高効率を実現するよう最適化されたデュアルフェー ズ・スイッチト・キャパシタ・アーキテクチャ (特許出願 中)

- 入力電圧はバッテリ電圧の2倍

- 出力電流は入力電流の2倍

- Aカケーブルの電源損失を低減

- 5A バイパス・モード高速充電機能を搭載

- 5A 入力と 5A 出力充電電流をサポートする R<sub>dson</sub> 21mΩ の充電パス抵抗

- 高速充電中の電源選択とUSB On-The-Go (OTG) / 逆方向 TX モードに対応可能なデュアル入力電源マ ルチプレクサ・コントローラ

- 幅広い入力電圧をサポート

- 最大 12.75V の動作時入力電圧

- 最大 40V の入力電圧に加え、外付け ACFET お よび外付け ACFET なしの 20V をオプション追加

- 最大 13A の充電電流で、同期動作する 2 台の BQ25960 に並列充電が可能

- 安全な動作の実現に役立つ、プログラマブルな各種保 護機能を統合

- 入力過電圧保護 (BUSOVP) およびバッテリ過電 圧保護 (BATOVP)

- 入力過電流保護 (BUSOCP) およびバッテリ過電 流保護 (BATOCP)

- 出力過電圧保護 (VOUTOVP)

- 入力低電流保護 (BUSUCP) と入力逆電流保護 (BUSRCP) によるアダプタの抜け検出およびブー ストバック防止機能

- バッテリおよびコネクタ温度のモニタリング機能 (TSBAT FLT および TSBUS FLT)

- 接合部過熱保護 (TDIE FLT)

- プログラム可能な設定によるシステム最適化

- 割り込みおよび割り込みマスク

- ADC の読み取りと構成

- ホスト制御用アラーム機能

- 電圧、電流、温度モニタリングのための 16 ビット ADC を内蔵

### 2 アプリケーション

- スマートフォン

- タブレット

### 3 概要

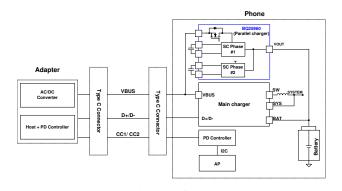

BQ25960 は、1 セルのリチウムイオン・バッテリ向けのスイ ッチト・キャパシタ・アーキテクチャを使用した、効率 98.1% の 8A バッテリ充電ソリューションです。スイッチト・ キャパシタ・アーキテクチャにより、ケーブル電流は充電電 流の半分になり、その結果、ケーブルの電源損失を低減 して、温度上昇を抑えることができます。デュアルフェー ズ・アーキテクチャにより、充電効率が上がり、入力と出力 に必要な容量は減少します。BQ2561x または BQ2589x などのメイン充電器と組み合わせて使用すると、システム は定電流 (CC) および定電圧 (CV) モードにおける電力 損失を低減することで、トリクル充電から終端までのフル充 電サイクルを有効にすることが可能です。

BQ25960 は、内蔵 MOSFET を経由する 5A バイパス・ モード充電 (旧名称はバッテリ・スイッチ充電) にも対応し ています。バイパス・モード充電経路の R<sub>dson</sub> は、大電流 動作時で 21mΩ です。 内蔵のバイパス・モードは 5V 高 速充電アダプタとの下位互換性があり、1 セルのバッテリ を充電することが可能です。

このデバイスは、内蔵のマルチプレクサ制御と外付け N-FET 用ドライバを経由するデュアル入力構成に対応して います。また、外付け N-FET がない場合や、単一 N-FET におけるシングル入力も可能です。

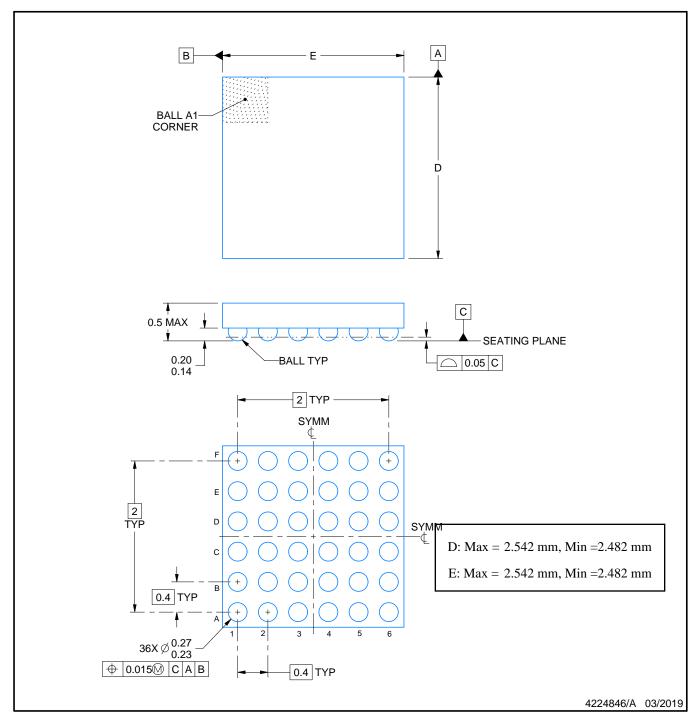

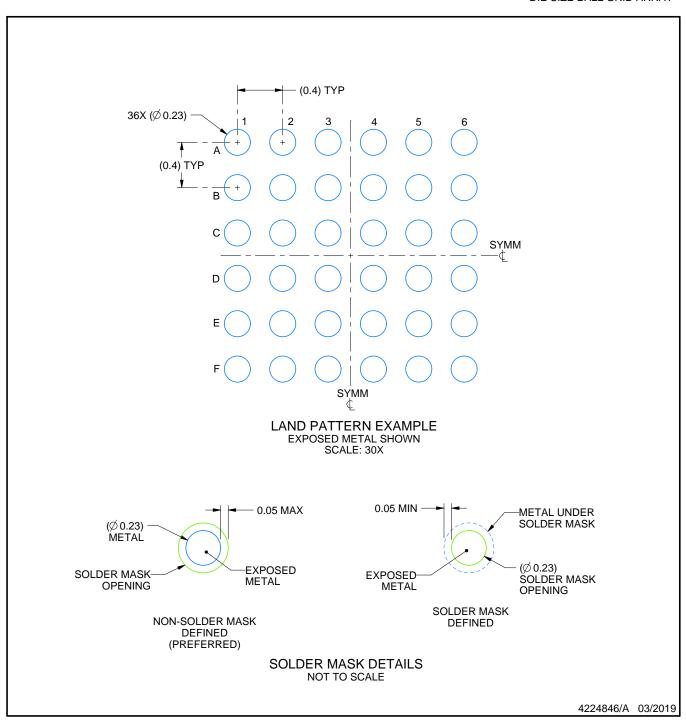

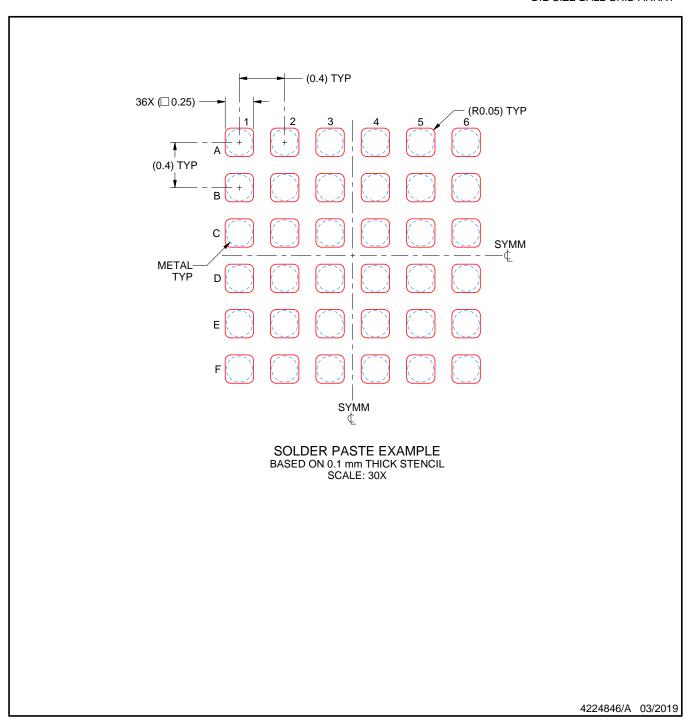

#### 製品情報

| 部品番号(1) | パッケージ      | 本体サイズ (公称)      |

|---------|------------|-----------------|

| BQ25960 | DSBGA (36) | 2.55mm x 2.55mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

簡略回路図

## **Table of Contents**

| 1 特長1                                 | 9.4 Programming                         | 29               |

|---------------------------------------|-----------------------------------------|------------------|

| <b>2</b> アプリケーション1                    | 9.5 Register Maps                       |                  |

| 3 概要1                                 | 10 Application and Implementation       | 63               |

| 4 Revision History2                   | 10.1 Application Information            | 63               |

| 5 概要 (続き)3                            | 10.2 Typical Application                |                  |

| 6 Device Comparison Table4            | 11 Power Supply Recommendations         | 69               |

| 7 Pin Configuration and Functions5    | 12 Layout                               |                  |

| 8 Specifications7                     | 12.1 Layout Guidelines                  | 70               |

| 8.1 Absolute Maximum Ratings7         | 12.2 Layout Example                     | 70               |

| 8.2 ESD Ratings                       | 13 Device and Documentation Support     | <mark>7</mark> 1 |

| 8.3 Recommended Operating Conditions7 | 13.1 Device Support                     | <mark>7</mark> 1 |

| 8.4 Thermal Information8              | 13.2 Documentation Support              | <mark>7</mark> 1 |

| 8.5 Electrical Characteristics8       | 13.3 ドキュメントの更新通知を受け取る方法                 | <mark>7</mark> 1 |

| 8.6 Timing Requirements               | 13.4 サポート・リソース                          | <b>7</b> 1       |

| 8.7 Typical Characteristics           | 13.5 Trademarks                         |                  |

| 9 Detailed Description15              | 13.6 静電気放電に関する注意事項                      | 71               |

| 9.1 Overview                          | 13.7 用語集                                |                  |

| 9.2 Functional Block Diagram          | 14 Mechanical, Packaging, and Orderable |                  |

| 9.3 Feature Description17             | Information                             | 72               |

|                                       |                                         |                  |

## **4 Revision History**

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| February 2021 | *        | Initial release. |

## 5 概要 (続き)

このデバイスには、安全な充電をサポートするために必要なすべての保護機能が搭載されています。例として、入力過電 圧および過電流保護、出力過電圧および過電流保護、入力低電流および逆電流保護、バッテリとケーブルの温度センシング、スイッチト・キャパシタとバイパス・モードの両方に対応した接合部過熱保護機能が挙げられます。

このデバイスには 16 ビットのアナログ / デジタル・コンバータ (ADC) が内蔵されており、VAC 電圧、バス電圧、バス電流、出力電圧、バッテリ電圧、バッテリ電流、入力コネクタ温度、バッテリ温度、接合部温度、およびアダプタやワイヤレス入力やパワーバンクからのバッテリ充電を管理するために必要なその他の算出測定値を提供します。

## **6 Device Comparison Table**

## 表 6-1. Device Comparison

| FUNCTION                         | BQ25960                      | BQ25970             | BQ25968             | BQ25980                      |

|----------------------------------|------------------------------|---------------------|---------------------|------------------------------|

| Package                          | YBG-36                       | YFF-56              | YFF-56              | YFF-80                       |

| Die size                         | 6.5 mm <sup>2</sup>          | 9.5 mm <sup>2</sup> | 9.5 mm <sup>2</sup> | 13.2 mm <sup>2</sup>         |

| Battery                          | 1 cell                       | 1 cell              | 1 cell              | 2 cell                       |

| Input MUX control                | Dual input power MUX control | Single OVPFET       | Single OVPFET       | Dual input power MUX control |

| Bypass Mode                      | Yes                          | No                  | No                  | Yes                          |

| Recommended 8-A charging current | 8 A                          | 8 A                 | 6 A                 | 8 A                          |

English Data Sheet: SLUSE08

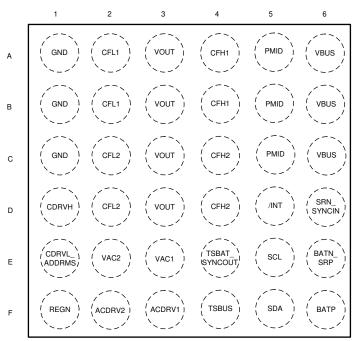

## 7 Pin Configuration and Functions

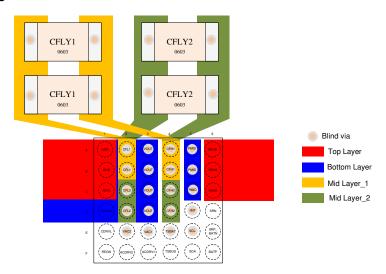

図 7-1. YBG Package - BQ25960 36-Pin DSBGA Top View

表 7-1. Pin Functions

|        | PIN                                                                                                                                                                                                                                                   | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME                                                                                                                                                                                                                                                  | ITPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                    |

| F3     | ACDRV1                                                                                                                                                                                                                                                | Р       | Input FETs Driver Pin 1 - The charge pump output to drive the port #1 input N-channel MOSFET (ACFET1) and the reverse blocking N-channel MOSFET (RBFET1). ACDRV1 voltage becomes 5 V above the common drain connection of the ACFET1 and RBFET1, when the turn-on condition is met. If ACFET1 and RBFET1 are not used, connect ACDRV1 to ground.                                                               |

| F2     | MOSFET (ACFET2) and the reverse blocking N-channel MOSFET (RBFET2). ACDRV2 voltage becomes 5 V above the common drain connection of the ACFET2 and RBFET2, the turn-on condition is met. If ACFET2 and RBFET2 are not used, connect ACDRV2 to ground. |         | voltage becomes 5 V above the common drain connection of the ACFET2 and RBFET2, when the turn-on condition is met. If ACFET2 and RBFET2 are not used, connect ACDRV2 to                                                                                                                                                                                                                                        |

| E6     | BATN_SRP                                                                                                                                                                                                                                              | AI      | Negative input for battery voltage sensing and positive input for battery current sensing- Connect to negative terminal of battery pack. It is also used for battery current sensing. Place RSNS (2 m $\Omega$ or 5 m $\Omega$ ) between BATN_SRP and SRN_SYNCIN. Short BATN_SRP to SRN_SYNCIN together and place 100- $\Omega$ series resistance between pin and negative terminal if RSNS is not being used. |

| F6     | BATP                                                                                                                                                                                                                                                  | Al      | Positive input for battery voltage sensing - Connect to positive terminal of battery pack. Place $100-\Omega$ series resistance between pin and positive terminal.                                                                                                                                                                                                                                             |

| D1     | CDRVH                                                                                                                                                                                                                                                 | AIO     | Charge pump for gate drive - Connect a 0.22-µF cap between CDRVH and CDRVL_ADDRMS.                                                                                                                                                                                                                                                                                                                             |

| E1     | CDRVL_ADDRMS                                                                                                                                                                                                                                          | AIO     | Charge pump for gate drive - Connect a 0.22-µF cap between CDRVH and CDRVL_ADDRMS. During Power ON Reset (POR), this pin is used to assign the address of the device and the mode of the device as Standalone, Primary, or Secondary.                                                                                                                                                                          |

| A4, B4 | CFH1                                                                                                                                                                                                                                                  | Р       | Switched cap flying cap connection -Connect 1 to 3 22-µF caps in parallel between this pin and CFL1.                                                                                                                                                                                                                                                                                                           |

| C4, D4 | CFH2                                                                                                                                                                                                                                                  | Р       | Switched cap flying cap connection -Connect 1 to 3 22-µF caps in parallel between this pin and CFL2.                                                                                                                                                                                                                                                                                                           |

| A2, B2 | CFL1                                                                                                                                                                                                                                                  | Р       | Switched cap flying cap connection -Connect 1 to 3 22-µF caps in parallel between this pin and CFH1.                                                                                                                                                                                                                                                                                                           |

## 表 7-1. Pin Functions (continued)

| PIN           | TVDE(1)                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME          | TYPE                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |  |

| CFL2          | Р                                                                                              | Switched cap flying cap connection -Connect 1 to 3 22-µF caps in parallel between this pin and CFH2.                                                                                                                                                                                                                                                                         |  |

| ĪNT           | DO                                                                                             | Open drain, active low interrupt output - Pull up to voltage with 10-k $\Omega$ resistor. Normally high, the device asserts low to report status and faults. $\overline{\text{INT}}$ is pulsed low for $t_{\text{INT}}$ .                                                                                                                                                    |  |

| GND           | Р                                                                                              | Ground return                                                                                                                                                                                                                                                                                                                                                                |  |

| PMID          | Р                                                                                              | Input to the switched cap power stage -Connect 10-µF cap to PMID.                                                                                                                                                                                                                                                                                                            |  |

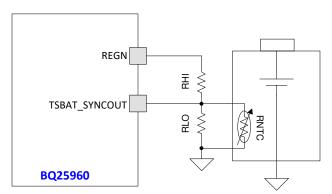

| REGN          | АО                                                                                             | harger internal LDO output - Connect a 4.7-μF cap between this pin and GND. When in rimary/Secondary Mode, connect through 1-kΩ resistor to the TSBAT_SYNCOUT and RN_SYNCIN pins. Do not use REGN for any other function.                                                                                                                                                    |  |

| SCL           | DI                                                                                             | <sup>2</sup> C interface clock - Pull up to 3.3 V with 10-kΩ resistor.                                                                                                                                                                                                                                                                                                       |  |

| SDA           | DIO                                                                                            | I <sup>2</sup> C interface data - Pull up to 3.3 V with 10-kΩ resistor.                                                                                                                                                                                                                                                                                                      |  |

| SRN_SYNCIN    | AI                                                                                             | Negative input for battery current sensing - Place RSNS ( $2 \text{ m}\Omega$ or $5 \text{ m}\Omega$ ) between SRN_SYNCIN and SRP. Short to SRP and SRN_SYNCIN together if not used. If configured as a secondary for dual charger configuration, this pin functions as SYNCIN, and connect to TSBAT_SYNCOUT of Primary, and connect a 1-k $\Omega$ pullup resistor to REGN. |  |

| TSBAT_SYNCOUT | AI                                                                                             | Battery temperature voltage input and Primary Mode SYNCOUT - Requires external resistor divider, NTC, and voltage reference. See the TSBAT section for choosing the resister divider values. If the device is in Primary Mode, connect this pin to SRN_SYNCIN of the Secondary device.                                                                                       |  |

| TSBUS         | Al                                                                                             | BUS temperature voltage input - Requires external resistor divider, NTC, and voltage reference. See the TSBUS section for choosing the resister divider values.                                                                                                                                                                                                              |  |

| VBUS          | Р                                                                                              | Device power input - Connect 1-µF capacitor from VBUS to GND.                                                                                                                                                                                                                                                                                                                |  |

| VOUT          | Р                                                                                              | Device power output - Connect 22-µF capacitor from VOUT to GND.                                                                                                                                                                                                                                                                                                              |  |

| VAC1          | Al                                                                                             | VAC1 input detection - Connected to VBUS if ACFET1 and RBFET1 are not used.                                                                                                                                                                                                                                                                                                  |  |

| VAC2          | Al                                                                                             | VAC2 input detection - Connected to VBUS if ACFET2 and RBFET2 are not used.                                                                                                                                                                                                                                                                                                  |  |

|               | NAME  CFL2  INT  GND  PMID  REGN  SCL  SDA  SRN_SYNCIN  TSBAT_SYNCOUT  TSBUS  VBUS  VOUT  VAC1 | NAME  CFL2  P  INT  DO  GND  P  PMID  P  REGN  AO  SCL  DI  SDA  DIO  SRN_SYNCIN  AI  TSBAT_SYNCOUT  AI  VBUS  P  VOUT  P  VAC1  AI                                                                                                                                                                                                                                          |  |

<sup>(1)</sup> Type: P = Power, AIO = Analog Input/Output, AI = Analog Input, DO = Digital Output, AO = Analog Output, DIO = Digital Input/Output

English Data Sheet: SLUSE08

## 8 Specifications

## 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                     |                                                               | MIN  | MAX | UNIT |

|---------------------|---------------------------------------------------------------|------|-----|------|

|                     | VAC1, VAC2 (converter not switching)                          | -2   | 40  | V    |

|                     | VBUS (converter not switching)                                | -2   | 20  | V    |

|                     | PMID (converter not switching)                                | -0.3 | 20  | V    |

|                     | ACDRV1, ACDRV2                                                | -0.3 | 30  | V    |

|                     | CFL1, CFL2                                                    | -0.3 | 7   | V    |

| Voltage             | CFH1 to VOUT, CFH2 to VOUT                                    | -0.3 | 7   | V    |

|                     | VOUT                                                          | -0.3 | 7   | V    |

|                     | BATP, BATN_SRP                                                | -0.3 | 6   | V    |

|                     | INT, SDA, SCL, CDRVL_ADDRMS, SRN_SYNCIN, TSBAT_SYNCOUT, TSBUS | -0.3 | 6   | V    |

|                     | CDRVH                                                         | -0.3 | 20  | V    |

| Output Sink Current | INT                                                           |      | 6   | mA   |

| T <sub>J</sub>      | Junction temperature                                          | -40  | 150 | °C   |

| T <sub>stg</sub>    | Storage temperature                                           | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±250  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                | MIN | NOM | MAX | UNIT |

|----------------------|--------------------------------|-----|-----|-----|------|

| VAC1, VAC2           | Input voltage at VAC1 and VAC2 |     |     | 12  | V    |

| VBUS                 | Input voltage at VBUS          |     |     | 12  | V    |

| PMID                 | Input voltage at PMID          |     |     | 12  | V    |

| PMID-CFH1, PMID-CFH2 | Voltage across QCH1, QCH2      |     |     | 6   | V    |

| CFH1-VOUT, CFH2-VOUT | Voltage across QDH1, QDH2      |     |     | 6   | V    |

| VOUT-CFL1, VOUT-CFL2 | Voltage across QCL1, QCL2      |     |     | 6   | V    |

| CFL1, CFL2           | Voltage across QDL1, QDL2      |     |     | 6   | V    |

| ICHG                 | Charging current               |     |     | 8   | Α    |

| T <sub>A</sub>       | Ambient temperature            | -40 |     | 85  | °C   |

| T <sub>J</sub>       | Junction temperature           | -40 |     | 120 | °C   |

| C <sub>CFLY</sub>    | Effective CFLY capacitance     | 6.6 | 20  |     | μF   |

| C <sub>VBUS</sub>    | Effective VBUS capacitance     | 0.2 | 1   |     | μF   |

| C <sub>PMID</sub>    | Effective PMID capacitance     | 2   | 10  |     | μF   |

### 8.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                   |                            | MIN | NOM | MAX | UNIT |

|-------------------|----------------------------|-----|-----|-----|------|

| C <sub>OUT</sub>  | Effective VOUT capacitance | 2   | 10  |     | μF   |

| C <sub>REGN</sub> | Effective REGN capacitance | 1   | 4.7 |     | μF   |

| C <sub>DRV</sub>  | Effective DRV capacitance  | 44  | 220 |     | nF   |

#### 8.4 Thermal Information

|                       |                                                                | BQ25960     |      |

|-----------------------|----------------------------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                                  | YBG (DSBGA) | UNIT |

|                       |                                                                | 36 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance (JEDEC <sup>(1)</sup> ) | 54.8        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                      | 0.2         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                           | 12          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter                     | 0.1         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter                   | 11.9        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 8.5 Electrical Characteristics

VBUS=8V, VOUT=4V,  $T_J$ = -40°C to +85°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

|                          | PARAMETER                                                          | TEST CONDITIONS                                                                        | MIN  | TYP | MAX  | UNIT |

|--------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|------|------|

| QUIESCENT CURR           | RENTS                                                              |                                                                                        |      |     |      |      |

| lo pat                   |                                                                    | ADC disabled, charge disabled,<br>VBUS, VAC1, and VAC2 not present,<br>VBAT=4V         |      | 12  | 20   | μA   |

| I <sub>Q_BAT</sub>       | Quiescent battery current                                          | ADC enabled (slowest mode), charge disabled, VBUS, VAC1, and VAC2 not present, VBAT=4V |      | 480 | 750  | μA   |

| I <sub>Q_VAC</sub>       | Quiescent VAC current                                              | ADC disabled, charge disabled,<br>ACDRV disabled, EN_HIZ=1, VAC1<br>or VAC2 =8V        |      | 90  |      | μΑ   |

|                          |                                                                    | ADC enabled, charge disabled,<br>ACDRV enabled, VAC1 or VAC2= 8V                       |      | 660 |      | μΑ   |

| INTERNAL THRES           | HOLD                                                               |                                                                                        |      |     |      |      |

| V <sub>VACUVLOZ</sub>    | VAC rising threshold for active I <sup>2</sup> C, no VOUT, no VBUS | VAC1 or VAC2 rising                                                                    | 3.24 | 3.4 | 3.6  | V    |

| V <sub>VACUVLO</sub>     | VAC falling threshold for I <sup>2</sup> C stop working            | VAC1 or VAC2 falling                                                                   | 3.05 | 3.2 | 3.4  | V    |

| V                        | VAC rising threshold to turn on ACFET-RBFET                        | VAC1 or VAC2 rising                                                                    | 3.3  | 3.4 | 3.5  | V    |

| V <sub>VACPRESENT</sub>  | VAC falling threshold to turn off ACFET-RBFET                      | VAC1 or VAC2 falling                                                                   | 3.1  | 3.2 | 3.3  | ٧    |

| V <sub>VBUSUVLOZ</sub>   | VBUS rising threshold for active I <sup>2</sup> C, no VOUT, no VAC | VBUS rising                                                                            | 3.24 | 3.4 | 3.6  | ٧    |

| V <sub>VBUSUVLO</sub>    | VBUS falling threshold for I <sup>2</sup> C stop working           | VBUS falling                                                                           | 2.65 | 2.8 | 2.95 | ٧    |

| V <sub>VBUSPRESENT</sub> | VBUS rising threshold to allow user set CHG_EN =1                  | VBUS rising                                                                            | 3.3  | 3.4 | 3.5  | ٧    |

|                          | VBUS falling                                                       | VBUS falling                                                                           | 3.1  | 3.2 | 3.3  | V    |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLUSE08

VBUS=8V, VOUT=4V,  $T_J$ = -40°C to +85°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

| PAI                                   | RAMETER                                                            | TEST CONDITIONS                                                  | MIN   | TYP   | MAX    | UNIT |

|---------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|-------|-------|--------|------|

| V <sub>VOUTUVLOZ</sub>                | VOUT rising threshold for active I <sup>2</sup> C, no VAC, no VBUS | VOUT rising                                                      | 2.48  | 2.6   | 2.72   | V    |

| Vvoutuvlo                             | VOUT falling threshold for I <sup>2</sup> C stop working           | VOUT falling                                                     | 2.25  | 2.4   | 2.55   | V    |

| V <sub>VOUTPRESENT</sub>              | VOUT rising to threshold allow user set CHG_EN =1                  | VOUT rising                                                      | 3.0   | 3.1   | 3.2    | V    |

|                                       | VOUT falling                                                       | VOUT falling                                                     | 2.9   | 3.0   | 3.1    | V    |

| RESISTANCE                            |                                                                    |                                                                  |       |       |        |      |

| R <sub>ON_BLK</sub>                   | VBUS to PMID resistance                                            | VBUS=8V                                                          |       | 6.1   | 10.5   | mΩ   |

| R <sub>ON_CH1</sub>                   | PMID to CFH1 resistance                                            | PMID=8V                                                          |       | 19.3  | 26.8   | mΩ   |

| R <sub>ON_DH1</sub>                   | CFH1 to VOUT resistance                                            | CFLY=4V                                                          |       | 11.4  | 16.8   | mΩ   |

| R <sub>ON_CL1</sub>                   | VOUT to CFL1 resistance                                            | VOUT=4V                                                          |       | 11.8  | 18     | mΩ   |

| R <sub>ON_DL1</sub>                   | CFL1 to GND resistance                                             | CFLY=4V                                                          |       | 12    | 18.3   | mΩ   |

| R <sub>ON_CH2</sub>                   | PMID to CFH2 resistance                                            | PMID=8V                                                          |       | 19.3  | 26.8   | mΩ   |

| R <sub>ON_DH2</sub>                   | CFH2 to VOUT resistance                                            | CFLY=4V                                                          |       | 11.4  | 16.8   | mΩ   |

| R <sub>ON_CL2</sub>                   | VOUT to CFL2 resistance                                            | VOUT=4V                                                          |       | 11.8  | 18     | mΩ   |

| R <sub>ON_DL2</sub>                   | CFL2 to GND resistance                                             | CFLY=4V                                                          |       | 12    | 18.3   | mΩ   |

| R <sub>VBUS_PD</sub>                  | VBUS pull down resistance                                          |                                                                  |       | 5     |        | kΩ   |

| R <sub>VAC_PD</sub>                   | VAC pull down resistance for both VAC1 and VAC2                    | VAC=10V                                                          |       | 125   |        | Ω    |

| PROTECTION AND ALAR                   | M THRESHOLD AND ACCURAC                                            | Y                                                                |       |       |        | •    |

| V <sub>BATOVP_RANGE</sub>             | Battery over-voltage range                                         |                                                                  | 3.491 |       | 4.759  | V    |

| V <sub>BATOVP_STEP</sub>              | Typical battery over-voltage step                                  |                                                                  |       | 9.985 |        | mV   |

| I <sub>BATP</sub>                     | BATP leakage current                                               |                                                                  |       |       | 1.2    | μΑ   |

| I <sub>BATN</sub>                     | BATN leakage current                                               |                                                                  |       |       | 1      | nA   |

| V <sub>BATOVP_ACC</sub>               | Battery over-voltage accuracy                                      | VBATOVP = 4.390V                                                 | 4.346 | 4.390 | 4.434  | V    |

| V <sub>OUTOVP_ACC</sub>               | VOUT over-voltage accuracy                                         | VOUTOVP= 5V                                                      | 4.9   | 5     | 5.1    | V    |

| I <sub>BATOCP_RANGE</sub>             | Battery over-current range                                         |                                                                  | 2.05  |       | 8.7125 | Α    |

| I <sub>BATOCP_STEP</sub>              | Typical battery over-current step                                  |                                                                  |       | 102.5 |        | mA   |

| I <sub>BATOCP_ACC</sub>               | Battery over-current accuracy                                      | IBATOCP=6.15A, RSNS=2m $\Omega$<br>T <sub>J</sub> = -20°C - 85°C | 5.842 | 6.15  | 6.458  | Α    |

| M                                     | VDLIC averagellana name                                            | Switched Cap Mode                                                | 7     |       | 12.75  | V    |

| V <sub>BUSOVP_RANGE</sub>             | VBUS over-voltage range                                            | Bypass Mode                                                      | 3.5   |       | 6.5    |      |

| V/                                    | T                                                                  | Switched Cap Mode                                                |       | 50    |        | mV   |

| V <sub>BUSOVP_STEP</sub>              | Typical VBUS over-voltage step                                     | Bypass Mode                                                      |       | 25    |        | mV   |

|                                       | \/DUO                                                              | VBUSOVP = 4.45V                                                  | 4.39  | 4.45  | 4.488  | V    |

| V <sub>BUSOVP_ACC</sub>               | VBUS over-voltage accuracy                                         | VBUSOVP = 9V                                                     | 8.91  | 9     | 9.09   | V    |

| V <sub>BUS_ERRHI_RISING_SC</sub>      | VBUS ERRHI rising threshold for switched cap mode stop switching   | VOUT=4V                                                          |       | 9.6   |        | ٧    |

| V <sub>BUS_ERRHI_FALLING_SC</sub>     | VBUS ERRHI falling threshold for switched cap mode start switching | VOUT=4V                                                          |       | 9.4   |        | ٧    |

| V <sub>BUS_ERRHI_RISING_BYPASS</sub>  | VBUS ERRHI rising threshold for bypass mode stop switching         | VOUT=4V                                                          |       | 4.8   |        | ٧    |

| V <sub>BUS_ERRHI_FALLING_BYPASS</sub> | VBUS ERRHI falling threshold for bypass mode start switching       | VOUT=4V                                                          |       | 4.68  |        | V    |

VBUS=8V, VOUT=4V,  $T_J$ = -40°C to +85°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

|                             | PARAMETER                                    | TEST CONDITIONS                                                      | MIN    | TYP    | MAX   | UNIT |

|-----------------------------|----------------------------------------------|----------------------------------------------------------------------|--------|--------|-------|------|

| V <sub>VACOVP_RANGE</sub>   | VAC over-voltage range                       |                                                                      | 6.5    |        | 18    | V    |

|                             |                                              | VACOVP=6.5V                                                          | 6.3    | 6.5    | 6.6   | V    |

| V <sub>VACOVP_ACC</sub>     | VAC over-voltage accuracy                    | VACOVP=10.5V                                                         | 10.2   | 10.5   | 10.7  | V    |

| _                           |                                              | VACOVP=12V                                                           | 11.7   | 12     | 12.2  | V    |

| V <sub>VACOVP_HYS</sub>     | VACOVP hysteresis                            |                                                                      |        | 3      |       | %    |

| <u> </u>                    |                                              | Switched Cap Mode                                                    | 1.0175 |        | 4.579 | Α    |

| BUSOCP_RANGE                | Input over-current range                     | Bypass Mode                                                          | 1.0475 |        | 6.809 | Α    |

|                             |                                              | Switched Cap Mode                                                    |        | 254    |       | mA   |

| BUSOCP_STEP                 | Typical input over current step              | Bypass Mode                                                          |        | 262    |       | mA   |

| I <sub>BUSOCP_ACC</sub>     | Input over current accuracy                  | IBUSOCP=3.05A, switched cap<br>mode<br>T <sub>J</sub> = -20°C - 85°C | 2.897  | 3.05   | 3.206 | А    |

|                             |                                              | IBUSOCP=3.14A, bypass mode $T_J = -20$ °C - 85°C                     | 2.983  | 3.14   | 3.297 | Α    |

| I <sub>BUSUCP_ACC</sub>     | Input under-current accuracy                 | BUSUCP=250mA, $T_J = -20$ °C - 85°C                                  | 100    | 250    | 450   | mA   |

| I <sub>BUSRCP_ACC</sub>     | Input reverse-current accuracy               | BUSRCP=300mA, T <sub>J</sub> = -20°C - 85°C                          | 150    | 300    | 450   | mA   |

| TS <sub>BUS_FLT_RANGE</sub> | TSBUS fault % of V <sub>REGN</sub> range     |                                                                      | 0      |        | 50    | %    |

| TS <sub>BUS_FLT_STEP</sub>  | TSBUS fault % of V <sub>REGN</sub> step size |                                                                      |        | 0.1953 |       | %    |

| TS <sub>BUSFLT_ACC</sub>    | TSBUS fault accuracy                         | TSBUS_FLT=20.12%                                                     | 18.5   | 20.12  | 21.5  | %    |

| TS <sub>BAT_FLT_RANGE</sub> | TSBAT fault % of V <sub>REGN</sub> range     |                                                                      | 0      |        | 50    | %    |

| TS <sub>BAT_FLT_STEP</sub>  | TSBAT fault % of V <sub>REGN</sub> step size |                                                                      |        | 0.1953 |       | %    |

| TS <sub>BAT_FLT_ACC</sub>   | TSBAT voltage accuracy                       | TSBAT_FLT=20.12%                                                     | 18.5   | 20.12  | 21.5  | %    |

| T <sub>DIE_FLT_RANGE</sub>  | TDIE over-temperature range                  |                                                                      | 80     |        | 140   | °C   |

| T <sub>DIE_FLT_STEP</sub>   | TDIE over-temperature step                   |                                                                      |        | 20     |       | °C   |

| T <sub>DIE_ALM_RANGE</sub>  | TDIE over-temperature alarm range            |                                                                      | 25     |        | 150   | °C   |

| T <sub>DIE_ALM_STEP</sub>   | TDIE over-temperature alarm step             |                                                                      |        | 0.5    |       | °C   |

| ADC MEASUREMEN              | T PERFORMANCE                                |                                                                      |        |        |       |      |

|                             |                                              | ADC_SAMPLE[1:0] = 00                                                 |        | 24     |       | ms   |

| 4                           | Conversion-time, Each                        | ADC_SAMPLE[1:0] = 01                                                 |        | 12     |       | ms   |

| <sup>L</sup> ADC_CONV       | Measurement                                  | ADC_SAMPLE[1:0] = 10                                                 |        | 6      |       | ms   |

|                             |                                              | ADC_SAMPLE[1:0] = 11                                                 |        | 3      |       | ms   |

|                             |                                              | ADC_SAMPLE[1:0] = 00                                                 | 14     | 15     |       | bit  |

| ADC <sub>RES</sub>          | Effective Resolution                         | ADC_SAMPLE[1:0] = 01                                                 | 13     | 14     |       | bit  |

|                             | Ellective Resolution                         | ADC_SAMPLE[1:0] = 10                                                 | 12     | 13     |       | bit  |

|                             |                                              | ADC_SAMPLE[1:0] = 11                                                 | 10     | 11     |       | bit  |

| ADC MEASUREMEN              | T RANGES AND ACCURACY                        |                                                                      |        |        |       |      |

| I <sub>BUSADC_RANGE</sub>   | ADC BUS current range                        |                                                                      | 0      |        | 7     | Α    |

| 1                           | ADC BUS current LSB                          | Switched Cap Mode                                                    |        | 0.9972 |       | mA   |

| IBUSADC_LSB                 | ADC BUS current LSB                          | Bypass Mode                                                          |        | 1.0279 |       | mA   |

| 1                           | ADC BUS current offset                       | Switched Cap Mode                                                    |        | 66     |       | mA   |

| BUSADC_OFFSET               | ADC BUS current offset                       | Bypass Mode                                                          |        | 64     |       | mA   |

English Data Sheet: SLUSE08

VBUS=8V, VOUT=4V,  $T_J$ = -40°C to +85°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

|                             | PARAMETER                                     | TEST CONDITIONS                                               | MIN          | TYP    | MAX          | UNIT |

|-----------------------------|-----------------------------------------------|---------------------------------------------------------------|--------------|--------|--------------|------|

| 1                           | ADC BUS current accuracy                      | IBUS=2A, ADC_SAMPLE[1:0]=00,<br>T <sub>J</sub> = -20°C - 85°C | 1.9          | 2      | 2.1          | Α    |

| IBUSADC_ACC                 | ADC BOS current accuracy                      | IBUS=3A, ADC_SAMPLE[1:0]=00,<br>T <sub>J</sub> = -20°C - 85°C | 2.85         | 3      | 3.15         | Α    |

| V <sub>BUSADC_RANGE</sub>   | ADC BUS voltage range                         |                                                               | 0            |        | 16.39        | V    |

| V <sub>BUSADC_LSB</sub>     | ADC BUS voltage LSB                           |                                                               |              | 1.002  |              | mV   |

| Vallanda naa                | ADC BUS voltage accuracy                      | VBUS=4V, ADC_SAMPLE[1:0]=00                                   | 3.96         | 4      | 4.04         | V    |

| V <sub>BUSADC_ACC</sub>     | ADC BOO voltage accuracy                      | VBUS=8V, ADC_SAMPLE[1:0]=00                                   | 7.92         | 8      | 8.08         | V    |

| V <sub>AC1ADC_RANGE</sub>   | ADC VAC1 voltage range                        |                                                               | 0            |        | 14           | V    |

| V <sub>AC1ADC_STEP</sub>    | ADC VAC1 voltage LSB                          |                                                               |              | 1.0008 |              | mV   |

| V <sub>AC1ADC_OFFSET</sub>  | ADC VAC1 voltage offset                       |                                                               |              | 3      |              | mV   |

| V <sub>AC1ADC_ACC</sub>     | ADC VAC1 voltage accuracy                     | VAC1=4V, ADC_SAMPLE[1:0]=00<br>VAC1=8V, ADC_SAMPLE[1:0]=00    | 3.96<br>7.92 | 8      | 4.04<br>8.08 | V    |

| V <sub>AC2ADC_RANGE</sub>   | ADC VAC2 voltage range                        |                                                               | 0            |        | 14           | V    |

| V <sub>AC2ADC_LSB</sub>     | ADC VAC2 voltage LSB                          |                                                               |              | 1.0006 |              | mV   |

| V <sub>AC2ADC_OFFSET</sub>  | ADC VAC2 voltage offset                       |                                                               |              | 5      |              | mV   |

| V <sub>AC2ADC_ACC</sub>     | ADC VAC2 voltage accuracy                     | VAC2=4V, ADC_SAMPLE[1:0]=00                                   | 3.96         | 4      | 4.04         | V    |

| V <sub>AC2ADC_ACC</sub>     | ADC VAC2 voltage accuracy                     | VAC2=8V, ADC_SAMPLE[1:0]=00                                   | 7.92         | 8      | 8.08         | V    |

| V <sub>BATADC_RANGE</sub>   | ADC BAT voltage range                         |                                                               | 0            |        | 6            | V    |

| V <sub>BATADC_LSB</sub>     | ADC BAT voltage LSB                           |                                                               |              | 1.017  |              | mV   |

| V <sub>BATADC_OFFSET</sub>  | ADC BAT voltage offset                        |                                                               |              | 1      |              | mV   |

| V <sub>BATADC_ACC</sub>     |                                               | VBAT=4V, ADC_SAMPLE[1:0]=00                                   | 3.96         | 4      | 4 4.04       | V    |

|                             | ADC BAT voltage accuracy                      | VBAT=4.4V, ADC_SAMPLE[1:0]=00                                 | 4.356        | 4.4    | 4.444        | V    |

| V <sub>OUTADC_RANGE</sub>   | ADC VOUT voltage range                        |                                                               | 0            |        | 6            | V    |

| V <sub>OUTADC_LSB</sub>     | ADC VOUT voltage LSB                          |                                                               |              | 1.0037 |              | mV   |

| V <sub>OUTADC_OFFSET</sub>  | ADC VOUT voltage offset                       |                                                               |              | 2      |              | mV   |

|                             | ADOMOLIT                                      | VOUT=4V, ADC_SAMPLE[1:0]=00                                   | 3.98         | 4      | 4.02         | V    |

| Voutadc_acc                 | ADC VOUT voltage accuracy                     | VOUT=4.4V, ADC_SAMPLE[1:0]=00                                 | 4.378        | 4.4    | 4.422        | V    |

| I <sub>BATADC_RANGE</sub>   | ADC battery current range                     |                                                               | -12          |        | 12           | Α    |

| I <sub>BATADC_LSB</sub>     | ADC battery current LSB                       |                                                               |              | 0.999  |              | mA   |

| I <sub>BATADC_OFFSET</sub>  | ADC battery current offset                    |                                                               |              | -150   |              | mA   |

|                             | ADC battery current accuracy                  | IBAT=4A, ADC_SAMPLE[1:0]=00, T <sub>J</sub><br>= -20°C - 85°C | 3.92         | 4.00   | 4.08         | Α    |

| BATADC_ACC_2mOhm            | through 2mOhm sense resistor                  | IBAT=6A, ADC_SAMPLE[1:0]=00, T <sub>J</sub> = -20°C - 85°C    | 5.88         | 6.00   | 6.12         | Α    |

| TS <sub>BUSADC_RANGE</sub>  | ADC TSBUS % of V <sub>REGN</sub> range        |                                                               | 0            |        | 50           | %    |

| TS <sub>BUSADC_STEP</sub>   | ADC TSBUS % of V <sub>REGN</sub> range LSB    |                                                               |              | 0.0986 |              | %    |

| TS <sub>BUSADC_OFFSET</sub> | ADC TSBUS % of V <sub>REGN</sub> range offset |                                                               |              | 0.1    |              | %    |

| TS <sub>BUSADC_ACC</sub>    | ADC TSBUS accuracy                            | TSBUS=20% of V <sub>REGN</sub> ,<br>ADC_SAMPLE[1:0]=00        | 19           | 20     | 21           | %    |

| TS <sub>BATADC_RANGE</sub>  | ADC TSBAT % of V <sub>REGN</sub> range        |                                                               | 0            |        | 50           | %    |

| TS <sub>BATADC_STEP</sub>   | ADC TSBAT % of V <sub>REGN</sub> range LSB    |                                                               |              | 0.0976 |              | %    |

| TS <sub>BATADC_OFFSET</sub> | ADC TSBAT % of V <sub>REGN</sub> range offset |                                                               |              | 0.065  |              | %    |

VBUS=8V, VOUT=4V,  $T_J$ = -40°C to +85°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

| PARAMETER                  |                                         | TEST CONDITIONS                                       | CONDITIONS MIN TYP I |        | MAX | UNIT |

|----------------------------|-----------------------------------------|-------------------------------------------------------|----------------------|--------|-----|------|

| TS <sub>BATADC_ACC</sub>   | ADC TSBAT accuracy                      | TSBAT=20% of V <sub>REGN</sub> ,<br>ADC_SAMPLE[10]=00 | 19                   | 20     | 21  | %    |

| TDIE_ADC_RANGE             | ADC TDIE range                          |                                                       | -40                  |        | 150 | °C   |

| TDIE_ADC_STEP              | ADC TDIE step                           |                                                       |                      | 0.5079 |     | °C   |

| TDIE_ADC_OFFSET            | ADC TDIE offset                         |                                                       |                      | -3.5   |     | °C   |

| REGN LDO                   |                                         |                                                       |                      |        |     |      |

| V <sub>REGN</sub>          | REGN LDO output voltage                 | V <sub>BUS</sub> =8V, I <sub>REGN</sub> =20mA         |                      | 5.0    |     | V    |

| I <sub>REGN</sub>          | REGN LDO current limit                  | V <sub>BUS</sub> =8V, V <sub>REGN</sub> =4.5V         | 40                   |        |     | mA   |

| I2C INTERFACE (SCI         | L, SDA)                                 |                                                       |                      |        |     |      |

| V <sub>IH</sub>            | Input high threshold level, SDA and SCL | Pull up rail 1.8V                                     | 1.3                  |        |     | V    |

| V <sub>IL</sub>            | Input low threshold level               | Pull up rail 1.8V                                     |                      |        | 0.4 | V    |

| V <sub>OL</sub>            | Output low threshold level              | Sink current = 5mA                                    |                      | ,      | 0.4 | V    |

| I <sub>BIAS</sub>          | High-level leakage current              | Pull up rail 1.8V                                     |                      |        | 1   | μΑ   |

| LOGIC OUTPUT PIN           | (INT, TSBAT_SYNCOUT)                    |                                                       |                      |        |     |      |

| V <sub>OL</sub>            | Output low threshold level, INT pin     | Sink current = 5mA                                    |                      |        | 0.4 | ٧    |

| I <sub>OUT</sub>           | High-level leakage current, INT pin     | Pull up rail 1.8V                                     |                      |        | 1   | μΑ   |

| LOGIC INPUT PIN (S         | RN_SYNCIN)                              |                                                       |                      |        |     |      |

| V <sub>IH_SRN_SYNCIN</sub> | Input high threshold level, SRN_SYNCIN  |                                                       | 1.3                  |        |     | V    |

| V <sub>IL_SRN_SYNCIN</sub> | Input low threshold level, SRN_SYNCIN   |                                                       |                      |        | 0.4 | ٧    |

| I <sub>IN_SRN_SYNCIN</sub> | High level leakage current              | Pull-up rail 1.8V                                     |                      |        | 1   | μΑ   |

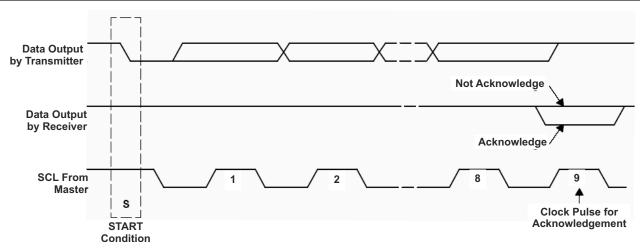

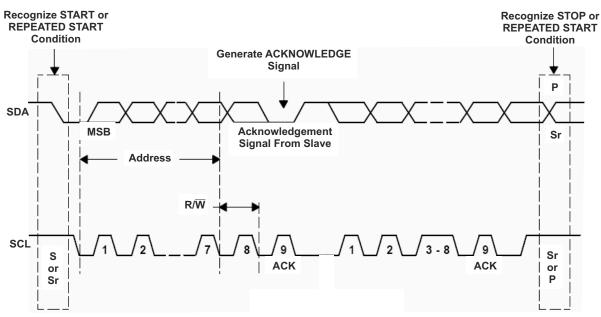

#### 8.6 Timing Requirements

| o.o i iiiiiiig ixc        | quironico                                            |     |     |      |      |

|---------------------------|------------------------------------------------------|-----|-----|------|------|

|                           |                                                      | MIN | NOM | MAX  | UNIT |

| TIMINGS                   |                                                      |     |     |      |      |

| t <sub>VACOVP</sub>       | VAC OVP response time                                |     | 100 |      | ns   |

| t <sub>BATOCP</sub>       | IBAT OCP response time                               |     | 640 |      | μs   |

| t <sub>INT</sub>          | Duration that INT is pulled low when an event occurs |     | 256 |      | μs   |

| t <sub>ALM_DEBOUNCE</sub> | Time between consecutive faults for ALM indication   |     | 120 |      | ms   |

| I2C INTERFACE             |                                                      |     |     |      |      |

| f <sub>SCL</sub>          | SCL clock frequency                                  |     |     | 1000 | kHz  |

Copyright © 2023 Texas Instruments Incorporated Product Folder Links: *BQ25960*

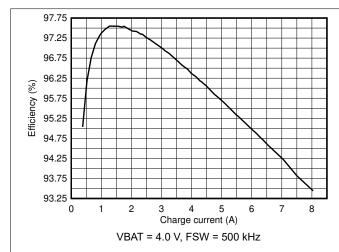

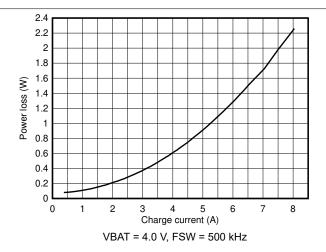

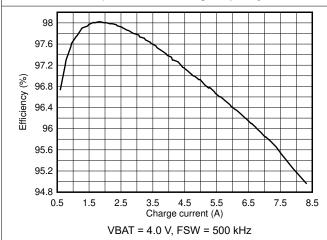

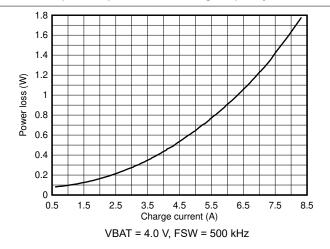

### 8.7 Typical Characteristics

Typical characteristics are taken with the BMS041 for switching test and GRM188R61C226M is used as CFLY.

図 8-1. Battery Charge Efficiency vs. Charge Current, 1 x 22-μF CFLY per Phase Switching Frequency

図 8-2. Battery Charge Power Loss vs. Charge Current, 1 x 22µF CFLY per Phase Switching Frequency

図 8-3. Battery Charge Efficiency vs. Charge Current, 2 x 22-µF CFLY per Phase

図 8-4. Battery Charge Power Loss vs. Charge Current, 2 x 22μF CFLY per Phase

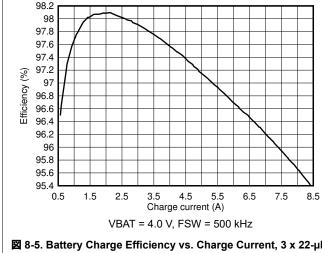

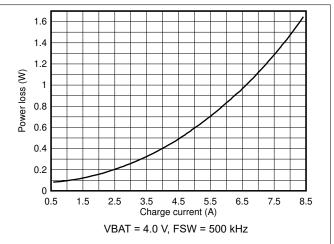

## 8.7 Typical Characteristics (continued)

Typical characteristics are taken with the BMS041 for switching test and GRM188R61C226M is used as CFLY.

図 8-5. Battery Charge Efficiency vs. Charge Current, 3 x 22-µF **CFLY** per Phase

図 8-6. Battery Charge Power Loss vs. Charge Current, 3 x 22μF CFLY per Phase

### 9 Detailed Description

#### 9.1 Overview

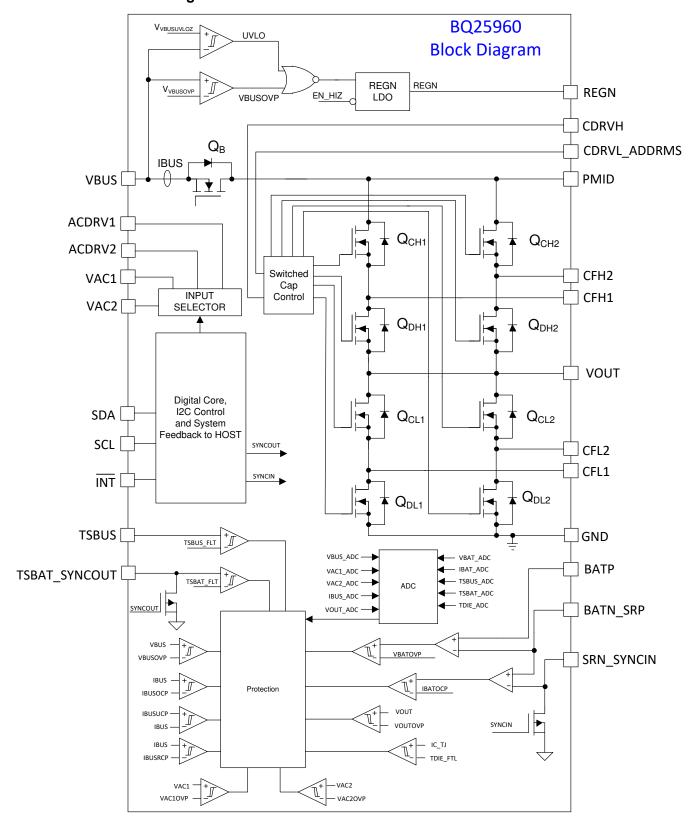

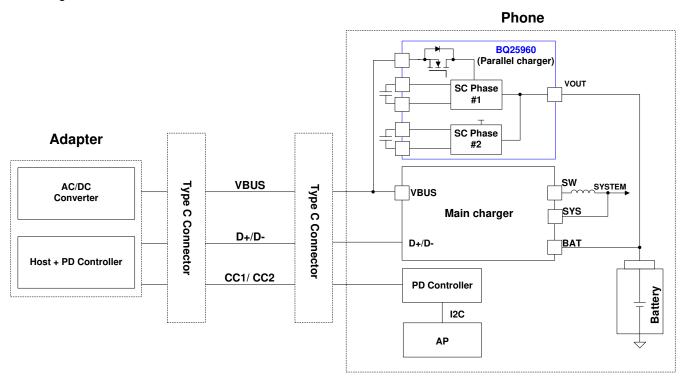

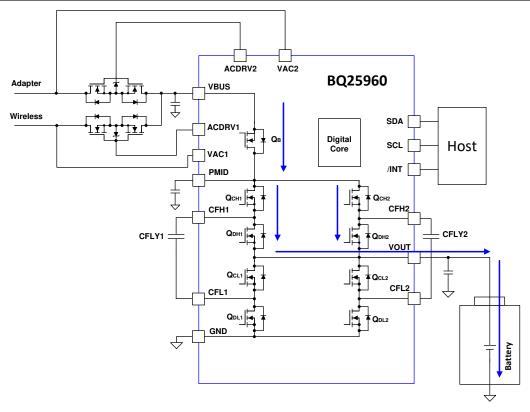

The BQ25960 is a 98.1% peak efficiency, 8-A battery charging solution using a switched cap architecture for 1-cell Li-ion battery. This architecture allows the cable current to be half the charging current, reducing the cable power loss, and limiting temperature rise. The dual-phase architecture increases charging efficiency and reduces the input and output cap requirements. When used with a main charger such as BQ2561x or BQ2589x, the system enables full charging cycle from trickle charge to termination with low power loss at Constant Current (CC) and Constant Voltage (CV) mode.

The device also operates in bypass mode charging the battery directly from VBUS through QB, QCH1 and QDH1 in parallel with QCH2 and QDH2. The impedance in bypass mode is limited to 21 m $\Omega$  for 5-A charging current.

The device supports dual input power path management which manages the power flowing from two different input sources. The inputs selection is controlled by host through I<sup>2</sup>C with default source #1 as the primary input and the source #2 as the secondary source.

The device integrates all the necessary protection features to ensure safe charging, including input overvoltage and overcurrent protection, output overvoltage and overcurrent protection, temperature sensing for the battery and cable, and monitoring the die temperature.

The device includes a 16-bit ADC to provide bus voltage, bus current, output voltage, battery voltage, battery current, input connector temperature, battery temperature, junction temperature, and other calculated measurements needed to manage the charging of the battery from the smart wall adapter or wireless input or power bank.

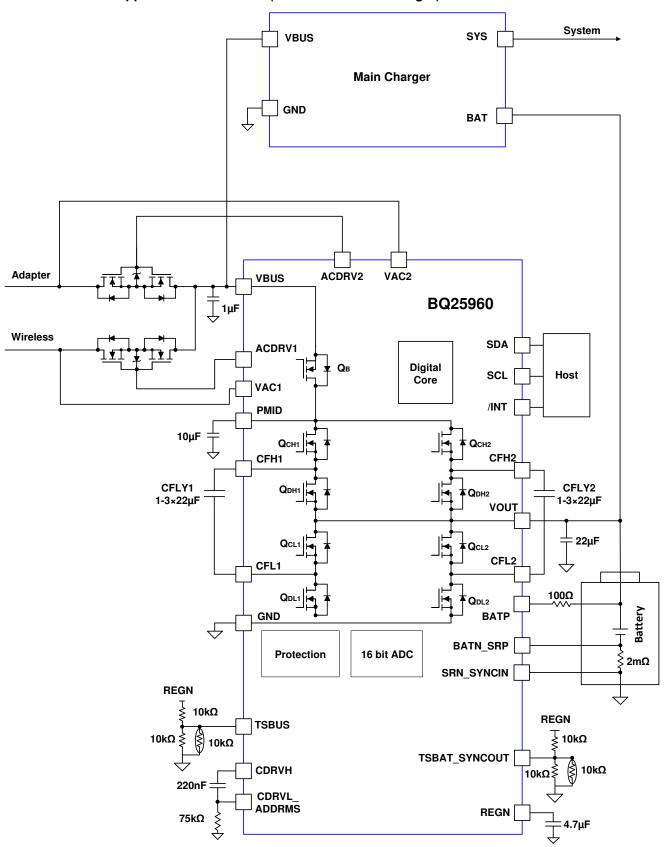

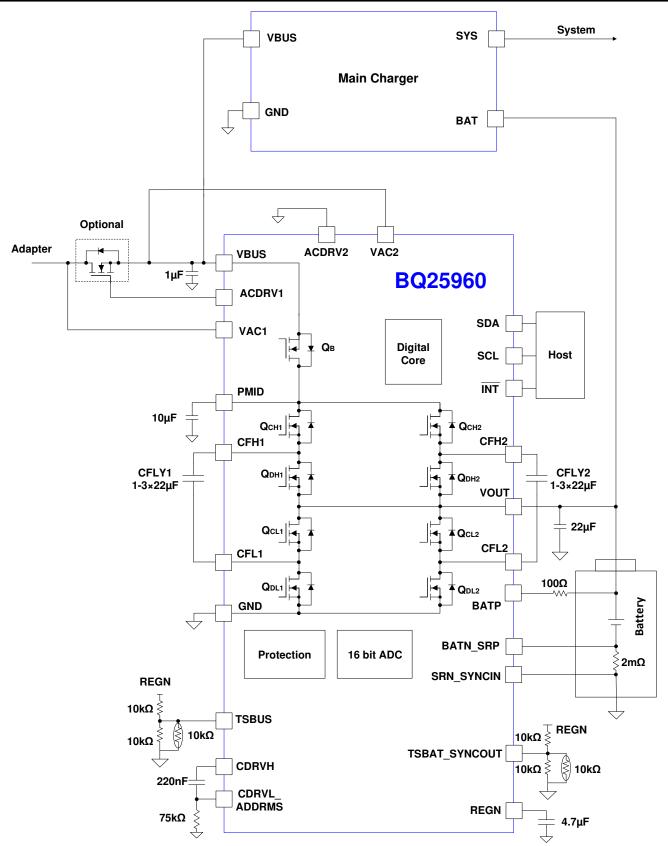

### 9.2 Functional Block Diagram

English Data Sheet: SLUSE08

#### 9.3 Feature Description

#### 9.3.1 Charging System

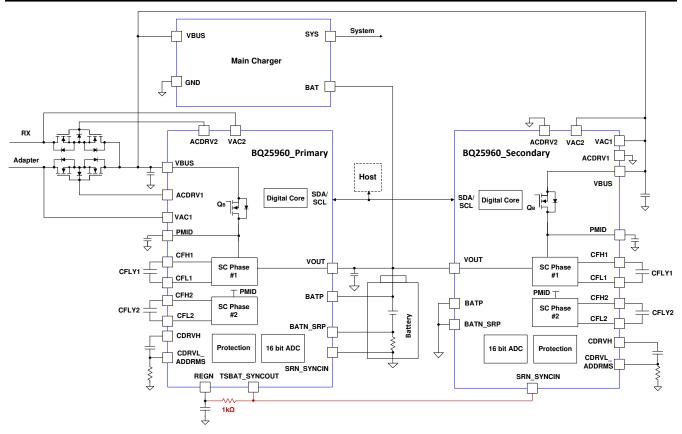

BQ25960 is a single-cell high efficiency switched cap charger, used in parallel with a switching mode charger. A host must set up the protections and alarms on BQ25960 prior to enabling the BQ25960. The host must monitor the alarms generated by BQ25960 and communicate with the smart adapter to control the current delivered to the charger.

図 9-1. BQ25960 System Diagram

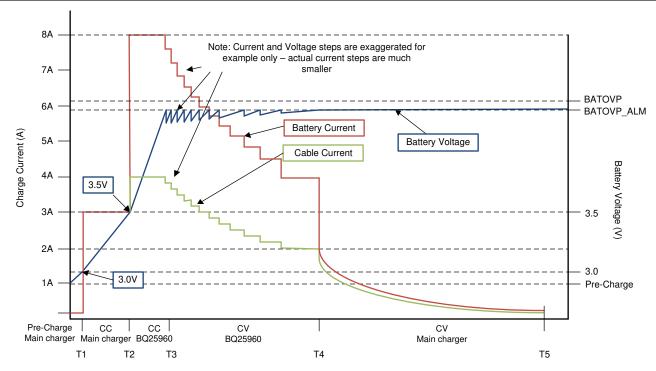

#### 9.3.2 Battery Charging Profile

The system will have a specific battery charging profile that is unique due to the switched cap architecture. The charging will be controlled by the main charger such as the BQ2561x or BQ2589x until ystem voltage reaches minimum system regulation voltage  $V_{\text{SYSMIN}}$ . Once the battery voltage reaches  $V_{\text{SYSMIN}}$  (3.5 V), the adapter can negotiate for a higher bus voltage, enable BQ25960 charging, and regulate the current on VBUS to charge the battery. In the CC phase, the protection in BQ25960 will not regulate the battery voltage, but will provide feedback to the system to increase and decrease current as needed, as well as disable the blocking and switching FETs if the voltage is exceeded. Once the CV point is reached, the BQ25960 will provide feedback to the adapter to reduce the current, effectively tapering the current until a point where the main charger takes over again. The BQ25960 can operate as long as input current is above the BUSUCP threshold.

図 9-2. BQ25960 System Charging Profile

#### 9.3.3 Device Power Up

The device is powered from the higher of VAC1 or VAC2 (with VAC1 being primary input), VBUS or VOUT (battery). The voltage must be greater than the  $V_{VACUVLOZ}$ ,  $V_{VBUSUVLOZ}$  or  $V_{VOUTUVLOZ}$  threshold to be a valid supply. When VAC1 or VAC2 rises above  $V_{VACUVLOZ}$  or VBUS rises above  $V_{VBUSUVLOZ}$  or VOUT rises above  $V_{VOUTUVLOZ}$ , I<sup>2</sup>C interface is ready for communication and all the registers are reset to default value. The host needs to wait VBUSPRESENT\_STAT and VOUTPRESENT\_STAT go high before setting CHG\_EN =1 and start charging.

#### 9.3.4 Device HIZ State

The device enters HIZ mode when EN\_HIZ bit is set to '1'. When device is in HIZ mode, the converter stops switching, ADC stops converting, ACDRV is turned off and REGN LDO is forced off even when the adapter is present and no fault condition is present. The device exits HIZ Mode when EN\_HIZ is set to '0' by host or device POR.

The faults conditions force the converter stop switching and clear CHG\_EN bit, but keep REGN on and EN\_HIZ bit = 0. More details can be found in the Device Protection section.

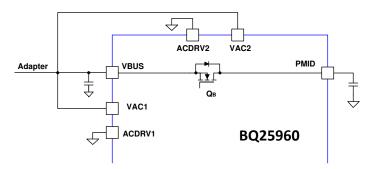

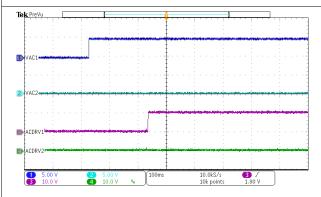

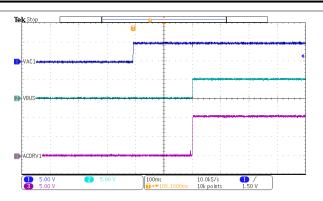

#### 9.3.5 Dual Input Bi-Directional Power Path Management

The device has two ACDRV pins to drive two sets of N-channel ACFET-RBFET, which select and manage the input power from two different input sources. In the POR sequence, the device detects if the ACFET-RBFET is populated based on if ACDRV pin is shorted to ground or not, and then updates the status register ACRB1\_CONFIG\_STAT or ACRB2\_CONFIG\_STAT to indicate the presence of ACFET-RBFET. If the external ACFET-RBFET is not populated in the schematic, then tie VAC to VBUS and connect ACDRV to GND. The device supports:

- single input without external FET

- 2. single input with one single ACFET

- dual input with one set of ACFET-RBFET

- 4. dual input with two sets of ACFET-RBFET

The power-up sequences for different applications are described in detail below.

#### 9.3.5.1 ACDRV Turn-On Condition

The ACDRV controls input power MUX for both BQ25960 and main charger. In order to turn the ACDRV, all of the following conditions must be valid:

- The corresponding AC-RB FET is populated: VAC is not short to VBUS and ACDRV is not short to ground

- 2. VAC is above V<sub>VACpresent</sub> threshold

- 3. VAC is below V<sub>VACOVP</sub> threshold

- 4. DIS\_ACDRV\_BOTH is not set to '1'

- 5. EN HIZ is not set to '1'

- 6. VBUS is below V<sub>VBUSpresent</sub> threshold

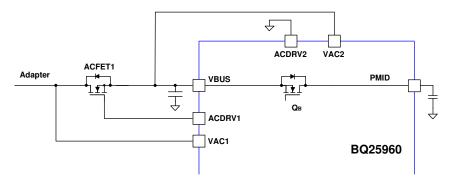

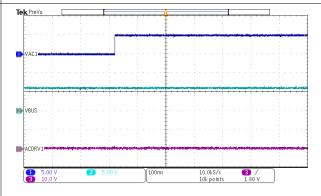

#### 9.3.5.2 Single Input from VAC to VBUS without ACFET-RBFET

In this scenario, VAC1 and VAC2 are both shorted to VBUS, ACDRV1 and ACDRV2 are pulled down to ground. The table below summarizes the VAC1/VAC2, ACDRV1/ACDRV2 connection, register control, and status functions.

| 32 3-1. Onigie input without External I E1 Cultimary |                                   |  |  |

|------------------------------------------------------|-----------------------------------|--|--|

| INPUT CONFIGURATION                                  | SINGLE INPUT                      |  |  |

| External FET connection                              | No external FET                   |  |  |

| Input pin connection                                 | VAC1 and VAC2 short to VBUS       |  |  |

| ACDRV pin connection                                 | ACDRV1 and ACDRV2 short to ground |  |  |

| ACDRV1_STAT                                          | 0                                 |  |  |

| ACDRV2_STAT                                          | 0                                 |  |  |

| DIS_ACDRV_BOTH                                       | 1                                 |  |  |

| ACRB1_CONFIG_STAT                                    | 0                                 |  |  |

| ACRB2_CONFIG_STAT                                    | 0                                 |  |  |

| EN_HIZ                                               | No impact on ACDRV                |  |  |

図 9-3. Single input without ACFET-RBFET

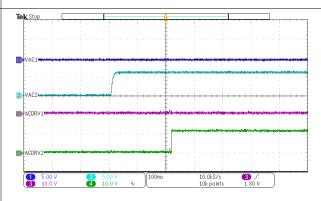

#### 9.3.5.3 Single Input with ACFET1

In this scenario, ACFET1 without RBFET1 is populated, but ACFET2-RBFET2 is not. VAC2 is short to VBUS and ACDRV2 is pulled down to ground. The table below summarizes the VAC1/ VAC2, ACDRV1/ACDRV2 connection, register control, and status functions. Use VAC1 for single input configuration.

表 9-2. Single Input with Single ACFET1

| INPUT CONFIGURATION     | SINGLE INPUT                                         |

|-------------------------|------------------------------------------------------|

| External FET connection | ACFET1, no ACFET2-RBFET2                             |

| Input pin connection    | VAC1 connected to input source<br>VAC2 short to VBUS |

| ACDRV pin connection    | ACDRV1 active<br>ACDRV2 tie to ground                |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

19

表 9-2. Single Input with Single ACFET1 (continued)

| 20 21 chilgie input that enigle / tel 21 1 (continuou) |                                                                                            |  |  |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| INPUT CONFIGURATION                                    | SINGLE INPUT                                                                               |  |  |  |

| ACDRV1_STAT                                            | 1: ACDRV1 is ON 0: ACDRV1 is OFF                                                           |  |  |  |

| ACDRV2_STAT                                            | 0                                                                                          |  |  |  |

| DIS_ACDRV_BOTH                                         | 0: Allow ACDRV1 to turn on if the conditions of ACDRV turn on are met. 1: Force ACDRV1 OFF |  |  |  |

| ACRB1_CONFIG_STAT                                      | 1                                                                                          |  |  |  |

| ACRB2_CONFIG_STAT                                      | 0                                                                                          |  |  |  |

| EN_HIZ                                                 | 0: Allow ACDRV1 to turn on if the conditions of ACDRV turn on are met. 1: Force ACDRV1 OFF |  |  |  |

図 9-4. Single Input with ACFET1

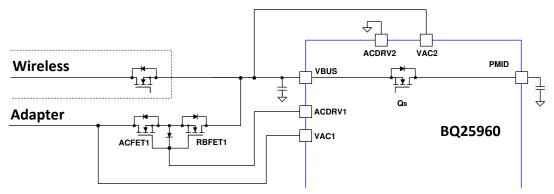

#### 9.3.5.4 Dual Input with ACFET1-RBFET1

In this scenario, ACFET1-RBFET1 is populated, but ACFET2-RBFET2 is not. VAC2 is short to VBUS and ACDRV2 is pulled down to ground. The table below summarizes the connection, register control and status functions. Use VAC1 for adapter input and VBUS for wireless input.

表 9-3. Dual Input with ACFET1-RBFET1

| INPUT CONFIGURATION     | DUAL INPUT                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------|

| External FET connection | ACFET1-RBFET1, no ACFET2-RBFET2                                                             |

| Input pin connection    | VAC1 connected to input source 1 VAC2 short to VBUS                                         |

| ACDRV pin connection    | ACDRV1 active ACDRV2 short to ground                                                        |

| ACDRV1_STAT             | 0: ACDRV1 OFF<br>1: ACDRV1 ON                                                               |

| ACDRV2_STAT             | 0                                                                                           |

| DIS_ACDRV_BOTH          | 0: Allow ACDRV1 to turn on if other conditions of ACDRV turn on are met 1: Force ACDRV1 OFF |

| ACRB1_CONFIG_STAT       | 1                                                                                           |

| ACRB2_CONFIG_STAT       | 0                                                                                           |

| EN_HIZ                  | 0: Allow ACDRV1 to turn on if other conditions of ACDRV turn on are met 1: Force ACDRV1 OFF |

Product Folder Links: BQ25960

Copyright © 2023 Texas Instruments Incorporated

図 9-5. Dual Input with ACFET-RBFET1

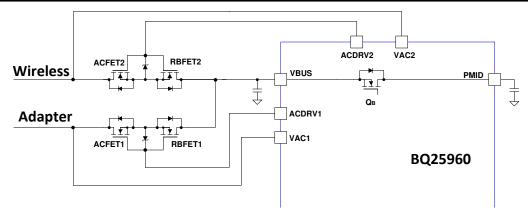

#### 9.3.5.5 Dual Input with ACFET1-RBFET1 and ACFET2-RBFET2

In this scenario, both ACFET1-RBFET1 and ACFET2-RBFET2 are populated and the device supports dual input. The table below summarizes the connection, register control and status functions. Connect input with high OVP threshold to VAC1.

表 9-4. Dual Input with Both ACFET1-RBFET1 and ACFET2-RBFET2 Summary

| INPUT CONFIGURATION     | DUAL INPUT                                                                                 |

|-------------------------|--------------------------------------------------------------------------------------------|

| External FET connection | ACFET1-RBFET1, ACFET1-RBFET2                                                               |

| Input pin connection    | VAC1 connected to input source 1                                                           |

|                         | VAC2 connected to input source 2                                                           |

|                         | No input source allowed to connect to VBUS                                                 |

| ACDRV pin connection    | ACDRV1 and ACDRV2 active                                                                   |

| ACDRV1_STAT             | 0: ACDRV1 OFF                                                                              |

|                         | 1: ACDRV1 ON                                                                               |

|                         | Once device is in dual input configuration with ACFET1-RBFET1 and ACFET2-RBFET2, the       |

|                         | host can use this bit to swap the input between VAC1 and VAC2 if both VAC1 and VAC2 are    |

|                         | valid.                                                                                     |

| ACDRV2_STAT             | 0: ACDRV2 OFF                                                                              |

|                         | 1: ACDRV2 ON                                                                               |

|                         | Once device is in dual input configuration with ACFET1-RBFET1 and ACFET2-RBFET2, the       |

|                         | host can use this bit to swap the input between VAC1 and VAC2 if both VAC1 and VAC2 are    |

|                         | valid.                                                                                     |

| DIS_ACDRV_BOTH          | 0: Allow ACDRV to turn on. By default, ACDRV1 is turned on if the conditions of ACDRV turn |

|                         | on are met, ACDRV1_STAT=1 and ACDRV2_STAT =0. In On-The-GO (OTG) or Reverse TX             |

|                         | Mode, refer to OTG and Reverse TX Mode Operation session for turn on precedence.           |

|                         | 1: Force both ACDRV to turn off, both ACDRV1_STAT and ACDRV2_STAT become 0.                |

| ACRB1_CONFIG_STAT       | 1                                                                                          |

| ACRB2_CONFIG_STAT       | 1                                                                                          |

| EN_HIZ                  | 0: Allow ACDRV to turn on for the port w/ VAC present if the conditions of ACDRV turn on   |

|                         | are met.                                                                                   |

|                         | ACDRV1 is turned on since VAC1 is the primary input source when both VAC1 and VAC2         |

|                         | present and the turn on conditions are met.                                                |

|                         | 1: Turns off both ACDRV                                                                    |

Product Folder Links: BQ25960

図 9-6. Two Inputs with ACFET-RBFET1 and ACFET-RBFET2

#### 9.3.5.6 OTG and Reverse TX Mode Operation

When the main charger is in OTG or reverse TX Mode, the input power MUX (ACFET-RBFET) also controls which port is desired for OTG output.

To enter OTG or reverse TX Mode, the host should follow the steps below:

- 1. Host writes EN OTG =1

- 2. BQ25960 sets DIS ACDRV BOTH =1

- 3. Host writes DIS\_ACDRV\_BOTH=0, and then writes ACDRV1\_STAT=1 or ACDRV2\_STAT=1 depending on which port is desired for OTG or reverse TX output