BQ25672

JAJSJN3B – DECEMBER 2020 – REVISED JULY 2023

BQ25672 デュアル入力セレクタ、ソーラー・パネル用 MPPT、ADC 内蔵、I<sup>2</sup>C 制御、 1~4 セル、3A 降圧バッテリ充電器

# 1 特長

TEXAS

INSTRUMENTS

- 1~4 セル・バッテリ向け高電力密度、高集積降圧

チャージャ

- スイッチング MOSFET (BATFET) を内蔵

- 入力および充電電流検出機能を内蔵

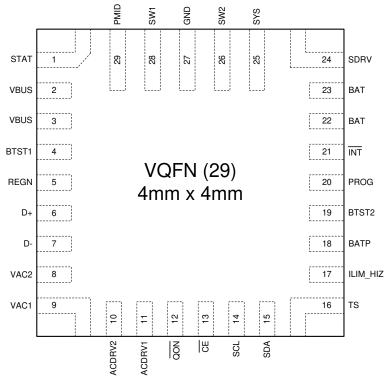

- 高効率

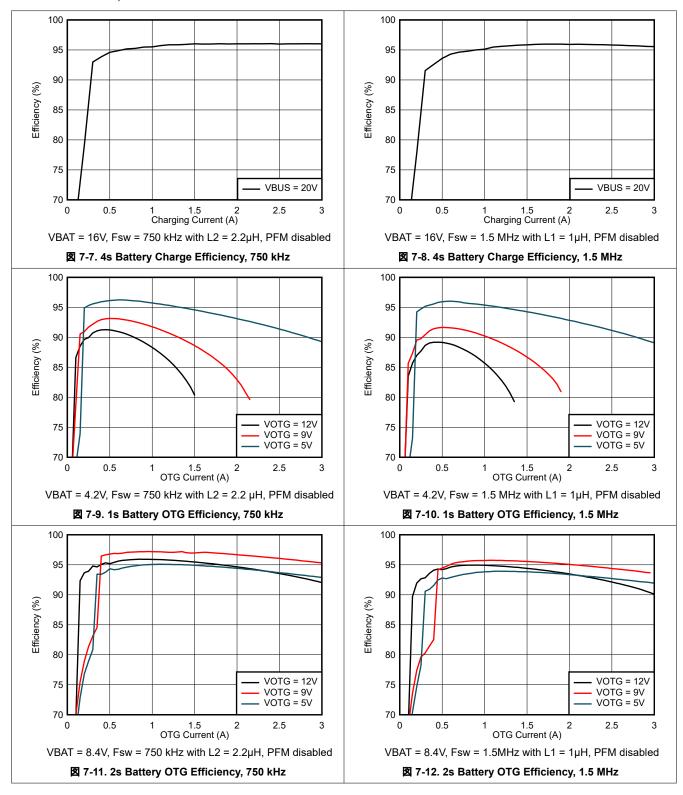

- 750kHz または 1.5MHz のスイッチング周波数

- 3A の充電電流 (分解能 10mA)

- 96.5%の効率:20V入力から3Aで16Vバ ッテリを充電する場合

- 幅広い入力電源をサポート

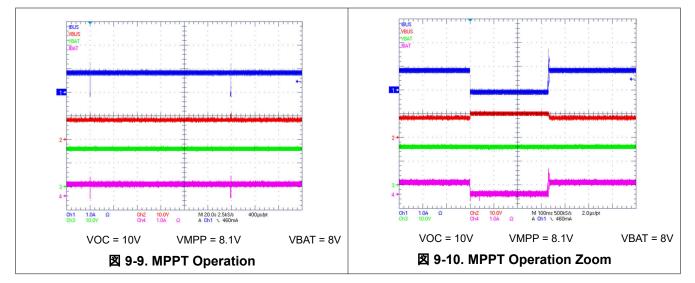

- 太陽光発電パネルから充電するための自律サン プリング型開路電圧 (V<sub>OC</sub>) 最大電力点トラッキ ング (MPPT)

- 3.6V~24Vの広い入力動作電圧範囲、30Vの絶対最大定格

- 最大 22V の入力電圧ダイナミック・パワー・マネージメント (VINDPM) と最大 3.3A の入力電流ダイナミック・パワー・マネージメント (IINDPM) に対応した最大電力トラッキング

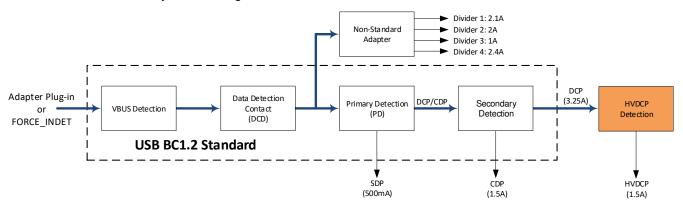

USB BC1.2、HVDCP、非標準アダプタを検出

- 電源を選択するためのデュアル入力電源マルチプ

- しつサ・コントローラ (オプション)

- Narrow VDC (NVDC) パワー・パス

- バッテリから USB ポートへの電源供給 (USB OTG)

- 5V~12VのOTG昇降圧出力電圧 (分解能 10mV)

- 最大 2A の OTG 出力電流レギュレーション (分 解能 40mA)

- 柔軟性の高い、自律および I<sup>2</sup>C モードにより最適 なシステム性能を実現

- 電圧、電流、温度を監視するための 16 ビット ADC を内蔵

- 小さいバッテリ静止電流

- 17μA (バッテリのみの動作)

- 500nA (チャージャ・シャットダウン・モード) 高い精度

- 2S バッテリで -0.25% ~ +0.65% の充電電圧レ ギュレーション

- ±5% の充電電流レギュレーション

- ±5% の入力電流レギュレーション

- 安全性

- サーマル・レギュレーションおよびサーマル・ シャットダウン

- 入力 / バッテリの OVP と OCP

- コンバータ MOSFET の OCP

- 充電安全タイマ

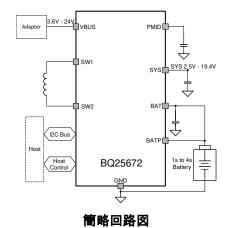

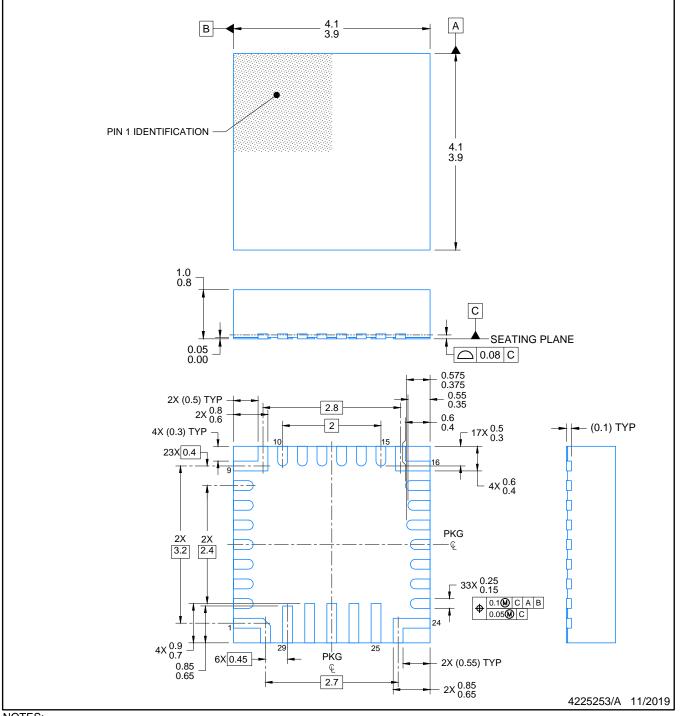

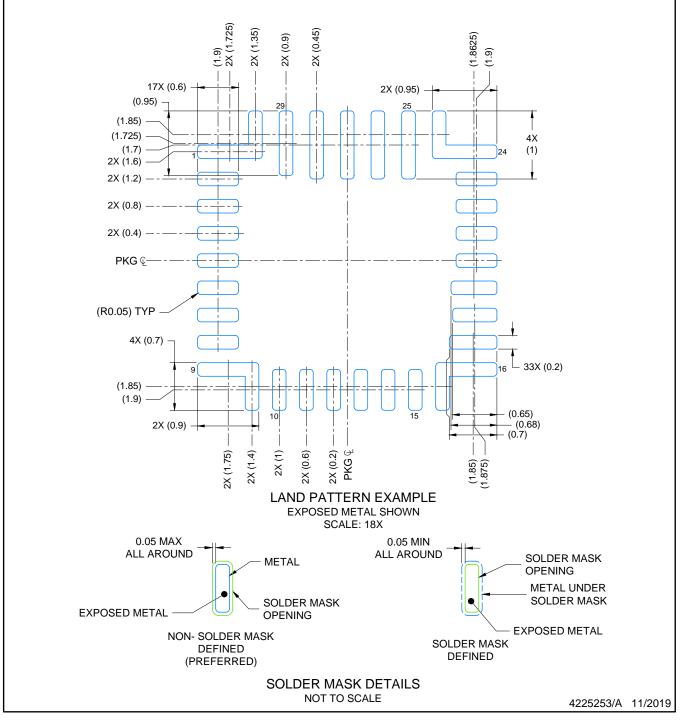

- ・ パッケージ

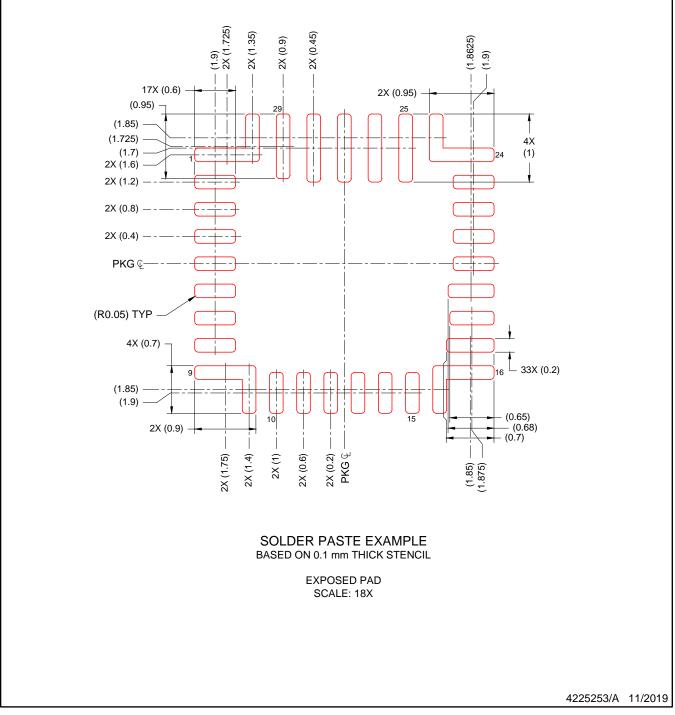

- 29 ピン、4mm × 4mm QFN

- 2 アプリケーション

- ビデオ・ドアベル、スマート・ホーム・コントロ ール

- データ・コンセントレータ、ロボット芝刈り機、 ロボット掃除機

- アセット・トラッキング、モバイル POS

- マルチパラメータ・メディカル・モニタ、心電図 (ECG)、超音波スマート・プローブ

## 3 概要

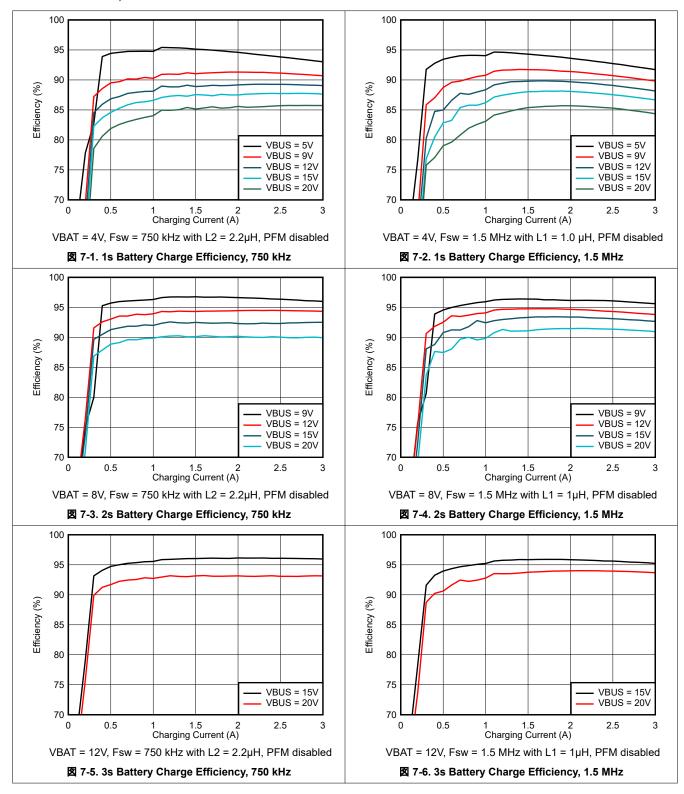

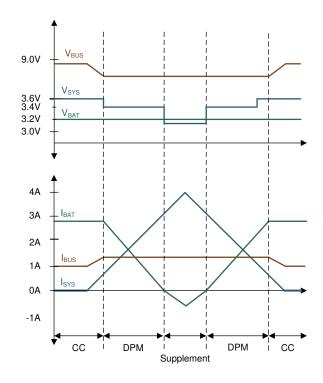

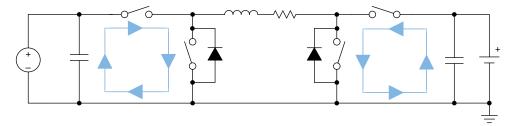

BQ25672 は、1~4 セル・リチウムイオン・バッテ リおよびリチウムポリマ・バッテリ用の完全統合型ス イッチ・モード降圧チャージャです。BQ25672 は、 OTG モードで動作している場合、VBUS 上に 5V~ 12Vの昇降圧出力電圧を生成することもできます。 つのスイッチング MOSFET、入力および充電電流検 出回路、バッテリ FET、コンバータのすべてのルー プ補償が統合されています。システム電圧が設定可能 な最小値を下回らないように、本デバイスは NVDC パワー・パス・マネージメント機能を使用して、シス テム電圧をレギュレートします。システム電圧が入力 電源定格を上回った場合、入力電源に過剰な負荷が掛 からないように、バッテリ補完モードがシステムを補 助します。 は、内蔵の V<sub>OC</sub> スケーリング MPPT アル ゴリズムを使って、太陽光発電パネルからの電力を最 大化することも行います。

デバイス情報

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |  |

|---------|----------------------|---------------|--|

| BQ25672 | QFN (29)             | 4.0mm × 4.0mm |  |

(1) 利用可能なパッケージについては、このデータシートの末尾 にある注文情報を参照してください。

↓ 英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長                                   | 1 |

|---|--------------------------------------|---|

| 2 | アプリケーション                             | 1 |

|   | 概要                                   | 1 |

| 4 | Revision History                     | 2 |

| 5 | 概要 (続き)                              | 3 |

| 6 | Pin Configuration and Functions      | 4 |

| 7 | Specifications                       | 7 |

|   | 7.1 Absolute Maximum Ratings         | 7 |

|   | 7.2 ESD Ratings                      | 7 |

|   | 7.3 Recommended Operating Conditions |   |

|   | 7.4 Thermal Information              | 8 |

|   | 7.5 Electrical Characteristics       | 8 |

|   | 7.6 Timing Requirements1             | 6 |

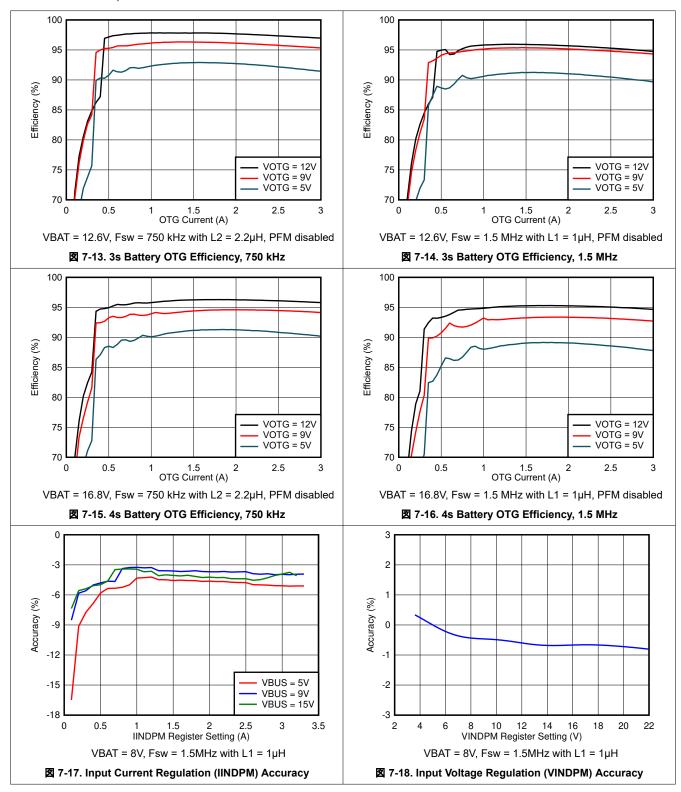

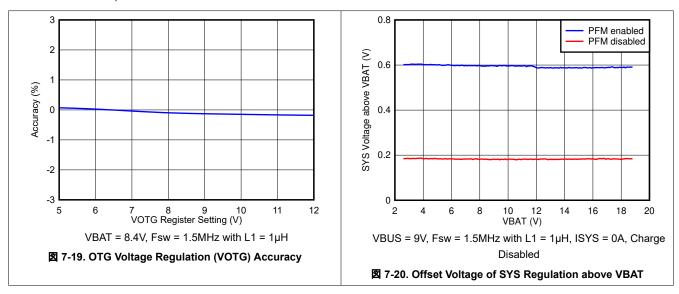

|   | 7.7 Typical Characteristics1         |   |

| 8 | Detailed Description2                |   |

|   | 8.1 Overview2                        | 2 |

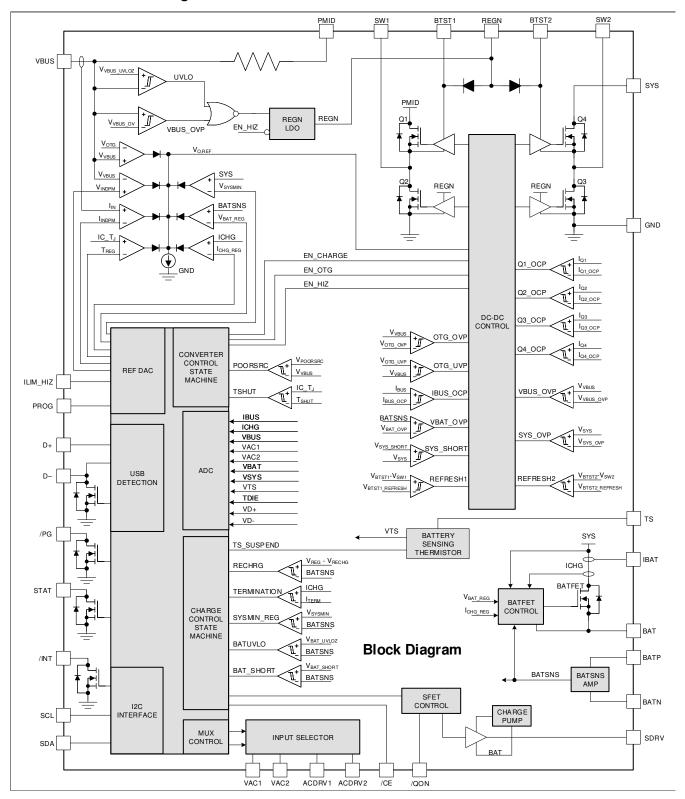

|   | 8.2 Functional Block Diagram2        | 3 |

|   | 8.3 Feature Description2             |   |

|   | 8.4 Device Functional Modes5         | 1 |

|   |                                      |   |

| 8.5 Register Map                        | 53               |

|-----------------------------------------|------------------|

| 9 Application and Implementation        |                  |

| 9.1 Application Information             | 125              |

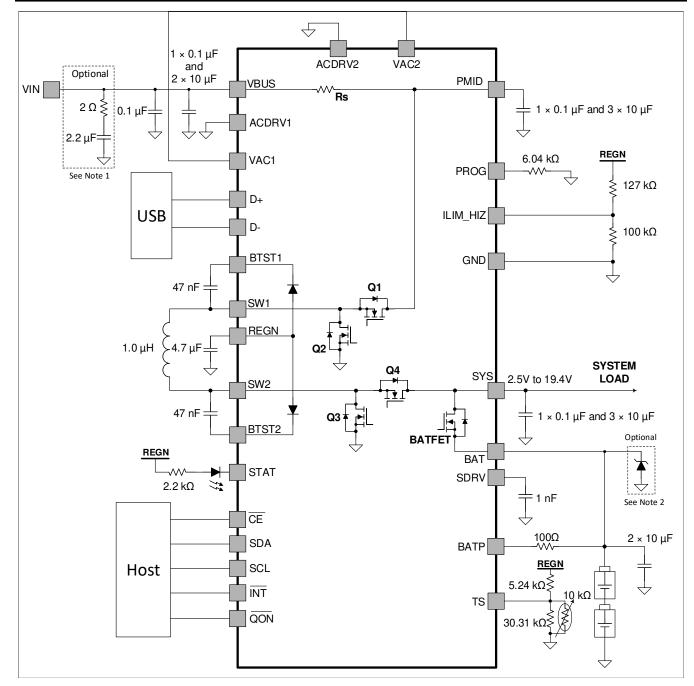

| 9.2 Typical Application                 | <mark>126</mark> |

| 10 Power Supply Recommendations         | 132              |

| 11 Layout                               | 133              |

| 11.1 Layout Guidelines                  | 133              |

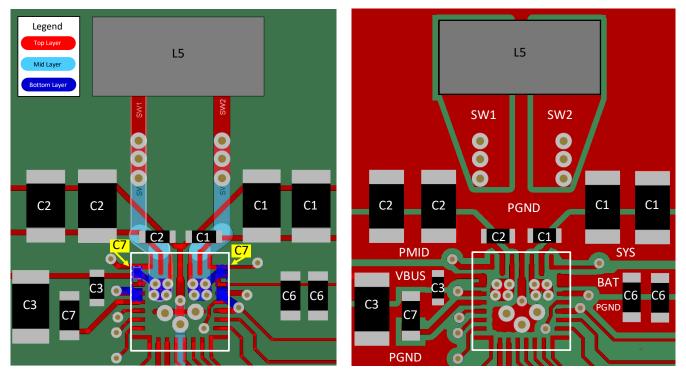

| 11.2 Layout Example                     | 134              |

| 12 Device and Documentation Support     | 135              |

| 12.1 Device Support                     | 135              |

| 12.2 Documentation Support              | 135              |

| 12.3 ドキュメントの更新通知を受け取る方法                 | 135              |

| 12.4 サポート・リソース                          | 135              |

| 12.5 Trademarks                         | 135              |

| 12.6 静電気放電に関する注意事項                      | 135              |

| 12.7 用語集                                | 135              |

| 13 Mechanical, Packaging, and Orderable |                  |

| Information                             | 136              |

|                                         |                  |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Cł | nanges from Revision A (May 2021) to Revision B (July 2023)                                              | Page |

|----|----------------------------------------------------------------------------------------------------------|------|

| •  | Corrected common drain to common source in ACDRVx pin function in $\pm 22 \pm 6$                         | 4    |

| •  | Clarified /QON pull up voltage in $222 \times 6$                                                         |      |

| •  | Deleted SDRV connected to BAT when shipFET disabled as an option in $\pm 22 \pm 6$                       | 4    |

| •  | Updated: V <sub>SYSMIN_REG_ACC</sub>                                                                     |      |

| •  | Updated V <sub>OTG_ACC</sub>                                                                             | 8    |

| •  | Changed Functional Block Diagram                                                                         |      |

| •  | Corrected default charge current to 1 A in セクション 8.3.2                                                   | 24   |

| •  | Clarified PFM peak inductor current in $272 \ge 8.3.6.4$                                                 | 33   |

| •  | Added charge current clamp during SYSMIN operation in $\pm 29 \ge 8.3.9.2$                               |      |

| •  | Clarified trickle to precharge regulation in セクション 8.3.9.2                                               |      |

| •  | Added SDRV typical output voltage and current to セクション 8.3.12                                            |      |

| •  | Updated I2C terminology in text and figures in $2723 > 8.3.14$                                           | 48   |

| •  | Corrected REG0x03 default charge current to 1A and max charge current to 3 A in $\pm 22 \approx 8.5.1$ . |      |

| •  | Changed REG0x09 bit5 from RESERVED to STOP WD CHG in セクション 8.5.1                                         | 53   |

| •  | Added REG0x10 bits5-4 in セクション 8.5.1                                                                     | 53   |

| •  | Clarified REG0x14 and REG0x33 regarding reporting IBAT discharge current in $\pm 29 \ge 8.5.1$           | 53   |

| •  | Changed REG0x2E to no longer recommend 12-bit ADC setting in セクション 8.5.1                                 |      |

| •  | Changed REG0x2E to Running average (not available for IBAT discharge) in セクション 8.5.1                     |      |

| •  | Corrected PN and DEV_REV naming in REG0x48 in セクション 8.5.1                                                |      |

| •  | Added optional input snubber/TVS to application diagrams in $\pm 29 \ge 9.2$                             |      |

|    |                                                                                                          |      |

| Changes from Revision * (December 2020) to Revision A (May 2021) |                |   |  |

|------------------------------------------------------------------|----------------|---|--|

| •                                                                | 事前情報から量産データに変更 | 1 |  |

# 5 概要 (続き)

この充電器は NVDC パワー・パス管理をサポートしています。この機能を使うと、システム電圧はバッテリ電 圧よりわずかに高い値にレギュレートされますが、最小システム電圧を下回ることはありません。バッテリが 完全に放電した場合や取り外された場合でも、システムは動作を続けられます。負荷電力が入力電源の定格を 超過すると、バッテリが補完モードに移行し、入力電源の過負荷とシステムの故障を防止します。

入力電流オプティマイザ (ICO) を使うと、未知の入力源の最大電力点を検出できます。

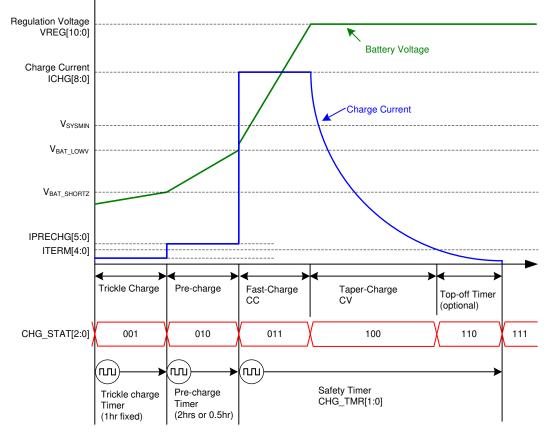

I<sup>2</sup>C ホスト制御充電モード以外に、この充電器は自律充電モードもサポートしています。電源投入後、充電はデフォルトのレジスタ設定を使って有効化されます。本デバイスは、ソフトウェアがまったく関与しなくても充電サイクルを完了できます。本デバイスは、各段階 (トリクル充電、プリチャージ、定電流 (CC) 充電、定電圧(CV) 充電) でバッテリ電圧を検出しバッテリを充電します。定電圧フェーズにおいて、充電サイクルの終わりに、充電電流があらかじめ設定された制限値 (終了電流) を下回ると、充電器は自動的に停止します。十分に充電されたバッテリが再充電スレッショルドを下回ると、充電器は自動的にまた充電サイクルを開始します。

入力電源が存在しない場合、このデバイスは、VBUS 上に 5V~12V の可変昇降圧出力電圧を 10mV 刻みで生成 するためにバッテリを放電することで USB OTG (On-the-Go) 機能に対応します。

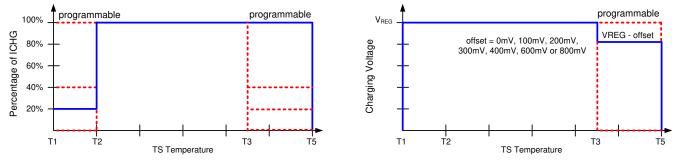

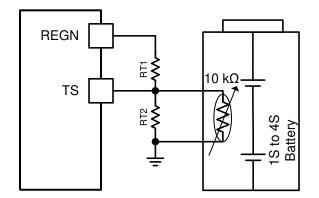

この充電器は、バッテリ温度の NTC サーミスタ監視、トリクル充電、プリチャージおよび高速充電タイマ、バ ッテリと入力の過電圧 / 過電流保護など、バッテリ充電とシステム動作のための各種安全機能を備えています。 サーマル・レギュレーションにより、接合部温度がプログラム可能なスレッショルドを超えると充電電流が低 減されます。本デバイスの STAT 出力は、充電ステータスとすべてのフォルト状態を報告します。フォルトが 発生すると、INT ピンにより即座にホストへ通知されます。

このデバイスには、充電電流と入力 / バッテリ / システム (VAC、VBUS、BAT、SYS、TS) 電圧を監視するための、16 ビットのアナログ / デジタル・コンバータ (ADC) も搭載されています。

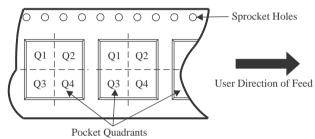

本デバイスは 29 ピンの 4mm × 4mm QFN パッケージで供給されます。

# **6** Pin Configuration and Functions

### 図 6-1. RQM Package 29-Pin VQFN Top View

#### 表 6-1. Pin Functions

| PIN   |                                                                                                                                                                                                    | /O   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME  | NO.                                                                                                                                                                                                | _ ″∪ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         |  |

| STAT  | 1                                                                                                                                                                                                  | DO   | <b>Open Drain Charge Status Output –</b> It indicates various charger operations. Connect to the pull up rail via a $10k\Omega$ resistor. LOW indicates charging in progress. HIGH indicates charging completed or charging disabled. When any fault condition occurs, STAT pin blinks at 1Hz. The STAT pin function can be disabled when DIS_STAT bit is set to 1. |  |

| VBUS  | 2-3                                                                                                                                                                                                | Р    | <b>Charger Input Voltage –</b> The power input terminal of the charger. An input current sensing circuit is connected between VBUS and PMID. The recommended capacitors at VBUS are 2 pieces of $10\mu$ F and one piece of $0.1\mu$ F ceramic capacitors. Place the $0.1\mu$ F ceramic capacitor as close as possible to the charger IC.                            |  |

| BTST1 | 4                                                                                                                                                                                                  | Р    | <b>Input High Side Power MOSFET Gate Driver Power Supply –</b> Connect a 10V or higher rating, 47nF ceramic capacitor between SW1 and BTST1 as the bootstrap capacitor for driving high side switching MOSFET (Q1).                                                                                                                                                 |  |

| REGN  | 5                                                                                                                                                                                                  | Р    | <b>The Charger Internal Linear Regulator Output –</b> It is supplied from either VBUS or BAT depended<br>on which voltage is higher. Connect a 10V, 4.7μF ceramic capacitor from REGN to power ground.<br>REGN LDO output is used for the internal MOSFETs gate driving voltage and the voltage bias for T<br>pin resistor divider.                                 |  |

| D+    | 6                                                                                                                                                                                                  | AIO  | <b>Positive Line of the USB Data Line Pair –</b> D+/D- based USB host/charging port detection for VIN1 input. The detection includes data contact detection (DCD), primary and secondary detection in BC1.2, and the adjustable high voltage adapter.                                                                                                               |  |

| D-    | 7                                                                                                                                                                                                  | AIO  | <b>Negative Line of the USB Data Line Pair –</b> D+/D- based USB host/charging port detection for VIN input. The detection includes data contact detection (DCD), primary and secondary detection in BC and the adjustable high voltage adapter.                                                                                                                    |  |

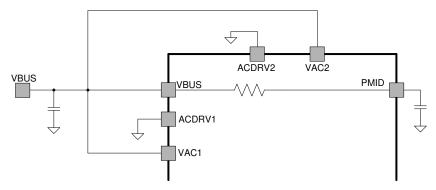

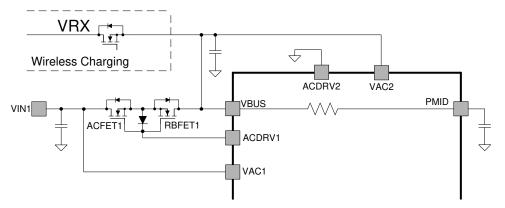

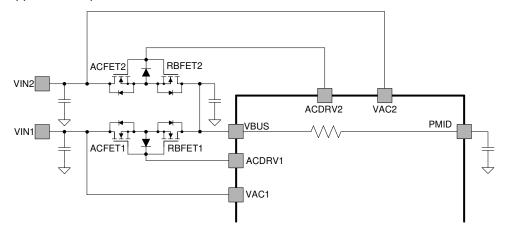

| VAC2  | 8                                                                                                                                                                                                  | Р    | <b>VAC2 Input Detection –</b> When a voltage between 3.6V and 24V is applied on VAC2, it represents a valid input being plugged into port #2. Connect to VBUS if the ACFET2 and RBFET2 are not installed.                                                                                                                                                           |  |

| VAC1  | AC1 9 P VAC1 Input Detection – When a voltage between 3.6V and 24V is applied on VAC1, it represent valid input being plugged into port #1. Connect to VBUS if the ACFET1 and RBFET1 are not insta |      |                                                                                                                                                                                                                                                                                                                                                                     |  |

#### 表 6-1. Pin Functions (continued)

| P        | 'IN   | I/O  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.   | _ "0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| ACDRV2   | 10    | Р    | <b>Input FETs Driver Pin 2</b> – The charge pump output to drive the port #2 input N-channel MOSFET (ACFET2) and the reverse blocking N-channel MOSFET (RBFET2). The charger turns on the back-to-back MOSFETs by increasing the ACDRV2 voltage 5V above the common source connection of the ACFET2 and RBFET2 when the turn-on condition is met. Tie ACDRV2 to GND if no ACFET2 and RBFET2 installed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| ACDRV1   | 11    | Р    | <b>Input FETs Driver Pin 1 –</b> The charge pump output to drive the port #1 input N-channel MOSFET (ACFET1) and the reverse blocking N-channel MOSFET (RBFET1). The charger turns on the back-to-back MOSFETs by increasing the ACDRV1 voltage 5V above the common source connection of the ACFET1 and RBFET1 when the turn-on condition is met. Tie ACDRV1 to GND if no ACFET1 and RBFET1 installed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| QON      | 12    | DI   | Ship FET Enable or System Power Reset Control Input – When the device is in ship mode or in the shutdown mode, the SDRV turns off the external ship FET to minimize the battery leakage current. A logic low on this pin with $t_{SM\_EXIT}$ duration turns on ship FET to force the device to exit the ship mode. A logic low on this pin with $t_{RST}$ duration resets system power by turning off the ship FET for $t_{RST\_SFET}$ (also setting the charger in HIZ mode when VBUS is high) and then turning on ship FET (also disabling the charger HIZ mode) to provide full system power reset. During $t_{RST\_SFET}$ when the ship FET is off, the charger applies a 30mA discharging current on SYS to discharge system voltage. The pin contains an internal pull-up through a $R_{QON}$ resistor. The typical output voltage is 3.6 V-3.8 V with VBUS and VBAT > 5V. |  |  |

| CE       | 13    | DI   | Active Low Charge Enable Pin – Battery charging is enabled when EN_CHG bit is 1 and $\overline{CE}$ pin is LOW. $\overline{CE}$ pin must be pulled HIGH or LOW, do not leave floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SCL      | 14    | DI   | I <sup>2</sup> C Interface Clock – Connect SCL to the logic rail through a 10 kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| SDA      | 15    | DIO  | I <sup>2</sup> C Interface Data – Connect SDA to the logic rail through a 10 kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TS       | 16    | AI   | <b>Temperature Qualification Voltage Input –</b> Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from REGN to TS to GND. Charge suspends when TS pin voltage is out of range. Recommend a 103AT-2 $10k\Omega$ thermistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ILIM_HIZ | 17    | AI   | <b>Input Current Limit Setting and HIZ Mode Control Pin –</b> Program ILIM_HIZ voltage by connecting<br>a resistor divider from pull up rail to ILIM_HIZ pin to ground. The pin voltage is calculated as: $V_{ILIM_HIZ}$<br>= 1V + 800m $\Omega$ × IINDPM, in which IINDPM is the target input current. The input current limit used by<br>the charger is the lower setting of ILIM_HIZ pin and the IINDPM register. When the pin voltage is below<br>0.75V, the buck converter enters non-switching mode, similar to HiZ mode using EN_HIZ bit, but with<br>REGN on. When the pin voltage is above 1V, the converter resumes switching. Connect ILIM_HIZ to<br>REGN to set the maximum input current limit.                                                                                                                                                                     |  |  |

| BATP     | 18    | Р    | <b>Positive Input for Battery Voltage Sensing –</b> Connect to the positive terminal of battery pack. Place $100\Omega$ series resistance between this pin and the battery positive terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| BTST2    | 19    | Р    | <b>Output High Side Power MOSFET Gate Driver Power Supply –</b> Connect a 10V or higher rating, 47nF ceramic capacitor between SW2 and BTST2 as the bootstrap capacitor for driving high side switching MOSFET (Q4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| PROG     | 20    | AI   | <b>Charger POR Default Settings Program –</b> At power up, the charger detects the resistance tied to PROG pin to determine the default switching frequency and the default battery charging profile. The surface mount resistor with $\pm 1\%$ or $\pm 2\%$ tolerance is recommended. Please refer to more details in the section of PROG Pin Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| INT      | 21    | DO   | <b>Open Drain Interrupt Output.</b> – Connect the $\overline{INT}$ pin to a logic rail via a 10k $\Omega$ resistor. The $\overline{INT}$ pin sends an active low, 256µs pulse to the host to report the charger device status and faults.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| BAT      | 22-23 | Р    | <b>The Battery Charging Power Connection –</b> Connect to the positive terminal of the battery pack.<br>The internal charging current sensing circuit is connected between SYS and BAT. The recommended capacitors at BAT are 2 pieces of 10µF ceramic capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| SDRV     | 24    | Р    | <b>External N-channel Ship FET (SFET) Gate Driver Output –</b> The driver pin of the external ship FET. The ship FET is always turned on when the ship mode is disabled, and it keeps off when the charger is in ship mode or shutdown mode. Connect a 1nF, 50V rated, 0402 package, ceramic capacitor from SDRV to GND when the ship FET is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SYS      | 25    | Р    | <b>The Charger Output Voltage to System –</b> The internal N-channel high side MOSFET (Q4) is connected between SYS and SW2 with drain on SYS and source on SW2. The recommended capacitors at SYS are 5 pieces of $10\mu$ F and one piece of $0.1\mu$ F ceramic capacitors. Place the $0.1\mu$ F ceramic capacitor as close as possible to the charger IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SW2      | 26    | Р    | Boost Side Half Bridge Switching Node Inductor connection to mid point of Q3 and Q4 switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

#### 表 6-1. Pin Functions (continued)

| P    | PIN |                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |

|------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | - I/O           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |

| GND  | 27  | P Ground Return |                                                                                                                                                                                                                                                                                                                                                     |  |

| SW1  | 28  | Р               | Ick Side Half Bridge Switching Node Inductor connection to mid point of Q1 and Q2 switches.                                                                                                                                                                                                                                                         |  |

| PMID | 29  | Р               | <b>Q1 MOSFET Drain Connection</b> – An internal N-channel high side MOSFET (Q1) is connected between PMID and SW1 with drain on PMID and source on SW1. The recommended capacitors at PMID are 3 pieces of $10\mu$ F and one piece of $0.1\mu$ F ceramic capacitors. Place the $0.1\mu$ F ceramic capacitor as close as possible to the charger IC. |  |

# **7** Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                       |                                                                | MIN       | MAX | UNIT |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------|-----|------|

|                                                                                       | VAC1, VAC2                                                     | -2        | 30  | V    |

|                                                                                       | VBUS (converter not switching)                                 | -2        | 30  | V    |

|                                                                                       | PMID (converter not switching)                                 | -0.3      | 30  | V    |

|                                                                                       | ACDRV1, ACDRV2, BTST1                                          | -0.3      | 32  | V    |

|                                                                                       | SYS (converter not switching)                                  | -0.3      | 23  | V    |

| Voltage range (with                                                                   | BATP, BAT                                                      | -0.3      | 20  | V    |

| Voltage range (with<br>respect to GND)<br>Output Sink Current<br>Differential Voltage | BTST2                                                          | -0.3      | 29  | V    |

|                                                                                       | SDRV                                                           | -0.3      | 26  | V    |

|                                                                                       | SW1                                                            | -2 (50ns) | 30  | V    |

|                                                                                       | SW2                                                            | -2 (50ns) | 23  | V    |

|                                                                                       | QON, D+, D-, CE, STAT, SCL, SDA, INT, ILIM_HIZ, PROG, TS, REGN | -0.3      | 6   | V    |

| Output Sink Current                                                                   | ĪNT, STAT                                                      |           | 6   | mA   |

|                                                                                       | BTST1-SW1, BTST2-SW2                                           | -0.3      | 6   | V    |

|                                                                                       | PMID-VBUS                                                      | -0.3      | 6   | V    |

| Differential voltage                                                                  | SYS-BAT                                                        | -0.3      | 16  | V    |

| Dutput Sink Current<br>Differential Voltage                                           | SDRV-BAT                                                       | -0.3      | 6   | V    |

| TJ                                                                                    | Junction temperature                                           | -40       | 150 | °C   |

| T <sub>stg</sub>                                                                      | Storage temperature                                            | -55       | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                                                                             |                                                                                          | VALUE | UNIT |

|--------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000                                                                                    |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                                     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                      | MIN | NOM MAX | UNIT |

|-------------------|--------------------------------------|-----|---------|------|

| V <sub>VBUS</sub> | Input voltage                        | 3.6 | 24      | V    |

| V <sub>BAT</sub>  | Battery voltage                      |     | 18.8    | V    |

| I <sub>VBUS</sub> | Input current                        |     | 3.3     | А    |

| I <sub>SW</sub>   | Output current (SW)                  |     | 5       | А    |

|                   | Fast charging current                |     | 3       | А    |

| I <sub>BAT</sub>  | RMS discharge current (continuously) |     | 6       | А    |

|                   | Peak discharge current (upto 1 sec)  |     | 10      | А    |

| T <sub>A</sub>    | Ambient temperature                  | -40 | 85      | °C   |

# 7.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                   |                            | MIN | NOM | MAX | UNIT |

|-------------------|----------------------------|-----|-----|-----|------|

| TJ                | Junction temperature       | -40 |     | 125 | °C   |

| C <sub>VBUS</sub> | Effective VBUS capacitance |     | 2   |     | μF   |

| C <sub>PMID</sub> | Effective PMID capacitance |     | 4   |     | μF   |

| C <sub>SYS</sub>  | Effective SYS capacitance  |     | 6   |     | μF   |

| C <sub>BAT</sub>  | Effective BAT capacitance  |     | 3   |     | μF   |

## 7.4 Thermal Information

|                               |                                              | BQ25672   |      |

|-------------------------------|----------------------------------------------|-----------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | RQM (QFN) | UNIT |

|                               |                                              | 29-PIN    |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 44.2      | °C/W |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 20.9      | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 9.7       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.5       | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 9.7       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

V<sub>VBUS UVLOZ</sub> < V<sub>VBUS</sub> < V<sub>VBUS OVP</sub>, T<sub>J</sub> = -40°C to +125°C, and T<sub>J</sub> = 25°C for typical values (unless otherwise noted)

|                        | PARAMETER                                                                                                                                 | TEST CONDITIONS                                                                                                                                                     | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| QUIESCENT C            | URRENTS                                                                                                                                   |                                                                                                                                                                     |     |     |     |      |

| I <sub>Q_BAT_ON</sub>  | Quiescent battery current (BATP,<br>BAT, SYS) when the charger is in<br>the battery only mode, battery FET<br>is enabled, ADC is disabled | VBAT = 8V, No VBUS, BATFET is<br>enabled, I2C enabled, ADC disabled, not<br>in ship mode or shut down mode, system<br>is powered by battery. $T_J < 85 \ ^{\circ}C$ |     | 17  | 24  | μΑ   |

| I <sub>Q_BAT_OFF</sub> | Quiescent battery current (BATP) for when the charger is in ship mode.                                                                    | VBAT = 8V, No VBUS, I2C enabled, ADC disabled, in ship mode, T <sub>J</sub> < 85 °C                                                                                 |     | 11  | 16  | μA   |

| I <sub>SD_BAT</sub>    | Shutdown battery current (BATP)<br>when charger is in shut down<br>mode.                                                                  | VBAT = 8V, No VBUS, I2C disabled, ADC disabled, in shut down mode, T <sub>J</sub> < 85 °C                                                                           |     | 0.5 | 0.7 | μA   |

| I <sub>Q_BAT_ON</sub>  | Quiescent battery current (BATP,<br>BAT, SYS) when the charger is in<br>the battery only mode, battery FET<br>is enabled, ADC is enabled  | VBAT = 8V, No VBUS, I2C enabled, ADC enabled, not in ship mode or shut down mode, $T_J < 85$ °C                                                                     |     | 540 |     | μΑ   |

|                        | Quiescent input current (VBUS)                                                                                                            | VBUS = 15V, VBAT = 8V, charge<br>disabled, converter switching, ISYS = 0A,<br>OOA disabled                                                                          |     | 3   |     | mA   |

| I <sub>Q_VBUS</sub>    | Quescent input current (VB03)                                                                                                             | VBUS = 15V, VBAT = 8V, charge<br>disabled, converter switching, ISYS = 0A,<br>OOA enabled                                                                           |     | 5   |     | mA   |

| 1                      | Shutdown input current (VBUS) in                                                                                                          | VBUS = 15V, HIZ mode, no battery, ADC disabled, ACDRV disabled                                                                                                      |     | 386 |     | μA   |

| ISD_VBUS               | HIZ                                                                                                                                       | VBUS = 15V, HIZ mode, no battery, ADC disabled, ACDRV enabled                                                                                                       |     | 590 |     | μA   |

V<sub>VBUS UVLOZ</sub> < V<sub>VBUS</sub> < V<sub>VBUS OVP</sub>, T<sub>J</sub> = -40°C to +125°C, and T<sub>J</sub> = 25°C for typical values (unless otherwise noted)

|                            | PARAMETER                                                     | TEST CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNIT |

|----------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

|                            | Quiescent battery current (BATP,                              | VBAT = 8V, VBUS = 5V, OTG mode<br>enabled, converter switching, I <sub>VBUS</sub> = 0A,<br>OOA disabled |      | 3    |      | mA   |

| Q_OTG                      | BAT, SYS) in OTG                                              | VBAT = 8V, VBUS = 5V, OTG mode<br>enabled, converter switching, $I_{VBUS}$ = 0A,<br>OOA enabled         |      | 5    |      | mA   |

| VBUS / VBAT SUF            | PPLY                                                          |                                                                                                         |      |      |      |      |

| V                          | VAC present rising threshold to turn on the ACFET-RBFET       | For both VAC1 and VAC2                                                                                  |      | 3.4  | 3.5  | V    |

| V <sub>VAC_PRESENT</sub>   | VAC present falling threshold to turn off the ACFET-RBFET     | For both VAC1 and VAC2                                                                                  | 3.1  | 3.2  |      | V    |

|                            | VAC overvoltage rising threshold, when VAC_OVP[1:0]=00        | For both VAC1 and VAC2                                                                                  | 25.2 | 26   | 26.8 | V    |

|                            | VAC overvoltage<br>falling threshold, when<br>VAC_OVP[1:0]=00 | For both VAC1 and VAC2                                                                                  | 24.4 | 25.2 | 26.0 | V    |

|                            | VAC overvoltage<br>rising threshold, when<br>VAC_OVP[1:0]=01  | For both VAC1 and VAC2                                                                                  | 17.4 | 18.0 | 18.6 | V    |

|                            | VAC overvoltage<br>falling threshold, when<br>VAC_OVP[1:0]=01 | For both VAC1 and VAC2                                                                                  | 16.9 | 17.5 | 18.1 | V    |

| V <sub>VAC_OVP</sub>       | VAC overvoltage<br>rising threshold, when<br>VAC_OVP[1:0]=10  | For both VAC1 and VAC2                                                                                  | 11.6 | 12   | 12.4 | V    |

|                            | VAC overvoltage<br>falling threshold, when<br>VAC_OVP[1:0]=10 | For both VAC1 and VAC2                                                                                  | 11.2 | 11.6 | 12.0 | V    |

|                            | VAC overvoltage<br>rising threshold, when<br>VAC_OVP[1:0]=11  | For both VAC1 and VAC2                                                                                  | 6.7  | 7    | 7.3  | V    |

|                            | VAC overvoltage<br>falling threshold, when<br>VAC_OVP[1:0]=11 | For both VAC1 and VAC2                                                                                  | 6.5  | 6.8  | 7.1  | V    |

| V <sub>VBUS_OP</sub>       | VBUS operating range                                          |                                                                                                         | 3.6  |      | 24   | V    |

| V <sub>VBUS_UVLOZ</sub>    | VBUS rising for active I2C, no battery                        | VBUS rising                                                                                             | 3.25 | 3.4  | 3.55 | V    |

| V <sub>VBUS_UVLO</sub>     | VBUS falling to turn off I2C, no battery                      | VBUS falling                                                                                            | 3.05 | 3.2  | 3.35 | V    |

| V <sub>VBUS_PRESENT</sub>  | VBUS to start switching                                       | VBUS rising                                                                                             | 3.3  | 3.4  | 3.5  | V    |

| V <sub>VBUS_PRESENTZ</sub> | VBUS to stop switching                                        | VBUS falling                                                                                            | 3.1  | 3.2  | 3.3  | V    |

| V <sub>VBUS_OVP</sub>      | VBUS overvoltage rising threshold                             | VBUS rising                                                                                             | 25.2 | 25.7 | 26.2 | V    |

| V <sub>VBUS_OVPZ</sub>     | VBUS overvoltage falling threshold                            | VBUS falling                                                                                            | 24.0 | 24.4 | 24.8 | V    |

| I <sub>BUS_OCP</sub>       | IBUS over-current rising threshold                            |                                                                                                         | 7.0  | 8.0  | 9.0  | А    |

| I <sub>BUS_OCPZ</sub>      | IBUS over-current falling threshold                           |                                                                                                         | 6.5  | 7.5  | 8.5  | А    |

| <b>V</b>                   | BAT voltage for active I2C, no                                | VBAT rising, with the ship FET (SFET) installed                                                         | 3.25 | 3.40 | 3.55 | V    |

| V <sub>BAT_UVLOZ</sub>     | VBUS, no VAC                                                  | VBAT rising, without the ship FET (SFET) installed                                                      | 2.50 | 2.60 | 2.71 | V    |

$V_{VBUS \_UVLOZ} < V_{VBUS \_OVP}, T_J = -40^{\circ}C$  to +125°C, and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

| VBUS_UVLOZ VV                | $BUS < V_{VBUS}_{OVP}, I J = -40 C tO I$                                                                                | $125$ C, and $1_{\rm J}$ = 25 C for typical values                            | (uniess of |        |       |      |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------|--------|-------|------|

|                              | PARAMETER                                                                                                               | TEST CONDITIONS                                                               | MIN        | TYP    | MAX   | UNIT |

| M                            | BAT voltage to turn off I2C, no                                                                                         | VBAT rising, with the ship FET (SFET) installed                               | 3.05       | 3.20   | 3.31  | V    |

| V <sub>BAT_UVLO</sub>        | VBUS, no VAC                                                                                                            | VBAT falling, without the ship FET (SFET) installed                           | 2.30       | 2.40   | 2.50  | V    |

| V <sub>BAT_OTG</sub>         | BAT voltage rising threshold to enable OTG mode                                                                         | VBAT rising                                                                   | 2.7        | 2.8    | 2.9   | V    |

| V <sub>BAT_OTGZ</sub>        | BAT voltage falling threshold to disable OTG mode                                                                       | VBAT falling                                                                  | 2.4        | 2.5    | 2.6   | V    |

| V <sub>POORSRC</sub>         | Bad adapter detection threshold                                                                                         | VBUS falling                                                                  | 3.3        | 3.4    | 3.5   | V    |

| V <sub>POORSRC</sub>         | Bad adapter detection threshold hysteresis                                                                              | VBUS rising above V <sub>POORSRC</sub>                                        | 150        | 200    | 250   | mV   |

| IPOORSRC                     | Bad adapter detection current source                                                                                    |                                                                               | 7          | 12     | 20    | mA   |

| R <sub>VBUS_PD</sub>         | VBUS pull down resistance                                                                                               |                                                                               |            | 6      |       | kΩ   |

| R <sub>VAC_PD</sub>          | VAC pull down resistance                                                                                                | For both VAC1 and VAC2                                                        |            | 60     |       | Ω    |

|                              |                                                                                                                         | VOC_PCT = 000 (0.5625), VOC = 18.0V                                           |            | 10.125 |       | V    |

|                              |                                                                                                                         | VOC_PCT = 001 (0.625), VOC = 18.0V                                            |            | 11.25  |       | V    |

|                              |                                                                                                                         | VOC_PCT = 010 (0.6875), VOC = 18.0V                                           |            | 12.375 |       | V    |

| \/                           | VINDPM as set by the MPPT                                                                                               | VOC_PCT = 011 (0.75), VOC = 18.0V                                             |            | 13.5   |       | V    |

| $V_{VINDPM_MPPT}$            | algorithm                                                                                                               | VOC_PCT = 100 (0.8125), VOC = 18.0V                                           |            | 14.625 |       | V    |

|                              |                                                                                                                         | VOC_PCT = 101 (0.875), VOC = 18.0V                                            |            | 15.75  |       | V    |

|                              |                                                                                                                         | VOC_PCT = 110 (0.9375), VOC = 18.0V                                           |            | 16.875 |       | V    |

|                              |                                                                                                                         | VOC_PCT = 111 (1.0), VOC = 18.0V                                              |            | 18.0   |       | V    |

| POWER-PATH MA                | NAGEMENT                                                                                                                |                                                                               |            |        |       |      |

| V <sub>SYSMAX_REG_RNG</sub>  | System voltage regulation range, measured on SYS                                                                        |                                                                               | 3.2        |        | 19    | V    |

|                              |                                                                                                                         | V <sub>BAT</sub> = 16.8V (4s default)                                         | 16.82      | 17.00  | 17.25 | V    |

| V                            | System voltage regulation<br>accuracy (when V <sub>BAT</sub> >V <sub>SYSMIN</sub> ,<br>charging disabled, PFM disabled) | V <sub>BAT</sub> = 12.6V (3s default)                                         | 12.62      | 12.80  | 13.04 | V    |

| V <sub>SYSMAX_REG_ACC</sub>  |                                                                                                                         | V <sub>BAT</sub> = 8.4V (2s default)                                          | 8.44       | 8.60   | 8.77  | V    |

|                              |                                                                                                                         | V <sub>BAT</sub> = 4.2V (1s default)                                          | 4.268      | 4.40   | 4.550 | V    |

| Vsysmin_reg_rng              | V <sub>SYSMIN</sub> regulation range,<br>measured on SYS                                                                |                                                                               | 2.5        |        | 16    | V    |

| V <sub>SYSMIN_REG_STEP</sub> | V <sub>SYSMIN</sub> regulation step size                                                                                |                                                                               |            | 250    |       | mV   |

|                              |                                                                                                                         | 4s battery                                                                    | 11.9       | 12.2   | 12.75 | V    |

| Va. a                        | System voltage regulation                                                                                               | 3s battery                                                                    | 9.0        | 9.2    | 9.55  | V    |

| V <sub>SYSMIN_REG_ACC</sub>  | accuracy (when V <sub>BAT</sub> <v<sub>SYSMIN)</v<sub>                                                                  | 2s battery                                                                    | 7.12       | 7.2    | 7.52  | V    |

|                              |                                                                                                                         | 1s battery                                                                    | 3.5        | 3.7    | 4.1   | V    |

|                              | VSYS overvoltage rising threshold                                                                                       | As a percentage of the system regulation voltage, to turnoff the converter.   | 105.5      | 110.0  | 112.3 | %    |

| V <sub>SYS_OVP</sub>         | VSYS overvoltage falling threshold                                                                                      | As a percentage of the system regulation voltage, to re-enable the converter. | 95.5       | 100    | 102   | %    |

| V <sub>SYS_SHORT</sub>       | VSYS short voltage falling threshold                                                                                    |                                                                               | 2.1        | 2.2    | 2.3   | V    |

| BATTERY CHARG                | ER                                                                                                                      |                                                                               |            |        |       |      |

| V <sub>REG_RANGE</sub>       | Typical charge voltage regulation range                                                                                 |                                                                               | 3          |        | 18.8  | V    |

| V <sub>REG_STEP</sub>        | Typical charge voltage step                                                                                             |                                                                               |            | 10     |       | mV   |

V<sub>VBUS UVLOZ</sub> < V<sub>VBUS</sub> < V<sub>VBUS OVP</sub>, T<sub>J</sub> = -40°C to +125°C, and T<sub>J</sub> = 25°C for typical values (unless otherwise noted)

|                            | PARAMETER                                                                      | TEST CONDITIONS                                          | MIN   | TYP  | MAX  | UNI |

|----------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|-------|------|------|-----|

|                            |                                                                                | V <sub>REG</sub> = 16.8V                                 | -0.65 |      | 0.55 | %   |

|                            | Charge voltage accuracy, T <sub>J</sub> = –<br>40°C - 85°C                     | V <sub>REG</sub> = 12.6V                                 | -0.85 |      | 0.65 | %   |

| VREG_ACC                   |                                                                                | V <sub>REG</sub> = 8.4V                                  | -0.25 |      | 0.65 | %   |

|                            |                                                                                | V <sub>REG</sub> = 4.2V                                  | -0.45 |      | 0.95 | %   |

| CHG_RANGE                  | Typical charge current regulation range                                        |                                                          | 0.05  |      | 3    | А   |

| CHG_STEP                   | Typical charge current regulation step                                         |                                                          |       | 10   |      | mA  |

|                            | Typical buck mode PWM charge                                                   | ICHG = 2A; VBAT=8V                                       | -6.5  |      | 3.5  | %   |

| I <sub>CHG_ACC</sub>       | current accuracy, VBUS > VBAT,                                                 | ICHG = 1A; VBAT=8V                                       | -5    |      | 5    | %   |

|                            | $T_{\rm J} = -40^{\circ}{\rm C} - 85^{\circ}{\rm C}$                           | ICHG = 0.5A; VBAT=8V                                     | -7.5  |      | 7.5  | %   |

| IPRECHG_RANGE              | Typical pre-charge current range                                               |                                                          | 40    |      | 2000 | mA  |

| IPRECHG_STEP               | Typical pre-charge current step                                                |                                                          |       | 40   |      | mA  |

|                            | Turical LDO made charge surrent                                                | IPRECHG = 1000mA, VBAT = 6.5V                            | -4.5  |      | 3.5  | %   |

|                            | Typical LDO mode charge current accuracy when V <sub>BATP</sub> below          | IPRECHG = 480mA, VBAT = 6.5V                             | -8    |      | 8    | %   |

| PRECHG_ACC                 | $V_{BAT\_LOWV}$ , VBUS > VBAT, $T_J = -$                                       | IPRECHG = 200mA, VBAT = 6.5V                             | -20   |      | 20   | %   |

|                            | 40°C - 85°C                                                                    | IPRECHG = 120mA, VBAT = 6.5V                             | -30   |      | 30   | %   |

| I <sub>TERM_RANGE</sub>    | Typical termination current range                                              |                                                          | 40    |      | 1000 | mA  |

| I <sub>TERM_STEP</sub>     | Typical termination current step                                               |                                                          |       | 40   |      | mA  |

|                            | Termination current accuracy, $T_1 =$                                          | ITERM = 120mA, ICHG < 1000mA                             | -20   |      | 20   | %   |

| TERM_ACC                   | –40°C - 85°C                                                                   | ITERM = 480mA, ICHG > 1000mA                             | -14   |      | 14   | %   |

| V <sub>BAT_SHORTZ</sub>    | Battery short voltage rising threshold to start pre-charge                     | VBAT rising                                              |       | 2.25 |      | V   |

| V <sub>BAT_SHORT</sub>     | Battery short voltage falling threshold to stop pre-charge                     | VBAT falling                                             |       | 2.06 |      | v   |

| I <sub>BAT_SHORT</sub>     | Battery short trickle charging current                                         | VBAT < V <sub>BAT_SHORTZ</sub>                           |       | 100  |      | mA  |

|                            |                                                                                | VBAT_LOWV_1:0=00                                         | 13    | 15   | 17   | %   |

| N7                         | Battery voltage rising threshold to                                            | VBAT_LOWV_1:0=01                                         | 61.5  | 63.0 | 64.5 | %   |

| V <sub>BAT_LOWV_RISE</sub> | start fast-charge, as percentage of V <sub>REG</sub>                           | VBAT_LOWV_1:0=10                                         | 67.0  | 68.0 | 69.0 | %   |

|                            |                                                                                | VBAT_LOWV_1:0=11                                         | 71.0  | 72.5 | 74.0 | %   |

| V <sub>BAT_LOWV_HYS</sub>  | Battery voltage threshold<br>hysteresis to stop fast-charge on<br>falling edge | VBAT falling, as percentage of<br>VREG, VBAT_LOWV_1:0=11 |       | 1.4  |      | %   |

| N/                         | Detter / recharge threshold                                                    | VBAT falling, VRECHG=0011,<br>VREG=8.4V                  |       | 200  |      | mV  |

| V <sub>RECHG</sub>         | Battery recharge threshold                                                     | VBAT falling, VRECHG=0111,<br>VREG=16.8V                 |       | 400  |      | mν  |

| I <sub>BAT_LOAD</sub>      | Battery discharge load current                                                 |                                                          |       | 30   |      | mA  |

| SYS_LOAD                   | System discharge load current                                                  |                                                          |       | 30   |      | mA  |

| R <sub>BATP</sub>          | BATP Input Resistance                                                          |                                                          |       | 2.5  |      | MΩ  |

| BATFET                     |                                                                                |                                                          |       |      |      |     |

| R <sub>BATFET</sub>        | MOSFET on resistance from SYS to BAT                                           |                                                          |       | 11   |      | mΩ  |

| BATTERY PROTE              | CTIONS                                                                         |                                                          |       |      |      |     |

|                            |                                                                                | VBAT rising, as percentage of VREG                       | 103   | 104  | 105  | %   |

| V <sub>BAT_OVP</sub>       | Battery overvoltage threshold                                                  | VBAT falling, as percentage of VREG                      | 101   | 102  | 103  | %   |

| V <sub>VBUS UVLOZ</sub> < V <sub>VBUS</sub> < V <sub>VBUS</sub> OVP, T <sub>J</sub> = -40°C to +125°C, and T <sub>J</sub> = 25°C for typical values (unless otherwise noted) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | PARAMETER                                                 | TEST CONDITIONS                                                          | MIN   | TYP  | MAX  | UNI |

|------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------|-------|------|------|-----|

| M                            | Battery short voltage                                     | VBAT falling, to clamp the charging current as trickle charging current. |       | 2.06 |      | V   |

| V <sub>BAT_SHORT</sub>       | Dattery short voltage                                     | VBAT rising, to release the trickle charging current clamp               |       | 2.25 |      | V   |

| I <sub>BAT_OCP</sub>         | Battery discharging over-current rising threshold         |                                                                          | 9.3   |      |      | A   |

| INPUT VOLTAGE                | E / CURRENT REGULATION                                    |                                                                          |       |      |      |     |

| VINDPM_RANGE                 | Typical input voltage regulation range                    |                                                                          | 3.6   |      | 22   | V   |

| V <sub>INDPM_STEP</sub>      | Typical input voltage regulation step                     |                                                                          |       | 100  |      | m∖  |

|                              |                                                           | VINDPM=18.6V                                                             | -2    |      | 2    | %   |

| VINDPM_ACC                   | Input voltage regulation accuracy                         | VINDPM=10.6V                                                             | -3    |      | 3    | %   |

|                              |                                                           | VINDPM=4.3V                                                              | -5    |      | 5    | %   |

| IINDPM_RANGE                 | Typical input current regulation range                    |                                                                          | 0.1   |      | 3.3  | А   |

| IINDPM_STEP                  | Typical input current regulation step                     |                                                                          |       | 10   |      | m/  |

|                              |                                                           | IINDPM = 500mA, VBUS=9V, T <sub>J</sub> > -20°C                          | 415   | 460  | 500  | m/  |

|                              |                                                           | IINDPM = 1000mA,<br>VBUS=9V, T <sub>J</sub> > -20°C                      | 880   | 940  | 1000 | m/  |

| I <sub>INDPM_ACC</sub>       | Input current regulation accuracy                         | IINDPM = 2000mA,<br>VBUS=9V, T <sub>J</sub> > -20°C                      | 1800  | 1880 | 1960 | m   |

|                              |                                                           | IINDPM = 3000mA,<br>VBUS=9V, T <sub>J</sub> > -20°C                      | 2720  | 2820 | 2920 | m/  |

| VILIM_REG_RNG                | Voltage range for input current regultion at ILIM_HIZ pin |                                                                          | 1     |      | 4    | V   |

| I <sub>LEAK_ILIM</sub>       | ILIM_HIZ pin leakage current                              | V <sub>ILIM_HIZ</sub> = 4V                                               | -1.5  |      | 1.5  | μA  |

| D+ / D- DETECT               | ION                                                       | 1                                                                        |       |      |      |     |

| V <sub>D+ 600MVSRC</sub>     | D+ voltage source (600 mV)                                |                                                                          | 500   | 600  | 700  | m\  |

| I <sub>D+_10UASRC</sub>      | D+ current source (10 µA)                                 | V <sub>D+</sub> = 200 mV,                                                | 7     | 10   | 14   | μA  |

| <br>I <sub>D+_100UASNK</sub> | D+ current sink (100 µA)                                  | V <sub>D+</sub> = 500 mV,                                                | 50    | 90   | 150  | μA  |

| V <sub>D+_0P325</sub>        | D+ comparator threshold for<br>Secondary Detection        | D+ pin rising                                                            | 250   |      | 400  | m١  |

| V <sub>D+_0P8</sub>          | D+ comparator threshold for Data<br>Contact Detection     | D+ pin rising                                                            | 775   | 850  | 925  | m١  |

| I <sub>D+ LKG</sub>          | Leakage current into D+                                   | HIZ mode                                                                 | -1    |      | 1    | μA  |

| V <sub>D600MVSRC</sub>       | D- voltage source (600 mV)                                |                                                                          | 500   | 600  | 700  | m\  |

| ID- 100UASNK                 | D- current sink (100 µA)                                  | V <sub>D-</sub> = 500 mV,                                                | 50    | 90   | 150  | μA  |

| V <sub>D0P325</sub>          | D- comparator threshold for<br>Primary Detection          | D- pin Rising                                                            | 250   |      | 400  | m   |

| I <sub>DLKG</sub>            | Leakage current into D-                                   | HIZ mode                                                                 | -1    |      | 1    | μA  |

| R <sub>D19K</sub>            | D- resistor to ground (19 kΩ)                             | V <sub>D-</sub> = 500mV                                                  | 14.25 |      | 24.8 | kΩ  |

| V <sub>D+_2p8</sub>          | D+ comparator threshold for non-<br>standard adapter      | (combined $V_{D+_{2p8}hi}$ and $V_{D+_{2p8}lo}$ )                        | 2.55  |      | 2.85 | V   |

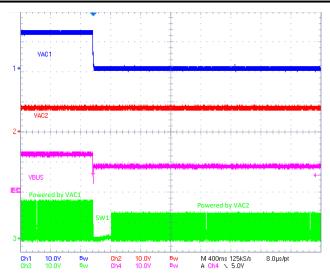

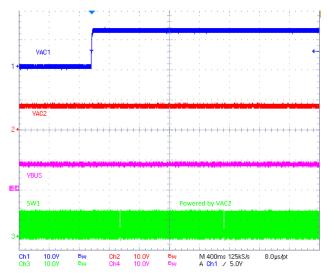

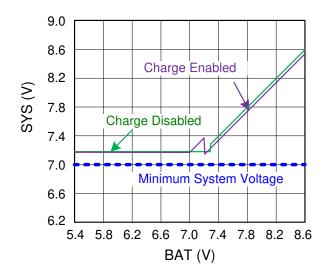

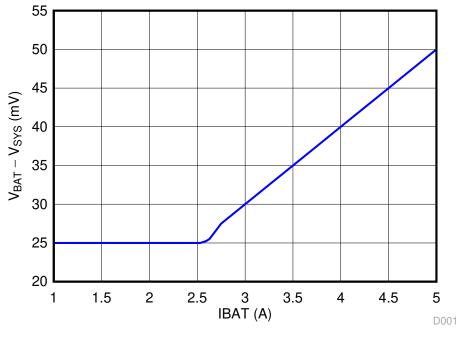

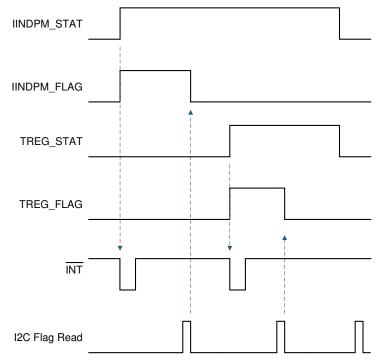

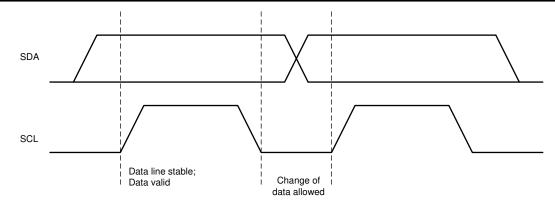

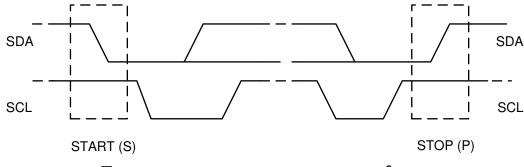

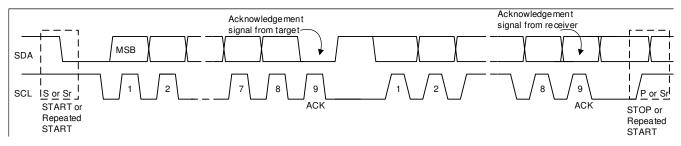

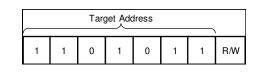

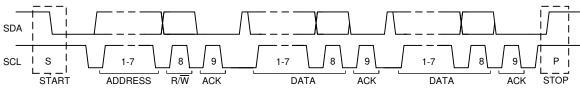

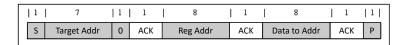

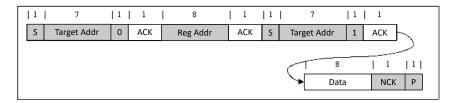

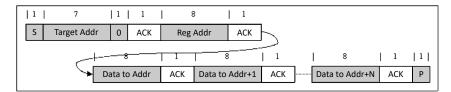

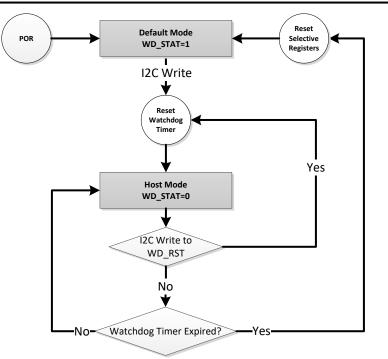

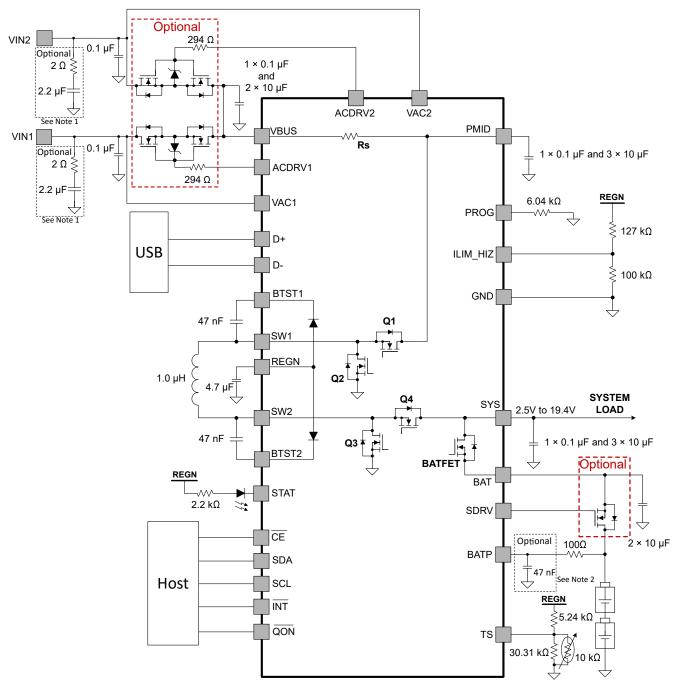

| V <sub>D2p8</sub>            | D- comparator threshold for non-<br>standard adapter      | (combined VD2p8_hi and VD2p8_lo)                                         | 2.55  |      | 2.85 | V   |