# ワンチップ充電/システム・パワーパス・マネージメントIC(bqTINY™-III)

## 特長

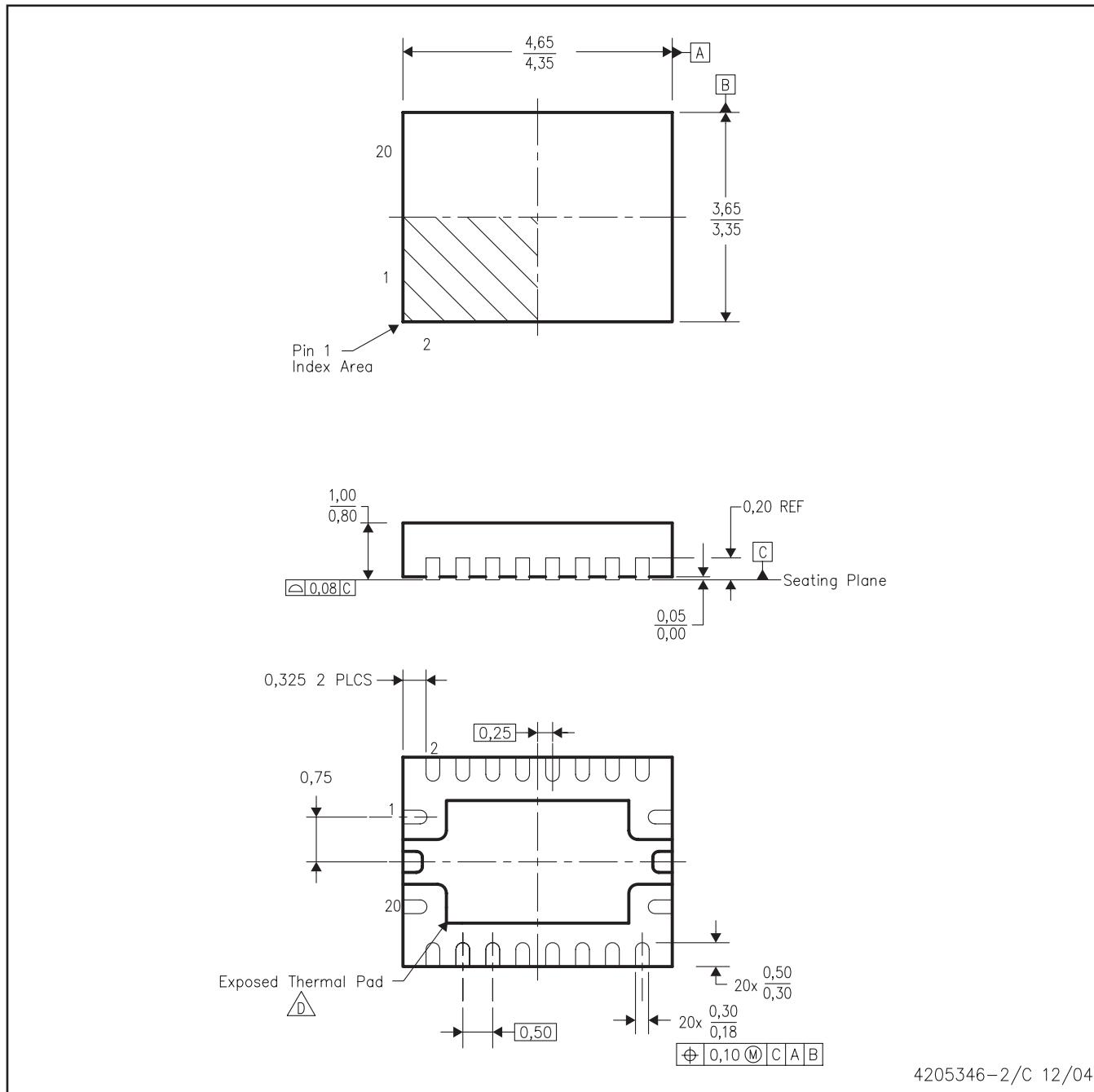

- 小型QFNパッケージ (3.5mm x 4.5mm)

- 1セルのリチウム・イオンまたはリチウム・ポリマー・バッテリーを使った携帯機器に最適

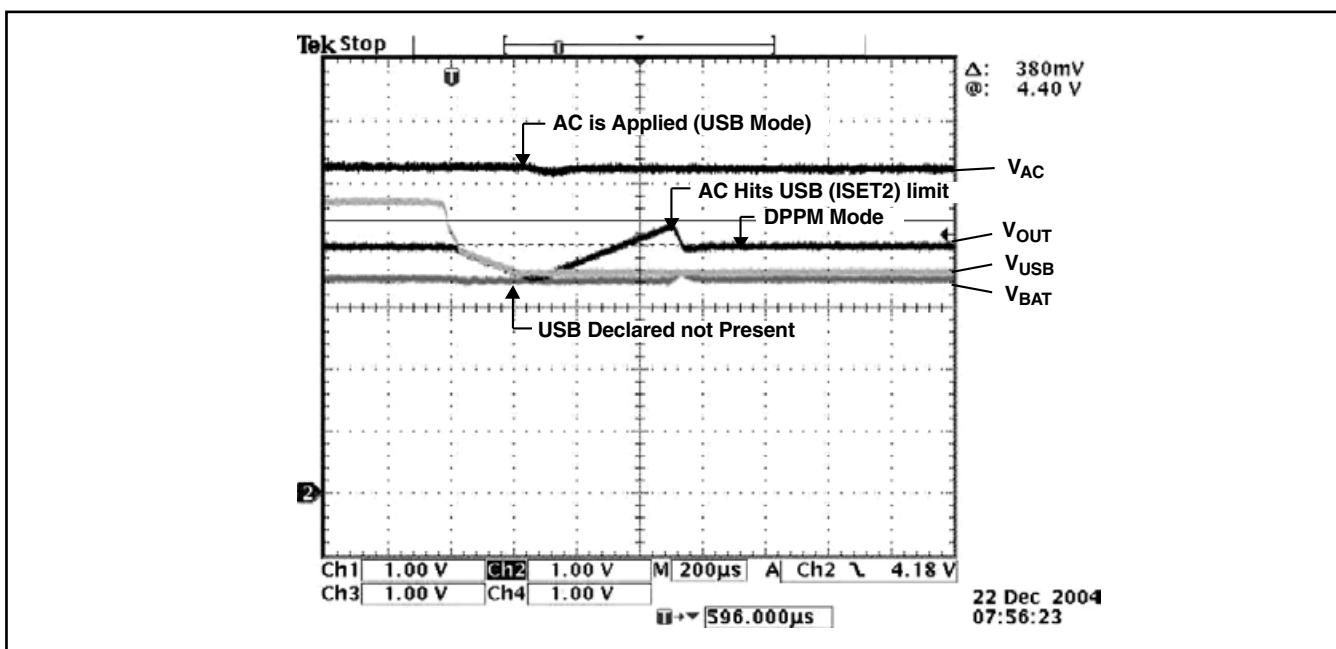

- ダイナミック・パワーパス・マネージメント(DPPM)機能によりACアダプタまたはUSBポートから同時にシステムへの電源供給とバッテリーの充電が可能

- パワー・サブルメント・モードによりバッテリーがUSBまたはACの電力不足時システムへ電力を補完

- 自動電源選択機能 (ACアダプタまたはUSB)

- USBを電源としたとき電流制限を100mA/500mAから選択可能

- トータル電流最大2Aまで対応

- 3.3V出力のLDOを内蔵

- 充電時コントロール用サーマル・レギュレーション機能

- 充電/異常状態を報告するLEDまたはシステム・インターフェイス用充電ステータス出力

- 逆電流防止、短絡保護、サーマルシャットダウン機能

- パワーグッド (ACアダプタ/USBポートあり) ステータス出力

● 充電電圧のオプション: 4.2Vまたは4.36V

## アプリケーション

- スマートフォン、PDA

- MP3プレーヤー

- デジタル・カメラ、携帯機器

- インターネット・アプライアンス

## 概要

bqTINY™-IIIシリーズは、小型化が要求される携帯機器を対象としたリチウム・イオンのリニア方式チャージャとシステム・パワーパス・マネージメント機能を集積したデバイスです。bqTINY-IIIシリーズは、USBポート/ACアダプタの電源を自動的に選択をするパワーパス・マネージメント、パワーFET/電流センサ、高精度の電流/電圧レギュレーション、充電ステータス出力、充電終了検出の機能をワンチップに内蔵しています。

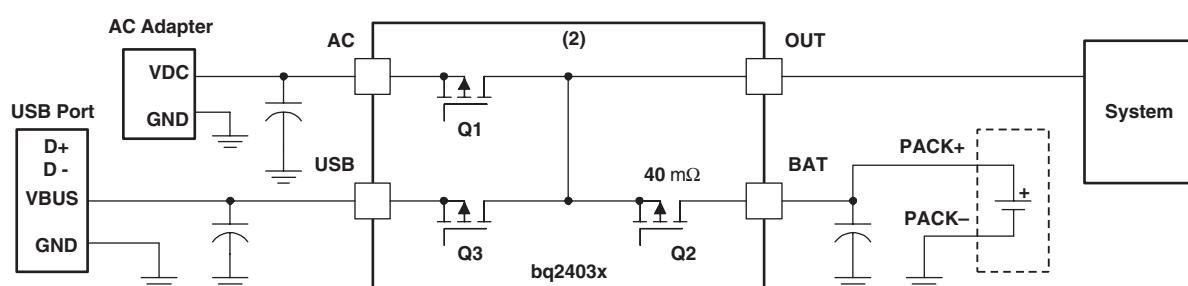

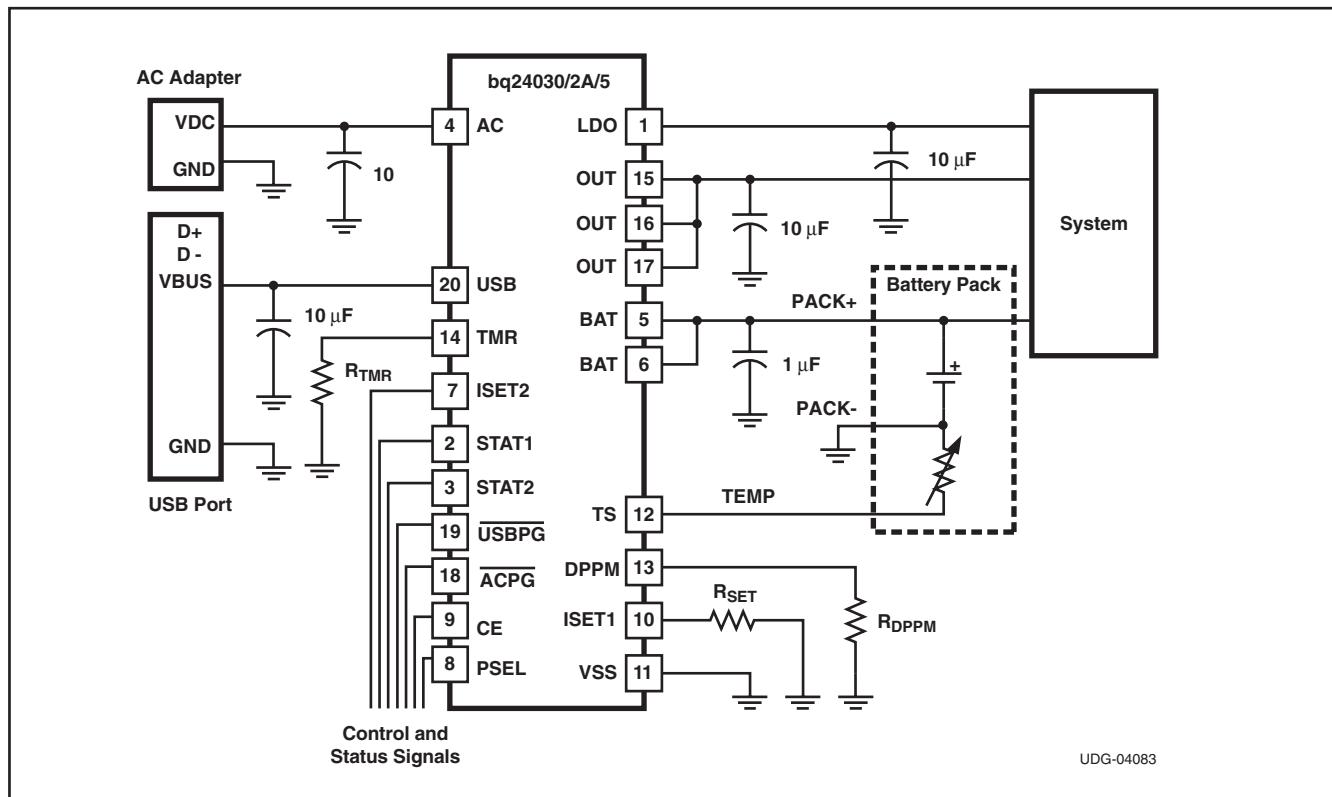

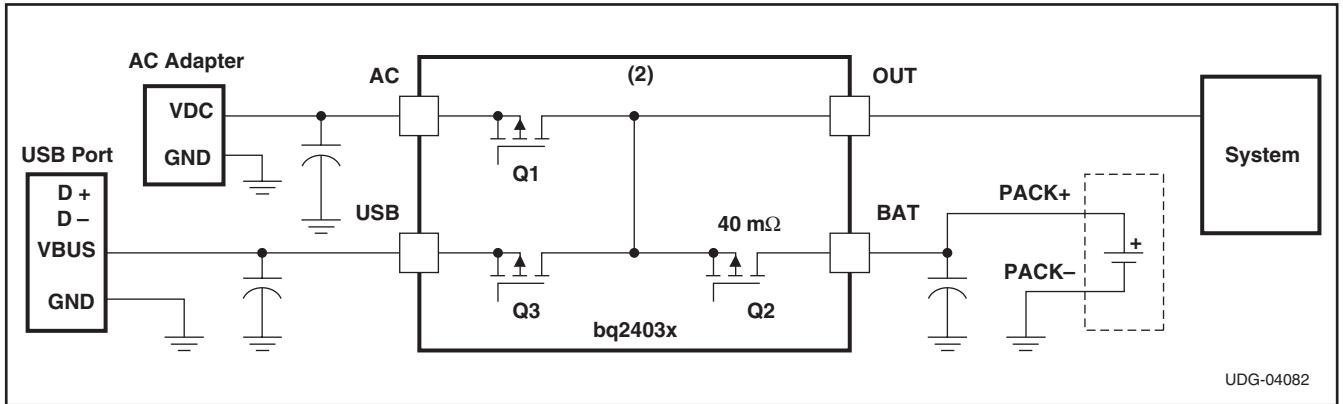

## POWER FLOW DIAGRAM<sup>(1)</sup>

UDG-04082

(1) See Figure 2 and functional block diagram for more detailed feature information.

(2) P-FET back gate body diodes are disconnected to prevent body diode conduction.

bqTINYは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

bqTINY-IIIはバッテリーを充電すると同時にシステムにも電源を供給します。この機能により、バッテリーの充放電を行う回数を低減し、充電終了の検出が精度よく行われ、また、バッテリーが挿入されていなくても、あるいは、バッテリーが劣化していてもシステムを動作できます。また、この機能により放電が進んだバッテリーが挿入されている場合でも外部電源からシステムへ電源が供給できます。このICの設計はAC、USB、バッテリーからの電源が利用可能な場合システムへ継続的に電源を供給することに重点を置いています。

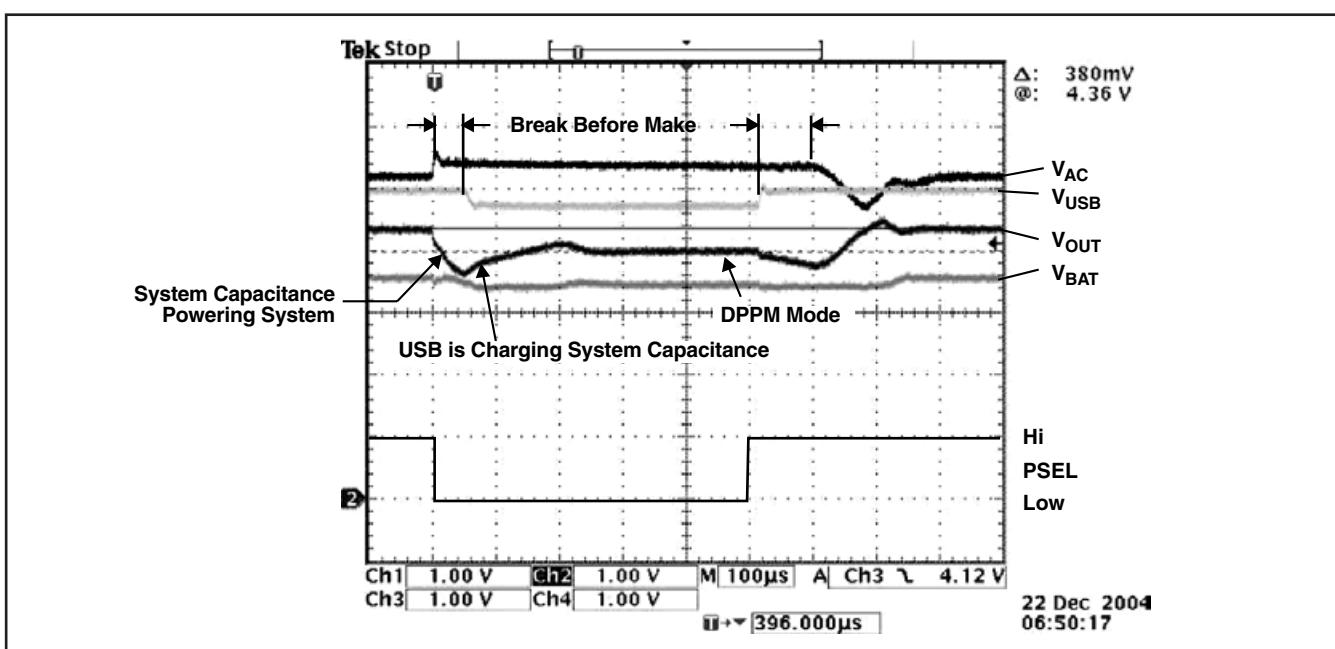

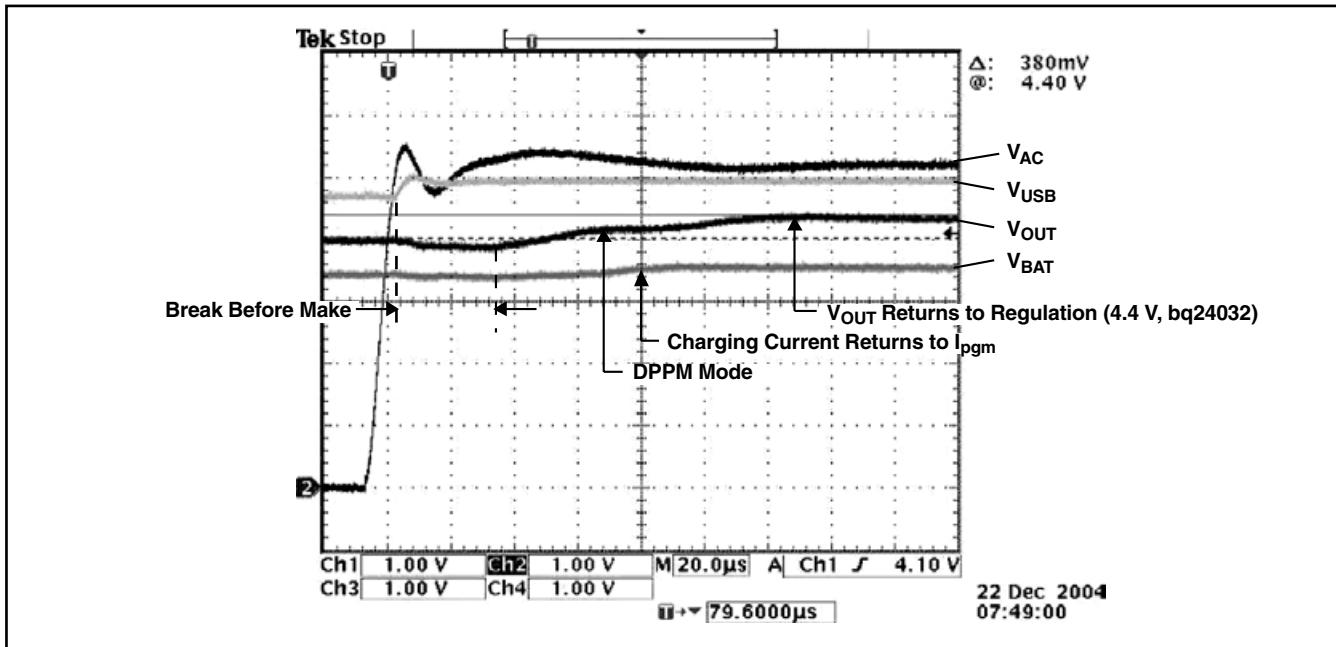

パワー・セレクト・ピン、PSEL入力電源(主電源がACまたはUSB)の優先順位を設定します。主電源が使用できない場合、ICは次に設定された電源(主電源がACの場合はUSB)または、両電源も使用できない場合はバッテリーに自動的に切り替えます。PSELが“L”レベルに設定されれば、USB入力が主電源となり最初に選択され、もしUSBが利用できなければACが選択されますが(利用可能であれば)、ただしこのとき(ACを使う場合)、USBの場合の電流制限(100mA/500mA Max)がACの場合にも適用されます。この機能(PSEL)により、電源の入力コネクタを1つにすることが出来ます。このときホスト側が接続される電源(ACアダプタまたはUSBポート)によってPSELピンの切り替え(“H”、“L”)る必要があります。

bq24038には $\overline{\text{USBP}}$ Gピンの代わりにVBSELピンが用意されており、ユーザーが充電電圧を選択することができます。そのピンに加え $\overline{\text{ACPG}}$ ピンも $\overline{\text{PG}}$ ピンに変更されています。 $\overline{\text{PG}}$ ピンはAC電源またはUSB電源のいずれかが検出された時アクティブ“L”レベルになります。

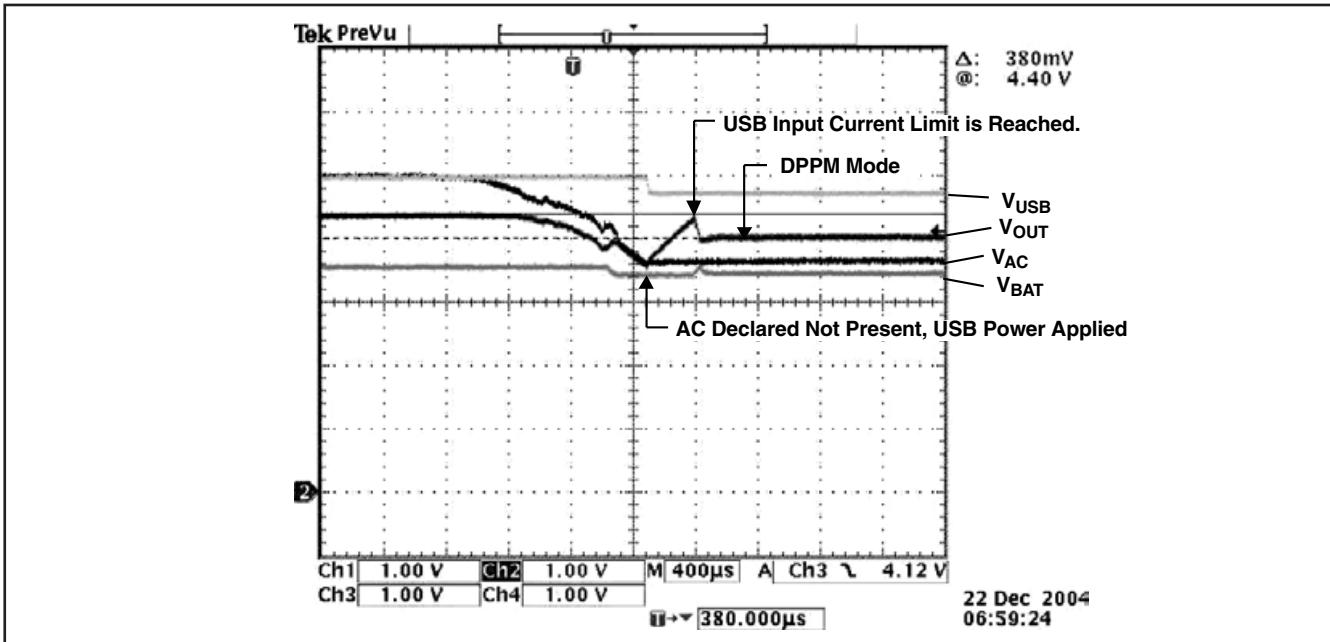

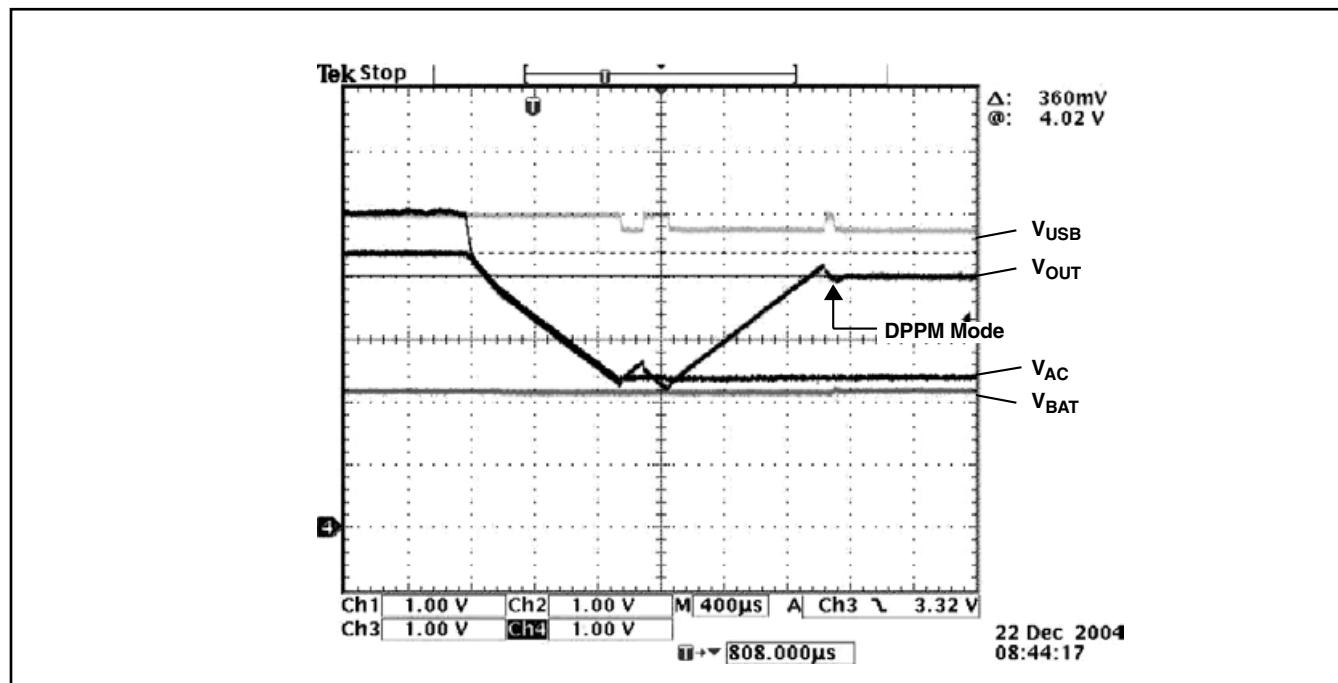

ISET1ピンは抵抗によりバッテリーの急速充電用定電流レベルをプログラムします。通常のAC電源動作時、入力電源はOUTピン(システム)とBATピンの両方に電源を供給します。入力電源に電流制限させたり、入力電源やシステム電圧を低下させたりするようなピークまたは過負荷に対してDPPM機能は、システム電圧の低下を防ぐために、充電電流を減少させます。この機能により、大きなピークの過渡負荷ではなく平均負荷( $I_{\text{SYS-AVG}} + I_{\text{BAT-PM}}$ )をもとに低い電流定格のアダプタを選択することができます。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行なうようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ご発注の手引き<sup>(1)</sup>

| T <sub>A</sub> | BATTERY VOLTAGE (V) | OUT PIN FOR AC INPUT CONDITIONS            | PART NUMBER <sup>(2)(3)</sup> | STATUS   | PACKAGE MARKING |

|----------------|---------------------|--------------------------------------------|-------------------------------|----------|-----------------|

| -40°C to 125°C | 4.2                 | Regulated to 6 V <sup>(4)</sup>            | bq24030RHLR                   | Released | ANB             |

|                | 4.2                 | Regulated to 4.4 V <sup>(4)</sup>          | bq24032ARHLR                  | Released | BPE             |

|                | 4.2                 | Cut off for AC over voltage <sup>(5)</sup> | bq24035RHLR                   | Released | ANA             |

|                | 4.2                 | Cut off for AC over voltage <sup>(5)</sup> | bq24039RHLR                   | Preview  | ANH             |

|                | 4.2/4.36 Selectable | Regulated to 4.4 V                         | bq24038HLR                    | Released | BOW             |

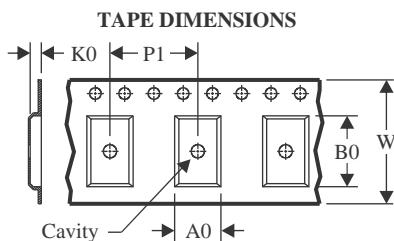

(1) 最新のパッケージ及び発注情報については、このデータシートの終わりの添付パッケージ・オプションまたは、TIホームページwww.ti.comを参照してください。

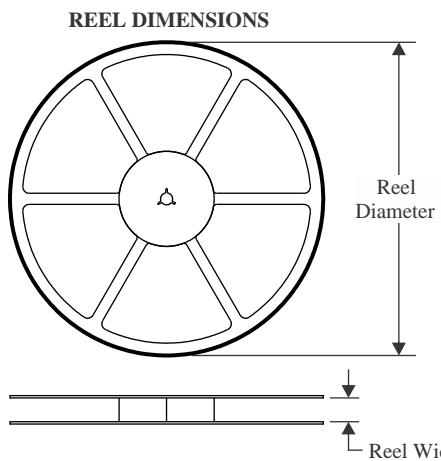

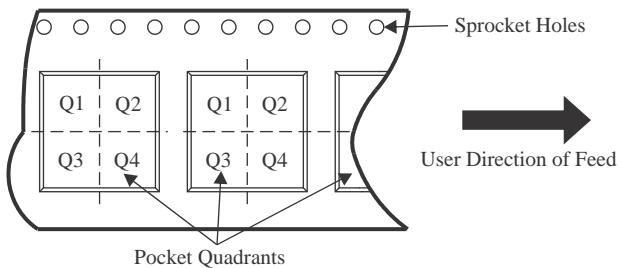

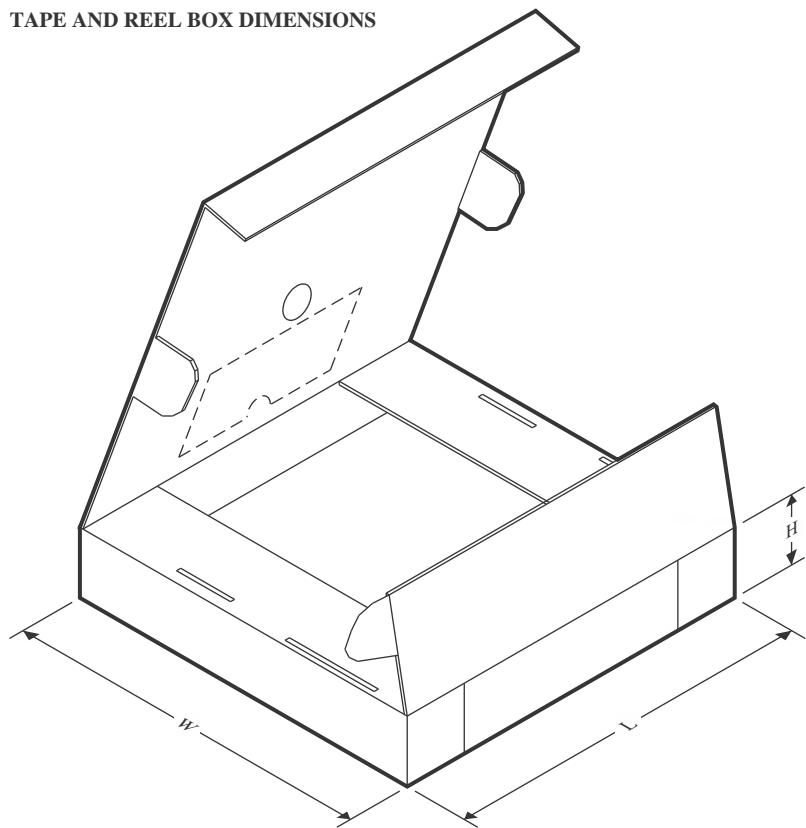

(2) RHLパッケージはテープ/リールのみで供給されており、数量はリール当たり3000個です。

(3) この製品はRoHS(特定有害物質使用制限指令)に準拠しており、鉛濃度は総製品重量の0.1%を越えません。また、特に無鉛はんだ実装工程での使用に適しています。さらに、この製品は総製品重量の0.1%を越えるハロゲン、臭素(Br)、アンチモン(Sb)を含まないパッケージ材を使用しています。

(4) AC <  $V_{O(\text{OUT-REG})}$  の場合、ACはP-FET(Q1)によりOUTピンに接続されます。

(5) AC >  $V_{(\text{CUT-OFF})}$  の場合、P-FETはOUTピンをACから切断します。

## 絶対最大定格<sup>(1)</sup>

動作温度範囲内(特に記述のない限り)

|                                                    |                                                                                                                   |                                        |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                                                    |                                                                                                                   | bq24030, bq24032A,<br>bq24035, bq24038 |

| Input voltage                                      | AC (DC voltage wrt (with respect to) VSS)<br>USB (DC voltage wrt VSS)                                             | -0.3 V to 18 V<br>-0.3 V to 7 V        |

| Input voltage                                      | BAT, CE, DPPM, ACPG, PSEL, OUT, ISET1, ISET2, ISET3, STAT1, STAT2, TS, USBPG, PG, VBSEL (all DC voltages wrt VSS) | -0.3 V to 7 V                          |

| Input voltage                                      | LDO (DC voltage wrt VSS)                                                                                          | -0.3 V to $V_{O(OUT)} + 0.3$ V         |

| Input current                                      | TMR                                                                                                               | -0.3 V to $V_{O(LDO)} + 0.3$ V         |

| Input current                                      | AC<br>USB                                                                                                         | 3.5 A<br>1000 mA                       |

| Output current                                     | OUT<br>BAT <sup>(2)</sup>                                                                                         | 4 A<br>-4 A to 3.5 A                   |

| Output source current (in regulation at 3.3 V LDO) | LDO                                                                                                               | 30 mA                                  |

| Output sink current                                | ACPG, STAT1, STAT2, USBPG, PG                                                                                     | 1.5 mA                                 |

| Storage temperature range, $T_{stg}$               |                                                                                                                   | -65°C to 150°C                         |

| Junction temperature range, $T_J$                  |                                                                                                                   | -40°C to 150°C                         |

| Lead temperature (soldering, 10 seconds)           |                                                                                                                   | 300°C                                  |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

(2) 負電流はBATピンに流れ込む電流として定義されます。

## 推奨動作条件

|                           |                                                                 | MIN  | MAX   | UNIT |

|---------------------------|-----------------------------------------------------------------|------|-------|------|

| V <sub>CC</sub><br>(1)(2) | Supply voltage (from AC input)                                  | 4.35 | 16.00 | V    |

|                           | bq24030/2A/5, bq24038 at VBSEL = LOW<br>bq24038 at VBSEL = HIGH | 4.55 | 16    |      |

| V <sub>CC</sub>           | Supply voltage (from USB input) <sup>(1)</sup>                  | 4.35 | 6.0   |      |

| I <sub>AC</sub>           | Input current, AC                                               |      | 2     | A    |

| I <sub>USB</sub>          | Input current, USB                                              |      | 0.5   |      |

| T <sub>J</sub>            | Operating junction temperature range                            | -40  | 125   | °C   |

(1) V<sub>CC</sub>はAC入力またはUSB入力のうちの大きいほうで定義されます。

(2) 消費電力と接合部温度は最大V<sub>CC</sub>時で制限範囲内にあることを確認してください。

## 損失定格

| PACKAGE                   | T <sub>A</sub> ≤ 40°C<br>POWER RATING | DERATING FACTOR<br>T <sub>A</sub> > 40°C | $\theta_{JA}$ |

|---------------------------|---------------------------------------|------------------------------------------|---------------|

| 20-pin RHL <sup>(1)</sup> | 1.81 W                                | 21 mW/°C                                 | 46.87 °C/W    |

(1) このデータはJEDEC High-Kボードを使用した場合のもので、露出したダイ・パッドはボード上の銅パッドに接続されています。

また、このパッドは2x3のマトリクスのピアでグランド・プレーンに接続されています。

## 電気的特性

動作接合部温度範囲内 ( $0^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ )、推奨電源電圧範囲 (特に記述のない限り)

| PARAMETER                                                      |                                                      | TEST CONDITIONS                                                                                                                                                                                                        | MIN                                                                                  | TYP           | MAX           | UNIT          |

|----------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------|---------------|---------------|

| <b>INPUT BIAS CURRENTS</b>                                     |                                                      |                                                                                                                                                                                                                        |                                                                                      |               |               |               |

| $I_{CC(SPLY)}$                                                 | Active supply current, V <sub>CC</sub>               | $V_{VCC} > V_{VCC(\min)}$                                                                                                                                                                                              | 1                                                                                    | 2             | mA            |               |

| $I_{CC(SLP)}$                                                  | Sleep current (current into BAT pin)                 | $V_{I(AC)} < V_{(BAT)}, V_{(USB)} < V_{(BAT)}, 2.6 \text{ V} \leq V_{I(BAT)} \leq V_{O(BAT-REG)}$ , Excludes load on OUT pin                                                                                           | 2                                                                                    | 5             | $\mu\text{A}$ |               |

| $I_{CC(AS-STDBY)}$                                             | AC standby current                                   | $V_{I(AC)} \leq 6\text{ V}$ , Total current into AC pin with chip disabled, Excludes all loads, CE = LOW, after $t_{(CE-HOLDOFF)}$ delay                                                                               | 200                                                                                  |               |               |               |

| $I_{CC(USB-STDBY)}$                                            | USB standby current                                  | Total current into USB pin with chip disabled, Excludes all loads, CE = LOW, after $t_{(CE-HOLDOFF)}$ delay                                                                                                            | 200                                                                                  |               |               |               |

| $I_{CC(BAT-STDBY)}$                                            | BAT standby current                                  | Total current into BAT pin with AC and/or USB present and chip disabled, Excludes all loads (OUT and LDO), CE=LOW, after $t_{(CE-HOLDOFF)}$ delay, $0^{\circ}\text{C} \leq T_J \leq 85^{\circ}\text{C}$ <sup>(1)</sup> | 45                                                                                   | 60            |               |               |

| $I_{IB(BAT)}$                                                  | Charge done current, BAT                             | Charge DONE, AC or USB supplying the load                                                                                                                                                                              | 1                                                                                    | 5             |               |               |

| <b>HIGH AC CUTOFF MODE</b>                                     |                                                      |                                                                                                                                                                                                                        |                                                                                      |               |               |               |

| $V_{CUT-OFF}$                                                  | Input ac cutoff voltage (bq24039 is product preview) | $V_{I(AC)} > 6.8 \text{ V}$ , AC FET (Q1) turns off, USB FET (Q3) turns on if USB power present otherwise BAT FET (Q2) turns on.                                                                                       | 6.1                                                                                  | 6.4           | 6.8           | V             |

| <b>LDO OUTPUT</b>                                              |                                                      |                                                                                                                                                                                                                        |                                                                                      |               |               |               |

| $V_{O(LDO)}$                                                   | Output regulation voltage                            | Active only if AC or USB is present, $V_{I(OUT)} \geq V_{O(LDO)} + (I_{O(LDO)} \times R_{DS(on)})$                                                                                                                     | 3.3                                                                                  |               | V             |               |

|                                                                | Regulation accuracy <sup>(2)</sup>                   |                                                                                                                                                                                                                        | -5%                                                                                  | 5%            |               |               |

| $I_{O(LDO)}$                                                   | Output current                                       |                                                                                                                                                                                                                        | 20                                                                                   | mA            |               |               |

| $R_{DS(on)}$                                                   | On resistance                                        | OUT to LDO                                                                                                                                                                                                             | 50                                                                                   | $\Omega$      |               |               |

| $C_{(OUT)}^{(3)}$                                              | Output capacitance                                   |                                                                                                                                                                                                                        | 1                                                                                    | $\mu\text{F}$ |               |               |

| <b>OUT PIN-VOLTAGE REGULATION</b>                              |                                                      |                                                                                                                                                                                                                        |                                                                                      |               |               |               |

| $V_{O(OUT-REG)}$                                               | Output regulation voltage                            | bq24030                                                                                                                                                                                                                | $V_{I(AC)} \geq 6 \text{ V} + V_{DO}$                                                | 6.0           | 6.3           | V             |

|                                                                |                                                      | bq24032A                                                                                                                                                                                                               | $V_{I(AC)} \geq 4.4 \text{ V} + V_{DO}$                                              | 4.4           | 4.5           |               |

|                                                                |                                                      | bq24038                                                                                                                                                                                                                | $VBSEL = \text{HIGH}$ or $VBSEL = \text{LOW}$ , $V_{I(AC)} > 4.4 \text{ V} + V_{DO}$ | 4.4           | 4.5           |               |

| <b>OUT PIN – DPPM REGULATION</b>                               |                                                      |                                                                                                                                                                                                                        |                                                                                      |               |               |               |

| $V_{(DPPM-SET)}$                                               | DPPM set point <sup>(4)</sup>                        | $V_{DPPM-SET} < V_{OUT}$                                                                                                                                                                                               | 2.6                                                                                  | 5             | V             |               |

| $I_{(DPPM-SET)}$                                               | DPPM current source                                  | AC or USB present                                                                                                                                                                                                      | 95                                                                                   | 100           | 105           | $\mu\text{A}$ |

| SF                                                             | DPPM scale factor                                    | $V_{(DPPM-REG)} = V_{(DPPM-SET)} \times SF$                                                                                                                                                                            | 1.139                                                                                | 1.150         | 1.162         |               |

| <b>OUT PIN – FET (Q1, Q3, AND Q2) DROP-OUT VOLTAGE (RDSon)</b> |                                                      |                                                                                                                                                                                                                        |                                                                                      |               |               |               |

| $V_{(ACDO)}$                                                   | AC to OUT dropout voltage <sup>(5)</sup>             | $V_{I(AC)} \geq V_{CC(\min)}$ , PSEL = High, $I_{I(AC)} = 1 \text{ A}$ , $(I_{O(OUT)} + I_{O(BAT)})$                                                                                                                   | 300                                                                                  | 475           | mV            |               |

| $V_{(USBDO)}^{(6)}$                                            | USB to OUT dropout voltage                           | $V_{I(USB)} \geq V_{CC(\min)}$ , PSEL = Low, or no AC (bq24039), ISET2 = High $I_{I(USB)} = 0.4 \text{ A}$ , $(I_{O(OUT)} + I_{O(BAT)})$                                                                               | 140                                                                                  | 180           |               |               |

|                                                                |                                                      | $V_{I(USB)} \geq V_{CC(\min)}$ , PSEL = Low, or no AC (bq24039), ISET2 = Low $I_{I(USB)} = 0.08 \text{ A}$ , $(I_{O(OUT)} + I_{O(BAT)})$                                                                               | 28                                                                                   | 36            |               |               |

|                                                                |                                                      | $V_{I(USB)} \geq V_{CC(\min)}$ , ISET2 = ISET3 = HIGH, $I_{I(USB)} = 0.9 \text{ A}$ , $(I_{O(OUT)} + I_{O(BAT)})$ , bq24039 only                                                                                       | 315                                                                                  | 405           | mV            |               |

(1) これには内蔵LDOの静止電流が含まれています。

(2) スタンバイ・モード (CE = “L” レベル) では精度は±10%です。

(3) LDOの出力コンデンサは不要ですが、0.1μFのものを推奨します。

(4)  $V_{(DPPM-SET)}$ は出力電圧 $V_{(DPPM-REG)}$ をコントロールする倍率で増大します。

(5) ドップアウト電圧 $V_{DO(max)}$ はFETの $R_{DS(on)}$ とドレイン電流の関数です。ドップアウト電圧は電流の増加に比例して増加します。

(6) USB FET Q3の $R_{DS(on)}$ は、 $I_{I(USB)} \leq I_{I(USB-MIN)}$ の時  $(V_{USB} - V_{OUT}) / (I_{OUT} + I_{BAT})$  で求められます (FETは完全にオンで、レギュレーション中ではありません)。

## 電気的特性

動作接合部温度範囲内 ( $0^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ )、推奨電源電圧範囲(特に記述のない限り)

| PARAMETER                                    |                                                                                                    | TEST CONDITIONS                                                                                                                                                                                                                                                                | MIN                                                     | TYP   | MAX         | UNIT |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|-------------|------|--|--|--|

| $V_{(\text{BATDO})}$                         |                                                                                                    | $V_{(\text{BAT})} \geq 3\text{ V}$ , $I_{(\text{BAT})} = 1.0\text{ A}$ , $V_{\text{CC}} < V_{(\text{BAT})}$                                                                                                                                                                    | 40                                                      |       | 100         | mV   |  |  |  |

| <b>OUT PIN - BATTERY SUPPLEMENT MODE</b>     |                                                                                                    |                                                                                                                                                                                                                                                                                |                                                         |       |             |      |  |  |  |

| $V_{(\text{BSUP1})}$                         | Enter battery supplement mode<br>(battery supplements OUT current in the presence of input source) | $V_{(\text{BAT})} > 2\text{ V}$                                                                                                                                                                                                                                                | $V_{(\text{OUT})} \leq V_{(\text{BAT})} - 60\text{ mV}$ | $V$   |             |      |  |  |  |

| $V_{(\text{BSUP2})}$                         | Exit battery supplement mode                                                                       | $V_{(\text{BAT})} > 2\text{ V}$                                                                                                                                                                                                                                                | $V_{(\text{OUT})} \geq V_{(\text{BAT})} - 20\text{ mV}$ |       |             |      |  |  |  |

| <b>OUT PIN - SHORT CIRCUIT</b>               |                                                                                                    |                                                                                                                                                                                                                                                                                |                                                         |       |             |      |  |  |  |

| $I_{(\text{OSH1})}$                          | BAT to OUT short circuit recovery                                                                  | Current source between BAT to OUT for short circuit recovery to $V_{(\text{OUT})} \leq V_{(\text{BAT})} - 200\text{mV}$                                                                                                                                                        | 10                                                      |       | mA          |      |  |  |  |

| $R_{(\text{SHAC})}$                          | AC to OUT short circuit limit                                                                      | $V_{(\text{OUT})} \leq 1\text{ V}$                                                                                                                                                                                                                                             | 500                                                     |       | $\Omega$    |      |  |  |  |

| $R_{(\text{SHVSB})}$                         | USB to OUT short circuit limit                                                                     | $V_{(\text{OUT})} \leq 1\text{ V}$                                                                                                                                                                                                                                             | 500                                                     |       |             |      |  |  |  |

| <b>BAT PIN CHARGING – PRECHARGE</b>          |                                                                                                    |                                                                                                                                                                                                                                                                                |                                                         |       |             |      |  |  |  |

| $V_{(\text{LOWV})}$                          | Precharge to fast-charge transition threshold                                                      | Voltage on BAT                                                                                                                                                                                                                                                                 | 2.9                                                     | 3.0   | 3.1         | V    |  |  |  |

| $T_{(\text{DGL(F})}$                         | Deglitch time for fast-charge to precharge transition <sup>(7)</sup>                               | $t_{\text{FALL}} = 100\text{ ns}$ , 10 mV overdrive, $V_{(\text{BAT})}$ decreasing below threshold                                                                                                                                                                             | 22.5                                                    |       | ms          |      |  |  |  |

| $I_{(\text{O(PRECHG})}$                      | Precharge range                                                                                    | $1\text{ V} < V_{(\text{BAT})} < V_{(\text{LOWV})}$ , $t < t_{(\text{PRECHG})}$ , $I_{(\text{O(PRECHG})} = (K_{(\text{SET})} \times V_{(\text{PRECHG})}) / R_{(\text{SET})}$                                                                                                   | 10                                                      | 150   |             | mA   |  |  |  |

| $V_{(\text{PRECHG})}$                        | Precharge set voltage                                                                              | $1\text{ V} < V_{(\text{BAT})} < V_{(\text{LOWV})}$ , $t < t_{(\text{PRECHG})}$                                                                                                                                                                                                | 230                                                     | 250   | 270         | mV   |  |  |  |

| <b>BAT PIN CHARGING - CURRENT REGULATION</b> |                                                                                                    |                                                                                                                                                                                                                                                                                |                                                         |       |             |      |  |  |  |

| $I_{(\text{O(BAT})}$                         | AC battery charge current range <sup>(8)</sup>                                                     | $V_{(\text{BAT})} > V_{(\text{LOWV})}$ , $V_{(\text{OUT})} - V_{(\text{BAT})} > V_{(\text{DO-MAX})}$ , PSEL = High<br>$I_{(\text{OUT(BAT})} = (K_{(\text{SET})} \times V_{(\text{SET})}) / R_{(\text{SET})}$ , $V_{(\text{OUT})} > V_{(\text{OUT-REG})} + V_{(\text{DO-MAX})}$ | 100                                                     | 1000  | 1500        | mA   |  |  |  |

| $R_{(\text{POUT})}$                          | AC to OUT and USB to OUT short-circuit pull-up                                                     | $V_{(\text{OUT})} < 1\text{ V}$                                                                                                                                                                                                                                                | 500                                                     |       | $\Omega$    |      |  |  |  |

| $V_{(\text{SET})}$                           | Battery charge current set voltage <sup>(9)</sup>                                                  | Voltage on ISET1, $V_{\text{CC}} \geq 4.35\text{ V}$ , $V_{(\text{OUT})} - V_{(\text{BAT})} > V_{(\text{DO-MAX})}$ , $V_{(\text{BAT})} > V_{(\text{LOWV})}$                                                                                                                    | 2.475                                                   | 2.500 | 2.525       | V    |  |  |  |

| $K_{(\text{SET})}$                           | Charge current set factor, BAT                                                                     | $100\text{ mA} \leq I_{(\text{O(BAT})} \leq 1\text{ A}$                                                                                                                                                                                                                        | 400                                                     | 425   | 450         |      |  |  |  |

|                                              |                                                                                                    | $10\text{ mA} \leq I_{(\text{O(BAT})} \leq 100\text{ mA}$ <sup>(10)</sup>                                                                                                                                                                                                      | 300                                                     | 450   | 600         |      |  |  |  |

| <b>USB PIN INPUT CURRENT REGULATION</b>      |                                                                                                    |                                                                                                                                                                                                                                                                                |                                                         |       |             |      |  |  |  |

| $I_{(\text{USB})}$                           | USB input current range, bq24030/2/5; bq24039 <sup>(11)</sup>                                      | $V_{(\text{BAT})} > V_{(\text{LOWV})}$ , $V_{(\text{USB})} - V_{(\text{BAT})} > V_{(\text{DO-MAX})}$ , ISET2 = Low, ISET3 = Low, PSEL = Low or no AC (bq24039) <sup>(12)</sup>                                                                                                 | 100                                                     |       | $\text{mA}$ |      |  |  |  |

|                                              |                                                                                                    | $V_{(\text{BAT})} > V_{(\text{LOWV})}$ , $V_{(\text{USB})} - V_{(\text{BAT})} > V_{(\text{DO-MAX})}$ , ISET2 = High, ISET3 = Low, PSEL = Low, or no AC (bq24039) <sup>(11)</sup>                                                                                               | 400                                                     | 500   |             |      |  |  |  |

(7) デグリッチの全期間はタイマ設定の閾数で、DPPMモードまたはサーマル・レギュレーション・モードでプログラム電流が減少する割合で修正されます。

(8) 入力電流が2Aより低いままである場合、バッテリー充電電流はサーマル・レギュレーションが充電電流を制限するまで上昇する可能性があります。

(9) ハーフ充電レートの場合、bq24032A/38のみV(SET)は $1.25\text{V} \pm 25\text{mV}$ です。

(10) この仕様は電圧レギュレーション・モード時ISET1ピンにより充電電流をモニタした場合であり、低減高速充電レベルの場合ではありません。

(11) PSEL = “L” レベルの場合、bqTINY-IIIはUSB充電をデフォルトとします。USB入力が $V_{\text{BAT}}$ 以下の場合、bqTINY-IIIはUSB充電レートでAC入力から充電します。この設定では、仕様値はbq24030/2A/5のみ400mA (Min)、500mA (Max)です。

(12) PSEL = “L” レベルの場合、bqTINY-IIIはUSB充電をデフォルトとします。USB入力が $V_{\text{BAT}}$ 以下の場合、bqTINY-IIIはUSB充電レートでAC入力から充電します。この設定では、仕様値はbq24030/2A/5で80mA (Min)、100mA (Max)です。

## 電気的特性

動作接合部温度範囲内 ( $0^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ )、推奨電源電圧範囲 (特に記述のない限り)

| PARAMETER                                                                                                                                                    |                                                               | TEST CONDITIONS                                                                                                                | MIN                      | TYP                      | MAX                      | UNIT          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|---------------|

| <b>BAT PIN CHARGING VOLTAGE REGULATION, <math>V_{O(BAT-REG)} + V_{(DO-MAX)} &lt; V_{CC}</math>, <math>I_{TERM} &lt; I_{BAT(OUT)} \leq 1 \text{ A}</math></b> |                                                               |                                                                                                                                |                          |                          |                          |               |

| $V_{O(BAT-REG)}$                                                                                                                                             | voltage<br>Battery charge                                     | bq24030/2A/5                                                                                                                   |                          | 4.2                      |                          | V             |

|                                                                                                                                                              |                                                               | bq24038                                                                                                                        | VBXL = HI                | 4.36                     |                          |               |

|                                                                                                                                                              | Battery charge voltage regulation<br>accuracy                 | VBXL = LO                                                                                                                      |                          | 4.2                      |                          |               |

|                                                                                                                                                              |                                                               | $T_A = 25^{\circ}\text{C}$                                                                                                     | -0.5%                    | 0.5%                     |                          |               |

|                                                                                                                                                              |                                                               |                                                                                                                                | -1%                      |                          | 1%                       |               |

| <b>CHARGE TERMINATION DETECTION</b>                                                                                                                          |                                                               |                                                                                                                                |                          |                          |                          |               |

| $I_{(TERM)}$                                                                                                                                                 | Charge termination detection range                            | $V_{I(BAT)} < V_{(RCH)}$ ,<br>$I_{(TERM)} = (K_{(SET)} \times V_{(TERM)}) / R_{SET}$                                           | 10                       | 150                      | mA                       |               |

| $V_{(TERM-AC)}$<br>bq24030/2A/5)                                                                                                                             | AC-charge termination detection voltage, measured on ISET1    | $V_{I(BAT)} > V_{(RCH)}$ , PSEL = High,<br>ACPG = Low                                                                          | 235                      | 250                      | 265                      | mV            |

| $V_{(TAPER-USB)}$<br>bq24030/2A/5)                                                                                                                           | USB-charge termination detection voltage, measured on ISET1   | $V_{I(BAT)} > V_{(RCH)}$ , PSEL = Low or<br>PSEL = High and ACPG = High                                                        | 95                       | 100                      | 130                      | mV            |

| $T_{DGL(TERM)}$                                                                                                                                              | Deglitch time for termination detection                       | $t_{FALL} = 100 \text{ ns}$ , 10 mV overdrive,<br>$I_{CHG}$ increasing above or decreasing below threshold                     |                          | 22.5                     |                          | ms            |

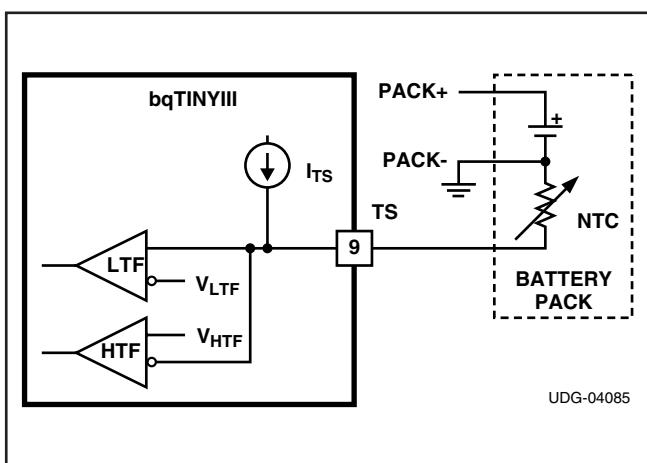

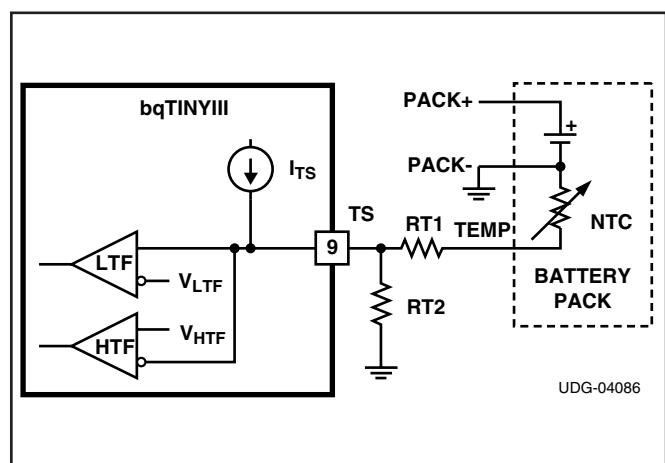

| <b>TEMPERATURE SENSE COMPARATORS</b>                                                                                                                         |                                                               |                                                                                                                                |                          |                          |                          |               |

| $V_{LTF}$                                                                                                                                                    | High voltage threshold                                        | Temp fault at $V(TS) > V_{LTF}$                                                                                                | 2.465                    | 2.500                    | 2.535                    | V             |

| $V_{HTF}$                                                                                                                                                    | Low voltage threshold                                         | Temp fault at $V(TS) < V_{HTF}$                                                                                                | 0.485                    | 0.500                    | 0.515                    | V             |

| $I_{TS}$                                                                                                                                                     | Temperature sense current source                              |                                                                                                                                | 94                       | 100                      | 106                      | $\mu\text{A}$ |

| $T_{DGL(TF)}$                                                                                                                                                | Deglitch time for temperature fault detection <sup>(13)</sup> | $R_{(TMR)} = 50 \text{ k}\Omega$ , $V_{I(BAT)}$ increasing or decreasing above and below;<br>100-ns fall time, 10-mV overdrive |                          | 22.5                     |                          | ms            |

| <b>BATTERY RECHARGE THRESHOLD</b>                                                                                                                            |                                                               |                                                                                                                                |                          |                          |                          |               |

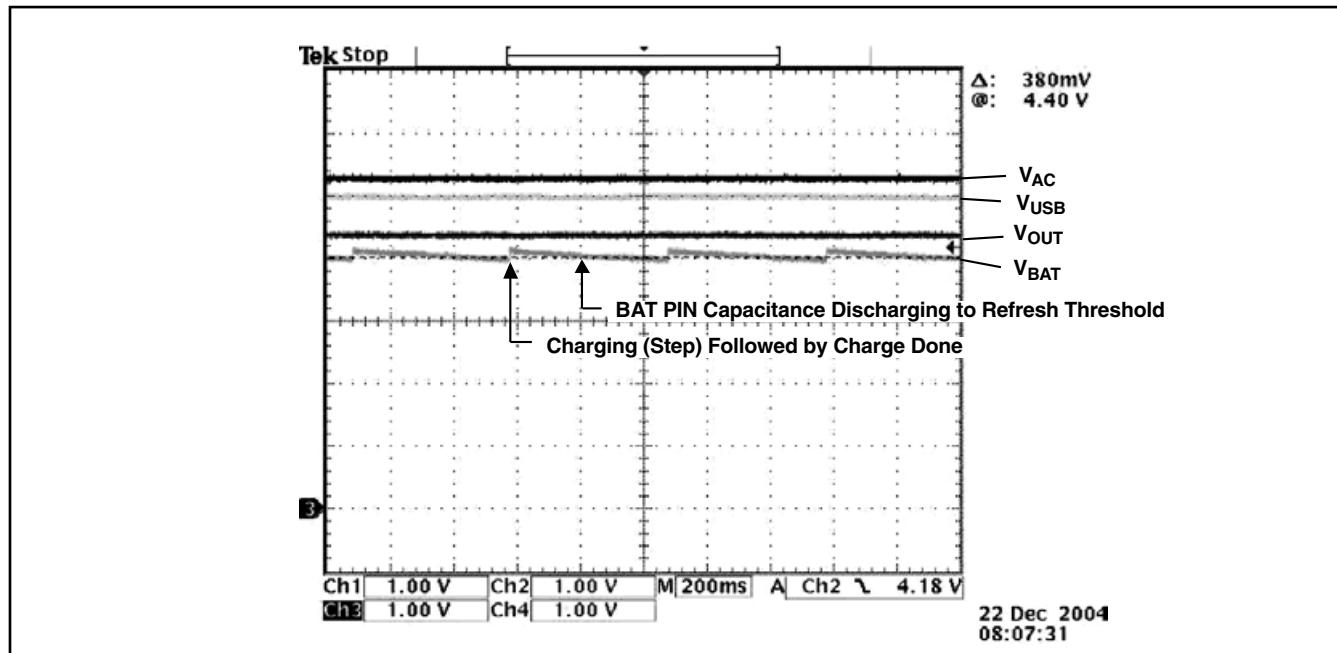

| $V_{RCH}$                                                                                                                                                    | Recharge threshold voltage                                    |                                                                                                                                | $V_{O(BAT-REG)} - 0.075$ | $V_{O(BAT-REG)} - 0.100$ | $V_{O(BAT-REG)} - 0.125$ | V             |

| $T_{DGL(RCH)}$                                                                                                                                               | Deglitch time for recharge detection <sup>(13)</sup>          | $R_{(TMR)} = 50 \text{ k}\Omega$ , $V_{I(BAT)}$ increasing or decreasing below threshold,<br>100-ns fall time, 10-mV overdrive |                          | 22.5                     |                          | ms            |

| <b>STAT1, STAT2, ACPG AND USBPG, PG OPEN DRAIN (OD), OUTPUTS<sup>(14)</sup></b>                                                                              |                                                               |                                                                                                                                |                          |                          |                          |               |

| $V_{OL}$                                                                                                                                                     | Low-level output saturation voltage                           | $I_{OL} = 5 \text{ mA}$ , An external pull-up resistor $\geq 1 \text{ K}$ required.                                            |                          | 0.25                     |                          | V             |

| $I_{LKG}$                                                                                                                                                    | Input leakage current                                         |                                                                                                                                |                          | 1                        | 5                        | $\mu\text{A}$ |

| <b>ISET2, CE, VBSEL AND ISET3 INPUTS</b>                                                                                                                     |                                                               |                                                                                                                                |                          |                          |                          |               |

| $V_{IL}$                                                                                                                                                     | Low-level input voltage                                       |                                                                                                                                | 0                        | 0.4                      |                          | V             |

| $V_{IH}$                                                                                                                                                     | High-level input voltage                                      |                                                                                                                                | 1.4                      |                          |                          |               |

| $I_{IL}$                                                                                                                                                     | Low-level input current, CE or ISET3                          |                                                                                                                                | -1                       |                          |                          |               |

| $I_{IH}$                                                                                                                                                     | High-level input current, CE or ISET3                         |                                                                                                                                |                          | 1                        |                          |               |

| $I_{IL}$                                                                                                                                                     | Low-level input current, ISET2                                | $V_{ISET2} = 0 \text{ V}$                                                                                                      | -20                      |                          |                          | $\mu\text{A}$ |

| $I_{IH}$                                                                                                                                                     | High-level input current, ISET2                               | $V_{ISET2} = V_{CC}$                                                                                                           |                          | 40                       |                          |               |

| $I_{IL1}$                                                                                                                                                    | Low level input current                                       | $VBSEL = \text{Low}$                                                                                                           | 5                        | 1                        |                          |               |

| $I_{IH1}$                                                                                                                                                    | High level input current                                      | $VBSEL = \text{High}$                                                                                                          |                          | 15                       |                          |               |

| $t_{(CE-HLDOFF)}$                                                                                                                                            | Hold off time, CE                                             | CE going low only                                                                                                              | 4                        | 6                        | ms                       |               |

(13) デグリッチの全期間はタイマ設定の関数で、DPPMモードまたはサーマル・レギュレーション・モードでプログラム電流が減少する割合で修正されます。

(14) ACPG ( $V_{CC} = V_{AC}$ ) 及びUSBPG ( $V_{CC} = V_{USB}$ ) の仕様については充電器のスリープ・モードを参照してください。

## 電気的特性

動作接合部温度範囲内 ( $0^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ )、推奨電源電圧範囲(特に記述のない限り)

|                                                                                   | PARAMETER                                                                        | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                         | MIN                                                     | TYP                                                     | MAX                            | UNIT               |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|--------------------------------|--------------------|

| <b>PSEL INPUT</b>                                                                 |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

| $V_{IL}$                                                                          | Low-level input voltage                                                          | Falling Hi→Low; $280\text{ K} \pm 10\%$ applied when low.                                                                                                                                                                                                                                                                                               | 0.975                                                   | 1.0                                                     | 1.025                          | V                  |

| $V_{IH}$                                                                          | High-level input voltage                                                         | Input $R_{PSEL}$ sets external hysteresis                                                                                                                                                                                                                                                                                                               | $V_{IL} + .01$                                          | $V_{IL} + .024$                                         |                                | V                  |

| $I_{IL}$                                                                          | Low-level input current, PSEL                                                    |                                                                                                                                                                                                                                                                                                                                                         | -1                                                      |                                                         |                                | $\mu\text{A}$      |

| $I_{IH}$                                                                          | High-level input current, PSEL                                                   |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                | $\mu\text{A}$      |

| <b>TIMERS</b>                                                                     |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

| $K_{(\text{TMR})}$                                                                | Timer set factor                                                                 | $t_{(\text{CHG})} = K_{(\text{TMR})} \times R_{(\text{TMR})}$                                                                                                                                                                                                                                                                                           | 0.313                                                   | 0.360                                                   | 0.414                          | $\text{s}/\Omega$  |

| $R_{(\text{TMR})}^{(15)}$                                                         | External resistor limits                                                         |                                                                                                                                                                                                                                                                                                                                                         | 30                                                      | 100                                                     |                                | $\text{k}\Omega$   |

| $t_{(\text{PRECHG})}$                                                             | Precharge timer                                                                  |                                                                                                                                                                                                                                                                                                                                                         | $0.09 \times t_{(\text{CHG})}$                          | $0.10 \times t_{(\text{CHG})}$                          | $0.11 \times t_{(\text{CHG})}$ | s                  |

| $I_{(\text{FAULT})}$                                                              | Timer fault recovery pull-up from OUT to BAT                                     |                                                                                                                                                                                                                                                                                                                                                         | 1                                                       |                                                         |                                | $\text{k}\Omega$   |

| <b>CHARGER SLEEP THRESHOLDS (ACPG , PG and USBPG THRESHOLDS, LOW → POWER GOOD</b> |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

| $V_{(\text{SLPENT})}^{(16)}$                                                      | Sleep mode entry threshold                                                       | $V_{(\text{UVLO})} \leq V_{I(\text{BAT})} \leq V_{O(\text{BAT-REG})}$ ,<br>No $t_{(\text{BOOT-UP})}$ delay                                                                                                                                                                                                                                              |                                                         | $V_{\text{VCC}} \leq V_{I(\text{BAT})} + 125\text{ mV}$ |                                | V                  |

| $V_{(\text{SLPEXIT})}^{(16)}$                                                     | Sleep mode exit threshold                                                        | $V_{(\text{UVLO})} \leq V_{I(\text{BAT})} \leq V_{O(\text{BAT-REG})}$ ,<br>No $t_{(\text{BOOT-UP})}$ delay                                                                                                                                                                                                                                              | $V_{\text{VCC}} \geq V_{I(\text{BAT})} + 190\text{ mV}$ |                                                         |                                |                    |

| $t_{(\text{DEGL})}$                                                               | Deglitch time for sleep mode <sup>(17)</sup>                                     | $R_{(\text{TMR})} = 50\text{ k}\Omega$ ,<br>$V_{(\text{AC})}$ or $V_{(\text{USB})}$ or decreasing below<br>threshold, 100-ns fall time, 10-mv overdrive                                                                                                                                                                                                 |                                                         | 22.5                                                    |                                | ms                 |

| <b>START-UP CONTROL and USB BOOT-UP</b>                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

| $t_{(\text{BOOT-UP})}$                                                            | Boot-up time                                                                     | Upon the first application of USB input power or AC input with PSEL Low                                                                                                                                                                                                                                                                                 | 120                                                     | 150                                                     | 180                            | ms                 |

| <b>SWITCHING POWER SOURCE TIMING</b>                                              |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

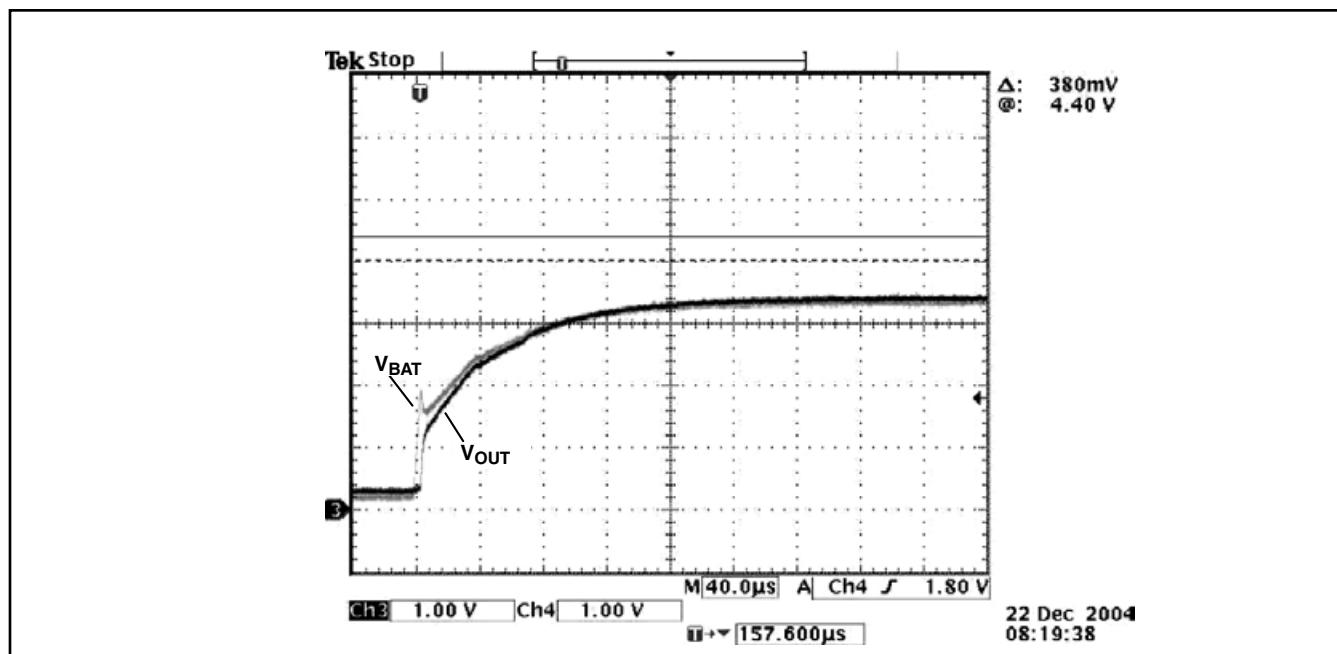

| $t_{\text{SW-BAT}}$                                                               | Switching power source from inputs (AC or USB) to battery                        | Only AC power or USB power applied.<br>Measure from:<br>[xxPG: Lo → Hi to $I_{(xx)} > 5\text{ mA}$ ],<br>$xx = \text{AC or USB}$ $I_{(\text{OUT})} = 100\text{ mA}$ ,<br>$R_{\text{TRM}} = 50\text{ K}$                                                                                                                                                 |                                                         |                                                         | 50                             | $\mu\text{s}$      |

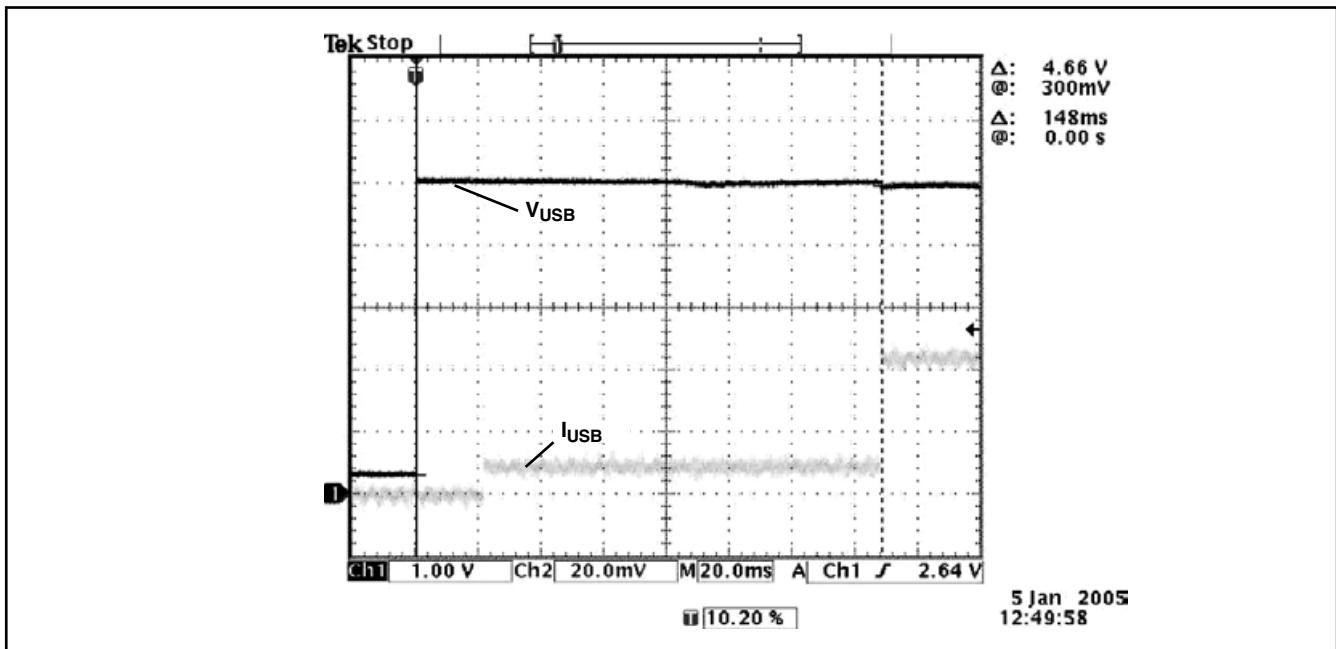

| $t_{\text{SW-AC/USB}}$                                                            | Switching from AC to USB, or, USB to AC by input source removal. <sup>(18)</sup> | Measure from:<br>$I_{(\text{AC})} < 5\text{ mA}$ to $I_{(\text{USB})} > 5\text{ mA}$ or $I_{(\text{USB})} < 5\text{ mA} \rightarrow I_{(\text{AC})} > 5\text{ mA}$ ;<br>$I_{(\text{OUT})} = 100\text{ mA}$ , $R_{\text{TRM}} = 50\text{ K}$ , $I_{\text{SET2}} = \text{hi}$ ,<br>$R_{\text{OUT}} > 15\text{ }\Omega$ , $V_{\text{DPPM}} = 2.5\text{ V}$ |                                                         | 100                                                     |                                |                    |

| $t_{\text{SW-PSEL}}$                                                              | Switching from AC to USB, or USB to AC by toggling PSEL, bq24030/2A/5/8 only     |                                                                                                                                                                                                                                                                                                                                                         |                                                         | 50                                                      | 100                            |                    |

| <b>THERMAL SHUTDOWN REGULATION<sup>(19)</sup></b>                                 |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

| $T_{(\text{SHTDWN})}$                                                             | Temperature trip                                                                 | $T_J$ (Q1 and Q3 only)                                                                                                                                                                                                                                                                                                                                  |                                                         | 155                                                     |                                | $^{\circ}\text{C}$ |

|                                                                                   | Thermal hysteresis                                                               | $T_J$ (Q1 and Q3 only)                                                                                                                                                                                                                                                                                                                                  |                                                         | 30                                                      |                                |                    |

| $T_{J(\text{REG})}$                                                               | Temperature regulation limit                                                     | $T_J$ (Q2)                                                                                                                                                                                                                                                                                                                                              |                                                         | 115                                                     | 135                            |                    |

| <b>UVLO</b>                                                                       |                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                                         |                                                         |                                |                    |

| $V_{(\text{UVLO})}$                                                               | Undervoltage lockout                                                             | Decreasing $V_{\text{CC}}$                                                                                                                                                                                                                                                                                                                              | 2.45                                                    | 2.50                                                    | 2.65                           | V                  |

|                                                                                   | Hysteresis                                                                       |                                                                                                                                                                                                                                                                                                                                                         |                                                         | 27                                                      |                                | mV                 |

(15) セーフティ・タイマ及び充電終了をディスエーブルにするには、TMRをLDOピンに接続します。

(16) ACとUSBの両方とも存在しない場合 (ACPG = USBPG = オープン・ドレイン)、ICはスリープ・モードであると見なされます。

(17) デグリッチ時間が終わるまでスリープ・モードは宣言されず、スイッチング仕様に従って直ちに必要とされるパワーの移動を行います。

(18) 取り除かれた電源がバッテリー電圧まで低下した場合であるPGピンが“H”レベル(取り除かれた電源のパワーグッド)になるとパワーの伝達が行われます。バッテリー電圧が非常に低ければ、システムがPSELピンをコントロールし、シャットダウンより前に利用可能な電源に切り替えない限りシステムはパワーを開放する可能性があります。USB電源は多くの場合有効電流が少ないため、システムはACからUSBへの切り替え時負荷を低減しなければならないことがあります(bq24030/2A/5)。

(19) サーマル・レギュレーションに達すると充電電流は減少します。バッテリー補完電流はサーマル・レギュレーションまたはシャットダウンを問わず制限されません。入力パワーFETはサーマル・シャットダウン時オフになります。バッテリーのFETは短絡制限によってのみ保護されており、一般的にそれ自身ではサーマル・シャットダウン(入力FETオフ)は起こりません。

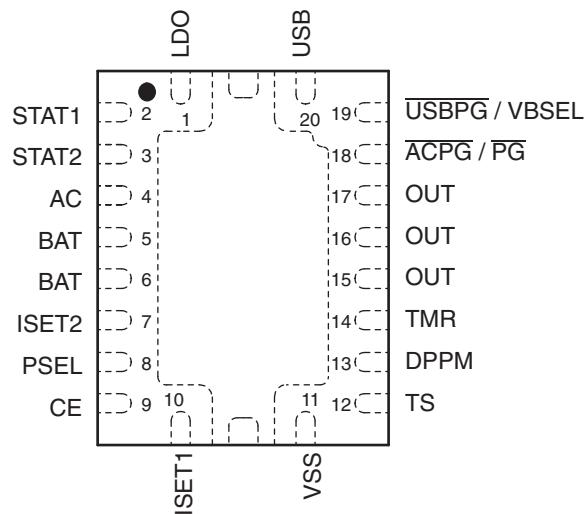

## デバイス情報

bq24030RHL - bq24038RHL

RHL PACKAGE

(TOP VIEW)

## 端子機能

| TERMINAL             | I/O        |                                                                                                                                                                             |

|----------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO.        |                                                                                                                                                                             |

| AC                   | 4          | I ACアダプタからの充電入力電圧端子。                                                                                                                                                        |

| ACPG <sup>(1)</sup>  | 18         | O ACパワーグッド・ステータス出力端子(オープン・ドレイン)                                                                                                                                             |

| BAT                  | 5, 6       | I/O バッテリー入出力端子                                                                                                                                                              |

| CE                   | 9          | I チップ・イネーブル入力端子(アクティブ “H” レベル)                                                                                                                                              |

| DPPM                 | 13         | I ダイナミック・パワーパス・マネージメント設定値(倍率から成る)                                                                                                                                           |

| ISET1                | 10         | I/O AC入力用充電電流設定値、及びAC/USB用プリチャージ/充電終了設定値                                                                                                                                    |

| ISET2                | 7          | I USBポート用充電電流設定値 (“H” レベルの場合500mA、“L” レベルの場合100mA)。bq24032の場合はISET2を使用したハーフ充電電流モードを参照してください。                                                                                |

| LDO                  | 1          | O 3.3V LDOレギュレータ端子                                                                                                                                                          |

| OUT                  | 15, 16, 17 | O システムへの出力端子                                                                                                                                                                |

| PG <sup>(1)</sup>    | 18         | O ACまたはUSBパワーグッド・ステータス出力端子(オープン・ドレイン)                                                                                                                                       |

| PSEL                 | 8          | I 電源選択入力端子(USBの場合“L” レベル、ACの場合“H” レベル)                                                                                                                                      |

| STAT1                | 2          | O 充電ステータス出力1端子(オープン・ドレイン)                                                                                                                                                   |

| STAT2                | 3          | O 充電ステータス出力2端子(オープン・ドレイン)                                                                                                                                                   |

| TMR                  | 14         | I/O 抵抗によりプログラムされるタイマ・プログラム入力端子。TMRをLDOに接続することによりセーフティ・タイマと充電終了がディスエーブルになります。                                                                                                |

| TS                   | 12         | I/O 温度検出入力端子                                                                                                                                                                |

| USB                  | 20         | I USB充電入力電圧端子                                                                                                                                                               |

| USBPG <sup>(1)</sup> | 19         | O USBパワーグッド・ステータス出力端子(オープン・ドレイン)                                                                                                                                            |

| VBSEL <sup>(2)</sup> | 19         | I バッテリーの充電電圧選択端子                                                                                                                                                            |

| VSS                  | 11         | - グランド入力(パッケージ底面のサーマル・パッド)。露出サーマル・パッドとデバイスのVSSピンの間には内部で電気的接続があります。露出サーマル・パッドはプリント回路基板のVSSピンと同じ電位に接続する必要があります。サーマル・パッドをデバイスの主グランド入力に使用しないでください。VSSピンは常にグランドに接続しておかなければなりません。 |

(1) 18ピンはbq24038では/PGで、bq24030/2A/5では/ACPGです。

(2) 19ピンはbq24038ではVBSELで、bq24030/5/6では/USBPGです。

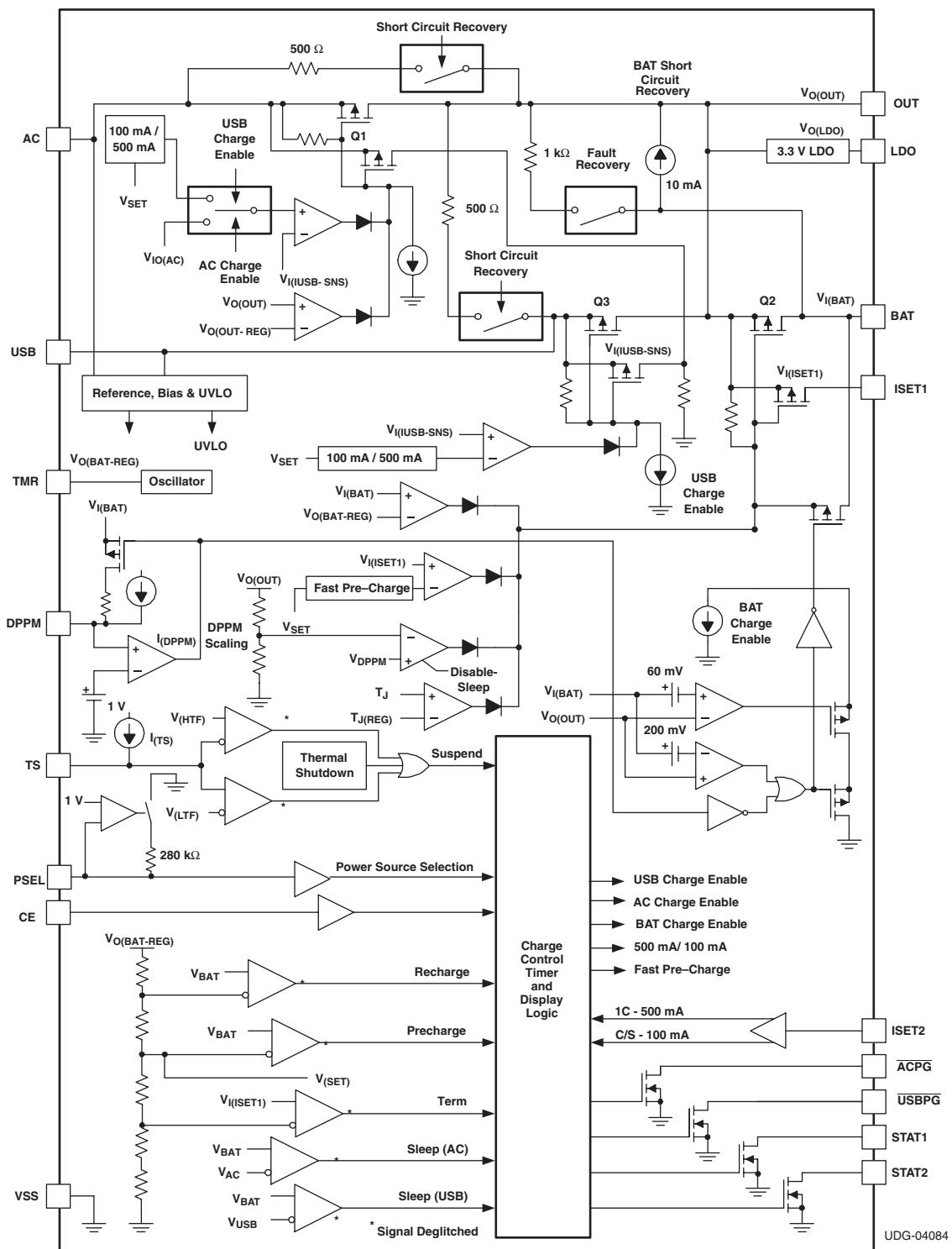

# FUNCTIONAL BLOCK DIAGRAM FOR bq24030/2A/5 ブロック図<sup>(1)</sup>

(1) bq24038については、機能説明の“bq24038の相違点”の項を参照してください。

UDG-04084

## 機能説明

### 充電コントロール

bqTINY-IIIは、単一セルの携帯機器に最適な精密リチウム・イオンまたはリチウム・ポリマー充電システムに対応しています。

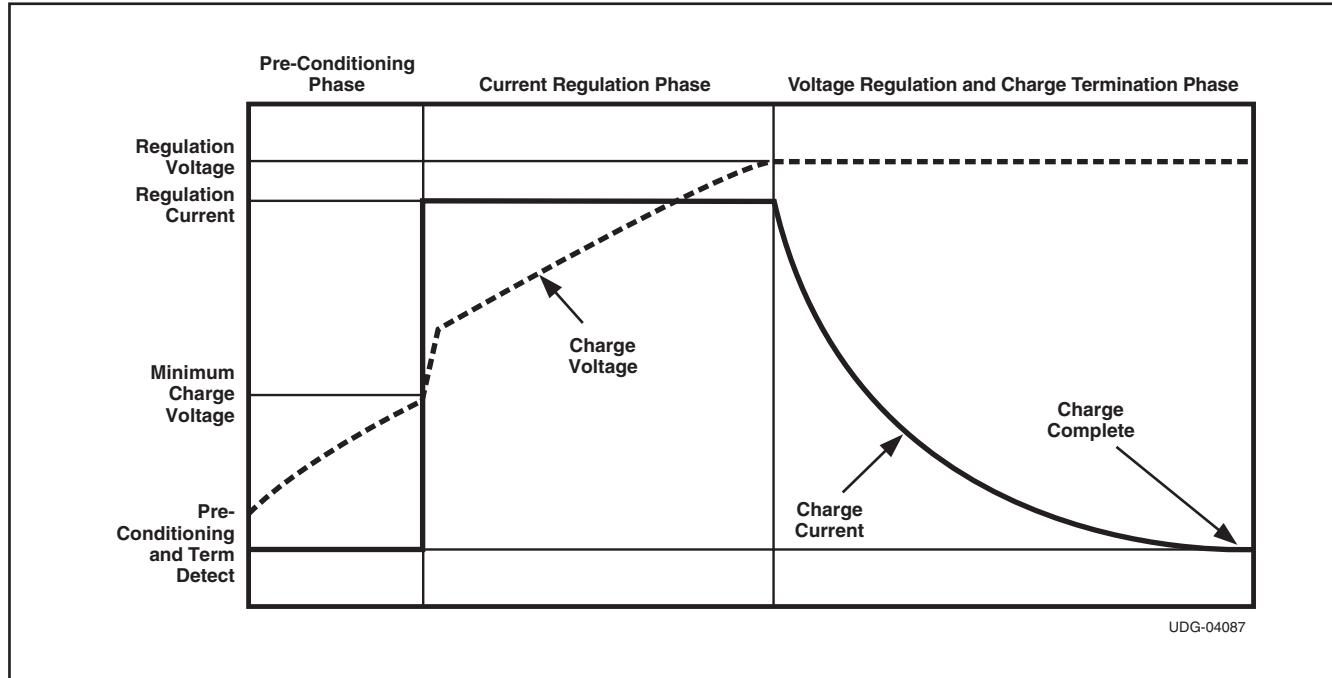

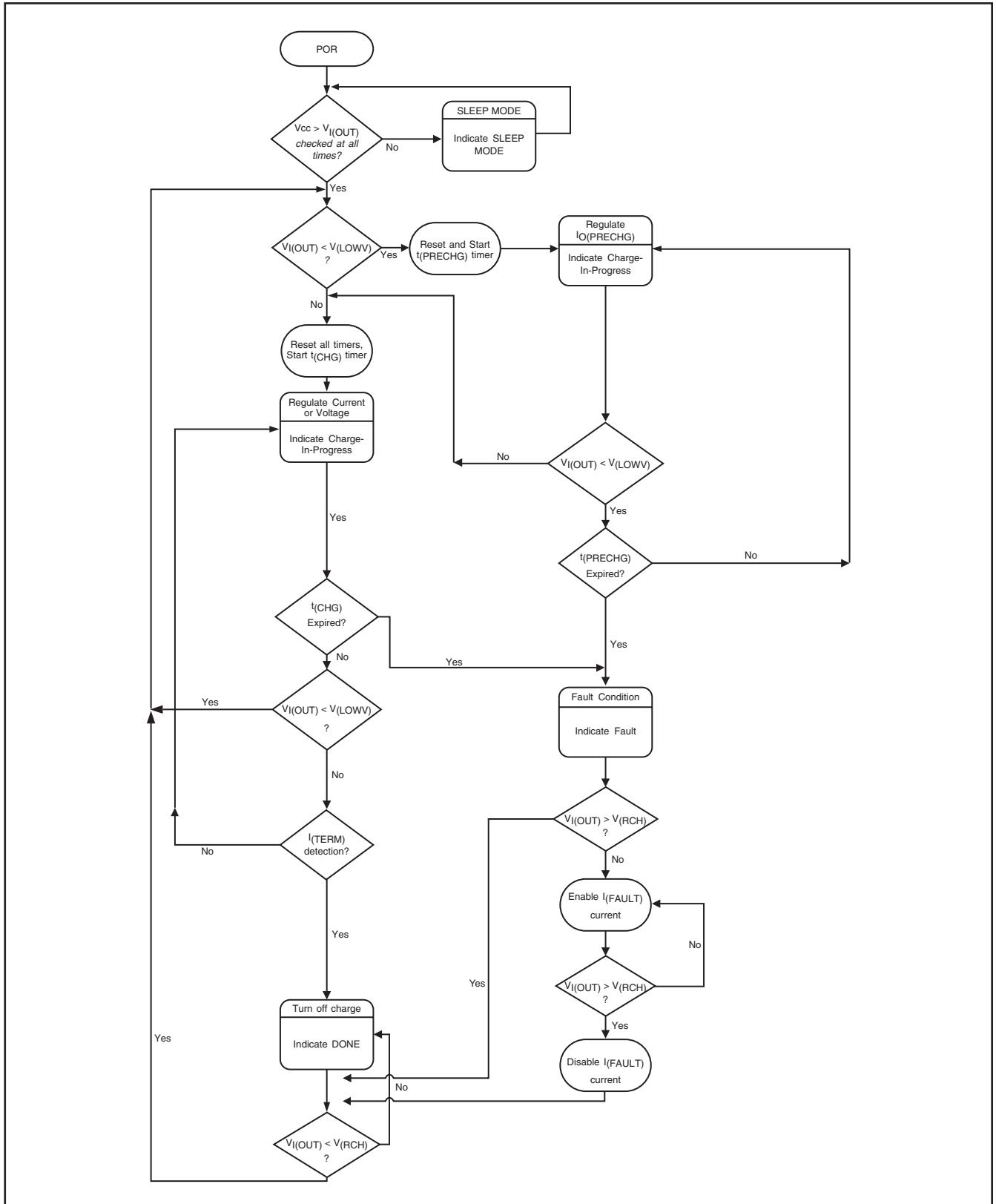

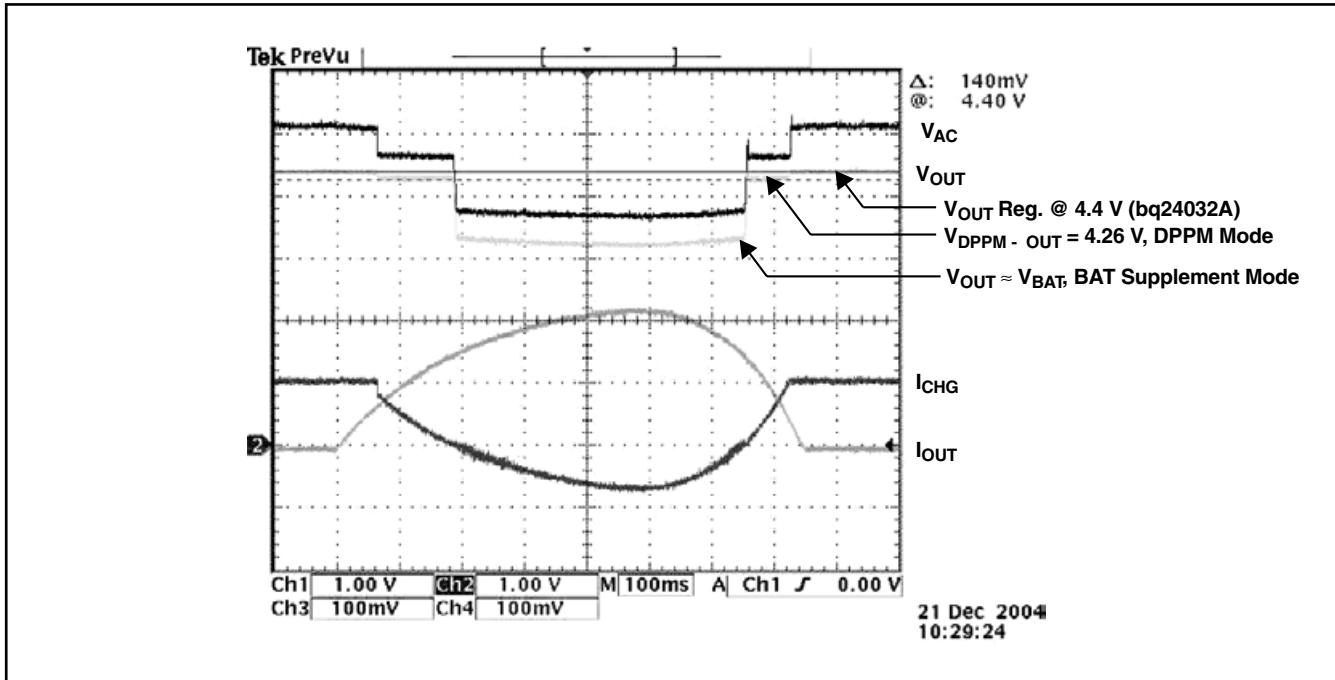

す。図1から図3のそれぞれ代表的充電プロファイル、アプリケーション回路、動作フローチャートを参照してください。

図1. Charge Profile

図2. Typical Application Circuit

图 3. Charge Control Operational Flow Chart

## 自動電源選択 (PSELコントロール・ピン)