# AMC23C12-Q1 車載用、高速応答、強化絶縁型ウィンドウ・コンパレータ、可変スレッショルドおよびラッチ機能付き

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1: -40°C ~ +125°C,  $T_A$

- 広いハイサイド電源電圧範囲: 3V ~ 25V

- ローサイド電源電圧範囲: 2.7V ~ 5.5V

- 可変スレッショルド:

- ウインドウコンパレータモード:  $\pm 20\text{mV} \sim \pm 300\text{mV}$

- 正(非反転)入力を使用するコンパレータモード: 600mV ~ 2.7V

- スレッショルド調整のためのリファレンス電流: 100 $\mu\text{A}$ ,  $\pm 1\%$

- トリップスレッショルドの誤差: 250mV のとき  $\pm 1\%$  (最大値)

- オプションのラッチモードに対応したオープンドレイン出力

- 伝搬遅延: 280 ns (標準値)

- 「高 CMTI: 55V/ns (最小値)

- 安全関連認証:

- DIN EN IEC 60747-17 (VDE 0884-17) に準拠した強化絶縁耐圧: 7000V<sub>PK</sub>

- UL 1577 に準拠した絶縁耐圧: 5000V<sub>RMS</sub> (1分間)

## 2 アプリケーション

- 次の用途での過電流または過電圧検出:

- HEV/EV 充電パイル

- HEV/EV のオンボード・チャージャ (OBC)

- HEV/EV の DC/DC コンバータ

- HEV/EV のトラクション・インバータ

## 3 概要

AMC23C12-Q1 は、応答時間が短い絶縁型ウィンドウコンパレータです。そのオープンドレイン出力は、磁気干渉に対して優れた耐性を示す絶縁バリアによって入力回路から分離されています。このバリアは、VDE 0884-17 および UL 1577 に従って最大 5kV<sub>RMS</sub> の強化ガルバニック絶縁を達成していることが認証されており、最大 1kV<sub>RMS</sub> の使用電圧に対応しています。

その比較ウインドウの中心は 0V です。つまり、入力電圧の絶対値がトリップスレッショルド値を超えると、コンパレータはトリップします。トリップスレッショルドは、1 個の外付け抵抗を使って 20mV ~ 300mV の範囲で調整可能です。したがって、比較ウインドウの範囲は  $\pm 20\text{mV} \sim \pm 300\text{mV}$  です。REF ピンの電圧が 550mV より高い場合、負のコンパレータは無効化され、正のコンパレータのみが機能します。このモードのリファレンス電圧は最高 2.7V で、電圧電源の監視に適しています。

透過モード (LATCH 入力を GND2 に接続) では、出力は入力状態に従います。ラッチモードでは、出力はラッチ入力信号の立ち下がりエッジでクリアされます。

AMC23C12-Q1 は 8 ピンのワイドボディ SOIC パッケージで供給され、-40°C ~ +125°C の車載用温度範囲全体で動作が規定されています。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| AMC23C12-Q1 | DWV (SOIC, 8)        | 5.85mm × 11.5mm          |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値で、該当する場合はピンも含まれます。

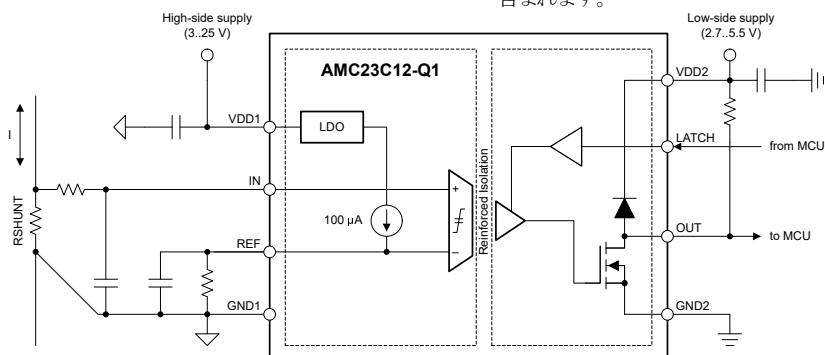

代表的なアプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                 |    |                        |    |

|-----------------|----|------------------------|----|

| 1 特長            | 1  | 6.1 概要                 | 21 |

| 2 アプリケーション      | 1  | 6.2 機能ブロック図            | 21 |

| 3 概要            | 1  | 6.3 機能説明               | 22 |

| 4 ピン構成および機能     | 3  | 6.4 デバイスの機能モード         | 29 |

| 5 仕様            | 4  | 7 アプリケーションと実装          | 29 |

| 5.1 絶対最大定格      | 4  | 7.1 アプリケーション情報         | 29 |

| 5.2 ESD 定格      | 4  | 7.2 代表的なアプリケーション       | 29 |

| 5.3 推奨動作条件      | 5  | 7.3 設計のベスト プラクティス      | 34 |

| 5.4 熱に関する情報     | 5  | 7.4 電源に関する推奨事項         | 35 |

| 5.5 電力定格        | 5  | 7.5 レイアウト              | 35 |

| 5.6 絶縁仕様 (強化絶縁) | 7  | 8 デバイスおよびドキュメントのサポート   | 37 |

| 5.7 安全性関連認証     | 8  | 8.1 ドキュメントのサポート        | 37 |

| 5.8 安全限界値       | 8  | 8.2 ドキュメントの更新通知を受け取る方法 | 37 |

| 5.9 電気的特性       | 9  | 8.3 サポート・リソース          | 37 |

| 5.10 スイッチング特性   | 11 | 8.4 商標                 | 37 |

| 5.11 タイミング図     | 11 | 8.5 静電気放電に関する注意事項      | 37 |

| 5.12 絶縁特性曲線     | 13 | 8.6 用語集                | 37 |

| 5.13 代表的特性      | 14 | 9 改訂履歴                 | 37 |

| 6 詳細説明          | 21 | 10 メカニカル、パッケージ、および注文情報 | 38 |

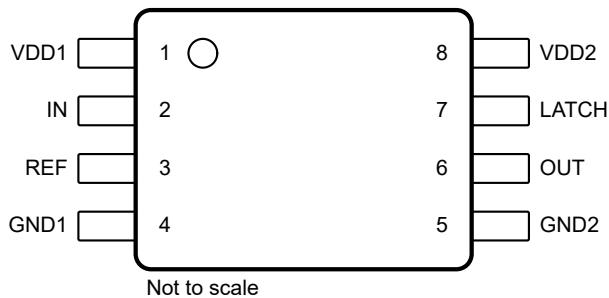

## 4 ピン構成および機能

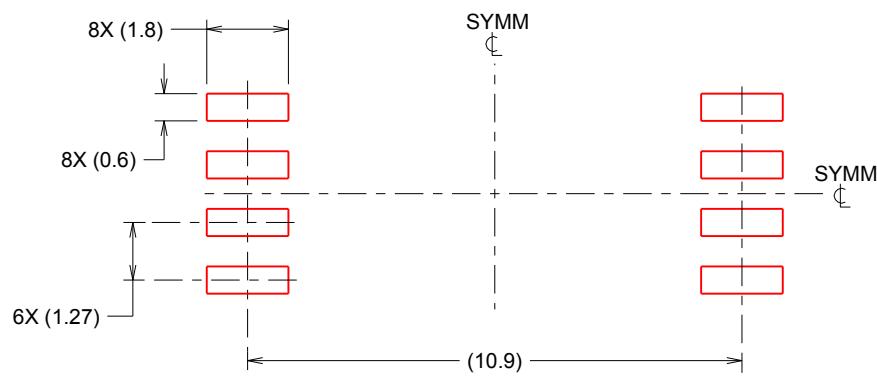

図 4-1. DWV パッケージ、8 ピン SOIC (上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名前 | タイプ        | 説明                                                                                                                                                                                                                                                                                      |

|----|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | VDD1     | ハイサイド電源    | ハイサイド電源 <sup>(1)</sup>                                                                                                                                                                                                                                                                  |

| 2  | IN       | アナログ入力     | ウインドウ コンパレータへのアナログ入力ピン                                                                                                                                                                                                                                                                  |

| 3  | REF      | アナログ入力     | トリップ スレッショルドを定義するリファレンス電圧ピン。「リファレンス入力」セクションで説明しているように、このピンの電圧はコンパレータ Cmp0 のヒステリシスにも影響します。このピンは 100 $\mu$ A の電流源に内部的に接続されています。トリップ スレッショルドを定義するために REF から GND1 に抵抗を接続し、リファレンス電圧をフィルタ処理するために REF から GND1 にコンデンサを接続します。最高の過渡ノイズ耐性を実現するため、コンデンサはピンにできるだけ近づけて配置します。このピンは、外部の電圧源で駆動することもできます。 |

| 4  | GND1     | ハイサイド グランド | ハイサイド グランド                                                                                                                                                                                                                                                                              |

| 5  | GND2     | ローサイド グランド | ローサイド グランド                                                                                                                                                                                                                                                                              |

| 6  | OUT      | デジタル出力     | ウインドウ コンパレータのオープンドレイン出力。外付けプルアップ抵抗に接続します。                                                                                                                                                                                                                                               |

| 7  | LATCH    | デジタル入力     | オープンドレイン出力のラッチ モード (High) またはトランスペアレント モード (Low) を選択するためのデジタル入力。この入力ピンを未接続 (フローティング) のまにしないでください。未使用時は GND2 に接続します。                                                                                                                                                                     |

| 8  | VDD2     | ローサイド電源    | ローサイド電源 <sup>(1)</sup>                                                                                                                                                                                                                                                                  |

(1) 電源のデカップリングに関する推奨事項については、「[電源に関する推奨事項](#)」セクションを参照してください。

## 5 仕様

### 5.1 絶対最大定格

(1) を参照

|          |                 | 最小値  | 最大値        | 単位 |

|----------|-----------------|------|------------|----|

| 電源電圧     | VDD1～GND1       | -0.3 | 30         | V  |

|          | VDD2～GND2       | -0.3 | 6.5        |    |

| アナログ入力電圧 | REF から GND1 へ   | -0.5 | 6.5        | V  |

|          | IN から GND1 へ    | -6   | 5.5        |    |

| デジタル入力電圧 | LATCH (GND2 基準) | -0.5 | VDD2 + 0.5 | V  |

| デジタル出力電圧 | OUT から GND2 へ   | -0.5 | VDD2 + 0.5 | V  |

| 入力電流     | 連続、電源ピンを除く任意のピン | -10  | 10         | mA |

| 温度       | 接合部、 $T_J$      |      | 150        | °C |

|          | 保存、 $T_{stg}$   | -65  | 150        |    |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、この条件、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗黙的に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                             | 値          | 単位 |

|-------------|------|-------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup> 、HBM ESD 分類レベル 2 準拠 | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM)、AEC Q100-011、CDM ESD 分類レベル C6 準拠            | $\pm 1000$ |    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 5.3 推奨動作条件

動作時周辺温度範囲内 (特に記述のない限り)

|                 |                           |                                | 最小値               | 公称値                 | 最大値 | 単位 |

|-----------------|---------------------------|--------------------------------|-------------------|---------------------|-----|----|

| <b>電源</b>       |                           |                                |                   |                     |     |    |

| $V_{VDD1}$      | ハイサイド電源電圧                 | $VDD1 \sim GND1$               | 3.0               | 5                   | 25  | V  |

| $V_{VDD2}$      | ローサイド電源電圧                 | $VDD2 \sim GND2$               | 2.7               | 3.3                 | 5.5 | V  |

| <b>アナログ入力</b>   |                           |                                |                   |                     |     |    |

| $V_{IN}$        | 入力電圧                      | IN (GND1 基準)、 $VDD1 \leq 4.3V$ | -0.4              | $VDD1 - 0.3$        | 4   | V  |

|                 |                           | IN (GND1 基準)、 $VDD1 > 4.3V$    | -0.4              |                     |     |    |

| $V_{REF}$       | リファレンス電圧、ウインドウ コンパレータ モード | REF から GND1 へ                  | 20 <sup>(2)</sup> | 300                 | 450 | mV |

|                 |                           | 低ヒステリシス モード                    | 20 <sup>(2)</sup> |                     |     |    |

|                 |                           | 高ヒステリシス モード<br>(Cmp0 のみ)       | 600               | 2700 <sup>(1)</sup> |     |    |

|                 | リファレンス電圧のヘッドルーム           | $VDD1 - V_{REF}$               | 1.4               |                     |     | V  |

|                 | REF ピンのフィルタ容量             |                                | 20                | 100                 |     | nF |

| <b>デジタル I/O</b> |                           |                                |                   |                     |     |    |

|                 | デジタル入力電圧                  | LATCH ピン                       | GND2              | $VDD2$              | V   |    |

|                 | デジタル出力電圧                  | OUT から GND2 へ                  | GND2              | $VDD2$              | V   |    |

|                 | シンク電流                     | OUT                            | 0                 | 4                   | mA  |    |

| <b>温度範囲</b>     |                           |                                |                   |                     |     |    |

| $T_A$           | 規定周囲温度                    |                                | -40               | 25                  | 125 | °C |

- リファレンス電圧 ( $V_{REF}$ ) が 1.6V を超える場合、最小限のヘッドルーム ( $V_{VDD1} - V_{REF} = 1.4V$ ) を維持するため、 $V_{VDD1} > V_{VDD1, MIN}$  とする必要があります。

- 本デバイスは、5mV という低い  $V_{REF}$  でテストされています。デバイスは引き続き機能しますが、オフセット誤差により、スイッチング スレッショルドの相対精度が低下する可能性があります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | DWV (SOIC) | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | 8 ピン       |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 102.8      | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 45.1       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 63.0       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 14.3       | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 61.1       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし       | °C/W |

- 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電力定格

| パラメータ    |                | テスト条件                        | 値   | 単位 |

|----------|----------------|------------------------------|-----|----|

| $P_D$    | 最大消費電力 (両サイド)  | $VDD1 = 25V$ 、 $VDD2 = 5.5V$ | 102 | mW |

|          |                | $VDD1 = VDD2 = 5.5V$         | 32  |    |

|          |                | $VDD1 = VDD2 = 3.6V$         | 21  |    |

| $P_{D1}$ | 最大消費電力 (ハイサイド) | $VDD1 = 25 V$                | 90  | mW |

|          |                | $VDD1 = 5.5 V$               | 20  |    |

|          |                | $VDD1 = 3.6 V$               | 13  |    |

| パラメータ    |                | テスト条件        | 値  | 単位 |

|----------|----------------|--------------|----|----|

| $P_{D2}$ | 最大消費電力 (ローサイド) | VDD2 = 5.5 V | 12 | mW |

|          |                | VDD2 = 3.6 V | 8  |    |

## 5.6 絶縁仕様 (強化絶縁)

動作時周辺温度範囲内 (特に記述のない限り)

| パラメータ                                                   |                                  | テスト条件                                                                                                                                                                                                         | 値           | 単位               |

|---------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|

| <b>一般</b>                                               |                                  |                                                                                                                                                                                                               |             |                  |

| CLR                                                     | 外部空間距離 <sup>(1)</sup>            | 空気中での最短のピン間距離                                                                                                                                                                                                 | $\geq 8.5$  | mm               |

| CPG                                                     | 外部沿面距離 <sup>(1)</sup>            | パッケージ表面に沿った最短のピン間距離                                                                                                                                                                                           | $\geq 8.5$  | mm               |

| DTI                                                     | 絶縁間の距離                           | 二重絶縁の最小内部ギャップ (内部距離)                                                                                                                                                                                          | $\geq 15.4$ | $\mu\text{m}$    |

| CTI                                                     | 比較トラッキング インデックス                  | DIN EN 60112 (VDE 0303-11), IEC 60112                                                                                                                                                                         | $\geq 600$  | V                |

|                                                         | 材料グループ                           | IEC 60664-1 に準拠                                                                                                                                                                                               | I           |                  |

|                                                         | IEC 60664-1 に準拠した過電圧カテゴリ         | 定格商用電源 $V_{\text{RMS}}$ が 600V 以下                                                                                                                                                                             | I-III       |                  |

|                                                         |                                  | 定格商用電源 $V_{\text{RMS}}$ が 1000V 以下                                                                                                                                                                            | I-II        |                  |

| <b>DIN EN IEC 60747-17 (VDE 0884-17) <sup>(2)</sup></b> |                                  |                                                                                                                                                                                                               |             |                  |

| $V_{\text{IORM}}$                                       | 最大反復ピーク絶縁電圧                      | AC 電圧で                                                                                                                                                                                                        | 1410        | $V_{\text{PK}}$  |

| $V_{\text{IOWM}}$                                       | 最大定格絶縁動作電圧                       | AC 電圧で (正弦波)                                                                                                                                                                                                  | 1000        | $V_{\text{RMS}}$ |

|                                                         |                                  | DC 電圧で                                                                                                                                                                                                        | 1410        | $V_{\text{DC}}$  |

| $V_{\text{IOTM}}$                                       | 最大過渡絶縁電圧                         | $V_{\text{TEST}} = V_{\text{IOTM}}, t = 60\text{s}$ (認定試験)、<br>$V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}}, t = 1\text{s}$ (100% 出荷時テスト)                                                                    | 7070        | $V_{\text{PK}}$  |

| $V_{\text{IMP}}$                                        | 最大インパルス電圧 <sup>(3)</sup>         | 気中でテスト、IEC 62368-1 に準拠した 1.2/50 $\mu\text{s}$ の波形                                                                                                                                                             | 7700        | $V_{\text{PK}}$  |

| $V_{\text{IOSM}}$                                       | 最大サーボ絶縁電圧 <sup>(4)</sup>         | IEC 62368-1 に準拠し油中でテスト (認定試験)、<br>1.2/50 $\mu\text{s}$ の波形                                                                                                                                                    | 10000       | $V_{\text{PK}}$  |

| $q_{\text{pd}}$                                         | 見掛けの電荷 <sup>(5)</sup>            | 手法 a、入力 / 出力安全性テストのサブグループ 2 および 3 の後、<br>$V_{\text{pd}(\text{ini})} = V_{\text{IOTM}}, t_{\text{ini}} = 60\text{s}, V_{\text{pd}(\text{m})} = 1.2 \times V_{\text{IORM}}, t_{\text{m}} = 10\text{s}$          | $\leq 5$    | pC               |

|                                                         |                                  | 手法 a、環境テストのサブグループ 1 の後、<br>$V_{\text{pd}(\text{ini})} = V_{\text{IOTM}}, t_{\text{ini}} = 60\text{s}, V_{\text{pd}(\text{m})} = 1.6 \times V_{\text{IORM}}, t_{\text{m}} = 10\text{s}$                        | $\leq 5$    |                  |

|                                                         |                                  | 手法 b1、事前条件設定 (タイプ テスト) およびルーチン テスト、<br>$V_{\text{pd}(\text{ini})} = 1.2 \times V_{\text{IOTM}}, t_{\text{ini}} = 1\text{s}, V_{\text{pd}(\text{m})} = 1.875 \times V_{\text{IORM}}, t_{\text{m}} = 1\text{s}$ | $\leq 5$    |                  |

|                                                         |                                  | 手法 b2、ルーチン テスト (100% 出荷時) <sup>(7)</sup><br>$V_{\text{pd}(\text{ini})} = V_{\text{pd}(\text{m})} = 1.2 \times V_{\text{IOTM}}, t_{\text{ini}} = t_{\text{m}} = 1\text{s}$                                     | $\leq 5$    |                  |

| $C_{\text{IO}}$                                         | バリア容量、<br>入力から出力へ <sup>(6)</sup> | $V_{\text{IO}} = 0.5V_{\text{PP}}$ (1MHz 時)                                                                                                                                                                   | $\cong 1.5$ | pF               |

| $R_{\text{IO}}$                                         | 絶縁抵抗、<br>入力から出力へ <sup>(6)</sup>  | $V_{\text{IO}} = 500\text{V}$ ( $T_A = 25^\circ\text{C}$ 時)                                                                                                                                                   | $> 10^{12}$ | $\Omega$         |

|                                                         |                                  | $V_{\text{IO}} = 500\text{V}$ ( $100^\circ\text{C} \leq T_A \leq 125^\circ\text{C}$ 時)                                                                                                                        | $> 10^{11}$ |                  |

|                                                         |                                  | $V_{\text{IO}} = 500\text{V}$ ( $T_S = 150^\circ\text{C}$ 時)                                                                                                                                                  | $> 10^9$    |                  |

|                                                         | 汚染度                              |                                                                                                                                                                                                               | 2           |                  |

|                                                         | 耐候性カテゴリ                          |                                                                                                                                                                                                               | 55/125/21   |                  |

| <b>UL1577</b>                                           |                                  |                                                                                                                                                                                                               |             |                  |

| $V_{\text{ISO}}$                                        | 絶縁耐圧                             | $V_{\text{TEST}} = V_{\text{ISO}}, t = 60\text{s}$ (認定試験)、<br>$V_{\text{TEST}} = 1.2 \times V_{\text{ISO}}, t = 1\text{s}$ (100% 出荷時テスト)                                                                      | 5000        | $V_{\text{RMS}}$ |

- (1) アプリケーションに固有の機器の絶縁規格に従って沿面距離および空間距離の要件を適用します。基板設計では、沿面距離および空間距離を維持し、プリント基板 (PCB) のアイソレータの取り付けパッドによりこの距離が短くならないよう注意が必要です。特定の場合には、PCB 上の沿面距離と空間距離は等しくなります。これらの規格値を増やすため、PCB 上にグループやリブを挿入するなどの技法が使用されます。

- (2) この絶縁素子は、安全定格内の安全な電気的絶縁のみに適しています。安全定格への準拠は、適切な保護回路によって保証する必要があります。

- (3) テストは、パッケージのサーボ耐性を判定するため、空気中で実行されます。

- (4) テストは、絶縁バリアの固有サーボ耐性を判定するため、油中で実行されます。

- (5) 見掛けの放電電荷とは、部分放電 (pd) により発生する放電です。

- (6) バリアのそれぞれの側にあるすべてのピンは互いに接続され、実質的に 2 ピンのデバイスになります。

- (7) 正式運用環境では、手法 b1 または b2 のいずれかが使用されます。

## 5.7 安全性関連認証

| VDE                                                                                                                                                   | UL                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| DIN EN IEC 60747-17 (VDE 0884-17),<br>EN IEC 60747-17,<br>DIN EN IEC 62368-1 (VDE 0868-1),<br>EN IEC 62368-1,<br>IEC 62368-1 条項:5.4.3, 5.4.4.4, 5.4.9 | 1577 component および<br>CSA component acceptance NO 5 programs により承認済み |

| 強化絶縁                                                                                                                                                  | 単一保護                                                                 |

| 認証書番号:40040142                                                                                                                                        | ファイル番号:E181974                                                       |

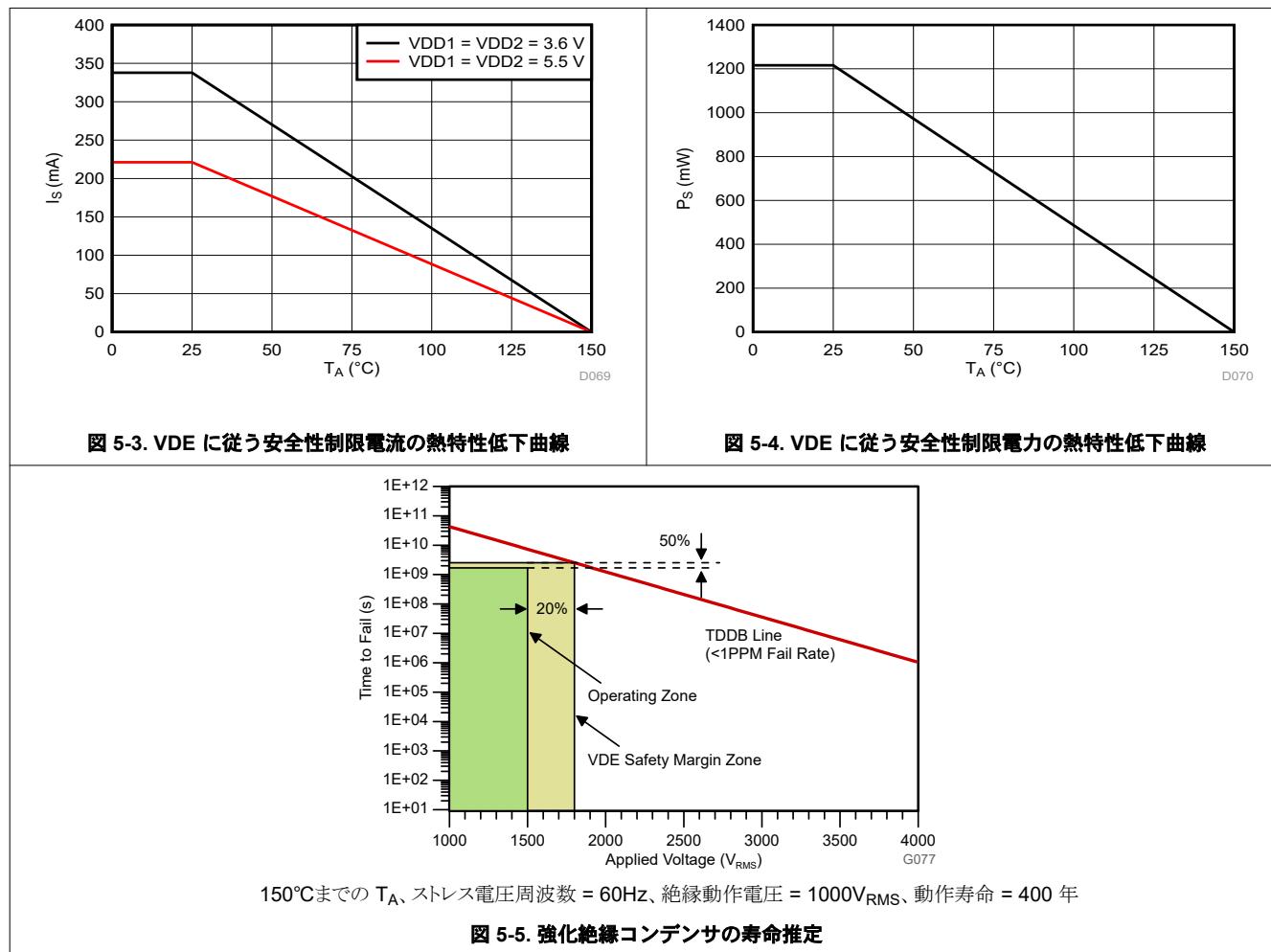

## 5.8 安全限界値

安全限界値<sup>(1)</sup>の目的は、入力または出力回路の故障による絶縁バリアの損傷の可能性を最小限に抑えることです。I/O回路の故障により、グランドあるいは電源との抵抗が低くなることがあります。電流制限がないと、チップがオーバーヒートして絶縁バリアが破壊されるほどの大電力が消費され、ひいてはシステムの2次故障に到る可能性があります。

| パラメータ |                 | テスト条件                                                                                                                                           | 最小値 | 標準値 | 最大値  | 単位 |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| Is    | 安全入力、出力、または電源電流 | $R_{\theta JA} = 102.8^{\circ}\text{C}/\text{W}$ ,<br>$VDD1 = VDD2 = 5.5\text{V}$ ,<br>$T_J = 150^{\circ}\text{C}$ , $T_A = 25^{\circ}\text{C}$ |     |     | 220  | mA |

|       |                 | $R_{\theta JA} = 102.8^{\circ}\text{C}/\text{W}$ ,<br>$VDD1 = VDD2 = 3.6\text{V}$ ,<br>$T_J = 150^{\circ}\text{C}$ , $T_A = 25^{\circ}\text{C}$ |     |     | 340  |    |

| Ps    | 安全入力、出力、または合計電力 | $R_{\theta JA} = 102.8^{\circ}\text{C}/\text{W}$ ,<br>$T_J = 150^{\circ}\text{C}$ , $T_A = 25^{\circ}\text{C}$                                  |     |     | 1220 | mW |

| Ts    | 最高安全温度          |                                                                                                                                                 |     |     | 150  | °C |

- (1) 最高安全温度  $T_S$  は、本デバイスに規定された最大接合部温度  $T_J$  と同じ値です。Is および Ps パラメータはそれぞれ安全電流と安全電力を表します。

Is と Ps の上限値を超えないようにします。これらの制限値は周囲温度  $T_A$  によって変化します。

「熱に関する情報」の表にある、接合部から外気への熱抵抗  $R_{\theta JA}$  は、リード付き表面実装パッケージ用の高誘電率テスト基板に実装されたデバイスのものです。これらの式を使って各パラメータの値を計算します。

$T_J = T_A + R_{\theta JA} \times P$ 、ここで P は本デバイスで消費される電力です。

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ 、ここで  $T_{J(max)}$  は最大接合部温度です。

$P_S = I_S \times AVDD_{max} + I_S \times DVDD_{max}$ 、ここで AVDD<sub>max</sub> は最大ハイサイド電圧、DVDD<sub>max</sub> はコントローラ側の最大電源電圧です。

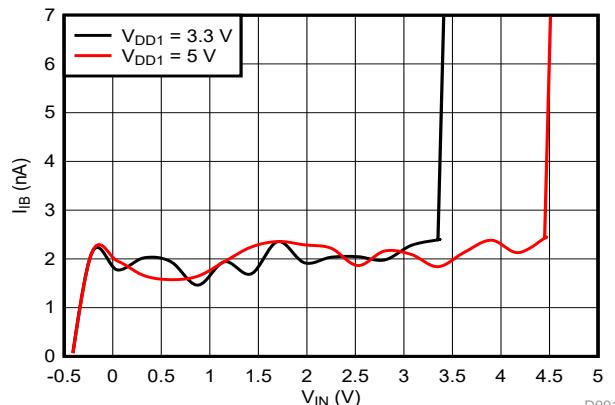

## 5.9 電気的特性

最小値と最大値の仕様には  $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $VDD1 = 3.0\text{V} \sim 25\text{V}$ 、 $VDD2 = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{REF} = 20\text{mV} \sim 2.7\text{V}$ <sup>(1)</sup>、 $V_{IN} = -400\text{mV} \sim 4\text{V}$ <sup>(3)</sup> が適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$ 、 $VDD1 = 5\text{V}$ 、 $VDD2 = 3.3\text{V}$ 、 $V_{REF} = 250\text{mV}$  でのものです (特に記述のない限り)。

| パラメータ           |                             | テスト条件                                                                                     | 最小値               | 標準値                  | 最大値 | 単位               |

|-----------------|-----------------------------|-------------------------------------------------------------------------------------------|-------------------|----------------------|-----|------------------|

| <b>アナログ入力</b>   |                             |                                                                                           |                   |                      |     |                  |

| $R_{IN}$        | 入力抵抗                        | $IN$ ピン、 $0 \leq V_{IN} \leq 4\text{V}$                                                   |                   | 1                    |     | $\text{G}\Omega$ |

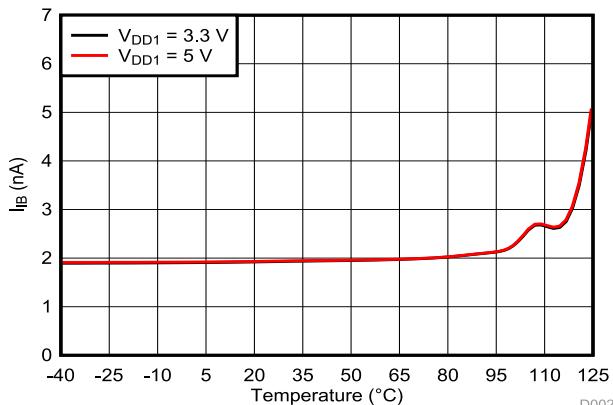

| $I_{BIAS}$      | 入力バイアス電流                    | $IN$ ピン、 $0 \leq V_{IN} \leq 4\text{V}$ <sup>(4)</sup>                                    |                   | 0.1                  | 25  | $\text{nA}$      |

|                 |                             | $IN$ ピン、 $-400\text{mV} \leq V_{IN} \leq 0\text{V}$ <sup>(5)</sup>                        | -310              | -0.5                 |     |                  |

| $C_{IN}$        | 入力容量                        | $IN$ ピン                                                                                   |                   | 4                    |     | $\text{pF}$      |

| <b>リファレンスピン</b> |                             |                                                                                           |                   |                      |     |                  |

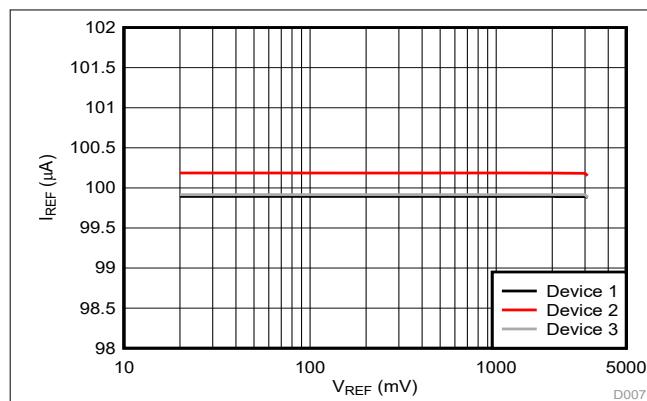

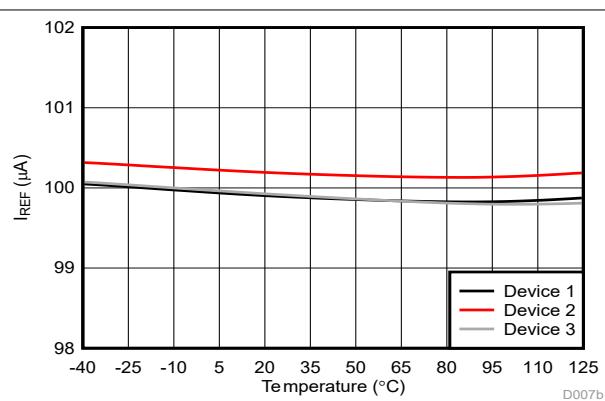

| $I_{REF}$       | リファレンス電流                    | REF から GND1 に流れる電流、 $20\text{mV} < V_{REF} \leq 2.7\text{V}$                              | 99                | 100                  | 101 | $\mu\text{A}$    |

| $V_{MSEL}$      | モード選択スレッショルド <sup>(2)</sup> | $V_{REF}$ 立ち上がり                                                                           | 500               | 550                  | 600 | $\text{mV}$      |

|                 |                             | $V_{REF}$ 立ち下がり                                                                           | 450               | 500                  | 550 |                  |

|                 | モード選択スレッショルドのヒステリシス         |                                                                                           |                   | 50                   |     | $\text{mV}$      |

| <b>コンパレータ</b>   |                             |                                                                                           |                   |                      |     |                  |

| $V_{IT+}$       | 正方向のトリップスレッショルド             | Cmp0                                                                                      |                   | $V_{REF} + V_{HYS}$  |     | $\text{mV}$      |

| $E_{IT+}$       | 正方向のトリップスレッショルドの誤差          | Cmp0、 $(V_{IT+} - V_{REF} - V_{HYS})$ 、 $V_{REF} = 20\text{mV}$ 、 $V_{HYS} = 4\text{mV}$  | -2                | 2                    |     | $\text{mV}$      |

|                 |                             | Cmp0、 $(V_{IT+} - V_{REF} - V_{HYS})$ 、 $V_{REF} = 250\text{mV}$ 、 $V_{HYS} = 4\text{mV}$ | -2                | 2                    |     |                  |

|                 |                             | Cmp0、 $(V_{IT+} - V_{REF} - V_{HYS})$ 、 $V_{REF} = 2\text{V}$ 、 $V_{HYS} = 25\text{mV}$   | -5                | 5                    |     |                  |

| $V_{IT-}$       | 負方向のトリップスレッショルド             | Cmp0                                                                                      |                   | $V_{REF}$            |     | $\text{mV}$      |

| $E_{IT-}$       | 負方向のトリップスレッショルドの誤差          | Cmp0、 $(V_{IT-} - V_{REF})$ 、 $V_{REF} = 20\text{mV}$                                     | -2.5              | 2.5                  |     | $\text{mV}$      |

|                 |                             | Cmp0、 $(V_{IT-} - V_{REF})$ 、 $V_{REF} = 250\text{mV}$                                    | -2.5              | 2.5                  |     |                  |

|                 |                             | Cmp0、 $(V_{IT-} - V_{REF})$ 、 $V_{REF} = 2\text{V}$                                       | -5                | 5                    |     |                  |

| $V_{IT-}$       | 負方向のトリップスレッショルド             | Cmp1                                                                                      |                   | $-V_{REF} - V_{HYS}$ |     | $\text{mV}$      |

| $E_{IT-}$       | 負方向のトリップスレッショルドの誤差          | Cmp1、 $(V_{IT-} + V_{REF} + V_{HYS})$ 、 $V_{REF} = 20\text{mV}$ 、 $V_{HYS} = 4\text{mV}$  | -3                | 3                    |     | $\text{mV}$      |

|                 |                             | Cmp1、 $(V_{IT-} + V_{REF} + V_{HYS})$ 、 $V_{REF} = 250\text{mV}$ 、 $V_{HYS} = 4\text{mV}$ | -3                | 3                    |     |                  |

| $V_{IT+}$       | 正方向のトリップスレッショルド             | Cmp1                                                                                      |                   | $-V_{REF}$           |     | $\text{mV}$      |

| $E_{IT+}$       | 正方向のトリップスレッショルドの誤差          | Cmp1、 $(V_{IT+} + V_{REF})$ 、 $V_{REF} = 20\text{mV}$                                     | -3.5              | 3.5                  |     | $\text{mV}$      |

|                 |                             | Cmp1、 $(V_{IT+} + V_{REF})$ 、 $V_{REF} = 250\text{mV}$                                    | -3.5              | 3.5                  |     |                  |

| $V_{HYS}$       | トリップスレッショルドのヒステリシス          | Cmp0 および Cmp1、 $(V_{IT+} - V_{IT-})$ 、 $V_{REF} \leq 450\text{mV}$                        |                   | 4                    |     | $\text{mV}$      |

|                 |                             | Cmp0 のみ、 $(V_{IT+} - V_{IT-})$ 、 $V_{REF} \geq 600\text{mV}$                              |                   | 25                   |     |                  |

| <b>デジタル I/O</b> |                             |                                                                                           |                   |                      |     |                  |

| $V_{IH}$        | High レベル入力電圧                | LATCH ピン                                                                                  | $0.7 \times VDD2$ | $VDD2 + 0.3$         |     | $\text{V}$       |

| $V_{IL}$        | Low レベル入力電圧                 | LATCH ピン                                                                                  | -0.3              | $0.3 \times VDD2$    |     | $\text{V}$       |

| $C_{IN}$        | 入力容量                        | LATCH ピン                                                                                  |                   | 4                    |     | $\text{pF}$      |

| $V_{OL}$        | Low レベル出力電圧                 | $I_{SINK} = 4\text{mA}$                                                                   |                   | 80                   | 250 | $\text{mV}$      |

| $I_{LKG}$       | オープンドレイン出力リーコンダクタ電流         | $VDD2 = 5\text{V}$ 、 $V_{OUT} = 5\text{V}$                                                |                   | 5                    | 100 | $\text{nA}$      |

| $CMTI$          | 同相過渡耐性                      | $ V_{IN} - V_{REF}  \geq 4\text{mV}$ 、 $R_{PULLUP} = 10\text{k}\Omega$                    | 55                | 110                  |     | $\text{V/ns}$    |

## 5.9 電気的特性 (続き)

最小値と最大値の仕様には  $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $VDD1 = 3.0\text{V} \sim 25\text{V}$ 、 $VDD2 = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{REF}} = 20\text{mV} \sim 2.7\text{V}$ <sup>(1)</sup>、 $V_{\text{IN}} = -400\text{mV} \sim 4\text{V}$ <sup>(3)</sup> が適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$ 、 $VDD1 = 5\text{V}$ 、 $VDD2 = 3.3\text{V}$ 、 $V_{\text{REF}} = 250\text{mV}$  でのものですが (特に記述のない限り)。

| パラメータ               |                          | テスト条件                        | 最小値 | 標準値 | 最大値 | 単位 |

|---------------------|--------------------------|------------------------------|-----|-----|-----|----|

| <b>電源</b>           |                          |                              |     |     |     |    |

| VDD1 <sub>UV</sub>  | VDD1 低電圧検出スレッショルド        | VDD1 の立ち上がり                  |     | 3   |     | V  |

|                     |                          | VDD1 の立ち下がり                  |     | 2.9 |     |    |

| VDD1 <sub>POR</sub> | VDD1 パワー・オン・リセット・スレッショルド | VDD1 の立ち下がり                  |     | 2.3 |     | V  |

| VDD2 <sub>UV</sub>  | VDD2 低電圧検出スレッショルド        | VDD2 の立ち上がり                  |     | 2.7 |     | V  |

|                     |                          | VDD2 の立ち下がり                  |     | 2.1 |     |    |

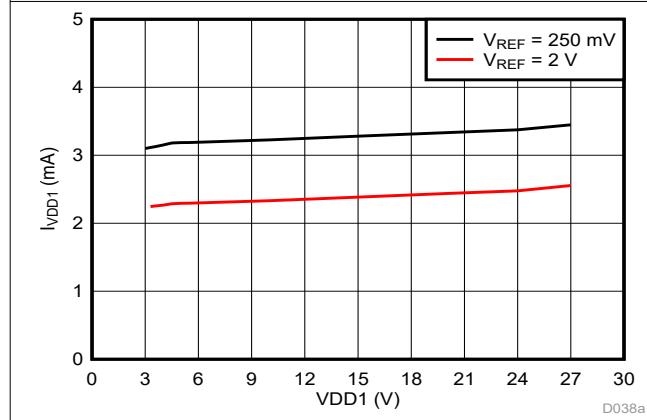

| I <sub>DD1</sub>    | ハイサイド電源電流                | 3.0V $\leq$ VDD1 $\leq$ 3.4V |     | 4.0 |     | mA |

|                     |                          | 3.4V $<$ VDD1 $\leq$ 25V     |     | 3.2 | 4.3 |    |

| I <sub>DD2</sub>    | ローサイド電源電流                |                              | 1.8 | 2.2 |     | mA |

- (1) リファレンス電圧が 1.6V を上回る場合、 $VDD1 > VDD1_{\text{MIN}}$  とする必要があります。詳細については、「推奨動作条件」の表を参照してください。

- (2) 電圧レベル  $V_{\text{REF}}$  によって、本デバイスが正と負のスレッショルドを持つウインドウ・コンパレータとして動作するか、または正のスレッショルドのみを持つ単純なコンパレータとして動作するかが決まります。詳細については、「基準電圧入力」セクションを参照してください。

- (3) しかし、「推奨動作条件」の表に規定された最大入力電圧を超えないようにします。

- (4) 標準値は、 $V_{\text{IN}} = 0.4\text{V}$  で測定されます。

- (5) 標準値は、 $V_{\text{IN}} = -400\text{mV}$  で測定されます。

## 5.10 スイッチング特性

動作時周辺温度範囲内 (特に記述のない限り)

| パラメータ             | テスト条件                    | 最小値                                                              | 標準値 | 最大値 | 単位 |

|-------------------|--------------------------|------------------------------------------------------------------|-----|-----|----|

| <b>LATCH 入力</b>   |                          |                                                                  |     |     |    |

|                   | グリッヂ除去時間                 | 立ち下がりエッジ                                                         | 1.8 | 3.2 | μs |

| <b>オープンドレイン出力</b> |                          |                                                                  |     |     |    |

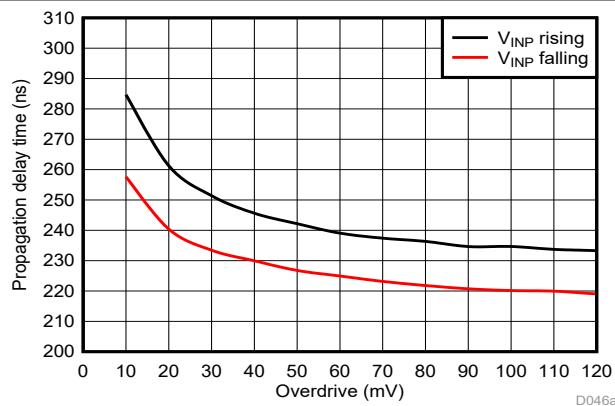

| $t_{pH}$          | 伝搬遅延時間、 $ V_{IN} $ 立ち上がり | $VDD2 = 3.3V, V_{REF} = 250mV, V_{OVERDRIVE} = 10mV, C_L = 15pF$ | 280 | 410 | ns |

|                   |                          | $VDD2 = 3.3V, V_{REF} = 2V, V_{OVERDRIVE} = 50mV, C_L = 15pF$    | 240 | 370 |    |

| $t_{pL}$          | 伝搬遅延時間、 $ V_{IN} $ 立ち下がり | $VDD2 = 3.3V, V_{REF} = 250mV, V_{OVERDRIVE} = 10mV, C_L = 15pF$ | 280 | 410 | ns |

|                   |                          | $VDD2 = 3.3V, V_{REF} = 2V, V_{OVERDRIVE} = 50mV, C_L = 15pF$    | 240 | 370 |    |

| $t_f$             | 出力信号の立ち下がり時間             | $R_{PULLUP} = 4.7k\Omega, C_L = 15pF$                            | 2   |     | ns |

| <b>モード選択</b>      |                          |                                                                  |     |     |    |

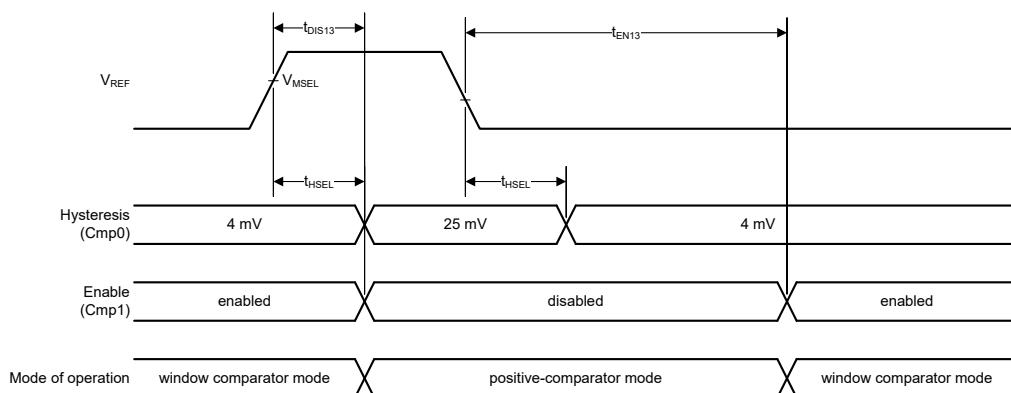

| $t_{HSEL}$        | コンパレータのヒステリシス選択のグリッヂ除去時間 | Cmp0、 $V_{REF}$ 立ち上がりまたは立ち下がり                                    | 10  |     | μs |

| $t_{DIS13}$       | コンパレータのディセーブルのグリッヂ除去時間   | Cmp1、 $V_{REF}$ 立ち上がり                                            | 10  |     | μs |

| $t_{EN13}$        | コンパレータのイネーブルのグリッヂ除去時間    | Cmp1、 $V_{REF}$ 立ち下がり                                            | 100 |     | μs |

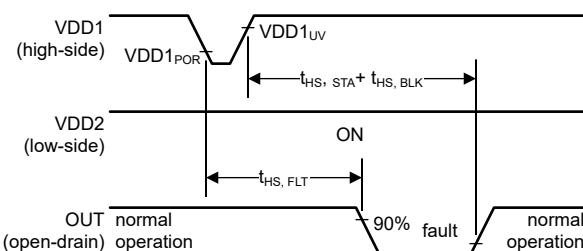

| <b>起動タイミング</b>    |                          |                                                                  |     |     |    |

| $t_{LS, STA}$     | ローサイド起動時間                | $2.7V$ への $VDD2$ のステップ、 $VDD1 \geq 3.0V$                         | 40  |     | μs |

| $t_{HS, STA}$     | ハイサイド起動時間                | $3.0V$ への $VDD1$ のステップ、 $VDD2 \geq 2.7V$                         | 45  |     | μs |

| $t_{HS, BLK}$     | ハイサイドのブランディング時間          |                                                                  | 200 |     | μs |

| $t_{HS, FLT}$     | ハイサイド フォルト検出遅延時間         |                                                                  | 100 |     | μs |

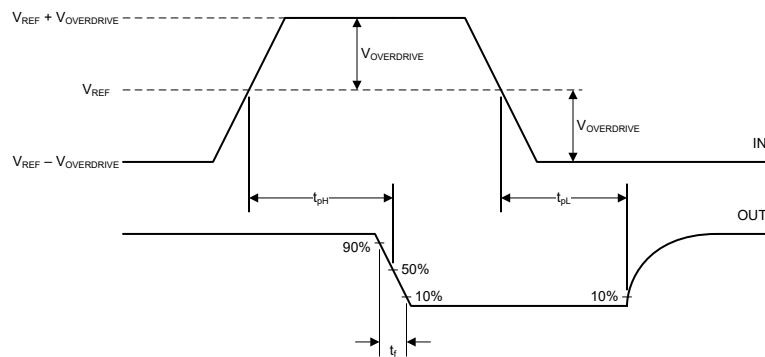

## 5.11 タイミング図

図 5-1. 立ち上がり、立ち下がり、遅延時間の定義 (LATCH = Low)

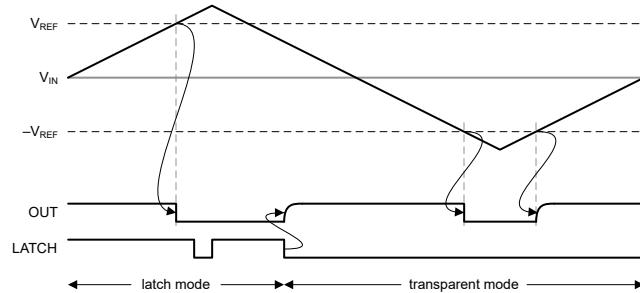

図 5-2. 動作時のタイミング図

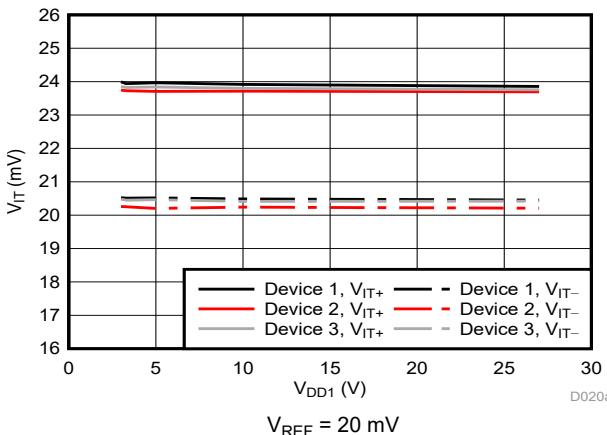

## 5.12 絶縁特性曲線

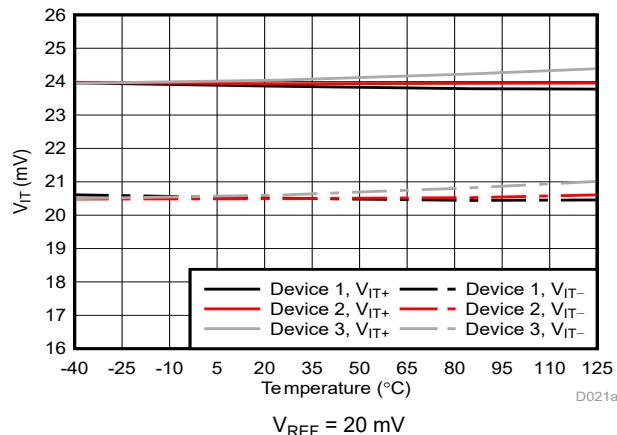

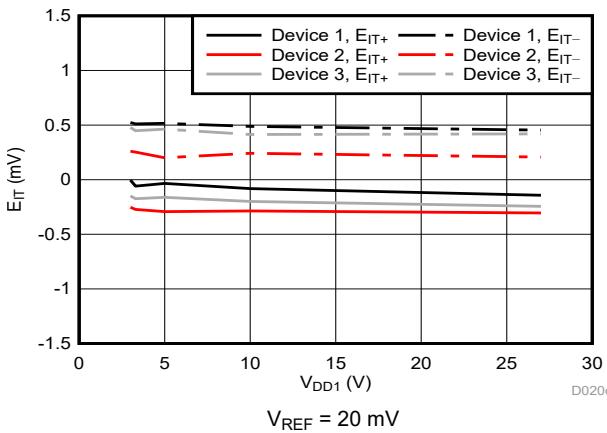

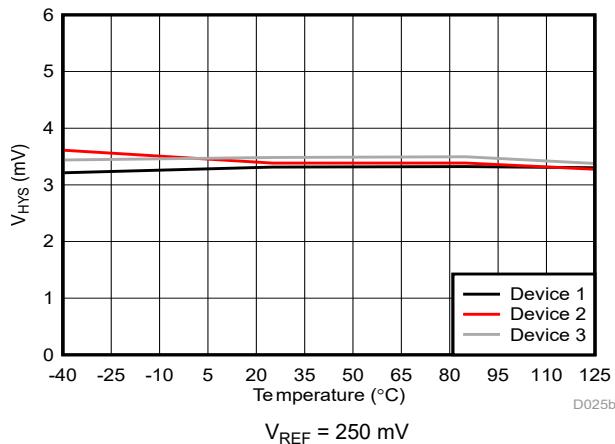

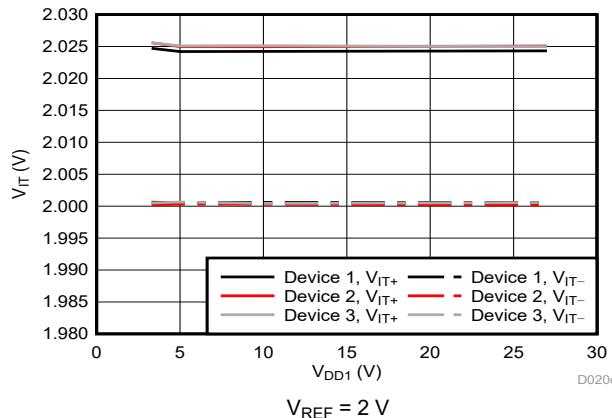

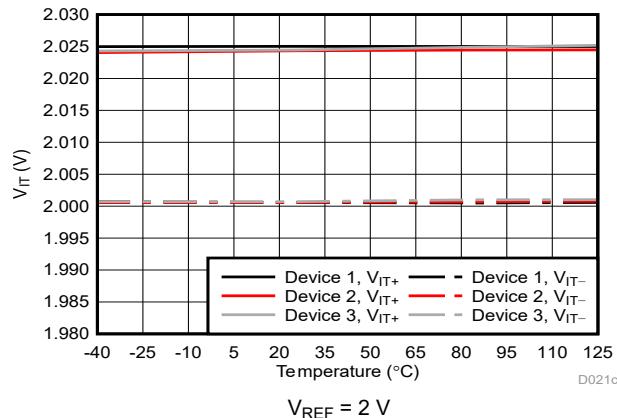

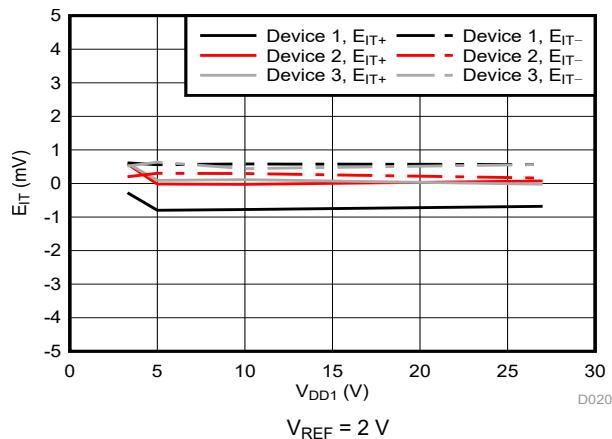

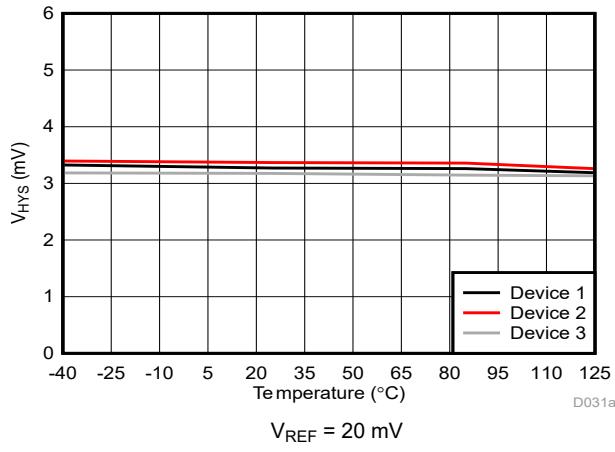

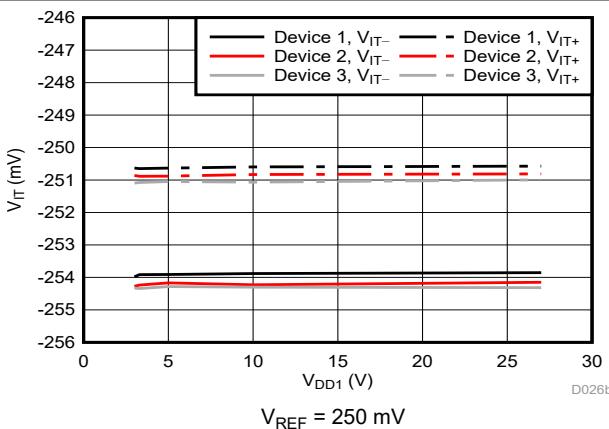

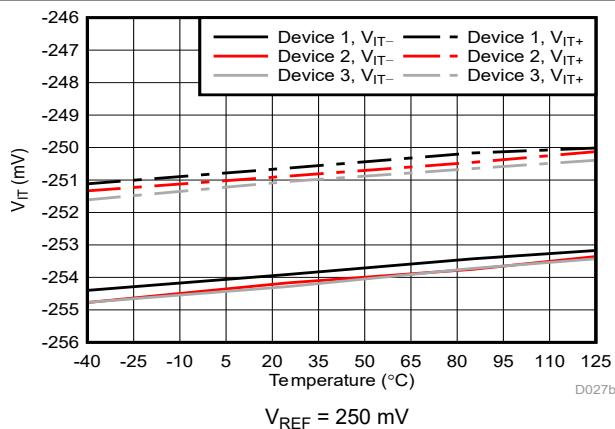

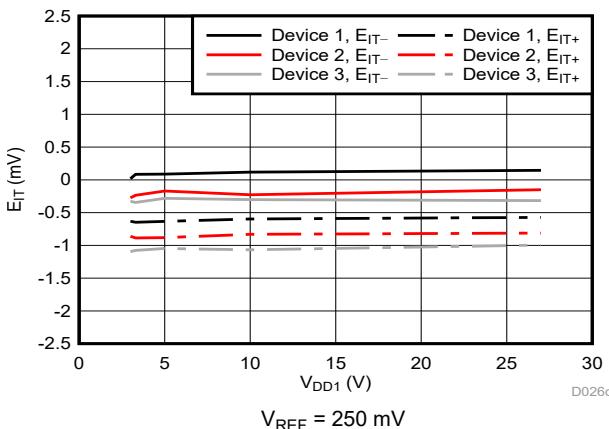

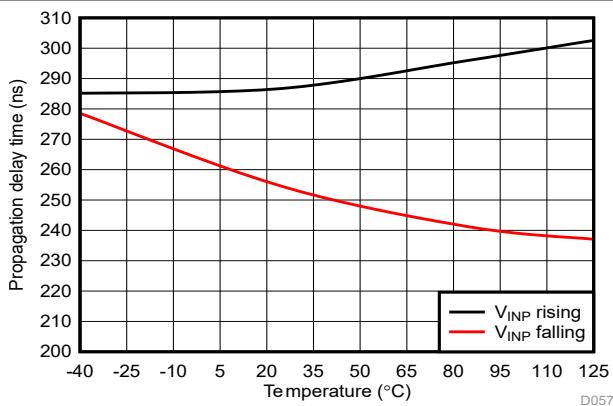

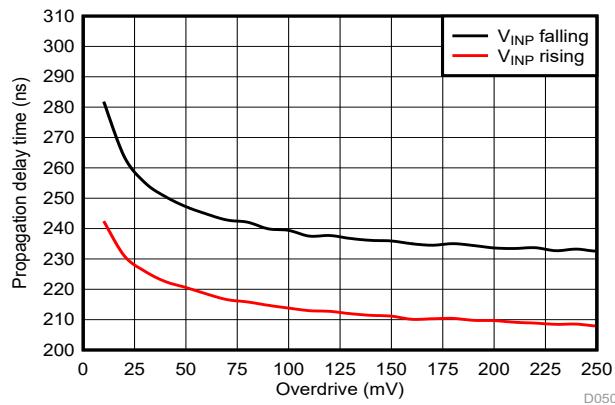

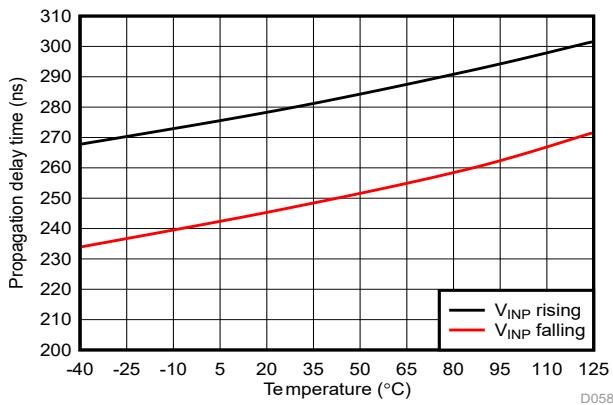

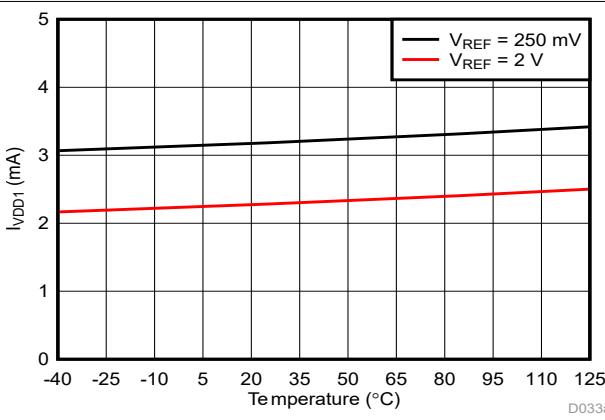

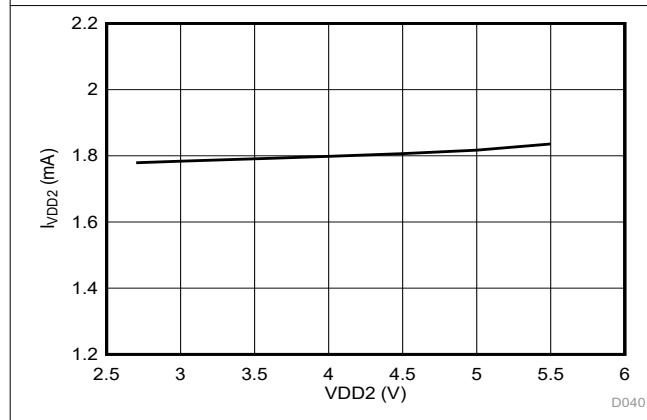

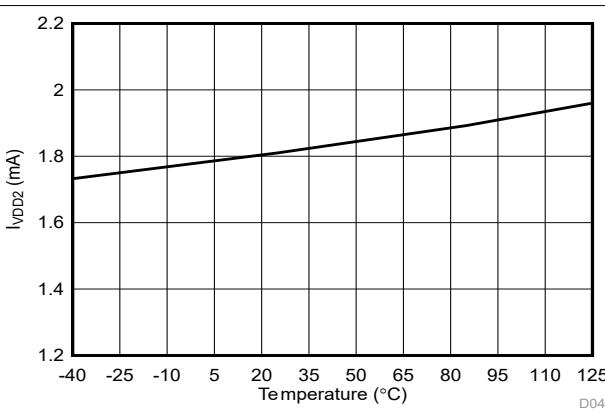

## 5.13 代表的特性

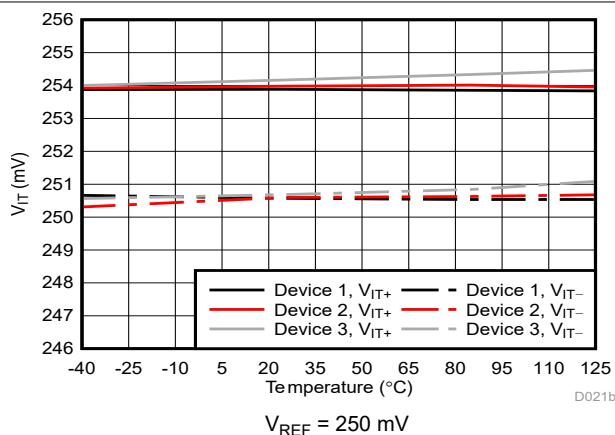

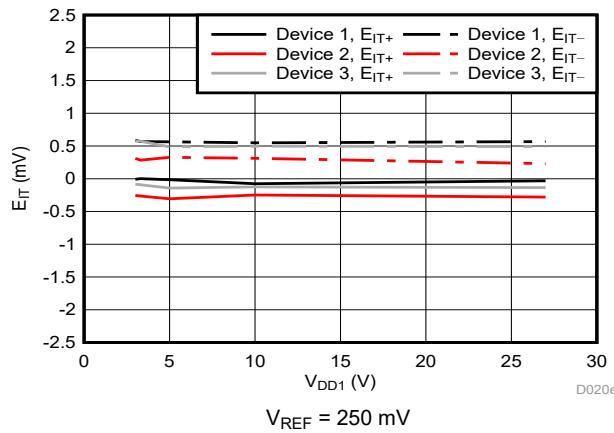

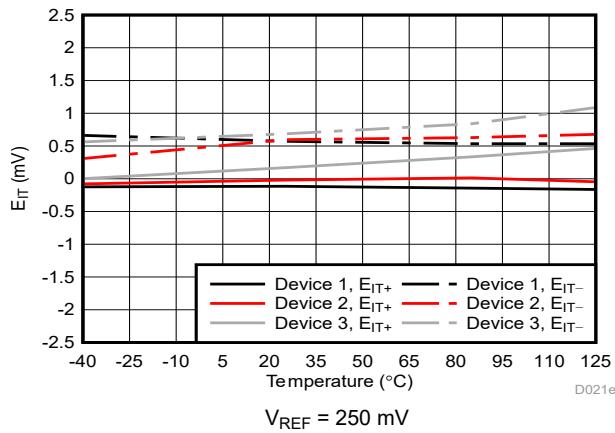

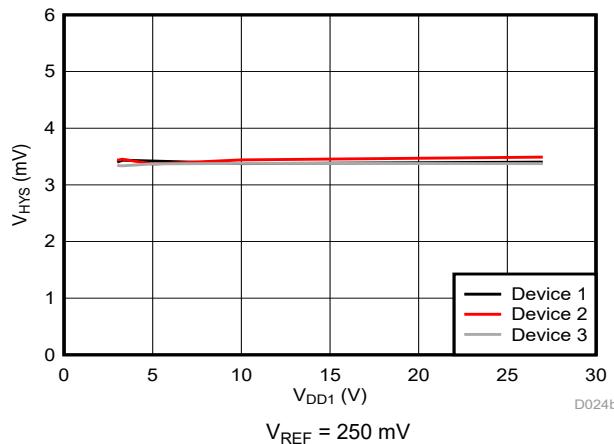

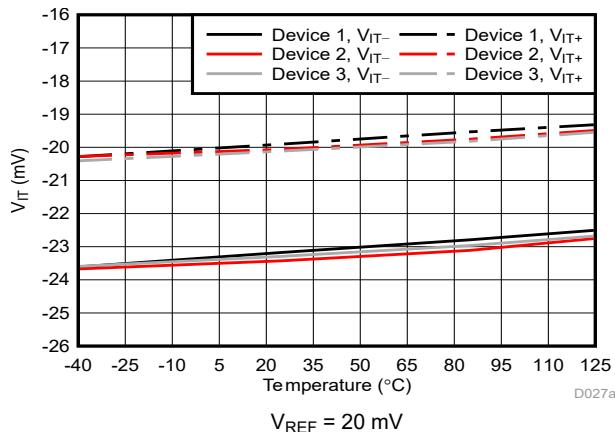

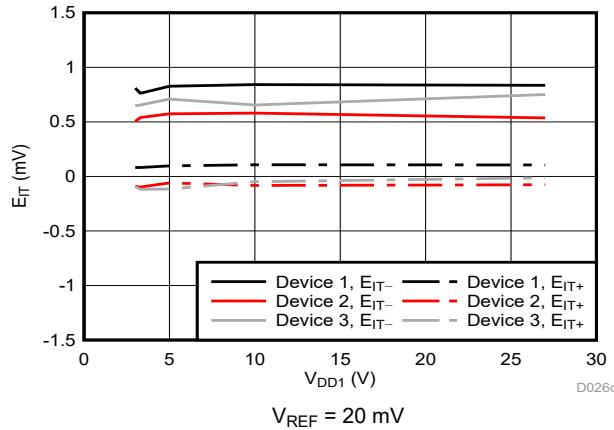

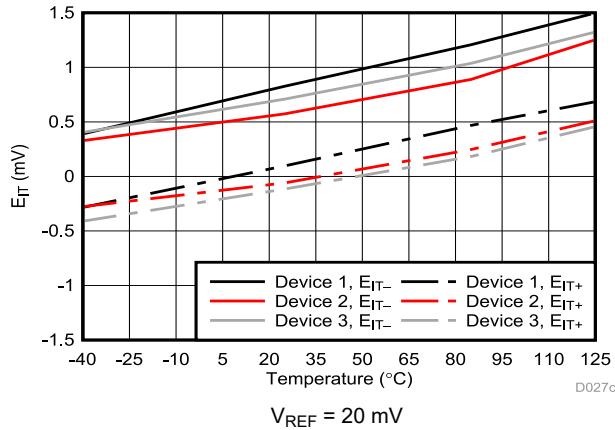

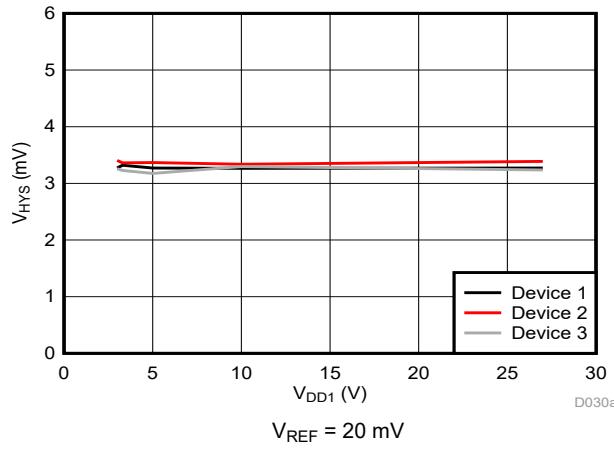

VDD1 = 5V, VDD2 = 3.3V のとき (特に記述のない限り)

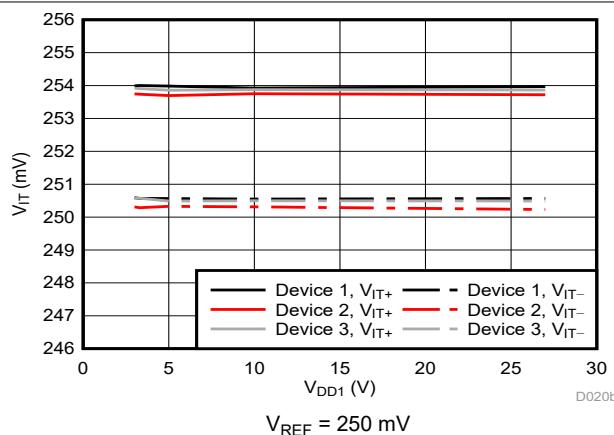

図 5-6. Cmp0 のトリップスレッショルドと電源電圧との関係

図 5-7. Cmp0 のトリップスレッショルドと温度との関係

図 5-8. Cmp0 のトリップスレッショルド誤差と電源電圧との関係

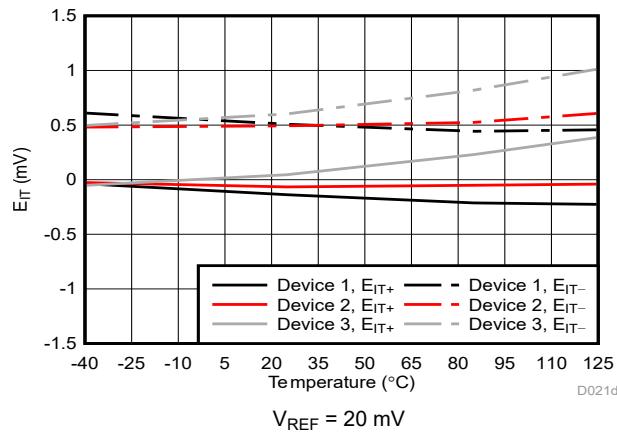

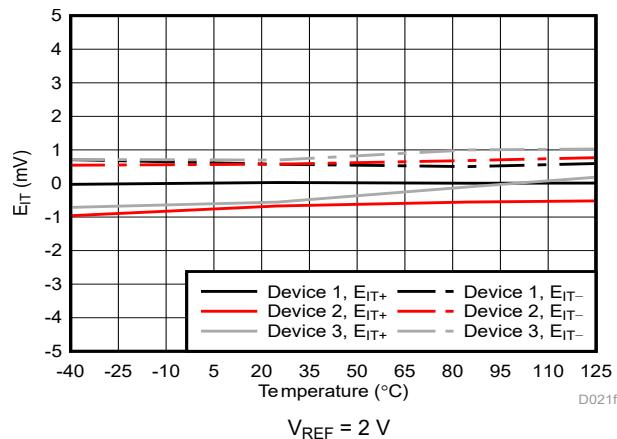

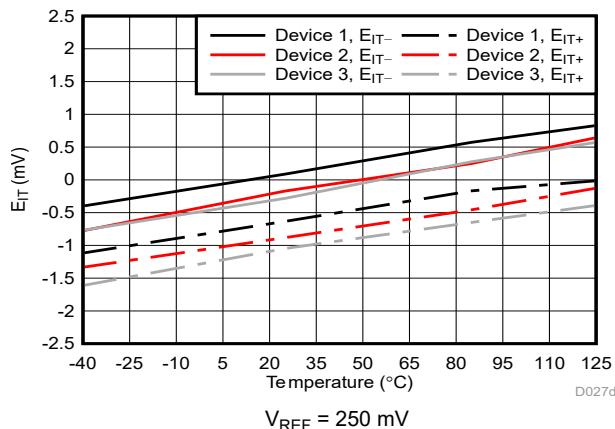

図 5-9. Cmp0 のトリップスレッショルド誤差と温度との関係

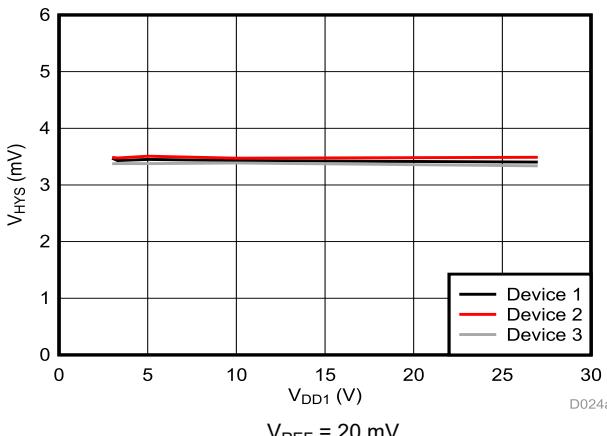

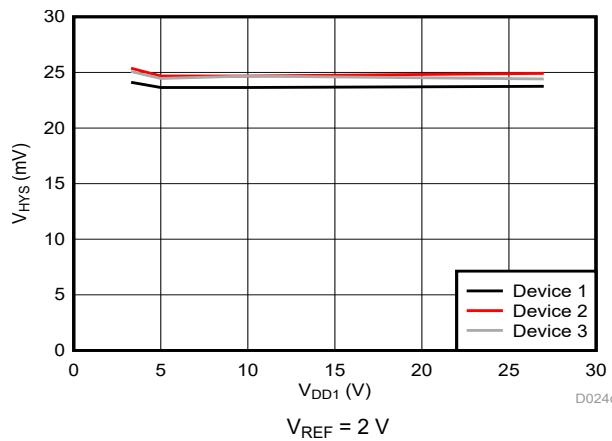

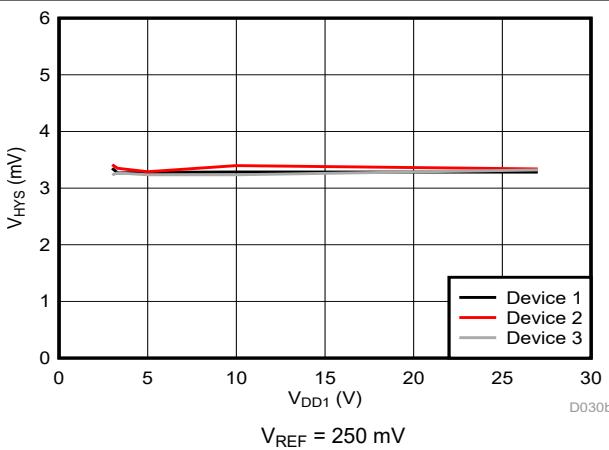

図 5-10. Cmp0 のトリップスレッショルドのヒステリシスと電源電圧との関係

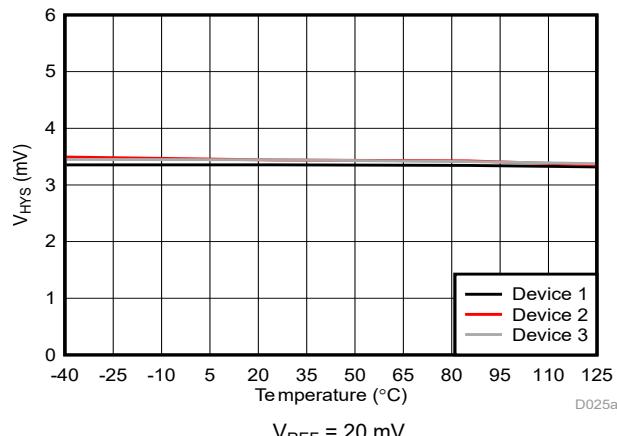

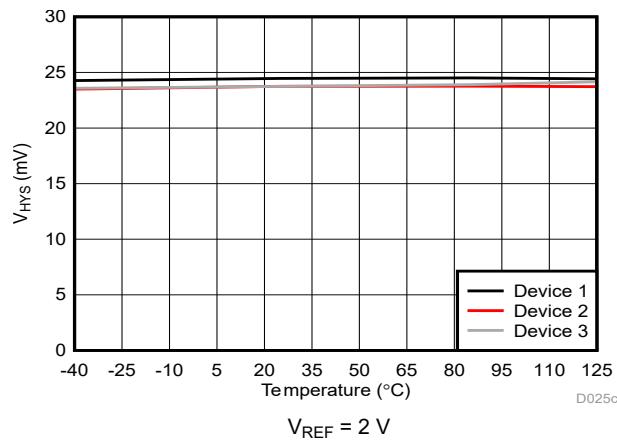

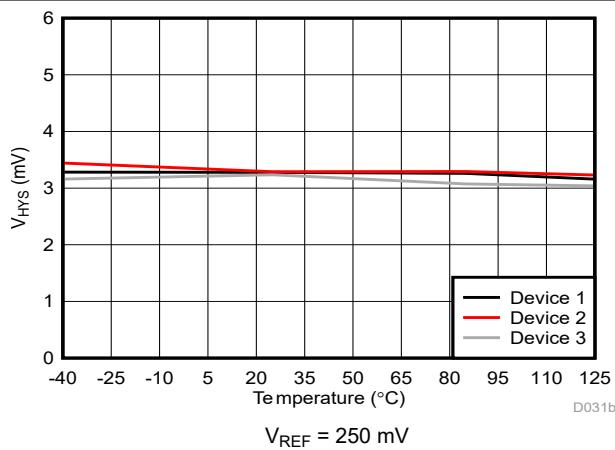

図 5-11. Cmp0 のトリップスレッショルドのヒステリシスと温度との関係

## 5.13 代表的特性 (続き)

VDD1 = 5V, VDD2 = 3.3V のとき (特に記述のない限り)

図 5-12. Cmp0 のトリップスレッショルドと電源電圧との関係

図 5-13. Cmp0 のトリップスレッショルドと温度との関係

図 5-14. Cmp0 のトリップスレッショルド誤差と電源電圧との関係

図 5-15. Cmp0 のトリップスレッショルド誤差と温度との関係

図 5-16. Cmp0 のトリップスレッショルドのヒステリシスと電源電圧との関係

図 5-17. Cmp0 のトリップスレッショルドのヒステリシスと温度との関係

## 5.13 代表的特性 (続き)

VDD1 = 5V, VDD2 = 3.3V のとき (特に記述のない限り)

図 5-18. Cmp0 のトリップスレッショルドと電源電圧との関係

図 5-19. Cmp0 のトリップスレッショルドと温度との関係

図 5-20. Cmp0 のトリップスレッショルド誤差と電源電圧との関係

図 5-21. Cmp0 のトリップスレッショルド誤差と温度との関係

図 5-22. Cmp0 のトリップスレッショルドのヒステリシスと電源電圧との関係

図 5-23. Cmp0 のトリップスレッショルドのヒステリシスと温度との関係

## 5.13 代表的特性 (続き)

VDD1 = 5V, VDD2 = 3.3V のとき (特に記述のない限り)

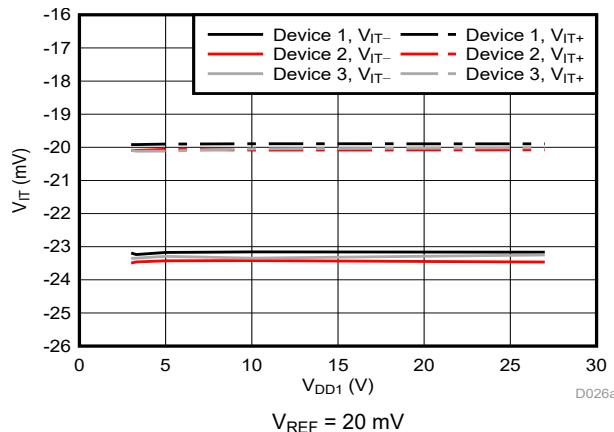

図 5-24. Cmp1 のトリップ スレッショルドと電源電圧との関係

図 5-25. Cmp1 のトリップ スレッショルドと温度との関係

図 5-26. Cmp1 のトリップ スレッショルド誤差と電源電圧との関係

図 5-27. Cmp1 のトリップ スレッショルド誤差と温度との関係

図 5-28. Cmp1 のトリップ スレッショルドのヒステリシスと電源電圧との関係

図 5-29. Cmp1 のトリップ スレッショルドのヒステリシスと温度との関係

## 5.13 代表的特性 (続き)

VDD1 = 5V, VDD2 = 3.3V のとき (特に記述のない限り)

図 5-30. Cmp1 のトリップスレッショルドと電源電圧との関係

図 5-31. Cmp1 のトリップスレッショルドと温度との関係

図 5-32. Cmp1 のトリップスレッショルド誤差と電源電圧との関係

図 5-33. Cmp1 のトリップスレッショルド誤差と温度との関係

図 5-34. Cmp1 のトリップスレッショルドのヒステリシスと電源電圧との関係

図 5-35. Cmp1 のトリップスレッショルドのヒステリシスと温度との関係

## 5.13 代表的特性 (続き)

VDD1 = 5V, VDD2 = 3.3V のとき (特に記述のない限り)

図 5-36. Cmp0 の伝搬遅延とオーバードライブとの関係

図 5-37. Cmp0 の伝搬遅延と温度との関係

図 5-38. Cmp1 の伝搬遅延とオーバードライブとの関係

図 5-39. Cmp1 の伝搬遅延と温度との関係

図 5-40. の入力バイアス電流と入力電圧との関係

図 5-41. の入力バイアス電流と温度との関係

### 5.13 代表的特性 (続き)

VDD1 = 5V、VDD2 = 3.3V のとき (特に記述のない限り)

図 5-42. リファレンス電流とリファレンス電圧との関係

図 5-43. リファレンス電流と温度との関係

図 5-44. ハイサイド電源電流と電源電圧との関係

図 5-45. ハイサイド電源電流と温度との関係

図 5-46. ローサイド電源電流と電源電圧との関係

図 5-47. ローサイド電源電流と温度との関係

## 6 詳細説明

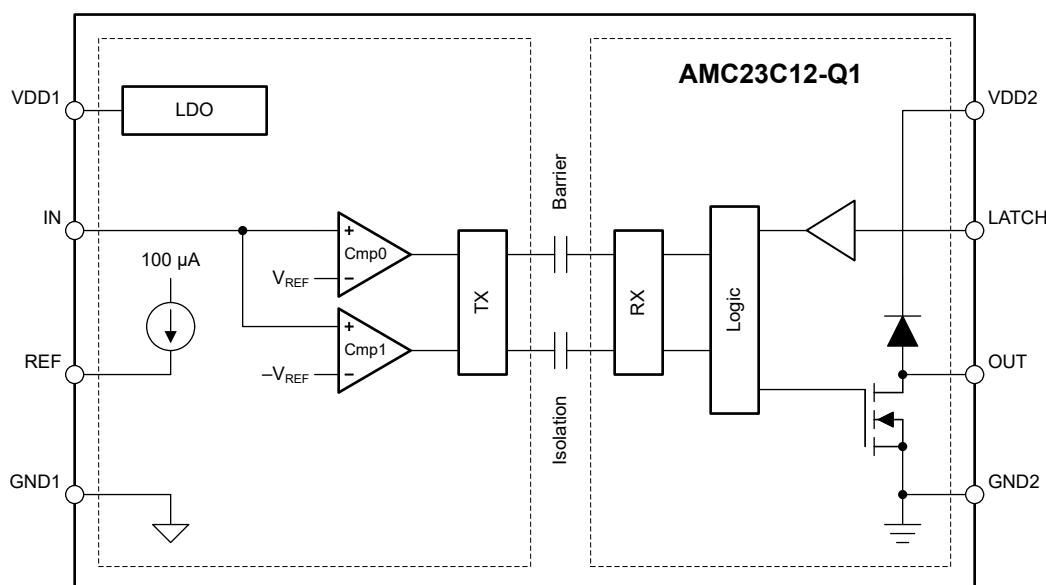

### 6.1 概要

AMC23C12-Q1 は、オープンドレイン出力とオプションのラッチ機能を備えた絶縁型ウインドウコンパレータです。このウインドウコンパレータはコンパレータ Cmp0 および Cmp1 で構成されます。Cmp0 は正のスレッショルド ( $V_{IT+}$ ) と入力電圧 ( $V_{IN}$ ) を比較し、Cmp1 は負のスレッショルド ( $V_{IT-}$ ) と入力電圧 ( $V_{IN}$ ) を比較します。 $V_{IT+}$  と  $V_{IT-}$  は、大きさは同じで符号は逆です。そのため、比較ウインドウの中心は 0V です。比較スレッショルドは、内部生成される  $100\mu\text{A}$  のリファレンス電流と 1 つの外付け抵抗で  $\pm 20\text{mV} \sim \pm 300\text{mV}$  に調整できます。

入力電圧 ( $V_{IN}$ ) が比較ウインドウを外れると、オープンドレイン出力はアクティブに Low になります。 $V_{IN}$  が低下してウインドウ内に戻った際の動作は、「[オープンドレイン デジタル出力](#)」セクションで説明されているように、LATCH ピンによって決まります。

REF ピンの電圧が  $V_{MSEL}$  より高い場合、本デバイスは正のコンパレータ モードで動作します。このモードは、正電圧を監視するのに特に便利です。負のコンパレータ (Cmp1) がディセーブルされ、正のコンパレータ (Cmp0) のみが機能します。このモードでのリファレンス電圧は最大  $2.7\text{V}$  に設定できます。

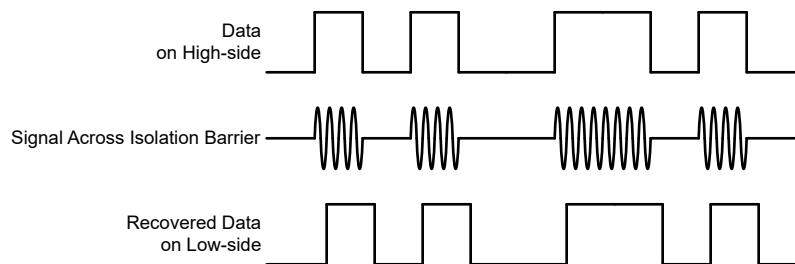

本デバイスの高電圧側と低電圧側の間のガルバニック絶縁は、 $\text{SiO}_2$  ベースの強化容量性絶縁バリア越しにコンパレータの状態を送信することで実現されます。この絶縁バリアは、『[ISO72x デジタルアイソレータの磁界耐性』アプリケーションレポート』に記載されているように、高水準の磁界耐性をサポートします。絶縁バリア越しにデータを送信するために AMC23C12-Q1 が採用しているデジタル変調方式と、絶縁バリアの特性自体により、優れた信頼性と同相過渡耐性が得られます。](#)

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 アナログ入力

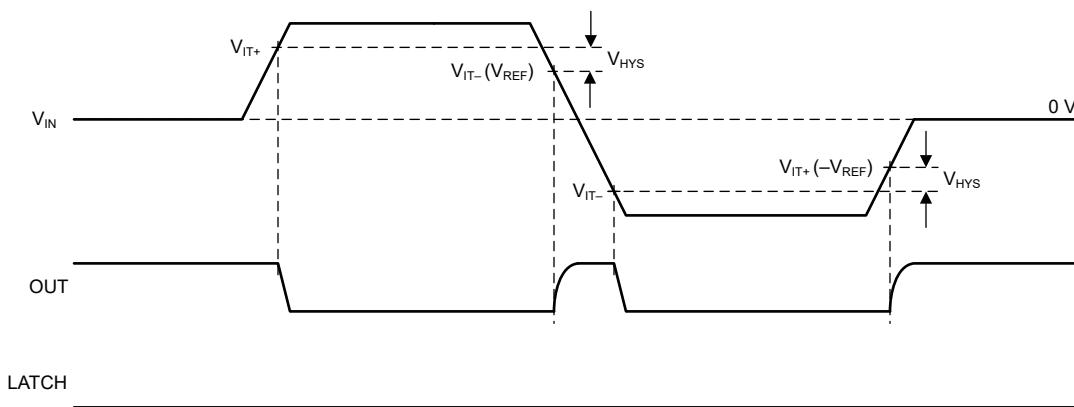

リファレンス値に内部ヒステリシス電圧を加えた値として定義される  $V_{IT+}$  スレッショルドを入力電圧 ( $V_{IN}$ ) が上回ると、正のコンパレータはトリップします。リファレンス値と等しい  $V_{IT-}$  スレッショルドを  $V_{IN}$  が下回ると、正のコンパレータはリリースされます。負のリファレンス値から内部ヒステリシス電圧を引いた値として定義される  $V_{IT-}$  スレッショルドを  $V_{IN}$  が下回ると、負のコンパレータはトリップします。負のリファレンス値と等しい  $V_{IT+}$  スレッショルドを  $V_{IN}$  が上回ると、負のコンパレータはリリースされます。

$V_{IT+}$  と  $V_{IT-}$  の差はコンパレータ ヒステリシスと呼ばれ、リファレンス電圧が 450mV 未満なら 4mV です。あらかじめヒステリシスが組み込まれているため、AMC23C12-Q1 は入力ノイズの影響を受けづらく、ノイズの多い環境でも安定して動作します。ヒステリシスを生成するための外部正帰還を追加する必要はありません。600mV を超えるリファレンス値 ( $V_{REF}$ ) の場合、Cmp0 のヒステリシスは 25mV に増加します。詳細については、「リファレンス入力」の説明を参照してください。

ヒステリシスとスイッチング スレッショルドとの関係を表すタイミング図を、図 6-1 に示します。

図 6-1. スイッチング スレッショルドとヒステリシス

### 6.3.2 リファレンス入力

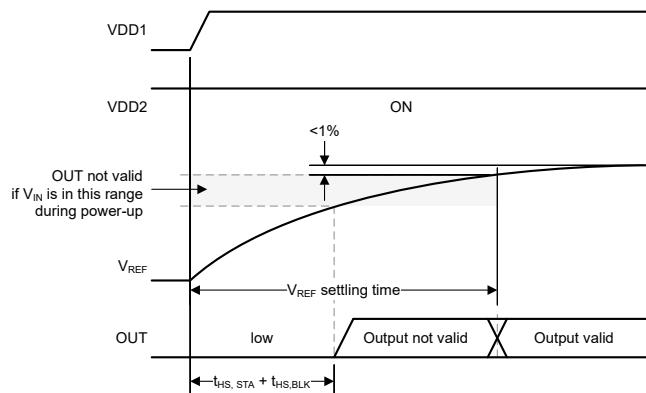

REF ピンの電圧は、ウインドウコンパレータのトリップスレッショルドを決定します。内部の高精度電流源は、REF ピンから GND1 に接続された外部抵抗に  $100\mu\text{A}$  の電流を流します。抵抗の両端に結果として生じる電圧 ( $V_{\text{REF}}$ ) は、正と負のトリップスレッショルドの大きさと等しくなります (図 6-1 を参照)。リファレンス電圧をフィルタ処理するため、抵抗と並列に  $100\text{nF}$  のコンデンサを配置します。このコンデンサは、起動中に  $100\mu\text{A}$  の電流源で充電される必要があり、その充電時間がハイサイドのプランギング時間 ( $t_{\text{HS, BLK}}$ ) を超えることがあります。この場合、図 6-2 に示すように、コンパレータは、ハイサイドのプランギング時間が経過した後で、 $V_{\text{REF}}$  が最終値に達するまでの間、正しくない状態を出力することができます。起動時の動作の詳細については、「パワーアップ動作とパワーダウン動作」セクションを参照してください。

図 6-2. リファレンス電圧のセッティングタイムが長いときの出力の動作

REF ピンの電圧は、負のコンパレータ (Cmp1) の機能と正のコンパレータ (Cmp0) のヒステリシスも決定します (機能ブロック図を参照)。「電気的特性」表に定義された  $V_{\text{MSEL}}$  スレッショルドを  $V_{\text{REF}}$  が上回ると、Cmp1 はディセーブルされ、Cmp0 のヒステリシスは  $4\text{mV}$  (標準値) から  $25\text{mV}$  に増加します。正のコンパレータモードは、高い入力電圧と高いノイズ耐性が必要な電圧監視アプリケーションを目的としています。

リファレンス電圧ピンは、動作中にコンパレータのスレッショルドを変更するために外部電圧源で駆動することもできます。しかし、通常動作中に  $V_{\text{MSEL}}$  スレッショルドを超えて  $V_{\text{REF}}$  を動的に駆動してはいけません。それにより、Cmp0 コンパレータのヒステリシスが変化し、出力が意図せずに切り替わる可能性があるためです。

図 6-3 に、モード選択のタイミング図を示します。

図 6-3. モード選択

### 6.3.3 絶縁チャネルの信号伝送

AMC23C12-Q1 は、 $\text{SiO}_2$  ベースの絶縁バリア越しにコンパレータの出力状態を送信するため、図 6-4 に示すオン / オフキーイング (OOK) 変調方式を採用しています。「機能ブロック図」に示す送信ドライバ (TX) は、デジタル 1 を表すために内部で生成された高周波キャリアを絶縁バリア越しに送信します。デジタル 0 を表す信号は送りません。

絶縁バリアの反対側のレシーバ (RX) は信号を回復および復調し、オープンドレイン出力バッファを駆動するロジックにデータを提供します。AMC23C12-Q1 の送信チャネルは、同相過渡耐性 (CMTI) を最大限に高め、高周波キャリアと RX/TX バッファのスイッチングに起因する放射妨害波を最小限に抑えるように最適化されています。

図 6-4. OOK ベースの変調方式

### 6.3.4 オープンドレインデジタル出力

AMC23C12-Q1 はラッチ機能付きオープンドレイン出力を備えています。REF ピンの電圧によって定義されたスレッショルド値を  $|V_{IN}|$  が上回ると、出力はアクティブに **Low** になります (図 6-1 を参照)。

オープンドレイン出力には、VDD2 電源に対してダイオードが接続されています (「機能ブロック図」を参照)。これは、OUT ピンに大電流が流れ込み始めない限り、VDD2 電源電圧より 500mV を超えて出力されないことを意味しています。特に VDD2 が GND2 レベルである場合、オープンドレイン出力は、グランドより 1 ダイオード分高い電圧にクランプされます。この動作を、図 6-5 から図 6-10 までの、灰色の網掛けで示します。

システム レベルでは、オープンドレイン信号ラインの CMTI 性能はプルアップ抵抗の値によって異なります。高いスルーレート ( $dV/dt$  が高い) の同相過渡イベント中、プリント基板 (PCB) のハイサイドとローサイドの間の寄生容量結合により、オープンドレイン信号ラインが **Low** にされることがあります。寄生結合が信号レベルに及ぼす影響は、プルアップ強度の関数であり、プルアップ抵抗の値が小さいほど CMTI の性能が向上します。AMC23C12-Q1 は、比較的弱いプルアップ抵抗値  $10\text{k}\Omega$  で特性付けされており、 $4.7\text{k}\Omega$  以下のプルアップ抵抗を使用する標準的なアプリケーションで、規定の CMTI 性能を確実に満たすことができます。

#### 6.3.4.1 透過出力モード

LATCH ピンを **LOW** にすると、本デバイスはトランスペアレント・モードに設定され、設定された閾値電圧と入力信号の関係に基づいて出力状態が変化します。たとえば、入力信号が閾値電圧を上回ると、OUT ピンは **LOW** に駆動されます。入力信号が閾値電圧を下回ると、出力はデフォルトの **HIGH** 出力状態に戻ります。トランスペアレント・モードでデバイスを使用する一般的な実装は、OUT ピンをコントローラのハードウェア割り込み入力に接続することです。本デバイスが範囲外状態を検出し、OUT ピンが **LOW** に駆動されるとすぐに、コントローラの割り込み端子が出力状態の変化を検出し、範囲外状態の対応に必要なシステム動作に変化し始めることができます。

#### 6.3.4.2 ラッチ出力モード

一部のアプリケーションには、過電流状態を検出するために OUT ピンの状態を継続的に監視できる機能がありません。このアプリケーションの代表例は、システムが正常に機能しているかどうかを確認するために OUT 端子の状態を定期的にポーリングできるだけのシステムです。この種のアプリケーションでデバイスをトランスペアレント モードに設定した場合、これらの定期的なポーリング イベントのいずれかの最中に範囲外状態が発生しない限り、OUT ピンの状態変化を見逃す可能性があります。

ラッチ モードは、特にこれらのアプリケーションに対応することを目的としています。LATCH 端子の電圧を論理 **HIGH** レベルに設定することで、本デバイスはラッチ モードに移行します。ラッチ モードとトランスペアレント モードの違いは、範囲外イベントが終了した際のアラート出力の応答の仕方です。トランスペアレント モードでは、入力信号が閾値電圧を下回ると、出力状態はデフォルトの **HIGH** 設定に戻り、範囲外イベントが終了したことを示します。

ラッチ モードでは、範囲外状態が検出され OUT ピンが **LOW** に駆動された場合、入力信号が閾値電圧レベルを下回っても OUT ピンはデフォルトの **HIGH** レベルには戻りません。このイベントをクリアするには、LATCH 端子を  $4\mu\text{s}$  以上の間 **LOW** にプルする必要があります。LATCH ピンを **LOW** にプルした場合、入力信号が閾値電圧を下回ると、OUT ピンはデフォルトの **HIGH** レベルに戻れます。LATCH ピンを **LOW** にプルした際に、入力信号が依然として閾値電圧を超えている場合、OUT 端子は **LOW** に維持されます。システム コントローラによって範囲外イベントが検出された場合、LATCH ピンを **HIGH** に戻すことで本デバイスをラッチ モードに戻せます。

### 6.3.5 パワーアップ動作とパワーダウン動作

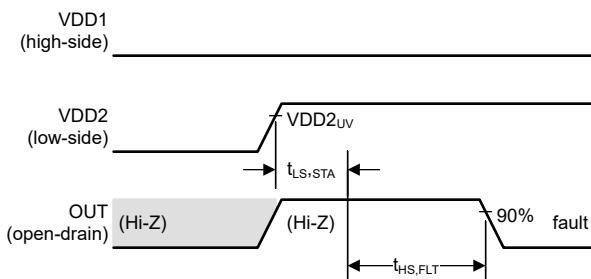

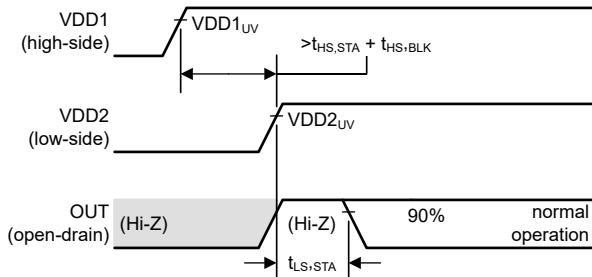

ローサイド電源 (VDD2) がオンになると、オープンドレイン出力はハイインピーダンス (Hi-Z) 状態で起動します。起動後、ハイサイドがまだ機能していない場合、出力はアクティブに Low になります。図 6-5 に示すように、この状態は、ローサイドの起動時間とハイサイドのフォルト検出遅延時間の和 ( $t_{LS, STA} + t_{HS, FLT}$ ) の後で発生します。同様に、通常動作中にハイサイドのフォルト検出遅延時間より長い間、ハイサイド電源が低電圧スレッショルド (VDD1uv) を下回ると、オープンドレイン出力は Low になります (図 6-8 を参照)。この遅延により、ハイサイド電源を喪失してもシステムは確実にシャットダウンできます。

REF ピンの電圧を安定させ、起動中にコンパレータ出力が意図せず切り替わることを防止するため、コンパレータのハイサイドとローサイドとの間での通信開始は、ハイサイドのブランкиング時間 ( $t_{HS, BLK}$ 、高電圧側に実装された時定数) だけ遅延します。

図 6-5 から図 6-10 までに、代表的な起動および停止のシナリオを示します。

図 6-5 では、ローサイド電源 (VDD2) がオンになりますが、ハイサイド電源 (VDD1) はオフのままです。出力は Hi-Z 状態で起動します。 $t_{HS, FLT}$  後、OUT は Low になり、ハイサイド電源喪失フォルトを示します。

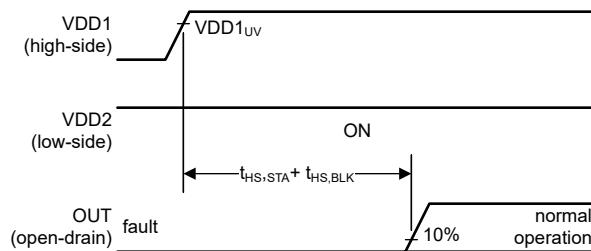

図 6-6 では、ローサイド電源 (VDD2) がオンになった後しばらくして、ハイサイド電源 (VDD1) がオンになります。出力は最初はアクティブ Low 状態です (図 6-5 を参照)。ハイサイド電源がイネーブルされた後、本デバイスが通常動作となり、出力がコンパレータの現在の状態を反映するまでに、 $t_{HS, STA} + t_{HS, BLK}$  の時間が経過します。

図 6-5. VDD2 がオンになり、VDD1 はオフのまま

図 6-6. VDD2 がオンで、VDD1 がオンになる

(遅延時間が長い)

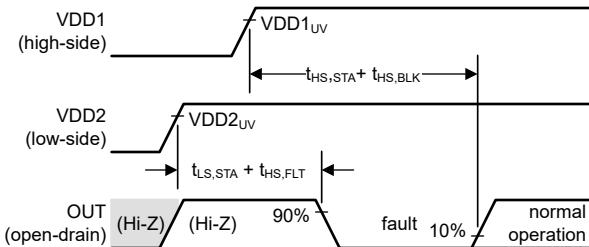

図 6-7 では、ローサイド電源 (VDD2) がオンになった後で、わずかに遅れてハイサイド電源 (VDD1) がオンになります。出力は最初は Hi-Z 状態です。ハイサイド フォルト検出遅延 ( $t_{HS, FLT}$ ) はハイサイドのブランкиング時間 ( $t_{HS, BLK}$ ) より短いため、出力は  $t_{HS, FLT}$  の後で Low になり、ハイサイドがまだ動作していないことを示します。ハイサイドのブランкиング時間 ( $t_{HS, BLK}$ ) が経過した後、本デバイスは通常動作になり、出力はコンパレータの現在の状態を反映します。

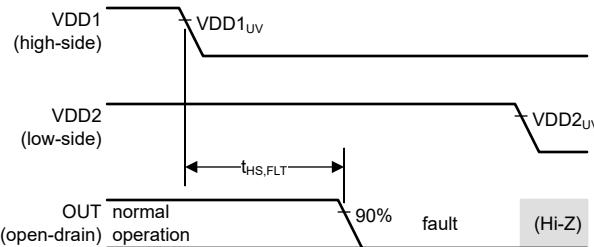

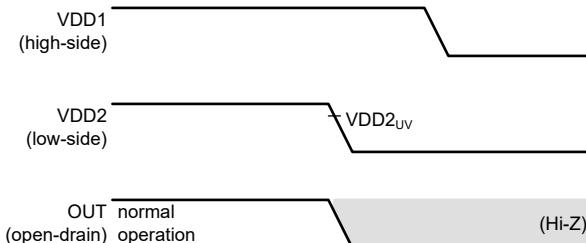

図 6-8 では、ハイサイド電源 (VDD1) がオフになった後で、ローサイド電源 (VDD2) がオフになります。ハイサイド フォルト検出遅延時間 ( $t_{HS, FLT}$ ) の後、出力はアクティブに Low になります。VDD2 が VDD2uv スレッショルドを下回るとすぐに、出力は Hi-Z 状態になります。

図 6-7. VDD2 がオンになってから VDD1 がオンになる

(遅延時間が短い)

図 6-8. VDD1 がオフになってから VDD2 がオフになる

図 6-9 では、ハイサイドが完全に起動した後で、ローサイド電源 (VDD2) がオンになります (VDD1 と VDD2 の間の遅延は ( $t_{HS, STA} + t_{HS, BLK}$ ) より大きい)。出力は Hi-Z 状態で起動します。ローサイドの起動時間 ( $t_{LS, STA}$ ) の後で、デバイスは通常動作になります。

図 6-10 では、ローサイド電源 (VDD2) がオフになってから、ハイサイド電源 (VDD1) がオフになります。VDD2 が VDD2\_UV スレッショルドを下回るとすぐに、出力は Hi-Z 状態になります。

図 6-9. VDD1 がオンになってから VDD2 がオンになる

(遅延時間が長い)

図 6-10. VDD2 がオフになってから VDD1 がオフになる

### 6.3.6 VDD1 のブラウンアウトおよび電源喪失時の動作

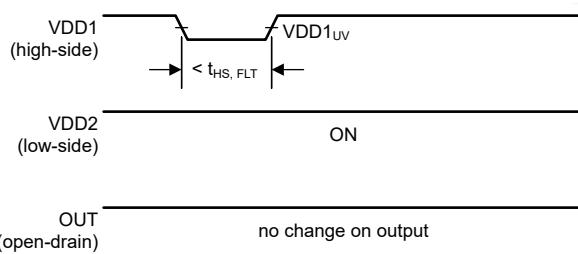

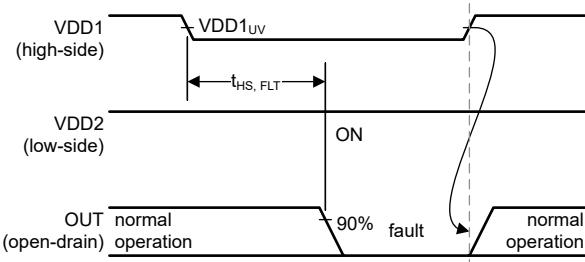

ブラウンアウトとは、仕様で規定された動作電圧範囲よりも VDD1 電源電圧が低下したが、そのデバイスは機能し続けている状態を指します。電源喪失とは、そのデバイスが機能を停止するレベルを VDD1 電源電圧が下回った状態を指します。その持続時間と電圧レベルに応じて、ブラウンアウト状態はそのデバイスの出力で観測される場合とされない場合があります。電源喪失状態は、絶縁型コンパレータの出力で常に通知されます。

図 6-11～図 6-13 に、代表的なブラウンアウトおよび電源喪失シナリオを示します。

図 6-11 では、VDD1 は低電圧検出閾値電圧 (VDD1<sub>UV</sub>) 未満に低下しますが、1 次側フォルト検出遅延時間 ( $t_{HS,FLT}$ ) が経過する前に復帰しています。ブラウンアウトイベントは、コンパレータの出力には影響しません。

図 6-12 では、1 次側フォルト検出の遅延時間 ( $t_{HS,FLT}$ ) より長い間、VDD1 が低電圧検出閾値電圧 (VDD1<sub>UV</sub>) を下回っています。このブラウンアウト状態はフォルトとして検出され、 $t_{HS,FLT}$  に等しい遅延の後、出力は LOW に駆動されます。VDD1<sub>UV</sub> 閾値電圧より高い電圧に VDD1 が回復するとすぐに、本デバイスは通常動作に復帰します。

図 6-11. VDD1 の短いブラウンアウトイベントに対する出力応答

図 6-12. VDD1 の長いブラウンアウトイベントに対する出力応答

図 6-13 では、VDD1 がパワーオンリセット (POR) 閾値電圧 (VDD1<sub>POR</sub>) 未満に低下しています。この電源喪失状態はフォルトとして検出され、 $t_{HS,FLT}$  に等しい遅延の後、出力は LOW に駆動されます。VDD1<sub>UV</sub> 閾値電圧より高い電圧に VDD1 が回復すると、 $t_{HS,STA} + t_{HS,BLK}$  に等しい遅延の後、本デバイスは通常動作に復帰します。

図 6-13. VDD1 の電源喪失イベントに対する出力応答

## 6.4 デバイスの機能モード

AMC23C12-Q1 デバイスは、[推奨動作条件](#)の表に規定された電源 (VDD1, VDD2) を使うことで機能します。

REF ピンの電圧が  $V_{MSEL}$  閾値電圧より低い場合、1 次側の両方のコンパレータは組み合わさって 1 つのウインドウ・コンパレータとして機能します。REF ピンの電圧が  $V_{MSEL}$  閾値電圧より高い場合、負のコンパレータ (Cmp0) は無効化され、Cmp1 はヒステリシスが大きい 1 つの正のコンパレータとして機能します ([リファレンス入力セクション](#)を参照)。

本デバイスは、LATCH 入力ピンの設定に基づいて選択される 2 つの出力動作モード (トランスペアレント・モード、ラッチ・モード) を備えています。これらのモードは、変化する入力信号の状態に対する OUT ピンの応答方法に影響します。詳細については、[オープン・ドレインデジタル出力](#)のセクションを参照してください。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

AMC23C12-Q1 は応答時間が短く、同相過渡耐性 (CMTI) が高く、強化絶縁バリアが組み込まれており、過酷でノイズの多い環境の高電圧アプリケーションで、高速かつ高い信頼性で過電流と過電圧を検出するように設計されています。

### 7.2 代表的なアプリケーション

#### 7.2.1 過電流の検出

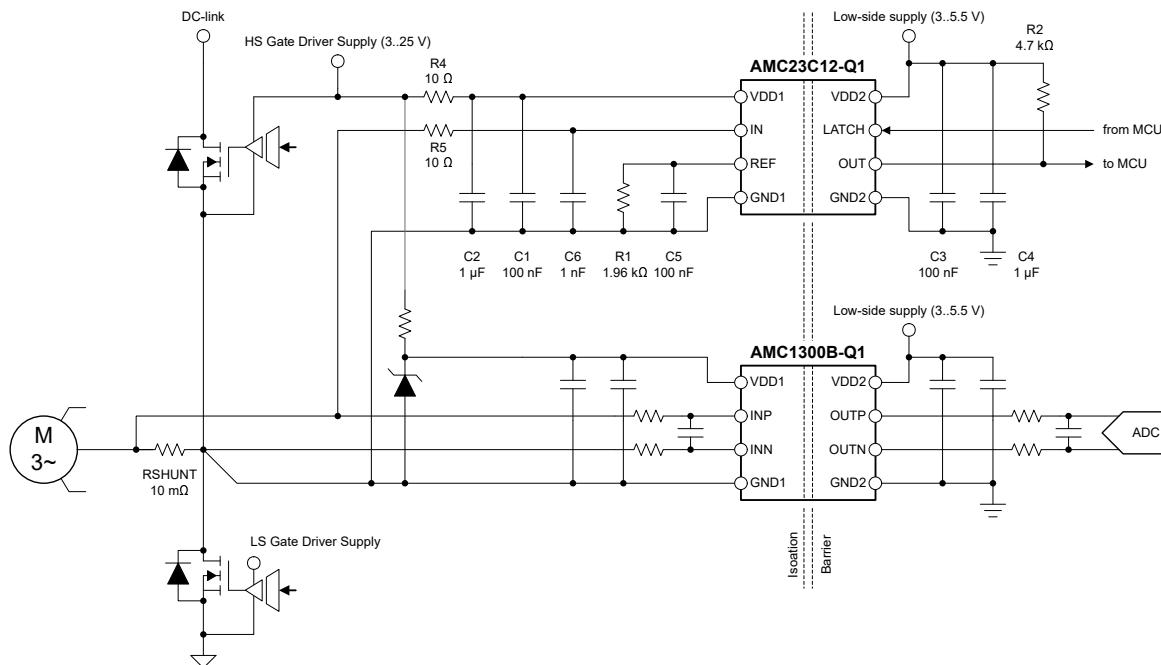

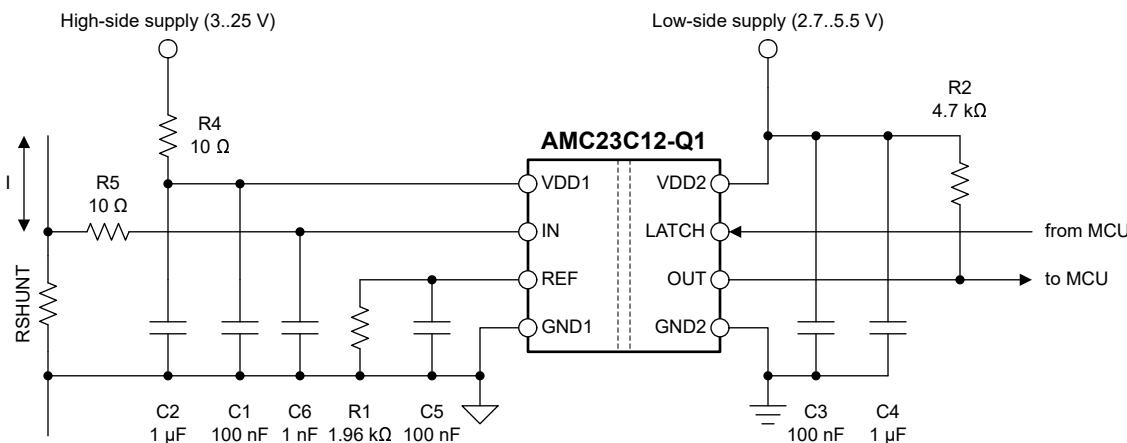

高速な過電流の検出は、DC/DC コンバータおよびモーター制御アプリケーションで一般的な要件で、図 7-1 に示すように AMC23C12-Q1 絶縁ウインドウ コンパレータを使用して実装できます。

図 7-1. AMC23C12-Q1 による過電流の検出

外部シャント抵抗  $R_{SHUNT}$  を流れる負荷電流によって電圧降下が発生し、制御目的で [AMC1300B-Q1](#) によって検出されます。同じ電圧が、電流検出アンプと並列に接続された [AMC23C12-Q1](#) によって監視され、正と負のフォルト電流を検出するための高速なセンシング パスになります。過電流検出スレッショルドは外付け抵抗  $R1$  によって設定され、過電流イベントはオープンドレイン出力  $OUT$  で通知されます。

[図 7-1](#) に示すように、ハイサイドに内蔵された低ドロップアウト (LDO) レギュレータにより、VDD1 入力を一般的に使用されるフローティング ゲートドライバ電源に直接接続できます。または、[AMC23C12-Q1](#) は [AMC1300B-Q1](#) と安定化電源を共有できます。この場合、[AMC23C12-Q1](#) の VDD1 ピンを [AMC1300B-Q1](#) の VDD1 ピンと R4 に直接接続する必要はありません。短い応答時間と優れた同相過渡耐性 (CMTI) を備えた [AMC23C12-Q1](#) を使うと、ノイズの多い環境でも信頼性と精度の高い動作を実現できます。

### 7.2.1.1 設計要件

[表 7-1](#) に、[図 7-1](#) のアプリケーション例のパラメータ一覧を示します。

**表 7-1. 設計要件**

| パラメータ                  | 値         |

|------------------------|-----------|

| ハイサイド電源電圧              | 3V~25V    |

| ローサイド電源電圧              | 2.7V~5.5V |

| シャント抵抗値                | 10mΩ      |

| AMC1300B-Q1 のリニア入力電圧範囲 | ±250mV    |

| 最大ピーク・モーター電流           | ±25A      |

| 過電流検出スレッショルド           | ±20A      |

### 7.2.1.2 詳細な設計手順

この例では、シャント抵抗の値は 10mΩ で、[AMC1300B-Q1](#) 電流検出アンプの線形入力電圧範囲 (±250mV) によって決定されます。フルスケール電流は ±25A です。

目的の 20A の過電流検出レベルでは、シャント抵抗の両端の電圧降下は  $10mΩ \times 20A = 200mV$  です。ウインドウ・コンペレータの正方向のトリップ・スレッショルドは  $V_{REF} + V_{HYS}$  です。ここで、 $V_{HYS}$  は「[電気的特性](#)」の表で規定されている 4mV で、 $V_{REF}$  は、REF ピンと GND1 ピンの間に接続された R1 の両端の電圧です。R1 は  $(V_{TRIP} - V_{HYS}) / I_{REF} = (200mV - 4mV) / 100μA = 1.96kΩ$  と計算され、E96 シリーズの値 (1% 精度) と一致します。

入力信号をフィルタ処理し、ノイズに対する感度を下げるため、10Ω、1nF の RC フィルタ (R5、C6) をコンパレータの入力に配置します。このフィルタにより、保護回路の総応答時間を計算する際に考慮すべき  $10Ω \times 1nF = 10ns$  の伝播遅延が追加されます。そのシステムが追加の遅延に耐えられる場合、ノイズ耐性を高めるためにフィルタ定数を大きくすることを推奨します。

[表 7-2](#) に、この設計の主要パラメータを示します。

**表 7-2. 過電流検出の設計例**

| パラメータ                            | 値           |

|----------------------------------|-------------|

| 基準抵抗の値 (R1)                      | 1.96kΩ      |

| 基準コンデンサの値 (C5)                   | 100nF       |

| リファレンス電圧                         | 196mV       |

| リファレンス電圧のセトリング・タイム (最終値の 90% まで) | 470μs       |

| 過電流トリップ・スレッショルド (立ち上がり)          | 200mV/20.0A |

| 過電流トリップ・スレッショルド (立ち下がり)          | 196mV/19.6A |

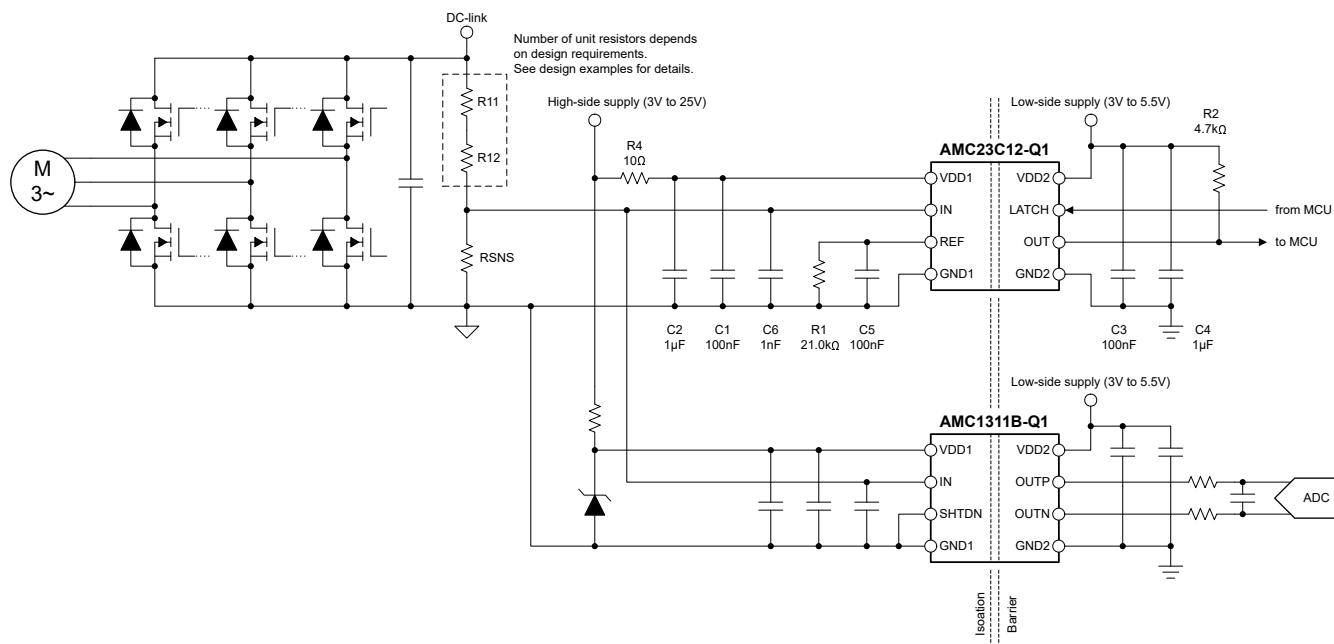

## 7.2.2 過電圧検出

AMC1311B-Q1などの絶縁アンプは、オンボードチャージャ(OBC)、DC/DCコンバータ、トラクションインバータなどのDCリンク電圧の測定に広く使用されています。DCリンクレールに接続された出力段は、(ブレーキ動作中など)発生する可能性のある過電圧条件に敏感な場合があります。絶縁アンプは、DCリンク電圧を低減するための適切なアクションを実行するのに十分な速度でシステムコントローラにアラートを送れない場合があります。したがって、過電圧状態を検出するには、高速の絶縁コンパレータが必要です。

図7-2に、AMC1311B-Q1絶縁アンプによってDCリンク電圧が検出されるトラクションインバータの概略回路図を示します。AMC23C12-Q1は、AMC1311B-Q1と並列に接続され、RSNSの両端の電圧を監視して、過電圧状態を検出します。過電圧トリップスレッショルドは、AMC23C12-Q1のREFピンに接続されているR1抵抗によって設定されます。AMC23C12-Q1のオープンドレインOUTピンは、MCUのGPIOまたは割り込みピンに接続され、入力電圧( $V_{IN}$ )がリファレンス電圧( $V_{REF}$ )を超えるとアクティブにLowになります。

図7-2. AMC23C12-Q1による過電圧検出

### 7.2.2.1 設計要件

表 7-3 に、図 7-2 のアプリケーション例のパラメータ一覧を示します。

表 7-3. 設計要件

| パラメータ                     | 値       |

|---------------------------|---------|

| ハイサイド電源電圧                 | 3V~25V  |

| ローサイド電源電圧                 | 3V~5.5V |

| 公称 DC リンク電圧               | 400V    |

| AMC1311B-Q1 の線形フルスケール入力電圧 | 2V      |

| 線形検出用の DC リンク電圧範囲         | 0V~450V |

| DC リンク過電圧検出スレッショルド        | 480V    |

### 7.2.2.2 詳細な設計手順

R11、R12、RSNS で構成される分圧器のサイズは、線形検出の対象となる最大 DC リンク電圧 (450V) で、RSNS の両端の電圧降下が AMC1311B-Q1 の線形フルスケール入力電圧 (2V) と等しくなるように設定されています。したがって、過電圧状態での RSNS 両端の電圧降下は  $480V / 450V \times 2V = 2.133V$  です。この値は、AMC23C12-Q1 のリファレンス電圧 ( $V_{REF}$ ) の目標値です。

$V_{REF}$  は、外付け抵抗  $R1$  と、AMC23C12-Q1 の内部  $100\mu A$  電流源によって決定されます。 $R1$  は、 $(V_{TRIP} - V_{HYS}) / I_{REF} = (2133mV - 25mV) / 100\mu A = 21.08k\Omega$  として計算されます。E192 シリーズの最も近い値は  $21.0k\Omega$  です。コンパレータは  $V_{REF} + V_{HYS}$  でトリップするため、 $V_{TRIP}$  からコンパレータのヒステリシス電圧 ( $V_{HYS}$ ) が減算されます。図 6-1 を参照してください。「リファレンス入力」セクションに説明されているように、リファレンス電圧が  $550mV$  を上回るため、ヒステリシスの値は  $25mV$  です。

表 7-4 に、この設計の主要パラメータを示します。

表 7-4. 過電圧と低電圧の検出の設計例

| パラメータ                            | 値       |

|----------------------------------|---------|

| 基準抵抗の値 (R1)                      | 21.0kΩ  |

| 基準コンデンサの値 (C5)                   | 100nF   |

| リファレンス電圧                         | 2100 mV |

| リファレンス電圧のセトリング タイム (最終値の 90% まで) | 4.85ms  |

| 過電圧トリップ スレッショルド (立ち上がり)          | 478 V   |

| 過電圧トリップ スレッショルド (立ち下がり)          | 472 V   |

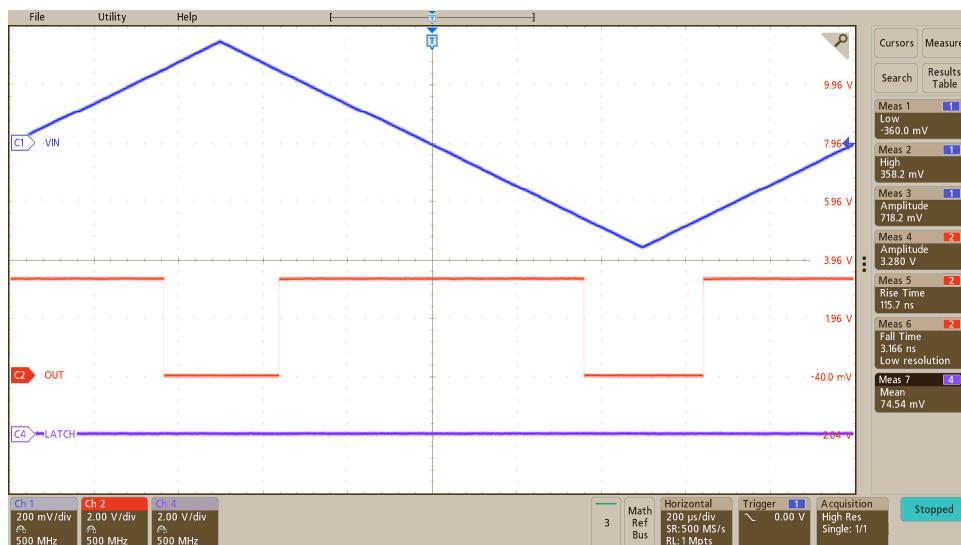

### 7.2.3 アプリケーション曲線

図 7-3 に、振幅  $720\text{mV}_{\text{PP}}$  のバイポーラ三角入力波に対する AMC23C12-Q1 の代表的な応答を示します。出力 (OUT) は、VIN が REF ピン電圧によって決定される  $\pm 250\text{mV}$  のレベルを交差すると、切り替わります。この例では、REF ピンの電圧は  $250\text{mV}$  にバイアスされます。

図 7-3. 三角入力波に対する AMC23C12-Q1 の出力応答

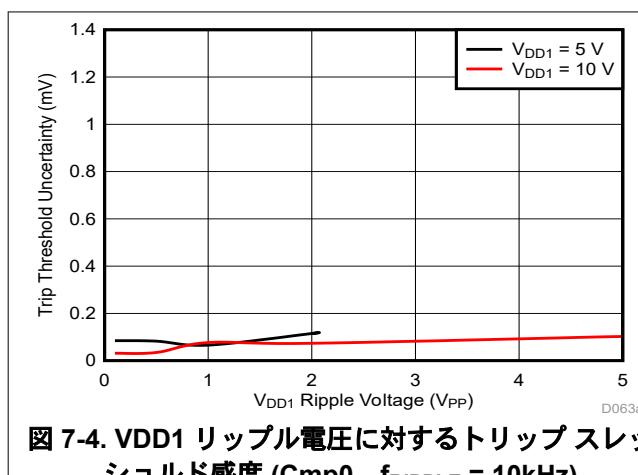

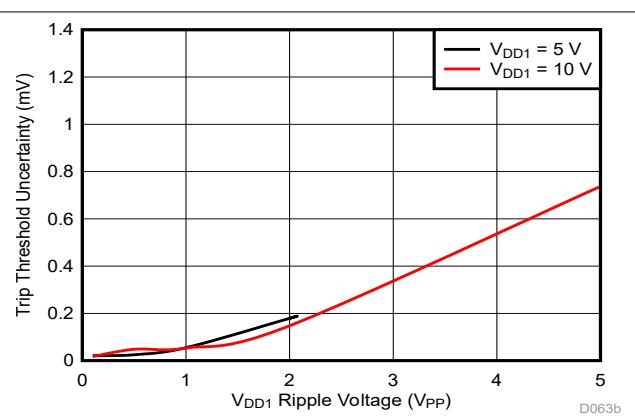

AMC23C12-Q1 の内蔵 LDO は、高電圧側の電源要件を大幅に緩和し、レギュレートされていないトランジスタ、チャージポンプ、ブートストラップ電源からデバイスに電力を供給できます。以下の図に示すように、内部 LDO は内部回路に安定した動作電圧を供給するため、 $2\text{V}_{\text{PP}}$  以上のリップル電圧でもトリップのスレッショルドにはほぼ影響しません。

図 7-4. VDD1 リップル電圧に対するトリップスレッショルド感度 (Cmp0,  $f_{\text{RIPPLE}} = 10\text{kHz}$ )

図 7-5. VDD1 リップル電圧に対するトリップスレッショルド感度 (Cmp1,  $f_{\text{RIPPLE}} = 10\text{kHz}$ )

## 7.3 設計のベスト プラクティス

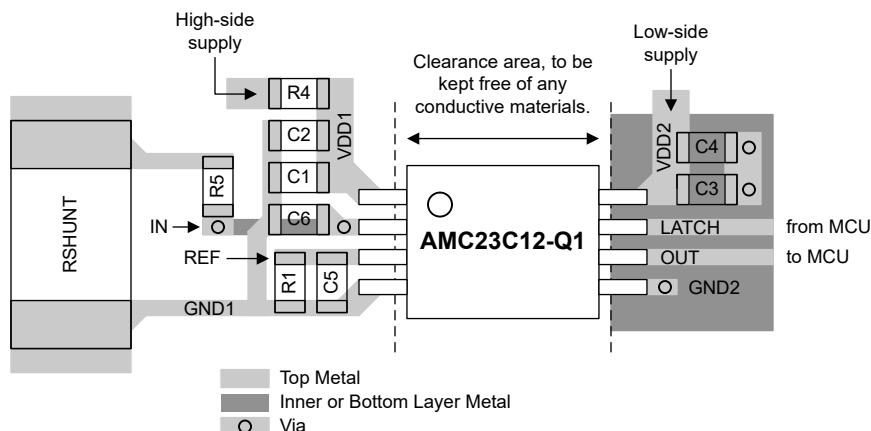

検出抵抗のローサイド側と、AMC23C12-Q1 の GND1 ピンとの間の接続は、短く、低インピーダンスにします。グランドラインの電圧降下はすべて、コンパレータの入力で検出される電圧に誤差を加え、トリップ スレッショルドの不正確さの原因となります。

同相過渡耐性を最大限に高めるには、図 7-7 に示すように、フィルタ コンデンサ C5 を REF ピンにできるだけ近づけて配置します。同相過渡イベント時にオープンドレイン信号ラインでの容量性結合の影響を最小限に抑えるため、「[オープンドレイン デジタル出力](#)」の説明に従って、オープンドレイン出力に小さい値 (10kΩ 未満) のプルアップ抵抗を使用します。

双方向電流検出アプリケーションでは、「[推奨動作条件](#)」の表に規定されている 300mV  $V_{REF}$  の制限値を超えないようにします。REF ピンを  $V_{MSEL}$  のスレッショルド (450mV~600mV の範囲) 付近にバイアスして本デバイスを動作させないでください ( $Cmp0$  のヒステリシスの動的スイッチングを避けるためです。「[リファレンス入力](#)」セクションの説明を参照)。

AMC23C12-Q1 には、起動中にリファレンス電圧 ( $V_{REF}$ ) が安定できるよう、制限付きの 200μs のブランкиング時間 ( $t_{HS, BLK}$ ) があります。多くのアプリケーションでは、リファレンス電圧が安定するのに 200μs のブランкиング時間よりも長くかかり、「[図 6-2](#)」で説明されているように、システムの起動中にコンパレータの出力にグリッチが起きる可能性があります。システム全体の起動設計におけるリファレンス電圧のセトリング タイムを考慮してください。

## 7.4 電源に関する推奨事項

AMC23C12-Q1 は、特定の起動シーケンスを必要としません。ハイサイド電源 (VDD1) は、低 ESR の  $1\mu\text{F}$  コンデンサ (C2) と並列接続された低 ESR の  $100\text{nF}$  コンデンサ (C1) でデカップリングされます。ローサイド電源 (VDD2) は、低 ESR の  $1\mu\text{F}$  コンデンサ (C4) と並列接続された低 ESR の  $100\text{nF}$  コンデンサ (C3) で同様にデカップリングされます。4 つのコンデンサ (C1, C2, C3, C4) はすべてデバイスのできるだけ近くに配置します。図 7-6 に、AMC23C12-Q1 のデカップリング回路図を示します。

VDD1 電源電圧が高い ( $> 5.5\text{V}$ ) 場合、追加のフィルタ処理のために、VDD1 電源と直列に  $10\Omega$  の抵抗 (R4) を接続します。

図 7-6. AMC23C12-Q1 のデカップリング

アプリケーションで発生する DC バイアス条件の下で、コンデンサは十分な実効容量を保つ必要があります。多層セラミックコンデンサ (MLCC) は通常、実際の使用条件における容量は、公称容量よりもはるかに小さいため、これらのコンデンサを選択する際はこの減少を考慮に入れる必要があります。この問題は、背の高い部品よりも絶縁体電界強度が高くなる薄型コンデンサで特に深刻です。信頼できるコンデンサ メーカーは、部品選択を非常に簡単にする容量対 DC バイアス曲線を提供しています。

## 7.5 レイアウト

### 7.5.1 レイアウトのガイドライン

デカップリング・コンデンサの重要な配置 (AMC1303 の電源ピンと可能な限り近く)、およびデバイスに必要な他のコンポーネントの配置を示したレイアウトの推奨事項を、図 7-7 に示します。AMC23C12-Q1

### 7.5.2 レイアウト例

図 7-7. AMC23C12-Q1 の推奨レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

#### 8.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『絶縁の用語集』アプリケーション レポート

- テキサス・インスツルメンツ、『半導体および IC パッケージの熱評価基準』アプリケーション レポート

- テキサス・インスツルメンツ、『ISO72x デジタル アイソレータの磁界耐性』アプリケーション レポート

- テキサス・インスツルメンツ、『AMC1300B-Q1 高精度、 $\pm 250\text{mV}$  入力、強化絶縁型アンプ』データシート

- テキサス・インスツルメンツ、『AMC1311x-Q1 高インピーダンス、2V 入力、強化絶縁型アンプ』データシート

- テキサス・インスツルメンツ、「絶縁型アンプの電圧センシング Excel カリキュレータ」設計ツール

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from JULY 27, 2022 to SEPTEMBER 30, 2024 (from Revision A (July 2022) to Revision B (December 2024))

|                                                                              | Page |

|------------------------------------------------------------------------------|------|

| ・ 「特長」セクションのリファレンス電流を $\pm 2\%$ から $\pm 1\%$ に変更                             | 1    |

| ・ ドキュメント全体にわたって表、図、相互参照の採番方法を更新                                              | 1    |

| ・ 「ピン構成および機能」セクションのパッケージ図を修正                                                 | 3    |

| ・ $V_{IOWM}$ を $750\text{V}_{\text{RMS}}$ から $1000\text{V}_{\text{RMS}}$ に変更 | 7    |

| ・ $V_{IOWM}$ を $1060\text{V}_{\text{DC}}$ から $1410\text{V}_{\text{DC}}$ に変更  | 7    |

---

|                                                     |    |

|-----------------------------------------------------|----|

| • $V_{IMP}$ を $8300V_{PK}$ から $7700V_{PK}$ に変更..... | 7  |

| • 安全関連認証番号を追加.....                                  | 8  |

| • $3.0V \leq VDD1 \leq 3.4V$ の IDD1 仕様を追加.....      | 9  |

| • 伝搬遅延とオーバードライブとの関係の図を変更.....                       | 14 |

| • 分圧器の抵抗記号を更新.....                                  | 31 |

---

| Changes from Revision * (March 2022) to Revision A (July 2022) | Page |

|----------------------------------------------------------------|------|

| • ドキュメントのステータスを「事前情報」から「量産データ」に変更.....                         | 1    |

---

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| AMC23C12QDWVRQ1       | Active        | Production           | SOIC (DWV)   8 | 1000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | MC23C12Q            |

| AMC23C12QDWVRQ1.A     | Active        | Production           | SOIC (DWV)   8 | 1000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | MC23C12Q            |

| AMC23C12QDWVRQ1.B     | Active        | Production           | SOIC (DWV)   8 | 1000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF AMC23C12-Q1 :**

- Catalog : [AMC23C12](#)

---

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

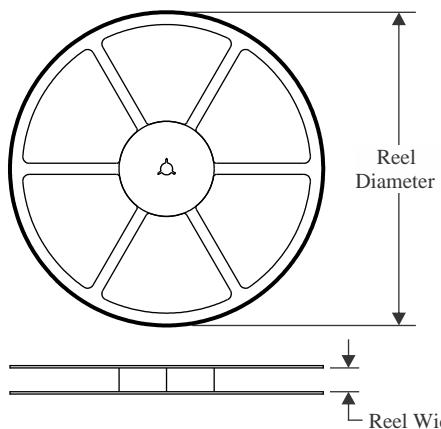

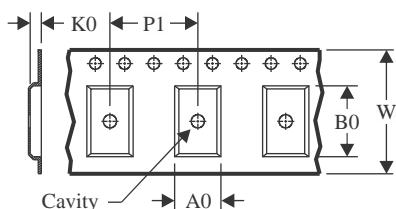

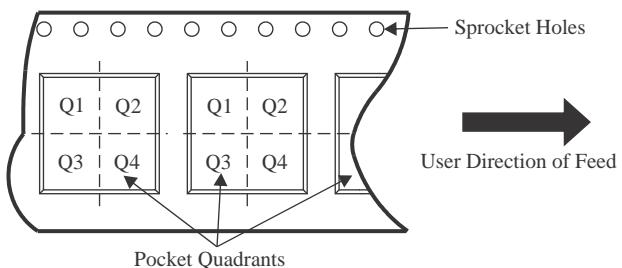

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| AMC23C12QDWVRQ1 | SOIC         | DWV             | 8    | 1000 | 330.0              | 16.4               | 12.05   | 6.15    | 3.3     | 16.0    | 16.0   | Q1            |

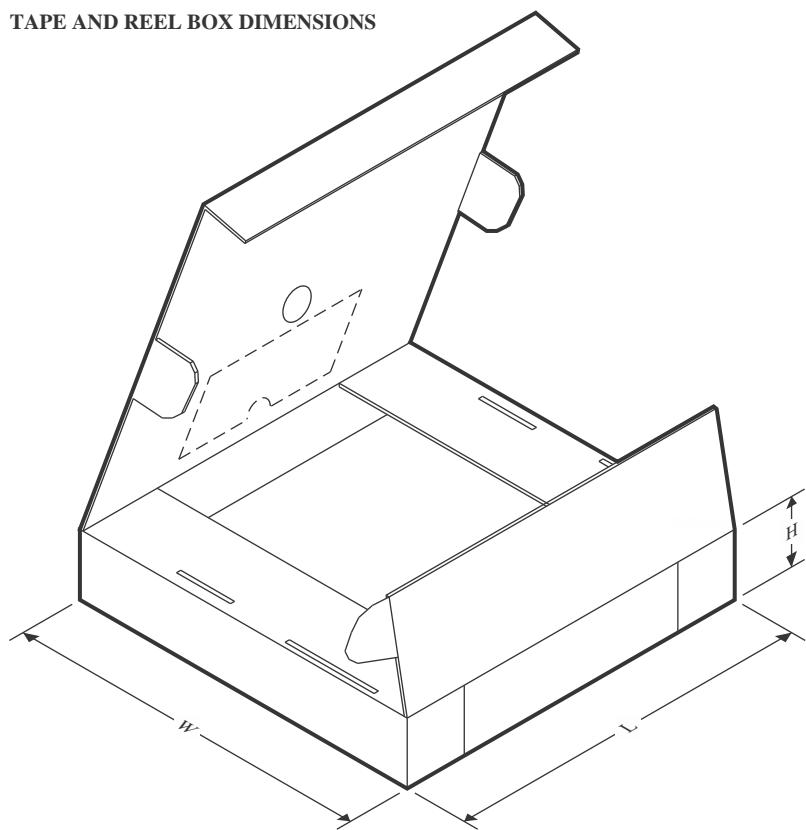

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| AMC23C12QDWVRQ1 | SOIC         | DWV             | 8    | 1000 | 350.0       | 350.0      | 43.0        |

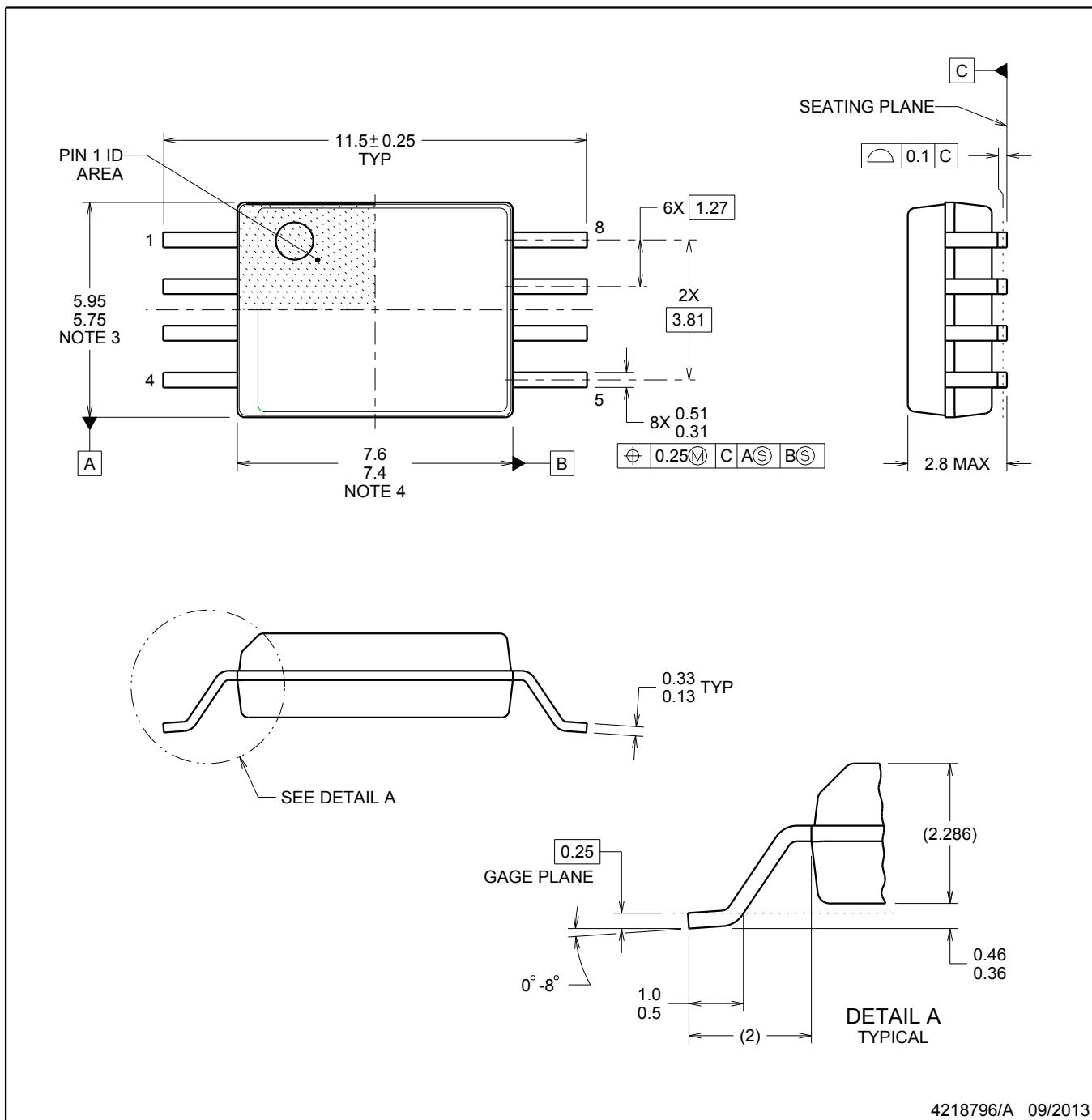

# PACKAGE OUTLINE

DWV0008A

SOIC - 2.8 mm max height

SOIC

4218796/A 09/2013

## NOTES:

1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

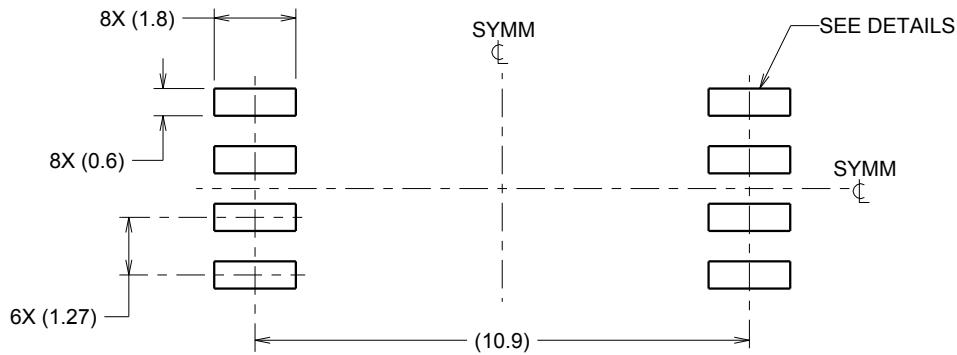

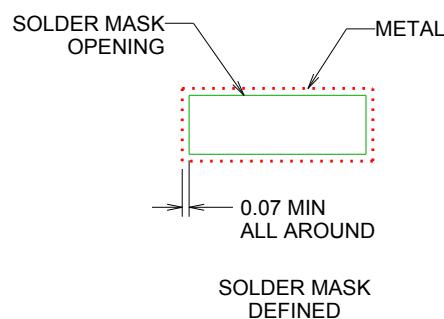

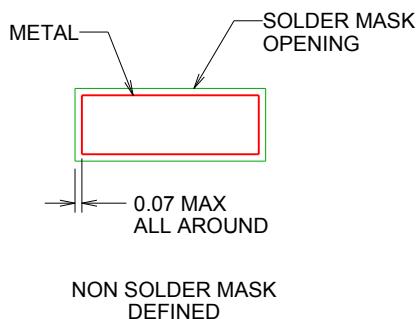

LAND PATTERN EXAMPLE

9.1 mm NOMINAL CLEARANCE/CREEPAGE

SCALE:6X

SOLDER MASK DETAILS

4218796/A 09/2013

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

DWV0008A

SOIC - 2.8 mm max height

SOIC

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:6X

4218796/A 09/2013

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月