# AM68x プロセッサ、シリコン・リビジョン 1.0

## 1 特長

### プロセッサ コア:

- 最大 2 つ、最高 2GHz の 64 ビット Arm® Cortex®-A72 マイクロプロセッサ サブシステム

- デュアルコア Cortex®-A72 クラスタごとに 1MB の共有 L2 キャッシュ、

- Cortex®-A72 コアごとに 32KB L1 D キャッシュと 48KB L1 I キャッシュ

- ディープ ラーニング アクセラレータ:

- 最大 8TOPS (1 秒あたり 8 兆回の演算)

- 画像信号プロセッサ (ISP) 搭載ビジョン処理アクセラレータ (VPAC) と複数のビジョン支援アクセラレータ

- デュアルコア Arm® Cortex®-R5F MCU、最大 1.0GHz、FFI を採用した汎用コンピューティング パーティション

- 16KB L1 D キャッシュ、16KB L1 I キャッシュ、および 64KB L2 TCM

- デュアルコア Arm® Cortex®-R5F MCU、最大 1.0GHz、デバイス管理をサポート

- 32K L1 D キャッシュ、32K I キャッシュ、64K L2 TCM、すべてのメモリに SECDED ECC 付き

- 画像信号プロセッサ (ISP) 搭載ビジョン処理アクセラレータ (VPAC) と複数のビジョン支援アクセラレータ

- 480MPixel/s ISP

- 最大 16 ビットの入力 RAW 形式をサポート

- ワイド ダイナミック レンジ (WDR)、レンズ歪み補正 (LDC)、ビジョン イメージング サブシステム (VISS)、マルチスカラ (MSC) のサポート

- 出力カラー フォーマット: 8 ビット、12 ビット、YUV 4:2:2、YUV 4:2:0、RGB、HSV/HSL

### マルチメディア:

- ディスプレイ サブシステムのサポート:

- 最大 4 台のディスプレイ

- 最大 2 つの DSI 4L TX (最大 2.5K)

- 1 つの eDP 4L

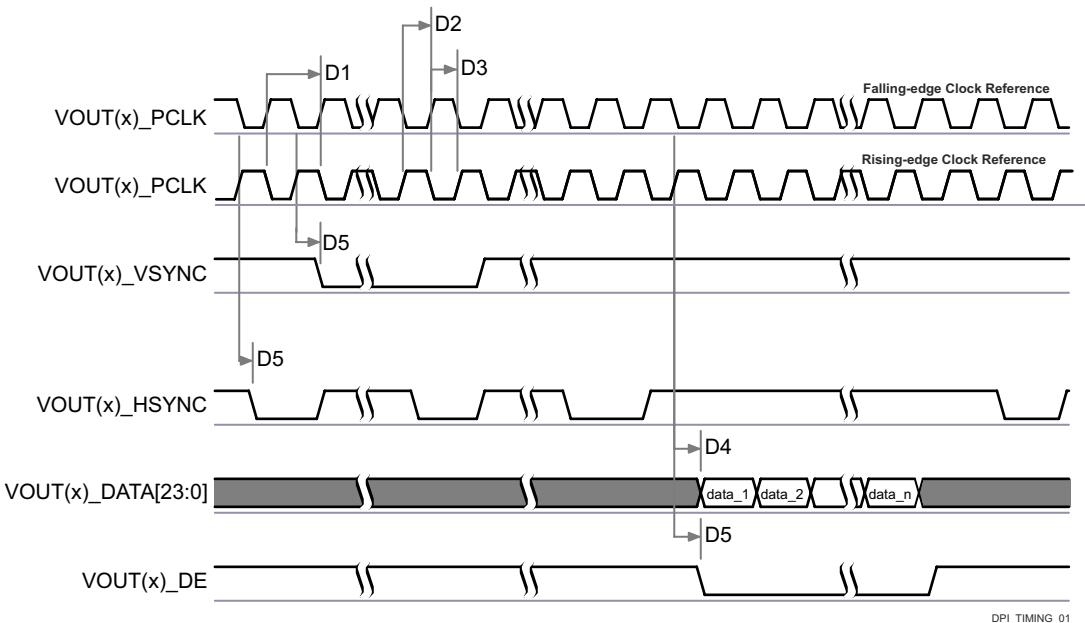

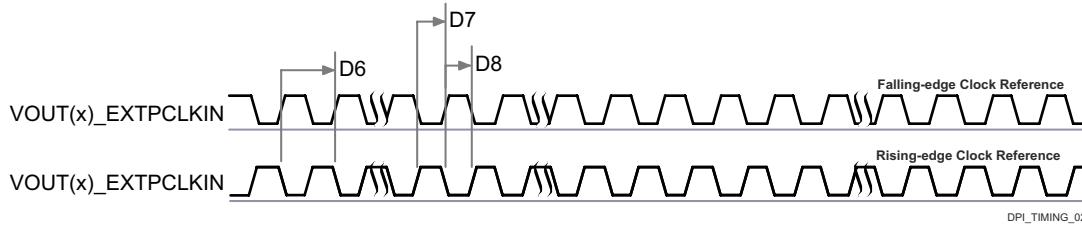

- 1 つの DPI 24 ビット RGB パラレル インターフェイス

- 凍結フレーム検出や MISR データ チェックなどの安全機能

- 3D グラフィックス処理ユニット

- 最大 800MHz の IMG BXS-4-64

- 50GFLOPS、4GTexels/s

- >500MTexels/s、>8GFLOPS

- 少なくとも 2 つの合成層をサポート

- 最大 2048x1080 @ 60fps をサポート

- ARGB32、RGB565、YUV 形式をサポート

- 2D グラフィックス対応

- OpenGL ES 3.1、Vulkan 1.2

- 2 つの CSI2.0 4L カメラ シリアル インターフェイス (CSI-Rx) と CSI2.- 4L Tx (CSI-Tx)、DPHY 付き

- MIPI CSI 1.3 準拠 + MIPI-DPHY 1.2

- 最大 2.5Gbps の 1、2、3、4 データレーン モードをサポート

- CRC チェック + RAM 上の ECC による ECC 検証 / 訂正

- 仮想チャネルのサポート (最大 16)

- DMA 経由で DDR にストリーム データを直接書き込む機能

- ビデオ エンコーダ / デコーダ

- HEVC (H.265) メイン プロファイルをレベル 5.1 上位層でサポート

- H.264 ベースライン / メイン / ハイ プロファイルをレベル 5.2 でサポート

- 最大 4K の UHD 解像度をサポート (3840 × 2160)

- 4K60 H.264/H.265 エンコード / デコード (最大 480MP/s)

### メモリ サブシステム:

- 最大 4MB のオンチップ L3 RAM、ECC およびコヒーレンシ機能付き

- ECC エラー保護

- 共有コヒーレント キャッシュ

- 内部 DMA エンジンをサポート

- ECC 付き、最大 2 つの外部メモリ インターフェイス (EMIF) モジュール

- LPDDR4 メモリ タイプをサポート

- 最大 4266MT/s の速度をサポート

- インライン ECC 付き、最大 2 つの 32 ビット データ バス、EMIF ごとに最大 17GB/s

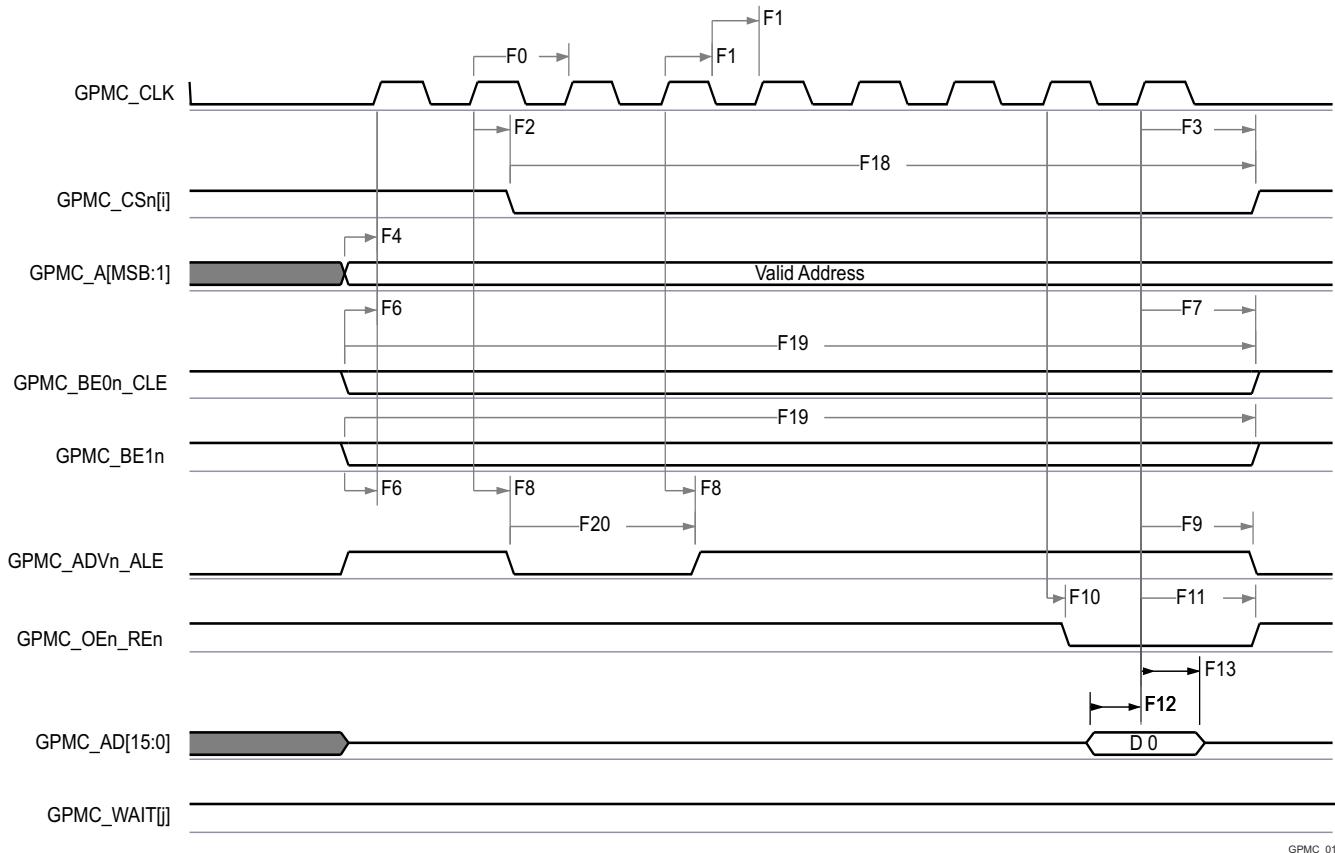

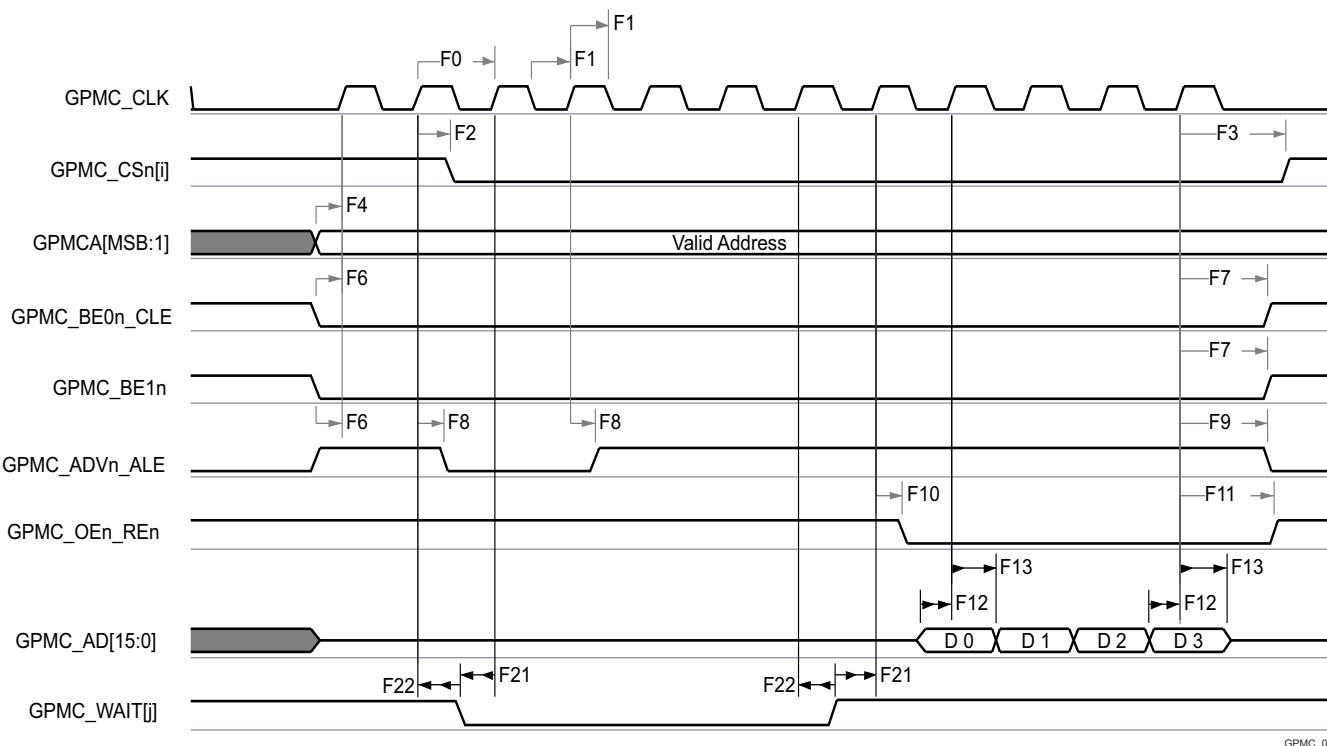

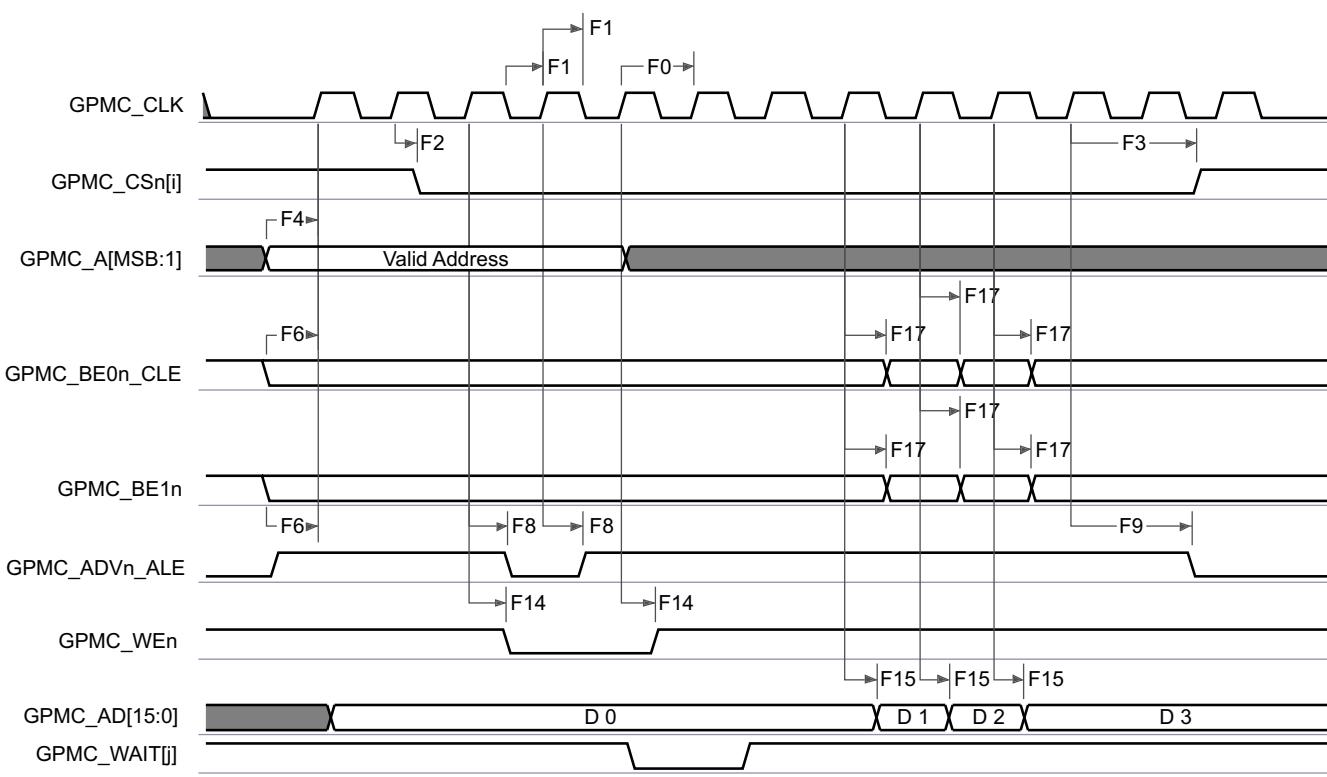

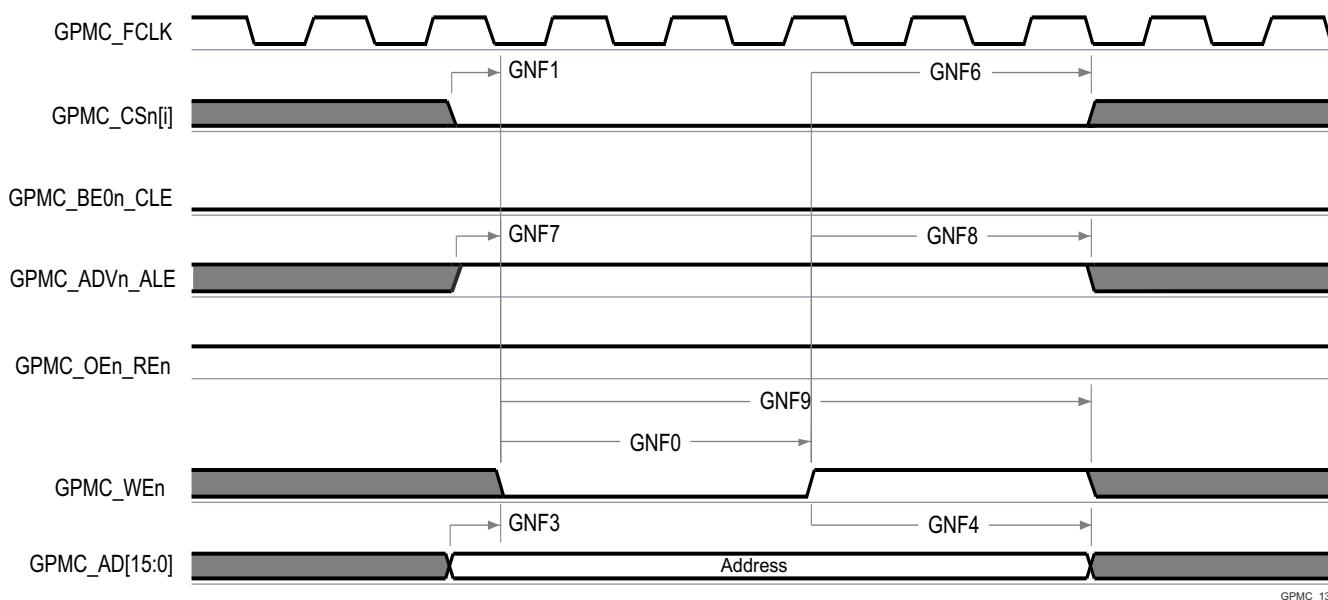

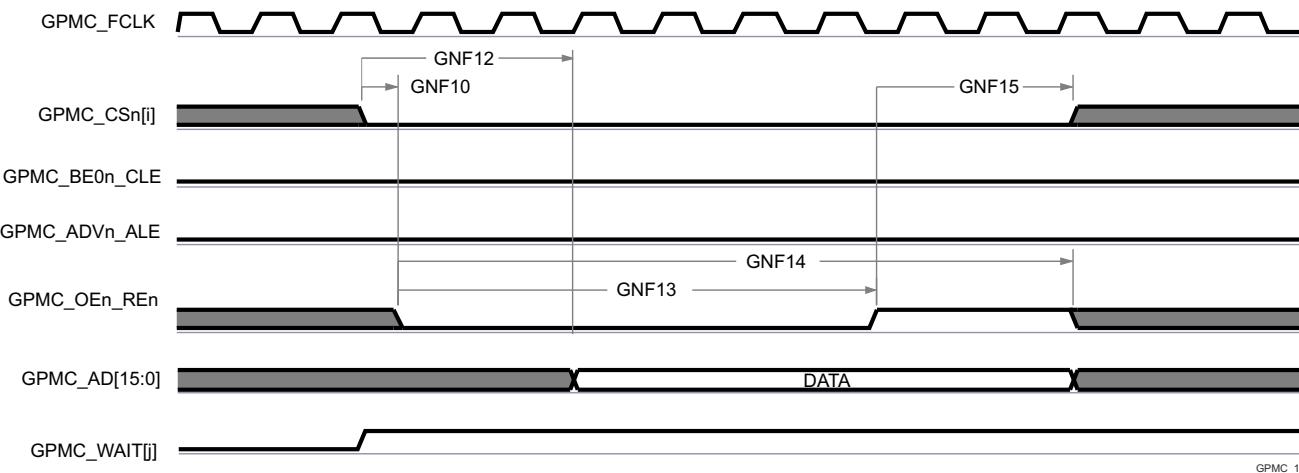

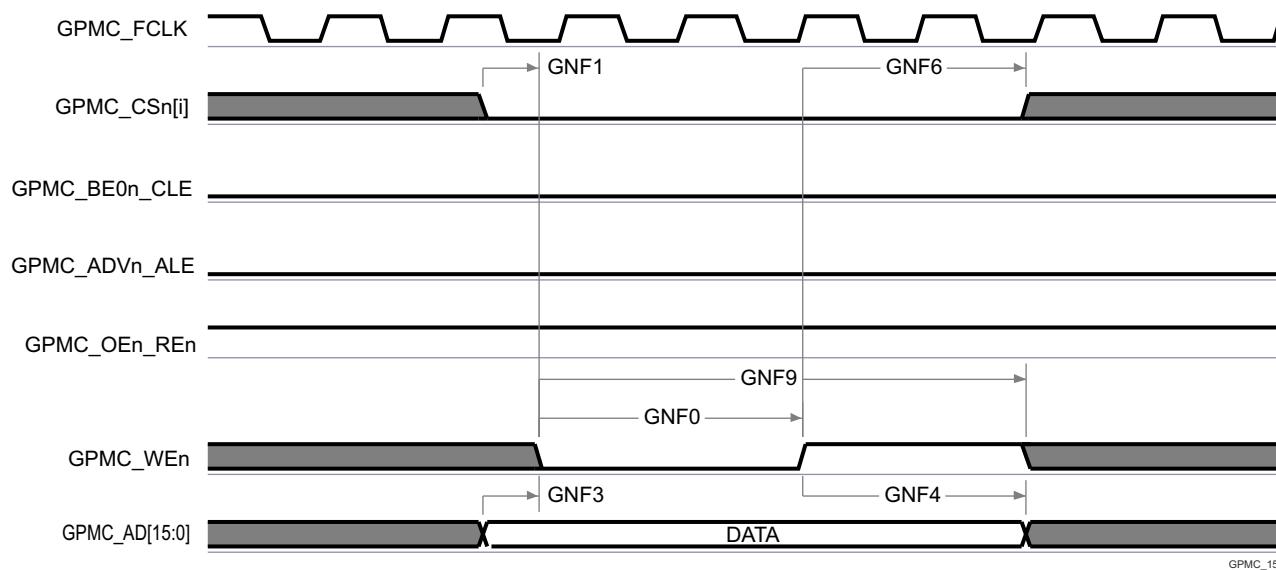

- 汎用メモリ コントローラ (GPMC)

- メインとメモリの最大 2 つの 512KB オンチップ SRAM、ECC 保護付き

### デバイスのセキュリティ:

- セキュアなランタイム サポートによるセキュア ブート

- お客様がプログラム可能なルート キー (RSA-4K または ECC-512 まで)

- 組み込みハードウェア セキュリティ モジュール

- 暗号化ハードウェア アクセラレーター – ECC 付き PKA、AES、SHA、RNG、DES、3DES

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

### 高速シリアルインターフェイス:

- 1 つの PCI-Express® (PCIe) Gen3 コントローラ

- コントローラごとに最大 4 つのレーン

- Gen1 (2.5GT/s)、Gen2 (5.0GT/s)、Gen3 (8.0GT/s) で動作 (オート ネゴシエーション付き)

- 1 つの USB 3.0 デュアルロール デバイス (DRD) サブシステム

- Enhanced SuperSpeed Gen1 ポート

- Type-C スイッチングをサポート

- USB ホスト、USB ペリフェラル、USB DRD として個別に構成可能

- 2 つの CSI2.0 4L カメラシリアルインターフェイス RX (CSI-RX) と、DPHY 付きの 2 つの CSI2.0 4L TX (CSI-TX)

- MIPI CSI 1.3 準拠 + MIPI-DPHY 1.2

- CSI-RX は各レーンで最大 2.5Gbps の 1、2、3、4 データレーン モードをサポート

- CSI-TX は各レーンで最大 2.5Gbps の 1、2、4 データレーン モードをサポート

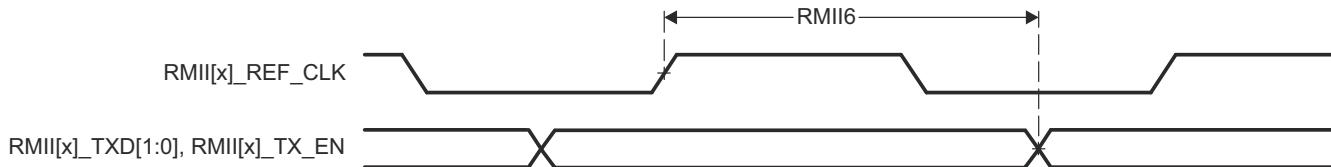

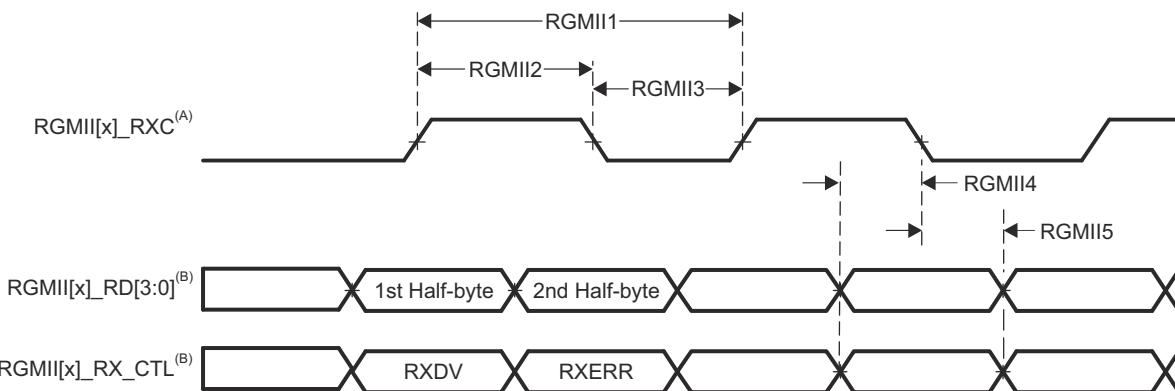

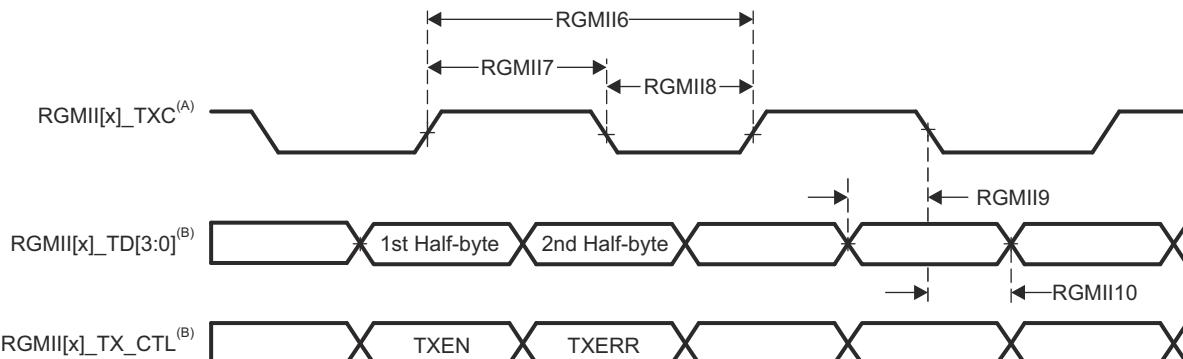

### イーサネット:

- 2 つのイーサネット RMII/RGMII インターフェイス

### フラッシュメモリインターフェイス:

- 組み込み MultiMediaCard インターフェイス (eMMC™ 5.1)

- 1 つの Secure Digital® 3.0/Secure Digital Input Output 3.0 インターフェイス (SD3.0/SDIO3.0)

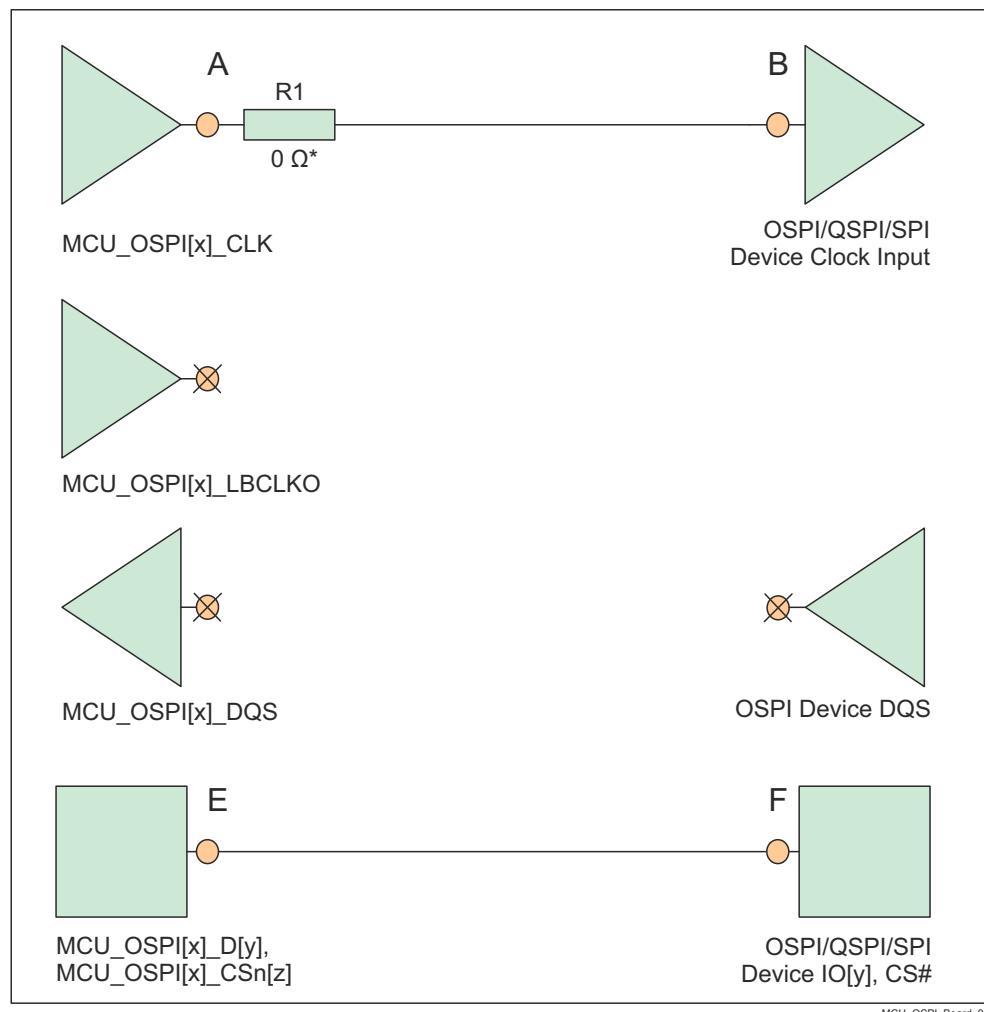

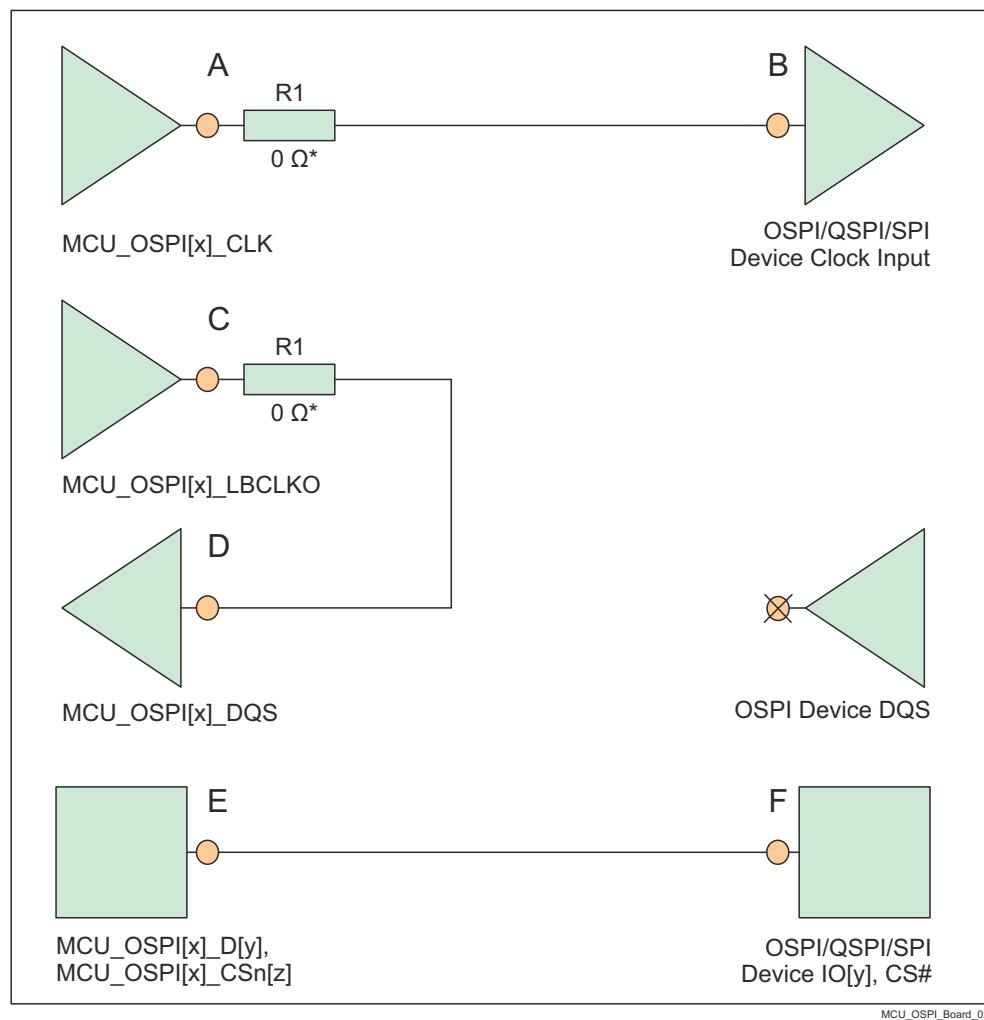

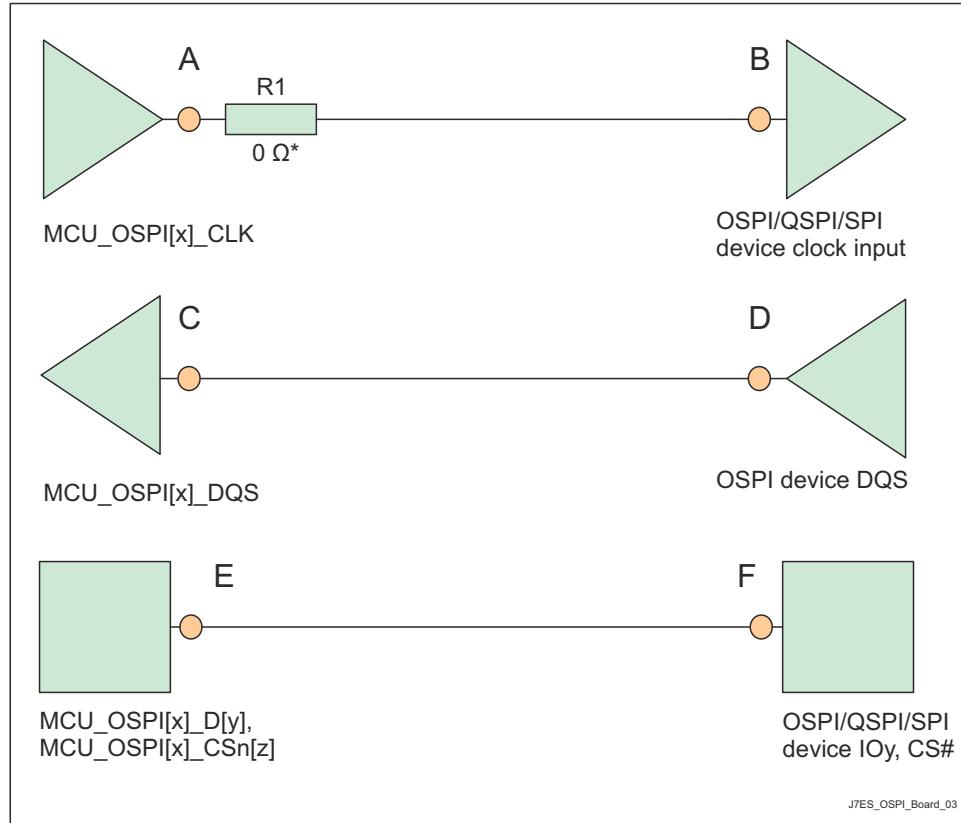

- 2 つの同時フラッシュインターフェイスを以下のように構成

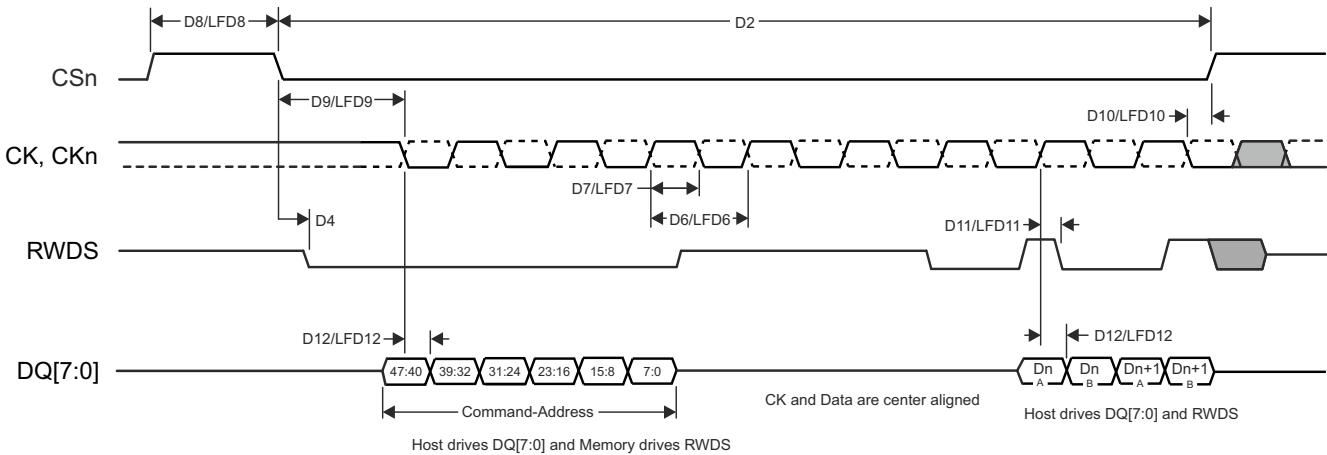

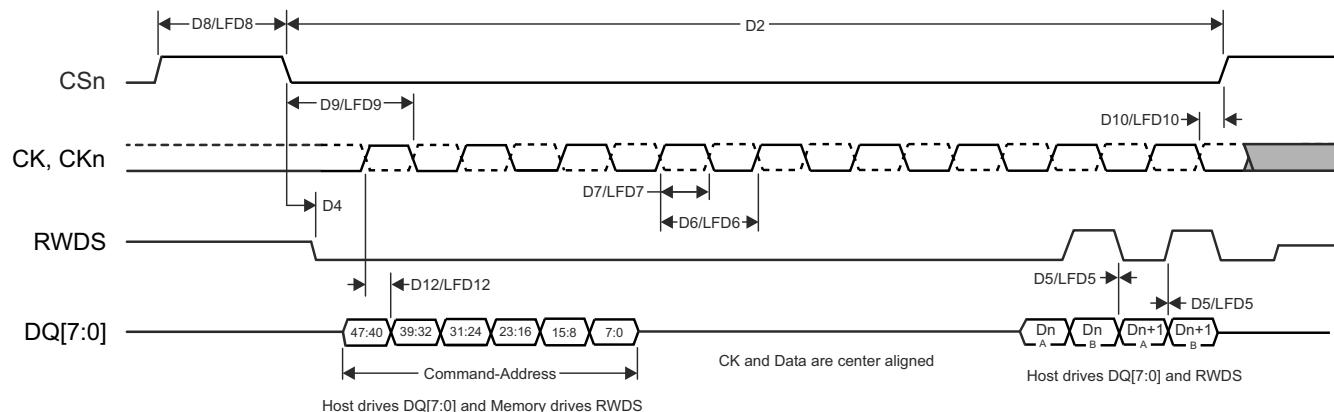

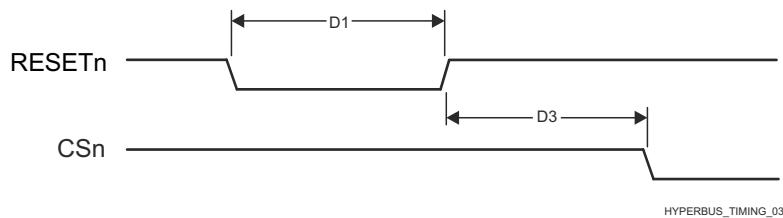

- 1 つの OSPI または HyperBus™ または QSPI、および

- 1 つの QSPI

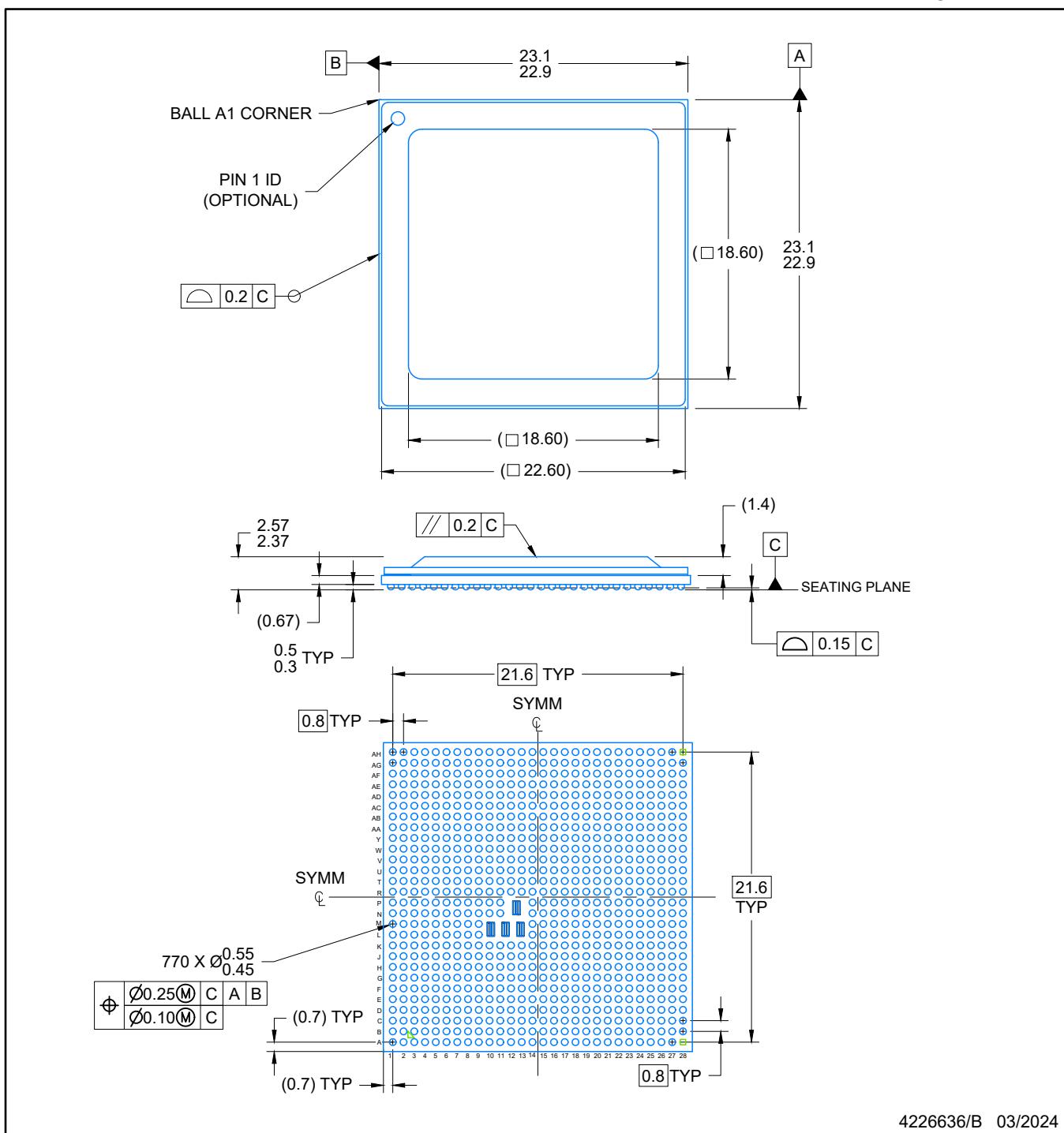

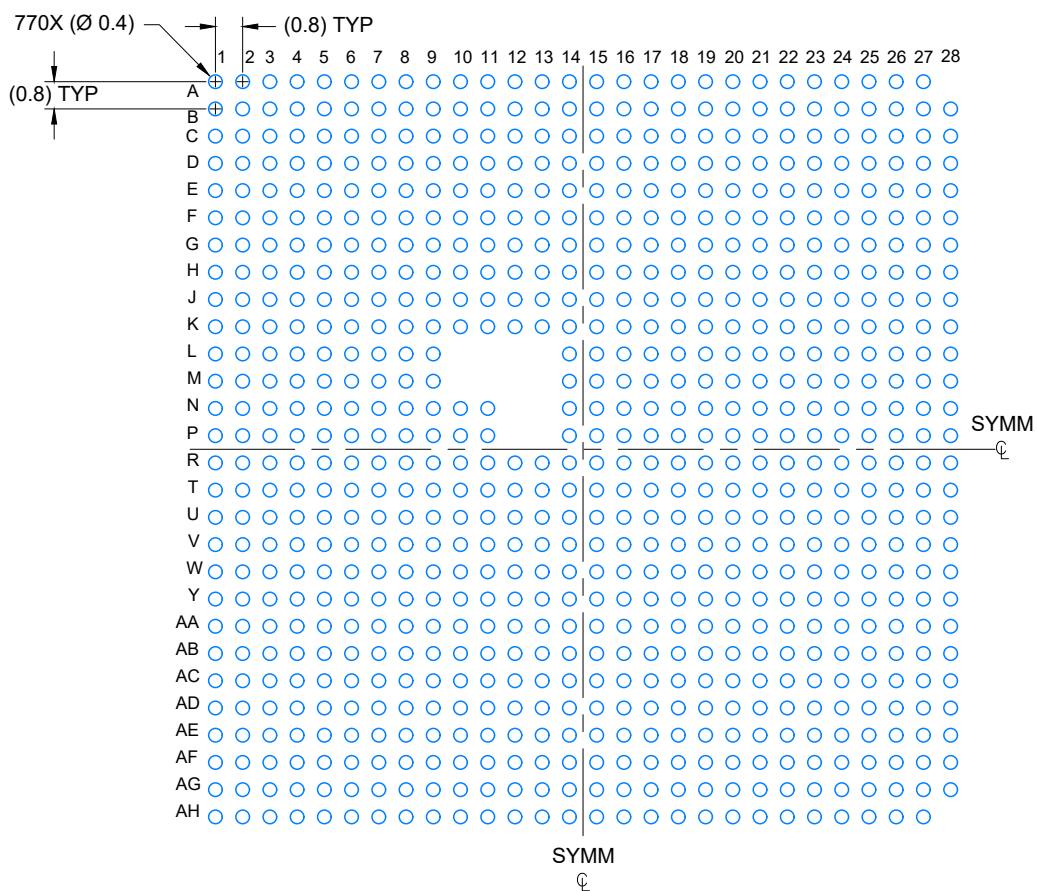

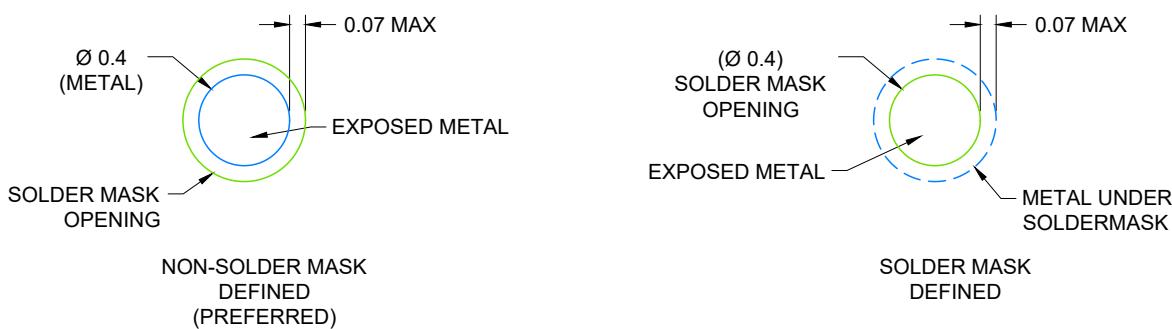

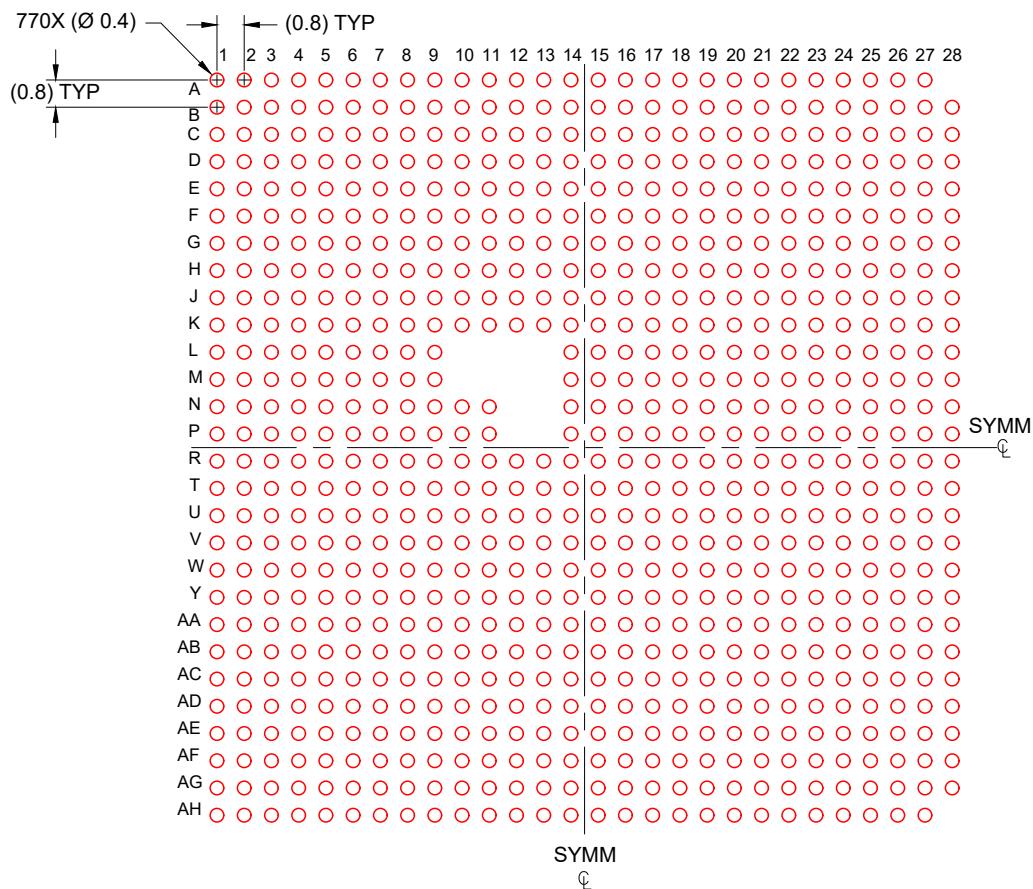

### テクノロジ / パッケージ:

- 16nm FinFET テクノロジ

- 23mm x 23mm、0.8mm ピッチ、770 ピンの FCBGA (ALZ)

### TPS6594-Q1 コンパニオン パワー マネージメント IC (PMIC):

- ASIL D/SIL 3 までの機能安全準拠サポートを対象

- 柔軟なマッピングにより各種の使用事例をサポート

## 2 アプリケーション

- マシン・ビジョン・カメラおよびコンピュータ

- スマート・ショッピング・カート

- リテール・オートメーション

- スマート農業

- ビデオ監視

- 交通監視

- 自律型モバイル・ロボット (AMR)

- ドローン

- 産業用輸送

- 産業用ヒューマン・マシン・インターフェイス (HMI)

- 産業用 PC

- シングル・ボード・コンピュータ

- 患者監視と医療機器

### 3 説明

AM68 拡張可能プロセッサ ファミリは、画期的な Jacinto™ 7 アーキテクチャを基礎とし、スマート ビジョン カメラおよび汎用コンピューティング アプリケーションを対象としており、ビジョン プロセッサ市場において テキサス・インスツルメンツがリーダーとして 10 年以上蓄積した膨大な市場知識の上に構築されています。AM68x ファミリは、ファクトリ オートメーション、ビル オートメーション、その他の市場におけるコスト重視の高性能コンピューティング アプリケーションを幅広く想定して構築されています。

AM68 は、高度なシステム統合によって、従来型ヒューリスティックとディープ ラーニングの両方のアルゴリズムを業界最高の電力 / 性能比で高速に計算するテクノロジを備え、先進ビジョン カメラ アプリケーションの拡張性とコスト低減を実現できます。主要なコアは、最新の汎用コンピューティング向け Arm および GPU プロセッサ、スカラおよびベクタ コアを搭載した次世代 DSP、専用のディープ ラーニングおよび従来のアルゴリズム アクセラレータ、統合型次世代イメージング サブシステム (ISP)、ビデオ コーデック、ならびに分離された MCU アイランドを備えています。これらはすべて、産業グレードの安全およびセキュリティ ハードウェア アクセラレータにより保護されています。

**汎用コンピューティング コアと統合の概要:** Arm® Cortex®-A72 の独立デュアル コア クラスタ構成を使うと、ソフトウェア ハイパーバイザの必要性を最小限に抑えながらマルチ OS アプリケーションを簡単に実現できます。最大 2 つの Arm® Cortex®-R5F サブシステムが低レベルのタイム クリティカルなタスクを処理し、Arm® Cortex®-A72 のコアに負荷がかからないようにしてアプリケーションの実行に備えます。既存の世界最先端の ISP に基づいて構築された テキサス・インスツルメンツの第 7 世代 ISP は、より広範なセンサ スイートを処理する柔軟性、より深いビット深度のサポート、分析アプリケーションを対象とした機能を備えています。内蔵セキュリティ機能が最新の攻撃からデータを保護する一方で、内蔵の診断および安全性機能は SIL-2 レベルまでの動作をサポートしています。CSI2.0 ポートにより、複数のセンサ入力が可能です。

**主要な高性能コアの概要:** C7000™ DSP 次世代コア (‘C7x’) は、テキサス・インスツルメンツの業界最先端の DSP と EVE コアを 1 つの高性能コアに統合し、浮動小数点ベクトル計算機能を追加することで、ソフトウェアのプログラミングを簡単にしながら従来のコードとの後方互換性を確保しています。新しい「MMA」ディープ ラーニング アクセラレータは、最も厳しい接合部温度である 105°C~125°C で動作する場合でも、業界最小の電力エンベロープ内で最大 8TOPS (1 秒あたり 8 兆回の演算) の性能を達成できます。専用ビジョン ハードウェア アクセラレータは、システム性能に影響を及ぼさずにビジョン前処理を実行します。C7x/MMA コアは、AM68 クラスのプロセッサのディープ ラーニング機能でのみ利用できます。

#### パッケージ情報

| 部品番号  | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------|----------------------|--------------------------|

| AM68x | ALZ (FCBGA, 770)     | 23mm × 23mm              |

(1) 詳細については、「[メカニカル、パッケージ、および注文情報](#)」セクションを参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

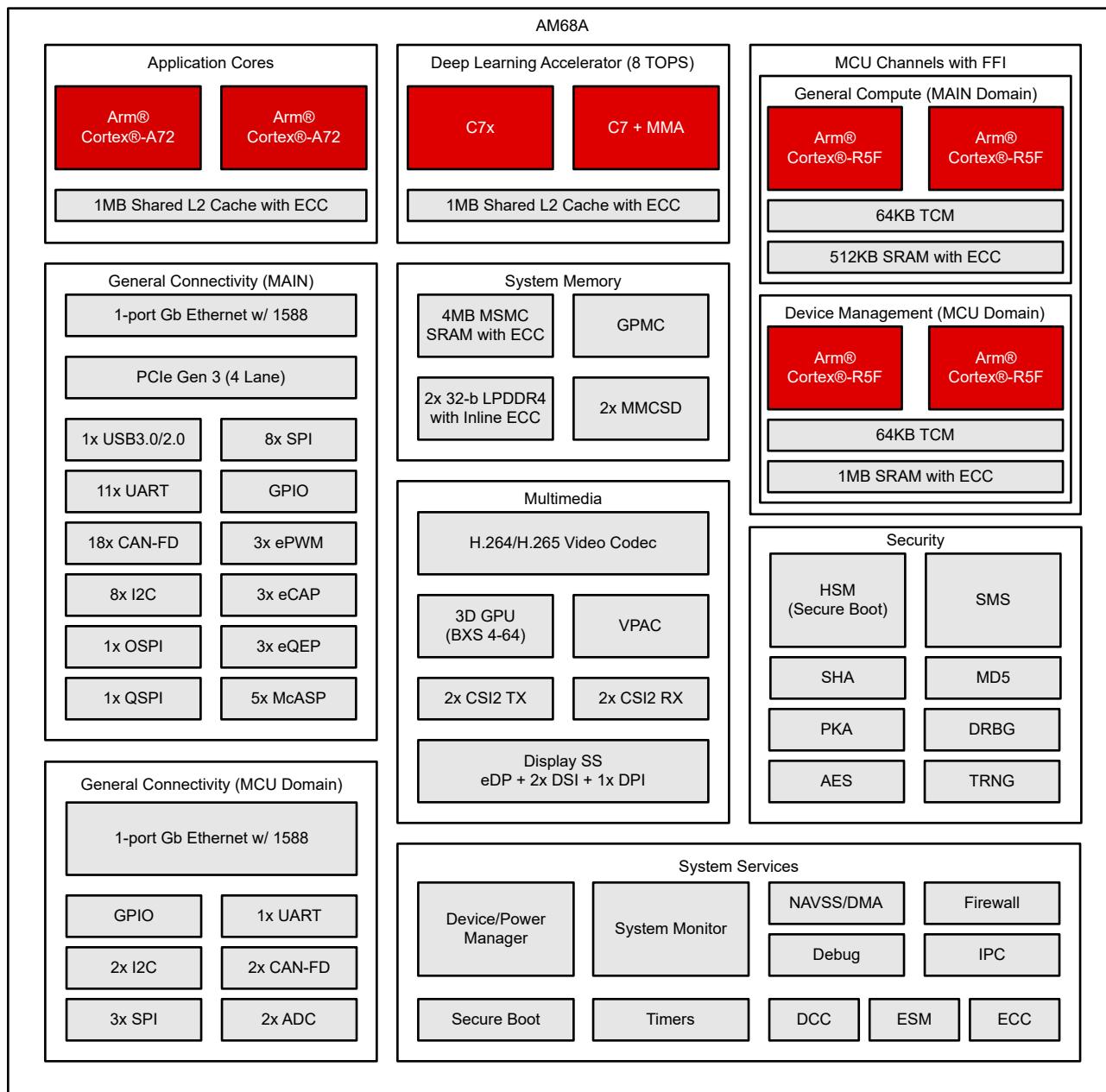

### 3.1 機能ブロック図

図 1-1 は、このデバイスの機能ブロック図です。

#### 注

テキサス・インスツルメンツのソフトウェア開発キット (SDK) が現在サポートしているデバイス機能の詳細については、[AM68 ソフトウェア ビルド シート \(PROCESSOR-SDK-AM68\)](#) および [AM68A ソフトウェア ビルド シート \(PROCESSOR-SDK-AM68A\)](#) を参照してください。

図 3-1. 機能ブロック図

## 目次

|                                        |            |                               |            |

|----------------------------------------|------------|-------------------------------|------------|

| <b>1 特長</b>                            | <b>1</b>   | 6.8 熱抵抗特性                     | <b>120</b> |

| <b>2 アプリケーション</b>                      | <b>2</b>   | 6.9 溫度センサの特性                  | <b>121</b> |

| <b>3 説明</b>                            | <b>3</b>   | 6.10 タイミングおよびスイッチング特性         | <b>122</b> |

| 3.1 機能ブロック図                            | 4          | <b>7 詳細説明</b>                 | <b>249</b> |

| <b>4 デバイスの比較</b>                       | <b>6</b>   | 8 アプリケーション、実装、およびレイアウト        | <b>250</b> |

| <b>5 端子構成および機能</b>                     | <b>8</b>   | 8.1 デバイスの接続およびレイアウトの基礎        | <b>250</b> |

| 5.1 ピン配置図                              | 8          | 8.2 ペリフェラルおよびインターフェイス固有の設計情報  | <b>250</b> |

| 5.2 ピン属性                               | 8          | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>257</b> |

| 5.3 信号の説明                              | 63         | 9.1 デバイスの命名規則                 | <b>257</b> |

| 5.4 未使用ピンの接続                           | 101        | 9.2 ツールとソフトウェア                | <b>259</b> |

| <b>6 仕様</b>                            | <b>105</b> | 9.3 ドキュメントのサポート               | <b>260</b> |

| 6.1 絶対最大定格                             | 105        | 9.4 商標                        | <b>260</b> |

| 6.2 ESD 定格                             | 108        | 9.5 サポート・リソース                 | <b>260</b> |

| 6.3 推奨動作条件                             | 108        | 9.6 静電気放電に関する注意事項             | <b>260</b> |

| 6.4 パワー オン時間 (POH) の制限                 | 110        | 9.7 用語集                       | <b>261</b> |

| 6.5 動作性能ポイント                           | 111        | <b>10 改訂履歴</b>                | <b>261</b> |

| 6.6 電気的特性                              | 112        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>262</b> |

| 6.7 ワンタイム プログラマブル (OTP) eFuse の VPP 仕様 | 118        | 11.1 パッケージ情報                  | <b>262</b> |

## 4 デバイスの比較

表 4-1 に、SoC の機能を示します。

### 注

テキサス・インスツルメンツのソフトウェア開発キット (SDK) が現在サポートしているデバイス機能の詳細については、[AM68 ソフトウェア ビルド シート \(PROCESSOR-SDK-AM68\)](#) および [AM68A ソフトウェア ビルド シート \(PROCESSOR-SDK-AM68A\)](#) を参照してください。

**表 4-1. デバイスの比較**

| 特長 <sup>(7)</sup>                               | 参照名                    | AM68A9                           | AM685 |

|-------------------------------------------------|------------------------|----------------------------------|-------|

| <b>プロセッサおよびアクセラレータ</b>                          |                        |                                  |       |

| 速度グレード                                          |                        | T                                | T     |

| Arm Cortex-A72 マイクロプロセッサ サブシステム                 | Arm A72                | デュアル コア                          |       |

| ARM Cortex-R5F                                  | Arm R5F<br>デバイス管理      | デュアル コア (10)                     |       |

|                                                 | Arm R5F<br>汎用コンピューティング | デュアル コア (10)                     |       |

| セキュリティ管理サブシステム                                  | SMS                    | あり                               |       |

| セキュリティアクセラレータ                                   | SA                     | あり                               |       |

| ディープ ラーニング アクセラレータ (8 TOPS)                     | C7x DSP                | あり <sup>(11)</sup>               | なし    |

|                                                 | C7x DSP + MMA          | あり <sup>(11)</sup>               | なし    |

| グラフィックス アクセラレータ IMG BXS-4-64                    | GPU                    | あり                               | あり    |

| 深度およびモーション処理アクセラレータ                             | DMPAC                  | なし                               |       |

| ビジョン処理アクセラレータ                                   | VPAC                   | あり                               | なし    |

| ビデオ エンコーダ / デコーダ                                | VENC/VDEC              | エンコード / デコード                     |       |

| <b>安全およびセキュリティ</b>                              |                        |                                  |       |

| 安全を対象                                           | 安全                     | なし (1)                           |       |

| デバイスのセキュリティ                                     | セキュリティ                 | オプション (2)                        |       |

| AEC-Q100 認定済み                                   | Q1                     | オプション (3)                        |       |

| <b>プログラムおよびデータストレージ</b>                         |                        |                                  |       |

| MAIN ドメインのオンチップ共有メモリ (RAM)                      | OCSRAM                 | 512KB SRAM                       |       |

| MCU ドメインのオンチップ共有メモリ (RAM)                       | MCU_MSRAM              | 1MB SRAM                         |       |

| マルチコア共有メモリコントローラ                                | MSMC                   | 4MB (ECC 付きのオンチップ SRAM)          |       |

| LPDDR4 DDR サブシステム                               | DDRSS0 <sup>(4)</sup>  | 最大 8GB (32 ビット データ)、インライン ECC 付き |       |

|                                                 | DDRSS1 <sup>(4)</sup>  | 最大 8GB (32 ビット データ)、インライン ECC 付き |       |

|                                                 | SECDED                 | あり                               |       |

| 汎用メモリコントローラ                                     | GPMC                   | 最大 1GB、ECC 付き                    |       |

| <b>ペリフェラル</b>                                   |                        |                                  |       |

| ディスプレイ サブシステム                                   | DSS                    | あり                               |       |

|                                                 | DSI 4L TX              | 2                                |       |

|                                                 | eDP 4L                 | 1                                |       |

|                                                 | DPI                    | 1                                |       |

| モジュール式コントローラ エリア ネットワーク インターフェイス、CAN-FD フル サポート | MCAN                   | 20                               |       |

| 汎用 I/O                                          | GPIO                   | 155                              |       |

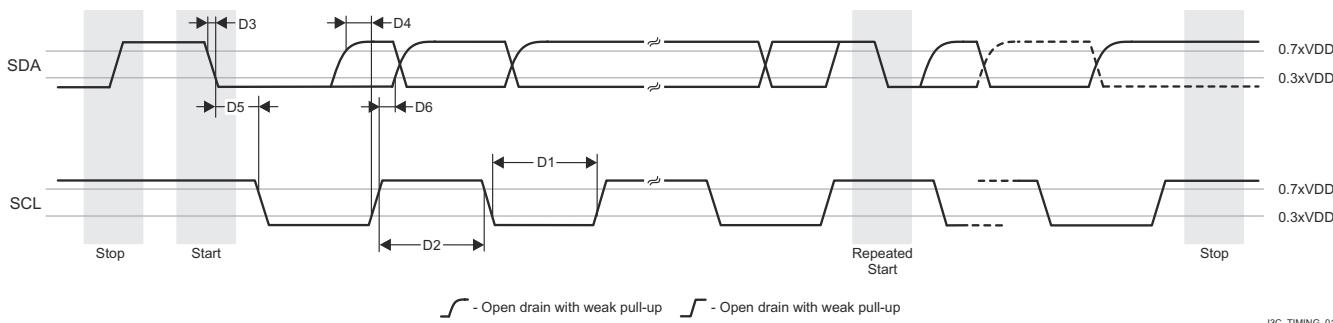

| 集積回路間インターフェイス                                   | I2C                    | 10                               |       |

**表 4-1. デバイスの比較 (続き)**

| 特長 <sup>(7)</sup>                                                   | 参照名                  | AM68A9                  | AM685 |

|---------------------------------------------------------------------|----------------------|-------------------------|-------|

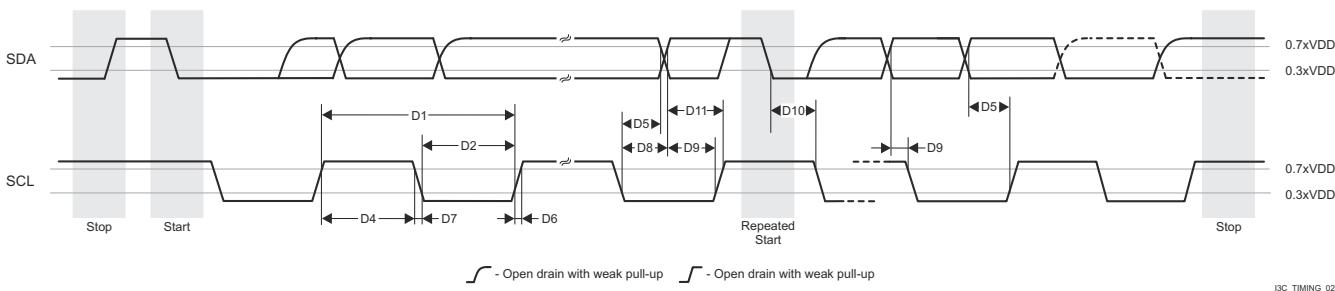

| 改良版集積回路間インターフェイス                                                    | I3C                  | 1                       |       |

| A/D コンバータ                                                           | ADC                  | 2                       |       |

| キャプチャ サブシステム、カメラ シリアル インターフェイス (CSI2) 付き                            | CSI2.0 4L RX         | 2                       |       |

|                                                                     | CSI2.0 4L TX         | 2                       |       |

| マルチチャネル シリアル ペリフェラル インターフェイス                                        | MCSPI                | 11                      |       |

| マルチチャネル オーディオ シリアル ポート                                              | MCASP0               | 16 個のシリアルライザ            |       |

|                                                                     | MCASP1               | 5 個のシリアルライザ             |       |

|                                                                     | MCASP2               | 5 個のシリアルライザ             |       |

|                                                                     | MCASP3               | 3 個のシリアルライザ             |       |

|                                                                     | MCASP4               | 5 個のシリアルライザ             |       |

| マルチメディア カード / セキュア デジタル インターフェイス                                    | MMCSD0               | eMMC (8 ビット)            |       |

|                                                                     | MMCSD1               | SD/SDIO (4 ビット)         |       |

| ユニバーサル フラッシュ ストレージ                                                  | UFS 2L               | なし                      |       |

| フラッシュ サブシステム (FSS)                                                  | OSPI0                | 8 ビット <sup>(6)</sup>    |       |

|                                                                     | OSPI1 <sup>(8)</sup> | 4 ビット                   |       |

|                                                                     | HyperBus             | あり <sup>(6)</sup>       |       |

| PHY 内蔵 PCI Express ポート × 4                                          | PCIE0                | 最大 4 レーン <sup>(5)</sup> |       |

| Hyperlink                                                           | HYP                  | なし <sup>(9)</sup>       |       |

| ギガビット イーサネット インターフェイス                                               | MCU                  | 1x RGMII または RMII       |       |

|                                                                     | メイン                  | 1x RGMII または RMII       |       |

| 汎用タイマー                                                              | TIMER                | 30                      |       |

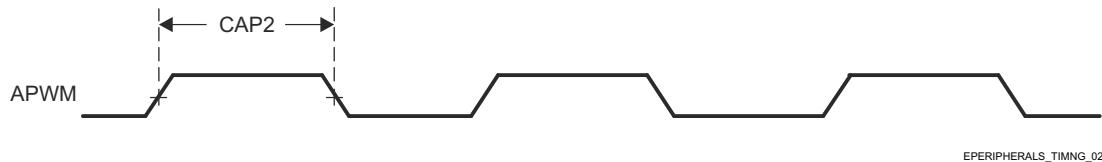

| 改良型高分解能パルス幅変調器モジュール                                                 | eHRPWM               | 6                       |       |

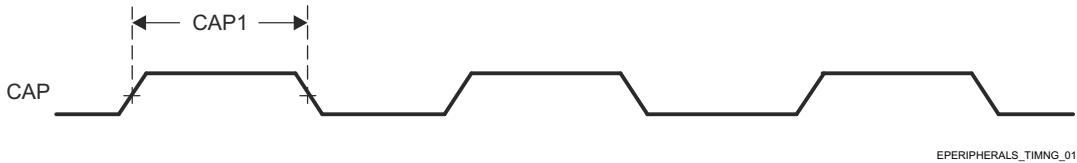

| 拡張キャプチャ モジュール                                                       | eCAP                 | 3                       |       |

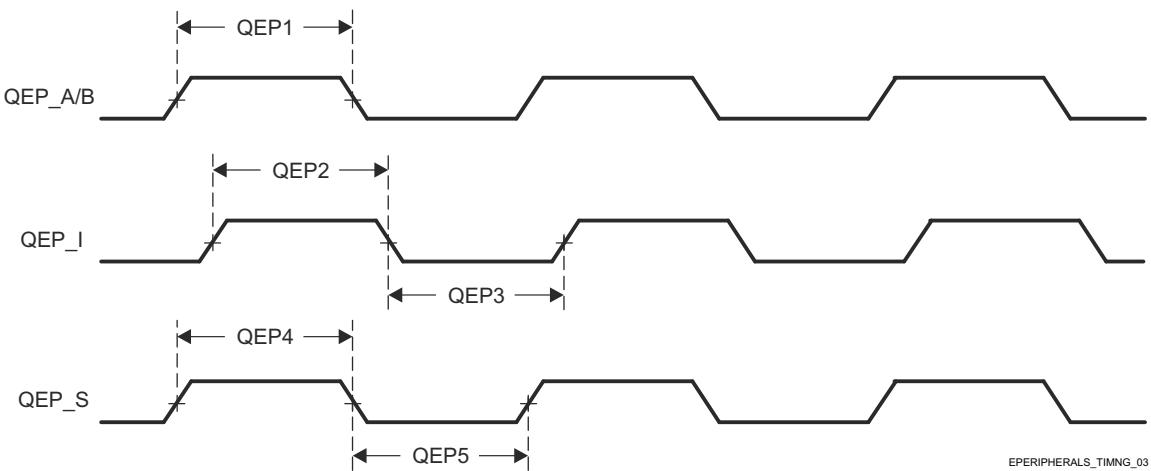

| 拡張直交エンコーダ パルス モジュール                                                 | eQEP                 | 3                       |       |

| 汎用非同期レシーバ / トランスマッタ                                                 | UART                 | 12                      |       |

| ユニバーサル シリアルバス (USB3.1) SuperSpeed デュアル ロール デバイス (DRD) ポート、SS PHY 付き | USB0                 | あり <sup>(5)</sup>       |       |

- (1) このデバイス ファミリは、機能安全をサポートしていません。この機能に关心をお持ちの場合、[TDA4VE デバイス ファミリ](#)をご覧ください。

- (2) セキュア ブートや顧客がプログラム可能なキーなどのデバイス セキュリティ機能は、表 10-1 項目名の説明の表のデバイスタイプ (Y) 識別子で示されている型番バリエントを選択する場合にのみ適用されます。

- (3) AEC-Q100 認定は、表 10-1 項目名の説明の表の車載識別記号 (Q1) 識別子で示されている型番バリエントを選択する場合にのみ適用されます。

- (4) DDRSS0 と DDRSS1 は常に増分の順序で使用する必要があります。たとえば、単一の LPDDR 部品を使用する場合は、DDR0\_\* インターフェイスに接続する必要があります。

- (5) USB3.0、PCIE で合計 4 つの SerDes レーンを共有しています。

- (6) 2 つの同時フラッシュ インターフェイスは OSPI0 と OSPI1、または HyperBus と OSPI1 として構成。

- (7) J721S2 はスーパーセット デバイスの基本型番です。ソフトウェアは、目的の量産デバイスに合わせて、使用する機能に制約を加える必要があります。

- (8) OSPI1 モジュールは 4 本のピンのみを配置しており、文脈によっては QSPI と呼ばれます。

- (9) この SoC ではハイパーリンクはサポートされていません。システム設計では信号 HYP\_\*、HYP0\_\*、HYP1\_\* を使用しないでください。

- (10) MCU\_R5FSS0 は、デバイス管理機能を提供するデュアルコア R5F を搭載しており、テキサス・インスツルメンツが提供するコードを実行するために予約されています。

- R5FSS1 は、マルチメディア制御機能を提供するデュアルコア R5F で、テキサス・インスツルメンツが提供するコードを実行するために予約されています。

- (11) 2 個の C7x DSP は、テキサス・インスツルメンツが提供するコードを実行するために予約されており、カスタム コードでは利用できません。

## 5 端子構成および機能

### 5.1 ピン配置図

パッケージ情報を参照。

### 5.2 ピン属性

- ボール番号:** ボールグリッドアレイパッケージの各端子に割り当てられたボール番号。

- ボール名:** ボールグリッドアレイパッケージの各端子に割り当てられたボール名 (通常はプライマリ MUXMODE 0 信号機能からつけた名前)。

- 信号名:** ボールに関連するすべての専用およびピン多重化信号機能の信号名。

#### 注

「ピン属性」表は、ピンに実装される SoC ピン多重化信号機能を定義しており、デバイスサブシステムに実装される信号機能の 2 次多重化は定義していません。信号機能の 2 次多重化については、この表では説明しません。2 次多重化信号機能の詳細については、デバイスのテクニカルリファレンスマニュアルで該当するペリフェラルの章を参照してください。

- MUXMODE:** 各ピンの多重化信号機能に関連付けられた MUXMODE 値:

- MUXMODE 0 は、プライマリピンの多重化信号機能です。ただし、プライマリピンの多重化信号機能は、必ずしもデフォルトのピン多重化信号機能とは限りません。

- ピン多重化信号機能には、MUXMODE の値 1~15 を使用できます。ただし、すべての MUXMODE 値が実装されているわけではありません。有効な MUXMODE 値は、「ピン属性」表でピン多重化された信号機能として定義された値のみです。MUXMODE の有効な値のみを使用できます。

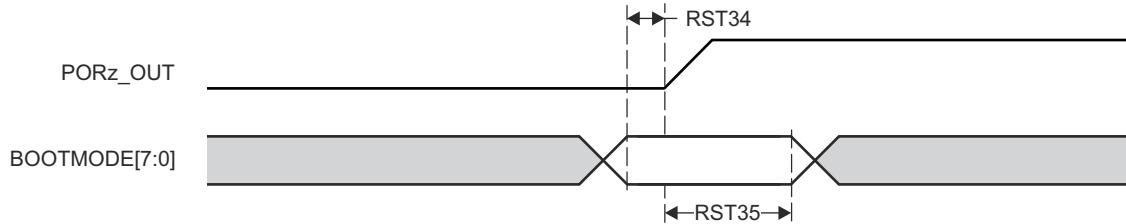

- ブートストラップは SOC 構成ピンを定義します。各ピンに適用されるロジック状態は、PORz\_OUT の立ち上がりエッジでラッチされます。これらの入力信号機能はそれぞれのピンに固定で、MUXMODE を使用してプログラムすることはできません。

- 空欄または「-」は、該当しないことを意味します。

#### 注

- 「リセット後の MUX モード」列の値は、MCU\_PORz がアサート解除されたときに選択されるデフォルトのピン多重化信号機能を定義します。

- 同じピン多重化信号機能に 2 つのピンを構成すると、予期しない結果が生じる可能性があるため、この構成はサポートされていません。これは、正しいソフトウェア構成によって防止できます。

- パッドを未定義の多重化モードに構成すると、未定義の動作が生じるため、このような構成は避ける必要があります。

- タイプ:** 信号の種類と方向:

- I = 入力

- O = 出力

- OD = 出力、オープンドレイン出力機能付き

- IO = 入力、出力、または同時に入力と出力

- IOD = 入力、出力、または同時に入力と出力、オープンドレイン出力機能付き

- IOZ = 入力、出力、または同時に入力と出力、3 ステート出力機能付き

- OZ = 出力、3 ステート出力機能付き

- A = アナログ

- CAP = LDO コンデンサ

- PWR = 電源

- GND = グラウンド

- I/O 動作電圧:** この列は、IO 電圧値 (対応する電源) を示します。

空欄は該当しないことを意味します。

7. **RESET 時のボールの状態:**MCU\_PORz がアサートされているときの端子の状態。ここで、RX は入力バッファの状態、TX は出力バッファの状態、PULL は内部プル抵抗の状態を定義します。

- RX (入力バッファ)

- オフ:入力バッファは無効です。

- オン:入力バッファは有効です。

- TX (出力バッファ)

- オフ:出力バッファは無効です。

- Low:出力バッファは有効であり、 $V_{OL}$  を駆動します。

- High:出力バッファは有効であり、 $V_{OH}$  を駆動します。

- PULL (内部プル抵抗)

- オフ:内部プル抵抗はオフになっています。

- アップ:内部プルアップ抵抗がオンになっています。

- ダウン:内部プルダウン抵抗がオンになっています。

- NA:内部プル抵抗なし。

- 空欄、または「-」は該当しないことを意味します。

8. **RESET 後のボールの状態:**MCU\_PORz がアサート解除された後の端子の状態。ここで、RX は入力バッファの状態、TX は出力バッファの状態、PULL は内部プル抵抗の状態を定義します。

- RX (入力バッファ)

- オフ:入力バッファは無効です。

- オン:入力バッファは有効です。

- TX (出力バッファ)

- オフ:出力バッファは無効です。

- SS: MUXMODE で選択されたサブシステムによって、出力バッファの状態が決まります。

- PULL (内部プル抵抗)

- オフ:内部プル抵抗はオフになっています。

- アップ:内部プルアップ抵抗がオンになっています。

- ダウン:内部プルダウン抵抗がオンになっています。

- NA:内部プル抵抗なし。

- 空欄、NA、「-」は該当しないことを意味します。

9. **リセット後の多重化モード:**この列の値は、MCU\_PORz がアサート解除された後のデフォルトのピン多重化信号機能を定義します。

- 空欄、NA、「-」は該当しないことを意味します。

10. **プルタイプ:**内部プルアップまたはプルダウン抵抗が存在することを示します。プルアップおよびプルダウン抵抗は、ソフトウェアによって有効化または無効化できます。

- PU:内部プルアップのみ

- PD:内部プルダウンのみ

- PU/PD:内部プルアップおよびプルダウン

- 空欄、NA、「-」は、内部プルが存在しないことを意味します。

---

## 注

同じピン多重化信号機能に 2 つのピンを構成すると、予期しない結果が生じる可能性があるため、この構成はサポートされていません。この問題は、正しいソフトウェア構成を使用すると簡単に防止できます。

ピン多重化で定義されない多重化モードにパッドが設定されたとき、そのパッドの挙動は未定義になります。これは避ける必要があります。

---

11. **電源:**関連付けられている I/O の電源 (該当する場合)。

- 空欄、NA、「-」は該当しないことを意味します。

12. **HYS:**この I/O に関連付けられている入力バッファにヒステリシスがあるかどうかを示します。

- あり:ヒステリシスのサポート

- なし:ヒステリシスのサポートなし

- 空欄、NA、「-」は該当しないことを意味します。

詳細については、「電気的特性」のヒステリシスの値を参照してください。

13. **電圧バッファのタイプ:**この列は、端末に関連付けられたバッファのタイプを定義します。この情報を使用して、該当する「電気的特性」表を決定できます。

- 空欄、NA、「-」は該当しないことを意味します。

電気的特性については、「電気的特性」セクションの適切なバッファ タイプの表を参照してください。

14. **IO RET:Yes** は、WKUP と IO 保持がサポートされていることを意味します。

15. **PADCFG 名:**デバイスのパッド / ピン構成レジスタの名前です。

16. **PADCFG アドレス:**これは、デバイスのパッド / ピン構成レジスタのメモリ アドレスです。

**表 5-1. ピン属性 (ALZ パッケージ)**

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]       | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                                 | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|---------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|-----------------------------------------|-------------|-----------------|-------------|

| T21       | CAP_VDDS0                                        | CAP_VDDS0     |            | CAP       |             |                               |                               |                  |             |                                         |             |                 |             |

| J20       | CAP_VDDS0_MCU                                    | CAP_VDDS0_MCU |            | CAP       |             |                               |                               |                  |             |                                         |             |                 |             |

| G16       | CAP_VDDS1_MCU                                    | CAP_VDDS1_MCU |            | CAP       |             |                               |                               |                  |             |                                         |             |                 |             |

| P21       | CAP_VDDS2                                        | CAP_VDDS2     |            | CAP       |             |                               |                               |                  |             |                                         |             |                 |             |

| H17       | CAP_VDDS2_MCU                                    | CAP_VDDS2_MCU |            | CAP       |             |                               |                               |                  |             |                                         |             |                 |             |

| M22       | CAP_VDDS5                                        | CAP_VDDS5     |            | CAP       |             |                               |                               |                  |             |                                         |             |                 |             |

| AH19      | CSI0_RXCLKN                                      | CSI0_RXCLKN   |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AH20      | CSI0_RXCLKP                                      | CSI0_RXCLKP   |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AC18      | CSI0_RXRCALIB                                    | CSI0_RXRCALIB |            | A         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AH22      | CSI1_RXCLKN                                      | CSI1_RXCLKN   |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AH23      | CSI1_RXCLKP                                      | CSI1_RXCLKP   |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AC21      | CSI1_RXRCALIB                                    | CSI1_RXRCALIB |            | A         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AG18      | CSI0_RXN0                                        | CSI0_RXN0     |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AF19      | CSI0_RXN1                                        | CSI0_RXN1     |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AE18      | CSI0_RXN2                                        | CSI0_RXN2     |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

| AD19      | CSI0_RXN3                                        | CSI0_RXN3     |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C_SIRX0_1 / VDDA_1P8_C_SIRX0_1 |             | D-PHY           |             |

表 5-1. ピン属性 (ALZ パッケージ) (続き)

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]   | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                                          | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-----------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|--------------------------------------------------|-------------|-----------------|-------------|

| AG19      | CSI0_RXP0                                        | CSI0_RXP0 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AF20      | CSI0_RXP1                                        | CSI0_RXP1 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AE19      | CSI0_RXP2                                        | CSI0_RXP2 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AD20      | CSI0_RXP3                                        | CSI0_RXP3 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AG21      | CSI1_RXN0                                        | CSI1_RXN0 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AF22      | CSI1_RXN1                                        | CSI1_RXN1 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AE21      | CSI1_RXN2                                        | CSI1_RXN2 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AD22      | CSI1_RXN3                                        | CSI1_RXN3 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AG22      | CSI1_RXP0                                        | CSI1_RXP0 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AF23      | CSI1_RXP1                                        | CSI1_RXP1 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AE22      | CSI1_RXP2                                        | CSI1_RXP2 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

| AD23      | CSI1_RXP3                                        | CSI1_RXP3 |            | I         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_C<br>SIRX0_1 /<br>VDDA_1P8_C<br>SIRX0_1 |             | D-PHY           |             |

**表 5-1. ピン属性 (ALZ パッケージ) (続き)**

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]     | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|------------------------|-------------|-----------------|-------------|

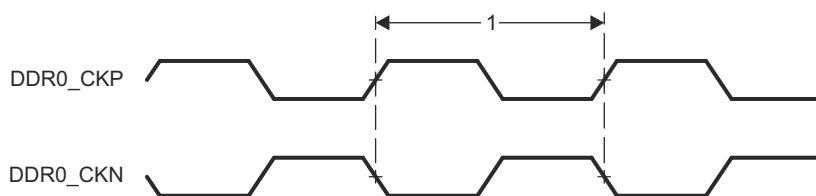

| R1        | DDR0_CKN                                         | DDR0_CKN    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| P1        | DDR0_CKP                                         | DDR0_CKP    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| R5        | DDR0_RESETn                                      | DDR0_RESETn |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| T8        | DDR0_RET                                         | DDR0_RET    |            | I         | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| A9        | DDR1_CKN                                         | DDR1_CKN    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| A10       | DDR1_CKP                                         | DDR1_CKP    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| F12       | DDR1_RESETn                                      | DDR1_RESETn |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| J10       | DDR1_RET                                         | DDR1_RET    |            | I         | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| P3        | DDR0_CA0                                         | DDR0_CA0    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| P5        | DDR0_CA1                                         | DDR0_CA1    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| N5        | DDR0_CA2                                         | DDR0_CA2    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| P2        | DDR0_CA3                                         | DDR0_CA3    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| P4        | DDR0_CA4                                         | DDR0_CA4    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| R3        | DDR0_CA5                                         | DDR0_CA5    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| R8        | DDR0_CAL0                                        | DDR0_CAL0   |            | A         | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| R2        | DDR0_CKE0                                        | DDR0_CKE0   |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

表 5-1. ピン属性 (ALZ パッケージ) (続き)

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]     | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | プルタイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧バッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|------------|------------------------|-------------|-----------------|-------------|

| R4        | DDR0_CKE1                                        | DDR0_CKE1   |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| V5        | DDR0_CSn0_0                                      | DDR0_CSn0_0 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| W5        | DDR0_CSn0_1                                      | DDR0_CSn0_1 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| T5        | DDR0_CSn1_0                                      | DDR0_CSn1_0 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| U6        | DDR0_CSn1_1                                      | DDR0_CSn1_1 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| H5        | DDR0_DM0                                         | DDR0_DM0    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| M3        | DDR0_DM1                                         | DDR0_DM1    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| U4        | DDR0_DM2                                         | DDR0_DM2    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AD1       | DDR0_DM3                                         | DDR0_DM3    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| F3        | DDR0_DQ0                                         | DDR0_DQ0    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| G4        | DDR0_DQ1                                         | DDR0_DQ1    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| F5        | DDR0_DQ2                                         | DDR0_DQ2    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| F1        | DDR0_DQ3                                         | DDR0_DQ3    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| J4        | DDR0_DQ4                                         | DDR0_DQ4    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| H3        | DDR0_DQ5                                         | DDR0_DQ5    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| J2        | DDR0_DQ6                                         | DDR0_DQ6    |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

**表 5-1. ピン属性 (ALZ パッケージ) (続き)**

| ボール番号 [1] | ボール名 [2]<br>PADCfg レジスタ [15]<br>PADCfg アドレス [16] | 信号名 [3]   | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-----------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|------------------------|-------------|-----------------|-------------|

| G2        | DDR0_DQ7                                         | DDR0_DQ7  |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| K5        | DDR0_DQ8                                         | DDR0_DQ8  |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| M5        | DDR0_DQ9                                         | DDR0_DQ9  |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| K3        | DDR0_DQ10                                        | DDR0_DQ10 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| K1        | DDR0_DQ11                                        | DDR0_DQ11 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| N4        | DDR0_DQ12                                        | DDR0_DQ12 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| N2        | DDR0_DQ13                                        | DDR0_DQ13 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| L4        | DDR0_DQ14                                        | DDR0_DQ14 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| L2        | DDR0_DQ15                                        | DDR0_DQ15 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| T1        | DDR0_DQ16                                        | DDR0_DQ16 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| T3        | DDR0_DQ17                                        | DDR0_DQ17 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| V3        | DDR0_DQ18                                        | DDR0_DQ18 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| U2        | DDR0_DQ19                                        | DDR0_DQ19 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| W2        | DDR0_DQ20                                        | DDR0_DQ20 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| W4        | DDR0_DQ21                                        | DDR0_DQ21 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| Y1        | DDR0_DQ22                                        | DDR0_DQ22 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

表 5-1. ピン属性 (ALZ パッケージ) (続き)

| ボール番号 [1] | ボール名 [2]<br>PADC <sub>FG</sub> レジスタ [15]<br>PADC <sub>FG</sub> アドレス [16] | 信号名 [3]    | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | プルタイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------------------------------|------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|------------|------------------------|-------------|-----------------|-------------|

| Y3        | DDR0_DQ23                                                                | DDR0_DQ23  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AB3       | DDR0_DQ24                                                                | DDR0_DQ24  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AA2       | DDR0_DQ25                                                                | DDR0_DQ25  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AA4       | DDR0_DQ26                                                                | DDR0_DQ26  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| Y5        | DDR0_DQ27                                                                | DDR0_DQ27  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AC2       | DDR0_DQ28                                                                | DDR0_DQ28  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AB5       | DDR0_DQ29                                                                | DDR0_DQ29  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AD2       | DDR0_DQ30                                                                | DDR0_DQ30  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AC4       | DDR0_DQ31                                                                | DDR0_DQ31  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| H1        | DDR0_DQS0N                                                               | DDR0_DQS0N |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| G1        | DDR0_DQS0P                                                               | DDR0_DQS0P |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| M1        | DDR0_DQS1N                                                               | DDR0_DQS1N |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| L1        | DDR0_DQS1P                                                               | DDR0_DQS1P |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| U1        | DDR0_DQS2N                                                               | DDR0_DQS2N |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| V1        | DDR0_DQS2P                                                               | DDR0_DQS2P |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| AC1       | DDR0_DQS3N                                                               | DDR0_DQS3N |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

**表 5-1. ピン属性 (ALZ パッケージ) (続き)**

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]     | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧バッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|------------------------|-------------|-----------------|-------------|

| AB1       | DDR0_DQS3P                                       | DDR0_DQS3P  |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C0 |             | DDR             |             |

| C10       | DDR1_CA0                                         | DDR1_CA0    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E10       | DDR1_CA1                                         | DDR1_CA1    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E9        | DDR1_CA2                                         | DDR1_CA2    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B10       | DDR1_CA3                                         | DDR1_CA3    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D10       | DDR1_CA4                                         | DDR1_CA4    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C9        | DDR1_CA5                                         | DDR1_CA5    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E8        | DDR1_CAL0                                        | DDR1_CAL0   |            | A         | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B9        | DDR1_CKE0                                        | DDR1_CKE0   |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D9        | DDR1_CKE1                                        | DDR1_CKE1   |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| F9        | DDR1_CSn0_0                                      | DDR1_CSn0_0 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| F8        | DDR1_CSn0_1                                      | DDR1_CSn0_1 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| F11       | DDR1_CSn1_0                                      | DDR1_CSn1_0 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| F10       | DDR1_CSn1_1                                      | DDR1_CSn1_1 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D16       | DDR1_DM0                                         | DDR1_DM0    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E13       | DDR1_DM1                                         | DDR1_DM1    |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

表 5-1. ピン属性 (ALZ パッケージ) (続き)

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]   | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | プルタイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧バッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-----------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|------------|------------------------|-------------|-----------------|-------------|

| F7        | DDR1_DM2                                         | DDR1_DM2  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B3        | DDR1_DM3                                         | DDR1_DM3  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B18       | DDR1_DQ0                                         | DDR1_DQ0  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E17       | DDR1_DQ1                                         | DDR1_DQ1  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D18       | DDR1_DQ2                                         | DDR1_DQ2  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| A17       | DDR1_DQ3                                         | DDR1_DQ3  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E15       | DDR1_DQ4                                         | DDR1_DQ4  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B16       | DDR1_DQ5                                         | DDR1_DQ5  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C15       | DDR1_DQ6                                         | DDR1_DQ6  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C17       | DDR1_DQ7                                         | DDR1_DQ7  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B14       | DDR1_DQ8                                         | DDR1_DQ8  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D14       | DDR1_DQ9                                         | DDR1_DQ9  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C13       | DDR1_DQ10                                        | DDR1_DQ10 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C11       | DDR1_DQ11                                        | DDR1_DQ11 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E11       | DDR1_DQ12                                        | DDR1_DQ12 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| A11       | DDR1_DQ13                                        | DDR1_DQ13 |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

**表 5-1. ピン属性 (ALZ パッケージ) (続き)**

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]   | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                | ヒステリシス [12] | 電圧バッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-----------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|------------------------|-------------|-----------------|-------------|

| B12       | DDR1_DQ14                                        | DDR1_DQ14 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D12       | DDR1_DQ15                                        | DDR1_DQ15 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B7        | DDR1_DQ16                                        | DDR1_DQ16 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D7        | DDR1_DQ17                                        | DDR1_DQ17 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C8        | DDR1_DQ18                                        | DDR1_DQ18 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| A8        | DDR1_DQ19                                        | DDR1_DQ19 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C6        | DDR1_DQ20                                        | DDR1_DQ20 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E6        | DDR1_DQ21                                        | DDR1_DQ21 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B5        | DDR1_DQ22                                        | DDR1_DQ22 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D5        | DDR1_DQ23                                        | DDR1_DQ23 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| B1        | DDR1_DQ24                                        | DDR1_DQ24 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| A4        | DDR1_DQ25                                        | DDR1_DQ25 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| C4        | DDR1_DQ26                                        | DDR1_DQ26 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| E4        | DDR1_DQ27                                        | DDR1_DQ27 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D1        | DDR1_DQ28                                        | DDR1_DQ28 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

| D3        | DDR1_DQ29                                        | DDR1_DQ29 |            | IO        | 1.1 V       |                               |                               |                  |             | VDDS_DDR / VDDS_DDR_C1 |             | DDR             |             |

表 5-1. ピン属性 (ALZ パッケージ) (続き)

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]     | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | プルタイプ [10] | 電源 [11]                                               | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|-------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|------------|-------------------------------------------------------|-------------|-----------------|-------------|

| C2        | DDR1_DQ30                                        | DDR1_DQ30   |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| E2        | DDR1_DQ31                                        | DDR1_DQ31   |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A15       | DDR1_DQS0N                                       | DDR1_DQS0N  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A16       | DDR1_DQS0P                                       | DDR1_DQS0P  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A12       | DDR1_DQS1N                                       | DDR1_DQS1N  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A13       | DDR1_DQS1P                                       | DDR1_DQS1P  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A7        | DDR1_DQS2N                                       | DDR1_DQS2N  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A6        | DDR1_DQS2P                                       | DDR1_DQS2P  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A2        | DDR1_DQS3N                                       | DDR1_DQS3N  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| A3        | DDR1_DQS3P                                       | DDR1_DQS3P  |            | IO        | 1.1 V       |                               |                               |                  |            | VDDS_DDR / VDDS_DDR_C1                                |             | DDR             |             |

| AG11      | DP0_AUXN                                         | DP0_AUXN    |            | IO        | 1.8 V       |                               |                               |                  |            | VDDA_1P8_S_ERDES2_4                                   |             | AUX-PHY         |             |

| AF11      | DP0_AUXP                                         | DP0_AUXP    |            | IO        | 1.8 V       |                               |                               |                  |            | VDDA_1P8_S_ERDES2_4                                   |             | AUX-PHY         |             |

| AH13      | DSI0_TXCLKN                                      | DSI0_TXCLKN | 0          | O         | 1.8 V       |                               |                               |                  |            | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI0_TXCLKN | 1          | O         |             |                               |                               |                  |            |                                                       |             |                 |             |

| AH14      | DSI0_TXCLKP                                      | DSI0_TXCLKP | 0          | O         | 1.8 V       |                               |                               |                  |            | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI0_TXCLKP | 1          | O         |             |                               |                               |                  |            |                                                       |             |                 |             |

**表 5-1. ピン属性 (ALZ パッケージ) (続き)**

| ボール番号 [1] | ボール名 [2]<br>PADCFG レジスタ [15]<br>PADCFG アドレス [16] | 信号名 [3]       | 多重化モード [4] | 信号タイプ [5] | I/O動作電圧 [6] | リセット時のボールの状態 (RX/TX/PULL) [7] | リセット後のボールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | ブルータイプ [10] | 電源 [11]                                               | ヒステリシス [12] | 電圧パッファのタイプ [13] | IO RET [14] |

|-----------|--------------------------------------------------|---------------|------------|-----------|-------------|-------------------------------|-------------------------------|------------------|-------------|-------------------------------------------------------|-------------|-----------------|-------------|

| AC13      | DSI0_TXRCALIB                                    | DSI0_TXRCALIB |            | A         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

| AH16      | DSI1_TXCLKN                                      | DSI1_TXCLKN   | 0          | O         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI1_TXCLKN   | 1          | O         |             |                               |                               |                  |             |                                                       |             |                 |             |

| AH17      | DSI1_TXCLKP                                      | DSI1_TXCLKP   | 0          | O         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI1_TXCLKP   | 1          | O         |             |                               |                               |                  |             |                                                       |             |                 |             |

| AC15      | DSI1_TXRCALIB                                    | DSI1_TXRCALIB |            | A         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

| AG12      | DSI0_TXN0                                        | DSI0_TXN0     | 0          | IO        | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI0_TXN0     | 1          | O         |             |                               |                               |                  |             |                                                       |             |                 |             |

| AF13      | DSI0_TXN1                                        | DSI0_TXN1     | 0          | O         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI0_TXN1     | 1          | O         |             |                               |                               |                  |             |                                                       |             |                 |             |

| AE12      | DSI0_TXN2                                        | DSI0_TXN2     | 0          | O         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI0_TXN2     | 1          | O         |             |                               |                               |                  |             |                                                       |             |                 |             |

| AD13      | DSI0_TXN3                                        | DSI0_TXN3     | 0          | O         | 1.8 V       |                               |                               |                  |             | VDDA_0P8_D_SITX / VDDA_0P8_D_SITX_C / VDDA_1P8_D_SITX |             | D-PHY           |             |

|           |                                                  | CSI0_TXN3     | 1          | O         |             |                               |                               |                  |             |                                                       |             |                 |             |

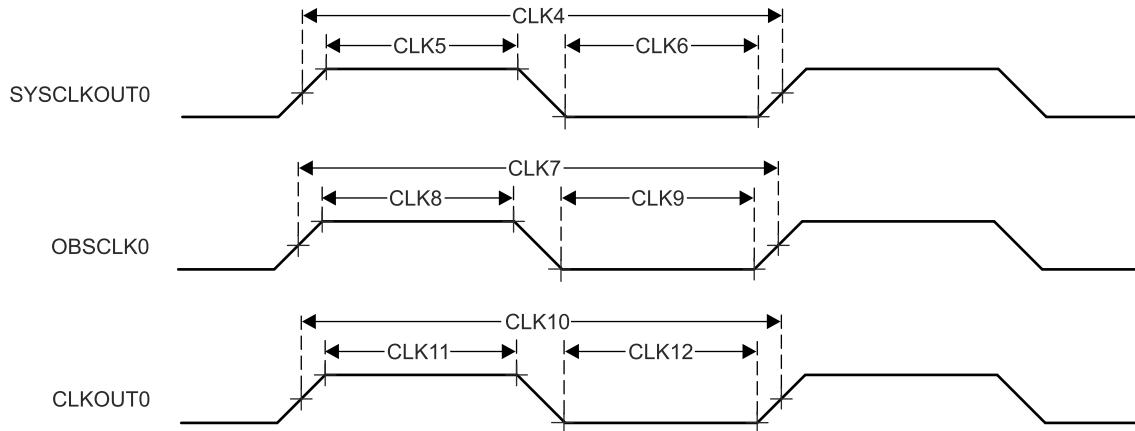

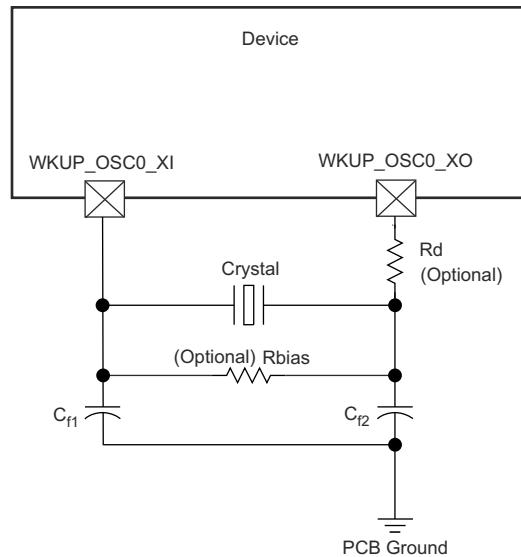

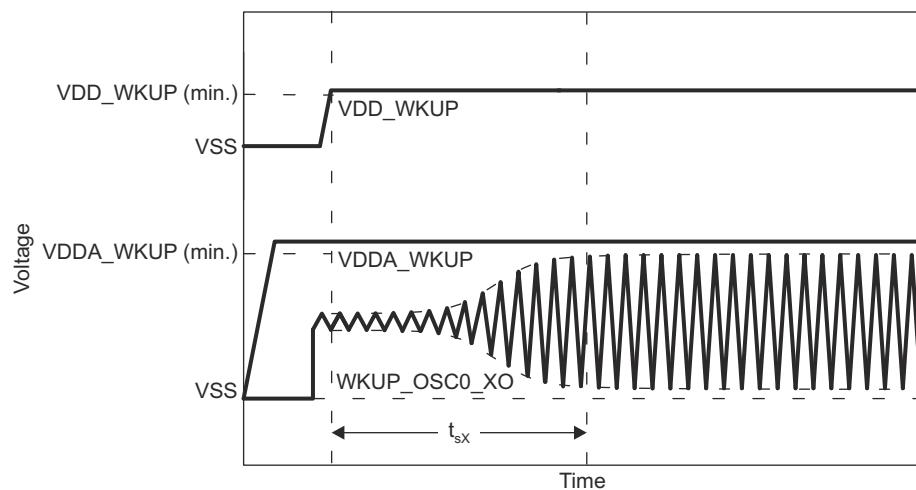

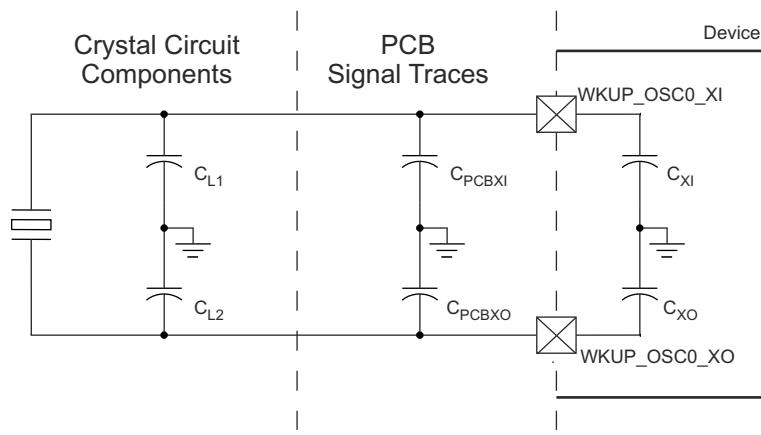

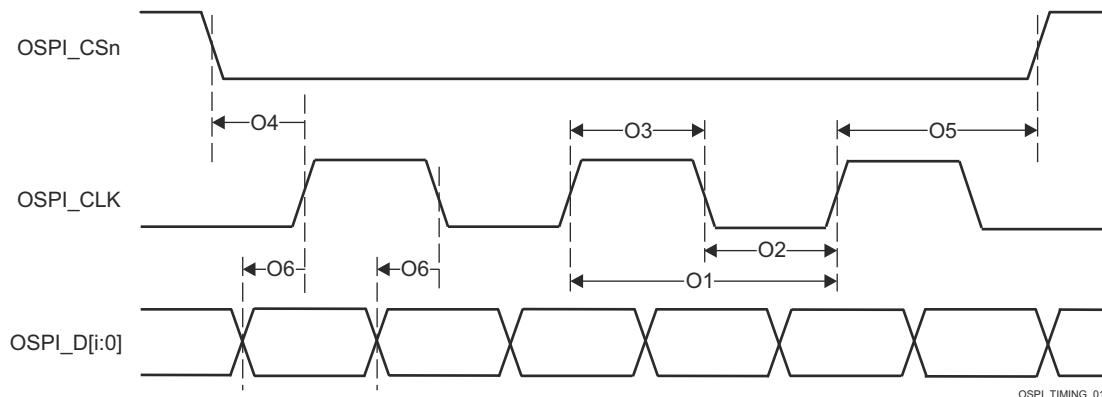

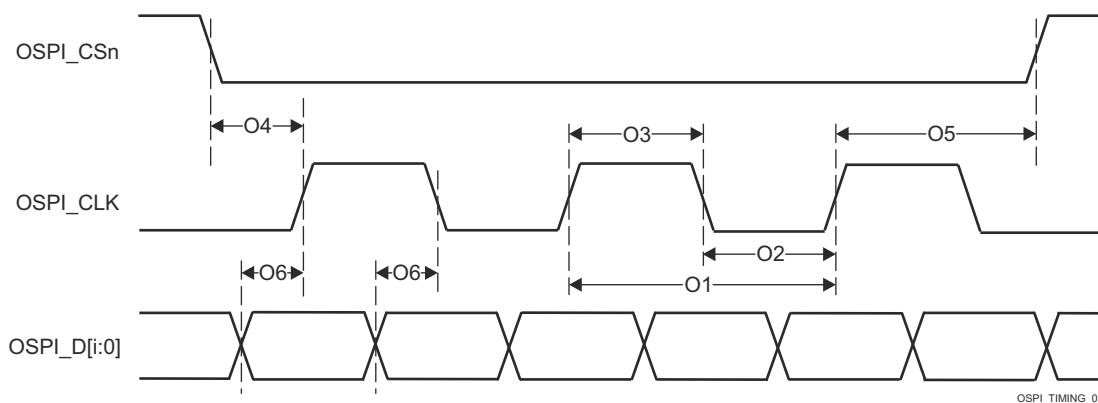

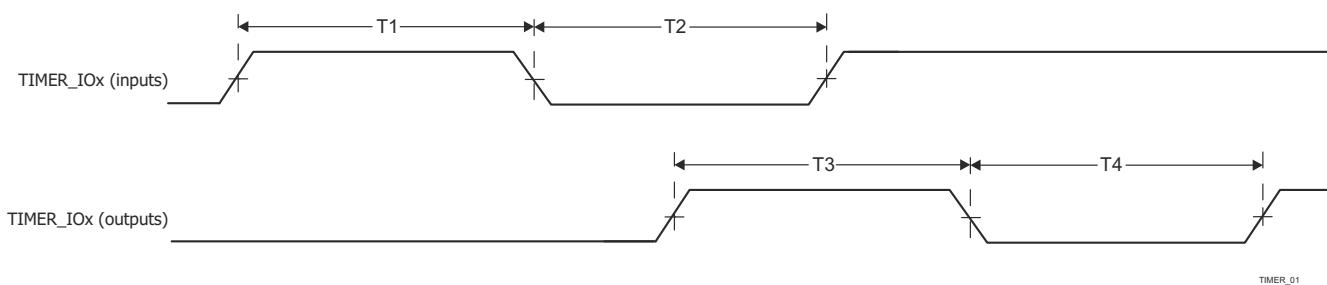

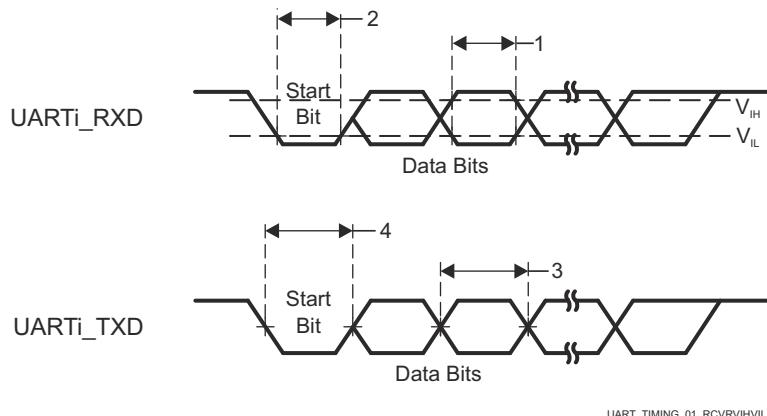

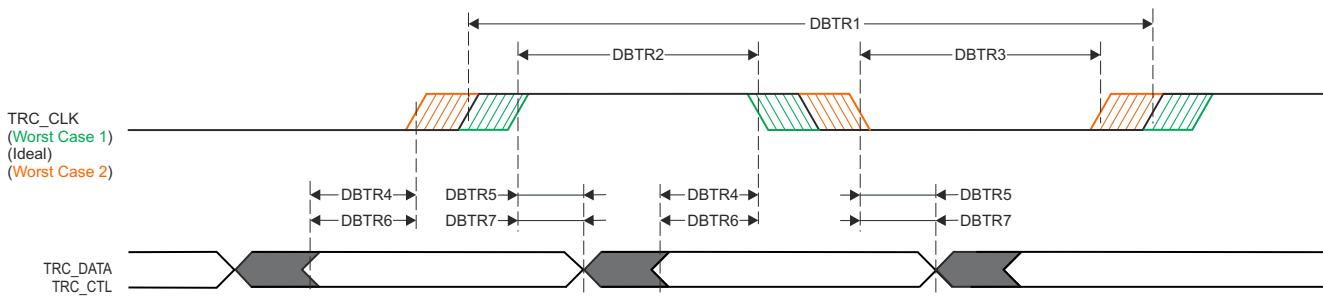

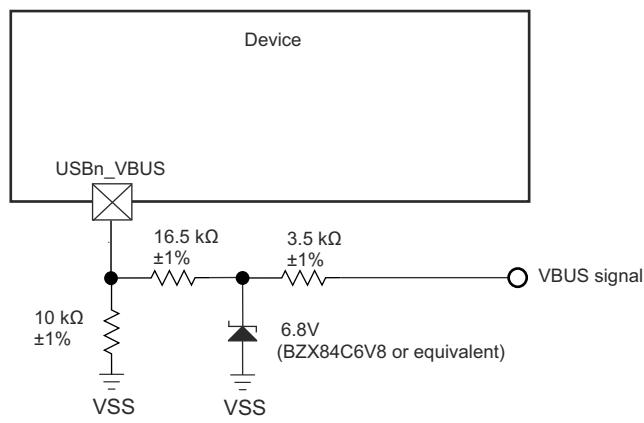

表 5-1. ピン属性 (ALZ パッケージ) (続き)