## AM62Dx Sitara™ プロセッサ

### 1 特長

#### プロセッサ コア:

- 最高 1.4GHz、クワッドまでの Arm® Cortex®-A53 マイクロプロセッサ サブシステム

- SECDED ECC 付き 512KB L2 共有キャッシュを搭載したクワッド コア Cortex-A53 クラスタ

- 各 A53 コアには、SECDED ECC を備えた 32KB L1 D キャッシュおよびパリティ保護を備えた 32KB L1 I キャッシュを搭載

- MCU チャネルの一部として統合され、最大 800MHz で動作するシングル コア Arm® Cortex®-R5F、FFI 付き

- 32KB の I キャッシュと 32KB の L1 D キャッシュ、64KB TCM (全メモリに SECDED ECC 付き)

- 512KB の SRAM (SECDED ECC 付き)

- デバイス管理をサポートするために集積化された、最大 800MHz、シングルコア Arm® Cortex®-R5F

- 32KB の I キャッシュと 32KB の L1 D キャッシュ、64KB TCM (全メモリに SECDED ECC 付き)

- シングルコア C7x ベースのマトリクス乗算アクセラレータ内蔵 DSP

- C7x 浮動小数点、1.0GHz、最大 40GFLOPS、256 ビットベクタ DSP

- マトリクス乗算アクセラレータ (MMA)、1.0GHz で最大 2TOPS (8b)

- SECDED ECC を備えた 64KB L1 D キャッシュ、およびパリティ保護を備えた 32KB L1 I キャッシュを搭載

- 1.25MB の L2 SRAM (SECDED ECC 付き)

#### メモリ サブシステム:

- 最大 2.29MB のオンチップ RAM

- SECDED ECC 付きの 64KB のオンチップ RAM (OCRAM) は、最大 2 つの独立したメモリ バンクについて、32KB 単位でより小さなバンクに分割可能

- SMS サブシステムに SECDED ECC を搭載した 256KB のオンチップ RAM

- テキサス・インスツルメンツのセキュリティファームウェア用の SMS サブシステムに SECDED ECC を搭載した 176KB のオンチップ RAM

- Cortex-R5F MCU サブシステムに SECDED ECC を搭載した 512KB のオンチップ RAM

- デバイス/パワー マネージャサブシステムに SECDED ECC を搭載した 64KB のオンチップ RAM

- C7x 内の SECDED ECC 付き 1.25MB L2 SRAM

#### マトリクス乗算アクセラレータ内蔵 DSP

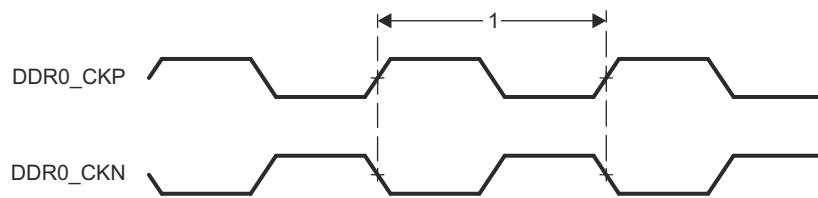

- DDR サブシステム (DDRSS)

- LPDDR4 対応

- インライン ECC 付きの 32 ビットデータバス

- 最大 3733MT/s の速度をサポート

- 8GBytes の最大アドレス可能範囲

#### 機能安全:

- 機能安全規格準拠**を対象とする [車載用]

- 機能安全アプリケーション向けに開発

- ISO 26262 機能安全システム設計を支援するドキュメントを準備中

- ASIL D までの決定論的対応能力を対象とする

- ASIL B までを対象とするハードウェア インテグリティ

- 安全関連の認証

- TÜV SÜD による ISO 26262 認証を計画中 (まで)

- AEC - Q100 認定済み [車載用]

#### セキュリティ:

- セキュア ブート対応

- ハードウェアで強化された RoT (Root-of-Trust: 信頼の基点)

- バックアップ キーによる RoT の切り替えをサポート

- ティクオーバー保護、IP 保護、ロールバック禁止保護のサポート

- 信頼できる実行環境 (TEE) に対応

- Arm TrustZone® をベースとする TEE

- 分離用の広範なファイアウォール サポート

- セキュアなウォッチドッグ / タイマ / IPC

- セキュアなストレージのサポート

- リプレイ保護メモリ ブロック (RPMB) のサポート

- ユーザー プログラマブルな HSM コアと専用セキュリティ DMA および IPC サブシステムの搭載により絶縁処理を実現した専用セキュリティコントローラ

- 暗号化アクセラレーションに対応

- 受信データストリームに基づいてキーマテリアルを自動的に切り替えできるセッション認識暗号化エンジン

- 暗号化コアをサポート

- AES - 128/192/256 ビットのキー サイズ

- SHA2 - 224/256/384/512 ビットのキー サイズ

- DRBG と真性乱数発生器

- セキュア ブート対応のため PKA (公開鍵アクセラレータ) により RSA/ECC 処理を支援

- デバッグのセキュリティ

- ソフトウェア制御によるセキュアなデバッグ アクセス

- セキュリティ対応のデバッグ

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

### 高速インターフェイス:

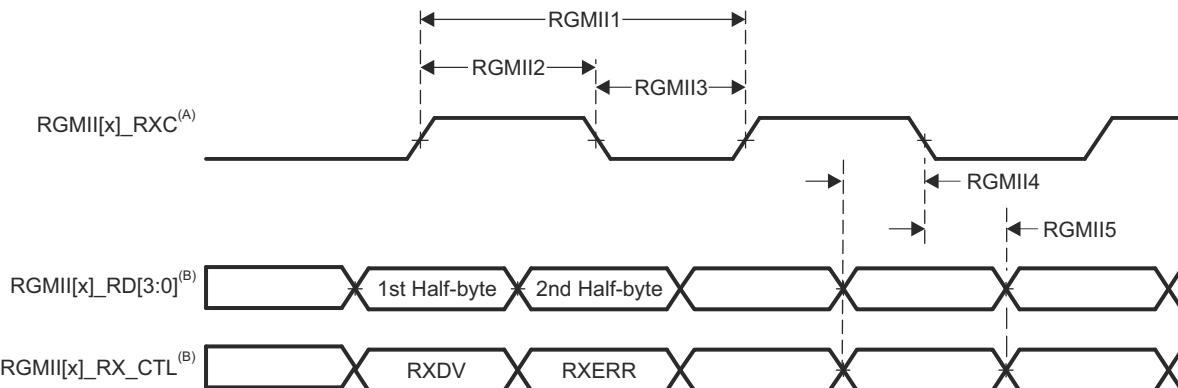

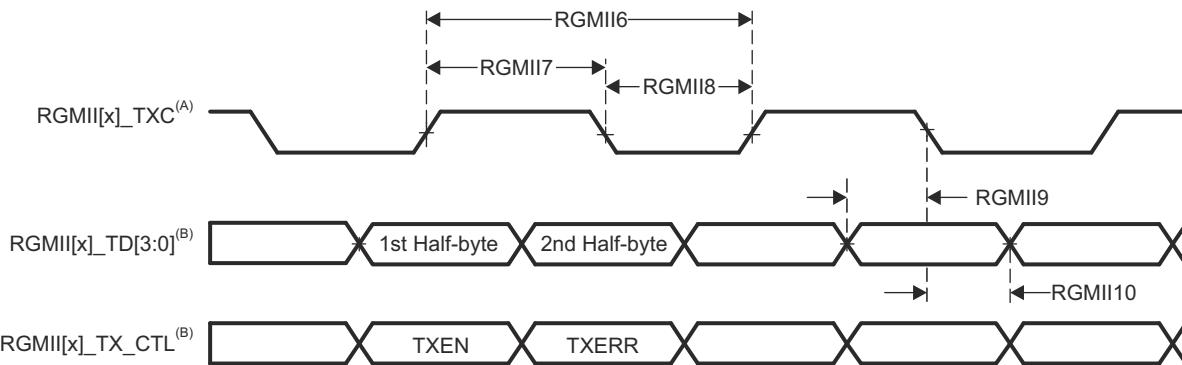

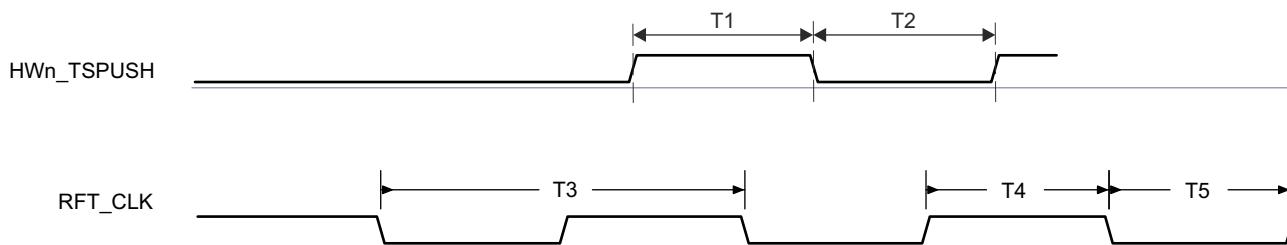

- 次の機能をサポートするイーサネットスイッチを内蔵(合計2つの外部ポート)

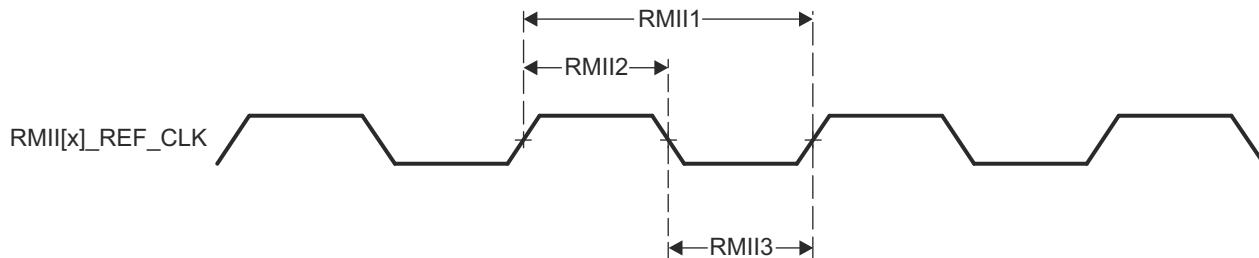

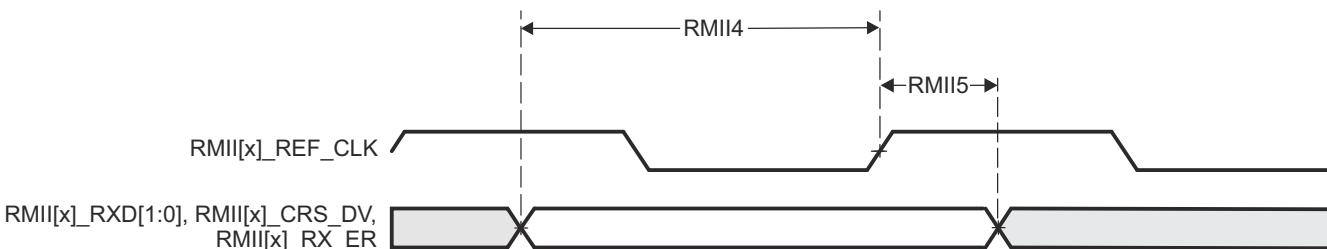

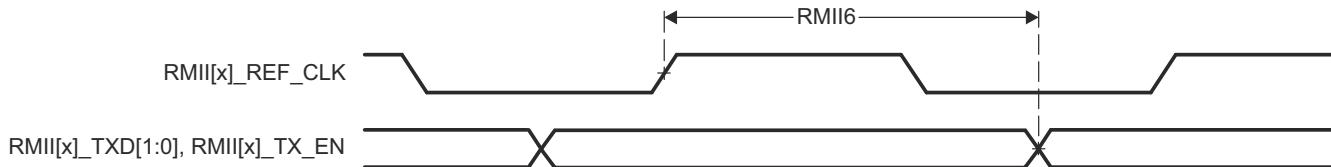

- RMII(10/100)またはRGMII(10/100/1000)

- IEEE1588(Annex D, Annex E, Annex Fと802.1AS PTP)

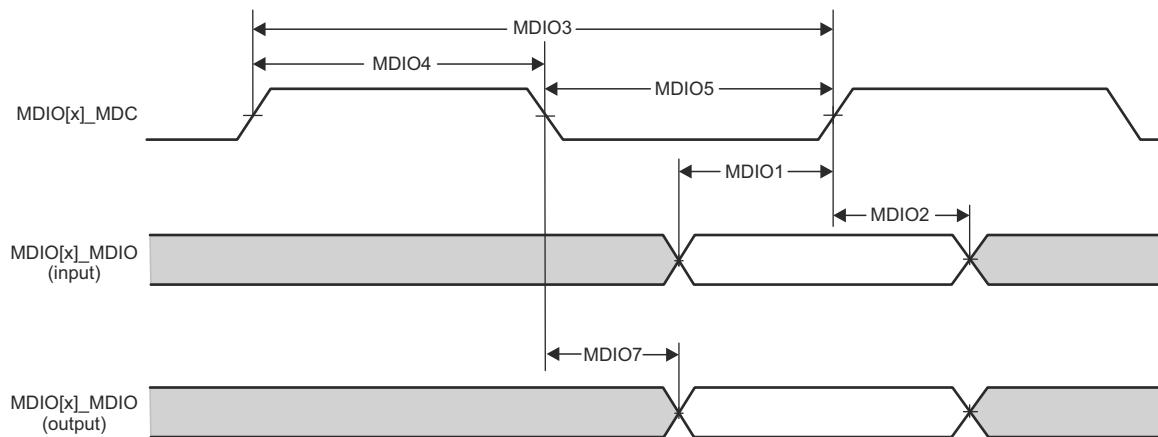

- Clause 45 MDIO PHY管理

- ALEエンジン(512の分類子)に基づくパケット分類器

- プライオリティベースのフロー制御

- タイムセンシティブネットワーキング(TSN)のサポート

- 4個のCPUハードウェア割り込みペーシング

- ハードウェアのIP/UDP/TCPチェックサムオフロード

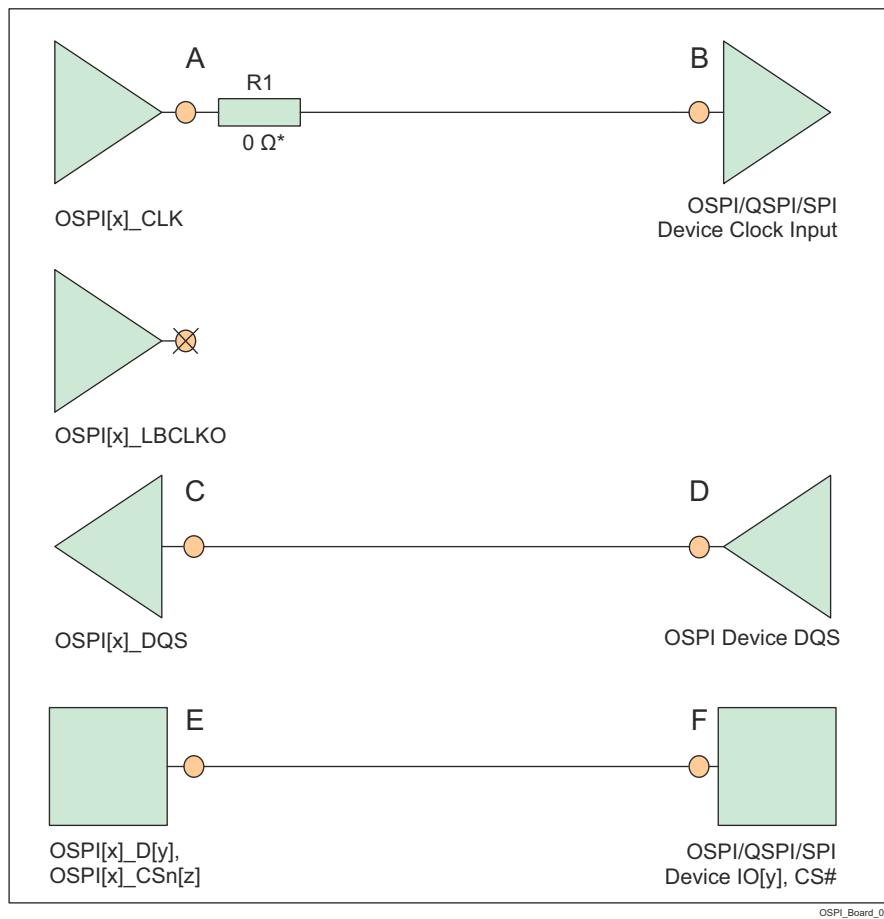

- 2つのUSB2.0ポート

- USBホスト、USBペリフェラル、USBデュアルロールデバイス(DRDモード)として構成可能なポート

- USBVBUS検出機能を内蔵

- 1つのCSI-2(カメラシリアルインターフェイス)レシーバ、4レーンD-PHY付き

- CSI-2とMIPI D-PHYを介した高速外部プロセッサデータ受信インターフェイス

### 一般的な接続機能:

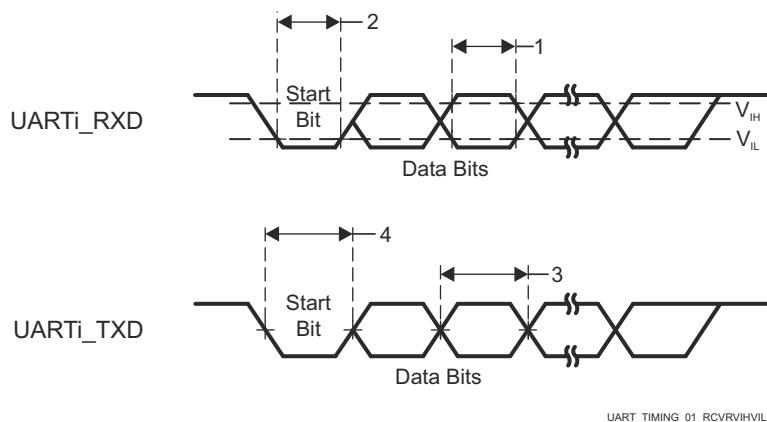

- 9個のユニバーサル非同期レシーバトランスマッタ(UART)

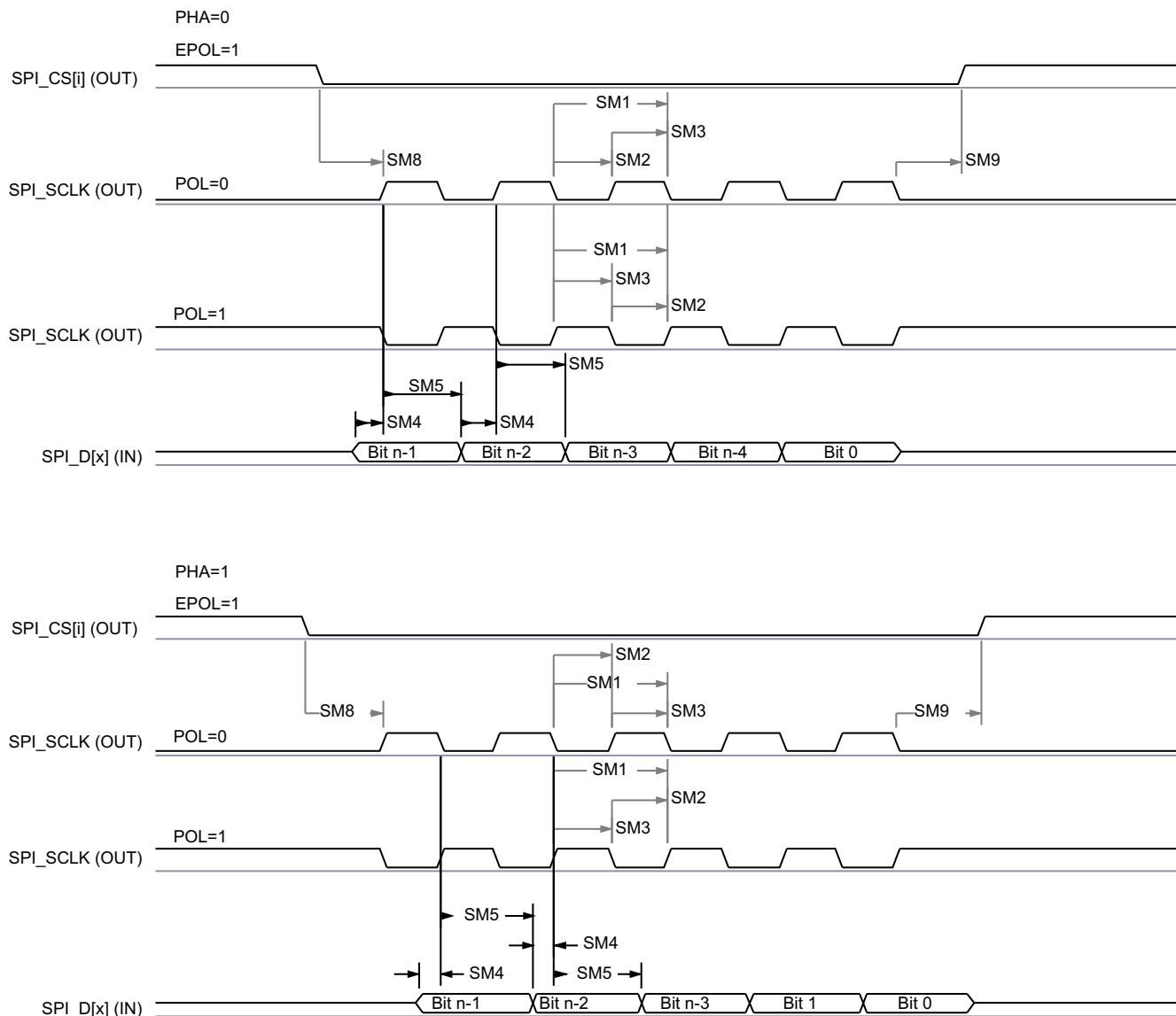

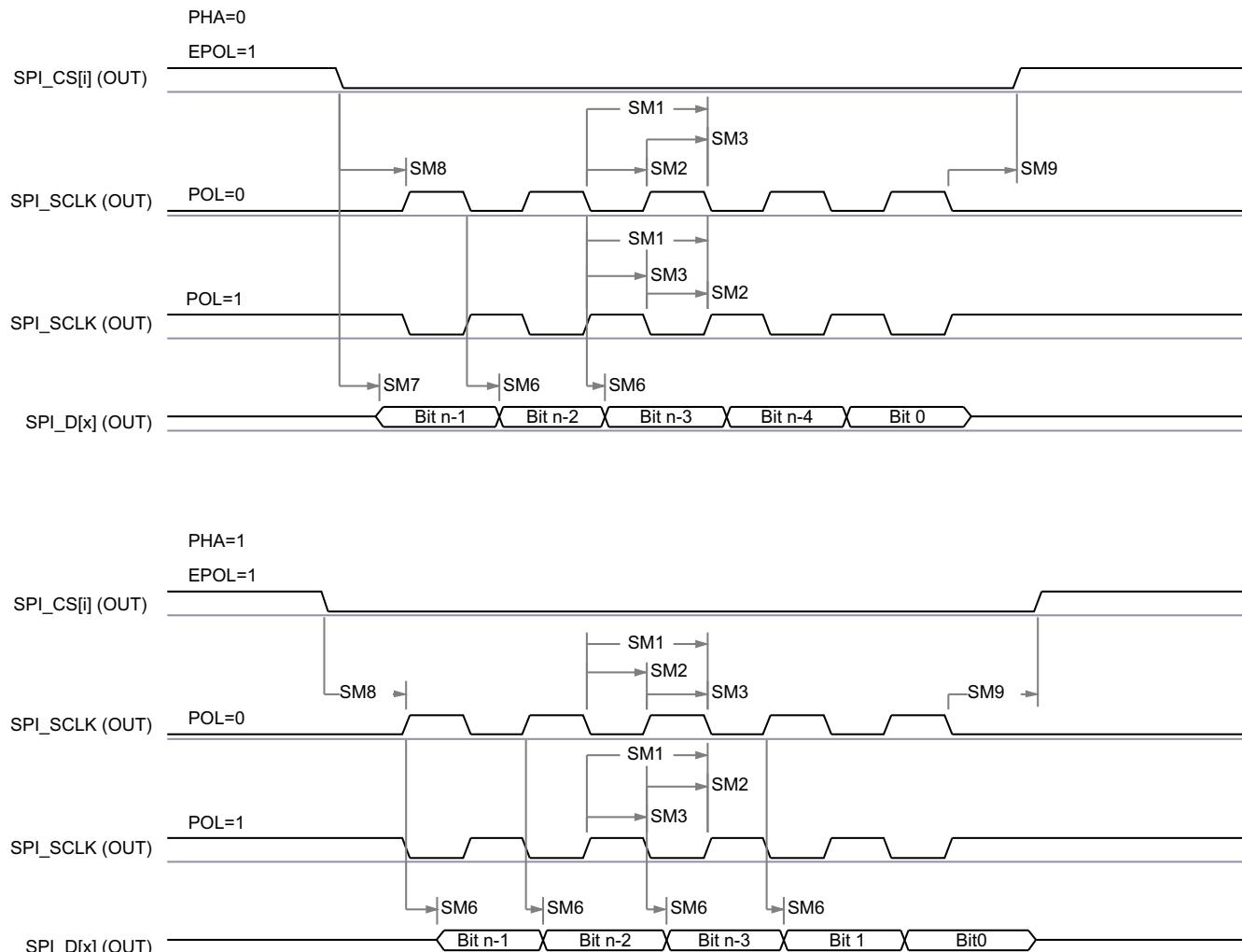

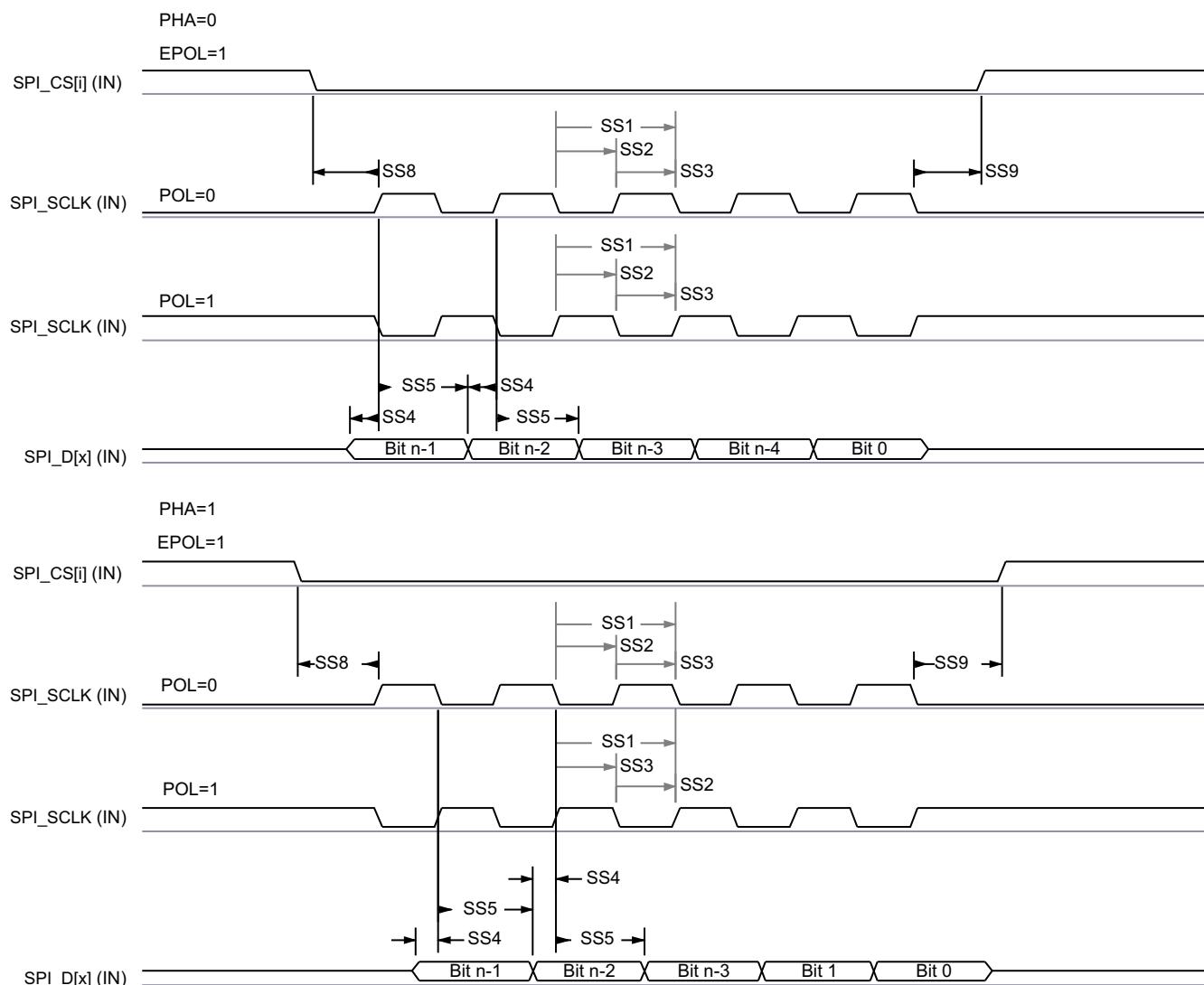

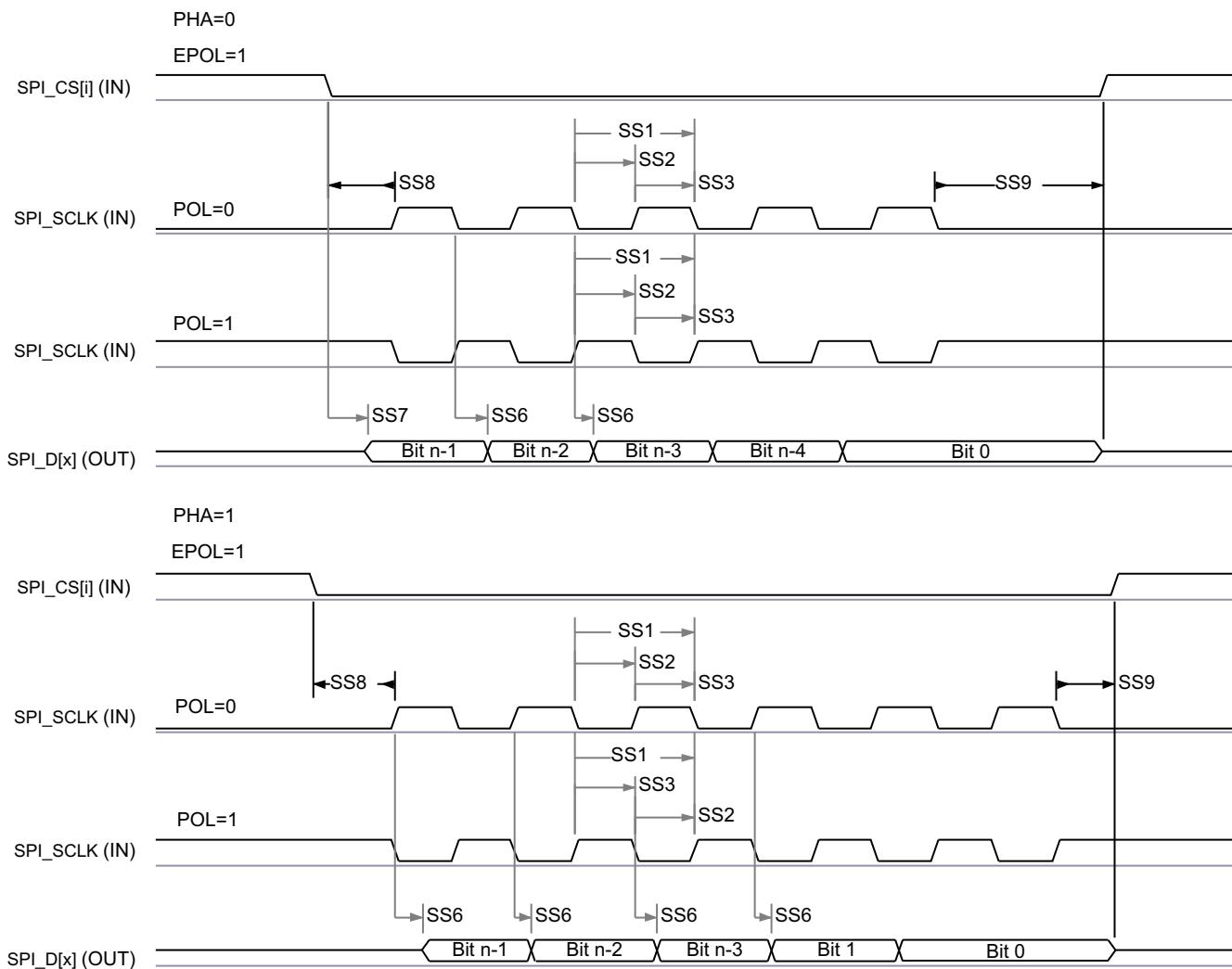

- 5個のシリアルペリフェラルインターフェイス(SPI)コントローラ

- 6個の内部集積回路(I<sup>2</sup>C)ポート

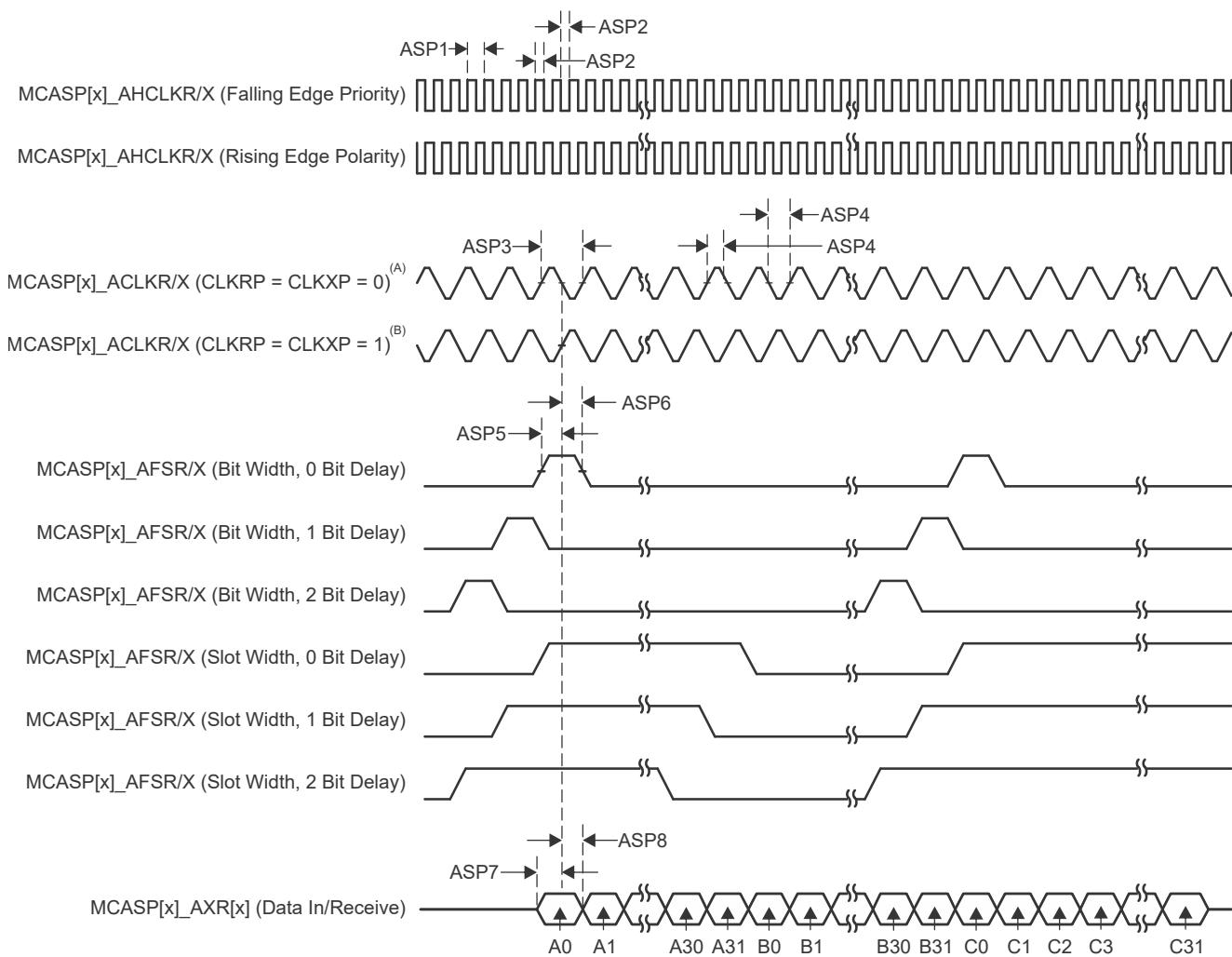

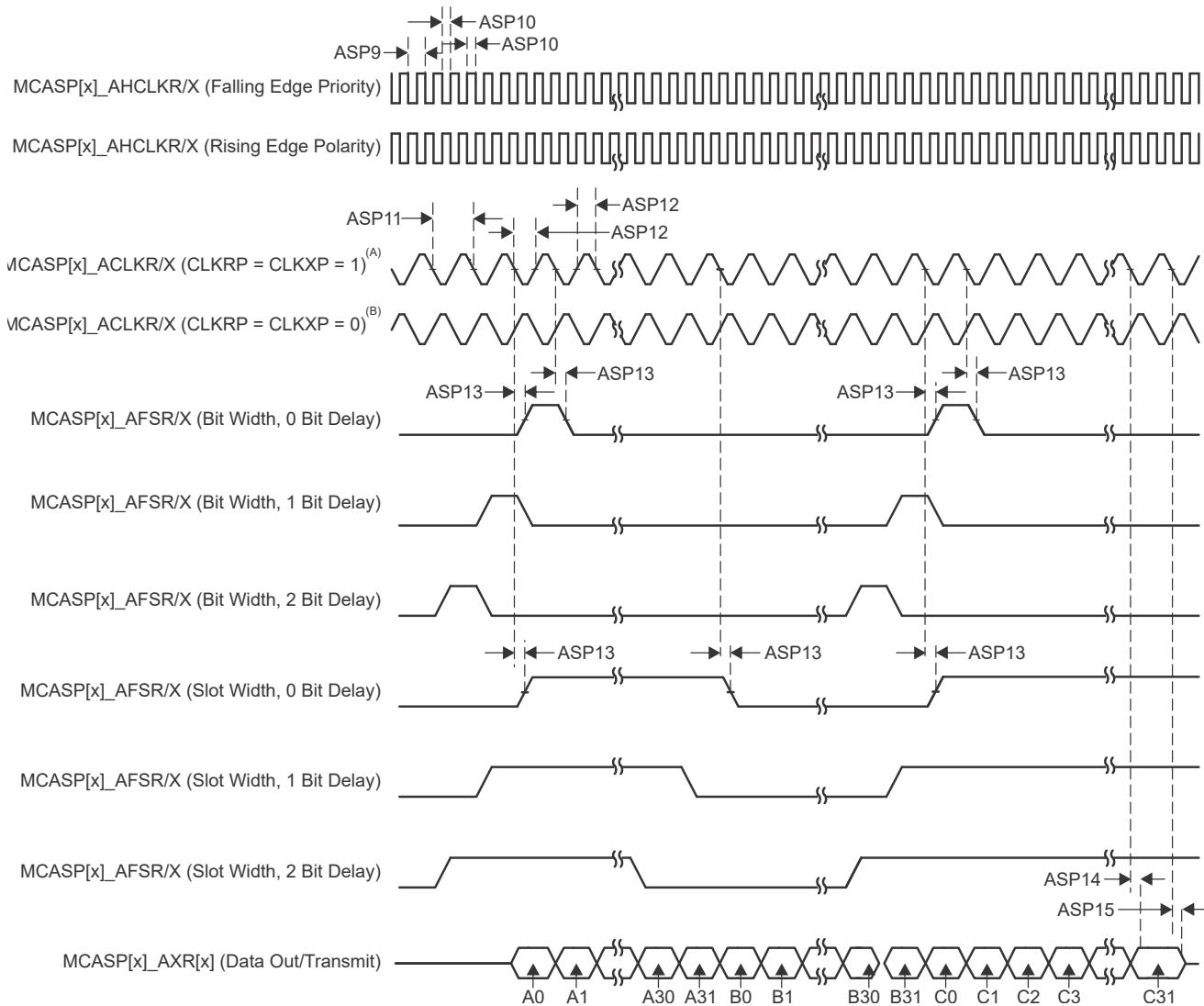

- 3個のマルチチャネルオーディオシリアルポート(McASP)

- 最高50MHzの送信および受信クロック

- 3個のMcASPで最大4/6/16本のシリアルデータピンを使用でき、TXとRXの各クロックは独立しています

- 時分割多重化(TDM)、IC間サウンド(I2S)、および類似のフォーマットをサポート

- デジタルオーディオインターフェイス送信(SPDIF、IEC60958-1、AES-3フォーマット)をサポート

- 送受信用FIFOバッファ(256バイト)

- オーディオリファレンス出力クロックのサポート

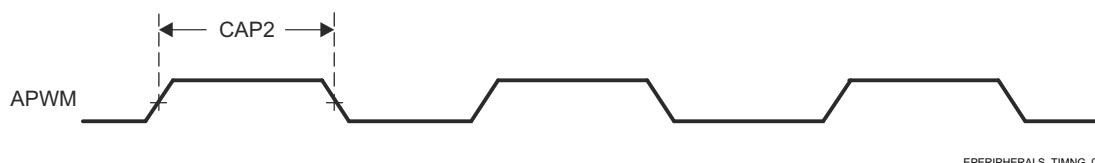

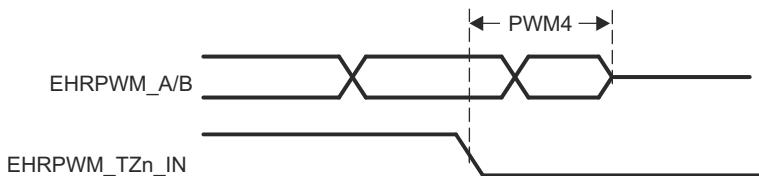

- 3つの拡張PWMモジュール(ePWM)

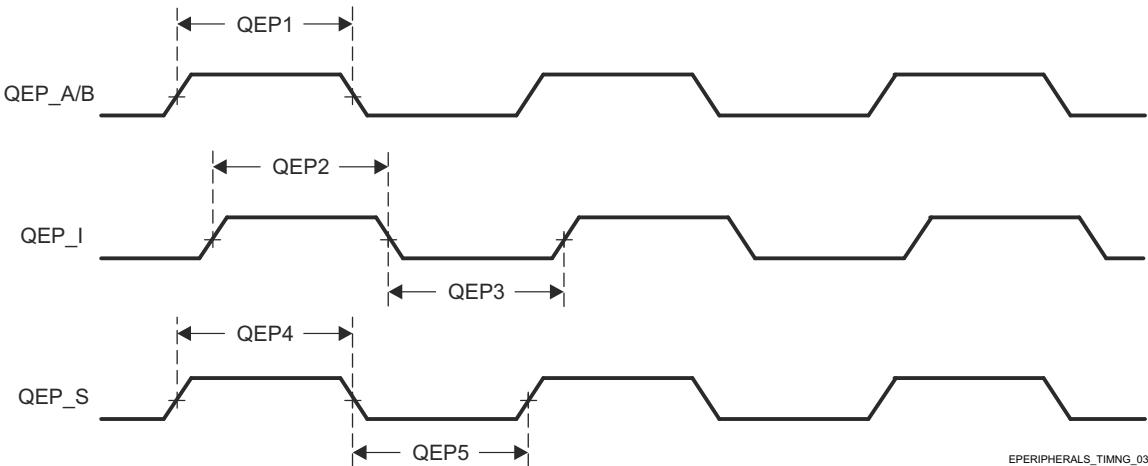

- 3個の拡張直交エンコーダパルスモジュール(EQEP)

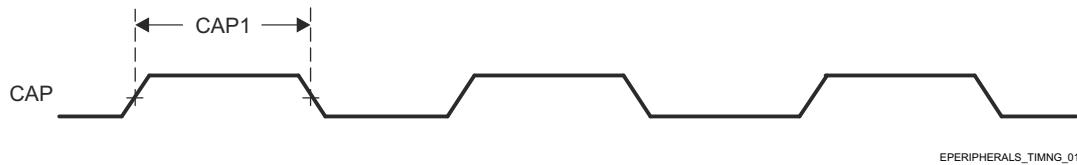

- 3個の拡張キャプチャモジュール(ECAP)

- 汎用I/O(GPIO)では、すべてのLVCMSI/OをGPIOとして構成可能

- 3個のコントローラエリアネットワーク(CAN)モジュール、CAN-FDをサポート

- CANプロトコル2.0A、B、ISO 11898-1に準拠

- 完全なCAN FDのサポート(最大64データバイト)

- メッセージRAMのパリティ/ECCチェック

- 最大速度:8Mbps

### メディアおよびデータストレージ:

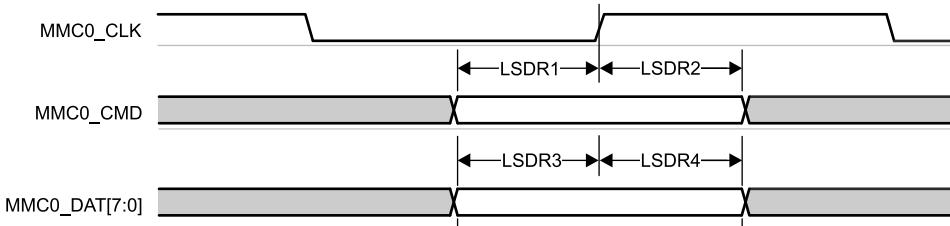

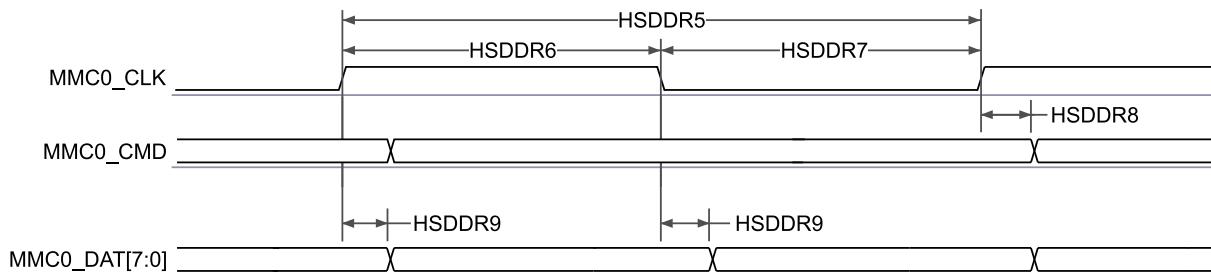

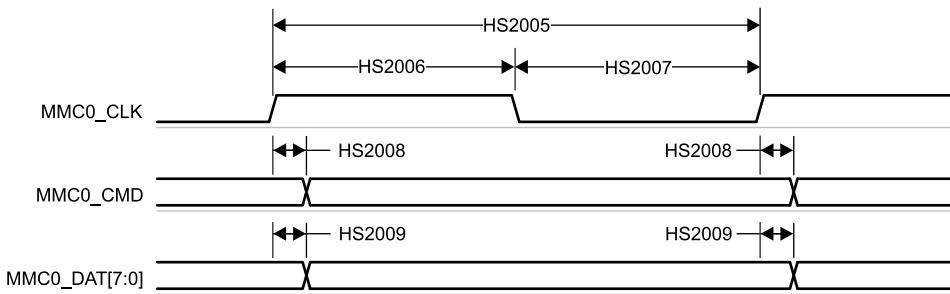

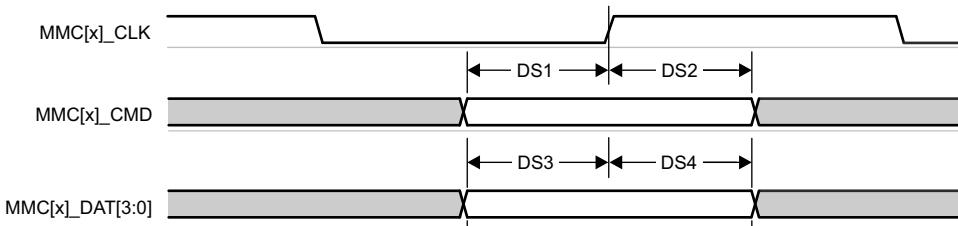

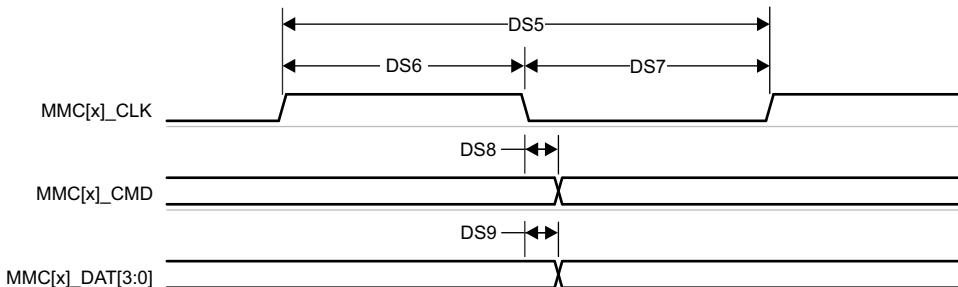

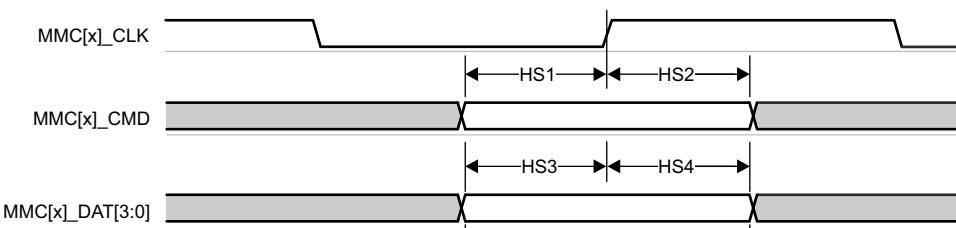

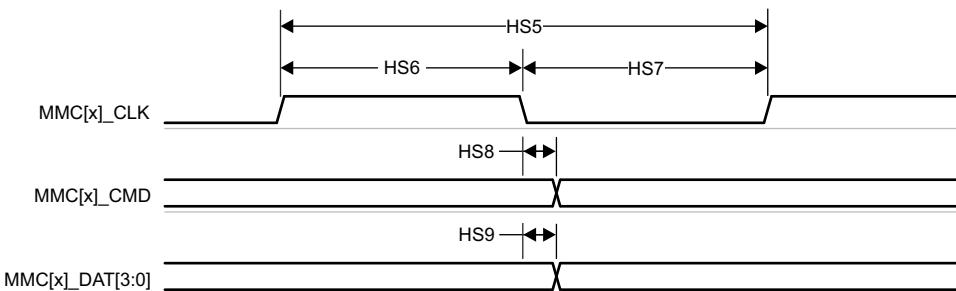

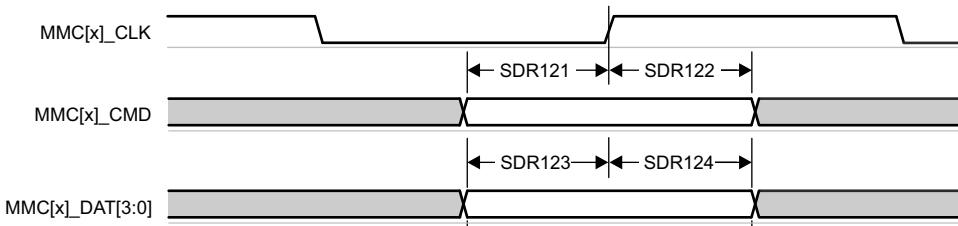

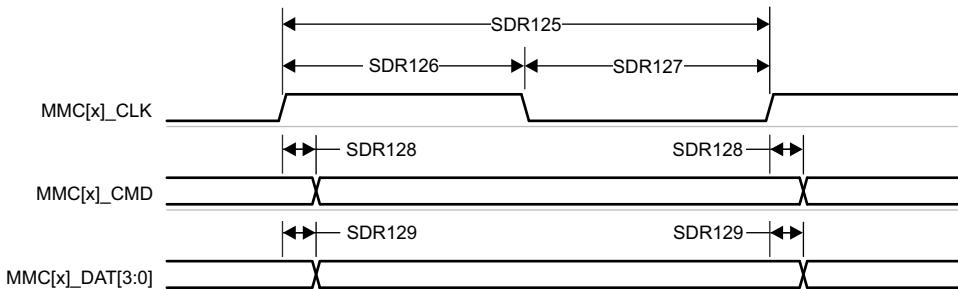

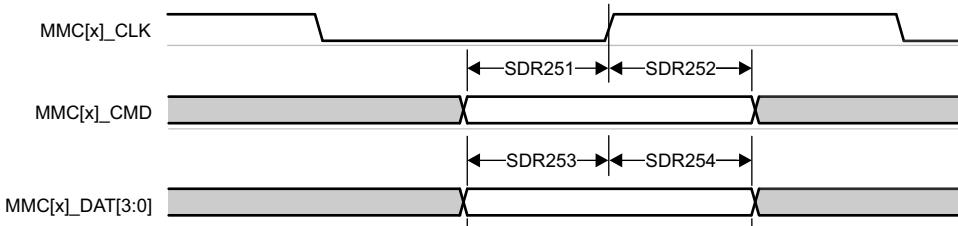

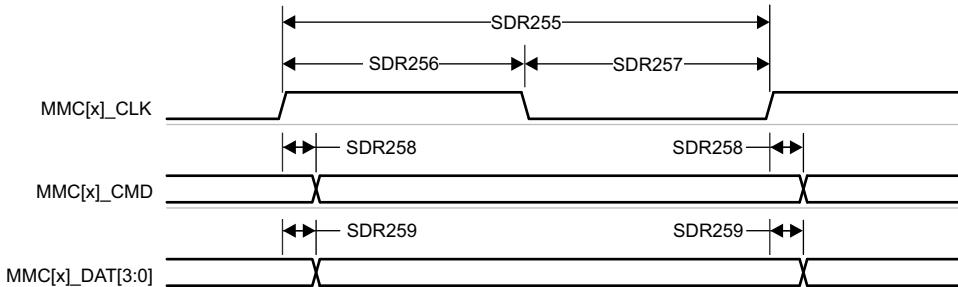

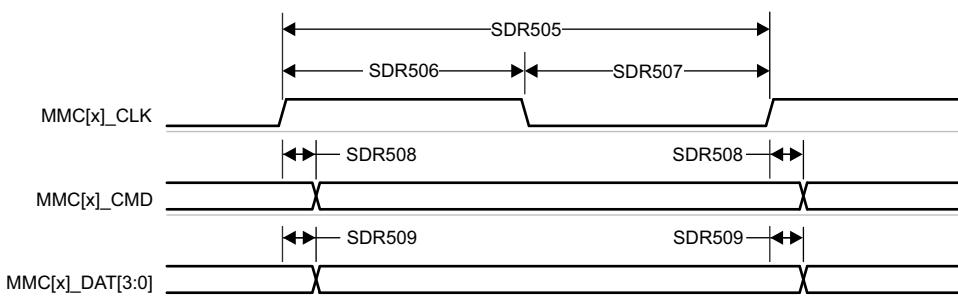

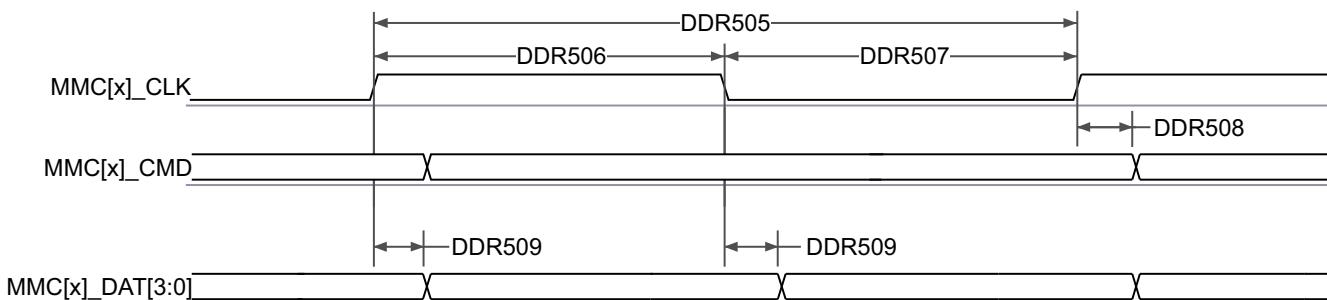

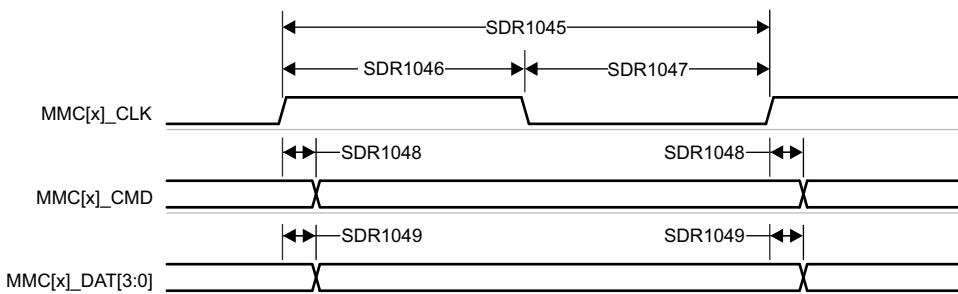

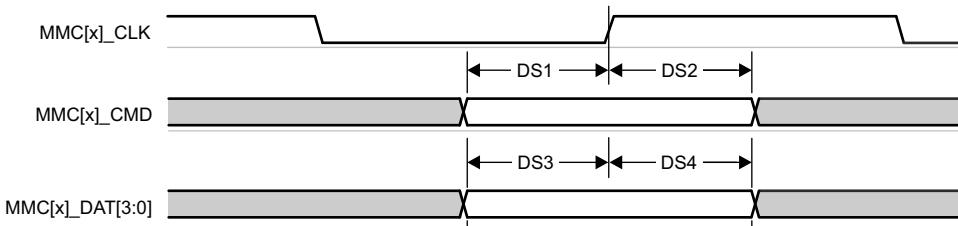

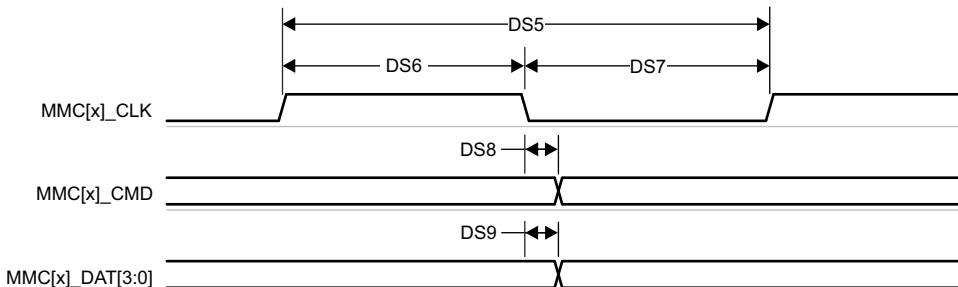

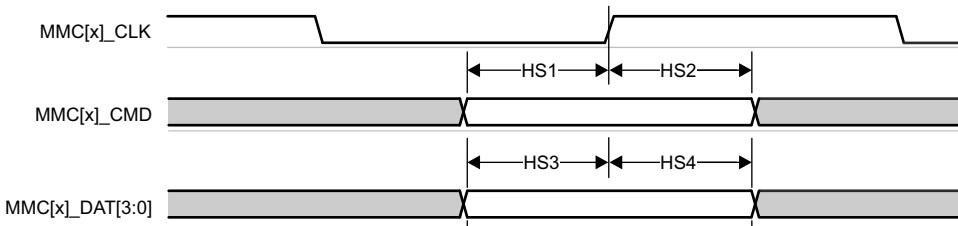

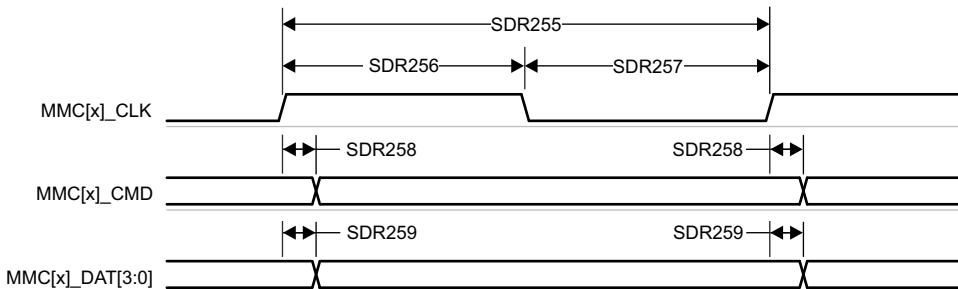

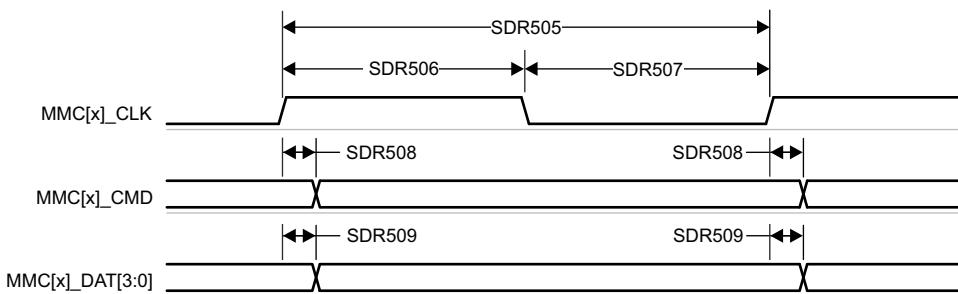

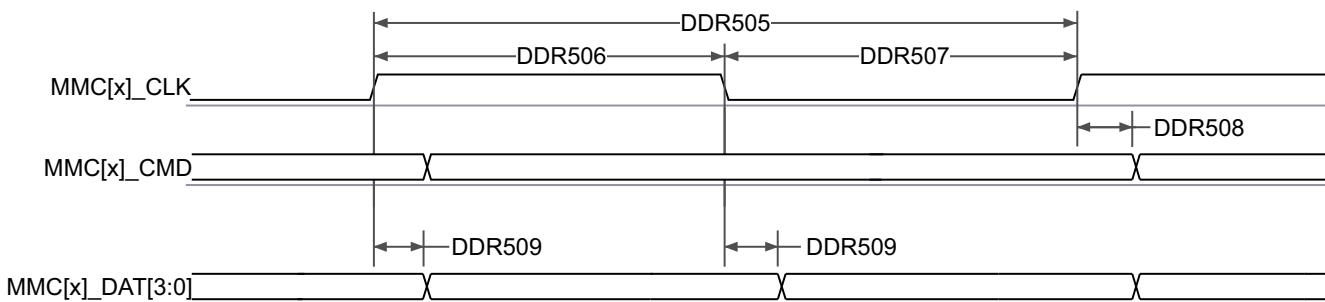

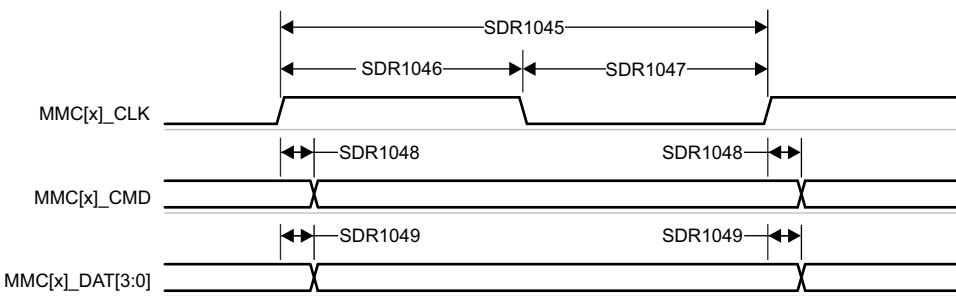

- 3つのマルチメディアカード/セキュアデジタル®(MMC/SD®/SDIO)インターフェイス

- 1個の8ビットeMMCインターフェイス、最大速度HS200

- 2個の4ビットSD/SDIOインターフェイス、最大UHS-I

- eMMC 5.1、SD 3.0、SDIOバージョン3.0に準拠

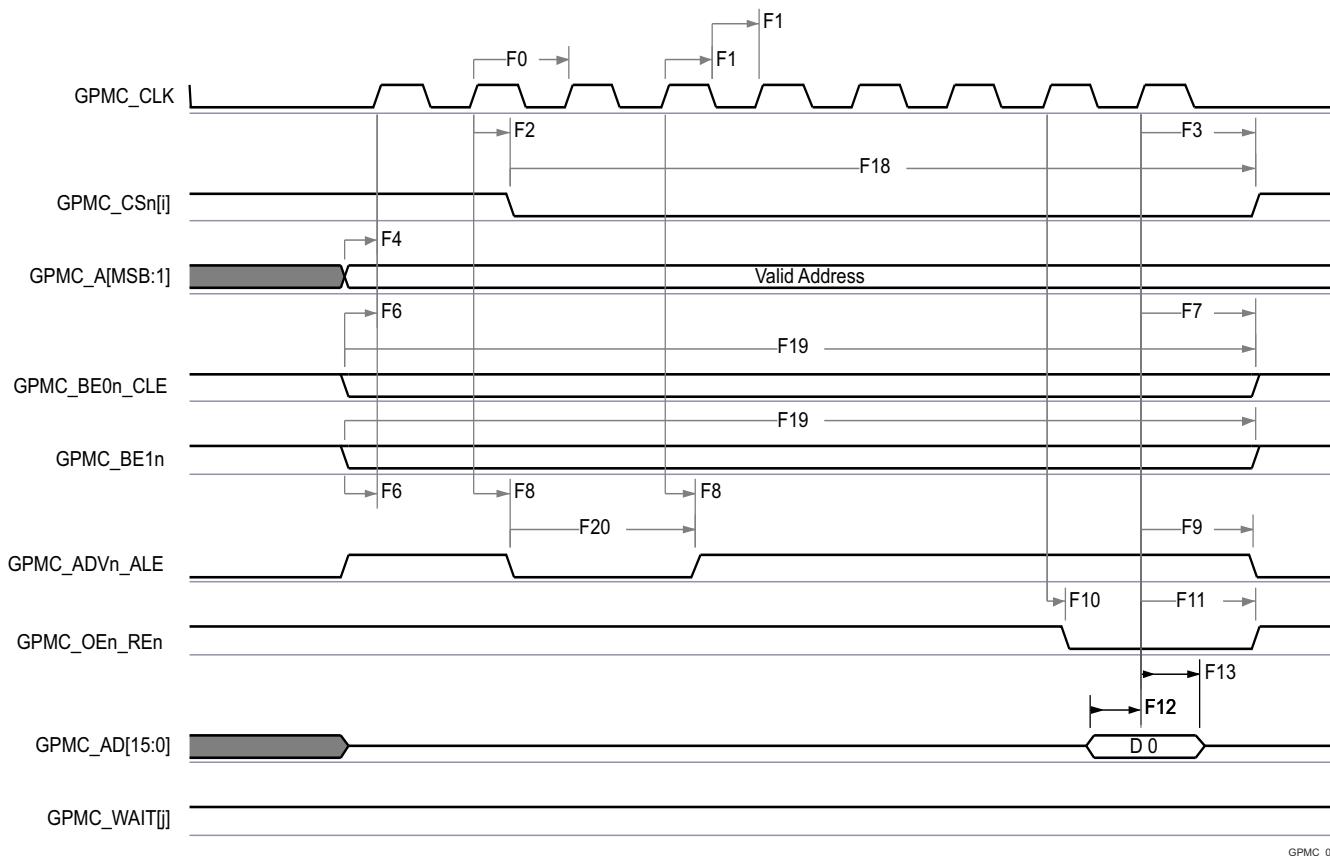

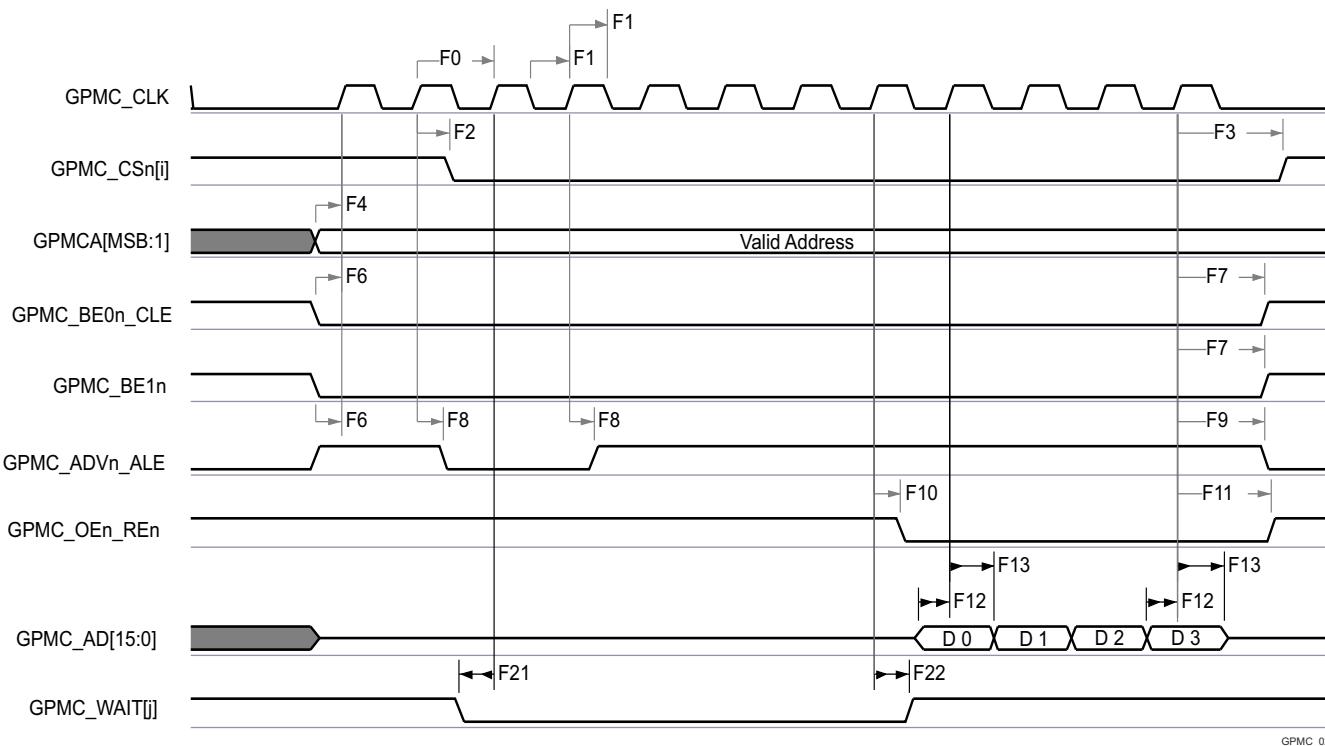

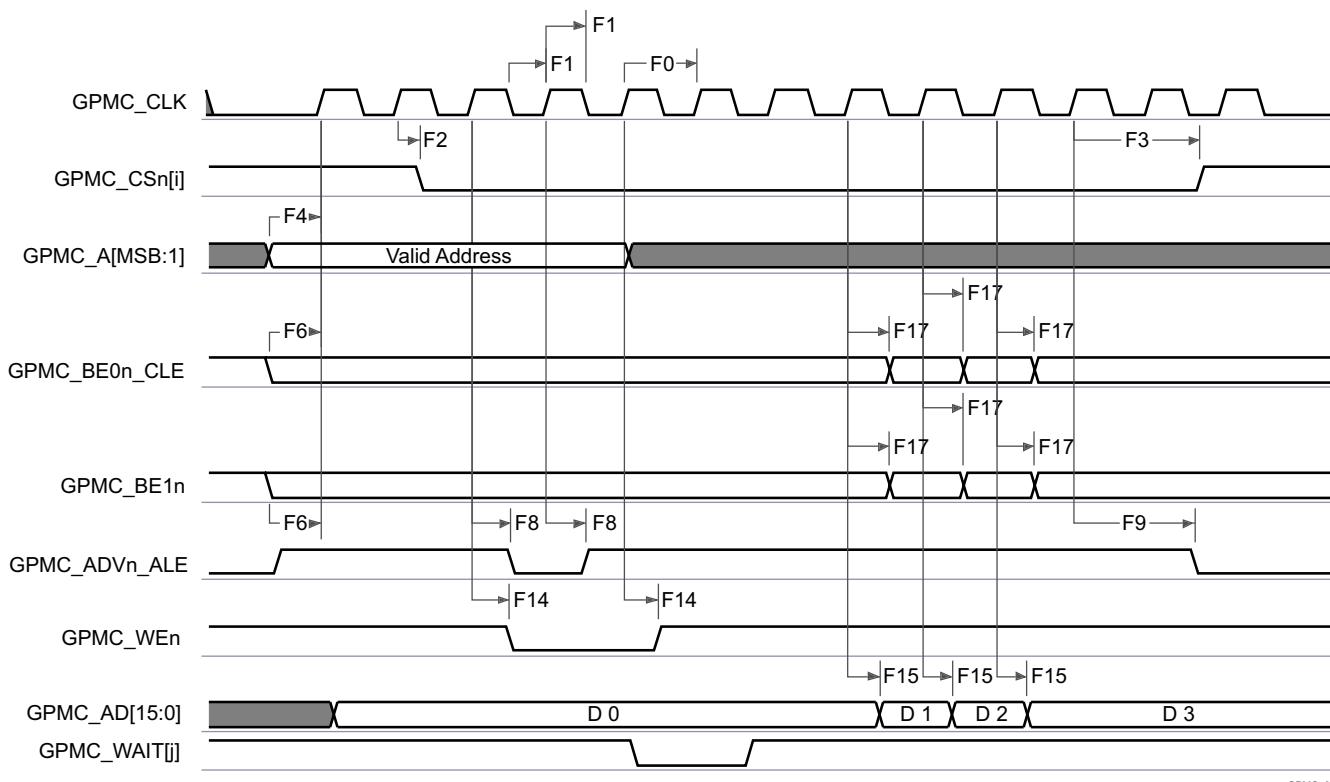

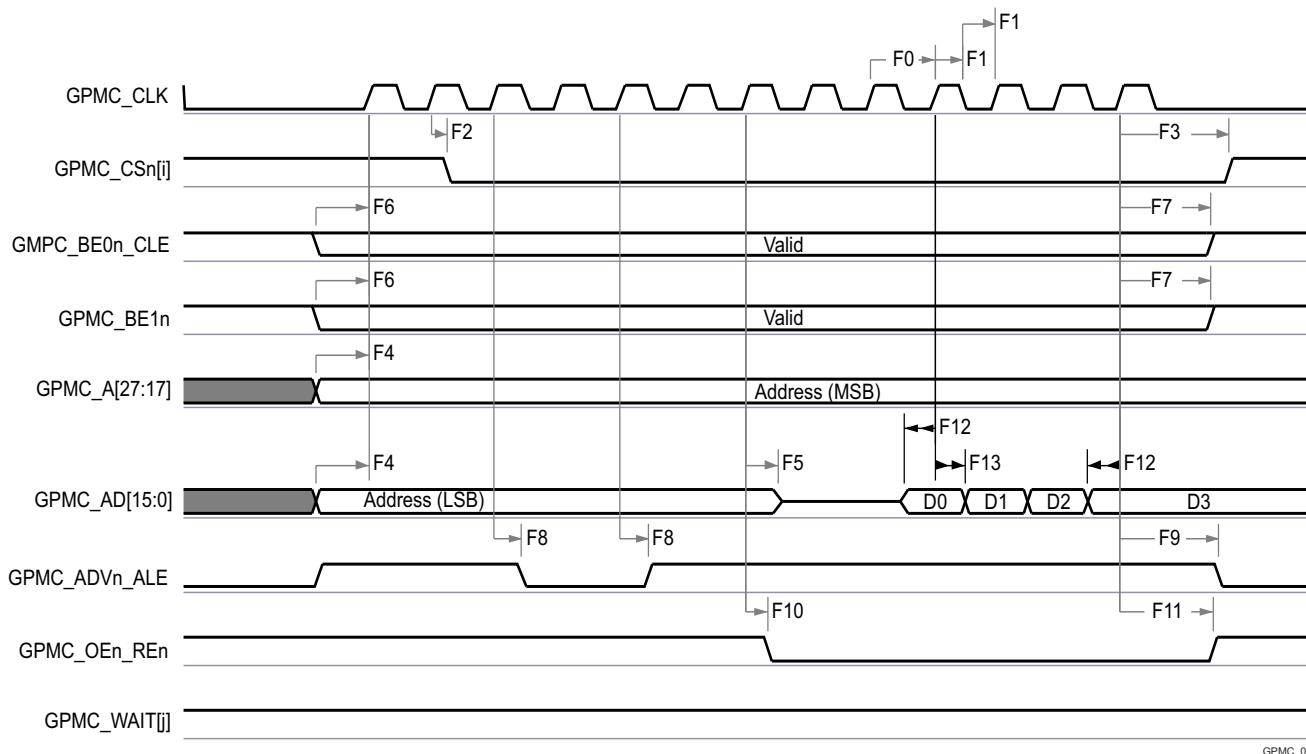

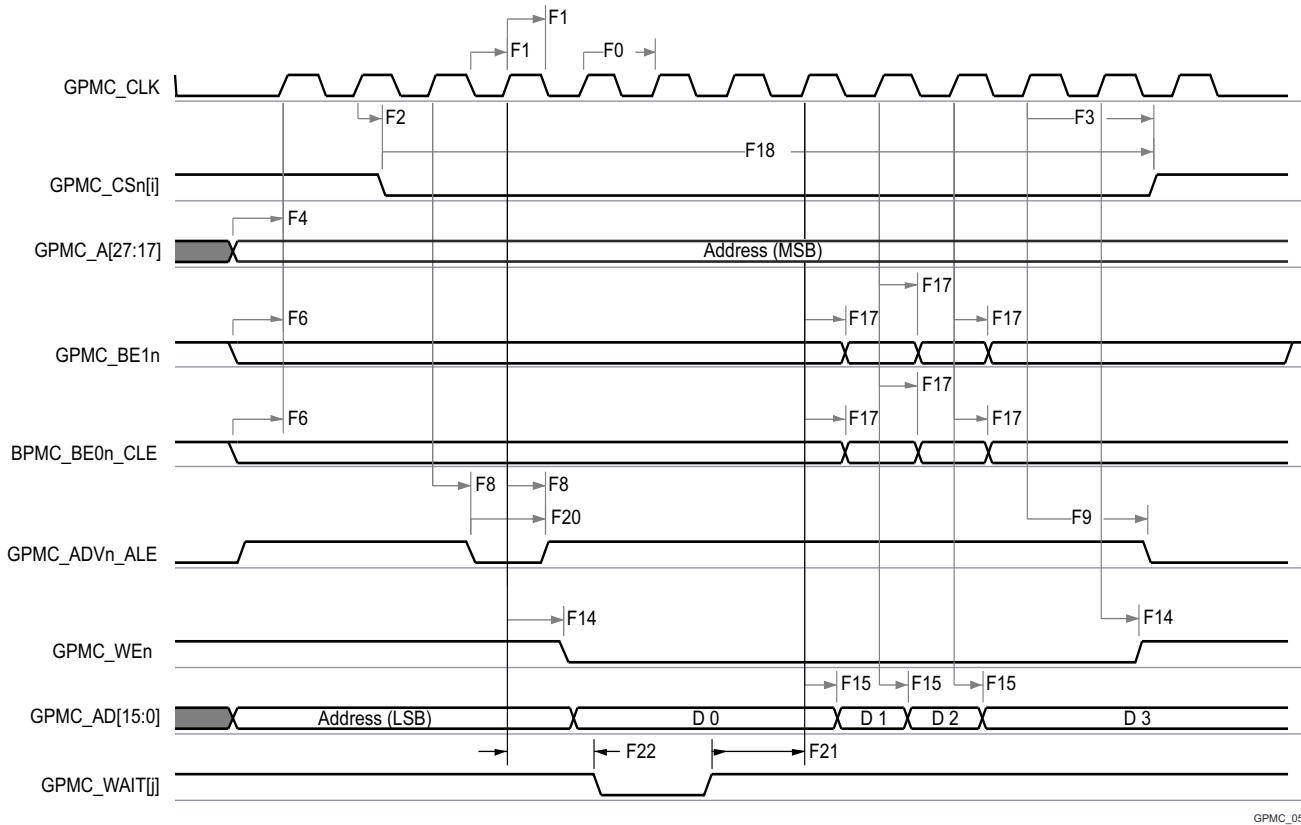

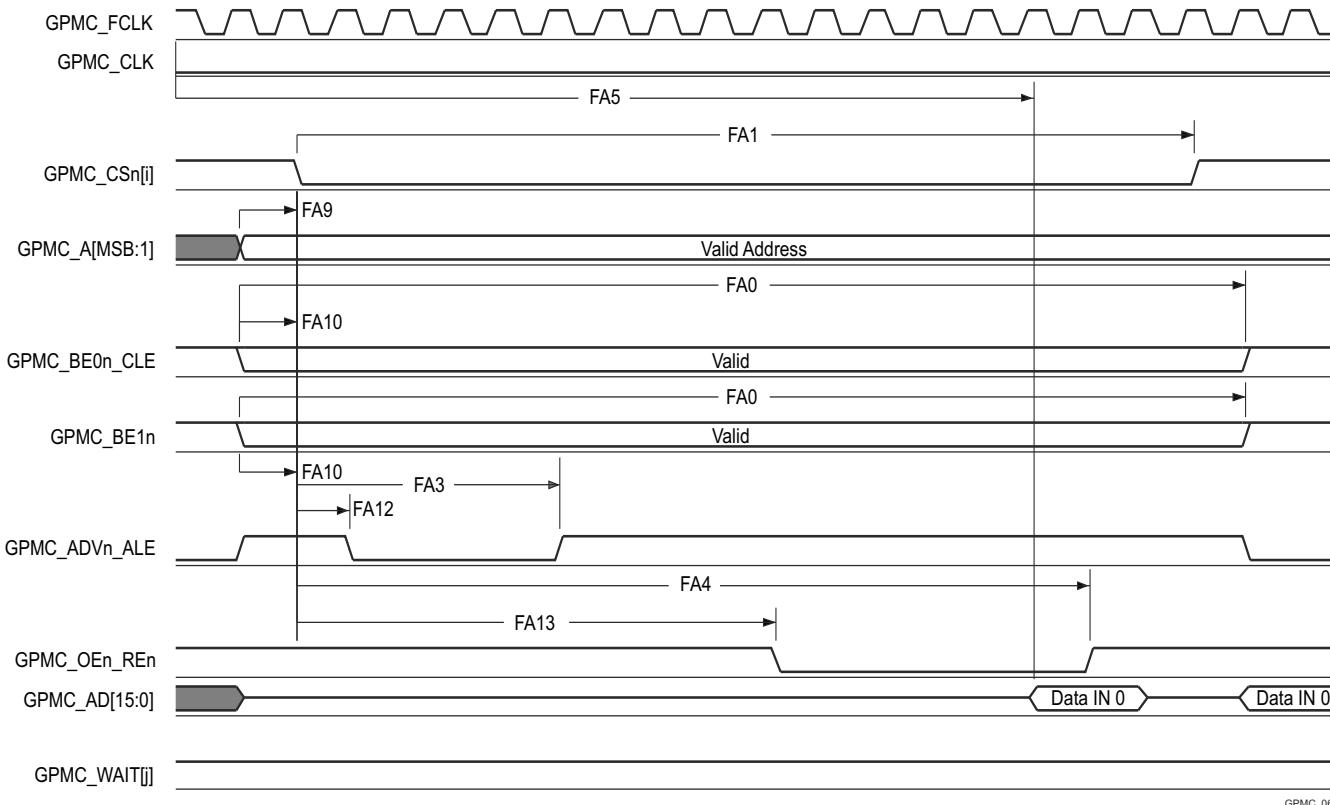

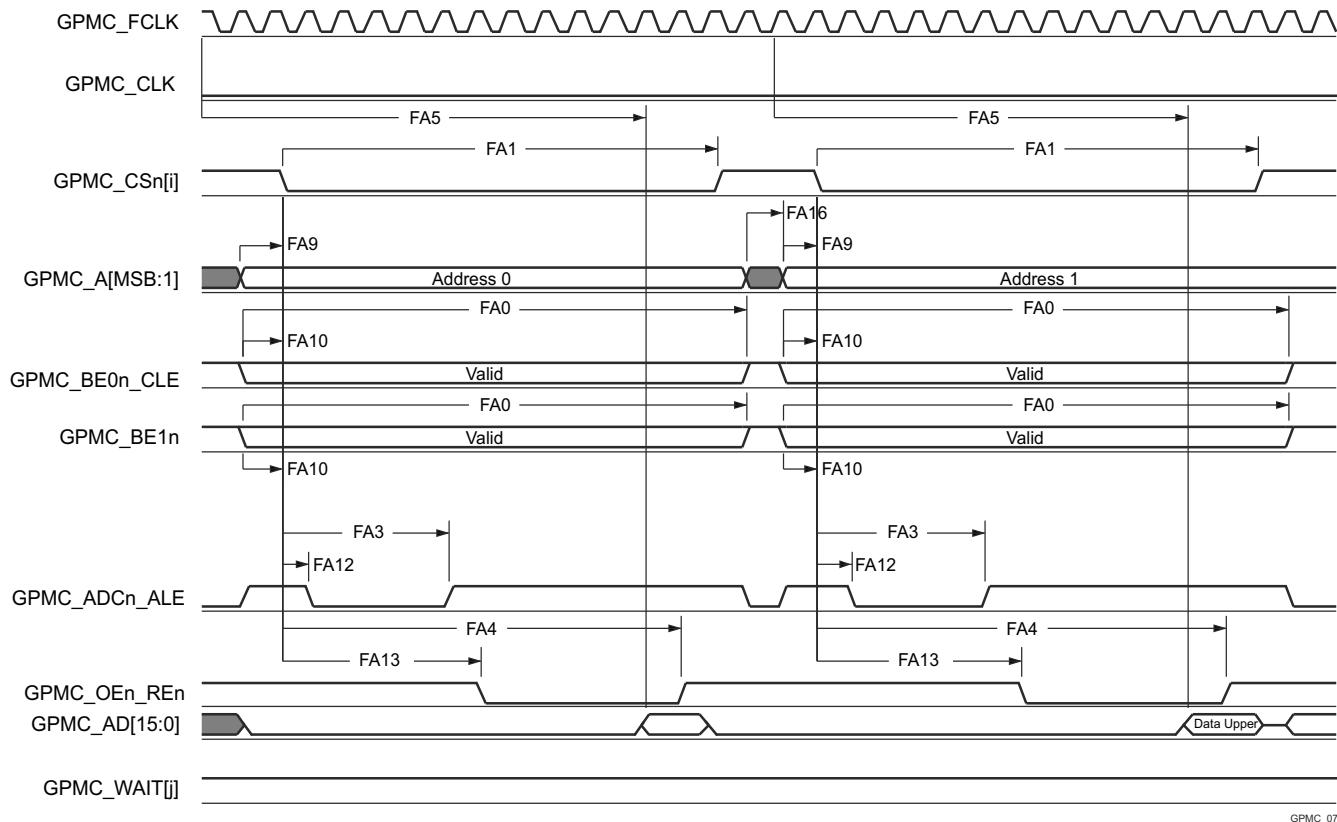

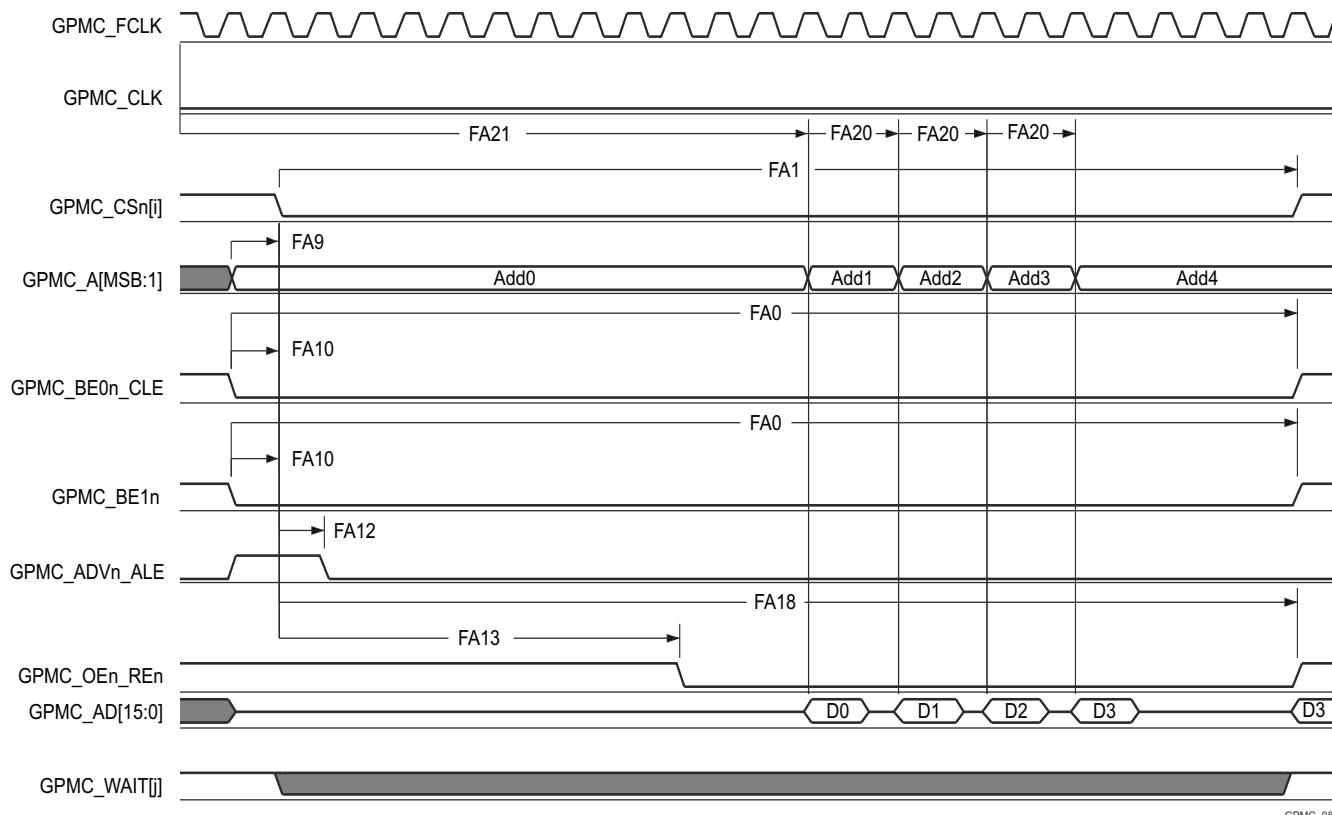

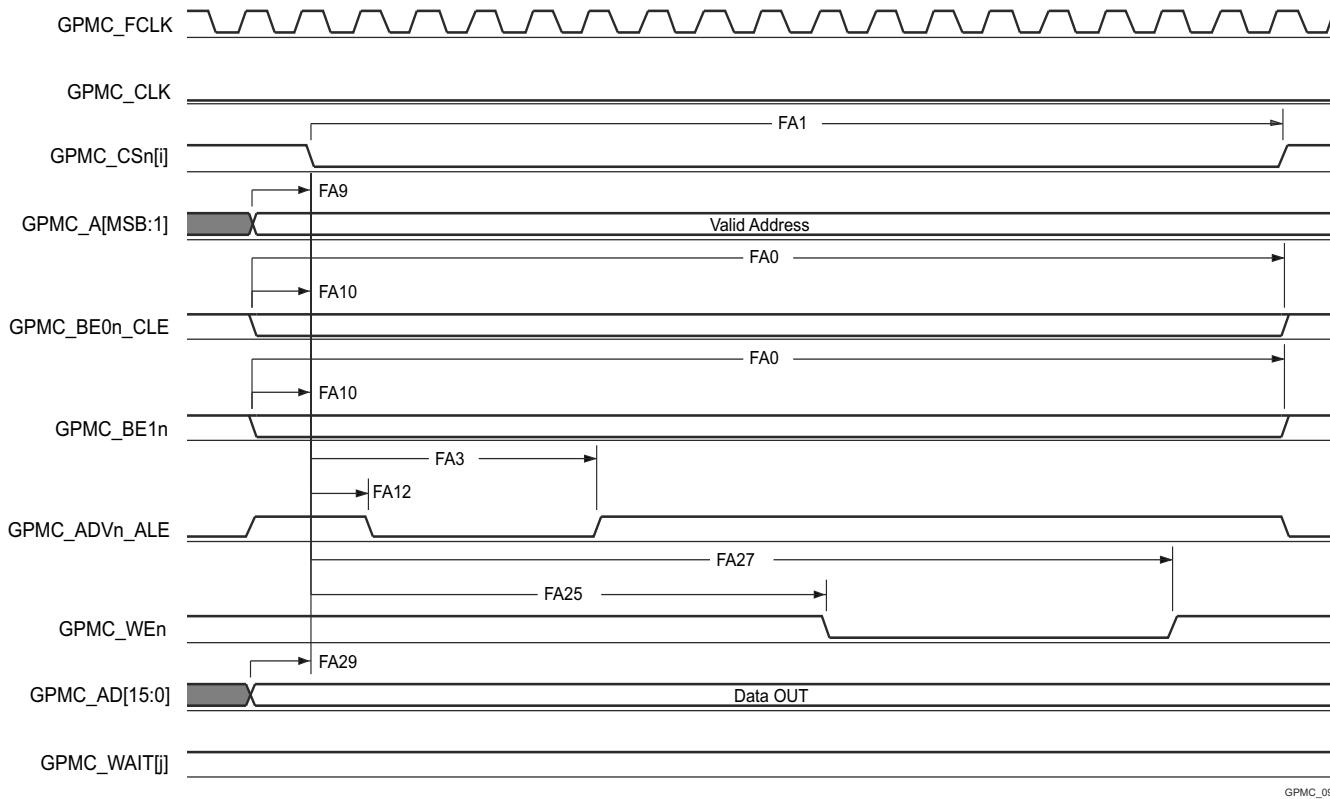

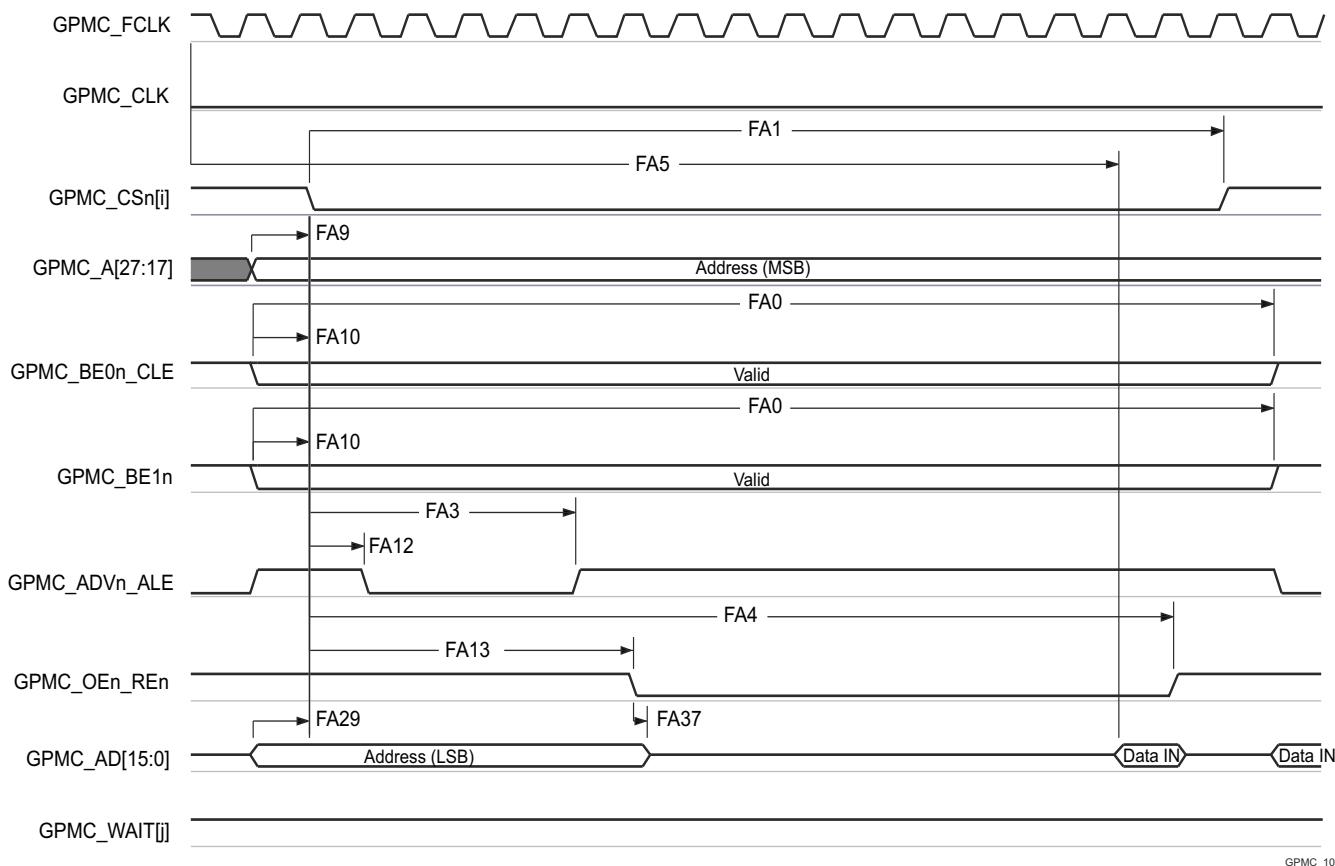

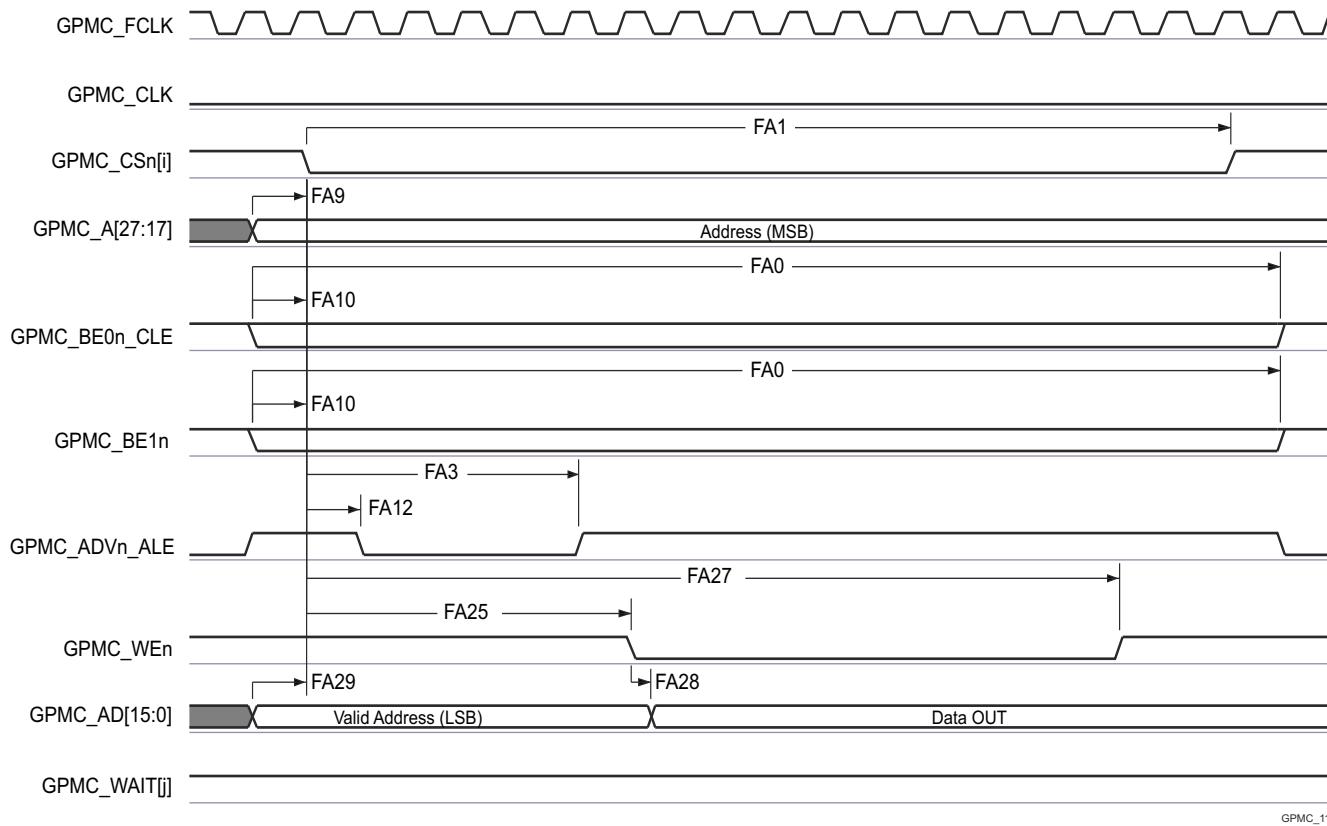

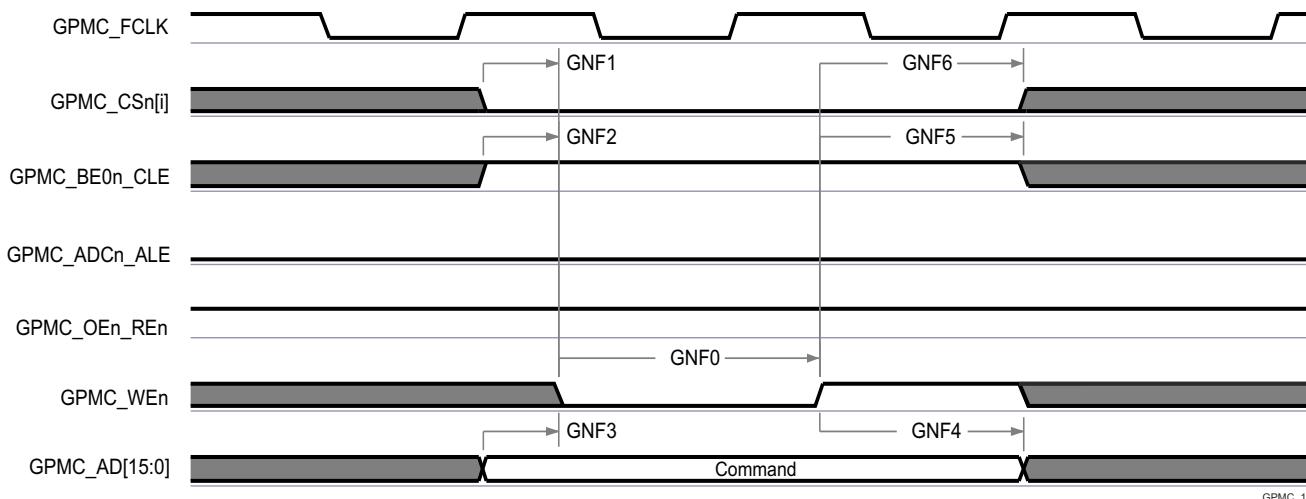

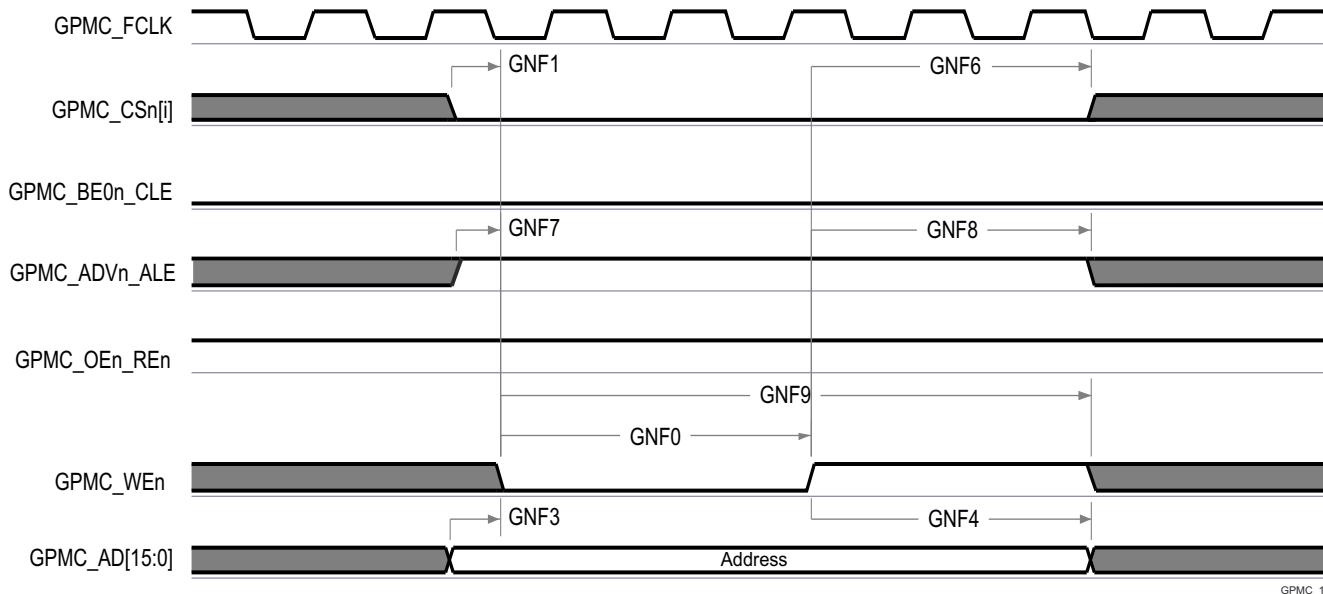

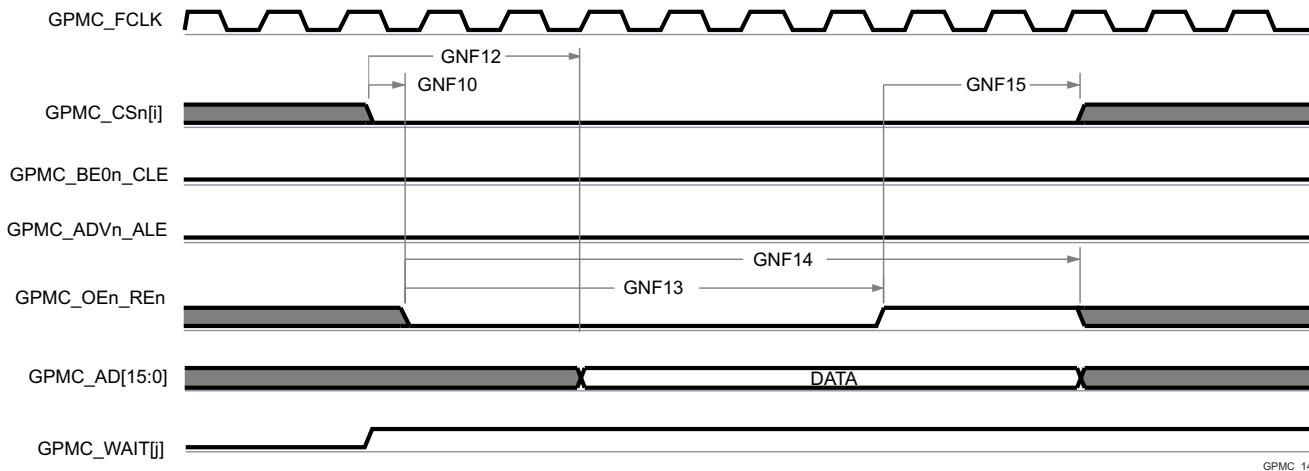

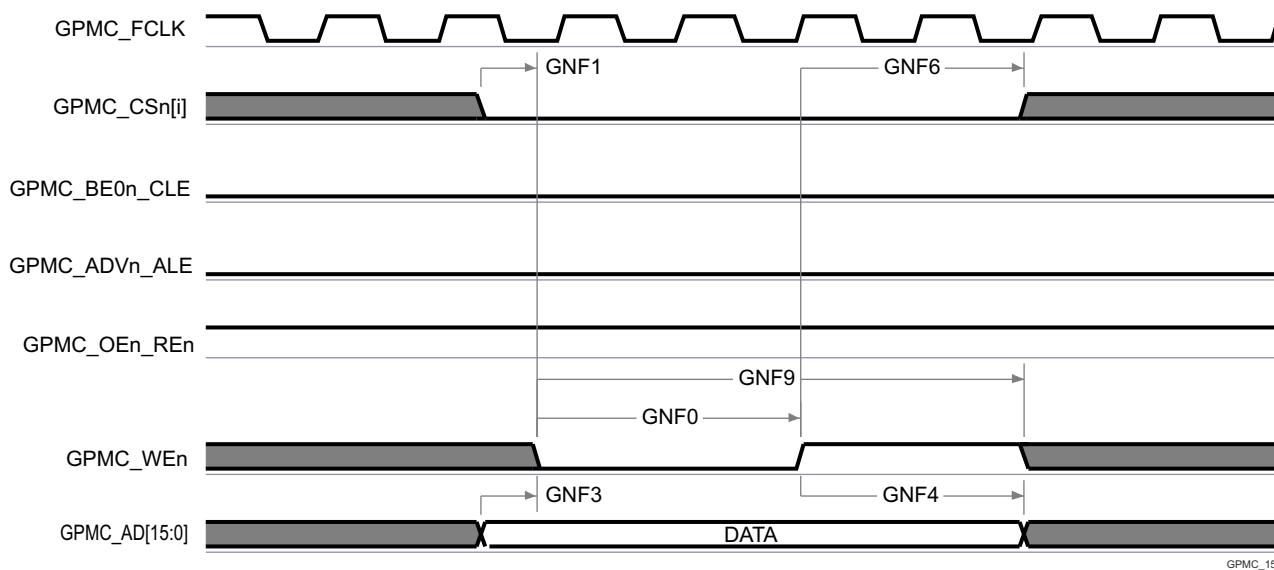

- 最大133MHzの1つの汎用メモリコントローラ(GPMC)

- 柔軟な8および16ビットの非同期メモリインターフェイスと、最大4つのチップ(22ビットアドレス)セレクト(NAND、NOR、Muxed-NOR、SRAM)

- BCHコードを使用して4、8、または16ビットECCをサポート

- ハミングコードを使用して1ビットECCをサポート

- エラー特定モジュール(ELM)

- GPMCと組み合わせて使用して、BCHアルゴリズムにより生成されたシンドローム多項式からデータエラーのアドレスを特定

- BCHアルゴリズムに基づいて、512バイトのブロックごとに4、8、16ビットのエラーを特定可能

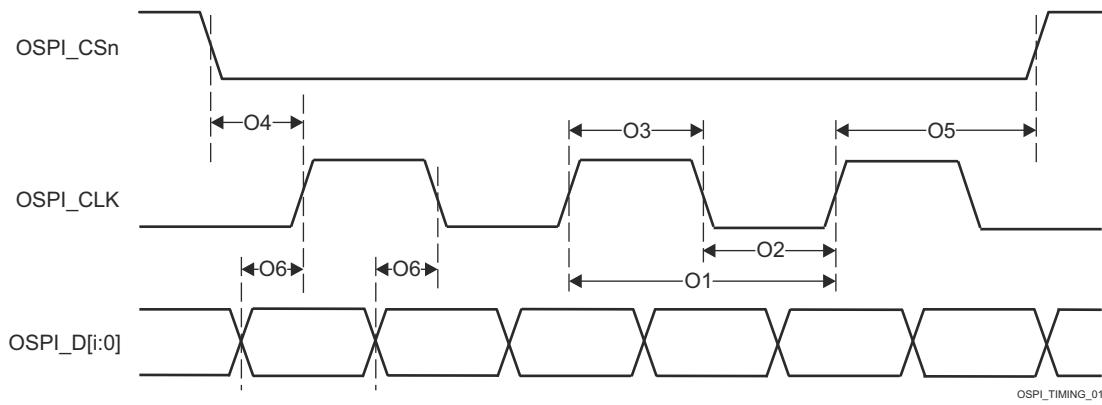

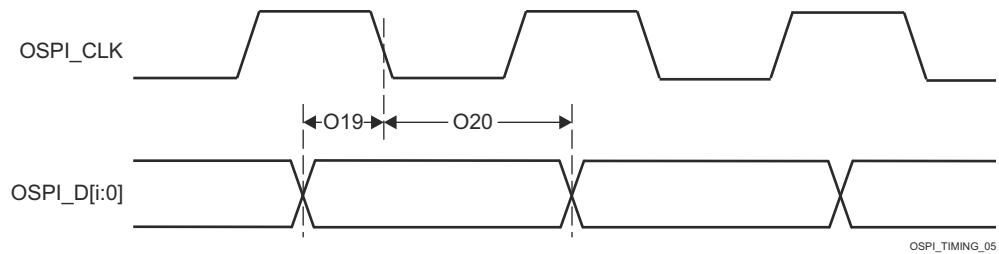

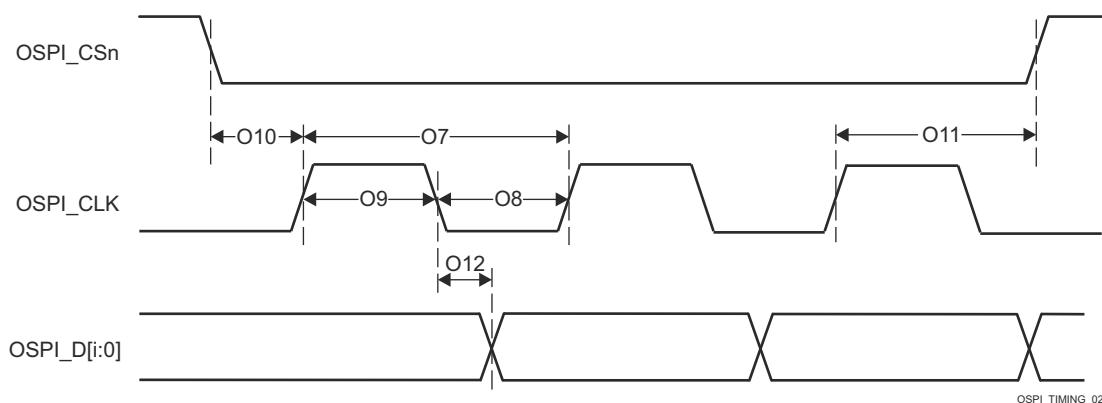

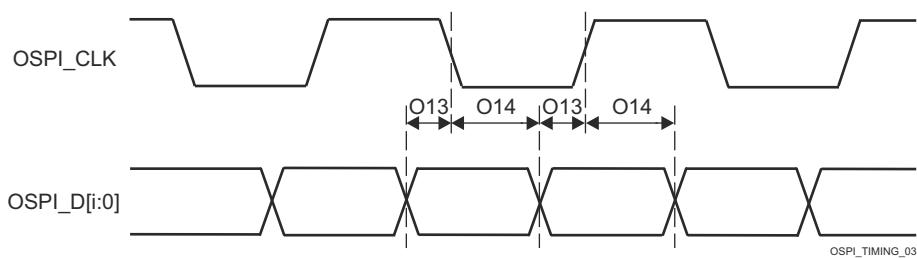

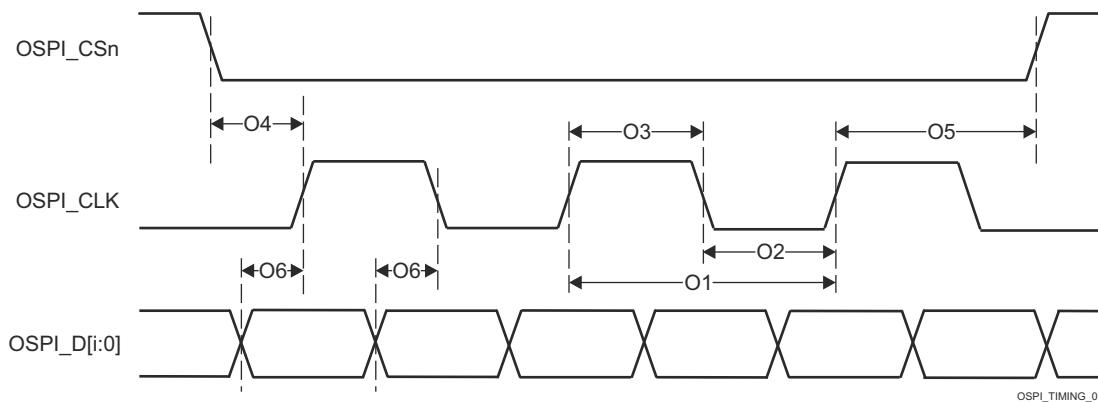

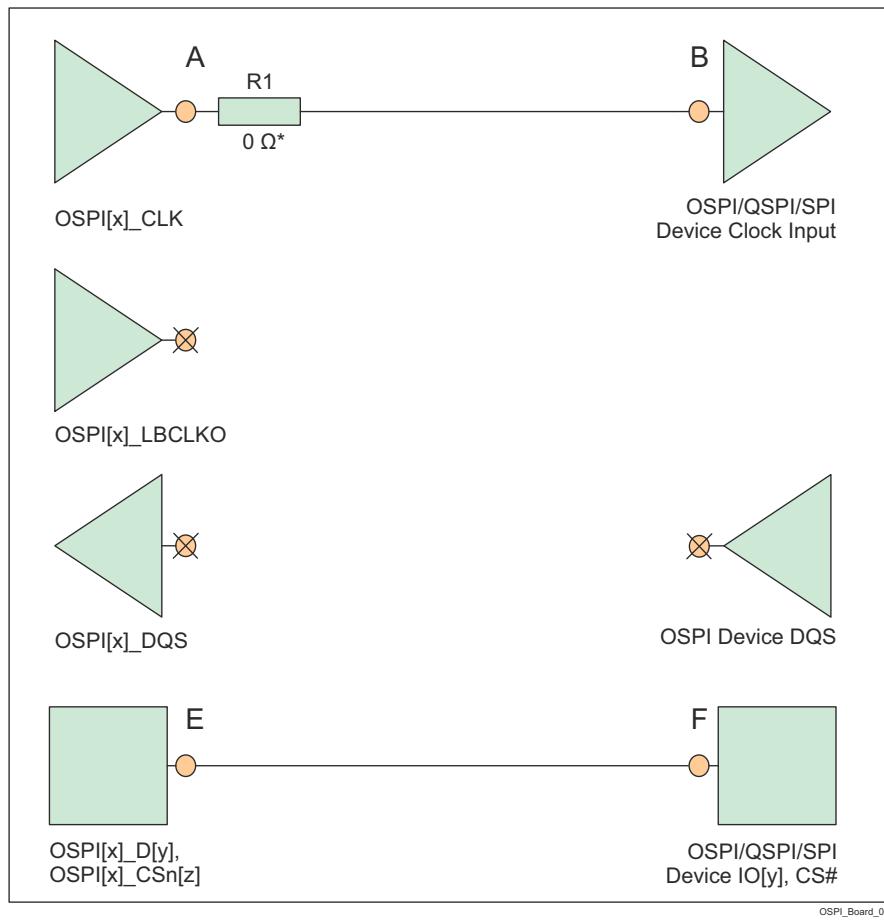

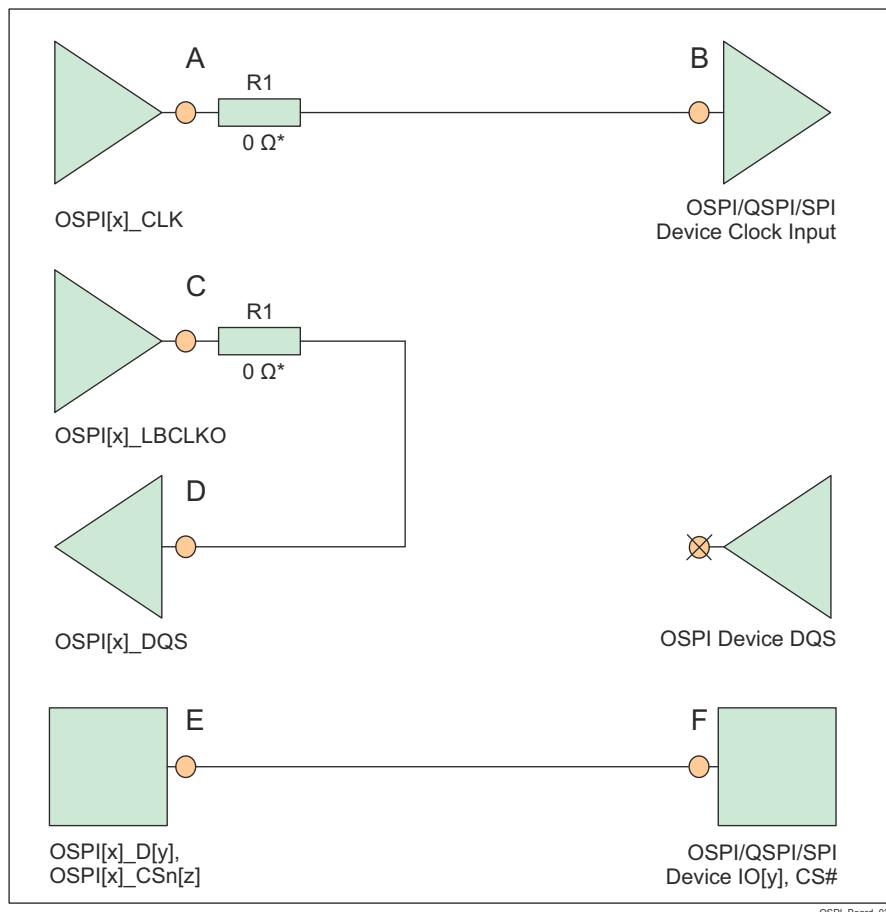

- DDR/SDRをサポートするOSPI/QSPI

- シリアルNANDおよびシリアルNORフラッシュデバイスをサポート

- 4GBytesのメモリアドレスをサポート

- オプションのオンザフライ暗号化を備えたXIPモード

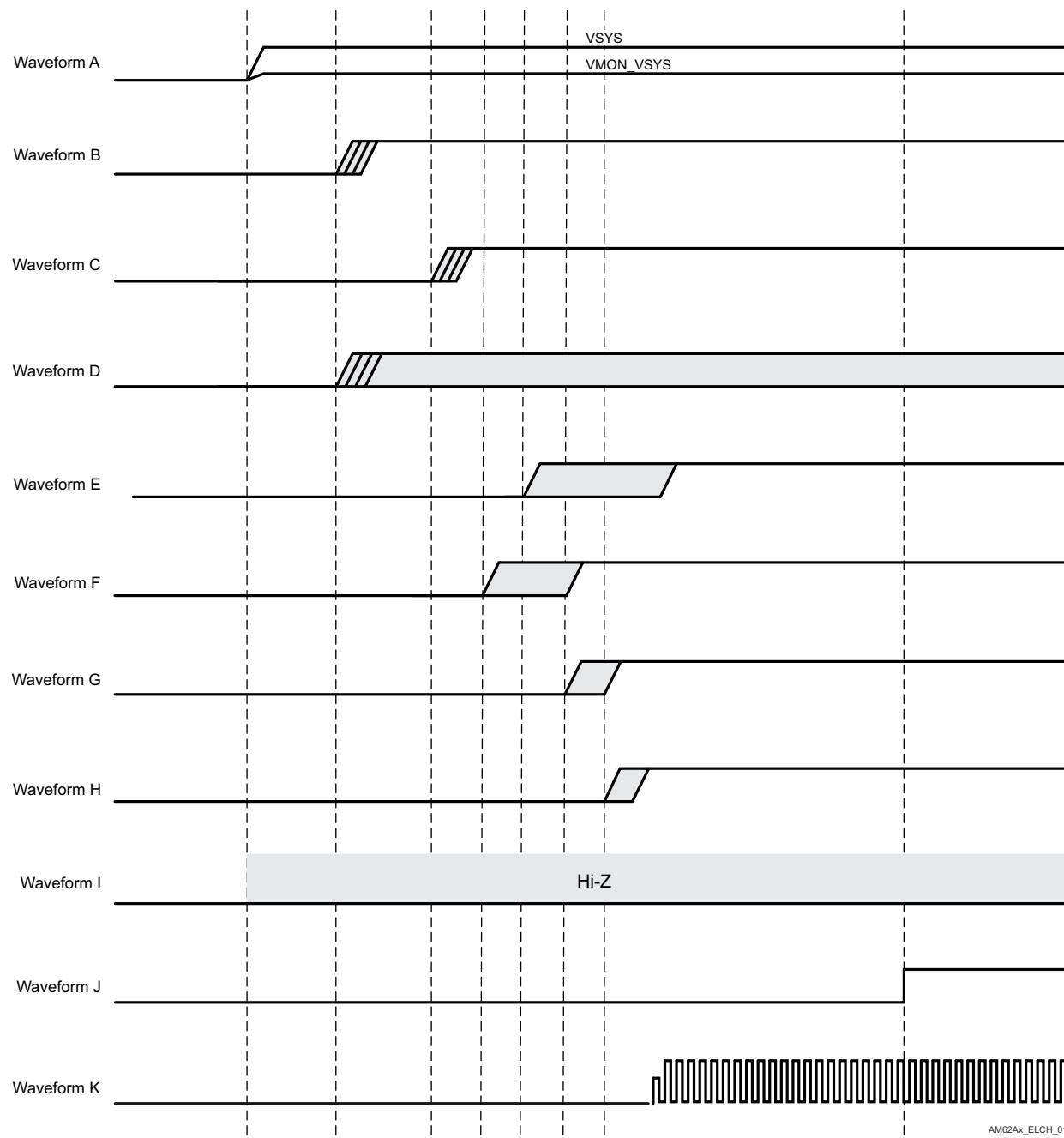

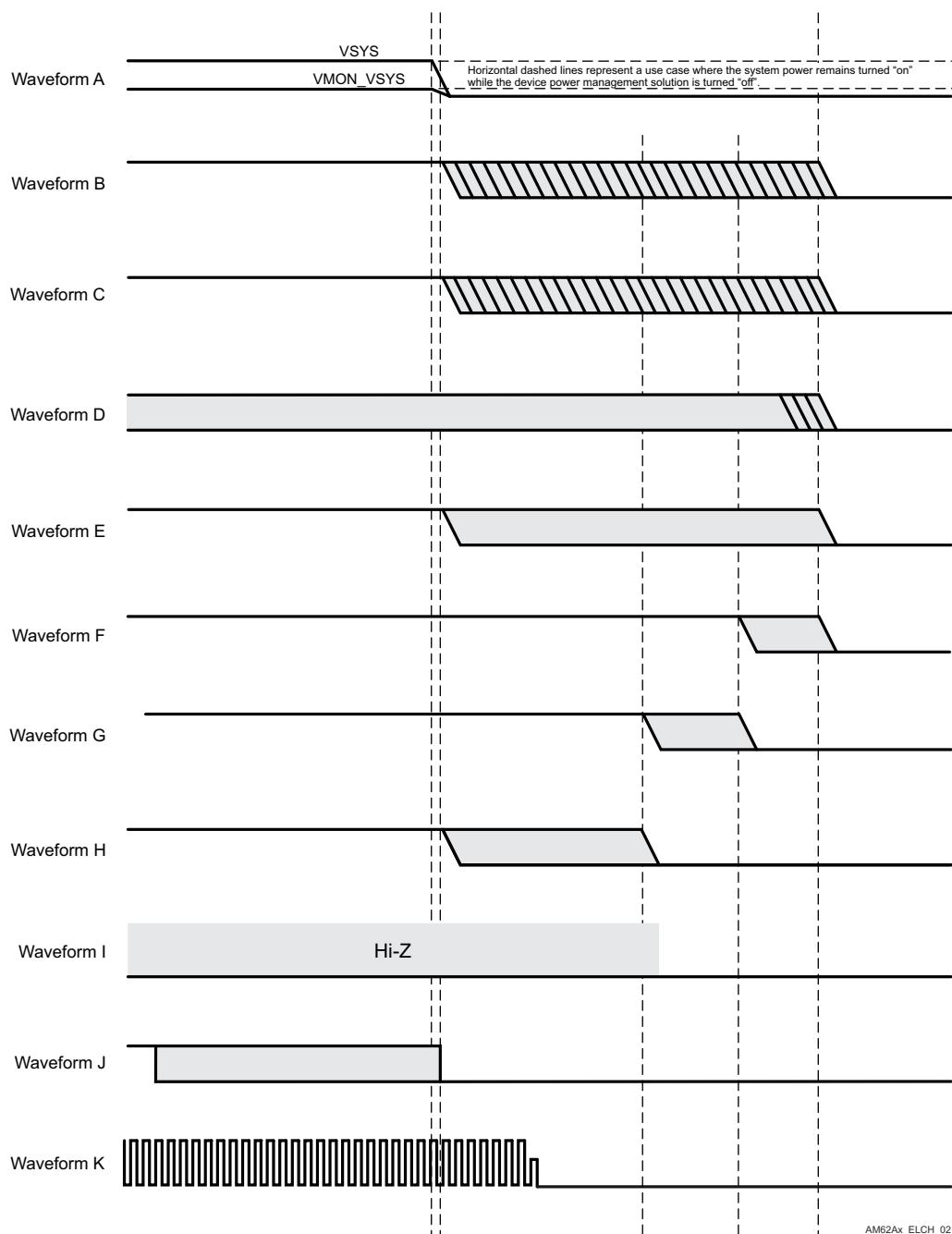

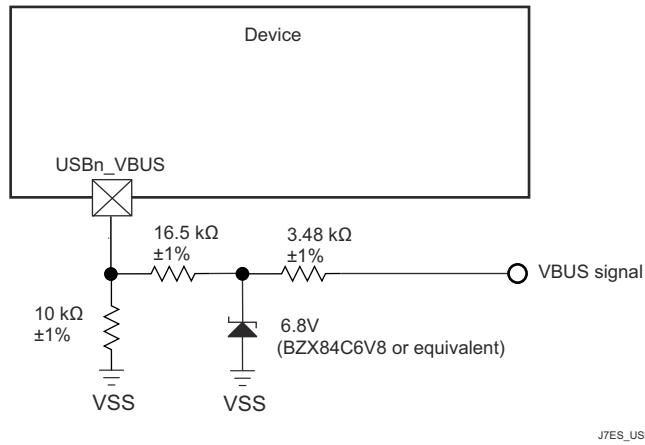

### パワー マネージメント:

- デバイス/パワー マネージャでサポートされている低消費電力モード

- CAN/GPIO/UARTウェイクアップに対する部分的IOサポート

### ポートオプション:

- UART

- I<sup>2</sup>C EEPROM

- OSPI/QSPIフラッシュ

- GPMC NOR/NANDフラッシュ

- シリアルNANDフラッシュ

- SD カード

- eMMC

- USB (ホスト) マス ストレージ デバイス

- 外部ホストからの USB (スレーブ) ポート (DFU モード)

- イーサネット

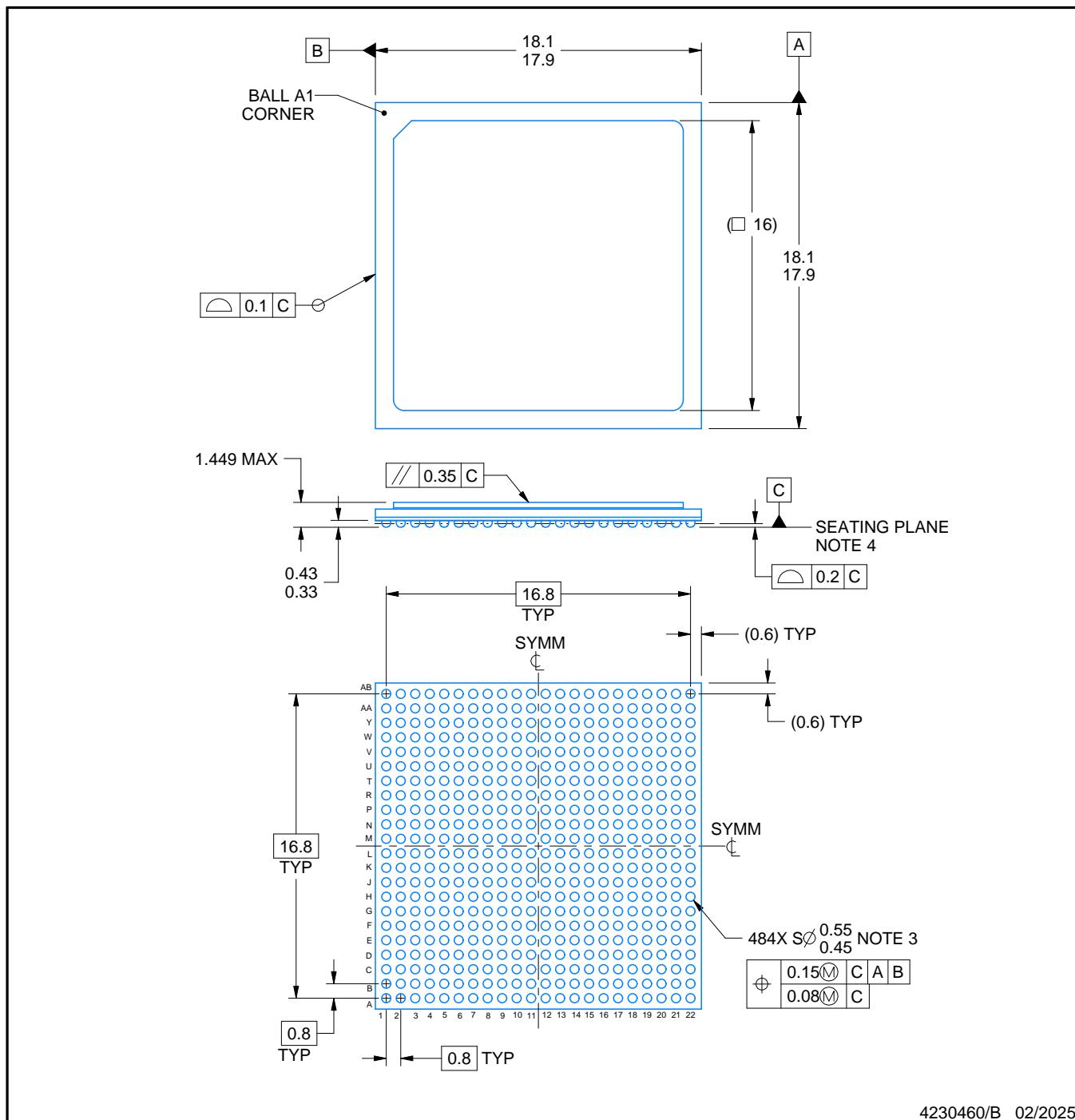

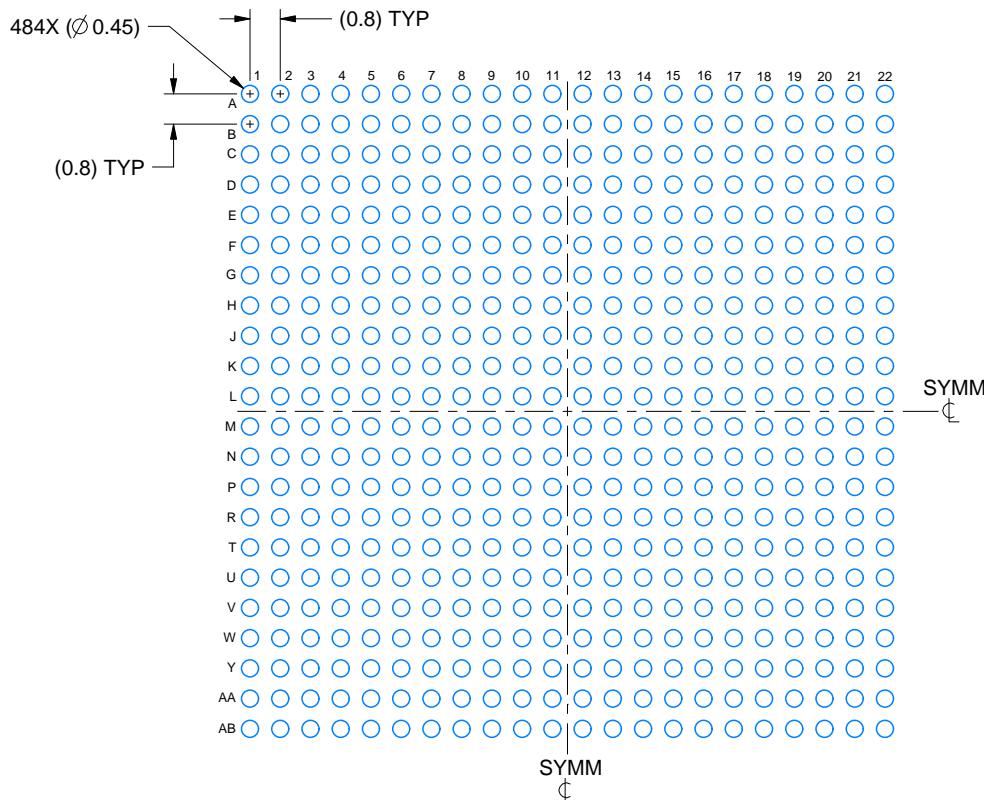

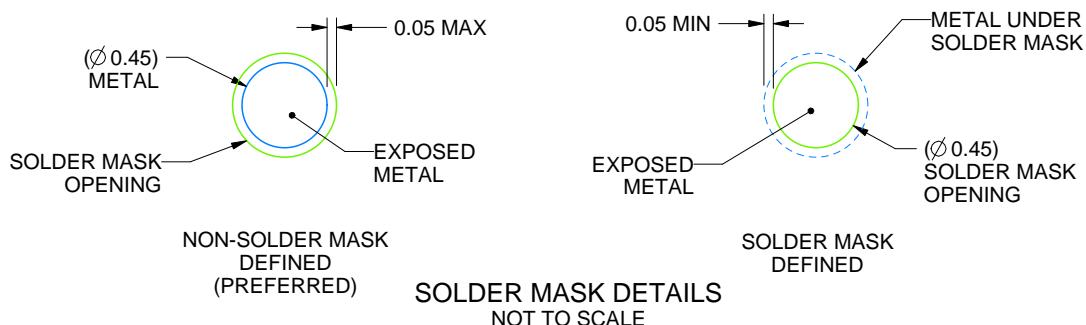

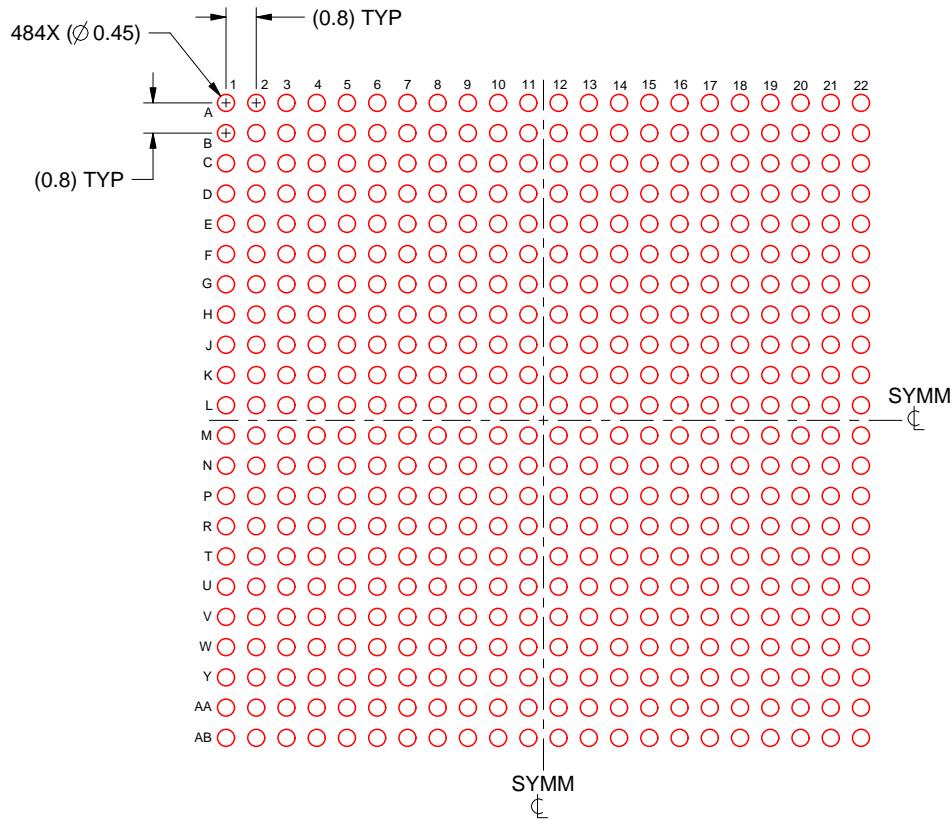

#### テクノロジ / パッケージ:

- 16nm FinFET テクノロジ

- 18mm × 18mm、0.8mm ピッチ フルアレイ、484 ピン FCCSP (ANF)

## 2 アプリケーション

- 車載用 / プレミアム オーディオ アンプ

- 産業用 / プロフェッショナル オーディオ

- 航空宇宙および防衛 / レーダーおよび無線

- 船舶用機器 / ソナー

- 医療およびヘルスケア / 超音波スキャナ

- 試験および測定 / 計測

## 3 概要

AM62D プロセッサは、Sitara™ マイクロコントローラ ファミリに属し、高性能のデジタル信号処理が必要なアプリケーションを対象としています。アプリケーションの一部を以下に示します。

- オーディオ: 車載プレミアム アンプと業務用オーディオ

- レーダーおよび無線: 航空宇宙 / 防衛

- ソナー: 海洋機器

- 超音波: 医療用機器

- 計測: 電流、電圧、その他の信号: 試験 / 測定機器

デバイスの主要なコアには、ARM® Cortex®-A53 およびテキサス・インスツルメンツの C7000™ (‘C7x’) スカラーおよびベクトル DSP コア、専用行列乗算アクセラレータ (MMA)、および分離された MCU アイランドが含まれています。これらはすべて、産業および車載グレードの安全性とセキュリティ ハードウェア アクセラレータにより保護されています。

**DSP コアの概要:** C7x ファミリの C7504 コアは、最大 40GFLOPS の DSP コンピューティングを実現します。前世代の C66x DSP コアに比べて、4~8 倍以上の性能を達成しています。主な特長には以下のものがあります。

- 256 ビットの固定小数点と浮動小数点 DSP ベクタ コア

- シングル サイクルのレイテンシでストリーミング エンジンを介して L2 メモリにアクセス

- 制御コード効率を向上

- 64 ビット メモリアドレッシングとシングル サイクルの 64 ビット ベースの算術演算を備えた真の 64 ビット マシン

**統合の概要:** C7x DSP コアとの組み合わせにより、AM62D SoC は最大で Quad Arm® Cortex®-A53 を統合し、追加の 16.8KDMIPS の計算能力と、Linux またはリアルタイム オペレーティング システム (RTOS) の HLOS のフレキシビリティを実現します。最大 2 つの Arm® Cortex®-R5F サブシステムが低レベルのタイム クリティカルなタスクを処理し、Arm® Cortex®-A53 および DSP のコアに負荷がかからないようにしてアプリケーションの実行に備えます。内蔵セキュリティ機能が現代の攻撃からデータを保護する一方で、内蔵の診断および安全性機能は SIL-2 および ASIL-B レベルまでの動作をサポートしています。また、AM62D デバイスには、時間に制約のあるネットワーク機能 (TSN) を備えた 3 ポートのギガビット イーサネット スイッチも搭載されており、イーサネット オーディオ ビデオ ブリッジ (eAVB) や DANTE などのオーディオ ネットワーク機能を実現できるのと同時に、McASP などのペリフェラルによりマルチチャネル I2S および TDM オーディオ入出力が可能です。

#### パッケージ情報

| 部品番号   | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------|----------------------|--------------------------|

| AM62Dx | ANF (FCCSP、484)      | 18 mm × 18mm             |

(1) 詳細については、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値で、該当する場合はピンも含まれます。

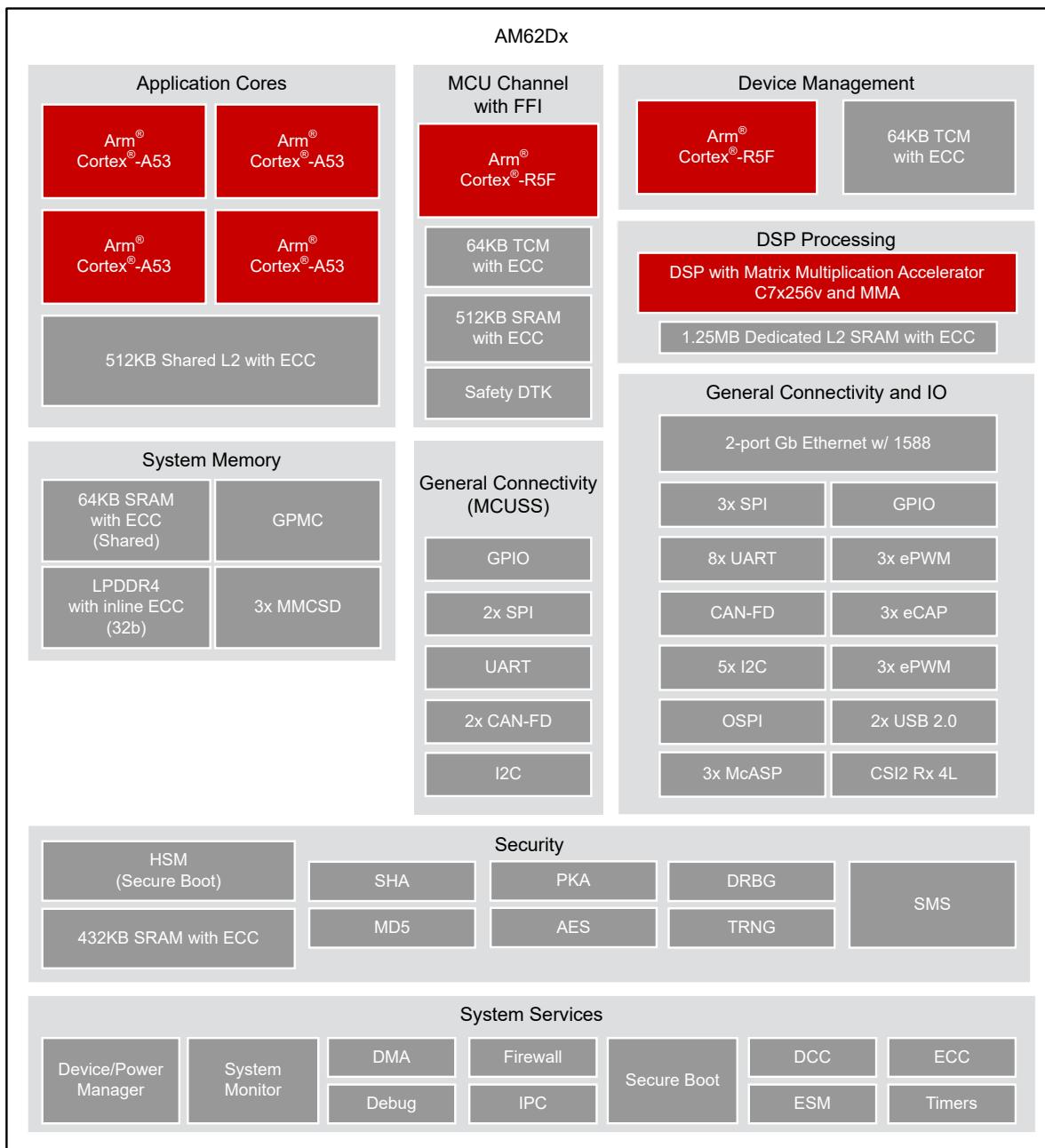

### 3.1 機能ブロック図

図 3-1 は、このデバイスの機能ブロック図です。

#### 注

テキサス・インスツルメンツのソフトウェア開発キット (SDK) で現在サポートされているデバイス機能を理解するには、[Processor-SDK-AM62D](#) の「ダウンロード」タブ オプションにある「AM62Dx ソフトウェア ビルド シート」を検索してください。

図 3-1. 機能ブロック図

## 目次

|                                        |    |                               |     |

|----------------------------------------|----|-------------------------------|-----|

| <b>1 特長</b>                            | 1  | 6.11 溫度センサの特性                 | 89  |

| <b>2 アプリケーション</b>                      | 3  | 6.12 タイミングおよびスイッチング特性         | 90  |

| <b>3 概要</b>                            | 3  | <b>7 詳細説明</b>                 | 211 |

| 3.1 機能ブロック図                            | 4  | 7.1 概要                        | 211 |

| <b>4 デバイスの比較</b>                       | 6  | 7.2 プロセッサ サブシステム              | 212 |

| 4.1 関連製品                               | 7  | 7.3 アクセラレータヒコプロセッサ            | 213 |

| <b>5 端子構成および機能</b>                     | 9  | 7.4 その他のサブシステム                | 214 |

| 5.1 ピン配置図                              | 9  | 7.5 ペリフェラル                    | 216 |

| 5.2 ピン属性                               | 10 | <b>8 アプリケーション、実装、およびレイアウト</b> | 220 |

| 5.3 信号の説明                              | 45 | 8.1 デバイスの接続およびレイアウトの基礎        | 220 |

| 5.4 ピン接続要件                             | 72 | 8.2 ペリフェラルおよびインターフェイス固有の設計情報  | 221 |

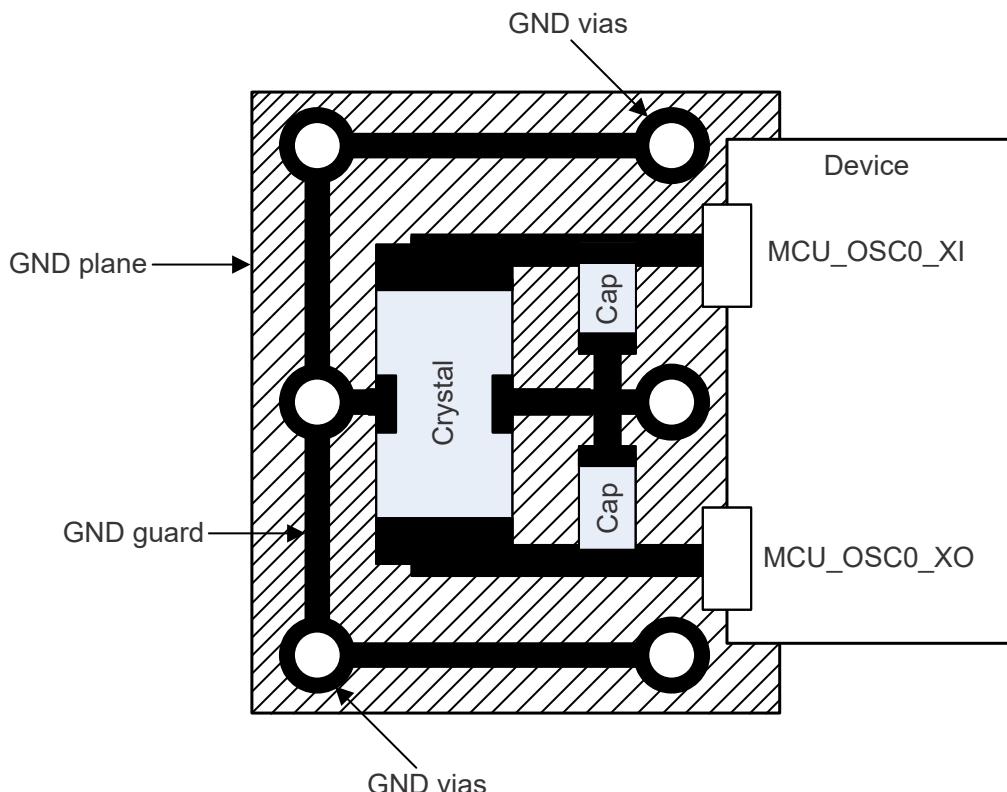

| <b>6 仕様</b>                            | 77 | 8.3 クロック配線のガイドライン             | 228 |

| 6.1 絶対最大定格                             | 77 | <b>9 デバイスおよびドキュメントのサポート</b>   | 229 |

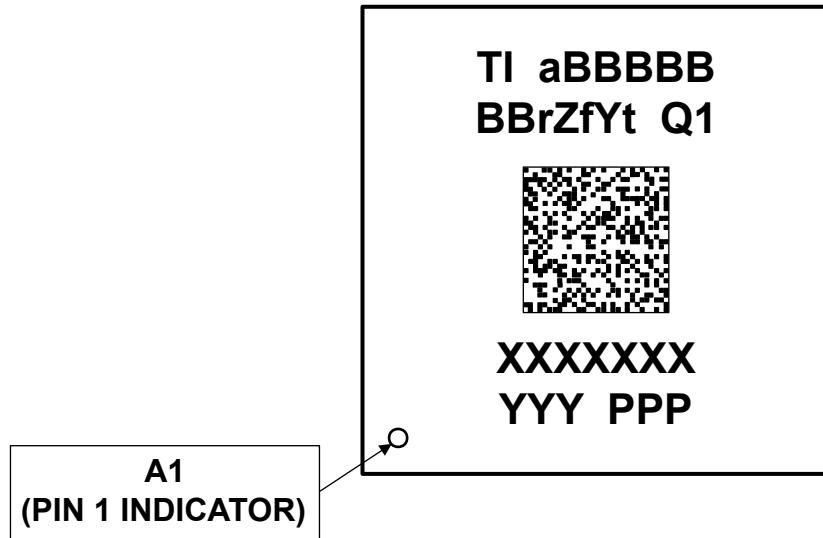

| 6.2 AEC-Q100 未認定デバイスの ESD 定格           | 79 | 9.1 デバイスの命名規則                 | 229 |

| 6.3 AEC-Q100 認定デバイスの ESD 定格            | 79 | 9.2 ツールとソフトウェア                | 232 |

| 6.4 電源投入時間 (POH)                       | 79 | 9.3 ドキュメントのサポート               | 232 |

| 6.5 推奨動作条件                             | 80 | 9.4 サポート・リソース                 | 232 |

| 6.6 動作性能ポイント                           | 82 | 9.5 商標                        | 232 |

| 6.7 消費電力の概略                            | 82 | 9.6 静電気放電に関する注意事項             | 233 |

| 6.8 電気的特性                              | 83 | 9.7 用語集                       | 233 |

| 6.9 ワンタイム プログラマブル (OTP) eFuse の VPP 仕様 | 88 | <b>10 改訂履歴</b>                | 234 |

| 6.10 熱抵抗特性                             | 89 | <b>11 メカニカル、パッケージ、および注文情報</b> | 235 |

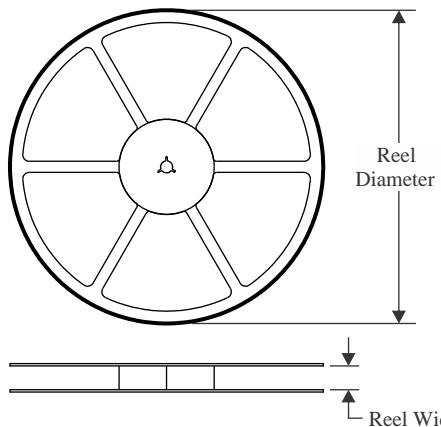

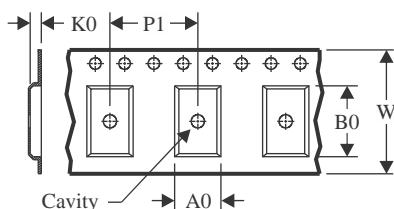

|                                        |    | 11.1 パッケージ情報                  | 235 |

## 4 デバイスの比較

表 4-1 に、デバイス間の比較を相違点を強調して示します。

### 注

多くの機能に関連付けられている IO 信号は限られた数のピンに多重化されるため、この表に記載されている機能が利用できるかどうかは、共有 IO ピンの使用状況によります。信号機能をピンに割り当てるには、**SysConfig** ツールを使用する必要があります。これにより、ピン多重化に関する制限をよりよく理解できます。

### 注

テキサス・インストルメンツのソフトウェア開発キット (SDK) で現在サポートされているデバイス機能を理解するには、**Processor-SDK-AM62D** の「ダウンロード」タブ オプションにある「AM62Dx ソフトウェア ビルド シート」を検索してください。

**表 4-1. デバイスの比較**

| 特長                                                                        | 参照名       | AM62D-Q1                                  |         |  |

|---------------------------------------------------------------------------|-----------|-------------------------------------------|---------|--|

|                                                                           |           | AM62D24                                   | AM62D22 |  |

| <b>WKUP_CTRL_MMR_CFG0_JTAG_USER_ID[31:13] (1)</b>                         |           |                                           |         |  |

| デバイスの「特長」コードごとのレジスタビット値 (デバイスの特長の詳細については、「 <a href="#">項目表記の説明</a> 」表を参照) |           |                                           |         |  |

|                                                                           |           |                                           |         |  |

| プロセッサおよびアクセラレータ                                                           |           |                                           |         |  |

| 速度グレード                                                                    |           | <a href="#">表 6-1 「デバイス速度グレード」</a> を参照    |         |  |

| Arm Cortex-A53<br>マイクロプロセッサ サブシステム                                        | Arm A53   | クワッド コア                                   | デュアル コア |  |

| 行列乗算アクセラレータ搭載 C7x256V DSP                                                 | C7x MMA   | 最高 1GHz                                   |         |  |

| MCU ドメインの ARM Cortex-R5F                                                  | MCU_R5F   | シングル コア<br>機能安全はオプション (3)                 |         |  |

| デバイス管理サブシステム                                                              | WKUP_R5F  | シングル コア                                   |         |  |

| ハードウェア セキュリティ モジュール                                                       | HSM       | あり                                        |         |  |

| 暗号化アクセラレータ                                                                | セキュリティ    | あり                                        |         |  |

| プログラムおよびデータストレージ                                                          |           |                                           |         |  |

| MAIN ドメインのオンチップ共有メモリ (RAM)                                                | OCSRAM    | 64KB                                      |         |  |

| MCU ドメインのオンチップ共有メモリ (RAM)                                                 | MCU_MSRAM | 512KB                                     |         |  |

| LPDDR4 DDR サブシステム                                                         | DDRSS     | インライン ECC 付きで最高 8GB の 32 ビットデータ           |         |  |

| 汎用メモリ コントローラ                                                              | GPMC      | 最大 128MB、ECC 付き                           |         |  |

| ペリフェラル                                                                    |           |                                           |         |  |

| モジュラー コントローラ エリア ネットワーク インターフェイス                                          | MCAN      | 3                                         |         |  |

| CAN-FD をフルサポート                                                            | CAN-FD    | あり                                        |         |  |

| 汎用 I/O                                                                    | GPIO      | 最大 168                                    |         |  |

| 集積回路間インターフェイス                                                             | I2C       | 6                                         |         |  |

| マルチチャネル オーディオシリアル ポート                                                     | MCASP     | 3                                         |         |  |

| マルチチャネルシリアルペリフェラルインターフェイス                                                 | MCSPI     | 5                                         |         |  |

| マルチメディアカード / セキュア デジタル インターフェイス                                           | MM/CSD    | 1 個の eMMC (8 ビット)<br>2 個の SD/SDIO (4 ビット) |         |  |

| OSPI/QSPI/SPI (2) フラッシュサブシステム                                             |           | あり                                        |         |  |

| ギガビットイーサネットインターフェイス                                                       | CPSW3G    | あり                                        |         |  |

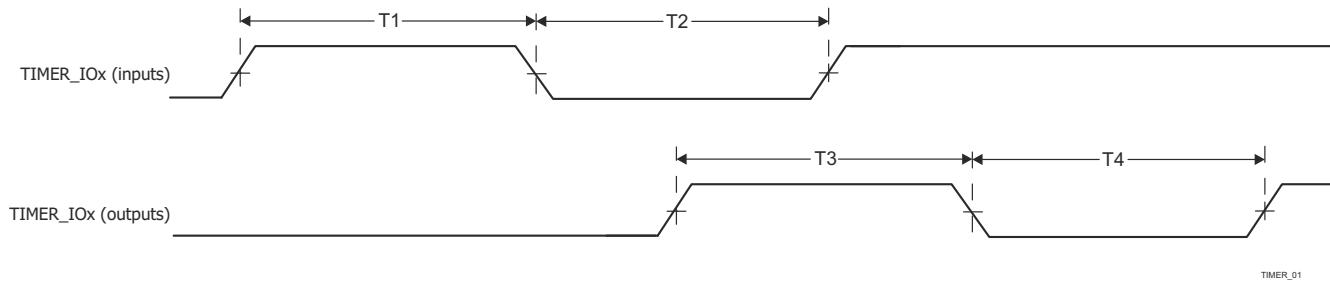

| 汎用タイマー                                                                    | TIMER     | 12 (MCU チャネル内に 4 個)                       |         |  |

| 拡張パルス幅変調器モジュール                                                            | EPWM      | 3                                         |         |  |

| 拡張キャプチャモジュール                                                              | ECAP      | 3                                         |         |  |

| 拡張直交エンコーダ パルス モジュール                                                       | EQEP      | 3                                         |         |  |

| 汎用非同期レシーバ / トランスマッタ                                                       | UART      | 9                                         |         |  |

| CSI2-RX コントローラ (DPHY 付き)                                                  | CSI-RX    | 1                                         |         |  |

表 4-1. デバイスの比較 (続き)

| 特長                     | 参照名     | AM62D-Q1 |         |

|------------------------|---------|----------|---------|

|                        |         | AM62D24  | AM62D22 |

| USB2.0 コントローラ (PHY 付き) | USB 2.0 |          | 2       |

- (1) CTRLMMR\_WKUP\_JTAG\_DEVICE\_ID レジスタおよび DEVICE\_ID ビットフィールドの詳細については、デバイスのテクニカルリファレンスマニュアルを参照してください。

- (2) OSPI/QSPI/SPI デバイスで動作するように構成された OSPI フラッシュホストの 1 つのインスタンス。

- (3) 機能安全は、機能安全コード S から Z を含む注文用型番を選択した場合に使用できます。機能コードの定義については、「[デバイスの命名規則](#)」を参照してください。

## 4.1 関連製品

**Sitara™ プロセッサ** Arm® Cortex®-A コアをベースとするスケーラブルなプロセッサで構成された幅広いファミリは、柔軟なアクセラレータやペリフェラル、接続性にくわえ、統合ソフトウェアのサポートにより、センサからサーバーまでさまざまな用途に最適です。Sitara プロセッサには、産業用や車載用でのアプリケーションに必要な信頼性と機能安全のサポートがあります。

**Sitara™ microcontrollers**、クラス最高の Arm® ベース 32 ビットマイコン (MCU) は、高性能で電力効率の高いデバイスで構成されたスケーラブルな製品ラインアップを提供し、開発中システムのニーズを満たす手助けとなります。開発中の設計で、機能安全、電力効率、リアルタイム制御、高度なネットワーク、アナリティクス、セキュリティなどの機能を実現できます。

**AM64x Sitara™** プロセッサは、ファクトリオートメーション / 制御 (FAC) やモーター制御などの産業用アプリケーションをターゲットとし、Linux アプリケーション プロセッシング コア (Cortex®-A53)、リアルタイム プロセッシング コア (Cortex®-R5F)、産業用通信サブシステム (PRU\_ICSSG) を使用して、EtherCAT、Profinet、EtherNet/IP などのプロトコルをサポートします。AM64x は、1 つの CPSW3G と 2 つの PRU\_ICSSG を実装しており、最大 5 つのギガビットイーサネットポートをサポートします。また、シングル レーンの PCIe Gen2 または USB SuperSpeed Gen1、機能安全オプション、セキュア ブート、ランタイム セキュリティなど包括的なペリフェラル セットもサポートしています。

**AM623 Sitara™** プロセッサ、Arm® Cortex®-A53 ベースの物体認識機能とジェスチャ認識機能を搭載した、IoT (モノのインターネット) とゲートウェイ向け SoC。低コストの AM623 Sitara™ MPU アプリケーション プロセッサ ファミリは、Linux® アプリケーション開発向けに構築されています。スケーラブルな Arm® Cortex®-A53 の性能と、デュアル ディスプレイ サポートなどの組込み機能に加えて、広範なペリフェラル セットを搭載する AM623 デバイスは広範な産業用および車載用アプリケーションに最適です。

**AM625 Sitara™** プロセッサ、Arm® Cortex®-A53 とフル HD デュアル ディスプレイを搭載した、人間と機械の対話型操作向け SoC。低コストの AM625 Sitara™ MPU アプリケーション プロセッサ ファミリは、Linux® アプリケーション開発向けに構築されています。スケーラブルな Arm® Cortex®-A53 の性能と、デュアル ディスプレイ サポートや 3D グラフィックス アクセラレーションなどの組込み機能に加えて、広範なペリフェラル セットを搭載する AM625 デバイスは広範な産業用および車載用アプリケーションに最適です。

**AM62A3、AM62A3-Q1、AM62A7、AM62A7-Q1** の各 Sitara™ プロセッサは、1~4 個の Cortex A-53 Arm コアと、1 または 2 TOPS のアナリティクス ハードウェア アクセラレータを活用する組込みビジョン SoC です。このスケーラブルで高性能な AM62Ax Sitara MPU アプリケーション プロセッサ ファミリは、Linux アプリケーション開発向けに構築されています。AM62Ax は h.264/h.265 エンコード / デコード、セキュア ブート、画像信号処理、ディープ ラーニング アクセラレータなどの組込み機能を搭載し、産業用と車載用の幅広いアプリケーションに最適です。

設計を完成させるための製品:

- イーサネット PHY

- パワー マネージメント / PMIC

- クロック / タイミング

- パワー スイッチ

- CAN トランシーバ

- ESD 保護

これらのデバイスをシステム設計で実装する方法の詳細と、推奨される特定の部品番号の部品表 (BOM) については、AUDIO-AM62D-EVM EVM の回路図を参照してください。

## 5 端子構成および機能

## 5.1 ピン配置図

## 注

「ボール」、「ピン」、「端子」という用語は、ドキュメント全体で同じ意味で使用されています。物理的なパッケージに言及する場合にのみ「ボール」が使用されています。

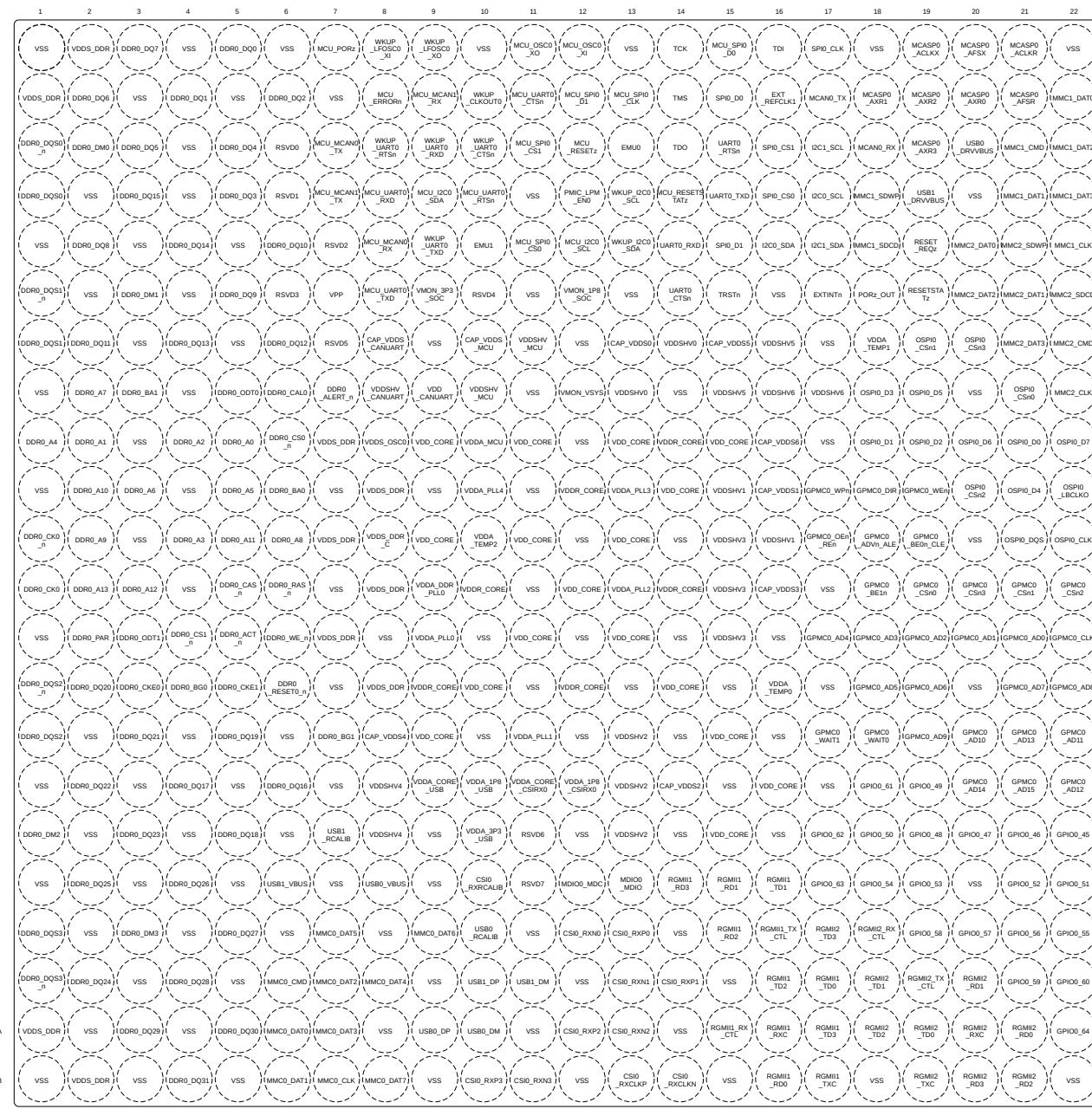

図 5-1 に、484 ボール フリップ チップ ボール グリッド アレイ (FCCSP BGA) パッケージのボールの位置を示します。ここで、HTML バージョンでは、ボールの上にカーソルを置くと追加情報が表示されます。この図は、表 5-1～表 5-70（「ピン属性」表、「ピン接続要件」表を含むすべての「信号説明」表）とともに使用します。

図 5-1. ANF FCCSP BGA ピン配置図 (上面図)

## 5.2 ピン属性

次のリストに、表 5-1「ピン属性 (ANF パッケージ)」の各列の内容を示します。

- ボール番号:** ボール グリッド アレイ パッケージの各端子に割り当てられたボール番号。

- ボール名:** ボール グリッド アレイ パッケージの各端子に割り当てられたボール名 (通常はプライマリ MUXMODE 0 信号機能からつけた名前)。

- 信号名:** ボールに関連付けられているすべての専用およびピン多重化信号機能の信号名。

### 注

多くのデバイスピンは複数の信号機能をサポートしています。一部の信号機能は、ピンに関連付けられた単一層のマルチプレクサで選択されます。他の信号機能は 2 層以上のマルチプレクサで選択され、ある層はピンに関連付けられ、他の層はペリフェラル ロジック機能に関連付けられます。

表 5-1「ピン属性 (ANF パッケージ)」では、ピンでの信号多重化のみが定義されています。ピンでの信号多重化の詳細については、デバイスのテクニカル リファレンス マニュアルで「デバイス構成」の章にある「パッド構成 レジスタ」セクションを参照してください。ペリフェラル信号の多重化に関する情報については、デバイスのテクニカル リファレンス マニュアルで該当するペリフェラルの章を参照してください。

- 多重化モード:** 各ピンの多重化信号機能に関連付けられた MUXMODE 値:

- MUXMODE 0 は、プライマリピンの多重化信号機能です。ただし、プライマリピンの多重化信号機能は、必ずしもデフォルトのピン多重化信号機能とは限りません。

### 注

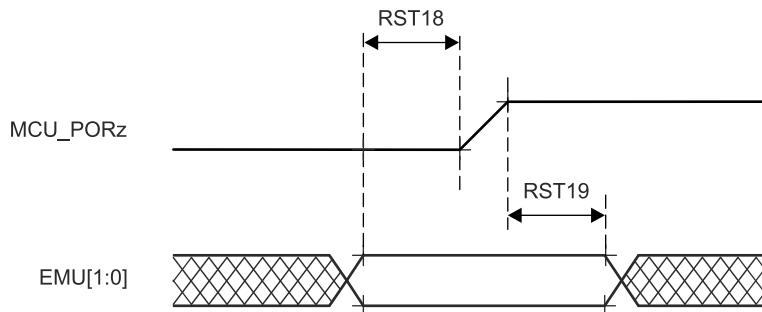

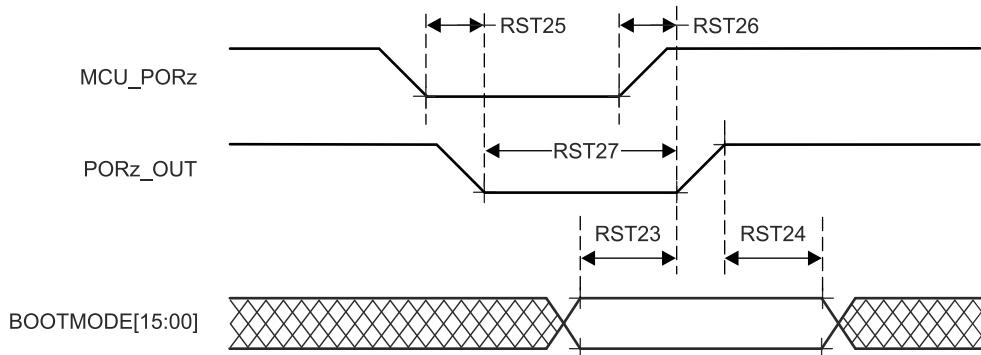

「リセット後の MUX モード」列の値は、MCU\_POR<sub>z</sub> がアサート解除されたときに選択されるデフォルトのピン多重化信号機能を定義します。

- ピン多重化信号機能には、MUXMODE の値 1~15 を使用できます。ただし、すべての MUXMODE 値が実装されているわけではありません。有効な MUXMODE 値は、「ピン属性」表でピン多重化信号機能として定義された値のみです。MUXMODE の有効な値のみを使用する必要があります。

- ブートストラップは SOC 構成ピンを定義します。各ピンに適用されるロジック状態は、POR<sub>z</sub>\_OUT の立ち上がりエッジでラッチされます。これらの入力信号機能はそれぞれのピンに固定で、MUXMODE を使用してプログラムすることはできません。

- 空欄は該当しないことを意味します。

### 注

デバイスを適切に動作させるには、以下の MUXMODE の構成を避ける必要があります。

- 複数のピンを同じピン多重化信号機能への入力として動作するように構成すると、予期しない結果が生じる可能性があるため、この構成はサポートされていません。

- ピンを未定義のピン多重化モードに設定すると、ピンの動作が未定義になります。

5. タイプ:信号の種類と方向:

- I = 入力

- O = 出力

- OD = 出力、オープンドレイン出力機能付き

- IO = 入力、出力、または同時に入力と出力

- IOD = 入力、出力、または同時に入力と出力、オープンドレイン出力機能付き

- IOZ = 入力、出力、または同時に入力と出力、3ステート出力機能付き

- OZ = 出力、3ステート出力機能付き

- A = アナログ

- PWR = 電源

- GND = グラウンド

- CAP = LDO コンデンサ。

6. **DSIS**:選択解除入力状態 (DSIS) は、MUXMODE によってピン多重化信号機能が選択されていないとき、サブシステム入力 (ロジック「0」、ロジック「1」、または「パッド」レベル) に駆動される状態を示します。

- 0:ロジック 0 がサブシステム入力に駆動されます。

- 1:ロジック 1 がサブシステム入力に駆動されます。

- パッド:パッドのロジック状態がサブシステム入力に駆動されます。

- 空欄は該当しないことを意味します。

7. リセット時のボールの状態 (RX/TX/PULL):MCU\_PORz がアサートされているときの端子の状態。ここで、RX は入力バッファの状態、TX は出力バッファの状態、PULL は内部プル抵抗の状態を定義します。

- RX (入力バッファ)

- オフ:入力バッファは無効です。

- オン:入力バッファは有効です。

- TX (出力バッファ)

- オフ:出力バッファは無効です。

- Low:出力バッファは有効であり、 $V_{OL}$  を駆動します。

- PULL (内部プル抵抗)

- オフ:内部プル抵抗はターンオフされています。

- アップ:内部プルアップ抵抗はターンオンされています。

- ダウン:内部プルダウン抵抗はターンオンされています。

- NA:該当なし。

- 空欄は該当しないことを意味します。

8. リセット後のボールの状態 (RX/TX/PULL):MCU\_PORz がアサート解除された後の端子の状態。ここで、RX は入力バッファの状態、TX は出力バッファの状態、PULL は内部プル抵抗の状態を定義します。

- RX (入力バッファ)

- オフ:入力バッファは無効です。

- オン:入力バッファは有効です。

- TX (出力バッファ)

- オフ:出力バッファは無効です。

- SS:MUXMODE で選択されたサブシステムによって、出力バッファの状態が決まります。

- PULL (内部プル抵抗)

- オフ:内部プル抵抗はターンオフされています。

- アップ:内部プルアップ抵抗はターンオンされています。

- ダウン:内部プルダウン抵抗はターンオンされています。

- NA:該当なし。

- 空欄は該当しないことを意味します。

9. **リセット後の多重化モード:**この列の値は、MCU\_PORZ がデアサートされた後のデフォルトのピン多重化信号機能を定義します。

空欄は該当しないことを意味します。

10. **I/O 動作電圧:**この列は、それぞれの電源の I/O 動作電圧オプションについて説明します (該当する場合)。

空欄は該当しないことを意味します。

詳細については、[セクション 6.5 「推奨動作条件」](#)で各電源に定義されている有効な動作電圧範囲を参照してください。

11. **電源:**関連付けられている I/O の電源 (該当する場合)。

空欄は該当しないことを意味します。

12. **HYS:**この I/O に関連付けられている入力バッファにヒステリシスがあるかどうかを示します。

- あり:ヒステリシス付き

- なし:ヒステリシスなし

- 空欄は該当しないことを意味します。

詳細については、[セクション 6.8 「電気的特性」](#)のヒステリシスの値を参照してください。

13. **バッファのタイプ:**この列は、端末に関連付けられたバッファのタイプを定義します。この情報を使用して、適用可能な電気的特性の表を決定できます。

空欄は該当しないことを意味します。

電気的特性については、[セクション 6.8 「電気的特性」](#)の適切なバッファ タイプの表を参照してください。

14. **プルアップ / ダウン タイプ:**内部プルアップまたはプルダウン抵抗が存在することを示します。プルアップおよびプルダウン抵抗は、ソフトウェアによって有効化または無効化できます。

- PU:内部プルアップ

- PD:内部プルダウン

- PU/PD:内部プルアップおよびプルダウン

- 空欄は内部プル抵抗がないことを意味します。

15. **PADCONFIG レジスタ:**ボールに関連付けられた IO パッド構成レジスタの名前。

16. **PADCONFIG アドレス:**ボールに関連付けられた IO パッド構成レジスタの物理アドレス。

表 5-1. ピン属性 (ANF パッケージ)

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16] | 信号名 [3]          | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11]                 | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|--------------------------------------------------------|------------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|-------------------------|----------|--------------|-------------------|

| G13       | CAP_VDDSO                                              | CAP_VDDSO        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| K16       | CAP_VDDS1                                              | CAP_VDDS1        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| T14       | CAP_VDDS2                                              | CAP_VDDS2        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| M16       | CAP_VDDS3                                              | CAP_VDDS3        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| R8        | CAP_VDDS4                                              | CAP_VDDS4        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| G15       | CAP_VDDS5                                              | CAP_VDDS5        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| J16       | CAP_VDDS6                                              | CAP_VDDS6        |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| G8        | CAP_VDDS_CANUART                                       | CAP_VDDS_CANUART |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| G10       | CAP_VDDS MCU                                           | CAP_VDDS MCU     |            | CAP     |          |                               |                               |                  |              |                         |          |              |                   |

| AB14      | CSI0_RXCLKN                                            | CSI0_RXCLKN      | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| AB13      | CSI0_RXCLKP                                            | CSI0_RXCLKP      | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| V10       | CSI0_RXRCALIB                                          | CSI0_RXRCALIB    | A          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| W12       | CSI0_RXN0                                              | CSI0_RXN0        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| Y13       | CSI0_RXN1                                              | CSI0_RXN1        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| AA13      | CSI0_RXN2                                              | CSI0_RXN2        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| AB11      | CSI0_RXN3                                              | CSI0_RXN3        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| W13       | CSI0_RXP0                                              | CSI0_RXP0        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| Y14       | CSI0_RXP1                                              | CSI0_RXP1        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| AA12      | CSI0_RXP2                                              | CSI0_RXP2        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| AB10      | CSI0_RXP3                                              | CSI0_RXP3        | I          |         |          |                               |                               |                  | 1.8 V        | VDDA_1P8_CSIRX          |          | D-PHY        |                   |

| N5        | DDR0_ACT_n                                             | DDR0_ACT_n       | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| H7        | DDR0_ALERT_n                                           | DDR0_ALERT_n     | IO         |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| M5        | DDR0_CAS_n                                             | DDR0_CAS_n       | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| N2        | DDR0_PAR                                               | DDR0_PAR         | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| M6        | DDR0_RAS_n                                             | DDR0_RAS_n       | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| N6        | DDR0_WE_n                                              | DDR0_WE_n        | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| J5        | DDR0_A0                                                | DDR0_A0          | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| J2        | DDR0_A1                                                | DDR0_A1          | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| J4        | DDR0_A2                                                | DDR0_A2          | O          |         |          |                               |                               |                  | 1.1 V        | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

表 5-1. ピン属性 (ANF パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16] | 信号名 [3]    | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11]                 | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|--------------------------------------------------------|------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|-------------------------|----------|--------------|-------------------|

| L4        | DDR0_A3                                                | DDR0_A3    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| J1        | DDR0_A4                                                | DDR0_A4    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| K5        | DDR0_A5                                                | DDR0_A5    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| K3        | DDR0_A6                                                | DDR0_A6    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| H2        | DDR0_A7                                                | DDR0_A7    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| L6        | DDR0_A8                                                | DDR0_A8    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| L2        | DDR0_A9                                                | DDR0_A9    |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| K2        | DDR0_A10                                               | DDR0_A10   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| L5        | DDR0_A11                                               | DDR0_A11   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| M3        | DDR0_A12                                               | DDR0_A12   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| M2        | DDR0_A13                                               | DDR0_A13   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| K6        | DDR0_BA0                                               | DDR0_BA0   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| H3        | DDR0_BA1                                               | DDR0_BA1   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| P4        | DDR0_BG0                                               | DDR0_BG0   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| R7        | DDR0_BG1                                               | DDR0_BG1   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| H6        | DDR0_CAL0                                              | DDR0_CAL0  |            | A       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| M1        | DDR0_CK0                                               | DDR0_CK0   |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| L1        | DDR0_CK0_n                                             | DDR0_CK0_n |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| P3        | DDR0_CKE0                                              | DDR0_CKE0  |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| P5        | DDR0_CKE1                                              | DDR0_CKE1  |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| J6        | DDR0_CS0_n                                             | DDR0_CS0_n |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

**表 5-1. ピン属性 (ANF パッケージ) (続き)**

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16] | 信号名 [3]    | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11]                 | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|--------------------------------------------------------|------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|-------------------------|----------|--------------|-------------------|

| N4        | DDR0_CS1_n                                             | DDR0_CS1_n |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| C2        | DDR0_DM0                                               | DDR0_DM0   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| F3        | DDR0_DM1                                               | DDR0_DM1   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| U1        | DDR0_DM2                                               | DDR0_DM2   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| W3        | DDR0_DM3                                               | DDR0_DM3   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| A5        | DDR0_DQ0                                               | DDR0_DQ0   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| B4        | DDR0_DQ1                                               | DDR0_DQ1   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| B6        | DDR0_DQ2                                               | DDR0_DQ2   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| D5        | DDR0_DQ3                                               | DDR0_DQ3   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| C5        | DDR0_DQ4                                               | DDR0_DQ4   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| C3        | DDR0_DQ5                                               | DDR0_DQ5   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| B2        | DDR0_DQ6                                               | DDR0_DQ6   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| A3        | DDR0_DQ7                                               | DDR0_DQ7   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| E2        | DDR0_DQ8                                               | DDR0_DQ8   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| F5        | DDR0_DQ9                                               | DDR0_DQ9   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| E6        | DDR0_DQ10                                              | DDR0_DQ10  |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| G2        | DDR0_DQ11                                              | DDR0_DQ11  |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| G6        | DDR0_DQ12                                              | DDR0_DQ12  |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| G4        | DDR0_DQ13                                              | DDR0_DQ13  |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| E4        | DDR0_DQ14                                              | DDR0_DQ14  |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| D3        | DDR0_DQ15                                              | DDR0_DQ15  |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

表 5-1. ピン属性 (ANF パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16] | 信号名 [3]     | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11]                 | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|--------------------------------------------------------|-------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|-------------------------|----------|--------------|-------------------|

| T6        | DDR0_DQ16                                              | DDR0_DQ16   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| T4        | DDR0_DQ17                                              | DDR0_DQ17   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| U5        | DDR0_DQ18                                              | DDR0_DQ18   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| R5        | DDR0_DQ19                                              | DDR0_DQ19   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| P2        | DDR0_DQ20                                              | DDR0_DQ20   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| R3        | DDR0_DQ21                                              | DDR0_DQ21   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| T2        | DDR0_DQ22                                              | DDR0_DQ22   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| U3        | DDR0_DQ23                                              | DDR0_DQ23   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| Y2        | DDR0_DQ24                                              | DDR0_DQ24   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| V2        | DDR0_DQ25                                              | DDR0_DQ25   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| V4        | DDR0_DQ26                                              | DDR0_DQ26   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| W5        | DDR0_DQ27                                              | DDR0_DQ27   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| Y4        | DDR0_DQ28                                              | DDR0_DQ28   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| AA3       | DDR0_DQ29                                              | DDR0_DQ29   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| AA5       | DDR0_DQ30                                              | DDR0_DQ30   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| AB4       | DDR0_DQ31                                              | DDR0_DQ31   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| D1        | DDR0_DQS0                                              | DDR0_DQS0   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| C1        | DDR0_DQS0_n                                            | DDR0_DQS0_n |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| G1        | DDR0_DQS1                                              | DDR0_DQS1   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| F1        | DDR0_DQS1_n                                            | DDR0_DQS1_n |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| R1        | DDR0_DQS2                                              | DDR0_DQS2   |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

表 5-1. ピン属性 (ANF パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16]  | 信号名 [3]                | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11]                 | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|---------------------------------------------------------|------------------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|-------------------------|----------|--------------|-------------------|

| P1        | DDR0_DQS2_n                                             | DDR0_DQS2_n            |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| W1        | DDR0_DQS3                                               | DDR0_DQS3              |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| Y1        | DDR0_DQS3_n                                             | DDR0_DQS3_n            |            | IO      |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| H5        | DDR0_ODT0                                               | DDR0_ODT0              |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| N3        | DDR0_ODT1                                               | DDR0_ODT1              |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| P6        | DDR0_RESET0_n                                           | DDR0_RESET0_n          |            | O       |          |                               |                               |                  | 1.1V         | VDDS_DDR,<br>VDDS_DDR_C |          | DDR          |                   |

| C13       | EMU0<br>PADCONFIG:<br>MCU_PADCONFIG30<br>0x04084078     | EMU0                   | 0          | IO      | 0        | オン/オフ/アップ                     | オン/オフ/アップ                     | 0                | 1.8V/3.3V    | VDDSHV_MCU              | あり       | LVC MOS      | PU/PD             |

| E10       | EMU1<br>PADCONFIG:<br>MCU_PADCONFIG31<br>0x0408407C     | EMU1                   | 0          | IO      | 0        | オン/オフ/アップ                     | オン/オフ/アップ                     | 0                | 1.8V/3.3V    | VDDSHV_MCU              | あり       | LVC MOS      | PU/PD             |

| F17       | EXTINTn<br>PADCONFIG:<br>PADCONFIG125<br>0x000F41F4     | EXTINTn                | 0          | I       | 1        | オフ/オフ/NA                      | オフ/オフ/NA                      | 7                | 1.8V/3.3V    | VDDSHV0                 | あり       | I2C OD FS    |                   |

|           | GPIO1_31                                                | 7                      | IO         | パッド     |          |                               |                               |                  |              |                         |          |              |                   |

| B16       | EXT_REFCLK1<br>PADCONFIG:<br>PADCONFIG124<br>0x000F41F0 | EXT_REFCLK1            | 0          | I       | 0        | オフ/オフ/オフ                      | オフ/オフ/オフ                      | 7                | 1.8V/3.3V    | VDDSHV0                 | あり       | LVC MOS      | PU/PD             |

|           |                                                         | SYNC1_OUT              | 1          | O       |          |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | SPI2_CS3               | 2          | IO      | 1        |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | SYSCLKOUT0             | 3          | O       |          |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | TIMER_IO4              | 4          | IO      | 0        |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | CLKOUT0                | 5          | O       |          |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | CP_GEMAC_CPTS0_RFT_CLK | 6          | I       | 0        |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | GPIO1_30               | 7          | IO      | パッド      |                               |                               |                  |              |                         |          |              |                   |

| U22       | GPIO0_45<br>PADCONFIG:<br>PADCONFIG46<br>0x000F40B8     | ECAP0_IN_APWM_OUT      | 8          | IO      | 0        | オフ/オフ/オフ                      | オフ/オフ/オフ                      | 7                | 1.8V/3.3V    | VDDSHV3                 | あり       | LVC MOS      | PU/PD             |

|           |                                                         | GPMC0_A0               | 1          | OZ      |          |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | UART2_RXD              | 4          | I       | 1        |                               |                               |                  |              |                         |          |              |                   |

| U21       | GPIO0_46<br>PADCONFIG:<br>PADCONFIG47<br>0x000F40BC     | GPIO0_45               | 7          | IO      | パッド      | オフ/オフ/オフ                      | オフ/オフ/オフ                      | 7                | 1.8V/3.3V    | VDDSHV3                 | あり       | LVC MOS      | PU/PD             |

|           |                                                         | GPMC0_A1               | 1          | OZ      |          |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | UART2_TXD              | 4          | O       |          |                               |                               |                  |              |                         |          |              |                   |

|           |                                                         | GPIO0_46               | 7          | IO      | パッド      |                               |                               |                  |              |                         |          |              |                   |

表 5-1. ピン属性 (ANF パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16] | 信号名 [3]    | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11] | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|--------------------------------------------------------|------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|---------|----------|--------------|-------------------|

| U20       | GPIO0_47<br>PADCONFIG: PADCONFIG48<br>0x000F40C0       | GPIO0_A2   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART3_RXD  | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_47   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| U19       | GPIO0_48<br>PADCONFIG: PADCONFIG49<br>0x000F40C4       | GPIO0_A3   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART3_TXD  | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_48   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| T19       | GPIO0_49<br>PADCONFIG: PADCONFIG50<br>0x000F40C8       | GPIO0_A4   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART4_RXD  | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_49   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| U18       | GPIO0_50<br>PADCONFIG: PADCONFIG51<br>0x000F40CC       | GPIO0_A5   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART4_TXD  | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_50   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| V22       | GPIO0_51<br>PADCONFIG: PADCONFIG52<br>0x000F40D0       | GPIO0_A6   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART5_RXD  | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_51   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| V21       | GPIO0_52<br>PADCONFIG: PADCONFIG53<br>0x000F40D4       | GPIO0_A7   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART5_TXD  | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_52   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| V19       | GPIO0_53<br>PADCONFIG: PADCONFIG54<br>0x000F40D8       | GPIO0_A8   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART6_RXD  | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_53   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| V18       | GPIO0_54<br>PADCONFIG: PADCONFIG55<br>0x000F40DC       | GPIO0_A9   | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART6_TXD  | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_54   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| W22       | GPIO0_55<br>PADCONFIG: PADCONFIG56<br>0x000F40E0       | GPIO0_A10  | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART6_RTSn | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_55   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| W21       | GPIO0_56<br>PADCONFIG: PADCONFIG57<br>0x000F40E4       | GPIO0_A11  | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART6_CTSn | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_56   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| W20       | GPIO0_57<br>PADCONFIG: PADCONFIG58<br>0x000F40E8       | GPIO0_A12  | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART5_RTSn | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_57   | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

表 5-1. ピン属性 (ANF パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]<br>PADCONFIG レジスタ [15]<br>PADCONFIG アドレス [16] | 信号名 [3]        | 多重化モード [4] | タイプ [5] | DSIS [6] | リセット時のポールの状態 (RX/TX/PULL) [7] | リセット後のポールの状態 (RX/TX/PULL) [8] | リセット後の多重化モード [9] | I/O動作電圧 [10] | 電源 [11] | HYS [12] | パッファタイプ [13] | ブルアップ/ダウンタイプ [14] |

|-----------|--------------------------------------------------------|----------------|------------|---------|----------|-------------------------------|-------------------------------|------------------|--------------|---------|----------|--------------|-------------------|

| W19       | GPIO0_58<br>PADCONFIG: PADCONFIG59<br>0x000F40EC       | GPIO0_A13      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART5_CTSn     | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_58       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| Y21       | GPIO0_59<br>PADCONFIG: PADCONFIG60<br>0x000F40F0       | GPIO0_A14      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART4_RTSn     | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_59       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| Y22       | GPIO0_60<br>PADCONFIG: PADCONFIG61<br>0x000F40F4       | GPIO0_A15      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART4_CTSn     | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_60       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| T18       | GPIO0_61<br>PADCONFIG: PADCONFIG62<br>0x000F40F8       | GPIO0_A16      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART3_RTSn     | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_61       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| U17       | GPIO0_62<br>PADCONFIG: PADCONFIG63<br>0x000F40FC       | GPIO0_A17      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART3_CTSn     | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_62       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| V17       | GPIO0_63<br>PADCONFIG: PADCONFIG64<br>0x000F4100       | GPIO0_A18      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART2_RTSn     | 4          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_63       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| AA22      | GPIO0_64<br>PADCONFIG: PADCONFIG65<br>0x000F4104       | GPIO0_A19      | 1          | OZ      |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | UART2_CTSn     | 4          | I       | 1        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_64       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| L18       | GPMC0_ADVn_ALE<br>PADCONFIG: PADCONFIG33<br>0x000F4084 | GPMC0_ADVn_ALE | 0          | O       |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | MCASP1_AXR2    | 2          | IO      | 0        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | TRC_DATA7      | 6          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_32       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| N22       | GPMC0_CLK<br>PADCONFIG: PADCONFIG31<br>0x000F407C      | GPMC0_CLK      | 0          | O       |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | MCASP1_AXR3    | 2          | IO      | 0        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPMC0_FCLK_MUX | 3          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | TRC_DATA6      | 6          | O       |          |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | GPIO0_31       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |

| K18       | GPMC0_DIR<br>PADCONFIG: PADCONFIG41<br>0x000F40A4      | GPMC0_DIR      | 0          | O       |          | オフ / オフ / オフ                  | オフ / オフ / オフ                  | 7                | 1.8V/3.3V    | VDDSHV3 | あり       | LVC MOS      | PU/PD             |

|           |                                                        | MCASP2_AXR13   | 3          | IO      | 0        |                               |                               |                  |              |         |          |              |                   |

|           |                                                        | TRC_DATA14     | 6          | O       |          |                               |                               |                  |              |         |          |              |                   |

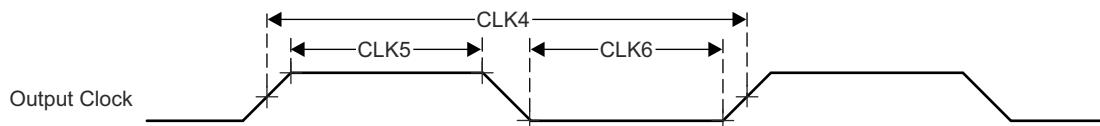

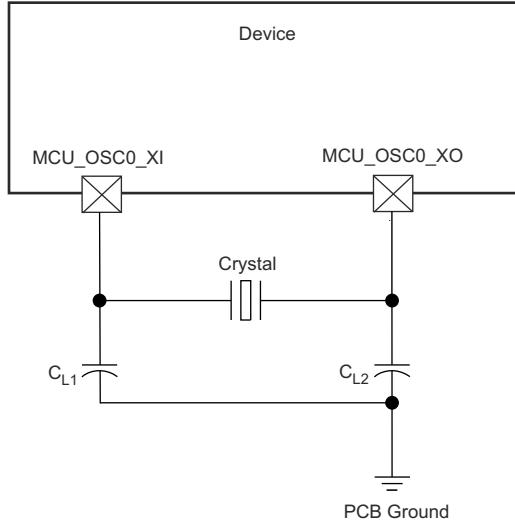

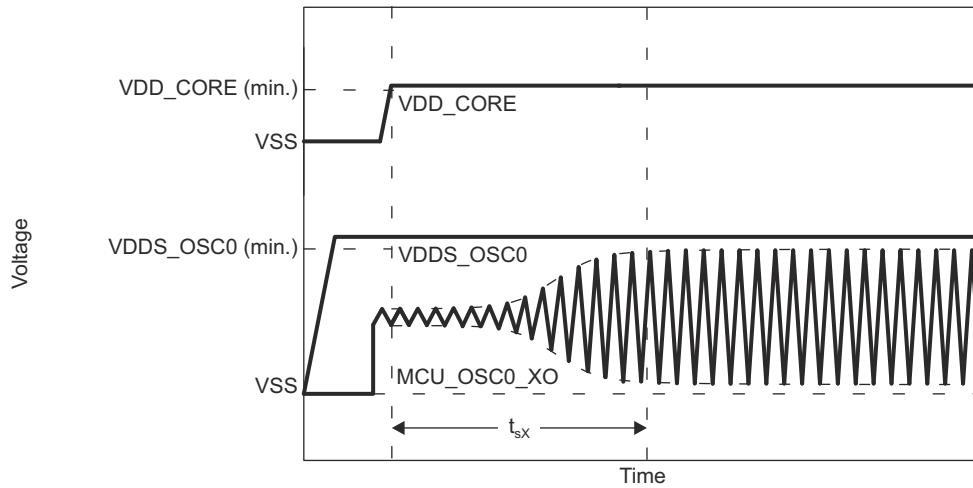

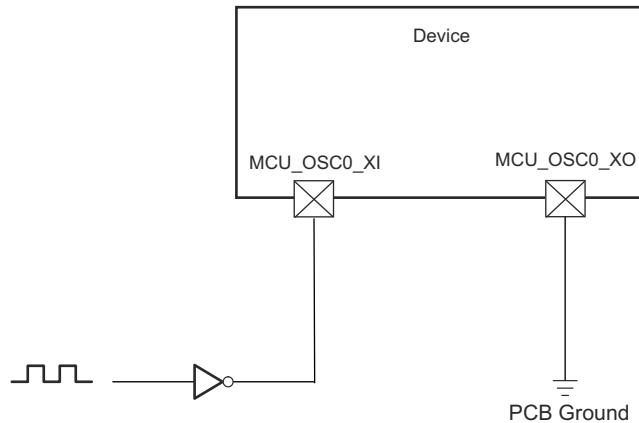

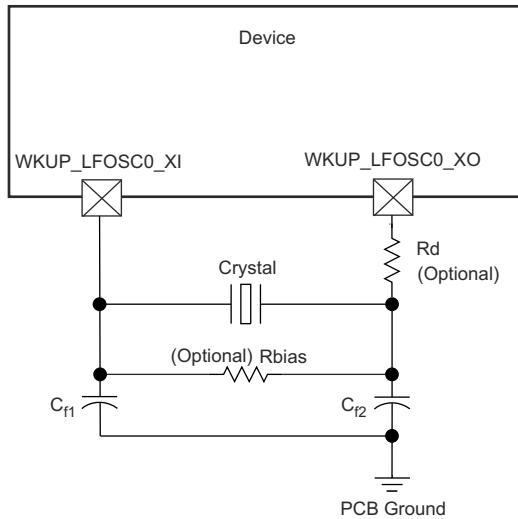

|           |                                                        | GPIO0_40       | 7          | IO      | パッド      |                               |                               |                  |              |         |          |              |                   |