## リアルタイム制御機能搭載 AM263x Sitara™ マイコン

### 1 特長

#### プロセッサ コア:

- シングル、デュアル、クワッド コアの Arm® Cortex®-R5F MCU、各コアは最大 400MHz で動作

- 16KB I キャッシュ、64 ビット ECC サポート (各 CPU コア)

- 16KB D キャッシュ、32 ビット ECC サポート (各 CPU コア)

- 64KB 密結合メモリ (TCM)、32 ビット ECC サポート (各 CPU コア)

- ロックステップまたはデュアルコア対応クラスタ

#### メモリ サブシステム:

- 2MB のオンチップ RAM (OCSRAM)

- 4 バンク x 512KB

- ECC エラー保護

- 内部 DMA エンジン サポート

#### システム オン チップ (SoC) サービスおよびアーキテクチャ:

- 1 個の EDMA、データ移動機能をサポート

- 以下のインターフェイスからのデバイス ブートをサポート:

- UART (プライマリ / バックアップ)

- QSPI NOR フラッシュ (4S/1S) (プライマリ)

- プロセッサ間通信モジュール

- 複数のコアで動作するプロセス同期用の SPINLOCK モジュール

- CTRLMMR レジスタに MAILBOX 機能を実装

- 時間同期および比較イベント割り込みルータによる中央プラットフォーム時間同期 (CPTS) サポート

#### メディアおよびデータ ストレージ:

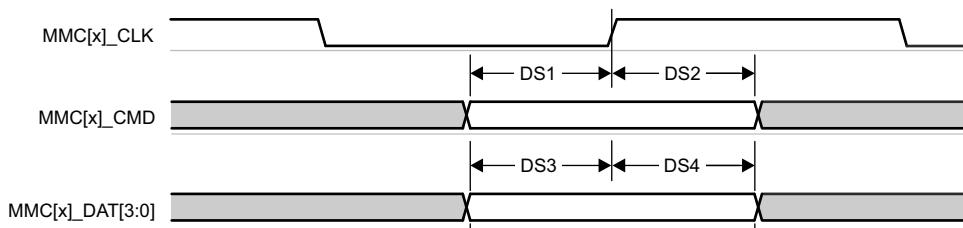

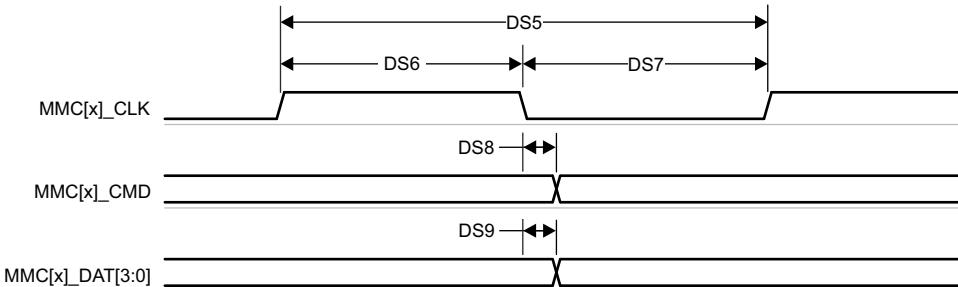

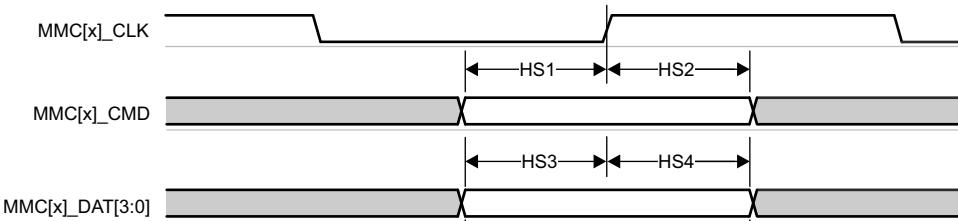

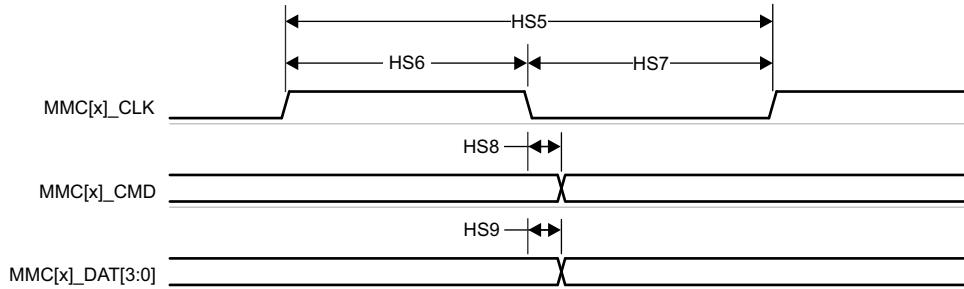

- 1 個の 4 ビットマルチメディア カード / セキュア デジタル (MMC/SD) インターフェイス

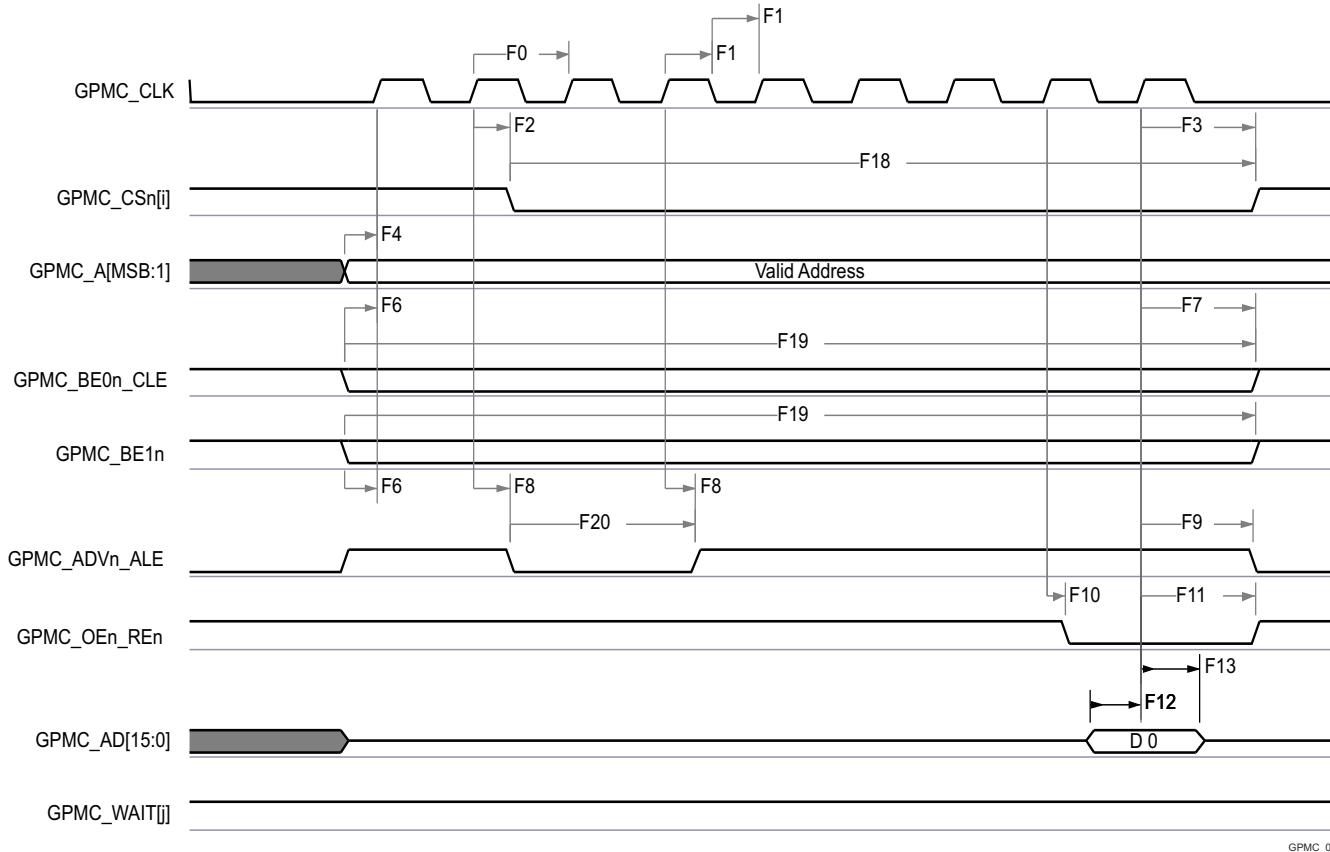

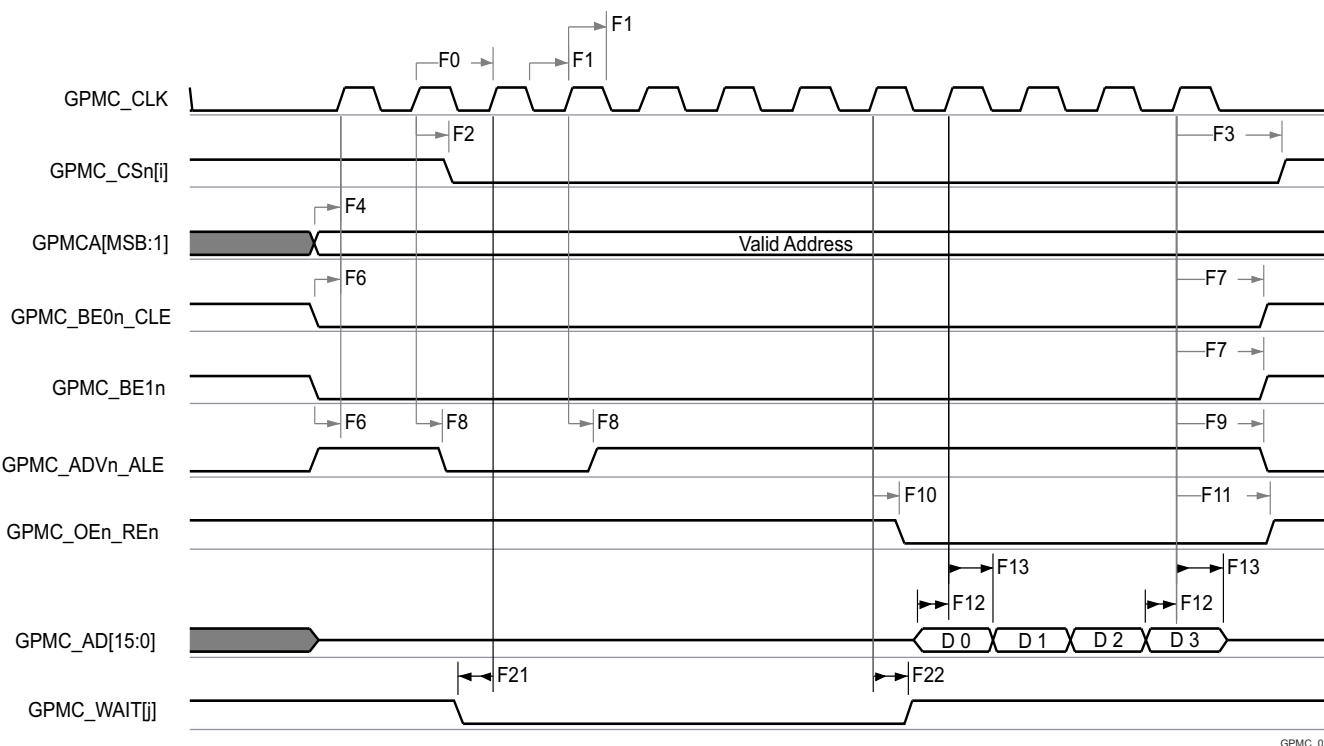

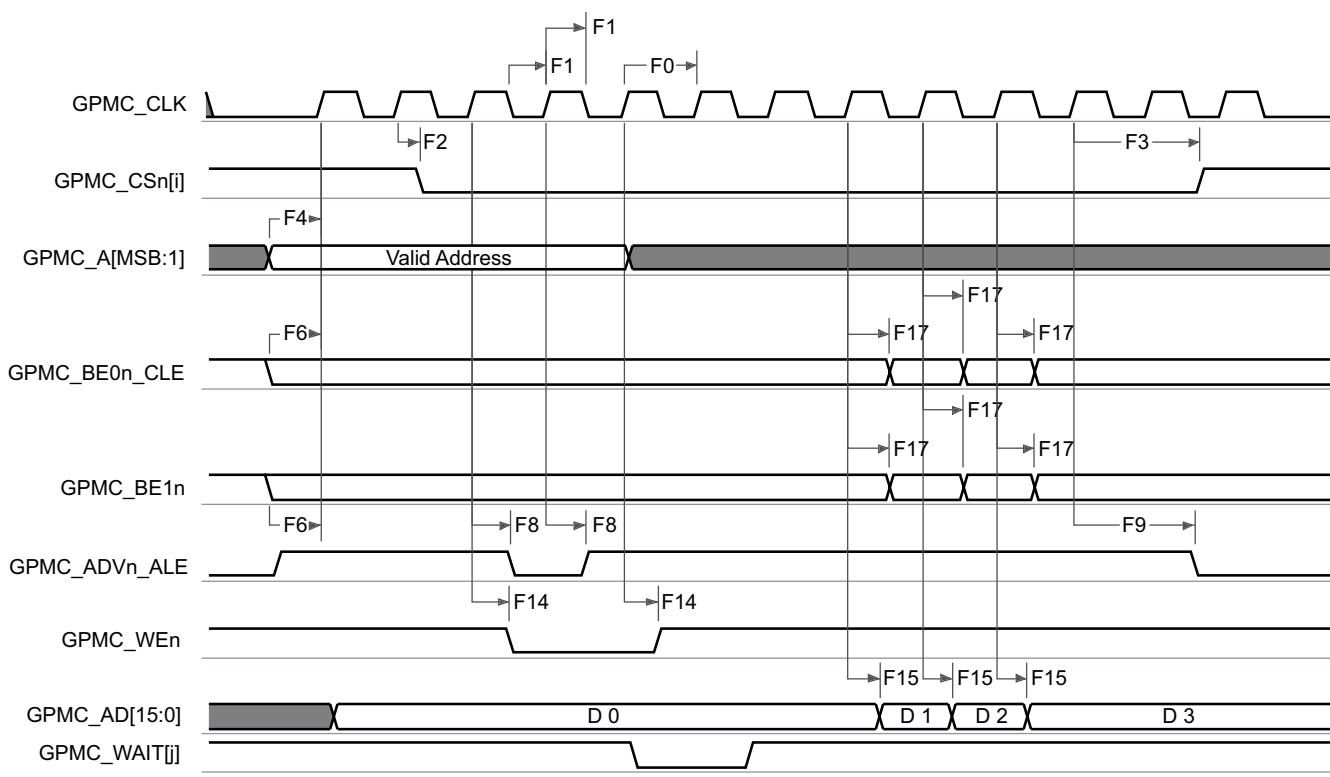

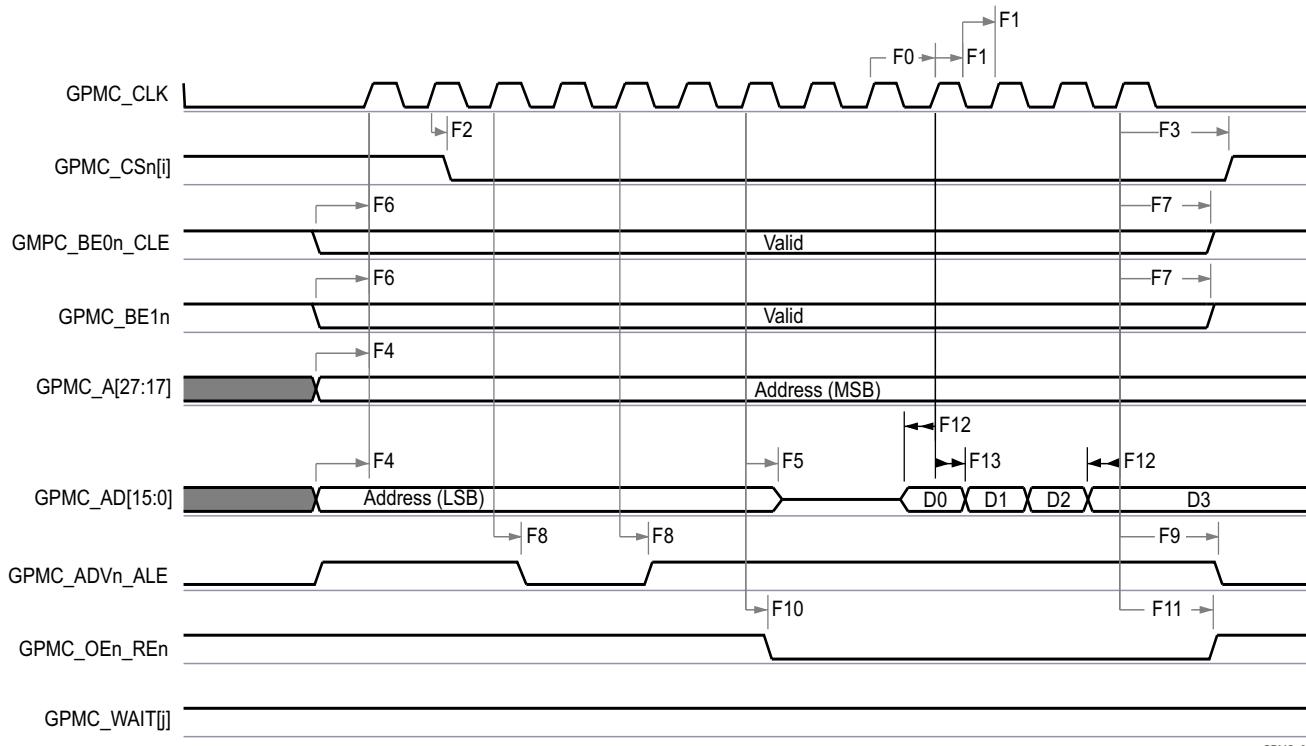

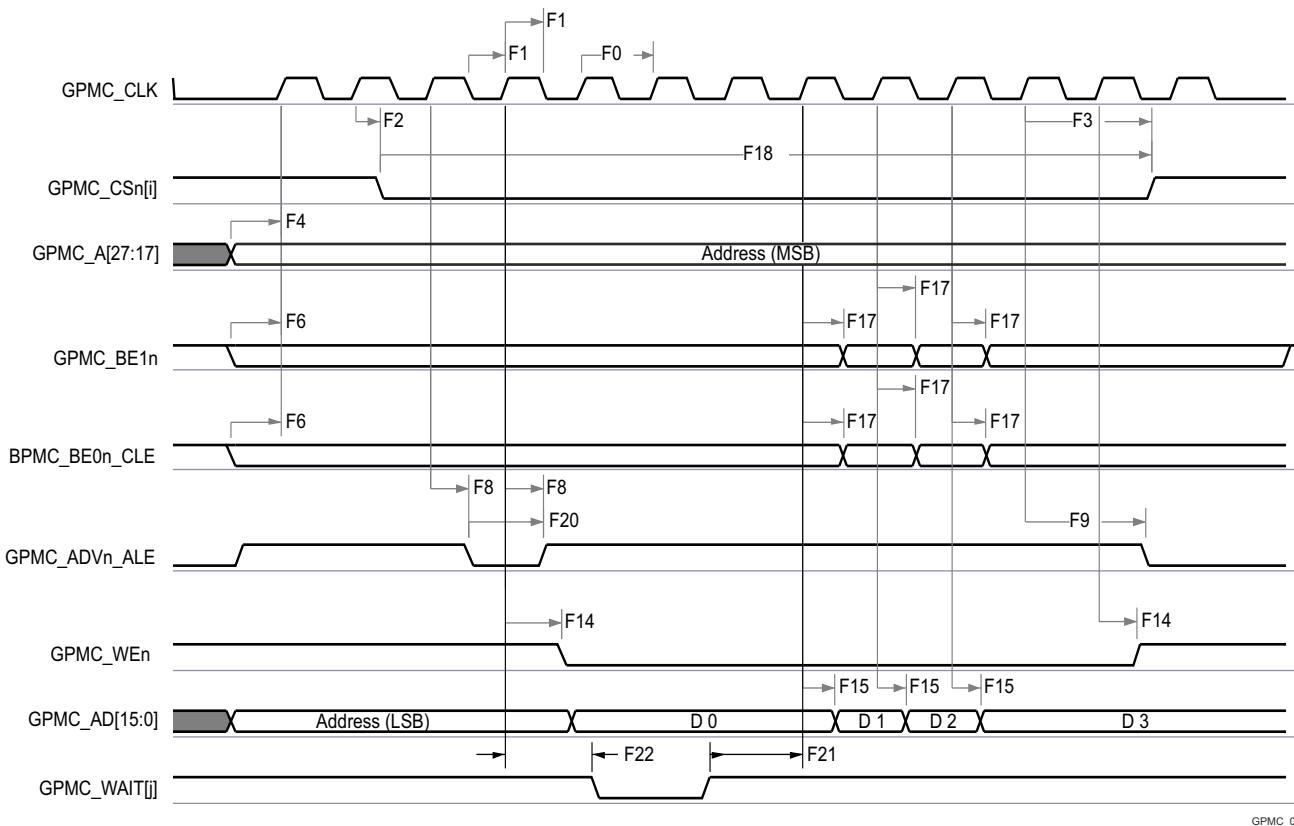

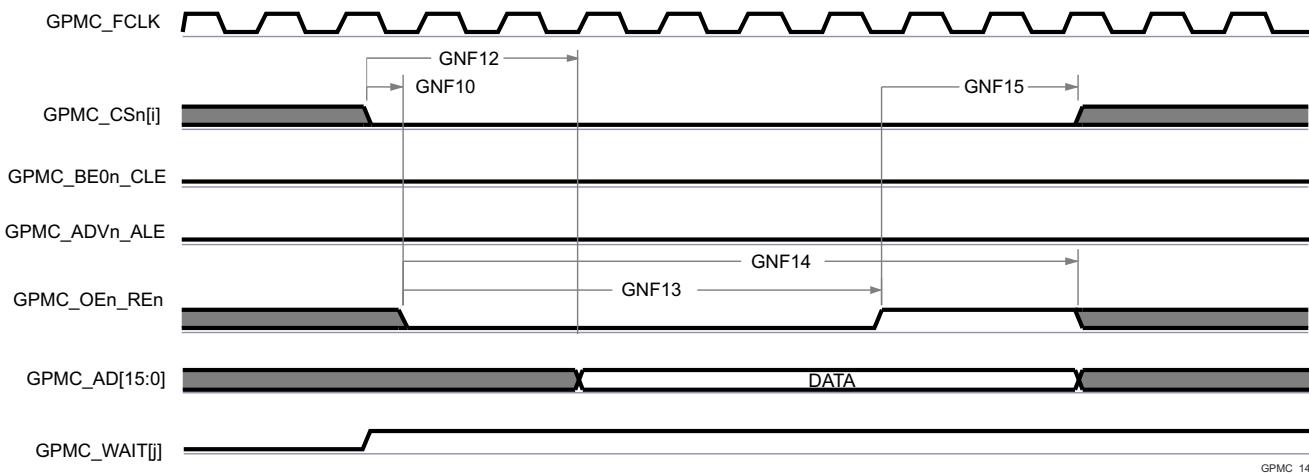

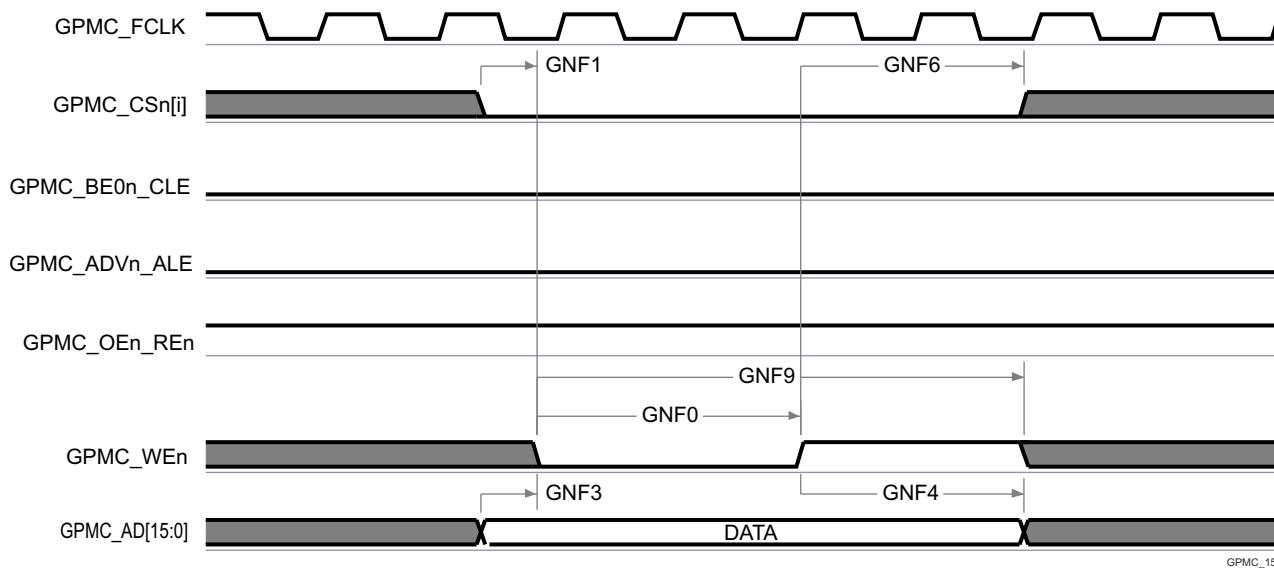

- 汎用メモリ コントローラ (GPMC)

- 22 ビットのアドレス バスを持つ 16 ビットのパラレル データ バス

- 最大 4MB のアドレス可能なメモリ空間

- エラー チェック用の内蔵エラー特定モジュール (ELM) 対応

#### 一般的な接続機能:

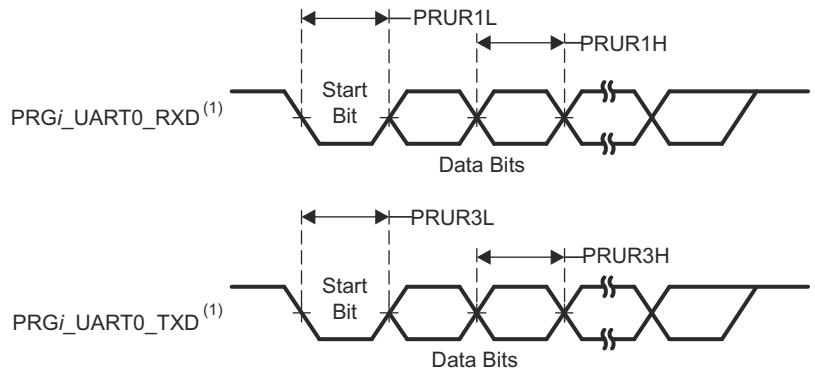

- 6 個のユニバーサル非同期 RX-TX (UART)

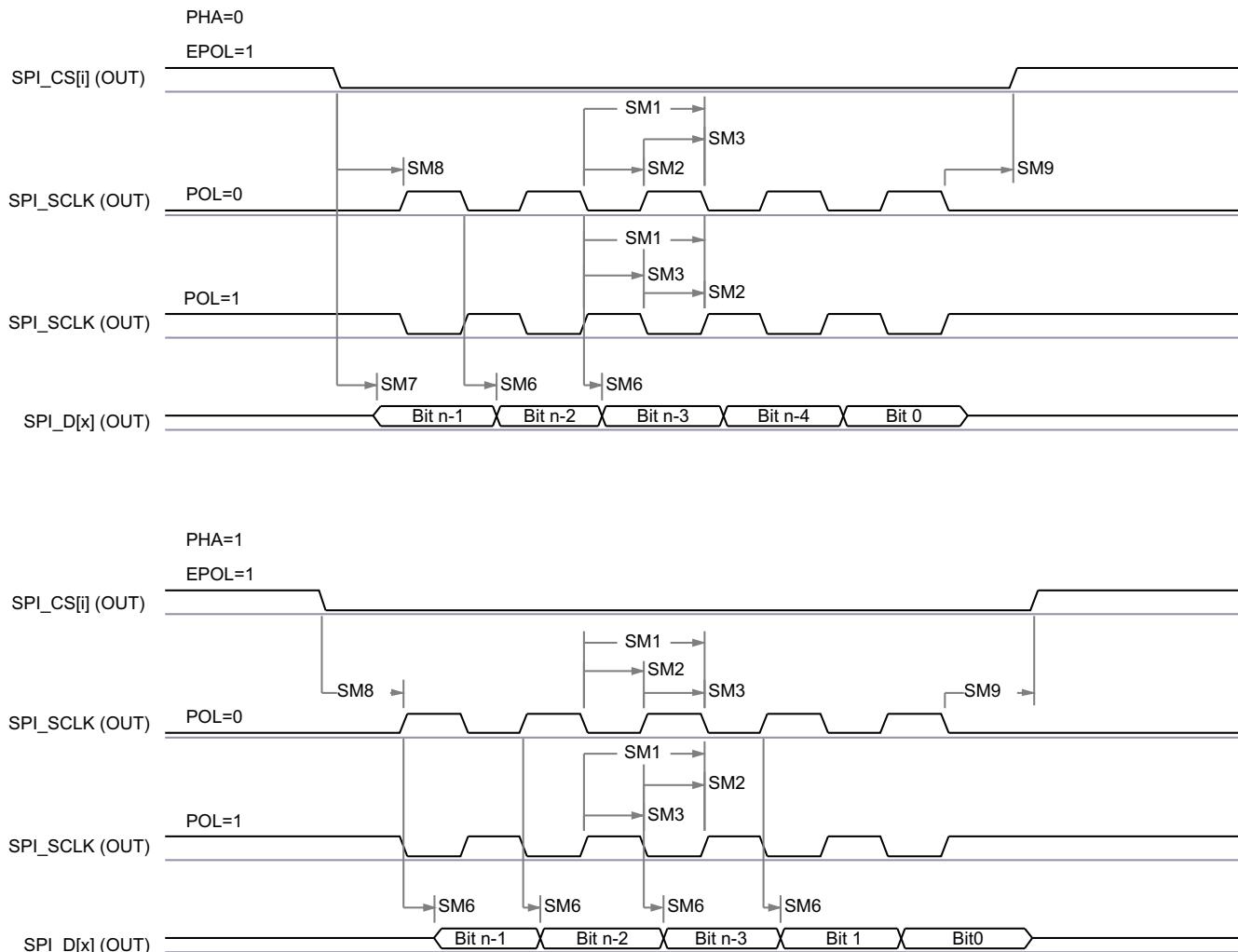

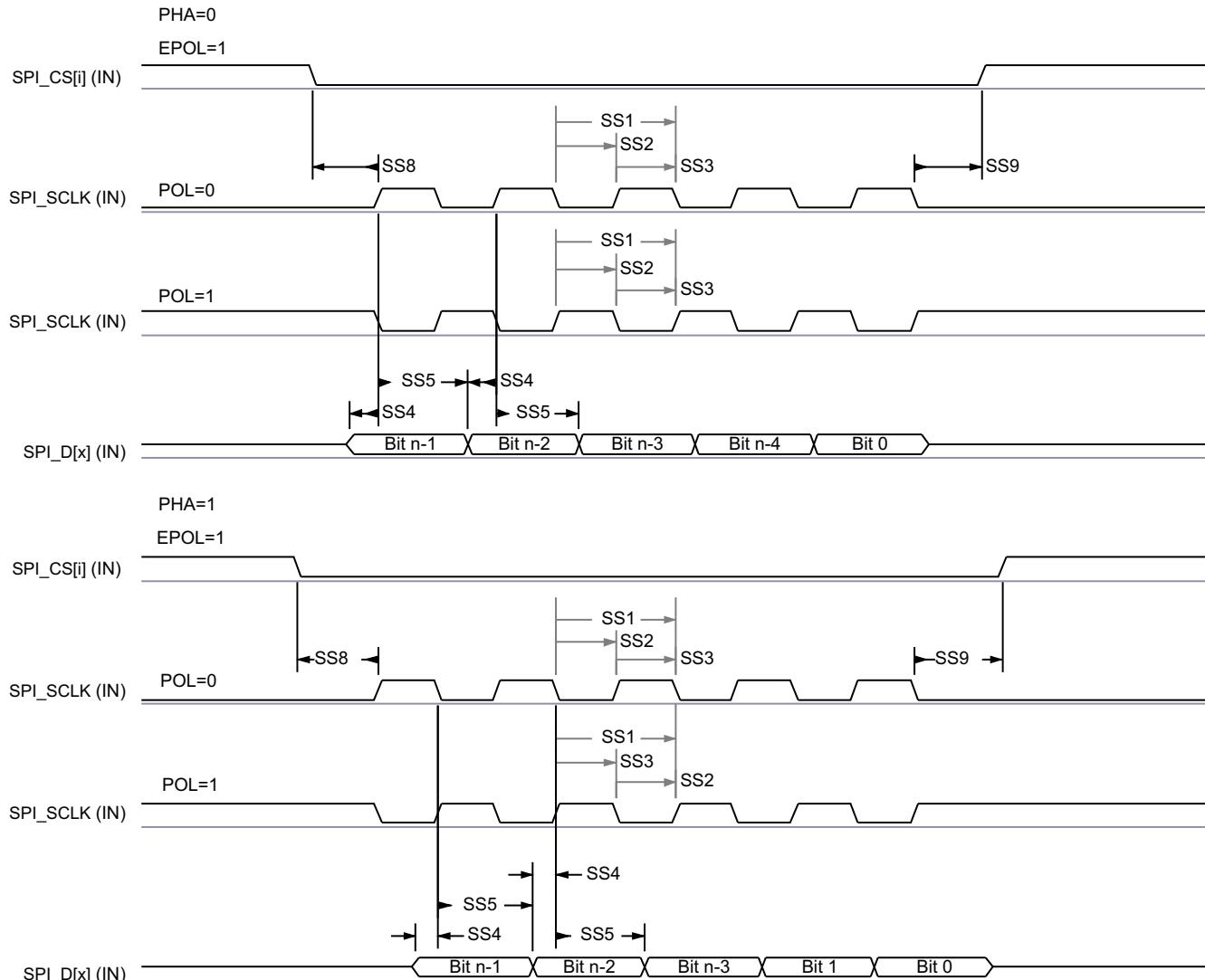

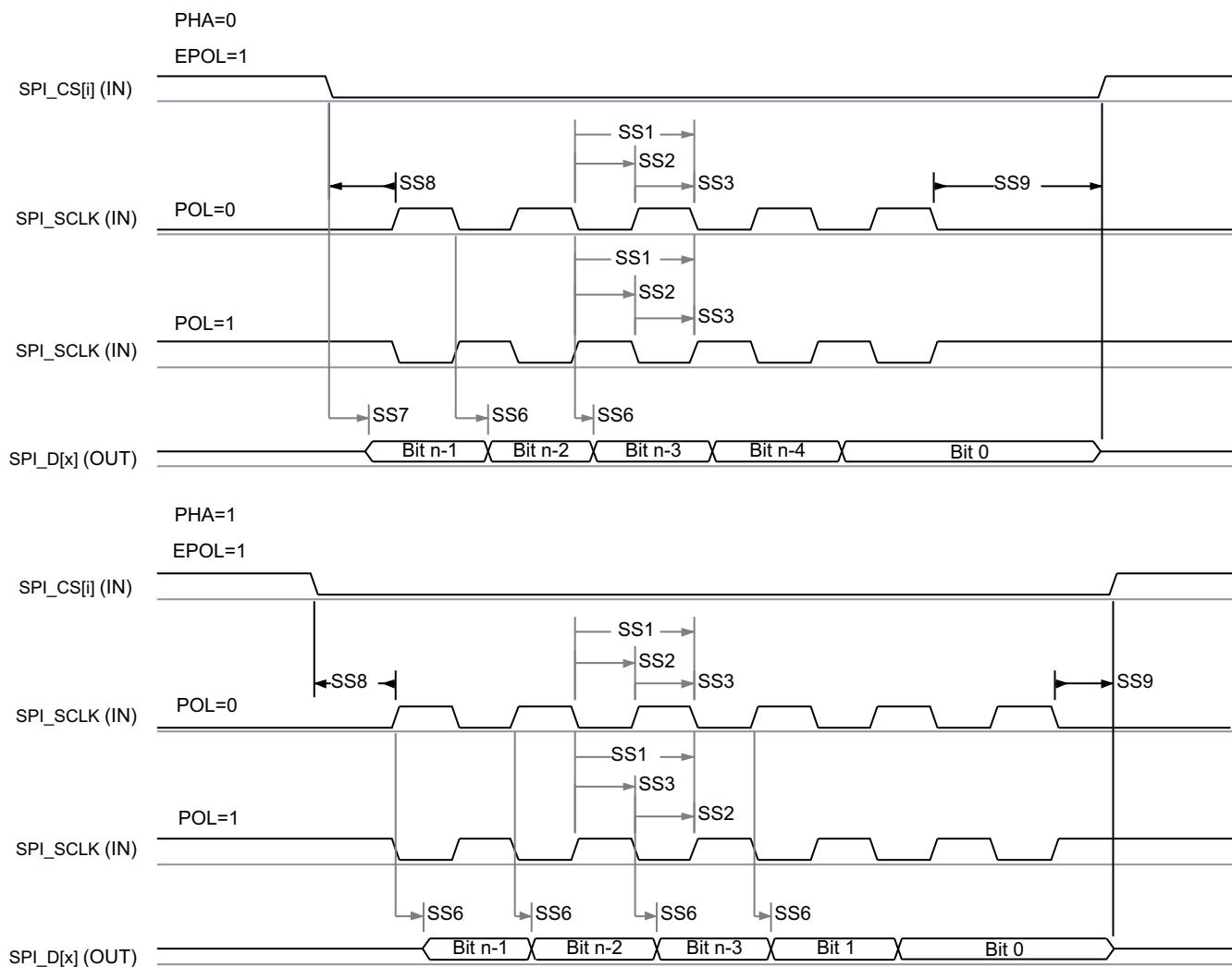

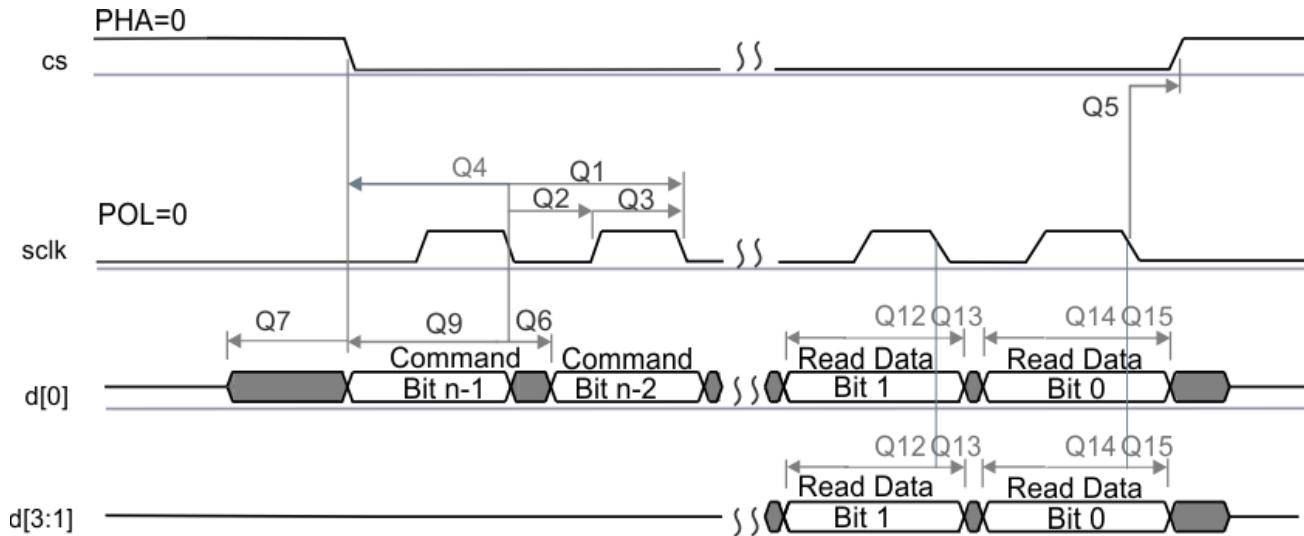

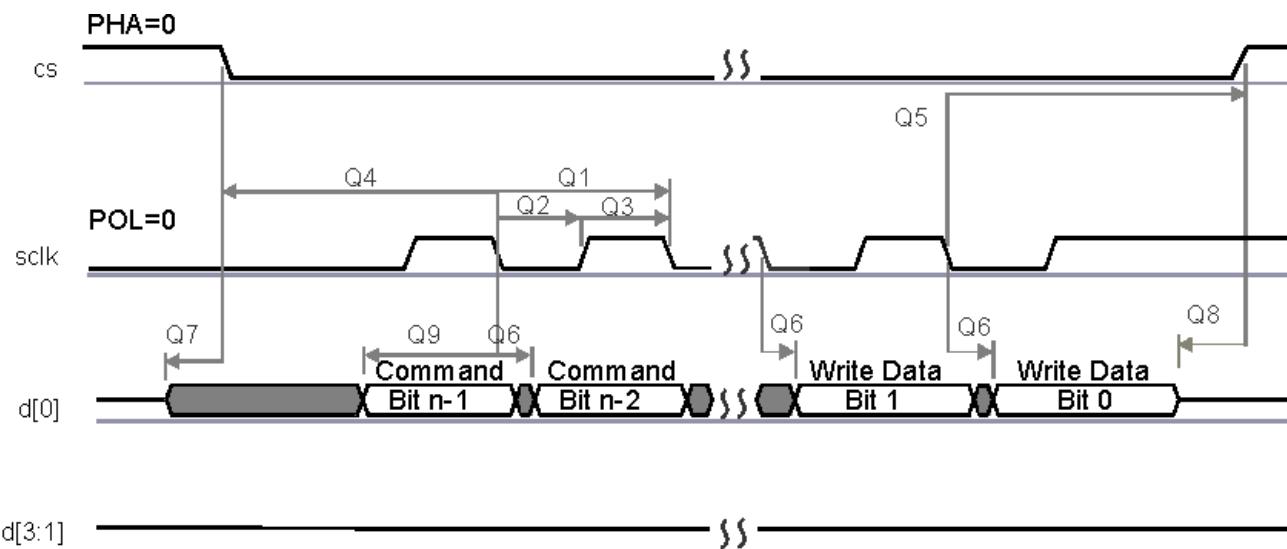

- 5 個のシリアル ペリフェラル インターフェイス (SPI) コントローラ

- 5 個の LIN (Local Interconnect Network) ポート

- 4 個の I2C (Inter-Integrated Circuit) ポート

- 4 個のモジュラー コントローラ エリア ネットワーク (MCAN) モジュール、CAN-FD をサポート

- 1 個のクワッドシリアル ペリフェラル インターフェイス (QSPI)

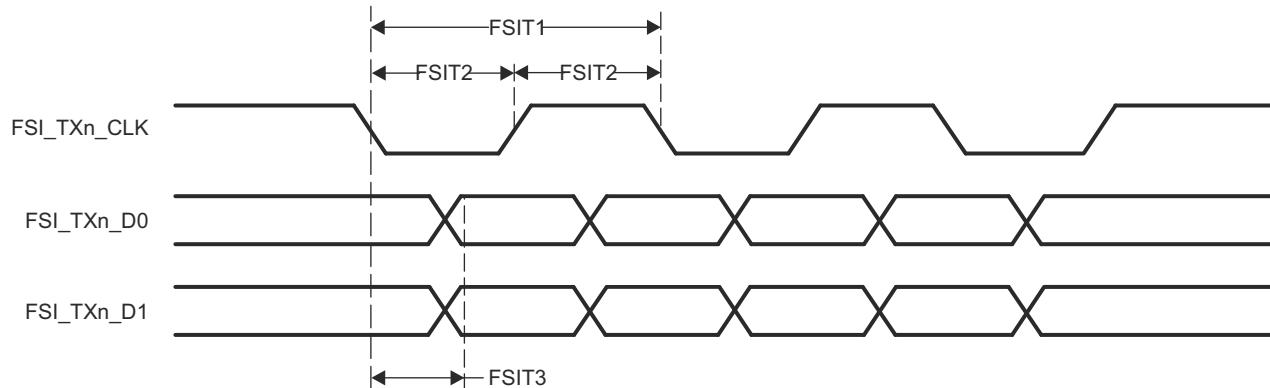

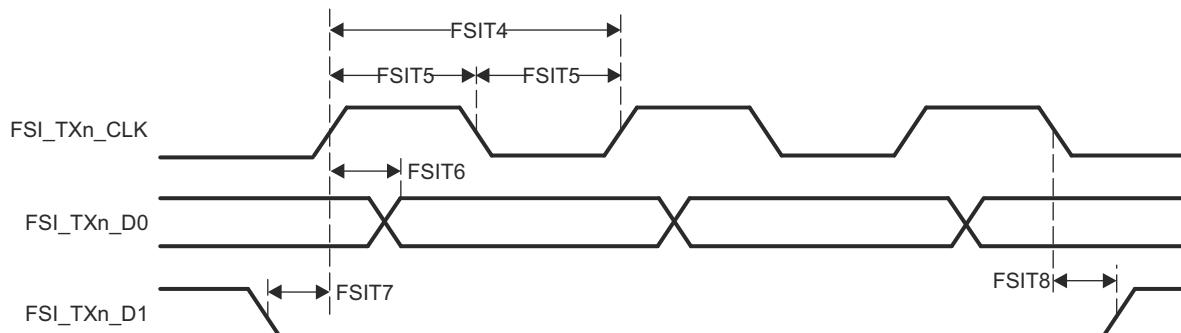

- 4 個の高速シリアル インターフェイス トランスマッタ (FSITX)

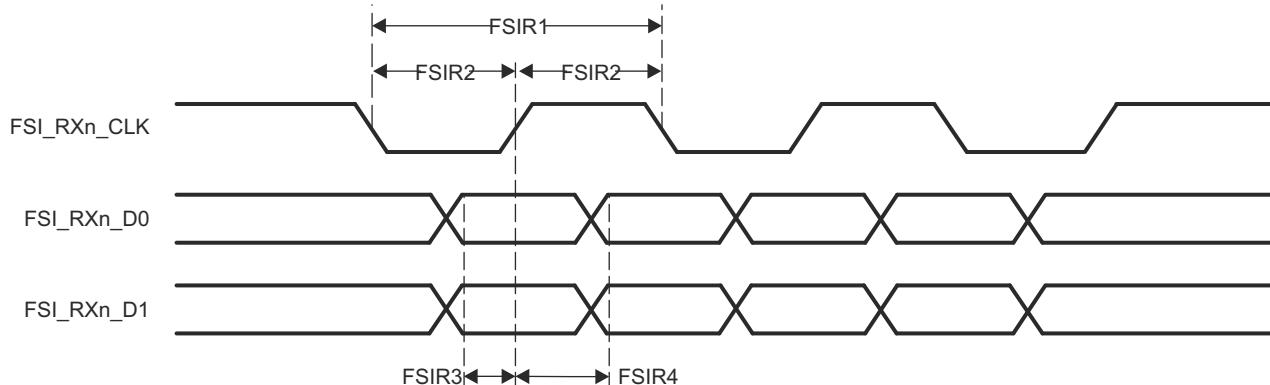

- 4 個の高速シリアル インターフェイス レシーバ (FSIRX)

- 最大 139 の汎用 I/O (GPIO) ピン

#### センシングと作動:

- リアルタイム制御サブシステム (CONTROLSS)

- フレキシブルな入出力クロスバー (XBAR)

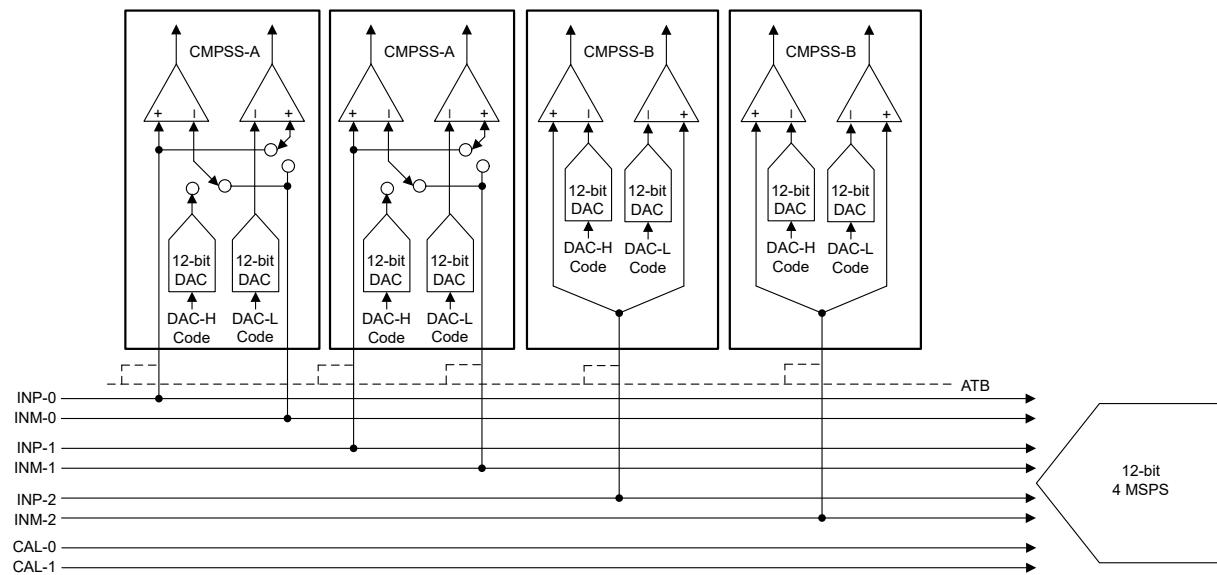

- 5 個の 12 ビット A/D コンバータ (ADC)

- 6 入力 SAR ADC、最大 4MSPS

- 6 個のシングルエンド チャネルまたは

- 3 個の差動チャネル

- 高度に構成可能な ADC デジタル ロジック

- XBAR 変換開始トリガ (SOC)

- ユーザー定義のサンプル / ホールド (S+H)

- フレキシブルな後処理ブロック (PPB)

- 10 個のアナログ コンバータ、タイプ A プログラマブル DAC リファレンス (CMPSS) 付き

- 10 個のアナログ コンバータ、タイプ B プログラマブル DAC リファレンス (CMPSS) 付き

- 1 個の 12 ビット D/A コンバータ (DAC)

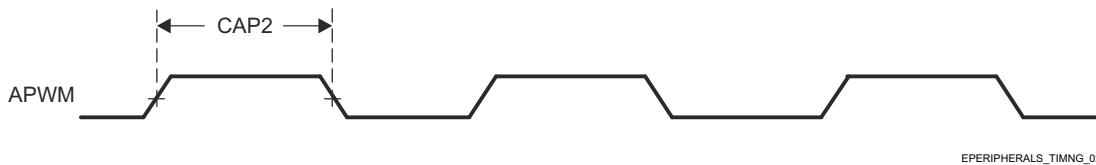

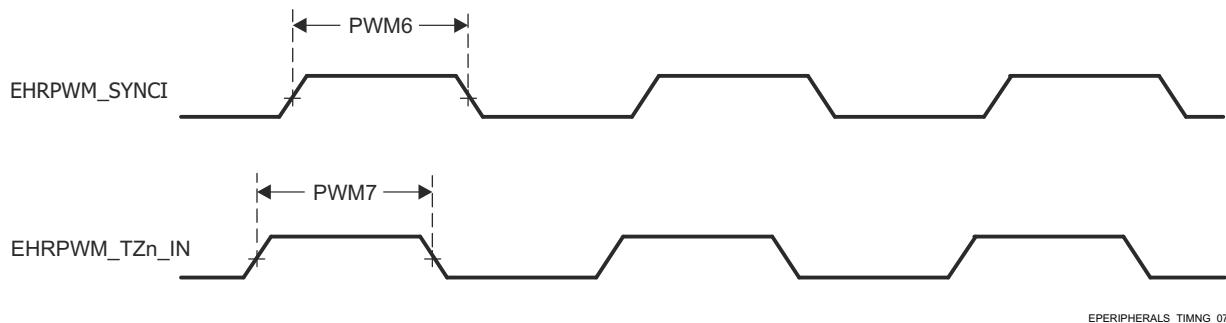

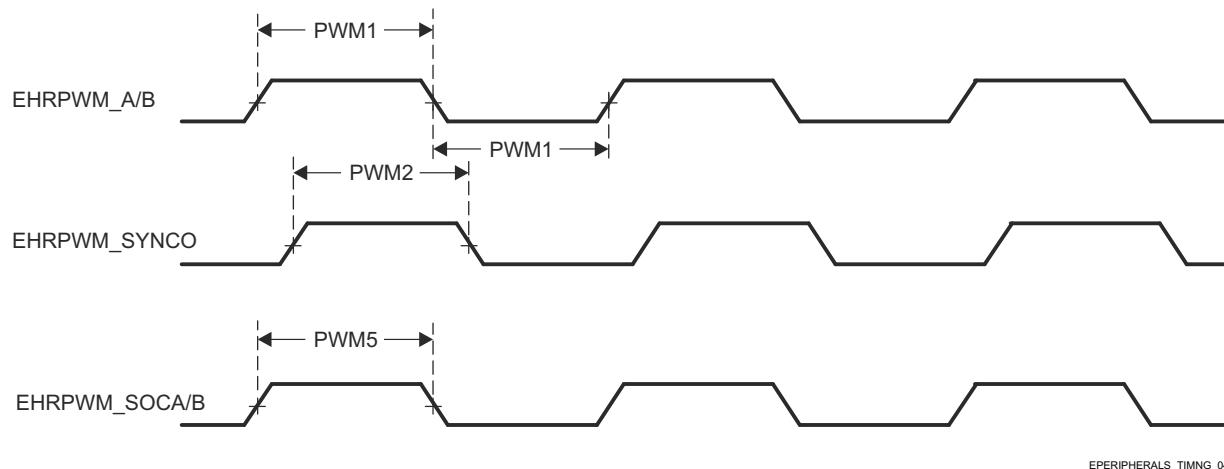

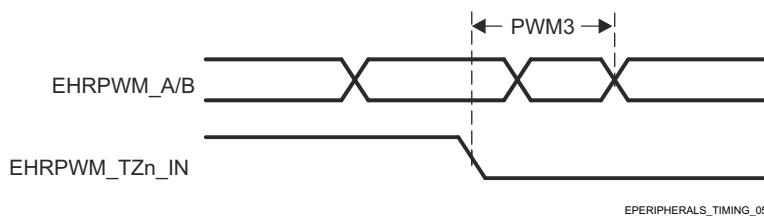

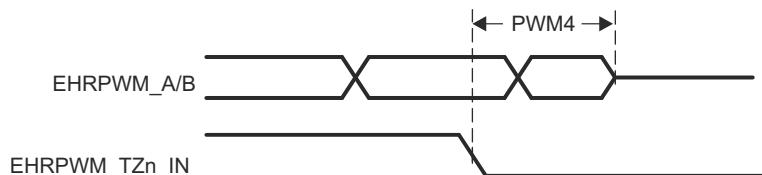

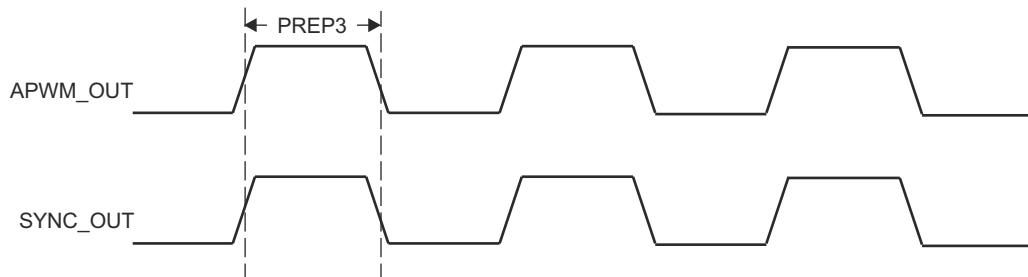

- 32 個のパルス幅変調 (EPWM) モジュール

- シングルまたはデュアル PWM チャンネル

- 高度な PWM 構成

- 拡張された HRPWM 時間分解能

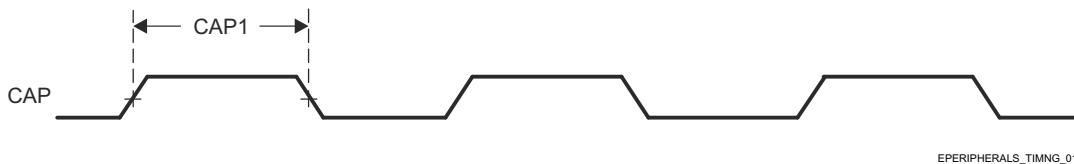

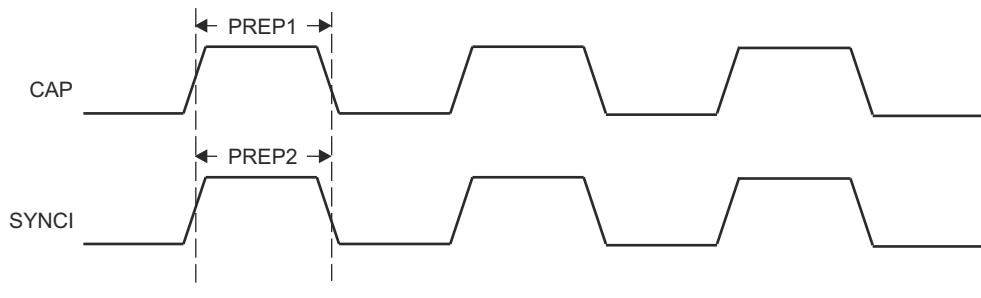

- 10 個の拡張キャプチャ (ECAP) モジュール

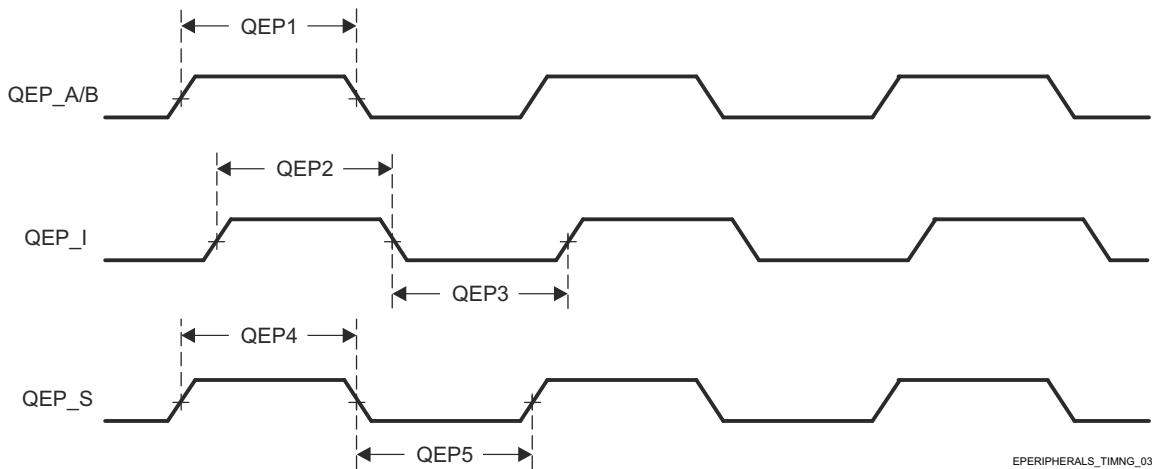

- 3 個の拡張直交エンコーダ パルス (EQEP) モジュール

- 2 個の 4 チャネル シグマ デルタ フィルタ モジュール (SDFM)

- 追加の信号多重化クロスバー (XBAR)

#### 産業用コネクティビティ:

- プログラマブル リアルタイム ユニット (PRU-SS) および PRU 産業用通信サブシステム (PRU-ICSS)

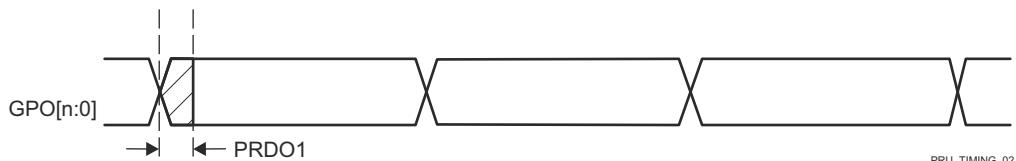

- デュアルコア プログラマブル リアルタイム ユニット サブシステム (PRU0/PRU1)

- 確定的なハードウェア

- 動的ファームウェア

- 20 チャネル拡張入力 (eGPI) (各 PRU)

- 20 チャネル拡張出力 (eGPO) (各 PRU)

- 組込みペリフェラル およびメモリ

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

- 1 個の UART、1 個の ECAP

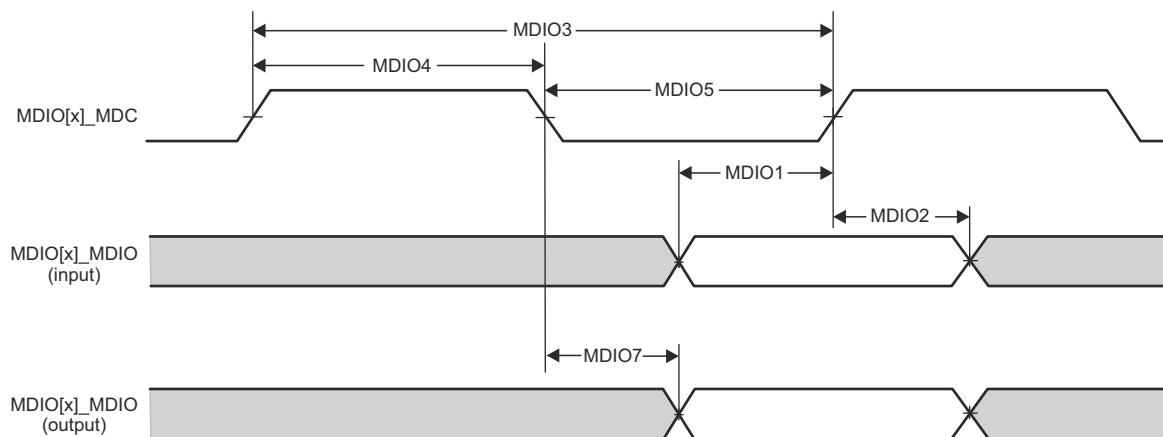

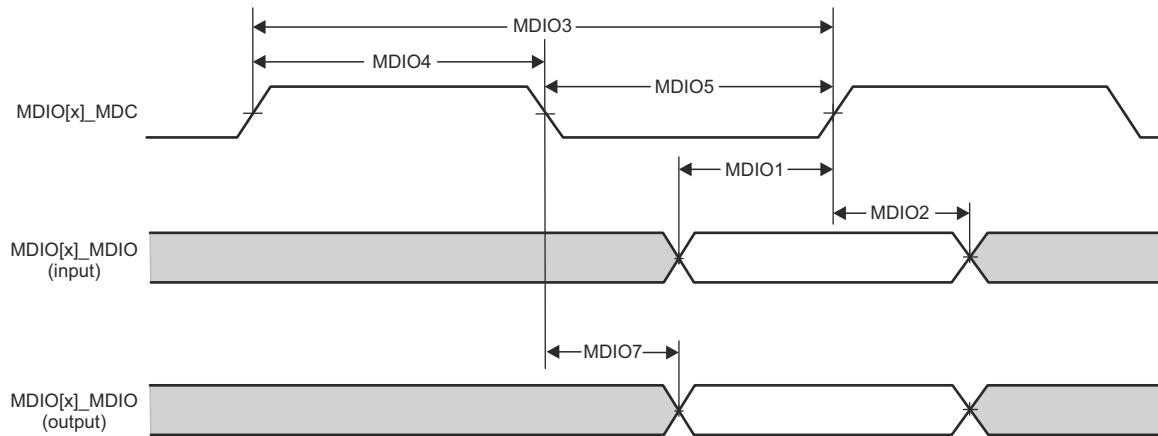

- 1 個の MDIO、1 個の IEP、

- 1 個の 32KB 共有汎用 RAM

- 2 個の 8KB 共有データ RAM

- 1 個の 16KB IRAM (各 PRU)

- スクラッチパッド (SPAD)、MAC/CRC

- デジタル エンコーダおよびシグマ-デルタ制御ループ

- PRU-ICSS は、次に示す高度な産業用プロトコルを可能にします。

- EtherCAT®、EtherNet/IP™、

- PROFINET®、IO-Link® がオーダー可能

- 専用割り込みコントローラ (INTC)

- 動的な CONTROLSS XBAR 統合

#### 高速インターフェイス:

- 2 つの外部ポートをサポートする統合型イーサネットスイッチ

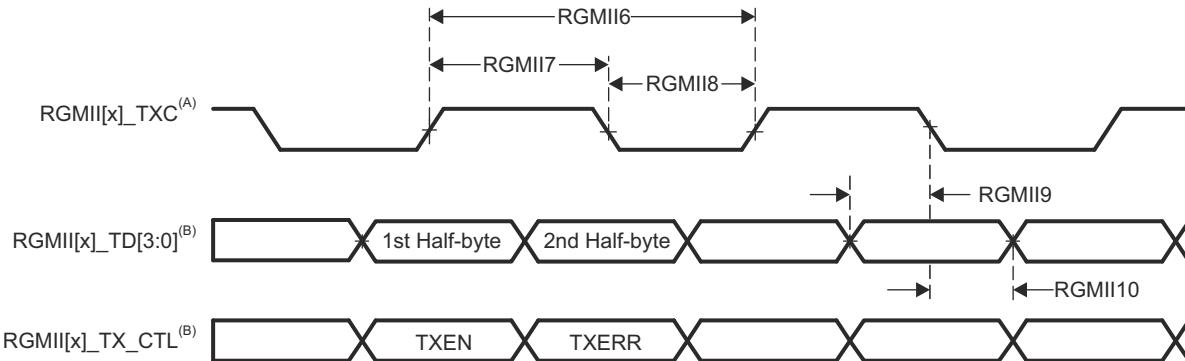

- MII (10/100)、RMII (10/100)、または RGMII (10/100/1000)

- IEEE 1588 (2008 Annex D, Annex E, Annex F) と 802.1AS PTP

- Clause 45 MDIO PHY 管理

- 512 個の ALE エンジンベースのパケットクラシファイア

- 最大 2KB のパケット サイズに対応する優先フロー制御

- 4 つの CPU ハードウェア割り込みベース設定

- ハードウェアの IP/UDP/TCP チェックサム オフロード

#### セキュリティ:

- ハードウェア セキュリティ モジュール (HSM)、Auto SHE 1.1/EVITA 対応

- セキュアブート対応

- デバイス ティク オーバー保護

- ハードウェアによる信頼の基点

- 認証済みブート

- SW アンチロールバック保護

- デバッグ セキュリティ

- 正規の認証完了後のみセキュアなデバイス デバッグを実行

- デバイス デバッグ機能を無効にする機能

- デバイス ID とキー管理

- OTP メモリ (FUSEROM) のサポート

- ルートキーとその他のセキュリティ フィールドを格納

- 個別の EFUSE コントローラと FUSE ROM

- 一意の公開デバイス識別子 (UID)

- メモリ保護ユニット (MPU)

- Cortex® R5F コアごとの専用 Arm® MPU

- システム MPU - SoC 内の各種インターフェイスに存在 (MPU またはファイアウォール)

- 8~16 のプログラム可能領域

- イネーブル / 特権 ID

- 開始 / 終了アドレス

- 読み取り / 書き込み / キャッシュ可能

- セキュア / ノンセキュア

- 暗号化アクセラレーション機能

- DMA サポート付きの暗号化コア

- AES - 128/192/256 ビットのキー サイズ

- SHA2 - 256/384/512 ビットのサポート

- DRBG、擬似および真性乱数発生器搭載

- PKA (公開鍵アクセラレータ) により RSA/ECC 処理を支援

#### 機能安全:

- 機能安全要件を満たすシステムの設計の実現

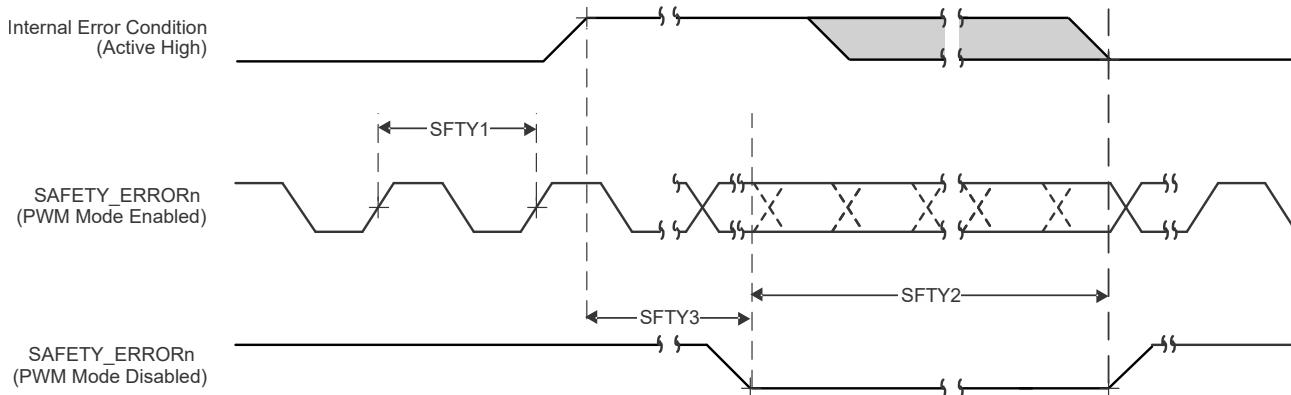

- エラーシグナリング モジュール (ESM)、SAFETY\_ERRORn ピン指定付き

- 演算上特に重要なメモリの ECC またはパリティ

- CPU とオンチップ RAM のための内蔵セルフテスト (BIST) とフォルト インジェクション

- 電圧 / 温度 / クロックの監視、ウインドウ付きウォッチドッグ タイマ、CRC エンジンを搭載したランタイム内部診断モジュールによるメモリ整合性チェック

- **機能安全準拠** [産業用]

- 機能安全アプリケーション向けに開発

- IEC 61508 機能安全システム設計を支援するドキュメントを準備中

- SIL-3 までの体系的対応能力に対応

- SIL-3 までのハードウェア安全度に対応

- 安全関連の認証

- [TUV SUD により IEC 61508 認証済み \(SIL-3 まで\)](#)

- **機能安全準拠** [車載用]

- 機能安全アプリケーション向けに開発

- ISO 26262 機能安全システム設計を支援するドキュメントを準備中

- ASIL-D までの体系的対応能力に対応

- ASIL-D までのハードウェア安全度に対応

- 安全関連の認証

- [TUV SUD により ISO 26262 認証済み \(ASIL-D まで\)](#)

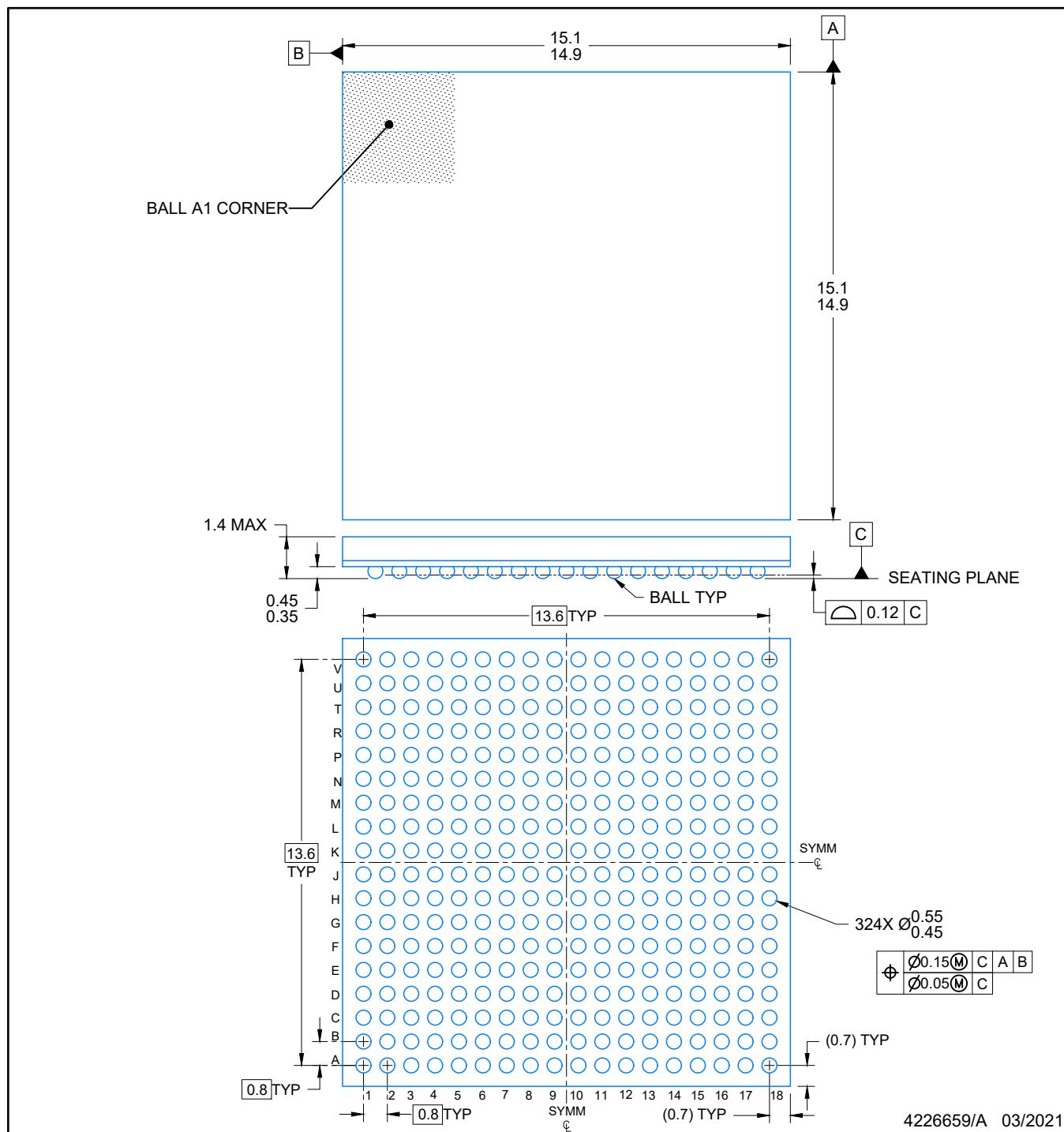

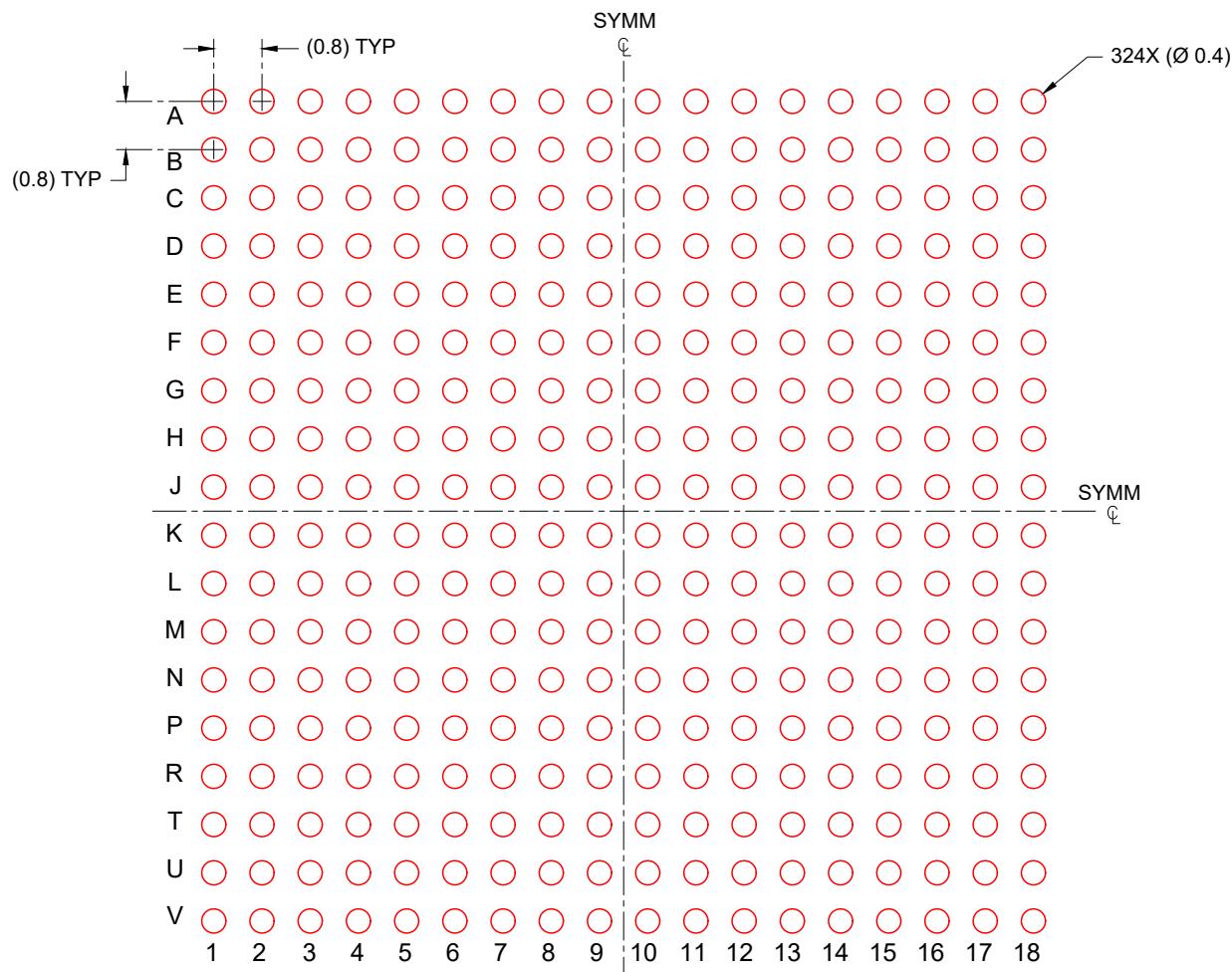

## テクノロジ / パッケージ:

- 車載アプリケーション向けに AEC-Q100 認証済み

- 45nm テクノロジ

- ZCZ パッケージ

- 324 ピン nFBGA

- 15.0mm × 15.0 mm

- 0.8mm ピッチ

## 2 アプリケーション

- 単軸と多軸のサーボ・ドライブ

- AC インバータと VF ドライブ

- ソーラー・エネルギー

- EV 充電

- 再生可能エネルギー・ストレージ

- トラクション・インバータ

- オンボード充電器

- DC/DC コンバータ

- バッテリ管理システム

- コンボ・ボックス・アキテクチャ

- IO アグリゲータ

- ドメイン・コントローラ

## 3 説明

AM263x Sitara™ Arm® マイクロコントローラは、次世代の産業用および車載用組込み製品の複雑なリアルタイム処理ニーズを満たすように構成されています。AM263x MCU ファミリは、最大 4 つの 400MHz Arm® Cortex®-R5F コアを搭載した複数のピン互換デバイスで構成されています。オプションとして、Arm® R5F サブシステムをプログラムして、ロックステップ モードまたはデュアル コア モードで複数の機能安全構成を実行することができます。産業用通信サブシステム (PRU-ICSS) を使用することで、PROFINET®、EtherNet/IP®、EtherCAT® (その他多数)、標準的なイーサネット接続、さらにカスタム I/O インターフェイスなどの産業用イーサネット通信プロトコルを統合できます。このファミリは、高度なアナログ センシング モジュールとデジタル アクチュエータ モジュールを搭載した、将来のモーター制御およびデジタル電源アプリケーション向けに設計されています。

複数の R5F コアをクラスタ サブシステムに配置し、256KB の共有密結合メモリ (TCM) と 2MB の共有 SRAM を備えているため、外部メモリの必要性が非常に小さくなっています。拡張 ECC をオンチップ メモリ、ペリフェラル、およびインターコネクトに備えることで、高度な信頼性を確保しています。ハードウェア セキュリティ マネージャ (HSM) が管理する粒度の細かいファイアウォールにより、開発者はセキュリティ重視のシステム設計要件を厳格に実装できます。AM263x デバイスでは、暗号化アクセラレーションとセキュア ブートも利用できます。

テキサス・インスツルメンツは、AM263x マイクロコントローラ ファミリのマイクロコントローラ ソフトウェアと開発ツール一式を提供します。

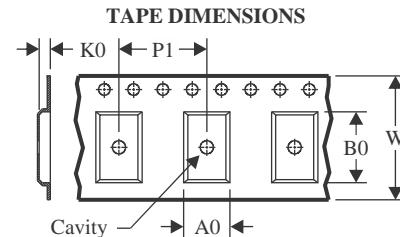

### パッケージ情報

| 部品番号 <sup>(1)</sup> (2) | パッケージ             | パッケージ サイズ <sup>(3)</sup> |

|-------------------------|-------------------|--------------------------|

| AM2634...ZCZ            | ZCZ (nFBGA、324)   | 15.0mm × 15.0mm          |

| AM2632...ZCZ            | ZCZ (nFBGA、324)   | 15.0mm × 15.0mm          |

| AM2631...ZCZ            | ZCZ (nFBGA、324)   | 15.0mm × 15.0mm          |

| AM2634...ZCZQ1          | ZCZQ1 (nFBGA、324) | 15.0mm × 15.0mm          |

| AM2632...ZCZQ1          | ZCZQ1 (nFBGA、324) | 15.0mm × 15.0mm          |

| AM2631...ZCZQ1          | ZCZQ1 (nFBGA、324) | 15.0mm × 15.0mm          |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) すべてのデバイスは、テープ アンド リールとトレイ両方のパッケージで供給されます。

(3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

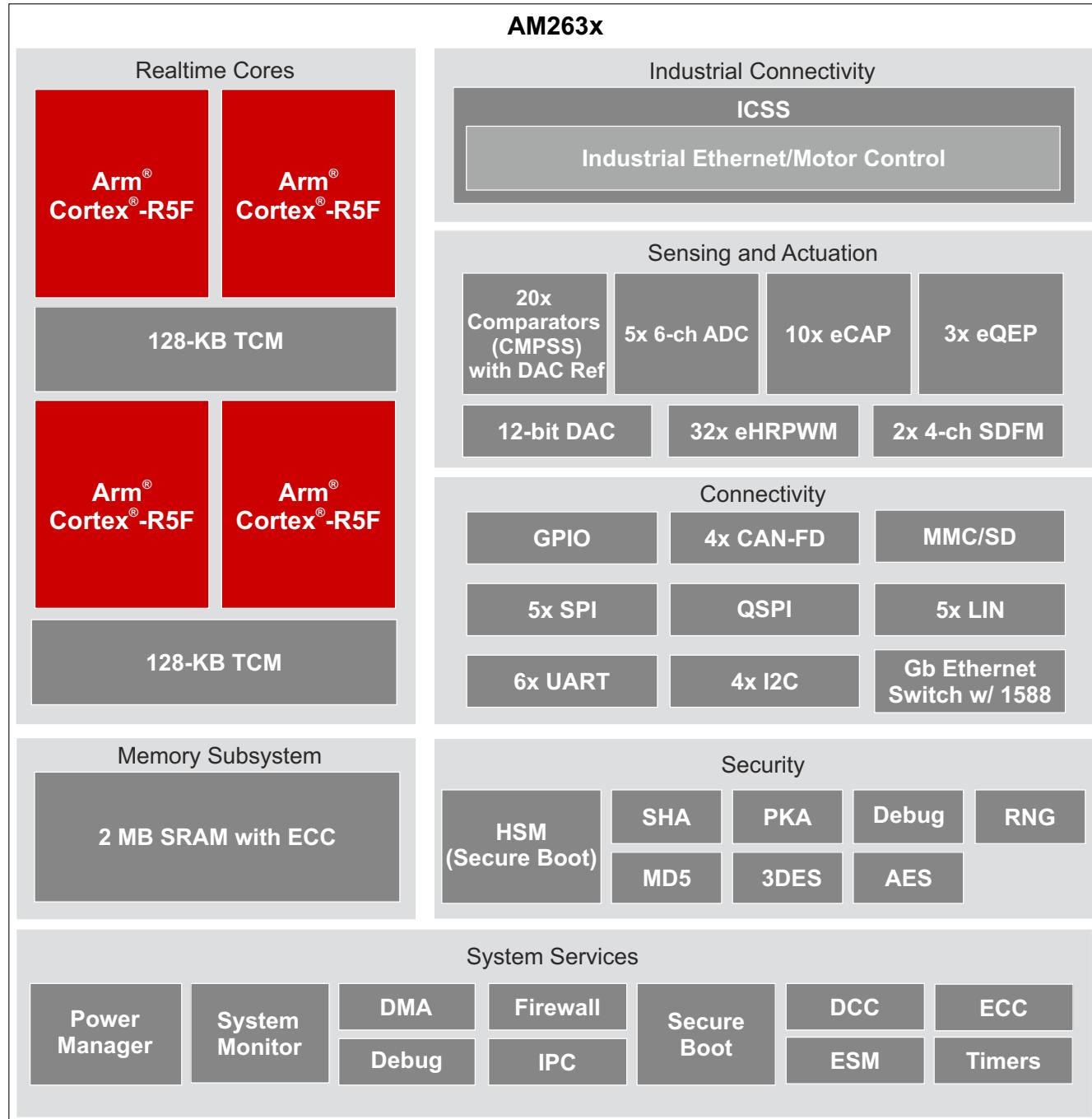

### 3.1 機能ブロック図

図 3-1 は、デバイスの機能ブロック図です。

図 3-1. 機能ブロック図

## 目次

|                        |    |                                       |     |

|------------------------|----|---------------------------------------|-----|

| 1 特長                   | 1  | 6.9 ワンタイムプログラマブル (OTP) eFuse の VPP 仕様 | 77  |

| 2 アプリケーション             | 3  | 6.10 熱抵抗特性                            | 78  |

| 3 説明                   | 3  | 6.11 タイミングおよびスイッチング特性                 | 79  |

| 3.1 機能ブロック図            | 4  | 6.12 デカップリング コンデンサの要件                 | 153 |

| 4 デバイスの比較              | 6  | 7 詳細説明                                | 155 |

| 4.1 関連製品               | 7  | 7.1 概要                                | 155 |

| 5 端子構成および機能            | 8  | 7.2 プロセッサ サブシステム                      | 156 |

| 5.1 ピンダイアグラム           | 8  | 8 アプリケーション、実装、およびレイアウト                | 157 |

| 5.2 ピン属性               | 9  | 8.1 デバイスの接続およびレイアウトの基礎                | 157 |

| 5.3 信号の説明              | 36 | 9 デバイスおよびドキュメントのサポート                  | 158 |

| 5.4 ピン接続要件             | 66 | 9.1 デバイスの命名規則                         | 158 |

| 6 仕様                   | 67 | 9.2 ツールとソフトウェア                        | 162 |

| 6.1 絶対最大定格             | 67 | 9.3 ドキュメントのサポート                       | 162 |

| 6.2 静電気放電 (ESD) 拡張車載定格 | 68 | 9.4 サポート・リソース                         | 162 |

| 6.3 静電気放電 (ESD) 産業用評価  | 68 | 9.5 商標                                | 162 |

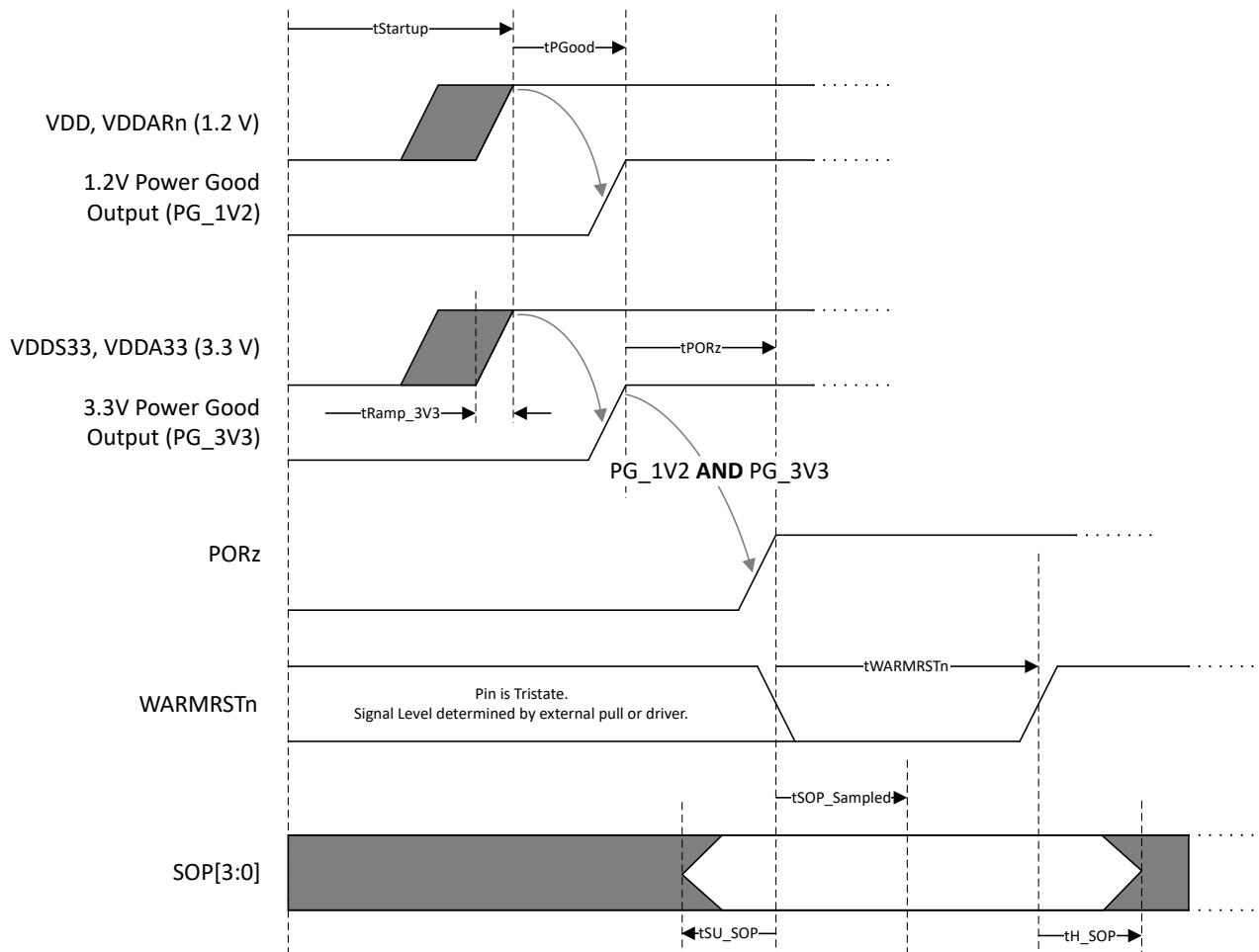

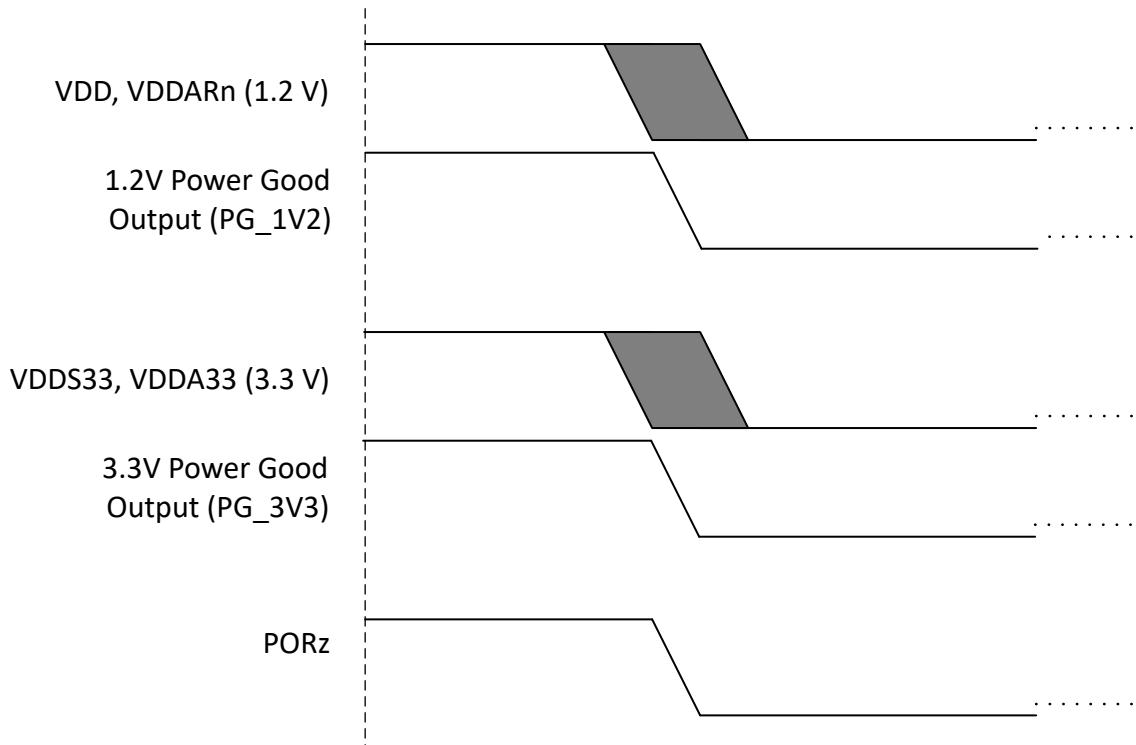

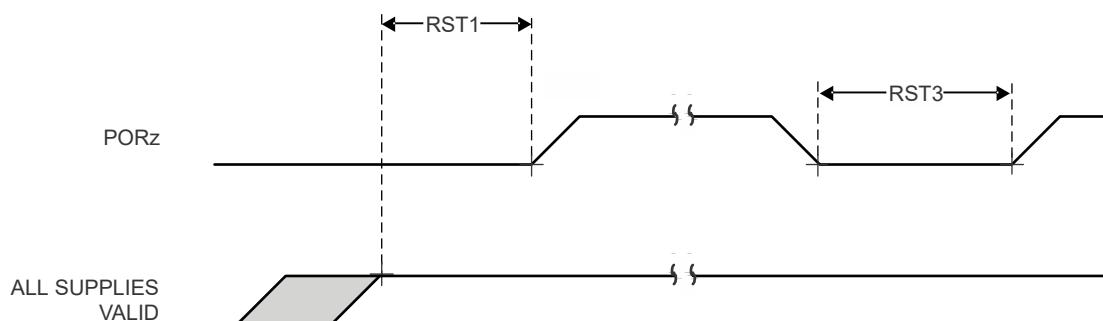

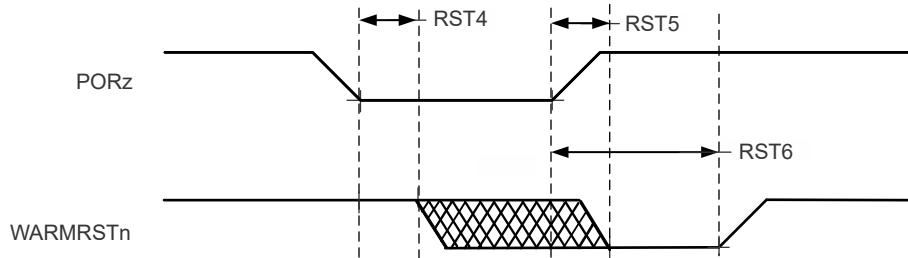

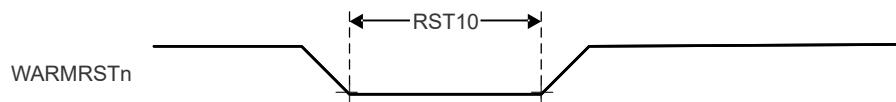

| 6.4 電源投入時間 (POH) の概要   | 68 | 9.6 静電気放電に関する注意事項                     | 163 |

| 6.5 推奨動作条件             | 69 | 9.7 用語集                               | 163 |

| 6.6 動作性能ポイント           | 69 | 10 改訂履歴                               | 163 |

| 6.7 消費電力の概略            | 70 | 11 メカニカル、パッケージ、および注文情報                | 165 |

| 6.8 電気的特性              | 71 |                                       |     |

## 4 デバイスの比較

表 4-1 に、デバイス間の比較を相違点を強調して示します。

表 4-1. デバイスの比較

| 特長                                        | 参照名                                        | AM2634 (1)                                                                   | AM2632 (1)                                                                   | AM2631                       |  |  |  |

|-------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|--|--|--|

| <b>JTAG デバイス ID 比較 (機能)</b>               |                                            |                                                                              |                                                                              |                              |  |  |  |

| JTAG デバイス ID (2)                          | 産業用:                                       | M:0x4111BBE6<br>L:0x41119BE6<br>K:0x41117BE6<br>E:0x4110BBE6<br>D:0x41109BE6 | M:0x4109BBE6<br>L:0x41099BE6<br>K:0x41097BE6<br>E:0x4108BBE6<br>D:0x41089BA6 | E:0x4104B3A6<br>D:0x410493A6 |  |  |  |

|                                           | 車載用拡張:                                     | K:0x41117BFE<br>D:0x41109BFE (グレード O)<br>D:0x41109C3E (グレード P)               | K:0x41097BFE<br>D:0x41089BFE (グレード O)<br>D:0x41089C3E (グレード P)               | D:0x410493BE                 |  |  |  |

| <b>プロセッサおよびアクセラレータ</b>                    |                                            |                                                                              |                                                                              |                              |  |  |  |

| 速度グレード                                    |                                            | セクション 6.6 動作性能ポイントを参照してください                                                  |                                                                              |                              |  |  |  |

| Arm® Cortex-R5F                           | R5FSS                                      | 4                                                                            | 2                                                                            | 1                            |  |  |  |

| ハードウェア セキュリティ モジュール                       | HSM                                        |                                                                              | あり                                                                           |                              |  |  |  |

| 暗号化アクセラレータ                                | セキュリティ                                     |                                                                              | あり                                                                           |                              |  |  |  |

| <b>プログラムおよびデータ ストレージ</b>                  |                                            |                                                                              |                                                                              |                              |  |  |  |

| オンチップ共有メモリ (RAM)                          | OCSRAM                                     | セクション 6.6 動作性能ポイントを参照してください                                                  |                                                                              |                              |  |  |  |

| R5F 密結合メモリ (TCM)                          | TCM                                        | 256KB (9)                                                                    |                                                                              |                              |  |  |  |

| 汎用メモリ コントローラ                              | GPMC                                       | 4MB                                                                          |                                                                              |                              |  |  |  |

| <b>ペリフェラル</b>                             |                                            |                                                                              |                                                                              |                              |  |  |  |

| モジュラー コントローラ エリア ネットワーク インターフェイス          | MCAN                                       | 4                                                                            |                                                                              |                              |  |  |  |

| CAN-FD をフルサポート                            | MCAN                                       | 4                                                                            |                                                                              |                              |  |  |  |

| 汎用 I/O                                    | GPIO                                       | 最大 139                                                                       |                                                                              |                              |  |  |  |

| シリアル ペリフェラル インターフェイス                      | SPI                                        | 5                                                                            |                                                                              |                              |  |  |  |

| 汎用非同期レシーバ / トランシミッタ                       | UART                                       | 6                                                                            |                                                                              |                              |  |  |  |

| ローカル相互接続ネットワーク                            | LIN                                        | 5                                                                            |                                                                              |                              |  |  |  |

| 集積回路間インターフェイス                             | I2C                                        | 4                                                                            |                                                                              |                              |  |  |  |

| A/D コンバータ                                 | ADC                                        | 3 <sup>(4)</sup> または 5 <sup>(5)</sup>                                        | 3 <sup>(4)</sup> または 5 <sup>(5)</sup>                                        | 3                            |  |  |  |

| コンバータ モジュール                               | CMPSS                                      | 12 <sup>(4)</sup> または 20 <sup>(5)</sup>                                      | 12 <sup>(4)</sup> または 20 <sup>(5)</sup>                                      | 12                           |  |  |  |

| D/A コンバータ                                 | DAC                                        | 1                                                                            |                                                                              |                              |  |  |  |

| プログラマブル リアルタイム ユニット サブシステム <sup>(6)</sup> | PRU-ICSS                                   | 0 または 1                                                                      |                                                                              |                              |  |  |  |

| 産業用通信サブシステムをサポート <sup>(7)</sup>           | PRU-ICSS                                   | オプション                                                                        |                                                                              |                              |  |  |  |

| ギガビット イーサネット インターフェイス                     | CPSW                                       | あり (2 ポート)                                                                   |                                                                              |                              |  |  |  |

| マルチメディア カード / セキュア デジタル インターフェイス          | MMCSD                                      | 1                                                                            |                                                                              |                              |  |  |  |

| 改良型高分解能パルス幅変調器モジュール                       | EHRPWM                                     | 16 <sup>(3)</sup> または 32 <sup>(5)</sup>                                      | 16 <sup>(4)</sup> または 32 <sup>(5)</sup>                                      | 16                           |  |  |  |

| 拡張キャプチャ モジュール                             | ECAP                                       | 5 <sup>(4)</sup> または 10 <sup>(5)</sup>                                       | 5 <sup>(4)</sup> または 10 <sup>(5)</sup>                                       | 5                            |  |  |  |

| 拡張直交エンコーダ パルス モジュール                       | EQEP                                       | 2 <sup>(4)</sup> または 3 <sup>(5)</sup>                                        | 2 <sup>(4)</sup> または 3 <sup>(5)</sup>                                        | 2                            |  |  |  |

| シグマ デルタ フィルタ モジュール                        | SDFM                                       | 1 <sup>(4)</sup> または 2 <sup>(5)</sup>                                        | 1 <sup>(4)</sup> または 2 <sup>(5)</sup>                                        | 1                            |  |  |  |

| 高速シリアル インターフェイス                           | FSI                                        | 4x FSI_RX + 4x FSI_TX                                                        |                                                                              |                              |  |  |  |

| クワッド SPI フラッシュ インターフェイス                   | QSPI                                       | 1                                                                            |                                                                              |                              |  |  |  |

| <b>その他</b>                                |                                            |                                                                              |                                                                              |                              |  |  |  |

| 接合部温度                                     | 産業用: -40°C ~ 105°C                         |                                                                              |                                                                              |                              |  |  |  |

|                                           | 拡張自動車用: -40°C ~ 150°C<br>車載: -40°C ~ 125°C |                                                                              |                                                                              |                              |  |  |  |

| 車載用認定                                     |                                            | AEC-Q100 <sup>(8)</sup> オプション                                                |                                                                              |                              |  |  |  |

- 機能安全用途用に開発された本デバイスは、ASIL-D または SIL-3 までのハードウェア整合性をサポートしています。詳細については、関連資料を参照してください。

- 「X:」文字は機能パラメータを示し、(グレード「X」)はセクション 6.6 のオペレーティングパフォーマンスポイント表のグレードを示します。

- CTRLMMR\_WKUP\_JTAG\_DEVICE\_ID レジスタおよび DEVICE\_ID ビットフィールドの詳細については、デバイスのテクニカルリファレンスマニュアルを参照してください。

- 標準アナログ構成には、3 個の ADC、16 個の EHRPWM、5 個の eCAP、2 個の EQEP、1 個の SDFM、12 個の CMPSS が含まれています

- 拡張アナログ構成には、5 個の ADC、32 個の EHRPWM、10 個の eCAP、3 個の EQEP、2 個の SDFM、20x CMPSS が含まれています

- (6) プログラム可能なリアルタイムユニットサブシステムは、機能コードとして D、E、F、K、L、M が付与された注文可能な部品番号を選択した場合に利用可能です。機能コードの定義については、「[命名法の説明](#)」表を参照してください。

- (7) 産業用通信サブシステム サポートは、機能コード D、E、F、K、L、M を含む注文可能な部品番号を選択した場合に利用できます。機能コードの定義については、「[命名法の説明](#)」表を参照してください。

- (8) AEC-Q100 認定は、[項目名の説明](#)の表の車載識別記号 (Q1) 識別子で示されている型番バリエントを選択する場合にのみ適用されます。

- (9) 各 R5FSS クラスタは、128KB の密結合メモリ (TCM) をサポートします。シングルコアまたはロックステップ動作モードでは、各コアが 128KB の TCM メモリ全体を使用可能ですが、デュアルコア モードでは各コアが割り当てられた半分 (64KB TCM) のみを使用できます。

#### 4.1 関連製品

高度なネットワーク機能、リアルタイム制御機能、信号処理アクセラレータを搭載した Arm® Cortex®-R ベースの高性能マイコンで構成された **Sitara™マイコン** ファミリは、産業用と車載の各アプリケーションで最新のマイコンの要件を満たすのに役立ちます。

**Sitara™ プロセッサ** 柔軟なアクセラレータ、周辺機器、接続性、統合ソフトウェア サポートを備えた Arm® Cortex®-A コアをベースとする、幅広くスケーラブルなプロセッサ ファミリで、センサからサーバーまで、さまざまな用途に最適です。Sitara™ プロセッサは、最新の産業用および車載用での用途レベルの要件に必要な機能と信頼性を備えています。

**Sitara™ マイコン - 評価基板** TI は、製品開発をすぐ始められるように、デバイス固有の評価基板 (EVM) を提供しています。詳細については、[AM263x controlCARD](#) と [AM263x LaunchPad](#) を参照してください。

**設計を完成させるための製品** 以下の製品リストは、システム設計要件を満たすために、AM263x デバイスと組み合わせて購入または使用されることが多いです。

- [TPS653850A-Q1](#) - 350mA I/O レールを備えたセーフティマイコン向けの機能安全準拠のマルチレール電源

- [TPS3704-Q1](#) - 車載対応、超高精度、コンパクトフォーム ファクタのマルチチャネル ウィンドウ スーパーバイザ

- [DP83TG720S-Q1](#) - 車載対応、RGMII 搭載、1000Base-T1、イーサネット PHY

- [DP83826E](#) - MII インターフェイスと拡張モード搭載、低レイテンシの 10/100-Mbps 産業用イーサネット PHY

- [TCAN1042H-Q1](#) - フレキシブル データレート対応車載用 70V バス障害保護 CAN トランシーバ。

## 5 端子構成および機能

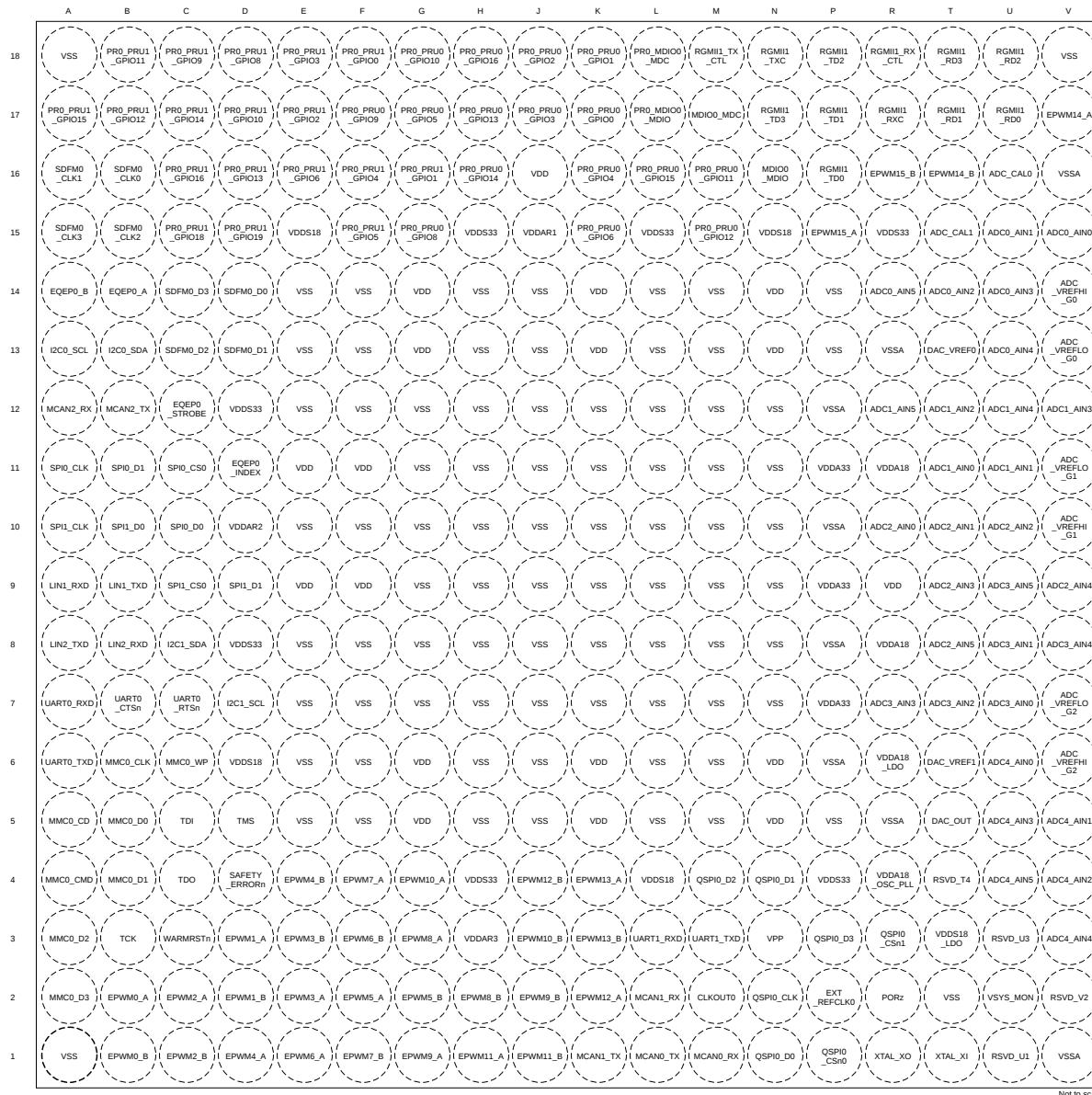

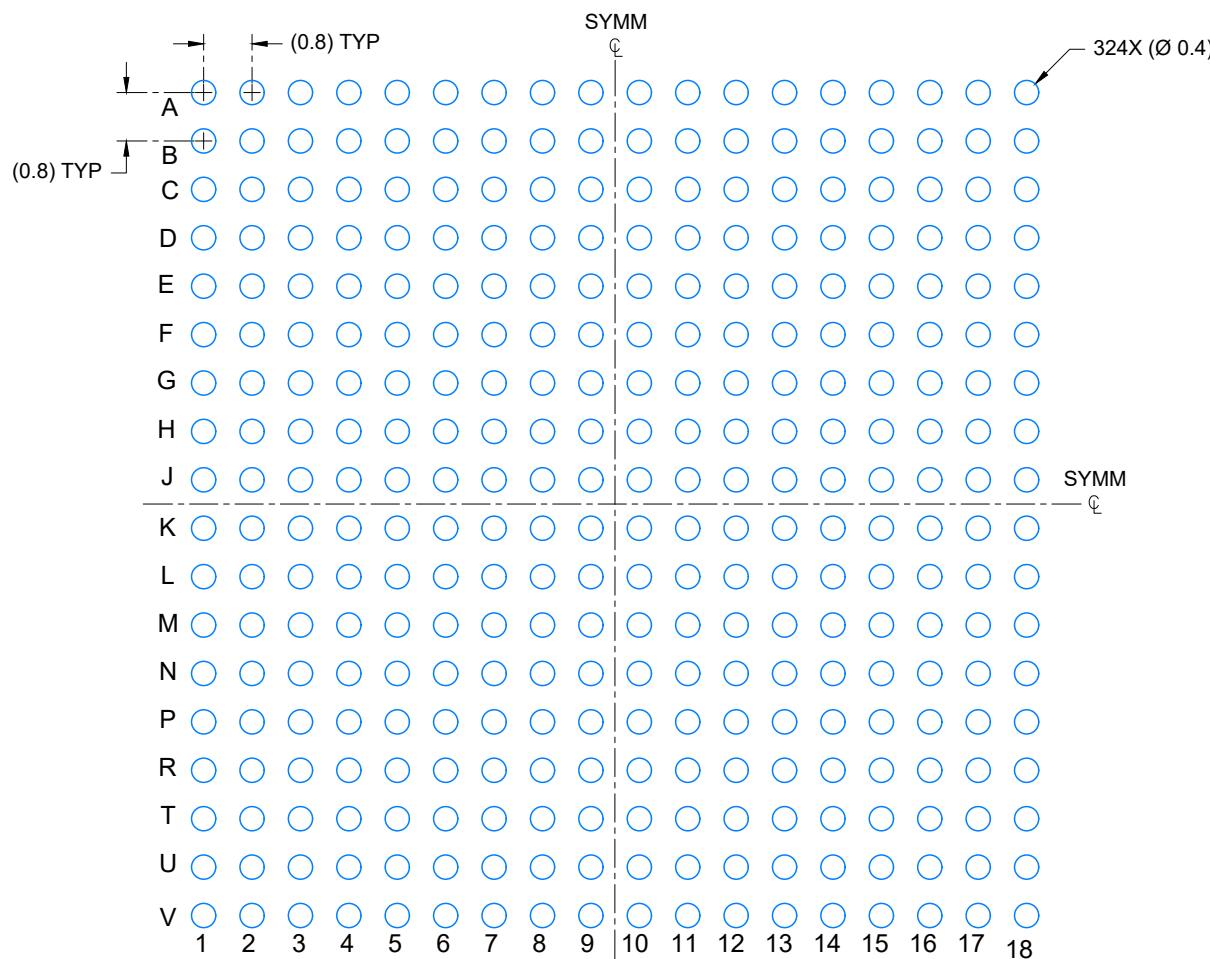

### 5.1 ピン ダイアグラム

#### 注

「ポール」、「ピン」、「端子」という用語は、ドキュメント全体で同じ意味で使用されています。物理的なパッケージに言及する場合にのみ「ポール」が使用されています。

このセクションの図を、その他の「端子構成および機能」表と組み合わせて使用することで、信号名とボール グリッド番号を特定できます。

#### 5.1.1 ZCZ ピン配置図

## 5.2 ピン属性

次のリストは、「ピン属性」表の各列の内容についての説明です。

- ボール番号:**ボール グリッド アレイ パッケージの各端子に割り当てられたボール番号。

- ボール名:**ボール グリッド アレイ パッケージの各端子に割り当てられたボール名 (通常はプライマリ MUXMODE 0 信号機能から付けられた名前)。

- 信号名:**ボールに関連するすべての専用およびピン多重化信号機能の信号名。

---

### 注

「ピン属性」表は、ピンに実装される SoC ピン多重化信号機能を定義しており、デバイス サブシステムに実装される信号機能の 2 次多重化は定義していません。信号機能の 2 次多重化については、この表では説明しません。2 次多重化信号機能の詳細については、デバイスのテクニカル リファレンス マニュアルで該当するペリフェラルの章を参照してください。

#### 4. MUX モード:各ピンの多重化信号機能に関連付けられた MUXMODE 値:

- MUXMODE 0 は、プライマリ ピンの多重化信号機能です。ただし、プライマリ ピンの多重化信号機能は、必ずしもデフォルトのピン多重化信号機能とは限りません。

- ピン多重化信号機能には、MUXMODE の値 1~15 を使用できます。ただし、すべての MUXMODE 値が実装されているわけではありません。有効な MUXMODE 値は、「ピン属性」表でピン多重化された信号機能として定義された値のみです。MUXMODE に定義された有効な値のみを使用できます。

- ブートストラップは SOC 構成ピンを定義します。各ピンに適用されるロジック状態は、PORz の立ち上がりエッジでラッ奇されます。これらの入力信号機能はそれぞれのピンに固定で、MUXMODE を使用してプログラムすることはできません。

- 空欄または「-」は、該当しないことを意味します。

---

### 注

- 「リセット後の MUX モード」列の値は、PORz がデアサートされたときに選択されるデフォルトのピン多重化信号機能を定義します。

- 同じピン多重化信号機能に 2 つのピンを構成すると、予期しない結果が生じる可能性があるため、この構成はサポートされていません。これは、正しいソフトウェア構成によって防止できます。

- パッドを未定義の多重化モードに構成すると、未定義の動作が生じるため、このような構成は避ける必要があります。

#### 5. 種類:信号の種類と方向:

- I = 入力

- O = 出力

- ID = 入力、オープン ドレイン出力機能付き

- OD = 出力、オープン ドレイン出力機能付き

- IO = 入力、出力、または同時に入力と出力

- IOD = 入力、出力、または同時に入力と出力、オープン ドレイン出力機能付き

- IOZ = 入力、出力、または同時に入力と出力、3 ステート出力機能付き

- OZ = 出力、3 ステート出力機能付き

- A = アナログ

- CAP = LDO コンデンサ

- PWR = 電源

- GND = グラウンド

#### 6. DSIS:選択解除入力状態 (DSIS) は、MUXMODE によってピン多重化信号機能が選択されていないとき、サブシステム入力 (ロジック「0」、ロジック「1」、または「パッド」レベル) に駆動される状態を示します。

- 0:ロジック 0 がサブシステム入力に駆動されます。

- 1:ロジック 1 がサブシステム入力に駆動されます。

- パッド:パッドのロジック状態がサブシステム入力に駆動されます。

- 空欄、NA、「-」は該当しないことを意味します。

7. リセット時のボール状態 (RX/TX/PULL):PORz がアサートされているときの端子の状態。ここで、RX は入力バッファの状態、TX は出力バッファの状態、PULL は内部プル抵抗の状態を定義します。

- RX (入力バッファ)

- オフ:入力バッファは無効です。

- オン:入力バッファは有効です。

- TX (出力バッファ)

- オフ:出力バッファは無効です。

- Low:出力バッファは有効であり、 $V_{OL}$  を駆動します。

- PULL (内部プル抵抗)

- オフ:内部プル抵抗はオフになっています。

- アップ:内部プルアップ抵抗がオンになっています。

- ダウン:内部プルダウン抵抗がオンになっています。

- NA:内部プル抵抗なし。

- 空欄、または「-」は該当しないことを意味します。

8. リセット後のボール状態 (RX/TX/PULL):PORz がデアサートされた後の端子の状態。ここで、RX は入力バッファの状態、TX は出力バッファの状態、PULL は内部プル抵抗の状態を定義します。

- RX (入力バッファ)

- オフ:入力バッファは無効です。

- オン:入力バッファは有効です。

- TX (出力バッファ)

- オフ:出力バッファは無効です。

- SS:MUXMODE で選択されたサブシステムによって、出力バッファの状態が決まります。

- PULL (内部プル抵抗)

- オフ:内部プル抵抗はオフになっています。

- アップ:内部プルアップ抵抗がオンになっています。

- ダウン:内部プルダウン抵抗がオンになっています。

- NA:内部プル抵抗なし。

- 空欄、NA、「-」は該当しないことを意味します。

9. リセット後の MUX モード:この列の値は、PORz がデアサートされた後のデフォルトのピン多重化信号機能を定義します。

- 空欄、NA、「-」は該当しないことを意味します。

10. I/O 電圧:この列は、該当する場合、それぞれの電源の I/O 動作電圧オプションを示します。

- 空欄、NA、「-」は該当しないことを意味します。

詳細については、「推奨動作条件」で、各電源に定義されている有効な動作電圧範囲を参照してください。

11. 電源:関連付けられている I/O の電源 (該当する場合)。

- 空欄、NA、「-」は該当しないことを意味します。

12. Hys:この I/O に関連付けられている入力バッファにヒステリシスがあるかどうかを示します。

- あり:ヒステリシスのサポート

- なし:ヒステリシスのサポートなし

- 空欄、NA、「-」は該当しないことを意味します。

詳細については、「電気的特性」のヒステリシスの値を参照してください。

13. プルタイプ: 内部プルアップまたはプルダウン抵抗が存在することを示します。内部抵抗は、ソフトウェアによって有効化または無効化できます。

- PU: 内部プルアップのみ

- PD: 内部プルダウンのみ

- PU/PD: 内部プルアップおよびプルダウン

- 空欄、NA、「-」は、内部プルが存在しないことを意味します。

---

#### 注

同じピン多重化信号機能に 2 つのピンを構成すると、予期しない結果が生じる可能性があるため、この構成はサポートされていません。この問題は、正しいソフトウェア構成を使用すると簡単に防止できます。

ピン多重化で定義されない多重化モードにパッドが設定されたとき、そのパッドの挙動は未定義になります。これは避ける必要があります。

---

14. バッファのタイプ: この列は、端末に関連付けられたバッファのタイプを定義します。この情報を使用して、該当する「電気的特性」表を決定できます。

- 空欄、NA、「-」は該当しないことを意味します。

電気的特性については、「電気的特性」の適切なバッファタイプの表を参照してください。

15. パッド構成レジスタ名: デバイスのパッド / ピン構成レジスタの名前です。

16. パッド構成レジスタのアドレス: デバイスのパッド / ピン構成レジスタのメモリアドレスです。

17. パッド構成レジスタのデフォルト値: POR<sub>z</sub> がデアサートされた後の、レジスタ デバイスのパッド / ピン構成レジスタのデフォルト値です。

表 5-1. ピン属性 (ZCZ パッケージ)

| ポート番号 [1] | ポート名 [2]/<br>IOMUX<br>レジスタ [15]/<br>アドレス [16]/<br>デフォルト値 [17] | 信号名 [3]       | 多重化モード [4] | 種類 [5] | リセット中のポートの状態<br>RX/TX/PULL [7] | リセット後のポートの状態<br>RX/TX/PULL [8] | リセット後の多重化モード [9] | IO 電圧 [10] | 電源 [11]  | HYS [12] | バッファタイプ [14] | ブルタイプ [13] |

|-----------|---------------------------------------------------------------|---------------|------------|--------|--------------------------------|--------------------------------|------------------|------------|----------|----------|--------------|------------|

| V15       | ADC0_AIN0                                                     | ADC0_AIN0     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U15       | ADC0_AIN1                                                     | ADC0_AIN1     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T14       | ADC0_AIN2                                                     | ADC0_AIN2     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U14       | ADC0_AIN3                                                     | ADC0_AIN3     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U13       | ADC0_AIN4                                                     | ADC0_AIN4     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| R14       | ADC0_AIN5                                                     | ADC0_AIN5     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T11       | ADC1_AIN0                                                     | ADC1_AIN0     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U11       | ADC1_AIN1                                                     | ADC1_AIN1     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T12       | ADC1_AIN2                                                     | ADC1_AIN2     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V12       | ADC1_AIN3                                                     | ADC1_AIN3     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U12       | ADC1_AIN4                                                     | ADC1_AIN4     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| R12       | ADC1_AIN5                                                     | ADC1_AIN5     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| R10       | ADC2_AIN0                                                     | ADC2_AIN0     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T10       | ADC2_AIN1                                                     | ADC2_AIN1     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U10       | ADC2_AIN2                                                     | ADC2_AIN2     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T9        | ADC2_AIN3                                                     | ADC2_AIN3     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V9        | ADC2_AIN4                                                     | ADC2_AIN4     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T8        | ADC2_AIN5                                                     | ADC2_AIN5     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U7        | ADC3_AIN0                                                     | ADC3_AIN0     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U8        | ADC3_AIN1                                                     | ADC3_AIN1     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T7        | ADC3_AIN2                                                     | ADC3_AIN2     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| R7        | ADC3_AIN3                                                     | ADC3_AIN3     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V8        | ADC3_AIN4                                                     | ADC3_AIN4     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U9        | ADC3_AIN5                                                     | ADC3_AIN5     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U6        | ADC4_AIN0                                                     | ADC4_AIN0     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V5        | ADC4_AIN1                                                     | ADC4_AIN1     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V4        | ADC4_AIN2                                                     | ADC4_AIN2     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U5        | ADC4_AIN3                                                     | ADC4_AIN3     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V3        | ADC4_AIN4                                                     | ADC4_AIN4     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U4        | ADC4_AIN5                                                     | ADC4_AIN5     |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| U16       | ADC_CAL0                                                      | ADC_CAL0      |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T15       | ADC_CAL1                                                      | ADC_CAL1      |            | I      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| V14       | ADC_VREFHI_G0                                                 | ADC_VREFHI_G0 |            | A      |                                |                                |                  | 1.8V       | VDDA_CIO |          | AnalogCIO    |            |

| V10       | ADC_VREFHI_G1                                                 | ADC_VREFHI_G1 |            | A      |                                |                                |                  | 1.8V       | VDDA_CIO |          | AnalogCIO    |            |

| V6        | ADC_VREFHI_G2                                                 | ADC_VREFHI_G2 |            | A      |                                |                                |                  | 1.8V       | VDDA_CIO |          | AnalogCIO    |            |

| V13       | ADC_VREFLO_G0                                                 | ADC_VREFLO_G0 |            | A      |                                |                                |                  | 1.8V       | VDDA_CIO |          | AnalogCIO    |            |

表 5-1. ピン属性 (ZCZ パッケージ) (続き)

| ポート番号 [1] | ポート名 [2]/<br>IOMUX<br>レジスタ [15]/<br>アドレス [16]/<br>デフォルト値 [17] | 信号名 [3]       | 多重化モード [4] | 種類 [5] | リセット中のポートの状態<br>RX/TX/PULL [7] | リセット後のポートの状態<br>RX/TX/PULL [8] | リセット後の多重化モード [9] | IO 電圧 [10] | 電源 [11]  | HYS [12] | バッファタイプ [14] | ブルタイプ [13] |

|-----------|---------------------------------------------------------------|---------------|------------|--------|--------------------------------|--------------------------------|------------------|------------|----------|----------|--------------|------------|

| V11       | ADC_VREFLO_G1                                                 | ADC_VREFLO_G1 |            | A      |                                |                                |                  | 1.8V       | VDDA_CIO |          | AnalogCIO    |            |

| V7        | ADC_VREFLO_G2                                                 | ADC_VREFLO_G2 |            | A      |                                |                                |                  | 1.8V       | VDDA_CIO |          | AnalogCIO    |            |

| M2        | CLKOUT0                                                       | CLKOUT0       | 0          | O      | オフ / オフ / オフ                   | オフ / SS / オフ                   | 0                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | CLKOUT0_CFG_REG<br>0x5310 0228<br>0x0000 0570                 | GPIO138       | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| T5        | DAC_OUT                                                       | DAC_OUT       |            | O      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T13       | DAC_VREF0                                                     | DAC_VREF0     |            | A      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| T6        | DAC_VREF1                                                     | DAC_VREF1     |            | A      |                                |                                |                  | 3.3V       | VDDA_CIO |          | AnalogCIO    |            |

| B2        | EPWM0_A                                                       | EPWM0_A       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM0_A_CFG_REG<br>0x5310 00AC<br>0x0000 05F7                 | GPIO43        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| B1        | EPWM0_B                                                       | EPWM0_B       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM0_B_CFG_REG<br>0x5310 00B0<br>0x0000 05F7                 | GPIO44        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| D3        | EPWM1_A                                                       | EPWM1_A       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM1_A_CFG_REG<br>0x5310 00B4<br>0x0000 05F7                 | GPIO45        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| D2        | EPWM1_B                                                       | EPWM1_B       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM1_B_CFG_REG<br>0x5310 00B8<br>0x0000 05F7                 | GPIO46        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| C2        | EPWM2_A                                                       | EPWM2_A       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM2_A_CFG_REG<br>0x5310 00BC<br>0x0000 05F7                 | GPIO47        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| C1        | EPWM2_B                                                       | EPWM2_B       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM2_B_CFG_REG<br>0x5310 00C0<br>0x0000 05F7                 | GPIO48        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| E2        | EPWM3_A                                                       | EPWM3_A       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM3_A_CFG_REG<br>0x5310 00C4<br>0x0000 05F7                 | GPIO49        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

| E3        | EPWM3_B                                                       | EPWM3_B       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0  | あり       | LVCMOS       | PU/PD      |

|           | EPWM3_B_CFG_REG<br>0x5310 00C8<br>0x0000 05F7                 | GPIO50        | 7          | IO     |                                |                                |                  |            |          |          |              |            |

表 5-1. ピン属性 (ZCZ パッケージ) (続き)

| ポート番号 [1] | ポート名 [2]/<br>IOMUX<br>レジスタ [15]/<br>アドレス [16]/<br>デフォルト値 [17] | 信号名 [3]      | 多重化モード [4] | 種類 [5] | リセット中のポートの状態<br>RX/TX/PULL [7] | リセット後のポートの状態<br>RX/TX/PULL [8] | リセット後の多重化モード [9] | IO 電圧 [10] | 電源 [11] | HYS [12] | パッファタイプ [14] | プルタイプ [13] |

|-----------|---------------------------------------------------------------|--------------|------------|--------|--------------------------------|--------------------------------|------------------|------------|---------|----------|--------------|------------|

| D1        | EPWM4_A<br>EPWM4_A_CFG_REG<br>0x5310 00CC<br>0x0000 05F7      | EPWM4_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | GPIO51       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| E4        | EPWM4_B<br>EPWM4_B_CFG_REG<br>0x5310 00D0<br>0x0000 05F7      | EPWM4_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSITX1_CLK   | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO52       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| F2        | EPWM5_A<br>EPWM5_A_CFG_REG<br>0x5310 00D4<br>0x0000 05F7      | EPWM5_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSITX1_DATA0 | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO53       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| G2        | EPWM5_B<br>EPWM5_B_CFG_REG<br>0x5310 00D8<br>0x0000 05F7      | EPWM5_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSITX1_DATA1 | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO54       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| E1        | EPWM6_A<br>EPWM6_A_CFG_REG<br>0x5310 00DC<br>0x0000 05F7      | EPWM6_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSIRX1_CLK   | 6          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO55       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| F3        | EPWM6_B<br>EPWM6_B_CFG_REG<br>0x5310 00E0<br>0x0000 05F7      | EPWM6_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSIRX1_DATA0 | 6          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO56       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| F4        | EPWM7_A<br>EPWM7_A_CFG_REG<br>0x5310 00E4<br>0x0000 05F7      | EPWM7_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSIRX1_DATA1 | 6          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO57       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| F1        | EPWM7_B<br>EPWM7_B_CFG_REG<br>0x5310 00E8<br>0x0000 05F7      | EPWM7_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | GPIO58       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| G3        | EPWM8_A<br>EPWM8_A_CFG_REG<br>0x5310 00EC<br>0x0000 05F7      | EPWM8_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART4_TXD    | 1          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | I2C3_SDA     | 2          | IOD    |                                |                                |                  |            |         |          |              |            |

|           |                                                               | FSITX2_CLK   | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO59       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| H2        | EPWM8_B<br>EPWM8_B_CFG_REG<br>0x5310 00F0<br>0x0000 05F7      | EPWM8_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART4_RXD    | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | I2C3_SCL     | 2          | IOD    |                                |                                |                  |            |         |          |              |            |

|           |                                                               | FSITX2_DATA0 | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO60       | 7          | IO     |                                |                                |                  |            |         |          |              |            |

**表 5-1. ピン属性 (ZCZ パッケージ) (続き)**

| ポート番号 [1] | ポート名 [2]/<br>IOMUX<br>レジスタ [15]/<br>アドレス [16]/<br>デフォルト値 [17] | 信号名 [3]       | 多重化モード [4] | 種類 [5] | リセット中のポートの状態<br>RX/TX/PULL [7] | リセット後のポートの状態<br>RX/TX/PULL [8] | リセット後の多重化モード [9] | IO 電圧 [10] | 電源 [11] | HYS [12] | バッファタイプ [14] | プルタイプ [13] |

|-----------|---------------------------------------------------------------|---------------|------------|--------|--------------------------------|--------------------------------|------------------|------------|---------|----------|--------------|------------|

| G1        | EPWM9_A<br>EPWM9_A_CFG_REG<br>0x5310 00F4<br>0x0000 05F7      | EPWM9_A       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | FSITX2_DATA1  | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO61        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| J2        | EPWM9_B<br>EPWM9_B_CFG_REG<br>0x5310 00F8<br>0x0000 05F7      | EPWM9_B       | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART1_RTSn    | 1          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | FSIRX2_CLK    | 6          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO62        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| G4        | EPWM10_A<br>EPWM10_A_CFG_REG<br>0x5310 00FC<br>0x0000 05F7    | EPWM10_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART1_CTSn    | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | FSIRX2_DATA0  | 6          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO63        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| J3        | EPWM10_B<br>EPWM10_B_CFG_REG<br>0x5310 0100<br>0x0000 05F7    | EPWM10_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART2_RTSn    | 1          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | FSIRX2_DATA1  | 6          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO64        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| H1        | EPWM11_A<br>EPWM11_A_CFG_REG<br>0x5310 0104<br>0x0000 05F7    | EPWM11_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART2_CTSn    | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_CLKLB   | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO65        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| J1        | EPWM11_B<br>EPWM11_B_CFG_REG<br>0x5310 0108<br>0x0000 05F7    | EPWM11_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART3_RTSn    | 1          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_OEn_REN | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO66        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| K2        | EPWM12_A<br>EPWM12_A_CFG_REG<br>0x5310 010C<br>0x0000 05F7    | EPWM12_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART3_CTSn    | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | SPI4_CS1      | 2          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_WEn     | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO67        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| J4        | EPWM12_B<br>EPWM12_B_CFG_REG<br>0x5310 0110<br>0x0000 05F7    | EPWM12_B      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART1_DCDn    | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_CSn0    | 6          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO68        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| K4        | EPWM13_A<br>EPWM13_A_CFG_REG<br>0x5310 0114<br>0x0000 05F7    | EPWM13_A      | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART1_RIn     | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_AD0     | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO69        | 7          | IO     |                                |                                |                  |            |         |          |              |            |

表 5-1. ピン属性 (ZCZ パッケージ) (続き)

| ポート番号 [1] | ポート名 [2]/<br>IOMUX<br>レジスタ [15]/<br>アドレス [16]/<br>デフォルト値 [17] | 信号名 [3]    | 多重化モード [4] | 種類 [5] | リセット中のポートの状態<br>RX/TX/PULL [7] | リセット後のポートの状態<br>RX/TX/PULL [8] | リセット後の多重化モード [9] | IO 電圧 [10] | 電源 [11] | HYS [12] | バッファタイプ [14] | プルタイプ [13] |

|-----------|---------------------------------------------------------------|------------|------------|--------|--------------------------------|--------------------------------|------------------|------------|---------|----------|--------------|------------|

| K3        | EPWM13_B<br>EPWM13_B_CFG_REG<br>0x5310 0118<br>0x0000 05F7    | EPWM13_B   | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART1_DTRn | 1          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_AD1  | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO70     | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| V17       | EPWM14_A<br>EPWM14_A_CFG_REG<br>0x5310 011C<br>0x0000 05F7    | EPWM14_A   | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART1_DSRn | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_AD2  | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO71     | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| T16       | EPWM14_B<br>EPWM14_B_CFG_REG<br>0x5310 0120<br>0x0000 05F7    | EPWM14_B   | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | MII1_RX_ER | 2          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_AD3  | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO72     | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| P15       | EPWM15_A<br>EPWM15_A_CFG_REG<br>0x5310 0124<br>0x0000 05F7    | EPWM15_A   | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART5_TXD  | 1          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | MII1_COL   | 2          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_AD4  | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO73     | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| R16       | EPWM15_B<br>EPWM15_B_CFG_REG<br>0x5310 0128<br>0x0000 05F7    | EPWM15_B   | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | UART5_RXD  | 1          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | MII1_CRS   | 2          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPMC0_AD5  | 6          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO74     | 7          | IO     |                                |                                |                  |            |         |          |              |            |

| B14       | EQEP0_A<br>EQEP0_A_CFG_REG<br>0x5310 0208<br>0x0000 05F7      | UART4_RTSn | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | SPI4_CLK   | 3          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO130    | 7          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | EQEP0_A    | 8          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | SDFM1_CLK0 | 9          | I      |                                |                                |                  |            |         |          |              |            |

| A14       | EQEP0_B<br>EQEP0_B_CFG_REG<br>0x5310 020C<br>0x0000 05F7      | UART4_CTSn | 0          | I      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                               | SPI4_CS0   | 3          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | GPIO131    | 7          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                               | EQEP0_B    | 8          | I      |                                |                                |                  |            |         |          |              |            |

|           |                                                               | SDFM1_D0   | 9          | I      |                                |                                |                  |            |         |          |              |            |

表 5-1. ピン属性 (ZCZ パッケージ) (続き)

| ポート番号 [1] | ポート名 [2]/<br>IOMUX<br>レジスタ [15]/<br>アドレス [16]/<br>デフォルト値 [17]      | 信号名 [3]      | 多重化モード [4] | 種類 [5] | リセット中のポートの状態<br>RX/TX/PULL [7] | リセット後のポートの状態<br>RX/TX/PULL [8] | リセット後の多重化モード [9] | IO 電圧 [10] | 電源 [11] | HYS [12] | パッファタイプ [14] | プルタイプ [13] |

|-----------|--------------------------------------------------------------------|--------------|------------|--------|--------------------------------|--------------------------------|------------------|------------|---------|----------|--------------|------------|

| D11       | EQEP0_INDEX<br>EQEP0_INDEX_CFG_REG<br>0x5310_0214<br>0x0000_05F7   | UART4_RXD    | 0          | I      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                                    | LIN4_RXD     | 1          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | SPI4_D1      | 3          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | GPIO133      | 7          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | EQEP0_INDEX  | 8          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | SDFM1_D1     | 9          | I      |                                |                                |                  |            |         |          |              |            |

| C12       | EQEP0_STROBE<br>EQEP0_STROBE_CFG_REG<br>0x5310_0210<br>0x0000_05F7 | UART4_TXD    | 0          | O      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                                    | LIN4_TXD     | 1          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | SPI4_D0      | 3          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | GPIO132      | 7          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | EQEP0_STROBE | 8          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | SDFM1_CLK1   | 9          | I      |                                |                                |                  |            |         |          |              |            |

| P2        | EXT_REFCLK0<br>EXT_REFCLK0_CFG_REG<br>0x5310_01E4<br>0x0000_05F7   | EXT_REFCLK0  | 0          | I      | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                                    | XBAROUT15    | 5          | O      |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | GPIO121      | 7          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | EQEP1_INDEX  | 9          | IO     |                                |                                |                  |            |         |          |              |            |

| A13       | I2C0_SCL<br>I2C0_SCL_CFG_REG<br>0x5310_021C<br>0x0000_05F7         | I2C0_SCL     | 0          | IOD    | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | I2C OD       |            |

|           |                                                                    | GPIO135      | 7          | IOD    |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | EQEP2_B      | 8          | ID     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | SDFM1_CLK3   | 9          | ID     |                                |                                |                  |            |         |          |              |            |

| B13       | I2C0_SDA<br>I2C0_SDA_CFG_REG<br>0x5310_0218<br>0x0000_05F7         | I2C0_SDA     | 0          | IOD    | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | I2C OD       |            |

|           |                                                                    | GPIO134      | 7          | IOD    |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | EQEP2_A      | 8          | ID     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | SDFM1_CLK2   | 9          | ID     |                                |                                |                  |            |         |          |              |            |

| D7        | I2C1_SCL<br>I2C1_SCL_CFG_REG<br>0x5310_005C<br>0x0000_05F7         | I2C1_SCL     | 0          | IOD    | オフ / オフ / オフ                   | オフ / オフ / オフ                   | 7                | 3.3V       | VDDSHV0 | あり       | LVCMOS       | PU/PD      |

|           |                                                                    | SPI3_CS0     | 2          | IO     |                                |                                |                  |            |         |          |              |            |

|           |                                                                    | XBAROUT7     | 5          | O      |                                |                                |                  |            |         |          |              |            |