# 完全統合型、8チャネル超音波アナログ・フロントエンド、 パッシブCWミキサ搭載、0.75nV/rtHz、 14/12ビット、65MSPS、153mW/CH

## 特 長

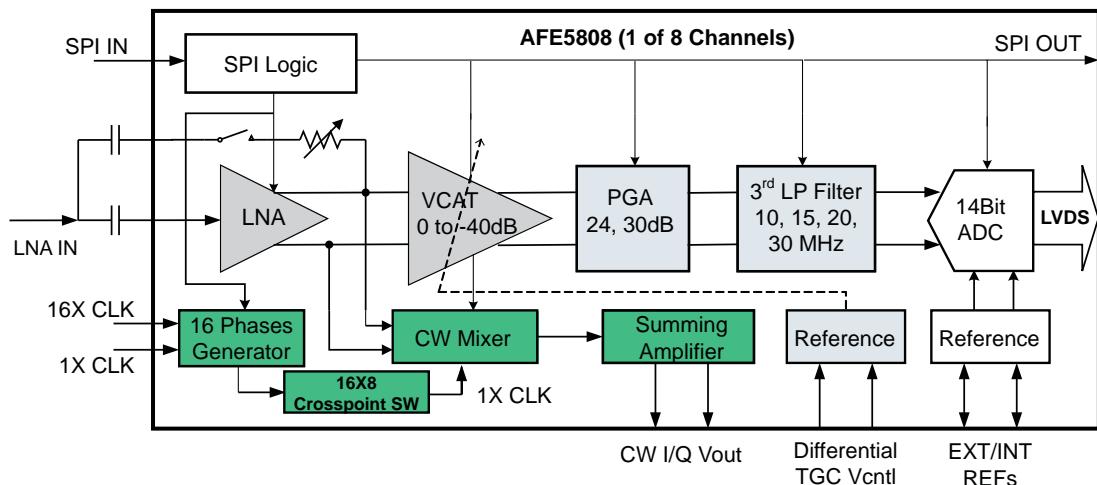

- 必要な回路を完全に統合した8チャネルのアナログ・フロントエンド

- LNA、VCAT、PGA、LPF、ADC、およびCWミキサ

- ゲインをプログラミング可能な低ノイズ・アンプ(LNA)

- ゲイン：24/18/12 dB

- リニア入力範囲：0.25/0.5/1 V<sub>PP</sub>

- 入力基準ノイズ：0.63/0.7/0.9 nV/rtHz

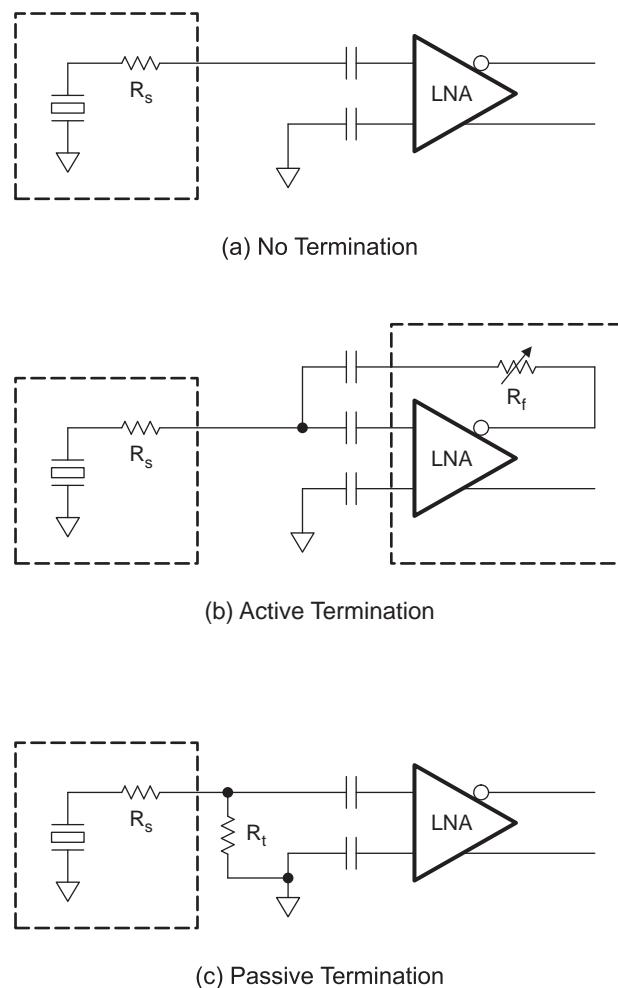

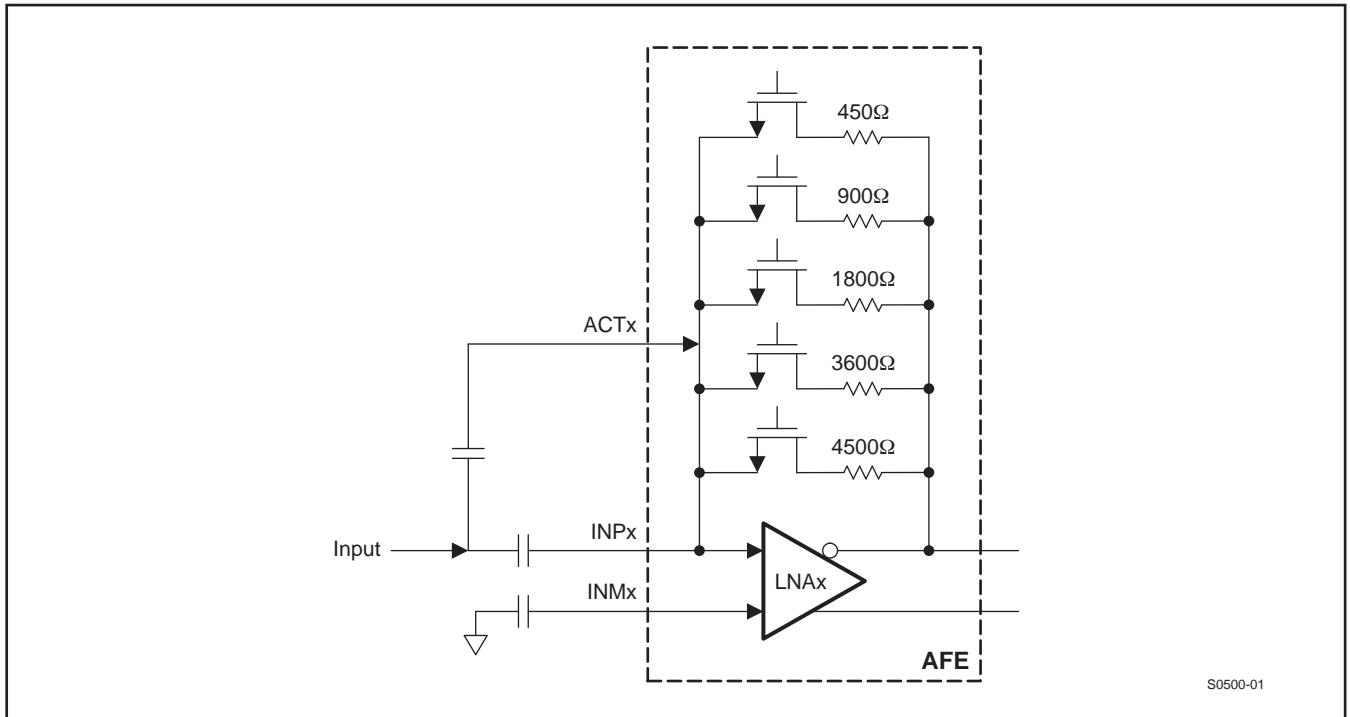

- プログラミング可能なアクティブ終端

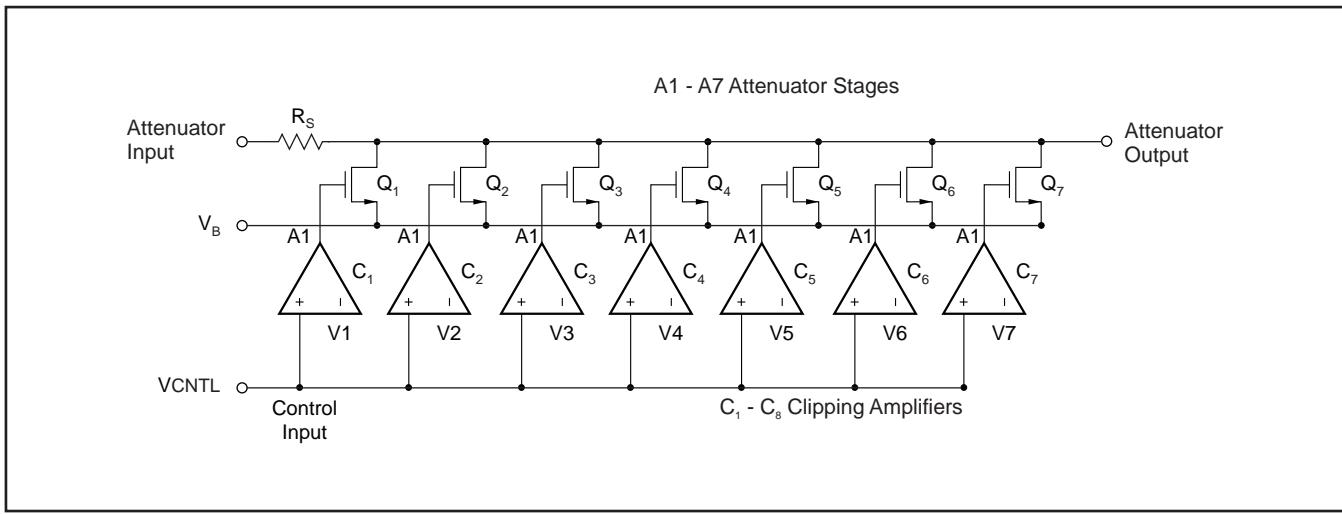

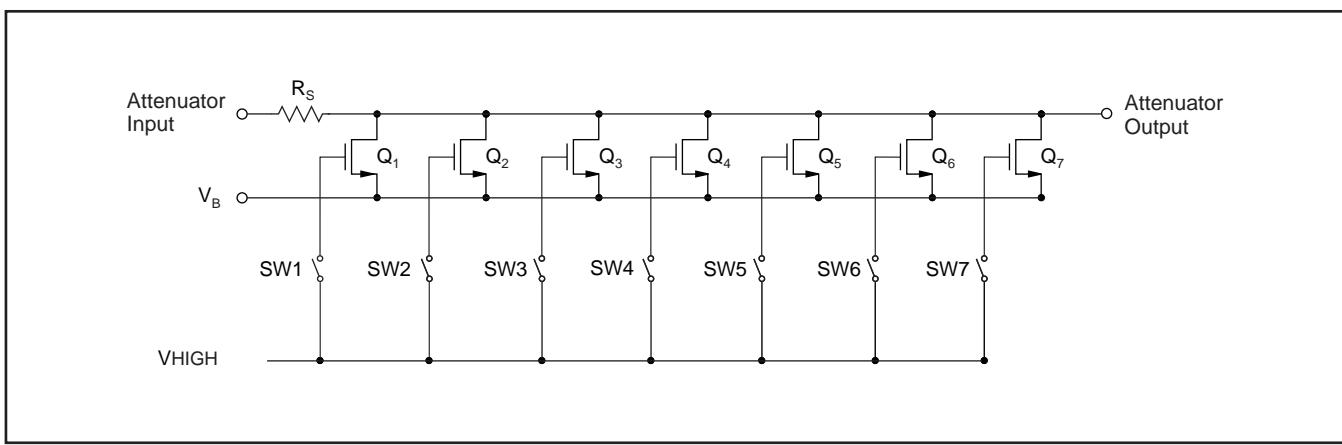

- 40dB低ノイズ電圧制御アッテネータ(VCAT)

- 24/30dBプログラマブル・ゲイン・アンプ(PGA)

- 3次リニア・フェーズ・ローパス・フィルタ(LPF)

- 10、15、20、30 MHz

- 14ビットA/Dコンバータ(ADC)

- SNR：77dBFS(65MSPS時)

- LVDS出力

- ノイズ/電力最適化(フル・チェーン)

- 153mW/CH(0.75nV/rtHz、65MSPS時)

- 98mW/CH(1.1nV/rtHz、40MSPS時)

- 80mW/CH(CWモード時)

- 優れたデバイス間ゲイン・マッチング

- ±0.5dB(typ)、±0.9dB(max)

- 低い高調波歪

- 高速で安定した過負荷回復

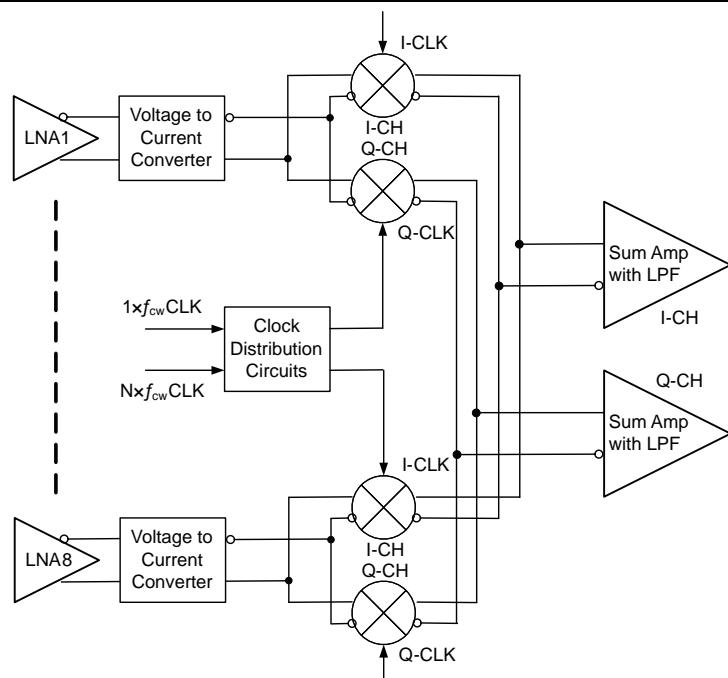

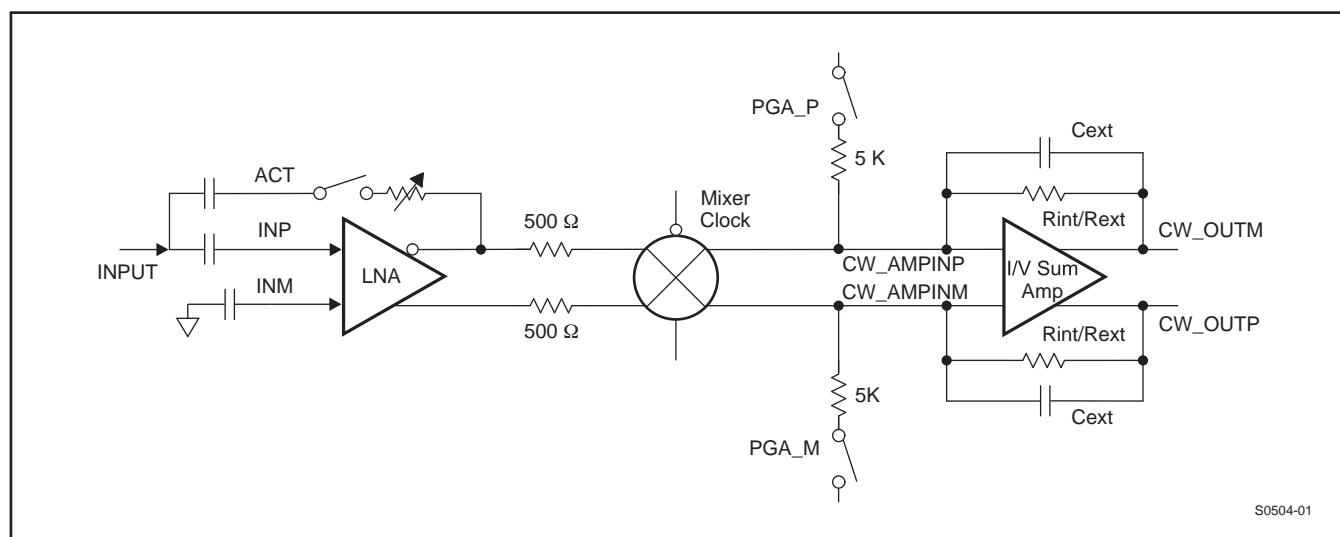

- 連続波ドップラー(CWD)用パッシブ・ミキサ

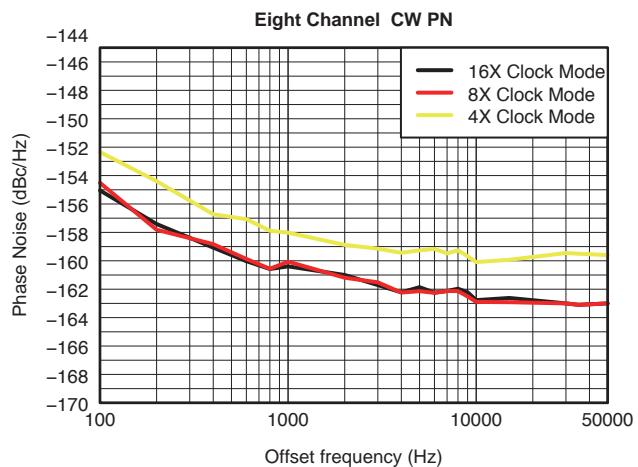

- 低い近接位相ノイズ：−156dBc/Hz(2.5MHzの搬送波から1kHzでの値)

- 位相分解能：1/16λ

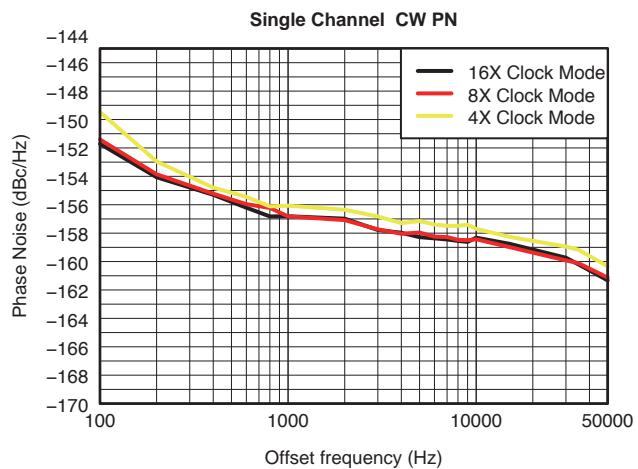

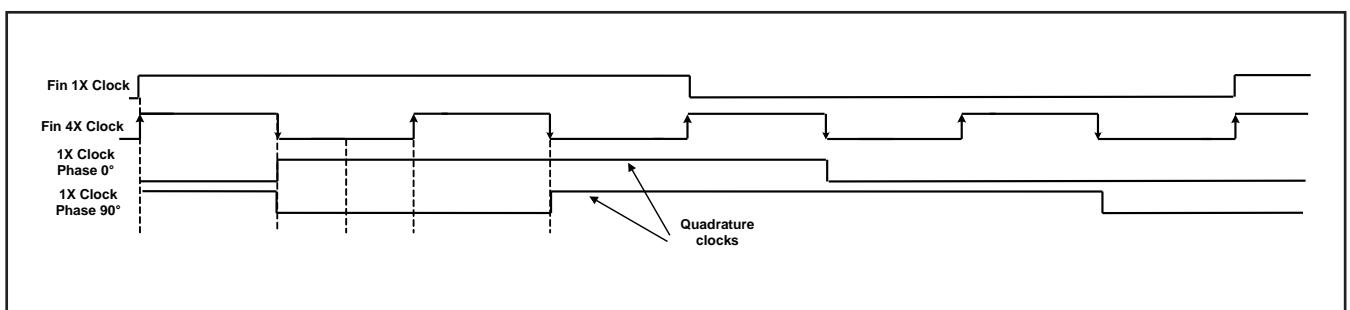

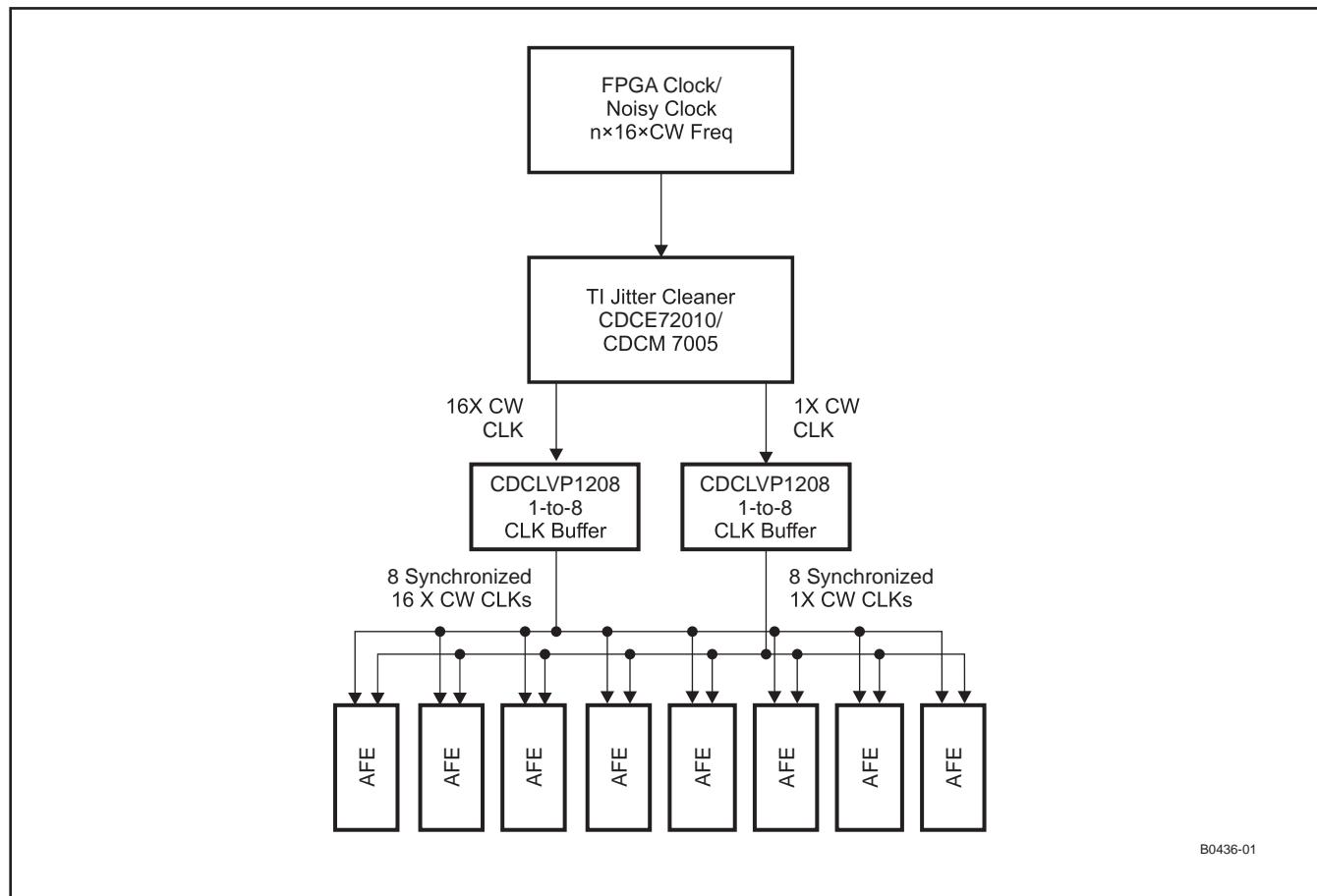

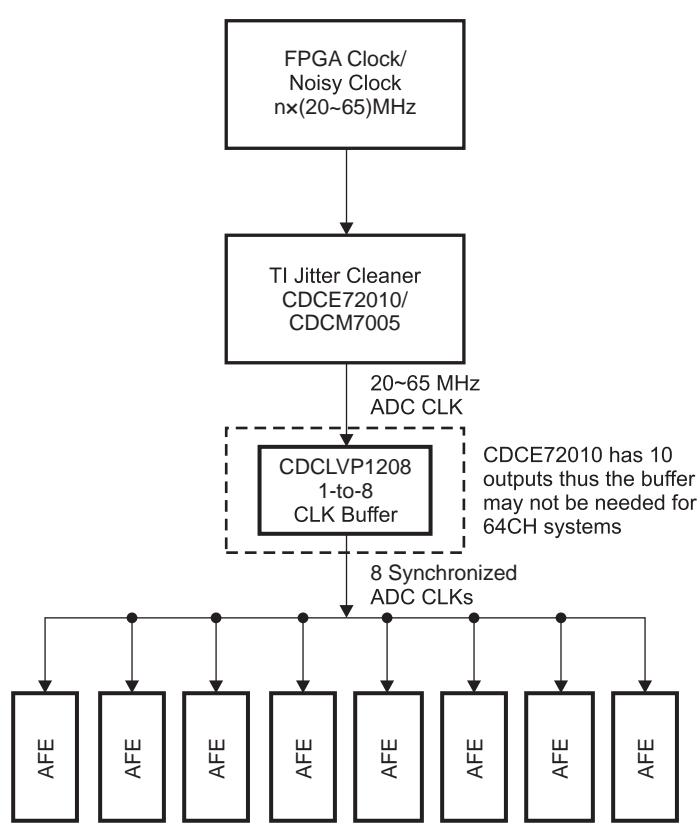

- 16X、8X、4X、1XのCWクロックをサポート

— 3次および5次高調波を12dB抑制

— 柔軟な入力クロック

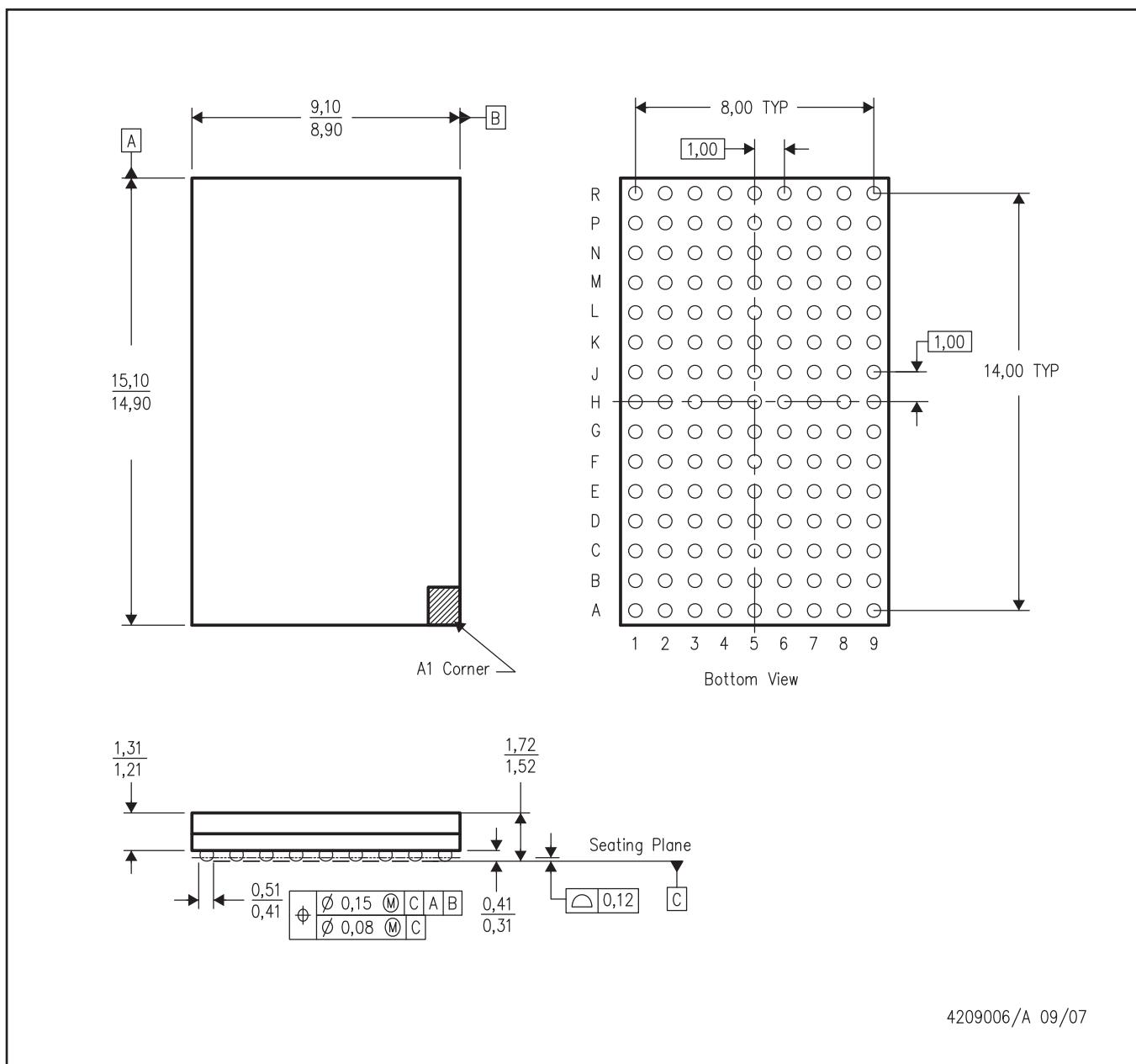

- 小さなパッケージ：15mm × 9mm、135-BGA

## ア プ リ ケ ー シ オ ン

- 医療用超音波イメージング

- 非破壊評価用機器

## 概 要

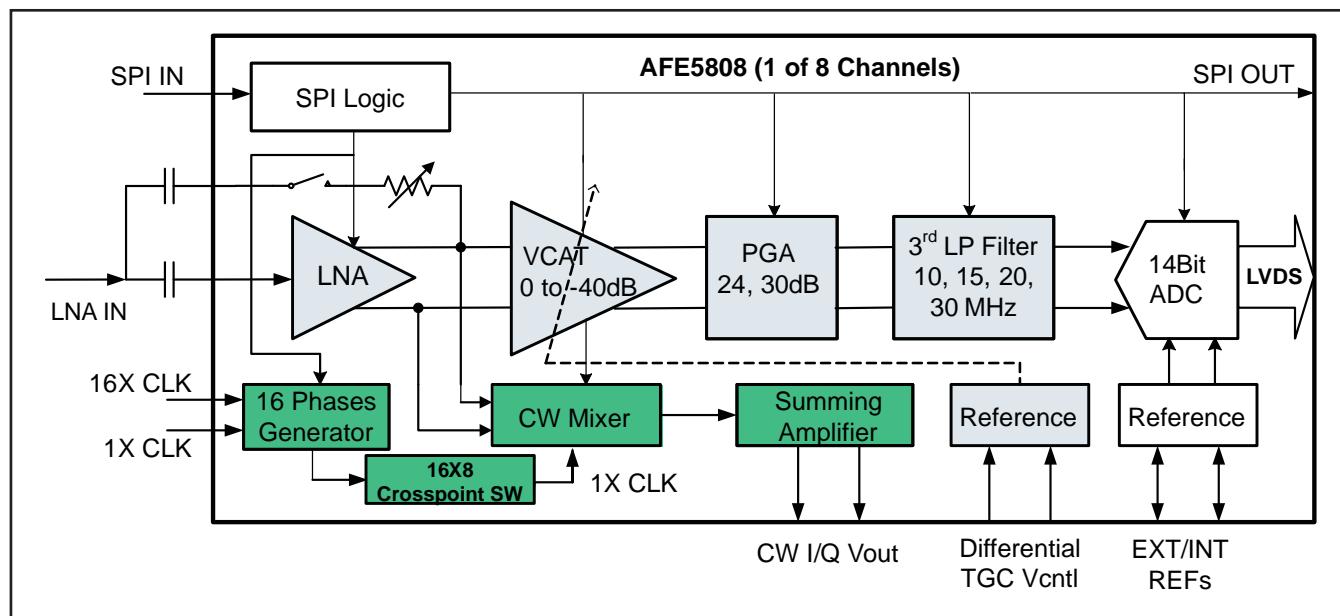

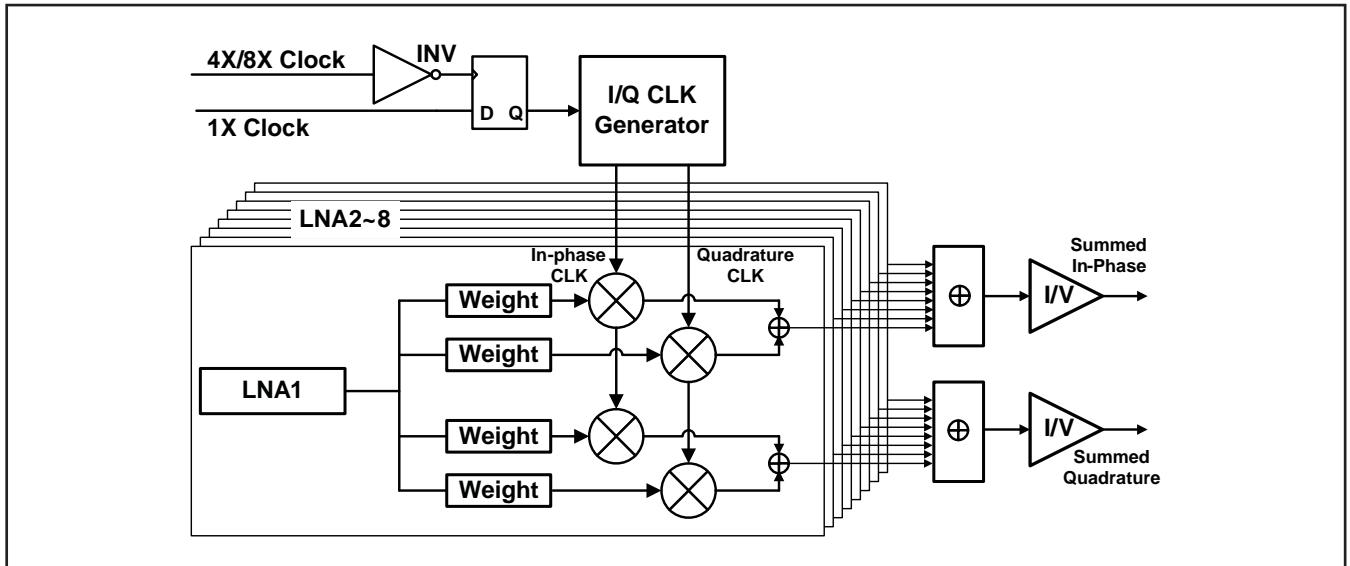

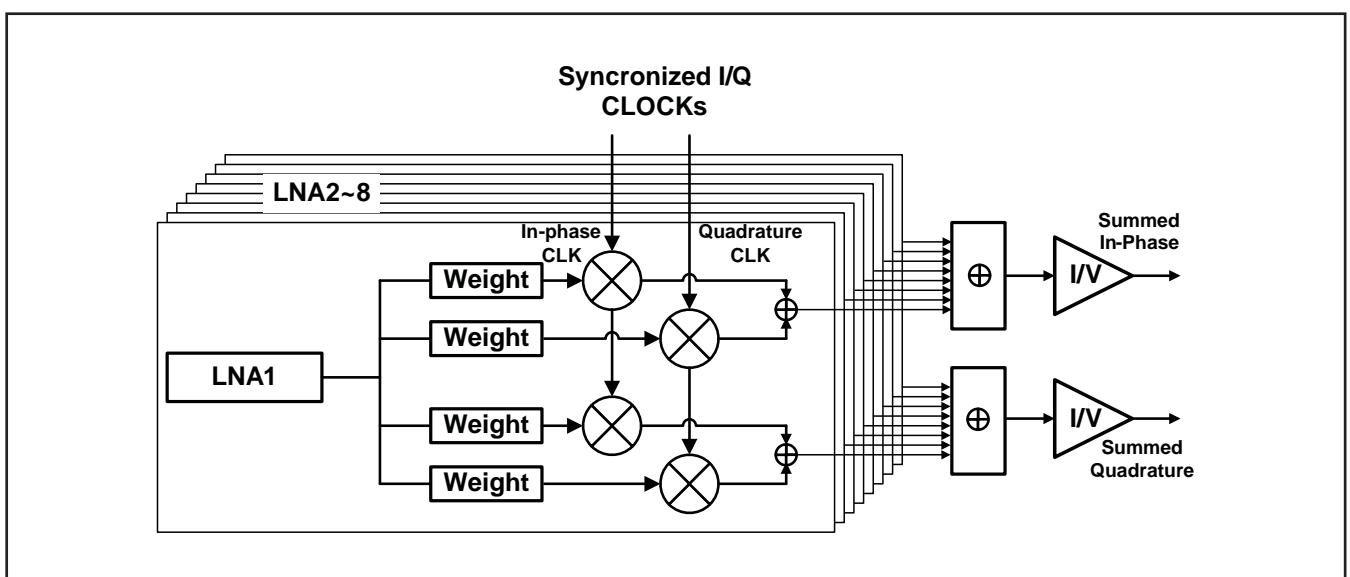

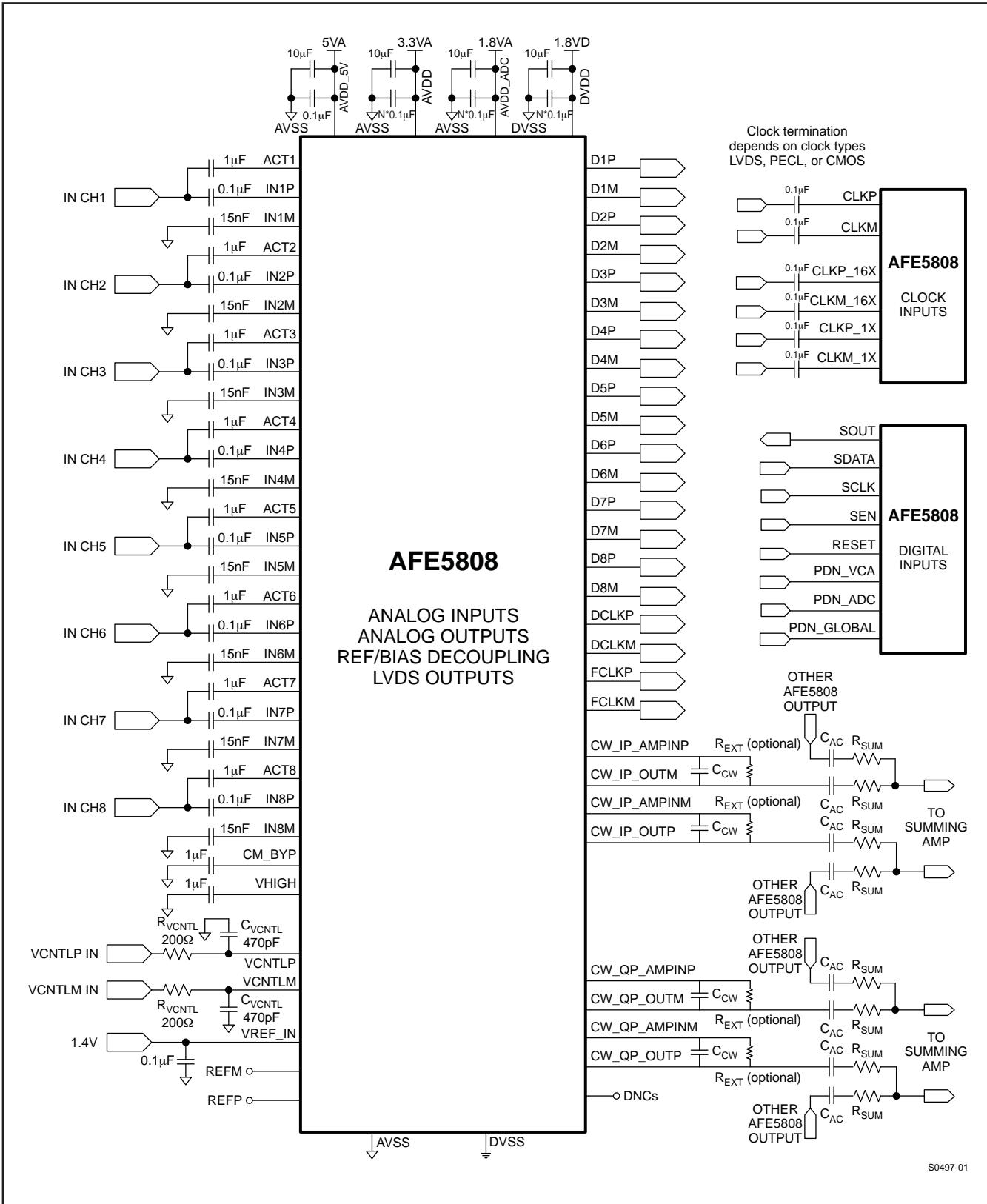

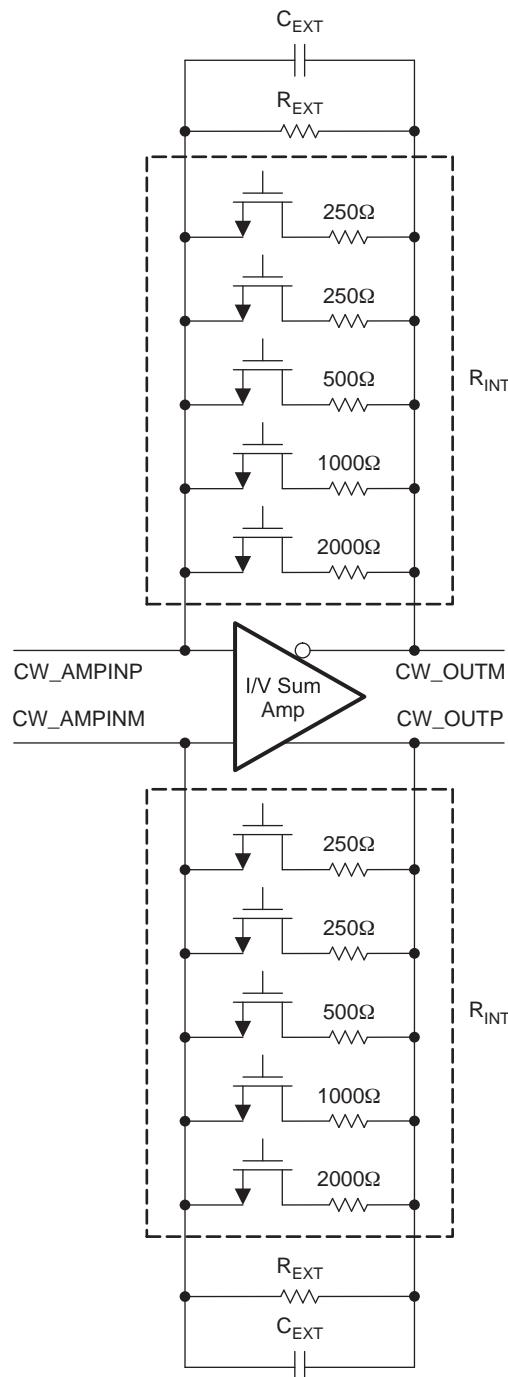

AFE5808は、高性能と小サイズが要求される超音波システム向けに設計された高集積アナログ・フロントエンド(AFE)ソリューションです。AFE5808は、完全な時間ゲイン制御(TGC)イメージング・パスと、連続波ドップラー(CWD)パスを統合しています。また、電力/ノイズ特性の適切な組み合わせを選択することで、システム性能を最適化できます。これにより、AFE5808は、ハイエンド・システムに対してだけでなく、ポータブル・システムに対しても優れた超音波アナログ・フロントエンド・ソリューションとなります。

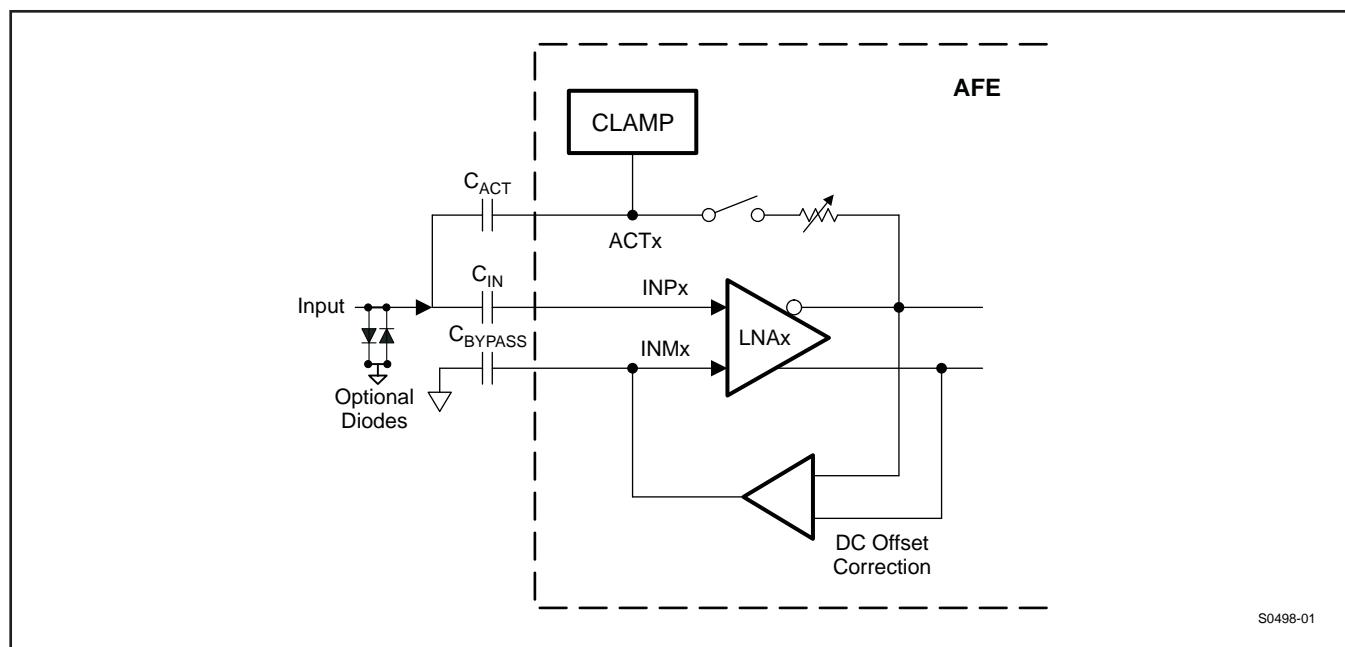

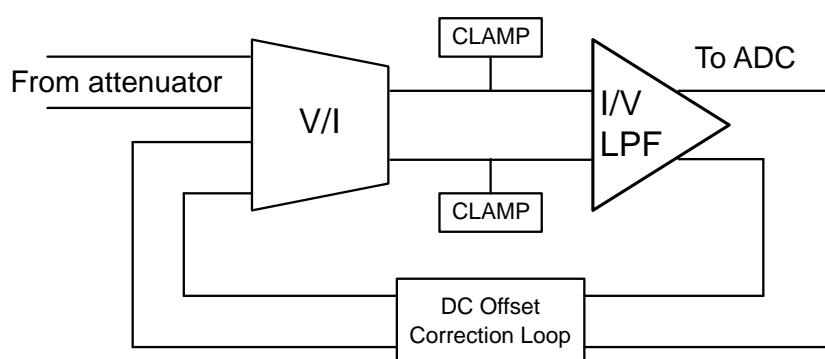

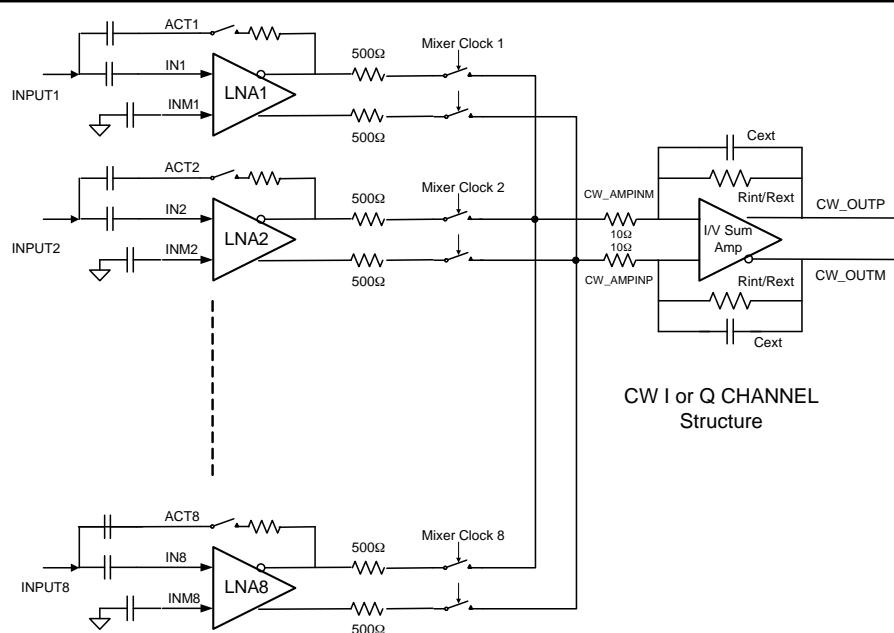

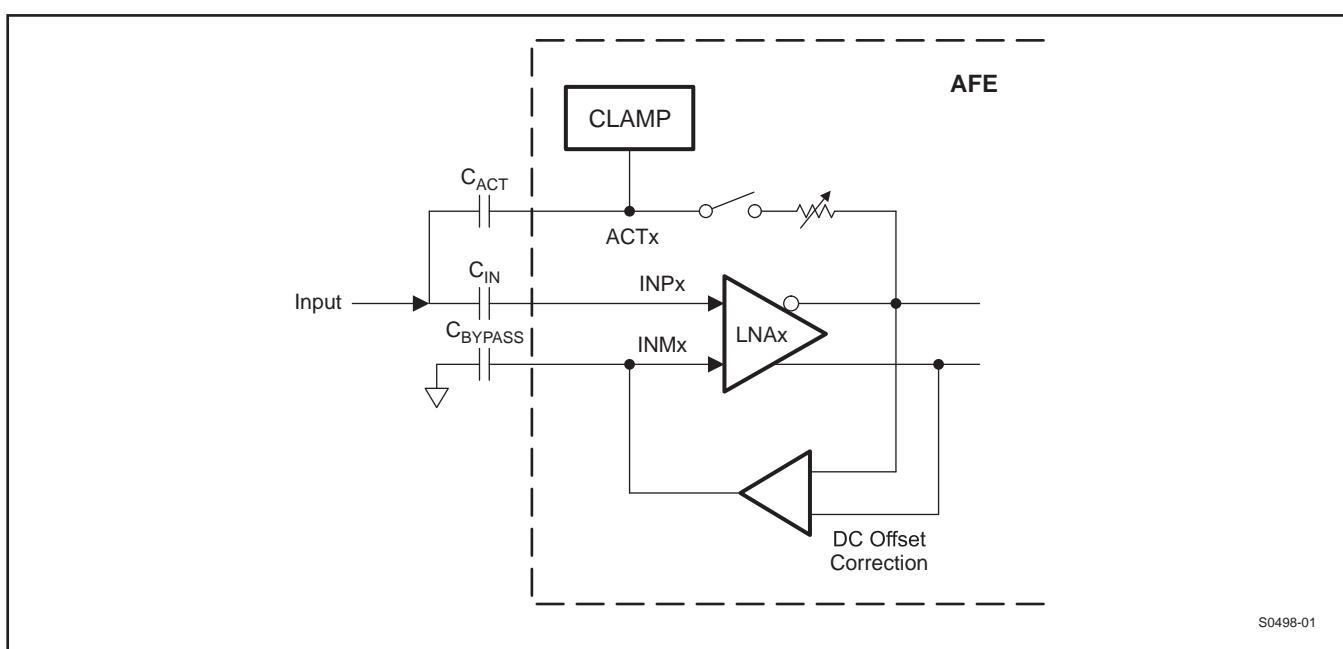

AFE5808には、8チャネルの電圧制御アンプ(VCA)、14/12ビットA/Dコンバータ(ADC)、およびCWミキサが内蔵されています。VCAには、低ノイズ・アンプ(LNA)、電圧制御アッテネータ(VCAT)、プログラマブル・ゲイン・アンプ(PGA)、およびローパス・フィルタ(LPF)が含まれています。LNAはゲインがプログラミング可能であり、250mV<sub>PP</sub>～1V<sub>PP</sub>の入力信号をサポートします。また、LNAはプログラミング可能なアクティブ終端もサポートしています。超低ノイズのVCATは、40dBの減衰制御範囲を持ち、低ゲインでのSNRを全体的に向上させることで、高調波イメージングおよびニア・フィールド・イメージングに有用です。PGAは、24dBおよび30dBのゲイン・オプションを備えています。ADCの前に、LPFを10MHz、15MHz、20MHz、または30MHzとして構成することで、異なる周波数の超音波アプリケーションをサポートできます。AFE5808が備える14

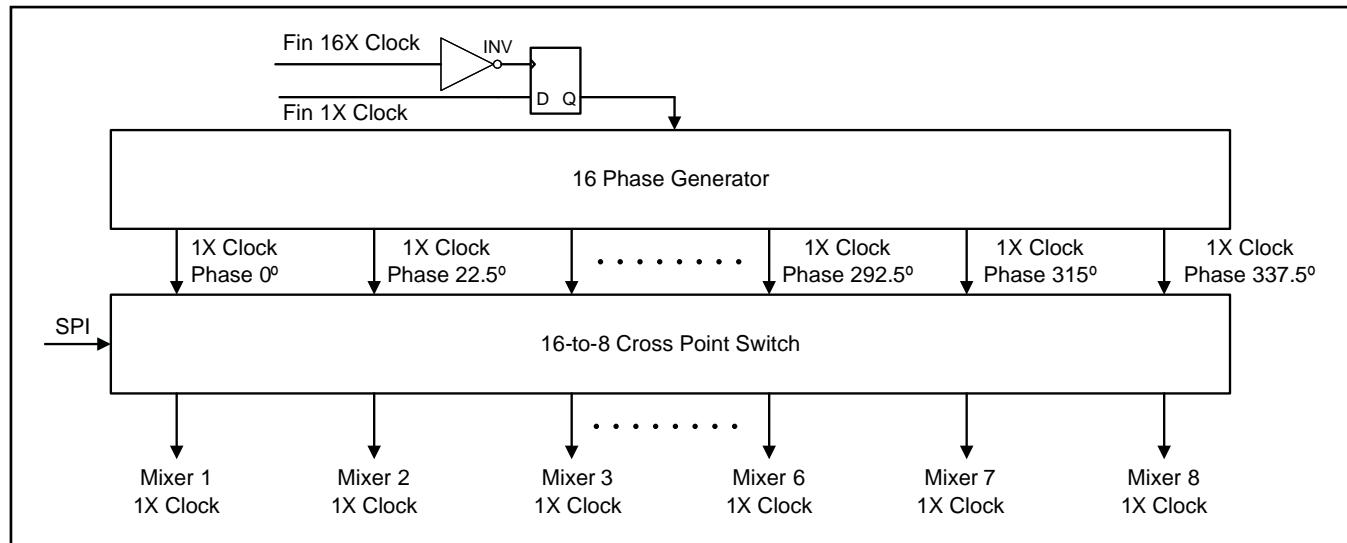

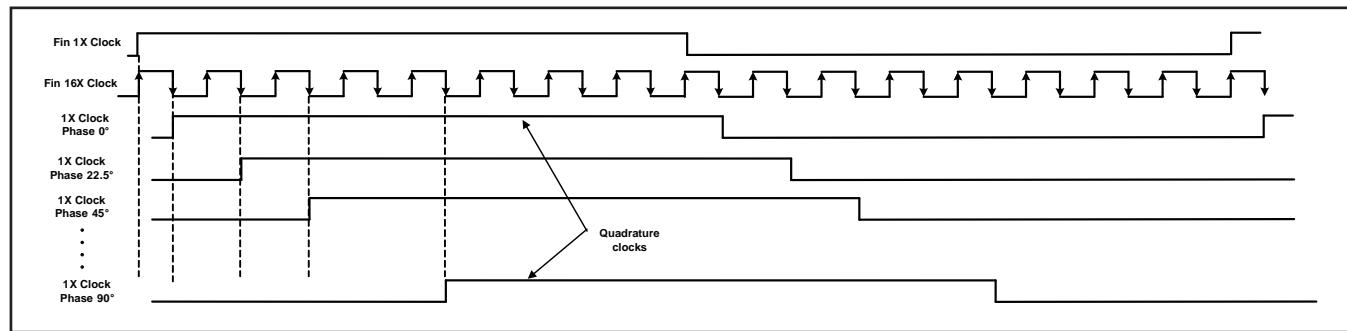

ビット/65MSPSの高性能ADCは、77dBFSのSNRを達成します。これにより、低いチェーン・ゲインで優れたSNRが確保されます。ADCのLVDS出力は、小型化されたシステムに求められる柔軟なシステム統合を可能にします。また、AFE5808は、低電力パッシブ・ミキサと低ノイズの加算アンプを内蔵しており、オンチップのCWDビームフォーマを実現できます。各アナログ入力信号に、16の選択可能な位相遅延を適用できます。さらに、独自の3次および5次高調波抑制フィルタの実装により、CW感度を強化しています。

AFE5808は15mm × 9mmの135ピンBGAパッケージで供給され、0°C～85°Cで仕様が規定されています。また、AFE5807とピン・コンパチブルです。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

図1. ブロック図

## 製品情報(1)

| 製品名     | パッケージの種類 | 動作         | 型番         | 出荷形態、数量 |

|---------|----------|------------|------------|---------|

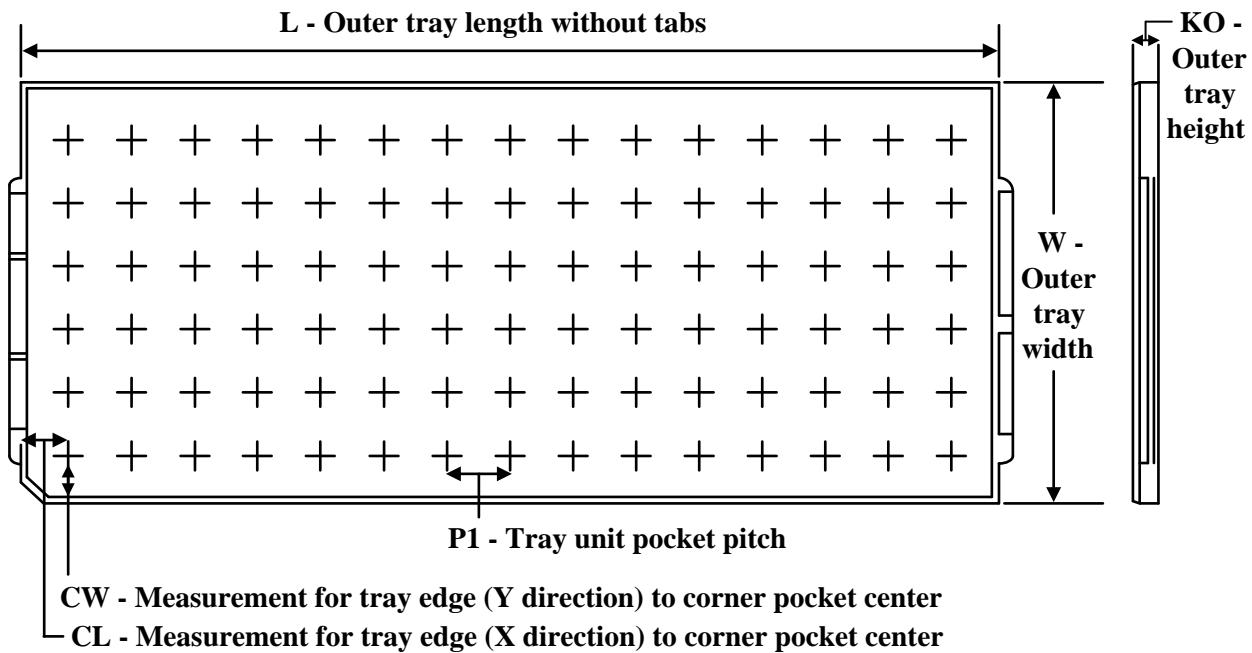

| AFE5808 | ZCF      | 0°C ~ 85°C | AFE5808ZCF | トレイ、160 |

(1) 最新のパッケージおよびご発注情報については、このデータシートの巻末にある「付録：パッケージ・オプション」を参照するか、TIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                        |          | VALUE |                     | 単位 |

|------------------------|----------|-------|---------------------|----|

|                        |          | MAX   | MIN                 |    |

| 電源電圧範囲                 | AVDD     | -0.3  | 3.9                 | V  |

|                        | AVDD_ADC | -0.3  | 2.2                 | V  |

|                        | AVDD_5V  | -0.3  | 6                   | V  |

|                        | DVDD     | -0.3  | 2.2                 | V  |

| AVSS-LVSS間の電圧          |          | -0.3  | 0.3                 | V  |

| アナログ入力およびデジタル入力の電圧     |          | -0.3  | min [3.6, AVDD+0.3] | V  |

| ピーク半田温度 <sup>(2)</sup> |          |       | 260                 | °C |

| 最大接合部温度( $T_J$ )、任意の条件 |          |       | 105                 | °C |

| 保存温度範囲                 |          | -55   | 150                 | °C |

| 動作温度範囲                 |          | 0     | 85                  | °C |

| ESD定格                  | HBM      |       | 2000                | V  |

|                        | CDM      |       | 500                 | V  |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作は含まれていません。

絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) デバイスはJSTD-020Dに準拠しています。

## 熱特性について

| 熱特性 <sup>(1)</sup> | AFE5808         | 単位   |

|--------------------|-----------------|------|

|                    | BGA             |      |

|                    | 135 135ピン       |      |

| $\theta_{JA}$      | 接合部-周囲間熱抵抗      | 34.1 |

| $\theta_{JCtop}$   | 接合部-ケース(上面)間熱抵抗 | 5    |

| $\theta_{JB}$      | 接合部-基板間熱抵抗      | 11.5 |

| $\psi_{JT}$        | 接合部-上面間特性パラメータ  | 0.2  |

| $\psi_{JB}$        | 接合部-基板間特性パラメータ  | 10.8 |

| $\theta_{JCbot}$   | 接合部-ケース(底面)間熱抵抗 | n/a  |

(1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

## 推奨動作条件

| パラメータ       | MIN  | MAX | 単位 |

|-------------|------|-----|----|

| AVDD        | 3.15 | 3.6 | V  |

| AVDD_ADC    | 1.7  | 1.9 | V  |

| DVDD        | 1.7  | 1.9 | V  |

| AVDD_5V     | 4.75 | 5.5 | V  |

| 周囲温度、 $T_A$ | 0    | 85  | °C |

## ピン配置情報

上面図 ZCF(BGA-135)

|   | 1            | 2            | 3        | 4      | 5        | 6        | 7       | 8          | 9        |

|---|--------------|--------------|----------|--------|----------|----------|---------|------------|----------|

| A | AVDD         | INP8         | INP7     | INP6   | INP5     | INP4     | INP3    | INP2       | INP1     |

| B | CM_BYP       | ACT8         | ACT7     | ACT6   | ACT5     | ACT4     | ACT3    | ACT2       | ACT1     |

| C | AVSS         | INM8         | INM7     | INM6   | INM5     | INM4     | INM3    | INM2       | INM1     |

| D | AVSS         | AVSS         | AVSS     | AVSS   | AVSS     | AVSS     | AVSS    | AVDD       | AVDD     |

| E | CW_IP_AMPINP | CW_IP_AMPINM | AVSS     | AVSS   | AVSS     | AVSS     | AVSS    | AVDD       | AVDD     |

| F | CW_IP_OUTM   | CW_IP_OUTP   | AVSS     | AVSS   | AVSS     | AVSS     | AVSS    | CLKP_16X   | CLKM_16X |

| G | AVSS         | AVSS         | AVSS     | AVSS   | AVSS     | AVSS     | AVSS    | CLKP_1X    | CLKM_1X  |

| H | CW_QP_OUTM   | CW_QP_OUTP   | AVSS     | AVSS   | AVSS     | AVSS     | AVSS    | PDN_GLOBAL | RESET    |

| J | CW_QP_AMPINP | CW_QP_AMPINM | AVSS     | AVSS   | AVDD_ADC | AVDD_ADC | PDN_VCA | SCLK       |          |

| K | AVDD         | AVDD_5V      | VCNTLP   | VCNTLM | VHIGH    | AVSS     | DNC     | AVDD_ADC   | SDATA    |

| L | CLKP_ADC     | CLKM_ADC     | AVDD_ADC | REFM   | DNC      | DNC      | DNC     | PDN_ADC    | SEN      |

| M | AVDD_ADC     | AVDD_ADC     | VREF_IN  | REFP   | DNC      | DNC      | DNC     | DNC        | SDOUT    |

| N | D8P          | D8M          | DVDD     | DNC    | DVSS     | DNC      | DVDD    | D1M        | D1P      |

| P | D7M          | D6M          | D5M      | FCLKM  | DVSS     | DCLKM    | D4M     | D3M        | D2M      |

| R | D7P          | D6P          | D5P      | FCLKP  | DVSS     | DCLKP    | D4P     | D3P        | D2P      |

## ピン機能

| ピン                                                           |              | 説明                                                                                                                                                                       |

|--------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号                                                           | 名前           |                                                                                                                                                                          |

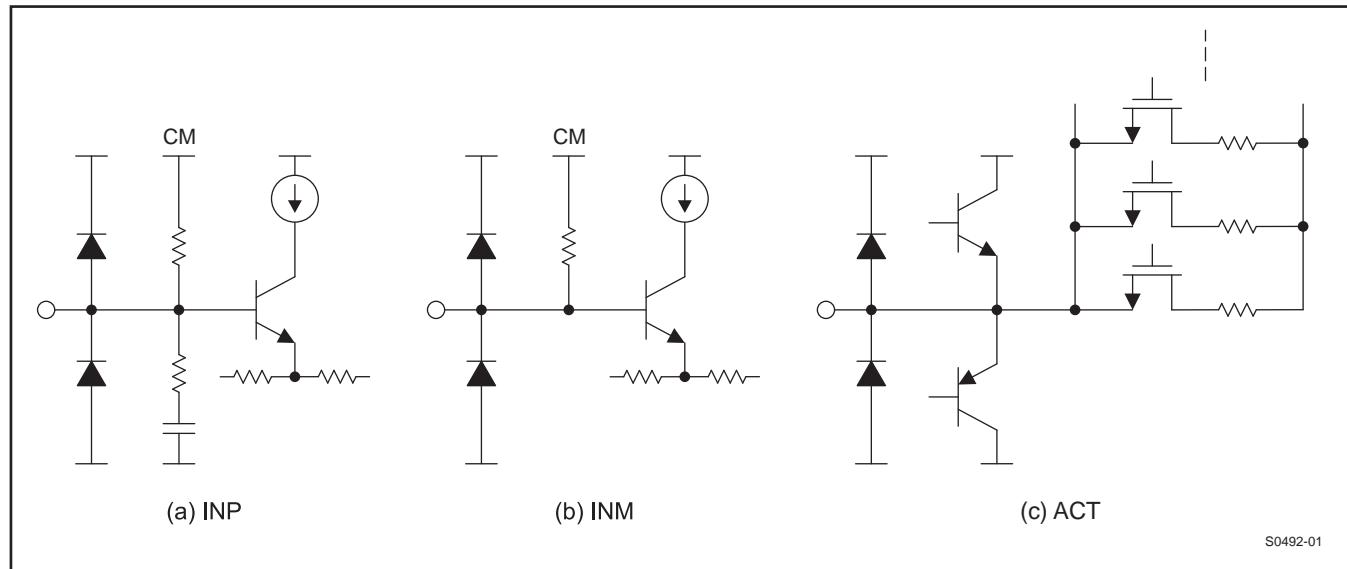

| B9~B2                                                        | ACT1...ACT8  | CH1~8のアクティブ終端入力ピン。1 μFのコンデンサを推奨します。<br>「アプリケーション情報」を参照してください。                                                                                                            |

| A1, D8, D9,<br>E8, E9, K1                                    | AVDD         | LNA、VCAT、PGA、LPF、およびCWDブロックの3.3Vアナログ電源。                                                                                                                                  |

| K2                                                           | AVDD_5V      | LNA、VCAT、PGA、LPF、およびCWDブロックの5.0Vアナログ電源。                                                                                                                                  |

| J6, J7, K8, L3,<br>M1, M2                                    | AVDD_ADC     | ADCの1.8Vアナログ電源。                                                                                                                                                          |

| C1, D1~D7,<br>E3~E7, F3~F7,<br>G1~G7,<br>H3~H7, J3~J5,<br>K6 | AVSS         | アナログ・グランド。                                                                                                                                                               |

| L2                                                           | CLKM_ADC     | 差動ADCクロックの負入力。シングルエンド・クロック・モードでは、直接または0.1μFのコンデンサを介してGNDに接続できます。                                                                                                         |

| L1                                                           | CLKP_ADC     | 差動ADCクロックの正入力。シングルエンド・クロック・モードでは、直接または0.1μFのコンデンサを介してクロック信号に接続できます。                                                                                                      |

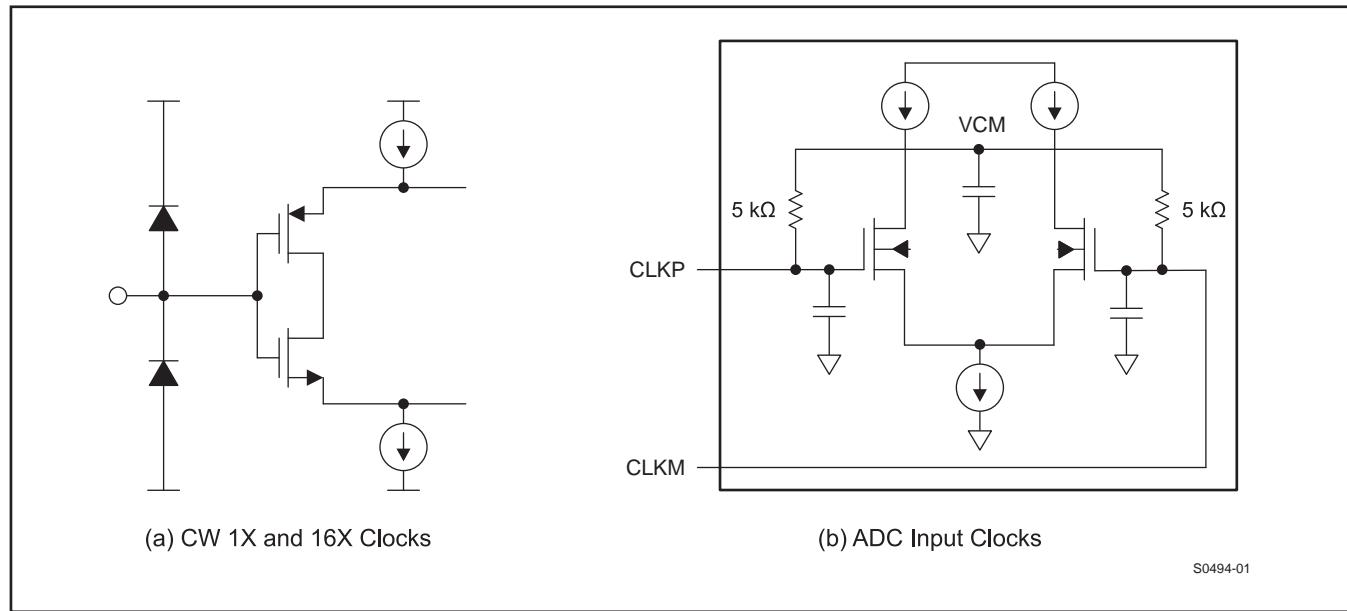

| F9                                                           | CLKM_16X     | CW 16Xクロックの負入力。CMOSクロック・モードがイネーブルのときは、GNDに接続します。4Xおよび8X CWクロック・モードの場合、このピンは4Xまたは8X CLKM入力となります。1X CWクロック・モードの場合、このピンはCWミキサの直角位相1X CLKMとなります。CWモードを使用しない場合は、フローティングにできます。 |

| F8                                                           | CLKP_16X     | CW 16Xクロックの正入力。4Xおよび8Xクロック・モードの場合、このピンは4Xまたは8X CLKP入力となります。1X CWクロック・モードの場合、このピンはCWミキサの直角位相1X CLKPとなります。CWモードを使用しない場合は、フローティングにできます。                                     |

| G9                                                           | CLKM_1X      | CW 1Xクロックの負入力。CMOSクロック・モードがイネーブルのときは、GNDに接続します(詳細は図88を参照)。1Xクロック・モードの場合、このピンはCWミキサの同相1X CLKMとなります。CWモードを使用しない場合は、フローティングにできます。                                           |

| G8                                                           | CLKP_1X      | CW 1Xクロックの正入力。1Xクロック・モードの場合、このピンはCWミキサの同相1X CLKPとなります。CWモードを使用しない場合は、フローティングにできます。                                                                                       |

| B1                                                           | CM_BYP       | バイアス電圧、グランドにバイパス。1μF以上を推奨します。超低周波ノイズを抑制するには、10μFを使用できます。                                                                                                                 |

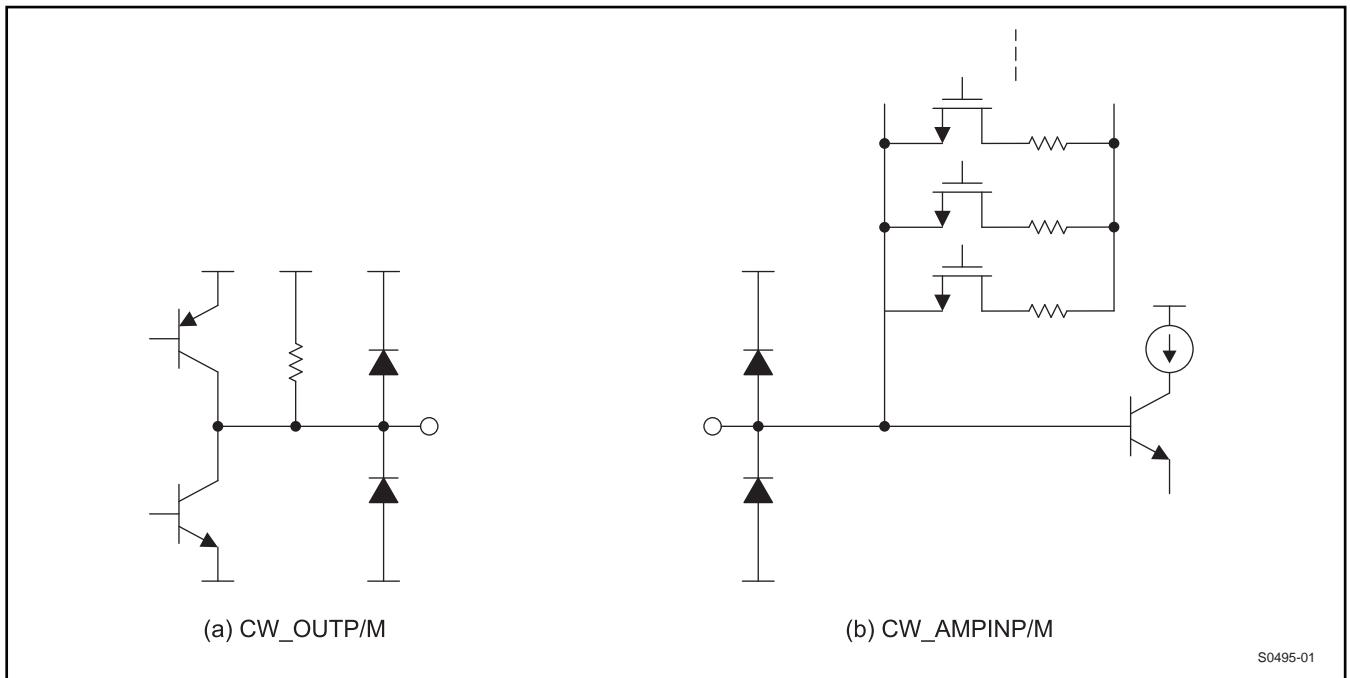

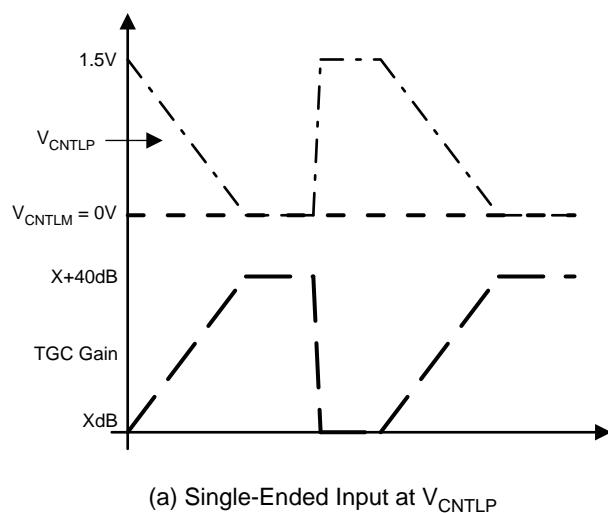

| E2                                                           | CW_IP_AMPINM | 同相加算アンプの負差動入力。CW_IP_AMPINMとCW_IP_OUTPの間に外部LPFコンデンサを接続する必要があります。PGAテスト・モードがイネーブルの場合、このピンはCH7 PGA負出力となります。未使用時は、フローティングにできます。                                              |

## ピン機能

| ピン                             |              | 説明                                                                                                                            |

|--------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| 番号                             | 名前           |                                                                                                                               |

| E1                             | CW_IP_AMPINP | 同相加算アンプの正差動入力。CW_IP_AMPINPとCW_IP_OUTMの間に外部LPFコンデンサを接続する必要があります。PGAテスト・モードがイネーブルの場合、このピンはCH7 PGA正出力となります。未使用時は、フローティングにできます。   |

| F1                             | CW_IP_OUTM   | 同相加算アンプの負差動出力。CW_IP_AMPINPとCW_IP_OUTPMの間に外部LPFコンデンサを接続する必要があります。未使用時は、フローティングにできます。                                           |

| F2                             | CW_IP_OUTP   | 同相加算アンプの正差動出力。CW_IP_AMPINMとCW_IP_OUTPの間に外部LPFコンデンサを接続する必要があります。未使用時は、フローティングにできます。                                            |

| J2                             | CW_QP_AMPINM | 直角位相加算アンプの負差動入力。CW_QP_AMPINMとCW_QP_OUTPの間に外部LPFコンデンサを接続する必要があります。PGAテスト・モードがイネーブルの場合、このピンはCH8 PGA負出力となります。未使用時は、フローティングにできます。 |

| J1                             | CW_QP_AMPINP | 直角位相加算アンプの正差動入力。CW_QP_AMPINPとCW_QP_OUTMの間に外部LPFコンデンサを接続する必要があります。PGAテスト・モードがイネーブルの場合、このピンはCH8 PGA正出力となります。未使用時は、フローティングにできます。 |

| H1                             | CW_QP_OUTM   | 直角位相加算アンプの負差動出力。CW_QP_AMPINPとCW_QP_OUTMの間に外部LPFコンデンサを接続する必要があります。未使用時は、フローティングにできます。                                          |

| H2                             | CW_QP_OUTP   | 直角位相加算アンプの正差動出力。CW_QP_AMPINMとCW_QP_OUTPの間に外部LPFコンデンサを接続する必要があります。未使用時は、フローティングにできます。                                          |

| N8, P9~P7,<br>P3~P1, N2        | D1M~D8M      | ADC CH1~8のLVDS負出力                                                                                                             |

| N9, R9~R7,<br>R3~R1, N1        | D1P~D8P      | ADC CH1~8のLVDS正出力                                                                                                             |

| P6                             | DCLKM        | LVDSビット・クロック(7x)負出力                                                                                                           |

| R6                             | DCLKP        | LVDSビット・クロック(7x)正出力                                                                                                           |

| K7,<br>L5~L7,M5~M8,<br>N4, N6  | DNC          | 接続しません。フローティングのままにする必要があります。                                                                                                  |

| N3, N7                         | DVDD         | ADCデジタルおよびI/O電源、1.8V                                                                                                          |

| N5, P5, R5                     | DVSS         | ADCデジタル・グランド                                                                                                                  |

| P4                             | FCLKM        | LVDSフレーム・クロック(1X)負出力                                                                                                          |

| R4                             | FCLKP        | LVDSフレーム・クロック(1X)正出力                                                                                                          |

| C9~C2                          | INM1...INM8  | CH1~8の相補アナログ入力。0.015μF以上のコンデンサでグランドにバイパスします。<br>LNAのHPF応答はコンデンサに依存します。                                                        |

| A9~A2                          | INP1...INP8  | CH1~8のアナログ入力。0.1μF以上のコンデンサで入力にAC結合します。                                                                                        |

| L8                             | PDN_ADC      | ADCの部分(高速)パワーダウン制御ピン。100kΩの内部プルダウン抵抗搭載。アクティブ・ハイ。                                                                              |

| J8                             | PDN_VCA      | VCAの部分(高速)パワーダウン制御ピン。20kΩの内部プルダウン抵抗搭載。アクティブ・ハイ。                                                                               |

| H8                             | PDN_GLOBAL   | チップ全体のグローバル(完全)パワーダウン制御ピン。20kΩの内部プルダウン抵抗搭載。<br>アクティブ・ハイ。                                                                      |

| L4                             | REFM         | 内部リファレンス・モードの0.05Vリファレンス出力。内部リファレンス・モードの場合は、フローティングのままにする必要があります。リファレンス出力のモニタ用に、PCB上にテスト・ポイントを追加することを推奨します。                   |

| M4                             | REFP         | 内部リファレンス・モードの1.5Vリファレンス出力。内部リファレンス・モードの場合は、フローティングのままにする必要があります。リファレンス出力のモニタ用に、PCB上にテスト・ポイントを追加することを推奨します。                    |

| H9                             | RESET        | ハードウェア・リセット・ピン。20kΩの内部プルダウン抵抗を搭載。アクティブ・ハイ。                                                                                    |

| J9                             | SCLK         | シリアル・インターフェイス・クロック入力。20kΩの内部プルダウン抵抗を搭載。                                                                                       |

| K9                             | SDATA        | シリアル・インターフェイス・データ入力。20kΩの内部プルダウン抵抗を搭載。                                                                                        |

| M9                             | SDOUT        | シリアル・インターフェイスのデータ読み出し。<br>読み出しがディスエーブルのときは、ハイ・インピーダンスです。                                                                      |

| L9                             | SEN          | シリアル・インターフェイス・イネーブル。20kΩの内部プルアップ抵抗を搭載。アクティブ・ロー。                                                                               |

| K4                             | VCNTLM       | 負の差動減衰制御ピン。                                                                                                                   |

| K3                             | VCNTLP       | 正の差動減衰制御ピン。                                                                                                                   |

| K5                             | VHIGH        | バイアス電圧。1μF以上でグランドにバイパス。                                                                                                       |

| M3                             | VREF_IN      | 外部リファレンス・モードのADC 1.4Vリファレンス入力。0.1μFでグランドにバイパスします。                                                                             |

| K7, L5~L7,<br>M5~M8, N4,<br>N6 | DNC          | 接続しません。フローティングのままにする必要があります。                                                                                                  |

## 電気的特性

特に記述のない限り、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8V、INPを0.1 $\mu$ FでAC結合、INMを15nFでグランドにバイパス、アクティブ終端なし、 $V_{CNTL}$  = 0V、 $f_{IN}$  = 5MHz、LNA = 18dB、PGA = 24dB、14ビット、サンプル・レート = 65MSPS、LPFフィルタ = 15MHz、低ノイズ・モード、 $V_{OUT}$  = -1dBFS、内部500 $\Omega$  CW帰還抵抗、CMOS CWクロック、ADCを内部リファレンス・モードに設定、シングルエンドVCNTLモード、VCNTLM = GND、周囲温度 $T_A$  = 25°C。最小値および最大値は、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8Vで温度範囲全体にわたって規定されています。

| パラメータ                                 | 測定条件                                        | MIN                                                                   | TYP            | MAX     | 単位         |

|---------------------------------------|---------------------------------------------|-----------------------------------------------------------------------|----------------|---------|------------|

| TGCフル信号チャネル (LNA+VCAT+LPF+ADC)        |                                             |                                                                       |                |         |            |

| en (RTI)                              | LNAゲインに対する入力電圧ノイズ<br>(低ノイズ・モード)             | Rs = 0 $\Omega$ , f = 2MHz, LNA = 24/18/12dB, PGA = 24dB              | 0.76/0.83/1.16 |         | nV/rtHz    |

|                                       |                                             | Rs = 0 $\Omega$ , f = 2MHz, LNA = 24/18/12dB, PGA = 30dB              | 0.75/0.86/1.12 |         |            |

|                                       | LNAゲインに対する入力電圧ノイズ<br>(低電力モード)               | Rs = 0 $\Omega$ , f = 2MHz, LNA = 24/18/12dB, PGA = 24dB              | 1.1/1.2/1.45   | nV/rtHz |            |

|                                       |                                             | Rs = 0 $\Omega$ , f = 2MHz, LNA = 24/18/12dB, PGA = 30dB              | 1.1/1.2/1.45   |         |            |

|                                       | LNAゲインに対する入力電圧ノイズ<br>(中電力モード)               | Rs = 0 $\Omega$ , f = 2MHz, LNA = 24/18/12dB, PGA = 24dB              | 1/1.05/1.25    | nV/rtHz |            |

|                                       |                                             | Rs = 0 $\Omega$ , f = 2MHz, LNA = 24/18/12dB, PGA = 30dB              | 0.95/1.0/1.2   |         |            |

| 入力基準電流ノイズ                             |                                             |                                                                       | 2.7            |         | pA/rtHz    |

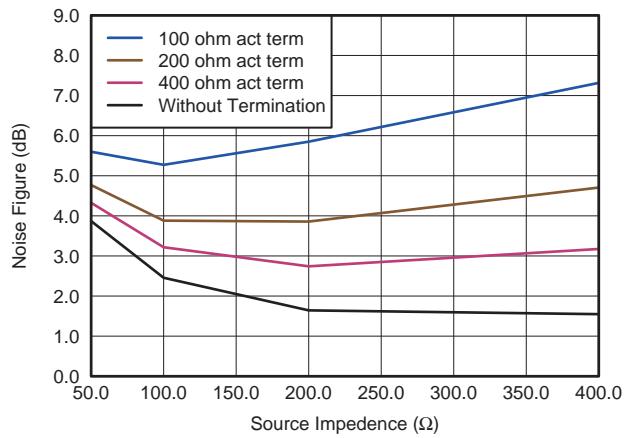

| NF                                    | ノイズ指数                                       | Rs = 200 $\Omega$ , 200 $\Omega$ アクティブ終端、PGA = 24dB, LNA = 12/18/24dB | 3.85/2.4/1.8   |         | dB         |

|                                       |                                             | Rs = 100 $\Omega$ , 100 $\Omega$ アクティブ終端、PGA = 24dB, LNA = 12/18/24dB | 5.3/3.1/2.3    |         | dB         |

| $V_{MAX}$                             | 最大直線入力電圧                                    | LNAゲイン = 24/18/12dB                                                   | 250/500/1000   |         | mVpp       |

| $V_{CLAMP}$                           | クランプ電圧                                      | Reg52[10:9] = 0, LNA = 24/18/12dB                                     | 350/600/1150   |         |            |

| PGAゲイン                                | 低ノイズ・モード                                    |                                                                       | 24/30          |         | dB         |

|                                       | 中/低電力モード                                    |                                                                       | 24/28.5        |         |            |

| 合計ゲイン                                 | LNA = 24dB, PGA = 30dB, 低ノイズ・モード            |                                                                       | 54             |         | dB         |

|                                       | LNA = 24dB, PGA = 30dB, 中電力モード              |                                                                       | 52.5           |         |            |

|                                       | LNA = 24dB, PGA = 30dB, 低電力モード              |                                                                       | 52.5           |         |            |

| チャネル間ノイズ相関係数<br>(信号なし) <sup>(1)</sup> | 8チャネルの合計                                    |                                                                       | 0              |         |            |

| チャネル間ノイズ相関係数<br>(信号あり) <sup>(1)</sup> | 全帯域(VCNTL = 0/0.8)                          |                                                                       | 0.15/0.17      |         |            |

|                                       | 搬送波から1MHzの帯域(VCNTL = 0/0.8)                 |                                                                       | 0.18/0.75      |         |            |

| 信号対雑音比(SNR)                           | VCNTL = 0.6V(合計チャネル・ゲイン22dB)                | 68                                                                    | 70             |         | dBFS       |

|                                       | VCNTL = 0, LNA = 18dB, PGA = 24dB           | 59.3                                                                  | 63             |         |            |

|                                       | VCNTL = 0, LNA = 24dB, PGA = 24dB           |                                                                       | 58             |         |            |

| ナロー・バンドSNR                            | 搬送波周辺の2MHz帯域でのSNR(VCNTL = 0.6V時)(合計ゲイン22dB) | 75                                                                    | 77             |         | dBFS       |

| 入力同相モード電圧                             | INPおよびINMピン                                 |                                                                       | 2.4            |         | V          |

| 入力抵抗                                  |                                             |                                                                       | 8              |         | k $\Omega$ |

|                                       | プリセット・アクティブ終端をイネーブル                         |                                                                       | 50/100/200/400 |         | $\Omega$   |

| 入力容量                                  |                                             |                                                                       | 20             |         | pF         |

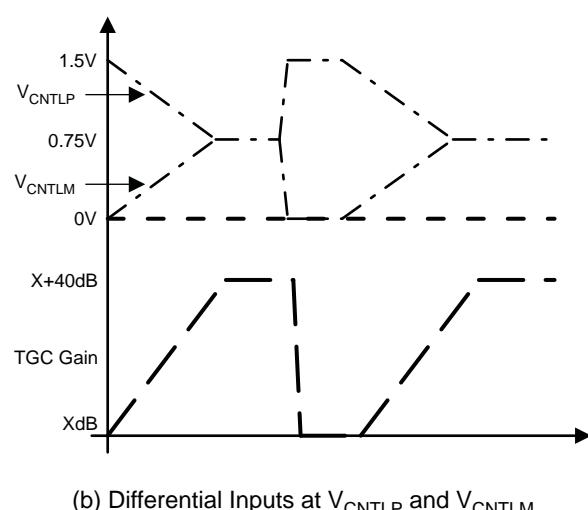

| 入力制御電圧                                | VCNTLP-VCNTLM                               | 0                                                                     | 1.5            |         | V          |

| 同相モード電圧                               | VCNTLP および VCNTLM                           |                                                                       | 0.75           |         | V          |

| ゲイン範囲                                 |                                             |                                                                       | -40            |         | dB         |

| ゲイン・スローブ                              | $V_{CNTL}$ = 0.1V ~ 1.1V                    |                                                                       | 35             |         | dB/V       |

| 入力抵抗                                  | VCNTLP - VCNTLM間                            |                                                                       | 200            |         | k $\Omega$ |

| 入力容量                                  | VCNTLP - VCNTLM間                            |                                                                       | 1              |         | pF         |

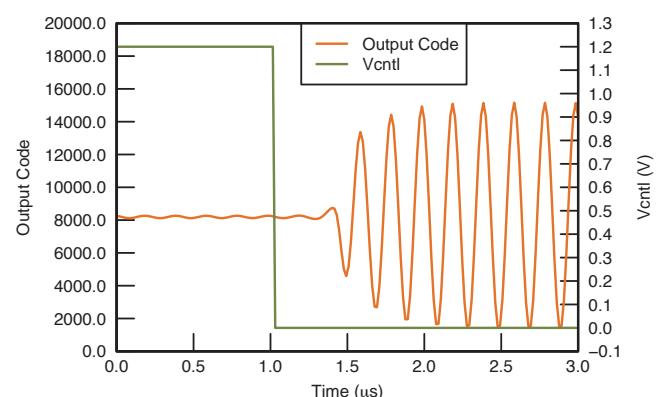

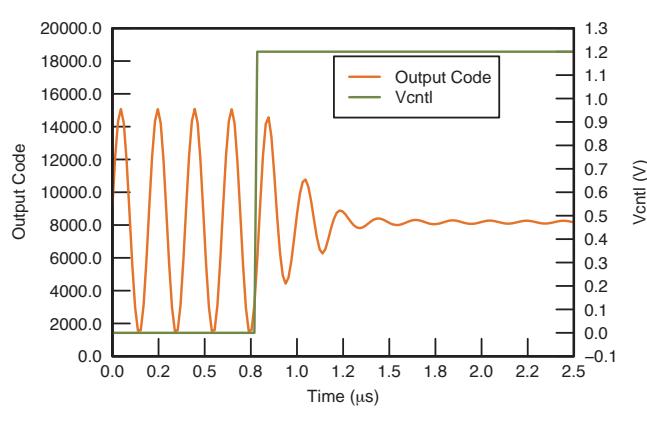

| TGC応答時間                               | VCNTL = 0V ~ 1.5V ステップ閏数                    |                                                                       | 1.5            |         | $\mu$ s    |

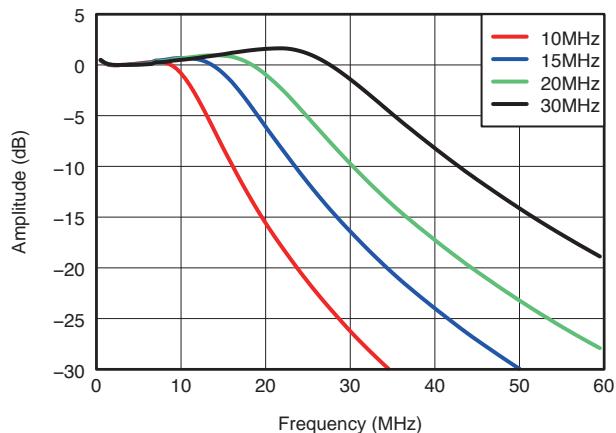

| 3次ローバス・フィルタ                           |                                             |                                                                       | 10, 15, 20, 30 |         | MHz        |

| LNAゲインの変化に対するセトリング・タイム                |                                             |                                                                       | 14             |         | $\mu$ s    |

| アクティブ終端設定の変化に対する<br>セトリング・タイム         |                                             |                                                                       | 1              |         | $\mu$ s    |

(1) ノイズ相関係数は、 $N_c/(N_u+N_c)$  として定義されます。ここで、 $N_c$ は単一チャネルの相関ノイズ電力、 $N_u$ は単一チャネルの非相関ノイズ電力です。

測定値は、次の式に従います。ここでは、単一チャネル信号のSNRと8チャネル合計信号のSNRが測定されます。

$$\frac{N_c}{N_u + N_c} = \frac{10 - \frac{8 \text{CH\_SNR}}{1 \text{CH\_SNR}}}{10 - \frac{1 \text{CH\_SNR}}{10}} \times \frac{1}{\frac{56}{55}} - \frac{1}{7}$$

## 電気的特性

特に記述のない限り、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8V、INPを0.1 $\mu$ FでAC結合、INMを15nFでグランドにバイパス、アクティブ終端なし、 $V_{CNTL}$ = 0V、 $f_{IN}$  = 5MHz、LNA = 18dB、PGA = 24dB、14ビット、サンプル・レート = 65MSPS、LPFフィルタ = 15MHz、低ノイズ・モード、 $V_{OUT}$  = -1dBFS、内部500 $\Omega$  CW帰還抵抗、CMOS CWクロック、ADCを内部リファレンス・モードに設定、シングルエンドVCNTLモード、VCNTLM = GND、周囲温度 $T_A$  = 25°C。最小値および最大値は、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8Vで温度範囲全体にわたって規定されています。

| パラメータ            | 測定条件                                                                          | MIN            | TYP  | MAX | 単位      |

|------------------|-------------------------------------------------------------------------------|----------------|------|-----|---------|

| <b>AC精度</b>      |                                                                               |                |      |     |         |

| LPF帯域幅公差         |                                                                               | ±5%            |      |     |         |

| チャネル間群遅延変動       | 2MHz ~ 15MHz                                                                  | 2              |      |     | ns      |

| チャネル間位相変動        | 15MHz 信号                                                                      | 11             |      |     | Degree  |

| ゲイン・マッチング        | 0V < VCNTL < 0.1V (デバイス間)                                                     | ±0.5           |      |     | dB      |

|                  | 0.1V < VCNTL < 1.1V (デバイス間)                                                   | -0.9           | ±0.5 | 0.9 |         |

|                  | 0.1V < VCNTL < 1.1V (デバイス間)、温度 = 0°C および 85°C                                 | -1.1           | ±0.5 | 1.1 |         |

|                  | 1.1V < VCNTL < 1.5V (デバイス間)                                                   | ±0.5           |      |     |         |

| ゲイン・マッチング        | チャネル間                                                                         | ±0.25          |      |     | dB      |

| 出力オフセット          | VCNTL = 0, PGA = 30dB, LNA = 24dB                                             | -75            | 75   |     | LSB     |

| <b>AC性能</b>      |                                                                               |                |      |     |         |

| HD2 2次高調波歪       | Fin = 2MHz; $V_{OUT}$ = -1dBFS                                                | -60            |      |     | dBc     |

|                  | Fin = 5MHz; $V_{OUT}$ = -1dBFS                                                | -60            |      |     |         |

|                  | Fin = 5MHz; $V_{IN}$ = 500mVpp, $V_{OUT}$ = -1dBFS, LNA = 18dB, VCNTL = 0.88V | -55            |      |     |         |

|                  | Fin = 5MHz; $V_{IN}$ = 250mVpp, $V_{OUT}$ = -1dBFS, LNA = 24dB, VCNTL = 0.88V | -55            |      |     |         |

| HD3 3次高調波歪       | Fin = 2MHz; $V_{OUT}$ = -1dBFS                                                | -55            |      |     | dBc     |

|                  | Fin = 5MHz; $V_{OUT}$ = -1dBFS                                                | -55            |      |     |         |

|                  | Fin = 5MHz; $V_{IN}$ = 500mVpp, $V_{OUT}$ = -1dBFS, LNA = 18dB, VCNTL = 0.88V | -55            |      |     |         |

|                  | Fin = 5MHz; $V_{IN}$ = 250mVpp, $V_{OUT}$ = -1dBFS, LNA = 24dB, VCNTL = 0.88V | -55            |      |     |         |

| THD 全高調波歪        | Fin = 2MHz; $V_{OUT}$ = -1dBFS                                                | -55            |      |     | dBc     |

|                  | Fin = 5MHz; $V_{OUT}$ = -1dBFS                                                | -55            |      |     |         |

| IMD3 相互変調歪       | f1 = 5MHz (-1dBFS)、f2 = 5.01MHz (-27dBFS)                                     | -60            |      |     | dBc     |

| XTALK クロストーク     | Fin = 5MHz; $V_{OUT}$ = -1dBFS                                                | -65            |      |     | dB      |

|                  | 5MHz から 1kHz (VCNTL= 0V)                                                      | -132           |      |     | dBc/Hz  |

| <b>LNA</b>       |                                                                               |                |      |     |         |

| 入力基準電圧ノイズ        | $R_s$ = 0 $\Omega$ , f = 2MHz, $R_{in}$ = High Z, ゲイン = 24/18/12dB            | 0.63/0.70/0.9  |      |     | nV/rtHz |

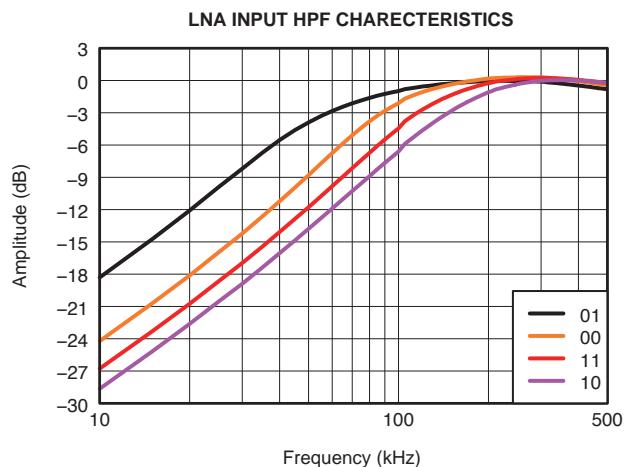

| ハイパス・フィルタ        | -3dBカットオフ周波数                                                                  | 50/100/150/200 |      |     | kHz     |

| LNAリニア出力         |                                                                               | 4              |      |     | Vpp     |

| <b>VCAT+PGA</b>  |                                                                               |                |      |     |         |

| VCAT入力ノイズ        | 0dB/-40dB減衰                                                                   | 2/10.5         |      |     | nV/rtHz |

| PGA入力ノイズ         | 24dB/30dB                                                                     | 1.75           |      |     | nV/rtHz |

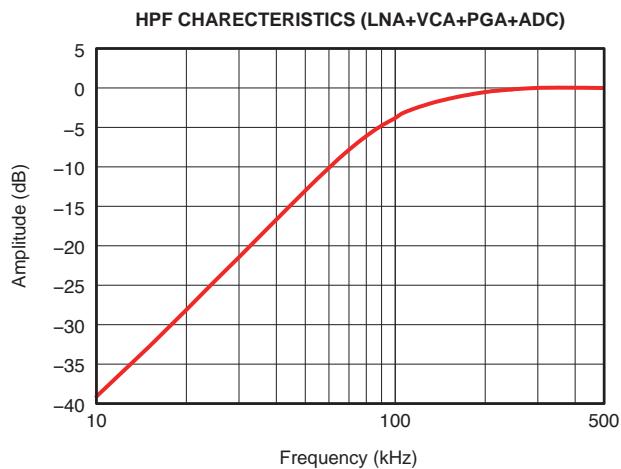

| -3dB HPFカットオフ周波数 |                                                                               | 80             |      |     | kHz     |

## 電気的特性

特に記述のない限り、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8V、INPを0.1 $\mu$ FでAC結合、INMを15nFでグランドにバイパス、アクティブ終端なし、 $V_{\text{CNTL}} = 0V$ 、 $f_{\text{IN}} = 5\text{MHz}$ 、LNA = 18dB、PGA = 24dB、14ビット、サンプル・レート = 65MSPS、LPFフィルタ = 15MHz、低ノイズ・モード、 $V_{\text{OUT}} = -1\text{dBFS}$ 、内部500 $\Omega$  CW帰還抵抗、CMOS CWクロック、ADCを内部リファレンス・モードに設定、シングルエンドVCNTLモード、VCNTLM = GND、周囲温度 $T_A = 25^\circ\text{C}$ 。最小値および最大値は、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8Vで温度範囲全体にわたって規定されています。

| パラメータ                          | 測定条件                                                                                              | MIN         | TYP | MAX | 単位            |

|--------------------------------|---------------------------------------------------------------------------------------------------|-------------|-----|-----|---------------|

| <b>CWドップラー</b>                 |                                                                                                   |             |     |     |               |

| en (RTI) 入力電圧ノイズ(CW)           | 1チャネル・ミキサ、LNA = 24dB、帰還抵抗500 $\Omega$                                                             | 0.8         |     |     | nV/rtHz       |

|                                | 8チャネル・ミキサ、LNA = 24dB、帰還抵抗62.5 $\Omega$                                                            | 0.33        |     |     |               |

| en (RTO) 出力電圧ノイズ(CW)           | 1チャネル・ミキサ、LNA = 24dB、帰還抵抗500 $\Omega$                                                             | 12          |     |     | nV/rtHz       |

|                                | 8チャネル・ミキサ、LNA = 24dB、帰還抵抗62.5 $\Omega$                                                            | 5           |     |     |               |

| en (RTI) 入力電圧ノイズ(CW)           | 1チャネル・ミキサ、LNA = 18dB、帰還抵抗500 $\Omega$                                                             | 1.1         |     |     | nV/rtHz       |

|                                | 8チャネル・ミキサ、LNA = 18dB、帰還抵抗62.5 $\Omega$                                                            | 0.5         |     |     |               |

| en (RTO) 出力電圧ノイズ(CW)           | 1チャネル・ミキサ、LNA = 18dB、帰還抵抗500 $\Omega$                                                             | 8.1         |     |     | nV/rtHz       |

|                                | 8チャネル・ミキサ、LNA = 18dB、帰還抵抗62.5 $\Omega$                                                            | 4.0         |     |     |               |

| NF ノイズ指数                       | $R_s = 100\Omega$ , $R_{IN} = \text{High Z}$ , $f_{IN} = 2\text{MHz}$ (LNA, I/Qミキサ、および加算アンプ/フィルタ) | 1.8         |     |     | dB            |

| $f_{CW}$ CW動作範囲 <sup>(2)</sup> | CW信号搬送波周波数                                                                                        | 8           |     |     | MHz           |

| CWクロック周波数                      | 1X CLK(16Xモード)                                                                                    | 8           |     |     | MHz           |

|                                | 16X CLK(16Xモード)                                                                                   | 128         |     |     |               |

|                                | 4X CLK(4Xモード)                                                                                     | 32          |     |     |               |

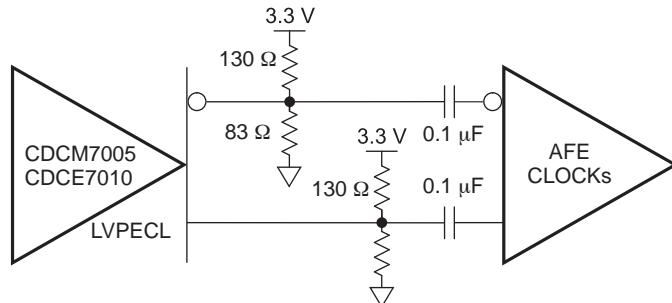

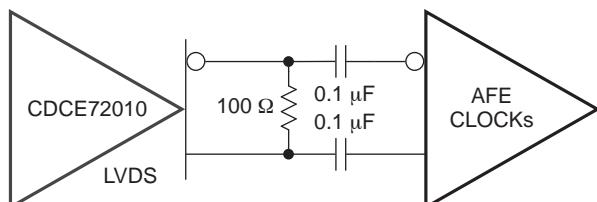

| AC結合LVDSクロック振幅                 |                                                                                                   | 0.7         |     |     | Vpp           |

| AC結合LVPECLクロック振幅               | CLKM_16X-CLKP_16X; CLKM_1X-CLKP_1X                                                                | 1.6         |     |     |               |

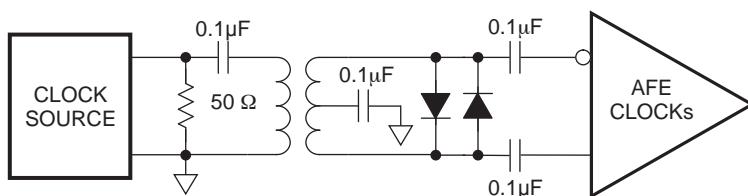

| CLKデューティ・サイクル                  | 1Xおよび16X CLK                                                                                      | 35%         |     | 65% |               |

| 同相モード電圧                        | 内部で提供                                                                                             | 2.5         |     |     | V             |

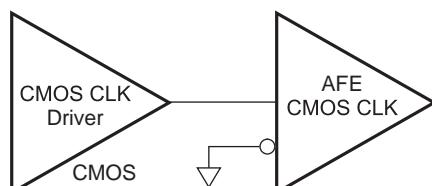

| $V_{CMOS}$ CMOS入力クロック振幅        |                                                                                                   | 4           |     | 5   | V             |

| CWミキサ変換損失                      |                                                                                                   | 4           |     |     | dB            |

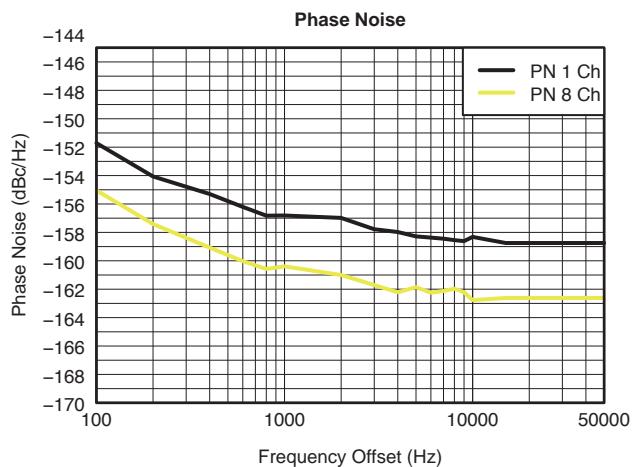

| CWミキサ位相ノイズ                     | 2MHz搬送波から1kHz                                                                                     | 156         |     |     | dBc/Hz        |

| DR 入力ダイナミック・レンジ                | $FIN = 2\text{MHz}$ , LNA = 24/18/12dB                                                            | 160/164/165 |     |     | dBFS/Hz       |

| IMD3 相互変調歪                     | $f_1 = 5\text{MHz}$ , $f_2 = 5.01\text{MHz}$ , 両トーンとも-8.5dBmの振幅、8チャネルを同相で加算、CW帰還抵抗 = 87 $\Omega$  | -50         |     |     | dBc           |

|                                | $f_1 = 5\text{MHz}$ , $f_2 = 5.01\text{MHz}$ , 両トーンとも-8.5dBmの振幅、单一チャネルの場合、CW帰還抵抗 = 500 $\Omega$   | -60         |     |     | dBc           |

| I/Qチャネル・ゲイン・マッチング              | 16X モード                                                                                           | $\pm 0.04$  |     |     | dB            |

| I/Qチャネル位相マッチング                 | 16X モード                                                                                           | $\pm 0.1$   |     |     | 度             |

| I/Qチャネル・ゲイン・マッチング              | 4X モード                                                                                            | $\pm 0.04$  |     |     | dB            |

| I/Qチャネル位相マッチング                 | 4X モード                                                                                            | $\pm 0.1$   |     |     | 度             |

| イメージ除去比                        | $fin = 2.01\text{MHz}$ , 入力振幅300mV、CWクロック周波数 = 2.00MHz                                            | -50         |     |     | dBc           |

| <b>CW加算アンプ</b>                 |                                                                                                   |             |     |     |               |

| $V_{CMO}$ 同相モード電圧              | 加算アンプの入力/出力                                                                                       | 1.5         |     |     | V             |

| 加算アンプ出力                        |                                                                                                   | 4           |     |     | Vpp           |

| 入力基準電圧ノイズ                      | 100Hz                                                                                             | 2           |     |     | nV/rtHz       |

|                                | 1kHz                                                                                              | 1.2         |     |     | nV/rtHz       |

|                                | 2kHz-100MHz                                                                                       | 1           |     |     | nV/rtHz       |

| 入力基準電流ノイズ                      |                                                                                                   | 2.5         |     |     | pA/rtHz       |

| ユニティ・ゲイン帯域幅                    |                                                                                                   | 200         |     |     | MHz           |

| 最大出力電流                         | 直線動作範囲                                                                                            | 20          |     |     | mApp          |

| <b>ADC仕様</b>                   |                                                                                                   |             |     |     |               |

| サンプル・レート                       |                                                                                                   | 10          |     | 65  | MSPS          |

| SNR 信号対雑音比                     | ADC 14bのアイドル・チャネルSNR                                                                              | 77          |     |     | dBFS          |

| 内部リファレンス・モード                   | REFP                                                                                              | 1.5         |     |     | V             |

|                                | REFM                                                                                              | 0.5         |     |     | V             |

| 外部リファレンス・モード                   | VREF_IN 電圧                                                                                        | 1.4         |     |     | V             |

|                                | VREF_IN 電流                                                                                        | 50          |     |     | $\mu\text{A}$ |

| ADC入力フルスケール範囲                  |                                                                                                   | 2           |     |     | Vpp           |

| LVDSレート                        | 14ビットで65MSPS                                                                                      | 910         |     |     | Mbps          |

- (2) In the 16X operation mode, the CW operation range is limited to 8MHz due to the 16X CLK. The maximum clock frequency for the 16X CLK is 128MHz. In the 8X, 4X, and 1X modes, higher CW signal frequencies up to 15 MHz can be supported with small degradation in performance, see application information: [CW clock selection](#).

## 電気的特性

特に記述のない限り、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8V、INPを0.1 $\mu$ FでAC結合、INMを15nFでグランドにバイパス、アクティブ終端なし、 $V_{CNTL}$ =0V、 $f_{IN}$ =5MHz、LNA = 18dB、PGA = 24dB、14ビット、サンプル・レート = 65MSPS、LPFフィルタ = 15MHz、低ノイズ・モード、 $V_{OUT}$ =-1dBFS、内部500 $\Omega$  CW帰還抵抗、CMOS CWクロック、ADCを内部リファレンス・モードに設定、シングルエンドVCNTLモード、VCNTLM = GND、周囲温度 $T_A$  = 25°C。最小値および最大値は、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8Vで温度範囲全体にわたって規定されています。

| パラメータ                | 測定条件                                                | MIN                  | TYP | MAX | 単位      |

|----------------------|-----------------------------------------------------|----------------------|-----|-----|---------|

| 消費電力                 |                                                     |                      |     |     |         |

| AVDD電圧               |                                                     | 3.15                 | 3.3 | 3.6 | V       |

| AVDD_ADC電圧           |                                                     | 1.7                  | 1.8 | 1.9 | V       |

| AVDD_5V電圧            |                                                     | 4.75                 | 5   | 5.5 | V       |

| DVDD電圧               |                                                     | 1.7                  | 1.8 | 1.9 | V       |

| チャネル毎の合計消費電力         | TGC低ノイズ・モード、65MSPS                                  | 153                  | 175 |     | mW/CH   |

|                      | TGC低ノイズ・モード、40MSPS                                  | 142                  |     |     |         |

|                      | TGC中電力モード、40MSPS                                    | 110                  |     |     |         |

|                      | TGC低電力モード、40MSPS                                    | 98                   |     |     |         |

| AVDD(3.3V)電流         | TGC低ノイズ・モード、信号なし                                    | 203                  | 235 |     | mA      |

|                      | TGC中電力モード、信号なし                                      | 126                  |     |     |         |

|                      | TGC低電力モード、信号なし                                      | 99                   |     |     |         |

|                      | CWモード、信号なし                                          | 147                  | 170 |     |         |

|                      | TGC低ノイズ・モード、500mVpp入力、1%デューティ・サイクル                  | 210                  |     |     |         |

|                      | TGC中電力モード、500mVpp入力、1%デューティ・サイクル                    | 133                  |     |     |         |

|                      | TGC低電力モード、500mVpp入力、1%デューティ・サイクル                    | 105                  |     |     |         |

|                      | CWモード、500mVpp入力                                     | 375                  |     |     |         |

| AVDD_5V電流            | TGCモード、信号なし                                         | 16.5                 | 22  |     | mA      |

|                      | CWモード、信号なし、16Xクロック = 32MHz                          | 32                   |     |     |         |

|                      | TGCモード、500mVpp入力、1%デューティ・サイクル                       | 16.5                 |     |     |         |

|                      | CWモード、500mVpp入力                                     | 42.5                 |     |     |         |

| VCA消費電力              | TGC低ノイズ・モード、信号なし                                    | 93.5                 | 107 |     | mW/CH   |

|                      | TGC中電力モード、信号なし                                      | 62                   |     |     |         |

|                      | TGC低電力モード、信号なし                                      | 50                   |     |     |         |

|                      | TGC低ノイズ・モード、500mVpp入力、1%デューティ・サイクル                  | 97                   |     |     |         |

|                      | TGC中電力モード、500mVpp入力、1%デューティ・サイクル                    | 65                   |     |     |         |

|                      | TGC低電力モード、500mVpp入力、1%デューティ・サイクル                    | 54                   |     |     |         |

| CW消費電力               | 信号なし、ADCシャットダウン、CWモード、16Xクロック = 32MHz               | 80                   |     |     | mW/CH   |

|                      | 500mVpp入力、ADCシャットダウン、16Xクロック = 32MHz                | 173                  |     |     |         |

| AVDD_ADC(1.8V)電流     | 65MSPS                                              | 187                  | 205 |     | mA      |

| DVDD(1.8V)電流         | 65MSPS                                              | 77                   | 110 |     | mA      |

| ADC消費電力/チャネル         | 65MSPS                                              | 59                   | 69  |     | mW/CH   |

|                      | 50MSPS                                              | 51                   |     |     |         |

|                      | 40MSPS                                              | 46                   |     |     |         |

|                      | 20MSPS                                              | 35                   |     |     |         |

| パワーダウン・モードの消費電力      | PDN_VCA = High, PDN_ADC = High                      | 25                   |     |     | mW/CH   |

|                      | 完全パワーダウン、PDN_Global = High                          | 0.6                  |     |     |         |

| パワーダウン応答時間           | パワーダウンに入るまでの所要時間                                    | 1                    |     |     | $\mu$ s |

| パワーアップ応答時間           | VCAパワーダウン                                           | 2 $\mu$ s + PDN時間の1% |     |     | $\mu$ s |

|                      | ADCパワーダウン                                           | 1                    |     |     |         |

|                      | 完全パワーダウン                                            | 2.5                  |     |     |         |

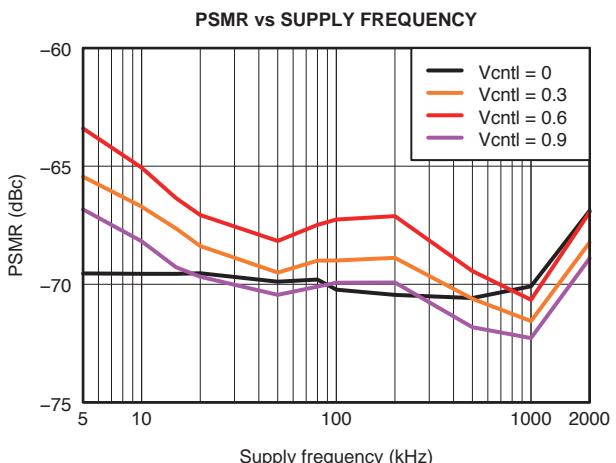

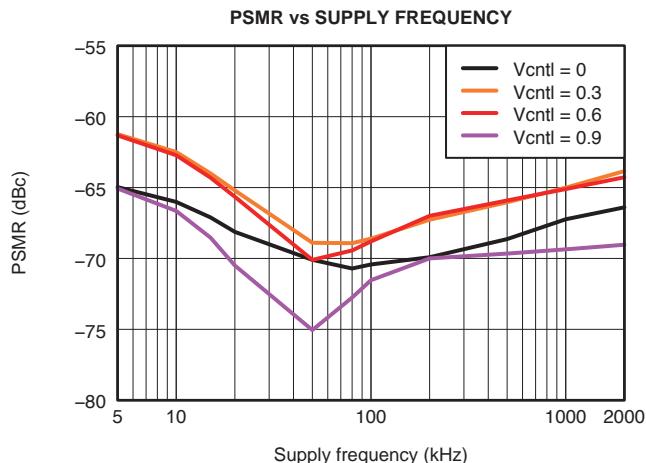

| 電源変調比、AVDDおよびAVDD_5V | $f_{IN}$ = 5MHz, 1kHzで電源に50mVppのノイズ <sup>(3)</sup>  | -65                  |     |     | dBc     |

|                      | $f_{IN}$ = 5MHz, 50kHzで電源に50mVppのノイズ <sup>(3)</sup> | -65                  |     |     | dBc     |

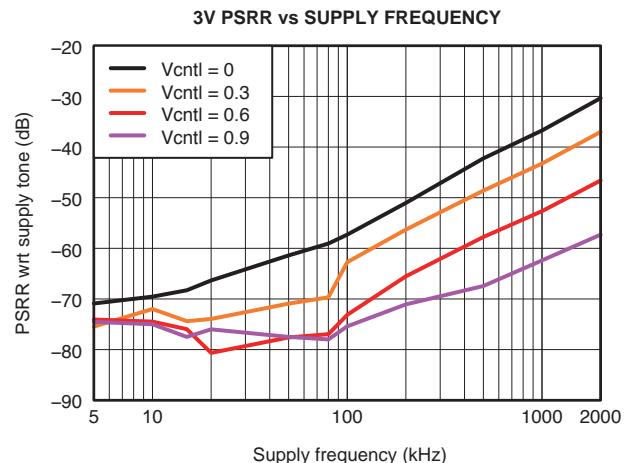

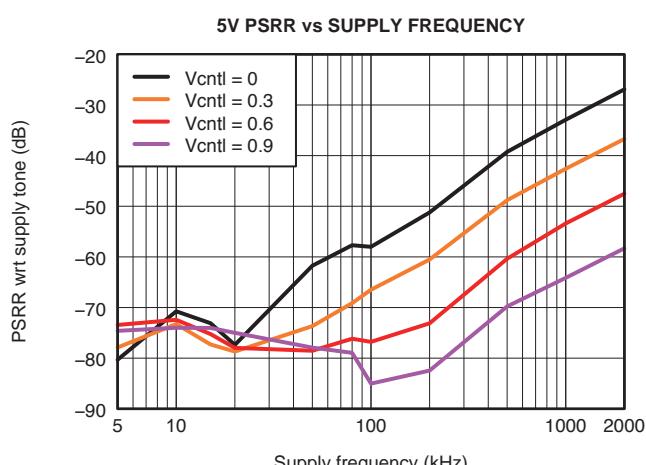

| 電源除去比                | $f$ = 10kHz, VCNTL = 0V (高ゲイン)、AVDD                 | -40                  |     |     | dBc     |

|                      | $f$ = 10kHz, VCNTL = 0V (高ゲイン)、AVDD_5V              | -55                  |     |     | dBc     |

|                      | $f$ = 10kHz, VCNTL = 1V (低ゲイン)、AVDD                 | -50                  |     |     | dBc     |

(3) PSMR仕様は、入力信号振幅を基準としています。

## デジタル特性

特に記述のない限り、標準値は+25°Cでの値、AVDD = 3.3V、AVDD\_5 = 5VおよびAVDD\_ADC = 1.8V、DVDD = 1.8Vです。最小値および最大値は温度範囲全体( $T_{MIN} = 0^{\circ}\text{C}$ ~ $T_{MAX} = +85^{\circ}\text{C}$ )での値です。

| パラメータ                                              | 条件                          | MIN  | TYP | MAX | 単位 <sup>(1)</sup> |

|----------------------------------------------------|-----------------------------|------|-----|-----|-------------------|

| <b>デジタル入出力</b>                                     |                             |      |     |     |                   |

| $V_{IH}$                                           | 論理High入力電圧                  | 2    | 3.3 |     | V                 |

| $V_{IL}$                                           | 論理Low入力電圧                   | 0    | 0.3 |     | V                 |

| 論理High入力電流                                         |                             | 200  |     |     | $\mu\text{A}$     |

| 論理Low入力電流                                          |                             | 200  |     |     | $\mu\text{A}$     |

| 入力容量                                               |                             | 5    |     |     | pF                |

| $V_{OH}$                                           | 論理High出力電圧                  | DVDD |     |     | V                 |

| $V_{OL}$                                           | 論理Low出力電圧                   | 0    |     |     | V                 |

| <b>LVDS出力</b>                                      |                             |      |     |     |                   |

| 出力差動電圧                                             | 100Ωの外部差動終端                 | 400  |     |     | mV                |

| 出力オフセット電圧                                          | 同相モード電圧                     | 1100 |     |     | mV                |

| FCLKPおよびFCLKM                                      | 1Xクロック・レート                  | 10   | 65  |     | MHz               |

| DCLKPおよびDCLKM                                      | 7Xクロック・レート                  | 70   | 455 |     | MHz               |

|                                                    | 6Xクロック・レート                  | 60   | 390 |     | MHz               |

| $t_{su}$                                           | データ・セットアップ時間 <sup>(2)</sup> | 350  |     |     | ps                |

| $t_h$                                              | データ・ホールド時間 <sup>(2)</sup>   | 350  |     |     | ps                |

| <b>ADC入力クロック</b>                                   |                             |      |     |     |                   |

| CLOCK周波数                                           |                             | 10   | 65  |     | MSPS              |

| クロック・デューティ・サイクル                                    |                             | 45%  | 50% | 55% |                   |

| クロック入力振幅、<br>差動( $V_{CLKP\_ADC} - V_{CLKM\_ADC}$ ) | 正弦波、AC結合                    | 0.5  |     |     | Vpp               |

|                                                    | LVPECL、AC結合                 | 1.6  |     |     | Vpp               |

|                                                    | LVDS、AC結合                   | 0.7  |     |     | Vpp               |

| 同相モード電圧 voltage                                    | 内部でバイアス                     | 1    |     |     | V                 |

| クロック入力振幅 $V_{CLKP\_ADC}$<br>(シングルエンド)              | CMOS CLOCK                  | 1.8  |     |     | Vpp               |

(1) DC仕様は、LVDS出力のスイッチングなし、および100Ωの外部終端により有効な論理レベル0または1に固定、の条件で規定されています。

(2) セットアップ時間およびホールド時間の仕様は、出力データおよびクロックに対するジッタの影響を考慮しています。これらの仕様では、データおよびクロックのバスがレシーバ内で完全にマッチングされていると仮定しています。レシーバ内でこれらのバスにミスマッチがあると、タイミング余裕が減少します。

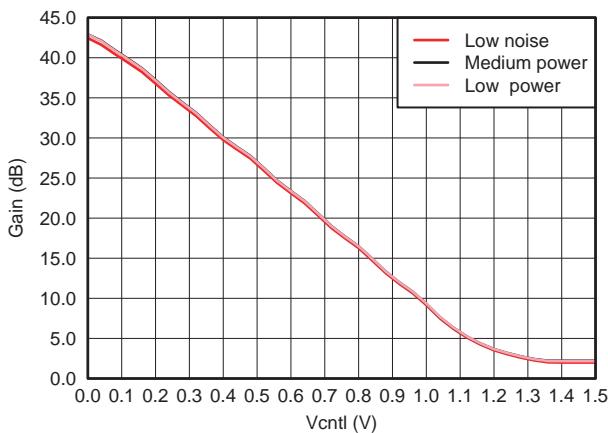

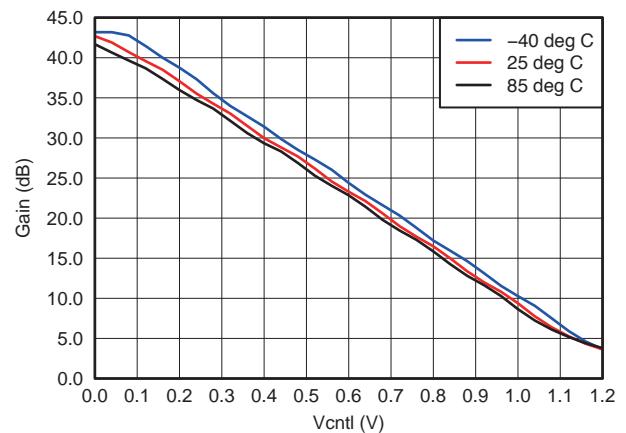

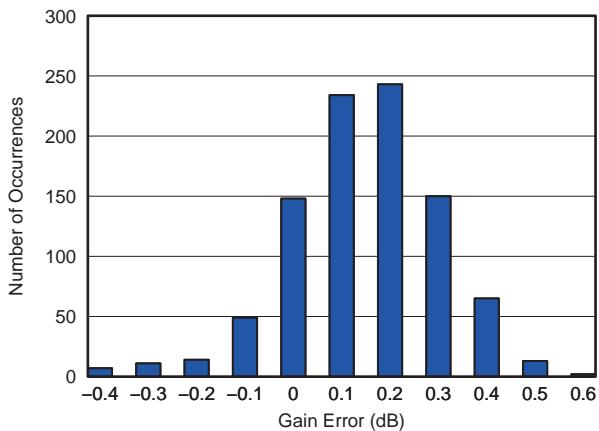

## 標準的特性

特に記述のない限り、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8V、INPに $0.1\mu\text{F}$ でAC結合、INMに $15\text{nF}$ 、アクティブ終端なし、VCNTL=0V、FIN = 5MHz、LNA = 18dB、PGA = 24dB、14ビット、サンプル・レート = 65MSPS、LPFフィルタ = 15MHz、低ノイズ・モード、VOUT =  $-1\text{dBFS}$ 、 $500\Omega$  CW帰還抵抗、CMOS 16Xクロック、ADCを内部リファレンス・モードに設定、シングルエンドVCNTLモード、VCNTLM = GND、周囲温度 $T_A$  = +25°C。

図2. ゲイン 対 VCNTL、LNA = 18dB

およびPGA = 24dB

図3. ゲイン変動 対 温度、LNA = 18dB

およびPGA = 24dB

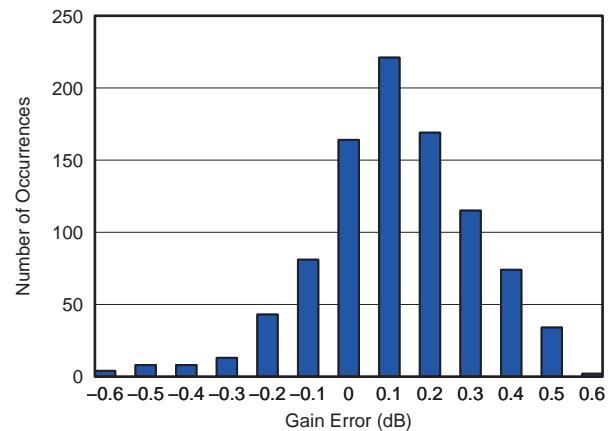

図4. ゲイン・マッチング・ヒストグラム、

VCNTL = 0.3V (936チャネル)

図5. ゲイン・マッチング・ヒストグラム、

VCNTL = 0.6V (936チャネル)

## 標準的特性

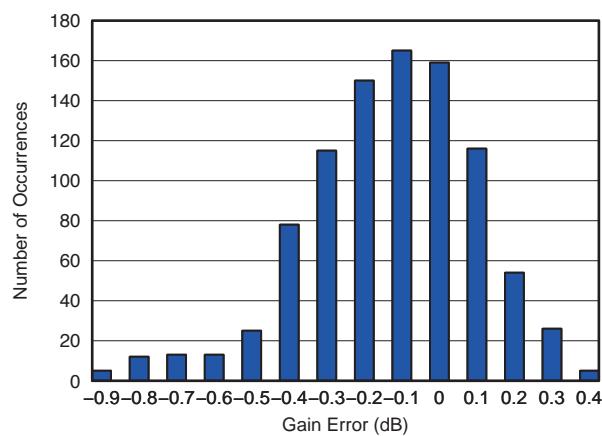

図 6. ゲイン・マッチング・ヒストグラム、

VCNTL = 0.9V (936チャネル)

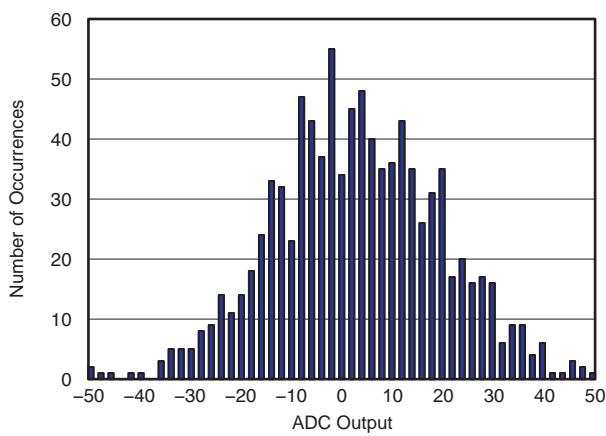

図 7. 出力オフセット・ヒストグラム、

VCNTL = 0V (936チャネル)

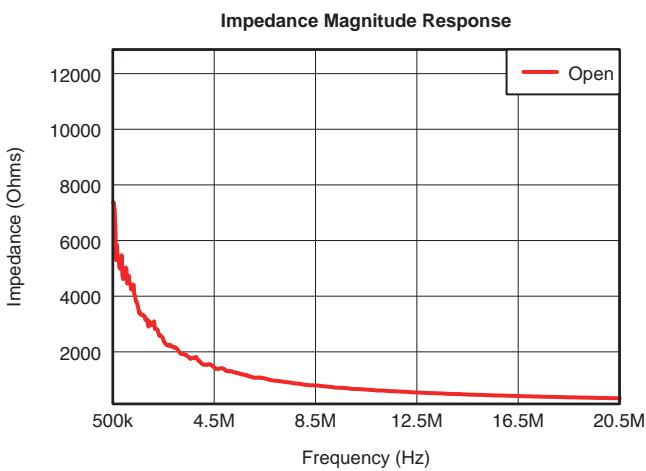

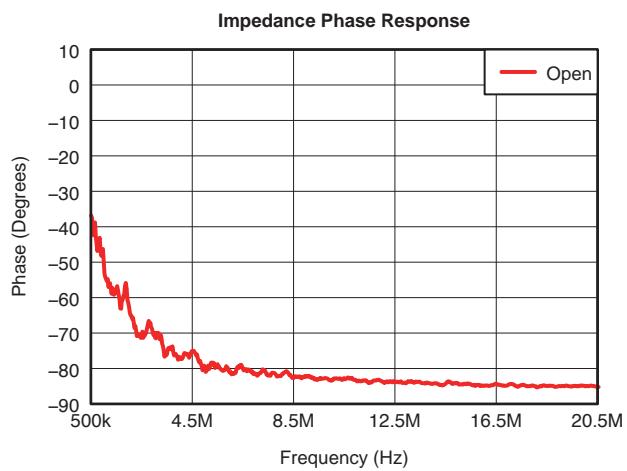

図 8. 入力インピーダンス、アクティブ終端なし(大きさ)

図 9. 入力インピーダンス、アクティブ終端なし(位相)

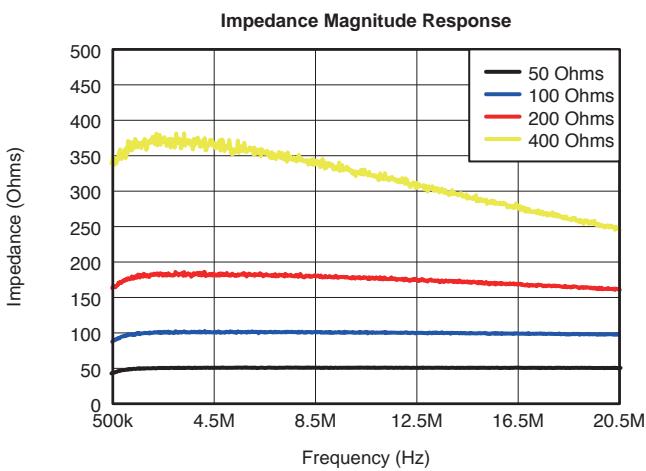

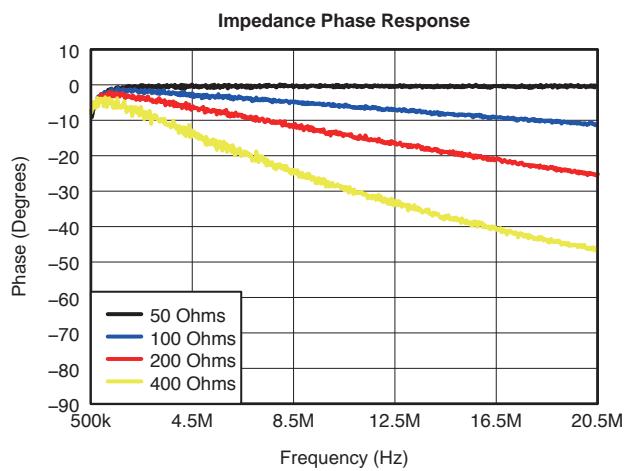

図 10. 入力インピーダンス、アクティブ終端あり(大きさ)

図 11. 入力インピーダンス、アクティブ終端あり(位相)

## 標準的特性

図 12. ローパス・フィルタ応答

図 13. LNAハイパス・フィルタ応答 対 Reg59[3:2]

図 14. 全チャネルのハイパス・フィルタ応答、デフォルト・レジスタ設定

図 15. CW位相ノイズ、Fin = 2MHz

図 16. CW位相ノイズ、Fin = 2MHz、1チャンネル対8チャンネル

図 17. CW位相ノイズ 対 クロック・モード、Fin = 2MHz

## 標準的特性

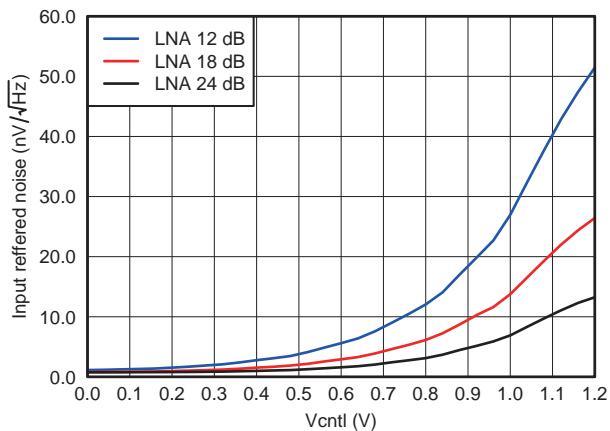

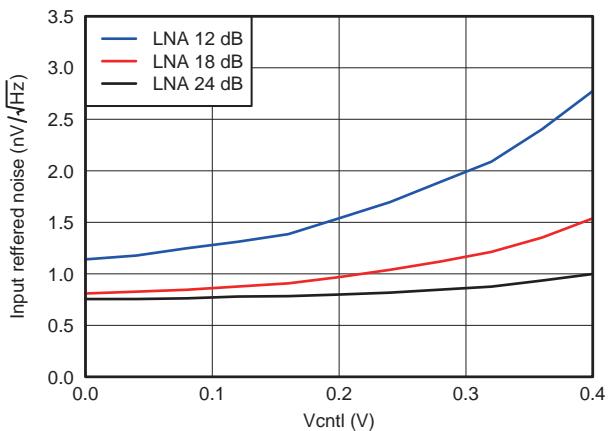

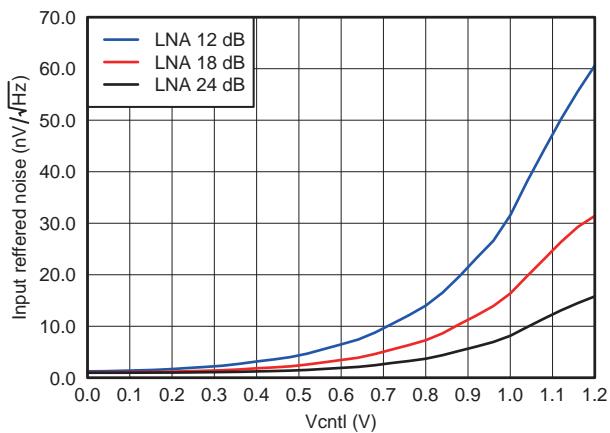

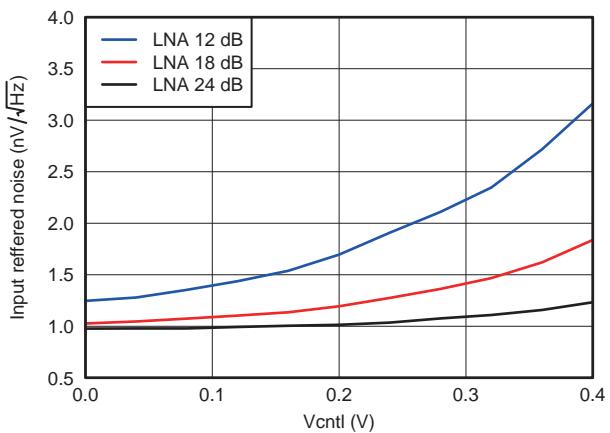

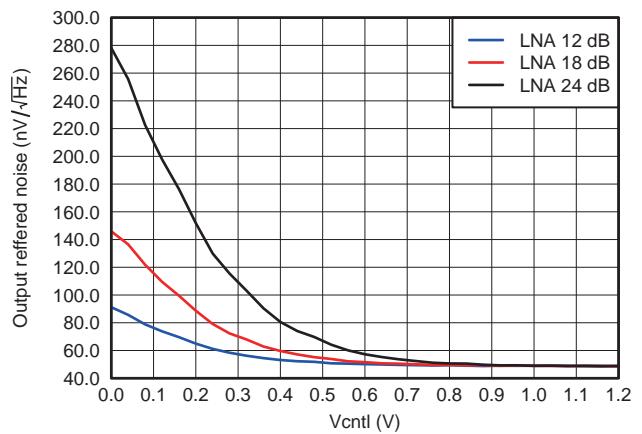

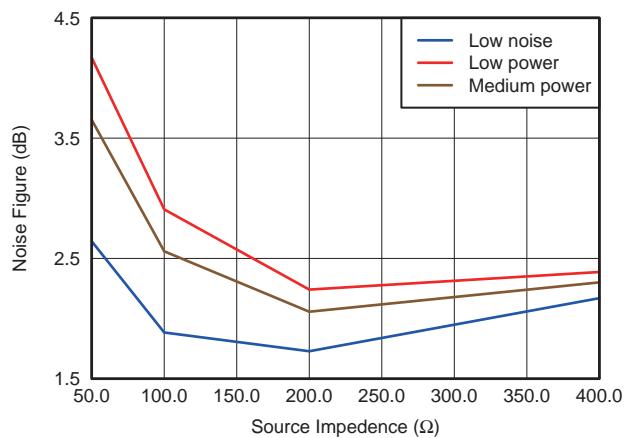

図 18. IRN、PGA = 24dBおよび低ノイズ・モード

図 19. IRN、PGA = 24dBおよび低ノイズ・モード

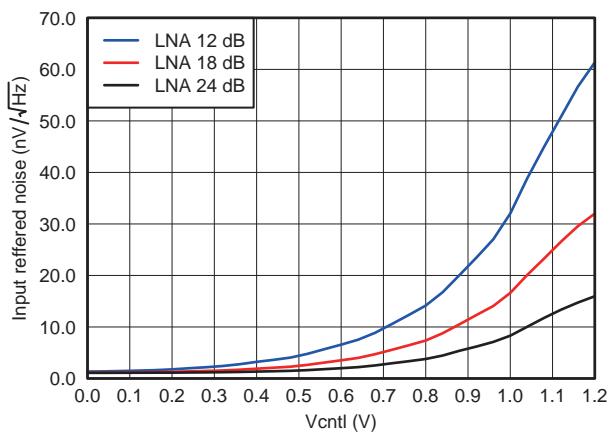

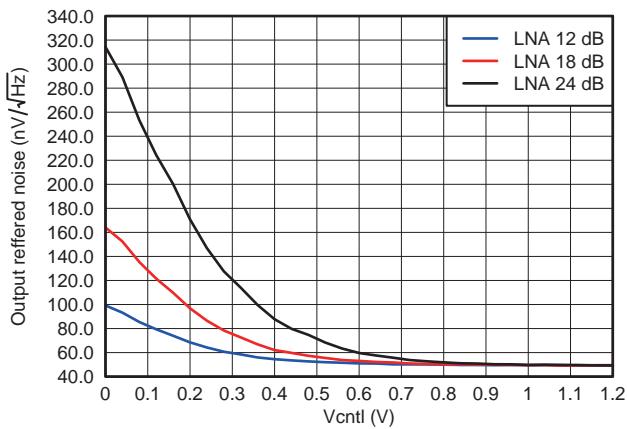

図 20. IRN、PGA = 24dBおよび中電力モード

図 21. IRN、PGA = 24dBおよび中電力モード

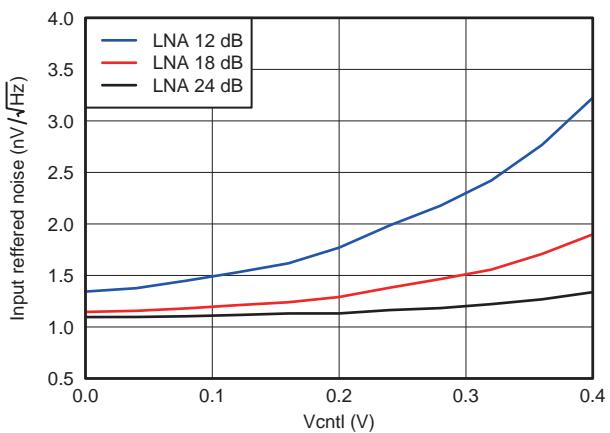

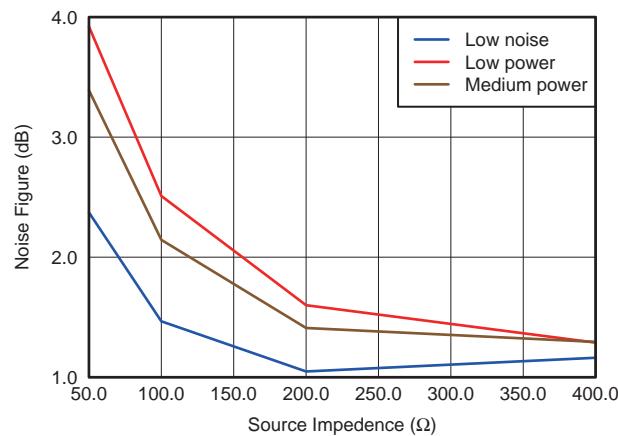

図 22. IRN、PGA = 24dBおよび低電力モード

図 23. IRN、PGA = 24dBおよび低電力モード

## 標準的特性

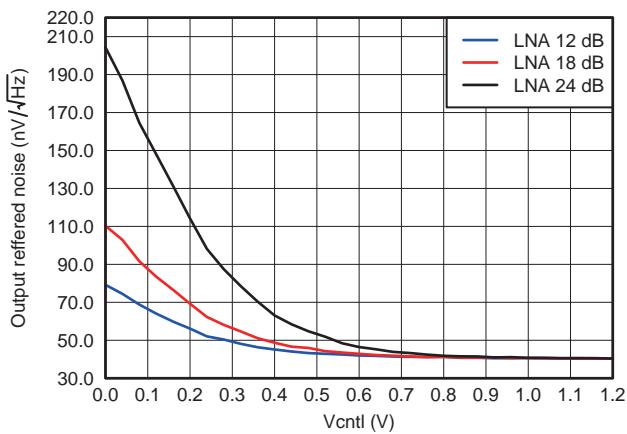

図 24. ORN、PGA = 24dBおよび低ノイズ・モード

図 25. ORN、PGA = 24dBおよび中電力モード

図 26. ORN、PGA = 24dBおよび低電力モード

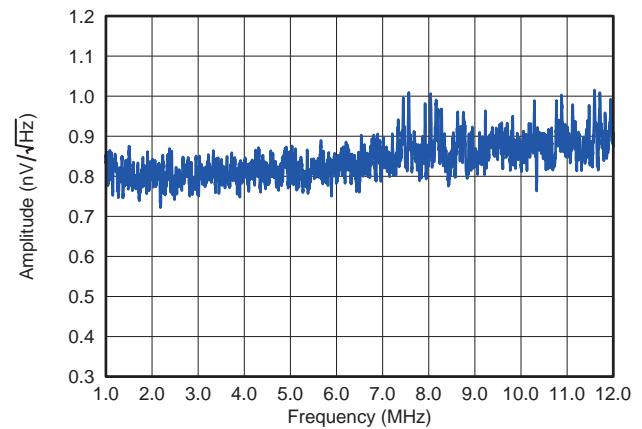

図 27. IRN、PGA = 24dBおよび低ノイズ・モード

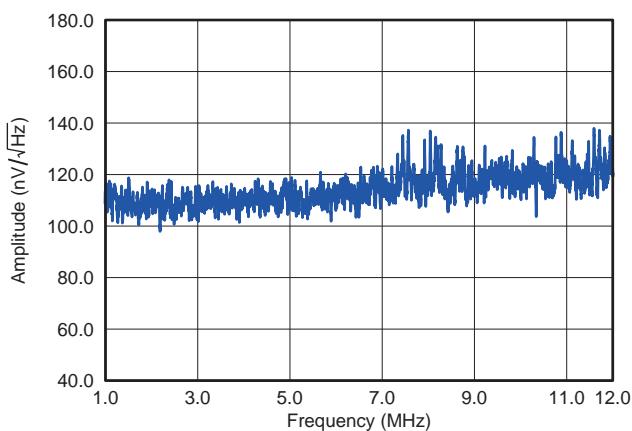

図 28. ORN、PGA = 24dBおよび低ノイズ・モード

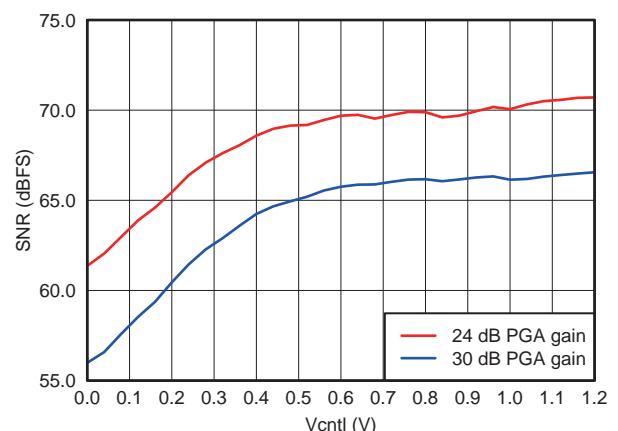

図 29. SNR、LNA = 18dBおよび低ノイズ・モード

## 標準的特性

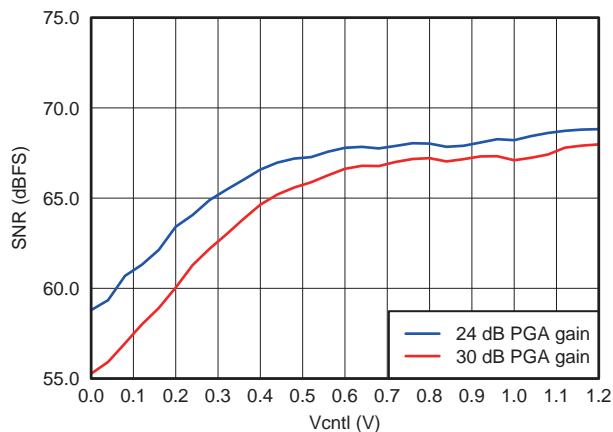

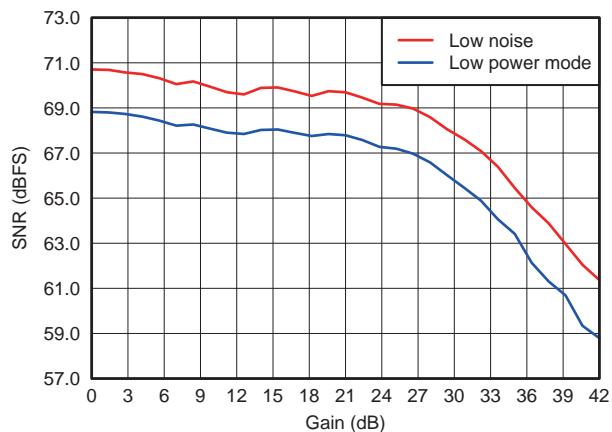

図 30. SNR、LNA = 18dBおよび低電力モード

図 31. SNR 対 各電力モード

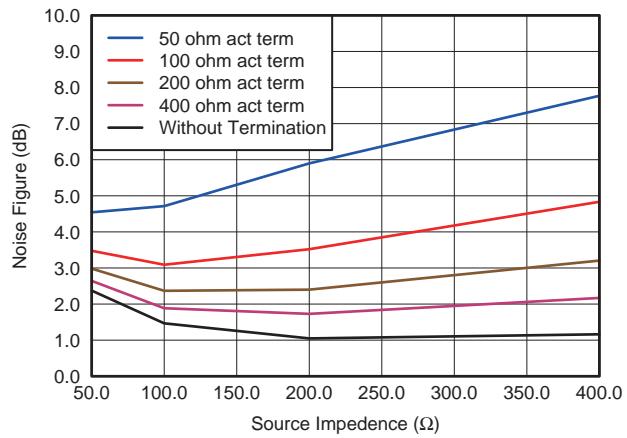

図 32. ノイズ指数、LNA = 12dBおよび

低ノイズ・モード

図 33. ノイズ指数、LNA = 18dBおよび

低ノイズ・モード

図 34. ノイズ指数、LNA = 24dBおよび

低ノイズ・モード

図 35. ノイズ指数 対 電力モード、400Ω終端

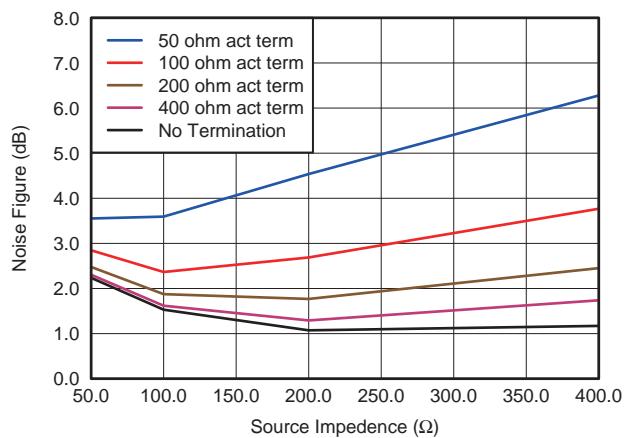

## 標準的特性

図 36. ノイズ指数 対 電力モード、終端なし

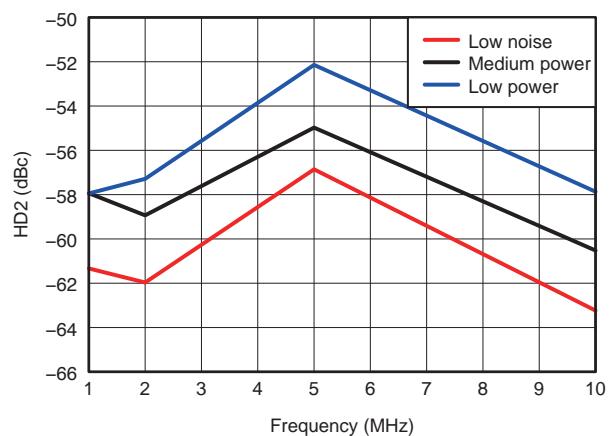

図 37. HD2 対 周波数、 $V_{IN} = 500\text{mV}_{PP}$ および

$V_{OUT} = -1\text{dBFS}$

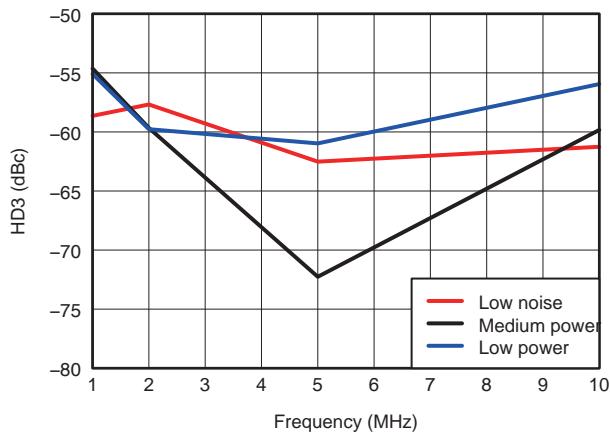

図 38. HD3 対 周波数、 $V_{IN} = 500\text{mV}_{PP}$ および

$V_{OUT} = -1\text{dBFS}$

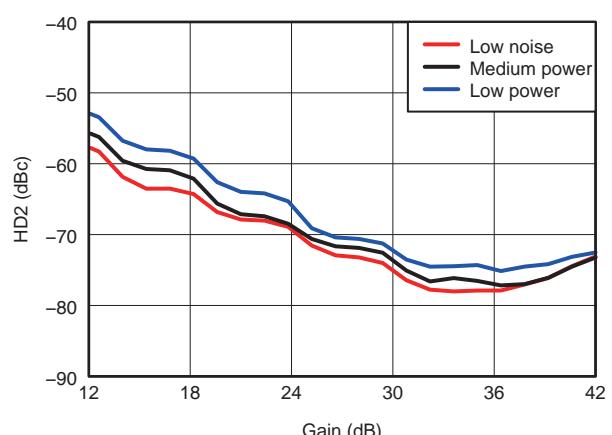

図 39. HD2 対 ゲイン、 $LNA = 12\text{dB}$ 、

$PGA = 24\text{dB}$ および $V_{OUT} = -1\text{dBFS}$

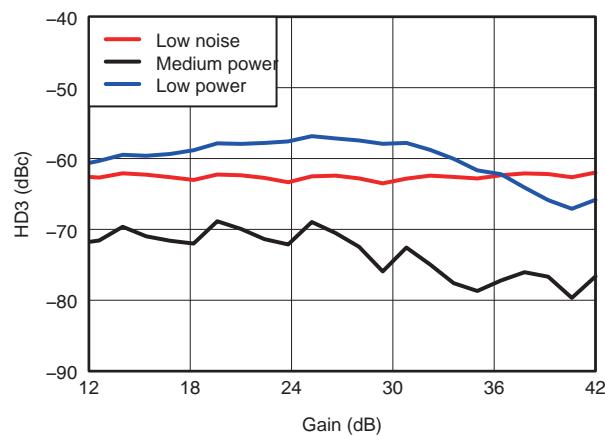

図 40. HD3 対 ゲイン、 $LNA = 12\text{dB}$ 、

$PGA = 24\text{dB}$ および $V_{OUT} = -1\text{dBFS}$

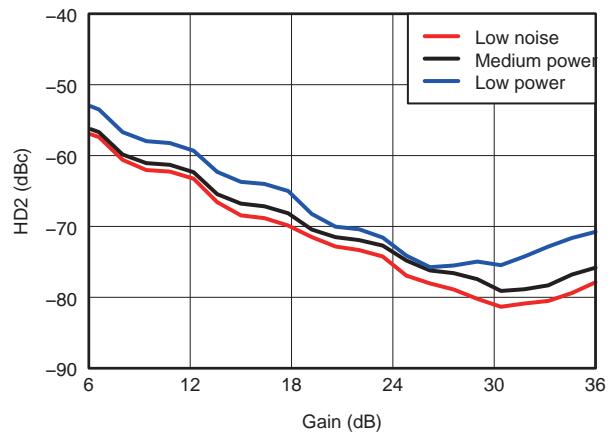

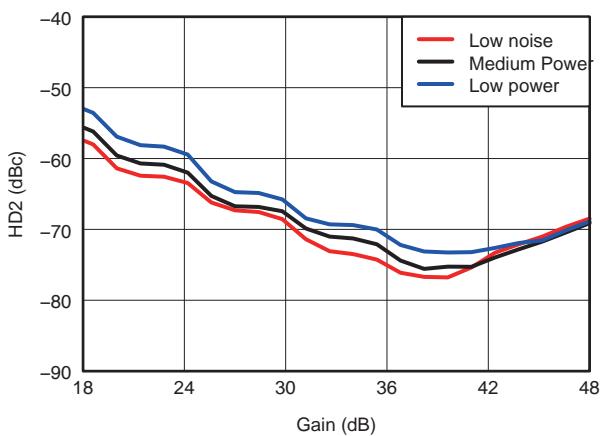

図 42. HD2 対 ゲイン、 $LNA = 18\text{dB}$ 、

$PGA = 24\text{dB}$ および $V_{OUT} = -1\text{dBFS}$

## 標準的特性

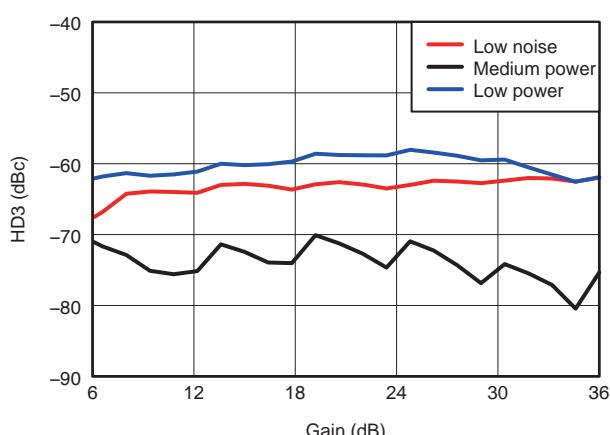

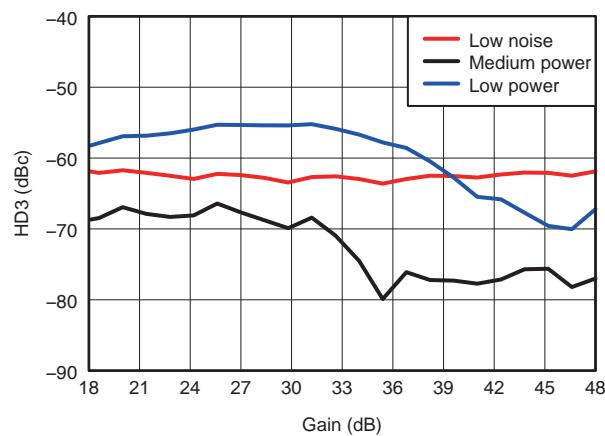

図 42. HD3 対 ゲイン、LNA = 18dB、

PGA = 24dBおよび $V_{\text{OUT}} = -1\text{dBFS}$

図 43. HD2 対 ゲイン、LNA = 24dB、

PGA = 24dBおよび $V_{\text{OUT}} = -1\text{dBFS}$

図 44. HD3 対 ゲイン、LNA = 24dB、

PGA = 24dBおよび $V_{\text{OUT}} = -1\text{dBFS}$

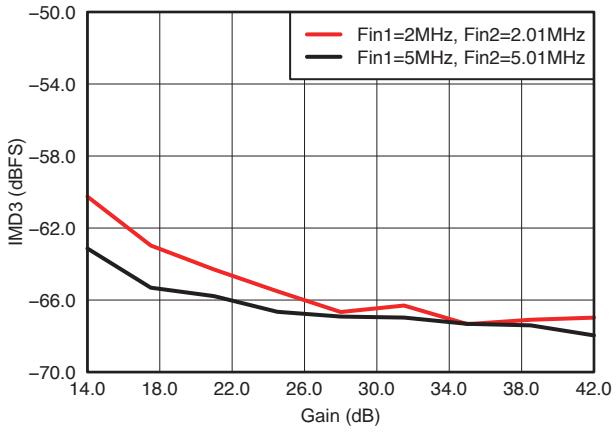

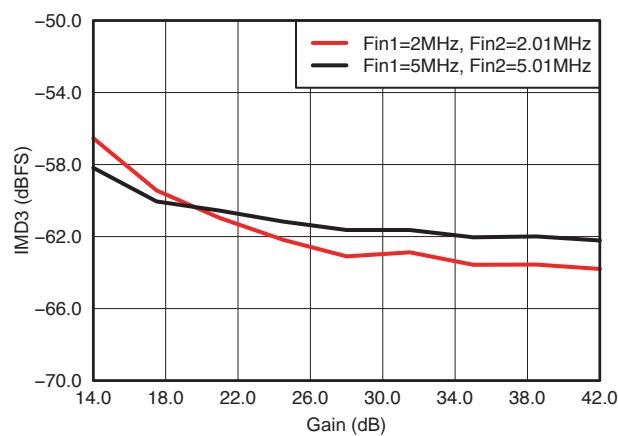

図 45. IMD3、 $F_{\text{out}1} = -7\text{dBFS}$ および

$F_{\text{out}2} = -21\text{dBFS}$

図 46. IMD3、 $F_{\text{out}1} = -7\text{dBFS}$ および $F_{\text{out}2} = -7\text{dBFS}$

図 47. AVDD電源変調比、 $100\text{mV}_{\text{PP}}$ 電源ノイズ、

各周波数

## 標準的特性

図 48. AVDD\_5V電源変調比、100mV<sub>PP</sub>電源ノイズ、各周波数

図 49. AVDD電源除去比、100mV<sub>PP</sub>電源ノイズ、各周波数

図 50. AVDD\_5V電源除去比、100mV<sub>PP</sub>電源ノイズ、各周波数

図 51. V<sub>CNTL</sub>応答時間、LNA = 18dBおよびPGA = 24dB

図 52. V<sub>CNTL</sub>応答時間、LNA = 18dBおよびPGA = 24dB

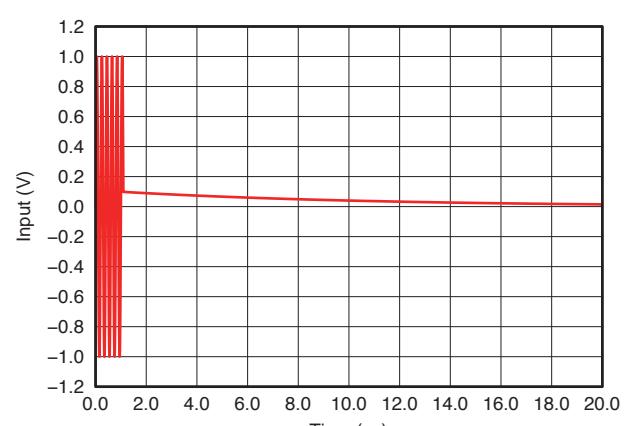

図 53. パルス反転非対称正入力

## 標準的特性

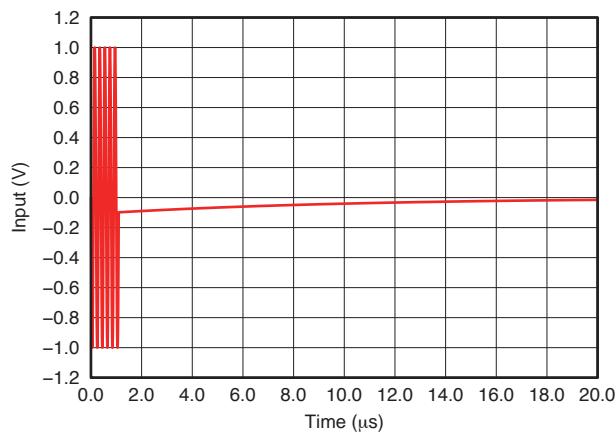

図 54. パルス反転非対称負入力

図 55. パルス反転、 $V_{IN} = 2V_{PP}$ 、 $PRF = 1\text{kHz}$ 、

ゲイン = 21dB

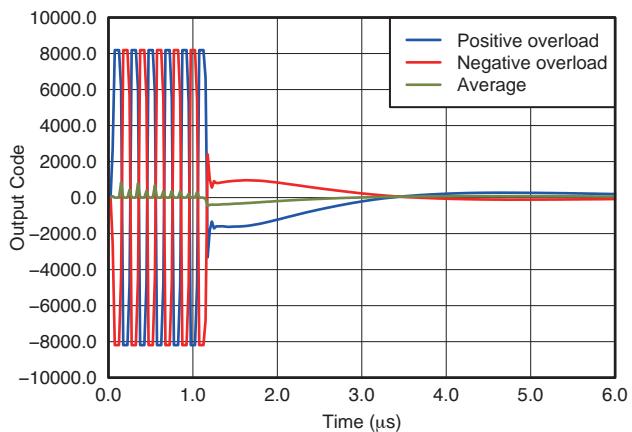

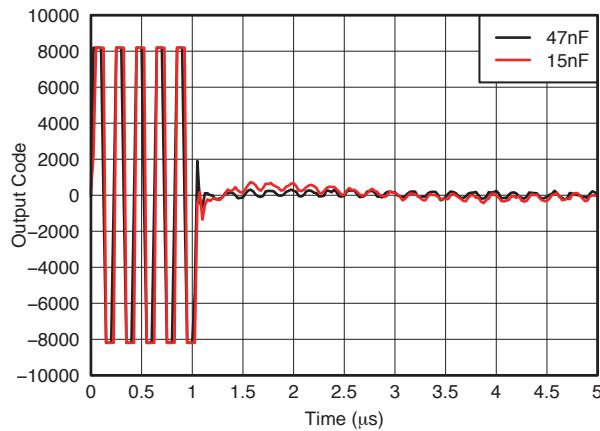

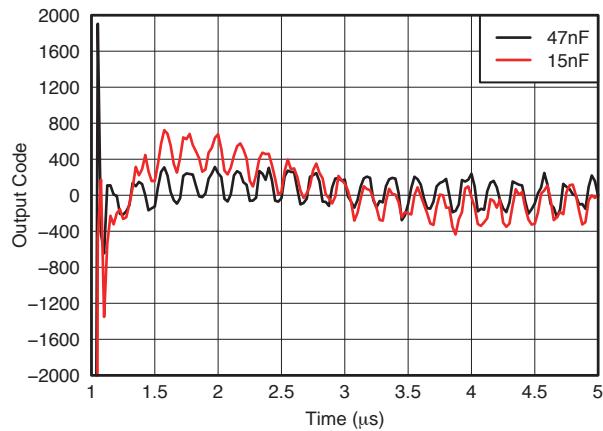

図 56. 過負荷回復応答 対 INMコンデンサ、

$V_{IN} = 50\text{mV}_{PP}/100\mu\text{V}_{PP}$ 、最大ゲイン

図 57. 過負荷回復応答 対 INMコンデンサ(拡大図)、

$V_{IN} = 50\text{mV}_{PP}/100\mu\text{V}_{PP}$ 、最大ゲイン

## タイミング特性<sup>(1)</sup>

特に記述のない限り、標準値は25°Cでの値、AVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8V、差動クロック、C<sub>LOAD</sub> = 5pF、R<sub>LOAD</sub> = 100Ω、14ビット、サンプル・レート = 65MSPSです。最小値および最大値は温度範囲全体(T<sub>MIN</sub> = 0°C～T<sub>MAX</sub> = 85°C)での値、およびAVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8Vです。

| パラメータ                 |                                   | 測定条件                                                                                     | MIN  | TYP  | MAX | 単位          |

|-----------------------|-----------------------------------|------------------------------------------------------------------------------------------|------|------|-----|-------------|

| ta                    | アバーチャ遅延                           | 入力サンプリング・クロックの立ち上がりエッジから、実際にサンプリングが行われるまでの遅延時間                                           | 0.7  | 3    |     | ns          |

|                       | アバーチャ遅延マッチング                      | 同じデバイス内のチャネル間                                                                            |      | ±150 |     | ps          |

| t <sub>j</sub>        | アバーチャ・ジッタ                         |                                                                                          |      | 450  |     | Fs rms      |

|                       | ADCレイテンシ                          | デフォルト、リセット後、または / 0 × 2 [12] = 1、LOW_LATENCY = 1                                         |      | 11/8 |     | 入力クロック・サイクル |

| t <sub>delay</sub>    | データおよびフレーム・クロック遅延                 | 入力クロックの立ち上がりエッジ(ゼロ・クロス)からフレーム・クロックの立ち上がりエッジ(ゼロ・クロス) - 入力クロック周期(T)の1/2                    | 3    | 5.4  | 7   | ns          |

| Δt <sub>delay</sub>   | 遅延変動                              | 固定電源、Tの差が20°C、デバイス間                                                                      | -1   | 1    |     | ns          |

| t <sub>RISE</sub>     | データ立ち上がり時間、データ立ち下がり時間             | 立ち上がり時間は-100mVから100mVまでを測定、立ち下がり時間は100mVから-100mVまでを測定、10MHz < f <sub>CLKIN</sub> < 65MHz | 0.14 |      |     | ns          |

| t <sub>FALL</sub>     |                                   |                                                                                          | 0.15 |      |     |             |

| t <sub>FCLKRISE</sub> | フレーム・クロック立ち上がり時間、フレーム・クロック立ち下がり時間 | 立ち上がり時間は-100mVから100mVまでを測定、立ち下がり時間は100mVから-100mVまでを測定、10MHz < f <sub>CLKIN</sub> < 65MHz | 0.14 |      |     | ns          |

| t <sub>FCLKFALL</sub> |                                   |                                                                                          | 0.15 |      |     |             |

|                       | フレーム・クロックのデューティ・サイクル              | 立ち上がりエッジのゼロ・クロスから立ち下がりエッジのゼロ・クロスまで                                                       | 48%  | 50%  | 52% |             |

| t <sub>DCLKRISE</sub> | ビット・クロック立ち上がり時間、ビット・クロック立ち下がり時間   | 立ち上がり時間は-100mVから100mVまでを測定、立ち下がり時間は100mVから-100mVまでを測定、10MHz < f <sub>CLKIN</sub> < 65MHz | 0.13 |      |     | ns          |

| t <sub>DCLKFALL</sub> |                                   |                                                                                          | 0.12 |      |     |             |

|                       | ビット・クロックのデューティ・サイクル               | 立ち上がりエッジのゼロ・クロスから立ち下がりエッジのゼロ・クロスまで、10MHz < f <sub>CLKIN</sub> < 65MHz                    | 46%  | 54%  |     |             |

(1) タイミング・パラメータは、設計および特性によって規定される値であり、実製品のテストは行っていません。

## 出力インターフェイス・タイミング<sup>(1)(2)(3)</sup>

| f <sub>CLKIN</sub> 、<br>入力クロック<br>周波数 | セットアップ時間(t <sub>su</sub> )、ns(出力データ<br>およびフレーム・クロック) | ホールド時間(t <sub>h</sub> )、ns(出力データ<br>およびフレーム・クロック) | t <sub>PROG</sub> = (3/7) × T + t <sub>delay</sub> , ns       |      |      |     |      |      |      |

|---------------------------------------|------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------|------|------|-----|------|------|------|

|                                       | データ有効から入力クロックの<br>ゼロ・クロスまで                           | 入力クロックのゼロ・クロスから<br>データ無効まで                        | 入力クロックのゼロ・クロス(立ち上<br>がりエッジ)からフレーム・クロックの<br>ゼロ・クロス(立ち上がりエッジ)まで |      |      |     |      |      |      |

| MHz                                   | MIN                                                  | TYP                                               | MAX                                                           | MIN  | TYP  | MAX | MIN  | TYP  | MAX  |

| 65                                    | 0.24                                                 | 0.37                                              |                                                               | 0.24 | 0.38 |     | 11   | 12   | 12.5 |

| 50                                    | 0.41                                                 | 0.54                                              |                                                               | 0.46 | 0.57 |     | 13   | 13.9 | 14.4 |

| 40                                    | 0.55                                                 | 0.70                                              |                                                               | 0.61 | 0.73 |     | 15   | 16   | 16.7 |

| 30                                    | 0.87                                                 | 1.10                                              |                                                               | 0.94 | 1.1  |     | 18.5 | 19.5 | 20.1 |

| 20                                    | 1.30                                                 | 1.56                                              |                                                               | 1.46 | 1.6  |     | 25.7 | 26.7 | 27.3 |

(1) FCLKタイミングは、出力データ・ラインの場合と同じです。DCLKとの関係は、データ・ピンの場合と同じです。

セットアップおよびホールドは、データとフレーム・クロックに対して同じです。

(2) データ有効は、論理High = +100mV、論理Low = -100mVです。

(3) タイミング・パラメータは、設計および特性によって規定される値であり、実製品のテストは行っていません。

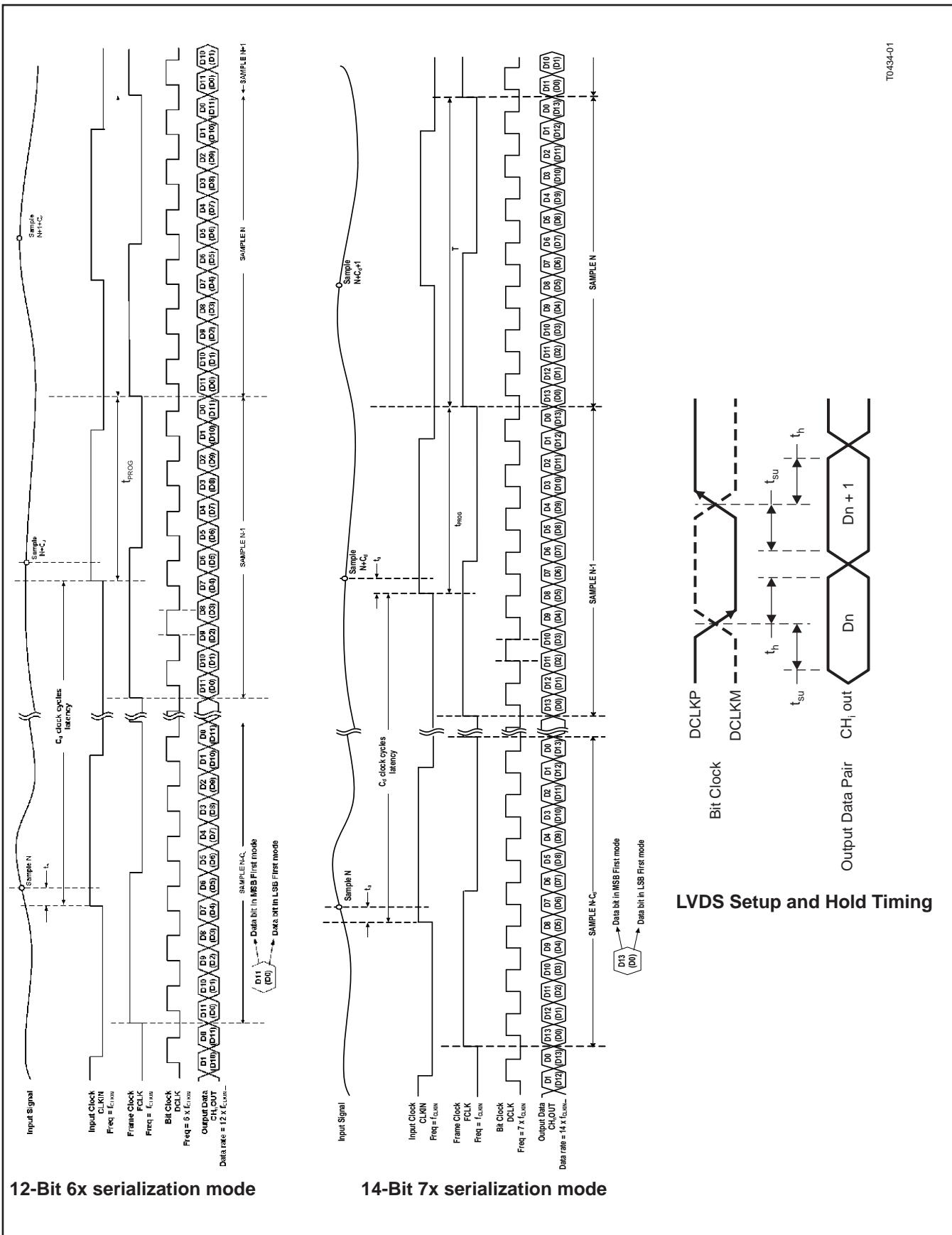

図 58. LVDS タイミング図

## LVDS出力インターフェイスの説明

AFE5808は、複数の出力形式をサポートするLVDS出力インターフェイスを備えています。ADCの分解能は、図58のLVDSタイミング図に示されるように、12ビットまたは14ビットに設定できます。AFE5808内のADCは、14ビットで動作しています。12ビット出力を選択すると、下位2ビットが除外されます。16ビット出力を選択すると、下位に0が2つ追加されます。適切なADC分解能を選択することで、システムのコスト・パフォーマンスを最適化できます。デバイスが16ビット・モードで動作する場合は、より高いレートのLVDSデータを処理するために、よりハイエンドのFPGAが必要となります。対応するレジスタ設定を表1に示します。

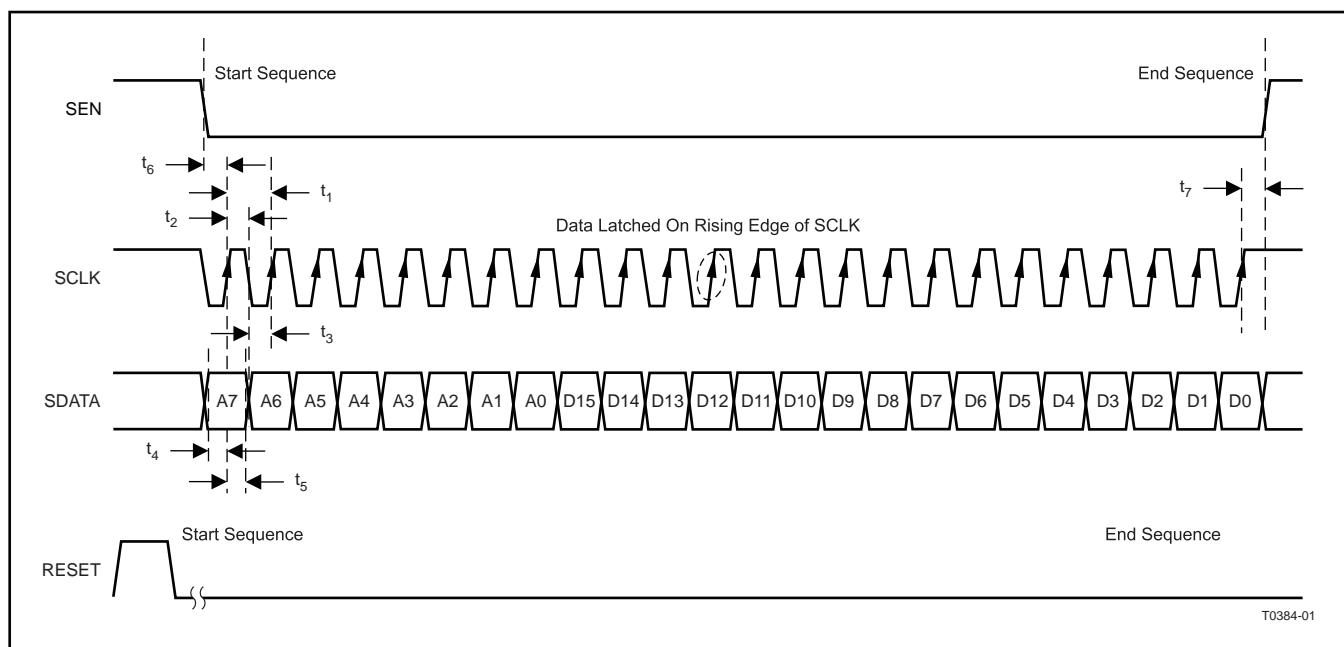

## シリアル・レジスタの動作

### シリアル・レジスタ書き込みの説明

各モードのプログラミングは、SEN(シリアル・インターフェイス・イネーブル)、SCLK(シリアル・インターフェイス・クロック)、SDATA(シリアル・インターフェイス・データ)、RESETの各ピンから構成されるシリアル・インターフェイスを使用して行えます。これらのピンはすべて、GNDとの間に $100\text{k}\Omega$ のプルダウン抵抗を備えています。SENがLowのとき

に、デバイスへのビットのシリアル・シフトがイネーブルになります。シリアル・データSDATAは、SENがアクティブ(Low)のときのSCLKの各立ち上がりエッジでラッチされます。ラッチされたシリアル・データは、SENがLowのときのSCLKの24回目の立ち上がりエッジで、レジスタにロードされます。ワード長が24ビットの倍数より大きい場合、超過するビットは無視されます。1回のアクティブなSENパルス内で、24ビット・ワードの整数倍のデータをロードできます(SENの立ち下がりエッジ後に24クロックのグループをカウントする内部カウンタがあります)。このインターフェイスは、20MHz～低速(数Hz)までにわたるSCLK周波数で動作し、デューティ・サイクルが50%以外のSCLKでも動作できます。データは2つの主要な部分に分けられます。レジスタ・アドレス(8ビット)と、アドレス指定されたレジスタにロードするデータそれ自体(16ビット)です。未使用ビットを含むレジスタに書き込むときには、それらのビットを0に設定する必要があります。これを図59に示します。

| LVDSレート       | 12ビット(6X DCLK) | 14ビット(7X DCLK) | 16ビット(8X DCLK) |

|---------------|----------------|----------------|----------------|

| Reg 3 [14:13] | 11             | 00             | 01             |

| Reg 4 [2:0]   | 010            | 000            | 000            |

| 説明            | 下位2ビットを除外      | N/A            | 下位に0を2つ追加      |

表1. 対応レジスタ設定

図 59. SPIタイミング

## SPIタイミング特性

最小値は温度範囲全体( $T_{MIN} = 0^{\circ}\text{C}$ ~ $T_{MAX} = 85^{\circ}\text{C}$ )での値、およびAVDD\_5V = 5V、AVDD = 3.3V、AVDD\_ADC = 1.8V、DVDD = 1.8Vです。

| パラメータ | 説明                                | MIN | TYP | MAX | 単位 |

|-------|-----------------------------------|-----|-----|-----|----|

| $t_1$ | SCLK周期                            | 50  |     |     | ns |

| $t_2$ | SCLK High時間                       | 20  |     |     | ns |

| $t_3$ | SCLK Low時間                        | 20  |     |     | ns |

| $t_4$ | データ・セットアップ時間                      | 5   |     |     | ns |

| $t_5$ | データ・ホールド時間                        | 5   |     |     | ns |

| $t_6$ | SEN立ち下がりからSCLK立ち上がりまで             | 8   |     |     | ns |

| $t_7$ | 最後のSCLK立ち上がりエッジからSEN立ち上がりエッジまでの時間 | 8   |     |     | ns |

| $t_8$ | SDOUT遅延                           | 12  | 20  | 28  | ns |

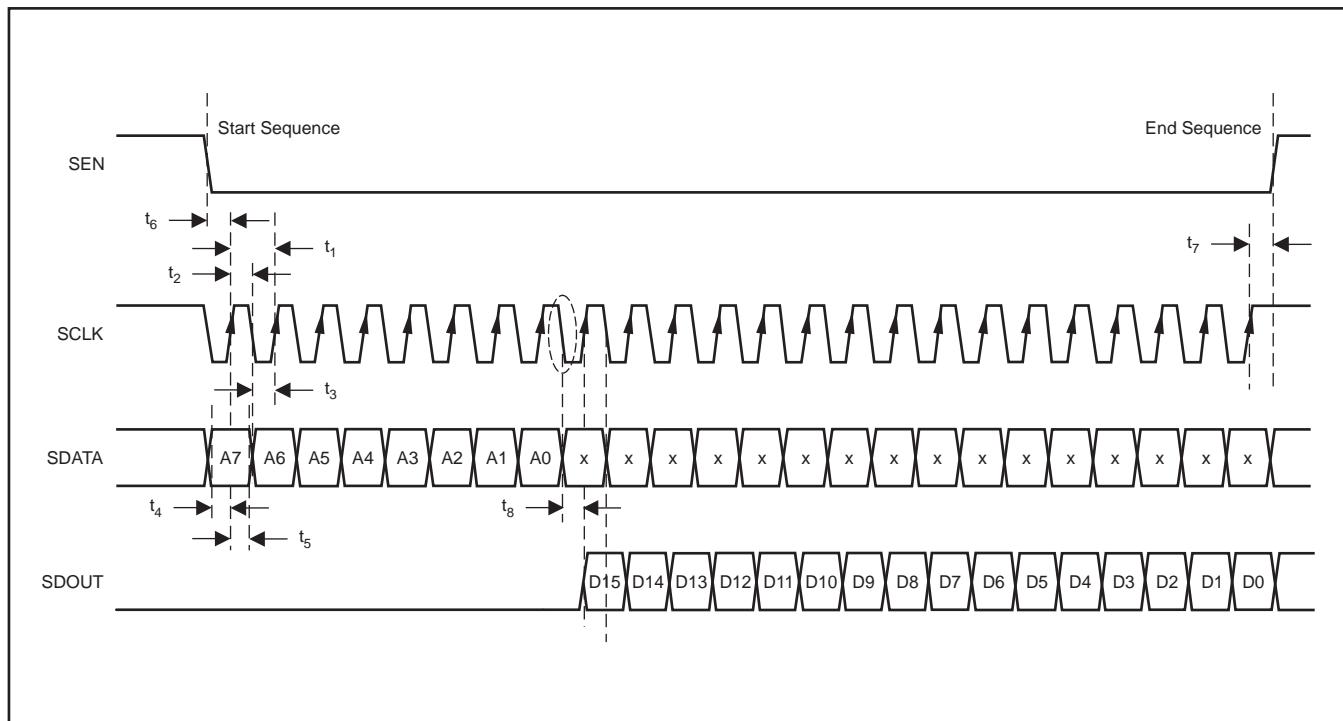

## レジスタ読み出し

デバイスには、内部レジスタの内容を読み出すためのオプションが用意されています。これは、外部のコントローラとAFEとの間のシリアル・インターフェイス通信を検査する診断テストに利用できます。まず、レジスタ読み出しイネーブル・ビット(Reg0[1])を1に設定する必要があります。次に、内容を読み出すレジスタのアドレス(A7-A0)を指定して、シリアル・インターフェイス・サイクルを開始します。データ・ビットは“don't care”です。デバイスは、選択されたレジスタの内容(D15-D0)をSDOUTピンに出力します。SDOUTには、SCLKの立ち下がりエッジから標準20nsの遅延時間 $t_8$ があります。SCLKが低速の場合は、SCLKの立ち上がりエッジでSDOUTをラッチできます。SCLKが高速(例えば、SCLK周期が60ns未

満)の場合は、次のSCLKの立ち下がりエッジでSDOUTをラッチする方が適切です。次のタイミング図に、この動作を示します(タイミング仕様は、表に示したものと同じ情報を従っています)。読み出しモードでも、ユーザーはSDATA/SCLK/SENを通じてレジスタ読み出しイネーブル・ビットにアクセスできます。シリアル・レジスタの書き込みをイネーブルにするには、レジスタ読み出しイネーブル・ビットを再び0に設定します。

AFE5808のSDOUTバッファは、3ステートであり、0[1](レジスタ読み出しイネーブル)をセットしたときのみイネーブルとなります。複数のAFE5808のSDOUTピンを、プルアップ抵抗なしで互いに接続できます。必要に応じて、レベル・シフタSN74AUP1T04を使用して1.8Vロジックを2.5V/3.3Vロジックに変換できます。

図 60. シリアル・インターフェイス・レジスタの読み出し

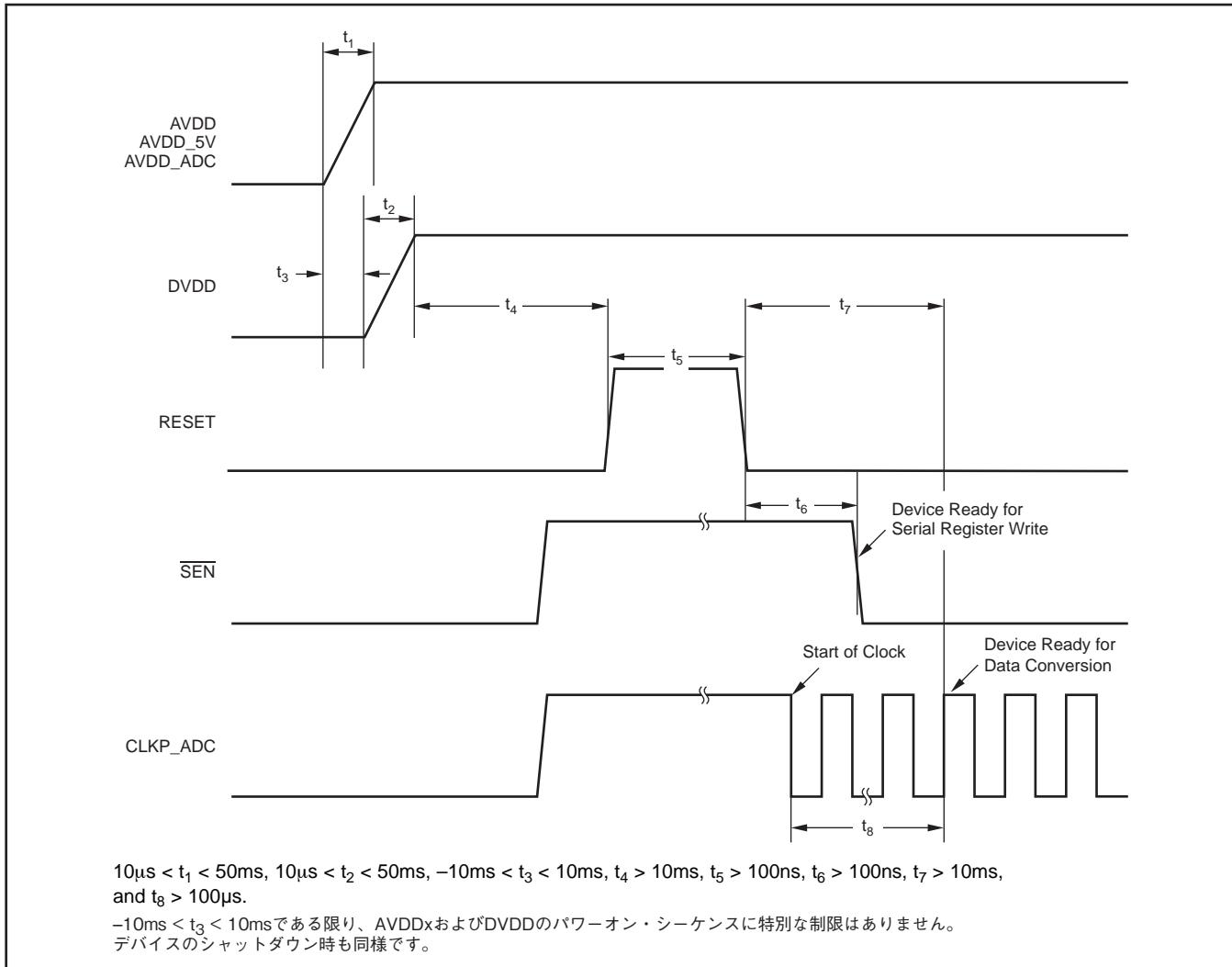

図 61. 推奨されるパワーアップ・シーケンスとリセット・タイミング

## レジスタ・マップ

AFE5808の初期化には、リセット・プロセスが必要です。初期化は、次の2つのうちいずれかの方法で実行できます。

- RESETピンに正パルスを印加することによるハードウェア・リセット

- シリアル・インターフェイスでSOFTWARE RESETビットをHighにするソフトウェア・リセット。このビットをセットすると、内部レジスタがそれぞれのデフォルト値(すべてゼロ)に初期化され、その後SOFTWARE RESETビットはLowに戻ります。この場合、RESETピンはLow(非アクティブ)のまま保持できます。

リセット後は、ADCおよびVCAのすべてのレジスタが0(デフォルト設定)に設定されます。レジスタのプログラミング時には、予約済み/未記載のレジスタ・ビットはすべて0に設定する必要があります。

## ADCレジスタ・マップ<sup>®</sup>

| アドレス<br>(10進) | アドレス<br>(16進) | デフォルト値 | 機能                                | 説明                                                                                        |

|---------------|---------------|--------|-----------------------------------|-------------------------------------------------------------------------------------------|

| 0[0]          | 0x0[0]        | 0      | SOFTWARE_RESET                    | 0:通常動作<br>1:デバイスをリセットし、ビットは自動的に0にクリア                                                      |

| 0[1]          | 0x0[1]        | 0      | REGISTER_READOUT_ENABLE           | 0:読み出しをディスエーブル<br>1:SDOUTピンでレジスタの読み出しをイネーブル                                               |

| 1[0]          | 0x1[0]        | 0      | ADC_COMPLETE_PDN                  | 0:通常動作<br>1:完全パワーダウン                                                                      |

| 1[1]          | 0x1[1]        | 0      | LVDS_OUTPUT_DISABLE               | 0:出力をイネーブル<br>1:出力をディスエーブル                                                                |

| 1[9 : 2]      | 0x1[9 : 2]    | 0      | ADC_PDN_CH<7 : 0>                 | 0:通常動作<br>1:パワーダウン。個々のADCチャネルをパワーダウン。<br>1[9]→CH8...1[2]→CH1                              |

| 1[10]         | 0x1[10]       | 0      | PARTIAL_PDN                       | 0:通常動作<br>1:ADCの部分パワーダウン                                                                  |

| 1[11]         | 0x1[11]       | 0      | LOW_FREQUENCY_NOISE_SUPPRESSION   | 0:抑制なし<br>1:抑制をイネーブル                                                                      |

| 1[13]         | 0x1[13]       | 0      | EXT_REF                           | 0:内部リファレンス<br>1:外部リファレンス。VREF_INを使用。外部リファレンス・モードでは、<br>3[15]と1[13]の両方を1に設定する必要があります。      |

| 1[14]         | 0x1[14]       | 0      | LVDS_OUTPUT_RATE_2X               | 0:1xレート<br>1:2xレート。2チャネルのデータを1つのLVDSペアに結合します。<br>ADCクロック・レートが低い場合に、この機能を使用できます。           |

| 1[15]         | 0x1[15]       | 0      | SINGLE-ENDED_CLK_MODE             | 0:差動クロック入力<br>1:シングルエンド・クロック入力                                                            |

| 2[2 : 0]      | 0x2[2 : 0]    | 0      | RESERVED                          | 0に設定                                                                                      |

| 2[10 : 3]     | 0x2[10 : 3]   | 0      | POWER-DOWN_LVDS                   | 0:通常動作<br>1:個別LVDS出力のパワーダウン。2[10]→CH8、...2[3]→CH1                                         |

| 2[11]         | 0x2[11]       | 0      | AVERAGING_ENABLE                  | 0:平均化なし<br>1:2つのチャネルを平均化してSNRを向上                                                          |

| 2[12]         | 0x2[12]       | 0      | LOW_LATENCY                       | 0:デジタル機能をサポートする既定のレイテンシ、11サイクル<br>1:デジタル機能をバイパスする低いレイテンシ、8サイクル                            |

| 2[15 : 13]    | 0x2[15 : 3]   | 0      | TEST_PATTERN_MODES                | 000:通常動作<br>001:同期<br>010:デスキュー<br>011:カスタム<br>100:オール1<br>101:トグル<br>110:オール0<br>111:ランプ |

| 3[7 : 0]      | 0x3[7 : 0]    | 0      | INVERT_CHANNELS                   | 0:反転なし<br>1:チャネルのデジタル出力を反転。3[7]→CH8、...3[0]→CH1                                           |

| 3[8]          | 0x3[8]        | 0      | CHANNEL_OFFSET_SUBTRACTION_ENABLE | 0:オフセット減算なし<br>1:オフセット値の減算をイネーブル                                                          |

| 3[9 : 11]     | 0x3[9 : 11]   | 0      | RESERVED                          | 0に設定                                                                                      |

表 2. ADCレジスタ・マップ<sup>®</sup>

| アドレス<br>(10進) | アドレス<br>(16進) | デフォルト値 | 機能                              | 説明                                                                                                                                                           |

|---------------|---------------|--------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3[12]         | 0x3[12]       | 0      | DIGITAL_GAIN_ENABLE             | 0: デジタル・ゲインなし<br>1: デジタル・ゲインをイネーブル                                                                                                                           |

| 3[14:13]      | 0x3[14:13]    | 0      | SERIALIZED_DATA_RATE            | シリアル化係数<br>00: 14x<br>01: 16x<br>10: 予約済み<br>11: 12x<br>4[1]=1のとき。16xのシリアル化レートでは、下位2ビットに2個の0が付加されます(表1を参照)。                                                  |

| 3[15]         | 0x3[15]       | 0      | ENABLE_EXTERNAL_REFERENCE_MODE  | 0: 内部リファレンス・モード<br>1: 外部リファレンス・モードに設定<br>注: デバイスを外部リファレンス・モードに設定する場合は、3[15]と1[13]の両方を1に設定する必要があります。                                                          |

| 4[1]          | 0x4[1]        | 0      | ADC_RESOLUTION_SELECT           | 0: 14ビット<br>1: 12ビット                                                                                                                                         |

| 4[3]          | 0x4[3]        | 0      | ADC_OUTPUT_FORMAT               | 0: 2の補数<br>1: オフセット・バイナリ                                                                                                                                     |

| 4[4]          | 0x4[4]        | 0      | LSB_MSB_FIRST                   | 0: LSBファースト<br>1: MSBファースト                                                                                                                                   |

| 5[13:0]       | 0x5[13:0]     | 0      | CUSTOM_PATTERN                  | LVDS出力のカスタム・パターン・データ(2[15:13] = 011)                                                                                                                         |

| 13[9:0]       | 0xD[9:0]      | 0      | OFFSET_CH1                      | チャネル1のコードから減算する値                                                                                                                                             |

| 13[15:11]     | 0xD[15:11]    | 0      | DIGITAL_GAIN_CH1                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 15[9:0]       | 0xF[9:0]      | 0      | OFFSET_CH2                      | チャネル2のコードから減算する値                                                                                                                                             |

| 15[15:11]     | 0xF[15:11]    | 0      | DIGITAL_GAIN_CH2                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 17[9:0]       | 0x11[9:0]     | 0      | OFFSET_CH3                      | チャネル3のコードから減算する値                                                                                                                                             |

| 17[15:11]     | 0x11[15:11]   | 0      | DIGITAL_GAIN_CH3                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 19[9:0]       | 0x13[9:0]     | 0      | OFFSET_CH4                      | チャネル4のコードから減算する値                                                                                                                                             |

| 19[15:11]     | 0x13[15:11]   | 0      | DIGITAL_GAIN_CH4                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 21[0]         | 0x15[0]       | 0      | DIGITAL_HPF_FILTER_ENABLE_CH1-4 | 0: デジタルHPFフィルタをディスエーブル<br>1: 1~4チャネルに対してイネーブル                                                                                                                |

| 21[4:1]       | 0x15[4:1]     | 0      | DIGITAL_HPF_FILTER_K_CH1-4      | ハイパス・フィルタのKを設定(Kは2~4、0010B~0100B)。<br>この4レジスタのグループは、出力データに適用されるデジタル・ハイパス伝達関数の特性を次の式に従って制御します。<br>$y(n) = 2^k/(2^k + 1) [x(n) - x(n - 1) + y(n - 1)]$ (表3を参照) |

| 25[9:0]       | 0x19[9:0]     | 0      | OFFSET_CH8                      | チャネル8のコードから減算する値                                                                                                                                             |

| 25[15:11]     | 0x19[15:11]   | 0      | DIGITAL_GAIN_CH8                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 27[9:0]       | 0x1B[9:0]     | 0      | OFFSET_CH7                      | チャネル7のコードから減算する値                                                                                                                                             |

| 27[15:11]     | 0x1B[15:11]   | 0      | DIGITAL_GAIN_CH7                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 29[9:0]       | 0x1D[9:0]     | 0      | OFFSET_CH6                      | チャネル6のコードから減算する値                                                                                                                                             |

| 29[15:11]     | 0x1D[15:11]   | 0      | DIGITAL_GAIN_CH6                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 31[9:0]       | 0x1F[9:0]     | 0      | OFFSET_CH5                      | チャネル5のコードから減算する値                                                                                                                                             |

| 31[15:11]     | 0x1F[15:11]   | 0      | DIGITAL_GAIN_CH5                | 0dB~6dB(0.2dBステップ)                                                                                                                                           |

| 33[0]         | 0x21[0]       | 0      | DIGITAL_HPF_FILTER_ENABLE_CH5-8 | 0: デジタルHPFフィルタをディスエーブル<br>1: 5~8チャネルに対してイネーブル                                                                                                                |

| 33[4:1]       | 0x21[4:1]     | 0      | DIGITAL_HPF_FILTER_K_CH5-8      | ハイパス・フィルタのKを設定(Kは2~4、0010B~0100B)。<br>この4レジスタのグループは、出力データに適用されるデジタル・ハイパス伝達関数の特性を次の式に従って制御します。<br>$y(n) = 2^k/(2^k + 1) [x(n) - x(n - 1) + y(n - 1)]$ (表3を参照) |

表2. ADCレジスタ・マップ

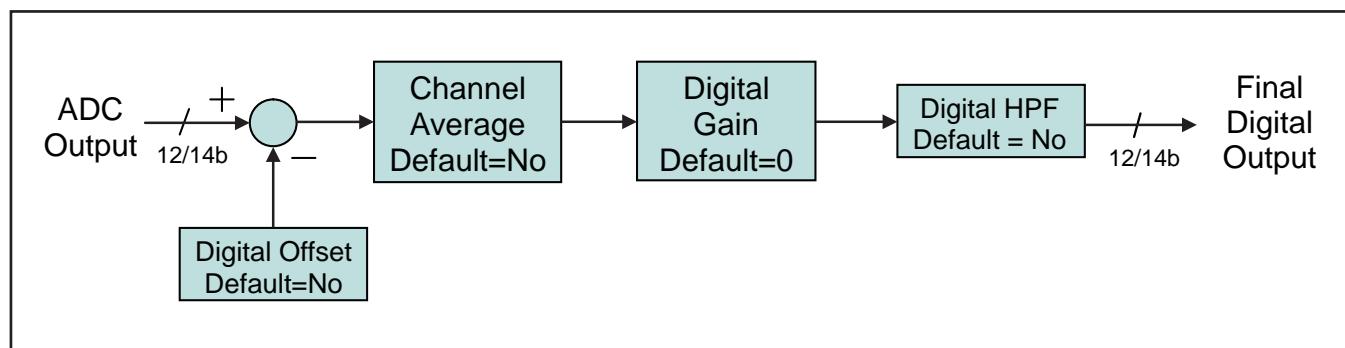

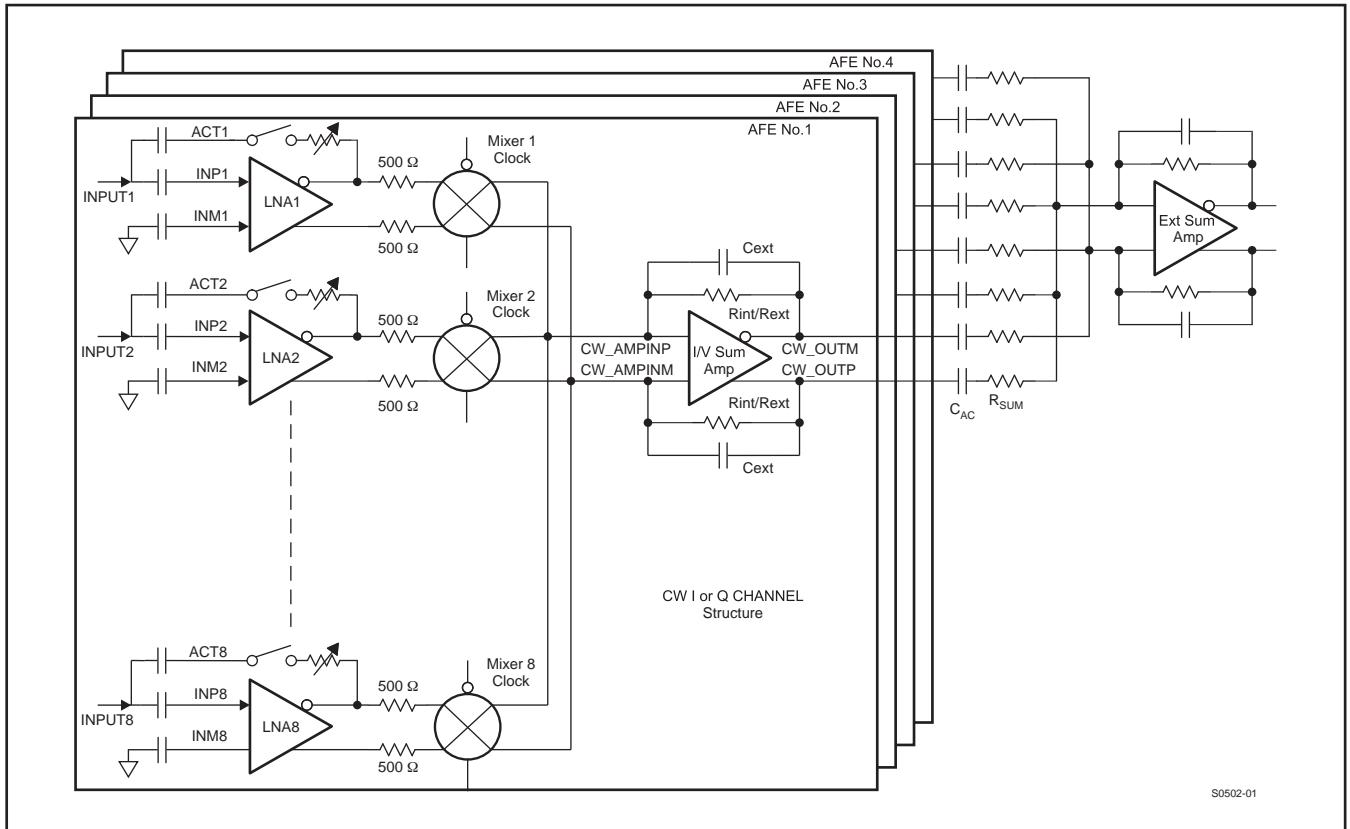

## AFE5808のADCレジスタ/デジタル処理の説明

AFE5808内のADCには、さまざまなデジタル処理機能が搭載され、超音波システムの性能向上に役立ちます。デジタル処理ブロックは、図62のように構成されています。

### AVERAGING\_ENABLE : アドレス : 2[11]

1に設定すると、2つの連続したチャネル（チャネル1と2、チャネル3と4、チャネル5と6、チャネル7と8）に対応した2つのサンプルが平均化されます。両方のチャネルの入力が同じである場合は、実効的にSNRが向上します。平均化は次のように行われます。

- ・チャネル1 + チャネル2をチャネル3に出力

- ・チャネル3 + チャネル4をチャネル4に出力

- ・チャネル5 + チャネル6をチャネル5に出力

- ・チャネル7 + チャネル8をチャネル6に出力

### ADC\_OUTPUT\_FORMAT : アドレス : 4[3]

デフォルトでは、ADC出力は2の補数モードになります。ADC\_OUTPUT\_FORMATビットを1にプログラミングすると、MSBが反転し、出力はストレート・オフセット・バイナリ・モードになります。

### DIGITAL\_GAIN\_ENABLE : アドレス : 3[12]

このビットを1に設定すると、各チャネル*i*について、対応するゲインがDIGITAL\_GAIN\_CH*i*<15:11>で与えられます。実際のゲインは、0dB + 0.2dB×DIGITAL\_GAIN\_CH*i*<15:11>となります。例えば、DIGITAL\_GAIN\_CH5<15:11> = 3の場合は、チャネル5のゲインが0.6dB増加します。DIGITAL\_GAIN\_CH*i*<15:11> = 31の場合は、DIGITAL\_GAIN\_CH*i*<15:11> = 30と同じ結果となり、チャネル*i*のゲインが6dBに設定されます。

### DIGITAL\_HPF\_ENABLE

- ・CH1-4 : アドレス21[0]

- ・CH5-8 : アドレス33[0]

### DIGITAL\_HPF\_FILTER\_K\_CHX

- ・CH1-4 : アドレス21[4:1]

- ・CH5-8 : アドレス3[4:1]

このレジスタのグループは、出力データに適用されるデジタル・ハイパス伝達関数の特性を式(1)に従って制御します。

$$y(n) = \frac{2^k}{2^k + 1} [x(n) - x(n-1) + y(n-1)] \quad (1)$$

これらのデジタルHPFレジスタ（最初の4チャネルに対して1つ、次の4チャネルに対して1つ）は、Kの設定を保持します。デジタル・ハイパス・フィルタを使用して、超音波エコー信号によく見られる低周波ノイズを抑制できます。このデジタル・フィルタは、T/Rスイッチの低周波応答によって、ニア・フィールドの回復時間を大きく向上させます。表3に、カットオフ周波数とKの関係を示します。

| K | 40 MSPS  | 50 MSPS  | 65 MSPS  |

|---|----------|----------|----------|

| 2 | 2780 kHz | 3480 kHz | 4520 kHz |

| 3 | 1490 kHz | 1860 kHz | 2420 kHz |

| 4 | 770 kHz  | 960 kHz  | 1250 kHz |

表3. KおよびFsに対応したデジタルHPFの-1dBコーナー周波数

図 62. ADCデジタル・ブロック図

## **LOW\_FREQUENCY\_NOISE\_SUPPRESSION : アドレス：1[11]**

低周波ノイズ抑制モードは、0MHz～1MHz(DC付近)の周波数帯で良好なノイズ特性が求められるようなアプリケーションで特に有用です。このモードを設定すると、AFE5808の低周波ノイズが約Fs/2までシフトされ、DC付近のノイズ・フロアがずっと低い値へと移動します。この機能は、レジスタ・ビット1[11]を使用してイネーブルまたはディスエーブルにできます。この機能をイネーブルにすると、デバイスの消費電力が約1mW/CHだけわずかに増加します。

## **LVDS\_OUTPUT\_RATE\_2X : アドレス：1[14]**

出力データは常にDDR形式を使用し、LVDSビット・クロック(DCLK)の立ち上がりおよび立ち下がりエッジで、有効な異なるビットが出力されます。出力レートはデフォルトで1X(LVDS\_OUTPUT\_RATE\_2X = 0)に設定され、各ADCに1つのLVDSストリームが関連付けられます。サンプリング・レートが十分に低い場合は、2つのADCが1つのLVDSストリームを共有します。それにより、インターフェイスへの消費電力が低減されます。未使用の出力では、ゼロが出力されます。これらの出力からの電力消費を避けるため、未使用出力への終端接続は不要です。使用する出力ペアの振り分けは、次のように行われます。

- チャネル1とチャネル2をチャネル3に出力します。チャネル1が最初に出力されます。

- チャネル3とチャネル4をチャネル4に出力します。チャネル3が最初に出力されます。

- チャネル5とチャネル6をチャネル5に出力します。チャネル5が最初に出力されます。

- チャネル7とチャネル8をチャネル6に出力します。チャネル7が最初に出力されます。

## **CHANNEL\_OFFSET\_SUBTRACTION\_ENABLE : アドレス：3[8]**

このビットを1に設定すると、対応するOFFSET\_CHx<9:0>(チャネルiのオフセット)の値がADC出力から減算されます。数値は2の補数形式で指定されます。例えば、OFFSET\_CHx<9:0> = 11 1000 0000の場合は、-128を減算することを意味します。OFFSET\_CHx<9:0> = 00 0111 1111の場合は、127が減算されます。実際には、加算と減算の両方を実行できます。オフセットはデジタル・ゲイン(DIGITAL\_GAIN\_ENABLEを参照)よりも前に適用されることに注意してください。内部ではデータ・パス全体が2の補数であり、デジタル・ゲインは最後のステップです。DFS = 1(ストレート・バイナリ・オフセット形式)の場合のみ、2の補数のワードが最後にオフセット・バイナリに変換されます。

## **SERIALIZED\_DATA\_RATE : アドレス： 3[14:13]**

詳細については、表1を参照してください。

## **TEST\_PATTERN\_MODES : アドレス： 2[15:13]**

AFE5808は、LVDS出力上で各種のテスト・パターンを出力できます。これらのテスト・パターンは、通常のADCデータ出力の代わりに出力されます。また、6つのプリセット・パターンを出力させることもできます。

1. ランプ：レジスタ2[15:13]を111に設定すると、すべてのチャネルで、繰り返しフルスケール・ランプ・パターンが出力されます。このパターンは、ゼロ・コードからフルスケール・コードまで、クロック・サイクル毎に1LSB単位で上昇します。フルスケール・コードに達すると、ゼロ・コードに戻って再び上昇を開始します。

2. オール0：レジスタ2[15:13]を110に設定することで、オール0を出力するようデバイスをプログラミングできます。