# ADS868xW バイポーラ入力範囲をプログラム可能な 16 ビット、高速、単一電源 SAR (逐次比較) ADC データ アクイジションシステム

## 1 特長

- アナログ フロントエンド内蔵の 16 ビット ADC

- 高速度:

- ADS8681W: 1MSPS

- ADS8685W: 500kSPS

- ADS8689W: 100kSPS

- 入力範囲をソフトウェアでプログラム可能

- バイポーラ差動範囲:  $\pm 12.288V$ ,  $\pm 10.24V$ ,  $\pm 6.144V$ ,  $\pm 5.12V$ ,  $\pm 2.56V$

- ユニポーラ差動範囲:  $0V \sim 12.288V$ ,  $0V \sim 10.24V$ ,  $0V \sim 6.144V$ ,  $0V \sim 5.12V$

- アナログ電源 (5V): 1.65V~5V の I/O 電源

- $1M\Omega$  以上の一定の抵抗性入力インピーダンス

- 入力帯域幅: 450kHz

- 入力過電圧保護: 最大  $\pm 20V$

- オンチップの低ドリフト 4.096V 基準電圧

- 優れた性能

- DNL:  $\pm 0.6LSB$ , INL:  $\pm 0.6LSB$

- 信号対雑音比: 80dB, THD: -105dB

- 高 / 低スレッショルドのアラーム機能

- デイジタル チェーン対応の multiSPI™ インターフェイス

- 温度範囲: -40°C ~ +125°C

## 2 アプリケーション

- アナログ入力モジュール

- 半導体テスト

- サーボドライブ制御モジュール

## 3 説明

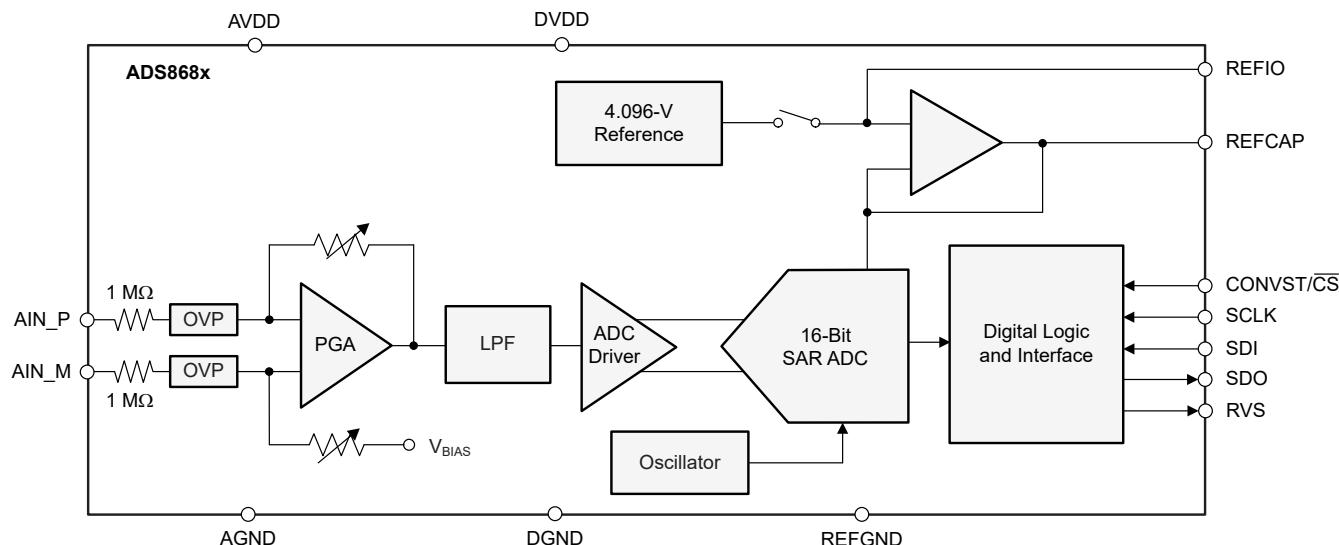

The ADS8681W, ADS8685W, および ADS8689W は、逐次比較型 (SAR) A/D コンバータ (ADC) トポロジを使った統合型データ アクイジション システム ファミリの製品です。これらのデバイスには、高速、高精度の SAR ADC と、統合型の差動アナログ フロントエンド (AFE) 入力ドライバ回路が。ADS868xW には、最大  $\pm 20V$  の過電圧保護回路と、温度ドリフトが非常に小さい 4.096V のオンチップ基準電圧が内蔵されています。

これらのデバイスは 5V の単一アナログ電源ですが、真のバイポーラ入力範囲とユニポーラ入力範囲をサポートします。バイポーラ入力範囲は  $\pm 12.288V$ ,  $\pm 6.144V$ ,  $\pm 10.24V$ ,  $\pm 5.12V$ ,  $\pm 2.56V$  です。また、ユニポーラ入力範囲は  $0V \sim 12.288V$ ,  $10.24V$ ,  $6.144V$ ,  $5.12V$  です。これらのデバイスは、選択した入力範囲にかかわらず、高い抵抗性入力インピーダンス ( $1M\Omega$  以上) を実現しています。

内蔵の multiSPI デジタル インターフェイスは、従来の SPI プロトコルと下位互換性があります。さらに、設定可能な機能により、広範なホストコントローラとの接続が簡素化されます。

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| ADS868xW | RUM (WQFN, 16)       | 4mm × 4mm                |

(1) 詳細については、[メカニカル、パッケージ、および注文情報](#)をご覧ください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

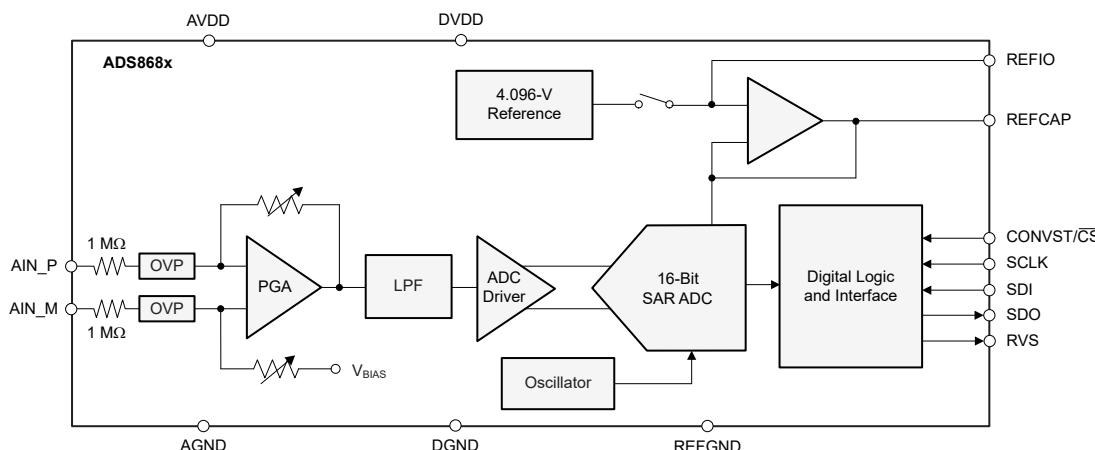

ブロック図

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | 6.4 デバイスの機能モード                | <b>36</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | 6.5 プログラミング                   | <b>41</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>7 レジスタ マップ</b>             | <b>50</b> |

| <b>4 ピン構成および機能</b> | <b>3</b>  | 7.1 デバイス構成およびレジスタ マップ         | <b>50</b> |

| <b>5 仕様</b>        | <b>4</b>  | <b>8 アプリケーションと実装</b>          | <b>59</b> |

| 5.1 絶対最大定格         | 4         | 8.1 アプリケーション情報                | 59        |

| 5.2 ESD 定格         | 4         | 8.2 代表的なアプリケーション              | 59        |

| 5.3 推奨動作条件         | 5         | 8.3 電源に関する推奨事項                | 62        |

| 5.4 熱に関する情報        | 5         | 8.4 レイアウト                     | 63        |

| 5.5 電気的特性          | 6         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>65</b> |

| 5.6 タイミング要件        | 10        | 9.1 ドキュメントのサポート               | 65        |

| 5.7 スイッチング特性       | 11        | 9.2 ドキュメントの更新通知を受け取る方法        | 65        |

| 5.8 タイミング図         | 13        | 9.3 サポート・リソース                 | 65        |

| 5.9 代表的特性          | 16        | 9.4 商標                        | 65        |

| <b>6 詳細説明</b>      | <b>22</b> | 9.5 静電気放電に関する注意事項             | 65        |

| 6.1 概要             | 22        | 9.6 用語集                       | 65        |

| 6.2 機能ブロック図        | 22        | <b>10 改訂履歴</b>                | <b>65</b> |

| 6.3 機能説明           | 23        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>65</b> |

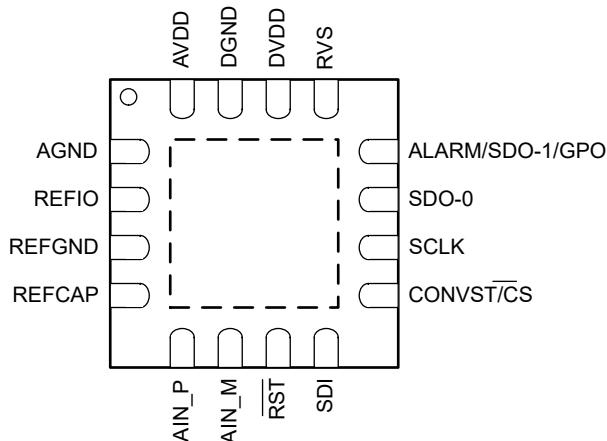

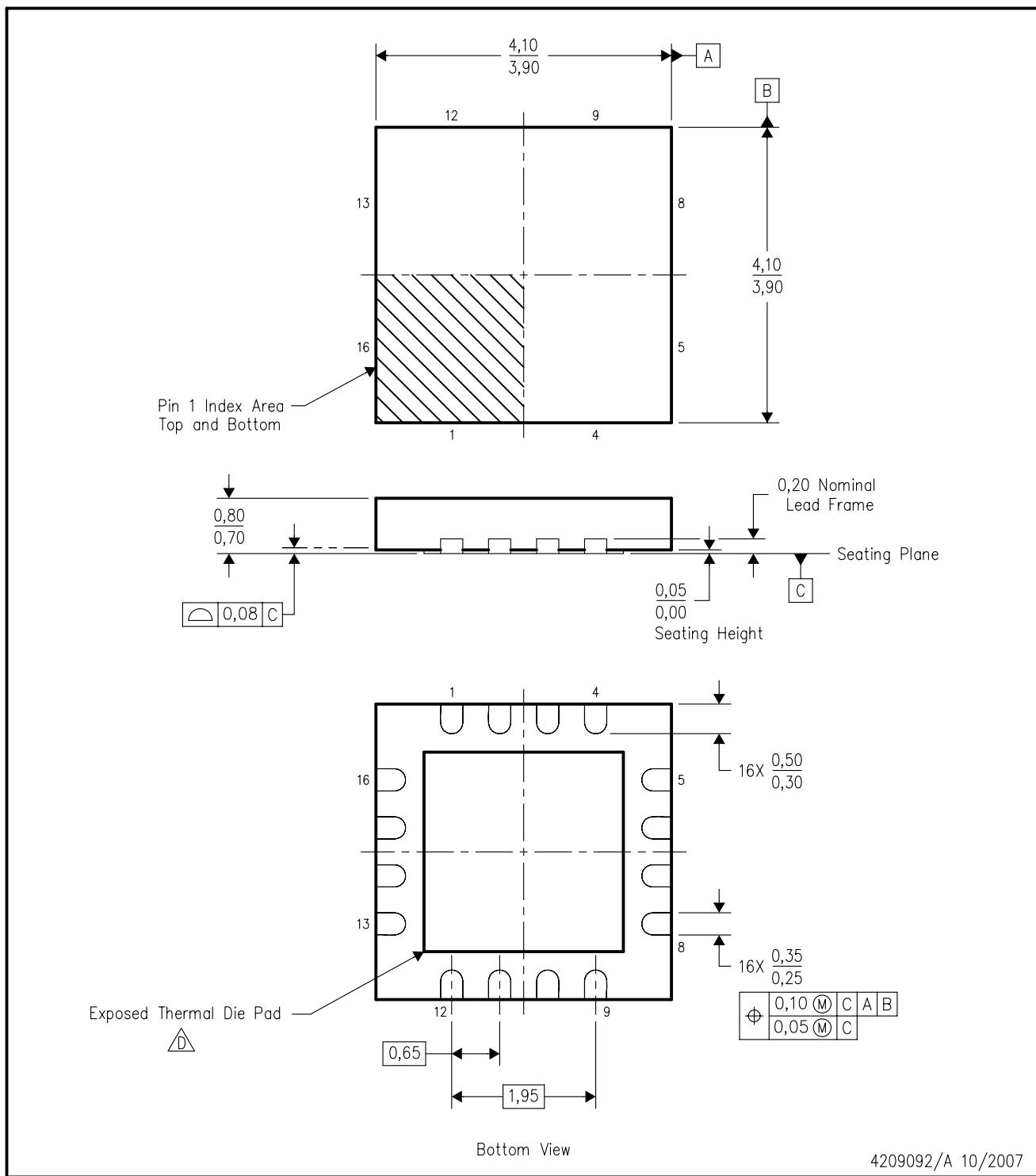

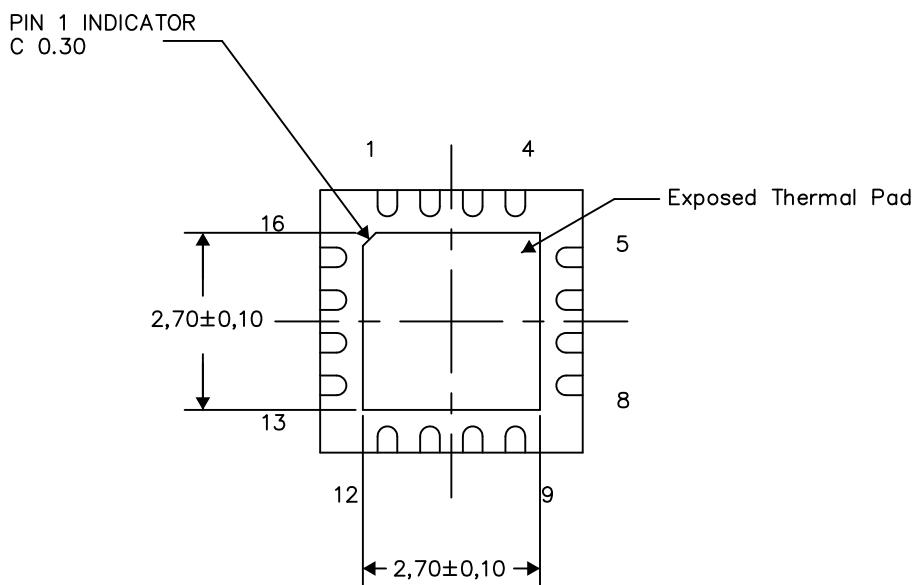

## 4 ピン構成および機能

図 4-1. RUM パッケージ、16 ピン WQFN (上面図)

表 4-1. ピンの機能

| 名称              | 番号 | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                  |

|-----------------|----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND            | 1  | P                 | アナログ グランドピン。AVDD ピンでデカッピング。                                                                                                                                                         |

| AIN_M           | 6  | AI                | アナログ入力: 負。AIN_P ピンでデカッピング。                                                                                                                                                          |

| AIN_P           | 5  | AI                | アナログ入力: 正。AIN_M ピンでデカッピング。                                                                                                                                                          |

| ALARM/SDO-1/GPO | 12 | DO                | マルチファンクション出力ピン。アクティブ High アラーム。<br>シリアル通信用のデータ出力 1。汎用出力ピン。                                                                                                                          |

| AVDD            | 16 | P                 | アナログ電源ピン。AGND ピンでデカッピング。                                                                                                                                                            |

| CONVST/CS       | 9  | DI                | デュアル機能ピン。<br>アクティブ High ロジック: 変換開始入力ピン。CONVST の立ち上がりエッジにより、デバイスがアクイジョンフェーズから変換フェーズに移行。<br>アクティブ Low ロジック: チップセレクト入力ピン。CS が Low のとき、デバイスがデータバスを制御。CS が High のとき、SDO-x ピンがトライステートに移行。 |

| DGND            | 15 | P                 | デジタルグランドピン。DVDD ピンでデカッピング。                                                                                                                                                          |

| DVDD            | 14 | P                 | デジタル電源ピン。DGND ピンでデカッピング。                                                                                                                                                            |

| REFCAP          | 4  | AO                | ADC リファレンスバッファデカッピングコンデンサピン。REFGND ピンでデカッピング。                                                                                                                                       |

| REFGND          | 3  | P                 | リファレンスグランドピン。このピンをアナロググランドプレーンに短絡。REFIO および REFCAP ピンでデカッピング。                                                                                                                       |

| REFIO           | 2  | AIO               | 内部リファレンス出力と外部リファレンス入力ピン。REFGND でデカッピング。                                                                                                                                             |

| RST             | 7  | DI                | デバイスをリセットするためのアクティブ Low ロジック入力。                                                                                                                                                     |

| RVS             | 13 | DO                | シリアルインターフェイスのマルチファンクション出力ピン。「RESET 状態」セクションを参照。<br>CS を High に保持すると、RVS は内部 ADCST 信号のステータスを反映する。<br>CS が Low の場合、RVS のステータスは出力プロトコルの選択によって異なる。                                      |

| SCLK            | 10 | DI                | シリアル通信: シリアルインターフェイスのクロック入力ピン。<br>すべてのシステム同期データ転送プロトコルは、SCLK 信号を基準にタイミングが調整されます。                                                                                                    |

| SDI             | 8  | DI                | デュアル機能: シリアル通信用のデータ入力ピン。<br>デイジーチェーンモードでのシリアル通信中のチェーンデータ入力。                                                                                                                         |

| SDO-0           | 11 | DO                | シリアル通信: データ出力 0。                                                                                                                                                                    |

(1) AI = アナログ入力、AIO = アナログ入出力、DI = デジタル入力、DO = デジタル出力、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                      |             | 最小値  | 最大値        | 単位 |

|--------------------------------------|-------------|------|------------|----|

| AIN_P、AIN_M から GND                   | AVDD = 5V   | -20  | 20         | V  |

|                                      | AVDD = 電源オフ | -15  | 15         |    |

| AVDD から GND または DVDD から GND          |             | -0.3 | 7          | V  |

| REFCAP から REFGND または REFIO から REFGND |             | -0.3 | 5.7        | V  |

| GND から REFGND                        |             | -0.3 | 0.3        | V  |

| デジタル入力ピンから GND                       |             | -0.3 | DVDD + 0.3 | V  |

| デジタル出力ピンから GND                       |             | -0.3 | DVDD + 0.3 | V  |

| 電源ピンを除く任意のピンへの入力電流                   |             | -10  | 10         | mA |

| 接合部温度、 $T_J$                         |             | -40  | 150        | °C |

| 保管温度、 $T_{stg}$                      |             | -60  | 150        | °C |

- (1) 絶対最大定格を超えた動作は、デバイスに恒久的な損傷を与える可能性があります。絶対最大定格は、これらの条件において、または 推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                                             | 値     | 単位 |

|-------------|------|-----------------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、アナログ入力ピン (AIN_P、AIN_M) <sup>(1)</sup> | ±4000 | V  |

|             |      | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、他すべてのピン <sup>(1)</sup>               | ±2000 |    |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup>            | ±500  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ            |                             | テスト条件                             | 最小値     | 標準値    | 最大値   | 単位 |

|------------------|-----------------------------|-----------------------------------|---------|--------|-------|----|

| <b>電源</b>        |                             |                                   |         |        |       |    |

| AVDD             | アナログ電源                      | AVDD から GND                       | 4.75    | 5      | 5.25  | V  |

| DVDD             | デジタル インターフェイス電源             | DVDD から GND                       | 1.65    | 3.3    | AVDD  | V  |

| <b>基準電圧</b>      |                             |                                   |         |        |       |    |

| $V_{REFIO\_EXT}$ | REFIO での外部リファレンス電圧          | REFIO ピンは入力として構成                  | 4.046   | 4.096  | 4.146 | V  |

| <b>アナログ入力</b>    |                             |                                   |         |        |       |    |

| AIN_x            | フルスケール入力範囲 (AIN_P から AIN_M) | 入力範囲 = $\pm 3 \times V_{REF}$     | -12.288 | 12.288 | V     |    |

|                  |                             | 入力範囲 = $\pm 2.5 \times V_{REF}$   | -10.24  | 10.24  |       |    |

|                  |                             | 入力範囲 = $\pm 1.5 \times V_{REF}$   | -6.144  | 6.144  |       |    |

|                  |                             | 入力範囲 = $\pm 1.25 \times V_{REF}$  | -5.12   | 5.12   |       |    |

|                  |                             | 入力範囲 = $\pm 0.625 \times V_{REF}$ | -2.56   | 2.56   |       |    |

|                  |                             | 入力範囲 = $3 \times V_{REF}$         | 0       | 12.288 |       |    |

|                  |                             | 入力範囲 = $2.5 \times V_{REF}$       | 0       | 10.24  |       |    |

|                  |                             | 入力範囲 = $1.5 \times V_{REF}$       | 0       | 6.144  |       |    |

|                  |                             | 入力範囲 = $1.25 \times V_{REF}$      | 0       | 5.12   |       |    |

| <b>温度範囲</b>      |                             |                                   |         |        |       |    |

| $T_A$            | 周囲温度                        |                                   | -40     | 25     | 125   | °C |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | ADS868xW   | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | RUM (WQFN) |      |

|                      |                     | 16 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 31.9       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 27.9       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 7.4        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.3        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 7.4        | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 1.9        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ            |           | テスト条件                                                                                     | 最小値                                     | 標準値 | 最大値 | 単位               |

|------------------|-----------|-------------------------------------------------------------------------------------------|-----------------------------------------|-----|-----|------------------|

| <b>アナログ入力</b>    |           |                                                                                           |                                         |     |     |                  |

| $R_{\text{IN}}$  | 入力インピーダンス | 入力範囲 = $T_A = 25^\circ\text{C}$ で $\pm 3 \times V_{\text{REF}}$                           | 1.02                                    | 1.2 |     | $\text{M}\Omega$ |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $\pm 2.5 \times V_{\text{REF}}$                         | 0.85                                    | 1   |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $\pm 1.5 \times V_{\text{REF}}$                         | 1.02                                    | 1.2 |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $\pm 1.25 \times V_{\text{REF}}$                        | 0.85                                    | 1   |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $\pm 0.625 \times V_{\text{REF}}$                       | 0.85                                    | 1   |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $3 \times V_{\text{REF}}$                               | 1.02                                    | 1.2 |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $2.5 \times V_{\text{REF}}$                             | 0.85                                    | 1   |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $1.5 \times V_{\text{REF}}$                             | 1.02                                    | 1.2 |     |                  |

|                  |           | 入力範囲 = $T_A = 25^\circ\text{C}$ で $1.25 \times V_{\text{REF}}$                            | 0.85                                    | 1   |     |                  |

| $I_{\text{IN}}$  | 入力電流      | 入力範囲 $\pm 3 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧       | $(V_{\text{IN}} - 2.5) / R_{\text{IN}}$ |     |     | $\mu\text{A}$    |

|                  |           | 入力範囲 = $\pm 2.5 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧   | $(V_{\text{IN}} - 2.2) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧   | $(V_{\text{IN}} - 2.0) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $\pm 1.25 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧  | $(V_{\text{IN}} - 2.0) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $\pm 0.625 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧 | $(V_{\text{IN}} - 1.6) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $3 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧         | $(V_{\text{IN}} - 2.6) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $2.5 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧       | $(V_{\text{IN}} - 2.5) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $1.5 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧       | $(V_{\text{IN}} - 2.7) / R_{\text{IN}}$ |     |     |                  |

|                  |           | 入力範囲 = $1.25 \times V_{\text{REF}}$ 、AIN_P ピン = $V_{\text{IN}}$ および AIN_M = GND での電圧      | $(V_{\text{IN}} - 2.5) / R_{\text{IN}}$ |     |     |                  |

| <b>入力過電圧保護回路</b> |           |                                                                                           |                                         |     |     |                  |

| $V_{\text{OVP}}$ | すべての入力範囲  | AVDD = 5V、すべての入力範囲                                                                        | -20                                     | 20  |     | $\text{V}$       |

|                  |           | AVDD = フローティング、すべての入力範囲                                                                   | -15                                     | 15  |     |                  |

| <b>入力帯域幅</b>     |           |                                                                                           |                                         |     |     |                  |

| $f_{3\text{dB}}$ | 小信号入力帯域幅  | -3dB 入力範囲 = $\pm 3 \times V_{\text{REF}}$                                                 | 454                                     |     |     | $\text{kHz}$     |

|                  |           | -3dB 入力範囲 = $\pm 2.5 \times V_{\text{REF}}$                                               | 454                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$                                               | 449                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $\pm 1.25 \times V_{\text{REF}}$                                              | 449                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $\pm 0.625 \times V_{\text{REF}}$                                             | 385                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $3 \times V_{\text{REF}}$                                                     | 414                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $2.5 \times V_{\text{REF}}$                                                   | 414                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $1.5 \times V_{\text{REF}}$                                                   | 368                                     |     |     |                  |

|                  |           | -3dB 入力範囲 = $1.25 \times V_{\text{REF}}$                                                  | 368                                     |     |     |                  |

## 5.5 電気的特性 (続き)

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ               |                   | テスト条件                                           | 最小値    | 標準値        | 最大値   | 単位                    |

|---------------------|-------------------|-------------------------------------------------|--------|------------|-------|-----------------------|

| $f_{-0.1\text{dB}}$ | 小信号入力帯域幅          | -0.1dB 入力範囲 = $\pm 3 \times V_{\text{REF}}$     | 74     |            |       | kHz                   |

|                     |                   | -0.1dB 入力範囲 = $\pm 2.5 \times V_{\text{REF}}$   | 74     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$   | 85     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $\pm 1.25 \times V_{\text{REF}}$  | 85     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $\pm 0.625 \times V_{\text{REF}}$ | 64     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $3 \times V_{\text{REF}}$         | 75     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $2.5 \times V_{\text{REF}}$       | 75     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $1.5 \times V_{\text{REF}}$       | 83     |            |       |                       |

|                     |                   | -0.1dB 入力範囲 = $1.25 \times V_{\text{REF}}$      | 83     |            |       |                       |

|                     |                   |                                                 |        |            |       |                       |

| <b>DC 特性</b>        |                   |                                                 |        |            |       |                       |

|                     | 分解能               |                                                 | 16     |            |       | ビット                   |

| NMC                 | ミッシング コードなし       |                                                 | 16     |            |       | ビット                   |

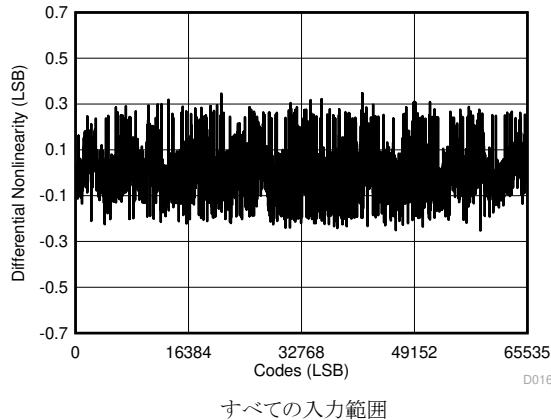

| DNL                 | 微分非直線性            | すべての入力範囲                                        | -0.9   | $\pm 0.6$  | 0.9   | LSB                   |

| INL                 | 積分非直線性            | すべての入力バイポーラ レンジ                                 | -2     | $\pm 0.8$  | 2     | LSB                   |

|                     |                   | すべてのユニポーラ レンジ                                   | -2     | $\pm 0.6$  | 2     |                       |

| $E_o$               | オフセット エラー         | すべての入力バイポーラ レンジ $T_A = 25^\circ\text{C}$        | -1.4   | $\pm 0.2$  | 1.4   | mV                    |

|                     |                   | すべてのユニポーラ レンジ $T_A = 25^\circ\text{C}$          | -2     | $\pm 0.2$  | 2     |                       |

|                     | 温度によるオフセット誤差のドリフト | すべての入力範囲                                        | -3     | $\pm 0.75$ | 3     | ppm/ $^\circ\text{C}$ |

| $E_G$               | ゲイン誤差             | $T_A = 25^\circ\text{C}$ でのすべての入力範囲             | -0.025 | $\pm 0.01$ | 0.025 | %FSR                  |

|                     | 温度によるゲイン誤差のドリフト   | すべての入力範囲                                        | -5     | $\pm 1$    | 5     | ppm/ $^\circ\text{C}$ |

| <b>AC 特性</b>        |                   |                                                 |        |            |       |                       |

| SNR                 | 信号対雑音比            | 入力範囲 = $\pm 3 \times V_{\text{REF}}$            | 79     | 80.4       |       | dB                    |

|                     |                   | 入力範囲 = $\pm 2.5 \times V_{\text{REF}}$          | 79     | 80.6       |       |                       |

|                     |                   | 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$          | 78     | 79.3       |       |                       |

|                     |                   | 入力範囲 = $\pm 1.25 \times V_{\text{REF}}$         | 78     | 79.2       |       |                       |

|                     |                   | 入力範囲 = $\pm 0.625 \times V_{\text{REF}}$        | 76     | 77.2       |       |                       |

|                     |                   | 入力範囲 = $3 \times V_{\text{REF}}$                | 77     | 78.8       |       |                       |

|                     |                   | 入力範囲 = $2.5 \times V_{\text{REF}}$              | 77     | 78.8       |       |                       |

|                     |                   | 入力範囲 = $1.5 \times V_{\text{REF}}$              | 76     | 77.5       |       |                       |

|                     |                   | 入力範囲 = $1.25 \times V_{\text{REF}}$             | 76     | 77.3       |       |                       |

| THD                 | 全高調波歪             | すべての入力範囲                                        |        | -105       |       | dB                    |

| SINAD               | 信号対雑音 + 歪み        | 入力範囲 = $\pm 3 \times V_{\text{REF}}$            | 79     | 80.4       |       | dB                    |

|                     |                   | 入力範囲 = $\pm 2.5 \times V_{\text{REF}}$          | 79     | 80.6       |       |                       |

|                     |                   | 入力範囲 = $\pm 1.5 \times V_{\text{REF}}$          | 78     | 79.4       |       |                       |

|                     |                   | 入力範囲 = $\pm 1.25 \times V_{\text{REF}}$         | 78     | 79.3       |       |                       |

|                     |                   | 入力範囲 = $\pm 0.625 \times V_{\text{REF}}$        | 76     | 77.3       |       |                       |

|                     |                   | 入力範囲 = $3 \times V_{\text{REF}}$                | 77     | 78.9       |       |                       |

|                     |                   | 入力範囲 = $2.5 \times V_{\text{REF}}$              | 77     | 78.8       |       |                       |

|                     |                   | 入力範囲 = $1.5 \times V_{\text{REF}}$              | 76     | 77.5       |       |                       |

|                     |                   | 入力範囲 = $1.25 \times V_{\text{REF}}$             | 76     | 77.4       |       |                       |

## 5.5 電気的特性 (続き)

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ                     |                              | テスト条件                                                                           | 最小値        | 標準値        | 最大値           | 単位                    |  |  |

|---------------------------|------------------------------|---------------------------------------------------------------------------------|------------|------------|---------------|-----------------------|--|--|

| SFDR                      | スプリアスフリー ダイナミックレンジ           | すべての入力範囲                                                                        | 109        |            | dB            |                       |  |  |

| <b>内部リファレンス出力</b>         |                              |                                                                                 |            |            |               |                       |  |  |

| $V_{\text{REFIO}}$        | REFIO ピン (出力として構成)           | $T_A = 25^\circ\text{C}$ での WQFN (RUM)                                          | 4.094      | 4.096      | 4.098         | V                     |  |  |

| $dV_{\text{REFIO}}/dT_A$  | 内部リファレンス温度ドリフト               |                                                                                 |            | 5          |               | ppm/ $^\circ\text{C}$ |  |  |

| $C_{\text{OUT\_REFIO}}$   | REFIO ピンのデカップリング コンデンサ       |                                                                                 | 4.7        |            | $\mu\text{F}$ |                       |  |  |

| $V_{\text{REFCAP}}$       | ADC へのリファレンス電圧 (REFCAP ピン経由) |                                                                                 | 4.095      | 4.096      | 4.097         | V                     |  |  |

|                           | REFCAP 温度ドリフト                |                                                                                 |            | 0.5        | 2             | ppm/ $^\circ\text{C}$ |  |  |

| $C_{\text{OUT\_REFCAP}}$  | REFCAP ピンのデカップリング コンデンサ      |                                                                                 | 10         |            | $\mu\text{F}$ |                       |  |  |

|                           | ターンオン時間                      | $C_{\text{OUT\_REFCAP}} = 10\mu\text{F}, C_{\text{OUT\_REFIO}} = 10\mu\text{F}$ | 20         |            | ms            |                       |  |  |

| <b>AVDD コンパレータ</b>        |                              |                                                                                 |            |            |               |                       |  |  |

| $V_{\text{TH\_HIGH}}$     | High スレッショルド電圧               |                                                                                 | 5.3        |            | V             |                       |  |  |

| $V_{\text{TH\_LOW}}$      | 低スレッショルド電圧                   |                                                                                 | 4.7        |            |               |                       |  |  |

| <b>デジタル入力 (CMOS)</b>      |                              |                                                                                 |            |            |               |                       |  |  |

| $V_{\text{IH}}$           | デジタル高入力電圧ロジック レベル            | DVDD > 2.35V                                                                    | 0.7 × DVDD | DVDD + 0.3 | V             |                       |  |  |

|                           |                              | DVDD ≤ 2.35V                                                                    | 0.8 × DVDD | DVDD + 0.3 |               |                       |  |  |

| $V_{\text{IL}}$           | デジタル低入力電圧ロジック レベル            | DVDD > 2.35V                                                                    | -0.3       | 0.3 × DVDD | V             |                       |  |  |

|                           |                              | DVDD ≤ 2.35V                                                                    | -0.3       | 0.2 × DVDD |               |                       |  |  |

|                           | 入力リーク電流                      |                                                                                 | 100        |            | nA            |                       |  |  |

|                           | 入力ピン容量                       |                                                                                 | 5          |            | pF            |                       |  |  |

| <b>デジタル出力 (CMOS)</b>      |                              |                                                                                 |            |            |               |                       |  |  |

| $V_{\text{OH}}$           | デジタル高出力電圧ロジック レベル            | $I_O = 500\mu\text{A}$ ソース                                                      | 0.8 × DVDD | DVDD       | V             |                       |  |  |

| $V_{\text{OL}}$           | デジタル低出力電圧ロジック レベル            | $I_O = 500\mu\text{A}$ シンク                                                      | 0          | 0.2 × DVDD | V             |                       |  |  |

|                           | フローティング状態のリーク電流              | デジタル出力ピンのみ                                                                      | 1          |            | $\mu\text{A}$ |                       |  |  |

|                           | 内部ピン容量                       |                                                                                 | 5          |            | pF            |                       |  |  |

| <b>電源要件</b>               |                              |                                                                                 |            |            |               |                       |  |  |

| AVDD                      | アナログ電源電圧                     | 動作範囲                                                                            | 4.75       | 5          | 5.25          | V                     |  |  |

| DVDD                      | デジタル電源電圧                     | 動作範囲                                                                            | 1.65       | 3.3        | AVDD          | V                     |  |  |

|                           |                              | 規定性能の電源電圧範囲                                                                     | 2.7        | 3.3        | AVDD          |                       |  |  |

| $ I_{\text{AVDD\_DY}} _N$ | アナログ電源電流、デバイスは最大スループットで変換    | 内部リファレンス ADS8681W                                                               | 8.2        |            | 10.5          | mA                    |  |  |

|                           |                              | 内部リファレンス ADS8681W                                                               | 5.6        |            | 7.25          |                       |  |  |

|                           |                              | 内部リファレンス ADS8685W                                                               | 4          |            | 5             |                       |  |  |

|                           |                              | 外部リファレンス ADS8689W                                                               | 7.0        |            | 8.75          |                       |  |  |

|                           |                              | 外部リファレンス ADS8685W                                                               | 4.4        |            | 5.5           |                       |  |  |

|                           |                              | 外部リファレンス ADS8689W                                                               | 2.7        |            | 3.25          |                       |  |  |

## 5.5 電気的特性 (続き)

すべての最小値および最大値の仕様は  $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、標準仕様は  $T_A = 25^{\circ}\text{C}$ 、AVDD = 5V、DVDD = 3.3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

| パラメータ                     |                            | テスト条件                      | 最小値 | 標準値  | 最大値 | 単位            |

|---------------------------|----------------------------|----------------------------|-----|------|-----|---------------|

| $I_{\text{AVDD\_STC}}$    | アナログ電源電流、デバイスは未変換          | 内部リファレンス ADS8681W          | 4.7 | 6.25 |     | mA            |

|                           |                            | 内部リファレンス ADS8685W、ADS8689W | 3.5 | 4.7  |     |               |

|                           |                            | 外部リファレンス ADS8681W          | 3.5 | 4.5  |     |               |

|                           |                            | 外部リファレンス ADS8685W、ADS8689W | 2.3 | 3    |     |               |

| $I_{\text{AVDD\_STD BY}}$ | アナログ電源電流、デバイスは STANDBY モード | 内部リファレンス                   | 2.8 |      |     | mA            |

|                           |                            | 外部リファレンス                   | 1.6 |      |     |               |

| $I_{\text{AVDD\_PD}}$     | アナログ電源電流、デバイスは PD モード      | 内部リファレンス                   | 10  |      |     | $\mu\text{A}$ |

|                           |                            | 外部リファレンス                   | 10  |      |     |               |

| $I_{\text{DVDD\_DYN}}$    | デジタル電源電流、最大スループット          |                            | 0.2 | 0.25 |     | mA            |

| $I_{\text{DVDD\_STD BY}}$ | デジタル電源電流、デバイスは STANDBY モード |                            | 1   |      |     | $\mu\text{A}$ |

| $I_{\text{DVDD\_PD}}$     | デジタル電源電流、デバイスは PD モード      |                            | 1   |      |     | $\mu\text{A}$ |

## 5.6 タイミング要件

すべての最小値および最大値の仕様は  $T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、標準仕様は  $T_A = 25^{\circ}\text{C}$ 、AVDD = 5V、DVDD = 3.3V、VREF = 4.096V (内部)、および最大スループット (特に記述のない限り)

|                                    |                                                                     |          | 最小値                    | 標準値   | 最大値  | 単位               |

|------------------------------------|---------------------------------------------------------------------|----------|------------------------|-------|------|------------------|

| <b>変換サイクル</b>                      |                                                                     |          |                        |       |      |                  |

| $f_{\text{cycle}}$                 | サンプリング周波数                                                           | ADS8681W |                        |       | 1000 | kSPS             |

|                                    |                                                                     | ADS8685W |                        |       | 500  |                  |

|                                    |                                                                     | ADS8689W |                        |       | 100  |                  |

| $t_{\text{cycle}}$                 | ADC サイクル時間周期                                                        |          | $1 / f_{\text{cycle}}$ |       |      | s                |

| $t_{\text{acq}}$                   | アクイジョン時間                                                            | ADS8681W | 335                    |       |      | ns               |

|                                    |                                                                     | ADS8685W | 1000                   |       |      |                  |

|                                    |                                                                     | ADS8689W | 5000                   |       |      |                  |

| <b>非同期リセット</b>                     |                                                                     |          |                        |       |      |                  |

| $t_{\text{wl\_RST}}$               | パルス幅 $\overline{\text{RST}}$ が Low                                  |          | 100                    |       |      | ns               |

| <b>SPI 互換シリアル インターフェイス</b>         |                                                                     |          |                        |       |      |                  |

| $f_{\text{CLK}}$                   | シリアル クロック周波数                                                        |          |                        | 66.67 | MHz  |                  |

| $t_{\text{CLK}}$                   | シリアル クロック期間                                                         |          | $1/f_{\text{CLK}}$     |       |      |                  |

| $t_{\text{PH\_CK}}$                | SCLK High 時間                                                        |          | 0.45                   | 0.55  |      | $t_{\text{CLK}}$ |

| $t_{\text{PL\_CK}}$                | SCLK Low 時間                                                         |          | 0.45                   | 0.55  |      | $t_{\text{CLK}}$ |

| $t_{\text{SU\_CSCK}}$              | セットアップ時間: CONVST/ $\overline{\text{CS}}$ 立ち下がりから最初の SCLK キャプチャエッジまで |          | 7.5                    |       |      | ns               |

| $t_{\text{SU\_CKDI}}$              | セットアップ時間: SDI データ有効から SCLK キャプチャエッジまで                               |          | 7.5                    |       |      | ns               |

| $t_{\text{HT\_CKDI}}$              | ホールド時間: SCLK キャプチャエッジから SDI での(前の)データ有効まで                           |          | 7.5                    |       |      | ns               |

| <b>ソース同期シリアル インターフェイス (外部クロック)</b> |                                                                     |          |                        |       |      |                  |

| $f_{\text{CLK}}$                   | シリアル クロック周波数                                                        |          |                        | 66.67 | MHz  |                  |

| $t_{\text{CLK}}$                   | シリアル クロック期間                                                         |          | $1/f_{\text{CLK}}$     |       |      |                  |

| $t_{\text{PH\_CK}}$                | SCLK High 時間                                                        |          | 0.45                   | 0.55  |      | $t_{\text{CLK}}$ |

| $t_{\text{PL\_CK}}$                | SCLK Low 時間                                                         |          | 0.45                   | 0.55  |      | $t_{\text{CLK}}$ |

## 5.7 スイッチング特性

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、VREF = 4.096V (内部)、および最大スループット (特に記述のない限り)

|                                    |                                                                                           | 最小値      | 標準値 | 最大値  | 単位                  |

|------------------------------------|-------------------------------------------------------------------------------------------|----------|-----|------|---------------------|

| <b>非同期リセット</b>                     |                                                                                           |          |     |      |                     |

| $t_{\text{conv}}$                  | 変換時間                                                                                      | ADS8681W |     | 665  | ns                  |

|                                    | 変換時間                                                                                      | ADS8685W |     | 1000 |                     |

|                                    | 変換時間                                                                                      | ADS8689W |     | 5000 |                     |

| $t_{\text{D\_RST\_POR}}$           | POR リセットの遅延時間: RST 立ち上がりから RVS 立ち上がりまで                                                    |          | 20  |      | ms                  |

| $t_{\text{D\_RST\_APP}}$           | アプリケーションリセットの遅延時間: $\overline{\text{RST}}$ 立ち上がりから CONVST/ $\overline{\text{CS}}$ 立ち上がりまで |          | 1   |      | $\mu\text{s}$       |

| $t_{\text{NAP\_WKUP}}$             | ウェークアップ時間: NAP モード                                                                        |          | 20  |      | $\mu\text{s}$       |

| $t_{\text{PWRUP}}$                 | パワーアップ時間: PD モード                                                                          |          | 20  |      | ms                  |

| <b>SPI 互換シリアル インターフェイス</b>         |                                                                                           |          |     |      |                     |

| $t_{\text{HT\_CKCS}}$              | 遅延時間: 最後の SCLK キャプチャエッジから CONVST/ $\overline{\text{CS}}$ 立ち上がりまで                          | 7.5      |     |      | ns                  |

| $t_{\text{DEN\_CSDO}}$             | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち下がりエッジからデータイネーブルまで                                 |          | 9.5 |      | ns                  |

| $t_{\text{DZ\_CSDO}}$              | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち上がりから SDO-x のトライステートへの移行まで                         |          | 10  |      | ns                  |

| $t_{\text{D\_CKDO}}$               | 遅延時間: SCLK 起動エッジから SDO-x での(次の)データ有効まで                                                    |          | 12  |      | ns                  |

| $t_{\text{D\_CSRVS}}$              | 遅延時間: CONVST/CS 立ち下がりエッジから RVS 立ち下がりまで                                                    |          | 14  |      | ns                  |

| <b>ソース同期シリアル インターフェイス (外部クロック)</b> |                                                                                           |          |     |      |                     |

|                                    | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち下がりエッジからデータイネーブルまで                                 |          | 9.5 |      | ns                  |

|                                    | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち上がりから SDO-x のトライステートへの移行まで                         |          | 10  |      | ns                  |

|                                    | 遅延時間: SCLK 立ち上がりエッジから RVS 立ち上がりまで                                                         |          | 14  |      | ns                  |

|                                    | 遅延時間: SCLK 立ち下がりエッジから RVS 立ち下がりまで                                                         |          | 14  |      | ns                  |

|                                    | 遅延時間: RVS 立ち上がりから SDO-x での(次の)データ有効まで                                                     |          | 2.5 |      | ns                  |

|                                    | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち上がりエッジから RVS で内部デバイスの状態が表示されるまで                    |          | 15  |      | ns                  |

| <b>ソース同期シリアル インターフェイス (内部クロック)</b> |                                                                                           |          |     |      |                     |

| $t_{\text{DEN\_CSDO}}$             | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち下がりエッジからデータイネーブルまで                                 |          | 9.5 |      | ns                  |

| $t_{\text{DZ\_CSDO}}$              | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち上がりから SDO-x のトライステートへの移行まで                         |          | 10  |      | ns                  |

| $t_{\text{DEN\_CSRVS}}$            | 遅延時間: CONVST/ $\overline{\text{CS}}$ 立ち下がりエッジから RVS の最初の立ち上がりエッジまで                        |          | 50  |      | ns                  |

| $t_{\text{D\_RVSDO}}$              | 遅延時間: RVS 立ち上がりから SDO-x での(次の)データ有効まで                                                     |          | 2.5 |      | ns                  |

| $t_{\text{INTCLK}}$                | 期間: 内部クロック                                                                                | 15       |     |      | ns                  |

| $t_{\text{CYC\_RVS}}$              | 期間: RVS 信号                                                                                | 15       |     |      | ns                  |

| $t_{\text{WH\_RVS}}$               | RVS High 時間                                                                               | 0.4      | 0.6 |      | $t_{\text{INTCLK}}$ |

| $t_{\text{WL\_RVS}}$               | RVS Low 時間                                                                                | 0.4      | 0.6 |      | $t_{\text{INTCLK}}$ |

## 5.7 スイッチング特性 (続き)

すべての最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、標準仕様は  $T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3.3V、VREF = 4.096V (内部)、および最大スループット (特に記述のない限り)

|                |                                                   | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|---------------------------------------------------|-----|-----|-----|----|

| $t_{D\_CSRVS}$ | 遅延時間: CONVST/CS 立ち上がりエッジから RVS で内部デバイスの状態が表示されるまで |     |     | 15  | ns |

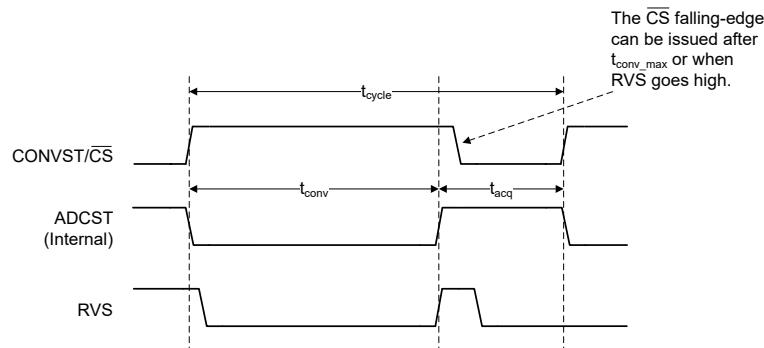

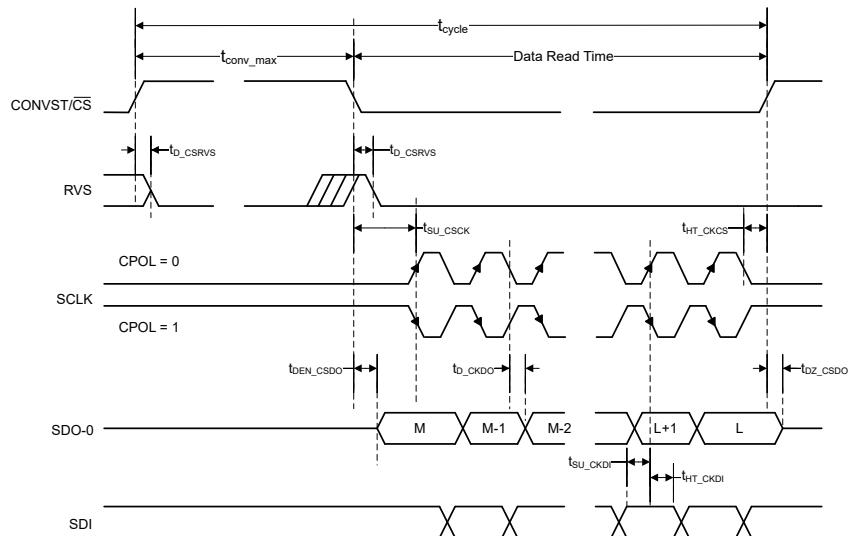

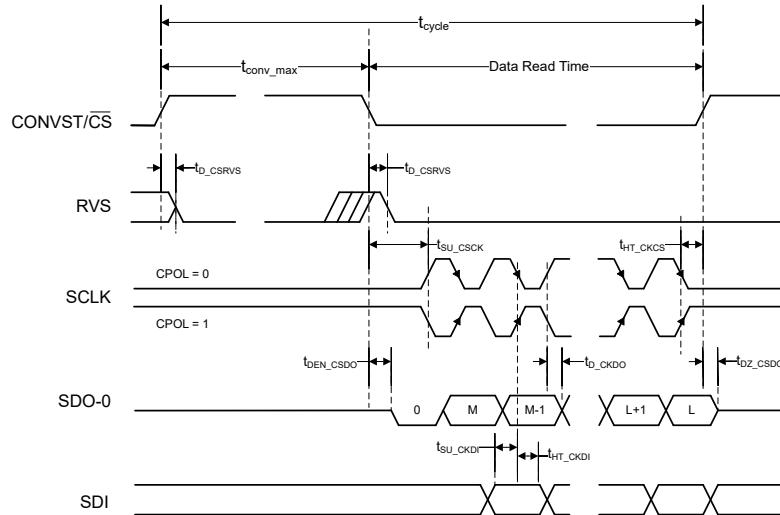

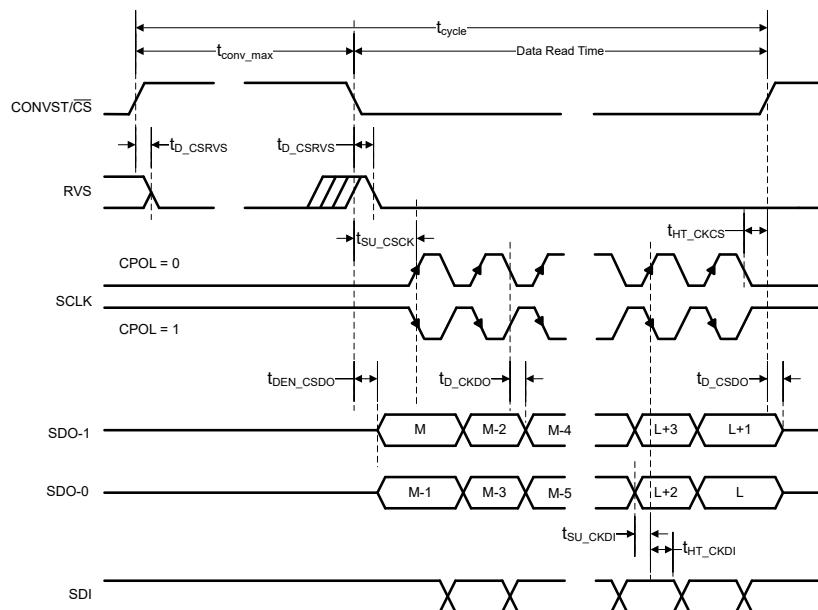

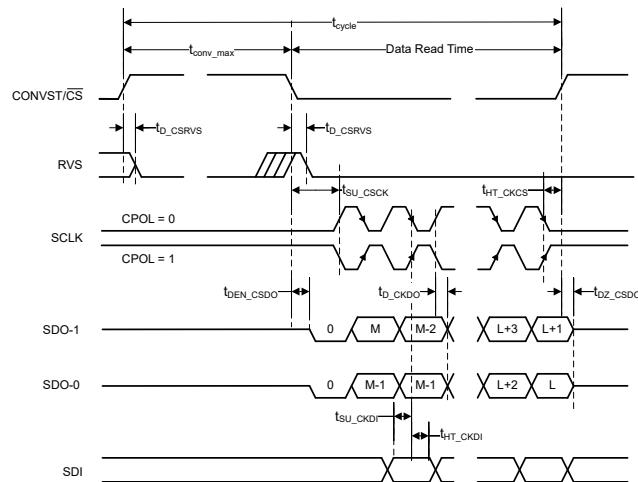

## 5.8 タイミング図

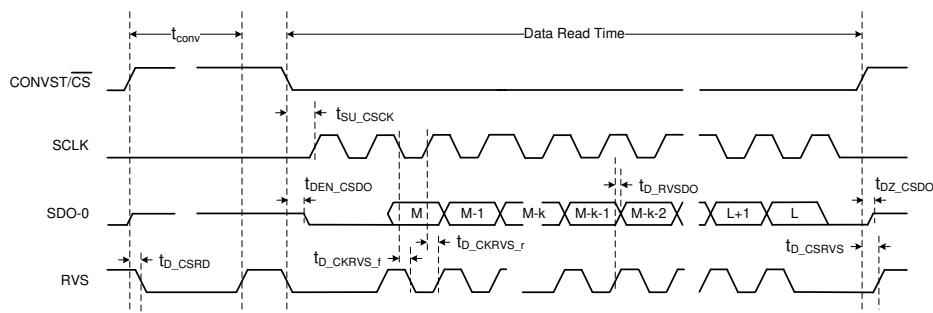

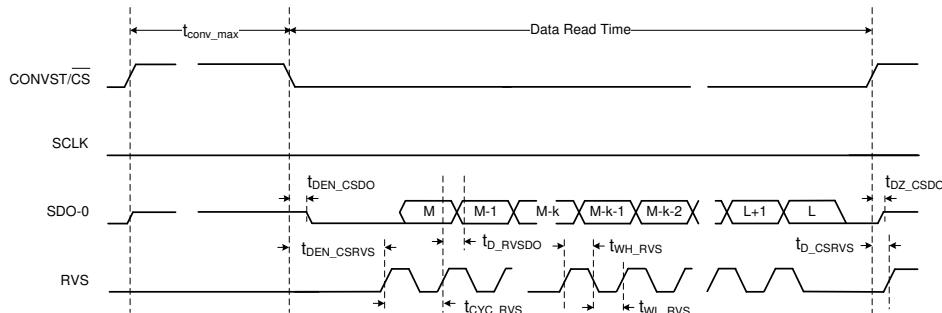

図 5-1. 変換サイクルのタイミング図

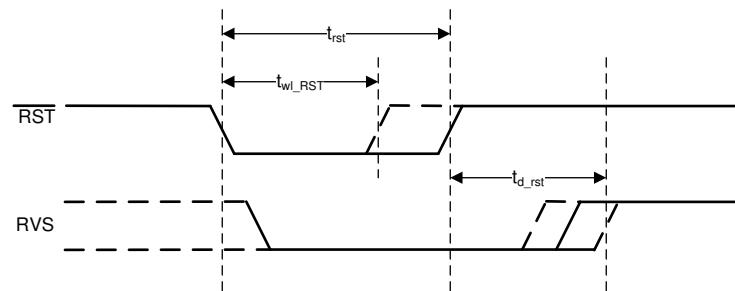

図 5-2. 非同期リセットのタイミング図

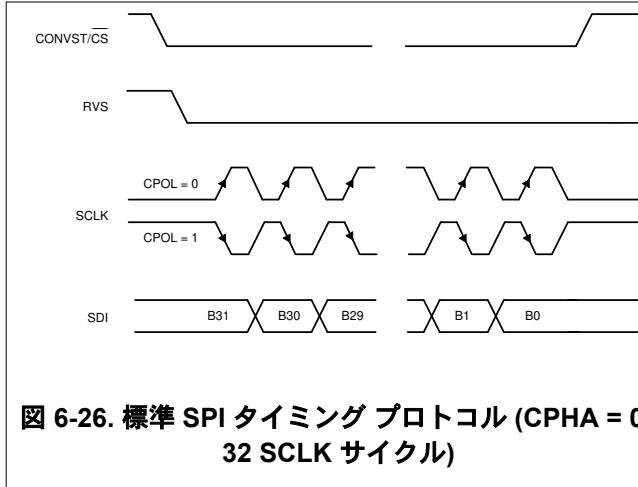

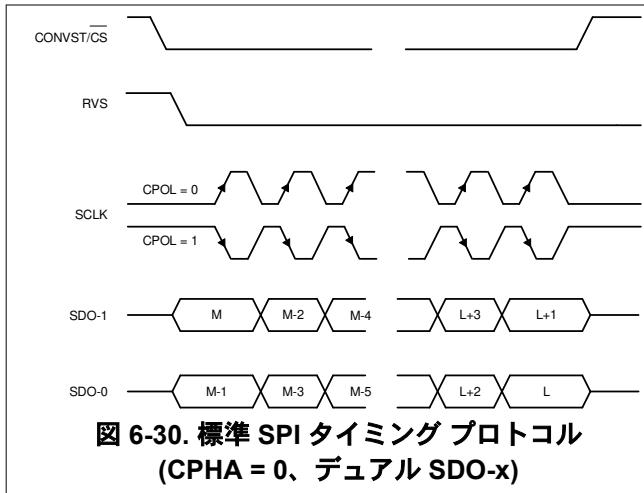

図 5-3. CPHA = 0 の標準 SPI インターフェイスのタイミング図

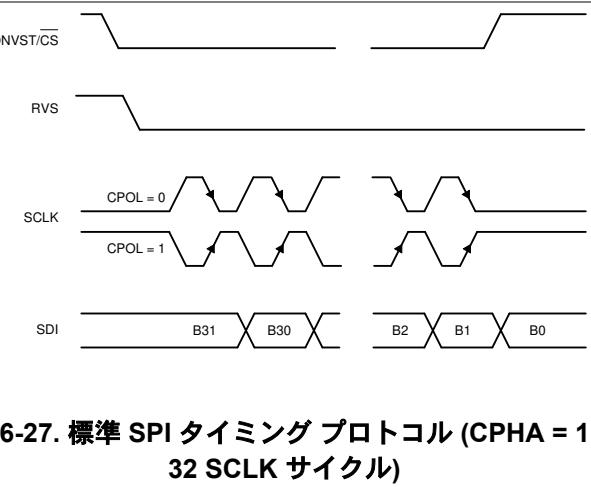

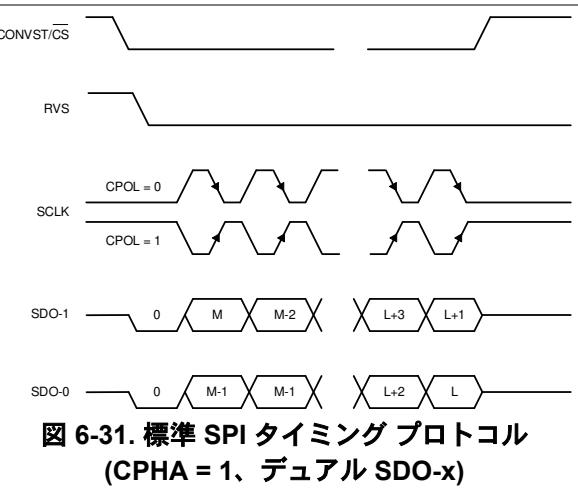

図 5-4. CPHA = 1 の標準 SPI インターフェイスのタイミング図

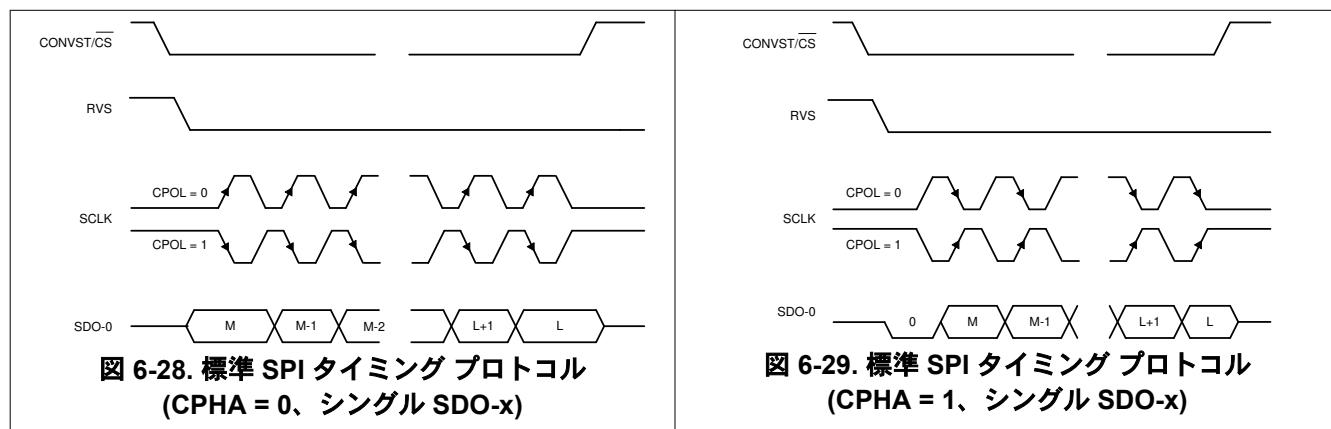

図 5-5. デュアル SDO-x および CPHA = 0 の multiSPI インターフェイスのタイミング図

図 5-6. デュアル SDO-x および CPHA = 1 の multiSPI インターフェイスのタイミング図

図 5-7. multiSPI ソース同期外部クロック シリアルインターフェイスのタイミング図

図 5-8. multiSPI ソース同期内部クロック シリアルインターフェイスのタイミング図

## 5.9 代表的特性

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

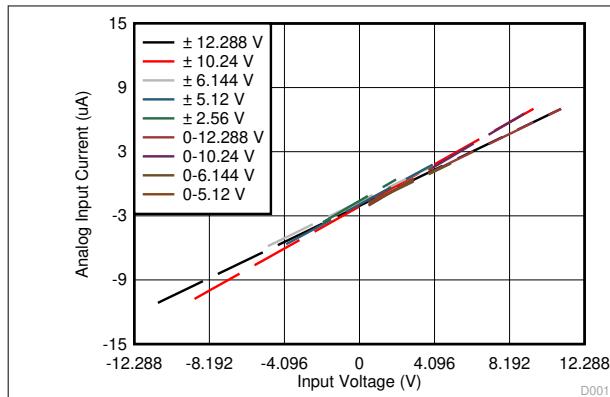

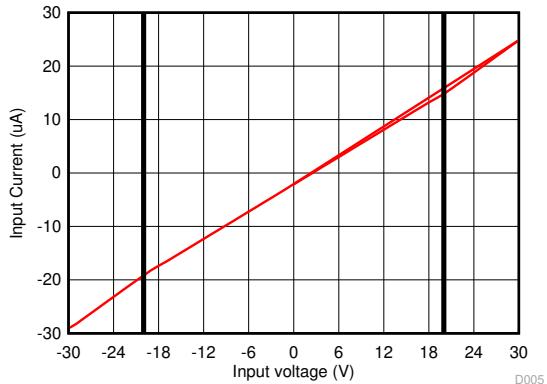

図 5-9.すべての入力範囲にわたる入力 I-V 特性

範囲 =  $\pm 12.288\text{V}$

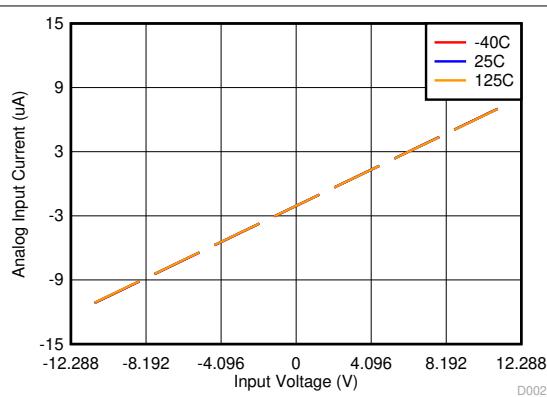

図 5-10.すべての温度にわたる入力 I-V 特性

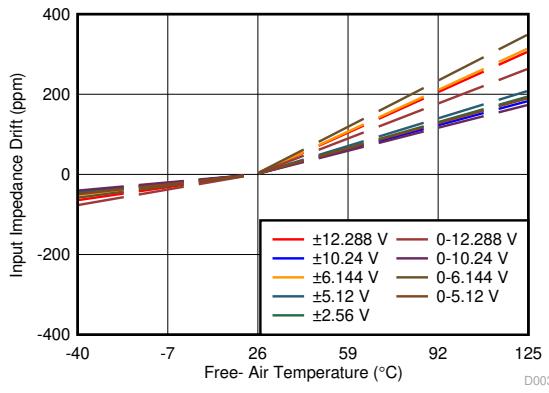

図 5-11.入力インピーダンス ドリフトと温度との関係

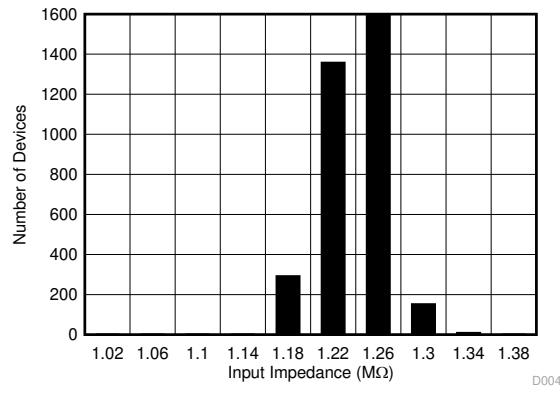

図 5-12.入力インピーダンスの標準的な分布

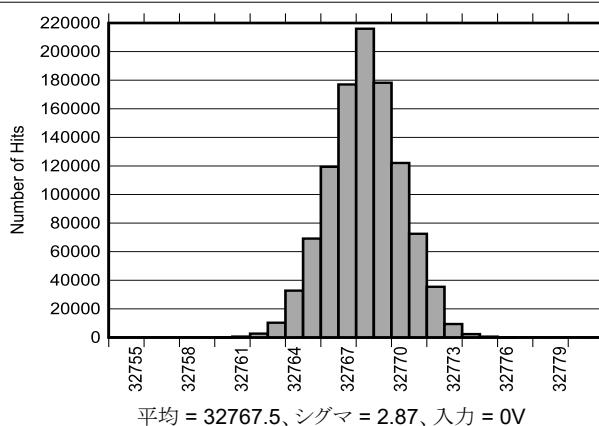

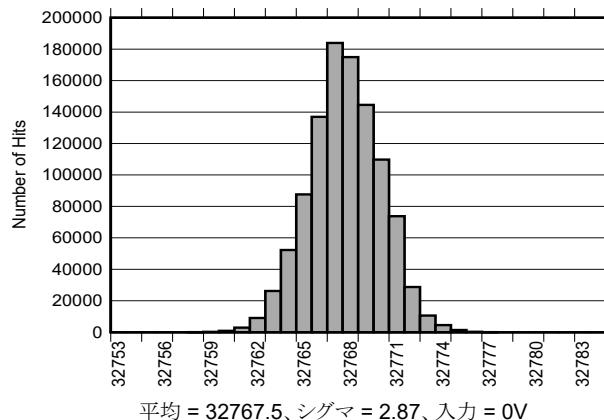

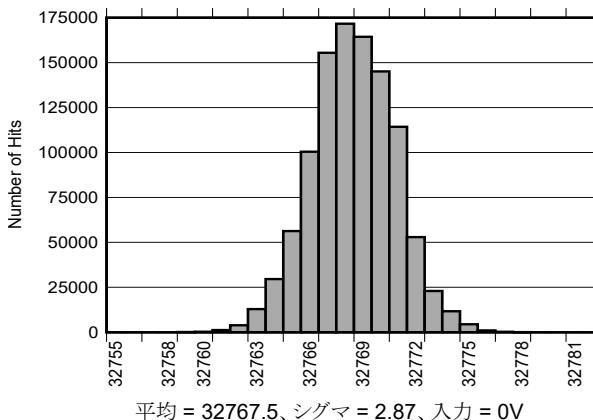

平均 = 32767.5、シグマ = 2.87、入力 = 0V

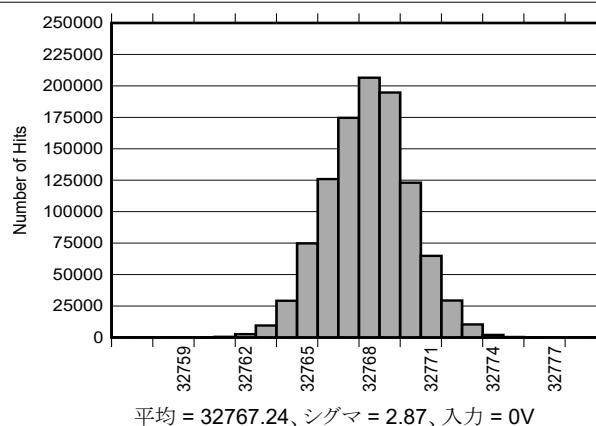

平均 = 32767.24、シグマ = 2.87、入力 = 0V

## 5.9 代表的特性 (続き)

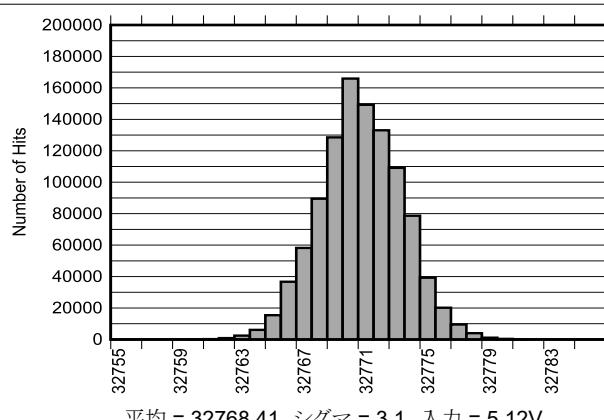

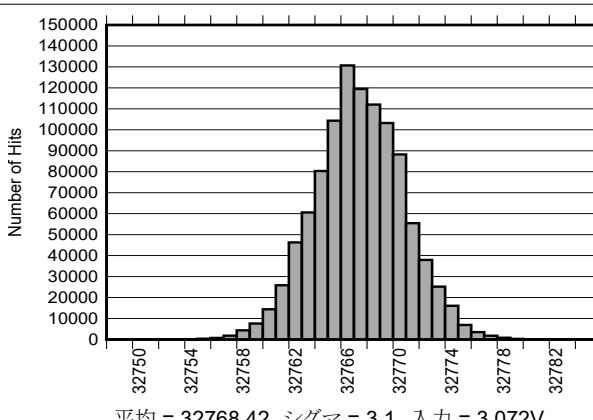

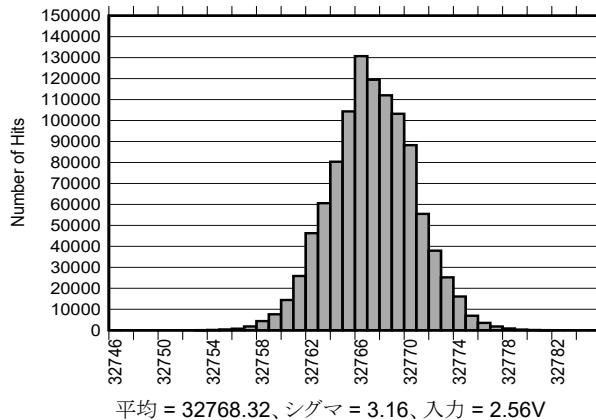

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

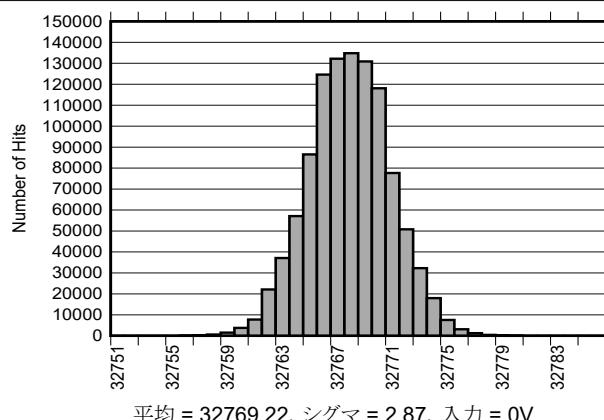

図 5-15. ミッドスケール入力の DC ヒストグラム ( $\pm 6.144\text{V}$ )

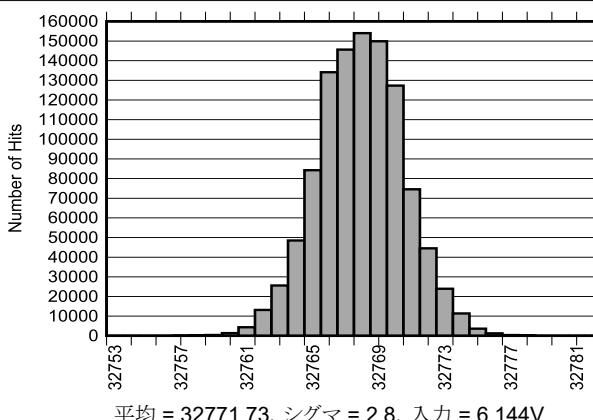

図 5-16. ミッドスケール入力の DC ヒストグラム ( $\pm 5.12\text{V}$ )

図 5-17. ミッドスケール入力の DC ヒストグラム ( $\pm 2.56\text{V}$ )

図 5-18. ミッドスケール入力の DC ヒストグラム (0V ~ 12.288V)

図 5-19. ミッドスケール入力の DC ヒストグラム (0V ~ 10.24V)

図 5-20. ミッドスケール入力の DC ヒストグラム (0V ~ 6.144V)

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

図 5-21. ミッドスケール入力の DC ヒストグラム (0V ~ 5.12V)

図 5-22. すべてのコードの標準 DNL

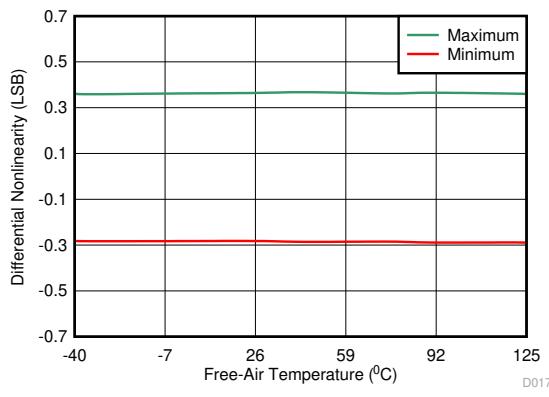

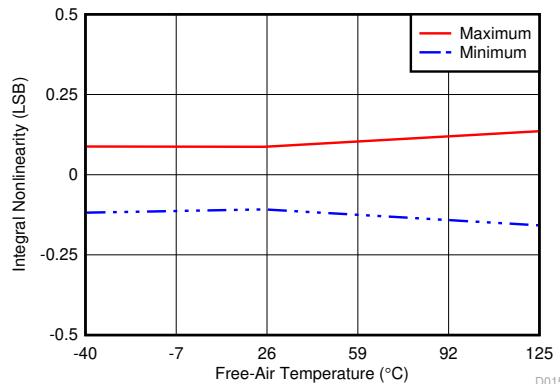

図 5-23. DNL と温度との関係

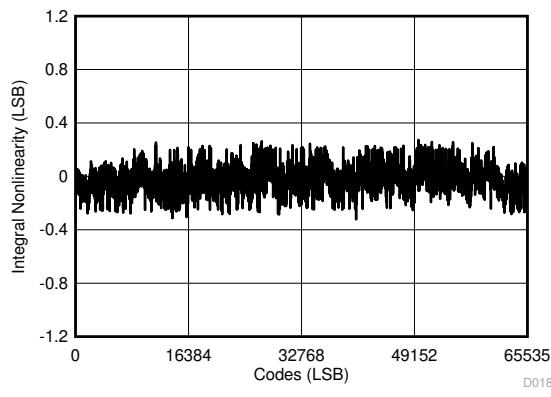

図 5-24. すべてのコードの標準 INL (すべてのバイポーラ レンジ)

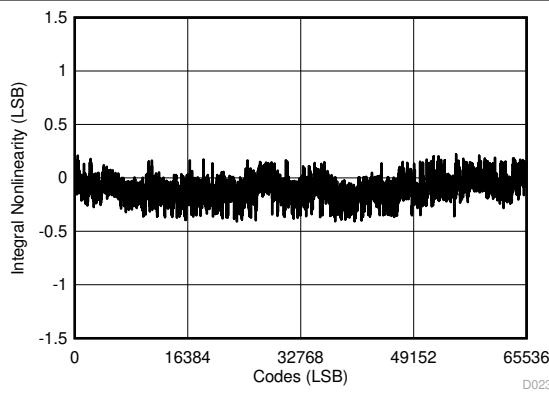

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

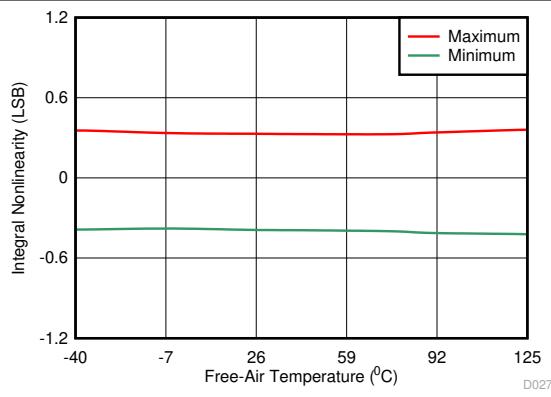

図 5-27. INL と温度との関係 (すべてのユニポーラ レンジ)

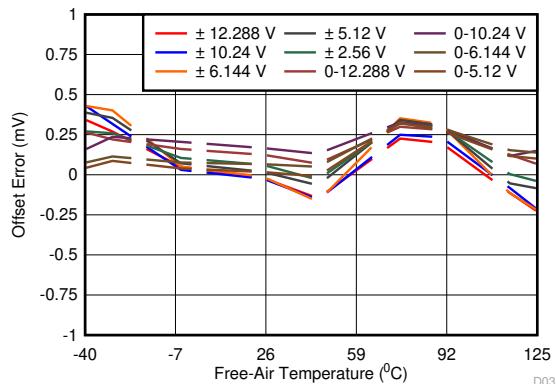

図 5-28. すべての入力範囲にわたるオフセット誤差と温度との関係

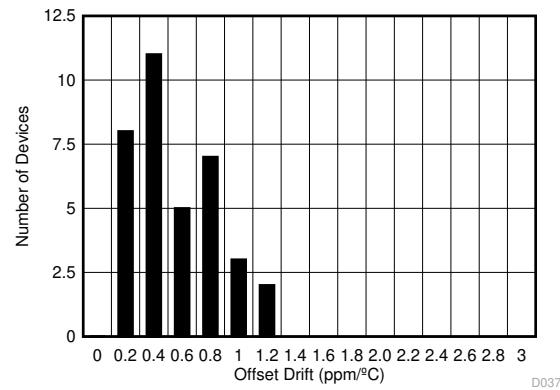

図 5-29. オフセット ドリフトの標準的なヒストグラム

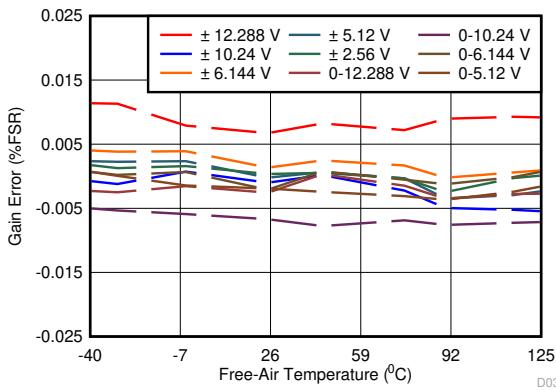

図 5-30. すべての入力範囲にわたるゲイン誤差と温度との関係

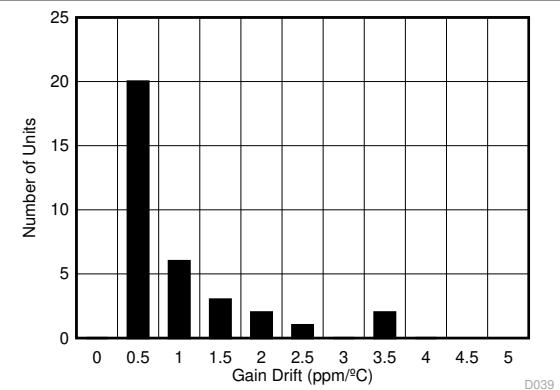

図 5-31. ゲイン誤差ドリフトの標準的なヒストグラム

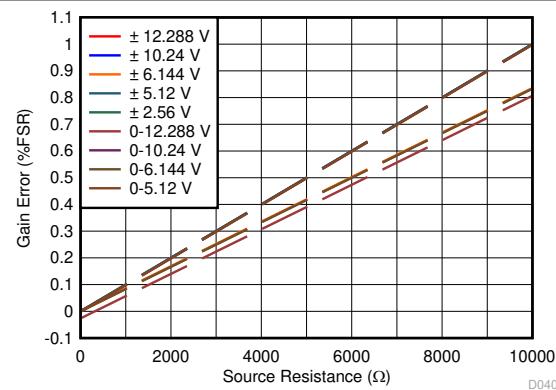

図 5-32. ゲイン誤差と外部抵抗との関係 ( $R_{\text{EXT}}$ )

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3\text{V}$ 、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

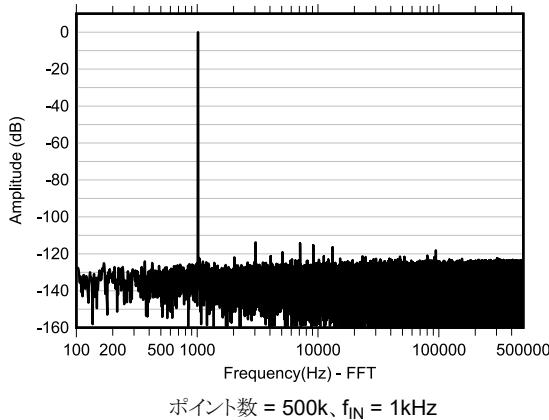

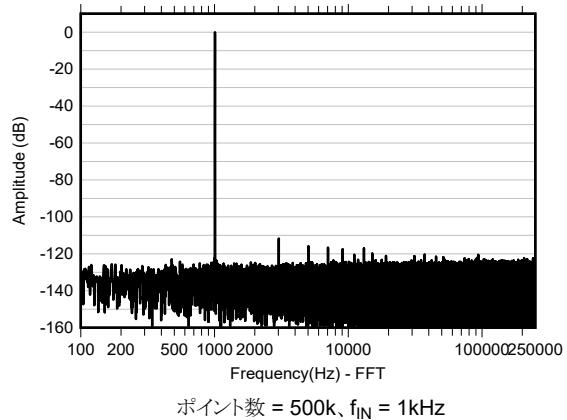

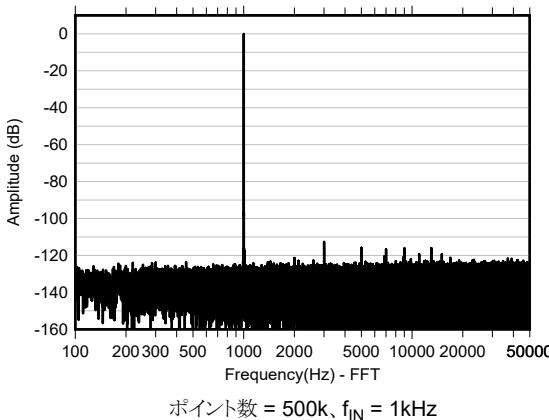

図 5-33. ADS8681W の標準的な FFT プロット (すべての範囲)

図 5-34. ADS8685W の標準的な FFT プロット (すべての範囲)

図 5-35. ADS8689W の標準的な FFT プロット (すべての範囲)

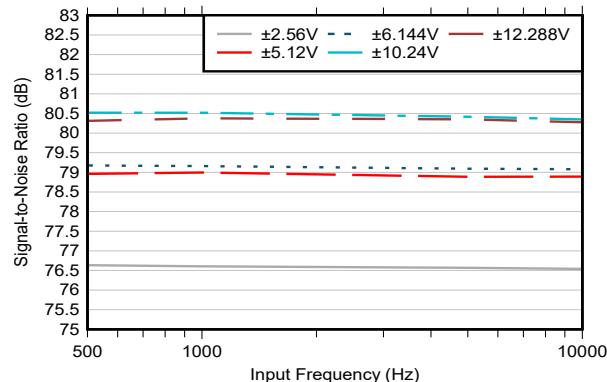

図 5-36. SNR と入力周波数との関係

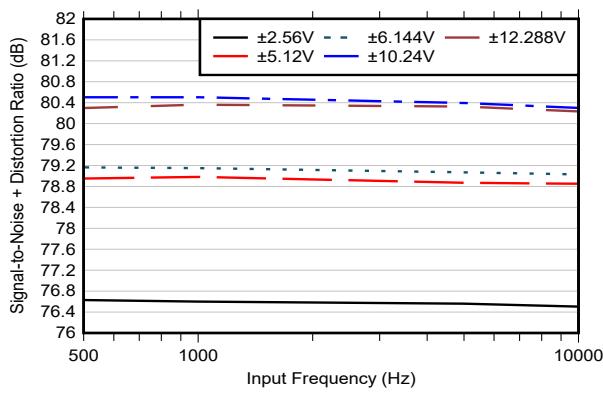

図 5-37. SINAD と入力周波数との関係

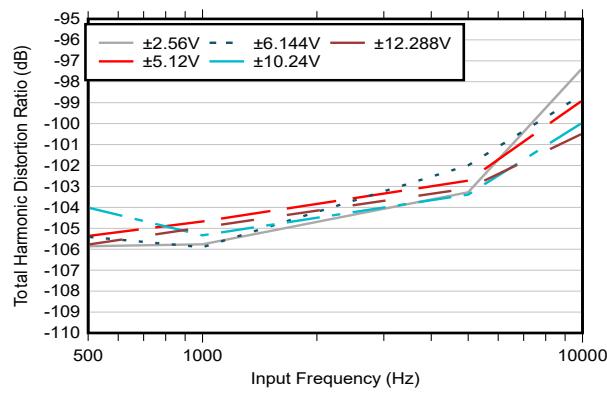

図 5-38. THD と入力周波数との関係

## 5.9 代表的特性 (続き)

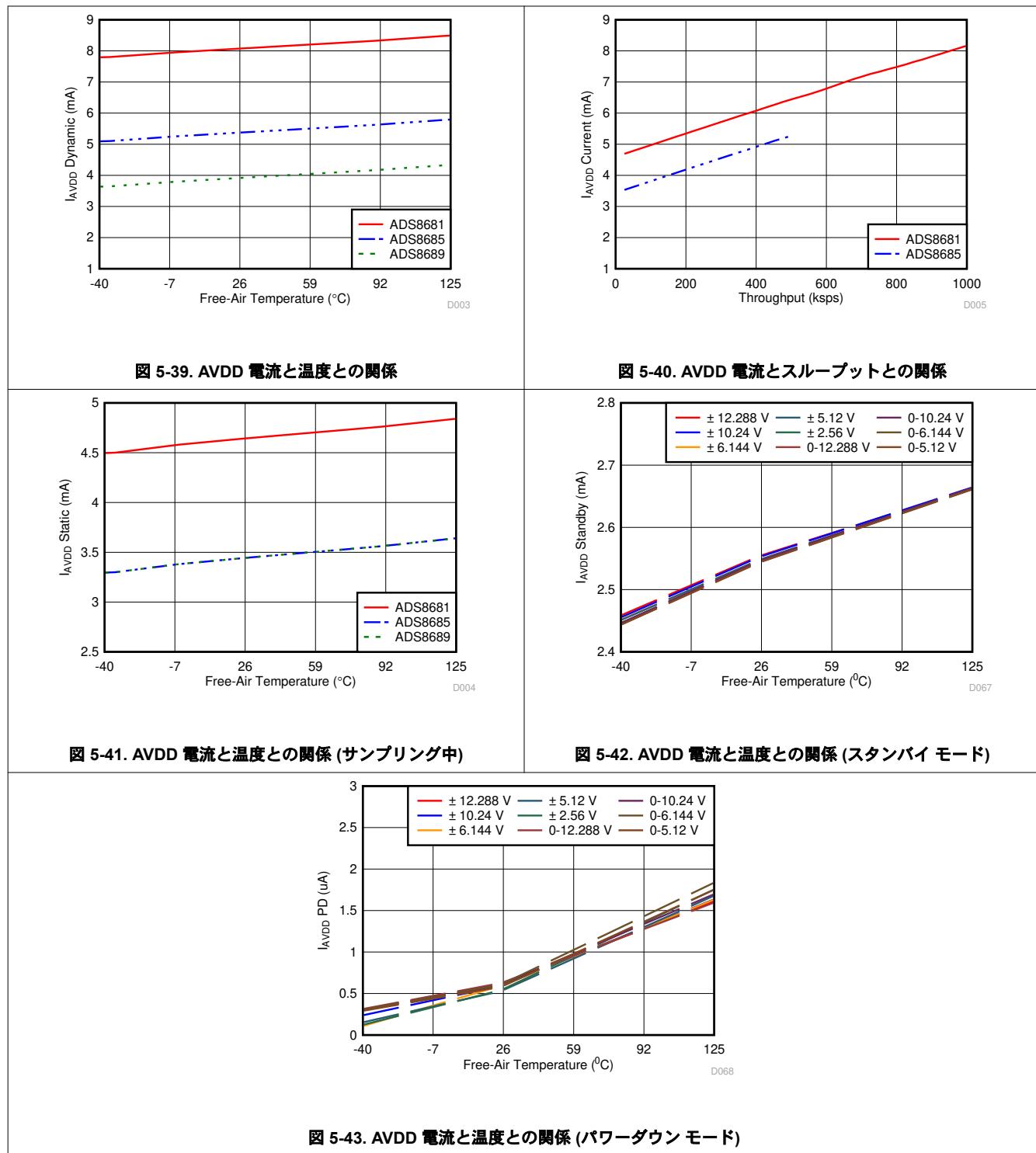

$T_A = 25^\circ\text{C}$ 、AVDD = 5V、DVDD = 3V、 $V_{\text{REF}} = 4.096\text{V}$  (内部)、および最大スループット (特に記述のない限り)

## 6 詳細説明

### 6.1 概要

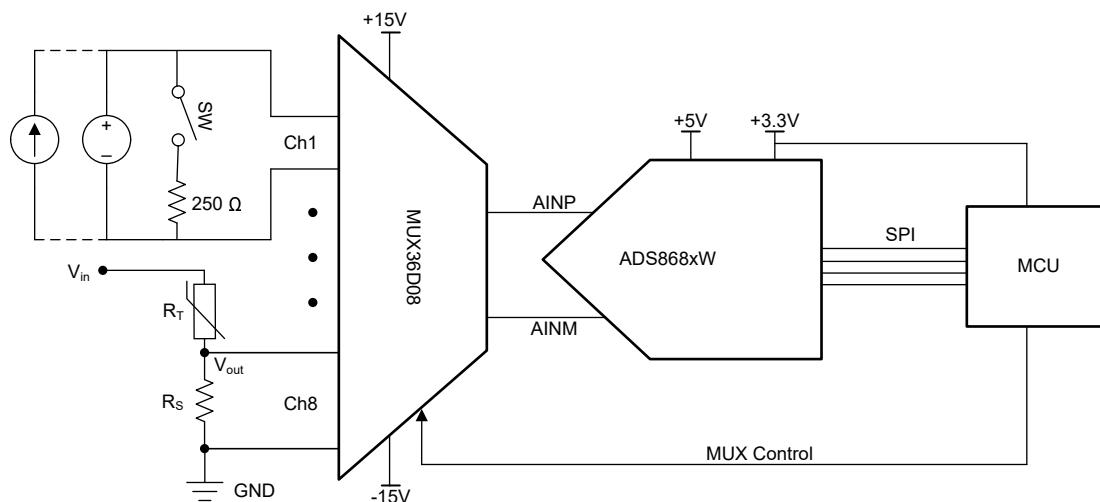

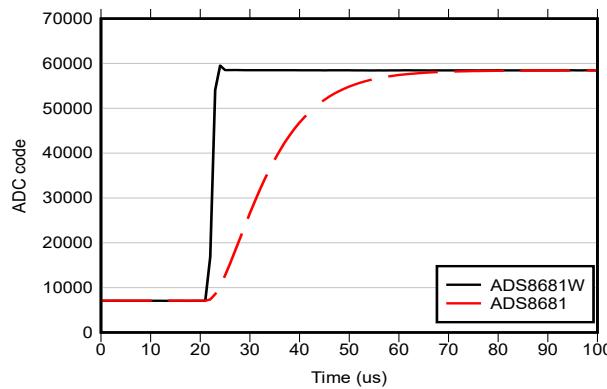

ADS868xW は、高速かつ高性能で使いやすい統合型データ アクイジション システム デバイスのファミリです。これらのシングル チャネル デバイスは、最大  $\pm 12.288V$  の真のバイポーラ差動およびシングルエンド入力電圧振幅をサポートし、単一の 5V アナログ電源で動作します。ADS868xW は拡張 SPI インターフェイス (multiSPI) を搭載しており、低速のホストコントローラでもサンプリング レートを最大化できます。

ADS868xW は、高精度の逐次比較型 (SAR) A/D コンバータ (ADC)、およびシグナル コンディショニング用に電力最適化されたアナログ フロントエンド (AFE) 回路で構成されています。ADS868xW は以下を備えています。

- サンプリング レートに依存しない高抵抗性入力インピーダンス ( $\geq 1M\Omega$ )

- 9つのソフトウェア プログラマブル ユニポーラおよびバイポーラ入力範囲をサポートする差動およびシングルエンド入力構成を備えたプログラマブル ゲイン アンプ (PGA)

- 2次ローパス アンチエイリアス フィルタ

- 高精度のために SAR ADC 入力の迅速なセトリングを実現する ADC ドライバ アンプ

- 最大  $\pm 20V$  の入力過電圧保護回路

このデバイスは、温度ドリフトが小さい 4.096V の内部リファレンスを搭載し、高速セトリング バッファ、およびデイジーチェーン (デイジー) とアラーム機能を搭載した multiSPI シリアル インターフェイスを特徴としています。

統合型の高精度 AFE 回路は、入力インピーダンスが高く、5V 単一電源で動作する高精度 ADC を内蔵しています。この AFE 回路は、外部高電圧バイポーラ電源や複雑なドライバ回路を必要とせずに、簡素化された最終ソリューションを実現します。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 アナログ入力構造

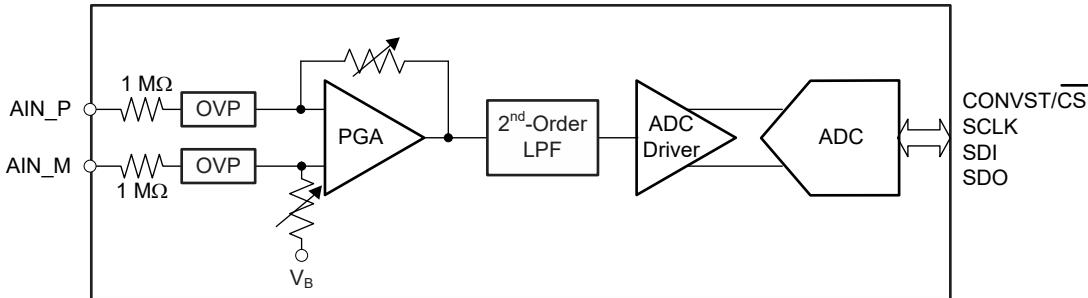

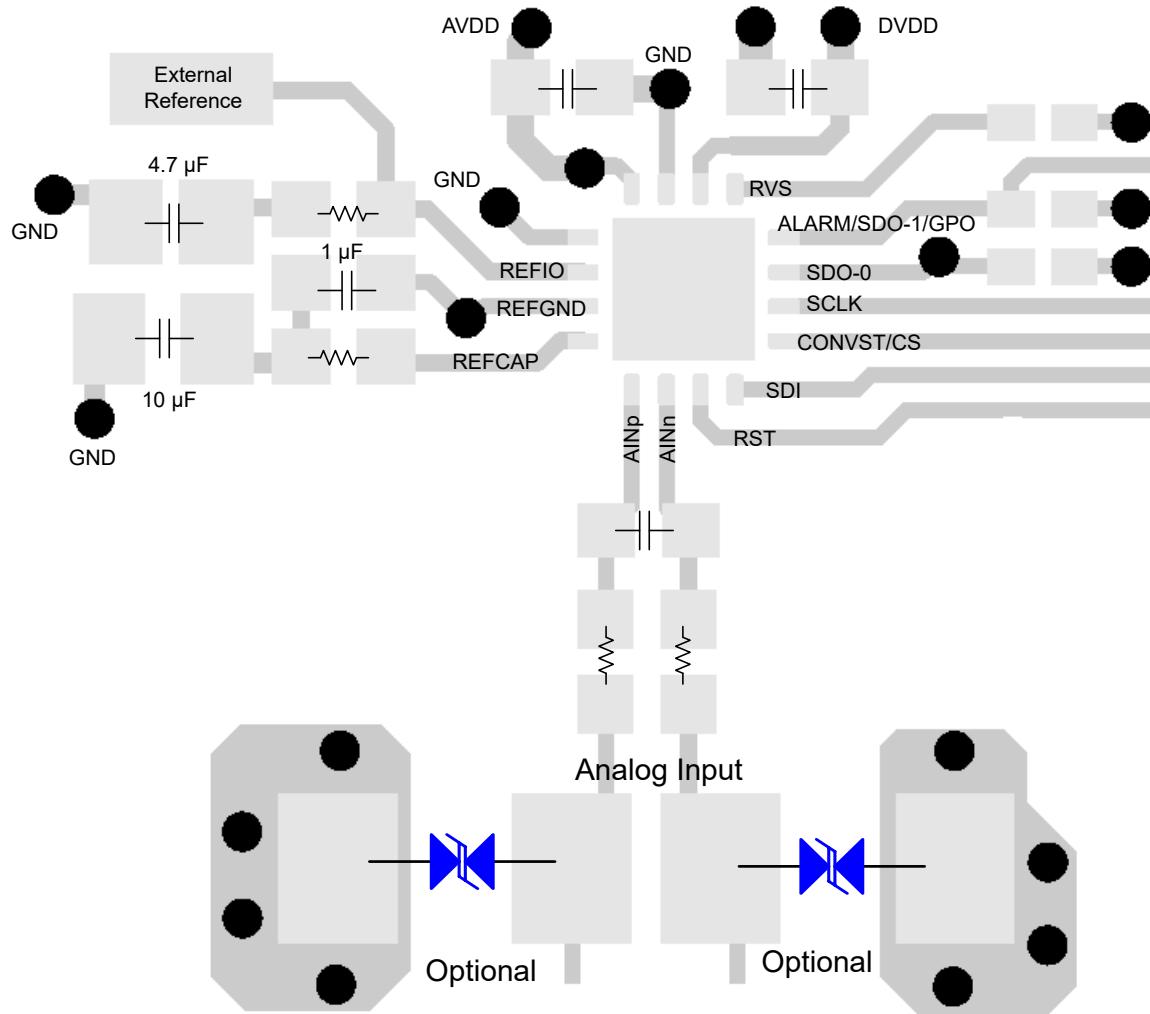

このデバイスは差動入力構造を採用しています。図 6-1 に、入力過電圧保護回路、PGA、ローパスフィルタ (LPF)、高速 ADC ドライバを含む、AFE 回路の概略回路図を示します。

図 6-1. アナログ フロント エンド回路の概略回路図

ADS868xW は、プログラム レジスタ構成に基づいて、複数のユニポーラまたはバイポーラ、シングルエンドおよび差動入力電圧範囲をサポートしています。RANGE\_SEL\_REG レジスタで説明されているように、入力電圧範囲をバイポーラまたはユニポーラに設定します。バイポーラ レンジは、 $\pm 3V \times V_{REF}$ 、 $\pm 2.5V \times V_{REF}$ 、 $\pm 1.5V \times V_{REF}$ 、 $\pm 1.25V \times V_{REF}$ 、および  $\pm 0.625V \times V_{REF}$  です。ユニポーラ レンジは、 $0V \sim 3V \times V_{REF}$ 、 $0V \sim 2.5V \times V_{REF}$ 、 $0V \sim 1.5 \times V_{REF}$ 、および  $0V \sim 1.25 \times V_{REF}$  です。内部リファレンス電圧または外部リファレンス電圧を  $4.096V$  に設定すると、デバイスの入力範囲をバイポーラ レンジまたはユニポーラ レンジに構成できます。構成されるバイポーラ レンジは、 $\pm 12.288V$ 、 $\pm 10.24V$ 、 $\pm 6.144V$ 、 $\pm 5.12V$ 、および  $\pm 2.56V$  です。構成されるユニポーラ レンジは、 $0V \sim 12.288V$ 、 $0V \sim 10.24V$ 、 $0V \sim 6.144V$ 、および  $0V \sim 5.12V$  です。

このデバイスは、AIN\_P ピンと AIN\_M ピンの電圧差をサンプリングします。最適な性能を達成するために、各入力バスに沿った入力電流とインピーダンスが一致していることを確認します。2 つのシングルエンド信号を AIN\_P と AIN\_M に、信号源から ADC 入力ピンまで、可能な限り対称的に配線します。

デバイスに対するアナログ入力ピン (AIN\_P) または (AIN\_M) がフローティングのままになっている場合、ADC の出力は内部バイアス電圧に対応します。デバイスがフローティング入力ピンで動作している場合、ADC の出力は無効と見なされます。この条件によってデバイスが損傷することではなく、ピンに有効な入力電圧が印加されると、完全に機能します。

### 6.3.2 アナログ入力インピーダンス

このデバイスは、各アナログ入力で  $1M\Omega$  以上の抵抗性入力インピーダンスを実現します。入力インピーダンスは、ADC サンプリング周波数や入力信号の周波数に依存しません。このような高インピーダンス入力の主な利点は、出力インピーダンスの低いアンプを駆動する必要がなく、ADC 入力を簡単に駆動できることです。この ADC は高電圧のフロント エンド ドライバを必要としないため、システムではバイポーラの高電圧電源は必要ありません。ほとんどのアプリケーションでは、信号源またはセンサ出力が ADC 入力に直接接続されるため、シグナル チェーンの設計を大幅に簡素化できます。

システムの DC 精度を維持するには、AIN\_P 入力ピンの外部ソース インピーダンスを AIN\_M ピンの等価抵抗と一致させます。一致させることで、外部抵抗に起因する追加のオフセット誤差を打ち消すのに役立ちます。

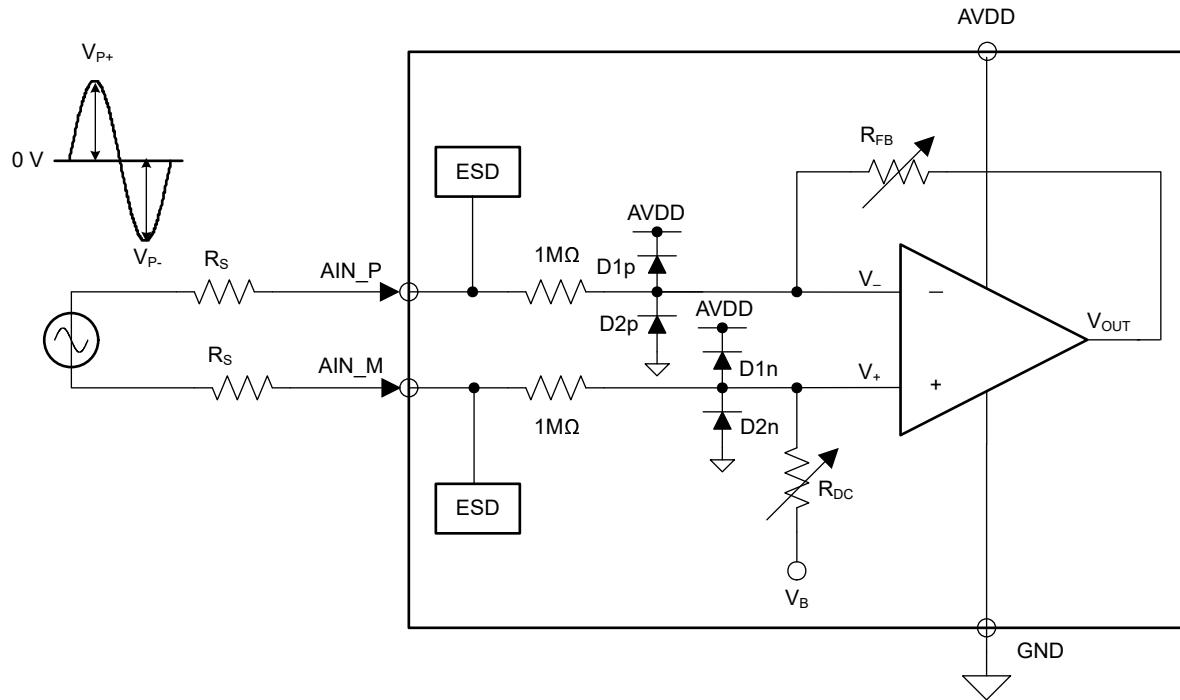

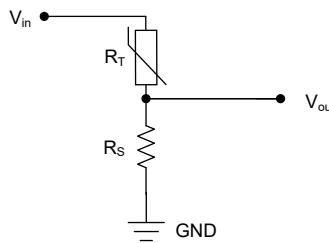

### 6.3.3 入力保護回路

このデバイスには、各アナログ入力に過電圧保護 (OVP) 回路が内蔵されています。最終アプリケーションでは、サーボ、静電放電 (ESD)、電気的高速過渡 (EFT) の状態から保護するために外部保護デバイスを使用してください。図 6-2 に、内部 OVP 回路の概念ブロック図を示します。

図 6-2. 入力過電圧保護回路の回路図

図 6-2 に示されているように、入力抵抗と PGA ゲイン設定抵抗  $R_{FB}$  および  $R_{DC}$  の組み合わせにより、入力ピンに流れる電流が制限されます。適切な入力範囲としては、 $1\text{M}\Omega$  (または  $1.2\text{M}\Omega$ ) の入力抵抗を使用します。逆並列ダイオード D1 および D2 の組み合わせを追加して、内部回路を保護し、過電圧保護制限を設定します。

表 6-1 に、電源オン時のデバイスのさまざまな動作条件を示します。デバイスの電源が正常にパワーアップされていること ( $\text{AVDD} = 5\text{V}$ )、または  $30\text{k}\Omega$  未満の低インピーダンスであることを確認します。適切に設定した場合、内部の過電圧保護回路はアナログ入力ピンで最大  $\pm 20\text{V}$  の耐性を持ちます。

表 6-1.  $\text{AVDD} = 5\text{V}$  時の入力過電圧保護制限

| 入力条件 <sup>(1)</sup><br>( $ V_{OVP}  = \pm 20\text{V}$ ) |                   | テスト条件    | ADC 出力 | 備考                                                            |

|---------------------------------------------------------|-------------------|----------|--------|---------------------------------------------------------------|

| 条件                                                      | RANGE             |          |        |                                                               |

| $ V_{IN}  <  V_{RANGE} $                                | 動作範囲内             | すべての入力範囲 | 有効     | デバイスは、データシートの仕様に従って機能します。                                     |

| $ V_{RANGE}  <  V_{IN}  <  V_{OVP} $                    | 動作範囲を超えているが過電圧範囲内 | すべての入力範囲 | 飽和状態   | ADC 出力は飽和していますが、デバイスは内部的に保護されています（これは長時間にわたって使用することは推奨されません）。 |

| $ V_{IN}  >  V_{OVP} $                                  | 過電圧範囲外            | すべての入力範囲 | 飽和状態   | この使用状態により、デバイスに回復できない損傷が発生する可能性があります。                         |

(1)  $\text{GND} = 0\text{V}$ ,  $\text{AIN\_M} = 0\text{V}$ ,  $|V_{RANGE}|$  は、選択されたすべての入力範囲の最大入力電圧です。 $|V_{OVP}|$  は、内部 OVP 回路のブレークダウン電圧です。 $R_S$  が約  $0\Omega$  であると仮定します。

表 6-1 に示されている結果は、アナログ入力ピンが非常に低いインピーダンスのソース ( $R_S$  が約  $0\Omega$ ) で駆動されていると仮定しています。しかし、入力を駆動するソースのインピーダンスがより高い場合、保護ダイオードを流れる電流がさらに減少し、OVP 電圧範囲が拡大します。ソース インピーダンスが高いほど、ゲイン誤差が発生し、システム全体のノイズ性能に影響します。

図 6-3 に、デバイスのパワーアップ時の内部過電圧保護回路の電圧と電流応答の関係を示します。この I-V (電流から電圧へ) 応答によると、デバイスの入力ピンに流れる電流は入力インピーダンスによって制限されます。入力インピーダンス

は  $1\text{M}\Omega$  (適切な入力範囲では  $1.2\text{M}\Omega$ ) です。しかし、 $\pm 20\text{V}$  を超える電圧の場合、内部のノード電圧は内部トランジスタのブレークダウン電圧を上回ります。そのため、過電圧保護の限界は入力ピンで設定されます。

**図 6-3. 入力 OVP 回路の I-V 曲線 (AVDD = 5V)**

同じ過電圧保護回路によって、デバイスの電源がオンになっていない場合や AVDD がフローティングになっている場合に、デバイスが保護されます。この状態は、ADC の電源が完全にオンになる前に入力信号が印加された場合に発生します。[表 6-2](#) に、この状態の過電圧保護の限界を示します。

**表 6-2. AVDD = フローティング時の入力過電圧保護の限界**

| 入力条件 <sup>(1)</sup><br>( $V_{OVP} = \pm 15\text{V}$ ) |        | テスト条件    | ADC 出力 | 備考                                    |

|-------------------------------------------------------|--------|----------|--------|---------------------------------------|

| 条件                                                    | RANGE  |          |        |                                       |

| $ V_{IN}  <  V_{OVP} $                                | 過電圧範囲内 | すべての入力範囲 | 無効     | このデバイスは機能しませんが、OVP 回路によって内部で保護されています。 |

| $ V_{IN}  >  V_{OVP} $                                | 過電圧範囲外 | すべての入力範囲 | 無効     | この使用状態により、デバイスに回復できない損傷が発生する可能性があります。 |

(1) AVDD = フローティング、GND = 0V、AIN\_M = 0V、 $|V_{RANGE}|$  は、選択されたすべての入力範囲の最大入力電圧です。 $|V_{OVP}|$  は、内部 OVP 回路のブレークダウン電圧です。 $R_S$  が約  $0\Omega$  であると仮定します。

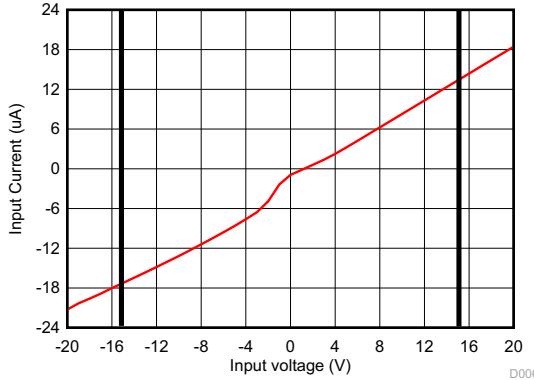

[図 6-4](#) に、デバイスのパワーダウン時の内部過電圧保護回路の I-V 応答を示します。この I-V 応答によると、デバイスの入力ピンに流れる電流は入力インピーダンスによって制限されます。しかし、 $\pm 15\text{V}$  を超える電圧の場合、内部のノード電圧は内部トランジスタのブレークダウン電圧を上回ります。そのため、過電圧保護の限界は入力ピンで設定されます。

図 6-4. 入力 OVP 回路の I-V 曲線 (AVDD = フローティング)

#### 6.3.4 プログラマブル ゲインアンプ(PGA)

このデバイスには、アナログ シグナルコンディショニング回路の一部としてプログラマブル ゲイン アンプ (PGA) が搭載されています。この回路は、元のシングルエンドまたは差動入力信号を、内部 SAR ADC を駆動する信号に変換します。また、PGA は、信号が SAR ADC に供給される前に、入力信号の同相レベルを調整します。このプロセスにより、ADC の入力ダイナミックレンジを最大限に使用できます。入力信号の範囲に応じて、構成レジスタの RANGE\_SEL[3:0] ビットを設定して、PGA ゲインを調整します。『[RANGE\\_SEL\\_REG レジスタ](#)』を参照してください。RANGE\_SEL[3:0] ビットのデフォルトまたはパワーオン状態は 0000 であり、 $\pm 3V \times V_{REF}$  の入力信号範囲に対応します。表 6-3 に、さまざまなアナログ入力電圧範囲に対する RANGE\_SEL[3:0] ビットのさまざまな設定を示します。

PGA は、複数のゲイン構成に正確に一致した抵抗のネットワークを使用します。これらの抵抗間のマッチングは正確に調整され、すべての入力範囲にわたって総合的なゲイン誤差が低く保たれます。

表 6-3. 入力レンジ選択ビット構成

| アナログ入力範囲<br>(AIN_P – AIN_M)    | RANGE_SEL[3:0] |       |       |       |

|--------------------------------|----------------|-------|-------|-------|

|                                | ビット 3          | ビット 2 | ビット 1 | ビット 0 |

| $\pm 3V \times V_{REF}$        | 0              | 0     | 0     | 0     |

| $\pm 2.5V \times V_{REF}$      | 0              | 0     | 0     | 1     |

| $\pm 1.5V \times V_{REF}$      | 0              | 0     | 1     | 0     |

| $\pm 1.25V \times V_{REF}$     | 0              | 0     | 1     | 1     |

| $\pm 0.625V \times V_{REF}$    | 0              | 1     | 0     | 0     |

| $0V \sim 3V \times V_{REF}$    | 1              | 0     | 0     | 0     |

| $0V \sim 2.5V \times V_{REF}$  | 1              | 0     | 0     | 1     |

| $0V \sim 1.5V \times V_{REF}$  | 1              | 0     | 1     | 0     |

| $0V \sim 1.25V \times V_{REF}$ | 1              | 0     | 1     | 1     |

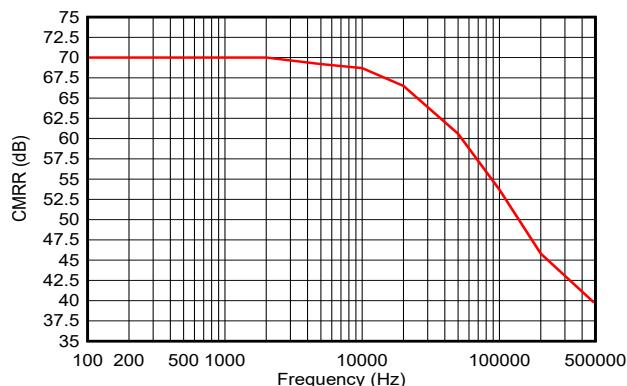

#### 6.3.5 2 次ローパス フィルタ (LPF)

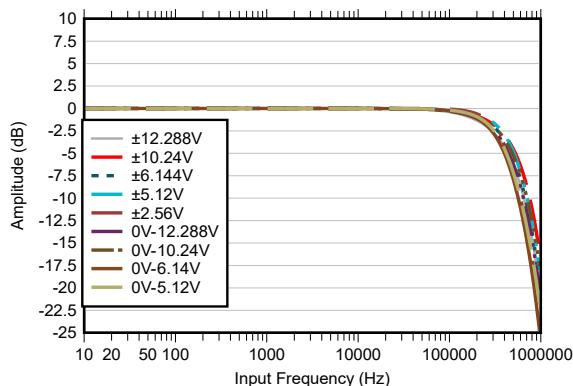

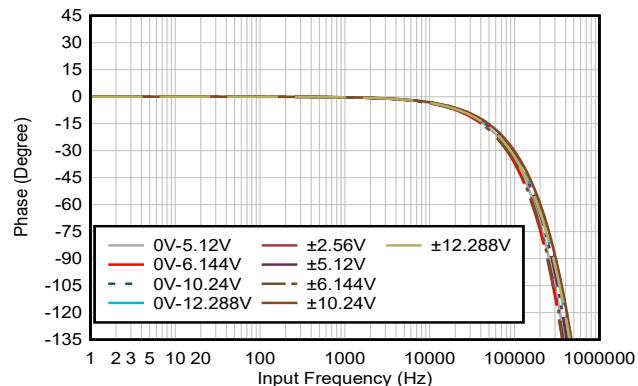

フロントエンド アンプおよび PGA ゲイン抵抗のノイズを低減するために、デバイスの AFE 回路には PGA 出力に 2 次アンチエイリアス LPF が備わっています。図 6-5 および 図 6-6 に、それぞれのアナログ アンチエイリアス フィルタの振幅と位相応答を示します。最大限の性能を得るために、アンチエイリアス フィルタの -3dB カットオフ周波数は、通常 500kHz に設定します。フィルタの性能は、ADC でサポートされるすべての入力範囲にわたって一貫しています。

図 6-5. 2 次 LPF 振幅応答

図 6-6. 2 次 LPF 位相応答

### 6.3.6 ADC ドライバ

最大サンプリング レートでデバイスの性能を満たすには、ADC 入力のサンプル/ホールド コンデンサが、アクイジョン時間枠内で正常に充放電できるようにします。ADC の入力時この駆動要件を満たすには、高帯域幅かつ低ノイズで安定したアンプ バッファを使用する必要があります。このような入力ドライバは、デバイスのアナログ入力チャネルのフロントエンド信号パスに組み込まれています。

### 6.3.7 リファレンス

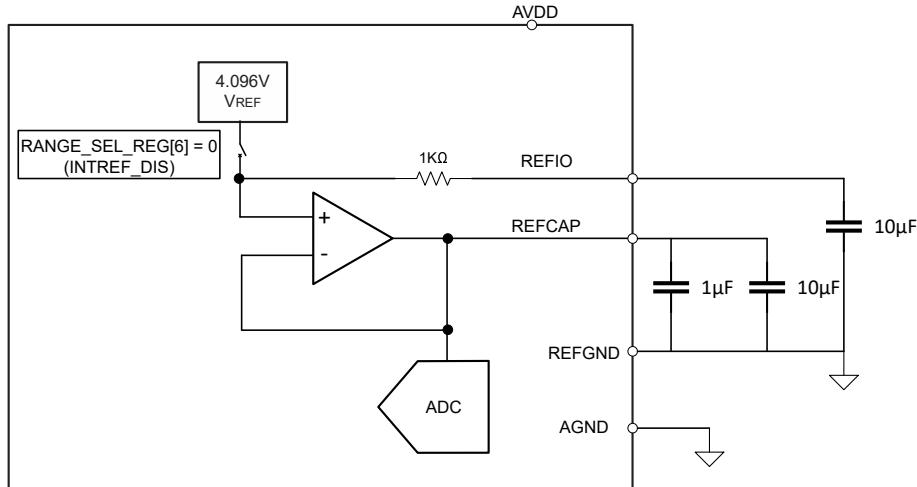

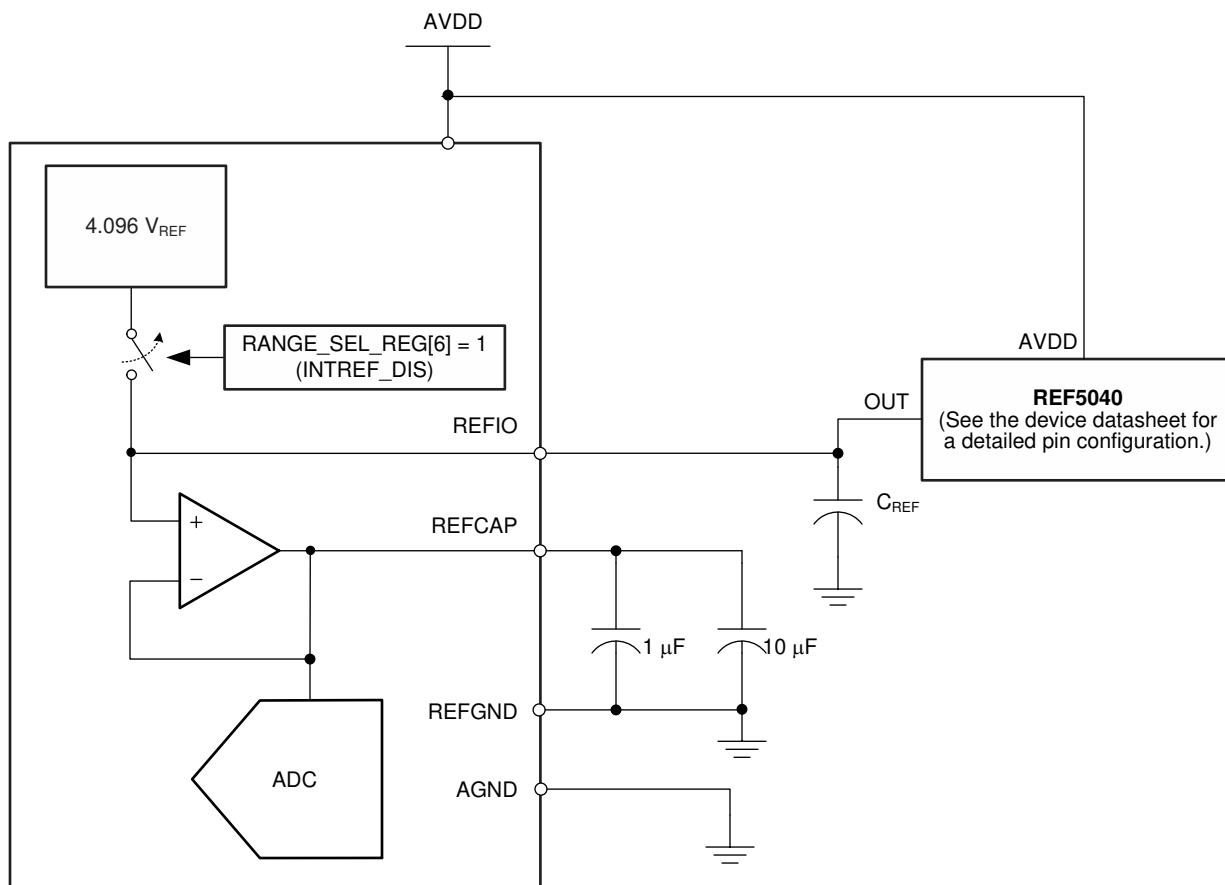

デバイスは、内部バッファを使用して、内部電圧リファレンスまたは外部電圧リファレンスで動作します。内部リファレンスまたは外部リファレンスの選択は、**RANGE\_SEL\_REG** レジスタの **INTREF\_DIS** ビットをプログラムすることで決まります。内部リファレンス ソースは、リセット後またはデバイスの起動時に、デフォルトで有効になります (**INTREF\_DIS = 0**)。外部リファレンス ソースを使用するたびに、**INTREF\_DIS** ビットをロジック 1 にプログラムして内部リファレンス ソースを無効化します。

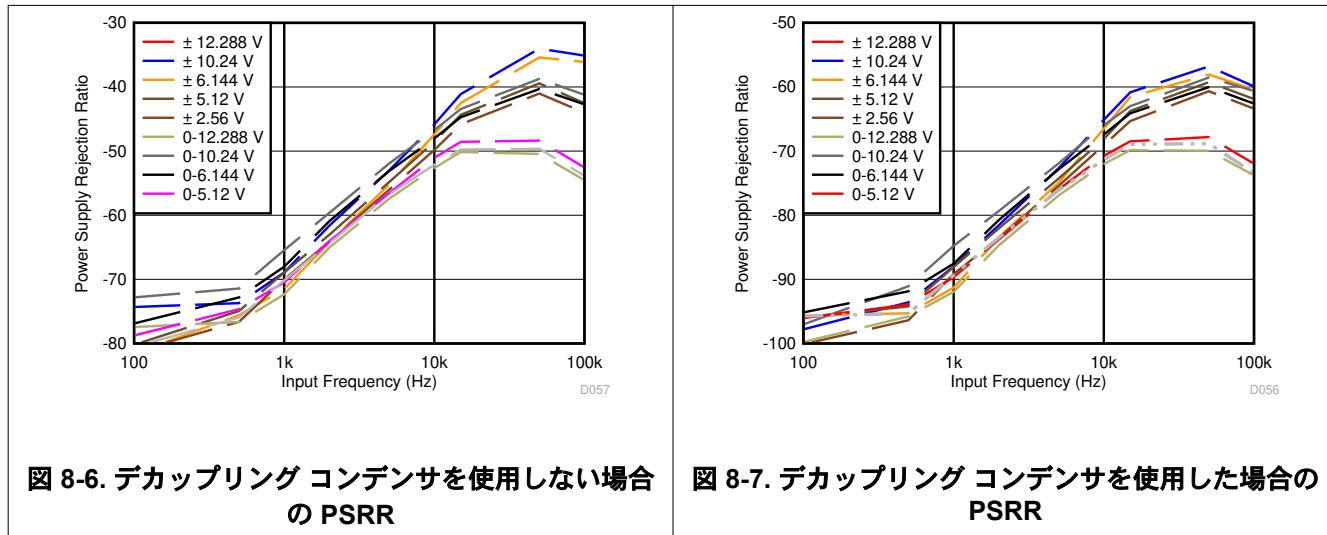

#### 6.3.7.1 内部リファレンス

デバイスには、公称出力値 4.096V の内部リファレンス ソースが備わっています。内部リファレンスを選択するには、**RANGE\_SEL\_REG** レジスタの **INTREF\_DIS** ビットをロジック 0 にプログラムします。内部リファレンスを使用すると、**REFIO** ピンは内部リファレンス値での出力になります。**図 6-7** に示されているように、**REFIO** ピンと **REFGND** ピンの間に 4.7 $\mu$ F (最小) のデカップリング コンデンサを配置します。内部バンドギャップ回路の出力インピーダンスによって、このコンデンサと一緒にローパス フィルタが形成され、リファレンスのノイズを帯域制限します。この値の小さいコンデンサを使用すると、システムのリファレンス ノイズが大きくなり、信号対雑音比と SINAD の性能が低下する可能性があります。電流出力能力は制限されているため、**REFIO** ピンを使用して外部 AC または DC 負荷を駆動しないでください。許容可能なオペアンプ バッファ (**OPA320** など) が続く場合は、**REFIO** ピンをソースとして使用します。

図 6-7. 4.096V 内部リファレンスを使用したデバイス接続

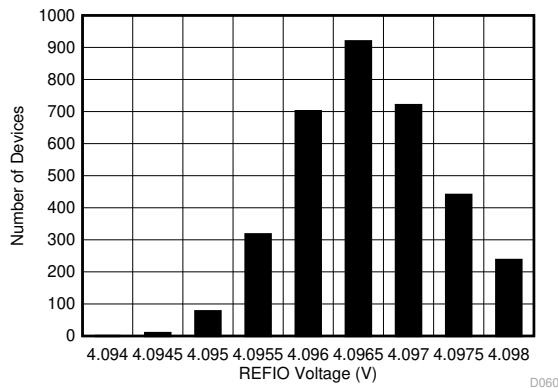

デバイスの内部リファレンス電圧は、初期精度仕様を提供するように工場出荷時に調整されます。図 6-8 のヒストグラムに、3420 を超える量産デバイスから取得した内部電圧リファレンス出力の分布を示します。

図 6-8. 室温での内部リファレンス精度ヒストグラム

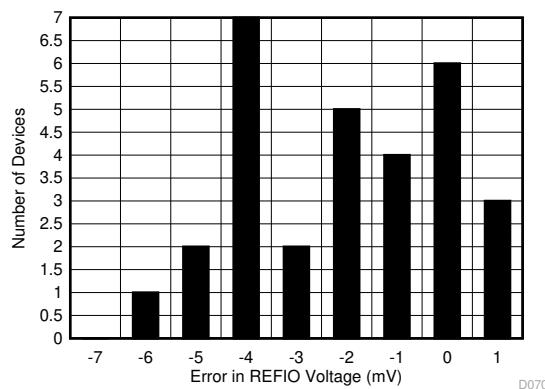

ダイが機械的ストレスまたは熱ストレスにさらされると、内部リファレンスの初期精度の仕様が低下します。 $V_{REF}$  値が変動する主な原因是、プリント基板 (PCB) への半田付け時に発生するデバイスへの加熱、およびそれ以降の半田リフローです。熱ヒステリシスの主な原因是、ダイストレスの変化です。これは、パッケージ、ダイ接続材料、モールド化合物、デバイスレイアウトによって決まります。

この効果を説明するために、メーカーが推奨するリフロー プロファイルに従い、鉛フリー半田ペーストを使用して 30 個のデバイスをはんだ付けしました。このプロセスの説明は、『AN-2029 取り扱いおよびプロセスの推奨事項』アプリケーションノートに記載されています。図 6-9 に示されているように、内部電圧リファレンス出力をリフロー プロセスの前後で測定して、値の標準的なシフトを示しています。テストしたユニットすべてで、出力電圧に正のシフトが示されました。負のシフトも可能です。図 6-9 のヒストグラムは、単一のリフロー条件にさらされた際の典型的なシフトを示しています。両面に表面実装部品があるプリント基板では、複数回のリフローにさらされることが一般的であり、これが出力電圧にさらなるシフトを引き起します。PCB にリフローが何回も行われる場合は、ADS868xW を 2 回目のパスで半田付けすることで、デバイスへの熱ストレスを最小限に抑えることができます。

図 6-9. 半田付けの熱によるシフトの分布ヒストグラム

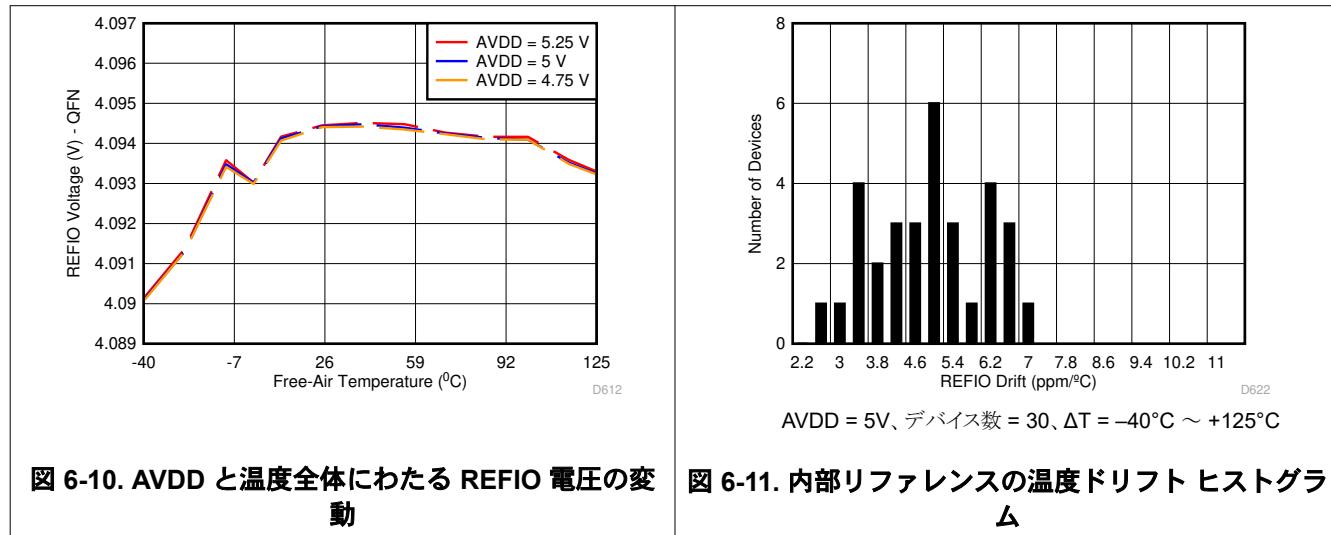

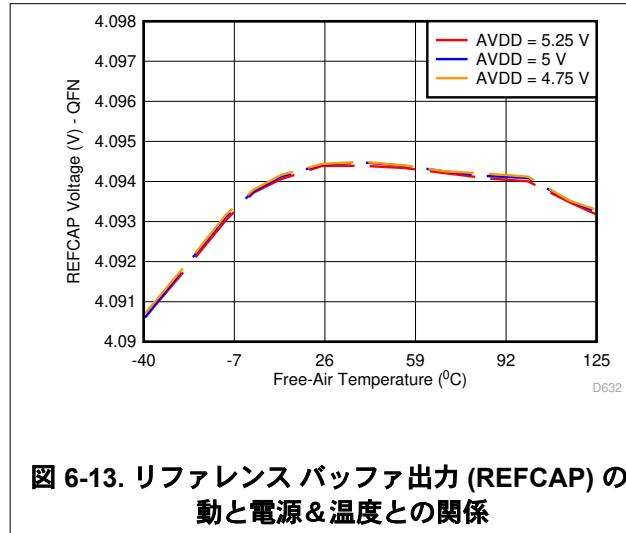

内部リファレンスも温度補償されており、-40°C ~ +125°C の拡張産業用温度範囲にわたって優れた温度ドリフトを提供します。図 6-10 に、AVDD 電源電圧の異なる値に対する温度全体の内部リファレンス電圧の変動を示します。図 6-11 に、WQFN (RUM) パッケージ

図 6-10. AVDD と温度全体にわたる REFIO 電圧の変動

図 6-11. 内部リファレンスの温度ドリフトヒストグラム

### 6.3.7.2 外部リファレンス

このデバイスは、より優れたリファレンス電圧または複数のデバイスの共通のリファレンス電圧を必要とするアプリケーションに適しています。このプロビジョニングでは、内部バッファとともに外部リファレンス ソースを使用して ADC リファレンス ピンを駆動できます。外部リファレンス モードを選択するには、RANGE\_SEL\_REG レジスタの INTREF\_DIS ビットをロジック 1 にプログラムします。このモードでは、4.096V 外部リファレンスを REFIO ピンに適用します。これは、入力として機能します。内部バッファは、ADC リファレンス入力に内部接続されている REFCAP ピンの動的な負荷を処理するように最適に設計されています。このモードでは、ローパワー、低ドリフト、小さい外部リファレンスをすべて適用できます。外部リファレンス ノイズがシステム性能に及ぼす影響を最小限に抑えるために、外部リファレンスの出力を適切にフィルタリングします。図 6-12 に、このモードの一般的なピン配置を示します。

図 6-12. 4.096V 外部リファレンスを使用したデバイス接続

内部リファレンス バッファの出力は、REFCAP ピンに現われます。REFCAP ピンと REFGND ピンの間に 10 $\mu$ F 以上の容量を配置します。高周波信号のデカップリングのために、別の 1 $\mu$ F コンデンサを REFCAP ピンのできるだけ近くに配置します。このバッファの電流出力能力は制限されているため、内部バッファを使用して外部 AC 負荷または DC 負荷を駆動しないでください。

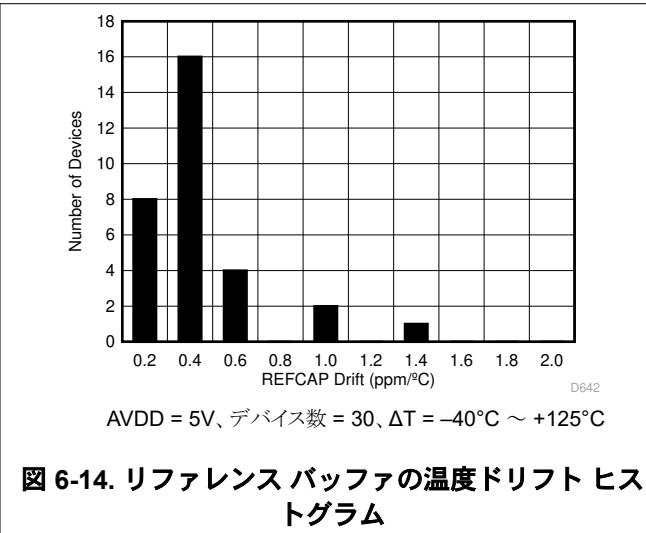

内部バッファ出力の性能は、 $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  の動作温度範囲全体で非常に安定します。図 6-13 に、AVDD 電源電圧の異なる値について、温度範囲全体にわたる REFCAP 出力の変動を示します。図 6-14 に示されているように、温度範囲全体でのリファレンス バッファドリフトの規定の標準値は  $0.5\text{ppm}/^{\circ}\text{C}$  です。規定の最大温度ドリフトは  $2\text{ppm}/^{\circ}\text{C}$  です。

図 6-13. リファレンス バッファ出力 (REFCAP) の変動と電源& 温度との関係

図 6-14. リファレンス バッファの温度ドリフトヒストグラム

### 6.3.8 ADC の伝達関数

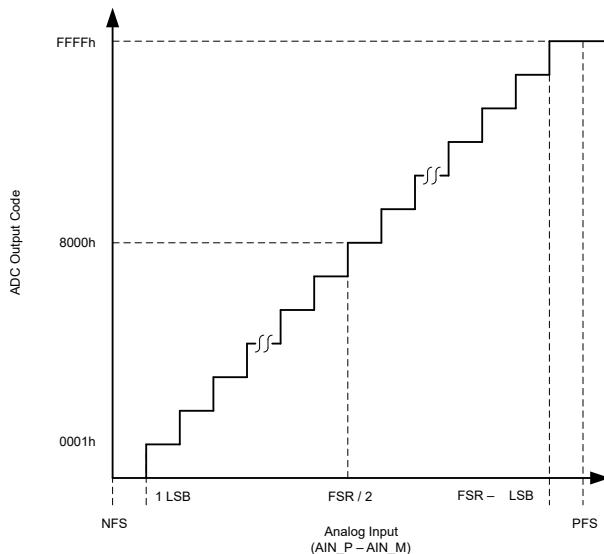

このデバイスはシングルエンドおよび差動入力をサポートしており、バイポーラとユニポーラの両方の入力範囲に対応します。デバイスの出力は、バイポーラとユニポーラの両方の入力範囲に対して、ストレートバイナリ形式です。

図 6-15 に、すべての入力範囲の理想的な伝達特性を示します。各入力信号のフルスケール範囲 (FSR) は、正のフルスケール (PFS) と負のフルスケール (NFS) の入力電圧の差に等しくなります。 LSB サイズは、 $FSR/2^{16}$  と等しくなります。リファレンス電圧  $V_{REF} = 4.096V$  については、表 6-4 にそれぞれの入力範囲に対応する LSB の値を示します。

図 6-15. デバイスの伝達関数 (ストレートバイナリ形式)

表 6-4. 異なる入力範囲の ADC LSB 値 ( $V_{REF} = 4.096V$ )

| 入力範囲                         | 正のフルスケール (V) | 負のフルスケール (V) | フルスケール レンジ (V) | LSB            |

|------------------------------|--------------|--------------|----------------|----------------|

| $\pm 3V \times V_{REF}$      | 12.288       | -12.288      | 24.576         | 375.0 $\mu$ V  |

| $\pm 2.5V \times V_{REF}$    | 10.24        | -10.24       | 20.48          | 312.5 $\mu$ V  |

| $\pm 1.5V \times V_{REF}$    | 6.144        | -6.144       | 12.288         | 187.5 $\mu$ V  |

| $\pm 1.25V \times V_{REF}$   | 5.12         | -5.12        | 10.24          | 156.25 $\mu$ V |

| $\pm 0.625V \times V_{REF}$  | 2.56         | -2.56        | 5.12           | 78.125 $\mu$ V |

| 0V から $3V \times V_{REF}$    | 12.288       | 0            | 12.288         | 187.5 $\mu$ V  |

| 0V から $2.5V \times V_{REF}$  | 10.24        | 0            | 10.24          | 156.25 $\mu$ V |

| 0V から $1.5V \times V_{REF}$  | 6.144        | 0            | 6.144          | 93.75 $\mu$ V  |

| 0V から $1.25V \times V_{REF}$ | 5.12         | 0            | 5.12           | 78.125 $\mu$ V |

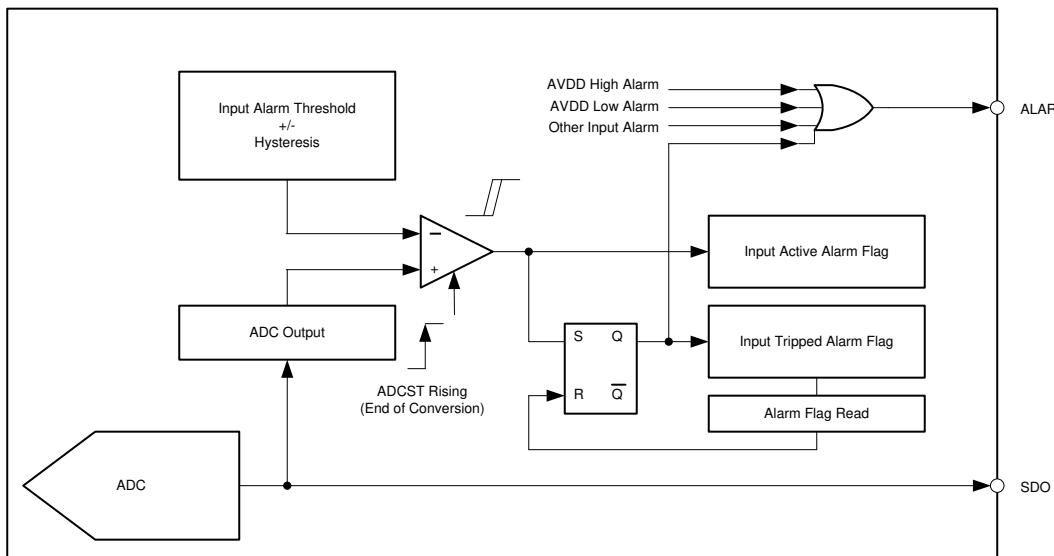

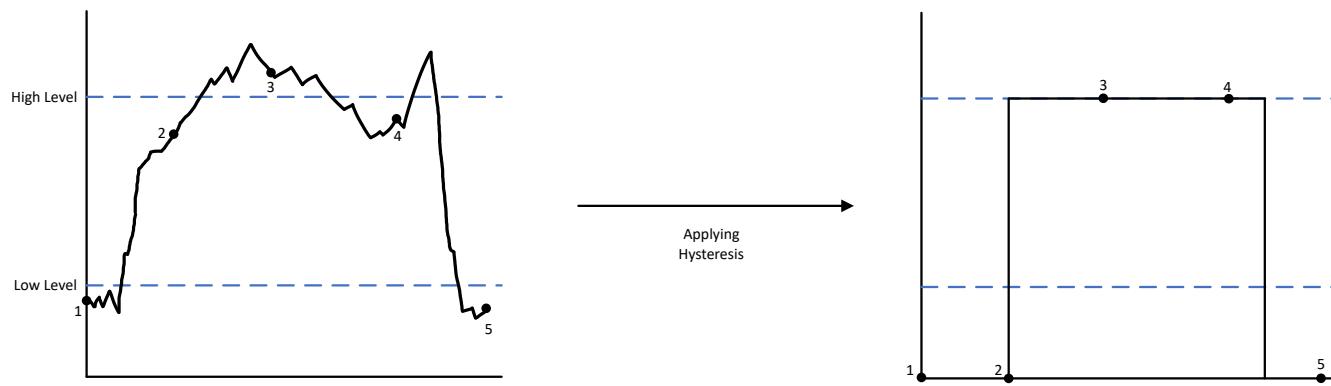

### 6.3.9 アラーム機能

このデバイスは、ピンがアラーム機能用に構成されている場合に限り、ALARM/SDO-1/GPO ピンにアクティブ High の ALARM 出力を備えています。マルチファンクション ピンで ALARM 出力を有効にするには、[SDO\\_CTL\\_REG レジスタ](#) の SDO1\_CONFIG[1:0] ビットを 01b に設定します。

このデバイスには、入力アラームと AVDD アラームの 2 種類のアラーム機能があります。

- 入力アラームの場合、ADC 入力の電圧が監視され、ユーザーがプログラマブル High および Low スレッショルド値と比較されます。デバイスは、入力信号に対応するデジタル値がユーザーによって設定された High または Low スレッショルドを超えると、アクティブ High の ALARM 出力を設定します。入力アラーム機能の詳細については、「[入力アラーム](#)」セクションを参照してください。

- AVDD アラームの場合、ADC アナログ電源電圧 (AVDD) が監視され、AVDD 電源の指定された標準スレッショルド値と比較されます。Low スレッショルド値は 4.7V、High スレッショルド値は 5.3V です。AVDD 値が、指定された Low (4.7V) または High (5.3V) のスレッショルド値をどちらかの方向に交差すると、このデバイスはアクティブ High の ALARM 出力を設定します。

アラーム機能をオンにすると、入力アラーム機能と AVDD アラーム機能の両方がデフォルトで有効になります。これらのアラーム機能は、[RST\\_PWRCTL\\_REG レジスタ](#) の IN\_AL\_DIS ビットと VDD\_AL\_DIS ビットを (それぞれ) プログラムすることで選択的に無効化されます。

各アラーム (入力または AVDD) には、「アクティブ」アラーム フラグと「トリップ」アラーム フラグの 2 種類のアラーム フラグが関連付けられています。すべてのアラーム フラグは、[ALARM\\_REG レジスタ](#)で読み取られます。両方のフラグは、関連付けられたアラームがトリガーされると設定されます。アクティブなアラームは、現在の ADC 変換の終了時にクリアされます (アラーム状態が続く場合は、再度設定されます)。しかし、トリップしたフラグは、[ALARM\\_REG](#) が読み出された後でのみクリアされます。

ALARM 出力フラグは、変換の終了時に内部で更新されます。これらの出力フラグは、ユーザーが開始した任意のデータフレーム中に CONVST/CS 信号を Low レベルにして読み取られます。

ALARM 出力フラグを 3 通りの方法で読み取ります。これらのフラグは、ALARM 出力ピンを使用して、内部の ALARM レジスタを読み取るか、またはデータ出力に ALARM フラグを追加して読み取ります。

- ALARM ピンが High レベルの場合、これは AVDD またはデバイスのアナログ入力チャネルの過電圧または低電圧状態を示しています。このピンを配線して、ホスト入力を割り込みさせることができます。

- ALARM\_REG レジスタの内部 ALARM フラグ ビットは、変換の終了時に更新されます。出力ピンで ALARM 割り込みを受信した後、内部アラーム フラグ レジスタでアラームを生成した条件の詳細を読み取ることができます。

- ALARM 出力フラグは、データ出力ビット ストリームに選択的に追加されます (構成の詳細については、『[DATAOUT\\_CTL\\_REG レジスタ](#)』を参照)。

図 6-16 は、デバイスアラーム機能の機能ブロック図を示しています。

図 6-16. アラーム機能の回路図

#### 6.3.9.1 入力アラーム

このデバイスは、アナログ入力に High および Low アラームを備えています。入力信号に対応するアラームでは、独立してプログラマブル スレッショルドと共にヒステリシス設定が **ALARM\_H\_TH\_REG** および **ALARM\_L\_TH\_REG** レジスタで制御されます。

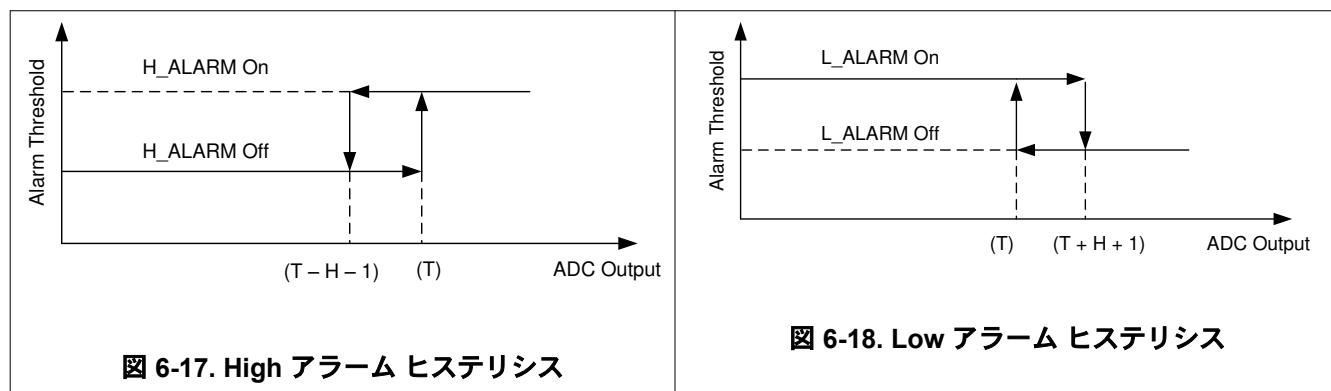

デジタル出力が High アラーム上限値 [High アラーム スレッショルド (T)] を超えると、デバイスは入力 High アラームを設定します。デジタル出力が High アラーム下限値 [High アラーム (T) - H - 1] を下回ると、アラームはリセットされます。[図 6-17](#) に、この関数を示します。

同様に、デジタル出力が Low アラーム下限値 [Low アラーム スレッショルド (T)] を下回ると、入力 Low アラームがトリガれます。デジタル出力が Low アラーム上限値 [Low アラーム (T) + H + 1] 以上になると、アラームはリセットされます。[図 6-18](#) に、この関数を示します。

#### 6.3.9.2 AVDD アラーム

このデバイスは、アナログ電源 AVDD に High および Low アラームを備えています。入力信号のアラームとは異なり、AVDD アラームには、設計で設定する固定トリップ ポイントがあります。このデバイスには、High および Low スレッショルド電圧に対してアナログ電源を定期的に監視する、内部アナログ コンパレータが搭載されています。High アラームは AVDD が標準値の 5.3V を超えた場合に設定され、AVDD が 4.7V 未満に低下すると Low アラームがアサートされます。この機能は、アナログ AVDD 電源のグリッチまたは電圧低下状況によって発生するデバイスの異常な動作をデバッging するのに特に役立ちます。

## 6.4 デバイスの機能モード

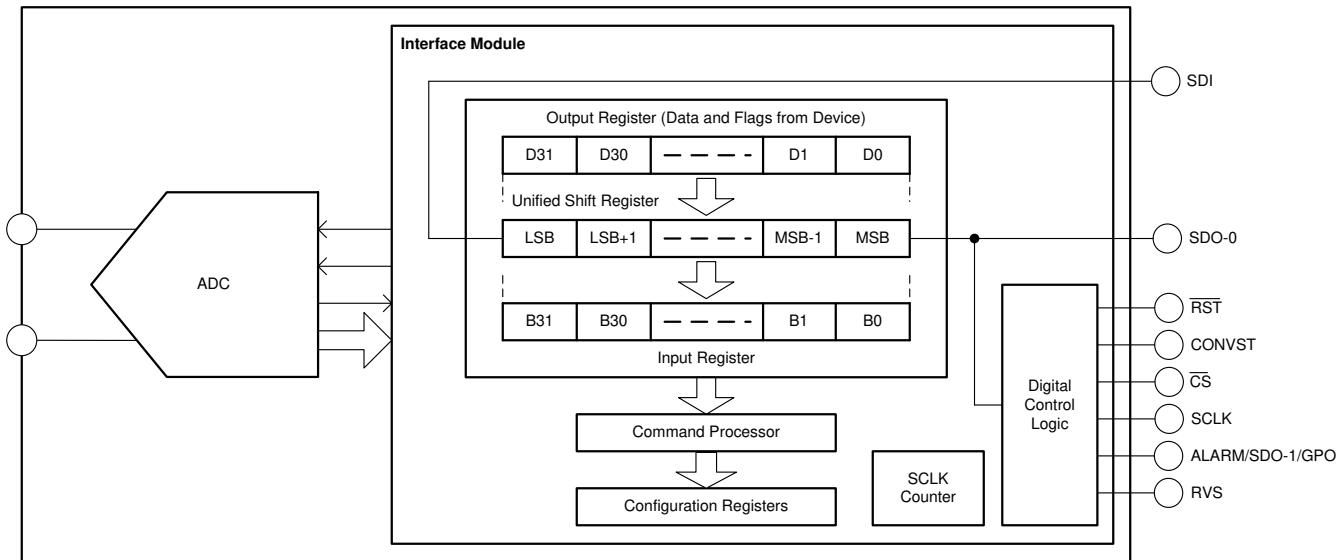

このデバイスには、デバイスとホストコントローラの間で通信およびデータ転送を行うための multiSPI デジタルインターフェイスが搭載されています。multiSPI インターフェイスは、ホストがデバイスとの間でデータおよびコマンドを交換するためには多くのデータ転送プロトコルをサポートしています。ホストは標準 SPI モードのいずれかを使用してデータをデバイスに転送します。しかし、スループットとレイテンシに関するアプリケーション固有の要求を満たすために、データを出力するためのさまざまな構成が用意されています。これらのモードのデータ出力はホストまたはデバイスによって制御され、タイミングはシステム同期またはソース同期です。サポートされているデータ転送プロトコルの詳細については、「[データ転送プロトコル](#)」セクションを参照してください。

このセクションでは、デジタルインターフェイスモジュールの主要コンポーネントと、サポートされている構成およびプロトコルについて説明します。[図 6-19](#) に示されているように、インターフェイスモジュールはシフトレジスタ（入力と出力の両方）、構成レジスタ、およびプロトコルユニットで構成されます。特定のデータフレーム中に、データはデバイスとの間で転送されます。その結果、ホストは常に 32 ビットの入出力シフトレジスタとしてデバイスを認識します。

図 6-19. デバイスインターフェイスモジュール

「[ピン構成および機能](#)」セクションでは、インターフェイスピンについて説明します。「[データ転送フレーム](#)」セクションでは、シフトレジスタ、SCLK カウンタ、コマンドプロセッサの機能について詳しく説明します。「[データ転送フレーム](#)」セクションでは、サポートされているプロトコルの詳細について説明します。「[レジスタマップ](#)」セクションでは、構成レジスタとビット設定について説明します。

#### 6.4.1 ホスト / デバイス間の接続トポロジ

multiSPI インターフェイスおよびデバイス構成レジスタにより、ホストコントローラがデバイスとデータまたはコマンドを交換する方法を柔軟に実現できます。ここでは、さまざまなシステム要件を満たすためにハードウェア接続トポロジを選択する方法について説明します。

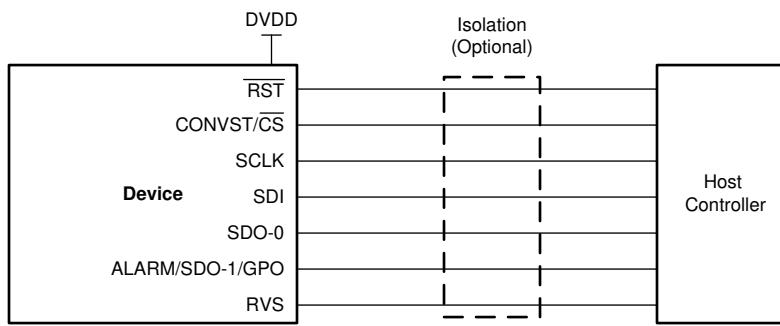

##### 6.4.1.1 シングル デバイス : すべての multiSPI オプション

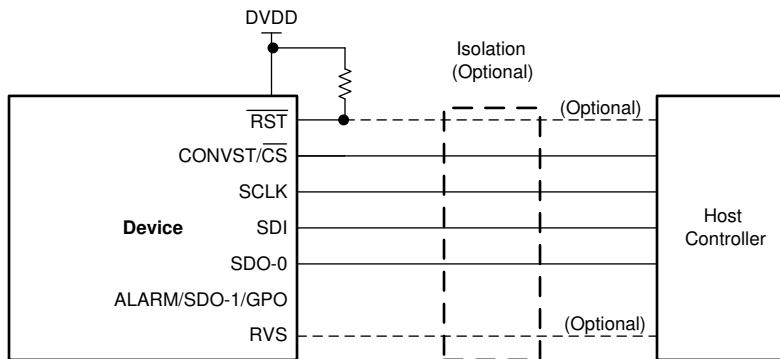

図 6-20 に、ホストコントローラとスタンダードアローン デバイスの間のピン接続を示し、multiSPI インターフェイスに提供されるすべてのオプションを実行します。

図 6-20. すべての multiSPI プロトコル ピン構成

##### 6.4.1.2 シングル デバイス : 標準 SPI インターフェイス

図 6-21 に、標準 SPI プロトコルを使用したアプリケーションの最小ピンインターフェイスを示します。

図 6-21. 標準 SPI プロトコル ピン構成

CONVST/CS、SCLK、SDI、および SDO-0 ピンは、ホストコントローラの標準 SPI ポートを構成します。RST ピンを DVDD に接続します。タイミングの利点を得るために、RVS ピンを監視します。ALARM/SDO-1/GPO ピンには、外部接続を行わないでください。

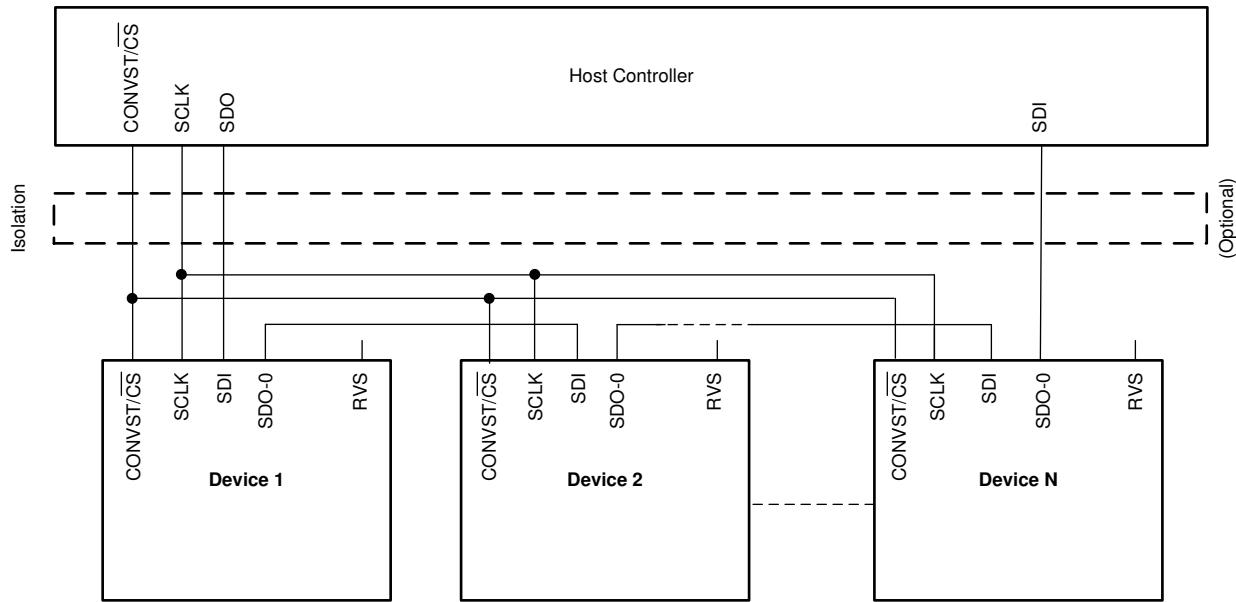

#### 6.4.1.3 複数のデバイス：デイジーチェーントポロジ

図 6-22 に、デイジーチェーントポロジで複数のデバイスを使用した一般的な接続図が示されています。

図 6-22. デイジーチェーン接続の回路図

すべてのデバイスの **CONVST/CS** および **SCLK** 入力は相互に接続され、それぞれホスト コントローラの单一の **CONVST/CS** および **SCLK** ピンによって制御されます。チェーンの最初のデバイス（デバイス 1）の **SDI** 入力ピンは、ホスト コントローラの **SDO-x** ピンに接続されます。デバイス 1 の **SDO-0** 出力ピンはデバイス 2 の **SDI** 入力ピンに接続され、以下同様に続きます。チェーンの最後のデバイス（デバイス N）の **SDO-0** 出力ピンは、ホスト コントローラの **SDI** ピンに接続されます。

デイジーチェーントポロジで複数のデバイスを動作させるには、ホスト コントローラによって各デバイスの構成レジスタを同じ値でプログラムします。このデバイスは、データ読み取りおよびデータ書き込み動作のため、任意のレガシー SPI 互換プロトコルと外部クロックを使用して、シングル **SDO-0** 出力で動作します。**SDO\_CTL\_REG レジスタ**で、ビット 7-0 を **00h** にプログラムします。

デイジーチェーントポロジ内のすべてのデバイスは、**CONVST/CS** 信号の立ち上がりエッジで、アナログ入力信号をサンプリングします。データ転送フレームは、同じ信号の立ち下がりエッジから開始します。**SCLK** 信号の起動エッジで、チェーン内のすべてのデバイスが **MSB** を **SDO-0** ピンにシフト アウトします。**SCLK** キャプチャエッジごとに、デイジーチェーン接続された各デバイスは、統合シフトレジスタの **LSB** ビットとして **SDI** ピンで受信したデータをシフトインします。図 6-19 に、このプロセスの図を示します。したがって、デイジーチェーン構成では、ホスト コントローラはデバイス N のデータを受信し、その後デバイス N-1 のデータを受信します（以下同様）。このプロセスは、**MSB** ファーストの方法で継続されます。**CONVST/CS** 信号の立ち上がりエッジで、各デバイスは統合シフトレジスタの内容をデコードし、適切な操作を実行します。

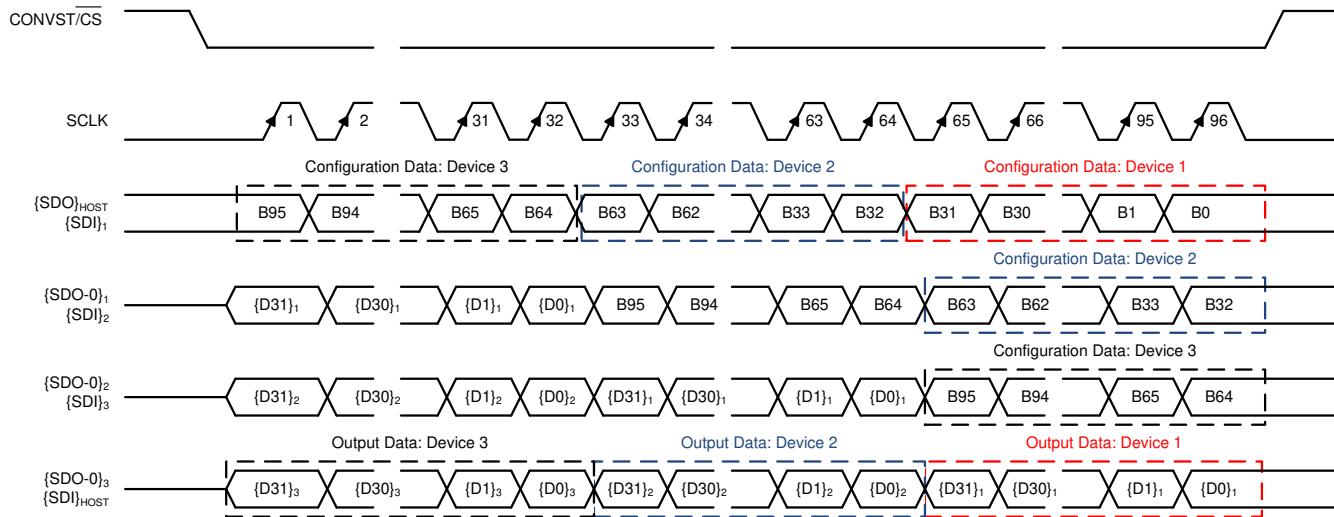

デイジーチェーントポロジで接続された N 個のデバイスの場合、最適なデータ転送フレームには  $32 \times N$  **SCLK** キャプチャエッジを含めます（図 6-23 を参照）。データ転送フレームを短くすると、デバイス構成に誤りが生じるため、これは避けてください。>  $32 \times N$  **SCLK** キャプチャエッジのデータ転送フレームの場合、ホスト コントローラは各デバイスの構成データを適切に揃えることができます。その後、ホストが **CONVST/CS** を High にします。

システム全体のスループットは、デイジーチェーントポロジで接続されるデバイスの数に比例して減少します。

図 6-23 に、デイジーチェーン接続で接続して、SPI-00-S プロトコルを使用した 3 つのデバイスの代表的タイミング図を示します。

図 6-23. デイジーチェーン モードの 3 つのデバイスのタイミング図

#### 6.4.2 デバイスの動作モード

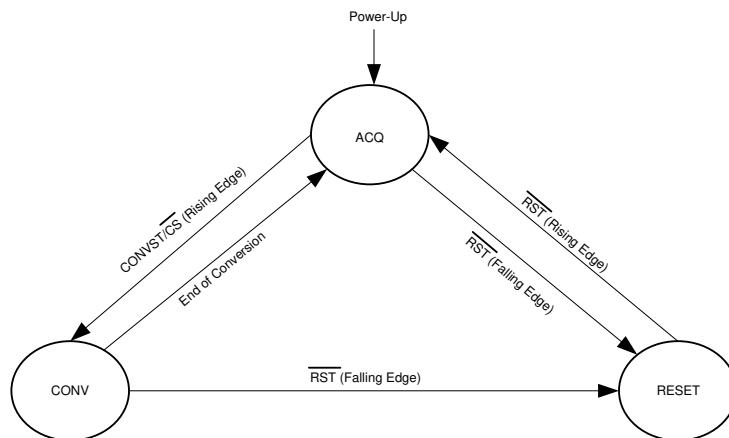

図 6-24 に示されているように、このデバイスは以下の 3 つの状態をサポートしています。RESET、ACQ、CONV。デバイスの状態は、ホストコントローラから供給される CONVST/CS および RST 制御信号の状態によって決まります。

図 6-24. デバイスの機能状態

#### 6.4.2.1 RESET 状態

デバイスは、非同期デジタル入力としてアクティブ Low の  $\overline{RST}$  ピンを備えています。RESET 状態に移行するには、(スイッチング特性の表に示されているように)  $t_{WL\_RST}$  期間にわたって、 $\overline{RST}$  ピンを Low にプルして保持します。

デバイスには、アプリケーションリセットまたはパワーオンリセット (POR) という 2 種類のリセット機能が搭載されています。 $\overline{RST}$  ピンの機能は、[RST\\_PWRCTL\\_REG レジスタ](#)の RSTn\_APP ビットの状態によって決まります。

- $\overline{RST}$  ピンを構成してアプリケーションリセットを発行するには、[RST\\_PWRCTL\\_REG レジスタ](#)の RSTn\_APP ビットを 1b に設定します。このリセット状態では、すべての構成レジスタ (レジスタマップを参照) がデフォルト値にリセットされ、RVS ピンは Low のままで、SDO-x ピンはトライステートになります。

- $\overline{RST}$  ピンのデフォルト構成は、Low レベルにプルされると、パワーオンリセットを発行します。この状態では、RSTn\_APP ビットは 0b に設定されます。POR が発行されると、すべての内部デバイス回路 (PGA、ADC ドライバ、電圧リファレンスを含む) がリセットされます。デバイスが POR 状態から回復する際は、内部回路が正確に安定するように、 $t_{D\_RST\_POR}$  時間の猶予を確保してください。 $t_{D\_RST\_POR}$  の期間については、スイッチング特性の表を参照してください。

いずれかのリセット状態を終了するには、CONVST/ $\overline{CS}$  および SCLK を Low に保持した状態で、 $\overline{RST}$  ピンを High にプルします。 $t_{D\_RST\_POR}$  または  $t_{D\_RST\_APP}$  の遅延後 (スイッチング特性の表を参照)、デバイスは ACQ 状態に移行し、RVS ピンは High になります。

デバイスを他の 2 つの状態 (ACQ または CONV) のいずれかで動作させるには、 $\overline{RST}$  ピンを High に保持します。 $\overline{RST}$  ピンが High に保持されると、CONVST/ $\overline{CS}$  ピンでの遷移により、デバイスの機能状態が決まります。[図 5-1](#) に、一般的な変換サイクルを示します。

#### 6.4.2.2 ACQ 状態

ACQ 状態では、デバイスはアナログ入力信号を取得します。デバイスは、パワーアップ時、非同期リセットの後、または各変換が終了した後に、ACQ 状態に移行します。

$\overline{RST}$  立ち下がりエッジで、デバイスは ACQ 状態から RESET 状態になります。CCONVST/ $\overline{CS}$  信号の立ち上がりエッジで、デバイスは ACQ 状態から CONV 状態になります。

このデバイスは、低消費電力 NAP モードを備えており、ACQ 状態で消費電力を低減できます。NAP モードの詳細については、「[NAP モード](#)」セクションを参照してください。

#### 6.4.2.3 CONV 状態

デバイスは、CONVST/ $\overline{CS}$  信号の立ち上がりエッジで、ACQ 状態から CONV 状態に移行します。変換プロセスでは内部クロックを使用し、進行中の変換が完了するまでデバイスは CONVST/ $\overline{CS}$  信号におけるさらなる遷移を無視します。つまり、デバイスは  $t_{conv}$  の時間間隔中、さらなる遷移を無視します。

変換が終了すると、デバイスは ACQ 状態に入ります。[式 1](#) の式で、デバイスのサイクル時間を計算します。

$$t_{cycle-min} = t_{conv} + t_{acq-min} \quad (1)$$

#### 注

(スイッチング特性表に指定されているように) 変換時間  $t_{conv}$  は、 $t_{conv\_min}$  および  $t_{conv\_max}$  の制限内で変動します。変換の開始後、ホストコントローラは RVS ピンの Low から High への遷移を監視するか、 $t_{conv\_max}$  が経過するまで待機します。その後、ホストは新しい動作 (データ転送または変換) を開始します。RVS が監視されていない場合は、[式 1](#) の  $t_{conv}$  を  $t_{conv\_max}$  に置き換えます。

## 6.5 プログラミング

このデバイスには（「レジスタ マップ」セクションで説明されているように）9つの構成レジスタが搭載されており、2種類のデータ転送動作をサポートしています。これらの動作は、データ書き込み（ホストがデバイスを構成）と、データの読み取り（ホストがデバイスからデータを読み取り）です。

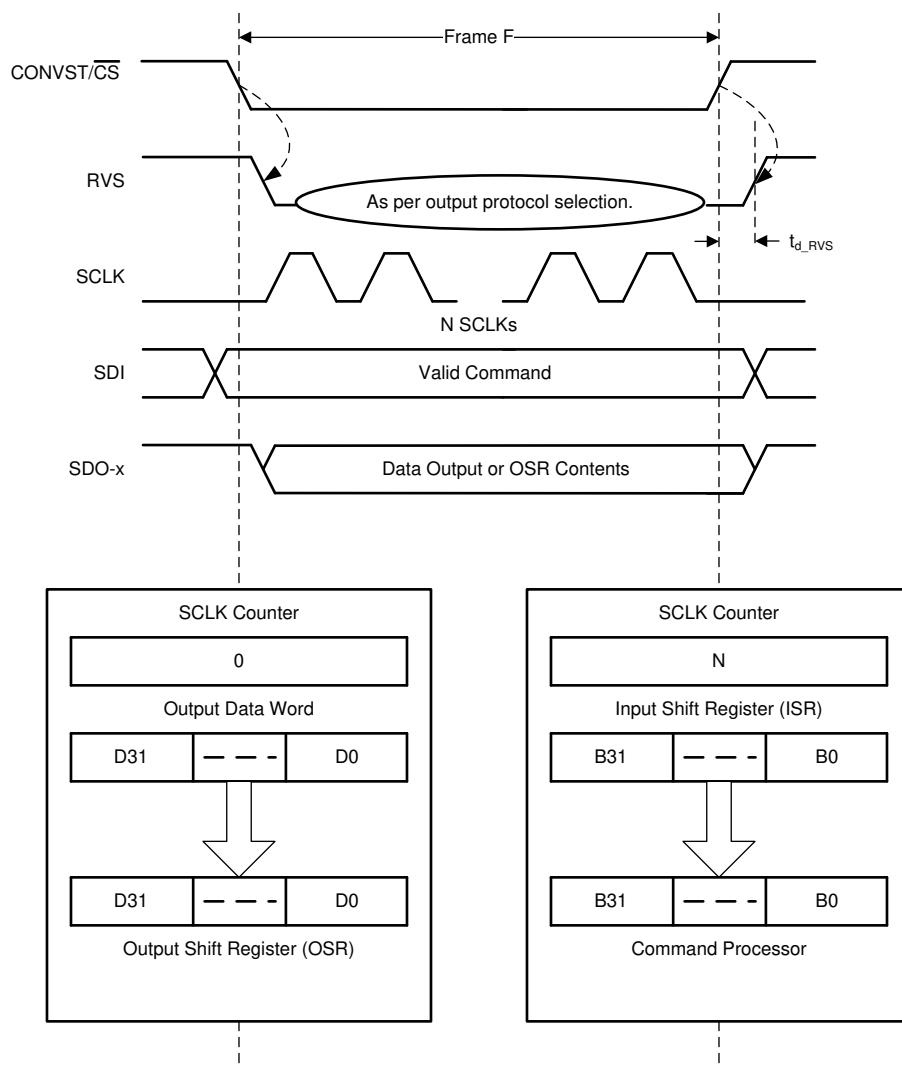

### 6.5.1 データ転送フレーム

デバイスとホスト コントローラとの間のデータ転送フレームは、CONVST/CS ピンの立ち下がりエッジで開始されます。このフレームは、デバイスが次の立ち上がりエッジで変換を開始すると終了します。ホスト コントローラは、CONV 相が終了した後で CONVST/CS 信号を Low (図 6-25) にすることで、データ転送フレームを開始します。「CONV 状態」セクションに、このプロセスの説明が記載されています。

図 6-25. データ転送フレーム

標準的なデータ転送フレーム F の場合:

1. ホストコントローラは CONVST/CS を Low にプルし、データ転送フレームを開始します。CONVST/CS 信号の立ち上がりエッジで、以下が発生します。

- RVS が Low になり、データ転送フレームの開始を示します。

- 内部 SCLK カウンタが 0 にリセットされます。

- デバイスはデータバスを制御します。図 6-25 に示されているように、出力データワードの内容は、32 ビットの出力シフトレジスタ (OSR) にロードされます。

- 内部構成レジスタは、NOP コマンドに対応する 0000h にリセットされます。

2. フレーム中、ホストコントローラは SCLK ピンにクロックを供給します。

- SCLK キャプチャエッジごとに、SCLK カウンタがインクリメントされます。SDI ピンで受信されたデータビットは、入力シフトレジスタの LSB にシフトインされます。

- 出力クロックの起動エッジごとに、出力シフトレジスタデータの MSB は、選択された SDO-x ピンでシフトアウトされます。この場合、SCLK は出力クロックです。

- RVS ピンのステータスは、出力プロトコルの選択によって異なります（「デバイスからの読み取りのプロトコル」セクションを参照）。

3. ホストコントローラは CONVST/CS ピンを High にして、データ転送フレームを終了します。CONVST/CS の立ち上がりエッジで、以下が発生します。

- SDO-x ピンがトライステートになります。

- 図 6-25 に示されているように、入力シフトレジスタの内容はコマンドプロセッサへ転送され、デコードとさらなる処理が行われます。

- RVS 出力が Low になり、変換が開始することを示します。

CONVST/CS を High にすると、ホストコントローラは RVS ピンの Low から High への遷移を監視します。または、ホストコントローラは、新しいデータ転送フレームを開始する前に、 $t_{conv\_max}$  時間（スイッチング特性の表を参照）が経過するまで待機します。

データ転送フレーム F の終了時に、以下が発生します。

- SCLK カウンタが 32 の場合、デバイスはフレーム F を読み取りまたは書き込み動作に「最適な」データ転送フレームとして扱います。最適なデータ転送フレームの終了時に、コマンドプロセッサは 32 ビットの入力シフトレジスタの内容を有効なコマンドワードとして扱います。

- SCLK カウンタが 32 未満の場合、デバイスはフレーム F を「短い」データ転送フレームとして扱います。

- デバイスへのデータ書き込み動作が無効で、デバイスはこのフレームを NOP コマンドとして扱います。

- SDO-x ピンで短いフレーム中に転送される出力データビットは、引き続き有効なデータです。ホストコントローラは、短いデータ転送フレームを使用して、32 ビット出力シフトレジスタから必要な MSB ビット数を読み出します。

- SCLK カウンタが 32 より大きい場合、デバイスはフレーム F を「長い」データ転送フレームとして扱います。長いデータ転送フレームの終了時に、コマンドプロセッサは、32 ビットの入力シフトレジスタの内容を有効なコマンドワードとして扱います。任意のデータ転送フレーム F 内に供給されるクロックの最大数に制限はありません。ホストが長いデータ転送フレームを提供する場合、CONVST/CS の立ち上がりエッジより前に、最後の 32 ビットがデバイスにシフトされて目的のコマンドが構成されます。

## 6.5.2 入力コマンド ワードおよびレジスタ書き込み動作

デバイスへのデータ書き込み動作は、常に SCLK ピンに供給される外部クロックと同期します。

このデバイスは、どのデバイスのプログラミング動作時にも、1 バイトまたは 2 バイト (ハーフワードに相当) の読み取りまたは書き込みを行うことができます。表 6-5 に、デバイスでサポートされている入力コマンドを一覧します。1 回の操作での 2 バイトの読み取りまたは書き込みに関連付けられる入力コマンドには「HWORD」のサフィックスが付きます。

すべての HWORD コマンドについて、9 ビット アドレスの LSB は常に無視され、0b とみなされます。たとえば、特定の HWORD コマンドにアドレス 04h と 05h のどちらが入力されているかに関わらず、デバイスは常にアドレス 04h でコマンドを実行します。

**表 6-5. 入力コマンドのリスト**

| オペコード<br>B[31:0]                                      | コマンドの頭字語    | コマンドの説明                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00000000_00000000_00000000_00000000                   | NOP         | 無操作                                                                                                                                                                                                                                                                                              |

| 11000_xx_<9-bit address>_<16-bit data> <sup>(1)</sup> | CLEAR_HWORD | <ul style="list-style-type: none"> <li>レジスタのいずれかのビット (またはグループ) をクリアするために使用されるコマンド。</li> <li>データ フィールドに 1 のマークが付いているビットがあると、指定されたレジスタの特定のビットは 0 にリセットされます。その他のビットは変更されません。</li> <li>ハーフワードコマンド (つまり、コマンドが一度に 16 ビットで機能します)。</li> <li>9 ビット アドレスの LSB は常に無視され、0b とみなされます。<sup>(2)</sup></li> </ul> |

| 11001_xx_<9-bit address>_00000000_00000000            | READ_HWORD  | <ul style="list-style-type: none"> <li>16 ビット読み取り動作を実行するためのコマンド。</li> <li>ハーフワードコマンド (つまり、デバイスは 16 ビットのレジスタ データを一度に出力します)。</li> <li>9 ビット アドレスの LSB は常に無視され、0b とみなされます。</li> <li>デバイスがこのコマンドを受信すると、次のフレームでレジスタの 16 ビットを送信します。</li> </ul>                                                         |

| 01001_xx_<9-bit address>_00000000_00000000            | 読み取り        | <ul style="list-style-type: none"> <li>READ_HWORD と同じですが、次のフレームでレジスタ (バイト読み出し) の 8 ビットのみが返される点が異なります。</li> </ul>                                                                                                                                                                                 |

| 11010_00_<9-bit address>_<16-bit data>                | 書き込み        | <ul style="list-style-type: none"> <li>ハーフワード書き込みコマンド (2 バイトの入力データが指定されたアドレスに書き込まれます)。</li> <li>9 ビット アドレスの LSB は常に無視され、0b とみなされます。</li> </ul>                                                                                                                                                   |

| 11010_01_<9-bit address>_<16-bit data>                |             | <ul style="list-style-type: none"> <li>ハーフワード書き込みコマンド。</li> <li>9 ビット アドレスの LSB は常に無視され、0b とみなされます。</li> <li>このコマンドでは、16 ビットのデータワードの MS バイトのみが、指定されたレジスタ アドレスに書き込まれます。LSB は無視されます。</li> </ul>                                                                                                    |

| 11010_10_<9-bit address>_<16-bit data>                |             | <ul style="list-style-type: none"> <li>ハーフワード書き込みコマンド。</li> <li>9 ビット アドレスの LSB は常に無視され、0b とみなされます。</li> <li>このコマンドでは、指定されたレジスタ アドレスに 16 ビットのデータワードの LSB のみが書き込まれます。MSB は無視されます。</li> </ul>                                                                                                      |

| 11011_xx_<9-bit address>_<16-bit data>                | SET_HWORD   | <ul style="list-style-type: none"> <li>レジスタの任意の (またはグループの) ビットを設定するために使用されるコマンド。</li> <li>データ フィールドに 1 のマークが付いているビットがあると、指定されたレジスタの特定のビットは 1 に設定されます。その他のビットは変更されません。</li> <li>ハーフワードコマンド (つまり、コマンドが一度に 16 ビットで機能します)。</li> <li>9 ビット アドレスの LSB は常に無視され、0b とみなされます。</li> </ul>                   |

| 他すべての入力コマンドの組み合わせ                                     | NOP         | 無操作                                                                                                                                                                                                                                                                                              |

(1) 表 7-1 で定義されているように、<9-bit address> は、MSB 位置に 0 を追加し、その後に 8 ビットのレジスタ アドレスを追加することで実行されます。レジスタ 0x04h の <9-bit address> は 0x0-0000-0100b です。

(2) HWORD コマンドは、レジスタ マップの 16 ビットのセットに対して動作し、通常はそれぞれ 8 ビットの 2 つのレジスタとして識別されます。たとえば、コマンド「11000\_xx\_<0\_0000\_0101><16-bit data>」は、RST\_PWRCTL\_REG レジスタのビット 15:0 のコマンド「11000\_xx\_<0\_0000\_0100><16-bit data>」と同じように扱われます。

内部レジスタの構成に使用されるすべての入力コマンド（表 6-5 に示されている CLEAR\_HWORD、WRITE、および SET\_HWORD コマンドを含む）が 32 ビット長であることを確認します。これらのコマンドのいずれかが特定のデータフレーム F で提供されている場合、そのコマンドは CONVST/CS 信号の立ち上がりエッジで実行されます。

### 6.5.3 出力データワード

デバイスからのデータ読み出しは、構成レジスタをプログラムすることにより、SCLK ピンの外部クロックまたは内部デバイスクロックに同期します。詳細については、「[データ転送プロトコル](#)」セクションを参照してください。

データ転送フレームでは、内部出力シフトレジスタの内容が SDO-x ピンでシフトアウトされます。任意のフレーム (F+1) の出力データは、フレーム F で発行されたコマンドおよび DATA\_VAL[2:0] ビットのステータスによって決まります。

- **DATAOUT\_CTL\_REG** レジスタの DATA\_VAL[2:0] ビットが 1xxb に設定されている場合、フレームの出力データワード (F+1) に固定データパターンが含まれます。