**ADS8320**

**Documents**

JAJS221E - MAY 2000 - REVISED DECEMBER 2016

# ADS8320 16ビット、高速、2.7V~5V microPowerサンプリング A/Dコンバータ

# 特長

- 100kHzのサンプリング・レート

- *micro*Power

- 100kHz、2.7Vで1.8mW

- 10kHz、2.7Vで0.3mW

- パワーダウン時: 3µA (最大値)

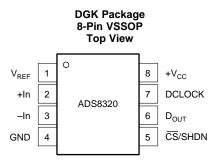

- 8ピンのVSSOPパッケージ

- ADS7816およびADS7822とピン互換

- シリアル(SPI™/SSI)インターフェイス

# 2 アプリケーション

- バッテリ動作のシステム

- リモート・データ収集

- 絶縁型データ収集

- 同時サンプリング、マルチチャネル・システム

- 産業用制御

- ロボティクス

- 振動解析

# 3 概要

ADS8320デバイスは、2.7V~5.25Vの電源電圧範囲で 動作が保証された、16ビット・サンプリングのアナログ/デジ タル(A/D)コンバータです。100kHzのフル・データ・レート で動作している時でも、必要な電力は非常に微少です。 それより低いデータ・レートでは、このデバイスの高速性に より、大半の時間をパワー・ダウン・モードとすることができ ます。平均消費電力は、10kHzのデータ・レート時で **100mW未満です。**

また、ADS8320は2V~5.25Vでの動作、同期シリアル (SPI/SSI互換)インターフェイス、差動入力も特長です。基 準電圧は、500mV~Vccの範囲で任意のレベルに設定 可能です。

非常に消費電力が低く、小型のため、ADS8320は携帯お よびバッテリ駆動のシステムに理想的です。また、リモー ト・データ収集モジュール、同時マルチチャネル・システ ム、絶縁型データ収集にも最適です。ADS8320は8ピン のVSSOPパッケージで供給されます。

# 製品情報(1)

| 型番      | パッケージ     | 本体サイズ(公称)     |

|---------|-----------|---------------|

| ADS8320 | VSSOP (8) | 3.00mm×3.00mm |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

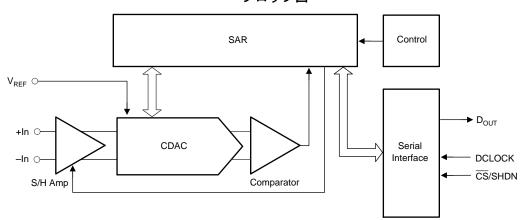

#### ブロック図

Copyright © 2016, Texas Instruments Incorporated

| 目 | 次 |

|---|---|

|   |   |

| 1 | 特長1                                                     |    | 7.4 Device Functional Modes    | 13              |

|---|---------------------------------------------------------|----|--------------------------------|-----------------|

| 2 | アプリケーション1                                               | 8  | Application and Implementation | 16              |

| 3 | 概要1                                                     |    | 8.1 Application Information    |                 |

| 4 | 改訂履歴2                                                   |    | 8.2 Typical Applications       | 16              |

| 5 | Pin Configuration and Functions                         | 9  | Power Supply Recommendations   | <mark>22</mark> |

| 6 | Specifications4                                         | 10 | Layout                         | <mark>22</mark> |

| • | 6.1 Absolute Maximum Ratings                            |    | 10.1 Layout Guidelines         | 22              |

|   | 6.2 ESD Ratings                                         |    | 10.2 Layout Example            | 23              |

|   | 6.3 Recommended Operating Conditions                    |    | 10.3 Power Dissipation         | 23              |

|   | 6.4 Thermal Information                                 | 11 | デバイスおよびドキュメントのサポート             | <mark>27</mark> |

|   | 6.5 Electrical Characteristics: V <sub>CC</sub> = 5 V   |    | 11.1 ドキュメントのサポート               | <mark>27</mark> |

|   | 6.6 Electrical Characteristics: V <sub>CC</sub> = 2.7 V |    | 11.2 ドキュメントの更新通知を受け取る方法        | <mark>27</mark> |

|   | 6.7 Typical Characteristics8                            |    | 11.3 コミュニティ・リソース               | <mark>27</mark> |

| 7 | Detailed Description 11                                 |    | 11.4 商標                        | <mark>27</mark> |

|   | 7.1 Overview                                            |    | 11.5 静電気放電に関する注意事項             | 27              |

|   | 7.2 Functional Block Diagram                            |    | 11.6 用語集                       | 27              |

|   | 7.3 Feature Description                                 | 12 | メカニカル、パッケージ、および注文情報            | 27              |

# 4 改訂履歴

# Revision D (March 2007) から Revision E に変更

Page

| • | 「ESD定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクション 追加 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Added Thermal Information table                                                                                                                  |

| • | Changed Application Circuits section To: Typical Connection Diagram                                                                              |

# 5 Pin Configuration and Functions

### **Pin Functions**

|          | PIN                |                     |                                                                                                                                                                                                                                                                                    |  |  |

|----------|--------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. NAME |                    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                        |  |  |

| 1        | $V_{REF}$          | Al                  | Reference input                                                                                                                                                                                                                                                                    |  |  |

| 2        | +In                | AI                  | Noninverting input                                                                                                                                                                                                                                                                 |  |  |

| 3        | -In                | AI                  | Inverting input: Connect to ground or to remote ground sense point.                                                                                                                                                                                                                |  |  |

| 4        | GND                | GND                 | und                                                                                                                                                                                                                                                                                |  |  |

| 5        | CS/SHDN            | DI                  | Chip select when LOW; Shutdown mode when HIGH.                                                                                                                                                                                                                                     |  |  |

| 6        | D <sub>OUT</sub>   | DO                  | The serial output data word is comprised of 16 bits of data. In operation the data is valid on the falling edge of $D_{\text{CLOCK}}$ . The second clock pulse after the falling edge of CS enables the serial output. After one null bit the data is valid for the next 16 edges. |  |  |

| 7        | D <sub>CLOCK</sub> | DI                  | Data clock synchronizes the serial data transfer and determines conversion speed.                                                                                                                                                                                                  |  |  |

| 8        | +V <sub>CC</sub>   | PWR                 | Power supply                                                                                                                                                                                                                                                                       |  |  |

<sup>(1)</sup> AI = Analog Input, DI = Digital Input, DO = Digital Output, GND = Ground, PWR = Power

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                        | MIN  | MAX            | UNIT |

|----------------------------------------|------|----------------|------|

| V <sub>CC</sub>                        |      | 6              | V    |

| Analog input                           | -0.3 | $V_{CC} + 0.3$ | V    |

| Logic input                            | -0.3 | 6              | °C   |

| External reference voltage             |      | 5.5            | V    |

| Input current to any pin except supply |      | ±10            | mA   |

| Case temperature                       |      | 100            | °C   |

| Junction temperature                   |      | 150            | °C   |

| Storage temperature, T <sub>stg</sub>  |      | 125            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| 1 5 1                                     | <b>3</b> (         |      |     |                       |      |  |

|-------------------------------------------|--------------------|------|-----|-----------------------|------|--|

|                                           |                    | MIN  | NOM | MAX                   | UNIT |  |

| Supply voltage V to CND                   | Low voltage levels | 2.7  |     | 3.3                   | V    |  |

| Supply voltage, V <sub>CC</sub> to GND    | 5-V logic levels   | 4.75 | 5   | 5.25                  | V    |  |

| Reference input voltage, V <sub>REF</sub> |                    | 0.5  |     | $V_{CC}$              | V    |  |

|                                           | -IN to GND         | -0.1 | 0   | 0.5                   |      |  |

| Analog input voltage                      | +IN to GND         | -0.1 |     | V <sub>CC</sub> + 0.1 | V    |  |

|                                           | +IN to - (-IN)     | 0    |     | $V_{REF}$             |      |  |

| Operating temperature, T <sub>A</sub>     |                    | -40  |     | 85                    | °C   |  |

# 6.4 Thermal Information

|                      |                                              | ADS8320     |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP) | UNIT |

|                      |                                              | 8 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 163.1       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 56.6        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 83.4        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 6.7         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 82          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | _           | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics: $V_{CC} = 5 V$

at  $-40^{\circ}$ C to 85°C,  $V_{REF} = 5$  V, -IN = GND,  $f_{SAMPLE} = 100$  kHz, and  $f_{CLK} = 24 \times f_{SAMPLE}$  (unless otherwise noted)

| PARAMETER                    | TEST COND                                                                     | ITIONS    | MIN   | TYP     | MAX                   | UNIT               |  |

|------------------------------|-------------------------------------------------------------------------------|-----------|-------|---------|-----------------------|--------------------|--|

| RESOLUTION                   | ·                                                                             |           |       |         |                       |                    |  |

| Resolution                   |                                                                               |           |       |         | 16                    | Bits               |  |

| ANALOG INPUT                 |                                                                               |           |       |         |                       |                    |  |

| Full-scale input span        | +ln – (–ln)                                                                   |           | 0     |         | VREF                  | V                  |  |

| AL 1                         | +In                                                                           |           | -0.1  |         | V <sub>CC</sub> + 0.1 | .,                 |  |

| Absolute input               | -In                                                                           |           | -0.1  |         | 1                     | V                  |  |

| Capacitance                  |                                                                               |           |       | 45      |                       | pF                 |  |

| Leakage current              |                                                                               |           |       | 1       |                       | nA                 |  |

| SYSTEM PERFORMANCE           |                                                                               |           |       |         |                       |                    |  |

| No missing and as            | ADS8320E                                                                      |           | 14    |         |                       | Dito               |  |

| No missing codes             | ADS8320EB                                                                     |           | 15    |         |                       | Bits               |  |

| Integral linearity array     | ADS8320E                                                                      |           |       | ±0.008% | ±0.018%               | רכם                |  |

| Integral linearity error     | ADS8320EB                                                                     |           |       | ±0.006% | ±0.012%               | FSR                |  |

| Office to a super            | ADS8320E                                                                      |           |       | ±1      | ±2                    | mV                 |  |

| Offset error                 | ADS8320EB                                                                     |           |       | ±0.5    | ±1                    | mv                 |  |

| Offset temperature drift     |                                                                               |           |       | ±3      |                       | μV/°C              |  |

| Cain anna                    | ADS8320E                                                                      |           |       |         | ±0.05%                | ECD                |  |

| Gain error                   | ADS8320EB                                                                     | ADS8320EB |       |         | ±0.024%               | FSR                |  |

| Gain error temperature drift |                                                                               |           |       | ±0.3    |                       | ppm/°C             |  |

| Noise                        |                                                                               |           |       | 20      |                       | μVrms              |  |

| Power-supply rejection ratio | 4.7 V < V <sub>CC</sub> < 5.25 V                                              |           |       | 3       |                       | LSB <sup>(1)</sup> |  |

| SAMPLING DYNAMICS            | •                                                                             |           |       |         |                       |                    |  |

| Conversion time              |                                                                               |           |       |         | 16                    | Clock<br>Cycles    |  |

| Acquisition time             |                                                                               |           | 4.5   |         |                       | Clock<br>Cycles    |  |

| Throughput rate              |                                                                               |           |       |         | 100                   | kHz                |  |

| Clock frequency              |                                                                               |           | 0.024 |         | 2.4                   | MHz                |  |

| DYNAMIC CHARACTERISTICS      |                                                                               |           |       |         |                       |                    |  |

| Total harmonic distortion    | $V_{IN} = 5 V_{P-P}$ at 10 kHz                                                | ADS8320E  |       | -84     |                       | dB                 |  |

| Total Harmonic distortion    | VIN = 3 VP-P at 10 KHZ                                                        | ADS8320EB |       | -86     |                       | GD.                |  |

| SINAD                        | $V_{IN} = 5 V_{P-P}$ at 10 kHz                                                | ADS8320E  |       | 82      |                       | dB                 |  |

| SINAD                        | VIN = 3 VP-P at 10 KHZ                                                        | ADS8320EB |       | 84      |                       | uБ                 |  |

| Spurious-free dynamic        | $V_{IN} = 5 V_{P-P}$ at 10 kHz                                                | ADS8320E  |       | 84      |                       | dB                 |  |

| Spurious-free dynamic        | VIN = 3 VP-P at 10 KHZ                                                        | ADS8320EB |       | 86      |                       | GD                 |  |

| SNR                          | ADS8320E                                                                      |           |       | 90      |                       | dB                 |  |

| SINC                         | ADS8320EB                                                                     |           |       | 92      |                       | uБ                 |  |

| REFERENCE INPUT              |                                                                               |           |       |         |                       |                    |  |

| Voltage                      |                                                                               |           | 0.5   |         | $V_{CC}$              | V                  |  |

| Resistance                   | $\overline{\text{CS}} = \text{GND},  \text{f}_{\text{SAMPLE}} = 0  \text{Hz}$ |           |       | 5       |                       |                    |  |

| เงองเงเสมเดีย                | $\overline{\text{CS}} = V_{\text{CC}}$                                        |           |       | 5       |                       | GΩ                 |  |

|                              |                                                                               |           |       | 40      | 80                    |                    |  |

| Current drain                | f <sub>SAMPLE</sub> = 0 Hz                                                    |           |       | 0.8     |                       | μΑ                 |  |

|                              | $\overline{\text{CS}} = V_{\text{CC}}$                                        |           |       | 0.1     | 3                     |                    |  |

<sup>(1)</sup> LSB means Least Significant Bit with VREF equal to 2.5 V, one LSB is 0.038 mV.

# Electrical Characteristics: V<sub>CC</sub> = 5 V (continued)

at -40°C to 85°C,  $V_{REF} = 5$  V, -IN = GND,  $f_{SAMPLE} = 100$  kHz, and  $f_{CLK} = 24 \times f_{SAMPLE}$  (unless otherwise noted)

| PA                             | RAMETER                  | TEST CONDITIONS                                | MIN  | TYP  | MAX                   | UNIT |  |

|--------------------------------|--------------------------|------------------------------------------------|------|------|-----------------------|------|--|

| DIGITAL INPU                   | JT/OUTPUT                |                                                | ,    |      | ,                     |      |  |

| Logic family                   |                          |                                                |      | CMOS |                       |      |  |

|                                | V <sub>IH</sub>          | $I_{IH} = 5 \mu A$                             | 3    |      | V <sub>CC</sub> + 0.3 |      |  |

| Lagia lavala                   | V <sub>IL</sub>          | $I_{IL} = 5 \mu A$                             | -0.3 |      | 0.8                   | V    |  |

| Logic levels                   | V <sub>OH</sub>          | $I_{OH} = -250 \mu A$                          | 4    |      |                       |      |  |

|                                | $V_{OL}$                 | I <sub>OL</sub> = 250 μA                       |      |      | 0.4                   |      |  |

| Data format                    | a format Straight Binary |                                                |      |      |                       |      |  |

| POWER SUPI                     | PLY REQUIREN             | IENTS                                          |      |      |                       |      |  |

| V <sub>CC</sub>                |                          | Specified performance                          | 4.75 |      | 5.25                  | V    |  |

| V <sub>CC</sub> <sup>(2)</sup> |                          |                                                | 2    |      | 5.25                  | V    |  |

| Quiescent current              |                          |                                                |      | 900  | 1700                  |      |  |

|                                |                          | f <sub>SAMPLE</sub> = 10 kHz <sup>(3)(4)</sup> |      | 200  |                       | μA   |  |

| Power dissipation              |                          |                                                |      | 4.5  | 8.5                   | mW   |  |

| Power down                     |                          | CS = V <sub>CC</sub>                           |      | 0.3  | 3                     | μA   |  |

- (2) See *Typical Characteristics* for more information.

(3) f<sub>CLK</sub> = 2.4 MHz, CS = V<sub>CC</sub> for 216 clock cycles out of every 240.

(4) See *Power Dissipation* for more information regarding lower sample rates.

# 6.6 Electrical Characteristics: V<sub>CC</sub> = 2.7 V

at -40°C to 85°C,  $V_{REF} = 5$  V, -IN = GND,  $f_{SAMPLE} = 100$  kHz, and  $f_{CLK} = 24 \times f_{SAMPLE}$  (unless otherwise noted)

| PARAMETER                    | TEST CONDITIONS                 | MIN      | TYP     | MAX                   | UNIT               |

|------------------------------|---------------------------------|----------|---------|-----------------------|--------------------|

| RESOLUTION                   |                                 | I .      |         |                       |                    |

| Resolution                   |                                 |          |         | 16                    | Bits               |

| ANALOG INPUT                 |                                 | <u>.</u> |         | <u> </u>              |                    |

| Full-scale input span        | +ln – (–ln)                     | 0        |         | VREF                  | V                  |

| Abaaluta isasut              | +In                             | -0.1     |         | V <sub>CC</sub> + 0.1 | V                  |

| Absolute input               | -In                             | -0.1     |         | 0.5                   | V                  |

| Capacitance                  |                                 |          | 45      |                       | pF                 |

| Leakage current              |                                 |          | 1       |                       | nA                 |

| SYSTEM PERFORMANCE           |                                 | <u>.</u> |         | <u>"</u>              |                    |

| No missing codes             | ADS8320E                        | 14       |         |                       | Dita               |

|                              | ADS8320EB                       | 15       |         |                       | Bits               |

| Internal Property and        | ADS8320E                        |          | ±0.008% | ±0.018%               | F0D                |

| Integral linearity error     | ADS8320EB                       |          | ±0.006% | ±0.012%               | FSR                |

| Officer                      | ADS8320E                        |          | ±1      | ±2                    | \/                 |

| Offset error                 | ADS8320EB                       |          | ±0.5    | ±1                    | mV                 |

| Offset temperature drift     |                                 |          | ±3      |                       | μV/°C              |

| 0-1                          | ADS8320E                        |          |         | ±0.05%                | FOD                |

| Gain error                   | ADS8320EB                       |          |         | ±0.024%               | FSR                |

| Gain error temperature drift |                                 |          | ±0.3    |                       | ppm/°C             |

| Noise                        |                                 |          | 20      |                       | ppm/°C             |

| Power-supply rejection ratio | 2.7 V < V <sub>CC</sub> < 3.3 V |          | 3       |                       | LSB <sup>(1)</sup> |

(1) LSB means Least Significant Bit with VREF equal to 2.5 V, one LSB is 0.038 mV.

# Electrical Characteristics: V<sub>CC</sub> = 2.7 V (continued)

at -40°C to 85°C,  $V_{REF} = 5 \text{ V}$ , -IN = GND,  $f_{SAMPLE} = 100 \text{ kHz}$ , and  $f_{CLK} = 24 \times f_{SAMPLE}$  (unless otherwise noted)

|                                | AMETER                                                                                                                                              | $V$ , $-IN = GND$ , $f_{SAMPLE} = 100$ TEST COND | MIN                                    | TYP   | MAX  | UNIT                  |                 |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|-------|------|-----------------------|-----------------|--|--|

| SAMPLING DY                    | NAMICS                                                                                                                                              |                                                  |                                        |       |      |                       |                 |  |  |

| Conversion tim                 | е                                                                                                                                                   |                                                  |                                        |       |      | 16                    | Clock<br>Cycles |  |  |

| Acquisition time               | )                                                                                                                                                   |                                                  |                                        | 4.5   |      |                       | Clock<br>Cycles |  |  |

| Throughput rate                | Э                                                                                                                                                   |                                                  |                                        |       |      | 100                   | kHz             |  |  |

| Clock frequenc                 | у                                                                                                                                                   |                                                  |                                        | 0.024 |      | 2.4                   | MHz             |  |  |

| DYNAMIC CHA                    | ARACTERISTIC                                                                                                                                        | CS                                               |                                        |       |      |                       |                 |  |  |

| Total harmonic distortion      |                                                                                                                                                     | $V_{IN} = 2.7 V_{P-P}$ at 1 kHz                  | ADS8320E                               |       | -86  |                       | dВ              |  |  |

|                                |                                                                                                                                                     | V <sub>IN</sub> = 2.7 Vp.p at 1 K112             | ADS8320EB                              |       | -88  |                       | dB              |  |  |

| SINAD                          |                                                                                                                                                     | V <sub>IN</sub> = 2.7 V <sub>P-P</sub> at 1 kHz  | ADS8320E                               |       | 84   |                       | dB              |  |  |

| SINAD                          | phput rate frequency  MIC CHARACTERISTIC parmonic distortion  us-free dynamic  RENCE INPUT e ance  at drain  AL INPUT/OUTPUT  Family  VIL  VOH  VOL | VIN = 2.7 VP-P at 1 K112                         | ADS8320EB                              |       | 86   |                       | uБ              |  |  |

| Spurious-free dynamic          |                                                                                                                                                     | \/ - 2.7.\/ ot 1.kHz                             | ADS8320E                               |       | 86   |                       | ٩D              |  |  |

|                                |                                                                                                                                                     | $V_{IN} = 2.7 V_{P-P}$ at 1 kHz                  | ADS8320EB                              |       | 88   |                       | dB              |  |  |

| SNR                            |                                                                                                                                                     | ADS8320E                                         | ADS8320E                               |       | 88   |                       | -10             |  |  |

| SINK                           |                                                                                                                                                     | ADS8320EB                                        | ADS8320EB                              |       |      |                       | dB              |  |  |

| REFERENCE I                    | NPUT                                                                                                                                                |                                                  |                                        |       |      | ·                     |                 |  |  |

| Voltage                        |                                                                                                                                                     |                                                  |                                        | 0.5   |      | $V_{CC}$              | V               |  |  |

| Resistance                     |                                                                                                                                                     | CS = GND, f <sub>SAMPLE</sub> = 0 Hz             | CS = GND, f <sub>SAMPLE</sub> = 0 Hz   |       |      |                       |                 |  |  |

|                                |                                                                                                                                                     | CS = V <sub>CC</sub>                             |                                        |       |      |                       | GΩ              |  |  |

| Current drain                  |                                                                                                                                                     |                                                  |                                        |       | 20   | 50                    |                 |  |  |

|                                |                                                                                                                                                     | $\overline{\text{CS}} = V_{\text{CC}}$           | CS = V <sub>CC</sub>                   |       |      | 3                     | μA              |  |  |

| DIGITAL INPU                   | T/OUTPUT                                                                                                                                            |                                                  |                                        | 1     |      |                       |                 |  |  |

| Logic Family                   |                                                                                                                                                     |                                                  |                                        |       | CMOS |                       |                 |  |  |

|                                | V <sub>IH</sub>                                                                                                                                     | I <sub>IH</sub> = 5 μA                           |                                        | 2     |      | V <sub>CC</sub> + 0.3 |                 |  |  |

|                                | V <sub>IL</sub>                                                                                                                                     | I <sub>IL</sub> = 5 μA                           |                                        | -0.3  |      | 0.8                   |                 |  |  |

| Logic levels                   |                                                                                                                                                     | I <sub>OH</sub> = -250 μA                        |                                        |       |      |                       | V               |  |  |

|                                |                                                                                                                                                     | I <sub>OL</sub> = 250 μA                         |                                        |       |      | 0.4                   |                 |  |  |

| Data format                    |                                                                                                                                                     |                                                  | Straight Binary                        |       |      |                       |                 |  |  |

| POWER SUPP                     | LY REQUIREM                                                                                                                                         | MENTS                                            |                                        |       |      | •                     |                 |  |  |

| V <sub>CC</sub>                |                                                                                                                                                     | Specified performance                            |                                        | 2.7   |      | 3.3                   | V               |  |  |

| V <sub>CC</sub> <sup>(2)</sup> |                                                                                                                                                     |                                                  | 2                                      |       | 5.25 | .,                    |                 |  |  |

|                                |                                                                                                                                                     | See <sup>(3)</sup>                               | See <sup>(3)</sup> 2                   |       |      | 2.7                   | V               |  |  |

| Quiescent current              |                                                                                                                                                     |                                                  |                                        |       | 650  | 1300                  | ^               |  |  |

|                                |                                                                                                                                                     | $f_{SAMPLE} = 10 \text{ kHz}^{(4)(5)}$           | $f_{SAMPLE} = 10 \text{ kHz}^{(4)(5)}$ |       |      |                       | μA              |  |  |

| Power dissipati                | on                                                                                                                                                  |                                                  |                                        |       | 1.8  | 3.8                   | mW              |  |  |

| Power down                     |                                                                                                                                                     | $\overline{\text{CS}} = V_{\text{CC}}$           |                                        |       | 0.3  | 3                     | μA              |  |  |

<sup>(2)</sup> See *Typical Characteristics* for more information.

The maximum clock rate of the ADS8320 is less than 2.4 MHz in this power supply range.

$f_{CLK}$  = 2.4 MHz, CS =  $V_{CC}$  for 216 clock cycles out of every 240. See *Power Dissipation* for more information regarding lower sample rates.

# TEXAS INSTRUMENTS

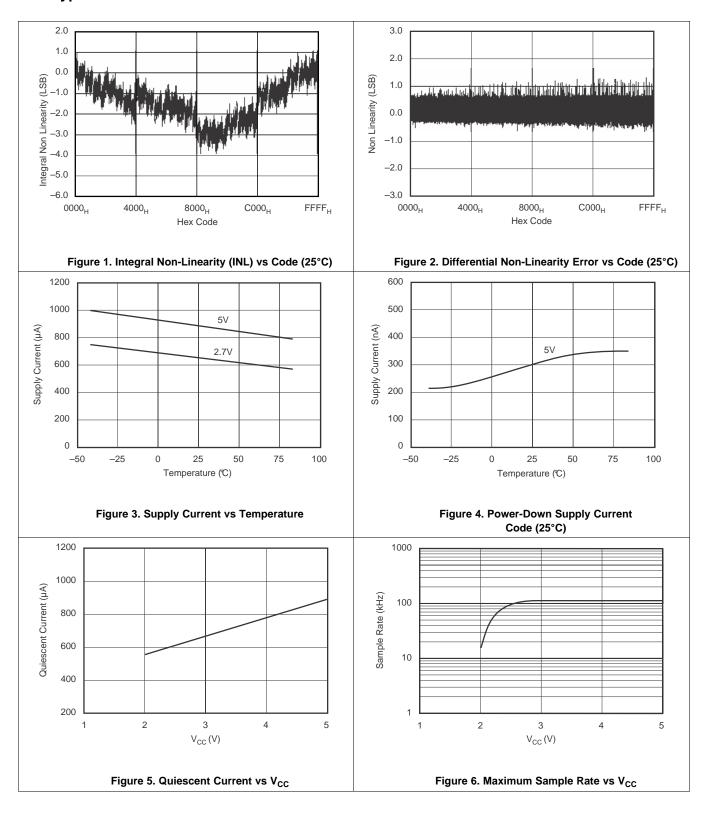

# 6.7 Typical Characteristics

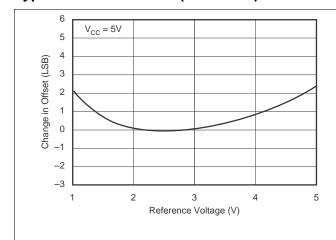

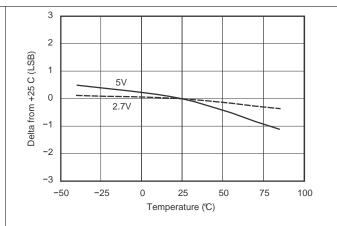

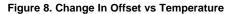

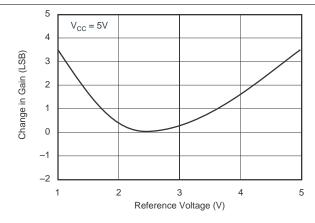

# **Typical Characteristics (continued)**

Figure 7. Change In Offset vs Reference Voltage

Figure 9. Change In Gain Error vs Reference Voltage

Figure 10. Change In Gain Error vs Temperature

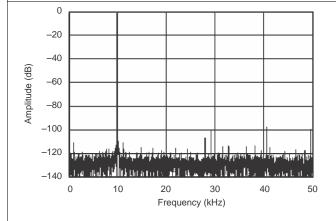

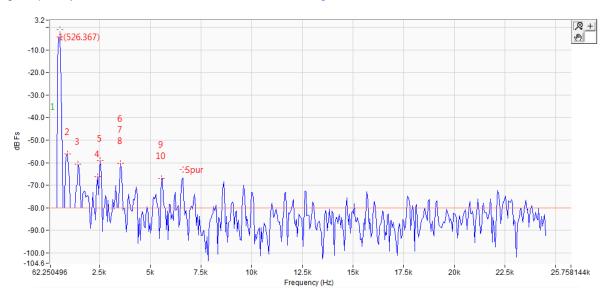

Figure 11. Frequency Spectrum (8192 Point FFT, FIN = 10.120 kHz, -0.3 dB)

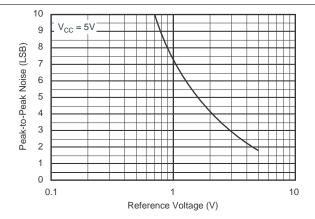

Figure 12. Peak-to-Peak Noise vs Reference Voltage

# **ISTRUMENTS**

# **Typical Characteristics (continued)**

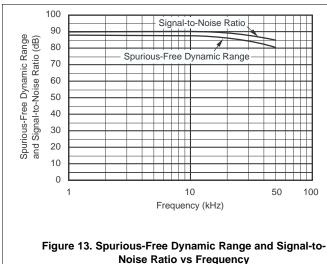

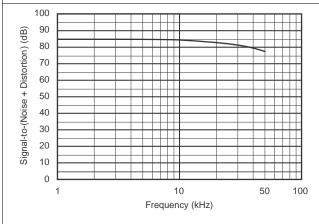

Noise Ratio vs Frequency

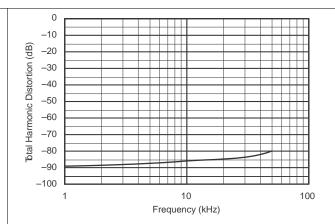

Figure 14. Total Harmonic Distortion vs Frequency

Figure 15. Signal-to-(Noise + Distortion) vs Frequency

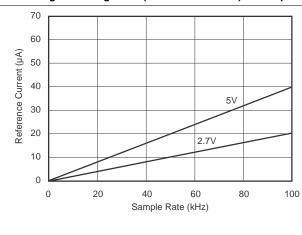

Figure 17. Reference Current vs Sample Rate

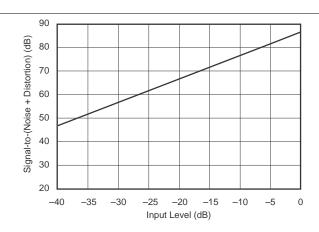

Figure 16. Signal-to-(Noise + Distortion) vs Input Level

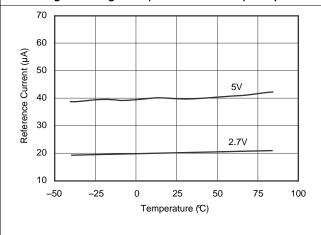

Figure 18. Reference Current vs Temperature

# 7 Detailed Description

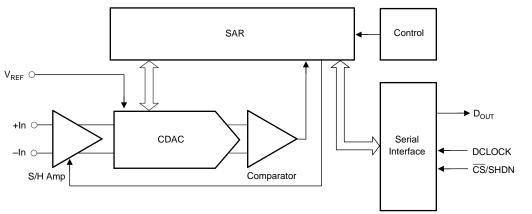

#### 7.1 Overview

The ADS8320 device is a classic successive approximation register (SAR) analog-to-digital (A/D) converter. The architecture is based on capacitive redistribution, which inherently includes a sample and hold function. The converter is fabricated on a  $0.6\mu m$  CMOS process. The architecture and process allow the ADS8320 to acquire and convert an analog signal at up to 100,000 conversions per second while consuming less than 4.5 mW from  $+V_{CC}$ .

The ADS8320 requires an external reference, an external clock, and a single power source ( $V_{CC}$ ). The external reference can be any voltage between 500 mV and  $V_{CC}$ . The value of the reference voltage directly sets the range of the analog input. The reference input current depends on the conversion rate of the ADS8320.

The external clock can vary between 24 kHz (1-kHz throughput) and 2.4 MHz (100-kHz throughput). The duty cycle of the clock is essentially unimportant, as long as the minimum high and low times are at least 200 ns ( $V_{CC} = 2.7 \text{ V}$  or greater). The minimum clock frequency is set by the leakage on the capacitors internal to the ADS8320.

The analog input is provided to two input pins: +In and -In. When a conversion is initiated, the differential input on these pins is sampled on the internal capacitor array. While a conversion is in progress, both inputs are disconnected from any internal function.

The digital result of the conversion is clocked out by the  $D_{CLOCK}$  input and is provided serially, most significant bit first, on the  $D_{OUT}$  pin. The digital data that is provided on the  $D_{OUT}$  pin is for the conversion currently in progress—there is no pipeline delay. It is possible to continue to clock the ADS8320 after the conversion is complete and to obtain the serial data least significant bit first. See *Device Functional Modes* for more information.

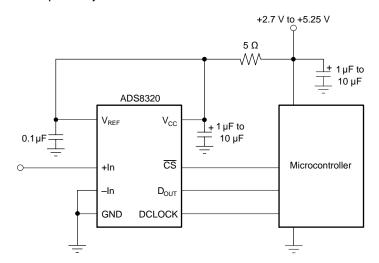

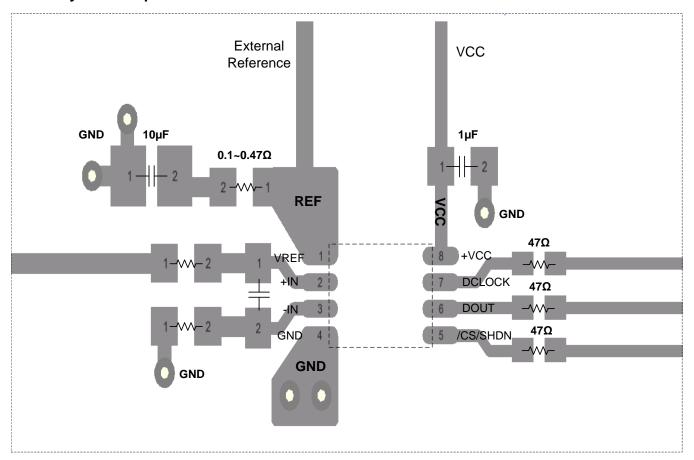

### 7.1.1 Typical Connection Diagram

Figure 19 shows a basic data acquisition system. The ADS8320 input range is 0 V to  $V_{CC}$ , as the reference input is connected directly to the power supply. The 5- $\Omega$  resistor and 1- $\mu$ F to 10- $\mu$ F capacitor filter the microcontroller *noise* on the supply, as well as any high-frequency noise from the supply itself. The exact values must be picked such that the filter provides adequate rejection of the noise.

Copyright © 2016, Texas Instruments Incorporated

Figure 19. Typical Connection Diagram With ADS8320

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 7.3 Feature Description

#### 7.3.1 Analog Input

The +In and -In input pins allow for a differential input signal. Unlike some converters of this type, the -In input is not resampled later in the conversion cycle. When the converter goes into the hold mode, the voltage difference between +In and -In is captured on the internal capacitor array.

The range of the –In input is limited to –0.1 V to 1 V (–0.1 V to 0.5 V when using a 2.7-V supply). Because of this, the differential input can be used to reject only small signals that are common to both inputs. Thus, the –In input is best used to sense a remote signal ground that may move slightly with respect to the local ground potential.

The input current on the analog inputs depends on a number of factors: sample rate, input voltage, source impedance, and power-down mode. Essentially, the current into the ADS8320 charges the internal capacitor array during the sample period. After this capacitance has been fully charged, there is no further input current. The source of the analog input voltage must be able to charge the input capacitance (45 pF) to a 16-bit settling level within 4.5 clock cycles. When the converter goes into the hold mode or while it is in the power down mode, the input impedance is greater than 1  $G\Omega$ .

Care must be taken regarding the absolute analog input voltage. To maintain the linearity of the converter, the -In input must not drop below GND - 100 mV or exceed GND + 1 V. The +In input must always remain within the range of GND - 100 mV to  $V_{CC}$  + 100 mV. Outside of these ranges, the converter linearity may not meet specifications. To minimize noise, low bandwidth input signals with lowpass filters must be used.

#### 7.3.2 Reference Input

The external reference sets the analog input range. The ADS8320 operates with a reference in the range of 500 mV to  $V_{CC}$ . There are several important implications of this.

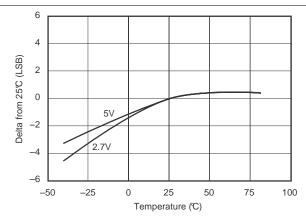

As the reference voltage is reduced, the analog voltage weight of each digital output code is reduced. This is often referred to as the Least Significant Bit (LSB) size and is equal to the reference voltage divided by 65,536. This means that any offset or gain error inherent in the A/D converter appears to increase, in terms of LSB size, as the reference voltage is reduced.

The noise inherent in the converter also appears to increase with lower LSB size. With a 5-V reference, the internal noise of the converter typically contributes only 1.5-LSB peak-to-peak of potential error to the output code. When the external reference is 500 mV, the potential error contribution from the internal noise is 10 times larger (15 LSBs). The errors due to the internal noise are gaussian in nature and can be reduced by averaging consecutive conversion results.

For more information regarding noise, see Figure 12. Note that the Effective Number of Bits (ENOB) figure is calculated based on the converter's signal-to-(noise + distortion) ratio with a 1-kHz, 0-dB input signal. SINAD is related to ENOB as shown in Equation 1.

# **Feature Description (continued)**

SINAD =

$$6.02 \times ENOB + 1.76$$

(1)

With lower reference voltages, extra care must be taken to provide a clean layout including adequate bypassing, a clean power supply, a low-noise reference, and a low-noise input signal. Because the LSB size is lower, the converter is also more sensitive to external sources of error such as nearby digital signals and electromagnetic interference.

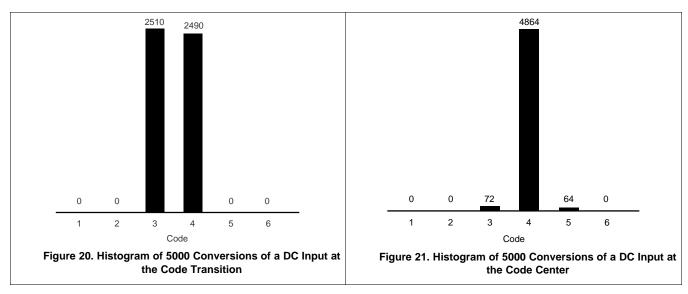

#### 7.3.3 Noise

The noise floor of the ADS8320 itself is extremely low, as can be seen from Figure 20 and Figure 21, and is much lower than competing A/D converters. It was tested by applying a low-noise DC input and a 5-V reference to the ADS8320 and initiating 5000 conversions. The digital output of the A/D converter varies in output code due to the internal noise of the ADS8320. This is true for all 16-bit SAR-type A/D converters. Using a histogram to plot the output codes, the distribution must appear bell-shaped with the peak of the bell curve representing the nominal code for the input value. The  $\pm 1\sigma$ ,  $\pm 2\sigma$ , and  $\pm 3\sigma$  distributions represents the 68.3%, 95.5%, and 99.7%, respectively, of all codes. The transition noise can be calculated by dividing the number of codes measured by 6 and this yields the  $\pm 3\sigma$  distribution or 99.7% of all codes. Statistically, up to 3 codes could fall outside the distribution when executing 1000 conversions. The ADS8320, with < 3 output codes for the  $\pm 3\sigma$  distribution, yields a < $\pm 0.5$ -LSB transition noise. Remember, to achieve this low-noise performance, the peak-to-peak noise of the input signal and reference must be < 50  $\mu$ V.

# 7.3.4 Averaging

The noise of the A/D converter can be compensated by averaging the digital codes. By averaging conversion results, transition noise is reduced by a factor of  $1/\sqrt{n}$ , where n is the number of averages. For example, averaging four conversion results reduces the transition noise by 1/2 to  $\pm 0.25$  LSBs. Averaging must only be used for input signals with frequencies near DC.

For AC signals, a digital filter can be used to low-pass filter and decimate the output codes. This works in a similar manner to averaging; for every decimation by 2, the signal-to-noise ratio improves 3 dB.

#### 7.4 Device Functional Modes

#### 7.4.1 Signal Levels

The digital inputs of the ADS8320 can accommodate logic levels up to 5.5 V regardless of the value of  $V_{CC}$ . Thus, the ADS8320 can be powered at 3 V and still accept inputs from logic powered at 5 V.

The CMOS digital output ( $D_{OUT}$ ) swings 0 V to  $V_{CC}$ . If  $V_{CC}$  is 3 V and this output is connected to a 5-V CMOS logic input, then that IC may require more supply current than normal and may have a slightly longer propagation delay.

# **Device Functional Modes (continued)**

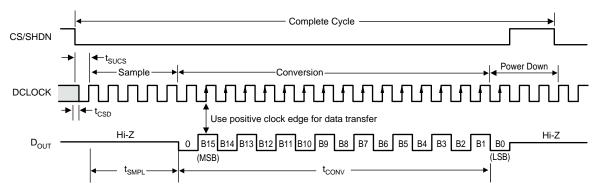

#### 7.4.2 Serial Interface

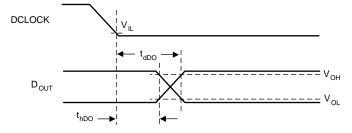

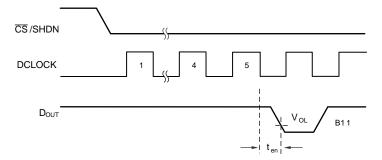

The ADS8320 communicates with microprocessors and other digital systems through a synchronous 3-wire serial interface, as shown in Figure 3 and Table 1. The  $D_{CLOCK}$  signal synchronizes the data transfer with each bit being transmitted on the falling edge of  $D_{CLOCK}$ . Most receiving systems capture the bitstream on the rising edge of  $D_{CLOCK}$ . However, if the minimum hold time for  $D_{OUT}$  is acceptable, the system can use the falling edge of  $D_{CLOCK}$  to capture each bit.

A falling CS signal initiates the conversion and data transfer. The first 4.5 to 5.0 clock periods of the conversion cycle are used to sample the input signal. After the fifth falling  $D_{CLOCK}$  edge,  $D_{OUT}$  is enabled and outputs a LOW value for one clock period. For the next 16  $D_{CLOCK}$  periods,  $D_{OUT}$  outputs the conversion result, most significant bit first. After the least significant bit (B0) has been output, subsequent clocks repeat the output data but in a least significant bit first format.

After the most significant bit (B15) has been repeated,  $D_{OUT}$  tri-states. Subsequent clocks has no effect on the converter. A new conversion is initiated only when  $\overline{CS}$  has been taken HIGH and returned LOW.

Table 1. Timing Specifications (V<sub>CC</sub> = 2.7 V and Above, -40°C to 85°C)

|                   |                                                                  | MIN | TYP | MAX | UNIT            |

|-------------------|------------------------------------------------------------------|-----|-----|-----|-----------------|

| t <sub>SMPL</sub> | Analog input sample time                                         | 4.5 |     | 5   | Clock<br>Cycles |

| t <sub>CONV</sub> | Conversion time                                                  |     | 16  |     | Clock<br>Cycles |

| t <sub>CYC</sub>  | Throughput rate                                                  |     |     | 100 | kHz             |

| t <sub>CSD</sub>  | CS falling to D <sub>CLOCK</sub> LOW                             |     |     | 0   | ns              |

| t <sub>SUCS</sub> | CS falling to D <sub>CLOCK</sub> rising                          | 20  |     |     | ns              |

| $t_{hDO}$         | D <sub>CLOCK</sub> falling to current D <sub>OUT</sub> not valid | 5   | 15  |     | ns              |

| $t_{dDO}$         | D <sub>CLOCK</sub> falling to next D <sub>OUT</sub> not valid    |     | 30  | 50  | ns              |

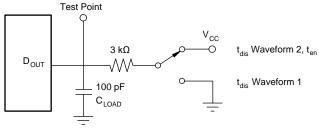

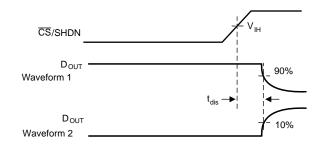

| t <sub>dis</sub>  | CS rising to D <sub>OUT</sub> Tri-state                          |     | 70  | 100 | ns              |

| t <sub>en</sub>   | D <sub>CLOCK</sub> falling to D <sub>OUT</sub>                   |     | 20  | 50  | ns              |

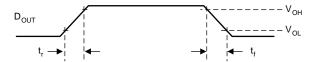

| t <sub>f</sub>    | D <sub>OUT</sub> fall time                                       |     | 5   | 25  | ns              |

| t <sub>r</sub>    | D <sub>OUT</sub> rise time                                       |     | 7   | 25  | ns              |

### 7.4.3 Data Format

The output data from the ADS8320 is in straight binary format, as shown in Table 2. This table represents the ideal output code for the given input voltage and does not include the effects of offset, gain error, or noise.

**Table 2. Ideal Input Voltages**

| DESCRIPTION                 | ANALOG VALUE                |

|-----------------------------|-----------------------------|

| Full-scale range            | $V_{REF}$                   |

| Least significant bit (LSB) | V <sub>REF</sub> /65,536    |

| Full-scale                  | V <sub>REF</sub> – 1 LSB    |

| Midscale                    | V <sub>REF</sub> /2         |

| Midscale – 1 LSB            | V <sub>REF</sub> /2 – 1 LSB |

| Zero                        | 0 V                         |

**Table 3. Ideal Output Codes**

| DIGITAL OUTPUT<br>STRAIGHT BINARY |          |  |  |  |  |

|-----------------------------------|----------|--|--|--|--|

| BINARY CODE                       | HEX CODE |  |  |  |  |

| 1111 1111 1111 1111               | FFF      |  |  |  |  |

| 1000 0000 0000 0000               | 8000     |  |  |  |  |

| 0111 1111 1111 1111               | 7FFF     |  |  |  |  |

| 0000 0000 0000 0000               | 0000     |  |  |  |  |

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

To maximize the performance of data acquisition (DAQ) system based on a high-precision, successive approximation register (SAR), and analog-to-digital converter (ADC), the input driver and the reference driver circuits must be designed properly and must be optimized. This section introduces some application circuits designed using the ADS8320, and the detailed information for the some general principles designing these circuits can be referred to the related documentation.

# 8.2 Typical Applications

#### 8.2.1 Universal Sensor IF SAR Booster Pack

# BoosterPack interface 000000000 **000000000** TIDA-00564 3.3 V U1 REF5030 SPI CLK 3.3 V 33V U3 Sensor ≥ 10M LMP7716 interface ADS8320 1.57 V SPI CS SPI MISO 0000000000 BoosterPack interface

Figure 22. Block Diagram for Universal Sensor IF SAR Booster Pack

16

# **Typical Applications (continued)**

#### 8.2.1.1 Design Requirements

This TI Design is a universal sensor IF based on a successive approximation register (SAR) ADC built in a Booster Pack form factor to be easily connected to TI LaunchPad for development and testing. The analog front end (AFE) of the board has been designed for sensors with low output voltage range and high output impedance such as thermopiles, infrared (IR) thermometers, thermocouple amplifiers, pH electrode buffers, piezoelectric accelerometers, and many others.

This application circuit for ADS8320 is designed to achieve the key specifications:

- 16-bit 100 KHz

- · Low-input referred noise and low-input bias (100 fA)

- Ideal choice for high-impedance output sensors

#### 8.2.1.2 Detailed Design Procedure

The ADS8320 was selected in this design because it best matches the design's input requirements and high performance. The maximum throughput rate of the ADS8320 is 100 ksps, the resolution is equal to 16 bits, and the input range of the ADS8320 is equal to the reference voltage supplied to the converter. In this design, the reference voltage is equal to 3 V. The REF5030 features low noise, very low drift, and high initial accuracy for high-performance data converters. The output of the REF5030 is 3 V, which fixes the voltage range of the ADC and can provide a stable reference voltage to maintain the accuracy.

Because the system is targeted for high-impedance output sensors, CMOS or JFET input amplifiers are preferable. The LMP7716 is a CMOS amplifier with low-input referred noise and low-input bias current, which make it an ideal choice for sensor interfaces such as thermopiles, IR thermometers, thermocouple amplifiers, and pH electrode buffers. To ensure the amplifier settles in enough time for the ADC to complete the signal acquisition. The gain bandwidth product of the amplifier is high enough to make sure that the input signal bandwidth is accounted for, and the amplifier is stable with the filter load. The amplifier has a fast slew rate to charge the filter changes and to quickly react to changes of the input.

A low-pass filter must be placed between the input of the ADC and input amplifier. Choosing the capacitor and resistor values play an important role to have a good AFE design. CFLT serves two purposes. Firstly, this capacitor stores energy to charge the ADC internal sampling capacitor. Secondly, CFLT provides a place for the internal capacitor's charge to go. Due to the storage capabilities of CFLT, this design guide sometimes refers to this capacitor as the *flywheel* capacitor. CFLT has this alternative name because, like a flywheel, it stores energy for the acquisition time of the ADC. Another name used to describe CFLT is *charge reservoir*. This TI design has a CFLT equal to 1 nF. This capacitor must be a high-quality capacitor with low voltage and frequency coefficients. The recommended capacitor type is COG. As a check, make sure the filter capacitor value chosen is at least 20 times the internal capacitor value of ADC. In this case, the value is more than 20 times the size.

The external  $R_{FLT} \mid C_{FLT}$  in the low-pass filter must settle within the ADC acquisition time. As a rule of thumb, set the external  $R_{FLT} \mid C_{FLT}$  settling time constant a bit faster than ideal (for example, 60%) to allow a margin for error of the op-amp load transient and the small signal settling time. TI design has an RFLT equal to 100  $\Omega$ . The detailed discussion and calculation can be found in *Universal Sensor IF SAR BoosterPack* (TIDUAI7).

# **Typical Applications (continued)**

# 8.2.1.3 Application Curves

#### 8.2.1.3.1 Static Test (DC)

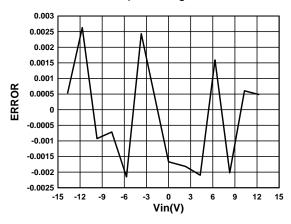

Figure 23 shows the error, which is the measured output voltage minus the ideal output voltage.

Figure 23. Error (Measured V<sub>OUT</sub> Minus Ideal V<sub>OUT</sub>) vs Input Voltage

#### 8.2.1.3.2 Dynamic Test (AC)

For the dynamic test, sine wave is applied at the input of the board with fixed amplitude equal to -1 dBFS and a varying frequency of 0.5 kHz, 1 kHz, 5 kHz, and 10 kHz. Figure 24 shows the test result for 0.5 kHz.

Figure 24. FFT at 500 Hz (Input Signal -1 dBFS)

For step-by-step design procedure, circuit schematics, bill of materials, printed circuit board (PCB) files, simulation results, and test results, refer to TI Precision Design TIDA-00564, *Universal Sensor IF SAR Booster Pack Reference Design*.

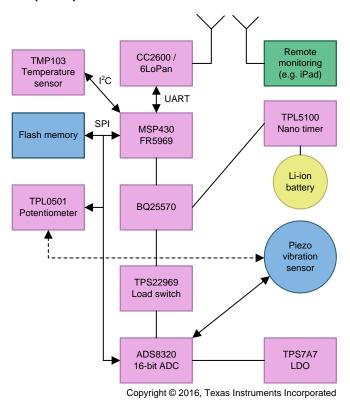

#### 8.2.2 Wireless Motor Monitor (WMM)

Figure 25. System Block Diagram for Wireless Motor Monitor (WMM)

#### 8.2.2.1 Design Requirements

This application circuit for ADS8320 is designed to achieve the key specifications:

- 16-bit 100 KHz

- 4-K FFT for vibration spectral

- Optimized for ultra-low sleep-mode current: I<sub>Q</sub> < 45-nA (typical; BQ-harvester in smart mode)</li>

#### 8.2.2.2 Detailed Design Procedure

This TI Design is inspired by the need to monitor the health of motors and machines to accurately predict and schedule maintenance (or replacement) while minimizing cost and down time during industrial production.

This design uses a Piezo vibration sensor to monitor machine vibrations, and a 16-bit precision SAR ADC, ADS8320, is connected to the Piezo shock sensor signal chain for signal acquisition. Because Piezo sensors have high-impedance output nodes, so it's important to carefully design the analog front-end (AFE) circuitry to reduce the noise and increase the sensitivity of the system, also drive ADS8320 and settle the signal properly during the acquisition time.

# 8.2.2.3 Application Curves

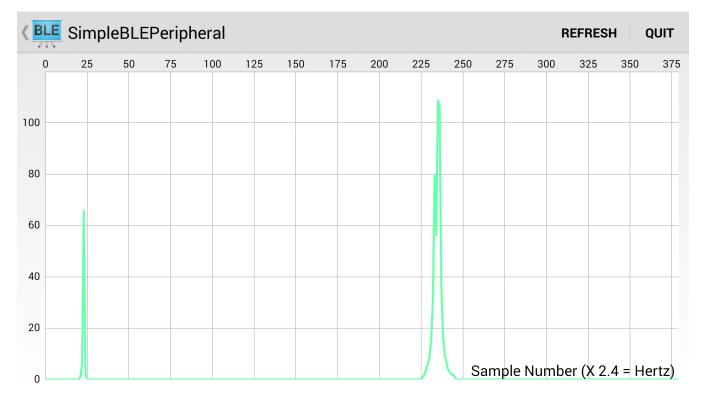

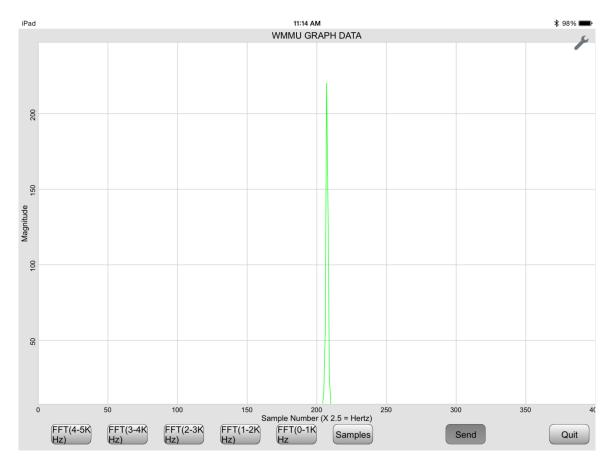

When testing the system with a portable speaker, the test result graph with 4-K FFT is shown in Figure 26.

Figure 26. Android Screen Shot of FFT at 600-Hz Excitation With Portable Speaker

When testing the system with a shaker calibrated with a accelerometer, the ADC is used and the AFE gain is set to 11, then configure the software to output 0.1-g of vibration at 500 KHz (or 1.5 KHz, and 2.5 KHz) as depicted in Figure 27.

Figure 27. BLE Received FFT at 500-Hz 0.1-g Excitation (X 2.4 = Hertz)

For step-by-step design procedure, circuit schematics, bill of materials, printed circuit board (PCB) files, simulation results, and test results, refer to TI Precision Design TIDM-WLMOTORMONITOR, *Wireless Motor Monitor Reference Design*.

# 9 Power Supply Recommendations

The ADS8320 is designed to operate using a simple power supply voltage from 2.0 V to 5.25 V, but the specifications are ensured over a 2.7-V to 5.25-V supply range. This supply must be well regulated and bypassed. A ceramic decoupling capacitor must be placed on the supply pin as close as possible to the ADS8320 package. In addition, a 1- $\mu$ F to 10- $\mu$ F capacitor and a 5- $\Omega$  or 10- $\Omega$  series resistor may be used to low-pass filter a noisy supply.

# 10 Layout

#### 10.1 Layout Guidelines

For optimum performance, care must be taken with the physical layout of the ADS8320 circuitry. This is particularly true if the reference voltage is low and/or the conversion rate is high. At a 100-kHz conversion rate, the ADS8320 makes a bit decision every 416 ns. That is, for each subsequent bit decision, the digital output must be updated with the results of the last bit decision, the capacitor array appropriately switched and charged, and the input to the comparator settled to a 16-bit level all within one clock cycle.

TI recommends following these layout guidelines:

- A printed-circuit board (PCB) with at least four layers to keep all critical components on the top layer.

- Analog input signals and the reference input signals must be kept away from noise sources. Crossing digital

lines with the analog signal path must be avoided. The analog input and the reference signals are routed on

to the left side of the board and the digital connections are routed on the right side of the device.

- Due to the dynamic currents that occur during conversion and data transfer, the supply pin (+V<sub>CC</sub>) must have a decoupling capacitor that keeps the supply voltage stable. A 1-μF ceramic decoupling capacitor is recommended for the supply pin.

- A layout that interconnects the converter and accompanying capacitors with the low inductance path is critical for achieving optimal performance. Using 15-mil vias to interconnect components to a solid analog ground plane at the subsequent inner layer minimizes stray inductance. Avoid placing vias between the supply pin and the decoupling capacitor. Any inductance between the supply capacitor and the supply pin of the converter must be kept to less than 5 nH by placing the capacitor within 0.2 inches from the supply or input pins of the ADS8320 and by using 20-mil traces.

- Dynamic currents are also present at the REF pin during the conversion phase. Therefore, good decoupling is

critical to achieve optimal performance. The inductance between the reference capacitor and the REF pin

must be kept to less than 2 nH by placing the capacitor within 0.1 inches from the REFIN pin and by using

20-mil traces.

- A single 10-μF, X7R-grade, 0805-size ceramic capacitor with at least a 10-V rating for good performance over temperature range.

- A small, 0.1-Ω to 0.47-Ω, 0603-size resistor placed in series with the reference capacitor keeps the overall impedance low and constant, especially at very high frequencies.

- Avoid using additional lower value capacitors because the interactions between multiple capacitors can affect the ADC performance at higher sampling rates.

- Place the RC filters immediately next to the input pins. Among surface-mount capacitors, COG (NPO) ceramic capacitors provide the best capacitance precision. The type of dielectric used in COG (NPO) ceramic capacitors provides the most stable electrical properties over voltage, frequency, and temperature changes.

- The GND pin on the ADS8320 must be placed on a clean ground plane. In many cases, this is the analog ground.

# 10.2 Layout Example

Figure 28. Layout Example

# 10.3 Power Dissipation

The architecture of the converter, the semiconductor fabrication process, and a careful design allow the ADS8320 to convert at up to a 100kHz rate while requiring very little power. Still, for the absolute lowest power dissipation, there are several things to keep in mind.

The power dissipation of the ADS8320 scales directly with conversion rate. Therefore, the first step to achieving the lowest power dissipation is to find the lowest conversion rate that satisfies the requirements of the system.

In addition, the ADS8320 is in power-down mode under two conditions: when the conversion is complete and whenever  $\overline{\text{CS}}$  is HIGH (as shown in Figure 29). Ideally, each conversion must occur as quickly as possible, preferably at a 2.4-MHz clock rate. This way, the converter spends the longest possible time in the power-down mode. This is very important as the converter not only uses power on each  $D_{\text{CLOCK}}$  transition (as is typical for digital CMOS components), but also uses some current for the analog circuitry, such as the comparator. The analog section dissipates power continuously, until the power-down mode is entered.

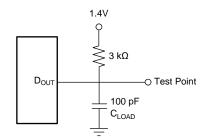

The following timing diagrams and test circuits pertain to the parameters in Table 1.

# **Power Dissipation (continued)**

Minimum 22 clock cycles required for 16-bit conversion. Shown are 24 clock cycles.

If  $\overline{\text{CS}}$  remains LOW at the end of conversion, a new datastream with LSB-first is shifted out again.

Figure 29. ADS8320 Basic Timing Diagrams

Copyright © 2016, Texas Instruments Incorporated

Figure 30. Load Circuit for  $t_{dDO}$ ,  $t_r$ , and  $t_f$

Figure 31. Voltage Waveforms for  $D_{OUT}$  Rise and Fall Times,  $t_r$ ,  $t_f$

Figure 32. Voltage Waveforms for D<sub>OUT</sub> Delay Times, t<sub>dDO</sub>

# **Power Dissipation (continued)**

Copyright © 2016, Texas Instruments Incorporated

Waveform 1 is for an output with internal conditions such that the output is HIGH unless disabled by the output control. (2) Waveform 2 is for an output with internal conditions such that the output is LOW unless disabled by the output control.

Figure 33. Load Circuit for  $t_{dDO}$ ,  $t_r$ , and  $t_f$  Table 1

Figure 34. Voltage Waveforms for t<sub>dis</sub>

Figure 35. Voltage Waveforms for ten

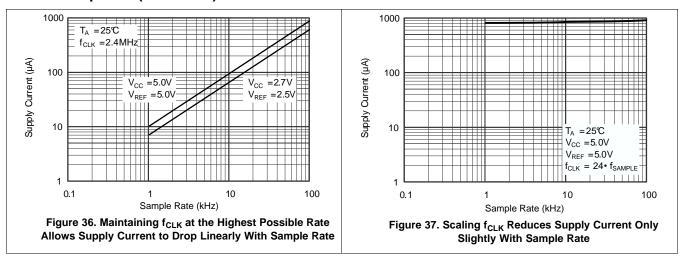

Figure 36 shows the current consumption of the ADS8320 versus sample rate. For this graph, the converter is clocked at 2.4 MHz regardless of the sample rate;  $\overline{\text{CS}}$  is HIGH for the remaining sample period. Figure 37 also shows current consumption versus sample rate. However, in this case, the  $D_{\text{CLOCK}}$  period is 1/24th of the sample period— $\overline{\text{CS}}$  is HIGH for one  $D_{\text{CLOCK}}$  cycle out of every 16.

# TEXAS INSTRUMENTS

#### **Power Dissipation (continued)**

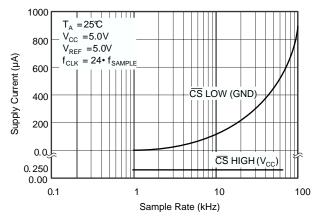

There is an important distinction between the power-down mode that is entered after a conversion is complete and the full power-down mode which is enabled when CS is HIGH. CS LOW shuts down only the analog section. The digital section is completely shut down only when  $\overline{\text{CS}}$  is HIGH. Thus, if  $\overline{\text{CS}}$  is left LOW at the end of a conversion and the converter is continually clocked, the power consumption is not as low as when CS is HIGH. Figure 38 shows more information.

Power dissipation can also be reduced by lowering the power-supply voltage and the reference voltage. The ADS8320 operates over a  $V_{CC}$  range of 2 V to 5.25 V. However, at voltages below 2.7 V, the converter does not run at a 100-kHz sample rate. See *Typical Characteristics* for more information regarding power supply voltage and maximum sample rate.

Shutdown current with  $\overline{\text{CS}}$  LOW varies with sample rate

Figure 38. Shutdown Current With CS HIGH is 50 nA (Typically, Regardless of the Clock)

### 10.3.1 Short Cycling

Another way of saving power is to use the CS signal to short cycle the conversion. Because the ADS8320 places the latest data bit on the  $D_{OUT}$  line as it is generated, the converter can easily be short cycled. This term means that the conversion can be terminated at any time. For example, if only 14 bits of the conversion result are required, then the conversion can be terminated (by pulling CS HIGH) after the 14th bit has been clocked out.

This technique can be used to lower the power dissipation (or to increase the conversion rate) in those applications where an analog signal is being monitored until some condition becomes true. For example, if the signal is outside a predetermined range, the full 16-bit conversion result may not be required. If so, the conversion can be terminated after the first n bits, where n might be as low as 3 or 4. This results in lower power dissipation in both the converter and the rest of the system, as they spend more time in the power-down mode.

# 11 デバイスおよびドキュメントのサポート

### 11.1 ドキュメントのサポート

#### 11.1.1 関連資料

関連資料については、以下を参照してください。

- 『ユニバーサル・センサのIF SAR BoosterPack』(TIDUAI7)

- TI Precision Design TIDU032、『絶縁抵抗を使用した容量性負荷の駆動ソリューション』(TIDU032)

### 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通 知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。 変更の 詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ TIのE2E (Engineer-to-Engineer) コミュニティ。エンジニア間の共同作 業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有 し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることが できます。技術サポート用の連絡先情報も参照できます。

#### 11.4 商標

SPI. E2E are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内 蔵しています。保存時または取り扱い時は、MOSゲートに対す ろ静電破壊を防 ▲ 止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 11.6 用語集

SLYZ022 — TI用語集.

この用語集には、用語や略語の一覧および定義が記載されています。

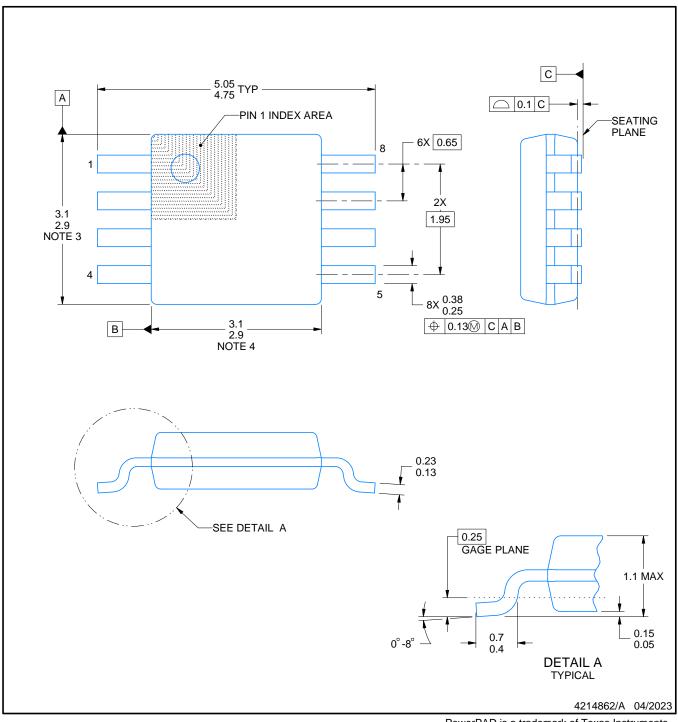

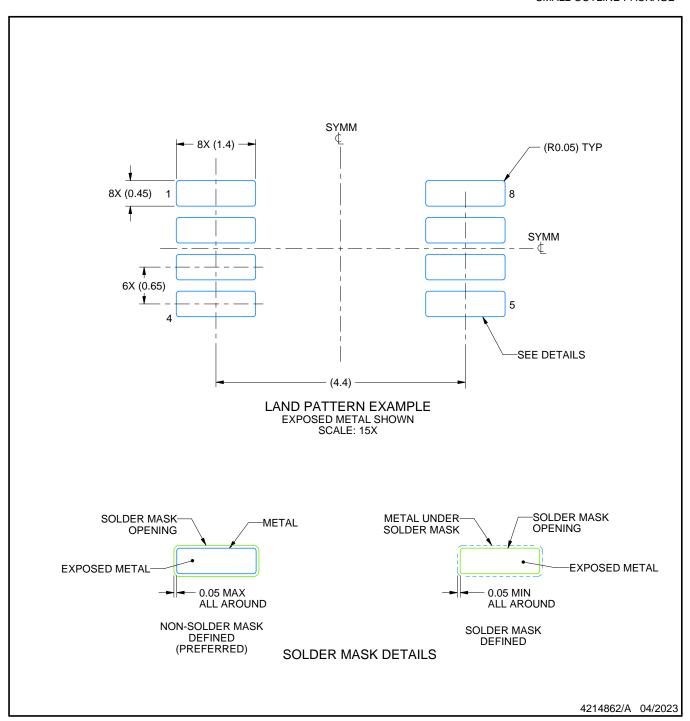

# 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスに ついて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もありま す。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| ADS8320E/250          | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320E/250.B        | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320E/250G4        | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320E/2K5          | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320E/2K5.B        | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320EB/250         | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320EB/250.B       | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320EB/250G4       | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320EB/2K5         | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

| ADS8320EB/2K5.B       | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | Call TI       | Level-2-260C-1 YEAR | -40 to 85    | A20          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF ADS8320:

NOTE: Qualified Version Definitions:

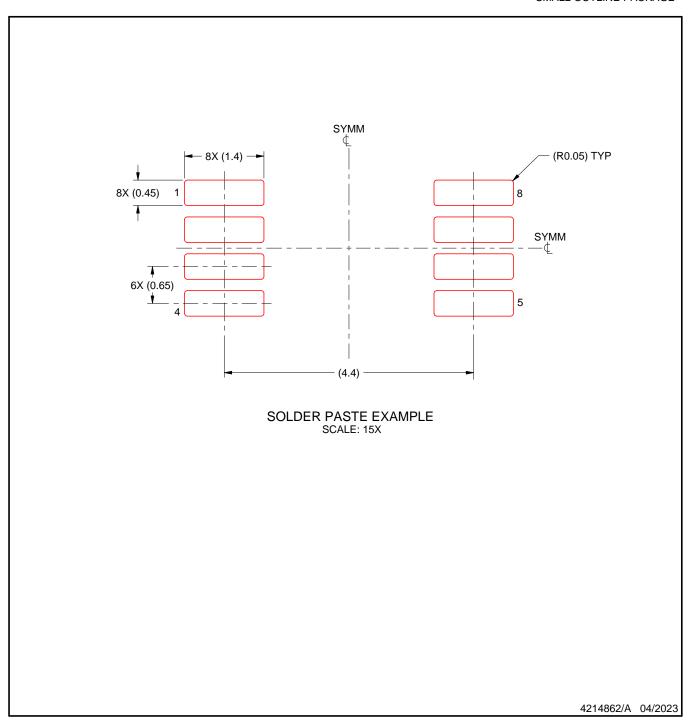

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.