# QUAD CHANNEL, 12-BIT, 105/80/65 MSPS ADC WITH SERIAL LVDS INTERFACE

Check for Samples: ADS6424, ADS6423, ADS6422

# FEATURES

- 12-Bit Resolution With No Missing Codes

- Simultaneous Sample and Hold

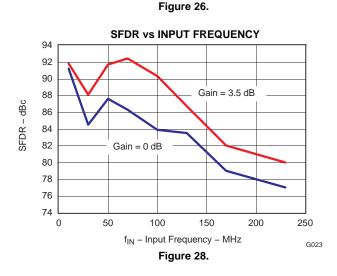

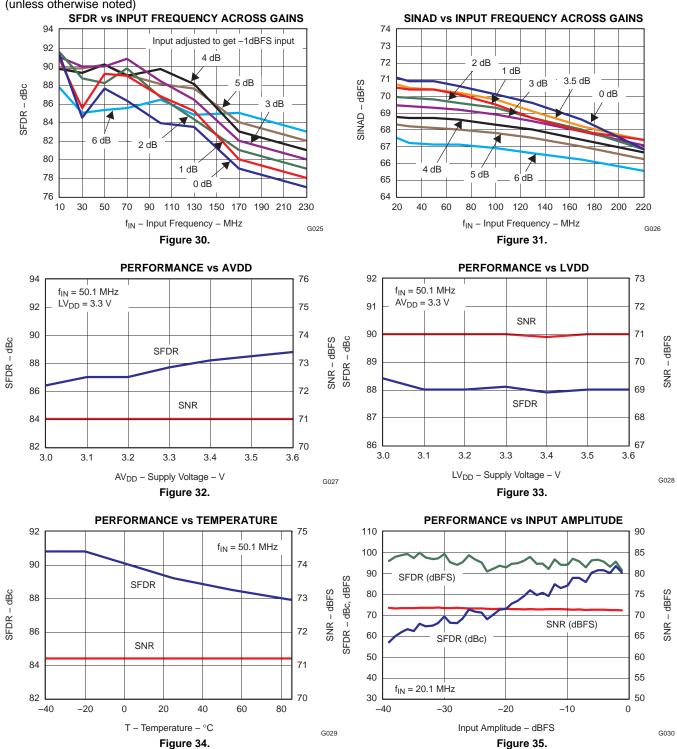

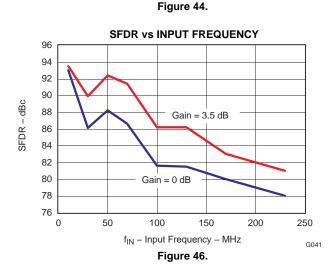

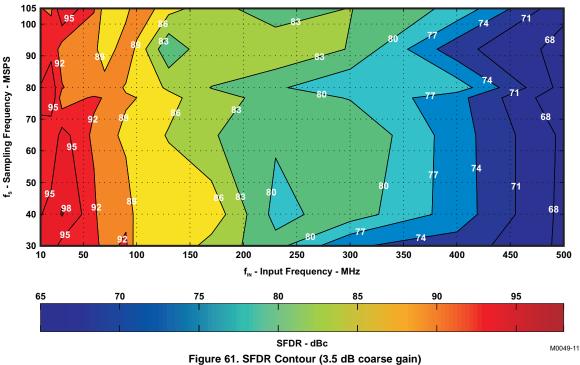

- 3.5dB Coarse Gain and upto 6dB Programmable Fine Gain for SFDR/SNR Trade-Off

- Serialized LVDS Outputs With Programmable Internal Termination Option

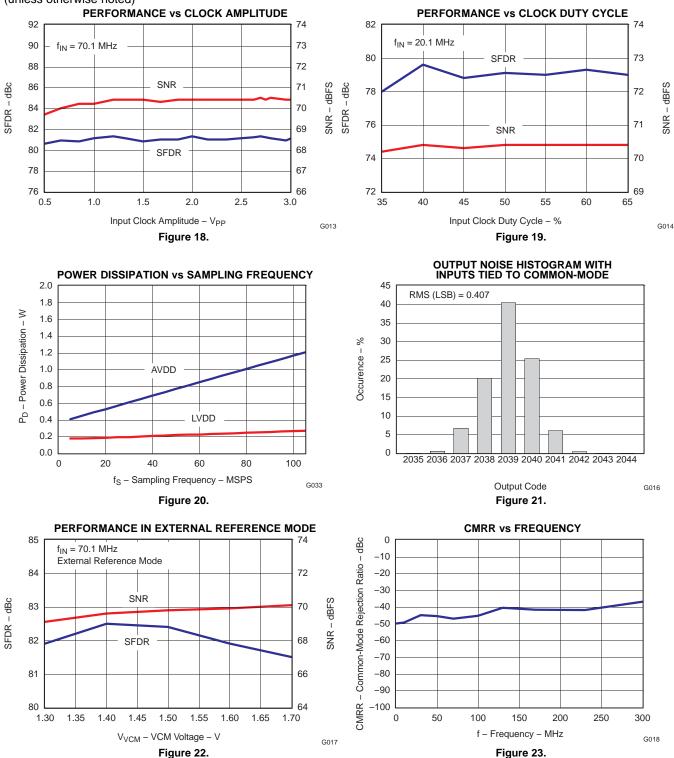

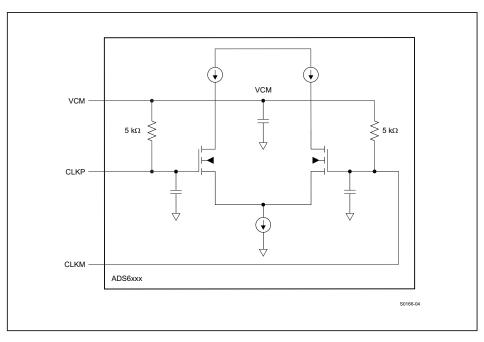

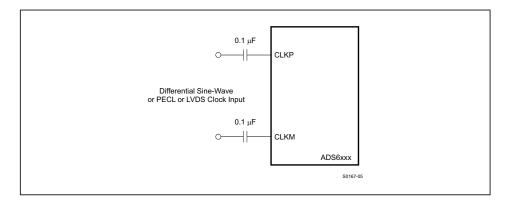

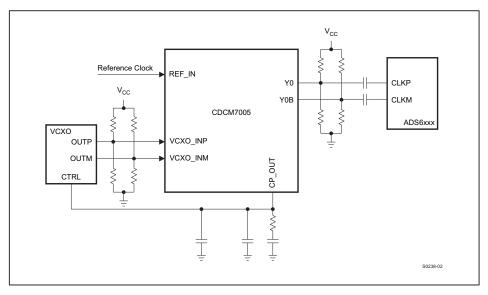

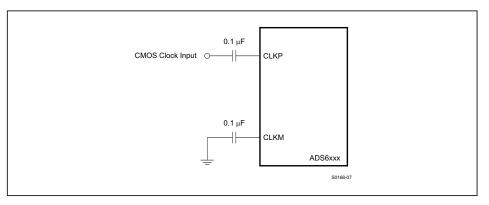

- Supports Sine, LVCMOS, LVPECL, LVDS Clock Inputs and Amplitude down to 400 mV<sub>PP</sub>

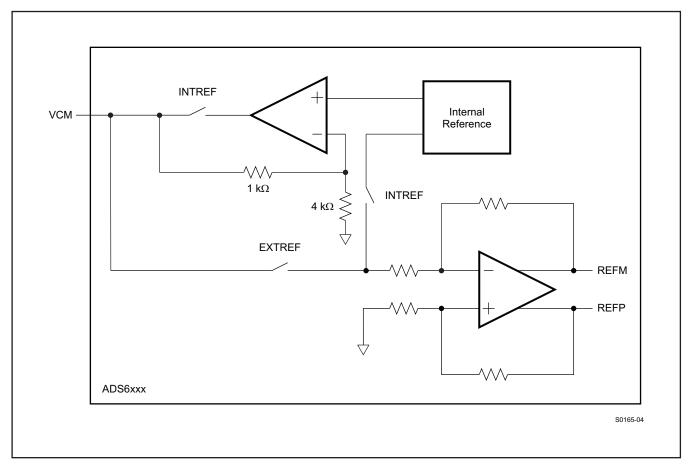

- Internal Reference With External Reference

Support

- No External Decoupling Required for References

- 3.3-V Analog and Digital Supply

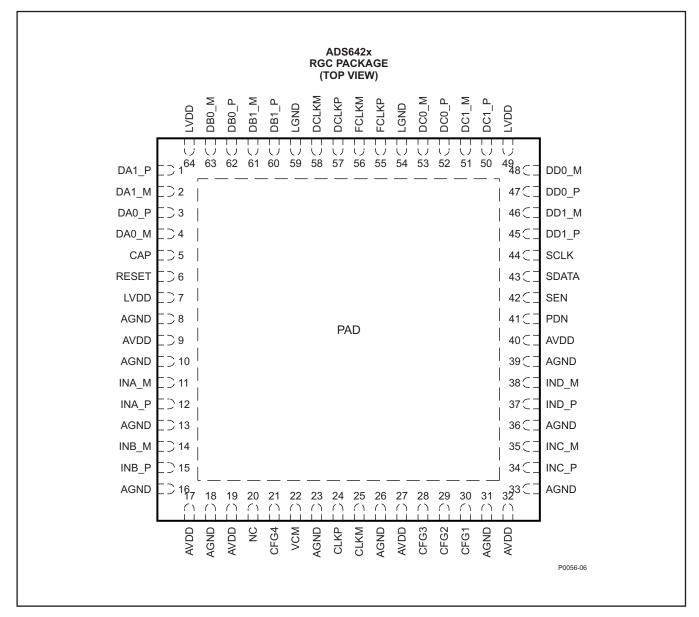

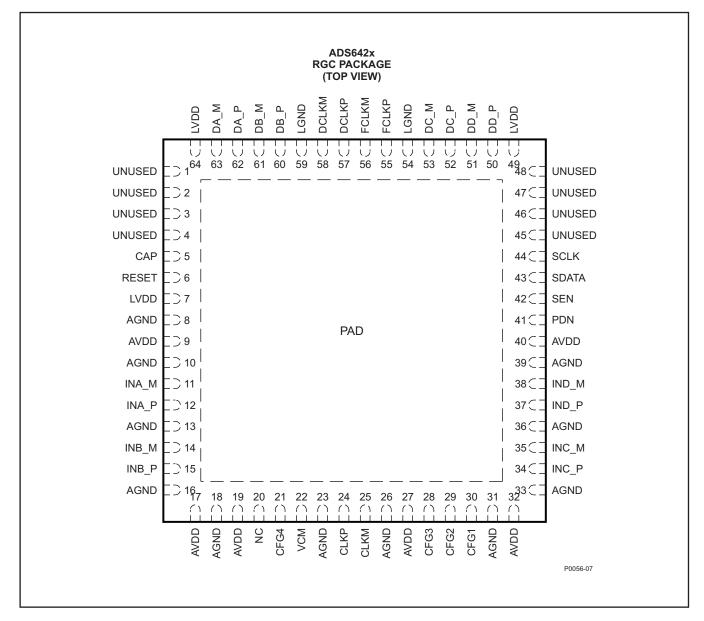

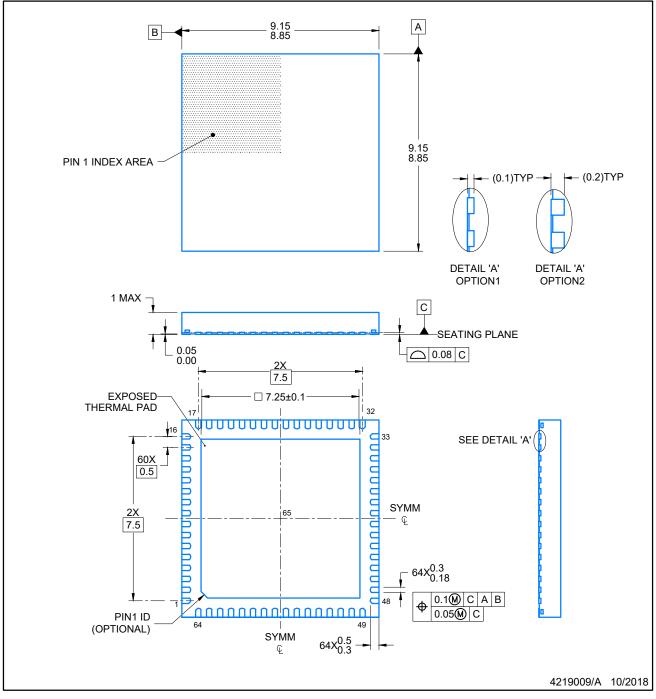

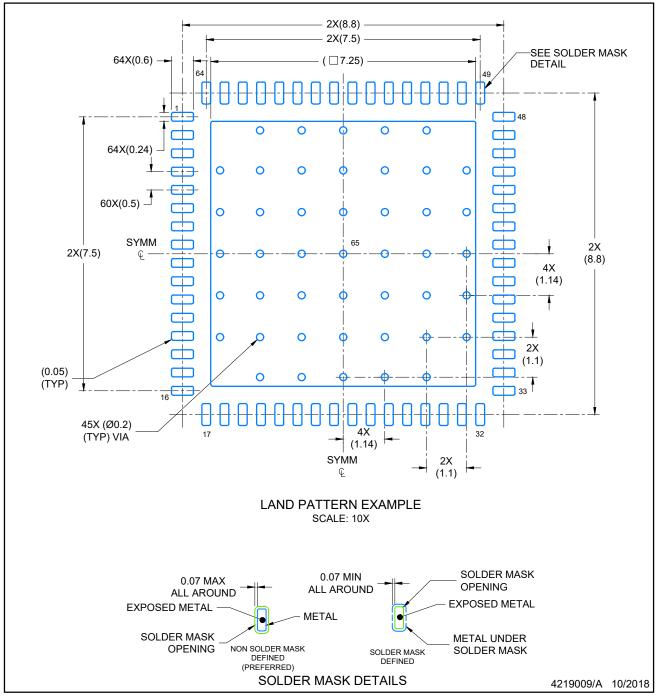

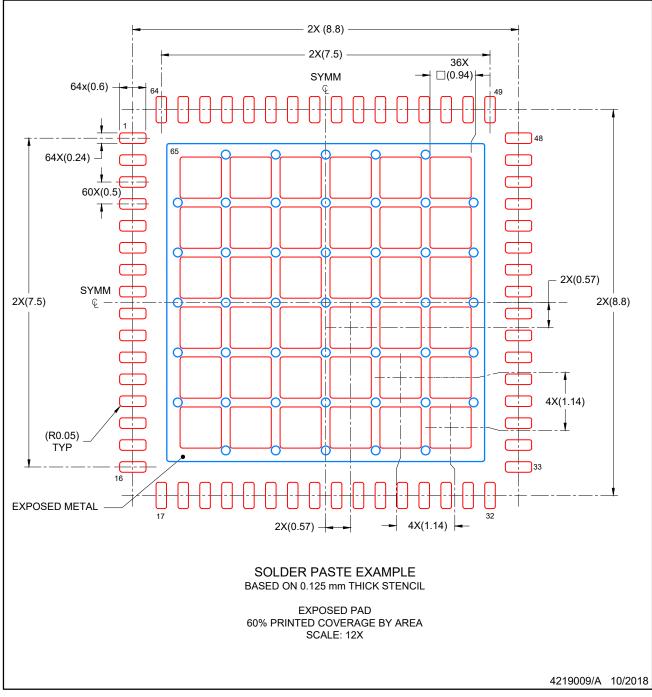

- 64 QFN Package (9 mm × 9 mm)

- Pin Compatible 14-Bit Family (ADS644X SLAS531A)

Feature Compatible Dual Channel Family (ADS624X - SLAS542A, ADS622X - SLAS543A)

# **APPLICATIONS**

- Base-station IF Receivers

- Diversity Receivers

- Medical Imaging

- Test Equipment

## Table 1. ADS64XX Quad Channel Family

|                   | 125 MSPS             | 105 MSPS | 80 MSPS | 65 MSPS |

|-------------------|----------------------|----------|---------|---------|

| ADS644X<br>14 Bit | ADS6445              | ADS6444  | ADS6443 | ADS6442 |

| ADS642X<br>12 Bit | ADS6425<br>(SLWS197) | ADS6424  | ADS6423 | ADS6422 |

|                       |                            | ADS6425 | ADS6424 | ADS6423 | ADS6422 |

|-----------------------|----------------------------|---------|---------|---------|---------|

|                       | Fin = 10MHz (0 dB gain)    | 90      | 91      | 91      | 93      |

| SFDR, dBc             | Fin = 170MHz (3.5 dB gain) | 79      | 81      | 82      | 83      |

|                       | Fin = 10MHz (0 dB gain)    | 70.7    | 71.1    | 71.3    | 71.3    |

| SINAD, dBFS           | Fin = 170MHz (3.5 dB gain) | 67.4    | 68.1    | 68.2    | 68.7    |

| Power per channel, mW |                            | 420     | 340     | 300     | 265     |

### **Table 2. Performance Summary**

# DESCRIPTION

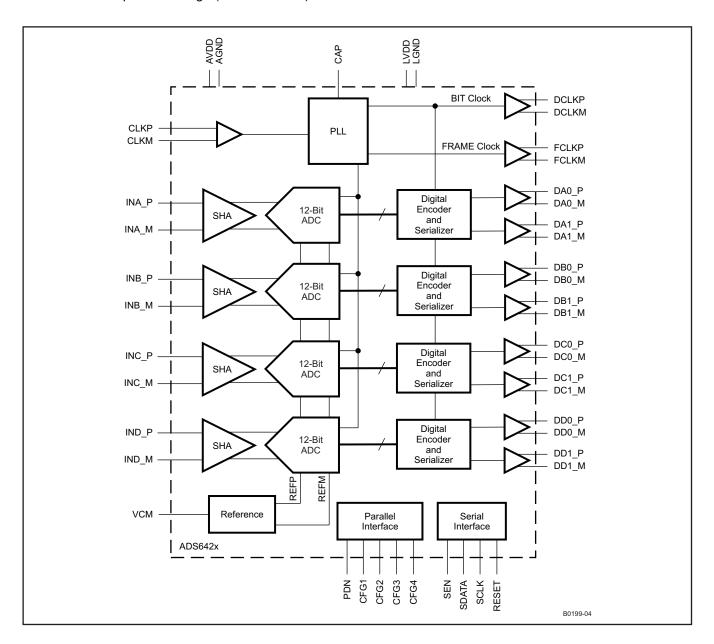

The ADS6424/ADS6423/ADS6422 (ADS642X) is a family of high performance 12-bit 105/80/65 MSPS quad channel A-D converters. Serial LVDS data outputs reduce the number of interface lines, resulting in a compact 64-pin QFN package (9 mm × 9 mm) that allows for high system integration density. The device includes 3.5dB coarse gain option that can be used to improve SFDR performance with little degradation in SNR. In addition to the coarse gain, fine gain options also exist, programmable in 1dB steps up to 6dB.

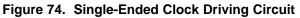

The output interface is 2-wire, where each ADC data is serialized and output over two LVDS pairs. This makes it possible to halve the serial data rate (compared to a 1-wire interface) and restrict it to less than 1Gbps easing receiver design. The ADS642X also includes the traditional 1-wire interface that can be used at lower sampling frequencies.

An internal phase lock loop (PLL) multiplies the incoming ADC sampling clock to derive the bit clock. The bit clock is used to serialize the 12-bit data from each channel. In addition to the serial data streams, the frame and bit clocks are also transmitted as LVDS outputs. The LVDS output buffers have features such as programmable LVDS currents, current doubling modes and internal termination options. These can be used to widen eye-openings and improve signal integrity, easing capture by the receiver.

The ADC channel outputs can be transmitted either as MSB or LSB first and 2s complement or straight binary.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ADS6424 ADS6423 ADS6422

SLAS532B-MAY 2007-REVISED DECEMBER 2013

www.ti.com

ADS642X has internal references, but can also support an external reference mode. The device is specified over the industrial temperature range (-40°C to 85°C).

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

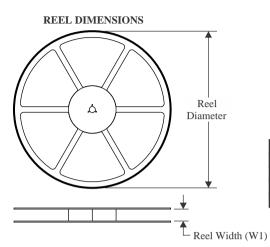

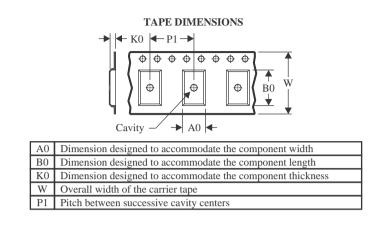

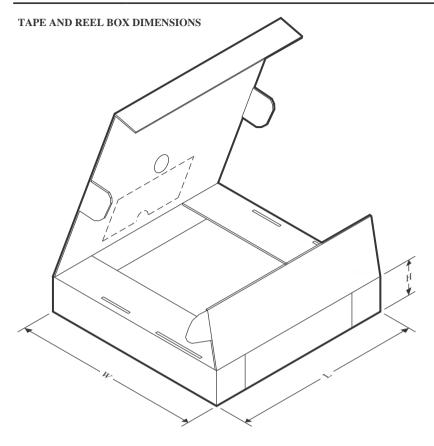

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|---------|-----------------------|-----------------------|-----------------------------------|--------------------|-----------------|---------------------------------|

| ADS6424 | QFN-64 <sup>(2)</sup> | RGC                   | –40°C to 85°C                     | AZ6424             | ADS6424IRGCT    | 250, Tape/reel                  |

| AD56424 | QFIN-04               | RGC                   | -40 C 10 85 C                     | AZ0424             | ADS6424IRGCR    | 2000, Tape/reel                 |

| ADS6423 | QFN-64 <sup>(2)</sup> | RGC                   | –40°C to 85°C                     | AZ6423             | ADS6423IRGCT    | 250, Tape/reel                  |

| AD56423 |                       | RGC                   | -40 C 10 85 C                     | AZ0423             | ADS6423IRGCR    | 2000, Tape/reel                 |

| ADS6422 | QFN-64 <sup>(2)</sup> | RGC                   | -40°C to 85°C                     | AZ6422             | ADS6422IRGCT    | 250, Tape/reel                  |

| AD36422 | QFIN-04               | KGU                   | -40 0 10 85 0                     | AZ0422             | ADS6422IRGCR    | 2000, Tape/reel                 |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) For thermal pad size on the package, see the mechanical drawings at the end of this data sheet. θ<sub>JA</sub> = 23.17 °C/W (0 LFM air flow), θ<sub>JC</sub> = 22.1 °C/W when used with 2 oz. copper trace and pad soldered directly to a JEDEC standard four layer 3 in. x 3 in. PCB.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                  |                                      | VALUE                                | UNIT |

|------------------|--------------------------------------|--------------------------------------|------|

| AVDD             | Supply voltage range                 | -0.3 to 3.9                          | V    |

| LVDD             | Supply voltage range                 | -0.3 to 3.9                          | V    |

|                  | Voltage between AGND and DGND        | -0.3 to 0.3                          | V    |

|                  | Voltage between AVDD to LVDD         | -0.3 to 3.3                          | V    |

|                  | Voltage applied to external pin, VCM | -0.3 to 2.0                          | V    |

|                  | Voltage applied to analog input pins | -0.3V to minimum ( 3.6, AVDD + 0.3V) | V    |

| T <sub>A</sub>   | Operating free-air temperature range | -40 to 85                            | °C   |

| TJ               | Operating junction temperature range | 125                                  | °C   |

| T <sub>stg</sub> | Storage temperature range            | -65 to 150                           | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                   |                                                                       |                              | MIN  | NOM         | MAX  | UNIT            |

|-------------------|-----------------------------------------------------------------------|------------------------------|------|-------------|------|-----------------|

| SUPPL             | IES                                                                   |                              |      |             |      |                 |

| AVDD              | Analog supply voltage                                                 |                              | 3.0  | 3.3         | 3.6  | V               |

| LVDD              | LVDS Buffer supply voltage                                            |                              | 3.0  | 3.3         | 3.6  | V               |

| ANALC             | DG INPUTS                                                             |                              |      |             |      |                 |

|                   | Differential input voltage range                                      |                              |      | 2           |      | V <sub>pp</sub> |

|                   | Input common-mode voltage                                             |                              |      | 1.5<br>±0.1 |      | V               |

|                   | Voltage applied on VCM in external reference mode                     |                              | 1.45 | 1.50        | 1.55 | V               |

| CLOC              | ( INPUT                                                               |                              |      |             |      |                 |

|                   |                                                                       | ADS6424                      | 5    |             | 105  |                 |

|                   | Input clock sample rate, Fs                                           | ADS6423                      | 5    |             | 80   | MSPS            |

|                   |                                                                       | ADS6422                      | 5    |             | 65   |                 |

|                   |                                                                       | Sine wave, ac-coupled        | 0.4  | 1.5         |      |                 |

|                   |                                                                       | LVPECL, ac-coupled           |      | ±0.8        |      | Ň               |

|                   | Input clock amplitude differential ( $V_{CLKP} - V_{CLKM}$ )          | LVDS, ac-coupled             |      | ±0.35       |      | V <sub>PP</sub> |

|                   |                                                                       | LVCMOS, ac-coupled           |      | 3.3         |      |                 |

|                   | Input clock duty cycle                                                |                              | 35%  | 50%         | 65%  |                 |

| DIGITA            | L OUTPUTS                                                             |                              | ·    |             |      |                 |

| $C_{\text{LOAD}}$ | Maximum external load capacitance from each output pin to             | Without internal termination |      | 5           |      | - <b>F</b>      |

|                   | DGND                                                                  | With internal termination    |      | 10          |      | pF              |

| R <sub>LOAD</sub> | Differential load resistance (external) between the LVDS output pairs |                              |      | 100         |      | Ω               |

| T <sub>A</sub>    | Operating free-air temperature                                        |                              | -40  |             | 85   | °C              |

4

# **ELECTRICAL CHARACTERISTICS**

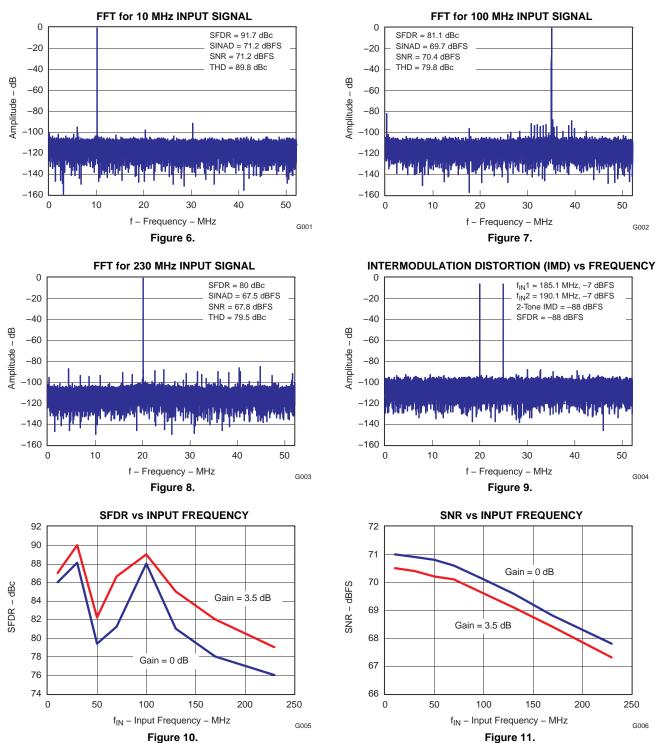

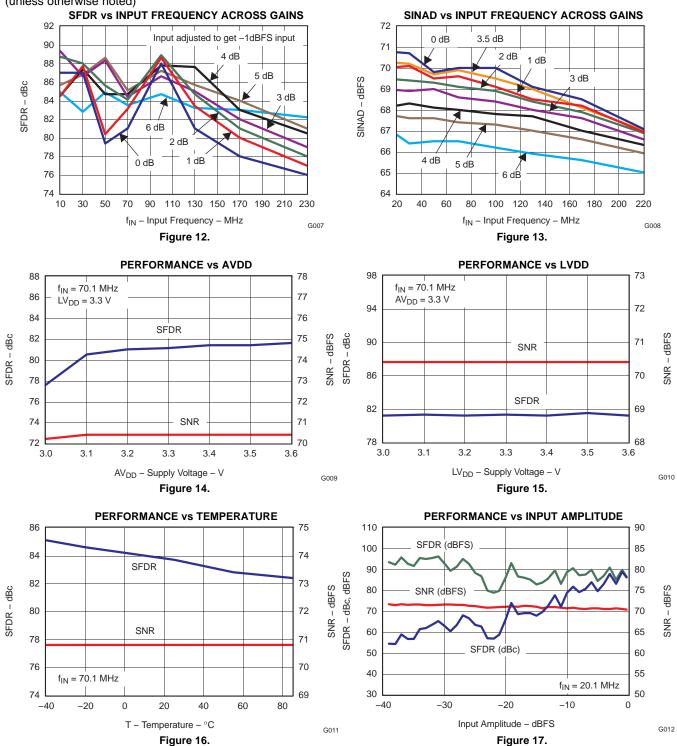

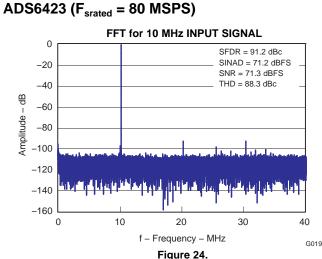

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode (unless otherwise noted).

|                    | PARAMETER                                                                                               |            | ADS6424<br>= 105 MSP | s        |            | ADS6423<br>= 80 MSP | s         |       | ADS6422<br>F <sub>s</sub> = 65 MSPS |      | UNIT     |

|--------------------|---------------------------------------------------------------------------------------------------------|------------|----------------------|----------|------------|---------------------|-----------|-------|-------------------------------------|------|----------|

|                    |                                                                                                         | MIN        | TYP                  | MAX      | MIN        | TYP                 | MAX       | MIN   | TYP                                 | MAX  |          |

| RESOLUT            | ION                                                                                                     |            | 12                   |          |            | 12                  |           |       | 12                                  |      | Bits     |

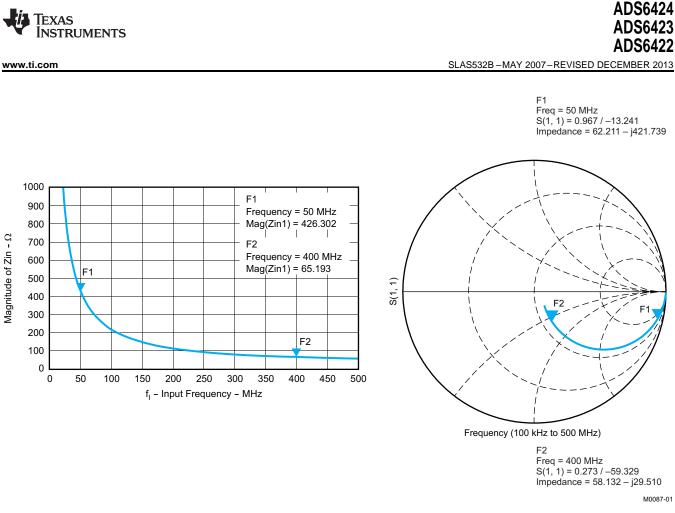

| ANALOG             | INPUT                                                                                                   | · · ·      |                      |          |            |                     | +         |       |                                     |      |          |

|                    | Differential input voltage range                                                                        |            | 2.0                  |          |            | 2.0                 |           |       | 2.0                                 |      | $V_{PP}$ |

|                    | Differential input capacitance                                                                          |            | 7                    |          |            | 7                   |           |       | 7                                   |      | pF       |

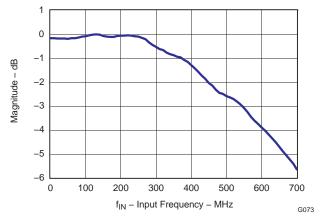

|                    | Analog input bandwidth                                                                                  |            | 500                  |          |            | 500                 |           |       | 500                                 |      | MHz      |

|                    | Analog input common<br>mode current (per input pin<br>of each ADC)                                      |            | 130                  |          |            | 100                 |           |       | 81                                  |      | μA       |

| REFEREN            | CE VOLTAGES                                                                                             | ÷          |                      |          |            |                     | ŀ         |       |                                     |      |          |

| VREFB              | Internal reference bottom voltage                                                                       |            | 1.0                  |          |            | 1.0                 |           |       | 1.0                                 |      | V        |

| VREFT              | Internal reference top voltage                                                                          |            | 2.0                  |          |            | 2.0                 |           |       | 2.0                                 |      | V        |

| $\Delta V_{REF}$   | Internal reference error,<br>(VREFT–VREFB)                                                              | -15        | ±2                   | 15       | -15        | ±2                  | 15        | -15   | ±2                                  | 15   | mV       |

| VCM                | Common mode output voltage                                                                              |            | 1.5                  |          |            | 1.5                 |           |       | 1.5                                 |      | V        |

|                    | VCM output current<br>capability                                                                        |            | ±4                   |          |            | ±4                  |           |       | ±4                                  |      | mA       |

| DC ACCU            | RACY                                                                                                    |            |                      |          |            |                     |           |       |                                     | ·    |          |

|                    | No missing codes                                                                                        | ;          | Specified            |          |            | Specified           |           | S     | pecified                            |      |          |

| E <sub>O</sub>     | Offset error, across devices<br>and across channels within<br>a device                                  | -15        | ±2                   | 15       | -15        | ±2                  | 15        | -15   | ±2                                  | 15   | mV       |

|                    | Offset error temperature<br>coefficient, across devices<br>and across channels within<br>a device       |            | 0.05                 |          |            | 0.05                |           |       | 0.05                                |      | mV/°C    |

|                    | There are two sources of gain                                                                           | error - in | ternal refer         | ence ina | ccuracy ar | nd channel          | gain erro | r     |                                     | ·    |          |

| E <sub>GREF</sub>  | Gain error due to internal reference inaccuracy alone, $(\Delta V_{REF} / 2.0) \%$                      | -0.75      | ±0.1                 | 0.75     | -0.75      | ±0.1                | 0.75      | -0.75 | ±0.1                                | 0.75 | % FS     |

|                    | Reference gain error<br>temperature coefficient                                                         |            | 0.0125               |          |            | 0.0125              |           |       | 0.0125                              |      | ∆%/°C    |

| E <sub>GCHAN</sub> | Gain error of channel<br>alone, across devices and<br>across channels within a<br>device <sup>(1)</sup> | -1         | ±0.3                 | 1        | -1         | ±0.3                | 1         | -1    | ±0.3                                | 1    | % FS     |

|                    | Channel gain error<br>temperature coefficient,<br>across devices and across<br>channels within a device |            | 0.005                |          |            | 0.005               |           |       | 0.005                               |      | ∆%/°C    |

| DNL                | Differential nonlinearity                                                                               | -0.9       | ±0.5                 | 2.0      | -0.9       | ±0.4                | 1.8       | -0.9  | ±0.4                                | 1.8  | LSB      |

| INL                | Integral nonlinearity                                                                                   | -2.2       | ±1.25                | 2.2      | -2.0       | ±1.25               | 2.0       | -2.0  | ±1.0                                | 2.0  | LSB      |

| PSRR               | DC power supply rejection ratio                                                                         |            | 0.5                  |          |            | 0.5                 |           |       | 0.5                                 |      | mV/V     |

| POWER S            | UPPLY                                                                                                   | · · ·      |                      |          |            |                     |           |       |                                     | Ļ    |          |

| I <sub>CC</sub>    | Total supply current                                                                                    |            | 410                  |          |            | 360                 |           |       | 320                                 |      | mA       |

(1) This is specified by design and characterization; it is not tested in production.

Copyright © 2007–2013, Texas Instruments Incorporated

SLAS532B-MAY 2007-REVISED DECEMBER 2013

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode (unless otherwise noted).

|                   | PARAMETER                                |     | ADS6424<br>F <sub>s</sub> = 105 MSPS |      |     | ADS6423<br>F <sub>s</sub> = 80 MSPS |      |     | ADS6422<br>F <sub>s</sub> = 65 MSPS |      |    |

|-------------------|------------------------------------------|-----|--------------------------------------|------|-----|-------------------------------------|------|-----|-------------------------------------|------|----|

|                   |                                          | MIN | TYP                                  | MAX  | MIN | TYP                                 | MAX  | MIN | TYP                                 | MAX  |    |

| I <sub>AVDD</sub> | Analog supply current                    |     | 322                                  |      |     | 280                                 |      |     | 245                                 |      | mA |

| I <sub>LVDD</sub> | LVDS supply current                      |     | 88                                   |      |     | 80                                  |      |     | 75                                  |      | mA |

|                   | Total power                              |     | 1.35                                 | 1.55 |     | 1.18                                | 1.35 |     | 1.05                                | 1.25 | W  |

|                   | Power down (with input<br>clock stopped) |     | 77                                   | 150  |     | 77                                  | 150  |     | 77                                  | 150  | mW |

6

Copyright © 2007–2013, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode (unless otherwise noted).

| PARAMETER                            |                    |                          |      | DS6424<br>105 MS |     |      | DS6423<br>80 MSI |     |      | 0S6422<br>65 MSI |     | UNIT |

|--------------------------------------|--------------------|--------------------------|------|------------------|-----|------|------------------|-----|------|------------------|-----|------|

|                                      |                    |                          | MIN  | TYP              | MAX | MIN  | TYP              | MAX | MIN  | TYP              | MAX |      |

| DYNAMIC AC CHAR                      | ACTERISTICS        |                          |      |                  |     |      |                  |     |      |                  |     |      |

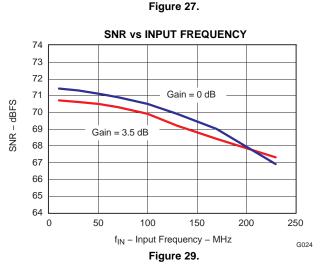

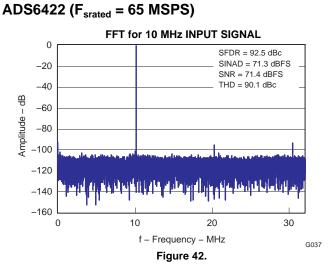

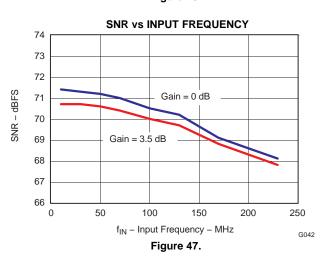

|                                      | Fin = 10 MHz       |                          |      | 71.2             |     |      | 71.4             |     |      | 71.4             |     |      |

|                                      | Fin = 50 MHz       |                          |      | 70.8             |     | 68   | 71.1             |     | 68   | 71.2             |     |      |

|                                      | Fin = 70 MHz       |                          | 67.5 | 70.6             |     |      | 70.9             |     |      | 71               |     |      |

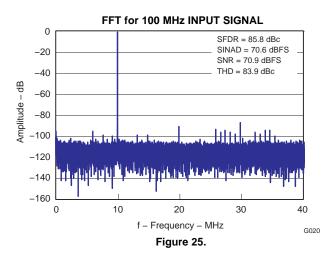

|                                      | Fin = 100 MHz      |                          |      | 70.1             |     |      | 70.5             |     |      | 70.5             |     |      |

| CNID                                 |                    | 0 dB gain                |      | 68.8             |     |      | 69               |     |      | 69.1             |     |      |

| SNR<br>Signal to noise ratio         | Fin = 170 MHz      | 3.5 dB<br>Coarse<br>gain |      | 68.4             |     |      | 68.4             |     |      | 68.8             |     | dBFS |

|                                      |                    | 0 dB gain                |      | 67.8             |     |      | 66.9             |     |      | 68.1             |     |      |

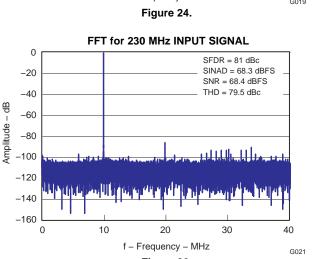

|                                      | Fin = 230 MHz      | 3.5 dB<br>Coarse<br>gain |      | 67.3             |     |      | 67.3             |     |      | 67.8             |     |      |

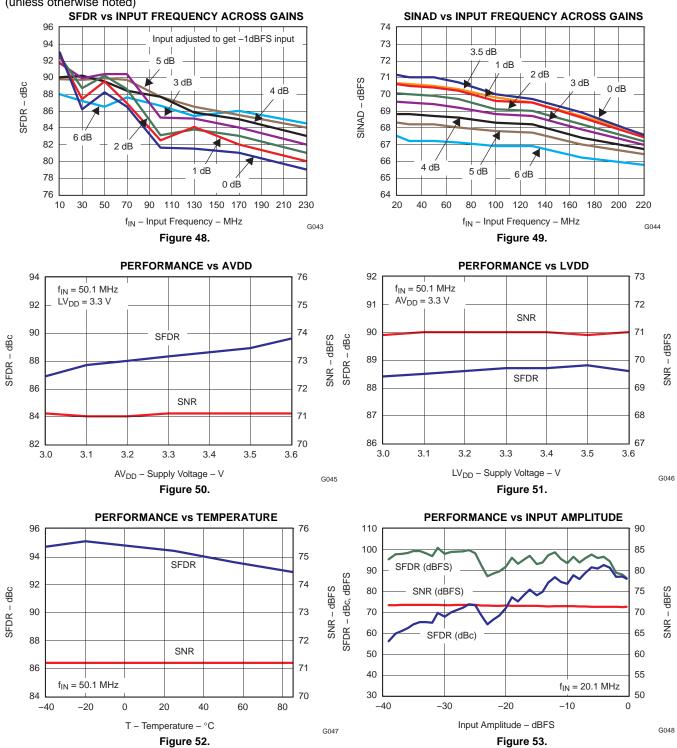

|                                      | Fin = 10 MHz       |                          |      | 71.1             |     |      | 71.3             |     |      | 71.3             |     |      |

| Fin = 50 MHz                         |                    |                          |      | 69.8             |     | 67.5 | 70.9             |     | 67.5 | 71               |     |      |

|                                      | Fin = 70 MHz       |                          | 67   | 70               |     |      | 70.6             |     |      | 70.7             |     |      |

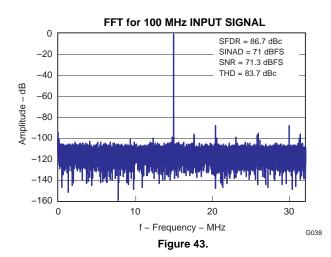

|                                      | Fin = 100 MHz      |                          |      | 70               |     |      | 70.1             |     |      | 70               |     |      |

| SINAD                                |                    | 0 dB gain                |      | 68.5             |     |      | 68.6             |     |      | 68.9             |     |      |

| Signal to noise and distortion ratio | Fin = 170 MHz      | 3.5 dB<br>Coarse<br>gain |      | 68.1             |     |      | 68.2             |     |      | 68.7             |     | dBFS |

|                                      |                    | 0 dB gain                |      | 66.8             |     |      | 66.5             |     |      | 67.3             |     |      |

|                                      | Fin = 230 MHz      | 3.5 dB<br>Coarse<br>gain |      | 66.8             |     |      | 67.2             |     |      | 67.4             |     |      |

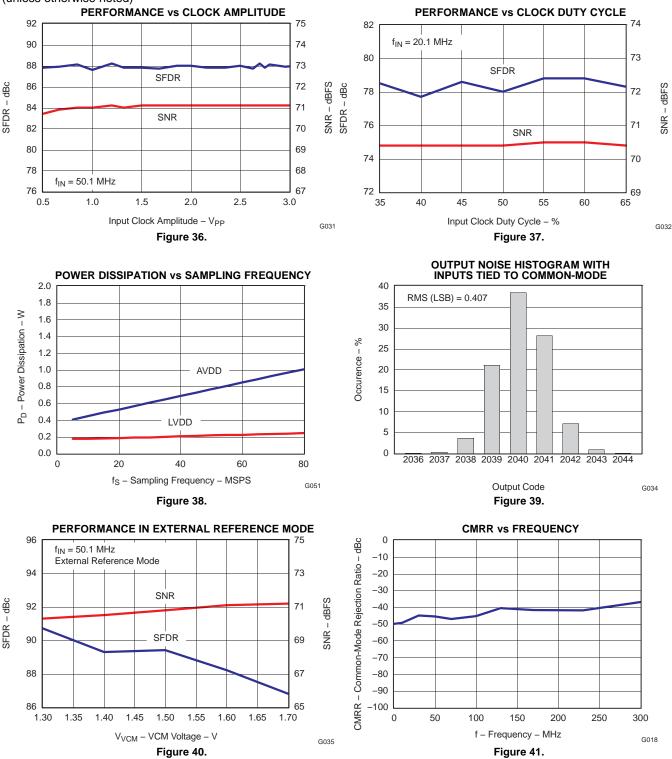

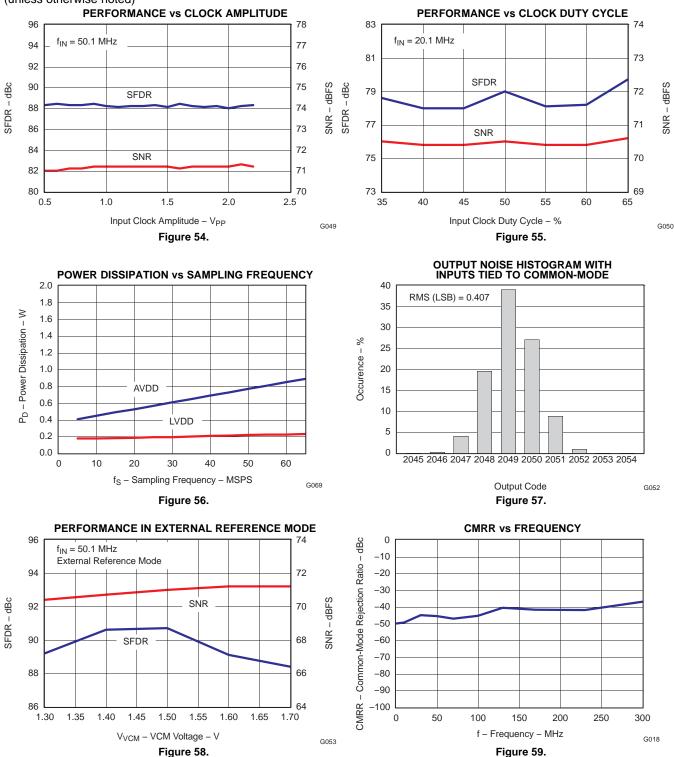

| RMS Output noise                     | Inputs tied to con | nmon-mode                |      | 0.407            |     |      | 0.407            |     |      | 0.407            |     | LSB  |

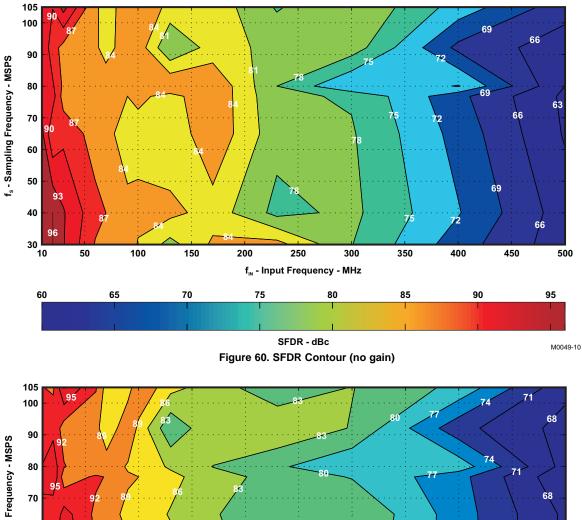

|                                      | Fin = 10 MHz       |                          |      | 91               |     |      | 91               |     |      | 93               |     |      |

|                                      | Fin = 50 MHz       |                          |      | 80               |     | 76   | 87               |     | 76   | 88               |     |      |

|                                      | Fin = 70 MHz       |                          | 73   | 81               |     |      | 86               |     |      | 86               |     |      |

|                                      | Fin = 100 MHz      |                          |      | 85               |     |      | 85               |     |      | 83               |     |      |

| SFDR                                 |                    | 0 dB gain                |      | 78               |     |      | 79               |     |      | 80               |     |      |

| FDR<br>purious free<br>ynamic range  | Fin = 170 MHz      | 3.5 dB<br>Coarse<br>gain |      | 81               |     |      | 82               |     |      | 83               |     | dBc  |

|                                      |                    | 0 dB gain                |      | 76               |     |      | 77               |     |      | 78               |     |      |

|                                      | Fin = 230 MHz      | 3.5 dB<br>Coarse<br>gain |      | 79               |     |      | 80               |     |      | 81               |     |      |

SLAS532B-MAY 2007-REVISED DECEMBER 2013

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode (unless otherwise noted).

| PARAMETER                     | TEST CON                     | ADS6424ADS6423ADS6422T CONDITIONS $F_s = 105 \text{ MSPS}$ $F_s = 80 \text{ MSPS}$ $F_s = 65 \text{ MSPS}$ MINTYPMAXMINTYPMAX |      |      | UNIT |      |      |     |      |      |      |

|-------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|-----|------|------|------|

|                               |                              |                                                                                                                               | MIN  | TYP  | MAX  | MIN  | TYP  | MAX | MIN  |      |      |

|                               | Fin = 10 MHz                 |                                                                                                                               |      | 94   |      |      | 96   |     |      | 97   |      |

|                               | Fin = 50 MHz                 |                                                                                                                               |      | 88   |      | 76   | 90   |     | 76   | 92   |      |

|                               | Fin = 70 MHz                 |                                                                                                                               | 73   | 88   |      |      | 90   |     |      | 92   |      |

|                               | Fin = 100 MHz                |                                                                                                                               |      | 90   |      |      | 87   |     |      | 87   |      |

|                               |                              | 0 dB gain                                                                                                                     |      | 84   |      |      | 86   |     |      | 86   |      |

| HD2<br>Second harmonic        | Fin = 170 MHz                | 3.5 dB<br>Coarse<br>gain                                                                                                      |      | 86   |      |      | 88   |     |      | 88   | dBc  |

|                               |                              | 0 dB gain                                                                                                                     |      | 81   |      |      | 82   |     |      | 83   | _    |

|                               | Fin = 230 MHz                | 3.5 dB<br>Coarse<br>gain                                                                                                      |      | 83   |      |      | 84   |     |      | 85   |      |

|                               | Fin = 10 MHz                 |                                                                                                                               |      | 91   |      |      | 91   |     |      | 93   |      |

|                               | Fin = 50 MHz                 |                                                                                                                               |      | 80   |      | 76   | 87   |     | 76   | 88   |      |

|                               | Fin = 70 MHz                 |                                                                                                                               | 73   | 81   |      |      | 86   |     |      | 86   |      |

|                               | Fin = 100 MHz                |                                                                                                                               |      | 85   |      |      | 85   |     |      | 83   |      |

|                               |                              | 0 dB gain                                                                                                                     |      | 78   |      |      | 79   |     |      | 80   |      |

| HD3<br>Third harmonic         | Fin = 170 MHz                | 3.5 dB<br>Coarse<br>gain                                                                                                      |      | 82   |      |      | 82   |     |      | 83   | dBc  |

|                               |                              | 0 dB gain                                                                                                                     |      | 76   |      |      | 77   |     |      | 78   |      |

|                               | Fin = 230 MHz                | 3.5 dB<br>Coarse<br>gain                                                                                                      |      | 79   |      |      | 80   |     |      | 81   |      |

|                               | Fin = 10 MHz                 |                                                                                                                               |      | 95   |      |      | 96   |     |      | 98   |      |

|                               | Fin = 50 MHz                 |                                                                                                                               |      | 94   |      |      | 95   |     |      | 95   |      |

| Worst harmonic                | Fin = 70 MHz                 |                                                                                                                               |      | 94   |      |      | 95   |     |      | 95   |      |

| (other than HD2,<br>HD3)      | Fin = 100 MHz                |                                                                                                                               |      | 92   |      |      | 93   |     |      | 93   | dBc  |

| -,                            | Fin = 170 MHz                |                                                                                                                               |      | 89   |      |      | 90   |     |      | 90   |      |

|                               | Fin = 230 MHz                |                                                                                                                               |      | 86   |      |      | 87   |     |      | 87   |      |

|                               | Fin = 10 MHz                 |                                                                                                                               |      | 89.5 |      |      | 89.5 |     |      | 91   |      |

|                               | Fin = 50 MHz                 |                                                                                                                               |      | 78.5 |      | 74   | 85.5 |     | 74   | 86   |      |

| THD                           | Fin = 70 MHz                 |                                                                                                                               | 70   |      |      |      |      |     |      |      |      |

| Total harmonic distortion     | Fin = 100 MHz                |                                                                                                                               |      | 84   |      |      | 83   |     |      | 80.5 | dBc  |

|                               | Fin = 170 MHz                |                                                                                                                               |      | 76   |      |      | 77.5 |     |      | 78.5 |      |

|                               | Fin = 230 MHz                |                                                                                                                               |      | 74   |      |      | 75.5 |     |      | 76.5 |      |

| ENOB                          | Fin = 50 MHz                 |                                                                                                                               |      |      |      | 10.9 | 11.5 |     | 10.9 | 11.5 |      |

| Effective number of<br>bits   | Fin = 70 MHz                 |                                                                                                                               | 10.8 | 11.4 |      |      |      |     |      |      | Bits |

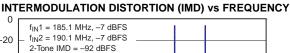

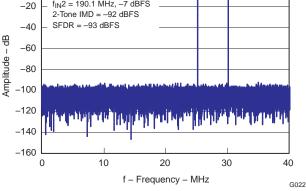

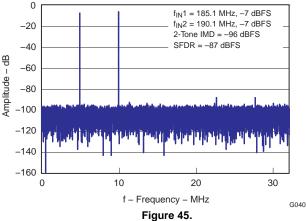

| IMD<br>2-Tone                 | F1= 46.09 MHz,<br>MHz        | F2 = 50.09                                                                                                                    |      | 90   |      |      | 94   |     |      | 97.5 | dBFS |

| intermodulation<br>distortion | F1= 185.09 MHz<br>190.09 MHz | F1= 185.09 MHz, F2 =                                                                                                          |      | 88   |      |      | 92   |     |      | 96   | UDFC |

Copyright © 2007–2013, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS (continued)**

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode (unless otherwise noted).

| PARAMETER                                  | PARAMETER TEST CONDITIONS                                                     |     | ADS6424<br>F <sub>s</sub> = 105 MSPS |     |     | ADS6423<br>F <sub>s</sub> = 80 MSPS |     |     | ADS6422<br>F <sub>s</sub> = 65 MSPS |     |                 |

|--------------------------------------------|-------------------------------------------------------------------------------|-----|--------------------------------------|-----|-----|-------------------------------------|-----|-----|-------------------------------------|-----|-----------------|

|                                            |                                                                               | MIN | TYP                                  | MAX | MIN | TYP                                 | MAX | MIN | TYP                                 | MAX |                 |

| Cross-talk                                 | Near channel<br>Cross-talk signal frequency<br>= 10 MHz                       |     | 92                                   |     |     | 94                                  |     |     | 100                                 |     | dBc             |

| CIUSS-LAIK                                 | Far channel<br>Cross-talk signal frequency<br>= 10 MHz                        | 105 |                                      |     | 106 |                                     |     | 108 |                                     |     | авс             |

| Input overload<br>recovery                 | Recovery to within 1% (of final value) for 6-dB overload with sine wave input |     | 1                                    |     |     | 1                                   |     |     | 1                                   |     | Clock<br>cycles |

| AC PSRR<br>Power Supply<br>Rejection Ratio | < 100 MHz signal, 100 mV_{PP} on AVDD supply                                  |     | 35                                   |     |     | 35                                  |     |     | 35                                  |     | dBc             |

# DIGITAL CHARACTERISTICS

The DC specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1 AVDD = LVDD = 3.3V,  $I_0 = 3.5mA$ ,  $R_{LOAD} = 100 \Omega^{(1)}$ .

| All LVDS specifications are characterized, but not tested at production. |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

|                 | PARAMETER                   | TEST CONDITIONS                                                    | MIN | TYP  | MAX | UNIT |

|-----------------|-----------------------------|--------------------------------------------------------------------|-----|------|-----|------|

| DIGIT           | AL INPUTS                   |                                                                    |     |      |     |      |

|                 | High-level input voltage    |                                                                    | 2.4 |      |     | V    |

|                 | Low-level input voltage     |                                                                    |     |      | 0.8 | V    |

|                 | High-level input current    |                                                                    |     | 10   |     | μA   |

|                 | Low-level input current     |                                                                    |     | 10   |     | μA   |

|                 | Input capacitance           |                                                                    |     | 4    |     | pF   |

| DIGIT           | AL OUTPUTS                  |                                                                    |     |      |     |      |

|                 | High-level output voltage   |                                                                    |     | 1375 |     | mV   |

|                 | Low-level output voltage    |                                                                    |     | 1025 |     | mV   |

| V <sub>OD</sub> | Output differential voltage |                                                                    | 250 | 350  | 450 | mV   |

| V <sub>OS</sub> | Output offset voltage       | Common-mode voltage of OUTP and OUTM                               |     | 1200 |     | mV   |

|                 | Output capacitance          | Output capacitance inside the device, from either output to ground |     | 2    |     | pF   |

(1) Io refers to the LVDS buffer current setting, RLOAD is the external differential load resistance between the LVDS output pair.

# TIMING SPECIFICATIONS<sup>(1)</sup>

SLAS532B-MAY 2007-REVISED DECEMBER 2013

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, sine wave input clock, 1.5 V<sub>PP</sub> clock amplitude, C<sub>L</sub> = 5 pF <sup>(2)</sup>, I<sub>O</sub> = 3.5 mA, R<sub>L</sub> = 100  $\Omega$  <sup>(3)</sup>, no internal termination, unless otherwise noted.

| I                    | PARAMETER                                        | TEST                                                                                        | ADS6424<br>F <sub>s</sub> = 105 MSPS |                               |         | ADS6423<br>F <sub>s</sub> = 80 MSPS |         |      | ADS6422<br>F <sub>s</sub> = 65 MSPS |     |     | UNIT            |

|----------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------|---------|-------------------------------------|---------|------|-------------------------------------|-----|-----|-----------------|

|                      |                                                  | CONDITIONS                                                                                  | MIN                                  | TYP         MAX           250 |         | MIN                                 | TYP     | MAX  | MIN                                 | TYP | MAX |                 |

| tj                   | Aperture jitter                                  | Uncertainty in the sampling instant                                                         |                                      |                               |         | 250                                 |         |      |                                     | 250 |     | fs rms          |

| Interfac<br>serializ | ce: 2-wire, DDR bit c                            | lock, 14x                                                                                   |                                      |                               |         |                                     |         |      |                                     |     | ·   |                 |

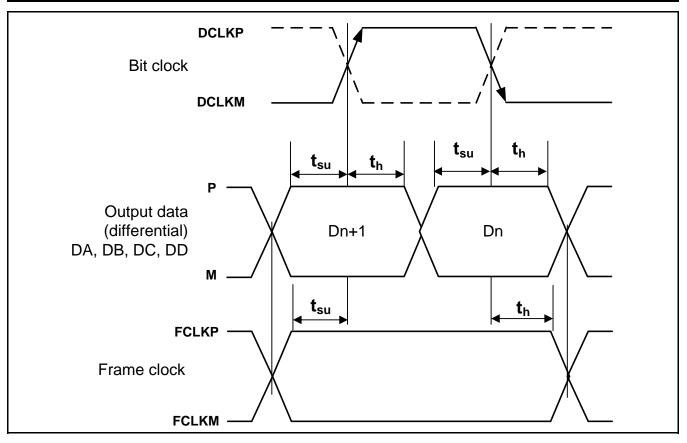

| t <sub>su</sub>      | Data setup time <sup>(4)</sup>                   | From data cross-<br>over to bit clock<br>cross-over                                         | 0.45                                 | 0.65                          |         | 0.65                                | 0.85    |      | 0.8                                 | 1.1 |     | ns              |

| t <sub>h</sub>       | Data hold time <sup>(4)</sup> <sup>(5)</sup> (6) | From bit clock<br>cross-over to data<br>cross-over                                          | 0.5                                  | 0.7                           |         | 0.7                                 | 0.9     |      | 0.8                                 | 1.1 |     | ns              |

| t <sub>su</sub>      | Frame setup time                                 | From frame clock<br>rising edge cross-<br>over to bit clock<br>rising edge cross-<br>over   | 0.45                                 | 0.65                          |         | 0.65                                | 0.85    |      | 0.8                                 | 1.1 |     | ns              |

| t <sub>h</sub>       | Frame hold time                                  | From bit clock<br>falling edge cross-<br>over to frame clock<br>falling edge cross-<br>over | 0.5                                  | 0.7                           |         | 0.7                                 | 0.9     |      | 0.8                                 | 1.1 |     | ns              |

| t <sub>pd_clk</sub>  | Clock<br>propagation delay<br>(6)                | Input clock rising<br>edge cross-over to<br>frame clock rising<br>edge cross-over           | 3.4                                  | 4.4                           | 5.4     | 3.4                                 | 4.4     | 5.4  | 3.4                                 | 4.4 | 5.4 | ns              |

|                      | Bit clock cycle-<br>cycle jitter <sup>(5)</sup>  |                                                                                             |                                      | 350                           |         |                                     | 350     |      |                                     | 350 |     | ps pp           |

|                      | Frame clock<br>cycle-cycle jitter                |                                                                                             |                                      | 75                            |         |                                     | 75      |      |                                     | 75  |     | ps pp           |

| Below                | specifications apply                             | for 5 MSPS ≤ Sampli                                                                         | ing freq ≤                           | 105 MSP                       | S and a | all interfa                         | ace opt | ions |                                     |     |     |                 |

| t <sub>A</sub>       | Aperture delay                                   | Delay from input<br>clock rising edge to<br>the actual sampling<br>instant                  | 1                                    | 2                             | 3       | 1                                   | 2       | 3    | 1                                   | 2   | 3   | ns              |

|                      | Aperture delay variation                         | Channel-channel within same device                                                          | -250                                 | ±80                           | 250     | -250                                | ±80     | 250  | -250                                | ±80 | 250 | ps              |

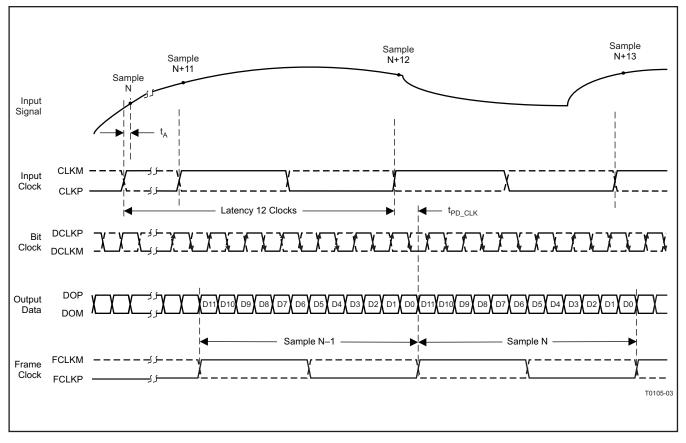

|                      | ADC Latency (7)                                  | Time for a sample<br>to propagate to<br>ADC outputs, see<br>Figure 1                        |                                      | 12                            |         |                                     | 12      |      |                                     | 12  |     | Clock<br>cycles |

Timing parameters are ensured by design and characterization and not tested in production.  $C_{\rm L}$  is the external single-ended load capacitance between each output pin and ground. (1)

(2)

(3)

$I_o$  refers to the LVDS buffer current setting;  $R_L$  is the external differential load resistance between the LVDS output pair. Timing parameters are measured at the end of a 2 inch pcb trace (100- $\Omega$  characteristic impedance) terminated by  $R_L$  and  $C_L$ . (4)

(5) Setup and hold time specifications take into account the effect of jitter on the output data and clock.

Refer to Output Timings in application section for timings at lower sampling frequencies and other interface options. (6)

Note that the total latency = ADC latency + internal serializer latency. The serializer latency depends on the interface option selected as (7)listed in Table 27.

10 Submit Documentation Feedback

# TIMING SPECIFICATIONS<sup>(1)</sup> (continued)

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, maximum rated sampling frequency, sine wave input clock, 1.5 V<sub>PP</sub> clock amplitude, C<sub>L</sub> = 5 pF <sup>(2)</sup>, I<sub>O</sub> = 3.5 mA, R<sub>L</sub> = 100  $\Omega$  <sup>(3)</sup>, no internal termination, unless otherwise noted.

|                   | PARAMETER                                 | TEST<br>CONDITIONS                                             | ADS6424<br>F <sub>s</sub> = 105 MSPS |     |     | ADS6423<br>F <sub>s</sub> = 80 MSPS |     |     | ADS6422<br>F <sub>s</sub> = 65 MSPS |     |     | UNIT         |

|-------------------|-------------------------------------------|----------------------------------------------------------------|--------------------------------------|-----|-----|-------------------------------------|-----|-----|-------------------------------------|-----|-----|--------------|

|                   |                                           | CONDITIONS                                                     | MIN                                  | TYP | MAX | MIN                                 | TYP | MAX | MIN                                 | TYP | MAX |              |

|                   |                                           | Time to valid data<br>after coming out of<br>global power down |                                      |     | 100 |                                     |     | 100 |                                     |     | 100 | μs           |

|                   | Wake up time                              | Time to valid data<br>after input clock is<br>re-started       |                                      |     | 100 |                                     |     | 100 |                                     |     | 100 | μs           |

|                   |                                           | Time to valid data<br>after coming out of<br>channel standby   |                                      |     | 200 |                                     |     | 200 |                                     |     | 200 | clock cycles |

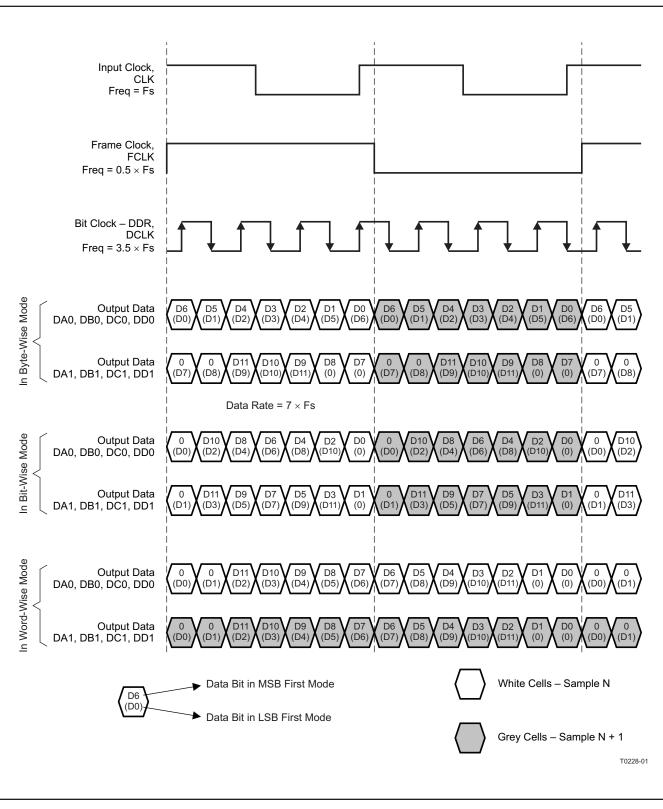

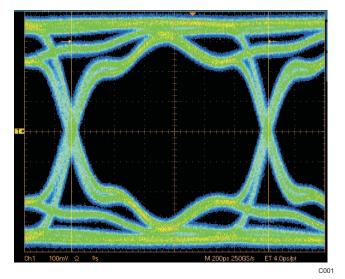

| t <sub>RISE</sub> | Data rise time                            | From -100 mV to<br>+100 mV                                     | 50                                   | 100 | 200 | 50                                  | 100 | 200 | 50                                  | 100 | 200 | ps           |

| t <sub>FALL</sub> | Data fall time                            | From +100 mV to<br>-100 mV                                     | 50                                   | 100 | 200 | 50                                  | 100 | 200 | 50                                  | 100 | 200 | ps           |

| t <sub>RISE</sub> | Bit clock and<br>Frame clock rise<br>time | From –100 mV to<br>+100 mV                                     | 50                                   | 100 | 200 | 50                                  | 100 | 200 | 50                                  | 100 | 200 | ps           |

| t <sub>FALL</sub> | Bit clock and<br>Frame clock fall<br>time | From +100 mV to<br>-100 mV                                     | 50                                   | 100 | 200 | 50                                  | 100 | 200 | 50                                  | 100 | 200 | ps           |

|                   | Bit clock duty cycle                      |                                                                | 45%                                  | 50% | 55% | 45%                                 | 50% | 55% | 45%                                 | 50% | 55% |              |

|                   | Frame clock duty cycle                    |                                                                | 47%                                  | 50% | 53% | 47%                                 | 50% | 53% | 47%                                 | 50% | 53% |              |

TEXAS INSTRUMENTS

www.ti.com

Figure 1. Latency

ADS6422 SLAS532B – MAY 2007 – REVISED DECEMBER 2013

ADS6424

ADS6423

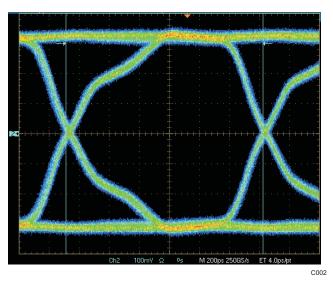

Figure 2. LVDS Timings

Texas Instruments

www.ti.com

#### **DEVICE PROGRAMMING MODES**

ADS642X offers flexibility with several programmable features that are easily configured.

The device can be configured independently using either parallel interface control or serial interface programming.

In addition, the device supports a third configuration mode, where both the parallel interface and the serial control registers are used. In this mode, the priority between the parallel and serial interfaces is determined by a priority table (refer to Table 4). If this additional level of flexibility is not required, the user can select either the serial interface programming or the parallel interface control.

# USING PARALLEL INTERFACE CONTROL ONLY

To control the device using parallel interface, keep RESET tied to *high* (LVDD). Pins CFG1, CFG2, CFG3, CFG4, PDN, SEN, SCLK, and SDATA are used to directly control certain functions of the ADC. After power-up, the device will automatically get configured as per the parallel pin voltage settings (refer to Table 5 to Table 8) and no reset is required. In this mode, SEN, SCLK, and SDATA function as parallel interface control pins.

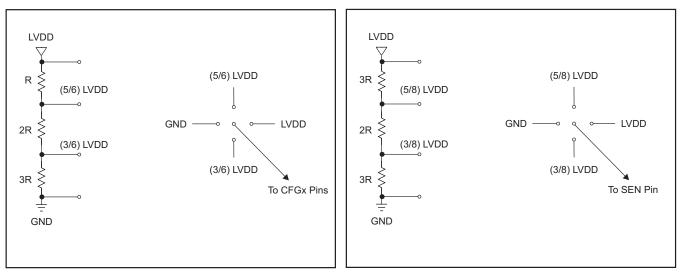

Frequently used functions are controlled in this mode—output data interface and format, power down modes, coarse gain and internal/external reference. The parallel pins can be configured using a simple resistor string (with 10% tolerance resistors) as illustrated in Figure 3.

Table 3 lists descriptions of the modes controlled by the parallel pins.

| PIN         | CONTROL FUNCTIONS                                    |

|-------------|------------------------------------------------------|

| PIN         | CONTROL FUNCTIONS                                    |

| SEN         | Coarse gain and internal/external reference.         |

| SCLK, SDATA | Sync, deskew patterns and global power down.         |

| PDN         | Dedicated pin for global power down                  |

| CFG1        | 1-Wire/2-wire and DDR/SDR bit clock                  |

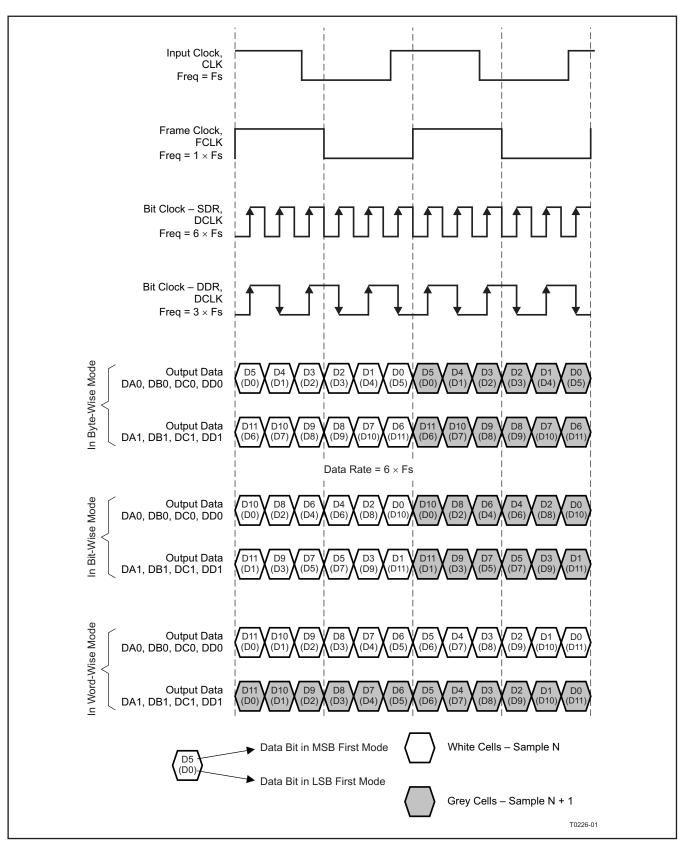

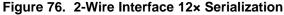

| CFG2        | 12x/14x Serialization and SDR bit clock capture edge |

| CFG3        | Reserved function. Tie CFG3 to Ground.               |

| CFG4        | MSB/LSB First and data format.                       |

#### **Table 3. Parallel Pin Definition**

#### USING SERIAL INTERFACE PROGRAMMING ONLY

In this mode, SEN, SDATA, and SCLK function as serial interface pins and are used to access the internal registers of ADC. The registers must first be reset to their default values either by applying a pulse on RESET pin or by a *high* setting on the <RST> bit (in register ). After reset, the RESET pin must be kept **low**.

The serial interface section describes the register programming and register reset in more detail.

Since the parallel pins (CFG1-4 and PDN) are not used in this mode, they must be tied to ground. The register override bit <OVRD> - D10 in register 0x0D has to be set *high* to disable the control of parallel interface pins in this serial interface control ONLY mode.

#### USING BOTH THE SERIAL INTERFACE AND PARALLEL CONTROLS

For increased flexibility, a combination of serial interface registers and parallel pin controls (CFG1-4 and PDN) can also be used to configure the device.

The parallel interface control pins CFG1 to CFG4 and PDN are available. After power-up, the device will automatically get configured as per the parallel pin voltage settings (refer to Table 5 to Table 11) and no reset is required. A simple resistor string can be used as illustrated in Figure 3.

SEN, SDATA, and SCLK function as serial interface pins and are used to access the internal registers of ADC. The registers must first be reset to their default values either by applying a pulse on RESET pin or by a *high* setting on the <RST> bit (in register ). After reset, the RESET pin must be kept **low**.

The serial interface section describes the register programming and register reset in more detail.

Since some functions are controlled using both the parallel pins and serial registers, the priority between the two is determined by a priority table (refer to Table 4).

| PIN                                                 | FUNCTIONS<br>SUPPORTED         | PRIORITY                                                                                                                                                                                                                   |

|-----------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG1 to CFG4 As described in Table 8<br>to Table 11 |                                | Register bits can control the modes <b>only</b> if the register bit <b><ovrd></ovrd></b> is <b>high</b> . If <b><ovrd></ovrd></b> is <b>low</b> , then the control voltage on these parallel pins determines the function. |

| PDN                                                 | Global Power Down              | Register bit <b><pdn global=""></pdn></b> controls global power down <b>only</b> if PDN pin is <b>low</b> . If PDN is <b>high</b> , device is in global power down mode.                                                   |

| SEN                                                 | Serial Interface Enable        | Coarse gain setting is controlled by bit <b><coarse gain=""></coarse></b> <i>only</i> if the <b><ovrd></ovrd></b> bit is <i>high</i> .<br>Else, it is in default setting of 0 dB gain.                                     |

|                                                     |                                | Internal/External reference setting is determined by bit <b><ref></ref></b> .                                                                                                                                              |

|                                                     | Serial Interface Clock         | Register bits <b><pattern></pattern></b> control the sync and deskew output patterns.                                                                                                                                      |

| SCLK, SDATA                                         | and Serial Interface Data pins | Power down is determined by bit <pdn global="">.</pdn>                                                                                                                                                                     |

Figure 3. Simple Scheme to Configure Parallel Pins

TEXAS INSTRUMENTS

www.ti.com

#### DESCRIPTION OF PARALLEL PINS

#### Table 5. SCLK, SDATA Control Pins

| SCLK | SDATA | DESCRIPTION                                                                                                                                                                            |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOW  | LOW   | NORMAL conversion.                                                                                                                                                                     |

| LOW  | HIGH  | SYNC - ADC outputs sync pattern on all channels. This pattern can be used by the receiver to align the deserialized data to the frame boundary. See Capture Test Patterns for details. |

| HIGH | LOW   | POWER DOWN –Global power down, all channels of the ADC are powered down, including internal references, PLL and output buffers.                                                        |

| HIGH | HIGH  | DESKEW - ADC outputs deskew pattern on all channels. This pattern can be used by the receiver to ensure deserializer uses the right clock edge. See Capture Test Patterns for details. |

## Table 6. SEN Control Pin

| SEN       | DESCRIPTION                                                             |

|-----------|-------------------------------------------------------------------------|

| 0         | External reference and 0 dB coarse gain (full-scale = $2 V_{PP}$ )      |

| (3/8)LVDD | External reference and 3.5 dB coarse gain (full-scale = $1.34 V_{PP}$ ) |

| (5/8)LVDD | Internal reference and 3.5 dB coarse gain (full-scale = $1.34 V_{PP}$ ) |

| LVDD      | Internal reference and 0 dB coarse gain (full-scale = $2 V_{PP}$ )      |

Independent of the programming mode used, after power-up the parallel pins PDN, CFG1 to CFG4 will automatically configure the device as per the voltage applied (refer to Table 7 to Table 11).

#### Table 7. PDN Control Pin

| PDN  | DESCRIPTION       |

|------|-------------------|

| 0    | Normal operation  |

| AVDD | Power down global |

#### Table 8. CFG1 Control Pin

| CFG1                   | DESCRIPTION                        |

|------------------------|------------------------------------|

| 0 (default) +<br>200mV | DDR Bit clock and 1-wire interface |

| (3/6) LVDD ±<br>200mV  | Not used                           |

| (5/6) LVDD ±<br>200mV  | SDR Bit clock and 2-wire interface |

| LVDD - 200mV           | DDR Bit clock and 2-wire interface |

#### Table 9. CFG2 Control Pin

| CFG2                   | DESCRIPTION                                                                                    |

|------------------------|------------------------------------------------------------------------------------------------|

| 0 (default) +<br>200mV | 12x Serialization and capture at falling edge of bit clock (only in 2-wire SDR bit clock mode) |

| (3/6) LVDD ±<br>200mV  | 14x Serialization and capture at falling edge of bit clock (only in 2-wire SDR bit clock mode) |

| (5/6) LVDD ±<br>200mV  | 14x Serialization and capture at rising edge of bit clock (only in 2-wire SDR bit clock mode)  |

| LVDD - 200mV           | 12x Serialization and capture at rising edge of bit clock (only in 2-wire SDR bit clock mode)  |

#### Table 10. CFG3 Control Pin

| CFG3 | RESERVED - TIE TO GROUND |

|------|--------------------------|

|      |                          |

Copyright © 2007-2013, Texas Instruments Incorporated

## Table 11. CFG4 Control Pin

| CFG4                   | DESCRIPTION                 |

|------------------------|-----------------------------|

| 0 (default) +<br>200mV | MSB First and 2s complement |

| (3/6) LVDD ±<br>200mV  | MSB First and offset binary |

| (5/6) LVDD ±<br>200mV  | LSB First and offset binary |

| LVDD - 200mV           | LSB First and 2s complement |

# SERIAL INTERFACE

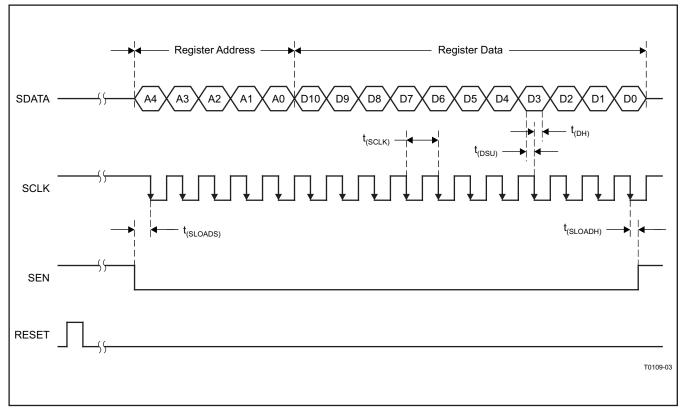

The ADC has a serial interface formed by pins SEN (serial interface enable), SCLK (serial interface clock), SDATA (serial interface data) and RESET. Serial shift of bits into the device is enabled when SEN is low. Serial data SDATA is latched at every falling edge of SCLK when SEN is active (low). The serial data is loaded into the register at every 16th SCLK falling edge when SEN is low. In case the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data can be loaded in multiple of 16-bit words within a single active SEN pulse. The interface can work with SCLK frequency from 20 MHz down to very low speeds (few hertz) and even with non-50% duty cycle SCLK.

The first 5-bits of the 16-bit word are the address of the register while the next 11 bits are the register data.

## **Register Reset**

After power-up, the internal registers *must* be reset to their default values. This can be done in one of two ways:

- 1. Either by applying a high-going pulse on RESET (of width greater than 10 ns) **OR**

- 2. By applying software reset. Using the serial interface, set the **<RST>** bit in register 0x00 to *high* this resets the registers to their default values and then self-resets the **<RST>** bit to LOW.

When RESET pin is not used, it must be tied to LOW.

Figure 4. Serial Interface Timing

# SERIAL INTERFACE TIMING CHARACTERISTICS

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, unless otherwise noted.

|                     | PARAMETER                                                                 | MIN  | TYP | MAX | UNIT |

|---------------------|---------------------------------------------------------------------------|------|-----|-----|------|

| f <sub>SCLK</sub>   | SCLK Frequency, f <sub>SCLK</sub> = 1/t <sub>SCLK</sub>                   | > DC |     | 20  | MHz  |

| t <sub>SLOADS</sub> | SEN to SCLK Setup time                                                    |      | 25  |     | ns   |

| t <sub>SLOADH</sub> | SCLK to SEN Hold time                                                     |      | 25  |     | ns   |

| t <sub>DSU</sub>    | SDATA Setup time                                                          |      | 25  |     | ns   |

| t <sub>DH</sub>     | SDATA Hold time                                                           |      | 25  |     | ns   |

|                     | Time taken for register write to take effect after 16th SCLK falling edge |      | 100 |     | ns   |

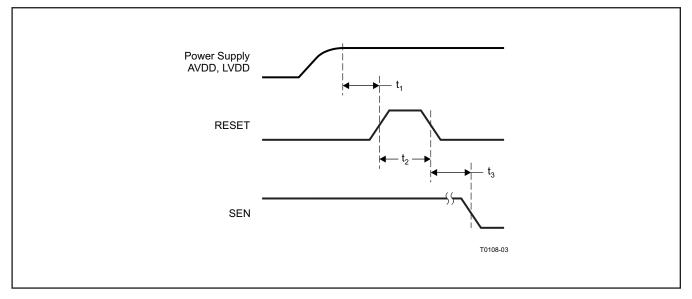

# **RESET TIMING**

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = LVDD = 3.3 V, unless otherwise noted.

|                 | PARMATER                  | CONDITIONS                                                 | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------|------------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub>  | Power-on delay time       | Delay from power-up of AVDD and LVDD to RESET pulse active | 5   |     |     | ms   |

| t <sub>2</sub>  | Reset pulse width         | Pulse width of active RESET signal                         | 10  |     |     | ns   |

| t <sub>3</sub>  | Register write delay time | Delay from RESET disable to SEN active                     | 25  |     |     | ns   |

| t <sub>PO</sub> | Power-up delay time       | Delay from power-up of AVDD and LVDD to output stable      |     | 6.5 |     | ms   |

Figure 5. Reset Timing

# SERIAL REGISTER MAP

| REGISTER<br>ADDRESS |                                                              |                                         |                                       |                              | REGIST              | ER FUNCTION                                                    | S <sup>(1) (2) (3)</sup>                                                 |                                           |                                            |                                            |                                                                   |

|---------------------|--------------------------------------------------------------|-----------------------------------------|---------------------------------------|------------------------------|---------------------|----------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|

| A4 - A0             | D10                                                          | D9                                      | D8                                    | D7                           | D6                  | D5                                                             | D4                                                                       | D3                                        | D2                                         | D1                                         | D0                                                                |

| 00                  | < <b>RST&gt;</b><br>S/W RESET                                | 0                                       | 0                                     | 0                            | 0                   | < <b>REF&gt;</b><br>INTERNAL<br>OR<br>EXTERNAL                 | <pdn chd=""><br/>POWER<br/>DOWN CH D</pdn>                               | <pdn chc=""><br/>POWER<br/>DOWN CHC</pdn> | <pdn chb=""><br/>POWER<br/>DOWN CH B</pdn> | <pdn cha=""><br/>POWER<br/>DOWN CH A</pdn> | <pdn<br>GLOBAL&gt;<br/>GLOBAL<br/>POWER<br/>DOWN</pdn<br>         |

| 04                  | 0                                                            | 0                                       | 0                                     | 0                            |                     |                                                                | <b><clkin gain=""></clkin></b><br>K BUFFER GA                            |                                           |                                            | 0                                          | 0                                                                 |

| 0A                  | 0 CDF><br>DATA<br>FORMAT 2S<br>COMP OR<br>STRAIGHT<br>BINARY |                                         |                                       |                              |                     | S                                                              | 0                                                                        | 0                                         | 0                                          | 0                                          | 0                                                                 |

| 0B                  |                                                              |                                         |                                       |                              | CUSTOM P.           | <custom a=""><br/>ATTERN (LOW</custom>                         |                                                                          |                                           |                                            |                                            |                                                                   |

| 0C                  | FINE GAIN                                                    | <fine gain=""><br/>N CONTROL (10</fine> | lB to 6 dB)                           | 0                            | 0                   | 0                                                              | 0                                                                        | 0                                         | 0                                          | 0                                          | <custom<br>B&gt;<br/>CUSTOM<br/>PATTERN<br/>(MSB BIT)</custom<br> |

| 0D                  | <ovrd><br/>OVERRIDE<br/>BIT</ovrd>                           | 0                                       | 0                                     | BYTE-WISE<br>OR BIT-<br>WISE | MSB OR<br>LSB FIRST | <coarse<br>GAIN&gt;<br/>COURSE<br/>GAIN<br/>ENABLE</coarse<br> | FALLING OR<br>RISING BIT<br>CLOCK<br>CAPTURE<br>EDGE                     | 0                                         | 12-BIT OR<br>14-BIT<br>SERIALIZE           | DDR OR<br>SDR BIT<br>CLOCK                 | 1-WIRE OR<br>2-WIRE<br>INTERFACE                                  |

| 10                  | LVDS                                                         | INTERNAL TER                            | <term clk=""><br/>MINATION BIT</term> | AND WORD CI                  | LOCKS               | <lvds curr=""><br/>LVDS CURRENT SETTINGS LV</lvds>             |                                                                          |                                           |                                            | <curr d<="" td=""><td></td></curr>         |                                                                   |

| 11                  | WORD-WIS                                                     | E CONTROL                               | 0                                     | 0                            | 0                   | 0                                                              | <b><term data=""></term></b><br>LVDS INTERNAL TERMINATION - DATA OUTPUTS |                                           |                                            |                                            | TS                                                                |

#### Table 12. Summary of Functions Supported By Serial Interface

The unused bits in each register (shown by blank cells in above table) must be programmed as 0. Multiple functions in a register can be programmed in a single write operation. After a hardware or software reset, all register bits are cleared to '0'. (1)

(2) (3)

# **DESCRIPTION OF SERIAL REGISTERS**

Note: After a hardware or software reset, all register bits are cleared to '0'.

### Table 13. Serial Register A

| REGISTER<br>ADDRESS |                               |                                                                                                                   |           |             |              | BITS                                         |                                            |                                           |                                            |                                            |                                             |

|---------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------|-------------|--------------|----------------------------------------------|--------------------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------|

| A4 - A0             | D10                           | D9                                                                                                                | D8        | D7          | D6           | D5                                           | D4                                         | D3                                        | D2                                         | D1                                         | D0                                          |

| 00                  | < <b>RST&gt;</b><br>S/W RESET | 0                                                                                                                 | 0         | 0           | 0            | <ref><br/>INTERNAL<br/>OR<br/>EXTERNAL</ref> | <pdn chd=""><br/>POWER<br/>DOWN CH D</pdn> | <pdn chc=""><br/>POWER<br/>DOWN CHC</pdn> | <pdn chb=""><br/>POWER<br/>DOWN CH B</pdn> | <pdn cha=""><br/>POWER<br/>DOWN CH A</pdn> | < <b>PDN&gt;</b><br>GLOBAL<br>POWER<br>DOWN |

| D0 - D4             |                               | Power do                                                                                                          | wn mode   | S           |              |                                              |                                            |                                           |                                            |                                            |                                             |