# デュアル・チャネル、12ビット、125/105/80/65 MSPS、シリアルLVDSインターフェイス付きADC

## 特 長

- 最大サンプリング・レート : 125 MSPS

- 分解能 : 12ビット ノー・ミッシング・コード

- 同時サンプル/ホールド

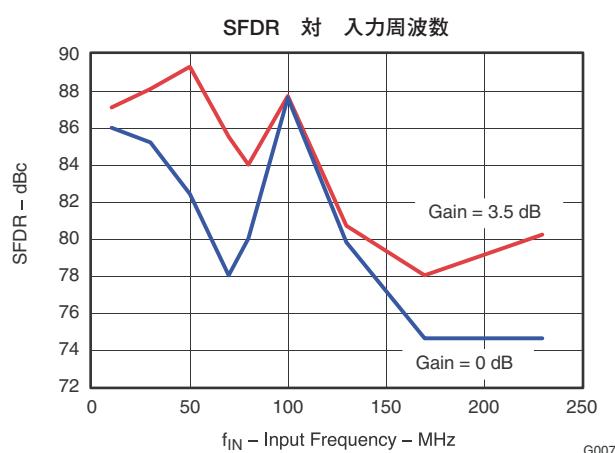

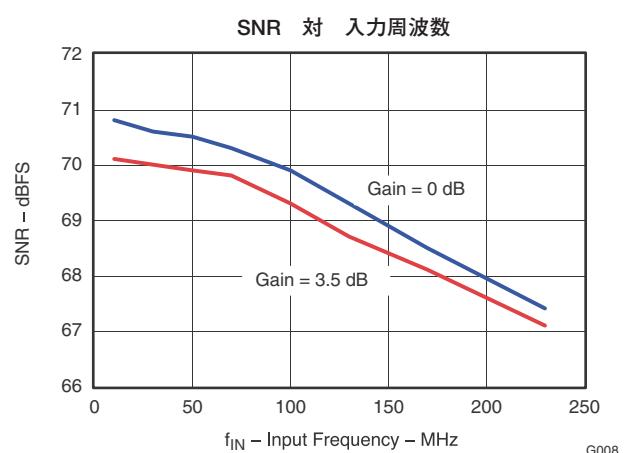

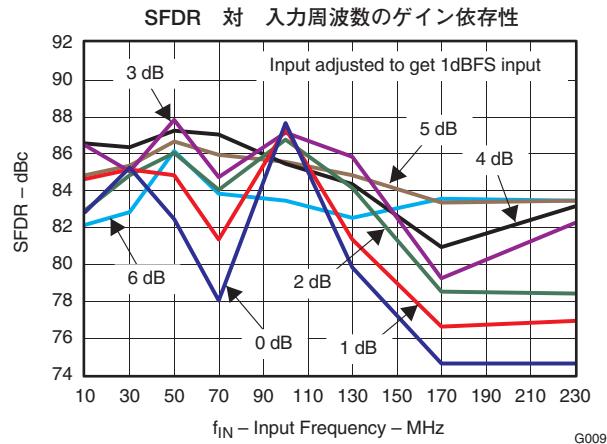

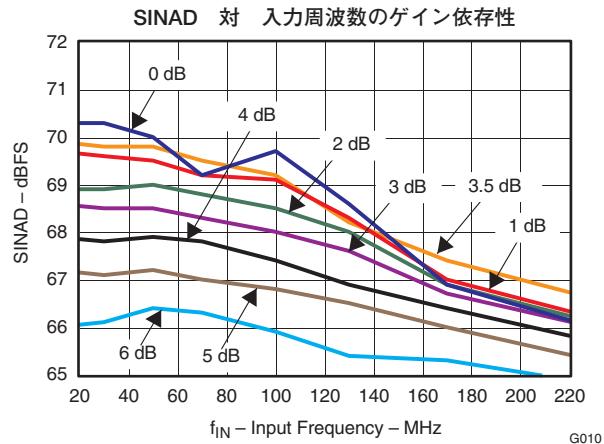

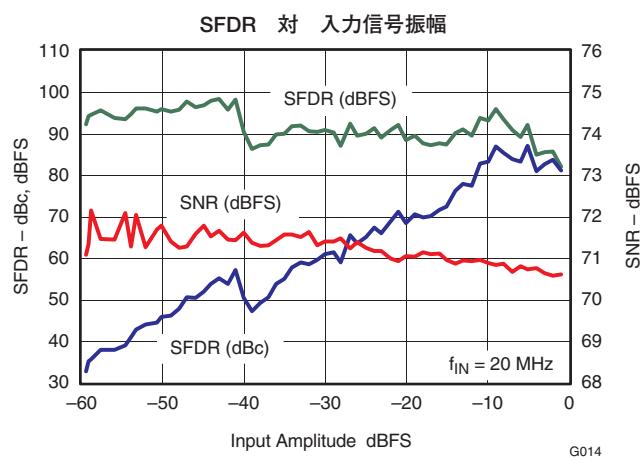

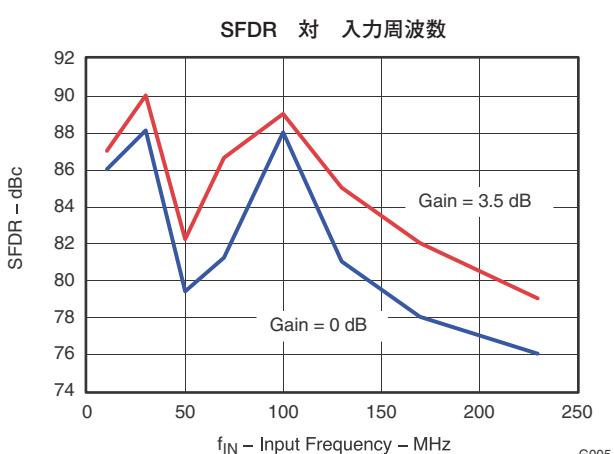

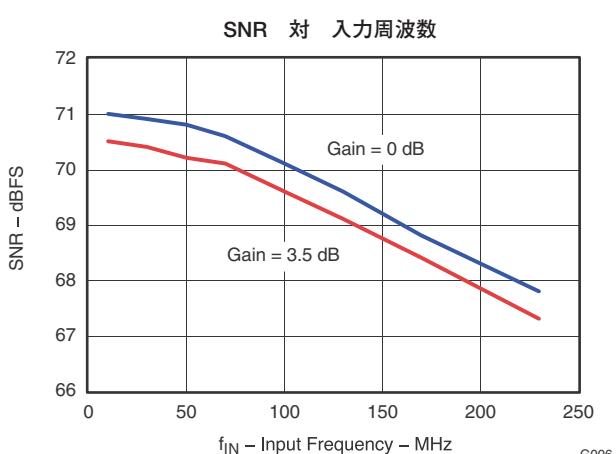

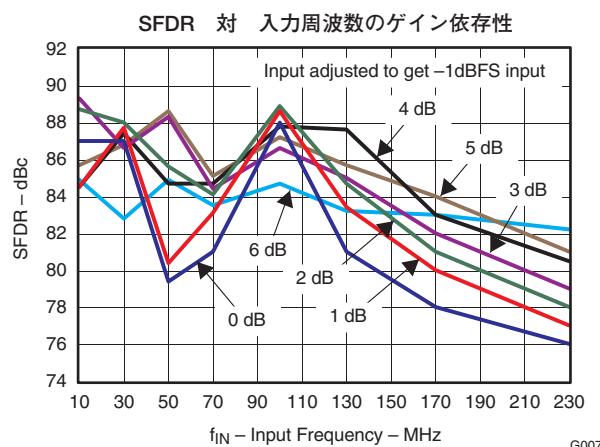

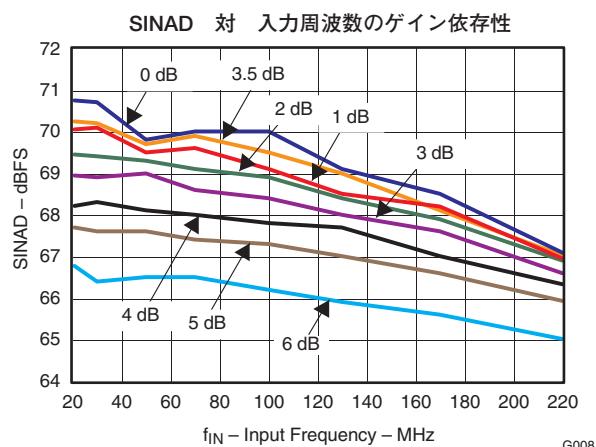

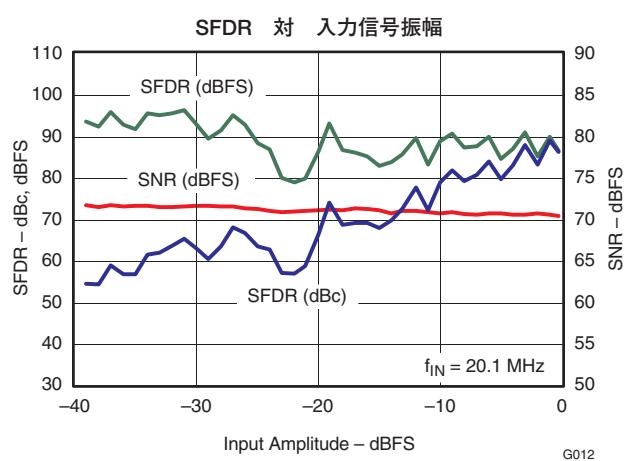

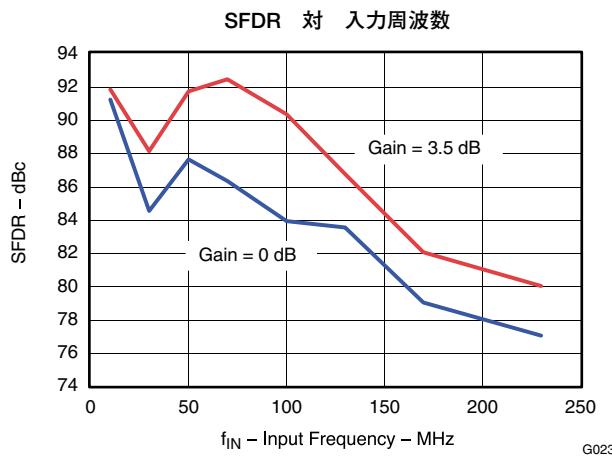

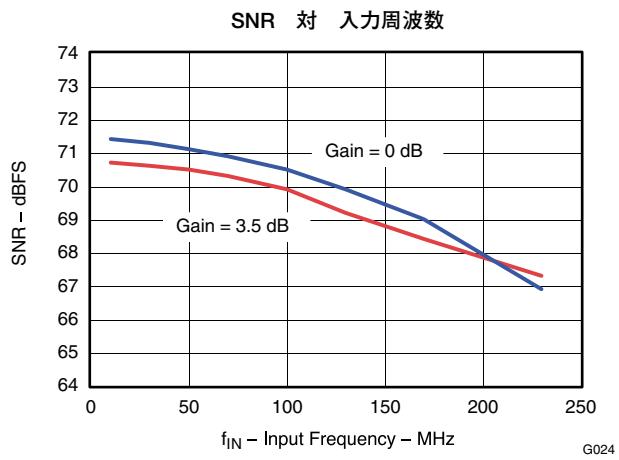

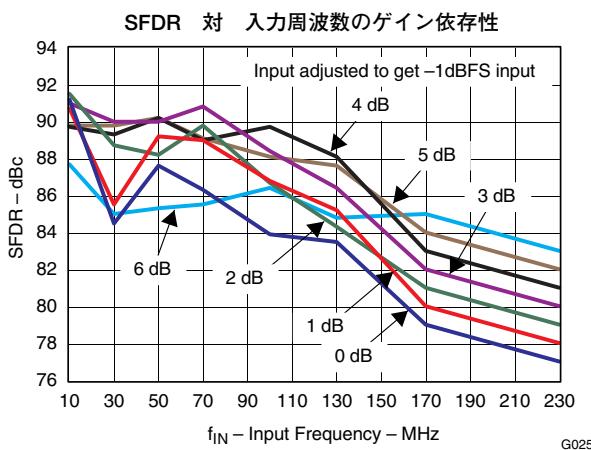

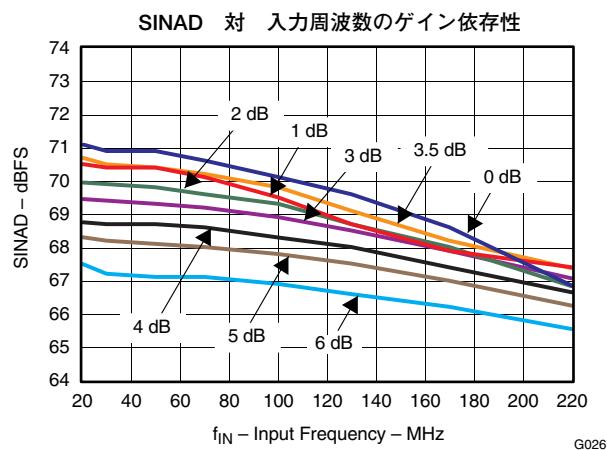

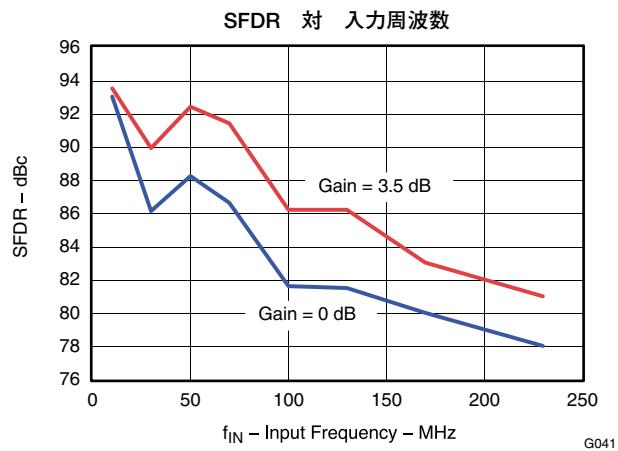

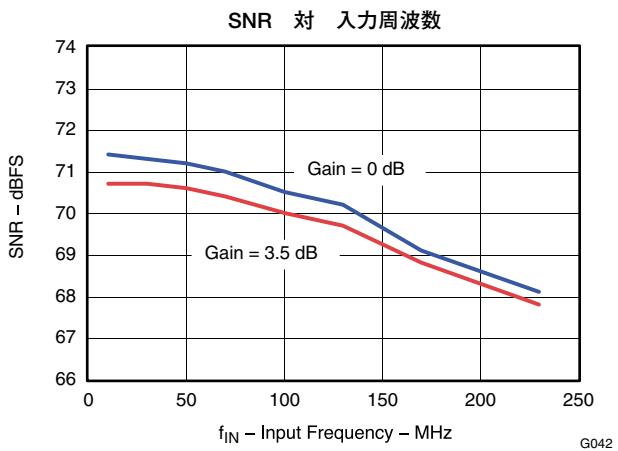

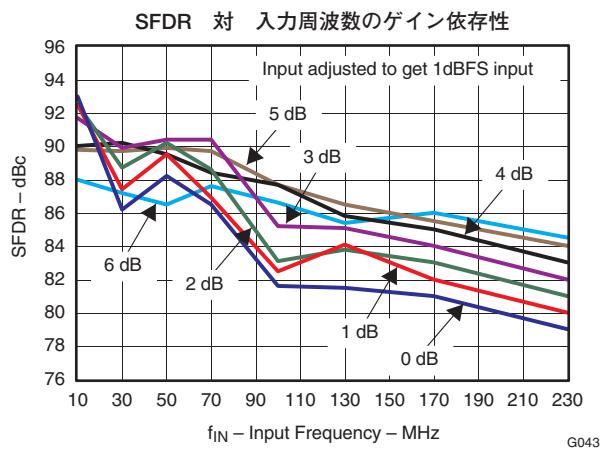

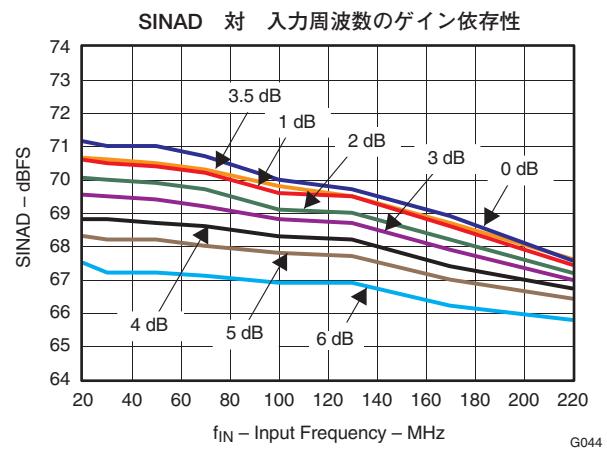

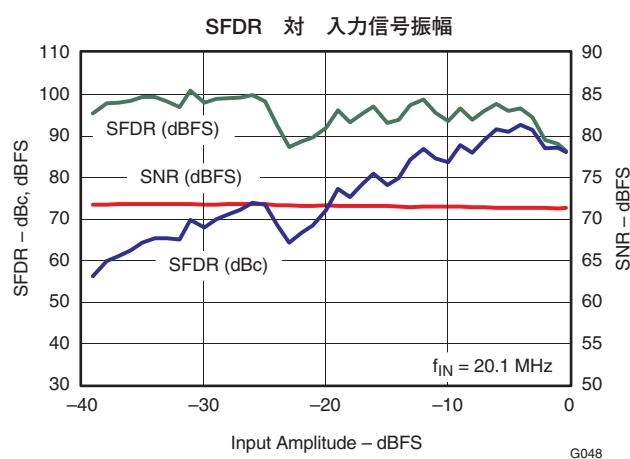

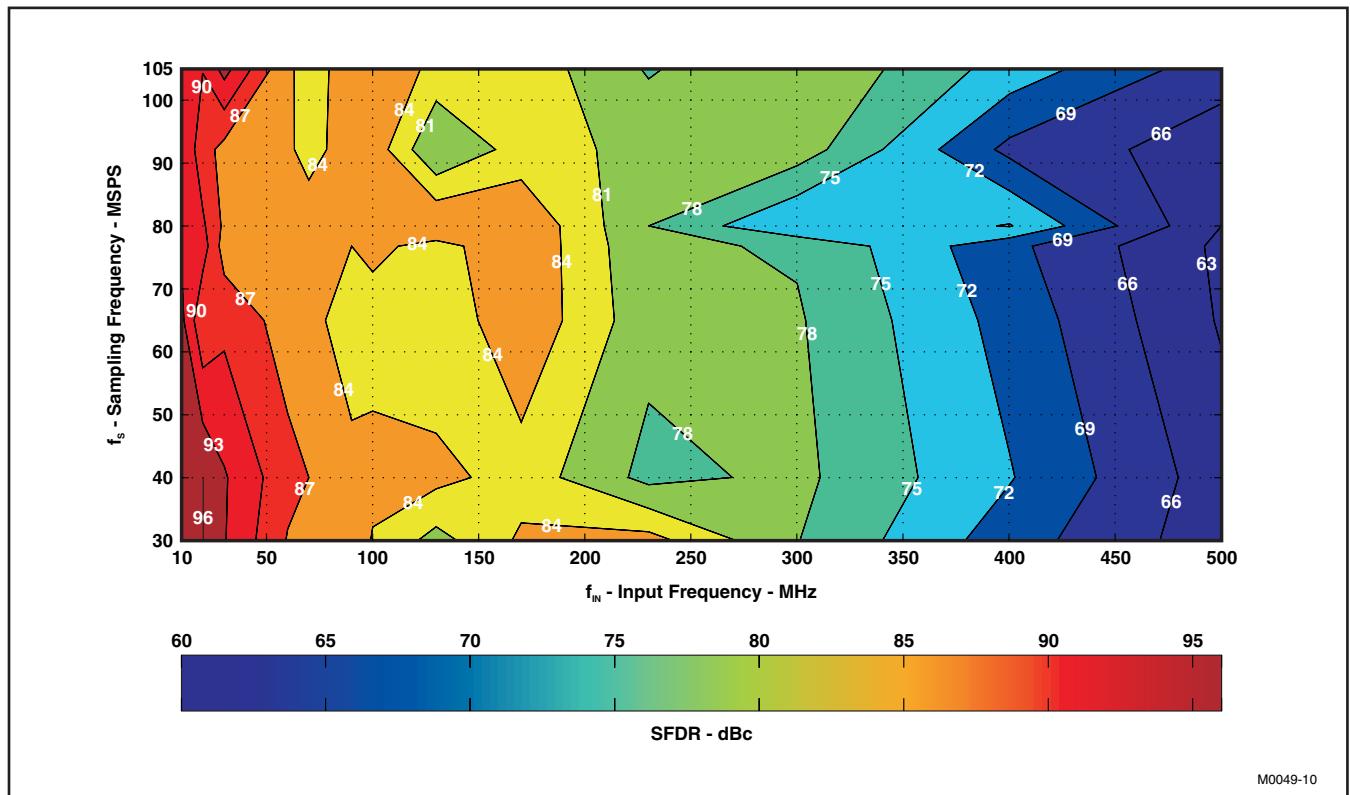

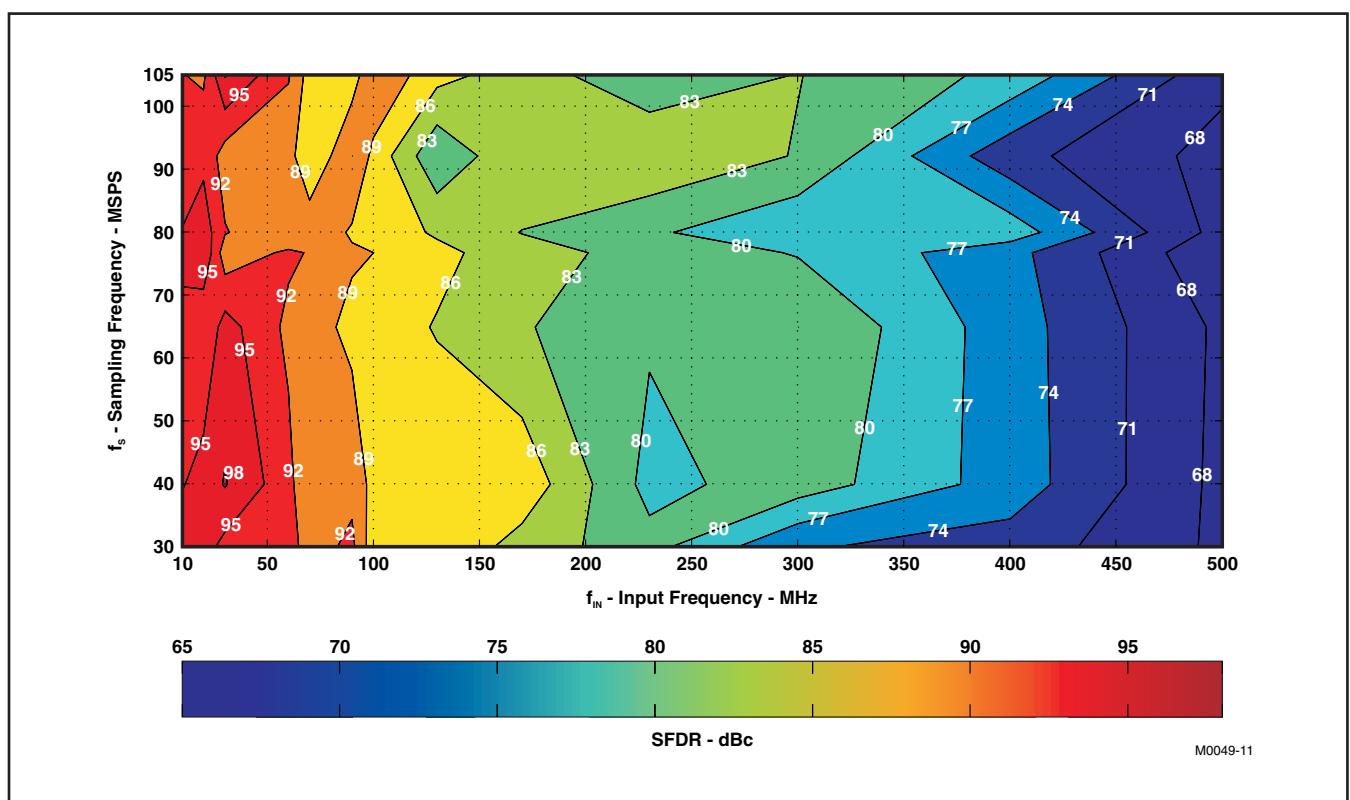

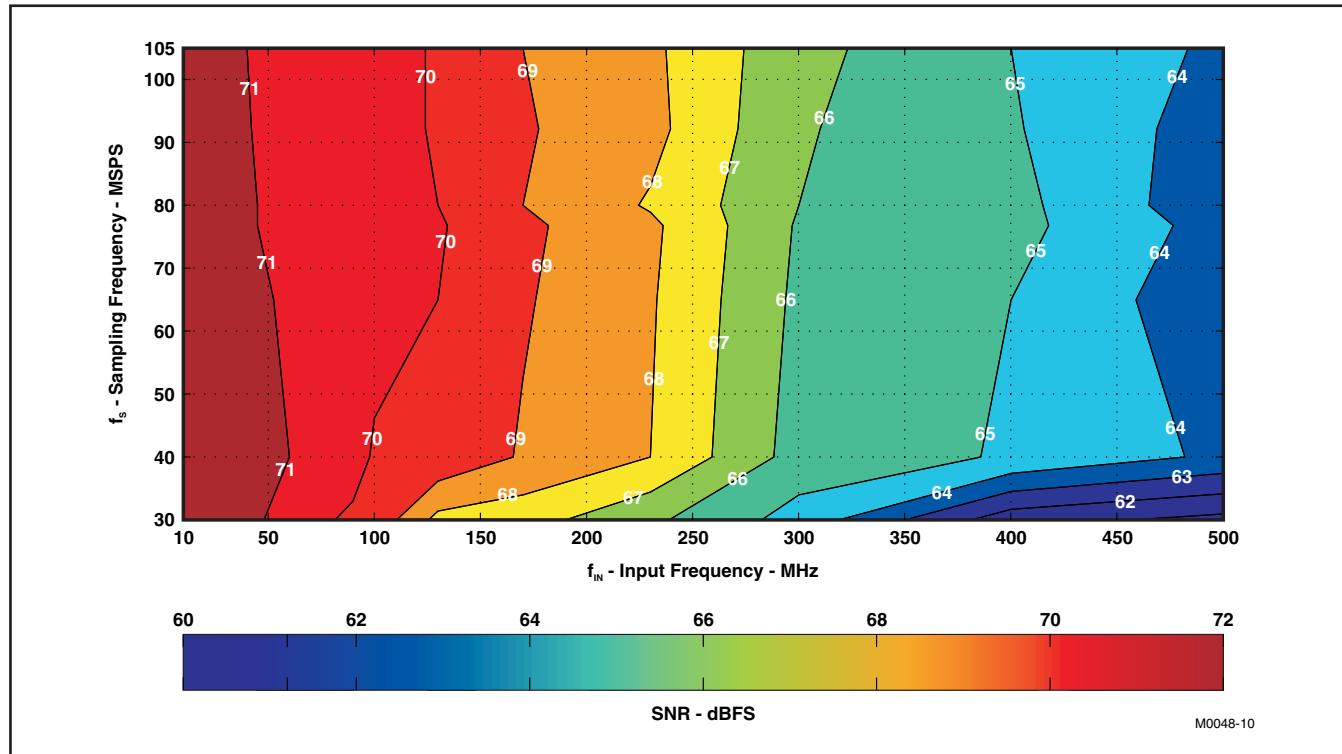

- 3.5dB Coarseゲイン、最大6dBプログラム可変 Fineゲイン、SFDR/SNRトレードオフ

- シリアルLVDS出力、プログラム可能な内部終端オプション

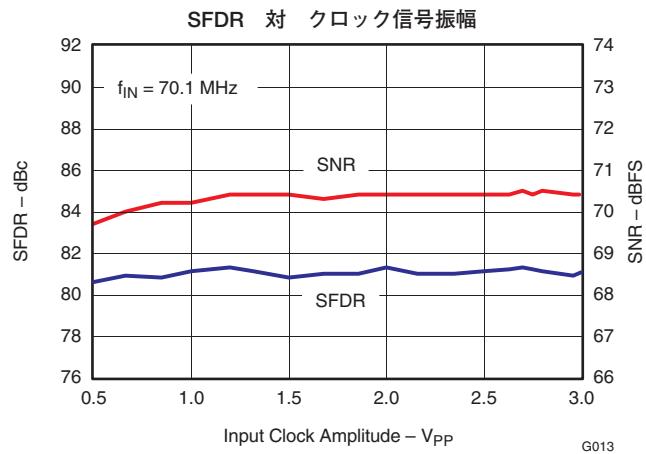

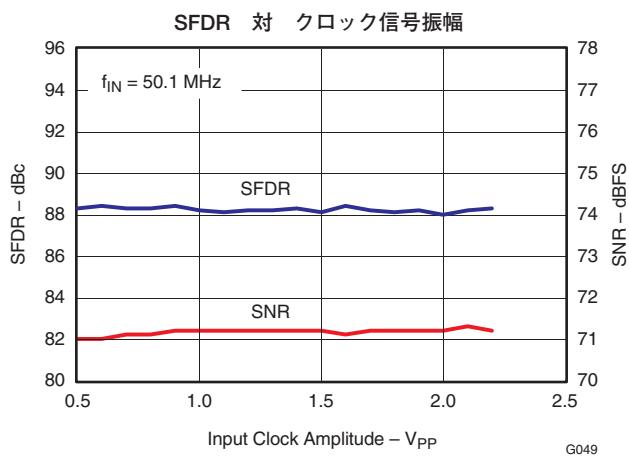

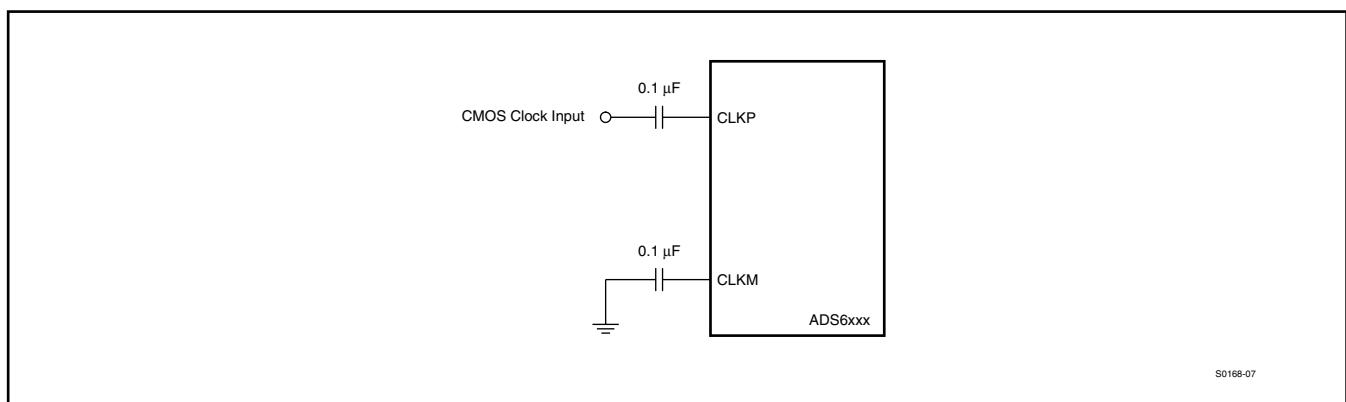

- クロック入力 : 正弦波、LVC MOS、LVPECL、LVDS、最小振幅400mV<sub>pp</sub>

- 内部リファレンス、外部リファレンス

- リファレンス用外部デカッピング不要

- 3.3Vアナログ/デジタル電源

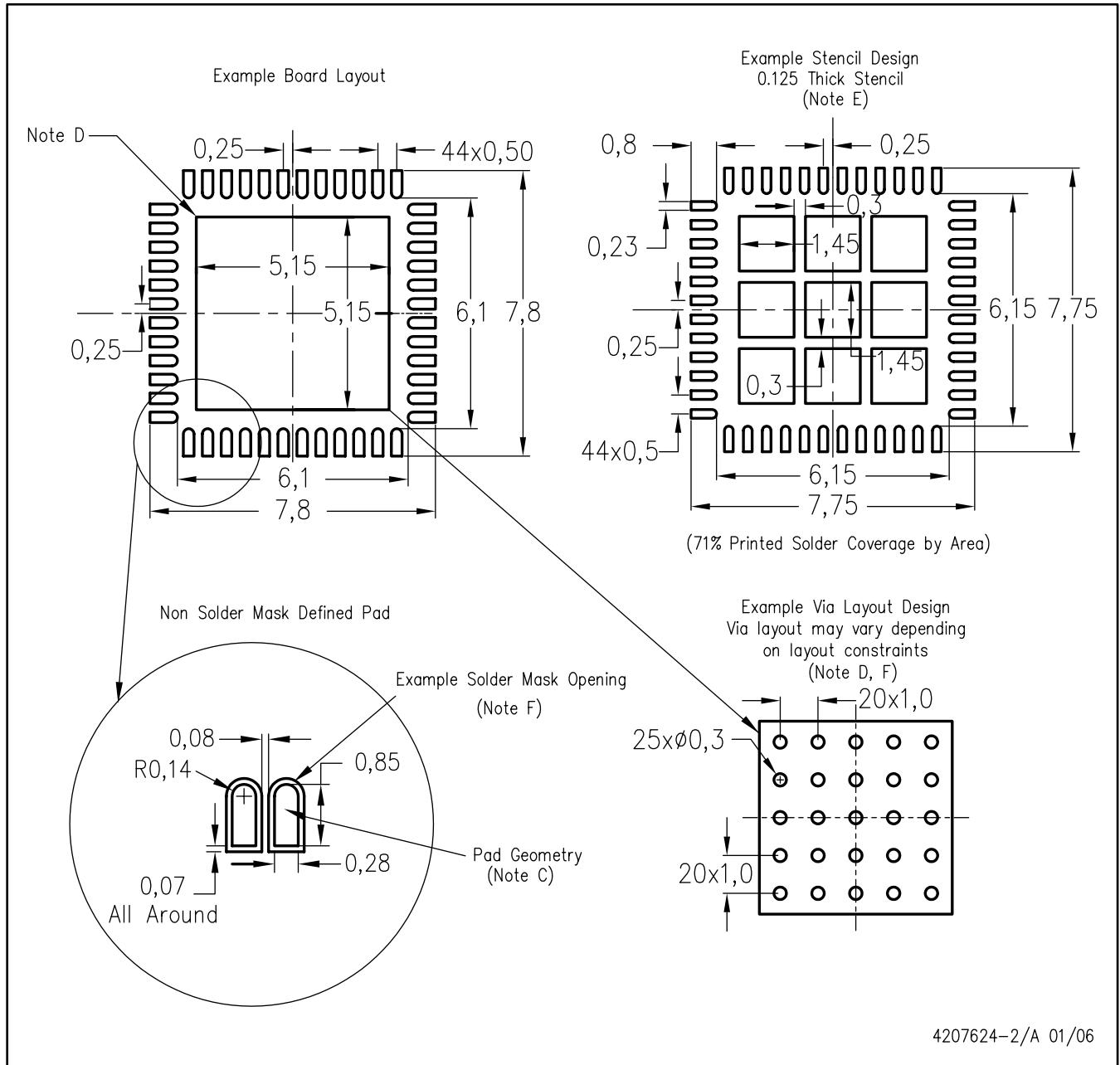

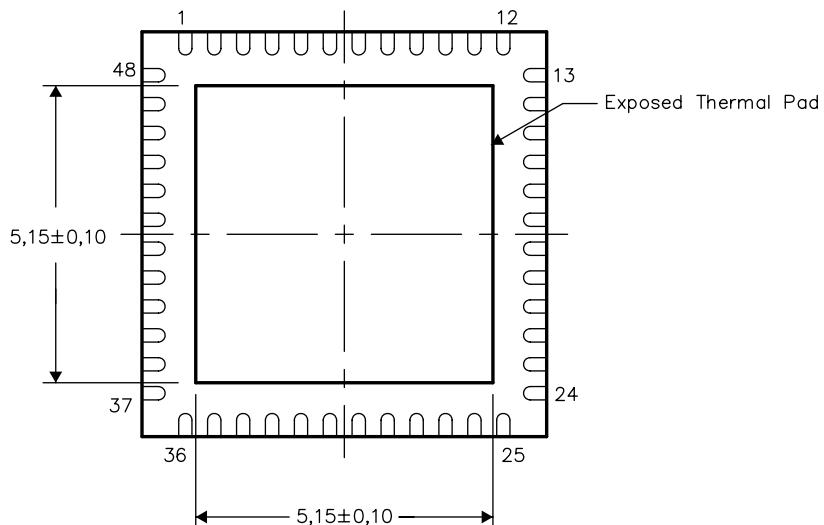

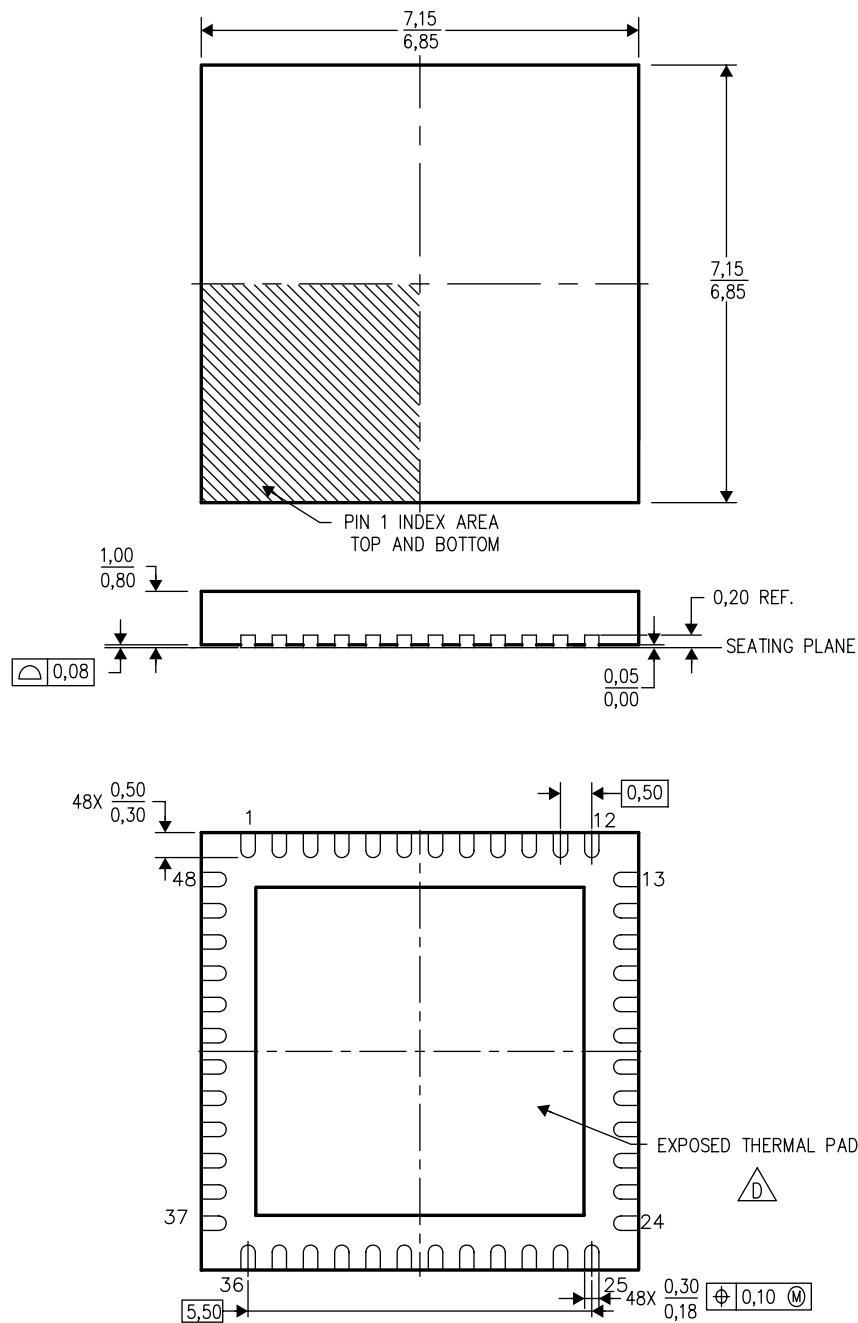

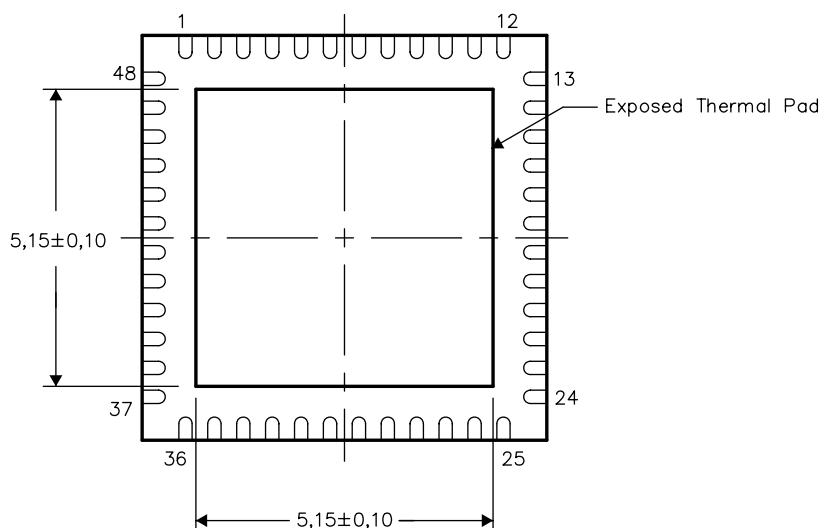

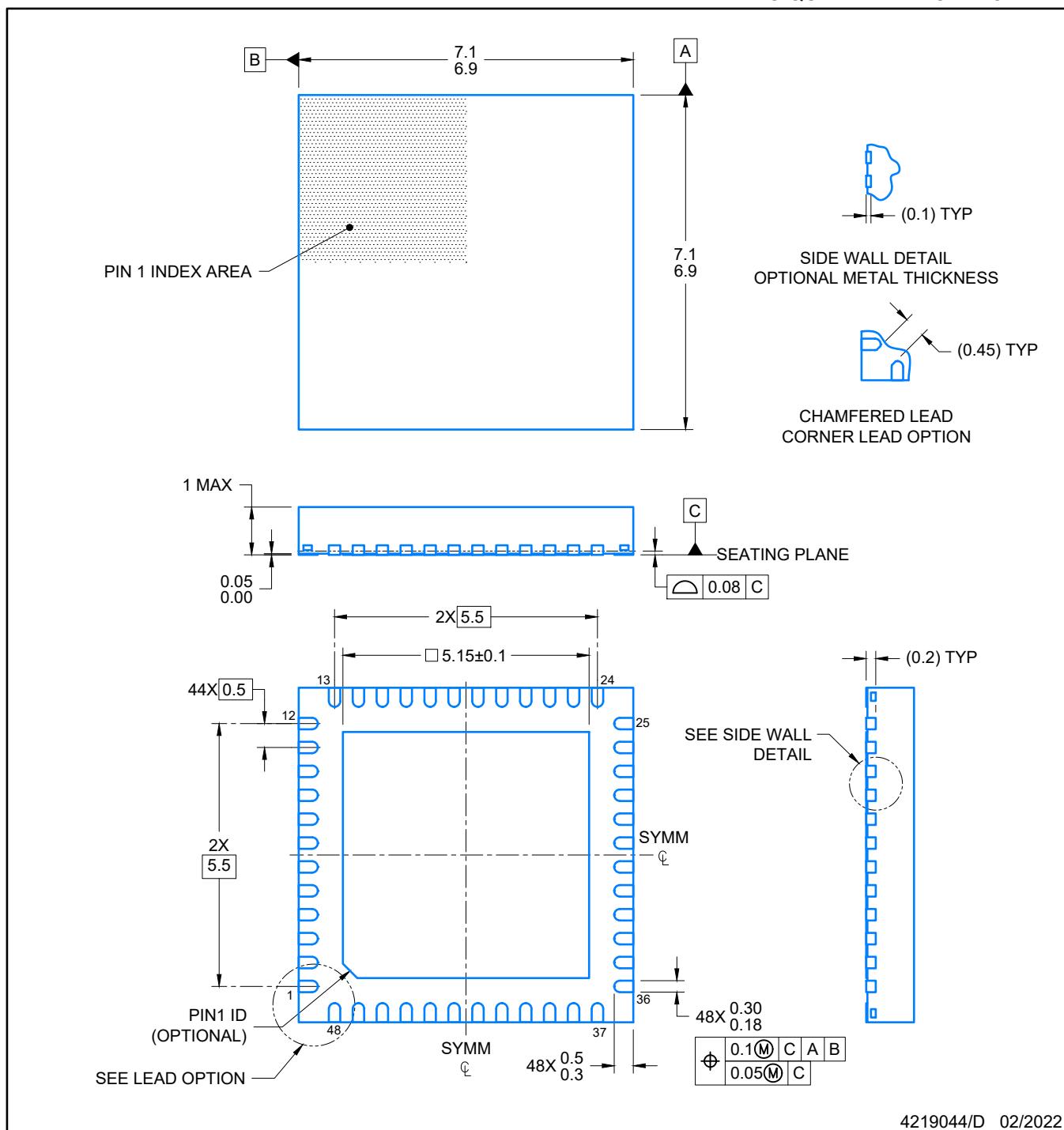

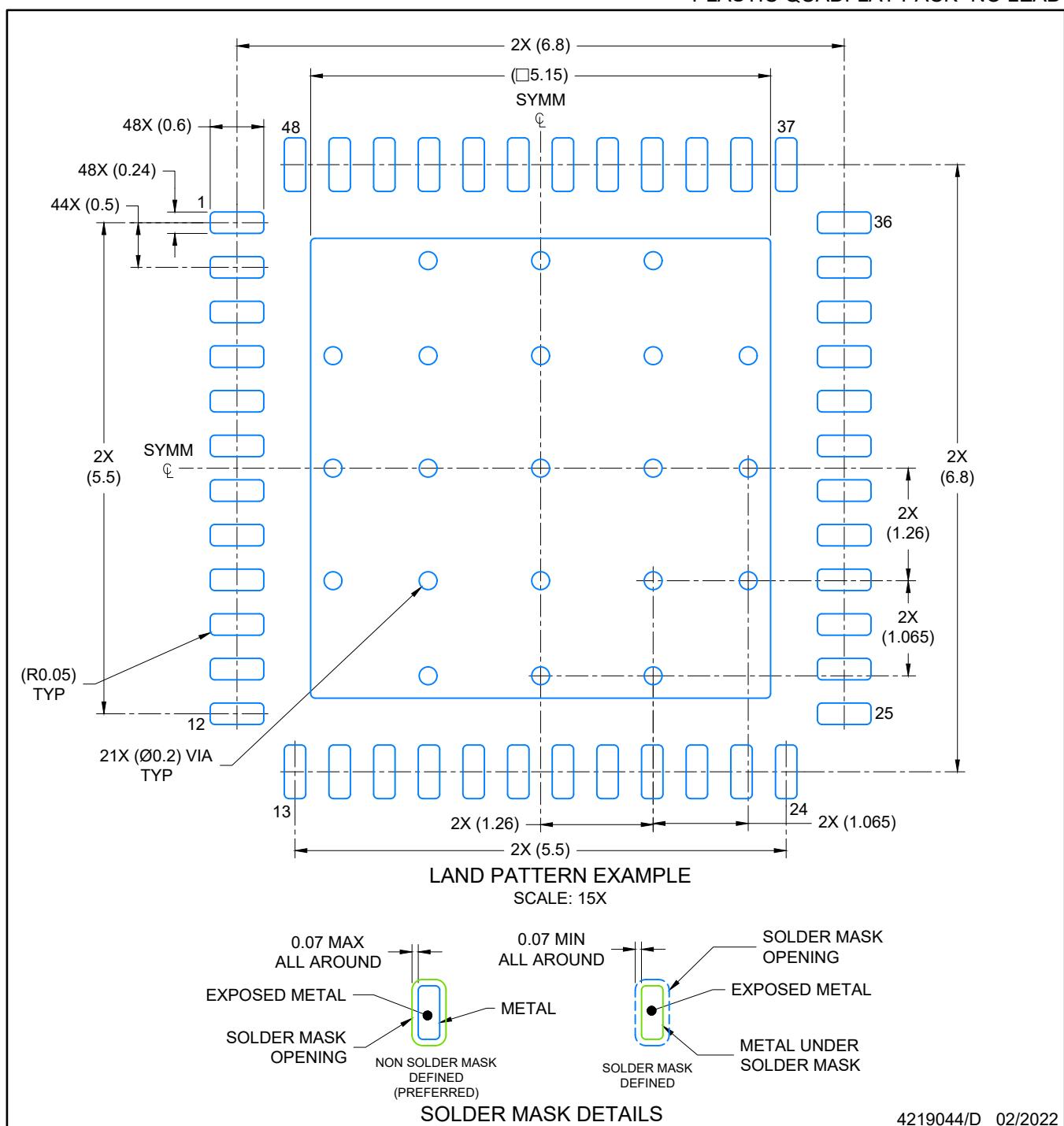

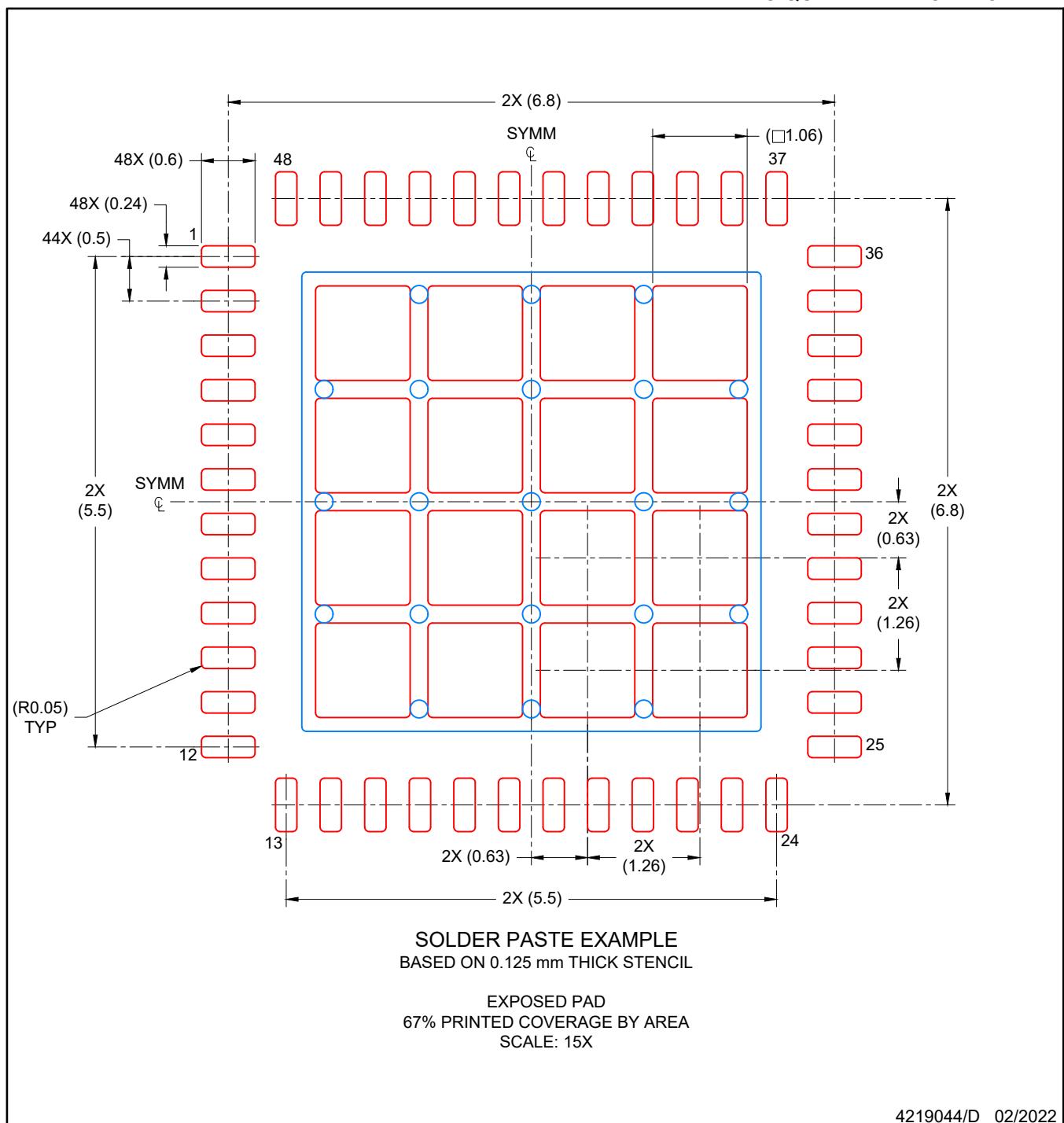

- 48ピンQFNパッケージ (7mm × 7mm)

- ピン・コンパチブルの14ビット・ファミリー (ADS624X - SLAS542)

- 機能互換の4チャネル・ファミリー (ADS644X - SLAS531 およびADS642X - SLAS532)

## ア プ リ ケ シ ョ ン

- 基地局IF受信器

- ダイバーシティ受信器

- 医療用イメージング

- 試験装置

## 概 要

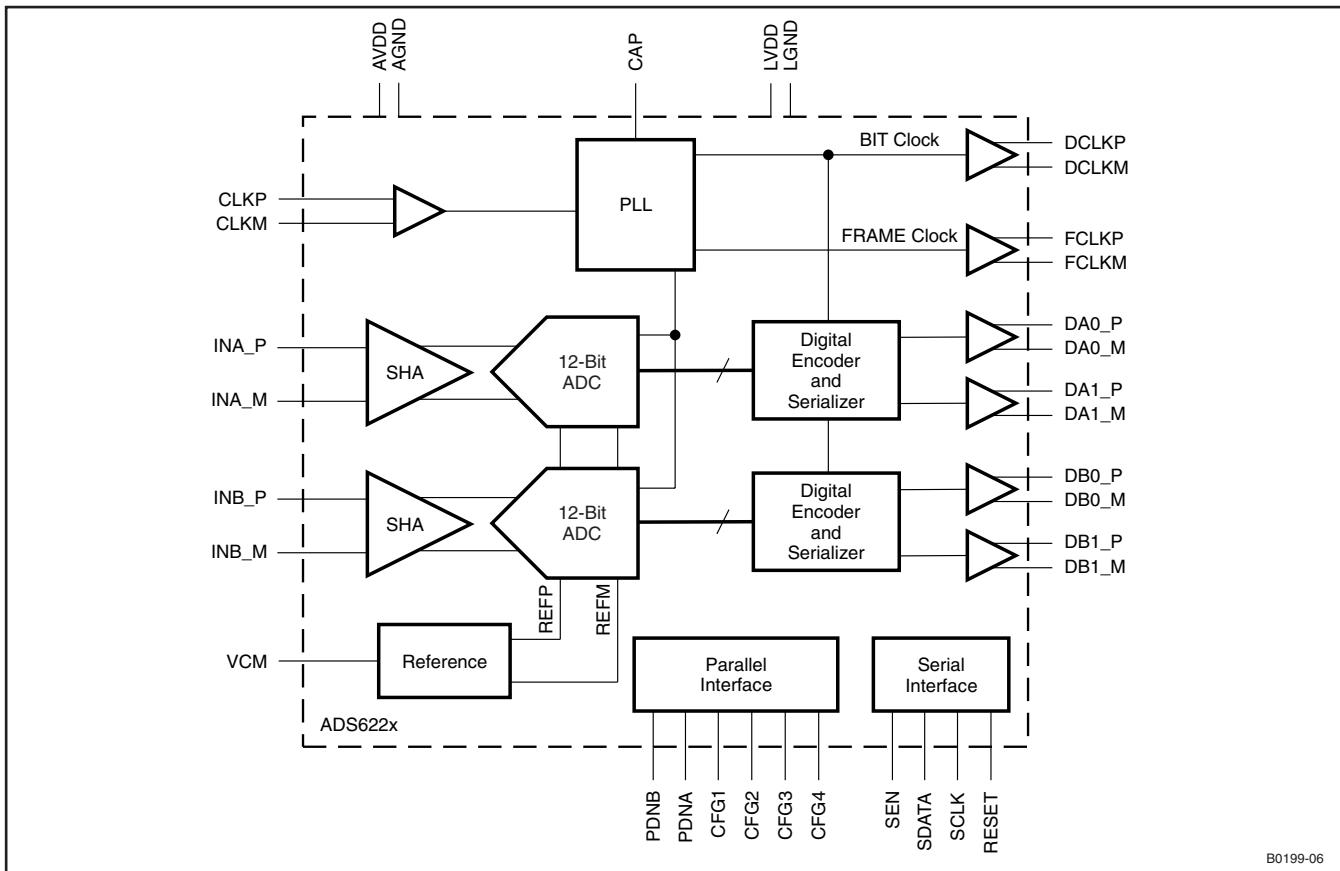

ADS6225/ADS6224/ADS6223/ADS6222 (ADS622X) は、高性能の12ビット125/105/80/65 MSPSデュアル・チャネルA/Dコンバータのファミリーです。シリアルLVDSデータ出力によってインターフェイスのライン数を減らし、コンパクトな48ピンQFNパッケージ (7mm × 7mm) で提供されるため、システム集積密度を高めることができます。3.5dBのCoarseゲイン・オプションにより、SNRをほとんど劣化させることなくSFDR特性の向上が可能です。Coarseゲイン(ゲイン粗調整)に加えて、1dB単位で6dBまでプログラム可能なFineゲイン(ゲイン微調整)・オプションも用意されています。

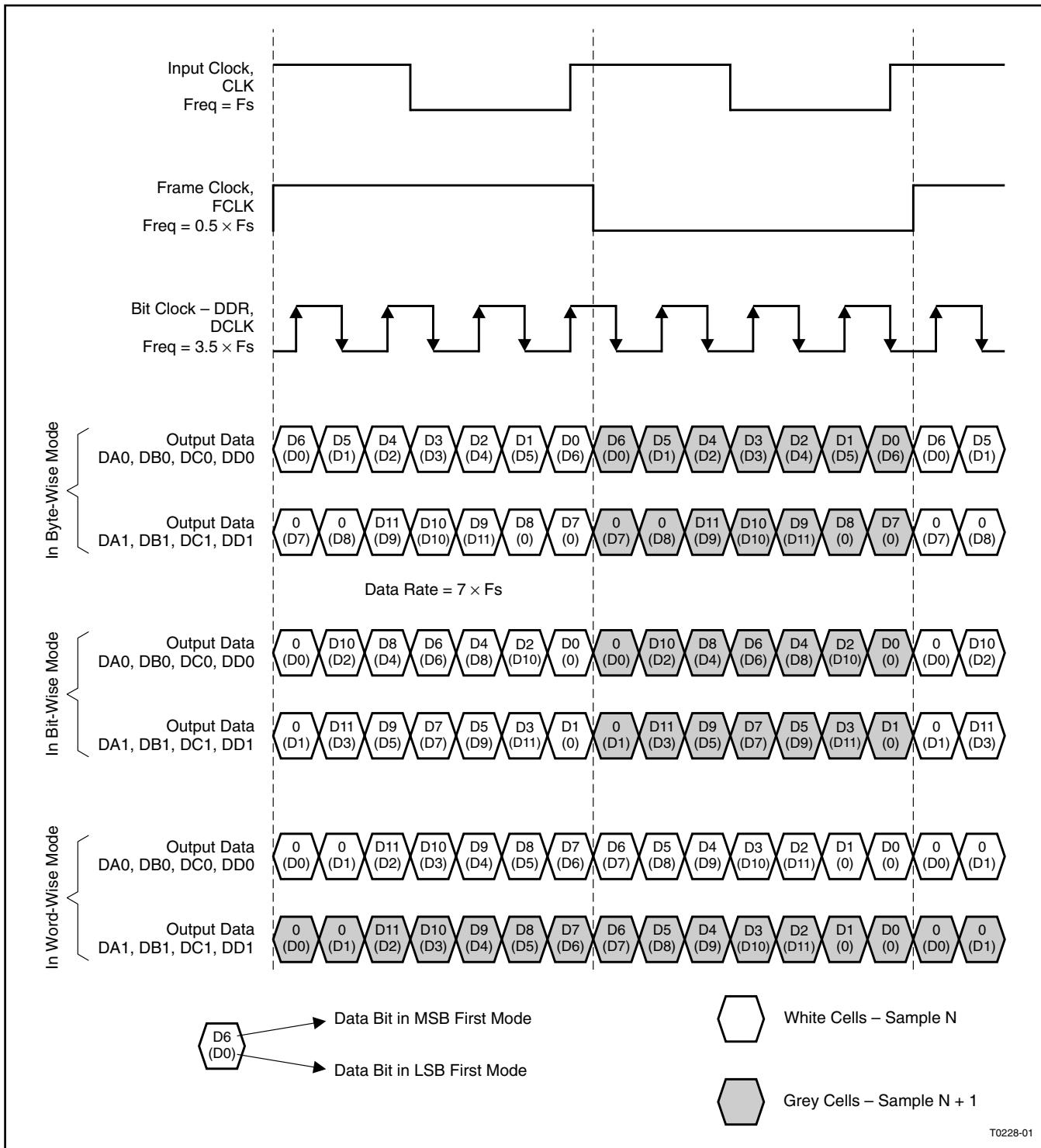

出力インターフェイスは2線式であり、各ADCデータがシリアル化されて2つのLVDSペア信号として出力されます。これにより、シリアル・データ・レートを(1線式インターフェイスと比べて)半分にし、1Gbps未満に制限することが可能となり、受信側の設計が容易になります。また、ADS622Xには、より低いサンプリング周波数用に従来の1線式インターフェイスも備えられています。

|                   | 125 MSPS | 105 MSPS | 80 MSPS | 65 MSPS |

|-------------------|----------|----------|---------|---------|

| ADS624X<br>14 Bit | ADS6245  | ADS6244  | ADS6243 | ADS6242 |

| ADS622X<br>12 Bit | ADS6225  | ADS6224  | ADS6223 | ADS6222 |

表 1. ADS62XXデュアル・チャネル・ファミリー

|               |                            | ADS6225 | ADS6224 | ADS6223 | ADS6222 |

|---------------|----------------------------|---------|---------|---------|---------|

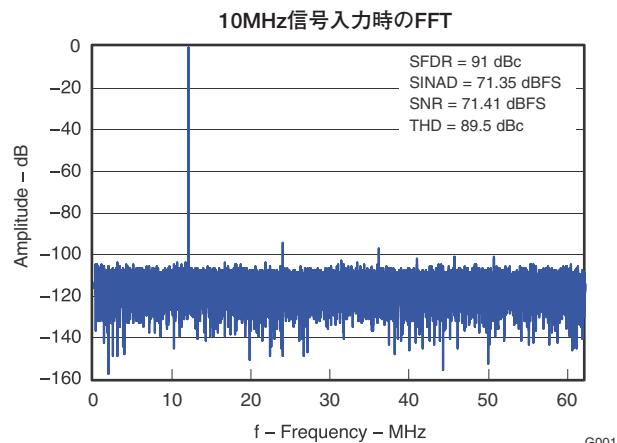

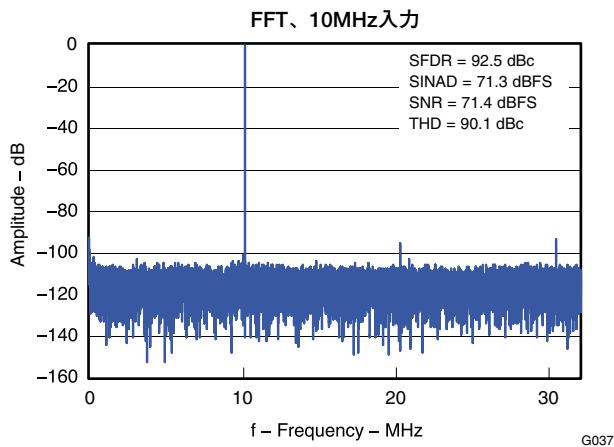

| SFDR, dBc     | Fin = 10MHz (0 dB gain)    | 90      | 91      | 91      | 93      |

|               | Fin = 170MHz (3.5 dB gain) | 79      | 81      | 82      | 83      |

| SINAD, dBFS   | Fin = 10MHz (0 dB gain)    | 70.7    | 70.8    | 71.3    | 71.3    |

|               | Fin = 170MHz (3.5 dB gain) | 67.4    | 68.1    | 68.2    | 68.7    |

| チャネル当り消費電力、mW |                            | 500     | 405     | 350     | 315     |

表 2. 性能一覧

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

最新の英語版資料

<http://focus.ti.com/lit/ds/symlink/ads6225.pdf>

SLAS543A 翻訳版

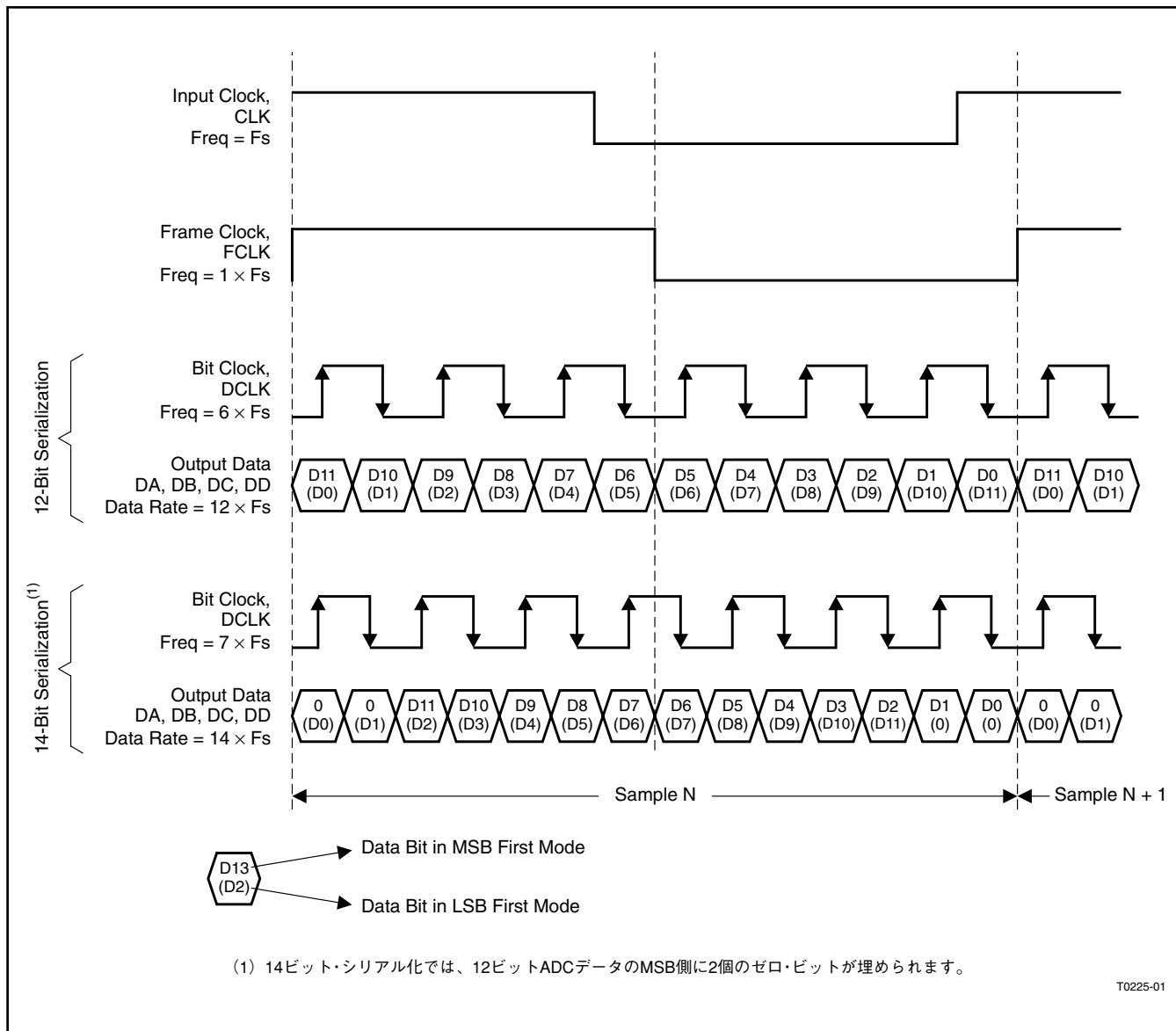

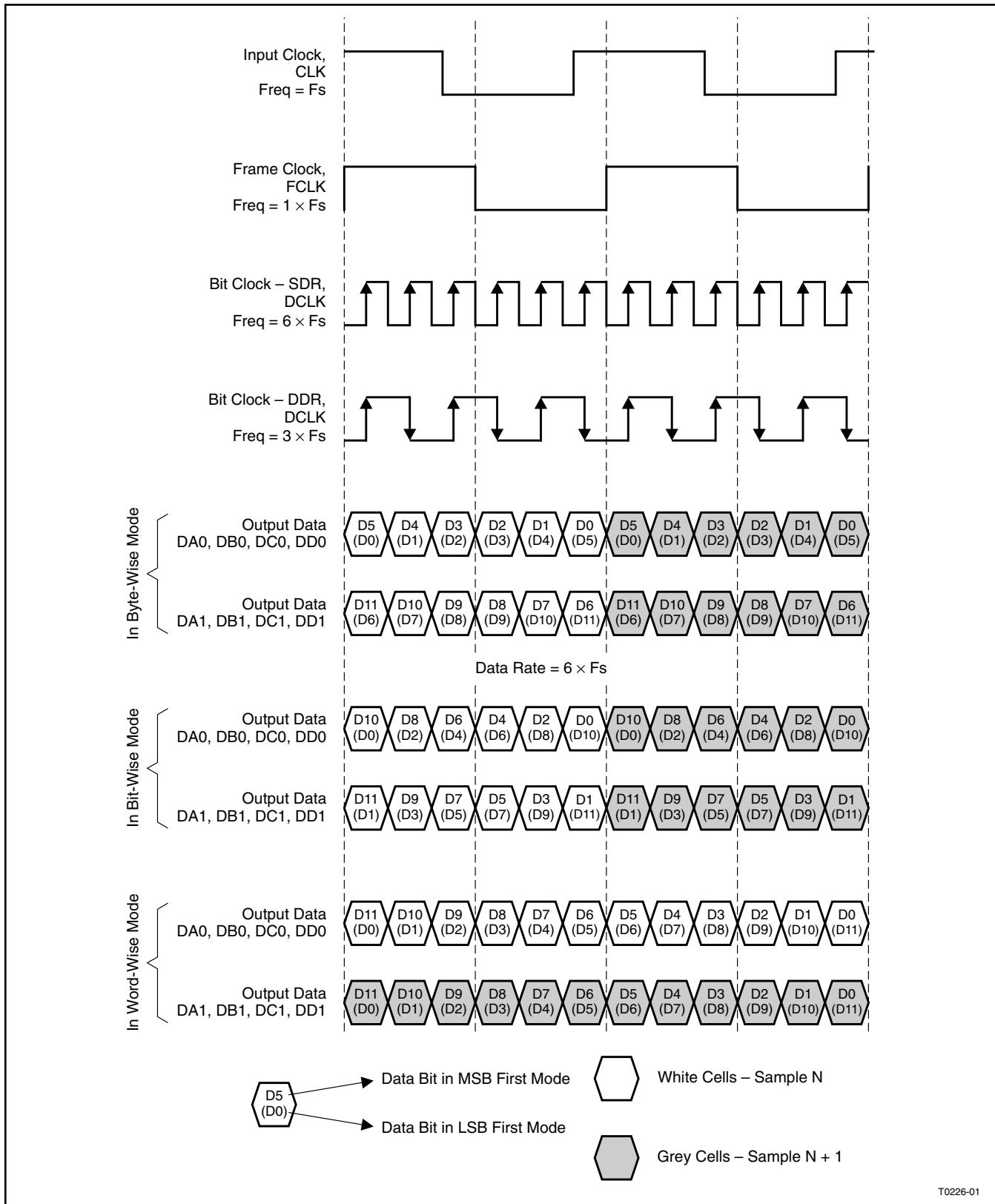

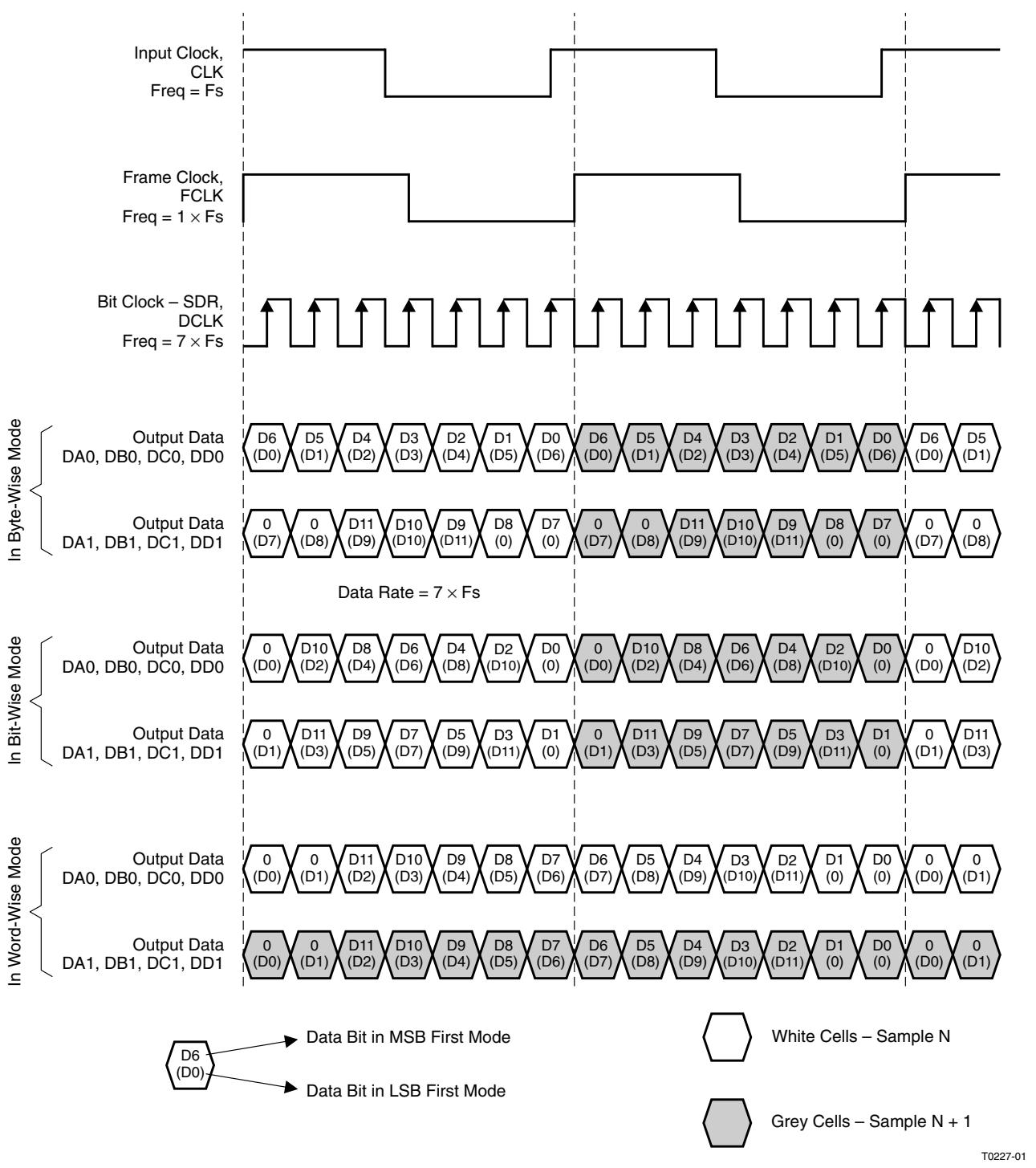

内部のフェーズ・ロック・ループ (PLL) により、ADCサンプリング・クロック入力を倍してビット・クロックを生成します。このビット・クロックを使用して、各チャネルからのADCデータをシリアル化します。シリアル・データ・ストリームに加えて、フレーム・クロックとビット・クロックもLVDS出力として送信されます。LVDS出力バッファには、プログラム可能なLVDS電流や、電流2倍モード、内部終端オプションなどの機能があります。これらの機能を使用して、アイ開口部を広げ、信号の完全性を向上させることで、受信側でのデータの取り込みが容易になります。

ADCチャネル出力は、2の補数またはストレート・バイナリ形式によりMSBファーストまたはLSBファーストで送信できます。

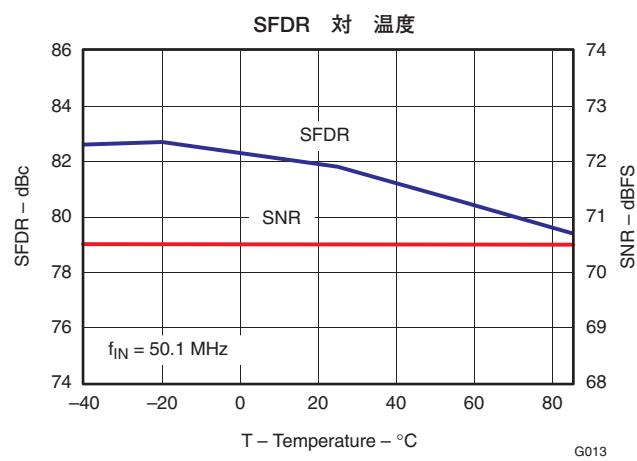

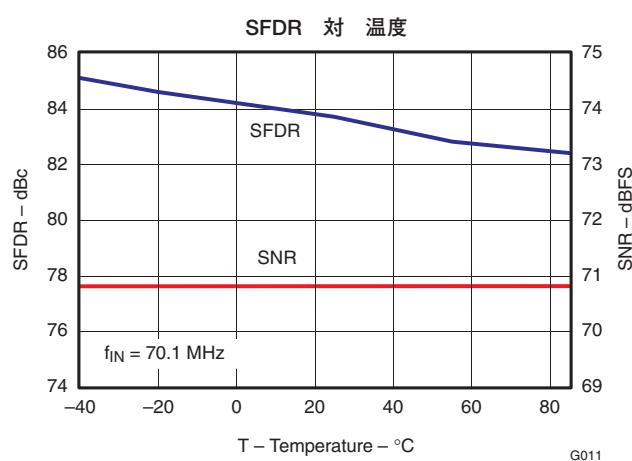

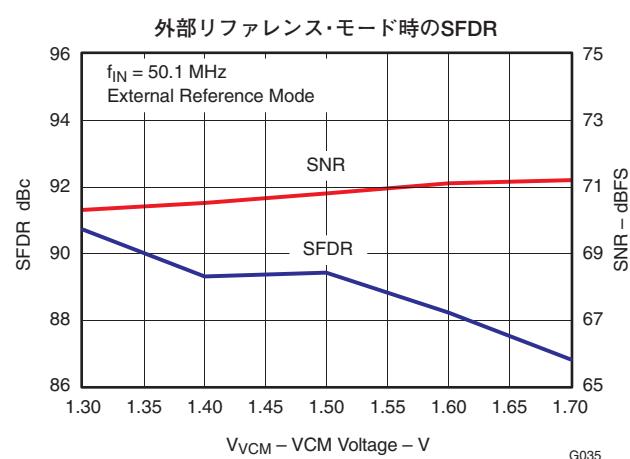

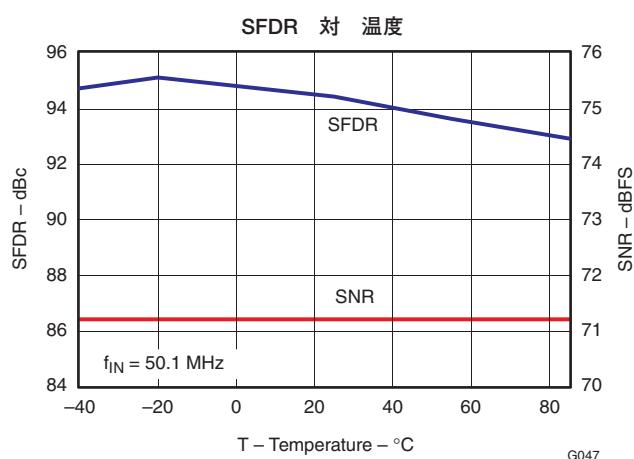

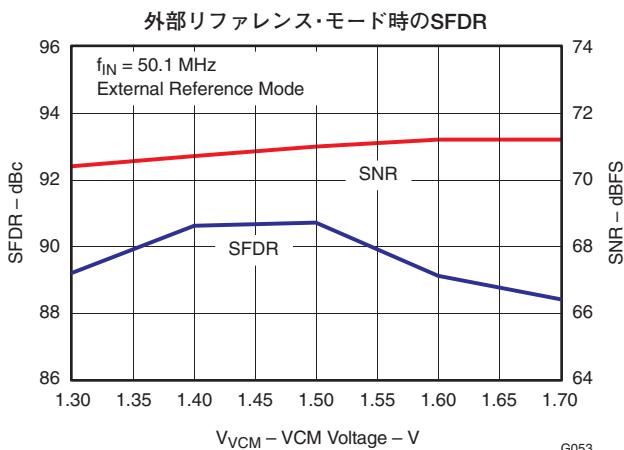

ADS622Xは内部リファレンスを備えていますが、外部リファレンス・モードもサポートできます。デバイスの仕様は、産業用温度範囲 ( $-40^{\circ}\text{C}$ ~ $85^{\circ}\text{C}$ ) で規定されています。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## 製品情報 (1)

| 製品名     | パッケージ                 | パッケージ・コード | 仕様温度範囲       | パッケージ<br>捺印 | 製品型番         | 出荷形態、<br>数量   |

|---------|-----------------------|-----------|--------------|-------------|--------------|---------------|

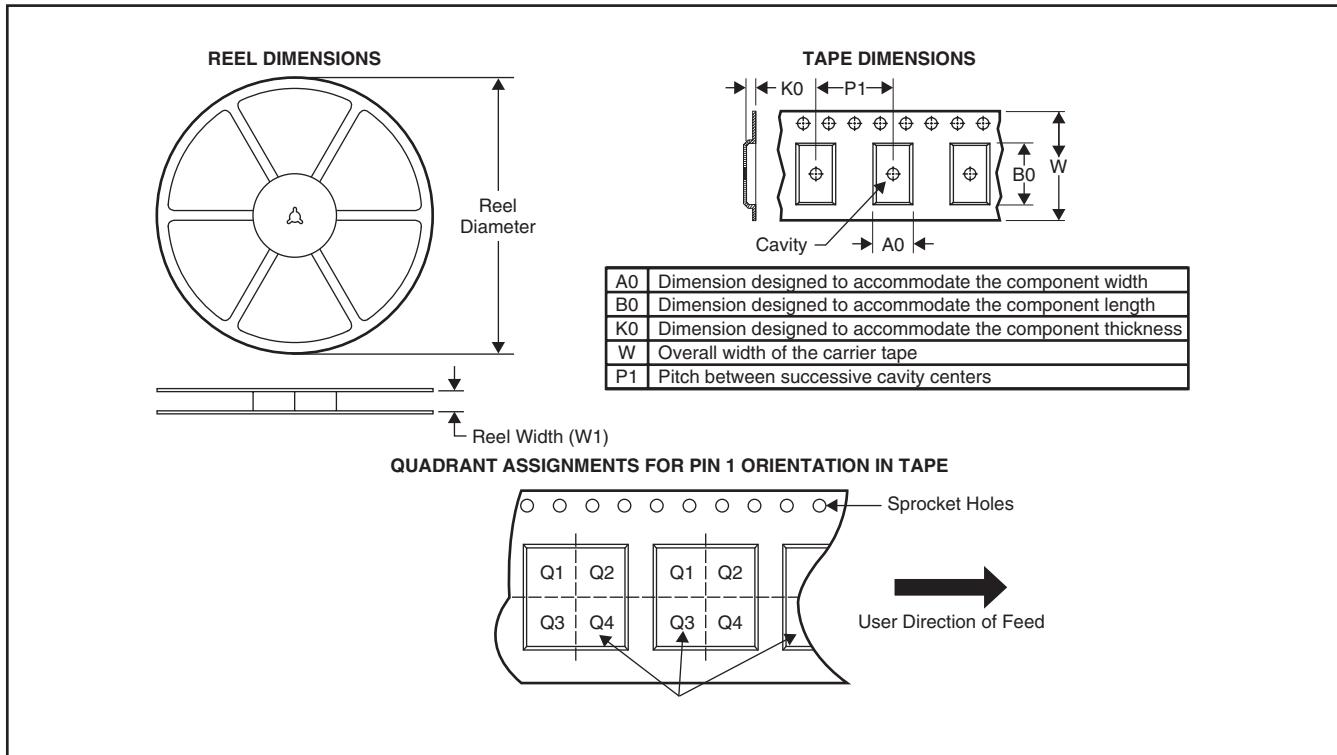

| ADS6225 | QFN-48 <sup>(2)</sup> | RGZ       | −40°C ~ 85°C | AZ6225      | ADS6225IRGZT | テープ・リール, 250  |

|         |                       |           |              |             | ADS6225IRGZR | テープ・リール, 2000 |

| ADS6224 | QFN-48 <sup>(2)</sup> | RGZ       | −40°C ~ 85°C | AZ6224      | ADS6224IRGZT | テープ・リール, 250  |

|         |                       |           |              |             | ADS6224IRGZR | テープ・リール, 2000 |

| ADS6223 | QFN-48 <sup>(2)</sup> | RGZ       | −40°C ~ 85°C | AZ6223      | ADS6223IRGZT | テープ・リール, 250  |

|         |                       |           |              |             | ADS6223IRGZR | テープ・リール, 2000 |

| ADS6222 | QFN-48 <sup>(2)</sup> | RGZ       | −40°C ~ 85°C | AZ6222      | ADS6222IRGZT | テープ・リール, 250  |

|         |                       |           |              |             | ADS6222IRGZR | テープ・リール, 2000 |

(1) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、またはTIのWebサイト([www.tij.co.jp](http://www.tij.co.jp), [www.ti.com](http://www.ti.com))をご覧ください。

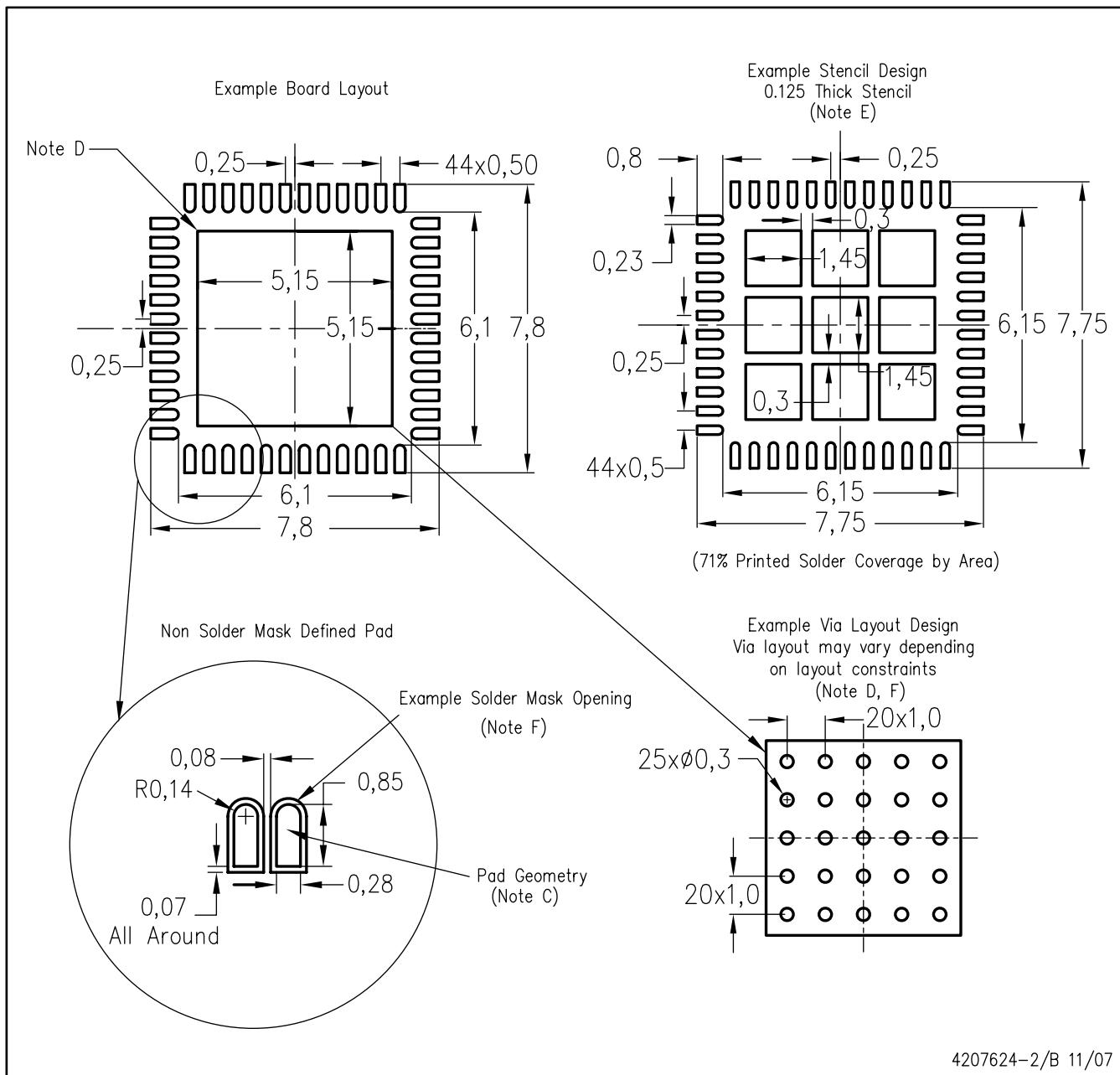

(2) パッケージのサーマル・パッドのサイズについては、このデータシートの巻末にあるメカニカル図面を参照してください。

2オンスの銅トレースを使用し、JEDEC標準の4層3×3インチPCBにパッドを直接半田付けした場合は、 $\theta_{JA} = 23.17^{\circ}\text{C}/\text{W}$  ( $0 \text{ LFM}$ エアフロー)、 $\theta_{JC} = 22.1^{\circ}\text{C}/\text{W}$ です。

## 絶対最大定格<sup>(1)</sup>

|                                      |           | 規定値                                 | 単位 |

|--------------------------------------|-----------|-------------------------------------|----|

| AVDD                                 | 電源電圧      | −0.3 ~ 3.9                          | V  |

| LVDD                                 | 電源電圧      | −0.3 ~ 3.9                          | V  |

| AVDD と LVDD間の電圧                      |           | −0.3 ~ 0.3                          | V  |

| 電圧AVDD 対 LVDD                        |           | −0.3 ~ 3.3                          | V  |

| Voltage applied to external pin, VCM |           | −0.3 ~ 2.0                          | V  |

| アナログ入力電圧                             |           | −0.3V ~ minimum ( 3.6, AVDD + 0.3V) | V  |

| T <sub>A</sub>                       | 動作温度範囲    | −40 ~ 85                            | °C |

| T <sub>J</sub>                       | ジャンクション温度 | 125                                 | °C |

| T <sub>stg</sub>                     | 保存温度      | −65 ~ 150                           | °C |

| 端子温度、ケースから1.6mm (1/16") の点、10sec     |           | 220                                 | °C |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                                       |               | MIN                   | NOM | MAX         | 単位              |

|---------------------------------------|---------------|-----------------------|-----|-------------|-----------------|

| 電源                                    |               |                       |     |             |                 |

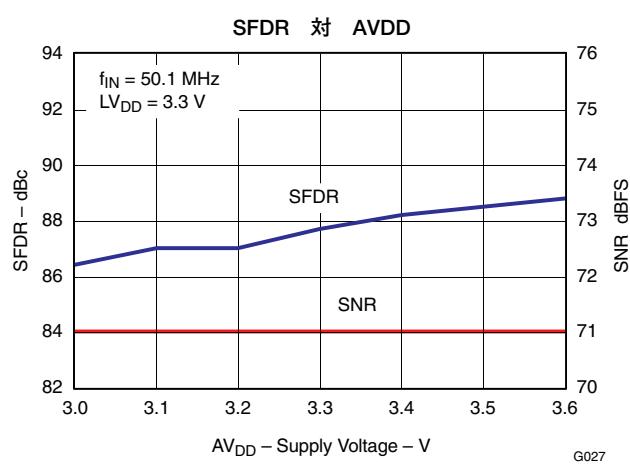

| AVDD                                  | アナログ電源電圧      | 3.0                   | 3.3 | 3.6         | V               |

| LVDD                                  | LVDS バッファ電源電圧 | 3.0                   | 3.3 | 3.6         | V               |

| アナログ入力                                |               |                       |     |             |                 |

| 差動入力電圧範囲                              |               |                       |     | 2           | V <sub>pp</sub> |

| 入力同相電圧                                |               |                       |     | 1.5<br>±0.1 | V               |

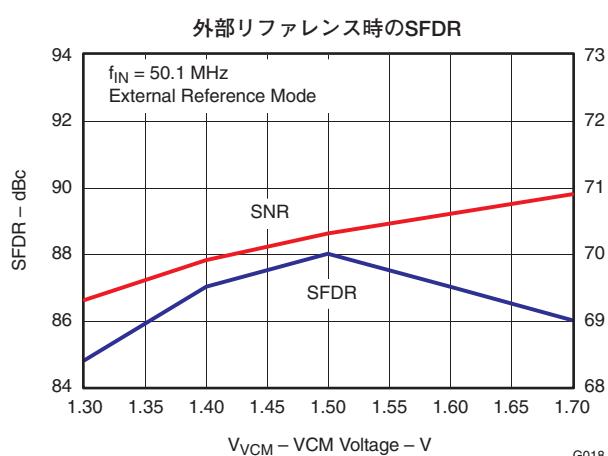

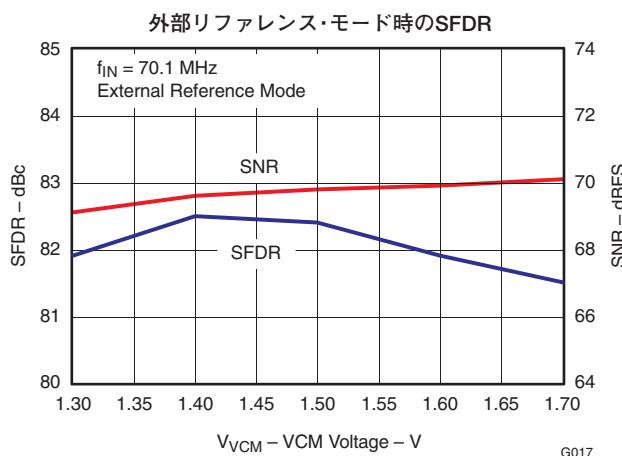

| VCM電圧、外部リファレンス時                       |               |                       |     | 1.45        | 1.50            |

| 1.55 V                                |               |                       |     |             |                 |

| クロック入力                                |               |                       |     |             |                 |

| 入力サンプリング・クロック・レート                     |               | ADS6225               | 5   | 125         |                 |

|                                       |               | ADS6224               | 5   | 105         | MSPS            |

|                                       |               | ADS6223               | 5   | 80          |                 |

|                                       |               | ADS6222               | 5   | 65          |                 |

| 入力クロック差動振幅 ( $V_{CLKP} - V_{CLKM}$ )  |               | Sine wave, ac-coupled | 0.4 | 1.5         |                 |

|                                       |               | LVPECL, ac-coupled    |     | ±0.8        | V <sub>pp</sub> |

|                                       |               | LVDS, ac-coupled      |     | ±0.35       |                 |

|                                       |               | LVCMOS, ac-coupled    |     | 3.3         |                 |

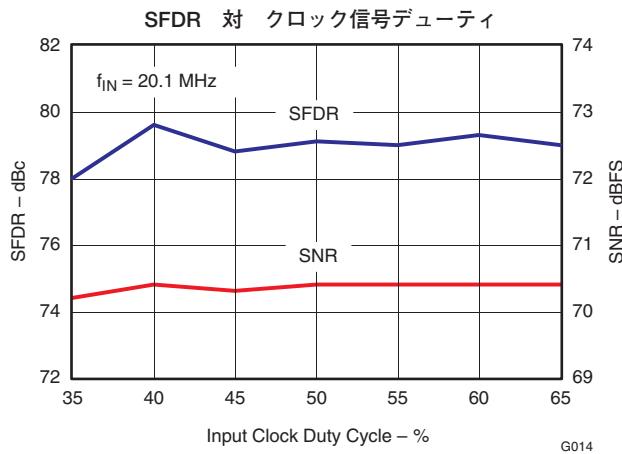

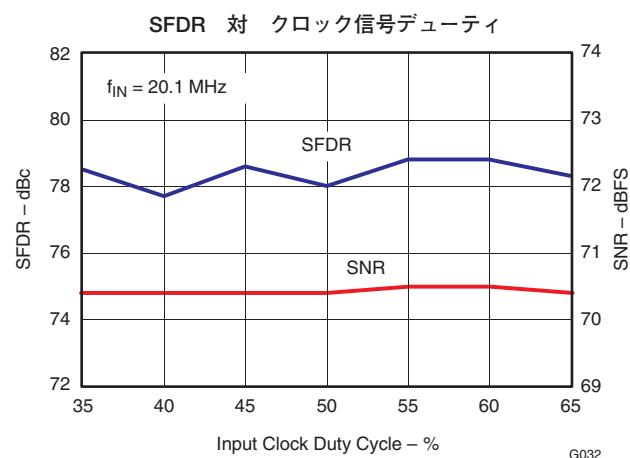

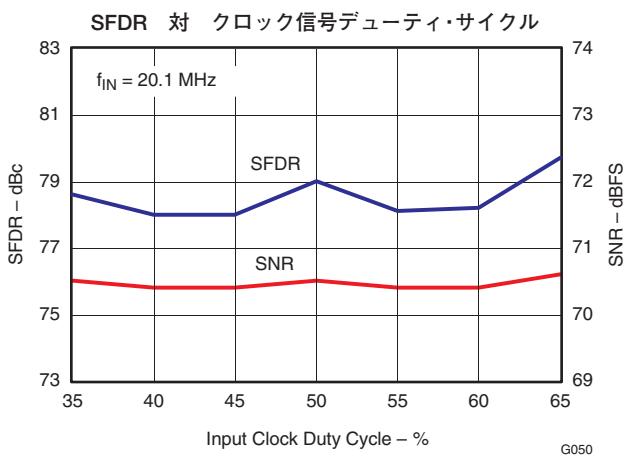

| 入力クロック・デューティ・サイクル                     |               |                       |     | 35%         | 50%             |

| 65%                                   |               |                       |     |             |                 |

| デジタル出力                                |               |                       |     |             |                 |

| C <sub>LOAD</sub> 最大容量性負荷、出力ピン 対 DGND |               | 内部ターミネーション無し          | 5   |             | pF              |

|                                       |               | 内部ターミネーション有り          | 10  |             |                 |

| R <sub>LOAD</sub>                     | LVDS出力差動負荷抵抗  |                       | 100 |             | Ω               |

| T <sub>A</sub>                        | 動作温度          |                       | -40 | 85          | °C              |

## 電気的特性

TYP値は25°C、最小値および最大値はT<sub>MIN</sub> = -40°C～T<sub>MAX</sub> = 85°Cの全温度範囲、AVDD = LVDD = 3.3 V、最大定格サンプリング周波数、50%のクロック・デューティ・サイクル、-1dBFSの差動アナログ入力、内部リファレンス・モード(特に記述のない限り)。

| パラメータ                  | ADS6225<br>$F_s = 125 \text{ MSPS}$ |     |     | ADS6224<br>$F_s = 105 \text{ MSPS}$ |     |     | ADS6223<br>$F_s = 80 \text{ MSPS}$ |     |     | ADS6222<br>$F_s = 65 \text{ MSPS}$ |     |     | 単位              |

|------------------------|-------------------------------------|-----|-----|-------------------------------------|-----|-----|------------------------------------|-----|-----|------------------------------------|-----|-----|-----------------|

|                        | MIN                                 | TYP | MAX | MIN                                 | TYP | MAX | MIN                                | TYP | MAX | MIN                                | TYP | MAX |                 |

| 分解能                    | 12                                  |     |     | 12                                  |     |     | 12                                 |     |     | 12                                 |     |     | Bits            |

| アナログ入力                 |                                     |     |     |                                     |     |     |                                    |     |     |                                    |     |     |                 |

| 差動入力電圧範囲               | 2.0                                 | 2.0 | 2.0 | 2.0                                 | 2.0 | 2.0 | 2.0                                | 2.0 | 2.0 | 2.0                                | 2.0 | 2.0 | V <sub>pp</sub> |

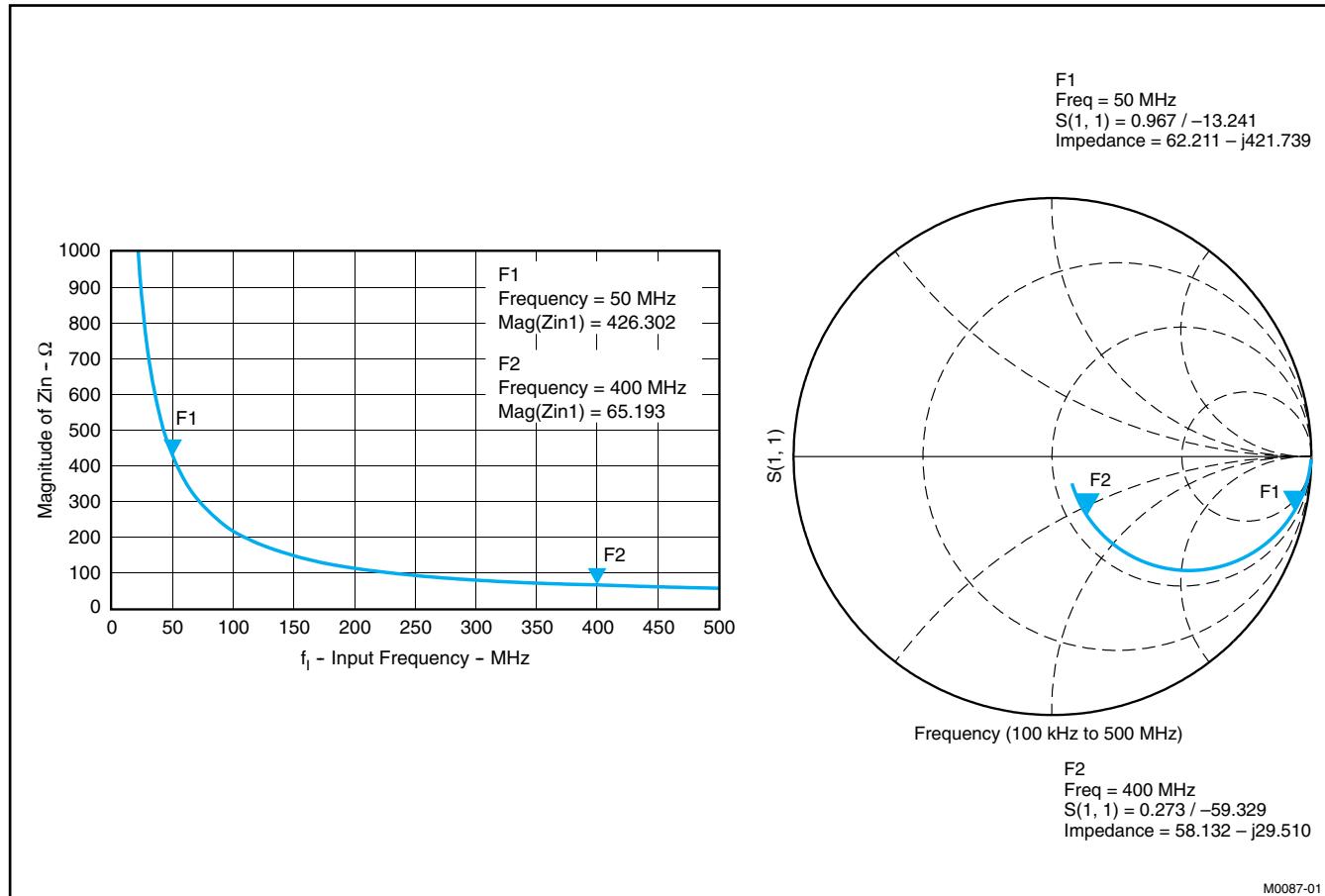

| 差動入力容量                 | 7                                   | 7   | 7   | 7                                   | 7   | 7   | 7                                  | 7   | 7   | 7                                  | 7   | 7   | pF              |

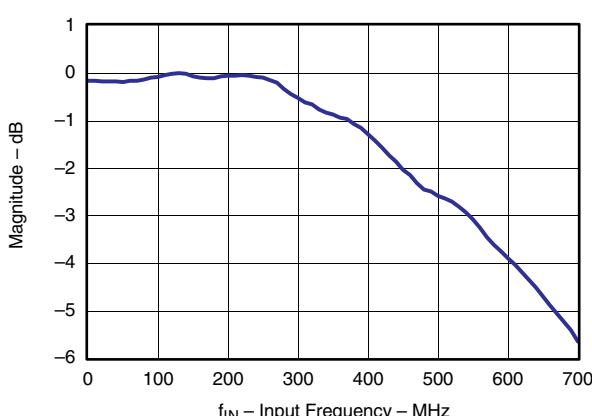

| アナログ入力バンド幅             | 500                                 | 500 | 500 | 500                                 | 500 | 500 | 500                                | 500 | 500 | 500                                | 500 | 500 | MHz             |

| アナログ入力同相電流 (ADC入力ピン当り) | 155                                 | 155 | 155 | 130                                 | 130 | 130 | 100                                | 100 | 100 | 81                                 | 81  | 81  | μA              |

| リファレンス電圧               |                                     |     |     |                                     |     |     |                                    |     |     |                                    |     |     |                 |

| VREFB                  | 内部リファレンス・ボトム電圧                      | 1.0 | 1.0 | 1.0                                 | 1.0 | 1.0 | 1.0                                | 1.0 | 1.0 | 1.0                                | 1.0 | 1.0 | V               |

| VREFT                  | 内部リファレンス・トップ電圧                      | 2.0 | 2.0 | 2.0                                 | 2.0 | 2.0 | 2.0                                | 2.0 | 2.0 | 2.0                                | 2.0 | 2.0 | V               |

| ΔV <sub>REF</sub>      | 内部リファレンス誤差 (VREFT-VREFB)            | -15 | ±2  | 15                                  | -15 | ±2  | 15                                 | -15 | ±2  | 15                                 | -15 | ±2  | 15              |

| VCM                    | 同相出力電圧                              | 1.5 | 1.5 | 1.5                                 | 1.5 | 1.5 | 1.5                                | 1.5 | 1.5 | 1.5                                | 1.5 | 1.5 | V               |

## 電気的特性

TYP値は25°C、最小値および最大値はT<sub>MIN</sub> = -40°C～T<sub>MAX</sub> = 85°Cの全温度範囲、AVDD = LVDD = 3.3 V、最大定格サンプリング周波数、50%のクロック・デューティ・サイクル、-1dBFSの差動アナログ入力、内部リファレンス・モード(特に記述のない限り)。

| パラメータ                                                           | ADS6225<br>F <sub>s</sub> = 125 MSPS |       |      | ADS6224<br>F <sub>s</sub> = 105 MSPS |       |      | ADS6223<br>F <sub>s</sub> = 80 MSPS |       |      | ADS6222<br>F <sub>s</sub> = 65 MSPS |      |      | 単位    |

|-----------------------------------------------------------------|--------------------------------------|-------|------|--------------------------------------|-------|------|-------------------------------------|-------|------|-------------------------------------|------|------|-------|

|                                                                 | MIN                                  | TYP   | MAX  | MIN                                  | TYP   | MAX  | MIN                                 | TYP   | MAX  | MIN                                 | TYP  | MAX  |       |

| VCM出力電流                                                         | 4                                    |       |      | 4                                    |       |      | 4                                   |       |      | 4                                   |      |      | mA    |

| <b>DC ACCURACY</b>                                              |                                      |       |      |                                      |       |      |                                     |       |      |                                     |      |      |       |

| ノード・ミッシング・コード                                                   | 12                                   |       |      | 12                                   |       |      | 12                                  |       |      | 12                                  |      |      | bit   |

| E <sub>O</sub> オフセット誤差                                          | -15                                  | ±2    | 15   | -15                                  | ±2    | 15   | -15                                 | ±2    | 15   | -15                                 | ±2   | 15   | mV    |

| オフセット・ドリフト                                                      | 0.05                                 |       |      | 0.05                                 |       |      | 0.05                                |       |      | 0.05                                |      |      | mV/°C |

| ゲイン誤差は内部リファレンス精度とゲイン誤差の和                                        |                                      |       |      |                                      |       |      |                                     |       |      |                                     |      |      |       |

| E <sub>GREF</sub> 内部リファレンス精度依存ゲイン誤差( $\Delta V_{REF} / 2.0\%$ ) | -0.75                                | ±0.1  | 0.75 | -0.75                                | ±0.1  | 0.75 | -0.75                               | ±0.1  | 0.75 | -0.75                               | ±0.1 | 0.75 | % FS  |

| ゲイン・ドリフト                                                        | 0.0125                               |       |      | 0.0125                               |       |      | 0.0125                              |       |      | 0.0125                              |      |      | Δ%/°C |

| E <sub>GCHAN</sub> ゲイン誤差(チャネル間、デバイス間) <sup>(1)</sup>            | -1                                   | ±0.3  | 1    | -1                                   | ±0.3  | 1    | -1                                  | ±0.3  | 1    | -1                                  | ±0.3 | 1    | % FS  |

| チャネル・ゲイン誤差<br>温度係数(チャネル間およびデバイス間)                               | 0.005                                |       |      | 0.005                                |       |      | 0.005                               |       |      | 0.005                               |      |      | Δ%/°C |

| DNL 微分非直線性                                                      | -0.95                                | ±0.5  | 2.0  | -0.95                                | ±0.5  | 2.0  | -0.9                                | ±0.4  | 1.8  | -0.9                                | ±0.4 | 1.8  | LSB   |

| INL 積分非直線性                                                      | -2.5                                 | ±1.25 | 2.5  | -2.2                                 | ±1.25 | 2.2  | -2.0                                | ±1.25 | 2.0  | -2.0                                | ±1.0 | 2.0  | LSB   |

| PSRR DC電源除去比                                                    | 0.5                                  |       |      | 0.5                                  |       |      | 0.5                                 |       |      | 0.5                                 |      |      | mV/V  |

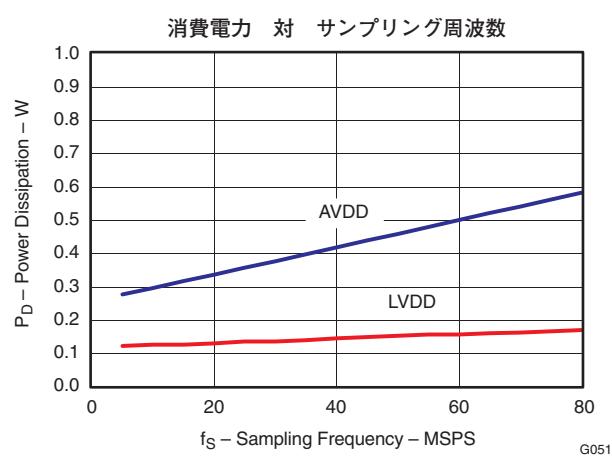

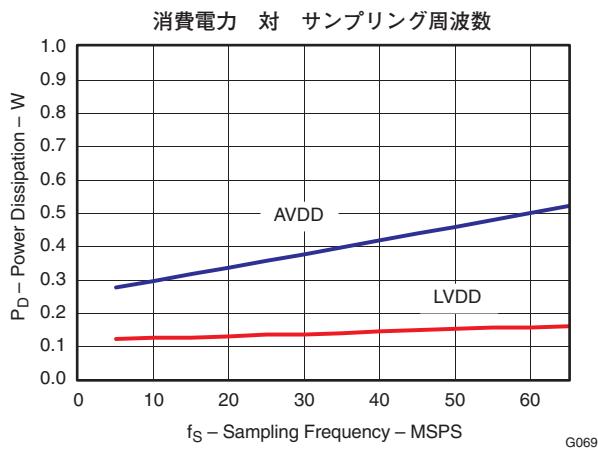

| <b>電源</b>                                                       |                                      |       |      |                                      |       |      |                                     |       |      |                                     |      |      |       |

| I <sub>CC</sub> 全電源電流                                           | 300                                  |       |      | 245                                  |       |      | 210                                 |       |      | 190                                 |      |      | mA    |

| I <sub>AVDD</sub> アナログ電源電流                                      | 237                                  |       |      | 185                                  |       |      | 155                                 |       |      | 140                                 |      |      | mA    |

| I <sub>LVDD</sub> LVDS電源電流                                      | 63                                   |       |      | 60                                   |       |      | 55                                  |       |      | 50                                  |      |      | mA    |

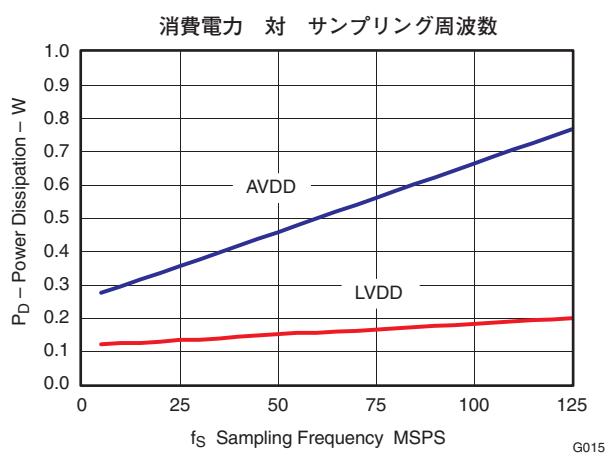

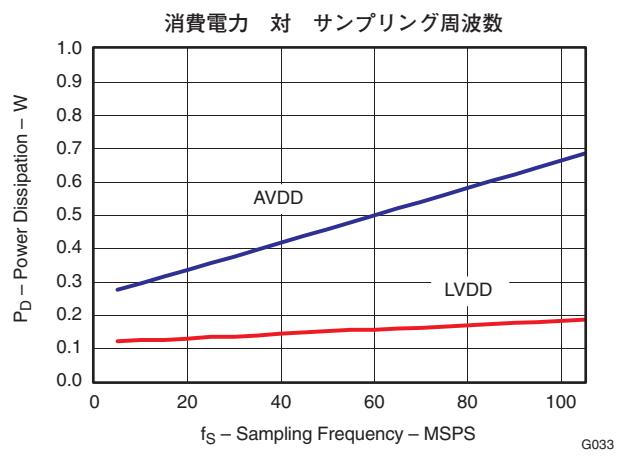

| 全消費電力                                                           | 1.0                                  | 1.2   |      | 0.81                                 | 0.97  |      | 0.7                                 | 0.85  |      | 0.63                                | 0.8  |      | W     |

| パワーダウン消費電力<br>(入力クロック停止時)                                       | 77                                   | 150   |      | 77                                   | 150   |      | 77                                  | 150   |      | 77                                  | 150  |      | mW    |

(1) これは設計で規定される値であり、実製品のテストは行っていません。

## 電気的特性

TYP値は25°C、最小値および最大値はT<sub>MIN</sub> = -40°C～T<sub>MAX</sub> = 85°Cの全温度範囲、AVDD = LVDD = 3.3 V、最大定格サンプリング周波数、50%のクロック・デューティ・サイクル、-1dBFSの差動アナログ入力、内部リファレンス・モード(特に記述のない限り)。

| パラメータ                               | テスト条件         | ADS6225<br>F <sub>s</sub> = 125 MSPS |      |     | ADS6224<br>F <sub>s</sub> = 105 MSPS |      |      | ADS6223<br>F <sub>s</sub> = 80 MSPS |      |      | ADS6222<br>F <sub>s</sub> = 65 MSPS |     |     | 単位   |

|-------------------------------------|---------------|--------------------------------------|------|-----|--------------------------------------|------|------|-------------------------------------|------|------|-------------------------------------|-----|-----|------|

|                                     |               | MIN                                  | TYP  | MAX | MIN                                  | TYP  | MAX  | MIN                                 | TYP  | MAX  | MIN                                 | TYP | MAX |      |

| <b>ダイナミック特性</b>                     |               |                                      |      |     |                                      |      |      |                                     |      |      |                                     |     |     |      |

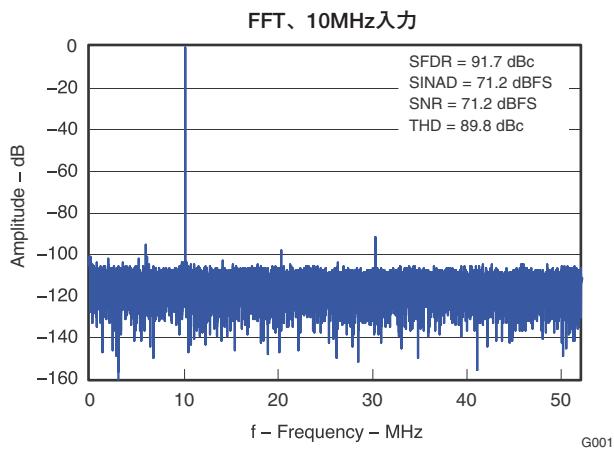

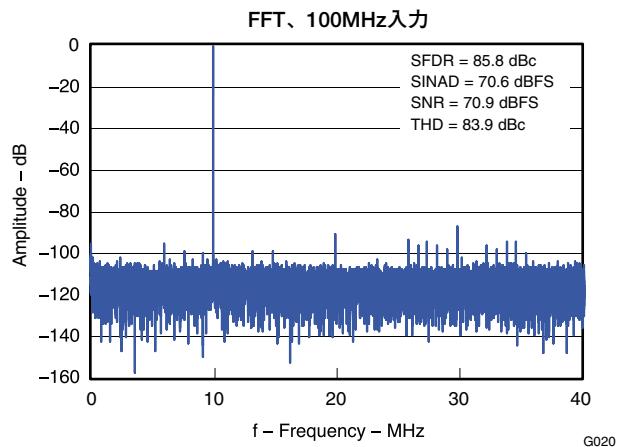

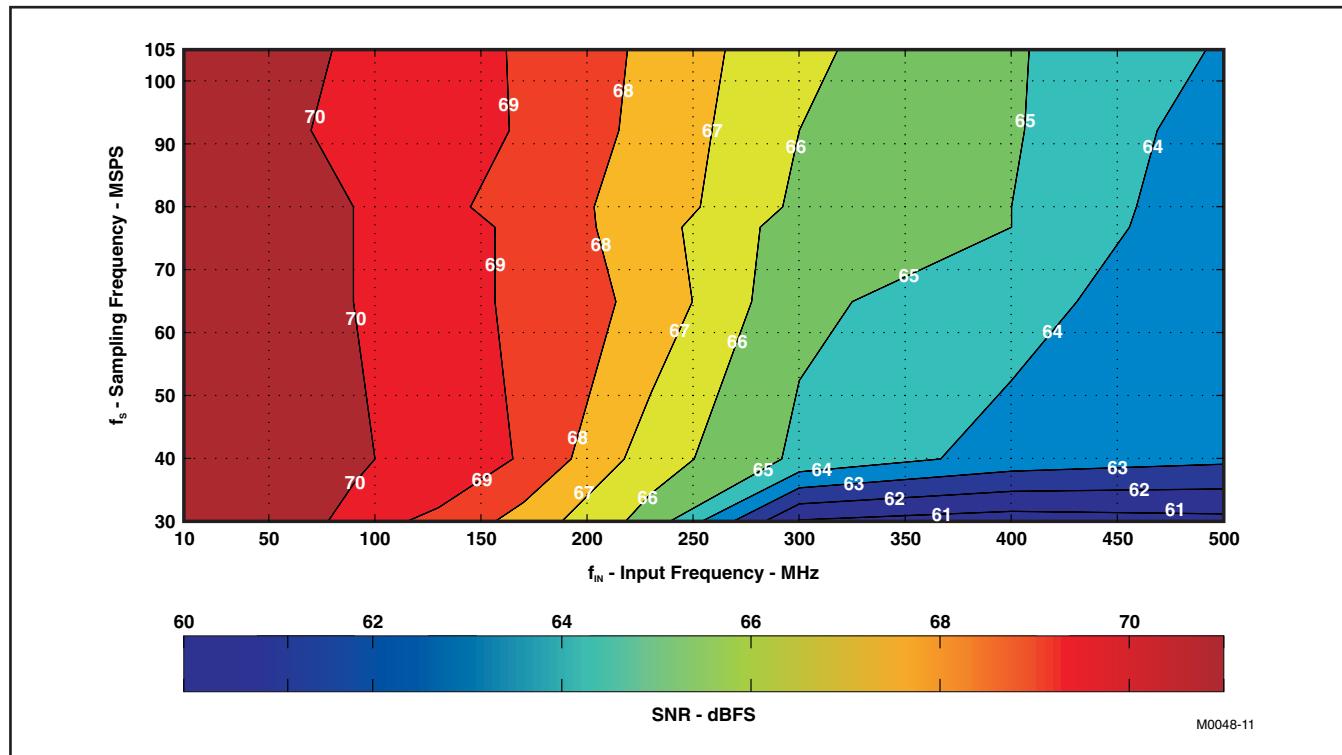

| SNR<br>信号/雑音比                       | Fin = 10 MHz  |                                      | 70.9 |     | 71                                   |      | 71.4 |                                     | 71.4 |      |                                     |     |     | dBFS |

|                                     | Fin = 50 MHz  | 67.5                                 | 70.5 |     | 70.8                                 |      | 68   | 71.1                                |      | 71.2 |                                     |     |     |      |

|                                     | Fin = 70 MHz  |                                      | 70.3 |     | 67.5                                 | 70.6 |      | 70.9                                |      | 68   | 71                                  |     |     |      |

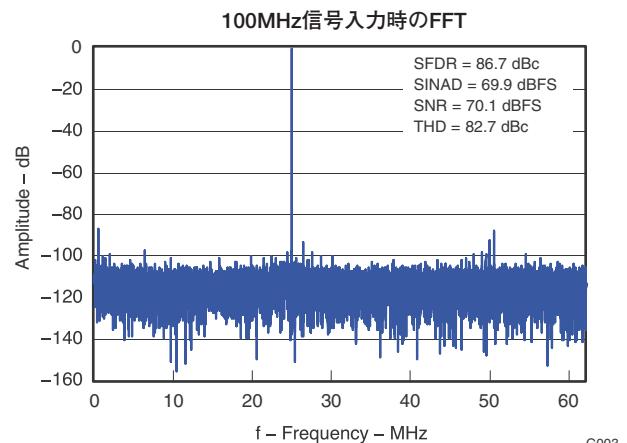

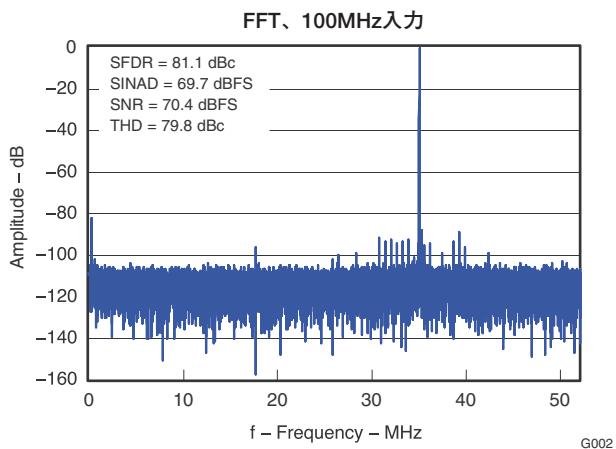

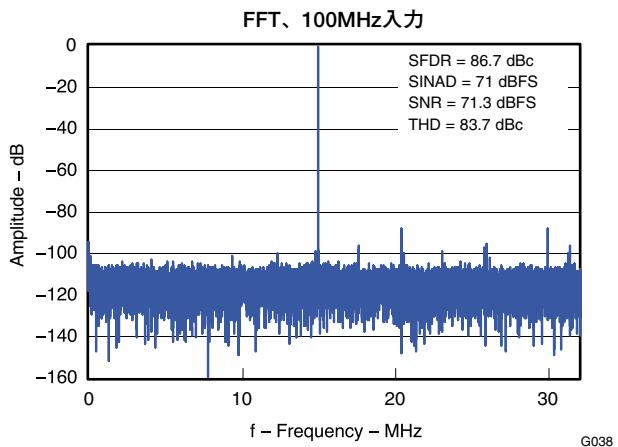

|                                     | Fin = 100 MHz |                                      | 69.9 |     | 70.1                                 |      | 70.5 |                                     | 70.5 |      | 70.5                                |     |     |      |

|                                     | Fin = 170 MHz | 0 dB ゲイン                             | 68.5 |     | 68.8                                 |      | 69   |                                     | 69.1 |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 68.1 |     | 68.4                                 |      | 68.4 |                                     | 68.8 |      |                                     |     |     |      |

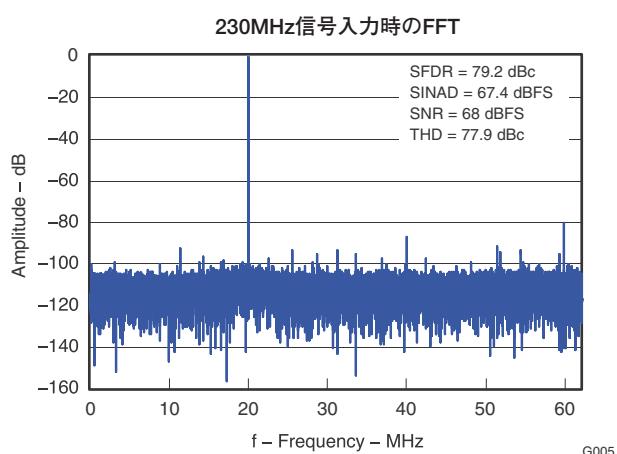

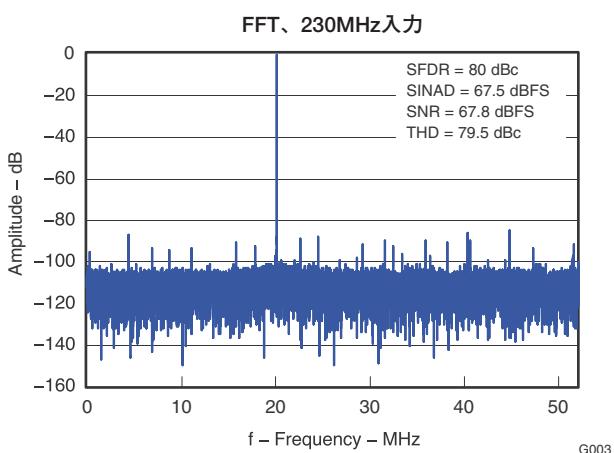

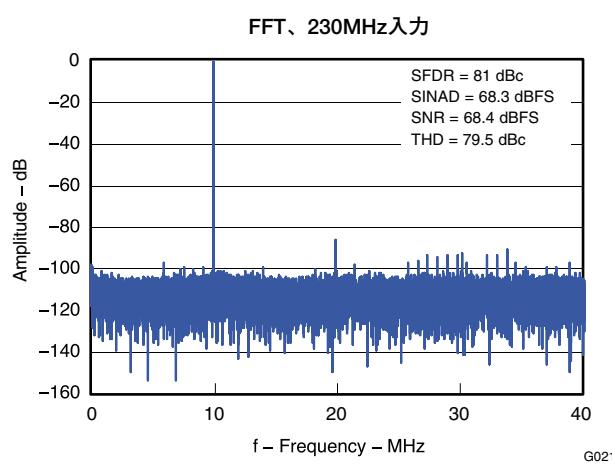

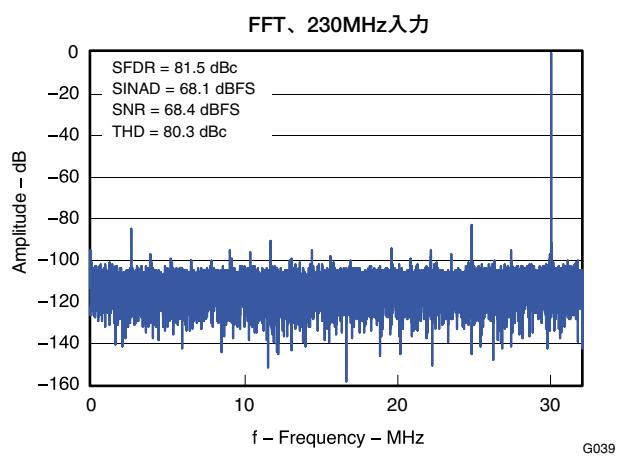

|                                     | Fin = 230 MHz | 0 dB ゲイン                             | 67.4 |     | 67.8                                 |      | 66.9 |                                     | 68.1 |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 67.1 |     | 67.3                                 |      | 67.3 |                                     | 67.8 |      |                                     |     |     |      |

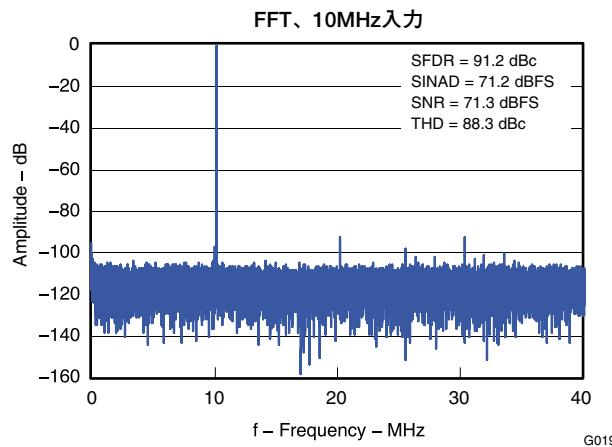

| SINAD<br>信号/(雑音+歪)比                 | Fin = 10 MHz  |                                      | 70.7 |     | 70.8                                 |      | 71.3 |                                     | 71.3 |      |                                     |     |     | dBFS |

|                                     | Fin = 50 MHz  | 67                                   | 70   |     | 69.8                                 |      | 67.5 | 70.9                                |      | 71   |                                     |     |     |      |

|                                     | Fin = 70 MHz  |                                      | 69.2 |     | 67                                   | 70   |      | 70.6                                |      | 67.5 | 70.7                                |     |     |      |

|                                     | Fin = 100 MHz |                                      | 69.7 |     | 70                                   |      | 70.1 |                                     | 70   |      |                                     |     |     |      |

|                                     | Fin = 170 MHz | 0 dB ゲイン                             | 66.9 |     | 68.5                                 |      | 68.6 |                                     | 68.9 |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 67.4 |     | 68.1                                 |      | 68.2 |                                     | 68.7 |      |                                     |     |     |      |

|                                     | Fin = 230 MHz | 0 dB ゲイン                             | 66   |     | 66.8                                 |      | 66.5 |                                     | 67.3 |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 66.5 |     | 66.8                                 |      | 67.2 |                                     | 67.4 |      |                                     |     |     |      |

| SFDR<br>スプリアス<br>フリー・ダイナ<br>ミック・レンジ | Fin = 10 MHz  |                                      | 90   |     | 91                                   |      | 91   |                                     | 93   |      |                                     |     |     | dBc  |

|                                     | Fin = 50 MHz  | 73                                   | 83   |     | 80                                   |      | 76   | 87                                  |      | 88   |                                     |     |     |      |

|                                     | Fin = 70 MHz  |                                      | 78   |     | 73                                   | 81   |      | 86                                  |      | 76   | 87                                  |     |     |      |

|                                     | Fin = 100 MHz |                                      | 87   |     | 85                                   |      | 85   |                                     | 83   |      |                                     |     |     |      |

|                                     | Fin = 170 MHz | 0 dB ゲイン                             | 75   |     | 78                                   |      | 79   |                                     | 80   |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 79   |     | 81                                   |      | 82   |                                     | 83   |      |                                     |     |     |      |

|                                     | Fin = 230 MHz | 0 dB ゲイン                             | 74   |     | 76                                   |      | 77   |                                     | 78   |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 78   |     | 79                                   |      | 80   |                                     | 81   |      |                                     |     |     |      |

| HD2<br>第2高調波                        | Fin = 10 MHz  |                                      | 93   |     | 94                                   |      | 96   |                                     | 97   |      |                                     |     |     | dBc  |

|                                     | Fin = 50 MHz  | 73                                   | 91   |     | 88                                   |      | 76   | 90                                  |      | 92   |                                     |     |     |      |

|                                     | Fin = 70 MHz  |                                      | 90   |     | 73                                   | 88   |      | 90                                  |      | 76   | 92                                  |     |     |      |

|                                     | Fin = 100 MHz |                                      | 90   |     | 90                                   |      | 87   |                                     | 87   |      |                                     |     |     |      |

|                                     | Fin = 170 MHz | 0 dB ゲイン                             | 85   |     | 84                                   |      | 86   |                                     | 86   |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 88   |     | 86                                   |      | 88   |                                     | 88   |      |                                     |     |     |      |

|                                     | Fin = 230 MHz | 0 dB ゲイン                             | 82   |     | 81                                   |      | 82   |                                     | 83   |      |                                     |     |     |      |

|                                     |               | 3.5 dB Coarse ゲイン                    | 85   |     | 83                                   |      | 84   |                                     | 85   |      |                                     |     |     |      |

## 電気的特性

TYP値は25°C、最小値および最大値は $T_{MIN} = -40^{\circ}\text{C}$ ～ $T_{MAX} = 85^{\circ}\text{C}$ の全温度範囲、AVDD = LVDD = 3.3 V、最大定格サンプリング周波数、50%のクロック・デューティ・サイクル、-1dBFSの差動アナログ入力、内部リファレンス・モード(特に記述のない限り)。

| パラメータ                           | テスト条件                                          | ADS6225<br>$F_s = 125 \text{ MSPS}$ |      |     | ADS6224<br>$F_s = 105 \text{ MSPS}$ |      |     | ADS6223<br>$F_s = 80 \text{ MSPS}$ |      |     | ADS6222<br>$F_s = 65 \text{ MSPS}$ |     |     | 単位            |

|---------------------------------|------------------------------------------------|-------------------------------------|------|-----|-------------------------------------|------|-----|------------------------------------|------|-----|------------------------------------|-----|-----|---------------|

|                                 |                                                | MIN                                 | TYP  | MAX | MIN                                 | TYP  | MAX | MIN                                | TYP  | MAX | MIN                                | TYP | MAX |               |

|                                 | Fin = 10 MHz                                   | 90                                  |      |     | 91                                  |      |     | 91                                 |      |     | 93                                 |     |     |               |

| HD3<br>第3高調波                    | Fin = 50 MHz                                   | 73                                  | 83   |     | 80                                  |      |     | 76                                 | 87   |     | 88                                 |     |     | dBc           |

|                                 | Fin = 70 MHz                                   |                                     | 78   |     | 73                                  | 81   |     |                                    | 86   |     | 76                                 | 86  |     |               |

|                                 | Fin = 100 MHz                                  |                                     | 87   |     |                                     | 85   |     |                                    | 85   |     |                                    | 83  |     |               |

|                                 | Fin = 170<br>MHz                               | 0 dB ゲイン                            | 75   |     | 78                                  |      |     | 79                                 |      |     | 80                                 |     |     |               |

|                                 |                                                | 3.5 dB<br>Coarse ゲイン                | 79   |     | 82                                  |      |     | 82                                 |      |     | 83                                 |     |     |               |

|                                 | Fin = 230<br>MHz                               | 0 dB ゲイン                            | 74   |     | 76                                  |      |     | 77                                 |      |     | 78                                 |     |     |               |

|                                 |                                                | 3.5 dB<br>Coarse ゲイン                | 78   |     | 79                                  |      |     | 80                                 |      |     | 81                                 |     |     |               |

| ワースト<br>高調波<br>(HD2, HD3<br>除く) | Fin = 10 MHz                                   | 95                                  |      |     | 95                                  |      |     | 96                                 |      |     | 98                                 |     |     | dBc           |

|                                 | Fin = 50 MHz                                   | 94                                  |      |     | 94                                  |      |     | 95                                 |      |     | 95                                 |     |     |               |

|                                 | Fin = 70 MHz                                   | 92                                  |      |     | 94                                  |      |     | 95                                 |      |     | 95                                 |     |     |               |

|                                 | Fin = 100 MHz                                  | 91                                  |      |     | 92                                  |      |     | 93                                 |      |     | 93                                 |     |     |               |

|                                 | Fin = 170 MHz                                  | 88                                  |      |     | 89                                  |      |     | 90                                 |      |     | 90                                 |     |     |               |

|                                 | Fin = 230 MHz                                  | 86                                  |      |     | 86                                  |      |     | 87                                 |      |     | 87                                 |     |     |               |

| THD<br>全高調波歪                    | Fin = 10 MHz                                   | 88                                  |      |     | 89.5                                |      |     | 89.5                               |      |     | 91                                 |     |     | dBc           |

|                                 | Fin = 50 MHz                                   | 70                                  | 81   |     | 78.5                                |      |     | 74                                 | 85.5 |     | 86                                 |     |     |               |

|                                 | Fin = 70 MHz                                   |                                     |      |     | 70                                  | 77   |     |                                    |      |     | 74                                 |     |     |               |

|                                 | Fin = 100 MHz                                  |                                     | 84   |     | 84                                  |      |     | 83                                 |      |     | 80.5                               |     |     |               |

|                                 | Fin = 170 MHz                                  |                                     | 73   |     | 76                                  |      |     | 77.5                               |      |     | 78.5                               |     |     |               |

|                                 | Fin = 230 MHz                                  |                                     | 72   |     | 74                                  |      |     | 75.5                               |      |     | 76.5                               |     |     |               |

| ENOB<br>有効ビット数                  | Fin = 50 MHz                                   | 10.8                                | 11.4 |     |                                     |      |     | 10.9                               | 11.5 |     | 11.5                               |     |     | Bits          |

|                                 | Fin = 70 MHz                                   |                                     |      |     | 10.8                                | 11.4 |     |                                    |      |     | 10.9                               |     |     |               |

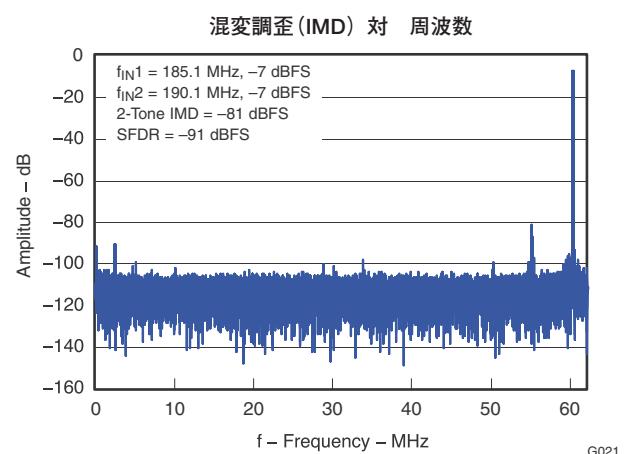

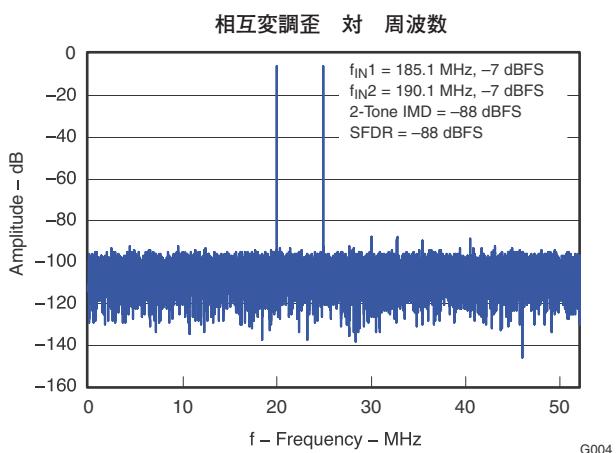

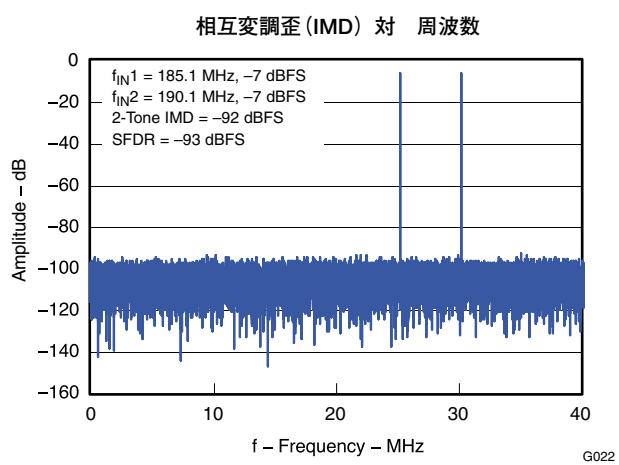

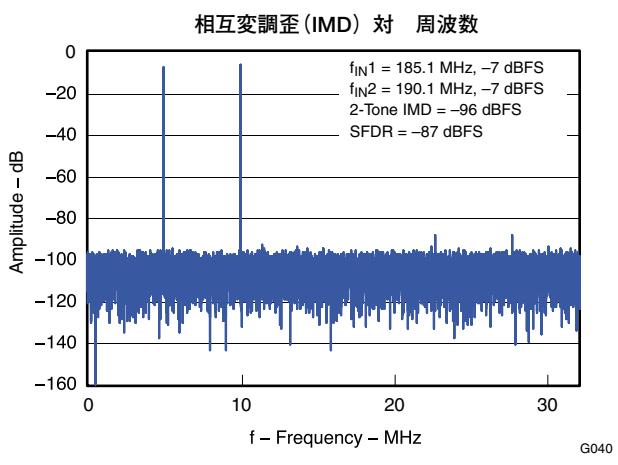

| IMD<br>2トーン<br>混変調歪             | F1= 46.09 MHz,<br>F2 = 50.09 MHz               | 90                                  |      |     | 90                                  |      |     | 94                                 |      |     | 97                                 |     |     | dBFS          |

|                                 | F1= 185.09 MHz,<br>F2 = 190.09 MHz             | 82                                  |      |     | 88                                  |      |     | 92                                 |      |     | 96                                 |     |     |               |

| クロストーク                          | クロストーク信号周波数<br>= 10 MHz                        | 105                                 |      |     | 105                                 |      |     | 106                                |      |     | 108                                |     |     | dBc           |

| 過負荷入力<br>復帰時間                   | 最終値の1%以内への復帰、<br>正弦波入力、6-dB過負荷                 | 1                                   |      |     | 1                                   |      |     | 1                                  |      |     | 1                                  |     |     | クロック・<br>サイクル |

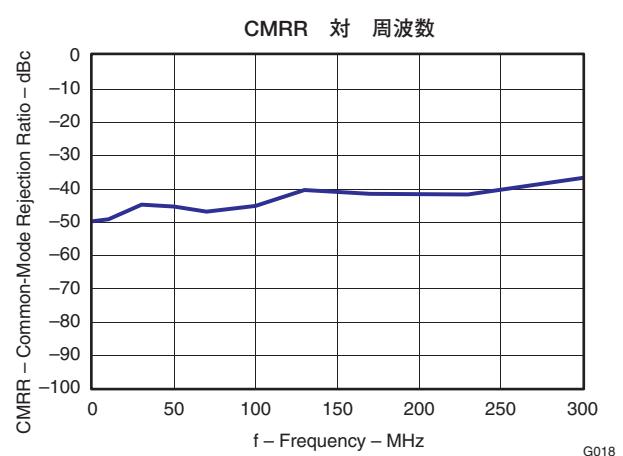

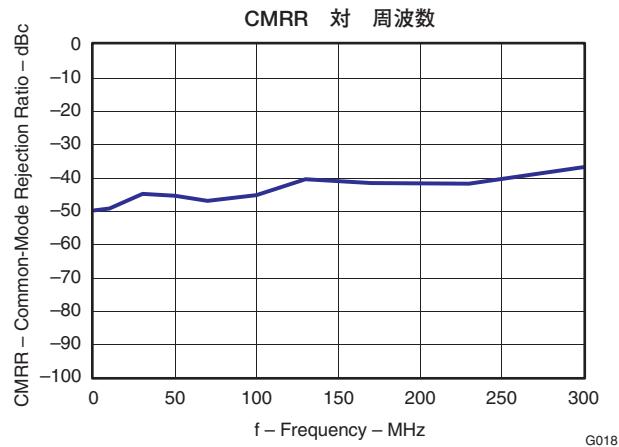

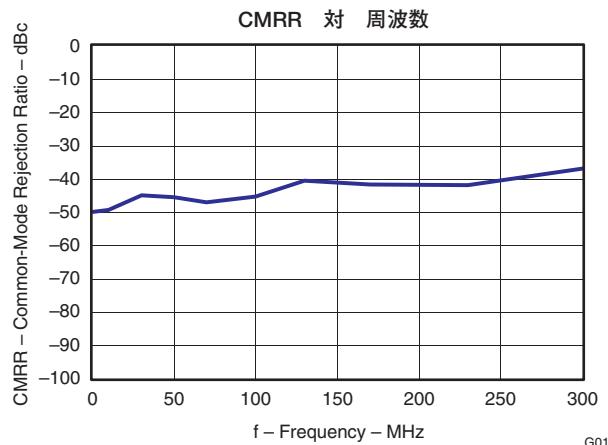

| AC PSRR<br>電源除去比                | Up to 100 MHz, 100 mV <sub>PP</sub> on<br>AVDD | 35                                  |      |     | 35                                  |      |     | 35                                 |      |     | 35                                 |     |     | dBc           |

## デジタル特性

DC仕様は、デジタル出力のスイッチングなし、有効な論理レベル0または1に固定、AVDD = LVDD = 3.3V、 $I_O = 3.5\text{mA}$ 、 $R_{LOAD} = 100\Omega$ の条件で規定されています<sup>(1)</sup>。

すべてのLVDS仕様は、設計で規定される値であり、実製品のテストは行っていません。

| パラメータ              | テスト条件            | ADS6225/ADS6224/AD<br>S6223/ADS6222 |      |     | 単位            |

|--------------------|------------------|-------------------------------------|------|-----|---------------|

|                    |                  | MIN                                 | TYP  | MAX |               |

| <b>デジタル入力</b>      |                  |                                     |      |     |               |

| “H” レベル入力電圧        |                  | 2.4                                 |      |     | V             |

| “L” レベル入力電圧        |                  |                                     | 0.8  |     | V             |

| “H” レベル入力電流        |                  |                                     | 10   |     | $\mu\text{A}$ |

| “L” レベル入力電流        |                  |                                     | 10   |     | $\mu\text{A}$ |

| 入力容量               |                  |                                     | 4    |     | pF            |

| <b>デジタル出力</b>      |                  |                                     |      |     |               |

| “H” レベル出力電圧        |                  |                                     | 1375 |     | mV            |

| “L” レベル出力電圧        |                  |                                     | 1025 |     | mV            |

| $ V_{ODI} $ 差動出力電圧 |                  | 250                                 | 350  | 450 | mV            |

| $V_{OS}$ 出力オフセット電圧 | OUTPとOUTM間同相電圧   |                                     | 1200 |     | mV            |

| 出力容量               | 出力 対 GND間の内部出力容量 |                                     | 2    |     | pF            |

(1)  $I_O$ はLVDSバッファの電流設定、 $R_{LOAD}$ はLVDS出力ペア間の外部差動負荷抵抗です。

## タイミング仕様<sup>(1)</sup>

TYP値は25°C、最小値および最大値はT<sub>MIN</sub> = -40°C～T<sub>MAX</sub> = 85°Cの全温度範囲、AVDD = LVDD = 3.3 V、最大定格サンプリング周波数、正弦波入力クロック、1.5 V<sub>PP</sub>のクロック振幅、C<sub>L</sub> = 5pF<sup>(2)</sup>、I<sub>O</sub> = 3.5mA、R<sub>L</sub> = 100Ω<sup>(3)</sup>、内部終端なし(特に記述のない限り)。

| パラメータ                                                        | 説明                                     | ADS6225                                             |      |      | ADS6224 |      |      | ADS6223 |      |     | ADS6222 |      |     | 単位     |           |

|--------------------------------------------------------------|----------------------------------------|-----------------------------------------------------|------|------|---------|------|------|---------|------|-----|---------|------|-----|--------|-----------|

|                                                              |                                        | MIN                                                 | TYP  | MAX  | MIN     | TYP  | MAX  | MIN     | TYP  | MAX | MIN     | TYP  | MAX |        |           |

| t <sub>J</sub>                                               | アバーチャジッタ                               | サンプリング時刻の不確定性                                       |      |      | 250     |      |      | 250     |      |     | 250     |      |     | fs rms |           |

| インターフェイス：2線式、DDR bitクロック、14xシリアルライゼーション                      |                                        |                                                     |      |      |         |      |      |         |      |     |         |      |     |        |           |

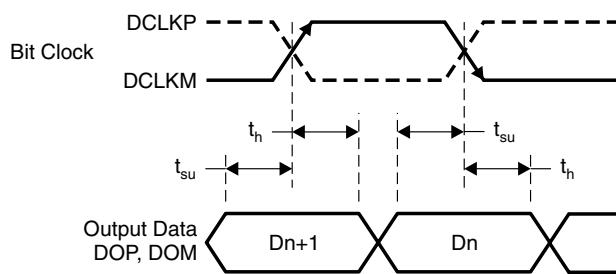

| t <sub>su</sub>                                              | データ・セットアップ時間 <sup>(4)(5)(6)</sup>      | データ・クロスオーバーからビット・クロック・クロスオーバーまで                     | 0.35 | 0.55 | 0.45    | 0.65 | 0.65 | 0.85    | 0.8  | 1.1 | 0.8     | 1.1  | ns  |        |           |

| t <sub>h</sub>                                               | データ・ホールド時間 <sup>(4)(5)(6)</sup>        | ビット・クロック・クロスオーバーからデータ・クロスオーバーまで                     | 0.35 | 0.58 | 0.5     | 0.7  | 0.7  | 0.9     | 0.8  | 1.1 | 0.8     | 1.1  | ns  |        |           |

| t <sub>pd_clk</sub>                                          | クロック伝搬遅延 <sup>(6)</sup>                | 入力クロック立ち上がりエッジ・クロスオーバーからフレーム・クロック立ち上がりエッジ・クロスオーバーまで | 3.4  | 4.4  | 5.4     | 3.4  | 4.4  | 5.4     | 3.4  | 4.4 | 5.4     | 3.4  | 4.4 | 5.4    | ns        |

|                                                              | ビット・クロック・サイクル・サイクル・ジッタ <sup>(5)</sup>  |                                                     | 350  |      |         | 350  |      |         | 350  |     |         | 350  |     |        | ps pp     |

|                                                              | フレーム・クロック・サイクル・サイクル・ジッタ <sup>(5)</sup> |                                                     | 75   |      |         | 75   |      |         | 75   |     |         | 75   |     |        | ps pp     |

| 以下の規定は 5 MSPS ≤ サンプリング周波数 ≤ 125 MSPS および全てのインターフェイスオプションに対して |                                        |                                                     |      |      |         |      |      |         |      |     |         |      |     |        |           |

| t <sub>A</sub>                                               | アバーチャ遅延                                | 入力クロック立ち上がりエッジから実際のサンプリング時刻までの遅延                    | 1    | 2    | 3       | 1    | 2    | 3       | 1    | 2   | 3       | 1    | 2   | 3      | ns        |

|                                                              | アバーチャ遅延変動                              | 同一デバイスのチャネル間                                        | -250 | ±80  | 250     | -250 | ±80  | 250     | -250 | ±80 | 250     | -250 | ±80 | 250    | ps        |

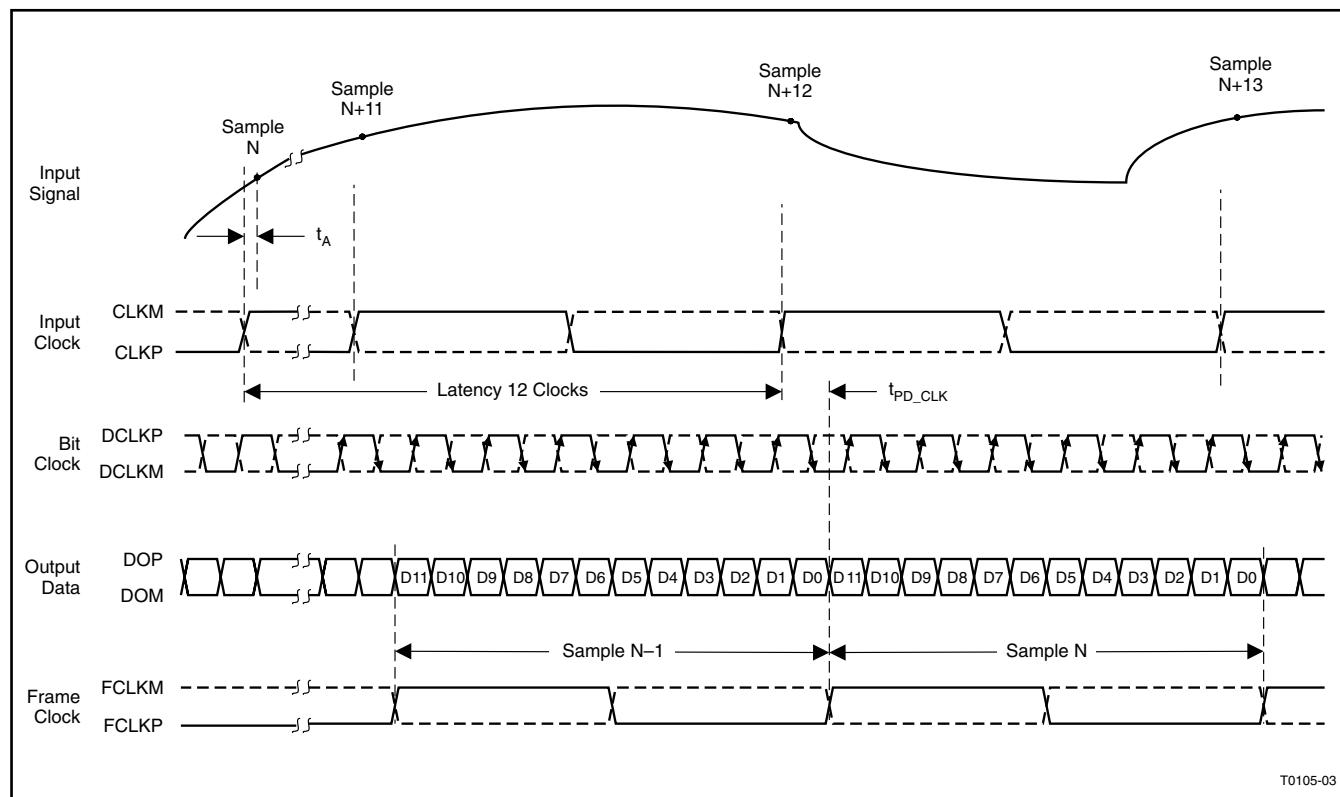

|                                                              | ADC レーテンシ <sup>(7)</sup>               | サンプリングからADC出力までの伝搬時間、図1参照                           | 12   |      |         | 12   |      |         | 12   |     |         | 12   |     |        | クロック・サイクル |

| ウェイクアップ時間                                                    | グローバル・パワードown起動後の有効データまでの時間            |                                                     | 100  |      |         | 100  |      |         | 100  |     |         | 100  |     |        | μs        |

|                                                              | 入力クロック・スタート後の有効データまでの時間                |                                                     | 100  |      |         | 100  |      |         | 100  |     |         | 100  |     |        | μs        |

|                                                              | チャネルスタンバイ後の有効データまでの時間                  |                                                     | 200  |      |         | 200  |      |         | 200  |     |         | 200  |     |        | クロック・サイクル |

| t <sub>Rise</sub>                                            | データ立ち上がり時間                             | -100 mV から +100 mV まで                               | 50   | 100  | 200     | 50   | 100  | 200     | 50   | 100 | 200     | 50   | 100 | 200    | ps        |

| t <sub>Fall</sub>                                            | データ立ち下がり時間                             | +100 mV から -100 mV まで                               | 50   | 100  | 200     | 50   | 100  | 200     | 50   | 100 | 200     | 50   | 100 | 200    | ps        |

| t <sub>Rise</sub>                                            | ビット・クロックおよびフレーム・クロック立ち上がり時間            | -100 mV から +100 mV まで                               | 50   | 100  | 200     | 50   | 100  | 200     | 50   | 100 | 200     | 50   | 100 | 200    | ps        |

(1) タイミング・パラメータは、設計によって規定される値であり、実製品のテストは行っていません。

(2) C<sub>L</sub>は、各出力ピンとグランドとの間の外部シングルエンド負荷容量です。

(3) I<sub>o</sub>はLVDSパッファの設定電流。R<sub>L</sub>はLVDS出力ペア間の外部差動負荷抵抗です。

(4) タイミング・パラメータは、R<sub>L</sub>およびC<sub>L</sub>で終端される2インチPCBトレース(100Ωの特性インピーダンス)の末端で測定されています。

(5) セットアップ時間およびホールド時間の規定は、出力データおよびクロックに対するジッタの影響を考慮しています。

(6) より低いサンプリング周波数および他のインターフェイス・オプションでのタイミングについては、アプリケーション情報の「出力タイミング」を参照してください。

(7) 合計のレイテンシ = ADCレイテンシ + 内部シリアルライザのレイテンシです。シリアルライザのレイテンシは、表28で選択されるインターフェイス・オプションによって異なります。

## タイミング仕様

TYP値は25°C、最小値および最大値は $T_{MIN} = -40^{\circ}\text{C}$ ～ $T_{MAX} = 85^{\circ}\text{C}$ の全温度範囲、AVDD = LVDD = 3.3 V、最大定格サンプリング周波数、正弦波入力クロック、1.5 V<sub>PP</sub>のクロック振幅、 $C_L = 5\text{pF}^{(2)}$ 、 $I_O = 3.5\text{mA}$ 、 $R_L = 100\Omega^{(3)}$ 、内部終端なし(特に記述のない限り)。

| パラメータ                    | 説明                                                   | ADS6225 |     |     | ADS6224 |     |     | ADS6223 |     |     | ADS6222 |     |     | 単位 |

|--------------------------|------------------------------------------------------|---------|-----|-----|---------|-----|-----|---------|-----|-----|---------|-----|-----|----|

|                          |                                                      | MIN     | TYP | MAX |    |

| $t_{FALL}$               | ビット・クロックおよびフレーム・クロック立ち上がり時間<br>+100 mV から -100 mV まで | 50      | 100 | 200 | 50      | 100 | 200 | 50      | 100 | 200 | 50      | 100 | 200 | ps |

| LVDSビット・クロック・デューティ・サイクル  |                                                      | 45%     | 50% | 55% | 45%     | 50% | 55% | 45%     | 50% | 55% | 45%     | 50% | 55% |    |

| LVDSフレーム・クロック・デューティ・サイクル |                                                      | 47%     | 50% | 53% | 47%     | 50% | 53% | 47%     | 50% | 53% | 47%     | 50% | 53% |    |

図 1. レイテンシ

T0106-03

図 2. LVDSのタイミング

## デバイスのプログラミング・モード

ADS622Xは、簡単に設定できるプログラム機能を備えたことにより、高い柔軟性を提供します。

パラレル・インターフェイス制御またはシリアル・インターフェイス・プログラミングを使用し、それぞれ独立に設定を行えます。

また、パラレル・インターフェイスとシリアル制御レジスタの両方を使用する第3の設定モードもサポートしています。このモードでは、パラレル・インターフェイスとシリアル・インターフェイスの間の優先順位が、優先順位表(表4)によって決定されます。このような柔軟な制御を必要としない場合は、シリアル・インターフェイス・プログラミングかパラレル・インターフェイス制御のどちらか一方を選択できます。

### パラレル・インターフェイス制御のみを使用

パラレル・インターフェイスを使用してデバイスを制御するには、RESETを“High”(LVDD)に維持します。CFG1、CFG2、CFG3、CFG4、PDNA、PDNB、SEN、SCLK、SDATAの各ピンは、ADCの特定の機能を直接制御するために使用されます。電源投入後、デバイスはパラレル・ピンの電圧設定(表5～表9)に従って自動的に設定され、リセットは不要です。このモードでは、SEN、SCLK、およびSDATAはパラレル・インターフェイス制御ピンとして機能します。

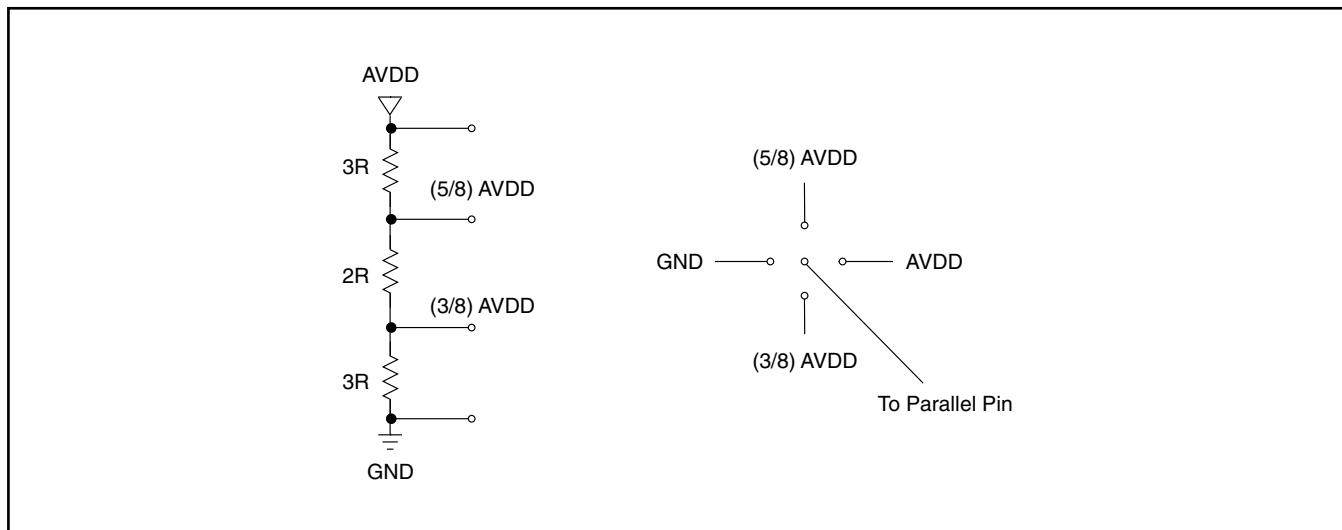

出力データのインターフェイスおよび形式、パワーダウン・モード、Coarseゲイン、内部/外部リファレンスなど、よく使用される機能はこのモードで制御されます。パラレル・ピンは、図3に示すような単純な抵抗ストリングを使用して設定されます。

表3に、パラレル・ピンで制御されるモードについて示します。

### シリアル・インターフェイス・プログラミングのみを使用

このモードでは、SEN、SDATA、SCLKはシリアル・インターフェイス・ピンとして機能し、ADCの内部レジスタへのアクセスに使用されます。これらのレジスタは最初に、RESETピンにパルスを印加するか、または(レジスタ内の) <rst>ビットを“High”に設定することで、デフォルト値にリセットする必要があります。リセット後は、RESETピンを“Low”に保持する必要があります。

“High”に設定することで、デフォルト値にリセットする必要があります。リセット後は、RESETピンを“Low”に保持する必要があります。

レジスタのプログラミングおよびリセットについては、「シリアル・インターフェイス」の節で詳しく説明します。

パラレル・ピン(CFG1-4、PDNA、PDNB)はこのモードでは使用しないため、これらはグランドに固定する必要があります。このシリアル・インターフェイス制御のみのモードでは、レジスタ・オーバライド・ビット<OVRD>(レジスタ0x0DのD10)を“High”に設定して、パラレル・インターフェイス・ピンをディスエーブルにする必要があります。

### シリアル・インターフェイスとパラレル制御の両方を使用

柔軟性を高めるために、シリアル・インターフェイス・レジスタとパラレル・ピン制御(CFG1-4、PDNA、PDNB)を組み合わせてデバイスを設定することもできます。

パラレル・インターフェイス制御ピンCFG1-4、PDNA、PDNBを使用できます。電源投入後、デバイスはパラレル・ピン電圧設定(表5～表12)に従って自動的に設定され、リセットは不要です。図3に示されるように、単純な抵抗ストリングを使用できます。

SEN、SDATA、SCLKはシリアル・インターフェイス・ピンとして機能し、ADCの内部レジスタへのアクセスに使用されます。これらのレジスタは最初に、RESETピンにパルスを印加するか、または(レジスタ内の) <rst>ビットを“High”に設定することで、デフォルト値にリセットする必要があります。リセット後は、RESETピンを“Low”に保持する必要があります。

レジスタのプログラミングおよびリセットについては、「シリアル・インターフェイス」の節で詳しく説明します。

いくつかの機能はパラレル・ピンとシリアル・レジスタの両方を使用して制御されるため、それらの間の優先順位が、優先順位表(表4)によって決定されます。

| ピン          | 制御機能                                  |

|-------------|---------------------------------------|

| SEN         | Coarseゲインおよび内部/外部リファレンス               |

| SCLK, SDATA | 同期、デスキー・パターン、およびグローバル・パワーダウン          |

| PDNA, PDNB  | 各チャネルのADCパワーダウン専用ピン                   |

| CFG1        | 1線/2線およびDDR/SDRビット・クロック               |

| CFG2        | 12倍/14倍シリアル化、およびSDRビット・クロックのキャプチャ・エッジ |

| CFG3        | 予約機能。CFG3はグランドに接続します。                 |

| CFG4        | MSB/LSBファーストおよびデータ形式                  |

表3. パラレル・ピンの定義

| ピン             | 機能                                                        | PRIORITY                                                                                             |

|----------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| CFG1 to CFG4   | 表9から11に機能説明                                               | <OVRD>ビットが“High”の場合は、レジスタビットでモードを制御できます。<OVRD>ビットが“Low”的場合は、これらのパラレル・ピンの制御電圧により、表に従って機能が決定されます。      |

| PDN            | グローバル・パワーダウン                                              | PDNピンが“Low”的場合のみ、レジスタ0x00のD0ビットでグローバル・パワーダウンが制御されます。PDNが“High”的場合、デバイスはグローバル・パワーダウン・モードになります。        |

| SEN            | シリアル・インターフェイス・イネーブル                                       | <OVRD>ビットが“High”的場合のみ、レジスタ0x0DのビットD5でCoarseゲイン設定が制御されます。それ以外の場合は、デフォルトのレジスタ設定に従ってCoarseゲインが0dBになります。 |

|                |                                                           | 内部/外部リファレンス設定は、レジスタ0x00のビットD6によって決定されます。                                                             |

| SCLK,<br>SDATA | シリアル・インターフェイスのクロックおよびシリアル・インターフェイスおよびシリアル・インターフェイス・データ・ピン | レジスタ0xAのD7、D6、D5ビットによって同期およびデスキュー出力パターンが制御されます。                                                      |

|                |                                                           | パワーダウンは、0x00レジスタのビットD0によって決定されます。                                                                    |

表4. パラレル・ピンとシリアル・レジスタの間の優先順位

図3. パラレル・ピンの設定概略図

### パラレル・ピンの説明

| SCLK | SDATA | 説明                                                                                                                      |

|------|-------|-------------------------------------------------------------------------------------------------------------------------|

| LOW  | LOW   | NORMAL – 通常変換。                                                                                                          |

| LOW  | HIGH  | SYNC – すべてのチャネルのADC出力同期パターン。受信側ではこのパターンを使用して、デシリアル化されたデータをフレーム境界に揃えます。詳細については、「キャプチャ・テスト・パターン」を参照してください。                |

| HIGH | LOW   | POWER DOWN – グローバル・パワーダウン。内部リファレンス、PLL、出力バッファを含めてADCのすべてのチャネルがパワーダウンされます。                                               |

| HIGH | HIGH  | DESKEW – すべてのチャネルのADC出力デスキュー・パターン。受信側ではこのパターンを使用して、デシリアライザが正しいクロック・エッジを使用することを保証できます。詳細については、「キャプチャ・テスト・パターン」を参照してください。 |

表5. SCLK、SDATA制御ピン

| SEN       | 説明                                           |

|-----------|----------------------------------------------|

| 0         | 外部リファレンスおよび0dB Coarseゲイン(フルスケール = 2Vpp)      |

| (3/8)LVDD | 外部リファレンスおよび3.5dB Coarseゲイン(フルスケール = 1.34Vpp) |

| (5/8)LVDD | 内部リファレンスおよび3.5dB Coarseゲイン(フルスケール = 1.34Vpp) |

| LVDD      | 内部リファレンスおよび0dB Coarseゲイン(フルスケール = 2Vpp)      |

表6. SEN制御ピン

使用されているプログラミング・モードに関係なく、電源投入後には、パラレル・ピンPDNA、PDNB、CFG1～CFG4に印加されている電圧に従って、デバイスが自動的に設定されます(表7～表12)。

| PDNA | 説明                     |

|------|------------------------|

| 0    | 通常動作                   |

| AVDD | チャネルA ADCのグローバル・パワーダウン |

表 7. PDNA制御ピン

| PDNB | 説明                     |

|------|------------------------|

| 0    | 通常動作                   |

| AVDD | チャネルB ADCのグローバル・パワーダウン |

表 8. PDNB制御ピン

| CFG1      | 説明                      |

|-----------|-------------------------|

| 0         | DDRビット・クロック、1線式インターフェイス |

| (3/8)LVDD | 未使用                     |

| (5/8)LVDD | SDRビット・クロック、2線式インターフェイス |

| LVDD      | DDRビット・クロック、2線式インターフェイス |

表 9. CFG1制御ピン

| CFG2      | 説明                                                              |

|-----------|-----------------------------------------------------------------|

| 0         | 12倍シリアル化、ビット・クロックの立ち下がりエッジでデータ取り込み<br>(2線式SDRビット・クロック・モードの場合のみ) |

| (3/8)LVDD | 14倍シリアル化、ビット・クロックの立ち下がりエッジでデータ取り込み<br>(2線式SDRビット・クロック・モードの場合のみ) |

| (5/8)LVDD | 14倍シリアル化、ビット・クロックの立ち上がりエッジでデータ取り込み<br>(2線式SDRビット・クロック・モードの場合のみ) |

| LVDD      | 12倍シリアル化、ビット・クロックの立ち上がりエッジでデータ取り込み<br>(2線式SDRビット・クロック・モードの場合のみ) |

表 10. CFG2制御ピン

|      |              |

|------|--------------|

| CFG3 | 予約 - グランドに接続 |

|------|--------------|

表 11. CFG3制御ピン

| CFG4      | 説明                  |

|-----------|---------------------|

| 0         | MSBファースト、2の補数       |

| (3/8)LVDD | MSBファースト、オフセット・バイナリ |

| (5/8)LVDD | LSBファースト、オフセット・バイナリ |

| LVDD      | LSBファースト、2の補数       |

表 12. CFG4制御ピン

## シリアル・インターフェイス

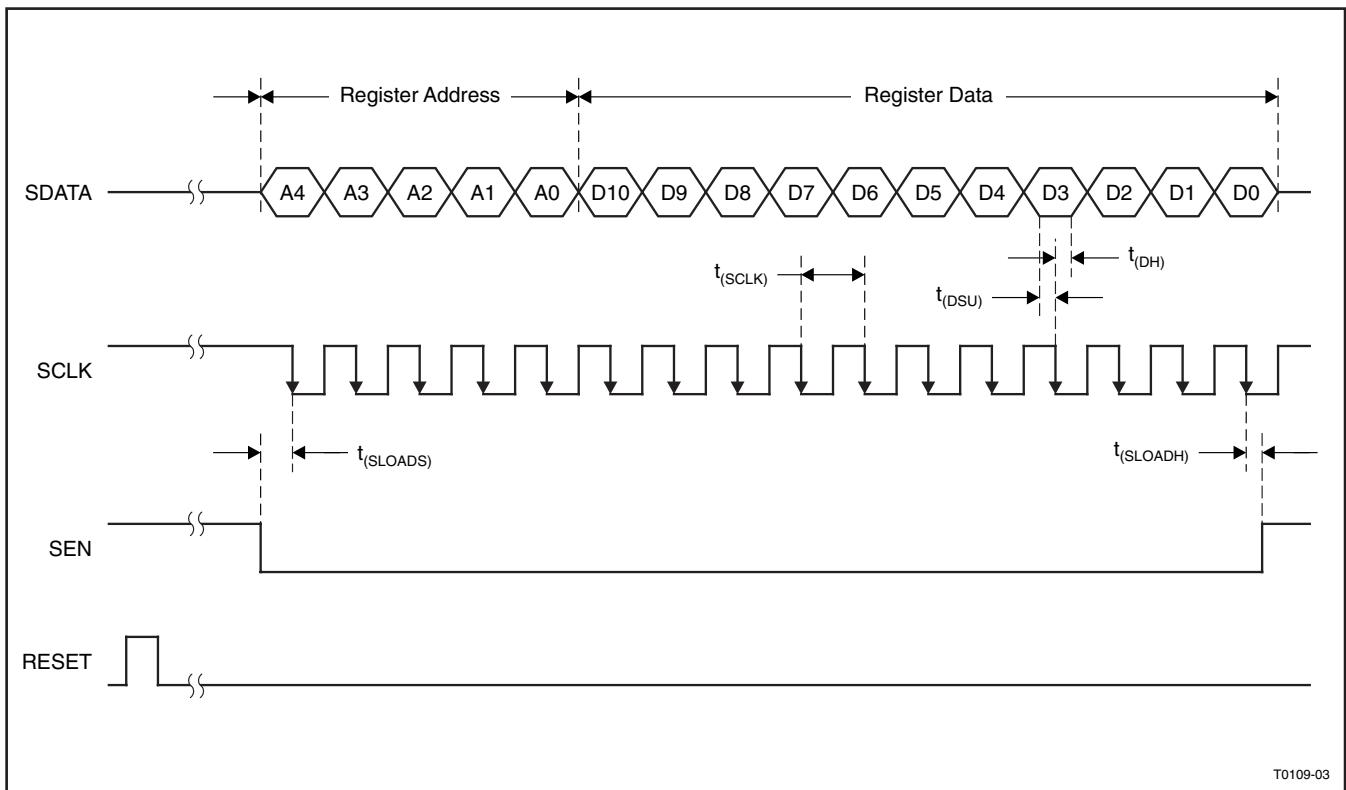

ADCには、SEN(シリアル・インターフェイス・イネーブル)、SCLK(シリアル・インターフェイス・クロック)、SDATA(シリアル・インターフェイス・データ)、RESETの各ピンから構成されるシリアル・インターフェイスが備えられています。SENが“Low”的ときに、デバイスへのビットのシリアル・シフトがイネーブルになります。シリアル・データSDATAは、SENがアクティブ(“Low”)のときのSCLKの各立ち下がりエッジでラッチされます。ラッチされたシリアル・データは、SENが“Low”的ときのSCLKの16回目の立ち下がりエッジで、レジスタにロードされます。ワード長が16ビットの倍数より大きい場合、超過するビットは無視されます。1回のアクティブなSENパルス内で、16ビット・ワードの整数倍のデータをロードできます。このインターフェイスは、20MHz～非常に低速(数Hz)までにわたるSCLK周波数で動作し、デューティ・サイクルが50%以外のSCLKでも動作できます。

16ビット・ワードの最初の5ビットはレジスタのアドレス、次の11ビットはレジスタ・データです。

## レジスタ・リセット

電源投入後、内部レジスタはデフォルト値にリセットする必要があります。これは、次の2つのうちいずれかの方法で行えます。

1. RESETに幅10ns以上の“High”パルスを印加する。

2. ソフトウェア・リセットを実行する。シリアル・インターフェイスを使用して、レジスタ0x00の<RST>ビットを“High”にセットします。これにより、レジスタがデフォルト値にリセットされ、<RST>ビットは“Low”にリセットされます。

RESETピンを使用しない場合は、“Low”に固定しておく必要があります。

図4. シリアル・インターフェイス・タイミング

## シリアル・インターフェイスのタイミング特性

Typ値は25°C、Min値およびMax値は $T_{MIN} = -40^{\circ}\text{C}$  ~  $T_{MAX} = 85^{\circ}\text{C}$ の全温度範囲、

AVDD = LVDD = 3.3 Vです（特に記述のない限り）。

| パラメータ        |                                         | MIN  | TYP | MAX | 単位 |

|--------------|-----------------------------------------|------|-----|-----|----|

| $t_{SCLK}$   | SCLK 周波数 $f_{SCLK} = 1/t_{SCLK}$        | > DC | 20  | MHz |    |

| $t_{SLOADS}$ | SEN から SCLK までのセットアップ時間                 | 25   |     | ns  |    |

| $t_{SLOADH}$ | SCLK から SEN までのホールド時間                   | 25   |     | ns  |    |

| $t_{DSU}$    | SDATA セットアップ時間                          | 25   |     | ns  |    |

| $t_{DH}$     | SDATA ホールド時間                            | 25   |     | ns  |    |

|              | SCLKの16番目の立ち上がりエッジからレジスタ書き込みが有効になるまでの時間 | 100  |     | ns  |    |

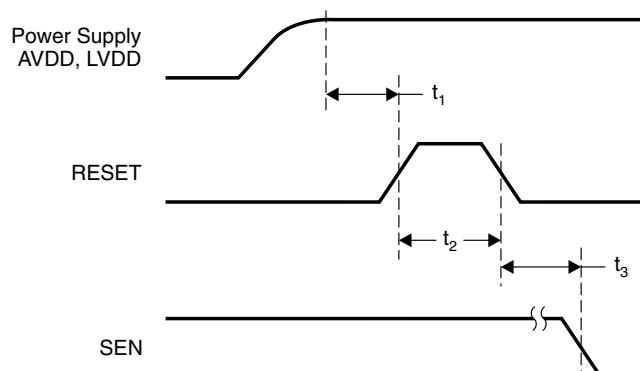

## リセット・タイミング

Typ値は25°C、Min値およびMax値は $T_{MIN} = -40^{\circ}\text{C}$  ~  $T_{MAX} = 85^{\circ}\text{C}$ の全温度範囲、

AVDD = LVDD = 3.3 Vです（特に記述のない限り）。

| パラメータ                  | 説明                                         | MIN | TYP | MAX | 単位 |

|------------------------|--------------------------------------------|-----|-----|-----|----|

| $t_1$ パワー・オン・ディレイ時間    | AVDDとLVDD電源立ち上がりからRESETパルスがアクティブとなるまでの遅延時間 | 5   |     | ms  |    |

| $t_2$ リセットパルス幅         | RESET信号のパルス幅                               | 10  |     | ns  |    |

| $t_3$ レジスタ書き込みディレイ時間   | RESETディスエーブルからSENアクティブまでの遅延時間              | 25  |     | ns  |    |

| $t_{PO}$ パワーアップ・ディレイ時間 | AVDDとLVDD電源立ち上がりから出力が安定するまでの遅延時間           | 6.5 |     | ms  |    |

T0108-03

図5. リセット・タイミング

## シリアル・レジスタ・マップ

| レジスタ・アドレス | レジスタの機能 <sup>(1)(2)</sup>                                   |                                                            |    |                             |                                                 |                                              |                                                         |                                |                                  |                                      |                                                 |

|-----------|-------------------------------------------------------------|------------------------------------------------------------|----|-----------------------------|-------------------------------------------------|----------------------------------------------|---------------------------------------------------------|--------------------------------|----------------------------------|--------------------------------------|-------------------------------------------------|

| A4-A0     | D10                                                         | D9                                                         | D8 | D7                          | D6                                              | D5                                           | D4                                                      | D3                             | D2                               | D1                                   | D0                                              |

| 00        | <RST><br>S/W RESET                                          | 0                                                          | 0  | 0                           | 0                                               | <REF><br>INTERNAL<br>OR<br>EXTERNAL          | 0                                                       | <PDN CHB><br>POWER<br>DOWN CHB | <PDN CHA><br>POWER<br>DOWN CH A  | 0                                    | <PDN<br>GLOBAL><br>GLOBAL<br>POWER<br>DOWN      |

| 04        | 0                                                           | 0                                                          | 0  | 0                           | <CLKIN GAIN><br>INPUT CLOCK BUFFER GAIN CONTROL |                                              |                                                         |                                |                                  |                                      | 0                                               |

| 0A        | 0                                                           | <DF><br>DATA<br>FORMAT 2S<br>COMP OR<br>STRAIGHT<br>BINARY | 0  | <PATTERNS><br>TEST PATTERNS |                                                 |                                              | 0                                                       | 0                              | 0                                | 0                                    | 0                                               |

| 0B        | <CUSTOM A><br>CUSTOM PATTERN (LOWER 11 BITS)                |                                                            |    |                             |                                                 |                                              |                                                         |                                |                                  |                                      |                                                 |

| 0C        | <FINE GAIN><br>FINE GAIN CONTROL (1dB to 6 dB)              |                                                            |    | 0                           | 0                                               | 0                                            | 0                                                       | 0                              | 0                                | 0                                    | <CUSTOM<br>B><br>CUSTOM<br>PATTERN<br>(MSB BIT) |

| 0D        | <OVRD><br>OVERRIDE<br>BIT                                   | 0                                                          | 0  | BYTE-WISE<br>OR<br>BIT-WISE | MSB OR<br>LSB FIRST                             | <COARSE<br>GAIN><br>COURSE<br>GAIN<br>ENABLE | FALLING OR<br>RISING BIT<br>CLOCK<br>CAPTURE<br>EDGE    | 0                              | 12-BIT OR<br>14-BIT<br>SERIALIZE | DDR OR<br>SDR BIT<br>CLOCK           | 1-WIRE OR<br>2-WIRE<br>INTERFACE                |

| 10        | <TERM CLK><br>LVDS INTERNAL TERMINATION BIT AND WORD CLOCKS |                                                            |    |                             |                                                 | <LVDS CURR><br>LVDS CURRENT SETTINGS         |                                                         |                                |                                  | <CURR DOUBLE><br>LVDS CURRENT DOUBLE |                                                 |

| 11        | WORD-WISE CONTROL                                           |                                                            | 0  | 0                           | 0                                               | 0                                            | <TERM DATA><br>LVDS INTERNAL TERMINATION - DATA OUTPUTS |                                |                                  |                                      |                                                 |

表 13. シリアル・インターフェイスによって

サポートされる機能の一覧

(1) 各レジスタ内の未使用ビット(表中で空白のセル)は、0に設定する必要があります。

(2) 1回の書き込み動作で1つのレジスタ内の複数の機能をプログラムできます。

## シリアル・レジスタの説明

| レジスタ・アドレス | ビット                |    |    |    |    |                                     |    |                                |                                 |    |                                  |  |

|-----------|--------------------|----|----|----|----|-------------------------------------|----|--------------------------------|---------------------------------|----|----------------------------------|--|

| A4-A0     | D10                | D9 | D8 | D7 | D6 | D5                                  | D4 | D3                             | D2                              | D1 | D0                               |  |

| 00        | <RST><br>S/W RESET | 0  | 0  | 0  | 0  | <REF><br>INTERNAL<br>OR<br>EXTERNAL | 0  | <PDN CHB><br>POWER<br>DOWN CHB | <PDN CHA><br>POWER<br>DOWN CH A | 0  | <PDN><br>GLOBAL<br>POWER<br>DOWN |  |

表 14

### D0 - D4 パワーダウン・モード

#### D0 <PDN GLOBAL>

0 通常動作

1 グローバル・パワーダウン。全チャネルのADC、内部リファレンス、内部PLL、出力バッファを含む。

#### D2 <PDN CHA>

0 CH Aパワーオン

1 CH A ADCパワーダウン

#### D3 <PDN CHB>

0 CH Bパワーオン

1 CH B ADCパワーダウン

#### D5 <REF> リファレンス

0 内部リファレンスがイネーブル

1 外部リファレンスがイネーブル

#### D10 <RST>

1 ソフトウェア・リセットの実行 - すべての内部レジスタをリセット (RSTは自動的に0に戻る)

| レジスタ・アドレス | ビット |    |    |    |                                                 |    |    |    |    |    |    |

|-----------|-----|----|----|----|-------------------------------------------------|----|----|----|----|----|----|

| A4 - A0   | D10 | D9 | D8 | D7 | D6                                              | D5 | D4 | D3 | D2 | D1 | D0 |

| 04        | 0   | 0  | 0  | 0  | <CLKIN GAIN><br>INPUT CLOCK BUFFER GAIN CONTROL |    |    |    |    | 0  | 0  |

表 15

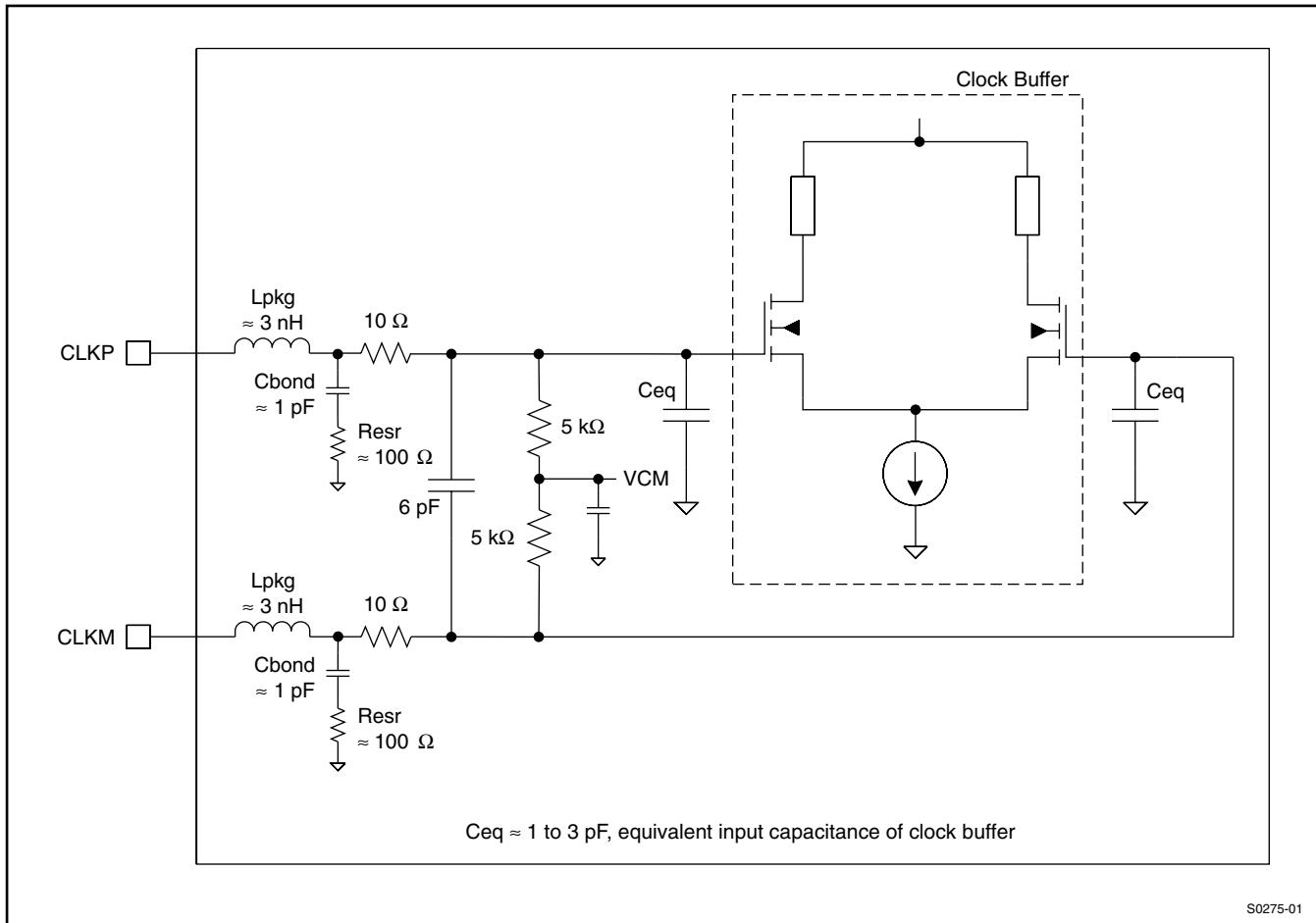

**D6-D2 <CLKIN GAIN> 入力クロック・バッファのゲイン制御**

|       |            |

|-------|------------|

| 11000 | ゲイン0、最小ゲイン |

| 00000 | ゲイン1       |

| 01100 | ゲイン2       |

| 01010 | ゲイン3       |

| 01001 | ゲイン4       |

| 01000 | ゲイン5、最大ゲイン |

| レジスタ・アドレス | ビット |                                                                 |    |                             |    |    |    |    |    |    |    |

|-----------|-----|-----------------------------------------------------------------|----|-----------------------------|----|----|----|----|----|----|----|

| A4-A0     | D10 | D9                                                              | D8 | D7                          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 00        | 0   | <DF><br>DATA<br>FORMAT -<br>2S COMP<br>OR<br>STRAIGHT<br>BINARY | 0  | <PATTERNS><br>TEST PATTERNS |    |    | 0  | 0  | 0  | 0  | 0  |

表 16

**D7-D5 <PATTERNS> キャプチャ・テスト・パターン**

|     |                                               |

|-----|-----------------------------------------------|

| 000 | 通常のADC動作                                      |

| 001 | すべて0を出力                                       |

| 010 | すべて1を出力                                       |

| 011 | トグル・パターンを出力                                   |

| 100 | 未使用                                           |

| 101 | カスタム・パターン (CUSTOMパターン・レジスタ0x0Bおよび0x0Cの内容) を出力 |

| 110 | DESKEWパターン (1010...のシリアル・ストリーム) を出力           |

| 111 | SYNCパターンを出力                                   |

**D9 <DF> データ形式選択**

|   |              |

|---|--------------|

| 0 | 2の補数形式       |

| 1 | ストレート・バイナリ形式 |

| レジスタ・アドレス | ビット                                          |    |    |    |    |    |    |    |    |    |    |

|-----------|----------------------------------------------|----|----|----|----|----|----|----|----|----|----|

| A4-A0     | D10                                          | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0B        | <CUSTOM A><br>CUSTOM PATTERN (LOWER 11 BITS) |    |    |    |    |    |    |    |    |    |    |

表 17

**D10 - D0** <CUSTOM A> カスタム・パターンの下位11ビット<DATAOUT10>...<DATAOUT0>

| レジスタ・アドレス | ビット                                             |    |    |    |    |    |    |    |    |    |                                    |

|-----------|-------------------------------------------------|----|----|----|----|----|----|----|----|----|------------------------------------|

| A4-A0     | D10                                             | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0                                 |

| 0C        | <FINE GAIN><br>FINE GAIN CONTROL (1 dB to 6 dB) |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | <CUSTOM B><br>CUSTOM PATTERN (MSB) |

表 18

**D0** <CUSTOM B> 12ビット・カスタム・パターンのMSB <DATAOUT11>

**D10-D8** <FINE GAIN> Fineゲイン制御

|     |                             |

|-----|-----------------------------|

| 000 | 0dBゲイン (フルスケール範囲 = 2.00Vpp) |

| 001 | 1dBゲイン (フルスケール範囲 = 1.78Vpp) |

| 010 | 2dBゲイン (フルスケール範囲 = 1.59Vpp) |

| 011 | 3dBゲイン (フルスケール範囲 = 1.42Vpp) |

| 100 | 4dBゲイン (フルスケール範囲 = 1.26Vpp) |

| 101 | 5dBゲイン (フルスケール範囲 = 1.12Vpp) |

| 110 | 6dBゲイン (フルスケール範囲 = 1.00Vpp) |

| レジスタ・アドレス | ビット                         |    |    |                             |                     |                                              |                                                      |    |                                  |                            |                                  |

|-----------|-----------------------------|----|----|-----------------------------|---------------------|----------------------------------------------|------------------------------------------------------|----|----------------------------------|----------------------------|----------------------------------|

| A4-A0     | D10                         | D9 | D8 | D7                          | D6                  | D5                                           | D4                                                   | D3 | D2                               | D1                         | D0                               |

| 0D        | <OVRD><br>OVER-RIDE<br>BITE | 0  | 0  | BYTE-WISE<br>OR<br>BIT-WISE | MSB OR<br>LSB FIRST | <COARSE<br>GAIN><br>COURSE<br>GAIN<br>ENABLE | FALLING OR<br>RISING BIT<br>CLOCK<br>CAPTURE<br>EDGE | 0  | 14-BIT OR<br>16-BIT<br>SERIALIZE | DDR OR<br>SDR BIT<br>CLOCK | 1-WIRE OR<br>2-WIRE<br>INTERFACE |

表 19

**D0** インターフェイス選択

|   |             |

|---|-------------|

| 0 | 1線式インターフェイス |

| 1 | 2線式インターフェイス |

**D1** ビット・クロック選択(2線式インターフェイスのみ)

|   |             |

|---|-------------|

| 0 | DDRビット・クロック |

| 1 | SDRビット・クロック |

**D2** シリアル化選択

|   |          |

|---|----------|

| 0 | 12倍シリアル化 |

| 1 | 14倍シリアル化 |

|            |                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------|

| <b>D4</b>  | ビット・クロックのキャップチャ・エッジ (SDRビット・クロック選択時 (D1 = 1) のみ)                                                           |

| 0          | ビット・クロックの立ち下がりエッジでデータを取り込み                                                                                 |

| 1          | ビット・クロックの立ち上がりエッジでデータを取り込み                                                                                 |

| <b>D5</b>  | <COARSE GAIN> Coarseゲイン制御                                                                                  |

| 0          | 0dB Coarseゲイン                                                                                              |

| 1          | 3.5dB Coarseゲイン (フルスケール範囲 = 1.34Vpp)                                                                       |

| <b>D6</b>  | MSBまたはLSBファーストの選択                                                                                          |

| 0          | MSBファースト                                                                                                   |

| 1          | LSBファースト                                                                                                   |

| <b>D7</b>  | バイト/ビット単位出力の選択 (2線式インターフェイスのみ)                                                                             |

| 0          | バイト単位                                                                                                      |

| 1          | ビット単位                                                                                                      |

| <b>D10</b> | <OVRD> オーバライド・ビットレジスタ0x0Dの機能はすべて、パラレル制御ピンを使用しても制御できます。ビット<OVRD>を1に設定すると、パラレル・ピンの設定がレジスタ0x0Dの内容でオーバライドされます。 |

| 0          | オーバライドをディスエーブル                                                                                             |

| 1          | オーバライドをイネーブル                                                                                               |

| レジスタ・アドレス | ビット   |  |                                                             |    |    |    |                                      |    |    |    |                                      |    |    |

|-----------|-------|--|-------------------------------------------------------------|----|----|----|--------------------------------------|----|----|----|--------------------------------------|----|----|

|           | A4-A0 |  | D10                                                         | D9 | D8 | D7 | D6                                   | D5 | D4 | D3 | D2                                   | D1 | D0 |

|           | 10    |  | <TERM CLK><br>LVDS INTERNAL TERMINATION BIT AND WORD CLOCKS |    |    |    | <LVDS CURR><br>LVDS CURRENT SETTINGS |    |    |    | <LVDS DOUBLE><br>LVDS CURRENT DOUBLE |    |    |

表 20

|              |                                          |

|--------------|------------------------------------------|

| <b>D0</b>    | <CURR DOUBLE> LVDSデータ出力電流の2倍化            |

| 0            | 通常のLVDS電流 (<D5...D2>で設定)                 |

| 1            | 通常値の2倍                                   |

| <b>D1</b>    | <CURR DOUBLE> LVDSビットおよびワード・クロック出力電流の2倍化 |

| 0            | 通常のLVDS電流 (<D5...D2>で設定)                 |

| 1            | 通常値の2倍                                   |

| <b>D3-D2</b> | <LVDS CURR> LVDSデータ出力の電流設定               |

| 00           | 3.5 mA                                   |

| 01           | 4 mA                                     |

| 10           | 2.5 mA                                   |

| 11           | 3 mA                                     |

| <b>D5-D4</b> | <LVDS CURR> LVDSビットおよびワード・クロック出力の電流設定    |

| 00           | 3.5 mA                                   |

| 01           | 4 mA                                     |

| 10           | 2.5 mA                                   |

| 11           | 3 mA                                     |

**D10-D6****<TERM CLK>** ビットおよびワード・クロック出力に対するLVDS内部終端

|       |        |

|-------|--------|

| 00000 | 内部終端なし |

| 00001 | 166 Ω  |

| 00010 | 200 Ω  |

| 00100 | 250 Ω  |

| 01000 | 333 Ω  |

| 10000 | 500 Ω  |

上記のビットは任意の組み合わせでプログラムでき、結果は選択した抵抗値の並列結合となります。例えば、00101は $166||250$ の並列結合 = 100Ωとなります。

|       |       |

|-------|-------|

| 00101 | 100 Ω |

|-------|-------|

| レジスタ・アドレス | ビット               |    |    |    |    |                                                         |    |    |    |    |    |

|-----------|-------------------|----|----|----|----|---------------------------------------------------------|----|----|----|----|----|

|           | D10               | D9 | D8 | D7 | D6 | D5                                                      | D4 | D3 | D2 | D1 | D0 |

| 11        | WORD-WISE CONTROL | 0  | 0  | 0  | 0  | <TERM DATA><br>LVDS INTERNAL TERMINATION - DATA OUTPUTS |    |    |    |    |    |

表 21

**D4-D0****<TERM DATA>** データ出力に対するLVDS内部終端

|       |        |

|-------|--------|

| 00000 | 内部終端なし |

| 00001 | 166 Ω  |

| 00010 | 200 Ω  |

| 00100 | 250 Ω  |

| 01000 | 333 Ω  |

| 10000 | 500 Ω  |

上記のビットは任意の組み合わせでプログラムでき、結果は選択した抵抗値の並列結合となります。例えば、00101は $166||250$ の並列結合 = 100Ωとなります。

|       |       |

|-------|-------|

| 00101 | 100 Ω |

|-------|-------|

**D10-D9**

## 2線式インターフェイスの選択時のみ

|       |                               |

|-------|-------------------------------|

| 00    | バイト単位またはビット単位の出力、1倍のフレーム・クロック |

| 11    | ワード単位の出力がイネーブル、0.5倍のフレーム・クロック |

| 01,10 | 設定できません                       |

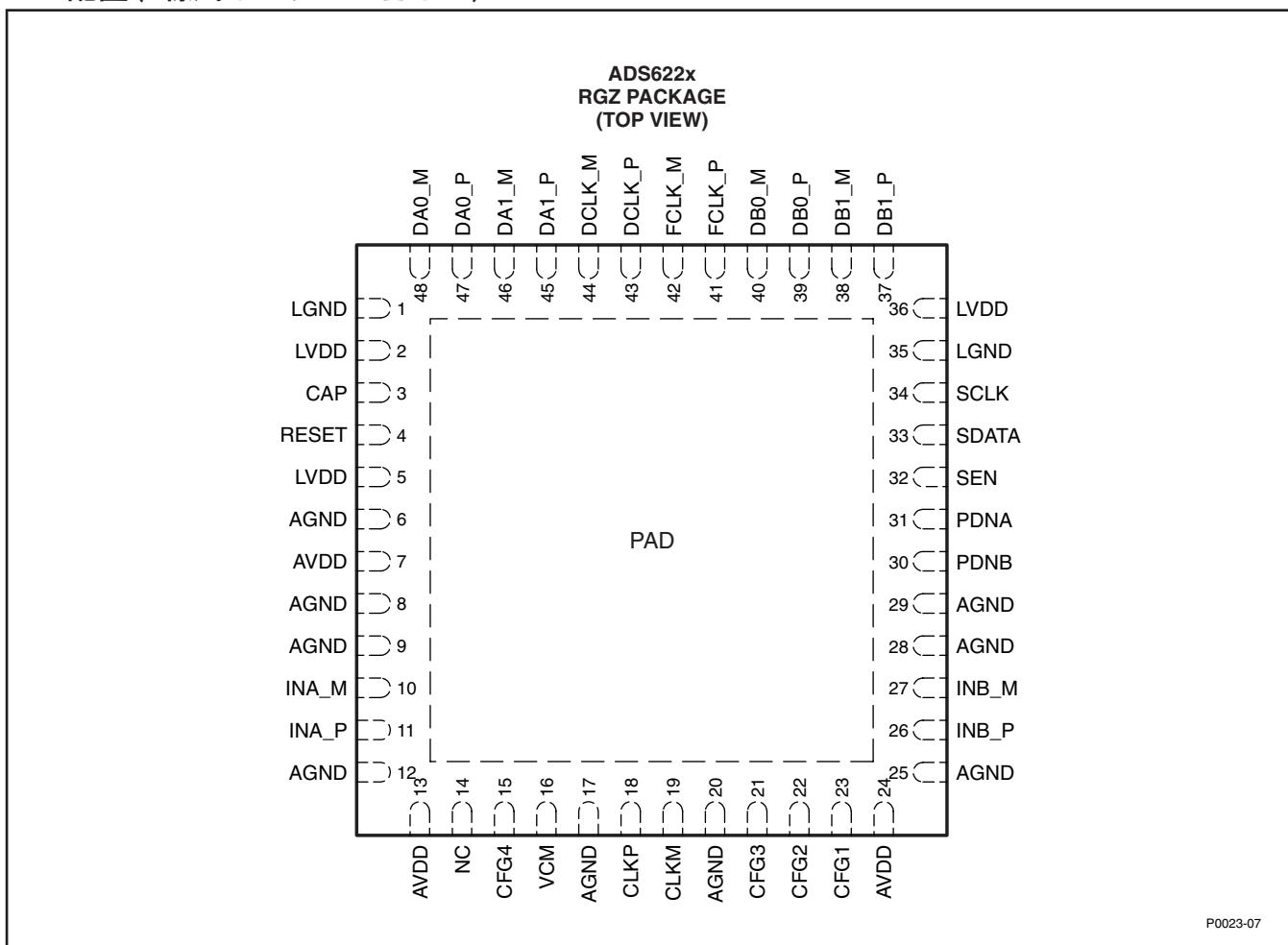

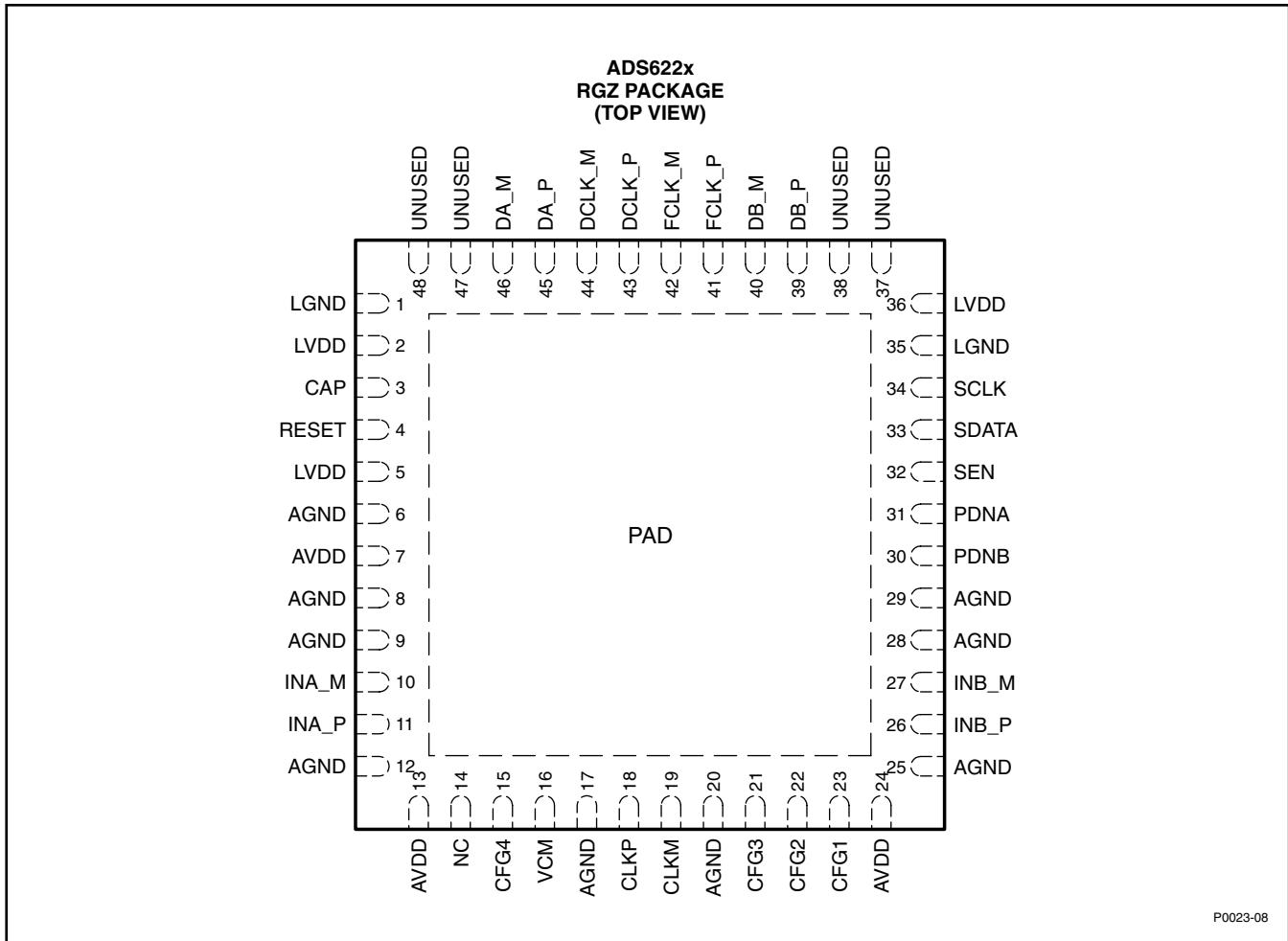

## ピン配置(2線式インターフェイス)

## ピン構成(2線式インターフェイス)

| ピン<br>名称            | I/O<br>番号                   | ピン数 | 説明                                                   |

|---------------------|-----------------------------|-----|------------------------------------------------------|

| <b>電源およびグランド・ピン</b> |                             |     |                                                      |

| AVDD                | 7,13,24                     | 3   | アナログ電源                                               |

| AGND                | 6,8,9,12,17,<br>20,25,28,29 | 9   | アナログ・グランド                                            |

| LVDD                | 2,5,36                      | 3   | デジタル電源                                               |

| LGND                | 1,35                        | 2   | デジタル・グランド                                            |

| <b>入力ピン</b>         |                             |     |                                                      |

| CLKP, CLKM          | 18,19                       | 1   | 差動入力クロック・ペア                                          |

| INA_P, INA_M        | 11,10                       | 1   | 差動入力信号ペア、チャネルA。使用しない場合は、VCMに接続します。フローティングにはしないでください。 |

| INB_P, INB_M        | 26,27                       | 1   | 差動入力信号ペア、チャネルB。使用しない場合は、VCMに接続します。フローティングにはしないでください。 |

| CAP                 | 3                           | 1   | グランドとの間に2nFのコンデンサを接続します。                             |

## ピン構成(2線式インターフェイス)

| ピン          |       | I/O | ピン数 | 説明                                                                                                                                                                                                                                                                                    |

|-------------|-------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称          | 番号    |     |     |                                                                                                                                                                                                                                                                                       |

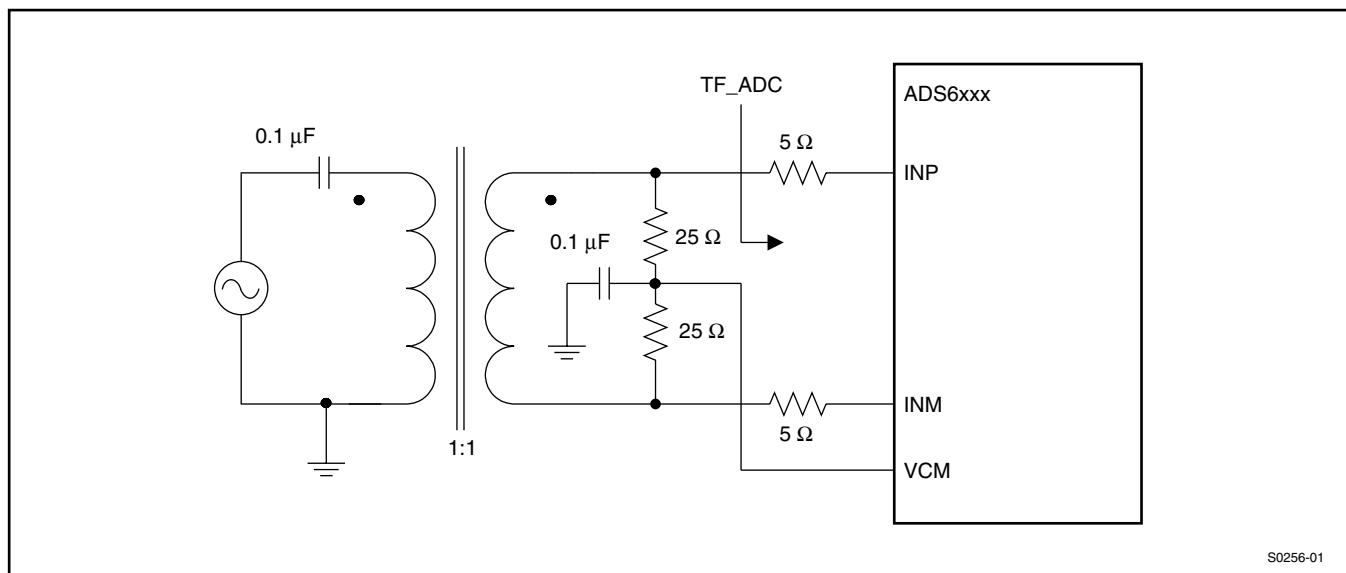

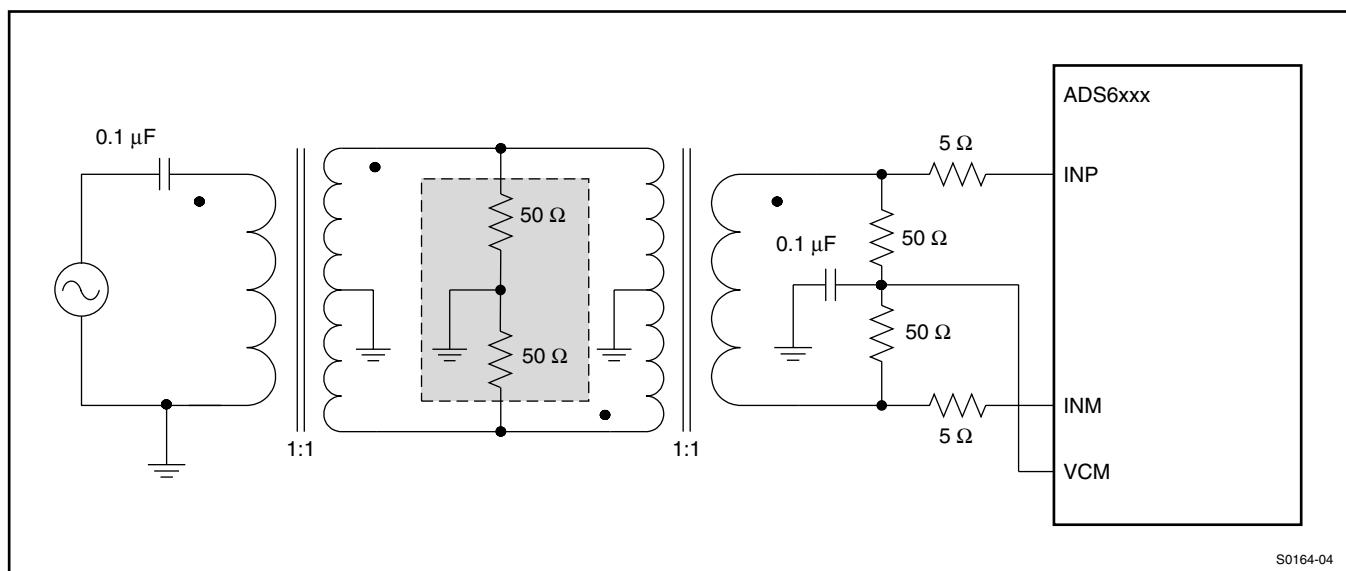

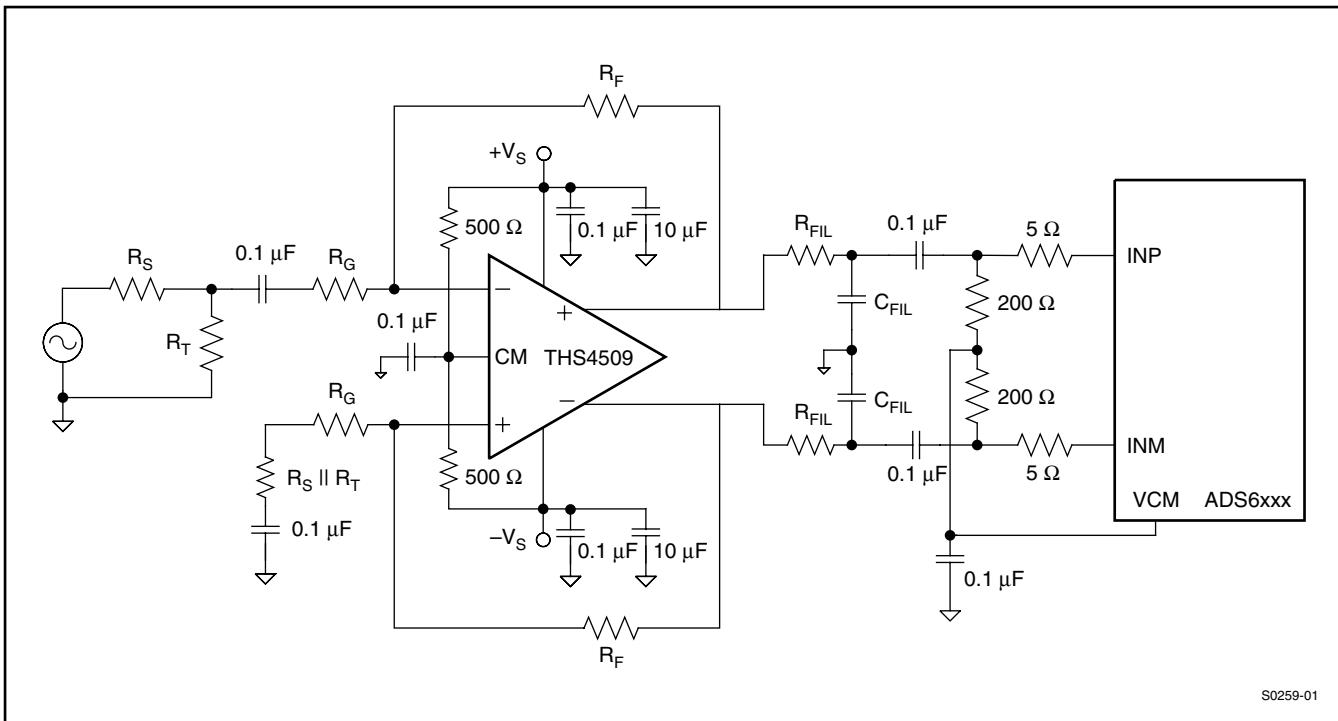

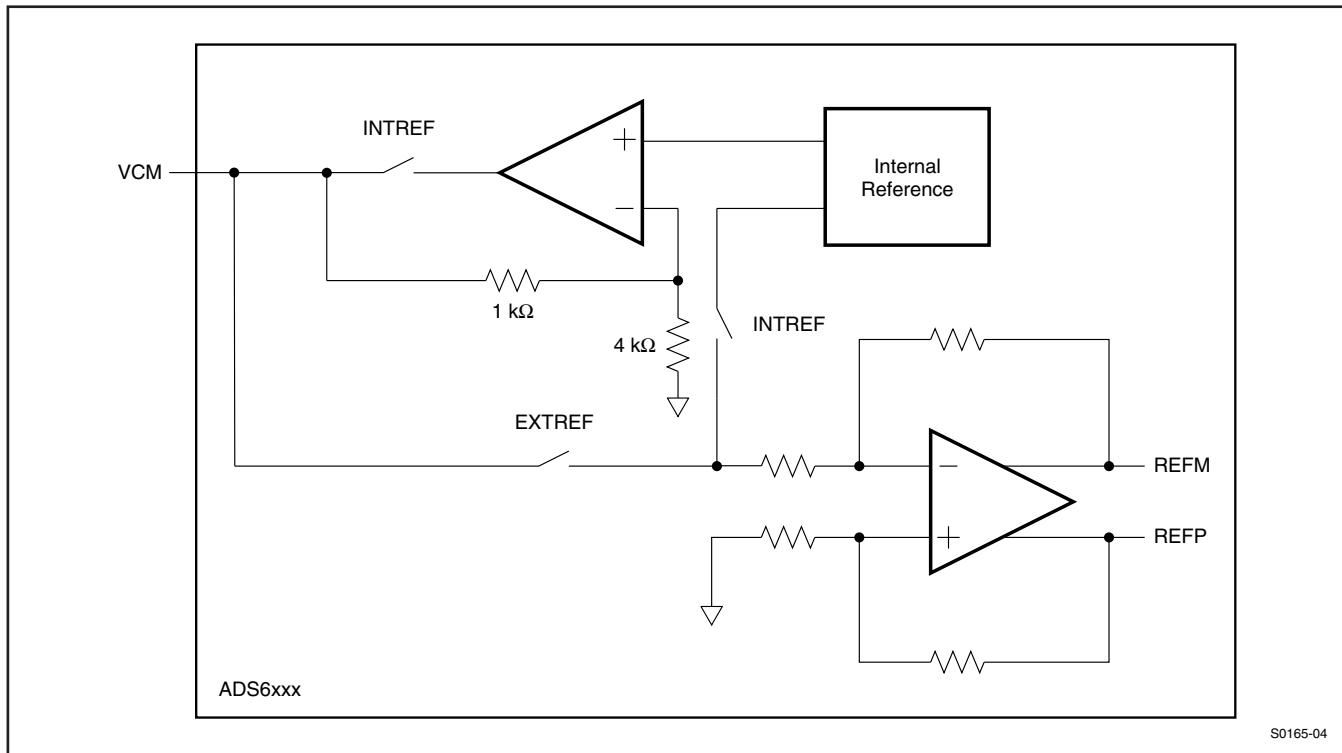

| SCLK        | 34    | I   | 1   | RESETが“Low”的とき、このピンはシリアル・インターフェイスのクロック入力として機能します。RESETが“High”的ときは、DESKEW、SYNC、およびグローバルPOWER DOWNモードを(SDATAとともに)制御します。表5を参照してください。<br>このピンには内部にプルダウン抵抗があります。                                                                                                                           |