# ADS131B26-Q1 電圧、電流、温度センシング向け、 SPI と 6 チャネルの ADC を搭載した車載用高電圧バッテリ パック モニタ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1: -40°C ~ +125°C, T<sub>A</sub>

- 機能安全準拠**

- 機能安全アプリケーション向けに開発

- ASIL D** までの ISO 26262 機能安全システム設計に役立つ資料を入手可能

- ASIL D までの決定論的対応能力

- ASIL D までのハードウェア機能

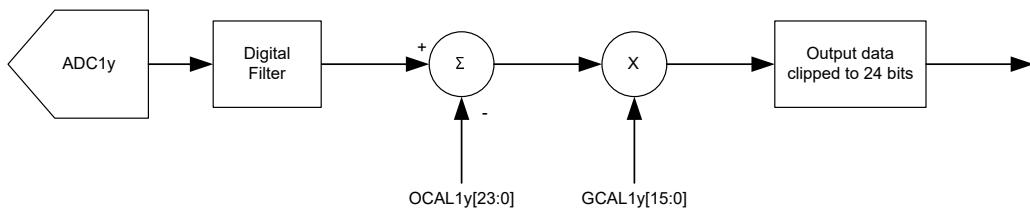

- 電流シャント測定用の 2 つの同時サンプリング 24 ビット ADC (ADC1A, ADC1B):

- フルスケールレンジをプログラム可能:

- ±39mV ~ ±312.5mV

- 幅広いシャント抵抗値と電流測定範囲をサポート

- 以下を使用して、高精度の電流シャント測定を実現:

- オフセット誤差: ±1.5µV (最大値)

- ゲインドリフト: 20ppm/°C (最大値)

- データレートをプログラム可能: 500SPS ~ 64kSPS

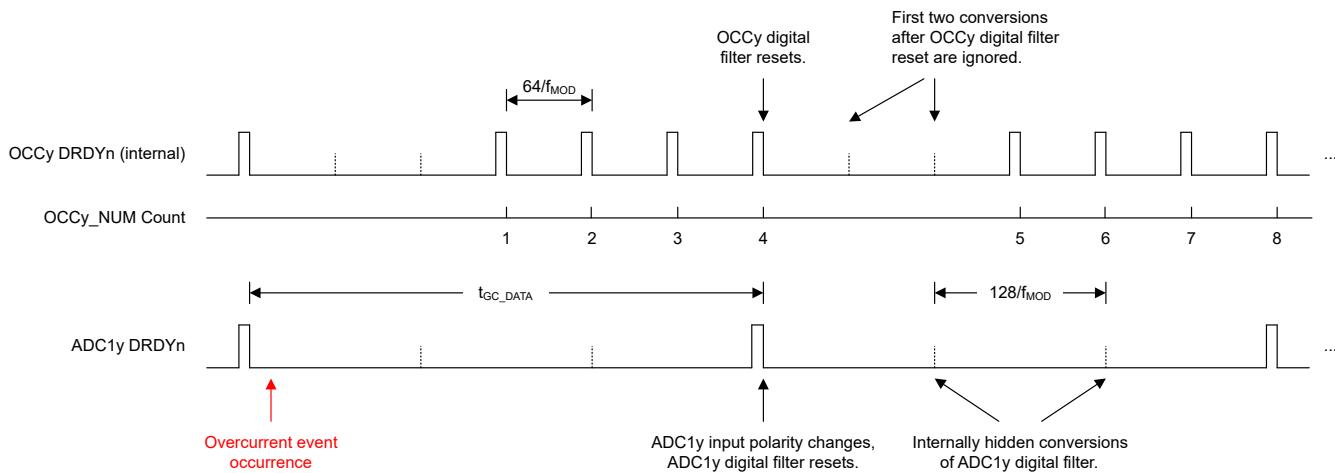

- 高速過電流検出用のプログラム可能なスレッショルドを備えた ADC ごとのデジタル過電流コンパレータ

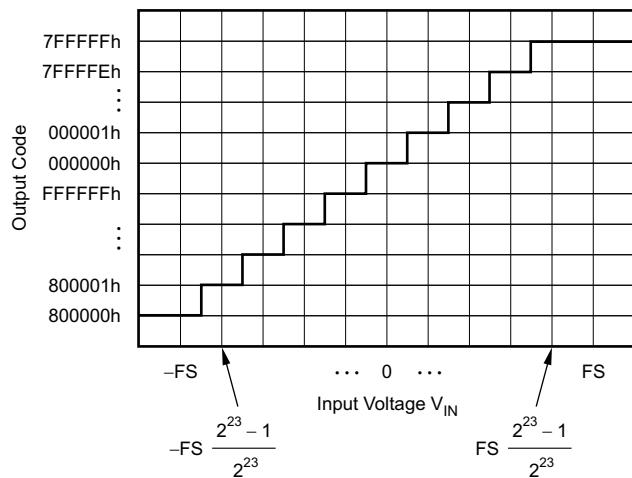

- 電圧測定用の 2 つの同時サンプリング 24 ビット ADC (ADC3A, ADC3B):

- データレートをプログラム可能: 500SPS ~ 64kSPS

- フルスケールレンジをプログラム可能:

- ±312.5mV ~ ±1.25V

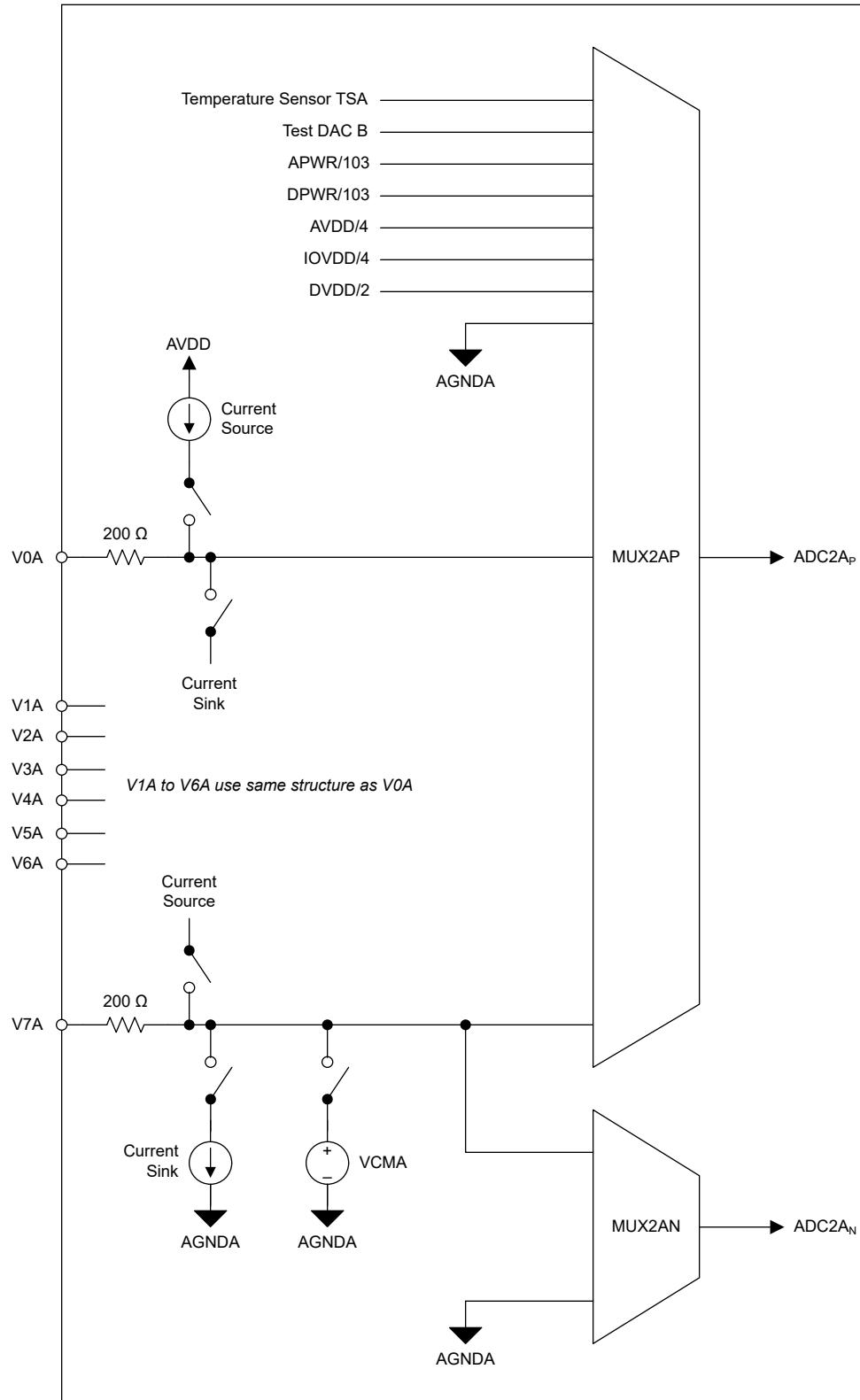

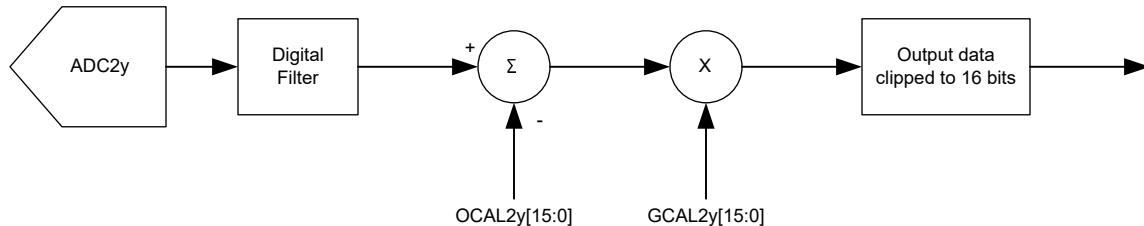

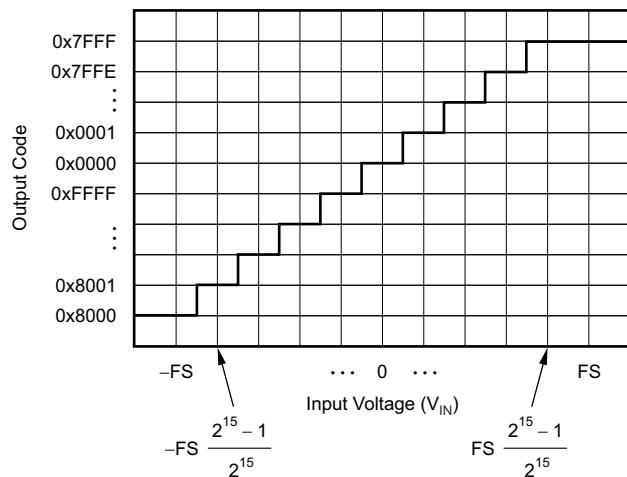

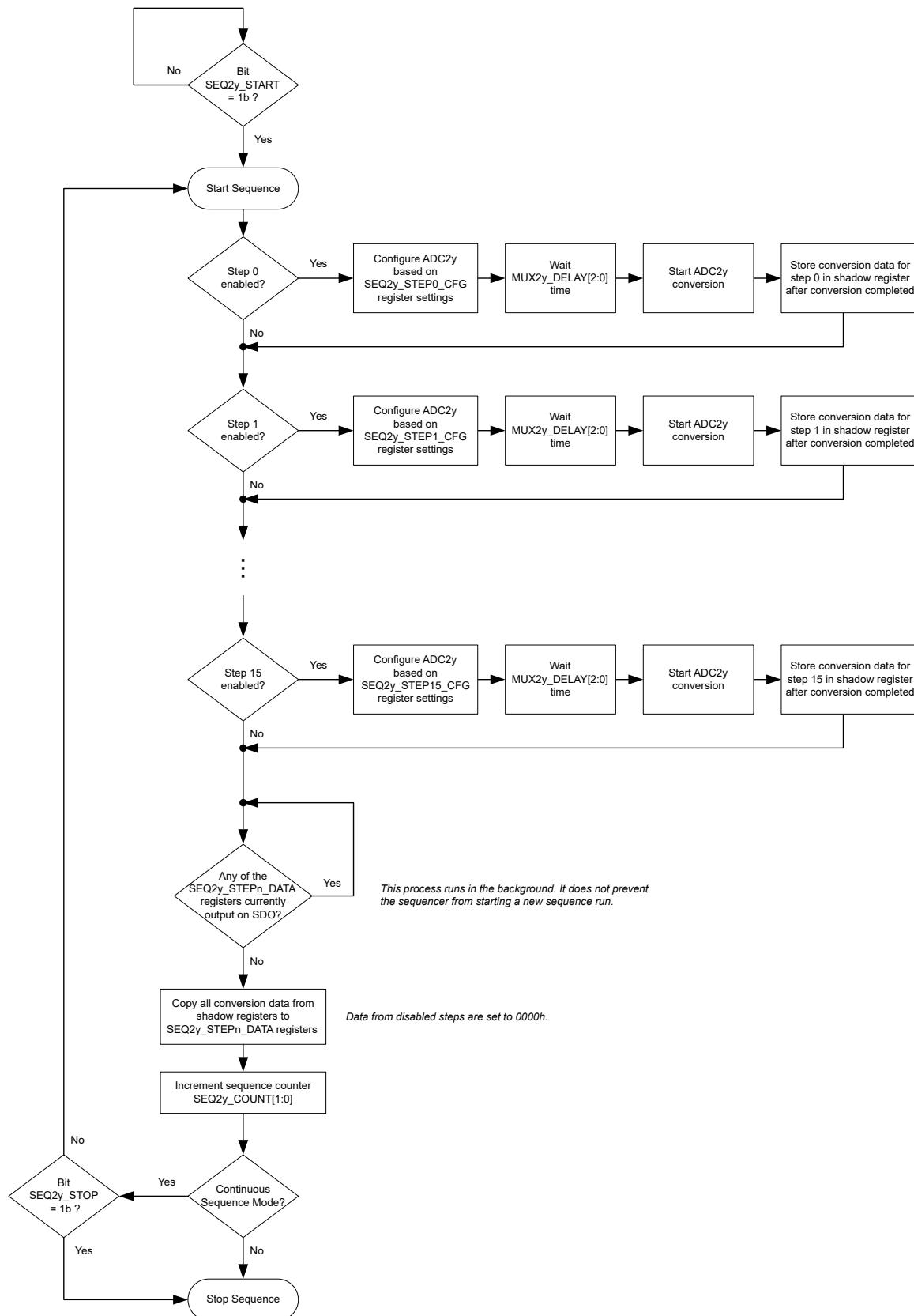

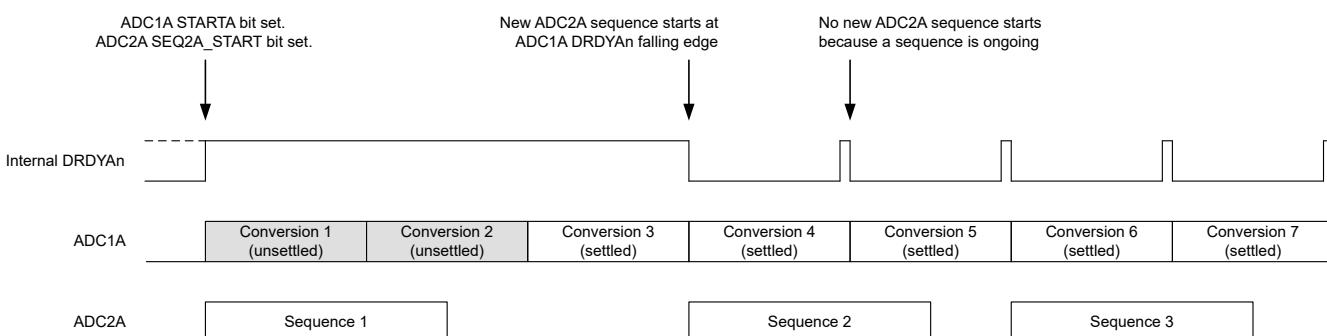

- 電圧および温度測定用の 2 つの多重化 16 ビット ADC (ADC2A, ADC2B):

- 8 つのアナログ入力 (各 ADC)

- フルスケールレンジをプログラム可能: ±312.5mV ~ ±1.25V

- チャネルシーケンサ

- ランダムなハードウェア障害を軽減および検出するための監視および診断機能

- 電源電圧範囲: 2.9V ~ 16V

- SPI 互換のインターフェイス

- PWM 機能を備えた 9 個の GPIO

## 2 アプリケーション

- 車載用バッテリ管理システム (BMS):**

- 電流シャント測定

- 外付け抵抗分圧器を使用した電圧測定

- サーミスタまたはアナログ出力温度センサを使用した温度測定

## 3 概要

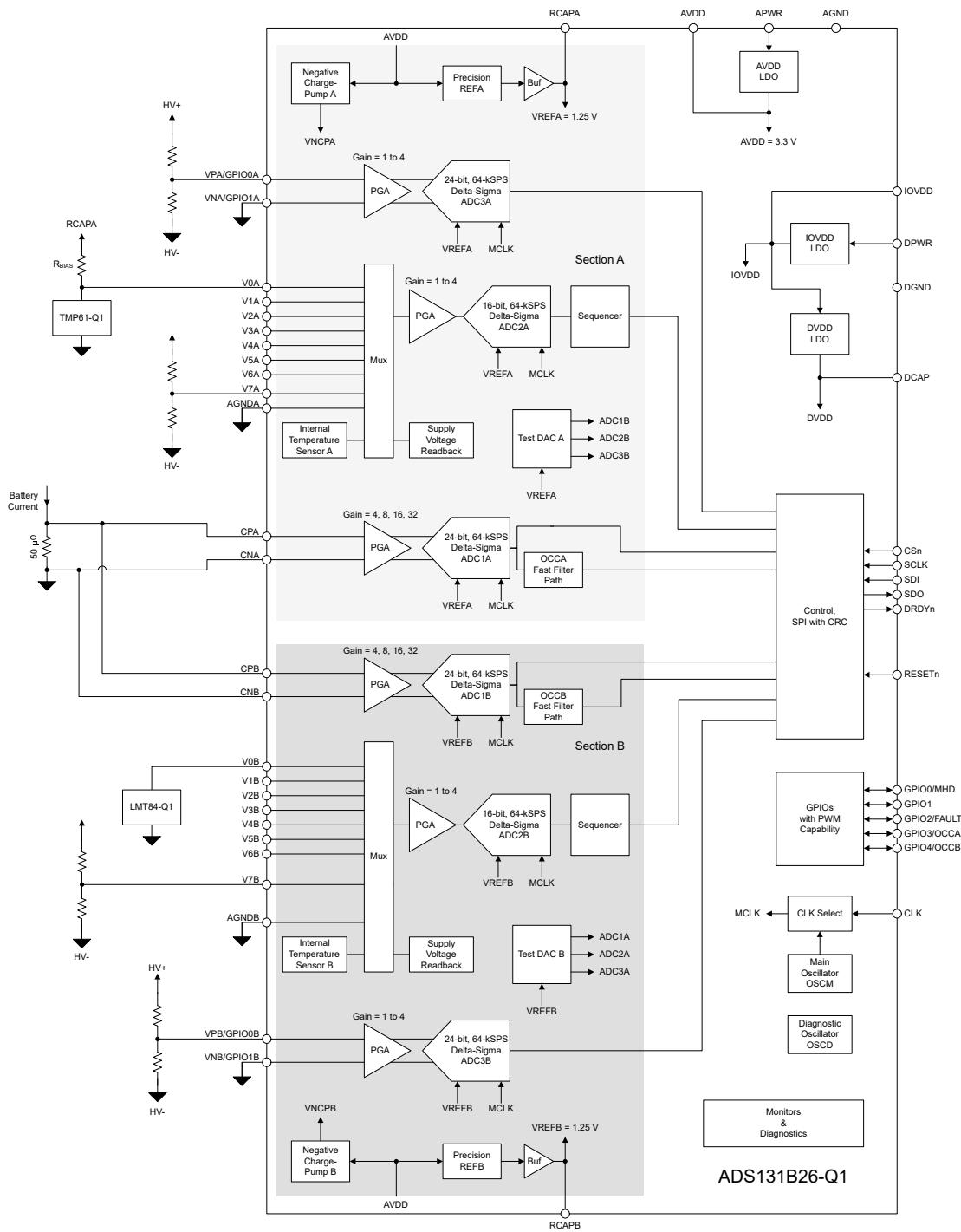

ADS131B26-Q1 は、車載用電気自動車 (EV) バッテリ管理システム (BMS) 向けの完全統合型高電圧バッテリ パック モニタです。

### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------------|----------------------|--------------------------|

| ADS131B26-Q1 | PHP (HTQFP, 48)      | 9mm × 9mm                |

(1) 詳細については、[メカニカル、パッケージ、および注文情報](#)をご覧ください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

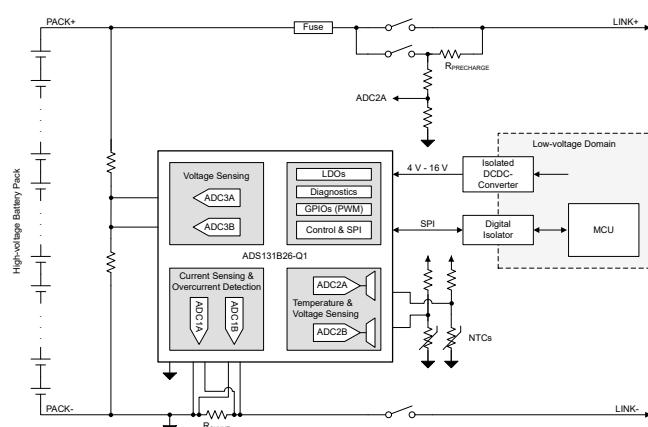

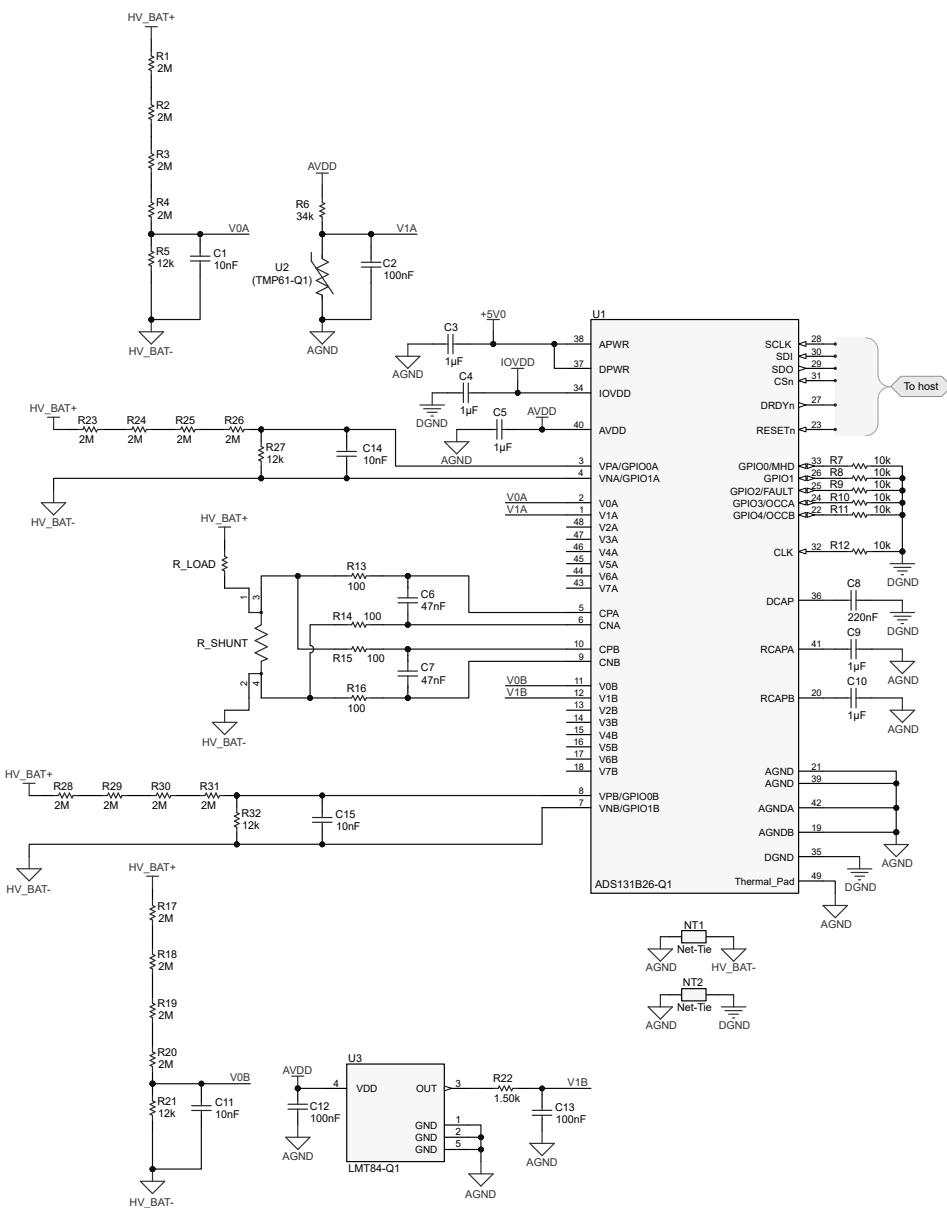

EV BMS バッテリ パック モニタのシステム ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

ADS131B26-Q1 には 2 つの同時サンプリング、高精度、24 ビット アナログ / デジタル コンバータ (ADC) チャネル (ADC1A, ADC1B) が内蔵されており、外付けのシャント抵抗を使用して高分解能かつ高精度でバッテリ電流を冗長測定できます。2 つの独立したデジタル コンパレータにより、2 つの ADC と並列で高速な過電流検出が可能です。

2 つの同時サンプリング 24 ビット ADC (ADC3A, ADC3B) がもう 1 組内蔵されており、外付けの高電圧抵抗分圧器を使用してバッテリ電流と同期してバッテリ パック電圧を測定し、バッテリの充電状態と健全性の正確な計算を実行できます。

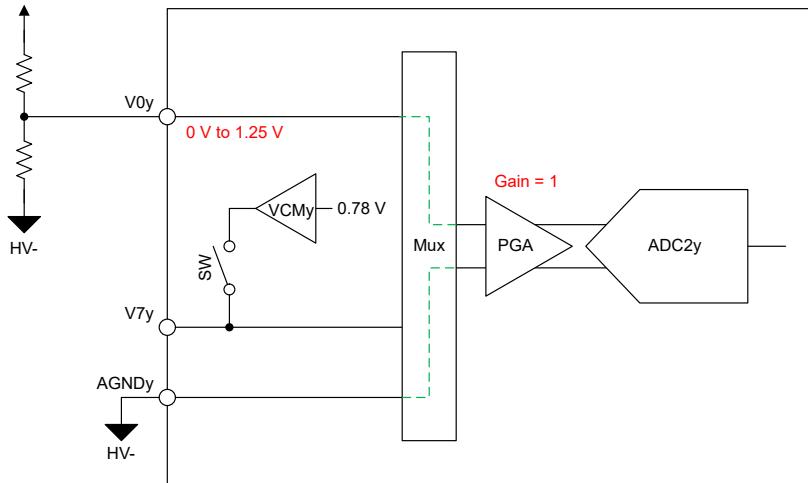

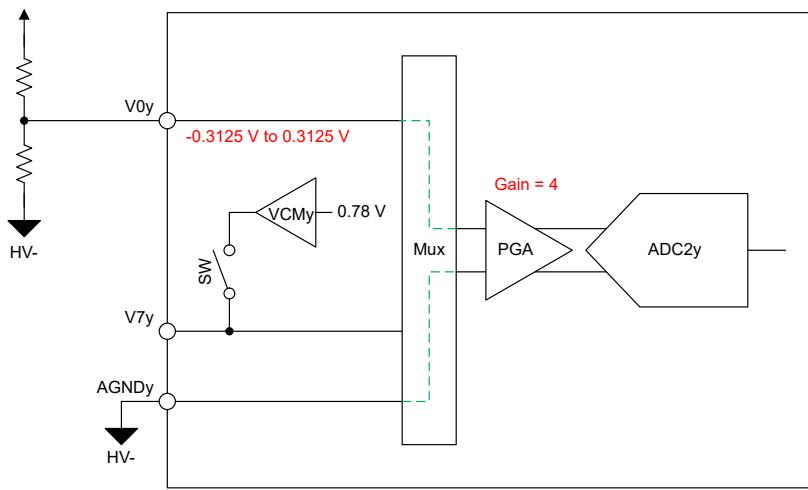

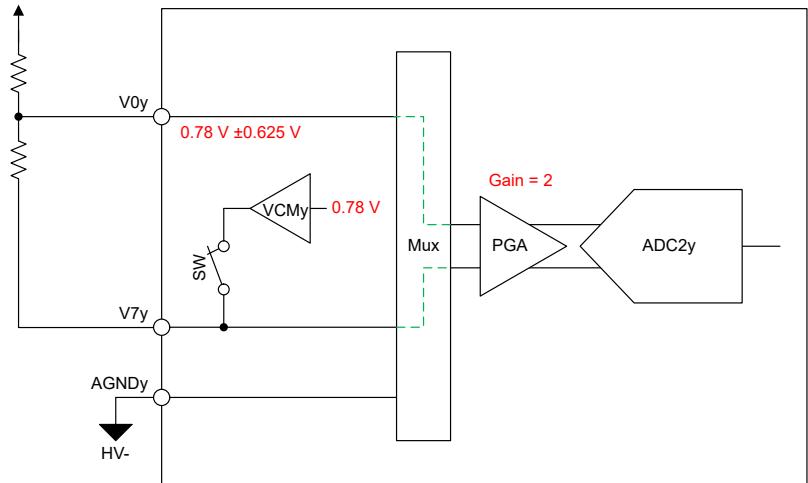

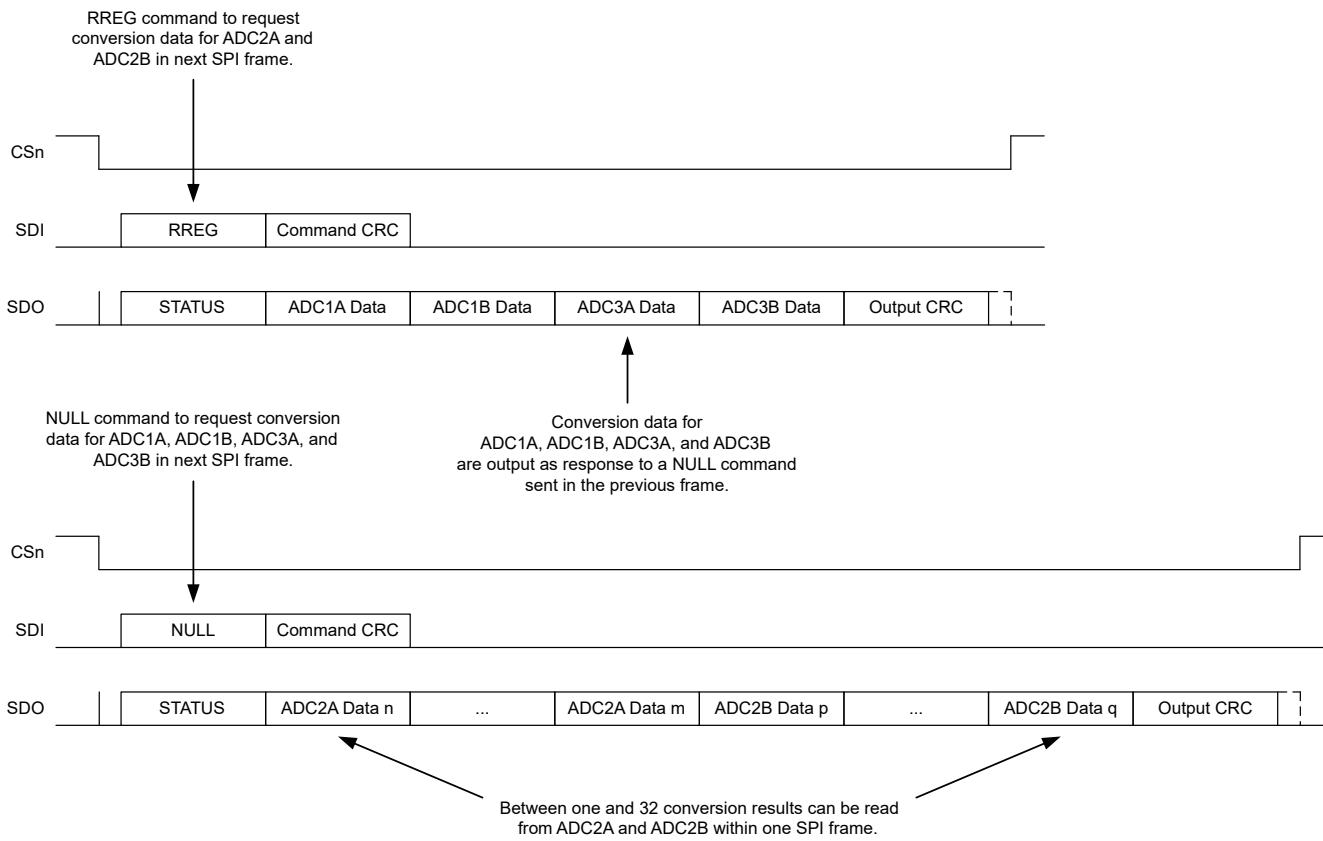

追加で 2 つの多重化 16 ビット ADC チャネル (ADC2A, ADC2B) を利用すれば、外付けの高電圧抵抗分圧器を使用した、シャント温度やシステム内の他の電圧 (バッテリ パック電圧など) の測定が可能です。シャント温度は、サーミスタやアナログ出力温度センサなどの外付け温度センサを使用して測定します。各 ADC には、構成済みのマルチプレクサ入力を自動的に流して SPI 上の通信を低減する、チャネル シーケンサが搭載されています。

本デバイスは、ランダムなハードウェア障害を軽減および検出できる多数の監視 / 診断機能を内蔵しているため、機能安全 BMS の開発が容易になります。

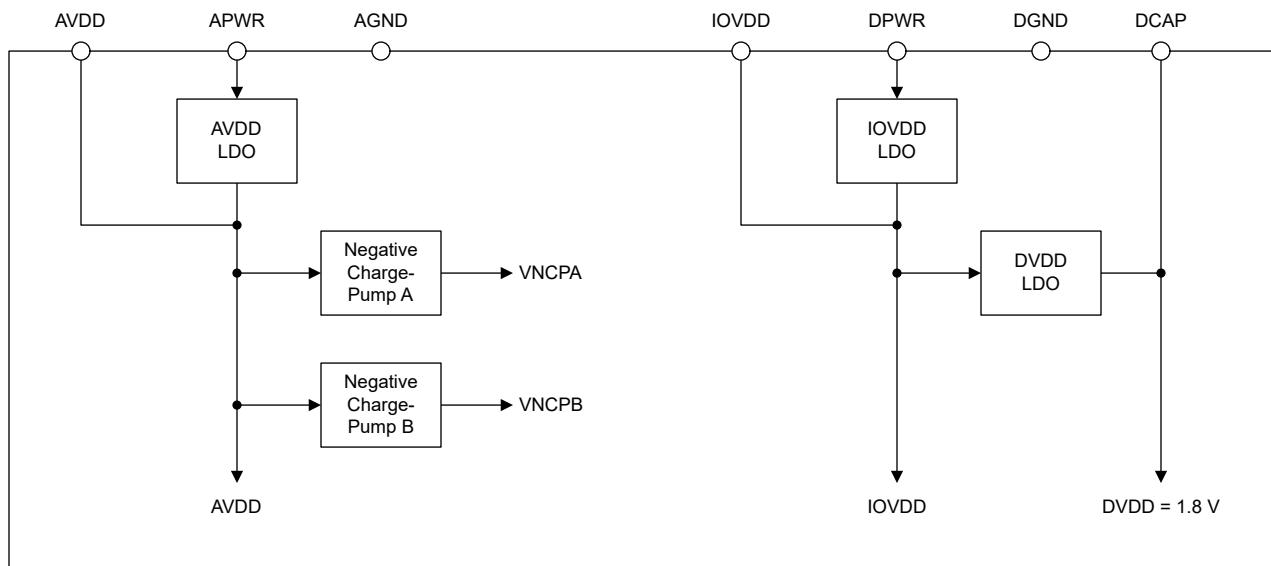

最大 16V の入力範囲を持つ内部リニア レギュレータは、非安定型 DC/DC コンバータを使用したデバイスへの電力供給をサポートしています。

ADS131B26-Q1 は、48 ピン HTQFP パッケージで供給され、車載用温度範囲の -40°C~+105°C で動作が規定されています。

## 目次

|                  |    |                         |     |

|------------------|----|-------------------------|-----|

| 1 特長             | 1  | 7.2 機能ブロック図             | 30  |

| 2 アプリケーション       | 1  | 7.3 機能説明                | 31  |

| 3 概要             | 1  | 7.4 デバイスの機能モード          | 60  |

| 4 ピン構成および機能      | 4  | 7.5 プログラミング             | 69  |

| 5 仕様             | 7  | 8 レジスタ マップ              | 83  |

| 5.1 絶対最大定格       | 7  | 8.1 レジスタ                | 84  |

| 5.2 ESD 定格       | 7  | 9 アプリケーションと実装           | 242 |

| 5.3 推奨動作条件       | 8  | 9.1 アプリケーション情報          | 242 |

| 5.4 熱に関する情報      | 9  | 9.2 代表的なアプリケーション        | 242 |

| 5.5 電気的特性        | 9  | 9.3 電源に関する推奨事項          | 246 |

| 5.6 タイミング要件      | 16 | 9.4 レイアウト               | 250 |

| 5.7 スイッチング特性     | 17 | 10 デバイスおよびドキュメントのサポート   | 252 |

| 5.8 タイミング図       | 18 | 10.1 ドキュメントのサポート        | 252 |

| 5.9 代表的特性        | 19 | 10.2 ドキュメントの更新通知を受け取る方法 | 252 |

| 6 パラメータ測定情報      | 26 | 10.3 サポート・リソース          | 252 |

| 6.1 オフセットドリフトの測定 | 26 | 10.4 商標                 | 252 |

| 6.2 ゲインドリフトの測定   | 26 | 10.5 静電気放電に関する注意事項      | 252 |

| 6.3 ノイズ性能        | 27 | 10.6 用語集                | 252 |

| 7 詳細説明           | 28 | 11 改訂履歴                 | 252 |

| 7.1 概要           | 28 | 12 メカニカル、パッケージ、および注文情報  | 253 |

## 4 ピン構成および機能

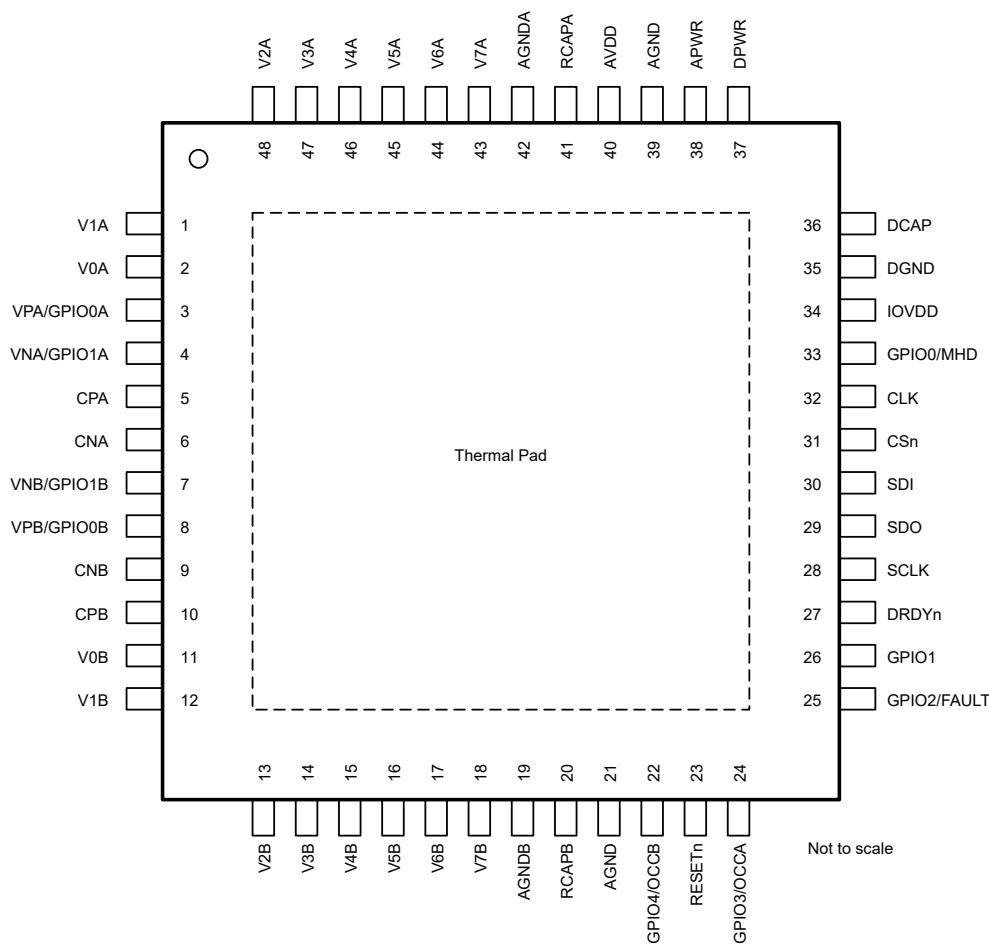

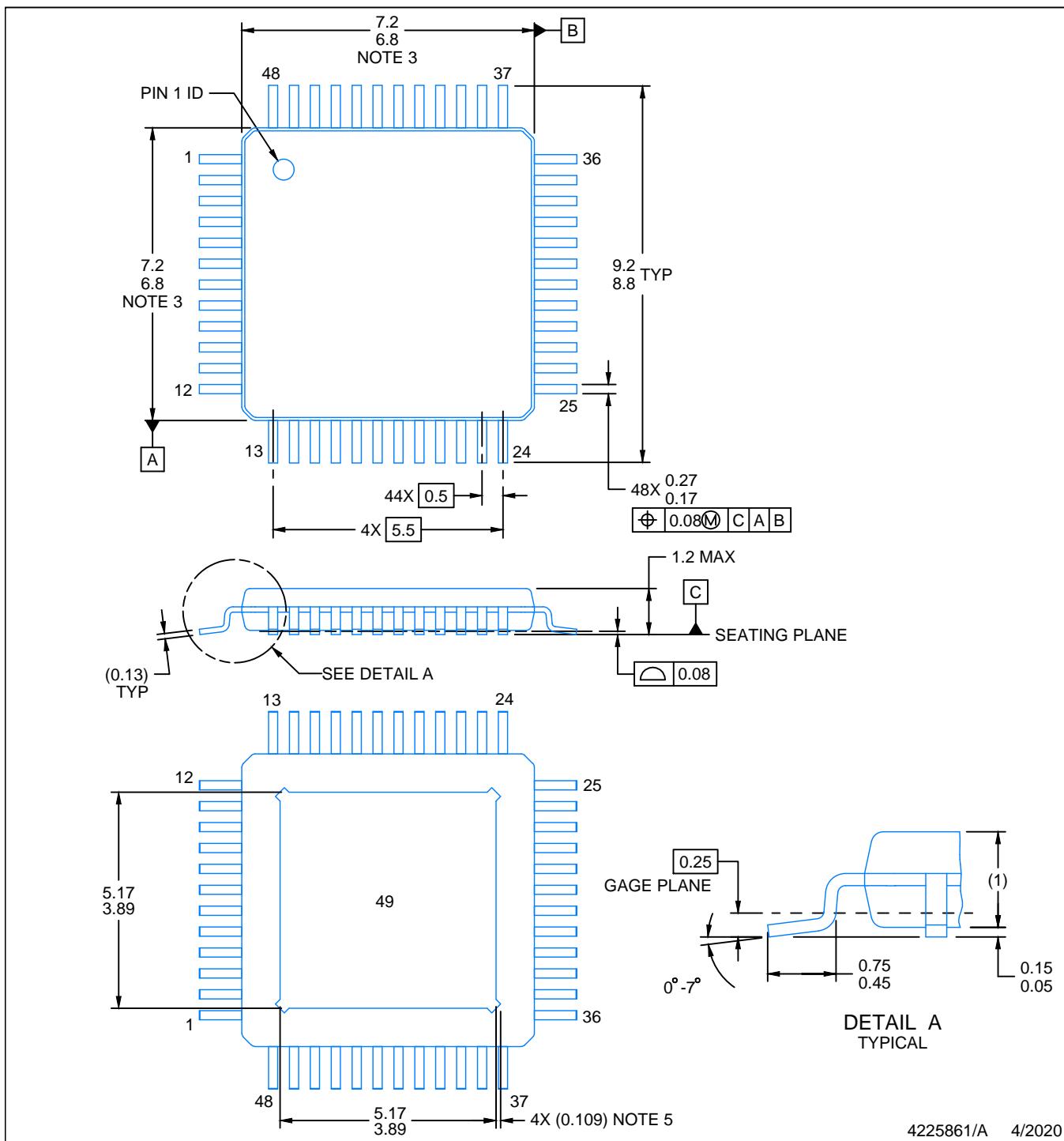

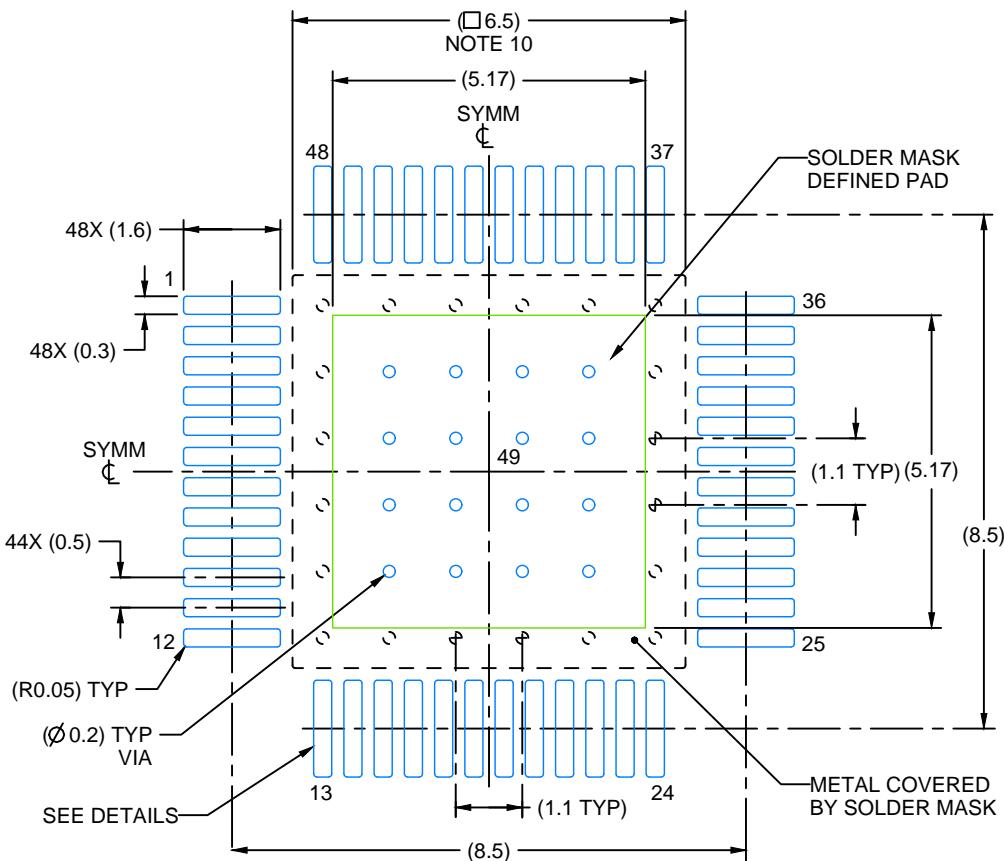

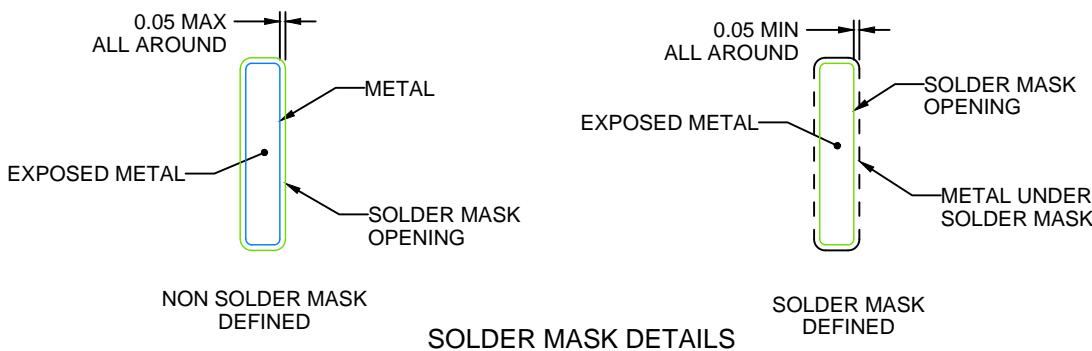

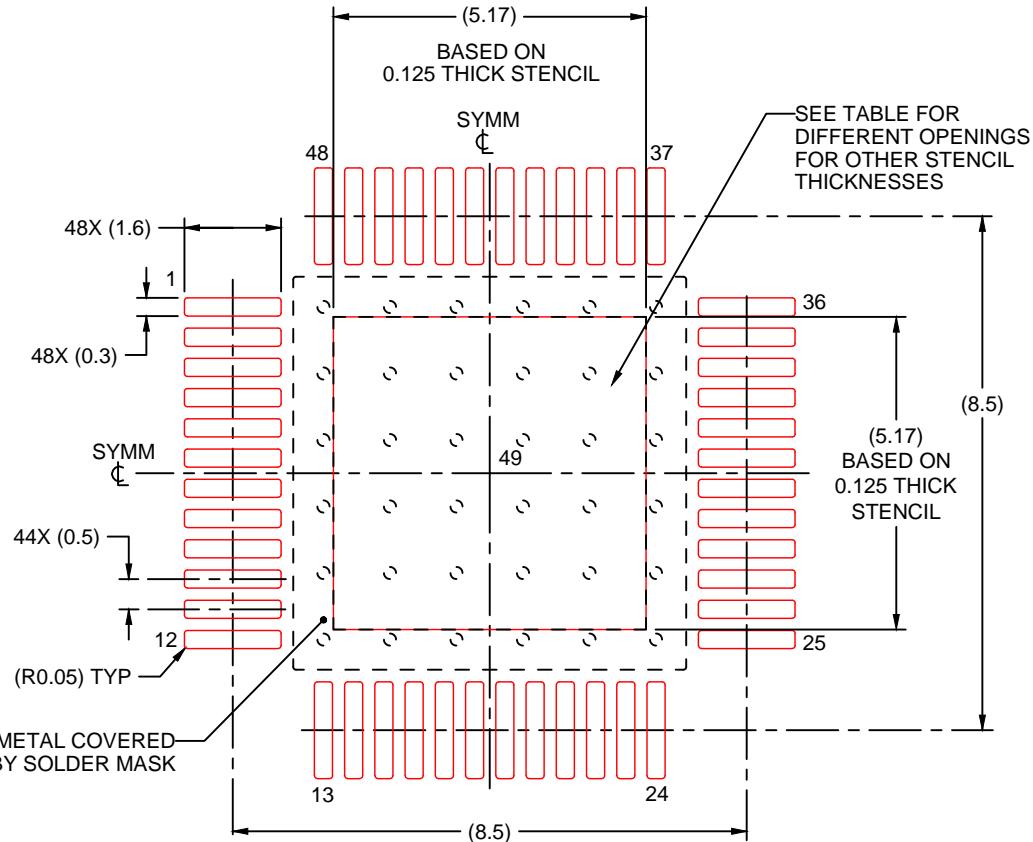

図 4-1. PHP パッケージ、48 ピン HTQFP (上面図)

表 4-1. ピンの機能

| ピン    |    | タイプ      | 説明 <sup>(1)</sup>                                                                    |

|-------|----|----------|--------------------------------------------------------------------------------------|

| 名称    | 番号 |          |                                                                                      |

| AGND  | 39 | アナログ電源   | アナログ グランド。                                                                           |

| AGND  | 21 | アナログ電源   | アナログ グランド。                                                                           |

| AGNDA | 42 | アナログ電源   | セクション A アナログ グランド。AGND に接続。                                                          |

| AGNDB | 19 | アナログ電源   | セクション B アナログ グランド。AGND に接続。                                                          |

| APWR  | 38 | アナログ電源   | アナログ電源。1- $\mu$ F コンデンサを AGND との間に接続します。                                             |

| AVDD  | 40 | アナログ電源   | アナログ電源。1- $\mu$ F コンデンサを AGND に接続します。GPIO0A, GPIO1A, GPIO0B, GPIO1B のロジック レベルを設定します。 |

| CLK   | 32 | デジタル I/O | メイン クロック入力。 <sup>(4)</sup>                                                           |

| CNA だ | 6  | アナログ入力   | ADC1A 負アナログ入力。                                                                       |

| CNB   | 9  | アナログ入力   | ADC1B 負アナログ入力。                                                                       |

| CPA   | 5  | アナログ入力   | ADC1A 正アナログ入力。                                                                       |

**表 4-1. ピンの機能 (続き)**

| ピン          |    | タイプ                 | 説明 <sup>(1)</sup>                                                                                       |

|-------------|----|---------------------|---------------------------------------------------------------------------------------------------------|

| 名称          | 番号 |                     |                                                                                                         |

| CPB         | 10 | アナログ入力              | ADC1B 正アナログ入力。                                                                                          |

| CSn         | 31 | デジタル入力              | チップ セレクト入力 (アクティブ Low) I/OVDD の内部プルアップ抵抗。 <sup>(4)</sup>                                                |

| DCAP です     | 36 | デジタル電源              | DVDD LDO 出力。220nF のコンデンサを DGND に接続します。                                                                  |

| DGND        | 35 | デジタル電源              | デジタルグランド。                                                                                               |

| DPWR        | 37 | デジタル電源              | デジタル電源。1- $\mu$ F コンデンサを DGND との間に接続します。                                                                |

| DRDY        | 27 | デジタル出力              | データ準備完了出力、アクティブ Low。 <sup>(2) (4)</sup>                                                                 |

| GPIO0/MHD   | 33 | デジタル I/O            | 汎用デジタル入出力 0。 <sup>(2) (4)</sup><br>ホスト検出出力がありません。 <sup>(2) (4)</sup>                                    |

| GPIO1       | 26 | デジタル I/O            | 汎用デジタル入出力 1。 <sup>(2) (4)</sup>                                                                         |

| GPIO2/FAULT | 25 | デジタル I/O            | 汎用デジタル入出力 2。 <sup>(2) (4)</sup><br>フォルト出力。 <sup>(2) (4)</sup>                                           |

| GPIO3/OCCA  | 24 | デジタル I/O            | 汎用デジタル入出力 3。 <sup>(2) (4)</sup><br>過電流コンバレータ A の出力。 <sup>(2) (4)</sup>                                  |

| GPIO4/OCCB  | 22 | デジタル I/O            | 汎用デジタル入出力 4。 <sup>(2) (4)</sup><br>過電流コンバレータ B の出力。 <sup>(2) (4)</sup>                                  |

| IOVDD       | 34 | デジタル電源              | デジタル I/O 電源。1- $\mu$ F コンデンサを DGND に接続します。<br>GPIO0A、GPIO1A、GPIO0B、GPIO1B を除く、デジタル I/O のロジック・レベルを設定します。 |

| RCAPA       | 41 | アナログ出力              | REFA 基準電圧出力。1- $\mu$ F コンデンサを AGNDA との間に接続します。                                                          |

| RCAPB       | 20 | アナログ出力              | REFB 基準電圧出力。1- $\mu$ F コンデンサを AGNDB との間に接続します。                                                          |

| RESETn      | 23 | デジタル入力              | リセット入力 (アクティブ Low) DGND への内部プルダウン抵抗。                                                                    |

| SCLK        | 28 | デジタル入力              | シリアル データクロック入力。 <sup>(4)</sup>                                                                          |

| SDI         | 30 | デジタル入力              | シリアル データ入力。 <sup>(4)</sup>                                                                              |

| SDO         | 29 | デジタル出力              | シリアル データ出力。 <sup>(2) (4)</sup>                                                                          |

| V0A         | 2  | アナログ入力              | ADC2A アナログ入力 0A。                                                                                        |

| V0B         | 11 | アナログ入力              | ADC2B アナログ入力 0B。                                                                                        |

| V1A         | 1  | アナログ入力              | ADC2A アナログ入力 1A。                                                                                        |

| V1B         | 12 | アナログ入力              | ADC2B アナログ入力 1B。                                                                                        |

| V2A         | 48 | アナログ入力              | ADC2A アナログ入力 2A。                                                                                        |

| V2B         | 13 | アナログ入力              | ADC2B アナログ入力 2B。                                                                                        |

| V3A         | 47 | アナログ入力              | ADC2A アナログ入力 3A。                                                                                        |

| V3B         | 14 | アナログ入力              | ADC2B アナログ入力 3B。                                                                                        |

| V4A         | 46 | アナログ入力              | ADC2A アナログ入力 4A。                                                                                        |

| V4B         | 15 | アナログ入力              | ADC2B アナログ入力 4B。                                                                                        |

| V5A         | 45 | アナログ入力              | ADC2A アナログ入力 5A。                                                                                        |

| V5B         | 16 | アナログ入力              | ADC2B アナログ入力 5B。                                                                                        |

| V6A         | 44 | アナログ入力              | ADC2A アナログ入力 6A。                                                                                        |

| V6B         | 17 | アナログ入力              | ADC2B アナログ入力 6B。                                                                                        |

| V7A         | 43 | アナログ入力              | ADC2A アナログ入力 7A。                                                                                        |

| V7B         | 18 | アナログ入力              | ADC2B アナログ入力 7B。                                                                                        |

| VNA/GPIO1A  | 4  | アナログ入力/<br>デジタル I/O | ADC3A 負アナログ入力。<br>汎用デジタル入出力 1A。 <sup>(2) (3)</sup>                                                      |

| VNB/GPIO1B  | 7  | アナログ入力/<br>デジタル I/O | ADC3B 負アナログ入力。<br>汎用デジタル入出力 1B。 <sup>(2) (3)</sup>                                                      |

| VPA/GPIO0A  | 3  | アナログ入力/<br>デジタル I/O | ADC3A 正アナログ入力。<br>汎用デジタル入出力 0A。 <sup>(2) (3)</sup>                                                      |

| VPB/GPIO0B  | 8  | アナログ入力/<br>デジタル I/O | ADC3B 負アナログ入力。<br>汎用デジタル入出力 0B。 <sup>(2) (3)</sup>                                                      |

表 4-1. ピンの機能 (続き)

| ピン       |     | タイプ | 説明 <sup>(1)</sup>      |

|----------|-----|-----|------------------------|

| 名称       | 番号  |     |                        |

| サーマル パッド | パッド | —   | サーマル パワー パッド。AGND に接続。 |

(1) 未使用ピンの接続方法の詳細については、[未使用入出力](#) セクションを参照してください。

(2) ブッシュプル出力。

(3) AVDD を基準とするロジック レベル。

(4) IOVDD を基準とするロジック レベル。

## 5 仕様

### 5.1 絶対最大定格

(1) 参照

|          |                                                                                             | 最小値         | 最大値         | 単位 |

|----------|---------------------------------------------------------------------------------------------|-------------|-------------|----|

| 電源電圧     | APWR から AGND へ                                                                              | -0.3        | 20          | V  |

|          | DPWR から DGND へ                                                                              | -0.3        | 20          |    |

|          | AGND、AGNDy から DGND へ                                                                        | -0.3        | 0.3         |    |

|          | AVDD から AGND へ                                                                              | -0.3        | 4           |    |

|          | IOVDD から DGND へ                                                                             | -0.3        | 7           |    |

|          | DCAP から DGND へ                                                                              | -0.3        | 2.2         |    |

|          | RCAPy から AGND へ                                                                             | -0.3        | 2.2         |    |

| アナログ入力電圧 | CPy、CNy、VPy、VNy、Vxy                                                                         | AGND - 1.6  | AVDD + 0.3  | V  |

| デジタル入力電圧 | CSn、SCLK、SDI、SDO、RESETn、DRDYn、CLK、<br>GPIO0/MHD、GPIO1、GPIO2/FAULT、GPIO3/OCCA、GPIO4/<br>OCCB | DGND - 0.3  | IOVDD + 0.3 | V  |

|          | GPIO0A、GPIO1A                                                                               | AGNDA - 0.3 | AVDD + 0.3  |    |

|          | GPIO0B、GPIO1B                                                                               | AGNDB - 0.3 | AVDD + 0.3  |    |

| 入力電流     | 連続、電源ピンを除くすべてのピン                                                                            | -10         | 10          | mA |

| 温度       | 接合部、 $T_J$                                                                                  |             | 150         | °C |

|          | 保存、 $T_{stg}$                                                                               | -60         | 150         |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の範囲内であっても 推奨動作条件の範囲外で短時間動作させると、デバイスは損傷を受けないかもしれません、完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                                    | 値                                                       | 単位 |

|-------------|------|--------------------------------------------------------------------|---------------------------------------------------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、<br>AEC Q100-002 <sup>(1)</sup><br>HBM ESD 分類レベル 2 に準拠 | $\pm 2000$                                              | V  |

|             |      | 荷電デバイス モデル (CDM)、<br>AEC Q100-011<br>CDM ESD 分類レベル C4B に準拠         | 角のピン<br>$\pm 750$<br>その他のすべてのコーナーなしの<br>ピン<br>$\pm 500$ |    |

|             |      |                                                                    |                                                         |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

動作時周辺温度範囲内 (特に記述のない限り)

|                                         |             |                                                                                                                         | 最小値                     | 公称値                    | 最大値 | 単位  |

|-----------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|-----|-----|

| <b>電源</b>                               |             |                                                                                                                         |                         |                        |     |     |

| 電源                                      |             | APWR から AGND へ                                                                                                          | 4                       | 16                     |     | V   |

|                                         |             | APWR = AVDD から AGND へ<br>(APWR は AVDD に短絡され、AVDD LDO は<br>バイパスされます)                                                     | 2.9                     | 3.3                    | 3.6 |     |

|                                         |             | DPWR から DGND へ                                                                                                          | 4                       | 16                     |     |     |

|                                         |             | DPWR = IOVDD から DGND へ<br>(DPWR は IOVDD に短絡され、IOVDD LDO<br>はバイパスされます)                                                   | 2.9                     | 3.3                    | 5.5 |     |

|                                         |             | AGND、AGNDy から DGND へ                                                                                                    | -0.2                    | 0                      | 0.2 |     |

| <b>アナログ入力 ADC1A、ADC1B<sup>(1)</sup></b> |             |                                                                                                                         |                         |                        |     |     |

| V <sub>Cpy</sub> 、V <sub>CNY</sub>      | 絶対入力電圧      | ゲイン: 4, 8, 16, 32                                                                                                       | AGND - 0.3125           | AVDD - 2.4             | V   |     |

| V <sub>IN1y</sub>                       | 差動入力電圧      | V <sub>IN1y</sub> = V <sub>Cpy</sub> - V <sub>CNY</sub>                                                                 | -V <sub>REFy</sub> /ゲイン | V <sub>REFy</sub> /ゲイン | V   |     |

| <b>アナログ入力 ADC2A、ADC2B<sup>(1)</sup></b> |             |                                                                                                                         |                         |                        |     |     |

| V <sub>Vxy</sub>                        | 絶対入力電圧      | ゲイン = 1, 2                                                                                                              | AGND - 0.1              | AVDD - 1.2             | V   |     |

|                                         |             | ゲイン = 4                                                                                                                 | AGND - 0.3125           | AVDD - 2.4             |     |     |

| V <sub>IN2y</sub>                       | 差動入力電圧      | V <sub>IN2y</sub> = V <sub>Vxy</sub> - V <sub>AGNDy</sub> または<br>V <sub>IN2y</sub> = V <sub>Vxy</sub> - V <sub>7y</sub> | -V <sub>REFy</sub> /ゲイン | V <sub>REFy</sub> /ゲイン | V   |     |

| <b>アナログ入力 ADC3A、ADC3B<sup>(1)</sup></b> |             |                                                                                                                         |                         |                        |     |     |

| V <sub>VPy</sub> 、V <sub>VNy</sub>      | 絶対入力電圧      | ゲイン = 1, 2                                                                                                              | AGND - 0.1              | AVDD - 1.2             | V   |     |

|                                         |             | ゲイン = 4                                                                                                                 | AGND - 0.3125           | AVDD - 2.4             | V   |     |

| V <sub>IN3y</sub>                       | 差動入力電圧      | V <sub>IN3y</sub> = V <sub>VPy</sub> - V <sub>VNy</sub>                                                                 | -V <sub>REFy</sub> /ゲイン | V <sub>REFy</sub> /ゲイン | V   |     |

| <b>外部クロック ソース<sup>(2)</sup></b>         |             |                                                                                                                         |                         |                        |     |     |

| f <sub>CLK</sub>                        | 外部クロック周波数設定 |                                                                                                                         | 7.8                     | 8.192                  | 8.4 | MHz |

|                                         | デューティ サイクル  |                                                                                                                         | 40%                     | 50%                    | 60% |     |

| <b>デジタル入力</b>                           |             |                                                                                                                         |                         |                        |     |     |

| 入力電圧                                    |             | CSN, SCLK, SDI, SDO, RESETn, DRDYn, CLK, GPIO0/MHD, GPIO1, GPIO2/FAULT, GPIO3/OCCA, GPIO4/OCCB                          | DGND                    | IOVDD                  | V   |     |

|                                         |             | GPIO0A, GPIO1A                                                                                                          | AGNDA                   | AVDD                   |     |     |

|                                         |             | GPIO0B, GPIO1B                                                                                                          | AGNDB                   | AVDD                   |     |     |

| <b>外付けコンデンサ</b>                         |             |                                                                                                                         |                         |                        |     |     |

| コンデンサ値 <sup>(3)</sup>                   |             | APWR, DPWR                                                                                                              | 1                       |                        |     | μF  |

|                                         |             | AVDD, IOVDD                                                                                                             | 0.5                     | 1                      | 2   |     |

|                                         |             | RCAPA, RCAPB                                                                                                            | 0.5                     | 1                      | 1.4 |     |

|                                         |             | DCAP です                                                                                                                 |                         | 220                    |     | nF  |

| <b>温度範囲</b>                             |             |                                                                                                                         |                         |                        |     |     |

| T <sub>A</sub>                          | 規定周囲温度      |                                                                                                                         | -40                     | 105                    | °C  |     |

|                                         | 動作時の周囲温度    |                                                                                                                         | -45                     | 125                    |     |     |

- (1) 下付き添字 *y* は、セクション *A* またはセクション *B* を参照します。

下付き添字 *x* は、ADC2y のアナログ入力の チャネル *x* を指します。

- (2) 内部発振器を使用する場合、外部クロックは不要です。

- (3) 温度範囲全体と寿命全体にわたって、満たす必要のあるコンデンサの値。

詳細については、[電源のデカッピング](#)セクションを参照してください。

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                     | TQFP (PHP) | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | 48 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗        | 23.7       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への热抵抗 | 15.3       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗        | 7.8        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.2        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 7.7        | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への热抵抗 | 1.3        | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体および IC パッケージの热評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

最小値および最大値の仕様は、 $T_A = -40^{\circ}\text{C}$  から  $+105^{\circ}\text{C}$  に適用され、標準仕様は  $T_A = 25^{\circ}\text{C}$  でのもの。すべての仕様は、APWR = 5V、DPWR = 5V、IOVDD = 3.3V、外部クロック、 $f_{\text{CLK}} = 8.192 \text{ MHz}$ 、グローバル チョップ モード無効、ADC1y および ADC3y データレート = 1kSPS でのものです (特に記述のない限り)

| パラメータ                          | テスト条件                      | 最小値                                                                                           | 標準値          | 最大値    | 単位                |    |

|--------------------------------|----------------------------|-----------------------------------------------------------------------------------------------|--------------|--------|-------------------|----|

| <b>電流測定 ADC (ADC1A, ADC1B)</b> |                            |                                                                                               |              |        |                   |    |

|                                | 分解能                        | 24                                                                                            |              |        | ビット               |    |

|                                | ゲイン設定                      |                                                                                               | 4, 8, 16, 32 |        | V/V               |    |

| $f_{\text{DATA}}$              | 出力データ レート                  | $f_{\text{CLK}} = 8.192 \text{ MHz}$                                                          | 500          | 64k    | SPS               |    |

|                                | 絶対入力電流                     | すべてのデータ レート、すべてのゲイン、グローバル チョップを有効にし、または無効にしました。 $V_{\text{CPY}} = V_{\text{CNY}} = 0\text{V}$ |              | ±0.5   | nA                |    |

|                                | 差動入力電流                     | すべてのデータ レート、すべてのゲイン、グローバル チョップを有効にし、または無効にしました。 $V_{\text{CPY}} = V_{\text{CNY}} = 0\text{V}$ | -5           | ±1     | 5                 | nA |

|                                | 差動入力インピーダンス                | すべてのデータ レート、すべてのゲイン、グローバル チョップを有効にし、または無効にしました                                                |              | 1.8    | MΩ                |    |

| オフセット誤差 (入力換算)                 | ゲイン = 4、グローバル チョップは無効      |                                                                                               | ±1           |        | µV                |    |

|                                | ゲイン = 8 ~ 32、グローバル チョップは無効 |                                                                                               | ±15          |        |                   |    |

|                                | すべてのゲイン、グローバル チョップは有効      | -1.5                                                                                          | ±0.5         | 1.5    |                   |    |

| オフセットのドリフト                     | すべてのゲイン、グローバル チョップは無効      | 20                                                                                            | 100          |        | nV/°C             |    |

|                                | すべてのゲイン、グローバル チョップは有効      | 1                                                                                             | 7            |        |                   |    |

|                                | ゲイン誤差                      | $T_A = 25^{\circ}\text{C}$ 、すべてのゲイン、REFy の初期精度を含む CNY を AGNDy に保持した状態でのシングル エンド動作             | -0.15%       | ±0.05% | 0.15%             |    |

|                                | ゲインドリフト                    | すべてのゲイン、REFy のドリフトを含む CNY を AGNDy に保持した状態でのシングル エンド動作                                         | 5            | 20     | ppm/°C            |    |

|                                | ゲイン長期ドリフト                  | 85°C で 1000 時間、REFy の長期ドリフトを含むすべてのゲイン                                                         |              | ±100   | ppm               |    |

|                                | ゲインマッピング                   | ゲイン設定の間                                                                                       | -0.12%       | ±0.03% | 0.12%             |    |

|                                | ノイズ (入力換算)                 | ゲイン = 8, $f_{\text{DATA}} = 1\text{kSPS}$                                                     | 0.65         |        | µV <sub>RMS</sub> |    |

| CMRR                           | 同相除去比                      | DC では、グローバル チョップは無効です                                                                         | 110          |        | dB                |    |

|                                |                            | DC では、グローバル チョップは有効です                                                                         | 113          |        |                   |    |

| PSRR                           | 電源除去比                      | DC での APWR、グローバル チョップは有効または無効                                                                 | 133          |        | dB                |    |

|                                |                            | DC での DPWR、グローバル チョップは有効または無効                                                                 | 133          |        |                   |    |

|                                |                            | DC での AVDD、グローバル チョップは有効または無効                                                                 | 115          |        |                   |    |

|                                |                            | DC での IOVDD、グローバル チョップは有効または無効                                                                | 131          |        |                   |    |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C}$  から  $+105^\circ\text{C}$  に適用され、標準仕様は  $T_A = 25^\circ\text{C}$  でのもの。すべての仕様は、APWR = 5V、DPWR = 5V、IOVDD = 3.3V、外部クロック、 $f_{\text{CLK}} = 8.192\text{ MHz}$ 、グローバル チョップ モード無効、ADC1y および ADC3y データ レート = 1kSPS でのものです (特に記述のない限り)

| パラメータ                                | テスト条件                                                                                   | 最小値                                                                                           | 標準値     | 最大値   | 単位                          |    |

|--------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------|-------|-----------------------------|----|

| <b>電圧および温度測定 ADCS (ADC2A, ADC2B)</b> |                                                                                         |                                                                                               |         |       |                             |    |

| 分解能                                  |                                                                                         | 16                                                                                            |         |       | ビット                         |    |

| ゲイン設定                                |                                                                                         |                                                                                               | 1, 2, 4 |       | V/V                         |    |

| 絶対入力電流                               | OSR2y = 64、すべてのゲイン、 $V_{Vxy} = 0\text{V}$                                               |                                                                                               | ±0.2    |       | nA                          |    |

| 差動入力電流                               | OSR2y = 64、すべてのゲイン、 $V_{Vxy} = 0\text{V}$                                               |                                                                                               | ±0.4    |       | nA                          |    |

| 差動入力インピーダンス                          | OSR2y = 64、すべてのゲイン                                                                      |                                                                                               | 15      |       | $\text{M}\Omega$            |    |

|                                      | OSR2y = 128、すべてのゲイン                                                                     |                                                                                               | 30      |       |                             |    |

|                                      | OSR2y = 256、すべてのゲイン                                                                     |                                                                                               | 60      |       |                             |    |

|                                      | OSR2y = 512、すべてのゲイン                                                                     |                                                                                               | 120     |       |                             |    |

| オフセット誤差 (入力換算)                       | ゲイン = 1                                                                                 | -350                                                                                          | ±85     | 350   | $\mu\text{V}$               |    |

|                                      | ゲイン = 2 と 4                                                                             | -25                                                                                           | ±5      | 25    |                             |    |

| オフセットのドリフト                           | ゲイン = 1                                                                                 |                                                                                               | 60      | 300   | $\text{nV}/^\circ\text{C}$  |    |

|                                      | ゲイン = 2 と 4                                                                             |                                                                                               | 30      | 150   |                             |    |

| ゲイン誤差                                | $T_A = 25^\circ\text{C}$ 、REFy の初期精度を含む<br>すべてのゲイン                                      | -0.3%                                                                                         | ±0.1%   | 0.3%  |                             |    |

| ゲインドリフト                              | すべてのゲイン (REFy のドリフトを含む)                                                                 |                                                                                               | 5       | 20    | $\text{ppm}/^\circ\text{C}$ |    |

| ゲイン長期ドリフト                            | 85°C で 1000 時間、<br>REFy の長期ドリフトを含むすべてのゲイン                                               |                                                                                               | ±100    |       | ppm                         |    |

| ゲインマッチング                             | ゲイン設定の間                                                                                 | -0.15%                                                                                        | ±0.06%  | 0.15% |                             |    |

| CMRR                                 | 同相除去比                                                                                   | DC で                                                                                          |         | 95    | dB                          |    |

| PSRR                                 | 電源除去比                                                                                   | DC の APWR                                                                                     |         | 103   | dB                          |    |

|                                      |                                                                                         | DC での DPWR                                                                                    |         | 103   |                             |    |

|                                      |                                                                                         | DC での AVDD                                                                                    |         | 91    |                             |    |

|                                      |                                                                                         | DC での IOVDD                                                                                   |         | 96    |                             |    |

| <b>パッテリ電圧測定 ADC (ADC3A, ADC3B)</b>   |                                                                                         |                                                                                               |         |       |                             |    |

| 分解能                                  |                                                                                         | 24                                                                                            |         |       | ビット                         |    |

| ゲイン設定                                |                                                                                         |                                                                                               | 1, 2, 4 |       | V/V                         |    |

| $f_{\text{DATA}}$                    | 出力データ レート                                                                               | $f_{\text{CLK}} = 8.192\text{ MHz}$                                                           | 500     | 64k   | SPS                         |    |

|                                      | 絶対入力電流                                                                                  | $f_{\text{DATA}} = 1\text{kSPS}$ 、すべてのゲイン、グローバル チョップが有効または無効、 $V_{VPy} = V_{VNy} = 0\text{V}$ |         | ±0.1  | nA                          |    |

|                                      | 差動入力電流                                                                                  | $f_{\text{DATA}} = 1\text{kSPS}$ 、すべてのゲイン、グローバル チョップが有効または無効、 $V_{VPy} = V_{VNy} = 0\text{V}$ | -2      | ±0.1  | 2                           | nA |

| 差動入力インピーダンス                          |                                                                                         | $f_{\text{DATA}} = 64\text{kSPS}$ 、すべてのゲイン、グローバル チョップは有効または無効                                 |         | 15    | $\text{M}\Omega$            |    |

|                                      |                                                                                         | $f_{\text{DATA}} = 16\text{kSPS}$ 、すべてのゲイン、グローバル チョップは有効または無効                                 |         | 60    |                             |    |

|                                      |                                                                                         | $f_{\text{DATA}} = 4\text{kSPS}$ 、すべてのゲイン、グローバル チョップは有効または無効                                  |         | 250   |                             |    |

|                                      |                                                                                         | $f_{\text{DATA}} = 1\text{kSPS}$ 、すべてのゲイン、グローバル チョップは有効または無効                                  |         | 1000  |                             |    |

| オフセット誤差 (入力換算)                       | すべてのゲイン、グローバル チョップは無効                                                                   | -400                                                                                          | ±80     | 400   | $\mu\text{V}$               |    |

|                                      | すべてのゲイン、グローバル チョップは有効                                                                   | -10                                                                                           | ±3      | 10    |                             |    |

| オフセットのドリフト                           | すべてのゲイン、グローバル チョップは無効                                                                   |                                                                                               | 50      | 300   | $\text{nV}/^\circ\text{C}$  |    |

|                                      | すべてのゲイン、グローバル チョップは有効                                                                   |                                                                                               | 4       | 15    |                             |    |

| ゲイン誤差                                | $T_A = 25^\circ\text{C}$ 、すべてのゲイン、 $V_{Ny}$ を AGNDy に保持した状態でのシングルエンド動作、REFy の初期精度も含まれます | -0.3%                                                                                         | ±0.1%   | 0.3%  |                             |    |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C}$  から  $+105^\circ\text{C}$  に適用され、標準仕様は  $T_A = 25^\circ\text{C}$  でのもの。すべての仕様は、 $\text{APWR} = 5\text{V}$ 、 $\text{DPWR} = 5\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、外部クロック、 $f_{\text{CLK}} = 8.192\text{ MHz}$ 、グローバル チョップ モード無効、 $\text{ADC1y}$  および  $\text{ADC3y}$  データ レート = 1kSPS でのものです (特に記述のない限り)

| パラメータ                               |                | テスト条件                                                                             | 最小値    | 標準値          | 最大値   | 単位                           |

|-------------------------------------|----------------|-----------------------------------------------------------------------------------|--------|--------------|-------|------------------------------|

|                                     | ゲインドリフト        | すべてのゲイン、 $\text{REFy}$ のドリフトを含む、 $\text{VNy}$ を $\text{AGNDy}$ に保持した状態でのシングルエンド動作 |        | 5            | 20    | $\text{ppm}/^\circ\text{C}$  |

|                                     | ゲイン長期ドリフト      | $85^\circ\text{C}$ で 1000 時間、 $\text{REFy}$ の長期ドリフトを含むすべてのゲイン                     |        | $\pm 100$    |       | ppm                          |

|                                     | ゲイン マッチング      | ゲイン設定の間                                                                           | -0.18% | $\pm 0.06\%$ | 0.18% |                              |

|                                     | ノイズ (入力換算)     | ゲイン = 4、 $f_{\text{DATA}} = 1\text{kSPS}$                                         |        | 3            |       | $\mu\text{V}_{\text{RMS}}$   |

| CMRR                                | 同相除去比          | DC では、グローバル チョップは無効です                                                             |        | 114          |       | dB                           |

|                                     |                | DC では、グローバル チョップは有効です                                                             |        | 120          |       |                              |

| PSRR                                | 電源除去比          | DC での APWR、グローバル チョップは有効または無効                                                     |        | 123          |       | dB                           |

|                                     |                | DC での DPWR、グローバル チョップは有効または無効                                                     |        | 123          |       |                              |

|                                     |                | DC での AVDD、グローバル チョップは有効または無効                                                     |        | 93           |       |                              |

|                                     |                | DC での IOVDD、グローバル チョップは有効または無効                                                    |        | 113          |       |                              |

| <b>高精度電圧リファレンス (REFA、REFB)</b>      |                |                                                                                   |        |              |       |                              |

| $V_{\text{REFA}} - V_{\text{REFB}}$ | リファレンス電圧       |                                                                                   |        | 1.25         |       | V                            |

|                                     | 精度             | $T_A = 25^\circ\text{C}$                                                          | -0.15% | $\pm 0.05\%$ | 0.15% |                              |

|                                     | 温度ドリフト         |                                                                                   |        | 3            | 15    | $\text{ppm}/^\circ\text{C}$  |

|                                     | 出力電流           | ソースのみ、 $\text{RCAPy}$ ピンで外部負荷に供給可能                                                |        | 250          |       | $\mu\text{A}$                |

|                                     | 回路短絡時の電流制限     | シンクまたはソース                                                                         | -10    |              | 10    | $\text{mA}$                  |

|                                     | スタートアップ時間      | $\text{RCAPy}$ に $1\mu\text{F}$ コンデンサを接続、0.01% セッティング                             |        | 8            |       | ms                           |

| <b>メイン発振回路 (OSCM)</b>               |                |                                                                                   |        |              |       |                              |

| $f_{\text{OSCM}}$                   | 周波数            |                                                                                   |        | 8.192        |       | MHz                          |

|                                     | 精度             |                                                                                   | -2.5%  |              | 2.5%  |                              |

| <b>診断発振器 (OSCD)</b>                 |                |                                                                                   |        |              |       |                              |

| $f_{\text{OSCD}}$                   | 周波数            |                                                                                   |        | 8.192        |       | MHz                          |

|                                     | 精度             |                                                                                   | -2.5%  |              | 2.5%  |                              |

| <b>過電流コンパレータ (OCCA、OCCB)</b>        |                |                                                                                   |        |              |       |                              |

|                                     | オフセット誤差 (入力換算) | すべてのゲイン                                                                           | -500   | $\pm 20$     | 500   | $\mu\text{V}$                |

|                                     | ゲイン誤差          | $\text{REFy}$ の誤差を含むすべてのゲイン                                                       | -0.5%  | $\pm 0.2\%$  | 0.5%  |                              |

| <b>温度センサ (TSA、TSB)</b>              |                |                                                                                   |        |              |       |                              |

| $TS_{\text{Offset}}$                | 出力電圧           | $T_A = 25^\circ\text{C}$                                                          |        | 118.4        |       | mV                           |

| $TS_{\text{TC}}$                    | 温度係数           |                                                                                   |        | 410          |       | $\mu\text{V}/^\circ\text{C}$ |

| <b>同相出力バッファ (VCMA、VCMB)</b>         |                |                                                                                   |        |              |       |                              |

| $V_{\text{CMA}} - V_{\text{CMB}}$   | 同相出力電圧         |                                                                                   | 0.75   | 0.78         | 0.81  | V                            |

|                                     | 出力電流           | シンクまたはソース                                                                         | -1     |              | 1     | $\text{mA}$                  |

|                                     | 回路短絡時の電流制限     | シンクまたはソース                                                                         | -5     |              | 5     | $\text{mA}$                  |

|                                     | 容量性負荷          |                                                                                   |        | 100          |       | $\text{pF}$                  |

| <b>テスト DACS (TDACA、TDACB)</b>       |                |                                                                                   |        |              |       |                              |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C}$  から  $+105^\circ\text{C}$  に適用され、標準仕様は  $T_A = 25^\circ\text{C}$  でのもの。すべての仕様は、APWR = 5V、DPWR = 5V、IOVDD = 3.3V、外部クロック、 $f_{\text{CLK}} = 8.192\text{ MHz}$ 、グローバル チョップ モード無効、ADC1y および ADC3y データ レート = 1kSPS でのものです (特に記述のない限り)

| パラメータ  | テスト条件  | 最小値                                                                                                                                                                                                                                                                      | 標準値 | 最大値                   | 単位 |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|----|

| 出力電圧設定 |        | $1 \times V_{\text{REFY}}/40$<br>$2 \times V_{\text{REFY}}/40$<br>$4 \times V_{\text{REFY}}/40$<br>$9 \times V_{\text{REFY}}/40$<br>$18 \times V_{\text{REFY}}/40$<br>$36 \times V_{\text{REFY}}/40$<br>$-4 \times V_{\text{REFY}}/40$<br>$-9 \times V_{\text{REFY}}/40$ |     |                       | V  |

| 精度     |        | $\pm 0.3\%$                                                                                                                                                                                                                                                              |     |                       |    |

| ドリフト   | 正の出力電圧 | 6                                                                                                                                                                                                                                                                        | 35  | ppm/ $^\circ\text{C}$ |    |

|        | 負の出力電圧 | 12                                                                                                                                                                                                                                                                       | 80  |                       |    |

### オープン線式の検出用電流ソースおよびシンク(OWD1A、OWD1B、OWD2A、OWD2B、OWD3A、OWD3B)

|         |  |            |    |

|---------|--|------------|----|

| 電流ソース設定 |  | 4, 40, 240 | μA |

| 電流シンク設定 |  | 4, 40, 240 | μA |

| 電流源の精度  |  | $\pm 8\%$  |    |

| 電流シンク精度 |  | $\pm 8\%$  |    |

### デジタル入出力 (GPIO0A、GPIO1A、GPIO0B、GPIO1B)

|          |                |                                                         |          |          |    |

|----------|----------------|---------------------------------------------------------|----------|----------|----|

| $V_{IL}$ | ロジック入力レベル、Low  |                                                         | AGNDY    | 0.3 AVDD | V  |

| $V_{IH}$ | ロジック入力レベル、High |                                                         | 0.7 AVDD | AVDD     | V  |

| $V_{OL}$ | ロジック出力レベル、Low  | $I_{OL} = -100\mu\text{A}$                              |          | 0.2 AVDD | V  |

| $V_{OH}$ | ロジック出力レベル、High | $I_{OH} = 100\mu\text{A}$                               | 0.8 AVDD |          | V  |

| $I_{IN}$ | 入力電流           | $\text{AGNDY} < V_{\text{Digital Input}} < \text{AVDD}$ | -1       | 1        | μA |

|          | 回路短絡時の電流制限     | シンクまたはソース                                               | -8       | 8        | mA |

### デジタル入出力 (CSN、SCLK、SDI、SDO、RESETn、DRDYn、CLK、GPIO0/MHD、GPIO1、GPIO2/FAULT、GPIO3/OCCA、GPIO4/OCCB)

|          |                |                                                         |           |           |    |

|----------|----------------|---------------------------------------------------------|-----------|-----------|----|

| $V_{IL}$ | ロジック入力レベル、Low  |                                                         | DGND      | 0.3 IOVDD | V  |

| $V_{IH}$ | ロジック入力レベル、High |                                                         | 0.7 IOVDD | IOVDD     | V  |

| $V_{OL}$ | ロジック出力レベル、Low  | $I_{OL} = -1\text{mA}$                                  |           | 0.2 IOVDD | V  |

| $V_{OH}$ | ロジック出力レベル、High | $I_{OH} = 1\text{mA}$                                   | 0.8 IOVDD |           | V  |

| $I_{IN}$ | 入力電流           | $\text{DGND} < V_{\text{Digital Input}} < \text{IOVDD}$ | -1        | 1         | μA |

|          | 回路短絡時の電流制限     | シンクまたはソース                                               | -80       | 80        | mA |

### クロック モニタ

|                           |                                        |                                                  |     |     |     |

|---------------------------|----------------------------------------|--------------------------------------------------|-----|-----|-----|

| $f_{\text{MCLK\_WD\_TH}}$ | メイン クロック (MCLK) のウォッチ ドッピング周波数のスレッショルド | ウォッチ ドッピングは、MCLK の周波数が周波数スレッショルドを下回った場合に�ルトを示します |     | 300 | kHz |

| $f_{\text{OSCD\_WD\_TH}}$ | 診断発振器 (OSCD) のウォッチ ドッピング周波数のスレッショルド    | ウォッチ ドッピングは、OSCD の周波数が周波数スレッショルドを下回った場合に�ルトを示します |     | 300 | kHz |

| $MCLK\_FAULT\_TH$         | メインクロック障害検出周波数スレッショルド                  | 障害を生成するための、MCLK と OSCD の間のクロック周波数の差              | 10% |     |     |

### 電源モニタ

|              |                  |                                    |      |      |      |                         |

|--------------|------------------|------------------------------------|------|------|------|-------------------------|

| AVDD_UV_TH   | AVDD 低電圧スレッショルド  |                                    | 2.9  | 2.95 | 3.0  | V                       |

| AVDD_OV_TH   | AVDD 過電圧スレッショルド  |                                    | 3.8  | 3.9  | 4.0  | V                       |

| IOVDD_UV_TH  | IOVDD 低電圧スレッショルド | $\text{IOVDD\_UV\_TH} = 1\text{b}$ | 2.9  | 2.95 | 3.0  | V                       |

|              |                  | $\text{IOVDD\_UV\_TH} = 0\text{b}$ | 4.2  | 4.3  | 4.4  |                         |

| IOVDD_OV_TH  | IOVDD 過電圧スレッショルド | $\text{IOVDD\_OV\_TH} = 1\text{b}$ | 3.8  | 3.9  | 4.0  | V                       |

|              |                  | $\text{IOVDD\_OV\_TH} = 0\text{b}$ | 5.6  | 5.75 | 5.9  |                         |

| DVDD_UV_TH   | DVDD 低電圧スレッショルド  |                                    | 1.55 | 1.6  | 1.65 | V                       |

| DVDD_OV_TH   | DVDD 過電圧スレッショルド  |                                    | 1.90 | 1.95 | 2.0  | V                       |

| AVDD_OSC_MAG | AVDD 発振検出の振幅     | 故障を生成するために必要な振幅                    | 500  |      |      | $\text{mV}_{\text{pp}}$ |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C}$  から  $+105^\circ\text{C}$  に適用され、標準仕様は  $T_A = 25^\circ\text{C}$  でのもの。すべての仕様は、 $\text{APWR} = 5\text{V}$ 、 $\text{DPWR} = 5\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、外部クロック、 $f_{\text{CLK}} = 8.192\text{ MHz}$ 、グローバル チョップ モード無効、 $\text{ADC1y}$  および  $\text{ADC3y}$  データ レート = 1kSPS でのものです (特に記述のない限り)

| パラメータ                 |                      | テスト条件                                                                     | 最小値                      | 標準値 | 最大値  | 単位               |

|-----------------------|----------------------|---------------------------------------------------------------------------|--------------------------|-----|------|------------------|

| AVDD_OSC_EQ           | AVDD 発振検出入力周波数       | 故障を発生させるための発振周波数範囲                                                        | 2                        | 500 |      | kHz              |

| IOVDD_OSC_MAG         | IOVDD 発振検出の振幅        | 故障を生成するために必要な振幅                                                           | 500                      |     |      | mV <sub>pp</sub> |

| IOVDD_OSC_FREQ        | IOVDD 発振検出入力周波数      | 故障を発生させるための発振周波数範囲                                                        | 2                        | 500 |      | kHz              |

| DVDD_OSC_MAG          | DVDD 発振検出の振幅         | 故障を生成するために必要な振幅                                                           | 500                      |     |      | mV <sub>pp</sub> |

| DVDD_OSC_EQ           | DVDD 発振検出入力周波数       | 故障を発生させるための発振周波数範囲                                                        | 2                        | 500 |      | kHz              |

| AVDD_OTW_TH           | AVDD 過熱警告スレッショルド     |                                                                           | -60<br>100<br>120<br>140 |     |      | °C               |

|                       | AVDD 過熱警告スレッショルド精度   |                                                                           | ±2                       |     |      | °C               |

| IOVDD_OTW_TH          | IOVDD 過熱警告スレッショルド    |                                                                           | -60<br>100<br>120<br>140 |     |      | °C               |

|                       | IOVDD 過熱警告スレッショルド精度  |                                                                           | ±2                       |     |      | °C               |

| ADC2y 電源によるリードバック減衰係数 | APWR                 |                                                                           | 103                      |     |      |                  |

|                       | DPWR                 |                                                                           | 103                      |     |      |                  |

|                       | AVDD                 |                                                                           | 4                        |     |      |                  |

|                       | IOVDD                |                                                                           | 4                        |     |      |                  |

|                       | DVDD                 |                                                                           | 2                        |     |      |                  |

|                       | ADC2y 電源によるリードバックの精度 | $\text{OSR2y} = 128, \text{MUX2y\_DELAY} \geq 256 \times t_{\text{MCLK}}$ | ±1%                      |     |      |                  |

| AVDD_POR_TH           | AVDD POR 解放スレッショルド   |                                                                           | 2.6                      | 2.7 | 2.85 | V                |

| IOVDD_POR_TH          | IOVDD POR 解放スレッショルド  |                                                                           | 2.6                      | 2.7 | 2.85 | V                |

| DVDD_POR_TH           | DVDD POR 解放スレッショルド   |                                                                           | 1.4                      | 1.5 | 1.6  | V                |

### 故障フラグ応答時間

|                         |                 |                                                    |    |    |

|-------------------------|-----------------|----------------------------------------------------|----|----|

| $t_p(\text{AVDD_OV})$   | AVDD 過電圧検出応答時間  | AVDD が AVDD 過電圧スレッショルドを超えてから故障ピンがアクティブになるまでの遅延時間   | 4  | μs |

| $t_p(\text{IOVDD_OV})$  | IOVDD 過電圧検出応答時間 | IOVDD が IOVDD 過電圧スレッショルドを超えてから故障ピンがアクティブになるまでの遅延時間 | 4  | μs |

| $t_p(\text{DVDD_OV})$   | DVDD 過電圧検出応答時間  | DVDD が DVDD 過電圧スレッショルドを超えてから故障ピンがアクティブになるまでの遅延時間   | 4  | μs |

| $t_p(\text{AVDD_UV})$   | AVDD 低電圧検出応答時間  | AVDD が AVDD 低電圧スレッショルドを下回るから故障ピンがアクティブになるまでの遅延時間   | 4  | μs |

| $t_p(\text{IOVDD_UV})$  | IOVDD 低電圧検出応答時間 | IOVDD が IOVDD 低電圧スレッショルドを下回るから故障ピンがアクティブになるまでの遅延時間 | 4  | μs |

| $t_p(\text{DVDD_UV})$   | DVDD 低電圧検出応答時間  | DVDD が DVDD 低電圧スレッショルドを下回るから故障ピンがアクティブになるまでの遅延時間   | 4  | μs |

| $t_p(\text{AVDD_OSC})$  | AVDD 発振検出応答時間   | AVDD 発振スレッショルドを超えてから、故障ピンがアクティブになるまでの遅延時間          | 30 | μs |

| $t_p(\text{IOVDD_OSC})$ | IOVDD 発振検出応答時間  | IOVDD 発振スレッショルドを超えてから、故障ピンがアクティブになるまでの遅延時間         | 30 | μs |

| $t_p(\text{DVDD_OSC})$  | DVDD 発振検出応答時間   | DVDD 発振スレッショルドを超えてから、故障ピンがアクティブになるまでの遅延時間          | 30 | μs |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は、 $T_A = -40^\circ\text{C}$  から  $+105^\circ\text{C}$  に適用され、標準仕様は  $T_A = 25^\circ\text{C}$  でのもの。すべての仕様は、APWR = 5V、DPWR = 5V、IOVDD = 3.3V、外部クロック、 $f_{\text{CLK}} = 8.192\text{ MHz}$ 、グローバル チョップ モード無効、ADC1y および ADC3y データ レート = 1kSPS でのものです (特に記述のない限り)

| パラメータ                                |                         | テスト条件                                                | 最小値  | 標準値  | 最大値 | 単位                |

|--------------------------------------|-------------------------|------------------------------------------------------|------|------|-----|-------------------|

| $t_{\text{p}}(\text{AVDD\_CL})$      | AVDD 電流制限検出応答時間         | AVDD が AVDD 電流制限スレッショルドを超えてから、故障ピンがアクティブになるまでの遅延時間   |      | 40   |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{IOVDD\_CL})$     | IOVDD 電流制限検出応答時間        | IOVDD が IOVDD 電流制限スレッショルドを超えてから、故障ピンがアクティブになるまでの遅延時間 |      | 40   |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{AVDD\_OTW})$     | AVDD 過熱警告応答時間           | AVDD が AVDD 過熱警告スレッショルドを超えてから故障ピンがアクティブになるまでの遅延時間    |      | 300  |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{IOVDD\_OTW})$    | IOVDD 過熱警告応答時間          | IOVDD が IOVDD 過熱警告スレッショルドを超えてから故障ピンがアクティブになるまでの遅延時間  |      | 300  |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{AVDD\_POR})$     | AVDD POR 検出応答時間         | AVDD が AVDD POR スレッショルドを下回ってから故障ピンがアクティブになるまでの遅延時間   |      | 30   |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{IOVDD\_POR})$    | IOVDD POR 検出応答時間        | IOVDD が IOVDD POR スレッショルドを下回ってから故障ピンがアクティブになるまでの遅延時間 |      | 30   |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{DVDD\_POR})$     | DVDD POR 検出応答時間         | DVDD が DVDD POR スレッショルドを下回ってから故障ピンがアクティブになるまでの遅延時間   |      | 30   |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{DGND\_OPEN})$    | DGND 開放検出応答時間           | DGND ピン切断から故障ピンがアクティブになるまでの遅延時間                      |      | 4    |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{AGNDy\_OPEN})$   | AGNDy 開放検出応答時間          | AGNDy ピン切断から故障ピンがアクティブになるまでの遅延時間                     |      | 4    |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{MEM\_MAP\_CRC})$ | メモリマップの CRC フォルト検出応答時間  | メモリマップでビット反転が発生してから、故障ピンがアクティブになるまでの遅延時間             | 69   | 138  |     | $t_{\text{OSCD}}$ |

| $t_{\text{p}}(\text{REG\_MAP\_CRC})$ | レジスタマップの CRC フォルト検出応答時間 | レジスタマップでビット反転が発生してから、故障ピンがアクティブになるまでの遅延時間            | 1024 | 2048 |     | $t_{\text{OSCD}}$ |

| $t_{\text{p}}(\text{MCLK\_WD})$      | メインクロック ウオッチドッグの応答時間    | メインクロック ウオッチドッグ タイムアウトから故障ピンがアクティブになるまでの遅延時間         |      | 2    |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{OSCD\_WD})$      | 診断発振器のウォッチドッグ応答時間       | 診断発振器のウォッチドッグ タイムアウトから故障ピンがアクティブになるまでの遅延時間           |      | 2    |     | $\mu\text{s}$     |

| $t_{\text{p}}(\text{MCLK\_FAULT})$   | メインクロック 故障検出応答時間        | メインクロック フォルト検出から故障ピンのアクティブまでの遅延時間                    |      | 4096 |     | $t_{\text{MCLK}}$ |

### AVDD LDO

|      |            |                      |     |     |     |                       |

|------|------------|----------------------|-----|-----|-----|-----------------------|

| AVDD | 出力電圧       |                      | 3.1 | 3.3 | 3.5 | V                     |

|      | 負荷電流       | AVDD ピン上で外部回路が利用できます |     | 20  |     | $\text{mA}$           |

|      | 回路短絡時の電流制限 |                      |     | 60  |     | $\text{mA}$           |

|      | 負荷レギュレーション |                      |     | 1   |     | $\text{mV}/\text{mA}$ |

### IOVDD LDO

|       |            |                       |     |     |     |                       |

|-------|------------|-----------------------|-----|-----|-----|-----------------------|

| IOVDD | 出力電圧       |                       | 3.1 | 3.3 | 3.5 | V                     |

|       | 負荷電流       | IOVDD ピン上で外部回路が利用できます |     | 20  |     | $\text{mA}$           |

|       | 回路短絡時の電流制限 |                       |     | 60  |     | $\text{mA}$           |

|       | 負荷レギュレーション |                       |     | 1   |     | $\text{mV}/\text{mA}$ |

### 供給電流

|                   |                       |                                                        |      |     |    |

|-------------------|-----------------------|--------------------------------------------------------|------|-----|----|

| $I_{\text{APWR}}$ | APWR 電源電流             | (パワーダウンモード)                                            | 0.01 | 7.7 | mA |

|                   |                       | スタンバイ モード                                              | 0.46 |     |    |

|                   |                       | アクティブ モード、すべての ADC は無効                                 | 0.8  |     |    |

|                   |                       | アクティブ モード、すべての ADC が有効、変換 (すべての機能が有効、AVDD LDO の外部負荷なし) | 6.3  |     |    |

|                   | 個別の ADC ごとの APWR 電源電流 | ADC1y が有効と変換、すべてのゲイン、すべてのデータ レート                       | 1.75 |     |    |

|                   |                       | ADC2y が有効と変換、すべてのゲイン、すべてのデータ レート                       | 0.5  |     |    |

|                   |                       | ADC3y が有効と変換、すべてのゲイン、すべてのデータ レート                       | 0.5  |     |    |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は、 $T_A = -40^{\circ}\text{C}$  から  $+105^{\circ}\text{C}$  に適用され、標準仕様は  $T_A = 25^{\circ}\text{C}$  でのもの。すべての仕様は、 $\text{APWR} = 5\text{V}$ 、 $\text{DPWR} = 5\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、外部クロック、 $f_{\text{CLK}} = 8.192\text{ MHz}$ 、グローバル チョップ モード無効、 $\text{ADC1y}$  および  $\text{ADC3y}$  データ レート =  $1\text{kSPS}$  でのものです (特に記述のない限り)

| パラメータ              |                                      | テスト条件                                                                                                 | 最小値  | 標準値 | 最大値 | 単位 |

|--------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----|-----|----|

| $I_{\text{DPWR}}$  | DPWR 電源電流 <sup>(1)</sup>             | (パワーダウンモード)                                                                                           | 0.01 |     |     | mA |

|                    |                                      | スタンバイ モード                                                                                             | 0.4  |     |     |    |

|                    |                                      | アクティブ モード、すべての ADC は無効                                                                                | 0.8  |     |     |    |

|                    |                                      | アクティブ モード、すべての ADC が有効、変換 (すべての機能が有効、 $\text{IOVDD LDO}$ の外部負荷なし)                                     | 1.1  | 1.7 |     |    |

|                    | 個別の ADC ごとの DPWR 電源電流 <sup>(1)</sup> | $\text{ADC1y}$ が有効になり、すべてのデータ レートを変換します                                                               | 0.06 |     |     |    |

|                    |                                      | $\text{ADC2y}$ が有効になり、すべてのデータ レートを変換します                                                               | 0.06 |     |     |    |

|                    |                                      | $\text{ADC3y}$ が有効になり、すべてのデータ レートを変換します                                                               | 0.06 |     |     |    |

|                    |                                      | APWR が $\text{AVDD}$ に短縮された ( $\text{AVDD LDO}$ がバイパスされた)。<br>アクティブ モード、すべての ADC が有効、変換 (すべての機能が有効)   | 6.3  |     |     |    |

| $I_{\text{AVDD}}$  | AVDD 電源電流                            | DPWR が $\text{IOVDD}$ に短縮された ( $\text{IOVDD LDO}$ がバイパスされた)。<br>アクティブ モード、すべての ADC が有効、変換 (すべての機能が有効) | 1.1  |     |     | mA |

| $I_{\text{IOVDD}}$ | IOVDD 電源電流 <sup>(1)</sup>            | アクティブ モード、すべての ADC が有効、変換 (すべての機能が有効、 $\text{IOVDD LDO}$ の外部負荷なし)                                     | 37   |     |     | mA |

| $P_D$              | 消費電力                                 |                                                                                                       |      |     |     | mW |

(1) 電流は SPI アイドル時に測定されます。

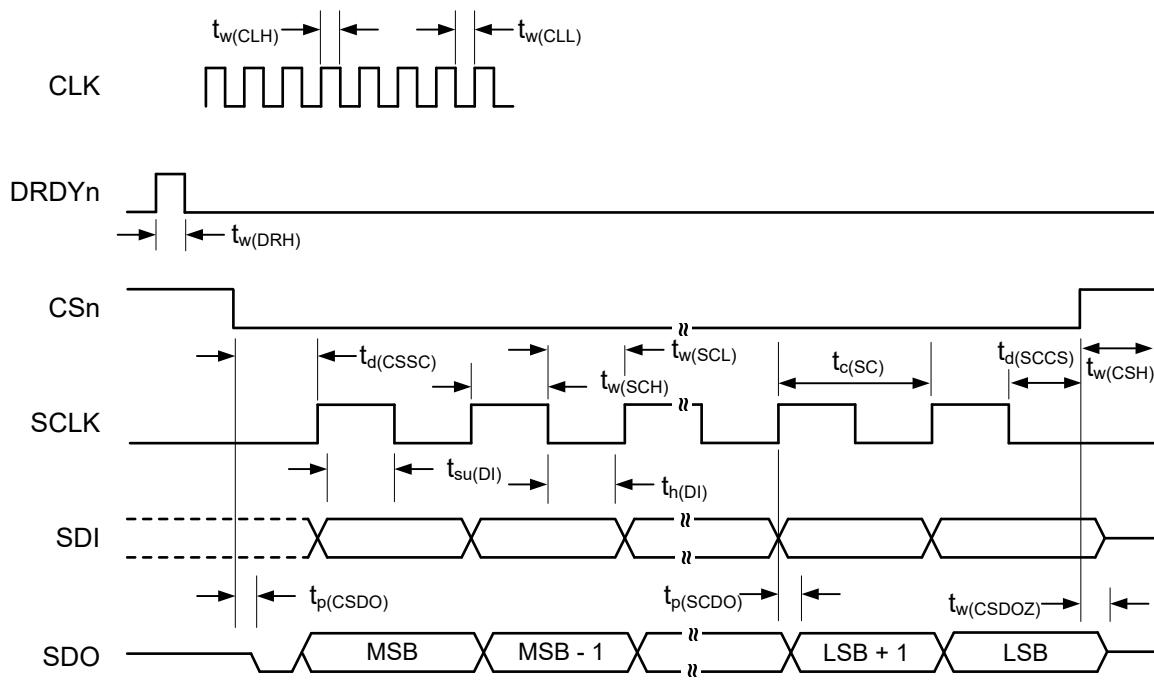

## 5.6 タイミング要件

全動作周囲温度範囲、SDO 負荷: 20pF || 100kΩ (特に注記のない限り)

|                            |                                         | 最小値 | 最大値 | 単位 |

|----------------------------|-----------------------------------------|-----|-----|----|

| <b>3.0V ≤ IOVDD ≤ 3.6V</b> |                                         |     |     |    |

| $t_w(CLH)$                 | パルス幅、CLK high                           | 49  |     | ns |

| $t_w(PLL)$                 | パルス幅、CLK low                            | 49  |     | ns |

| $t_c(SC)$                  | SCLK 周期                                 | 64  |     | ns |

| $t_w(SCL)$                 | パルス幅、SCLK low                           | 32  |     | ns |

| $t_w(SCH)$                 | パルス幅、SCLK high                          | 32  |     | ns |

| $t_d(CSSC)$                | 遅延時間、CSn 立ち下がりエッジから最初の SCLK 立ち上がりエッジまで  | 16  |     | ns |

| $t_d(SCCS)$                | 遅延時間、最後の SCLK 立ち下がりエッジから CSn 立ち上がりエッジまで | 10  |     | ns |

| $t_w(CSH)$                 | パルス幅、CSn high                           | 20  |     | ns |

| $t_{su(DI)}$               | セットアップ時間、SDI 有効から SCLK 立ち下がりエッジまで       | 5   |     | ns |

| $t_h(DI)$                  | ホールド時間、SCLK 立ち下がりエッジから SDI 有効まで         | 8   |     | ns |

| $t_w(RSL)$                 | パルス幅、RESETn low からデバイスリセット生成まで          | 500 |     | ns |

| <b>4.5V ≤ IOVDD ≤ 5.5V</b> |                                         |     |     |    |

| $t_w(PLL)$                 | パルス幅、CLK low                            | 49  |     | ns |

| $t_w(CLH)$                 | パルス幅、CLK high                           | 49  |     | ns |

| $t_c(SC)$                  | SCLK 周期                                 | 50  |     | ns |

| $t_w(SCL)$                 | パルス幅、SCLK low                           | 25  |     | ns |

| $t_w(SCH)$                 | パルス幅、SCLK high                          | 25  |     | ns |

| $t_d(CSSC)$                | 遅延時間、CSn 立ち下がりエッジから最初の SCLK 立ち上がりエッジまで  | 16  |     | ns |

| $t_d(SCCS)$                | 遅延時間、最後の SCLK 立ち下がりエッジから CSn 立ち上がりエッジまで | 10  |     | ns |

| $t_w(CSH)$                 | パルス幅、CSn high                           | 15  |     | ns |

| $t_{su(DI)}$               | セットアップ時間、SDI 有効から SCLK 立ち下がりエッジまで       | 5   |     | ns |

| $t_h(DI)$                  | ホールド時間、SCLK 立ち下がりエッジから SDI 有効まで         | 8   |     | ns |

| $t_w(RSL)$                 | パルス幅、RESETn low からデバイスリセット生成まで          | 500 |     | ns |

## 5.7 スイッチング特性

全動作周囲温度範囲、SDO 負荷: 20pF || 100kΩ (特に注記のない限り)

| パラメータ                      | テスト条件                                | 最小値                                      | 標準値 | 最大値 | 単位                |

|----------------------------|--------------------------------------|------------------------------------------|-----|-----|-------------------|

| <b>3.0V ≤ IOVDD ≤ 3.6V</b> |                                      |                                          |     |     |                   |

| $t_p(\text{CSDO})$         | 伝搬遅延時間、CSn 立ち下がりエッジから SDO 駆動まで       |                                          |     | 50  | ns                |

| $t_p(\text{CSDOZ})$        | 伝搬遅延時間、CSn 立ち上がりエッジから SDO 高インピーダンスまで |                                          |     | 75  | ns                |

| $t_p(\text{SCDO})$         | 伝搬遅延時間、SCLK 立ち上がりエッジから有効な新しい SDO まで  |                                          |     | 32  | ns                |

| $t_w(\text{DRH})$          | パルス幅、DRDYn High                      |                                          | 4   |     | $t_{\text{MCLK}}$ |

| $t_{\text{TIMEOUT}}$       | SPI タイムアウト                           | 16385                                    |     |     | $t_{\text{OSCD}}$ |

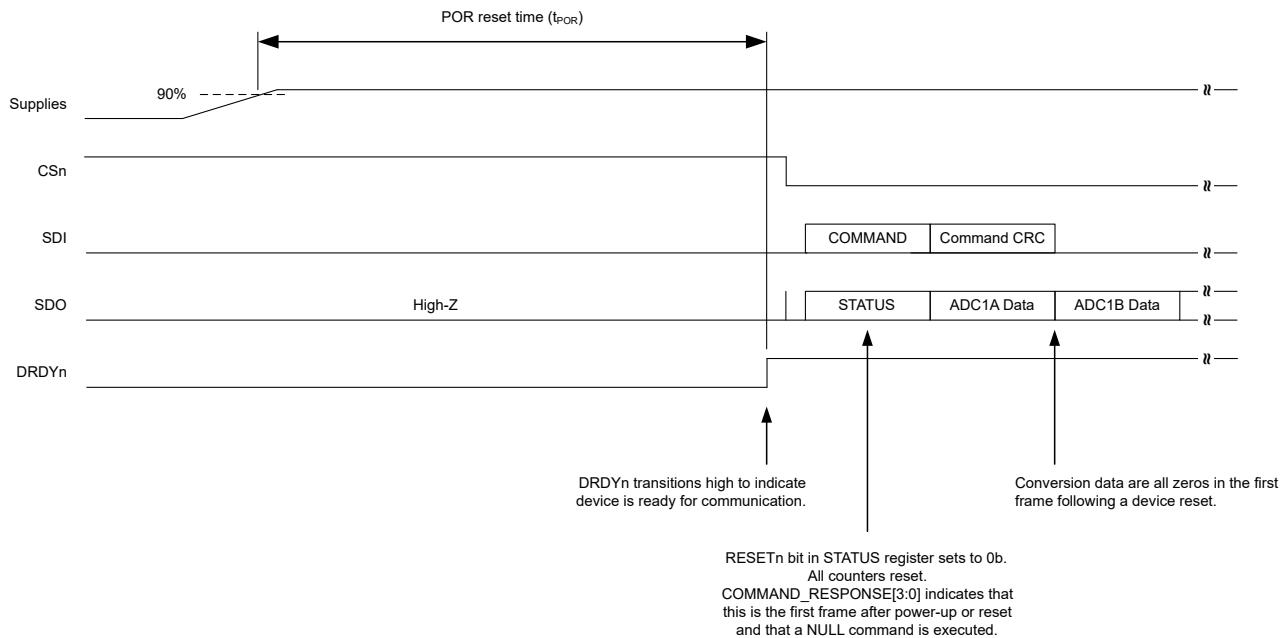

| $t_{\text{POR}}$           | パワーオンリセット電圧                          | POR スレッショルドを超える電源から DRDYn 立ち上がりエッジまで測定   | 250 |     | μs                |

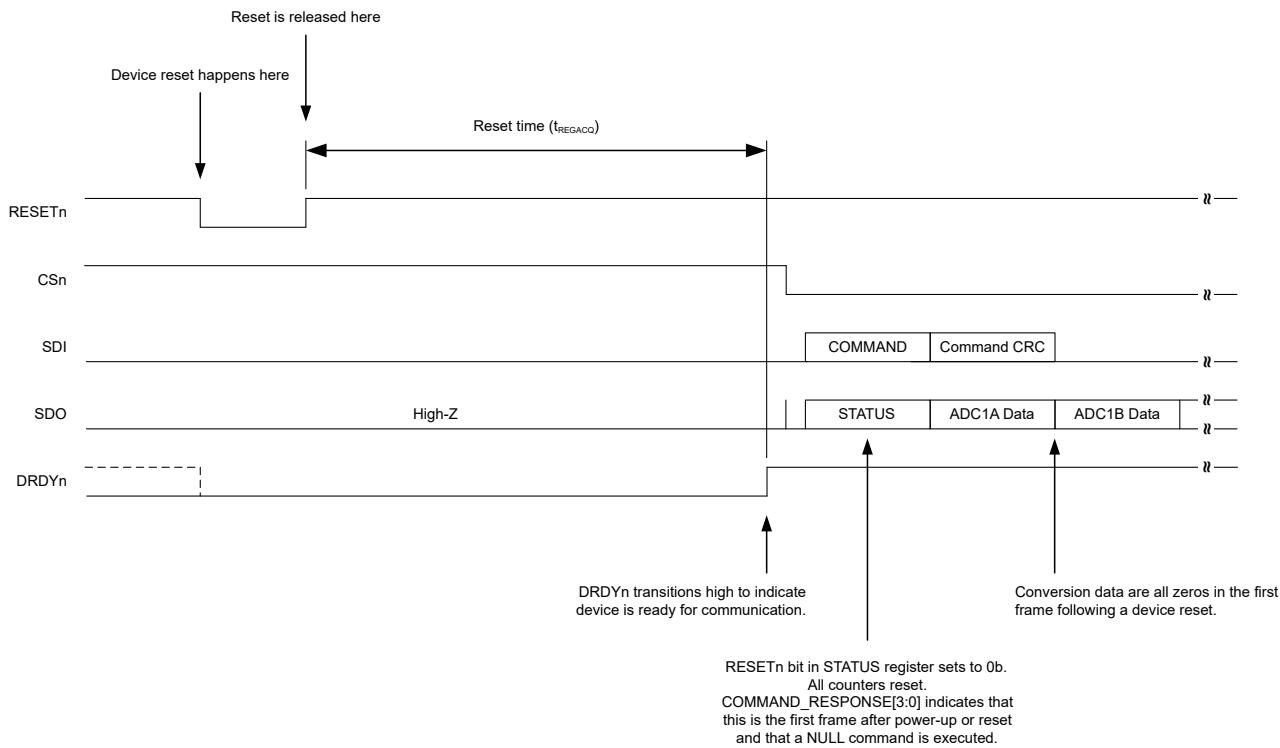

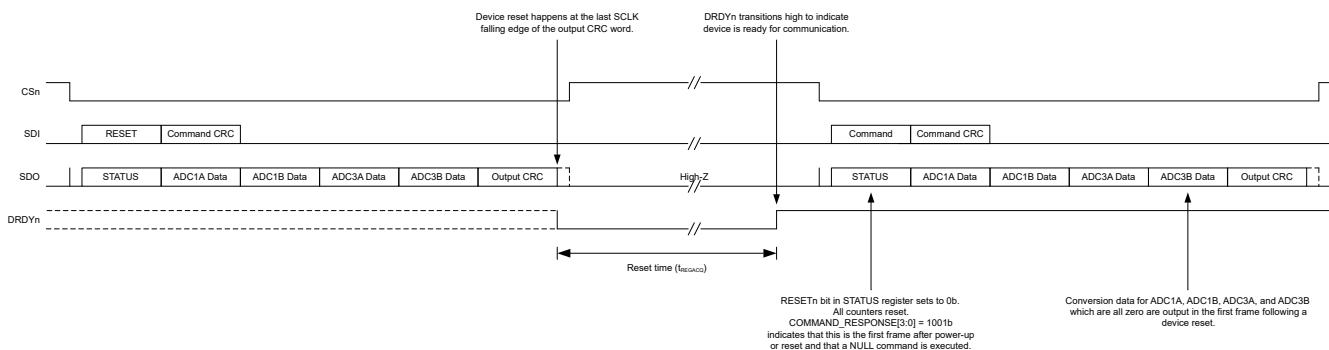

| $t_{\text{REGACQ}}$        | レジスタのデフォルト値のアクイジョン時間                 | RESETn 立ち上がりエッジから DRDYn 立ち上がりエッジまでを測定します | 44  | 114 | μs                |

| <b>4.5V ≤ IOVDD ≤ 5.5V</b> |                                      |                                          |     |     |                   |

| $t_p(\text{CSDO})$         | 伝搬遅延時間、CSn 立ち下がりエッジから SDO 駆動まで       |                                          |     | 50  | ns                |

| $t_p(\text{SCDO})$         | 伝搬遅延時間、SCLK 立ち上がりエッジから有効な新しい SDO まで  |                                          |     | 20  | ns                |

| $t_p(\text{CSDOZ})$        | 伝搬遅延時間、CSn 立ち上がりエッジから SDO 高インピーダンスまで |                                          |     | 75  | ns                |

| $t_w(\text{DRH})$          | パルス幅、DRDYn High                      |                                          | 4   |     | $t_{\text{MCLK}}$ |

| $t_{\text{TIMEOUT}}$       | SPI タイムアウト                           | 16385                                    |     |     | $t_{\text{OSCD}}$ |

| $t_{\text{POR}}$           | パワーオンリセット電圧                          | POR スレッショルドを超える電源から DRDYn 立ち上がりエッジまで測定   | 250 |     | μs                |

| $t_{\text{REGACQ}}$        | レジスタのデフォルト値のアクイジョン時間                 | RESETn 立ち上がりエッジから DRDYn 立ち上がりエッジまでを測定します | 44  | 114 | μs                |

## 5.8 タイミング図

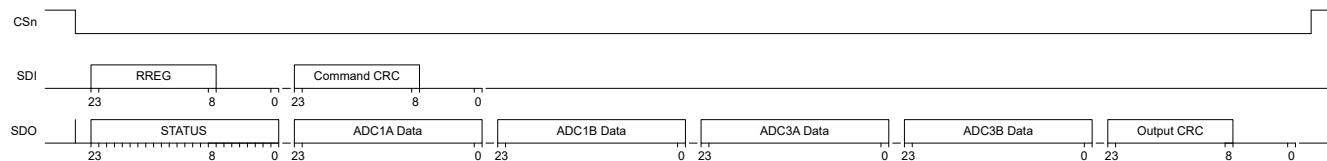

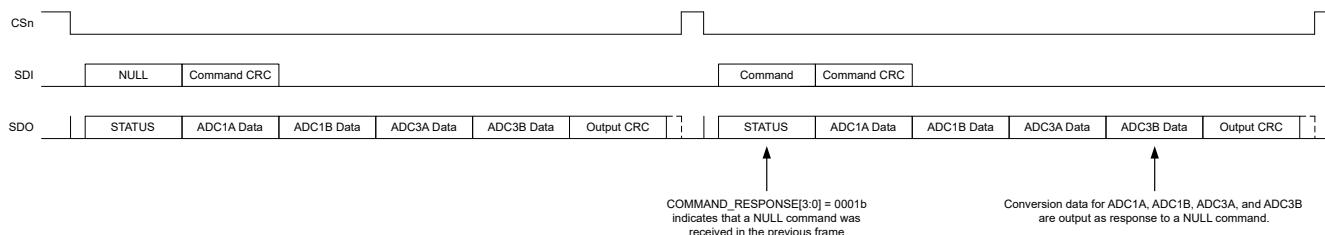

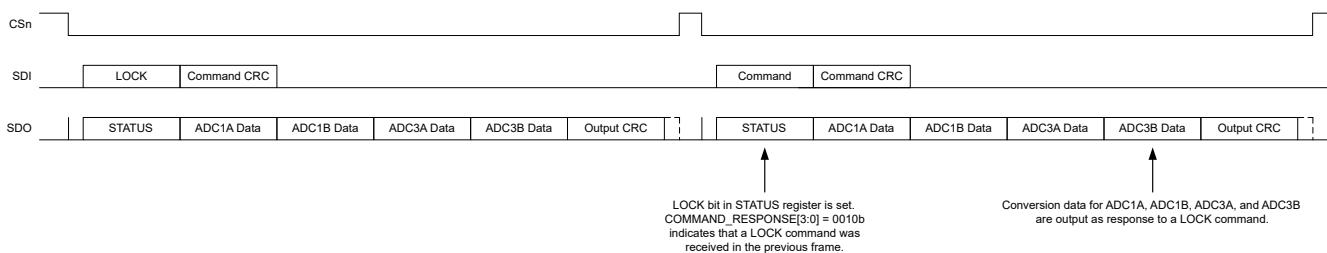

図 5-1. SPI のタイミング要件およびスイッチング特性

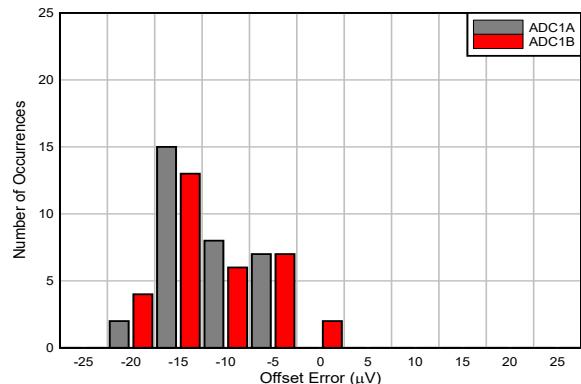

## 5.9 代表的特性

$T_A = 25^\circ\text{C}$ 、APWR = 5V、DPWR = 5V、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

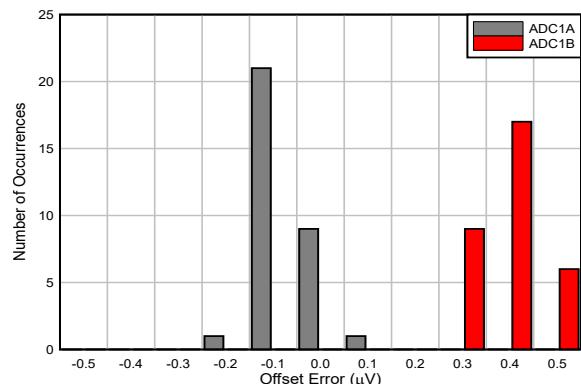

32 デバイス、ゲイン = 8、グローバル・チョップの無効化、入力換算

図 5-2. ADC1y オフセット誤差のヒストグラム

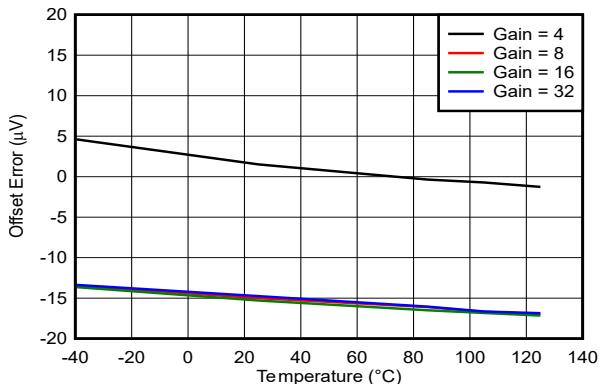

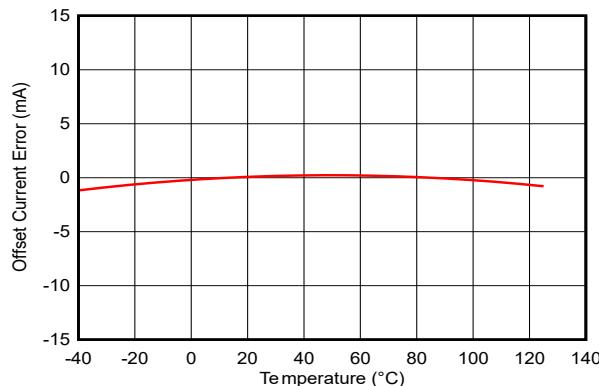

グローバル・チョップがディセーブル、入力換算

図 5-3. ADC1y オフセット誤差と温度との関係

32 デバイス、ゲイン = 8、グローバル・チョップ・イネーブル、入力換算

図 5-4. ADC1y オフセット誤差のヒストグラム

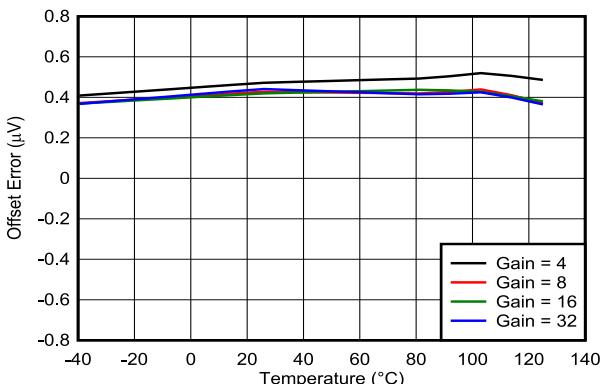

グローバル・チョップがイネーブル、入力換算

図 5-5. ADC1y オフセット誤差と温度との関係

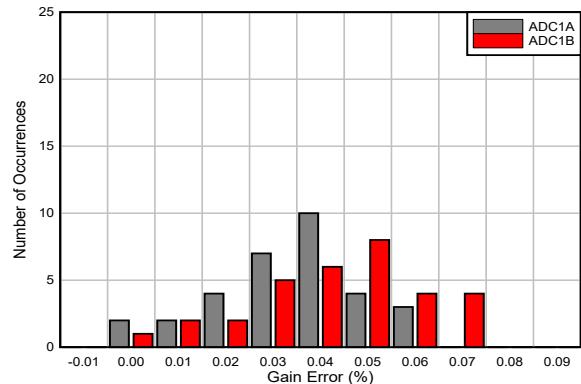

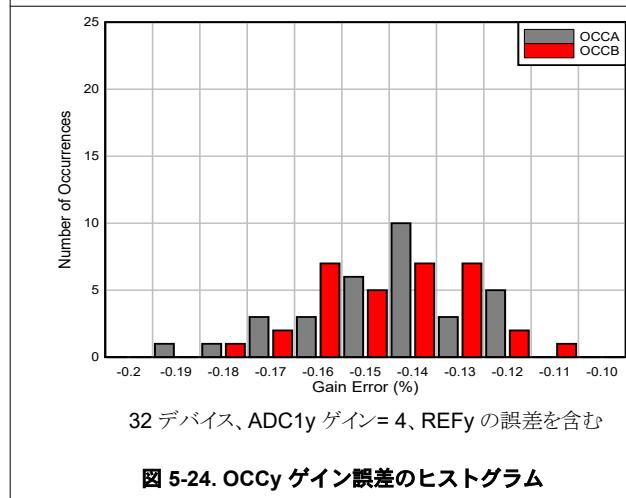

32 デバイス、ゲイン = 4、REFy の誤差を含む

図 5-6. ADC1y ゲイン誤差のヒストグラム

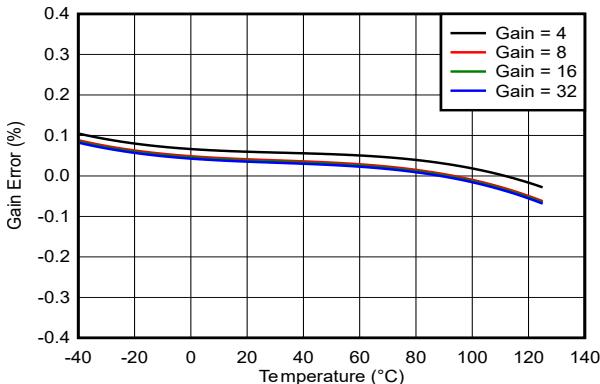

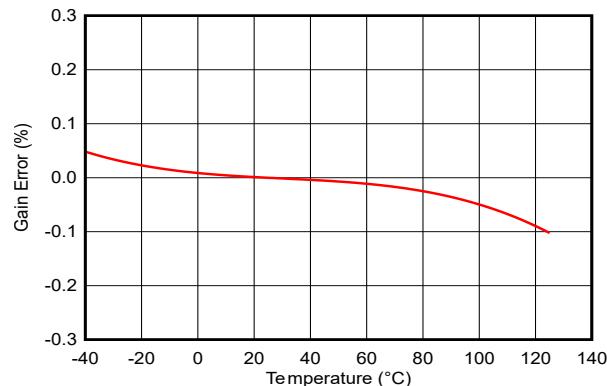

REFy の誤差を含む

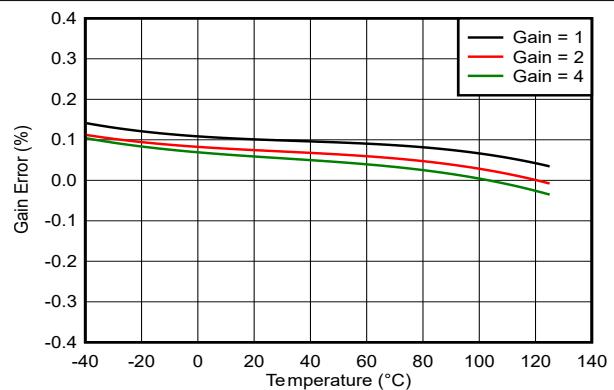

図 5-7. ADC1y ゲイン誤差と温度との関係

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、APWR = 5V、DPWR = 5V、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

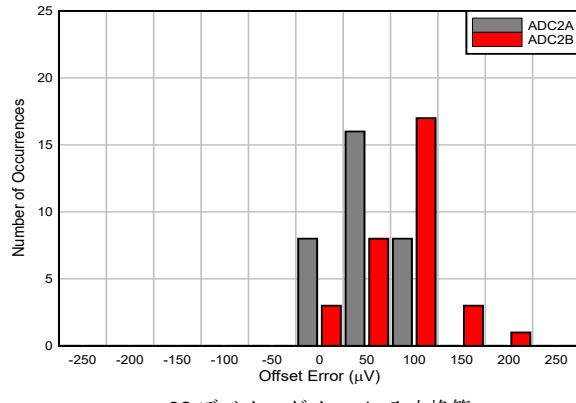

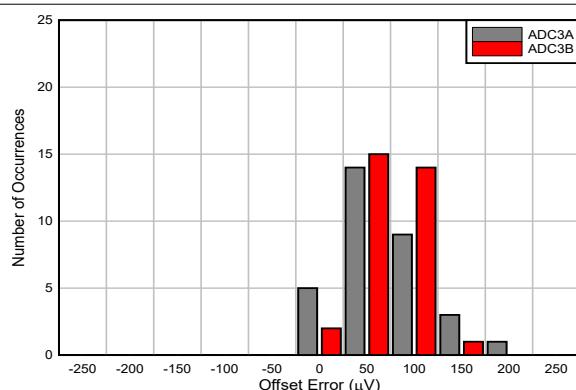

図 5-8. ADC2y オフセット誤差のヒストグラム

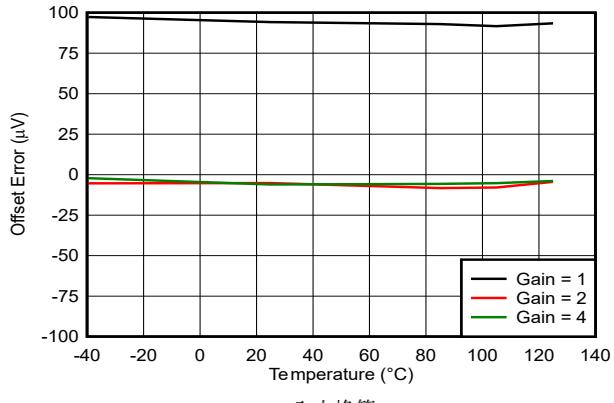

図 5-9. ADC2y のオフセット誤差と温度との関係

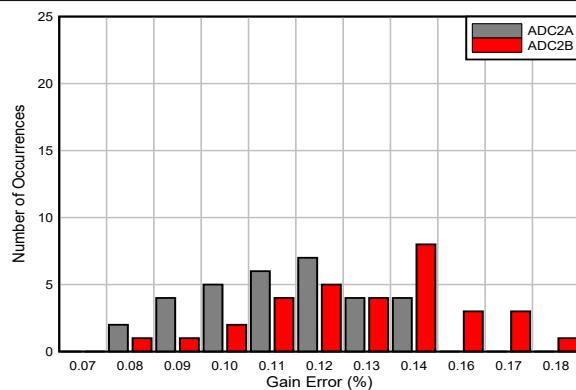

図 5-10. ADC2y のゲイン誤差のヒストグラム

図 5-11. ADC2y のゲイン誤差と温度との関係

図 5-12. ADC3y オフセット誤差のヒストグラム

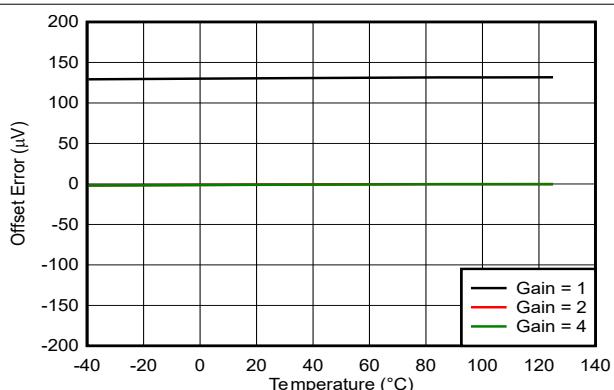

図 5-13. ADC3y オフセット誤差と温度との関係

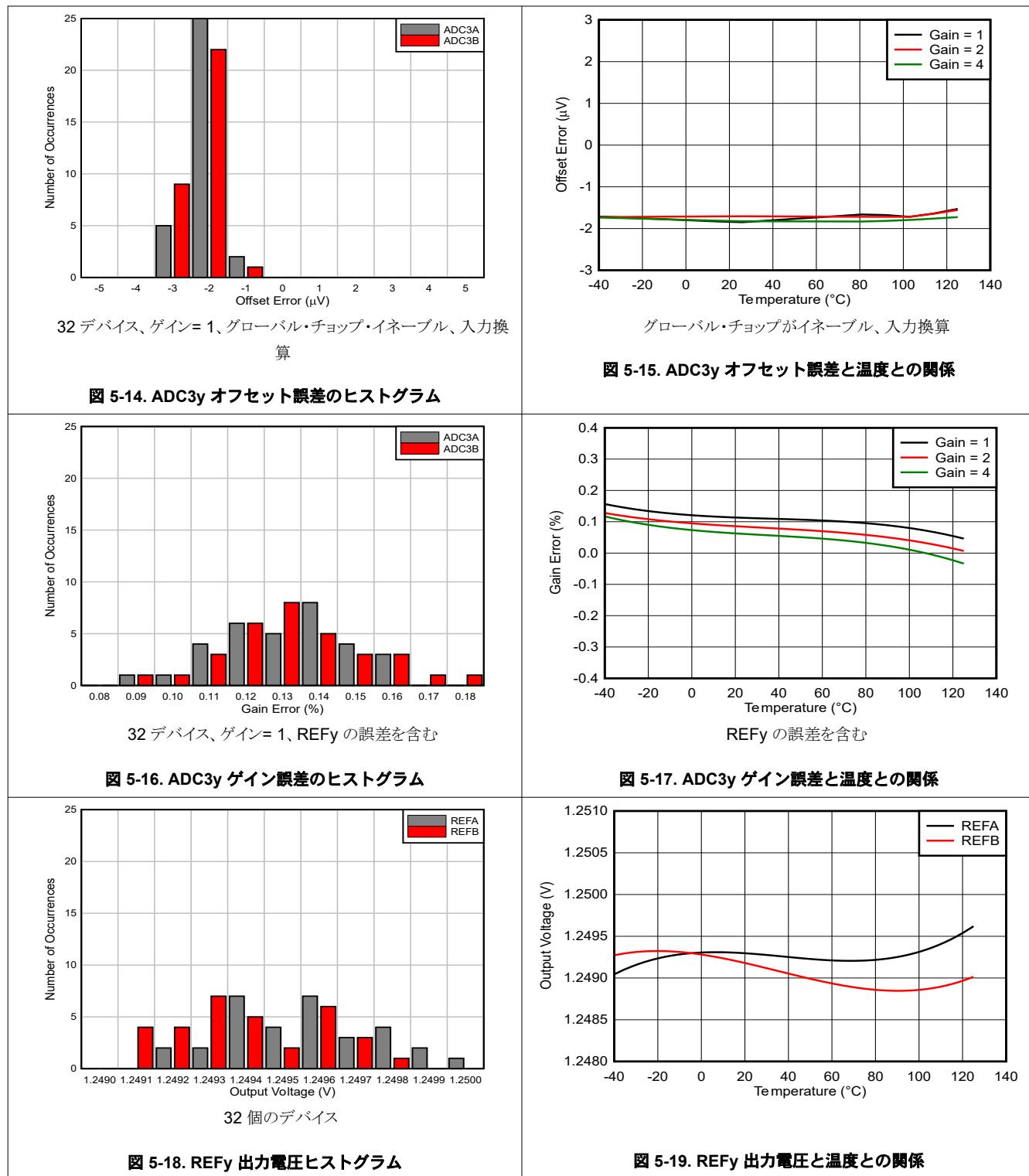

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、APWR = 5V、DPWR = 5V、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、APWR = 5V、DPWR = 5V、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

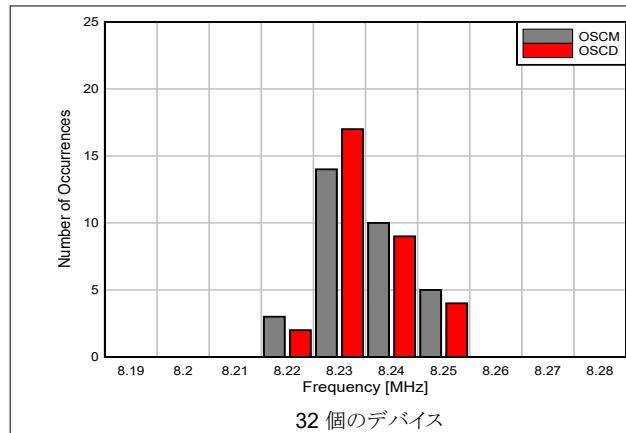

図 5-20. OSCM および OSCD の周波数ヒストグラム

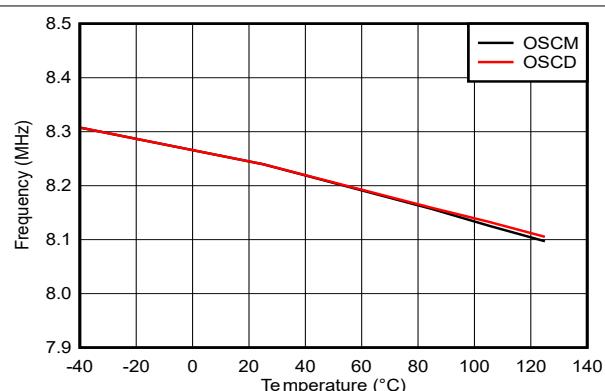

図 5-21. OSCM および OSCD 周波数と温度との関係

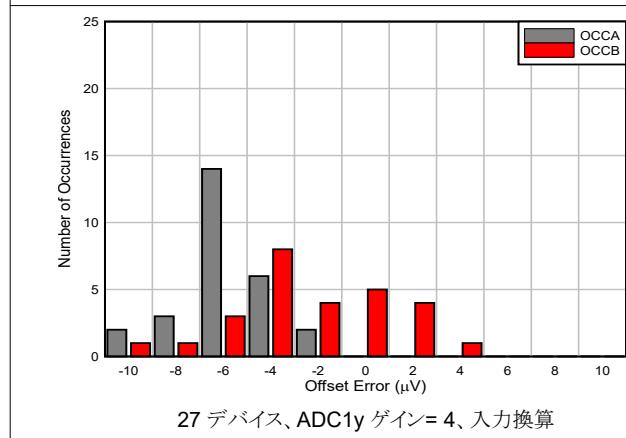

図 5-22. OCCy オフセット誤差のヒストグラム

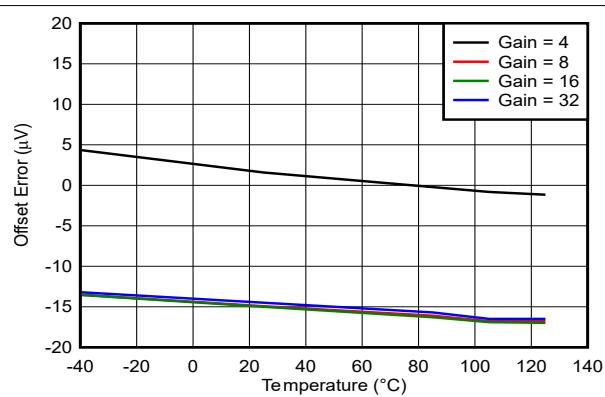

図 5-23. OCCy オフセット誤差と温度との関係

図 5-24. OCCy ゲイン誤差のヒストグラム

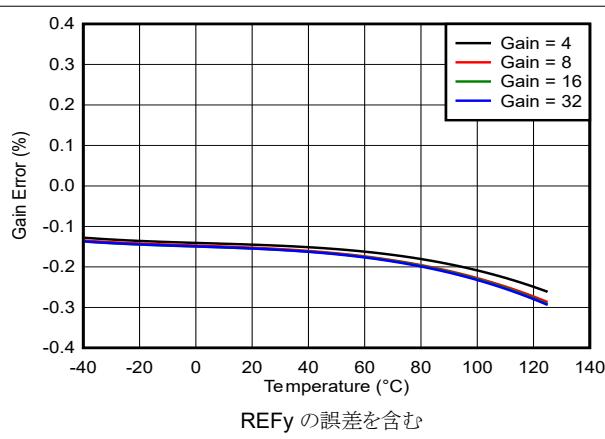

図 5-25. OCCy のゲイン誤差と温度との関係

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、APWR = 5V、DPWR = 5V、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

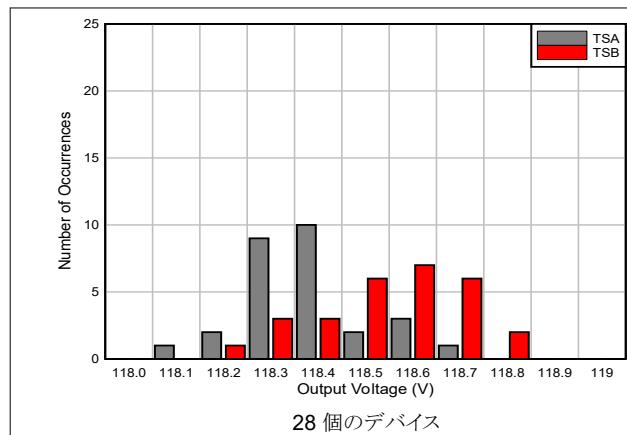

図 5-26. 温度センサ出力電圧のヒストグラム

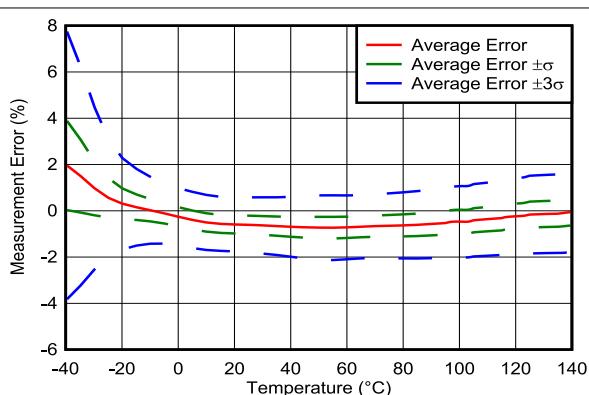

図 5-27. 温度センサ測定誤差と周囲温度との関係

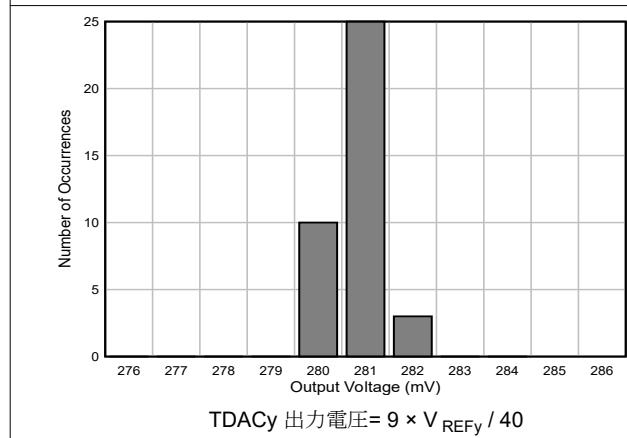

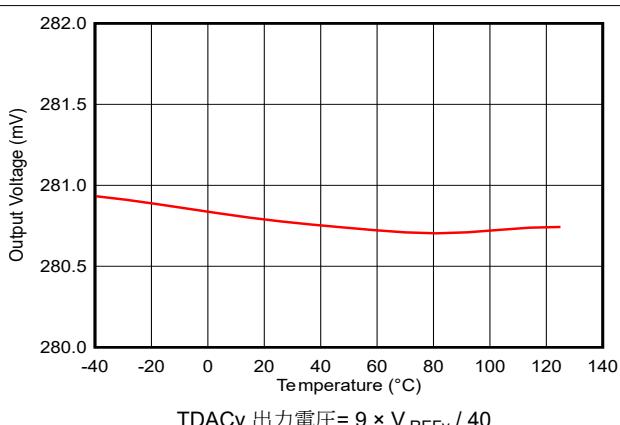

図 5-28. DACy 出力電圧ヒストグラムのテスト

図 5-29. テスト DACy 出力電圧と温度との関係

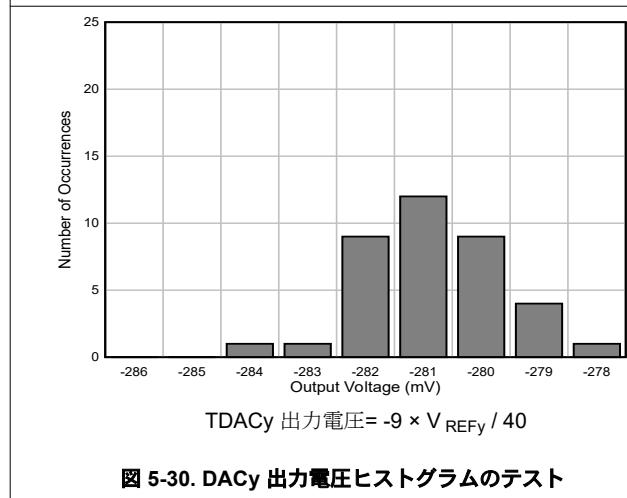

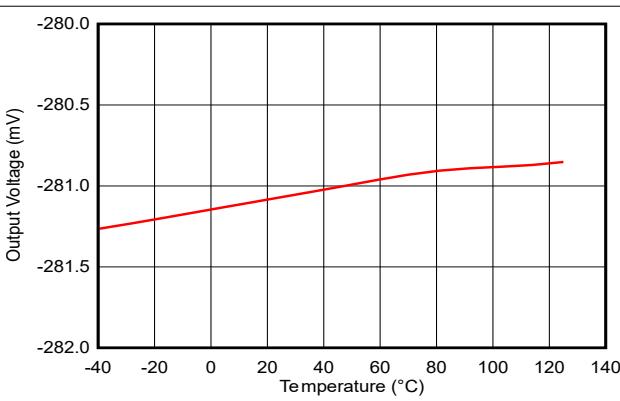

図 5-30. DACy 出力電圧ヒストグラムのテスト

図 5-31. テスト DACy 出力電圧と温度との関係

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、APWR = 5V、DPWR = 5V、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

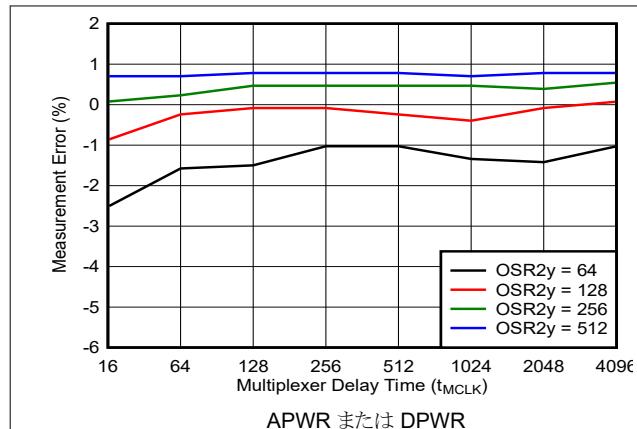

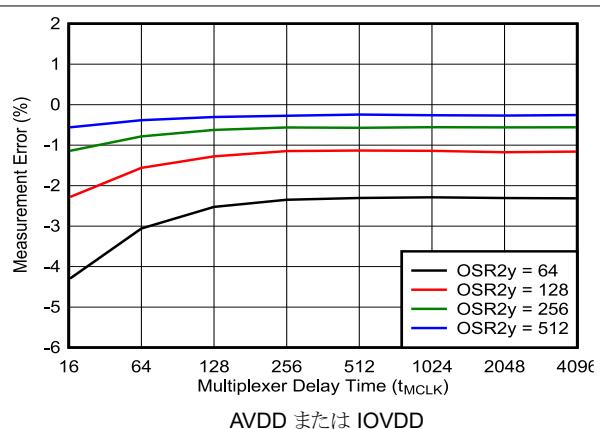

図 5-32. ADC2y 電源電圧リードバック測定精度

図 5-33. ADC2y 電源電圧リードバック測定精度

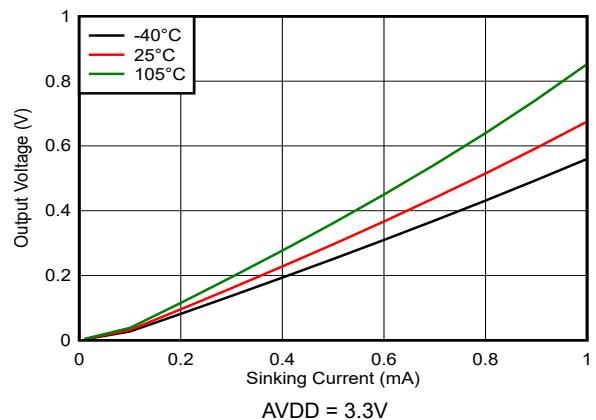

図 5-34. アナログ GPIO ピンの出力電圧の

シンク電流との関係

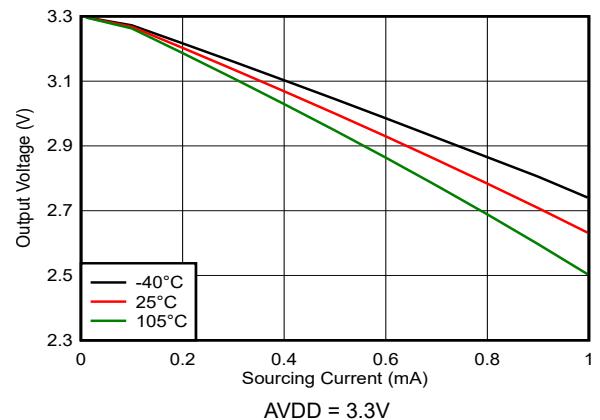

図 5-35. アナログ GPIO ピンの出力電圧と

ソース電流との関係

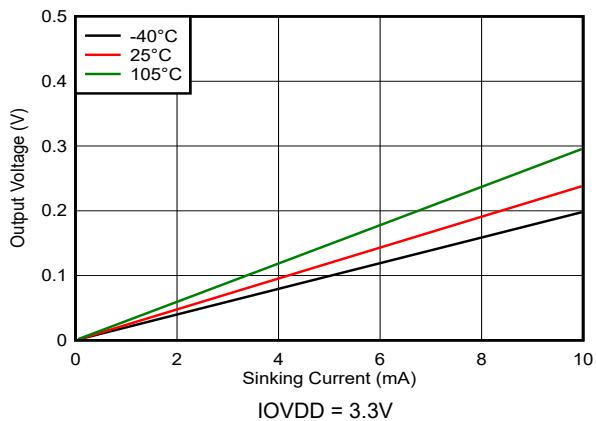

図 5-36. デジタル ピンの出力電圧とシンク電流との関係

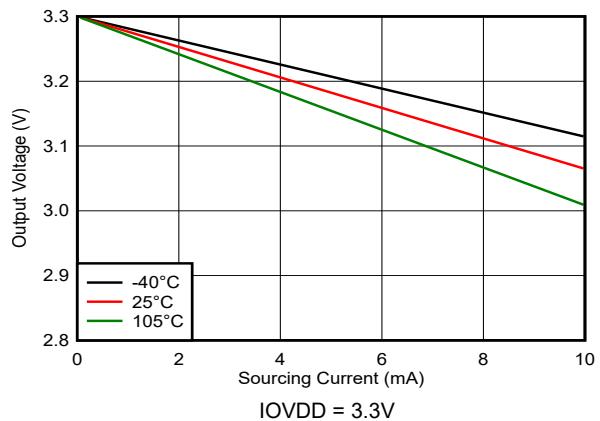

図 5-37. デジタル ピンの出力電圧とソース電流との関係

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $\text{APWR} = 5\text{V}$ 、 $\text{DPWR} = 5\text{V}$ 、および  $f_{\text{CLK}} = 8.192\text{ MHz}$  付きの外部クロック (特に記述のない限り)

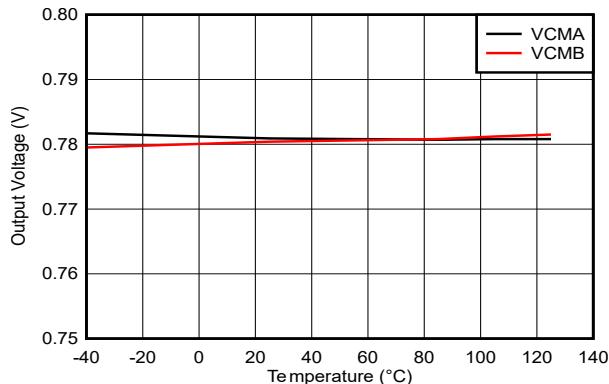

図 5-38. VCMY 出力電圧と温度との関係

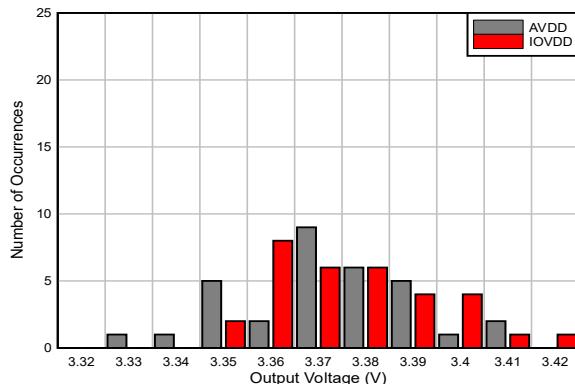

32 個のデバイス

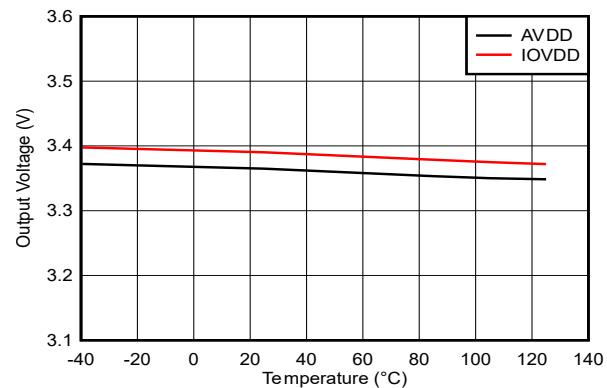

図 5-39. AVDD と IOVDD LDO の出力電圧ヒストグラム

図 5-40. AVDD および IOVDD LDO 出力電圧と温度との関係

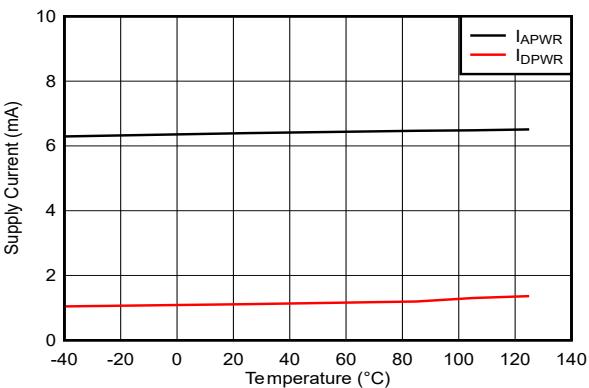

アクティブ モード、すべての有効 ADC、変換

図 5-41. 電源電流と温度との関係

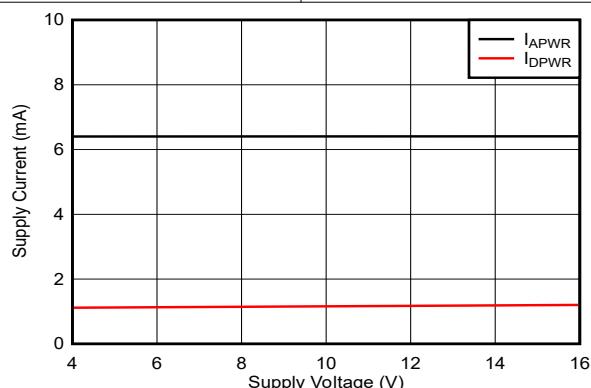

アクティブ モード、すべての有効 ADC、変換

図 5-42. 電源電流と電源電圧との関係

## 6 パラメータ測定情報

### 6.1 オフセット ドリフトの測定

オフセットドリフトは、指定された温度範囲全体にわたって測定される、オフセット電圧の変化として定義されます。オフセットドリフトは ボックス方式を使用して計算され、指定された温度範囲内で最大と最小のオフセット電圧を囲むボックスが形成されます。このボックス方式では、温度誤差の限界が規定されますが、テスト対象となるデバイスの測定結果について、正確な形状とスロープは規定されません。このため、オフセットドリフトは正の値のみとして規定されていますが、ドリフトは負の値になる可能性があります。ボックス方式を使用したオフセットドリフトの計算を、式 1 に示します。

$$\text{Offset Drift (nV/}^{\circ}\text{C)} = 10^9 \times (V_{\text{OFSMAX}} - V_{\text{OFSMIN}}) / (T_{\text{MAX}} - T_{\text{MIN}}) \quad (1)$$

ここで

- $V_{\text{OFSMIN}}$  および  $V_{\text{OFSMAX}}$  = 指定された温度範囲内の最小と最大のオフセット電圧

- $T_{\text{MIN}}$  と  $T_{\text{MAX}}$  = 最低と最高の温度

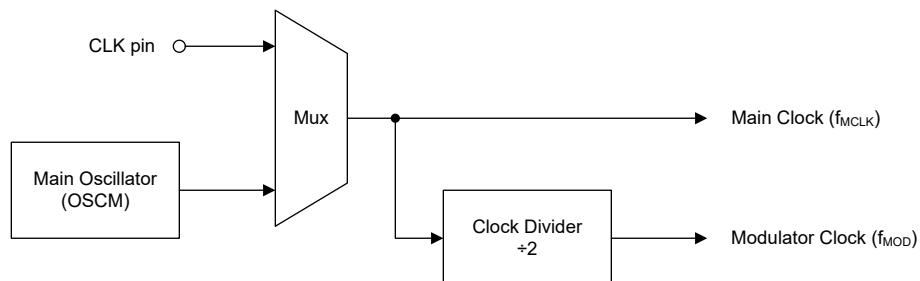

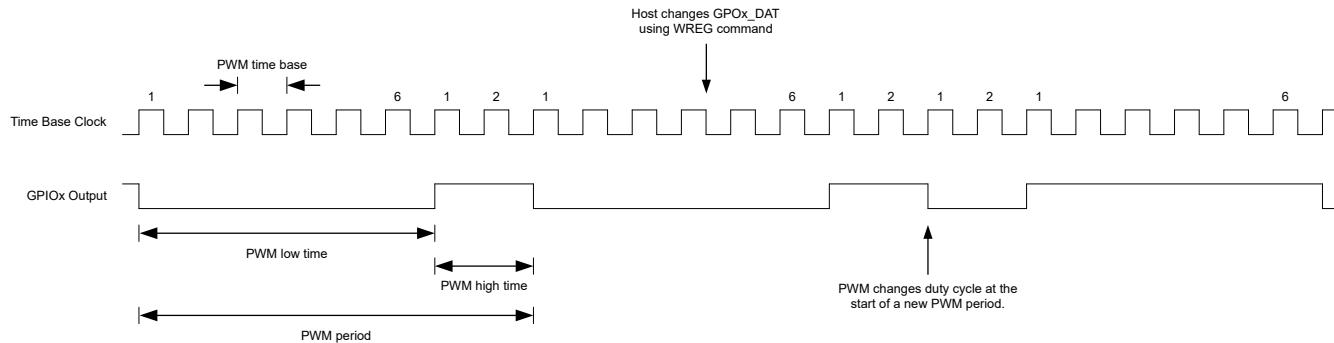

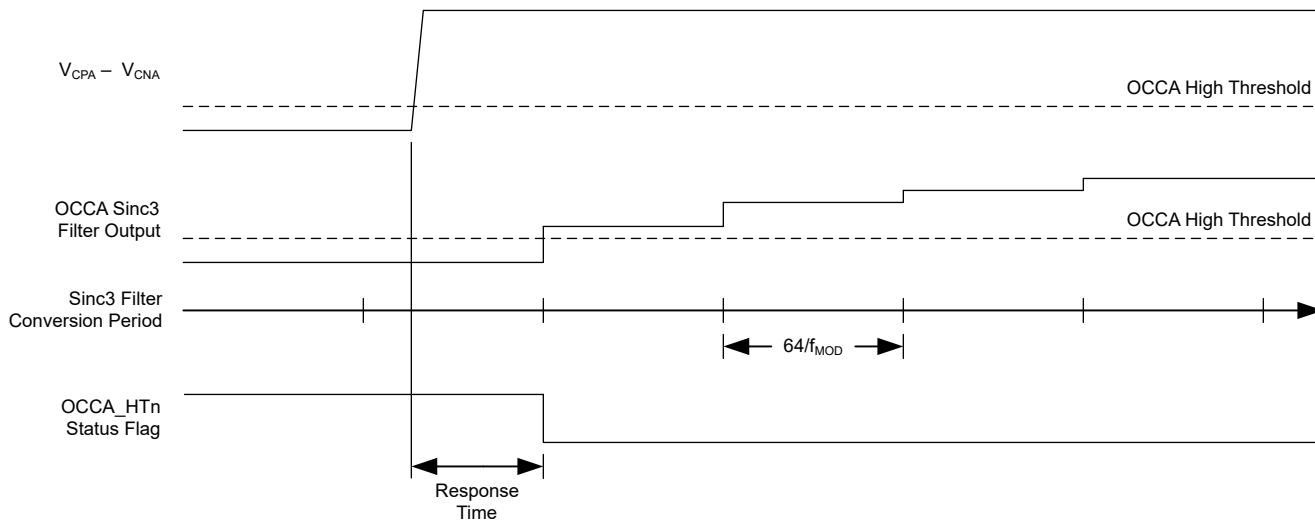

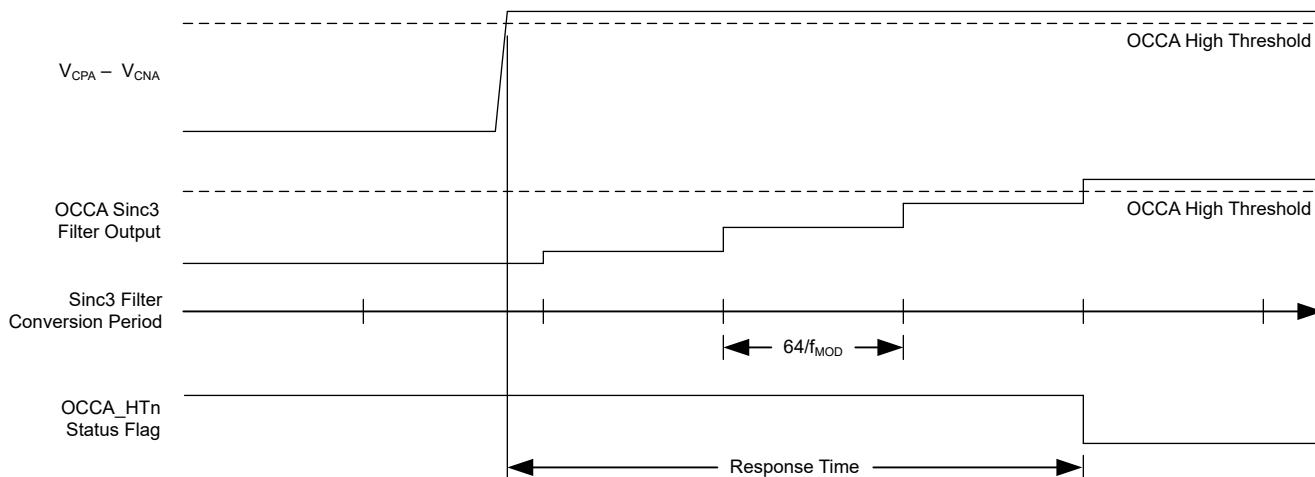

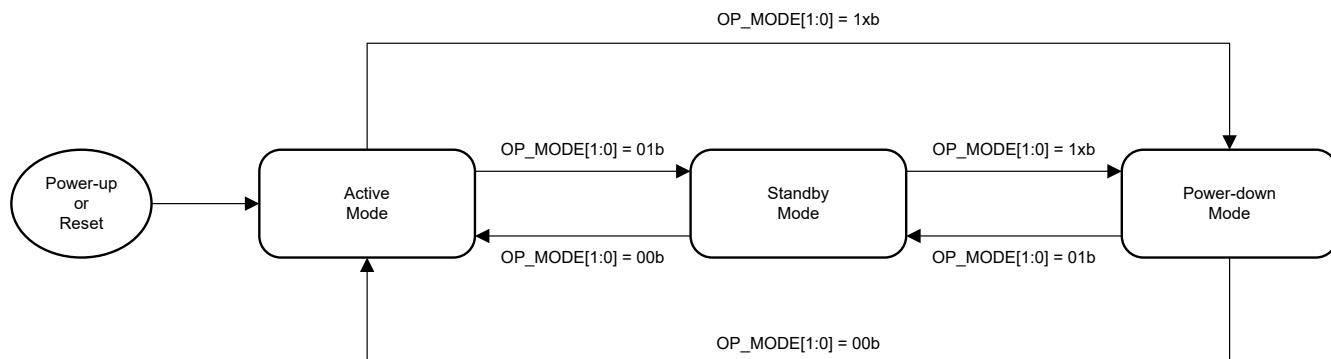

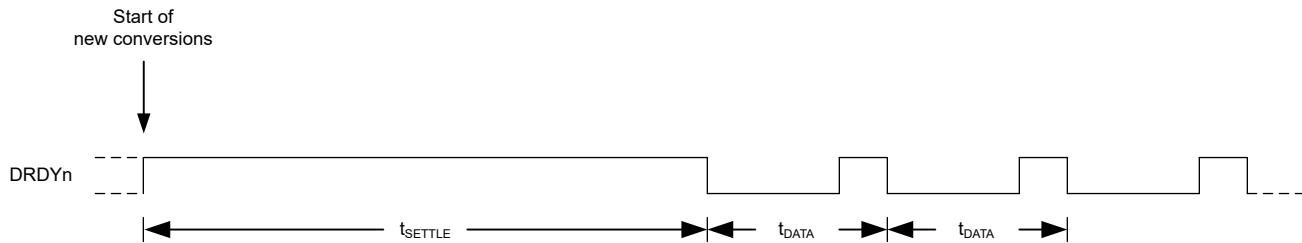

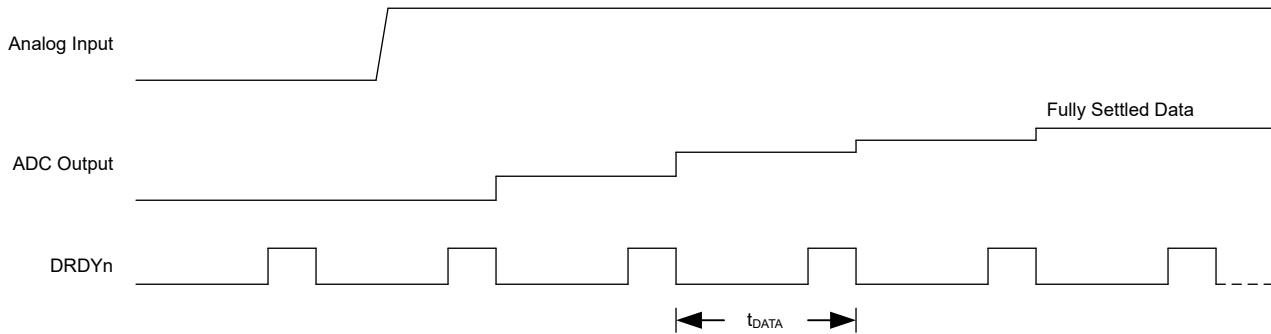

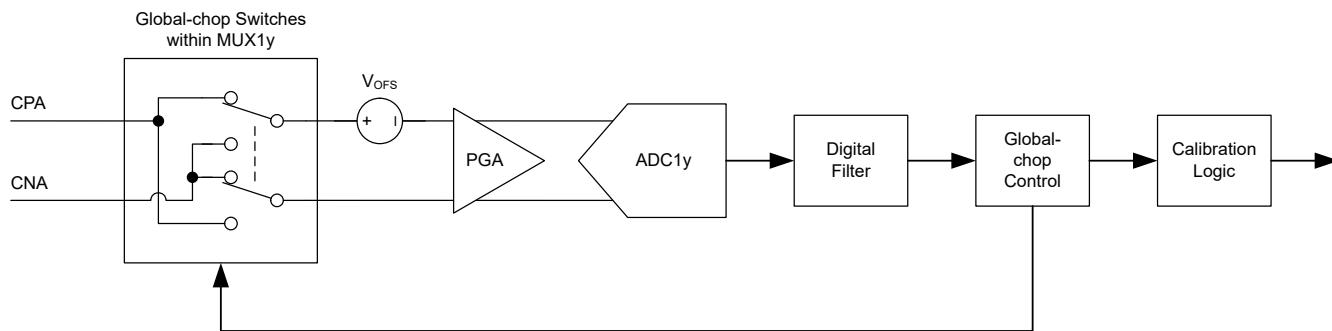

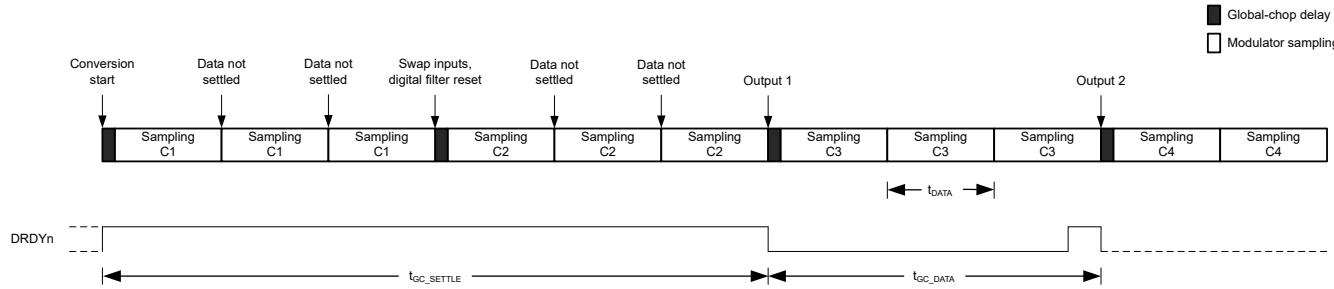

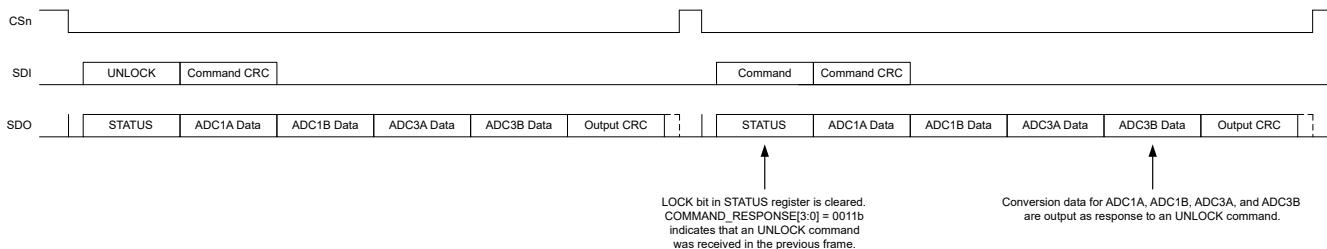

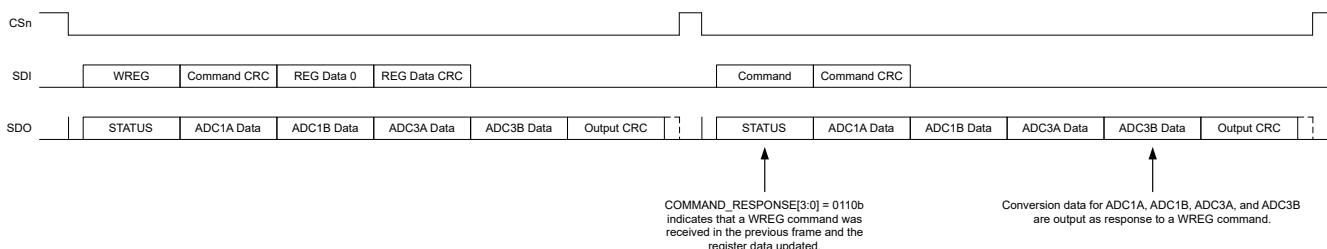

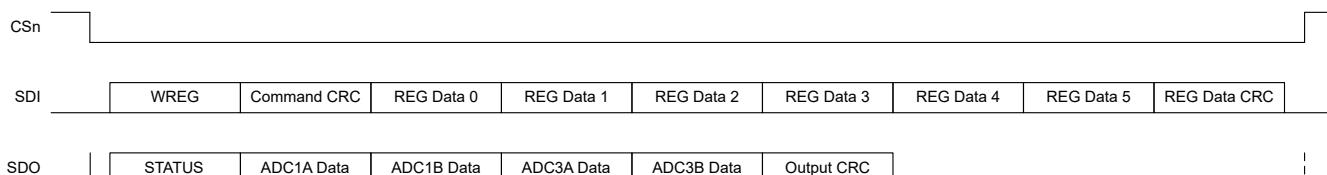

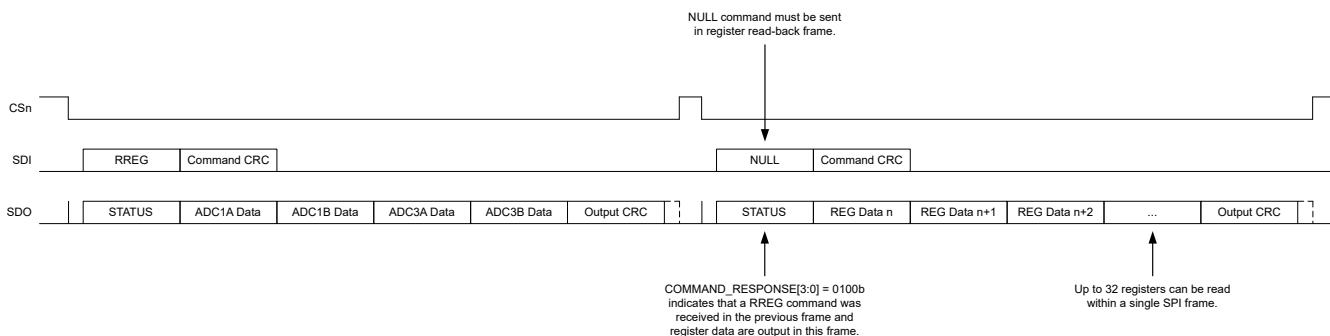

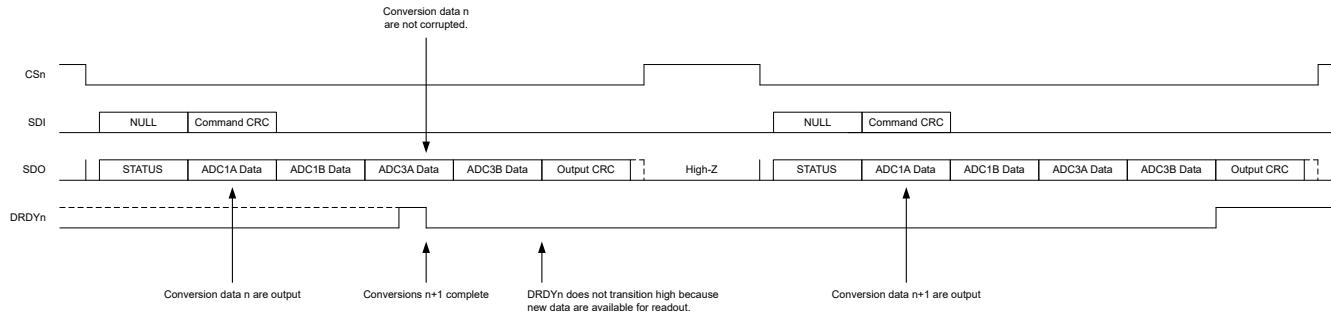

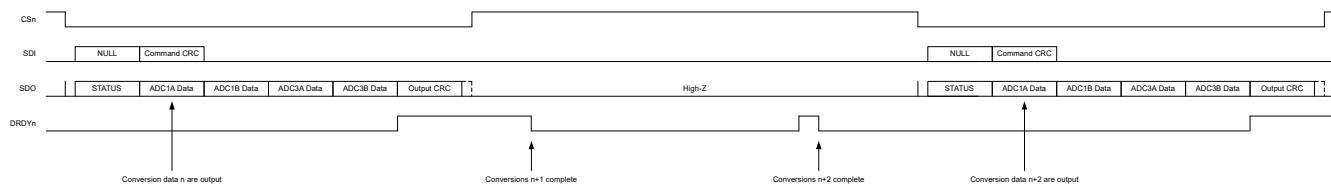

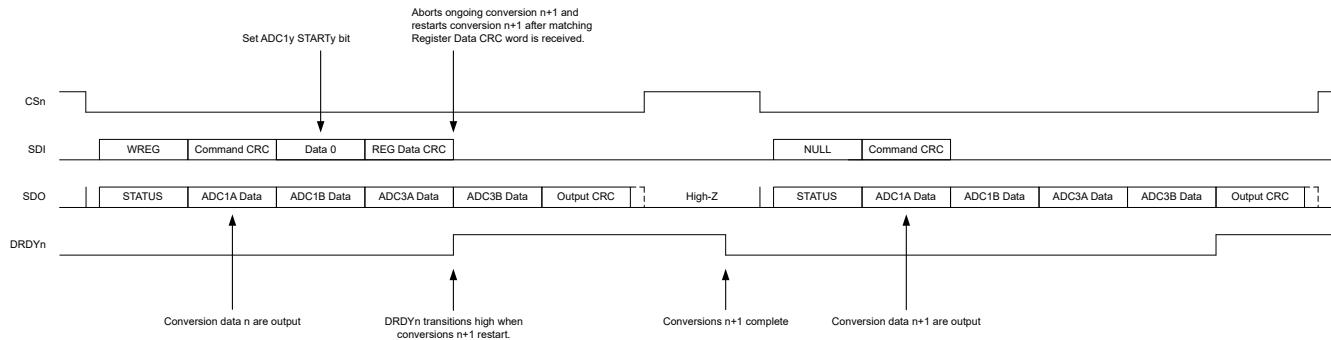

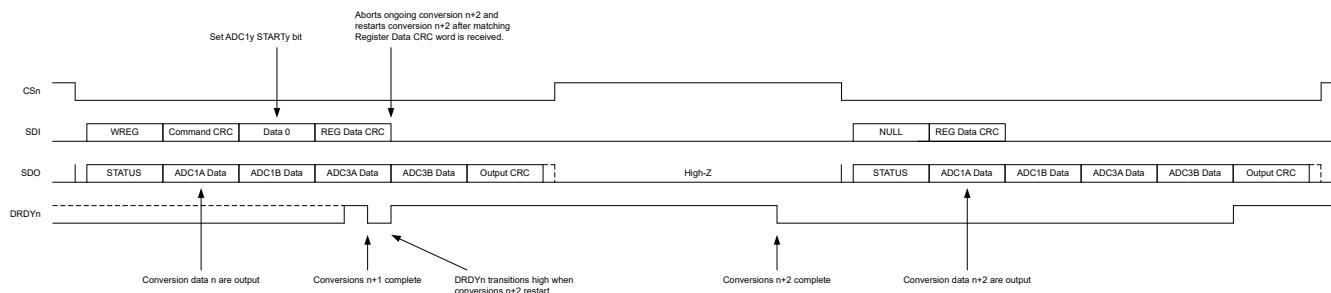

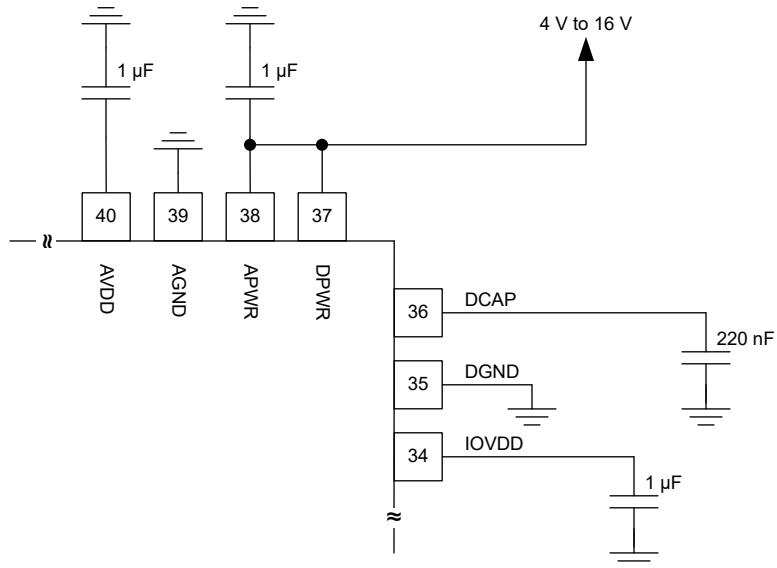

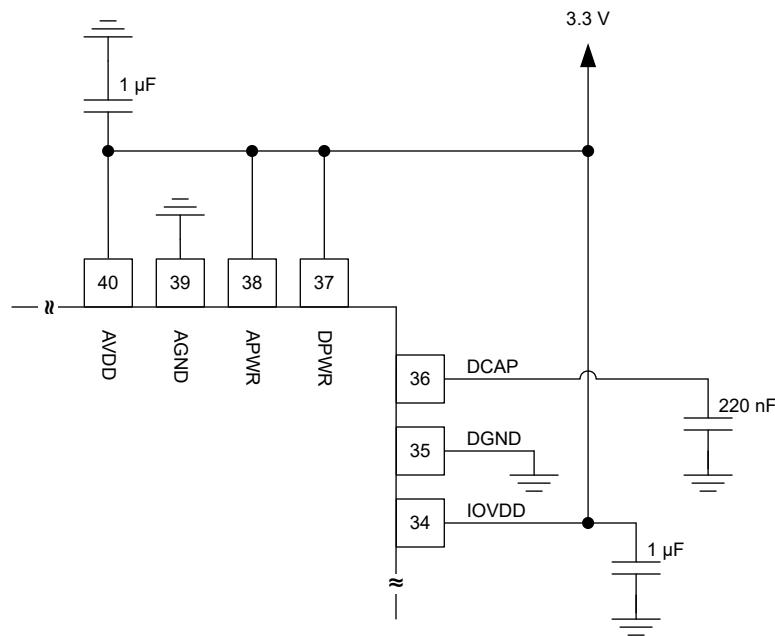

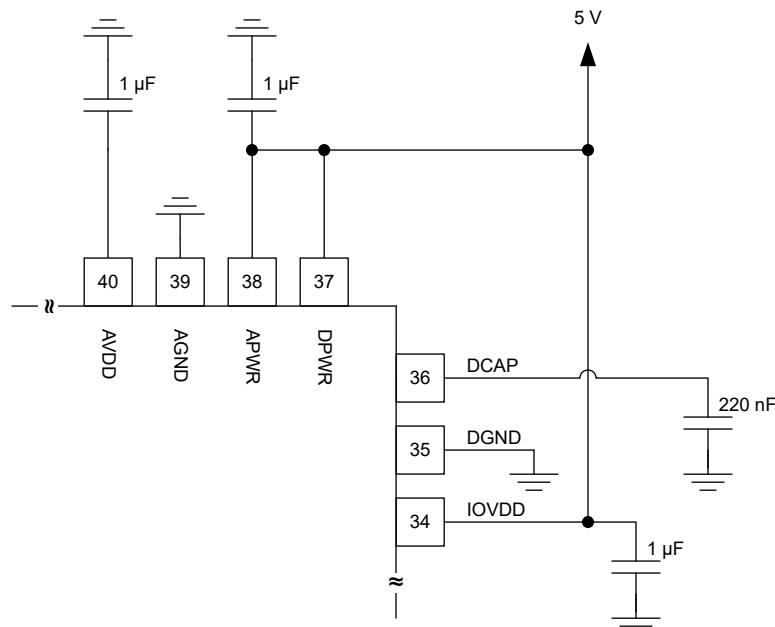

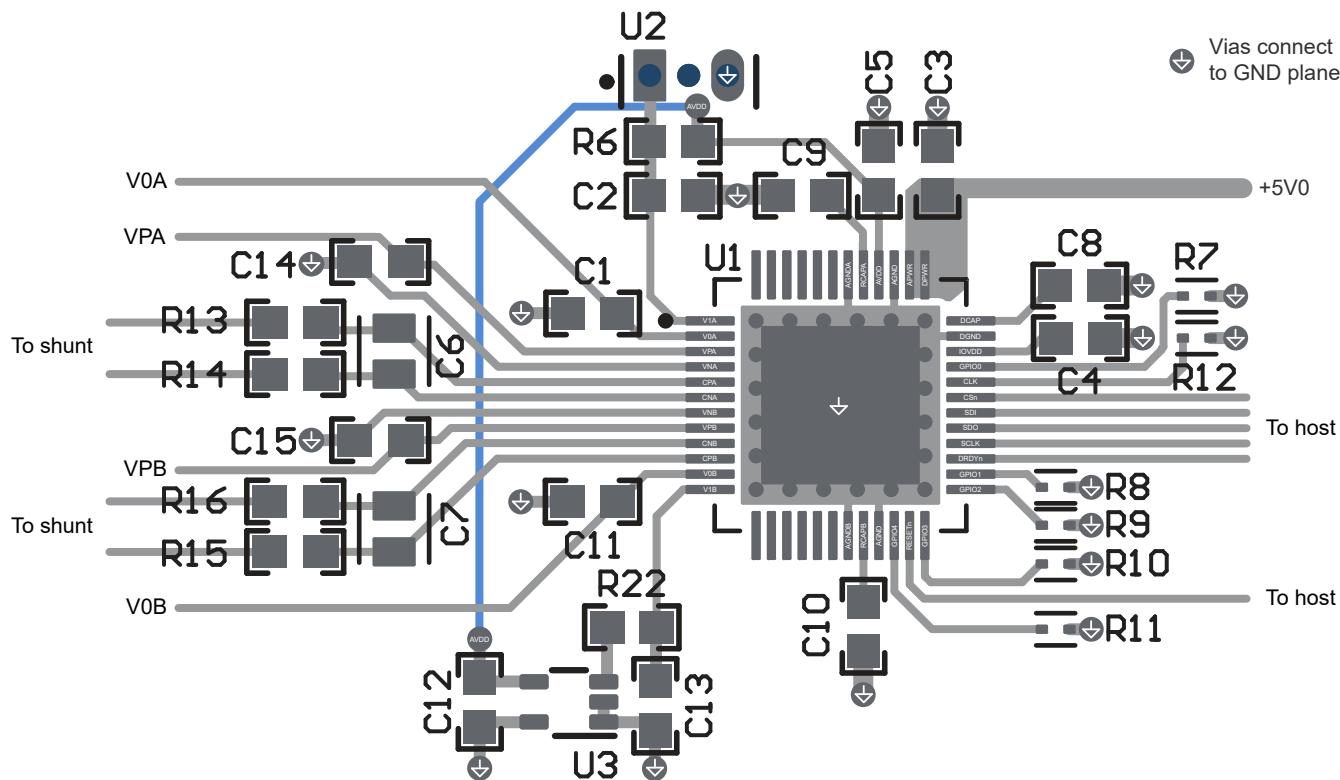

### 6.2 ゲイン ドリフトの測定