# ADS1288 地震検出アプリケーション向け、32 ビット、デルタ シグマ ADC

## 1 特長

- 消費電力:

- PGA 動作: 5mW (標準値)

- バッファ動作: 3mW (標準値)

- ダイナミックレンジ:

- PGA ゲイン: 1,500SPS (122dB、標準値)

- バッファ動作: 500SPS (122dB、標準値)

- THD: < -120dB (標準値)

- CMRR: 120dB (標準値)

- フレキシブルなデジタルフィルタ:

- Sinc + FIR + IIR (選択可能)

- 線形または最小位相

- ハイパスフィルタ

- データレート: 125SPS ~ 2000SPS

- PGA ゲイン: 1 ~ 64

- SYNC 入力

- クロック誤差補償

- 2 チャネル マルチプレクサ

- オフセットおよびゲインの較正

- 汎用デジタル I/O

- アナログ電源の動作: 5V、3.3V または ±2.5V

## 2 アプリケーション

- エネルギー探査

- 受動的地震波観測

- 地球科学および地質学

- 高精度計測機器

## 3 概要

ADS1288 は、プログラマブル ゲイン アンプ (PGA) と有限インパルス応答 (FIR) フィルタを備えた 32 ビット、低消費電力の A/D コンバータ (ADC) です。この ADC は、低消費電力による長いバッテリ動作時間が求められる地震関連機器の厳しい要件に合わせて設計されています。

低ノイズ PGA により、ADC のゲイン 1 ~ 64 のダイナミックレンジが拡張されます。この PGA により、外付けアンプを使用せずに、ジオフォンやトランス結合のハイドロフォンを直接接続できます。オプションのユニティ ゲイン バッファによって消費電力が低減されます。

この ADC は、高分解能のデルタシグマ ( $\Delta\Sigma$ ) 変調器と、位相応答を設定できる FIR フィルタを内蔵しています。ハイパスフィルタは、DC および低周波数成分を信号から除去します。サンプル レート コンバータは、最大 7ppb の分解能の精度でクロック周波数誤差を補償します。

デバイスの消費電力を最小限に抑えるため、この ADC は 3.3V の動作をサポートしています。消費電力は、バッファモード動作で 3mW (標準値)、PGA モード動作で 5mW (標準値) です。

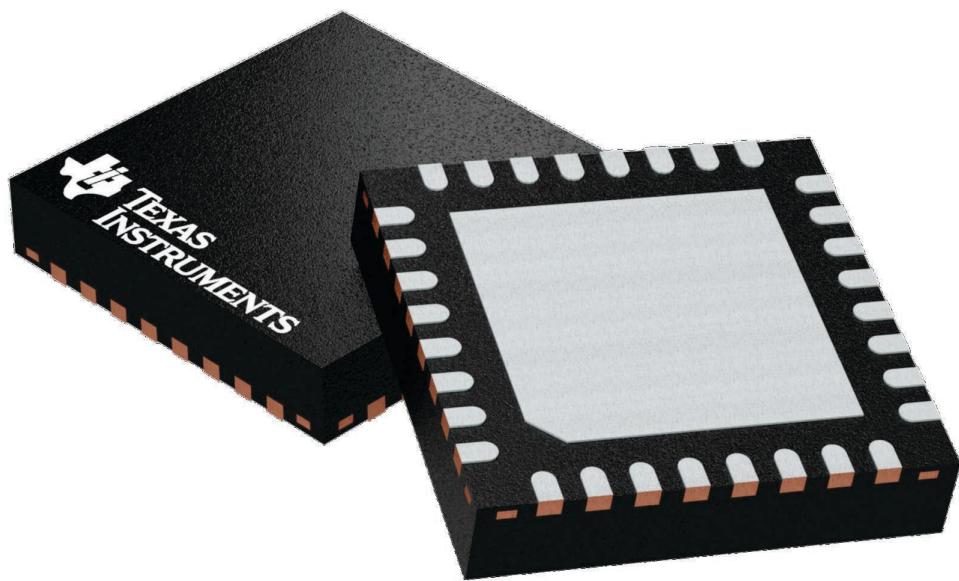

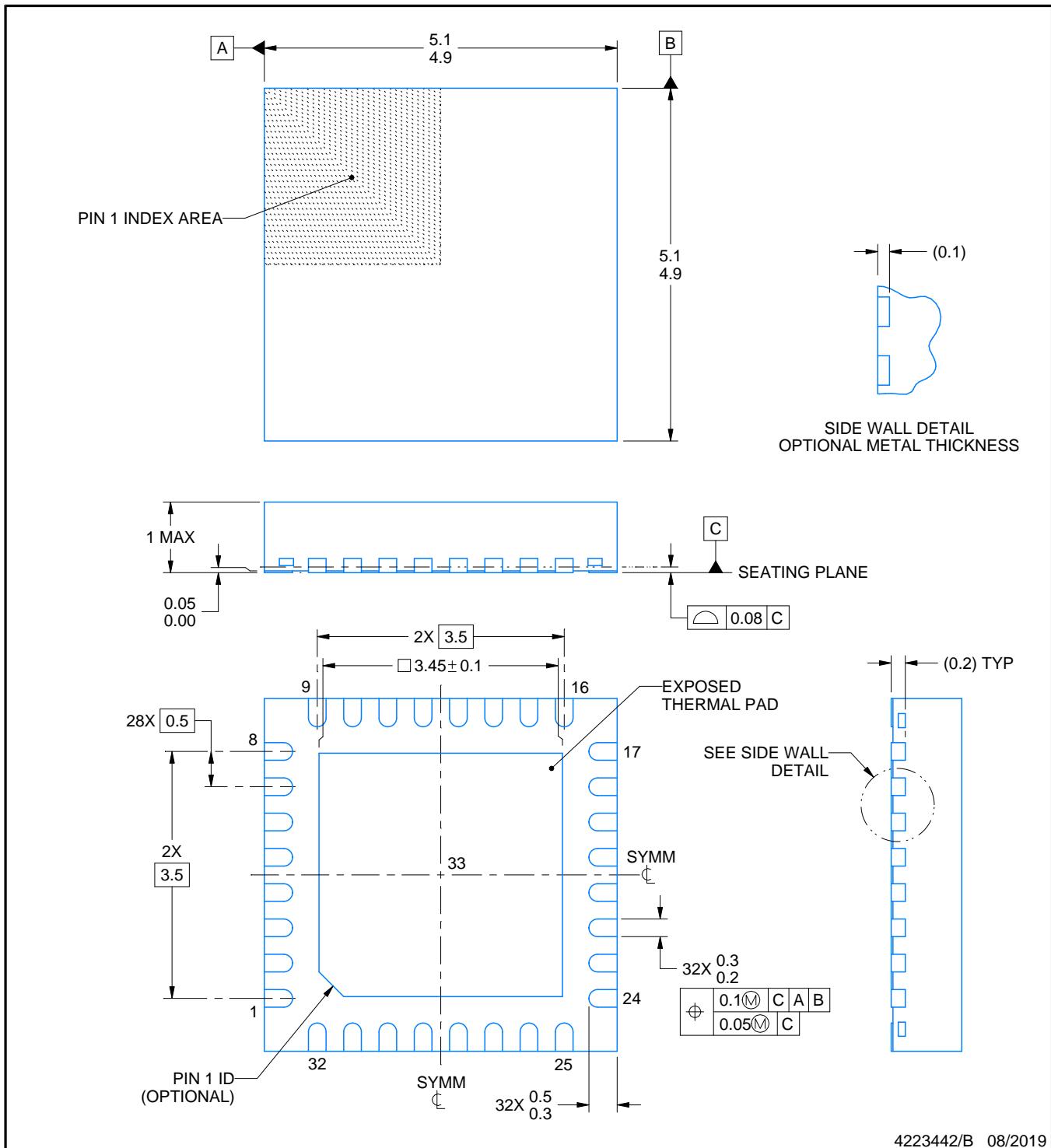

この ADC は小型の 5mm × 5mm VQFN パッケージで供給され、-40°C ~ +85°C の周囲温度範囲で仕様が規定されています。

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| ADS1288 | RHB (VQFN, 32)       | 5mm × 5mm                |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

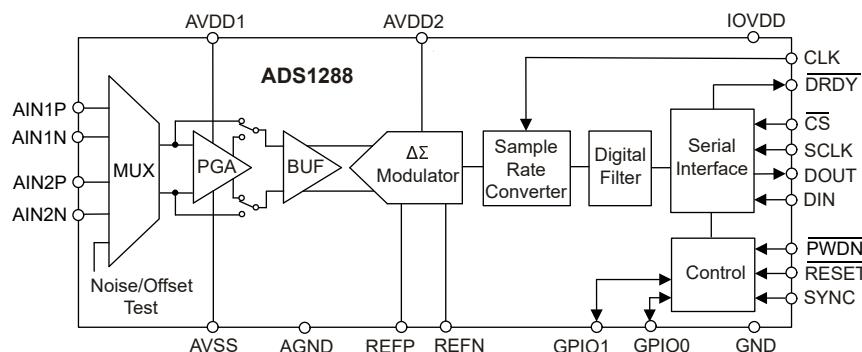

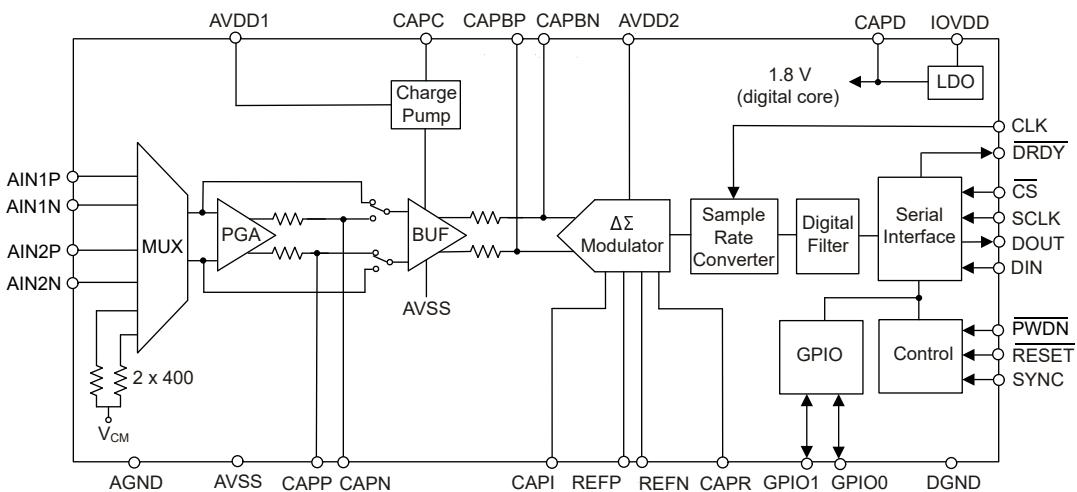

機能ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SBASAW0

## 目次

|                                                                                |           |                               |           |

|--------------------------------------------------------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                                                                    | <b>1</b>  | 7.2 機能ブロック図                   | <b>18</b> |

| <b>2 アプリケーション</b>                                                              | <b>1</b>  | 7.3 機能説明                      | <b>19</b> |

| <b>3 概要</b>                                                                    | <b>1</b>  | 7.4 デバイスの機能モード                | <b>33</b> |

| <b>4 ピン構成および機能</b>                                                             | <b>3</b>  | 7.5 プログラミング                   | <b>37</b> |

| <b>5 仕様</b>                                                                    | <b>5</b>  | <b>8 レジスタ マップ</b>             | <b>42</b> |

| 5.1 絶対最大定格                                                                     | 5         | 8.1 レジスタの説明                   | 42        |

| 5.2 ESD 定格                                                                     | 5         | <b>9 アプリケーションと実装</b>          | <b>48</b> |

| 5.3 推奨動作条件                                                                     | 5         | 9.1 アプリケーション情報                | 48        |

| 5.4 熱に関する情報                                                                    | 6         | 9.2 代表的なアプリケーション              | 48        |

| 5.5 電気的特性                                                                      | 7         | 9.3 電源に関する推奨事項                | 50        |

| 5.6 タイミング要件: $1.65V \leq IOVDD \leq 1.95V$ および<br>$2.7V \leq IOVDD \leq 3.6V$  | 9         | 9.4 レイアウト                     | 51        |

| 5.7 スイッチング特性: $1.65V \leq IOVDD \leq 1.95V$ および<br>$2.7V \leq IOVDD \leq 3.6V$ | 9         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>51</b> |

| 5.8 タイミング図                                                                     | 10        | 10.1 ドキュメントの更新通知を受け取る方法       | 51        |

| 5.9 代表的特性                                                                      | 12        | 10.2 サポート・リソース                | 52        |

| <b>6 パラメータ測定情報</b>                                                             | <b>17</b> | 10.3 商標                       | 52        |

| 6.1 ノイズ性能                                                                      | 17        | 10.4 静電気放電に関する注意事項            | 52        |

| <b>7 詳細説明</b>                                                                  | <b>17</b> | 10.5 用語集                      | 52        |

| 7.1 概要                                                                         | 17        | <b>11 改訂履歴</b>                | <b>52</b> |

|                                                                                |           | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>52</b> |

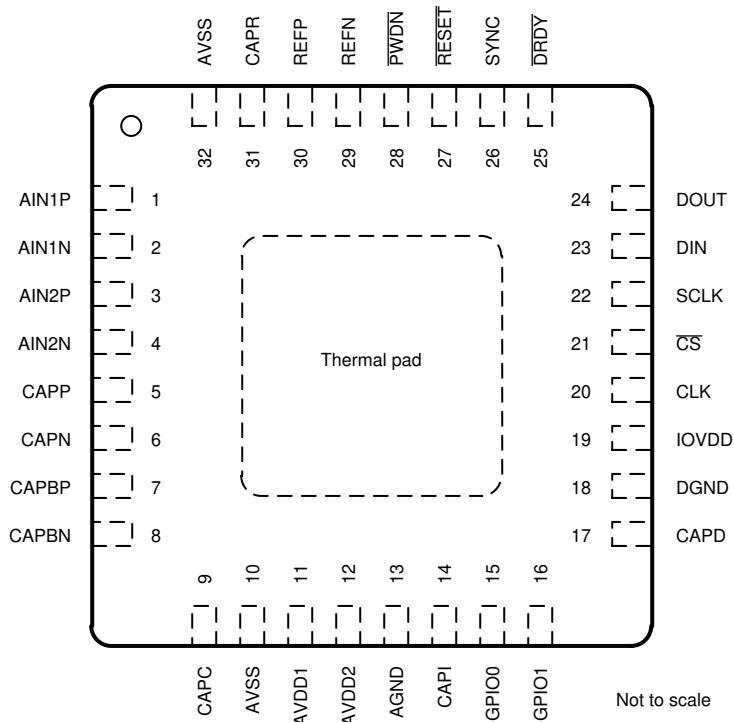

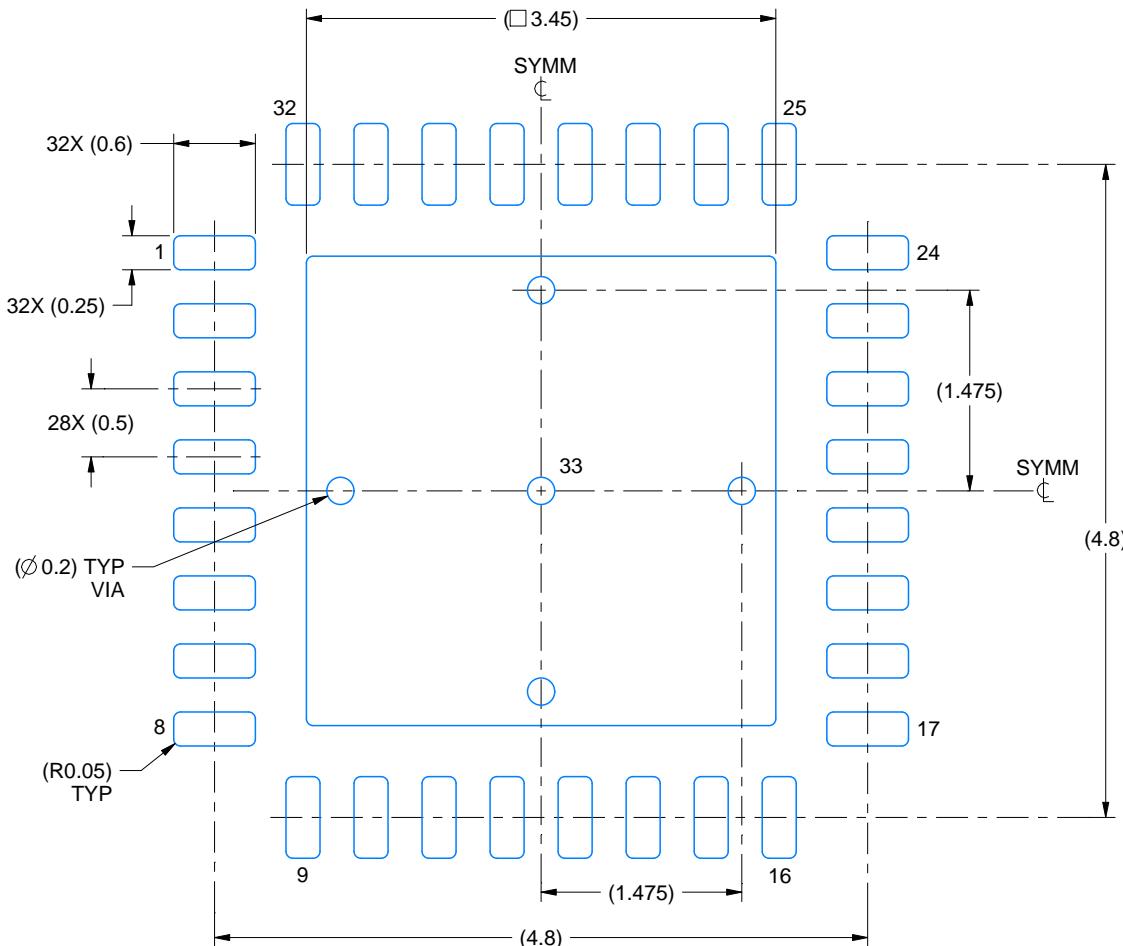

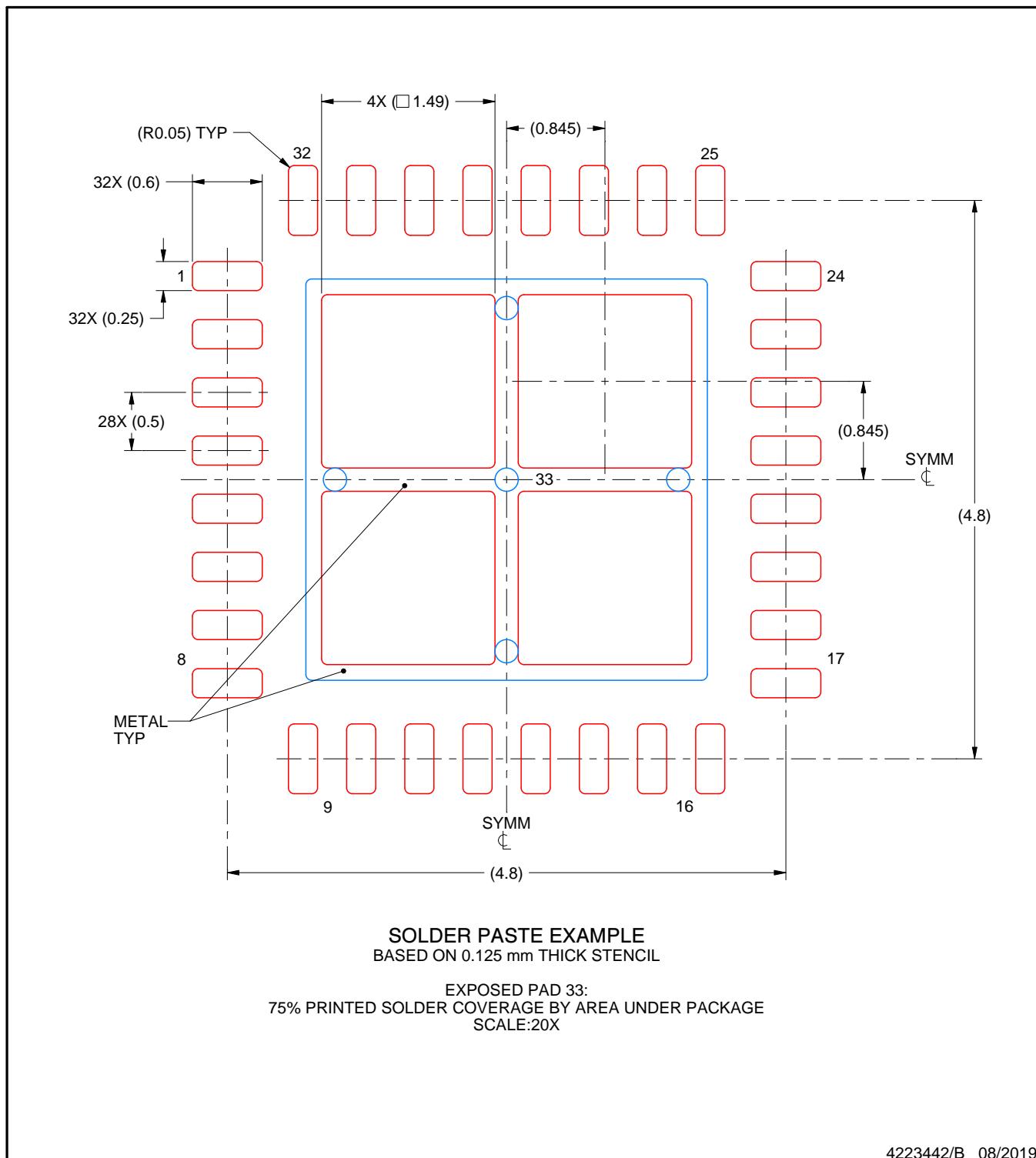

## 4 ピン構成および機能

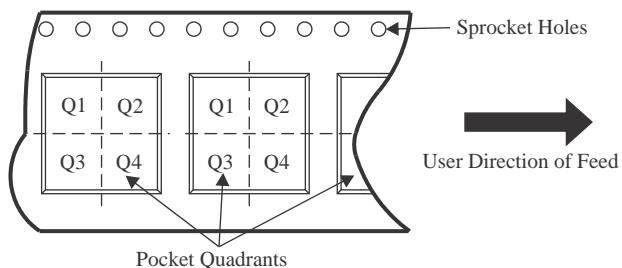

図 4-1. RHB パッケージ、32 ピン、5mm x 5mm VQFN (上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名称 | タイプ       | 説明                                                             |

|----|----------|-----------|----------------------------------------------------------------|

| 1  | AIN1P    | アナログ入力    | チャネル 1 の正入力。                                                   |

| 2  | AIN1N    | アナログ入力    | チャネル 1 の負入力。                                                   |

| 3  | AIN2P    | アナログ入力    | チャネル 2 の正入力。                                                   |

| 4  | AIN2N    | アナログ入力    | チャネル 2 の負入力。                                                   |

| 5  | CAPP     | アナログ内部    | PGA の正コンデンサ。CAPP と CAPN の間に、10nF の C0G コンデンサを接続します。            |

| 6  | CAPN     | アナログ内部    | PGA 負電圧コンデンサ。CAPP と CAPN の間に、10nF の C0G コンデンサを接続します。           |

| 7  | CAPBP    | アナログ内部    | バッファの正のコンデンサ。47nF の C0G コンデンサを AVSS に接続します。                    |

| 8  | CAPBN    | アナログ内部    | バッファの負のコンデンサ。47nF の C0G コンデンサを AVSS に接続します。                    |

| 9  | CAPC     | アナログ内部    | チャージポンプ コンデンサ。4.7nF、最低 10V 定格のコンデンサを AGND に接続します。              |

| 10 | AVSS     | アナログ電源    | PGA 負のアナログ電源。詳細については、 <a href="#">アナログ電源</a> セクションを参照してください。   |

| 11 | AVDD1    | アナログ電源    | PGA の正アナログ電源。詳細については、 <a href="#">アナログ電源</a> セクションを参照してください。   |

| 12 | AVDD2    | アナログ電源    | 変調器のアナログ電源。詳細については、 <a href="#">アナログ電源</a> セクションを参照してください。     |

| 13 | AGND     | アナログ グランド | アナログ グランド。                                                     |

| 14 | CAPI     | アナログ内部    | 入力バイアス コンデンサ。100nF のセラミックコンデンサを AGND に接続します。                   |

| 15 | GPIO0    | デジタル I/O  | 汎用 I/O。                                                        |

| 16 | GPIO1    | デジタル I/O  | 汎用 I/O。                                                        |

| 17 | CAPD     | アナログ出力    | デジタル低ドロップアウト レギュレータ (LDO) 出力。220nF のセラミックコンデンサを DGND に接続します。   |

| 18 | DGND     | グランド      | デジタル グランド。                                                     |

| 19 | IOVDD    | デジタル電源    | デジタル I/O 電源。詳細については、 <a href="#">IOVDD の電源</a> セクションを参照してください。 |

表 4-1. ピンの機能 (続き)

| ピン       |                 | タイプ                                                                    | 説明                                                             |

|----------|-----------------|------------------------------------------------------------------------|----------------------------------------------------------------|

| 番号       | 名称              |                                                                        |                                                                |

| 20       | CLK             | デジタル入力                                                                 | ADC クロック入力。                                                    |

| 21       | $\overline{CS}$ | デジタル入力                                                                 | シリアル インターフェース選択、アクティブ Low。                                     |

| 22       | SCLK            | デジタル入力                                                                 | シリアル インターフェイス クロック。                                            |

| 23       | DIN             | デジタル入力                                                                 | シリアル インターフェースのデータ入力。                                           |

| 24       | DOUT            | デジタル出力                                                                 | シリアル インターフェイスのデータ出力。                                           |

| 25       | DRDY            | デジタル出力                                                                 | データ準備完了、アクティブ Low。                                             |

| 26       | SYNC            | デジタル入力                                                                 | ADC 同期、アクティブ High。                                             |

| 27       | RESET           | デジタル入力                                                                 | ADC リセット、アクティブ Low。                                            |

| 28       | PWDN            | デジタル入力                                                                 | ADC パワーダウン、アクティブ Low。                                          |

| 29       | REFN            | アナログ入力                                                                 | 負のリファレンス入力。詳細については、 <a href="#">電圧リファレンス入力</a> セクションを参照してください。 |

| 30       | REFP            | アナログ入力                                                                 | 正のリファレンス入力。詳細については、 <a href="#">電圧リファレンス入力</a> セクションを参照してください。 |

| 31       | CAPR            | アナログ内部                                                                 | リファレンス バイアス コンデンサ。100nF のセラミックコンデンサを AVSS に接続します。              |

| 32       | AVSS            | アナログ電源                                                                 | PGA 負電源。                                                       |

| サーマル パッド |                 | サーマル パッドを AVSS に接続します。底面側の部品を実装する場合、プリント基板 (PCB) ランドに配置するサーマル ビアは任意です。 |                                                                |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|          |                                                     | 最小値        | 最大値         | 単位 |

|----------|-----------------------------------------------------|------------|-------------|----|

| 電源電圧     | AVDD1 から AVSS へ                                     | -0.3       | 5.5         | V  |

|          | AVSS から AGND へ                                      | -2.8       | 0.3         |    |

|          | AVDD2 から AGND へ                                     | -0.3       | 5.5         |    |

|          | AVDD2 から AVSS へ                                     | -0.3       | 5.5         |    |

|          | IOVDD から DGND へ                                     | -0.3       | 3.9         |    |

|          | IOVDD から DGND へ (IOVDD は CAPD に接続)                  | -0.3       | 2.2         |    |

| グランド     | AGND から DGND へ                                      | -0.3       | 0.3         | V  |

| アナログ入力電圧 | AIN1P, AIN1N, AIN2P, AIN2N, REFP, REFN              | AVSS - 0.3 | AVDD1 + 0.3 | V  |

| デジタル入力電圧 | CLK, DIN, SCLK, CS, GPIO0, GPIO1, SYNC, RESET, PWDN | DGND - 0.3 | IOVDD + 0.3 | V  |

| 入力電流     | 連続的、任意のデジタルまたはアナログピン <sup>(2)</sup>                 | -10        | 10          | mA |

| 温度       | 接合部、T <sub>J</sub>                                  |            | 150         | °C |

|          | 保存、T <sub>stg</sub>                                 | -60        | 150         |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件や、推奨動作条件を超えたその他の条件でデバイスが動作することを保証するものではありません。推奨動作条件を一時的に外れていても、絶対最大定格の範囲内であればデバイスが損傷しない場合もありますが、完全には動作しない可能性があります。これは、デバイスの信頼性、機能、性能に影響し、デバイスの寿命を短くすることにつながります。

- (2) アナログ入力ピン AIN1P, AIN1N, AIN2P, AIN2N, REFP, REFN は、AVDD1 と AVSS にダイオードでクランプされています。アナログ入力電圧が AVDD1 + 0.3V または AVSS - 0.3V を超えた場合、入力電流を 10mA に制限します。デジタル入力ピンは、IOVDD と DGND にクランプされます。デジタル入力電圧が IOVDD + 0.3V または DGND - 0.3V を超える場合、入力電流を制限します。

### 5.2 ESD 定格

|                    |      |                                                      | 値    | 単位 |

|--------------------|------|------------------------------------------------------|------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> | 2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、JEDEC JESD22-C101 準拠 <sup>(2)</sup>  | 1000 |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

動作時周囲温度範囲内 (特に記述のない限り)

|                 |                 |                                                         | 最小値        | 公称値                     | 最大値  | 単位 |

|-----------------|-----------------|---------------------------------------------------------|------------|-------------------------|------|----|

| <b>電源</b>       |                 |                                                         |            |                         |      |    |

| アナログ電源          | AVDD1 から AVSS へ | AVDD1 から AVSS へ                                         | 3          | 5.25                    | 5.25 | V  |

|                 |                 | AVDD1 から AGND へ                                         | 2.375      |                         |      | V  |

|                 |                 | AVSS から AGND へ                                          | -2.625     | 0                       | 0    |    |

|                 |                 | AVDD2 から AGND へ                                         | 2.375      | 5.25                    | 5.25 | V  |

|                 | AVDD2 から AVSS へ |                                                         |            | 5.25                    | 5.25 |    |

| デジタル電源          | IOVDD から DGND へ | IOVDD から DGND へ                                         | 2.7        | 3.6                     | 3.6  | V  |

|                 |                 | CAPD に接続された IOVDD                                       | 1.65       | 1.95                    | 1.95 |    |

| <b>アナログ入力</b>   |                 |                                                         |            |                         |      |    |

| V <sub>IN</sub> | 差動入力電圧          | V <sub>IN</sub> = V <sub>AINP</sub> - V <sub>AINN</sub> |            | ±V <sub>REF</sub> / ゲイン |      | V  |

| 絶対入力電圧          | バッファ動作          |                                                         | AVSS + 0.1 | AVDD1 - 0.1             |      | V  |

|                 | PGA動作           |                                                         | AVSS + 1.1 | AVDD1 - 0.85            |      |    |

## 5.3 推奨動作条件 (続き)

動作時周囲温度範囲内 (特に記述のない限り)

|                     |                                 |     | 最小値         | 公称値   | 最大値          | 単位  |

|---------------------|---------------------------------|-----|-------------|-------|--------------|-----|

| 絶対出力電圧              | パッファ動作                          |     | AVSS + 0.1  |       | AVDD1 - 0.1  | V   |

|                     | PGA動作                           |     | AVSS + 0.15 |       | AVDD1 - 0.15 |     |

| 較正範囲 <sup>(1)</sup> |                                 |     |             |       | 6%           | FSR |

| <b>電圧リファレンス入力</b>   |                                 |     |             |       |              |     |

| $V_{REF}$           | $V_{REF} = V_{REFP} - V_{REFN}$ |     | 2.4         | 2.5   | 2.6          | V   |

| $V_{REFN}$          | 負のリファレンス入力                      |     | AVSS - 0.05 |       |              | V   |

| $V_{REFP}$          | 正のリファレンス入力                      |     | AVDD1 + 0.1 |       |              | V   |

| <b>デジタル入力</b>       |                                 |     |             |       |              |     |

| $V_{INL}$           | Low レベル入力電圧                     |     | 0.2 × IOVDD |       |              | V   |

| $V_{INH}$           | High レベル入力電圧                    |     | 0.8 × IOVDD |       |              | V   |

| $f_{CLK}$           | クロック入力周波数                       |     | 3           | 4.096 | 4.15         | MHz |

| <b>温度</b>           |                                 |     |             |       |              |     |

| $T_A$               | 周囲温度                            | 動作中 | -50         |       | 85           | °C  |

|                     |                                 | 仕様  | -40         |       | 85           |     |

(1) 較正範囲は、オフセット補正とゲイン誤差補正の合計です。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | ADS1288    | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | RHB (VQFN) |      |

|                      |                     | 32 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 30         | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 19.4       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 10.9       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.2        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 10.8       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 1.8        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

## 5.5 電気的特性

–40°C～+85°C にわたる最小および最大仕様、典型値は 25°C でのものです。すべての仕様は、AVDD1 = 5V、AVDD2 = 2.5V～5V、AVSS = 0V、IOVDD = 1.8V、V<sub>REFP</sub> = 2.5V、V<sub>REFN</sub> = 0V、V<sub>CM</sub> = 2.5V、PGA ゲイン = 1、R<sub>S</sub> = 0Ω、f<sub>CLK</sub> = 4.096MHz、f<sub>DATA</sub> = 500SPS の条件で測定されています (特記がない限り)

| パラメータ                | テスト条件               |                                                                             | 最小値                 | 標準値                                           | 最大値          | 単位            |

|----------------------|---------------------|-----------------------------------------------------------------------------|---------------------|-----------------------------------------------|--------------|---------------|

| <b>アナログ入力</b>        |                     |                                                                             |                     |                                               |              |               |

|                      | 入力マルチブレクサのオン抵抗      | 入力 1 と入力 2 の交差接続                                                            |                     | 60                                            |              | Ω             |

| <b>PGA 動作</b>        |                     |                                                                             |                     |                                               |              |               |

| I <sub>B</sub>       | 入力電流                |                                                                             |                     | 45                                            |              | nA            |

| I <sub>os</sub>      | 入力オフセット電流           |                                                                             |                     | ±3                                            |              | nA            |

|                      | ゲイン                 |                                                                             |                     | 1, 2, 4, 8, 16, 32, 64                        |              | V/V           |

| e <sub>n</sub> -PGA  | 入力電圧ノイズ密度           | PGA ゲイン = 16                                                                |                     | 20                                            |              | nV/√Hz        |

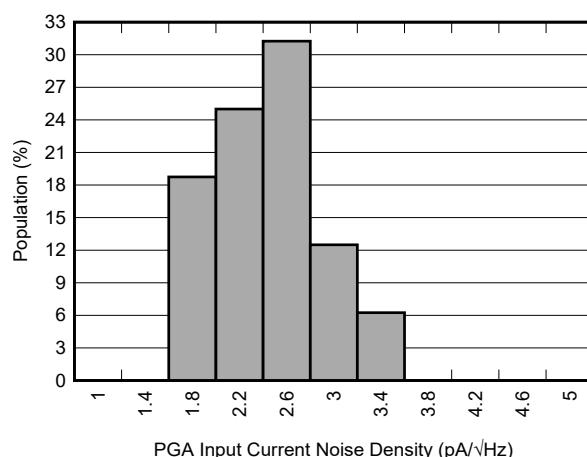

| i <sub>n</sub> -PGA  | 入力電流ノイズ密度           | 差動                                                                          |                     | 2.5                                           |              | pA/√Hz        |

|                      | アンチエイリアス フィルタ周波数    |                                                                             |                     | 30                                            |              | kHz           |

| <b>バッファ動作</b>        |                     |                                                                             |                     |                                               |              |               |

| I <sub>B</sub>       | 入力電流                | V <sub>IN</sub> = 2.5V                                                      |                     | ±0.3                                          |              | μA            |

| <b>DC 特性</b>         |                     |                                                                             |                     |                                               |              |               |

| e <sub>n</sub>       | ノイズ                 |                                                                             |                     | 詳細については、 <a href="#">ノイズ性能</a> セクションを参照してください |              |               |

| V <sub>OS</sub>      | オフセット誤差             | PGA 動作                                                                      |                     | –350/ ゲイン – 10                                | ±30/ ゲイン + 5 | 350/ ゲイン + 10 |

|                      |                     | バッファ動作                                                                      |                     | –600                                          | ±50          | 600           |

|                      |                     | キャリブレーション後                                                                  |                     |                                               | ±1           |               |

|                      | オフセット誤差のドリフト        | PGA 動作                                                                      |                     |                                               | 0.5/ ゲイン     |               |

|                      |                     | バッファ動作                                                                      |                     |                                               | 1            | μV/°C         |

|                      | ゲイン誤差               | PGA 動作、ゲイン = 1                                                              |                     | –0.05%                                        | ±0.02%       | 0.05%         |

|                      |                     | キャリブレーション後                                                                  |                     |                                               | 2            | ppm           |

|                      |                     | バッファ動作                                                                      |                     | –0.07%                                        | ±0.05%       | 0.07%         |

|                      | ゲインマッチング            | PGA ゲイン = 1 を基準                                                             |                     | –0.2%                                         | ±0.06%       | 0.2%          |

|                      |                     | すべての PGA ゲイン                                                                |                     |                                               | 2            | ppm/°C        |

| CMRR                 | 同相除去比               | f = 60Hz                                                                    |                     | 104                                           | 120          | dB            |

| PSRR                 | 電源除去比               | AVDD2                                                                       | DC 時                | 80                                            | 95           |               |

|                      |                     | AVSS、AVDD1                                                                  | DC 時                | 85                                            | 110          |               |

|                      |                     | IOVDD                                                                       | DC 時                | 100                                           | 120          |               |

| <b>AC 特性</b>         |                     |                                                                             |                     |                                               |              |               |

| e <sub>n</sub> -MOD  | 変調器電圧ノイズ密度          |                                                                             |                     | 100                                           |              | nV/√Hz        |

| THD                  | 全高調波歪               | AVDD1 = 3.3V、AVSS = 0V、f <sub>IN</sub> = 31.25Hz、V <sub>IN</sub> = –0.5dBFS | バッファ動作              |                                               | –124         | –117          |

|                      |                     |                                                                             | PGA ゲイン = 2         |                                               | –122         |               |

|                      |                     |                                                                             | PGA ゲイン = 4         |                                               | –124         | –116          |

|                      |                     |                                                                             | PGA ゲイン = 8         |                                               | –125         |               |

|                      |                     |                                                                             | PGA ゲイン = 16        |                                               | –123         | –115          |

|                      |                     |                                                                             | PGA ゲイン = 32 および 64 |                                               | –124         |               |

|                      |                     | AVDD1 = 5V、AVSS = 0V、f <sub>IN</sub> = 31.25Hz、V <sub>IN</sub> = –0.5dBFS   | バッファ動作              |                                               | –123         | –117          |

|                      |                     |                                                                             | PGA ゲイン = 1         |                                               | –121         | –115          |

|                      |                     |                                                                             | PGA ゲイン = 2         |                                               | –124         |               |

|                      |                     |                                                                             | PGA ゲイン = 4         |                                               | –125         | –115          |

| SFDR                 | スプリアスフリー ダイナミック レンジ | f <sub>IN</sub> = 31.25Hz、V <sub>IN</sub> = –0.5dBFS                        |                     | 115                                           |              | dB            |

|                      | クロストーク              | f <sub>IN</sub> = 31.25Hz、V <sub>IN</sub> = –0.5dBFS                        |                     | –140                                          |              | dB            |

| <b>電圧リファレンス入力</b>    |                     |                                                                             |                     |                                               |              |               |

|                      | 基準入力電流              |                                                                             |                     | 80                                            |              | μA/V          |

| <b>FIR デジタル フィルタ</b> |                     |                                                                             |                     |                                               |              |               |

| f <sub>DATA</sub>    | データ レート             |                                                                             |                     | 125                                           | 2000         | SPS           |

## 5.5 電気的特性 (続き)

-40°C～+85°C にわたる最小および最大仕様、典型値は 25°C でのものです。すべての仕様は、AVDD1 = 5V、AVDD2 = 2.5V～5V、AVSS = 0V、IOVDD = 1.8V、VREFP = 2.5V、VREFN = 0V、VCM = 2.5V、PGA ゲイン = 1、RS = 0Ω、fCLK = 4.096MHz、fDATA = 500SPS の条件で測定されています (特記がない限り)

| パラメータ                                     | テスト条件               | 最小値                          | 標準値         | 最大値           | 単位   |    |

|-------------------------------------------|---------------------|------------------------------|-------------|---------------|------|----|

| バス バンド リップル                               |                     | -0.003                       | 0.003       | 0.003         | dB   |    |

| バスバンド (-0.01 dB)                          |                     | 0.375 × fDATA                |             | 0.375 × fDATA | Hz   |    |

| 帯域幅 (-3dB)                                |                     | 0.413 × fDATA                |             | 0.413 × fDATA | Hz   |    |

| ストップ バンド                                  |                     | 0.5 × fDATA                  |             | 0.5 × fDATA   | Hz   |    |

| ストップ バンド減衰 <sup>(1)</sup>                 |                     | 135                          |             | 135           | dB   |    |

| 群遅延                                       | dc での最小位相フィルタ       | 5 / fDATA                    |             | 5 / fDATA     | s    |    |

|                                           | 線形位相フィルタ            | 31 / fDATA                   |             | 31 / fDATA    |      |    |

| セトリング タイム (レイテンシ)                         | 最小位相フィルタ            | 62 / fDATA                   |             | 62 / fDATA    | s    |    |

|                                           | 線形位相フィルタ            | 62 / fDATA                   |             | 62 / fDATA    |      |    |

| <b>IIR デジタル フィルタ</b>                      |                     |                              |             |               |      |    |

| ハイパス コーナー周波数                              |                     | 0.1                          |             | 10            | Hz   |    |

| <b>サンプル レート コンバータ</b>                     |                     |                              |             |               |      |    |

| 周波数補償範囲                                   |                     | -244                         |             | 244           | ppm  |    |

| 分解能                                       |                     | 7.45                         |             | 7.45          | ppb  |    |

| <b>デジタル入出力</b>                            |                     |                              |             |               |      |    |

| V <sub>OH</sub>                           | High レベル出力電圧        | I <sub>OH</sub> = 1mA        | 0.8 × IOVDD |               | V    |    |

| V <sub>OL</sub>                           | Low レベル出力電圧         | I <sub>OL</sub> = -1mA       |             | 0.2 × IOVDD   | V    |    |

| I <sub>lk</sub>                           | 入力リーケージ             |                              | -1          | 1             | μA   |    |

| <b>電源</b>                                 |                     |                              |             |               |      |    |

| I <sub>AVDD1</sub> 、<br>I <sub>AVSS</sub> | AVDD1、AVSS 電流       | AVDD1 = 3.3 V                | PGA 動作      | 0.85          | 1.1  | mA |

|                                           |                     |                              | バッファ動作      | 0.25          | 0.45 |    |

|                                           |                     | AVDD1 = 5 V                  | PGA 動作      | 0.85          | 1.1  |    |

|                                           |                     |                              | バッファ動作      | 0.25          | 0.45 |    |

| パワーダウン モード                                |                     |                              |             | 1             | 5    | μA |

| I <sub>AVDD2</sub>                        | AVDD2 電流            | AVDD2 = 2.5 V                |             | 0.7           | 0.85 | mA |

|                                           |                     | パワーダウン モード                   |             | 1             | 5    |    |

| I <sub>IOVDD</sub>                        | IOVDD 電流            |                              |             | 0.24          | 0.4  | mA |

|                                           |                     | パワーダウン モード                   |             | 1             | 10   |    |

|                                           |                     | スタンバイ モード                    |             | 200           |      |    |

| IOVDD 追加電流                                |                     |                              |             | 0.6           |      | mA |

| P <sub>d</sub>                            | 電力散逸 <sup>(2)</sup> | AVDD1 = 3.3V<br>AVDD2 = 2.5V | PGA 動作      | 5.0           | 6.5  | mW |

|                                           |                     |                              | バッファ動作      | 3.0           | 4.2  |    |

|                                           |                     | AVDD1 = 5V<br>AVDD2 = 2.5V   | PGA 動作      | 6.4           | 8.3  |    |

|                                           |                     |                              | バッファ動作      | 3.4           | 5.1  |    |

(1)  $N \times 16 \text{ kHz} \pm f_{\text{DATA}} / 2$  ( $N = 1, 2, 3, \dots$ ) の入力周波数は、チヨッパ クロックと相互変調を起こします。これらの周波数では、ストップ バンド減衰 = -90dBFS (標準値) です。

(2) 電圧リファレンス入力やサンプル レート コンバータの動作で消費される電流は除きます。サンプル レート コンバータ動作時の電圧リファレンス入力電流および IOVDD 供給電流を参照してください。

## 5.6 タイミング要件 : $1.65V \leq IOVDD \leq 1.95V$ および $2.7V \leq IOVDD \leq 3.6V$

動作時周囲温度範囲内 (特に記述のない限り)

|                      |                                                                    | 最小値 | 公称値    | 最大値 | 単位              |

|----------------------|--------------------------------------------------------------------|-----|--------|-----|-----------------|

| <b>クロック</b>          |                                                                    |     |        |     |                 |

| $t_{c(CLK)}$         | CLK 周期                                                             | 241 | 244.14 | 332 | ns              |

| $t_{w(CLKH)}$        | パルス幅、CLK high                                                      | 110 |        |     | ns              |

| $t_{w(CLKL)}$        | パルス幅、CLK low                                                       | 110 |        |     | ns              |

| <b>シリアル インターフェイス</b> |                                                                    |     |        |     |                 |

| $t_{w(CSH)}$         | パルス幅、 $\overline{CS}$ High                                         | 20  |        |     | ns              |

| $t_{d(CSSC)}$        | 遅延時間、 $\overline{CS}$ 立ち下がりエッジから最初の SCLK 立ち上がりエッジまで                | 20  |        |     | ns              |

| $t_{c(SCLK)}$        | SCLK 周期                                                            | 120 |        |     | ns              |

| $t_{w(SCH)}$         | パルス幅、SCLK high                                                     | 50  |        |     | ns              |

| $t_{w(SCL)}$         | パルス幅、SCLK low                                                      | 50  |        |     | ns              |

| $t_{su(DI)}$         | セットアップ時間、DIN 有効から SCLK 立ち下がりエッジまでの時間                               | 10  |        |     | ns              |

| $t_{h(DI)}$          | ホールド時間、SCLK の立ち上がりエッジの後も、DIN が有効であり続ける必要がある時間                      | 10  |        |     | ns              |

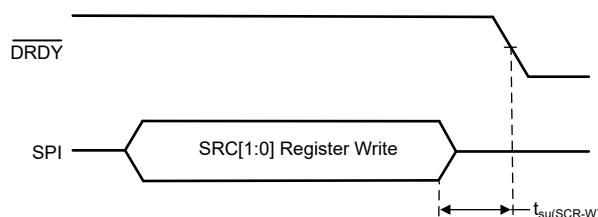

| $t_{su(SRC-W)}$      | セットアップ時間、 $\overline{DRDY}$ の立ち下がりエッジの前に、SRC[1:0] レジスタの書き込みが完了する時間 | 256 |        |     | $1 / f_{(CLK)}$ |

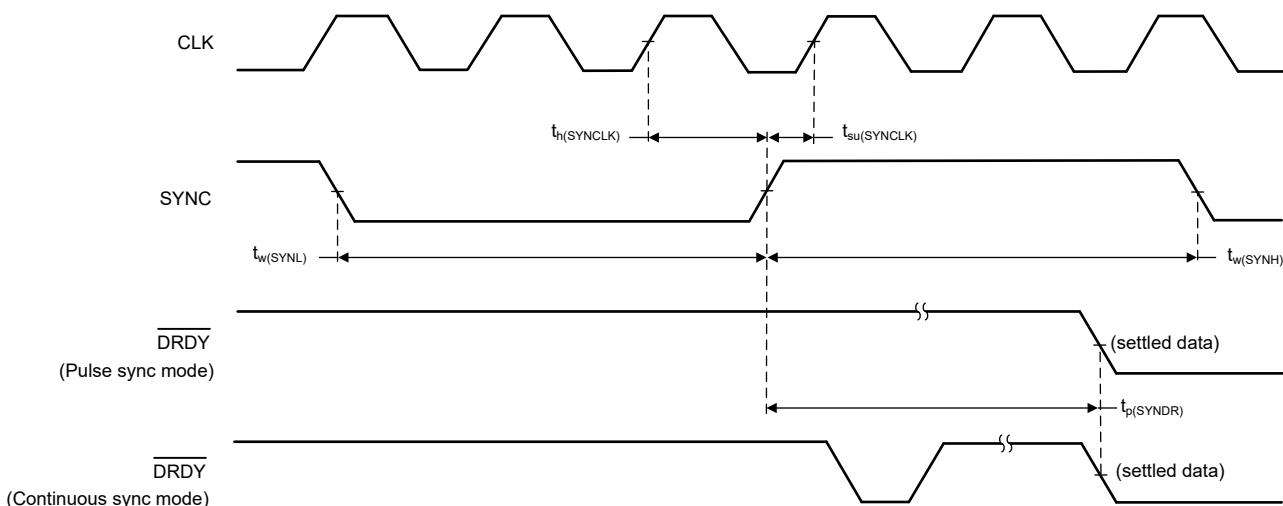

| <b>SYNC</b>          |                                                                    |     |        |     |                 |

| $t_{w(SYNL)}$        | パルス幅、SYNC low                                                      | 2   |        |     | $1 / f_{(CLK)}$ |

| $t_{w(SYNH)}$        | パルス幅、SYNC high                                                     | 2   |        |     | $1 / f_{(CLK)}$ |

| $t_{su(SYNCLK)}$     | セットアップ時間、CLK の立ち上がりエッジの前に SYNC が High になっている時間                     | 10  |        |     | ns              |

| $t_{h(SYNCLK)}$      | ホールド時間、CLK の立ち上がりエッジの後 SYNC が High のまま保持されている時間                    | 10  |        |     | ns              |

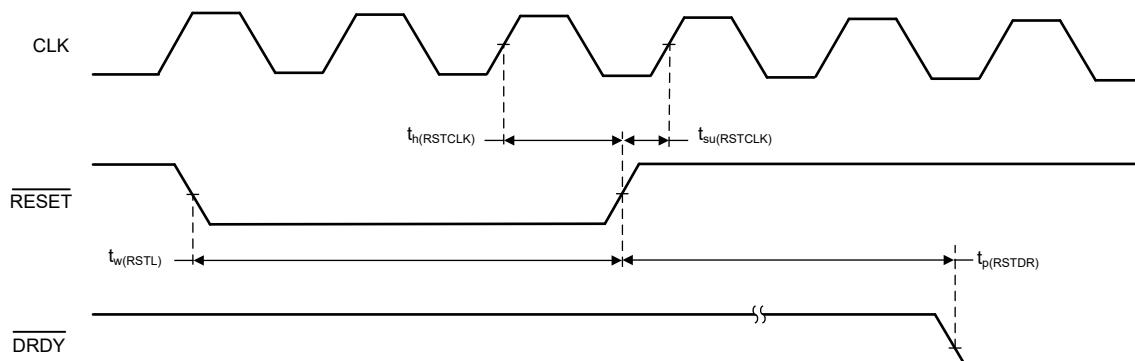

| <b>RESET</b>         |                                                                    |     |        |     |                 |

| $t_{w(RSTL)}$        | パルス幅、 $\overline{RESET}$ Low                                       | 2   |        |     | $1 / f_{(CLK)}$ |

| $t_{su(RSTCLK)}$     | セットアップ時間、CLK の立ち上がりエッジの前に、 $\overline{RESET}$ が High になっている時間      | 10  |        |     | ns              |

| $t_{h(RSTCLK)}$      | ホールド時間、CLK の立ち上がりエッジの後 $\overline{RESET}$ が High のまま保持されている時間      | 10  |        |     | ns              |

## 5.7 スイッチング特性: $1.65V \leq IOVDD \leq 1.95V$ および $2.7V \leq IOVDD \leq 3.6V$

動作時周囲温度範囲全体、 $C_{LOAD} = 20pF$  (特に記述のない限り)

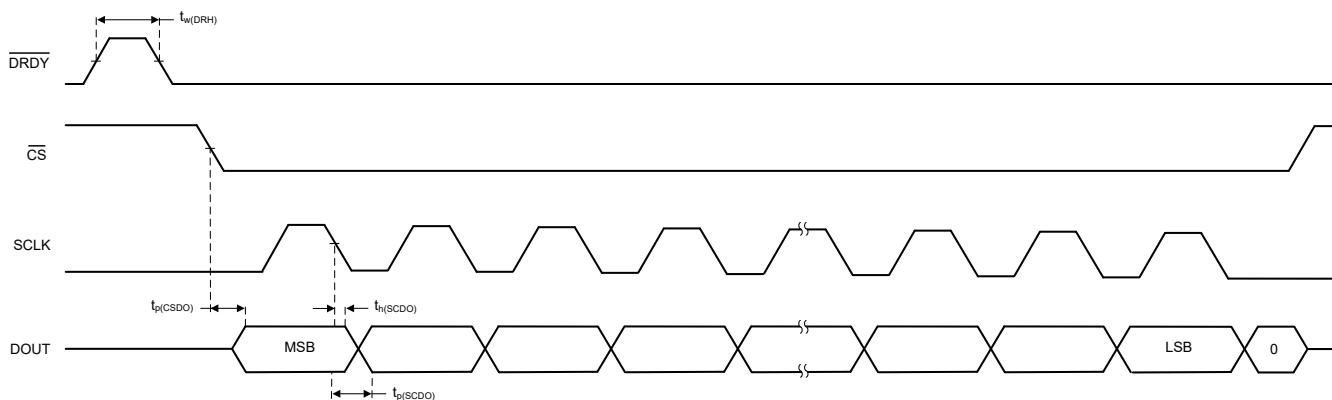

| パラメータ                |                                                                    | 最小値     | 標準値                                   | 最大値 | 単位              |

|----------------------|--------------------------------------------------------------------|---------|---------------------------------------|-----|-----------------|

| <b>シリアル インターフェイス</b> |                                                                    |         |                                       |     |                 |

| $t_{w(DRH)}$         | パルス幅、 $\overline{DRDY}$ High                                       |         |                                       | 8   | $1 / f_{(CLK)}$ |

| $t_{p(CSD0)}$        | 伝搬遅延時間、 $\overline{CS}$ 立ち下がりエッジから DOUT 駆動状態まで                     |         |                                       | 50  | ns              |

| $t_{p(SCDO)}$        | 伝搬遅延時間、SCLK の立ち下がりエッジから新しい DOUT が有効になるまでの時間                        |         |                                       | 50  | ns              |

| $t_{h(SCDO)}$        | 伝搬遅延時間、SCLK 立ち下がりエッジから DOUT 無効まで                                   | 5       |                                       |     | ns              |

| <b>SYNC</b>          |                                                                    |         |                                       |     |                 |

| $t_{p(SYNDR)}$       | 伝搬遅延時間、SYNC 立ち上がりエッジから、有効なデータを示す $\overline{DRDY}$ 立ち下がりエッジまで      |         | $62.98145 / f_{DATA} + 930 / f_{CLK}$ |     | s               |

| <b>RESET</b>         |                                                                    |         |                                       |     |                 |

| $t_{p(RSTDRL)}$      | 伝搬遅延時間、 $\overline{RESET}$ 立ち下がりエッジから $\overline{DRDY}$ 立ち上がりエッジまで | 516,874 |                                       |     | $1 / f_{CLK}$   |

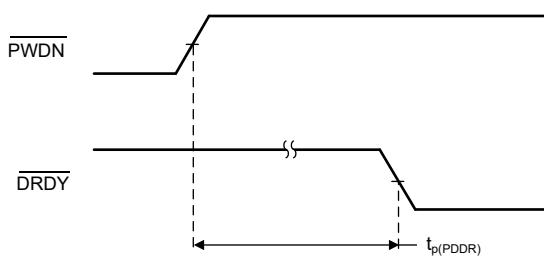

| <b>PWDN</b>          |                                                                    |         |                                       |     |                 |

| $t_{p(PDDR)}$        | 伝搬遅延時間、 $\overline{PWDN}$ 立ち下がりエッジから $\overline{DRDY}$ 立ち上がりエッジまで  |         | $62.98145 / f_{DATA} + 946 / f_{CLK}$ |     | s               |

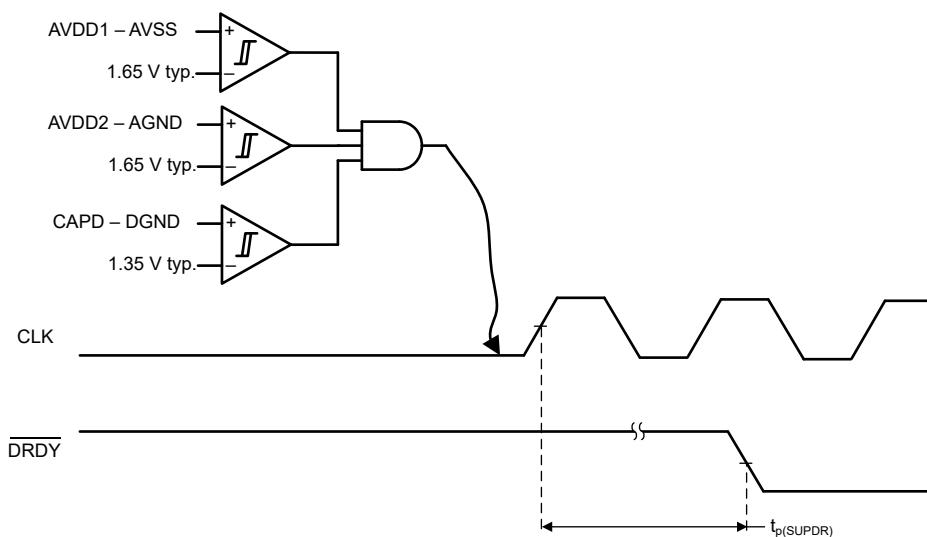

| <b>電源オン</b>          |                                                                    |         |                                       |     |                 |

| $t_{p(SUPDR)}$       | 伝搬遅延時間、電源と CLK が最初の $\overline{DRDY}$ パルスに印加されます                   | 650,000 |                                       |     | $1 / f_{CLK}$   |

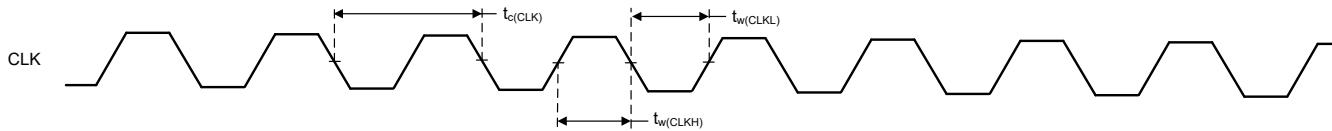

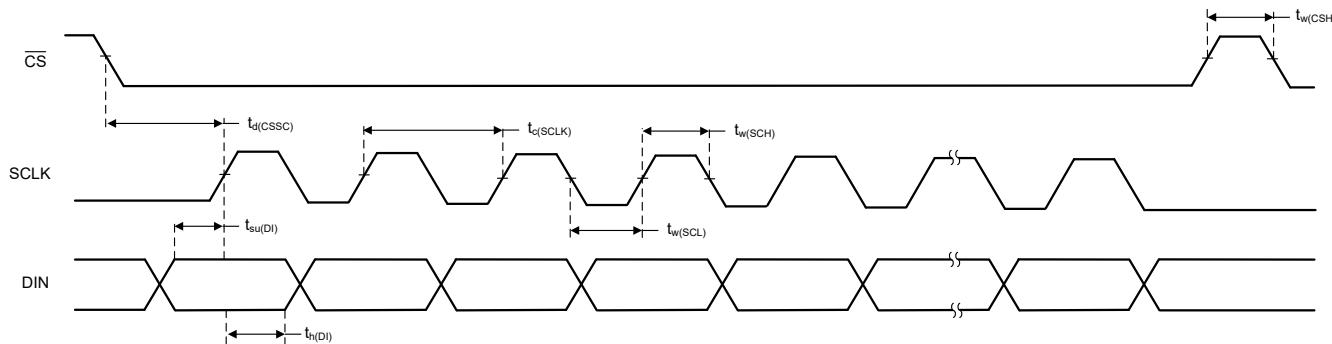

## 5.8 タイミング図

図 5-1. クロックのタイミング要件

図 5-2. シリアルインターフェイスのタイミング要件

図 5-3. シリアルインターフェイスのスイッチング特性

図 5-4. SYNC のタイミング要件およびスイッチング特性

図 5-5.  $\overline{\text{RESET}}$  のタイミング要件およびスイッチング特性

図 5-6.  $\overline{\text{PWDN}}$  のスイッ칭特性

図 5-7. サンプルレートコンバータ レジスタ - 書き込みのタイミング要件

図 5-8. パワーアップ時のスイッ칭特性

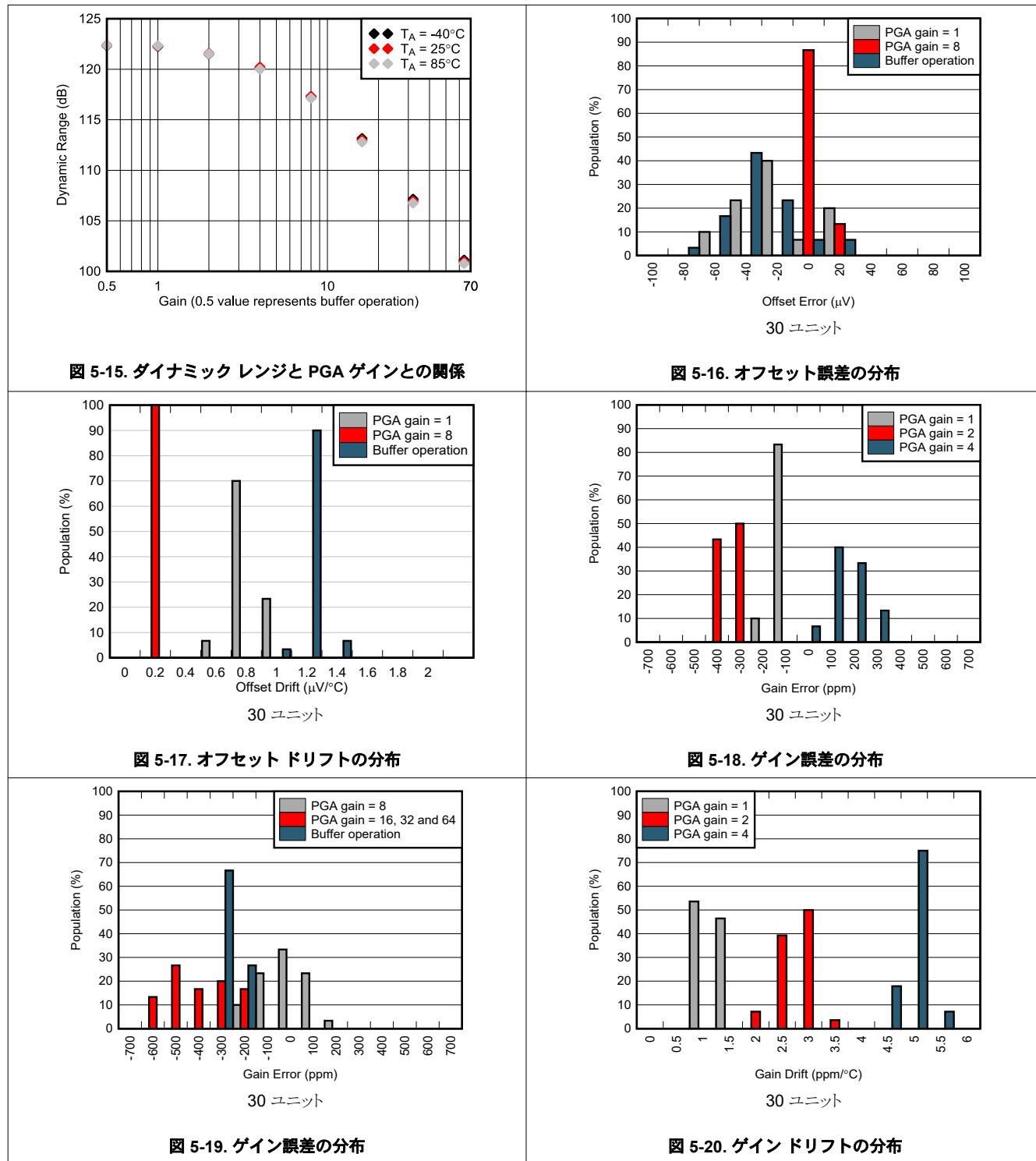

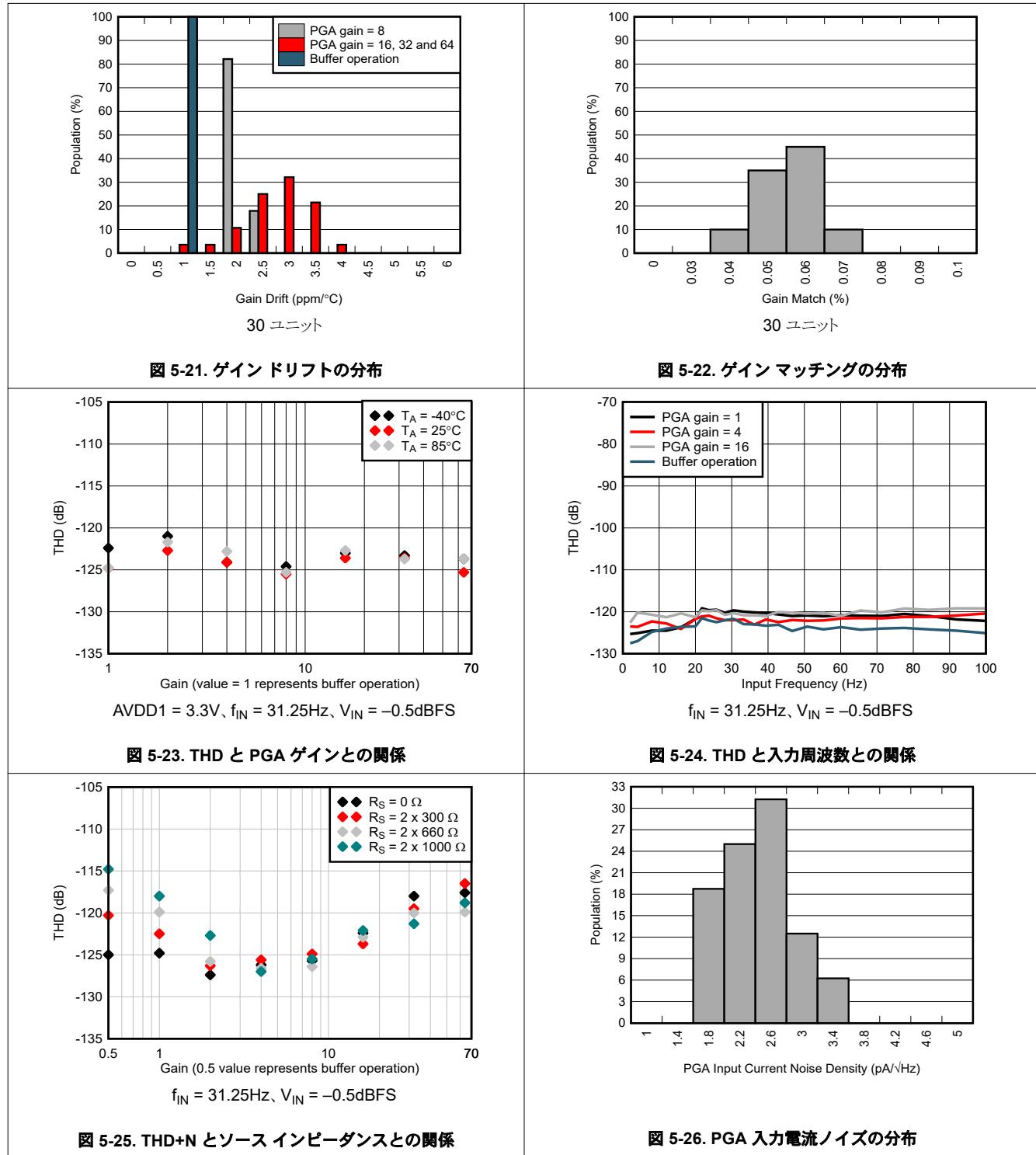

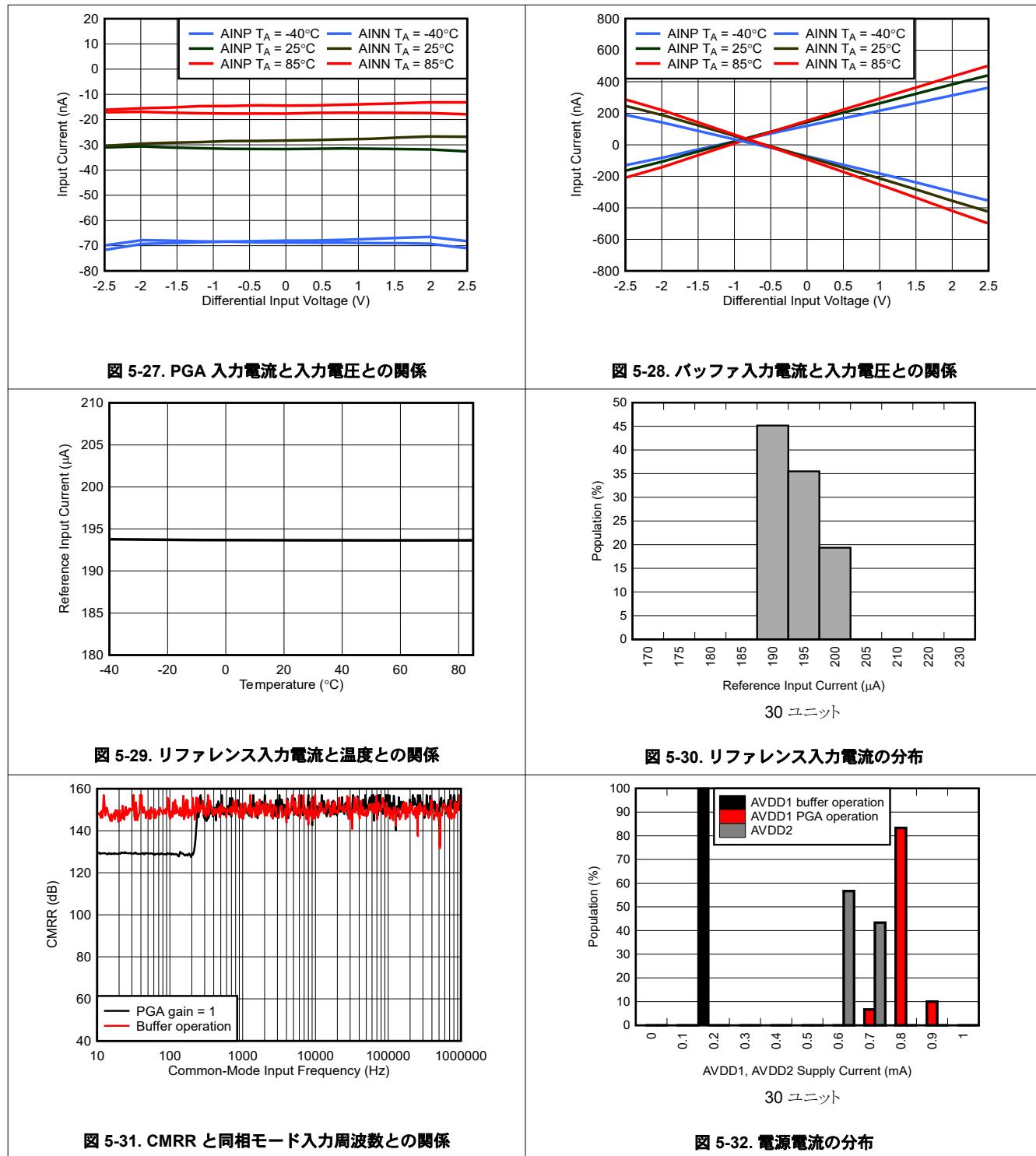

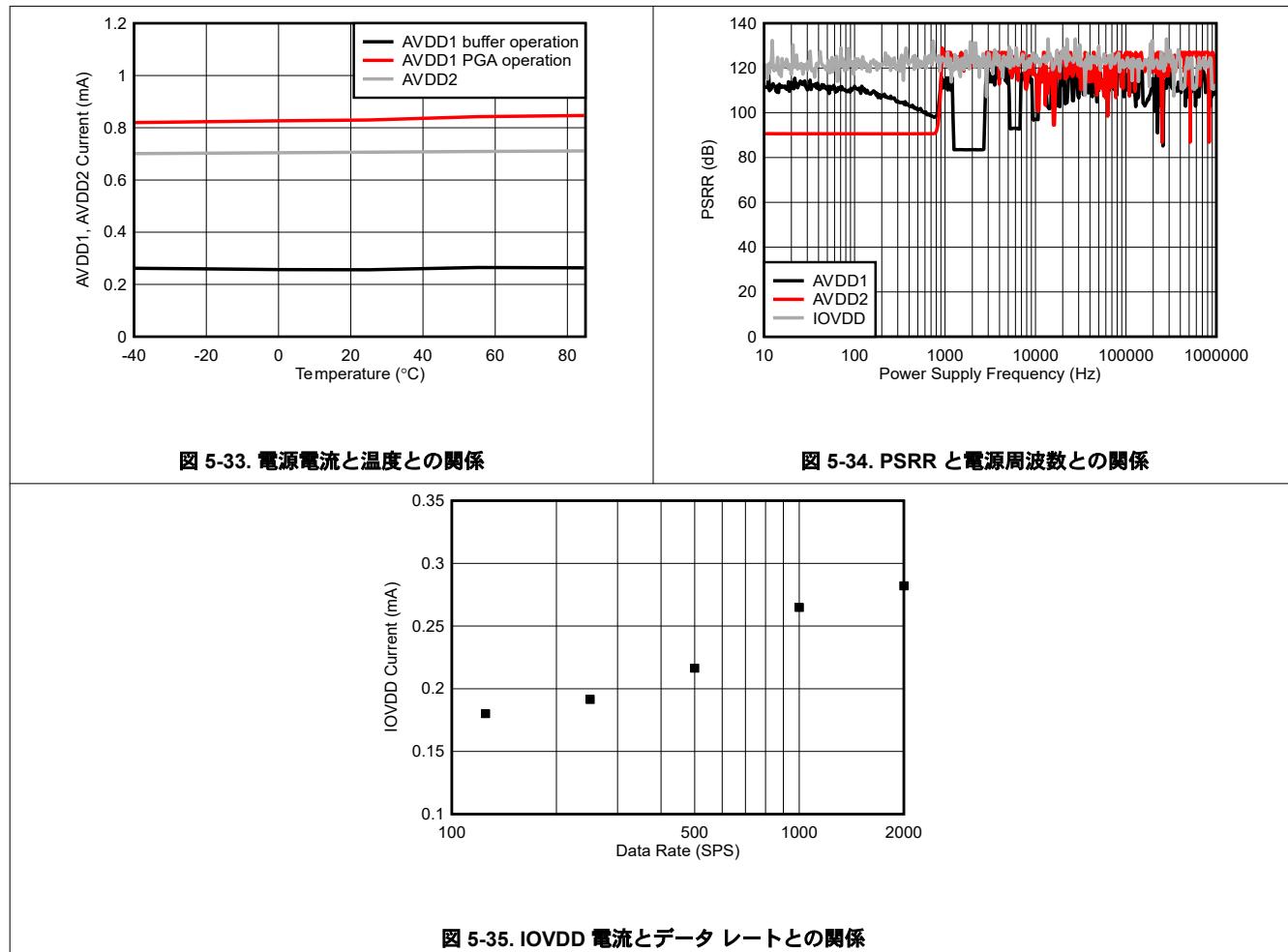

## 5.9 代表的特性

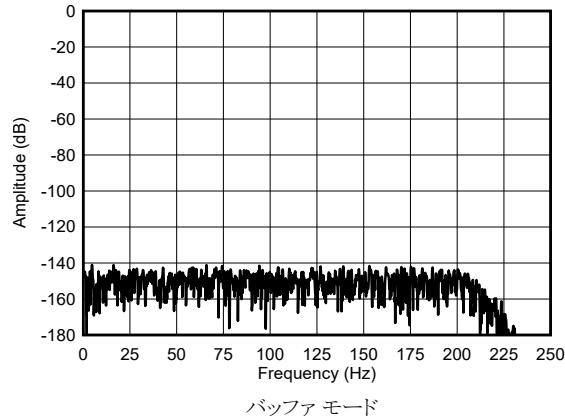

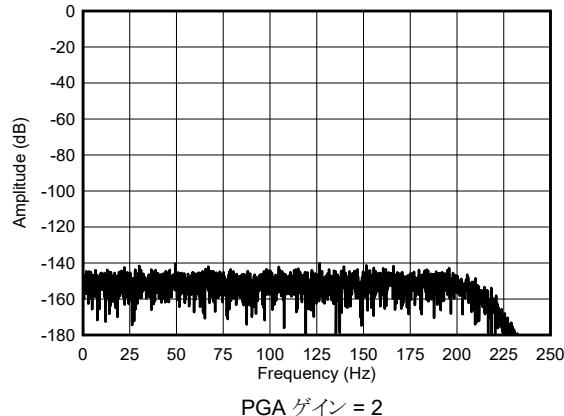

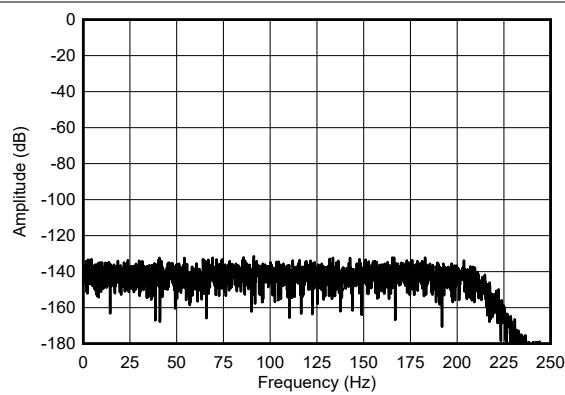

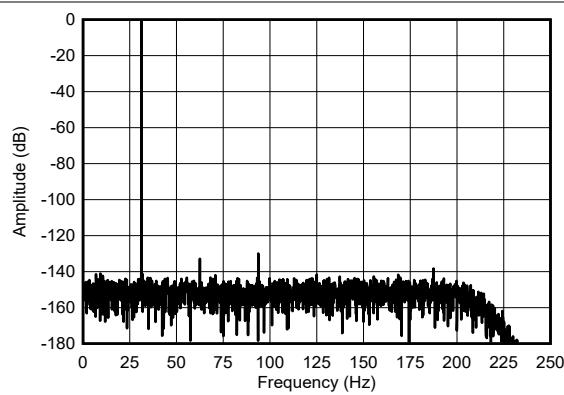

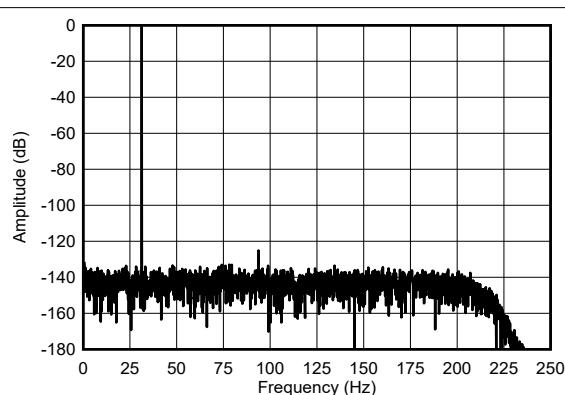

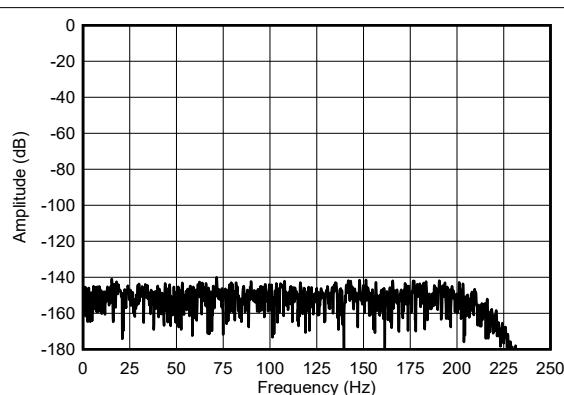

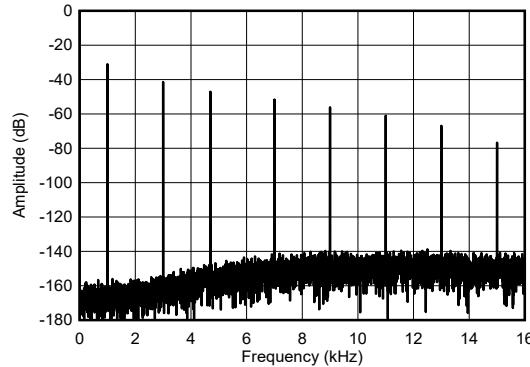

at  $T_A = 25^\circ\text{C}$ 、AVDD1 = 5V、AVSS = 0V、AVDD2 = 2.5V、IOVDD = 1.8V、 $f_{\text{CLK}} = 4.096\text{MHz}$ 、 $V_{\text{REFP}} = 2.5\text{V}$ 、 $V_{\text{REFN}} = 0\text{V}$ 、PGA

ゲイン = 1、 $R_S = 0\Omega$ 、 $V_{\text{CM}} = 2.5\text{V}$  および  $f_{\text{DATA}} = 500\text{SPS}$  (特に記述のない限り)

図 5-9. 入力 FFT の短絡

図 5-10. 入力 FFT の短絡

図 5-11. 入力 FFT の短絡

図 5-12. フルスケールの入力 FFT

図 5-13. フルスケールの入力 FFT

図 5-14. チャネルクロストーク

## 5.9 代表的特性 (続き)

at  $T_A = 25^\circ\text{C}$ 、AVDD1 = 5V、AVSS = 0V、AVDD2 = 2.5V、IOVDD = 1.8V、 $f_{\text{CLK}} = 4.096\text{MHz}$ 、 $V_{\text{REFP}} = 2.5\text{V}$ 、 $V_{\text{REFN}} = 0\text{V}$ 、PGA

ゲイン = 1、 $R_S = 0\Omega$ 、 $V_{\text{CM}} = 2.5\text{V}$  および  $f_{\text{DATA}} = 500\text{SPS}$  (特に記述のない限り)

## 5.9 代表的特性 (続き)

at  $T_A = 25^\circ\text{C}$ 、AVDD1 = 5V、AVSS = 0V、AVDD2 = 2.5V、IOVDD = 1.8V、 $f_{\text{CLK}} = 4.096\text{MHz}$ 、 $V_{\text{REFP}} = 2.5\text{V}$ 、 $V_{\text{REFN}} = 0\text{V}$ 、PGA ゲイン = 1、 $R_S = 0\Omega$ 、 $V_{\text{CM}} = 2.5\text{V}$  および  $f_{\text{DATA}} = 500\text{SPS}$  (特に記述のない限り)

## 5.9 代表的特性 (続き)

at  $T_A = 25^\circ\text{C}$ 、 $\text{AVDD1} = 5\text{V}$ 、 $\text{AVSS} = 0\text{V}$ 、 $\text{AVDD2} = 2.5\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $f_{\text{CLK}} = 4.096\text{MHz}$ 、 $V_{\text{REFP}} = 2.5\text{V}$ 、 $V_{\text{REFN}} = 0\text{V}$ 、PGA

ゲイン = 1、 $R_S = 0\Omega$ 、 $V_{\text{CM}} = 2.5\text{V}$  および  $f_{\text{DATA}} = 500\text{SPS}$  (特に記述のない限り)

## 5.9 代表的特性 (続き)

at  $T_A = 25^\circ\text{C}$ 、 $\text{AVDD1} = 5\text{V}$ 、 $\text{AVSS} = 0\text{V}$ 、 $\text{AVDD2} = 2.5\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $f_{\text{CLK}} = 4.096\text{MHz}$ 、 $V_{\text{REFP}} = 2.5\text{V}$ 、 $V_{\text{REFN}} = 0\text{V}$ 、PGA

ゲイン = 1、 $R_S = 0\Omega$ 、 $V_{\text{CM}} = 2.5\text{V}$  および  $f_{\text{DATA}} = 500\text{SPS}$  (特に記述のない限り)

## 6 パラメータ測定情報

### 6.1 ノイズ性能

ADS1288 は、オーバーサンプリング方式を採用した、低消費電力・低ノイズのデルタシグマ ADC です。オーバーサンプリングは、変調器の高周波データを平均化して最終的な出力データを生成します。オーバーサンプリング比を上げると、変調器からのサンプルをより多く平均して 1 回の変換結果を得るため、データレートと対応する信号帯域幅、そして合計ノイズが低下します。

ノイズ値が入力を基準とすると、PGA のゲインによりノイズが低減されます。ゲインを上げると、入力電圧範囲に対する入力換算電圧ノイズの比が小さくなるため、ダイナミックレンジ性能は低下します。

ダイナミックレンジと入力ノイズは、ADC で利用可能な分解能を表す等価パラメータです。式 1 は入力換算ノイズデータからダイナミックレンジを導出します：

$$\text{Dynamic Range (dB)} = 20 \times \log \left[ \frac{1.768 \text{ V}}{\text{Gain} \times e_n} \right] \quad (1)$$

ここで

- $e_n$  = 入力換算電圧ノイズ (RMS)

表 6-1 は、入力ソース抵抗 ( $R_S = 0\Omega$ ) の条件で試験したダイナミックレンジと入力換算ノイズ性能を示しています。ノイズデータは  $T_A = 25^\circ\text{C}$  であり、代表的な ADC の性能を表しています。このデータは、ADC の入力をショートした状態で連続する 4096 回の ADC 変換結果の標準偏差を示したもので、 $0.413 \times f_{\text{DATA}}$  の帯域幅で測定されています。ノイズは統計的な性質を持つため、繰り返し測定するとノイズ性能の結果が変動することがあります。

**表 6-1. ノイズ性能 (AVDD1 = 3.3V または 5V,  $R_S = 0\Omega$ )**

| ゲイン              | モード  | ダイナミックレンジ (dB)          |     |     |      |      | $e_n$ 、入力換算ノイズ ( $\mu\text{V}_{\text{RMS}}$ ) |      |      |      |      |

|------------------|------|-------------------------|-----|-----|------|------|-----------------------------------------------|------|------|------|------|

|                  |      | $f_{\text{DATA}}$ (SPS) |     |     |      |      | $f_{\text{DATA}}$ (SPS)                       |      |      |      |      |

|                  |      | 125                     | 250 | 500 | 1000 | 2000 | 125                                           | 250  | 500  | 1000 | 2000 |

| 1                | バッファ | 128                     | 125 | 122 | 119  | 116  | 0.70                                          | 0.99 | 1.4  | 2.0  | 2.8  |

| 1 <sup>(1)</sup> | PGA  | 128                     | 125 | 122 | 119  | 116  | 0.70                                          | 0.99 | 1.4  | 2.0  | 2.8  |

| 2                | PGA  | 127                     | 124 | 121 | 118  | 115  | 0.39                                          | 0.56 | 0.79 | 1.1  | 1.6  |

| 4                | PGA  | 126                     | 123 | 120 | 117  | 114  | 0.23                                          | 0.32 | 0.45 | 0.63 | 0.89 |

| 8                | PGA  | 123                     | 120 | 117 | 114  | 111  | 0.16                                          | 0.22 | 0.31 | 0.44 | 0.62 |

| 16               | PGA  | 118                     | 115 | 112 | 109  | 106  | 0.14                                          | 0.20 | 0.28 | 0.39 | 0.55 |

| 32               | PGA  | 112                     | 109 | 106 | 103  | 100  | 0.14                                          | 0.20 | 0.28 | 0.39 | 0.55 |

| 64               | PGA  | 106                     | 103 | 100 | 97   | 94   | 0.14                                          | 0.20 | 0.28 | 0.39 | 0.55 |

(1) PGA ゲイン = 1 のダイナミックレンジ性能は、AVDD1 = 5V の条件で規定されています。

## 7 詳細説明

### 7.1 概要

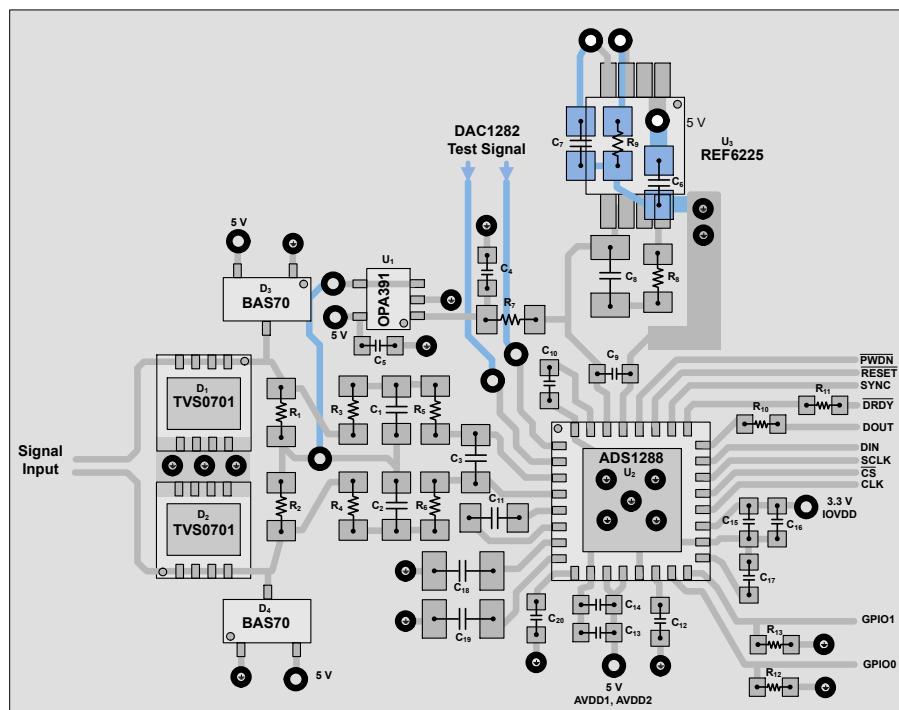

ADS1288 は、低消費電力と高い分解能が要求されるエネルギー探査、地質学、地震監視のアプリケーション向けに設計された高分解能、低消費電力の A/D コンバータ (ADC) です。出力データの分解能は 32 ビットで、125SPS から 2000SPS までのデータレートに対応しています。プログラマブル ゲインアンプ (PGA) は、 $\pm 2.5\text{V}_{\text{PP}} \sim \pm 0.039\text{V}_{\text{PP}}$  の 7 種類の入力レンジによってシステムのダイナミックレンジを拡張します。

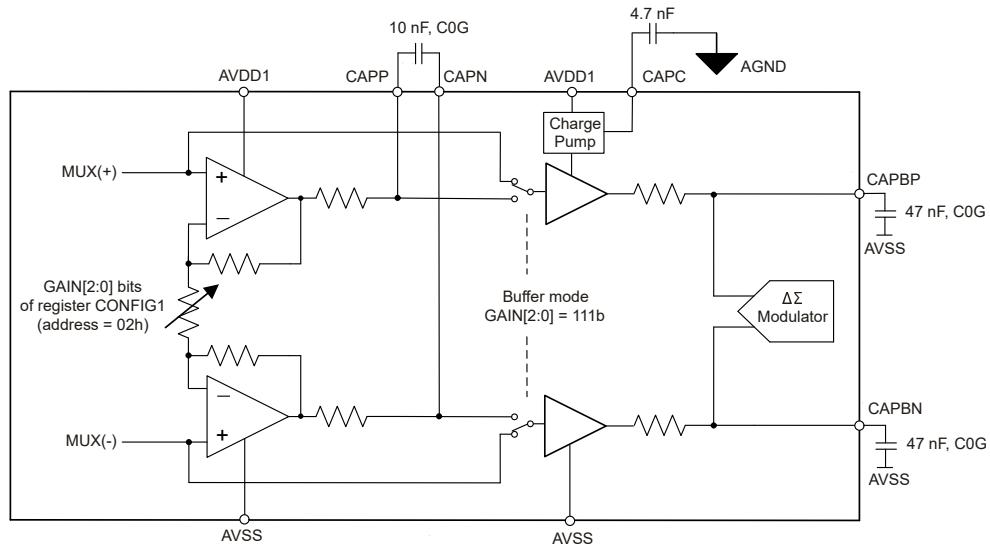

**機能ブロック図**に示すように、ADC は以下のセクションで構成されています。入力マルチプレクサ (MUX)、プログラマブル ゲインアンプ (PGA)、ユニティ ゲイン バッファ、デルタシグマ ( $\Delta\Sigma$ ) モジュレータ、サンプル レート コンバータ、無限インパルス応答 (IIR) ハイパス フィルタ (HPF)、有限インパルス応答 (FIR) ローパス フィルタ (LPF)、そしてデバイス設定と変換データの読み出しの両方に使用される SPI 互換のシリアル インターフェイスです。

入力マルチプレクサは、入力 1 または入力 2、さらにデバイスのオフセットやノイズ性能をテストするための入力短絡接続など、自己テスト用に設計された内部オプションを選択します。

入力マルチプレクサの後に低ノイズ PGA が接続されています。PGA のゲイン範囲は 1~16 で、ゲイン 32 と 64 はデジタル ゲインとして実装されています。PGA は、1/f ノイズと入力オフセット電圧を低減するために、チョッパ安定化方式が採用されています。PGA の出力は、モジュレータを駆動するバッファに接続されています。PGA 出力ピン CAPP および CAPN に接続された外部 10nF コンデンサは、入力信号用のアンチエイリアス フィルタになります。

PGA を無効にし、ユニティ ゲイン バッファで ADC を動作させることで、デバイスの消費電力を低減できます。各バッファ出力に接続された外部の 47nF コンデンサは、変調器のサンプリング パルスをフィルタ処理します。

$\Delta\Sigma$  変調器は、PGA の出力にある差動入力信号 ( $V_{IN}$ ) を、差動リファレンス電圧 ( $V_{REF} = 2.5V$ ) と比較して測定します。変調器のデータはデジタル フィルタによって処理され、最終的な変換結果が生成されます。デジタル フィルタは、同期フィルタに続いて、プログラム可能な位相の FIR ローパス フィルタと IIR ハイパス フィルタで構成されています。ハイパス フィルタは、データから dc 成分や低周波成分を除去します。

サンプル レートコンバータ (SRC) は、出力データを再サンプリングして出力データレートを補正することで、クロック信号の誤差を補償します。データ レートを補正するために、希望する補償値を SRC レジスタに書き込みます。補正精度は最大 7ppb です。

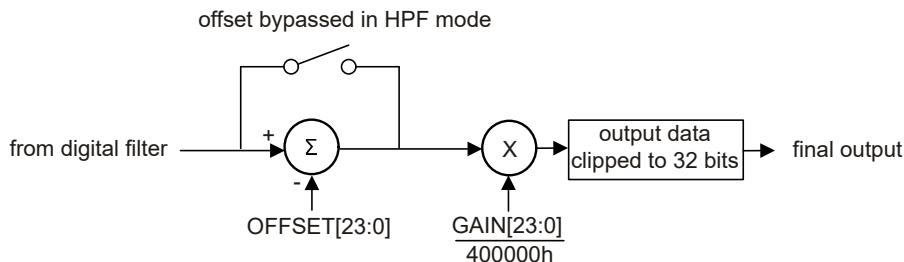

ユーザが設定できるゲインおよびオフセットのキャリブレーション レジスタによって、オフセット誤差とゲイン誤差を補正します。

SYNC ピンは ADC を同期します。同期には、パルス同期と連続同期という 2 つの動作モードがあります。RESET ピンは、ユーザ構成設定を含む ADC をリセットします。これらの端子はノイズに強いシムット リガ入力となっており、ノイズの多い環境でも信頼性が高まります。

PWDN ピンを使用しないときは、ADC の電源がオフになります。ソフトウェアのパワーダウン モード (スタンバイ) は、シリアル インターフェイス経由で利用できます

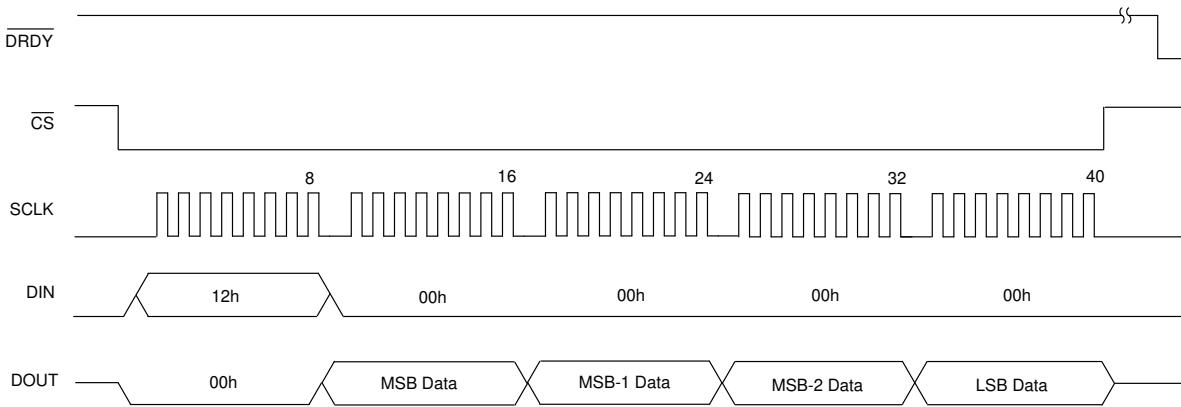

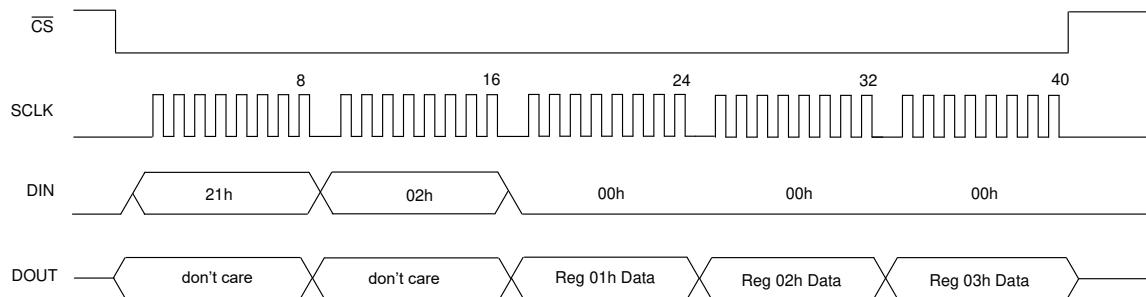

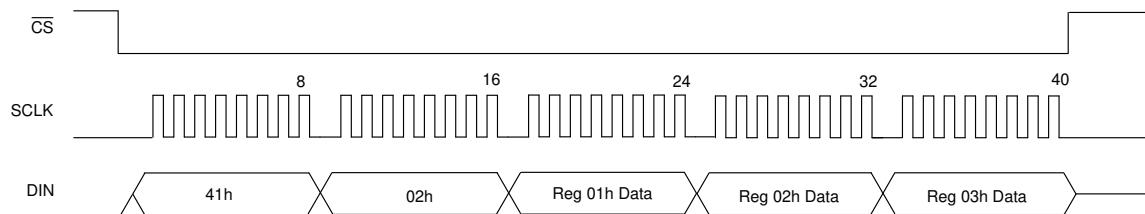

4 線式の SPI 互換シリアル インターフェイスは、変換データの読み取りや、デバイス レジスタ データの読み書きを行います。

診断テスト用に外部スイッチを制御できる汎用デジタル I/O が 2 つ利用できます。

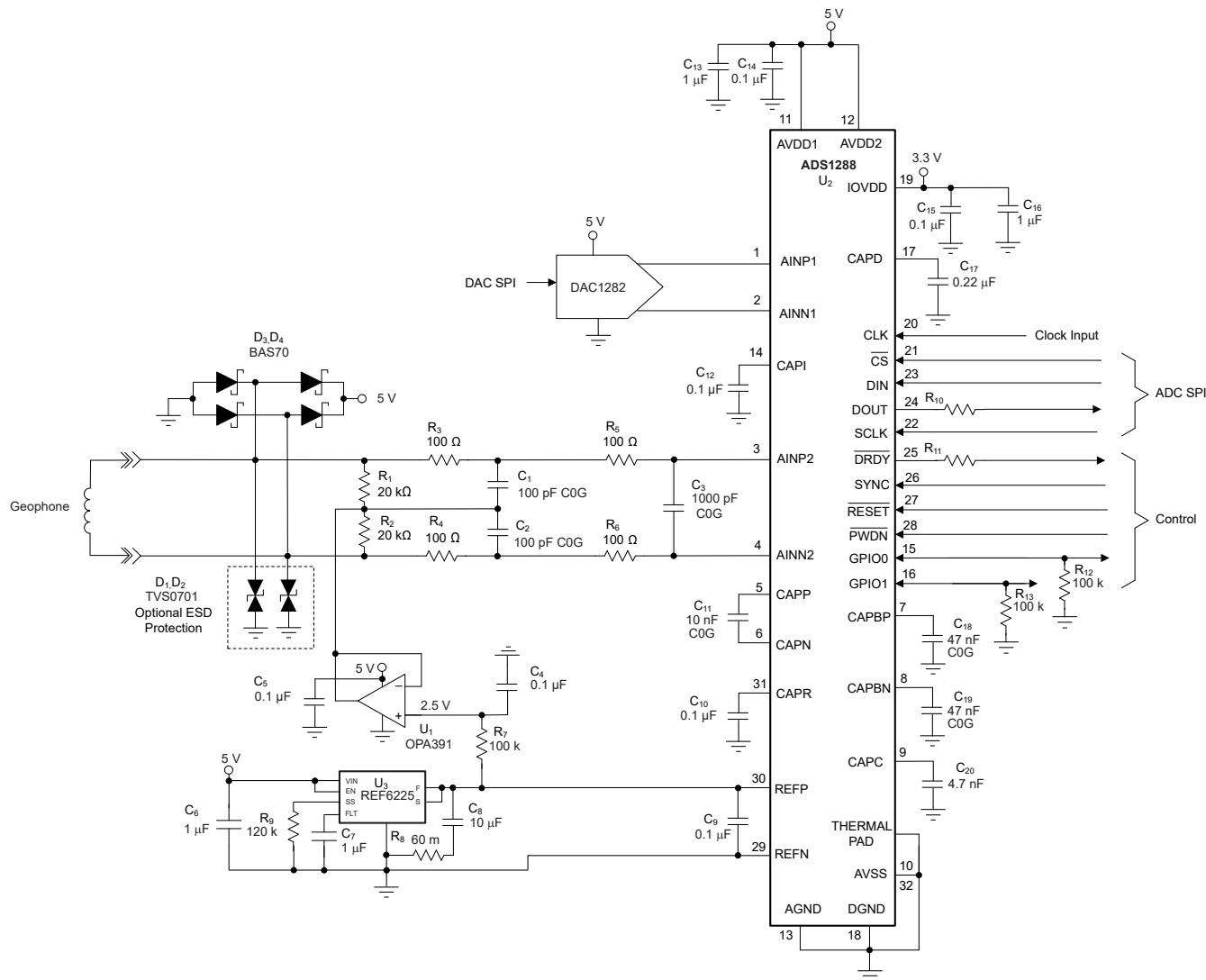

PGA とバッファの電源は、AVDD1 と AVSS ピンから供給されます。チャージ ポンプ式の電圧レギュレータがバッファの電源電圧を昇圧し、入力電圧レンジを広げます。変調器の電源は AVDD2 ピンから供給されます。デジタル I/O 電圧ピン (IOVDD) は、1.8V の低ドロップアウト レギュレータ (LDO) を通してデジタル ロジック コアに電力を供給します。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 アナログ入力

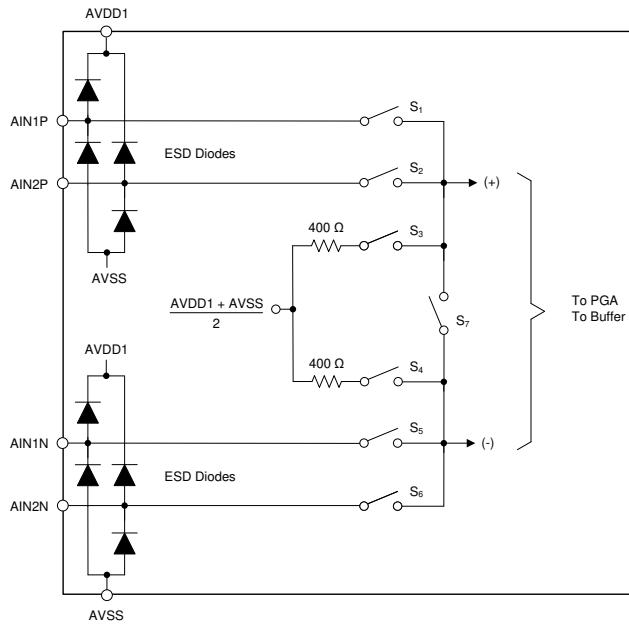

図 7-1 に、アナログ入力回路と入力マルチプレクサを示します。

図 7-1. アナログ入力およびマルチプレクサ

静電放電 (ESD) ダイオードは、デバイスの製造工程や、ESD 管理された環境でプリント基板 (PCB) を組み立てる際に発生する ESD 事象から ADC 入力を保護するために組み込まれています。システム レベルで保護するためには、ESD にさらされる入力を保護できる外付けの ESD 保護デバイスを使用することを検討してください。

入力が AVSS - 0.3V より下か、AVDD1 + 0.3V より上に駆動されると、保護ダイオードが導通することがあります。このような条件が起きる可能性がある場合は、外付けのクランプ ダイオード、直列抵抗、または両方を使用して、入力電流を指定の最大値に制限します。未使用の入力チャネルに過大入力を加えると、使用中の入力チャネルの変換結果に影響を及ぼすことがあります。チャネル間のクロストークを防ぐために、ショットキー ダイオードを使用して過大入力電圧をクランプします。

ADC には 2 つの差動入力チャネルが組み込まれています。マルチプレクサは、測定のために 2 つの差動入力から選択します。ノイズとオフセットを測定するためのテスト モードも、マルチプレクサによって提供されます。短絡入力のテスト構成は、800Ω のジオフォンで発生する熱雑音を模擬するために、400Ω の抵抗を使用する場合と使用しない場合のどちらも利用できます。表 7-1 に、マルチプレクサの構成を示します。

表 7-1. 入力マルチプレクサ モード

| MUX[2:0] のビット | スイッチ                                                              | 説明                                                |

|---------------|-------------------------------------------------------------------|---------------------------------------------------|

| 000           | S <sub>1</sub> , S <sub>5</sub>                                   | 入力 AIN1P, AIN1N 接続。                               |

| 001           | S <sub>2</sub> , S <sub>6</sub>                                   | 入力 AIN2P, AIN2N 接続。                               |

| 010           | S <sub>3</sub> , S <sub>4</sub>                                   | オフセットおよびノイズ テスト用 400Ω 入力短絡テスト モード。                |

| 011           | S <sub>1</sub> , S <sub>5</sub> , S <sub>2</sub> , S <sub>6</sub> | 相互接続テスト モード。入力 AIN1P, AIN2P および AIN2P, AIN2N が接続。 |

| 100           | —                                                                 | 予約済み                                              |

| 101           | S <sub>3</sub> , S <sub>4</sub> , S <sub>7</sub>                  | オフセットおよびノイズ テスト用、0Ω 入力短絡テスト モード。                  |

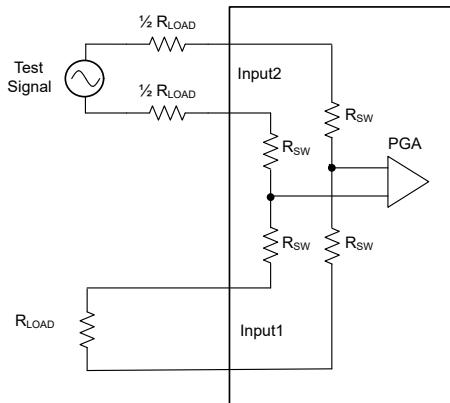

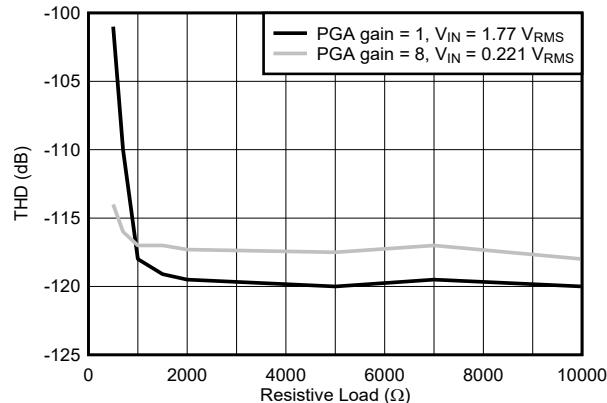

ジオフォンの THD 性能をテストするには、直列抵抗を介してテストチャネルにテスト信号を印加します。直列抵抗は、通常ジオフォンのインピーダンス値の半分が使用されます。相互接続テスト モードのマルチプレクサを選択します (MUX[2:0] = 011b)。相互接続モードでは、テスト信号がジオホン入力にクロスフィードされます。

ジオフォン THD テスト性能は、マルチプレクサの非線形形オン抵抗 ( $R_{SW}$ ) の影響を受ける可能性があります。図 7-2 に、ジオホン THD テストの入力マルチプレクサ抵抗のモデルを示します。図 7-3 に、THD ジオフォン抵抗をシミュレートするために使用されるテスト抵抗 ( $R_{LOAD}$ ) との関係を示します。小振幅のテスト信号 ( $V_{IN} = 0.221\text{V}$  など) では、ジオフォン抵抗が  $500\Omega$  未満の場合、THD 性能の劣化が少なくなります。

図 7-2. THD と  $R_{LOAD}$  との関係のテスト回路

図 7-3. THD 性能と  $R_{LOAD}$  との関係

### 7.3.2 PGA およびバッファ

図 7-4 に、PGA とバッファの簡略化したブロック図を示します。

図 7-4. PGA とバッファのブロック図

このデバイスは、PGA またはユニティゲイン バッファで動作できます。バッファ動作では PGA が無効化され、デバイスの消費電力が低減します。AVDD1 を  $3.3\text{V}$  で動作させる場合、PGA ゲイン = 1 では入力ヘッドルームが不足するため、この条件ではバッファを使用する必要があります。

### 7.3.2.1 プログラムルゲインアンプ (PGA)

PGA は低ノイズのチョッパ安定化差動アンプで、ADC のダイナミックレンジ性能を拡張します。PGA は 1 ~ 16 のアナログゲインを備えており、32 および 64 のゲインはデジタルスケーリングによって得られます。PGA 出力信号は、 $270\Omega$  の抵抗を経由して CAPP および CAPN ピンに配線されます。10nF の外付け C0G 誘電体コンデンサを、これらのピンの間に接続します。これらの部品によってアンチエイリエスフィルタが形成され、変調器のエイリアシング周波数 ( $f_{MOD}$ ) での信号レベルを減衰させます。

図 7-4 に示すように、PGA と変調器の間でバッファを使用します。各バッファ出力から 2 つの  $47nF$  C0G 誘電体コンデンサを AVSS (CAPBP および CAPBN) に接続します。電圧チャージポンプは、バッファの入力電圧のヘッドルームを増加させます。チャージポンプ動作のために、CAPC と AGND との間に外付けの  $4.7nF$  コンデンサを接続します。

速度モードは、**CONFIG1 レジスタ**の GAIN[2:0] ビットによってプログラムされます。表 7-2 に、PGA のゲイン設定とバッファ選択を示します。

表 7-2. PGA ゲイン

| GAIN[2:0] レジスタ ビット | PGA ゲイン          | 入力信号範囲 ( $V_{PP}$ ) |

|--------------------|------------------|---------------------|

| 000                | 1                | $\pm 2.5$           |

| 001                | 2                | $\pm 1.25$          |

| 010                | 4                | $\pm 0.625$         |

| 011                | 8                | $\pm 0.3125$        |

| 100                | 16               | $\pm 0.15625$       |

| 101                | 32               | $\pm 0.078125$      |

| 110                | 64               | $\pm 0.0390625$     |

| 111                | バッファ モード、ゲイン = 1 | $\pm 2.5$           |

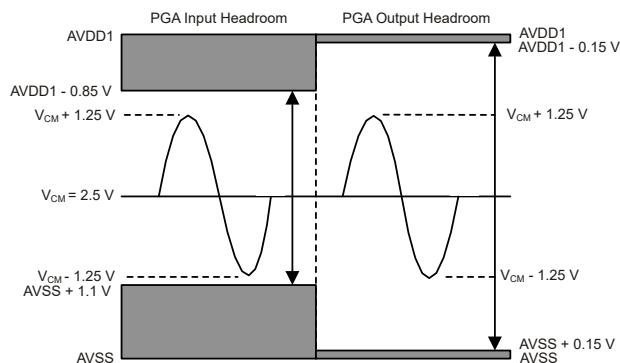

PGA の入力および出力電圧のヘッドルームの仕様を確認します。図 7-5 に、AVDD1 = 5V、入力同相電圧 ( $V_{CM}$ ) = 2.5V、差動入力電圧 =  $\pm 2.5V_{PP}$ 、ゲイン = 1 で動作しているときの、入力および出力電圧のヘッドルームを示します。PGA 入力の絶対最小および最大入力電圧 (1.25V と 3.75V) は、差動信号電圧の  $\pm 1/2$  に同相電圧を加えた値です。PGA は、負のピークで 0.15V の入力電圧マージン、正のピークで 0.4V の入力電圧マージンを提供します。PGA は、正と負のピークで 1.1V の出力電圧マージンを提供します。

図 7-5. PGA ヘッドルーム (AVDD1 = 5V、ゲイン = 1)

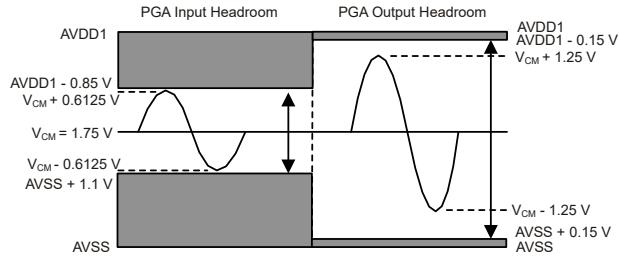

AVDD1 = 3.3V で動作している場合、PGA は  $\pm 2.5V_{PP}$  の入力信号をサポートできません。 $\pm 2.5V_{PP}$  の入力信号には、バッファを使用します。 $\pm 1.25V_{PP}$  の入力信号 (PGA ゲイン = 2) の場合、同相電圧を 0.1V から AVSS + 1.75V まで上げることで、入力ヘッドルームが増加します。図 7-6 に、AVDD1 = 3.3V、 $V_{CM}$  = 1.75V、入力信号 =  $\pm 1.25V_{PP}$ 、ゲイン = 2 の入力および出力動作ヘッドルームを示します。

図 7-6. PGA ヘッドルーム (AVDD1 = 3.3V、ゲイン = 2)

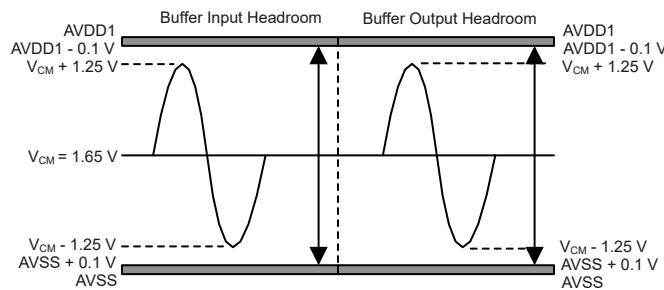

### 7.3.2.2 バッファ動作 (PGA バイパス)

ADC には、PGA をバイパスするバッファオプションがあります。PGA はバッファモードではパワーダウンします。AVDD1 を 3.3V で動作させる場合、 $\pm 2.5V_{PP}$  の入力信号には、バッファを使用します。CONFIG1 レジスタの GAIN[2:0] ビットを 111b に設定すると、バッファ動作が有効になります。

図 7-7 は、AVDD1 = 3.3V、 $V_{CM} = 1.65V$ 、入力信号 =  $\pm 2.5V_{PP}$  のときのバッファ電圧のヘッドルームを示します。AVDD1 = 3.3V で動作させている場合、このバッファには  $\pm 2.5V_{PP}$  の入力信号に対して十分な電圧ヘッドルームがあります。

図 7-7. バッファ ヘッドルーム (3.3V の動作を図示)

PGA動作でもバッファ動作でも、各バッファ出力(CAPBP と CAPBN)から AVSS に、C0G 誘電体の 47nF コンデンサを 2 個接続します。電圧チャージポンプは、バッファ入力の動作ヘッドルームを増加させます。チャージポンプ動作のために、CAPC と AGND との間に外付けの 4.7nF コンデンサを接続します。

### 7.3.3 電圧リファレンス入力

ADC は、動作にリファレンス電圧を必要とします。リファレンス電圧入力は差動で、REFP ピンと REFN ピンの間の電圧として定義されます:  $V_{REF} = V_{REFP} - V_{REFN}$ 。差動入力のため、グランドノイズを拾わないように、VREFN の配線は電圧リファレンスのグランド端子に接続します。測定帯域幅において、ノイズが  $2\mu V_{RMS}$  未満の精密な 2.5V 電圧リファレンスを使用してください。

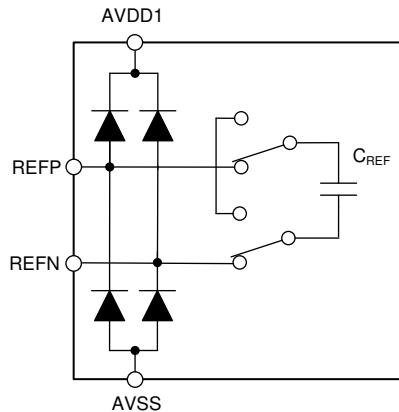

図 7-8 に、簡略化されたリファレンス入力回路を示します。アナログ入力と同様に、リファレンス入力は ESD ダイオードによって保護されます。リファレンス入力が AVSS - 0.3V より下か、AVDD1 + 0.3V より上に駆動されると、保護ダイオードが導通することがあります。このような条件が起きる可能性がある場合は、外付けのクランプダイオード、直列抵抗、または両方を使用して、リファレンス入力電流を指定の値に制限します。

図 7-8. 簡略化された電圧リファレンス入力回路

ADC は内部コンデンサ ( $C_{REF}$ ) によってリファレンス電圧をサンプリングし、変調器のサンプリング周波数 ( $f_{MOD}$ ) でコンデンサを放電します。サンプリング動作では、過渡電流がリファレンス入力に流れます。リファレンスピンのすぐ近くに配置した  $0.1\mu\text{F}$  のセラミックコンデンサで過渡電流をフィルタし、さらに基準電圧の出力側には  $10\mu\text{F} \sim 47\mu\text{F}$  の大きめのコンデンサを追加して安定させます。電圧リファレンスが複数の ADC を駆動するアプリケーションでは、各 ADC で  $0.1\mu\text{F}$  コンデンサを使用します。

外付けコンデンサが電流過渡をフィルタリングし、その結果、平均リファレンス電流は  $80\mu\text{A}/\text{V}$  になります。 $V_{REF} = 2.5\text{V}$  の場合、リファレンス入力電流は  $80\mu\text{A}/\text{V} \times 2.5\text{V} = 200\mu\text{A}$  です。

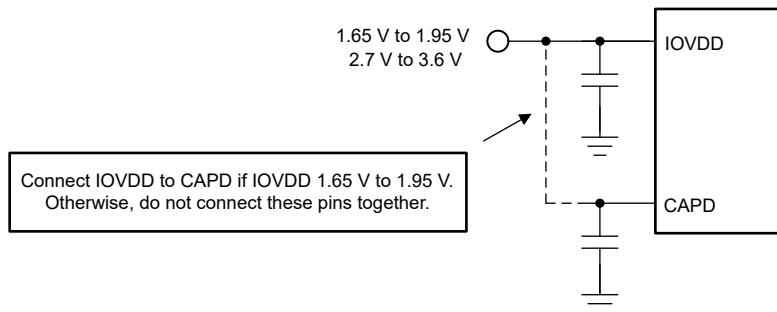

### 7.3.4 IOVDD の電源

IOVDD デジタル電源は、次の 2 つの電圧範囲で動作します:  $1.65\text{V} \sim 1.95\text{V}$  と  $2.7\text{V} \sim 3.6\text{V}$ 。 $1.65\text{V} \sim 1.95\text{V}$  の範囲で IOVDD を動作させる場合は、IOVDD を CAPD ピンに直接接続します。IOVDD が  $1.65\text{V} \sim 1.95\text{V}$  の範囲で動作している場合に必要な接続を、図 7-9 に示します。それ以外の場合、 $2.7\text{V} \sim 3.6\text{V}$  の範囲で IOVDD を動作させる場合、これらのピンを互いに接続しないでください。

図 7-9. IOVDD 電源の接続

### 7.3.5 変調器

変調器はマルチビットのデルタシグマアーキテクチャで、低消費電力であり、出力中のスプリアス成分が非常に少ないという特徴があります。変調器は内部量子化器の量子化ノイズを帯域外の周波数成分へとシェイピングし、ノイズはデジタルフィルタによって除去されます。通過帯域内に残るノイズは熱ノイズであり、一定のノイズ密度をもつ(ホワイトノイズ)という特性があります。ADC 出力の合計ノイズは、デジタルフィルタの OSR によって決まります。

#### 7.3.5.1 変調器のオーバードライブ

変調器は本質的に安定した設計であるため、入力オーバードライブから予測可能な回復を示します。入力信号のピークで変調器がオーバードライブされると、フィルタの出力データがクリップすることができます。ただし、デジタルフィルタによるデータ平均化の影響で、オーバードライブの持続時間によっては必ずしもクリップするとは限りません。変調器が大き

オーバードライブされると、出力で変換データがクリップする可能性が高くなります。デジタルフィルタのグループ遅延によって、入力のオーバードライブ発生時点から出力データに反映されるまでの時間が遅れることに注意してください。

### 7.3.6 デジタルフィルタ

デジタルフィルタは変調器のデータに対して間引きとフィルタ処理を行い、高分解能のデータを出力します。OSRによってフィルタ量を調整することで、出力データのノイズと帯域幅の間でバランスを取ることができます。OSRを上げると、出力データのノイズは減少しますが、信号帯域幅は狭くなります。

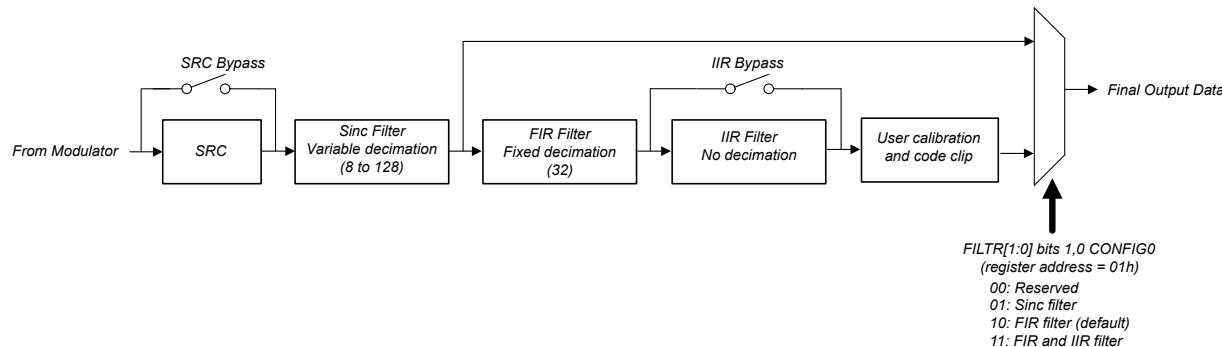

図 7-10 に示すように、サンプルレートコンバータ (SRC) は、デジタルフィルタブロックの前で変調器からデータを受け取ります。詳細については、[サンプルレートコンバータセクション](#)を参照してください。

図 7-10. デジタルフィルタのブロック図

デジタルフィルタは、次の三つのセクションで構成されています。可変デシメーションの **sinc** フィルタ、可変係数で固定デシメーションの **FIR** フィルタ、そしてプログラム可能なハイパスフィルタ(**IIR**)です。希望するフィルタセクションは、**CONFIG0** レジスタの **FILTER[1:0]** ビットで選択します。**sinc** フィルタは部分的にフィルタ処理されたデータを提供し、**FIR** フィルタ、**HPF** フィルタ、およびユーザ較正ステージをバイパスします。完全にフィルタ処理されたデータの場合は、**FIR** フィルタオプションを選択します。**IIR** フィルタ段は、**dc** および低周波数のデータを削除します。**FIR** フィルタ、および **FIR + IIR** の複合フィルタは、ユーザー較正ブロックと出力コードクリッピングブロックヘルーティングされます。ユーザ較正の詳細については、[オフセットおよびゲインの較正](#)セクションを参照してください。

#### 7.3.6.1 Sinc フィルタセクション

デジタルフィルタの最初のセクションは、可変デシメーションの 5 次シンクフィルタ (**sinx/x**) です。変調器のデータは、サンプルレートコンバータを通り、標準レート  $f_{MOD} = f_{CLK} / 4 = 1.024\text{MHz}$  でシンクフィルタに渡されます。**sinc** フィルタは、**FIR** フィルタのデータの一部フィルタリングを行い、最終的な周波数応答を生成します。**sinc** フィルタ出力データは、最終的な周波数応答を形成するために後処理フィルタとともに使用することを意図しています。

**sinc** フィルタのデシメーション比と結果として生じる出力データレートを [表 7-3](#) に示します。**sinc** フィルタのデータレートは、**CONFIG0** レジスタの **DR[2:0]** ビットによって設定されます。

表 7-3. Sinc フィルタのデータレート

| DR[2:0] ビット | SINC デシメーション比 (N) | データレート (SPS) |

|-------------|-------------------|--------------|

| 000         | 256               | 4,000        |

| 001         | 128               | 8,000        |

| 010         | 64                | 16,000       |

| 011         | 32                | 32,000       |

| 100         | 16                | 64,000       |

**sinc** フィルタの Z 領域伝達関数を、[式 2](#) に示します。

$$H(Z) = \left[ \frac{1 - Z^{-N}}{N(1 - Z^{-1})} \right]^5 \quad (2)$$

ここで

- $N$  = 表 7-3 のデシメーション比

sinc フィルタの周波数ドメイン伝達関数を、式 3 に示します。

$$|H(f)| = \left| \frac{\sin \left( \frac{\pi N \times f}{f_{MOD}} \right)}{N \sin \left( \frac{\pi \times f}{f_{MOD}} \right)} \right|^5 \quad (3)$$

ここで

- 表 7-3 に、 $N$  = デシメーション比を示します

- $f$  = 入力信号の周波数

- $f_{MOD}$  = 変調器のサンプリング周波数 =  $f_{CLK}/4$  (サンプルレートコンバータはディスエーブル)

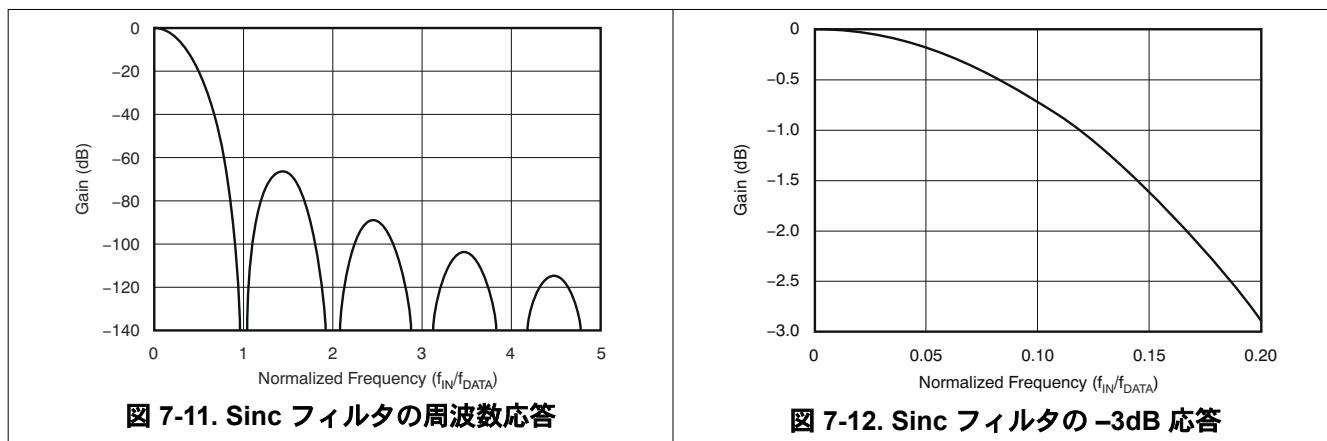

sinc フィルタの周波数応答には、出力データレートとその倍数でノッチ (またはゼロ) が発生します。これらの周波数では、フィルタのゲインはゼロになります。sinc フィルタの広帯域周波数応答を 図 7-11 に示し、図 7-12 に  $-3\text{dB}$  応答を示します。

$f_{DATA} = 32\text{kSPS}$  での sinc フィルタの周波数応答を 図 7-13 に示します。1kHz および高調波のトーンは、アイドルトーンを抑制するために変調器入力にディザリングを追加した結果です。デザリング信号の周波数は、表 7-4 に示されている合成デシメーション比で  $f_{MOD}$  を割った値です 2kHz でのノイズ フロアの上昇は、変調器のノイズ成形によるものです。sinc フィルタのデシメーション  $N = 32$  (データ レート = 32kSPS) の場合、外部ポスト フィルタを使用したときの有効帯域幅は 500Hz です。

図 7-13. Sinc フィルタの FFT 出力 ( $f_{DATA} = 32\text{kSPS}$ )

sinc フィルタのデータは、データ スケーリング、クリップ処理、ユーザ キャリブレーション ステージを通過しないため、FIR フィルタ データの場合とは異なるスケーリングになります。sinc フィルタのデータ スケーリングの詳細については、[変換データの形式](#) セクションを参照してください。

### 7.3.6.2 FIR フィルタ セクション

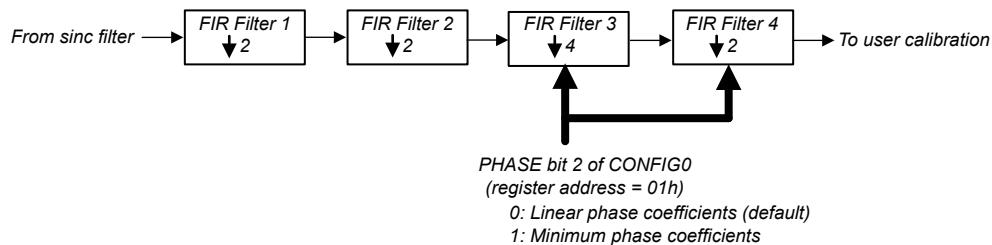

デジタル フィルタの 2 番目のセクションは、多段 FIR ローパス フィルタです。シンク フィルタで部分的にフィルタ処理されたデータが、FIR フィルタに入力されます。FIR フィルタは、最終的な出力データの周波数応答と位相応答を決定します。図 7-14 は、FIR フィルタが 4 つの段で構成されることを示しています。

図 7-14. FIR フィルタ

最初の 2 つの FIR 段はハーフバンド フィルタで、各段のデシメーション率は 2 です。3 番目と 4 番目の FIR 段では、最終的な周波数応答と位相応答が決まります。第 3 段と第 4 段では、デシメーション率はそれぞれ 4 と 2 です。FIR フィルタの合計デシメーション比は 32 です。第 3 段と第 4 段の異なるフィルタ係数セットによって、リニア位相か最小位相かのフィルタ特性が決まります。位相応答は、CONFIG0 レジスタの位相ビットによって選択されます。sinc および FIR フィルタ段の合成デシメーション比、および対応する FIR フィルタ データ レートを、表 7-4 に示します。

表 7-4. FIR フィルタのデータ レート

| DR[2:0] ビット | 合成デシメーション比 | データ レート (SPS) |

|-------------|------------|---------------|

| 000         | 8192       | 125           |

| 001         | 4096       | 250           |

| 010         | 2048       | 500           |

| 011         | 1024       | 1000          |

| 100         | 512        | 2000          |

表 7-5 に、FIR フィルタ係数と、線形および最小位相係数のデータ スケーリングを示します。

表 7-5. FIR フィルタ係数

| 係数              | STAGE 1       |         | STAGE 2           |          | STAGE 3             |           | STAGE 4             |      |

|-----------------|---------------|---------|-------------------|----------|---------------------|-----------|---------------------|------|

|                 | SCALE = 1/512 |         | SCALE = 1/8388608 |          | SCALE = 1/134217728 |           | SCALE = 1/134217728 |      |

|                 | 線形位相          | 線形位相    | 線形位相              | 最小位相     | 線形位相                | 最小位相      | 線形位相                | 最小位相 |

| b <sub>0</sub>  | 3             | -10944  | 0                 | 819      | -132                | 11767     |                     |      |

| b <sub>1</sub>  | 0             | 0       | 0                 | 8211     | -432                | 133882    |                     |      |

| b <sub>2</sub>  | -25           | 103807  | -73               | 44880    | -75                 | 769961    |                     |      |

| b <sub>3</sub>  | 0             | 0       | -874              | 174712   | 2481                | 2940447   |                     |      |

| b <sub>4</sub>  | 150           | -507903 | -4648             | 536821   | 6692                | 8262605   |                     |      |

| b <sub>5</sub>  | 256           | 0       | -16147            | 1372637  | 7419                | 17902757  |                     |      |

| b <sub>6</sub>  | 150           | 2512192 | -41280            | 3012996  | -266                | 30428735  |                     |      |

| b <sub>7</sub>  | 0             | 4194304 | -80934            | 5788605  | -10663              | 40215494  |                     |      |

| b <sub>8</sub>  | -25           | 2512192 | -120064           | 9852286  | -8280               | 39260213  |                     |      |

| b <sub>9</sub>  | 0             | 0       | -118690           | 14957445 | 10620               | 23325925  |                     |      |

| b <sub>10</sub> | 3             | -507903 | -18203            | 20301435 | 22008               | -1757787  |                     |      |

| b <sub>11</sub> |               | 0       | 224751            | 24569234 | 348                 | -21028126 |                     |      |

| b <sub>12</sub> |               | 103807  | 580196            | 26260385 | -34123              | -21293602 |                     |      |

| b <sub>13</sub> |               | 0       | 893263            | 24247577 | -25549              | -3886901  |                     |      |

| b <sub>14</sub> |               | -10944  | 891396            | 18356231 | 33460               | 14396783  |                     |      |

| b <sub>15</sub> |               |         | 293598            | 9668991  | 61387               | 16314388  |                     |      |

| b <sub>16</sub> |               |         | -987253           | 327749   | -7546               | 1518875   |                     |      |

| b <sub>17</sub> |               |         | -2635779          | -7171917 | -94192              | -12979500 |                     |      |

表 7-5. FIR フィルタ係数 (続き)

| 係数              | STAGE 1       |      | STAGE 2           |           | STAGE 3             |           | STAGE 4             |  |

|-----------------|---------------|------|-------------------|-----------|---------------------|-----------|---------------------|--|

|                 | SCALE = 1/512 |      | SCALE = 1/8388608 |           | SCALE = 1/134217728 |           | SCALE = 1/134217728 |  |

|                 | 線形位相          | 線形位相 | 線形位相              | 最小位相      | 線形位相                | 最小位相      |                     |  |

| b <sub>18</sub> |               |      | -3860322          | -10926627 | -50629              | -11506007 |                     |  |

| b <sub>19</sub> |               |      | -3572512          | -10379094 | 101135              | 2769794   |                     |  |

| b <sub>20</sub> |               |      | -822573           | -6505618  | 134826              | 12195551  |                     |  |

| b <sub>21</sub> |               |      | 4669054           | -1333678  | -56626              | 6103823   |                     |  |

| b <sub>22</sub> |               |      | 12153698          | 2972773   | -220104             | -6709466  |                     |  |

| b <sub>23</sub> |               |      | 19911100          | 5006366   | -56082              | -9882714  |                     |  |

| b <sub>24</sub> |               |      | 25779390          | 4566808   | 263758              | -353347   |                     |  |

| b <sub>25</sub> |               |      | 27966862          | 2505652   | 231231              | 8629331   |                     |  |

| b <sub>26</sub> |               |      | 25779390          | 126331    | -215231             | 5597927   |                     |  |

| b <sub>27</sub> |               |      | 19911100          | -1496514  | -430178             | -4389168  |                     |  |

| b <sub>28</sub> |               |      | 12153698          | -1933830  | 34715               | -7594158  |                     |  |

| b <sub>29</sub> |               |      | 4669054           | -1410695  | 580424              | -428064   |                     |  |

| b <sub>30</sub> |               |      | -822573           | -502731   | 283878              | 6566217   |                     |  |

| b <sub>31</sub> |               |      | -3572512          | 245330    | -588382             | 4024593   |                     |  |

| b <sub>32</sub> |               |      | -3860322          | 565174    | -693209             | -3679749  |                     |  |

| b <sub>33</sub> |               |      | -2635779          | 492084    | 366118              | -5572954  |                     |  |

| b <sub>34</sub> |               |      | -987253           | 231656    | 1084786             | 332589    |                     |  |

| b <sub>35</sub> |               |      | 293598            | -9196     | 132893              | 5136333   |                     |  |

| b <sub>36</sub> |               |      | 891396            | -125456   | -1300087            | 2351253   |                     |  |

| b <sub>37</sub> |               |      | 893263            | -122207   | -878642             | -3357202  |                     |  |

| b <sub>38</sub> |               |      | 580196            | -61813    | 1162189             | -3767666  |                     |  |

| b <sub>39</sub> |               |      | 224751            | -4445     | 1741565             | 1087392   |                     |  |

| b <sub>40</sub> |               |      | -18203            | 22484     | -522533             | 3847821   |                     |  |

| b <sub>41</sub> |               |      | -118690           | 22245     | -2490395            | 919792    |                     |  |

| b <sub>42</sub> |               |      | -120064           | 10775     | -688945             | -2918303  |                     |  |

| b <sub>43</sub> |               |      | -80934            | 940       | 2811738             | -2193542  |                     |  |

| b <sub>44</sub> |               |      | -41280            | -2953     | 2425494             | 1493873   |                     |  |

| b <sub>45</sub> |               |      | -16147            | -2599     | -2338095            | 2595051   |                     |  |

| b <sub>46</sub> |               |      | -4648             | -1052     | -4511116            | -79991    |                     |  |

| b <sub>47</sub> |               |      | -874              | -43       | 641555              | -2260106  |                     |  |

| b <sub>48</sub> |               |      | -73               | 214       | 6661730             | -963855   |                     |  |

| b <sub>49</sub> |               |      | 0                 | 132       | 2950811             | 1482337   |                     |  |

| b <sub>50</sub> |               |      | 0                 | 33        | -8538057            | 1480417   |                     |  |

| b <sub>51</sub> |               |      | 0                 | 0         | -10537298           | -586408   |                     |  |

| b <sub>52</sub> |               |      |                   |           | 9818477             | -1497356  |                     |  |

| b <sub>53</sub> |               |      |                   |           | 41426374            | -168417   |                     |  |

| b <sub>54</sub> |               |      |                   |           | 56835776            | 1166800   |                     |  |

| b <sub>55</sub> |               |      |                   |           | 41426374            | 644405    |                     |  |

| b <sub>56</sub> |               |      |                   |           | 9818477             | -675082   |                     |  |

| b <sub>57</sub> |               |      |                   |           | -10537298           | -806095   |                     |  |

| b <sub>58</sub> |               |      |                   |           | -8538057            | 211391    |                     |  |

| b <sub>59</sub> |               |      |                   |           | 2950811             | 740896    |                     |  |

| b <sub>60</sub> |               |      |                   |           | 6661730             | 141976    |                     |  |

| b <sub>61</sub> |               |      |                   |           | 641555              | -527673   |                     |  |

| b <sub>62</sub> |               |      |                   |           | 4511116             | -327618   |                     |  |

| b <sub>63</sub> |               |      |                   |           | -2338095            | 278227    |                     |  |

| b <sub>64</sub> |               |      |                   |           | 2425494             | 363809    |                     |  |

| b <sub>65</sub> |               |      |                   |           | 2811738             | -70646    |                     |  |

| b <sub>66</sub> |               |      |                   |           | -688945             | -304819   |                     |  |

| b <sub>67</sub> |               |      |                   |           | -2490395            | -63159    |                     |  |

| b <sub>68</sub> |               |      |                   |           | -522533             | 205798    |                     |  |

| b <sub>69</sub> |               |      |                   |           | 1741565             | 124363    |                     |  |

**表 7-5. FIR フィルタ係数 (続き)**

| 係数               | STAGE 1       | STAGE 2           | STAGE 3             |      | STAGE 4             |         |

|------------------|---------------|-------------------|---------------------|------|---------------------|---------|

|                  | SCALE = 1/512 | SCALE = 1/8388608 | SCALE = 1/134217728 |      | SCALE = 1/134217728 |         |

|                  | 線形位相          | 線形位相              | 線形位相                | 最小位相 | 線形位相                | 最小位相    |

| b <sub>70</sub>  |               |                   |                     |      | 1162189             | -107173 |

| b <sub>71</sub>  |               |                   |                     |      | -878642             | -131357 |

| b <sub>72</sub>  |               |                   |                     |      | -1300087            | 31104   |

| b <sub>73</sub>  |               |                   |                     |      | 132893              | 107182  |

| b <sub>74</sub>  |               |                   |                     |      | 1084786             | 15644   |

| b <sub>75</sub>  |               |                   |                     |      | 366118              | -71728  |

| b <sub>76</sub>  |               |                   |                     |      | -693209             | -36319  |

| b <sub>77</sub>  |               |                   |                     |      | -588382             | 38331   |

| b <sub>78</sub>  |               |                   |                     |      | 283878              | 38783   |

| b <sub>79</sub>  |               |                   |                     |      | 580424              | -13557  |

| b <sub>80</sub>  |               |                   |                     |      | 34715               | -31453  |

| b <sub>81</sub>  |               |                   |                     |      | -430178             | -1230   |

| b <sub>82</sub>  |               |                   |                     |      | -215231             | 20983   |

| b <sub>83</sub>  |               |                   |                     |      | 231231              | 7729    |

| b <sub>84</sub>  |               |                   |                     |      | 263758              | -11463  |

| b <sub>85</sub>  |               |                   |                     |      | -56082              | -8791   |

| b <sub>86</sub>  |               |                   |                     |      | -220104             | 4659    |

| b <sub>87</sub>  |               |                   |                     |      | -56626              | 7126    |

| b <sub>88</sub>  |               |                   |                     |      | 134826              | -732    |

| b <sub>89</sub>  |               |                   |                     |      | 101135              | -4687   |

| b <sub>90</sub>  |               |                   |                     |      | -50629              | -976    |

| b <sub>91</sub>  |               |                   |                     |      | -94192              | 2551    |

| b <sub>92</sub>  |               |                   |                     |      | -7546               | 1339    |

| b <sub>93</sub>  |               |                   |                     |      | 61387               | -1103   |

| b <sub>94</sub>  |               |                   |                     |      | 33460               | -1085   |

| b <sub>95</sub>  |               |                   |                     |      | -25549              | 314     |

| b <sub>96</sub>  |               |                   |                     |      | -34123              | 681     |

| b <sub>97</sub>  |               |                   |                     |      | 348                 | 16      |

| b <sub>98</sub>  |               |                   |                     |      | 22008               | -349    |

| b <sub>99</sub>  |               |                   |                     |      | 10620               | -96     |

| b <sub>100</sub> |               |                   |                     |      | -8280               | 144     |

| b <sub>101</sub> |               |                   |                     |      | -10663              | 78      |

| b <sub>102</sub> |               |                   |                     |      | -266                | -46     |

| b <sub>103</sub> |               |                   |                     |      | 7419                | -42     |

| b <sub>104</sub> |               |                   |                     |      | 6692                | 9       |

| b <sub>105</sub> |               |                   |                     |      | 2481                | 16      |

| b <sub>106</sub> |               |                   |                     |      | -75                 | 0       |

| b <sub>107</sub> |               |                   |                     |      | -432                | -4      |

| b <sub>108</sub> |               |                   |                     |      | -132                | 0       |

| b <sub>109</sub> |               |                   |                     |      | 0                   | 0       |

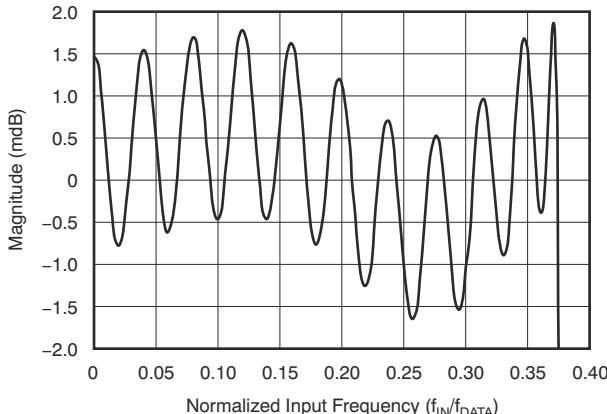

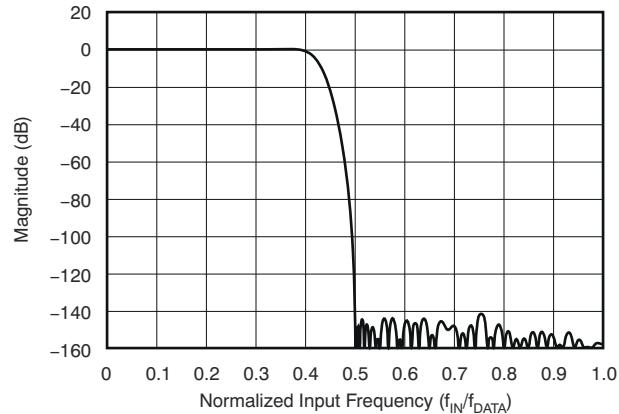

図 7-15 は、 $0.375 \times f_{\text{DATA}}$  までの FIR パスバンド周波数応答を、 $\pm 0.003\text{dB}$  のパスバンド リップルで示しています。図 7-16 は、0Hz から  $f_{\text{DATA}}$  までの、パスバンド、遷移バンド、ストップ バンドの性能を示します。このフィルタは、ナイキスト周波数において  $-135\text{ dB}$  のストップバンド減衰となるように設計されています。

図 7-15. FIR フィルタのパスバンド応答

図 7-16. FIR フィルタの遷移帯域応答

多くのサンプリング システムと同様に、このフィルタ応答は変調器のサンプル レート ( $f_{\text{MOD}}$ ) の整数倍の周波数で繰り返されます。フィルタ応答は、周波数  $N \times f_{\text{MOD}} \pm f_0$  で、ここで  $N = 1, 2, \dots$ 、 $f_0$  はフィルタのパスバンド周波数において繰り返されます。信号中にこれらの周波数が含まれている場合、それらは折り返して(エイリアスして)通過帯域に入り込み、誤差を引き起します。入力部のローパス入力フィルタが帯域外の信号を除去し、エイリアシング誤差を減らします。多くのジオフォンに見られる低周波の出力信号に対しては、PGA 出力に設けた 1 次フィルタだけで、ジオフォンの熱ノイズによるエイリアシングを十分に低減できます。

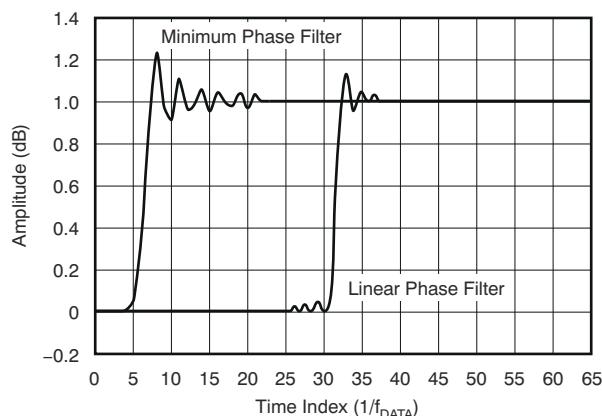

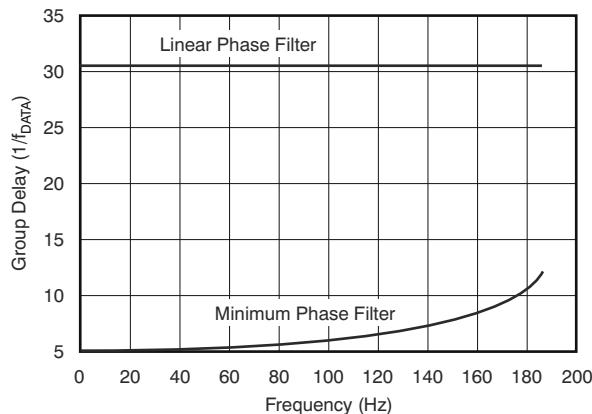

### 7.3.6.3 グループ遅延とステップ応答

FIR フィルタは、線形フィルタと最小位相フィルタのオプションを提供します。リニアおよび最小位相フィルタのパスバンド、遷移バンド、ストップ バンドの応答は同じですが、位相応答とステップ応答の動作が異なります。

#### 7.3.6.3.1 線形位相応答

線形位相フィルタは、入力から出力までの遅延がすべての入力周波数にわたって一定である(すなわち、一定の群遅延)独自の特性を持っています。一定遅延特性は入力信号の性質(インパルスまたはスイープトーン)に依存しないため、位相は周波数全体で線形であるため、マルチトーン信号を解析する際に重要なことがあります。ただし、図 7-17 に示すように、線形位相フィルタでは、最小位相よりもグループ遅延は長くなります。線形フィルタと最小フィルタのどちらの場合でも、ステップ入力の変化が発生してから 62 回の変換後に、完全に安定したデータが得られます。

図 7-17. FIR ステップ応答

### 7.3.6.3.2 最小位相応答

最小位相フィルタにより、フィルタ入力からフィルタ出力までのデータの短いグループ遅延が得られます。最小および線形位相フィルタのグループ遅延を、図 7-18 に示します。最小位相フィルタのグループ遅延は、信号周波数の関数です。CONFIG0 レジスタの PHASE ビットは、フィルタの位相を設定します。

図 7-18. FIR グループ遅延 ( $f_{DATA} = 500\text{SPS}$ )

### 7.3.6.4 HPF ステージ

デジタル フィルタの最後の段はハイパス フィルタ (HPF) です。ハイパス フィルタは、1 次の IIR フィルタとして実装されています。ハイパス フィルタは、データから dc 成分や低周波成分を除去します。HPF は、CONFIG0 レジスタの FILTR[1:0] ビットを 11b に設定することで有効になります。

式 4 には、このフィルタの z 領域での伝達関数が示されています：

$$H(z) = \frac{2-a}{2} \frac{1-z^{-1}}{1-(1-a)z^{-1}} \quad (4)$$

ここで

- $a = \frac{2\sin(\omega_N)}{\cos(\omega_N) + \sin(\omega_N)}$

- $\omega_N = \pi \times f_C / f_{DATA}$  (正规化されたコーナー周波数、ラジアン)

- $f_C$  = コーナー周波数 (Hz)

- $f_{DATA}$  = 出力データレート (Hz)

コーナー周波数プログラミングは  $f_{DATA}$  の関数であることに注意してください。式 5 に示すように、HPF1、HPF0 レジスタに書き込まれる値は  $a$  で、式  $4 \times 2^{16}$  で計算されます。

$$HPF[15:0] = a \times 2^{16} \quad (5)$$

表 7-6 に、ハイパス フィルタのプログラミング例を示します。

表 7-6. ハイパス フィルタの値の例

| HPF[15:0] | $f_C$ (Hz) | $f_{DATA}$ (SPS) |

|-----------|------------|------------------|

| 0332h     | 0.5        | 250              |

| 0332h     | 1.0        | 500              |

| 019Ah     | 1.0        | 1000             |

HPF は、ハイパス機能を実行するためにデータを蓄積します。入力に **dc** ステップ変化が加わった後のアナログ HPF の動作と同様に、このフィルタも信号から **dc** 成分を除去するためにデータを蓄積する時間が必要になります。コーナー周波数が低いほど、フィルタの安定性は長くなります。

HPF セトリング時間を短縮するために、オフセットレジスタは HPF アキュームレータのシード値として使用されます。アキュームレータには、HPF 状態がディスエーブルからイネーブルに変更されるたびに、オフセットレジスタがロードされます。オフセットレジスタには、推定値をあらかじめ設定することも、**dc** レベルが分かっている場合は較正済みの値を設定することもできます。精度を向上させるためには、オフセット値を **GAIN[3:0]** / **400000h** の逆数でスケーリングします。HPF が有効化されている場合、通常のオフセット動作は無効化されます。

HPF アキュームレータを **OFFSET[2:0]** レジスタで初期化する場合:

1. HPF をディスエーブルにします。

2. 希望する値を **OFFSET[2:0]** レジスタに書き込みます。

3. HPF をイネーブルにします。**OFFSET[2:0]** は HPF のデータアキュームレータにロードされます。

4. HPF は、信号からの残りの **dc** 値を追跡します。

その後に **OFFSET[2:0]** レジスタへ書き込みを行っても無視されます。**OFFSET[2:0]** レジスタの内容を HPF に再ロードするには、HPF を無効化し、再度有効化します。

### 7.3.7 クロック入力

動作にはクロック信号が必要です。クロック信号は、4.096MHz の **CLK** ピンに印加されます。多くの高精度データコンバータと同様、本デバイスでもデータシートどおりの性能を得るには低ジッタのクロックが必要です。R-C クロック発振器は使用しないでください。水晶振動子ベースのクロックソースを推奨します。クロック信号のリシグギングを防ぐため、クロック用のPCB配線に直列抵抗を入れてソース終端します。クロック信号は、他のクロック信号、入力ピン、アナログ部品から遠ざけて配線してください。

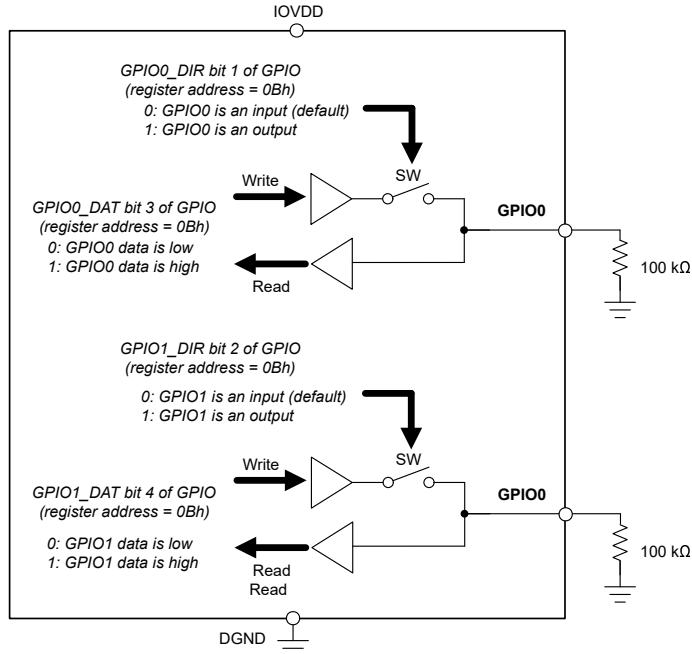

### 7.3.8 GPIO

ADC には 2 本の汎用 I/O (GPIO) ピンがあり、デジタル入出力として使用できます。GPIO の電圧レベルは、**IOVDD** および **DGND** です。[図 7-19](#) に GPIO のブロック図を示します。

GPIO は、**GPIO** レジスタによってプログラムされます。**GPIO** は、**GPIOx\_DIR** ビットによって、入力または出力としてプログラミングされます。**GPIO** の状態は、**GPIOx\_DAT** ビットで読み書きされます。出力としてプログラムされている場合、**GPIOx\_DAT** ビットを読み出すと、以前に書き込まれたレジスタビット値が返されます。**GPIO** を使用しない場合は、ピンがフローティングにならないように、プルダウン抵抗で **GPIO** を終端します。

図 7-19. GPIO 動作

## 7.4 デバイスの機能モード

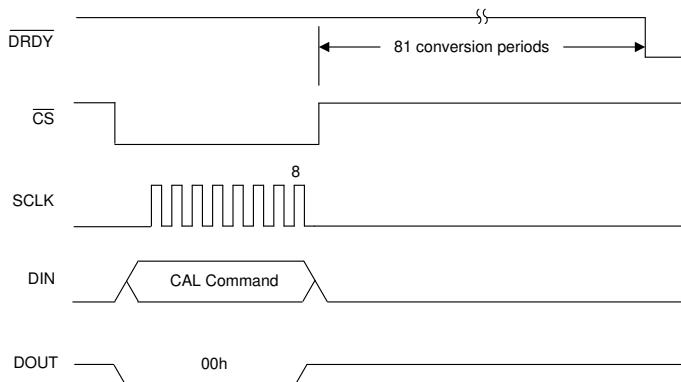

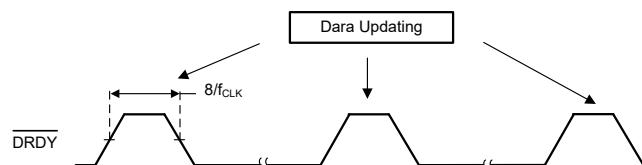

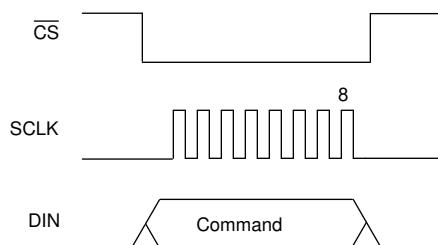

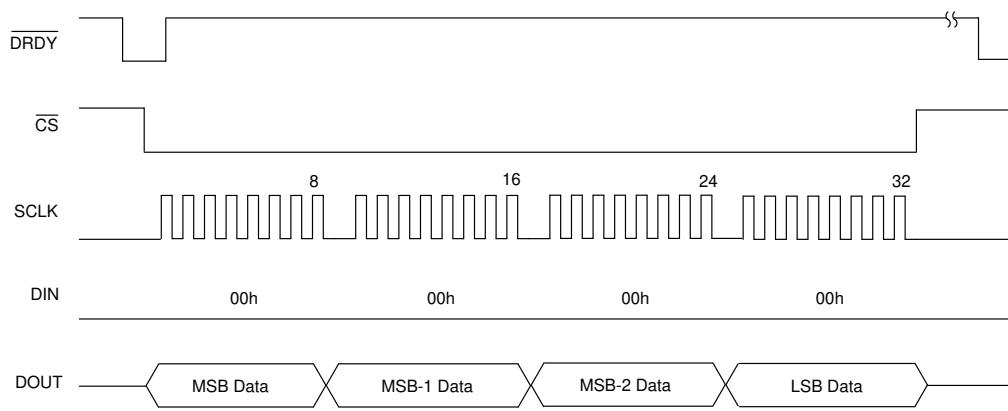

### 7.4.1 パワーダウン モード