**ADS1287**

JAJSHV5B – JUNE 2017 – REVISED AUGUST 2019

# ADS1287 低消費電力、1000SPS、広帯域幅 アナログ/デジタル・コンバータ、プログラム可能なゲイン・アンプ搭載

## 1 特長

• 動作モードを選択可能

• 高分解能モード:

- SNR: 113dB (1000SPS、ゲイン = 1)

- 消費電力: 4.5mW

• 低消費電力モード

- SNR: 110dB (1000SPS、ゲイン = 1)

- 消費電力: 2.4mW

THD: -115dBCMRR: 115dB

高インピーダンスのCMOS PGA

ゲイン: 1、2、4、8、16

• データ・レート: 62.5SPS~1000SPS

柔軟なデジタル・フィルタ:

- Sinc + FIR + IIR (選択可能)

- リニアおよび最小位相応答

- プログラム可能なハイパス・フィルタ

• オフセットおよびゲインの較正

• 同期制御

• SPI互換のインターフェイス

アナログ電源: 5Vまたは±2.5V

デジタル電源: 2.5V~3.3V

#### 2 アプリケーション

- エネルギー調査

- 受動的地震波観測

- ポータブル機器

## 3 概要

ADS1287デバイスは低消費電力のアナログ/デジタル・コンバータ(ADC)で、プログラム可能なゲイン・アンプ(PGA)と有限インパルス応答(FIR)デジタル・フィルタが内蔵されています。このADCは、高精度のデジタル化と低消費電力が要求される地震関連機器の厳しい要件に適しています。

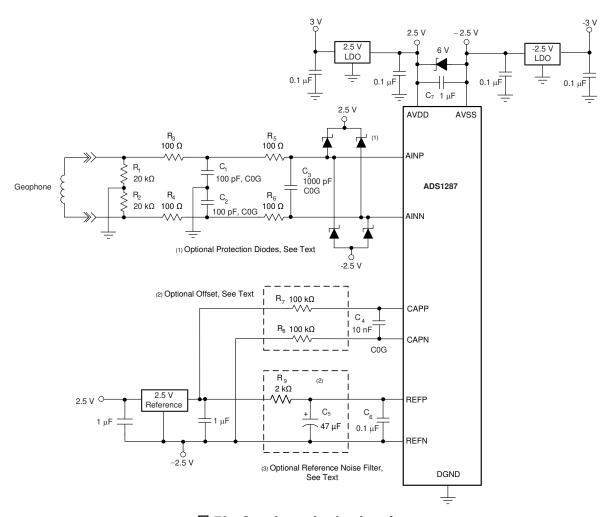

このADCはゲインをプログラム可能で、高インピーダンスの相補形金属酸化膜半導体(CMOS)アンプが搭載されており、広い範囲の入力信号(±2.5V~±0.156V)でジオホン・センサやハイドロホン・センサをADCへ直接接続するために適しています。

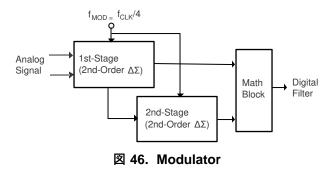

このADCには4次の、本質的に安定したデルタ-シグマ (ΔΣ)変調器が内蔵されています。変調器のデジタル出力は内部のFIRデジタル・フィルタによってフィルタ処理とデシメーションが行われ、ADC変換結果が生成されます。

FIRデジタル・フィルタは、毎秒1000サンプル(SPS)までのデータ・レートに対応できます。ハイパス・フィルタ(HPF)により、DCおよび低周波数の成分は変換結果から除去されます。オンチップのゲインおよびオフセットのスケーリング・レジスタが、システム較正をサポートします。

## 製品情報<sup>(1)</sup>

|         | 2000117116 |               |

|---------|------------|---------------|

| 型番      | パッケージ      | 本体サイズ(公称)     |

| ADS1287 | VQFN (24)  | 5.00mm×4.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にあるパッケージ・オプションについての付録を参照してくださ い。

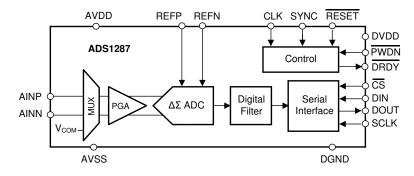

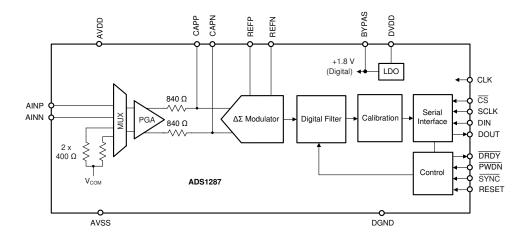

#### 機能ブロック図

|   | ٠,            |

|---|---------------|

|   |               |

| П | $\mathcal{I}$ |

| 1 | 特長                                   | 1    | 9.3 Feature Description        | 22 |

|---|--------------------------------------|------|--------------------------------|----|

| 2 | アプリケーション                             |      | 9.4 Device Functional Modes    | 35 |

| 3 | 概要                                   |      | 9.5 Programming                | 41 |

| 4 | 改訂履歴                                 |      | 9.6 Register Map               | 46 |

| 5 | 概要(続き)                               | 40   | Application and Implementation | 52 |

| 6 | Pin Configuration and Functions      |      | 10.1 Application Information   | 52 |

| _ | _                                    |      | 10.2 Typical Applications      | 52 |

| 7 | Specifications                       |      | 10.3 Initialization Set Up     |    |

|   | 7.1 Absolute Maximum Ratings         | 11   |                                |    |

|   | 7.2 ESD Ratings                      |      | 11.1 Analog Power Supplies     |    |

|   | 7.3 Recommended Operating Conditions | 6    | 11.2 Digital Power Supply      |    |

|   | 7.4 Thermal Information              | 6    |                                |    |

|   | 7.5 Electrical Characteristics       |      | 11.3 Power-Supply Sequence     |    |

|   | 7.6 Timing Requirements              | 9 12 |                                |    |

|   | 7.7 Switching Characteristics        |      | 12.1 Layout Guidelines         | 56 |

|   | 7.8 Typical Characteristics 1        | 42   | デバイスおよびドキュメントのサポート             | 57 |

| 8 | Parameter Measurement Information    |      | 13.1 ドキュメントの更新通知を受け取る方法        | 57 |

| U | 8.1 Noise Performance                |      | 13.2 コミュニティ・リソース               | 57 |

| _ |                                      |      | 13.3 商標                        |    |

| 9 | Detailed Description2                |      | 13.4 静電気放電に関する注意事項             |    |

|   | 9.1 Overview                         |      | 13.5 Glossary                  |    |

|   | 9.2 Functional Block Diagram 2       | 1    | メカニカル、パッケージ、および注文情報            |    |

|   |                                      | 14   | アルールル、ハツグーン、ねよい仕又情報            | 57 |

|   |                                      |      |                                |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Re | evision A (November 2017) から Revision B に変更 Pag                                                                                                                                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | Web にフルバージョンをリリースするためにドキュメントを変更                                                                                                                                                   |

| 20 | <b>Pag</b> Pag                                                                                                                                                                    |

| •  | Added second row to t <sub>c(SC)</sub> parameter                                                                                                                                  |

| •  | Changed $t_{w(SCH)}$ and $t_{w(SCL)}$ parameters to be merged together, added second row to $t_{w(SCH)}$ , $t_{w(SCL)}$ parameter                                                 |

| •  | Changed t <sub>d(CLSY)</sub> unit from 1 / f <sub>CLK</sub> to ns                                                                                                                 |

| •  | Added unit to t <sub>p(RSDR)</sub> and t <sub>p(PWDR)</sub> parameters of <i>Switching Characteristics</i> table                                                                  |

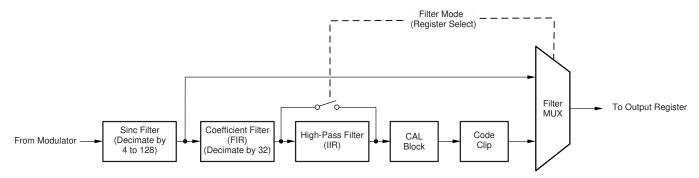

| •  | 変更 sinc filter block of <i>Digital Filter and Output Code Processing</i> figure from <i>Decimate by 8 to 128</i> to <i>Decimate by 4 to 128</i> to include low-power mode setting |

| •  | 追加 f <sub>MOD</sub> = f <sub>CLK</sub> / 8 for low-power mode to first paragraph of <i>Sinc Filter Stage</i> section                                                              |

| •  | 追加 sinc decimation ratio for low-power mode column and added high-resolution mode column header to <i>Sinc Filter Data Rates</i> table                                            |

| •  | 変更 f <sub>MOD</sub> description in Equation 9                                                                                                                                     |

| •  | 追加 sinc decimation ratio for low-power mode column and added high-resolution mode column header to FIR Filter  Data Rates table                                                   |

# 5 概要(続き)

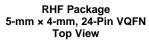

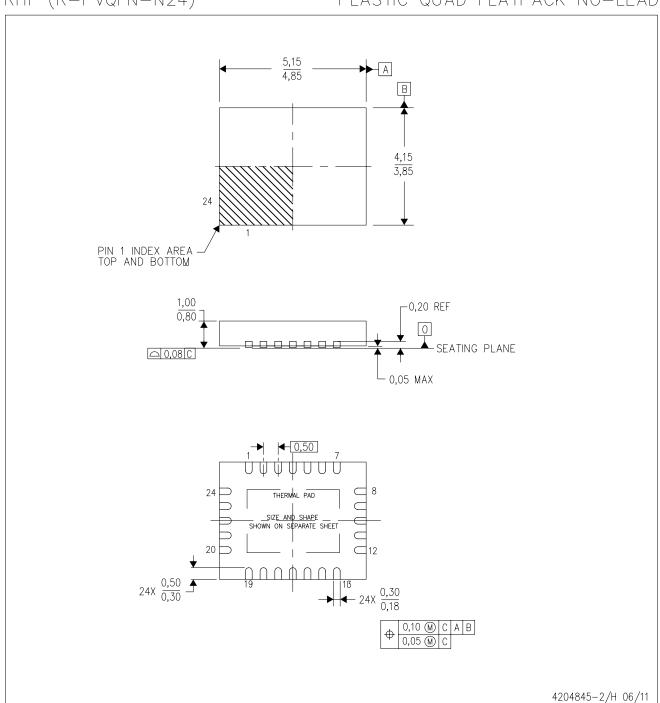

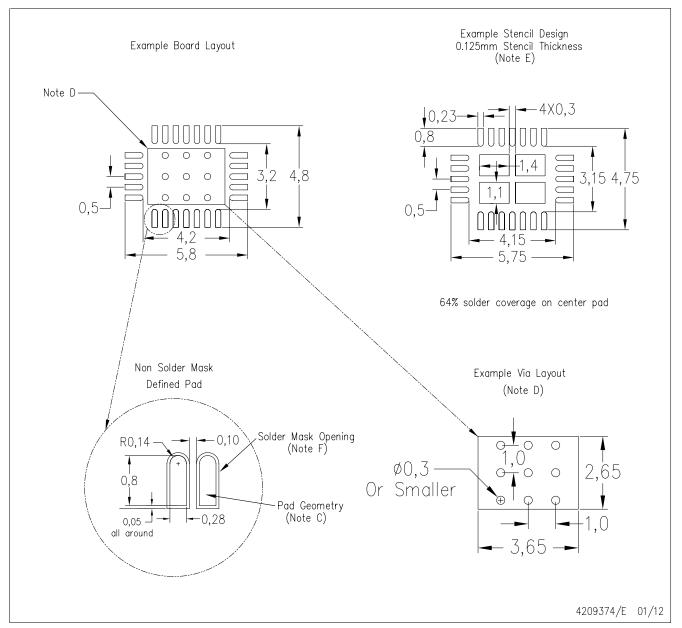

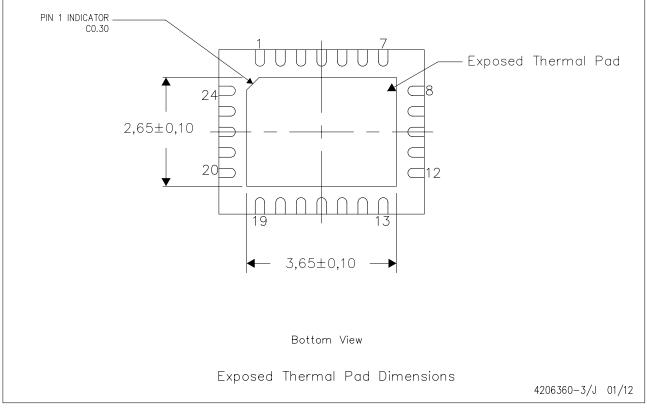

アンプ、変調器、デジタル・フィルタの合計消費電力は、高分解能モードで4.5mW (低消費電力モードで2.4mW)です。このADCは、小型の5mm×4mmのVQFNパッケージに格納されています。このADCは、-40℃~+85℃の温度範囲について完全に動作が規定されています。

# 6 Pin Configuration and Functions

## **Pin Functions**

|        | PIN    | FUNCTION       | DECORPTION                                                                                                                                     |

|--------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME   | FUNCTION       | DESCRIPTION                                                                                                                                    |

| 1      | DRDY   | Digital output | Data ready, active low                                                                                                                         |

| 2      | DOUT   | Digital output | Serial data output                                                                                                                             |

| 3      | DIN    | Digital input  | Serial data input                                                                                                                              |

| 4      | CS     | Digital input  | Serial interface select, active low                                                                                                            |

| 5      | SYNC   | Digital input  | Synchronize, active high                                                                                                                       |

| 6      |        |                | No connection                                                                                                                                  |

| 7      | DGND   | Ground         | Digital ground                                                                                                                                 |

| 8      | CAPN   | Analog output  | PGA negative output; connect a 10-nF C0G capacitor from CAPP to CAPN                                                                           |

| 9      | CAPP   | Analog output  | PGA positive output; connect a 10-nF C0G capacitor from CAPP to CAPN                                                                           |

| 10     | NC     | _              | No connection                                                                                                                                  |

| 11     | NC     | _              | No connection                                                                                                                                  |

| 12     | AINP   | Analog input   | Positive analog input                                                                                                                          |

| 13     | AINN   | Analog input   | Negative analog input                                                                                                                          |

| 14     | AVDD   | Analog         | Positive analog power supply                                                                                                                   |

| 15     | AVSS   | Analog         | Negative analog power supply                                                                                                                   |

| 16     | REFN   | Analog input   | Negative reference input                                                                                                                       |

| 17     | REFP   | Analog input   | Positive reference input                                                                                                                       |

| 18     | PWDN   | Digital input  | Power-down, active low                                                                                                                         |

| 19     | RESET  | Digital input  | Reset, active low                                                                                                                              |

| 20     | DVDD   | Digital        | Digital power supply                                                                                                                           |

| 21     | DGND   | Ground         | Digital ground (tie to digital ground plane)                                                                                                   |

| 22     | BYPAS  | Analog output  | Sub-regulator bypass; connect a 1-µF capacitor to DGND                                                                                         |

| 23     | CLK    | Digital input  | Master clock input (1.024 MHz)                                                                                                                 |

| 24     | SCLK   | Digital input  | Serial interface clock input                                                                                                                   |

| Therma | al pad | _              | Electrically float the thermal pad. The thermal pad must be soldered to the PCB for optimum mechanical strength. PCB layout vias are optional. |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

|                       | , in the second | MIN        | MAX        | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------|

|                       | AVDD to AVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3       | 6          |      |

| Power-supply voltage  | AVSS to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -2.8       | 0.3        | V    |

|                       | DVDD to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3       | 3.9        |      |

| Analog input voltage  | AINx, REFx, CAPx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AVSS - 0.3 | AVDD + 0.3 | V    |

| Digital input voltage | $\overline{\text{CS}}$ , SCLK, DIN, DOUT, $\overline{\text{DRDY}}$ , SYNC, $\overline{\text{RESET}}$ , CLK, $\overline{\text{PWDN}}$ , BYPAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DGND - 0.3 | DVDD + 0.3 | V    |

| Input current         | Continuous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | 10         | mA   |

| Tomporoturo           | Junction, T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 150        | °C   |

| Temperature           | Storage, T <sub>stg</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -60        | 150        | C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Floatroatatio disaborge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                     |                                       |                                     | MIN                        | NOM   | MAX                        | UNIT |

|---------------------|---------------------------------------|-------------------------------------|----------------------------|-------|----------------------------|------|

| POWER               | SUPPLY                                |                                     | •                          |       |                            |      |

|                     | A mala manuan annah .                 | AVSS to DGND                        | -2.6                       |       | 0                          | V    |

|                     | Analog power supply                   | AVDD to AVSS                        | 4.75                       |       | 5.25                       | V    |

|                     | Digital power supply                  | DVDD to DGND                        | 2.25                       |       | 3.6                        | V    |

| PGA INF             | PUT AND OUTPUT                        |                                     | ·                          |       |                            |      |

| V <sub>IN</sub>     | Differential input voltage            | $V_{IN} = V_{(AINP)} - V_{(AINN)}$  | –V <sub>REF</sub> / Gain   |       | V <sub>REF</sub> / Gain    | V    |

| V <sub>(AINx)</sub> | Absolute input voltage <sup>(1)</sup> |                                     | AVSS + 1                   |       | AVDD - 1.25                | V    |

| V <sub>(CAPx)</sub> | Absolute output voltage               |                                     | AVSS + 0.4                 |       | AVDD - 0.4                 | V    |

| VOLTAG              | SE REFERENCE INPUT                    |                                     | ·                          |       |                            |      |

| V <sub>REF</sub>    | Differential reference input voltage  | $V_{REF} = V_{(REFP)} - V_{(REFN)}$ | 2.45                       | 2.5   | 2.55                       | V    |

| V <sub>(REFN)</sub> | Negative reference input voltage      |                                     | AVSS - 0.1                 |       | V <sub>(REFP)</sub> – 2.45 | V    |

| V <sub>(REFP)</sub> | Positive reference input voltage      |                                     | V <sub>(REFN)</sub> + 2.45 |       | AVDD + 0.1                 | V    |

| CLOCK               | INPUT                                 |                                     |                            |       |                            |      |

| f <sub>(CLK)</sub>  | External clock frequency              |                                     | 0.4                        | 1.024 | 1.05                       | MHz  |

| DIGITAL             | . INPUTS                              |                                     |                            |       |                            |      |

|                     | Input voltage                         |                                     | DGND                       |       | DVDD                       | V    |

| TEMPER              | RATURE RANGE                          |                                     |                            |       |                            |      |

|                     | Operating ambient temperature         |                                     | -45                        |       | 125                        | °C   |

<sup>(1)</sup> Absolute input voltage is the signal voltage plus the common-mode voltage; see the *Programmable Gain Amplifier (PGA)* section.

## 7.4 Thermal Information

|                      |                                              | ADS1287    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHF (VQFN) | UNIT |

|                      |                                              | 24 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 27.5       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.5        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 8.6        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

maximum and minimum specifications apply from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ; typical specifications are at 25°C; all specifications are at AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{\text{(CLK)}} = 1.024$  MHz,  $V_{\text{(REFP)}} = 0$  V,  $V_{\text{(REFN)}} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, and  $f_{\text{DATA}} = 1000$  SPS (unless otherwise noted)

|                   | PARAMETER                                   | TEST CONDITIONS                             | MIN     | TYP                | MAX  | UNIT              |

|-------------------|---------------------------------------------|---------------------------------------------|---------|--------------------|------|-------------------|

| ANALO             | G INPUTS                                    |                                             |         |                    |      |                   |

|                   | Input ourrent                               | Chop disabled                               |         | 10                 |      | pA                |

|                   | Input current                               | Chop enabled                                |         | 50                 |      | pΑ                |

|                   |                                             | Common-mode, chop disabled                  |         | 50                 |      |                   |

|                   | Input resistance                            | Differential-mode, chop disabled            |         | 100                |      | $G\Omega$         |

|                   |                                             | Differential-mode, chop enabled             |         | 20                 |      |                   |

|                   | latit                                       | Common-mode                                 |         | 20                 |      |                   |

|                   | Input capacitance                           | Differential-mode                           |         | 5                  |      | pF                |

| PGA               |                                             |                                             |         |                    |      |                   |

|                   | V 1                                         | High-resolution mode                        |         | 15                 |      | \//\ <del> </del> |

|                   | Voltage noise density                       | Low-power mode                              |         | 25                 |      | nV/√Hz            |

|                   | 1/f noise corner                            | Chop disabled                               |         | 25                 |      | Hz                |

|                   | Gain factors                                |                                             |         | 1, 2, 4, 8, 16     |      | V/V               |

|                   |                                             | Nominal                                     |         | 1.7                |      | kΩ                |

|                   | Differential output impedance               | Tolerance                                   | -15%    |                    | 15%  |                   |

|                   | PGA output capacitor                        |                                             |         | 10                 |      | nF                |

| ADC               |                                             |                                             |         |                    |      |                   |

|                   | Resolution                                  | FIR filter mode                             | 31      |                    |      | Bits              |

|                   |                                             | High-resolution mode                        |         | 190                |      |                   |

|                   | Voltage noise density                       | Low-power mode                              |         | 275                |      | nV/√Hz            |

| f <sub>DATA</sub> | Data rate                                   | FIR filter mode                             | 62.5, 1 | 25, 250, 500, 1000 |      | SPS               |

|                   | M PERFORMANCE                               |                                             | 1       |                    | I    |                   |

|                   |                                             | High-resolution mode, gain = 1              | 110     | 113                |      |                   |

|                   |                                             | High-resolution mode, gain = 2              | 110     | 113                |      |                   |

|                   | Signal-to-noise ratio                       | High-resolution mode, gain = 4              | 108     | 113                |      |                   |

| SNR               | (see 表 1 through 表 4)                       | High-resolution mode, gain = 8              | 107     | 112                |      | dB                |

|                   |                                             | High-resolution mode, gain = 16             | 105     | 110                |      |                   |

|                   |                                             | Low-power mode, gain = 1                    | 106     | 110                |      |                   |

|                   | 40                                          | Gain = 1                                    |         | -115               | -105 |                   |

| THD               | Total harmonic distortion <sup>(1)</sup>    | Gain = 2, 4, 8, and 16                      |         | -115               |      | dB                |

| SFDR              | Spurious-free dynamic range                 |                                             |         | 115                |      | dB                |

|                   | , , ,                                       | T <sub>A</sub> = 25°C                       | -300    | ±50                | 300  |                   |

| $V_{IO}$          | Input offset voltage                        | Chop disabled, T <sub>A</sub> = 25°C        |         | ±300               |      | μV                |

| 10                |                                             | After calibration (2)                       |         | ±1                 |      | •                 |

|                   |                                             |                                             |         | 0.05               |      |                   |

|                   | Input offset voltage drift                  | Chop disabled                               |         | 1                  |      | μV/°C             |

|                   |                                             | High-resolution mode, T <sub>A</sub> = 25°C | -0.8%   | -0.3%              | 0.2% |                   |

|                   | Gain error                                  | Low-power mode, T <sub>A</sub> = 25°C       | -0.6%   | -0.1%              | 0.4% |                   |

|                   | Gain error after calibration <sup>(2)</sup> |                                             | 0.079   | 0.0005%            | 370  |                   |

|                   | Gain drift                                  | All gains                                   |         | 1                  |      | ppm/°C            |

|                   | Gain match                                  | All gains relative to gain = 1              | -0.5%   | ±0.1%              | 0.5% | PP111/ U          |

| -                 |                                             | , iii gains relative to gain – 1            |         | ±0.170             |      |                   |

|                   | Calibration margin <sup>(3)</sup>           |                                             | -106%   |                    | 106% |                   |

<sup>(1)</sup> Test signal: 31.25 Hz, -0.5 dBFS.

<sup>(2)</sup> Calibration accuracy is on the level of noise reduced by four (calibration averages 16 readings).

<sup>3)</sup> Calibration margin is the maximum allowed input voltage range after calibration operations.

# **Electrical Characteristics (continued)**

maximum and minimum specifications apply from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ; typical specifications are at 25°C; all specifications are at AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{\text{(CLK)}} = 1.024$  MHz,  $V_{\text{(REFP)}} = 0$  V,  $V_{\text{(REFN)}} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, and  $f_{\text{DATA}} = 1000$  SPS (unless otherwise noted)

|                     | PARAMETER                    | TEST CONDITIONS                    | MIN        | TYP                         | MAX        | UNIT |

|---------------------|------------------------------|------------------------------------|------------|-----------------------------|------------|------|

| SYSTE               | // PERFORMANCE, continued    |                                    |            |                             | <u>'</u>   |      |

| 01.100              |                              | High-resolution mode, DC to 60 Hz  | 100        | 115                         |            |      |

| CMRR                | Common-mode rejection ratio  | Low-resolution mode, DC to 60 Hz   | 95         | 110                         |            | dB   |

|                     |                              | Analog supplies, DC to 60 Hz       | 75         | 90                          |            |      |

| PSRR                | Power-supply rejection ratio | Digital supply, DC to 60 Hz        | 90         | 105                         |            | dB   |

| VOLTA               | SE REFERENCE INPUT           |                                    |            |                             |            |      |

|                     |                              | High-resolution mode               |            | 320                         |            |      |

|                     | Input impedance              | Low-power mode                     |            | 640                         |            | kΩ   |

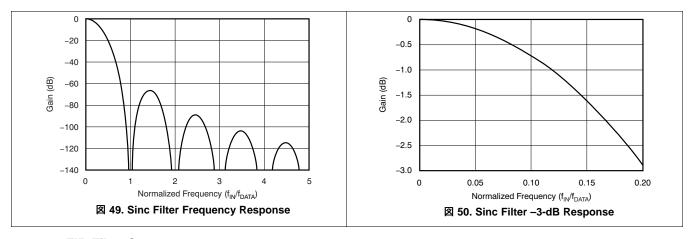

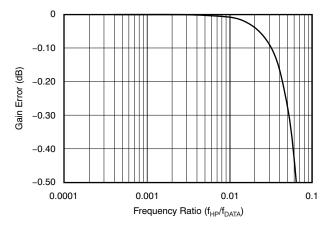

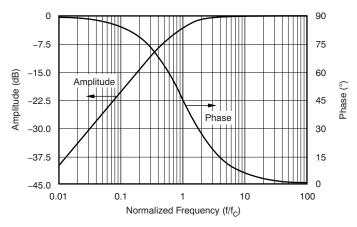

| DIGITAI             | FILTER RESPONSE              |                                    | 1          |                             |            |      |

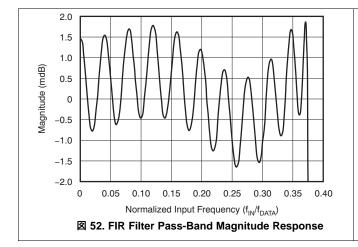

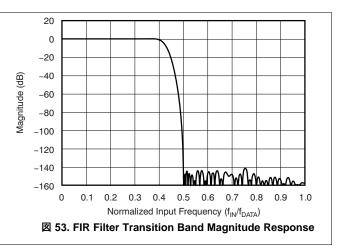

|                     | Pass-band ripple             |                                    |            |                             | ±0.003     | dB   |

|                     | Pass band (-0.01 dB)         |                                    |            | $0.375 \times f_{(DATA)}$   |            | Hz   |

|                     | Bandwidth (-3 dB)            |                                    |            | 0.413 × f <sub>(DATA)</sub> |            | Hz   |

|                     | High-pass filter corner      |                                    | 0.1        |                             | 10         | Hz   |

|                     | Stop-band attenuation (4)    |                                    | 135        |                             |            | dB   |

|                     | Stop band                    |                                    |            | 0.500 × f <sub>DATA</sub>   |            | Hz   |

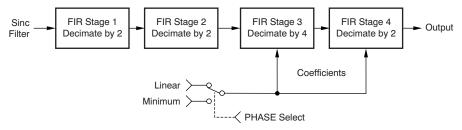

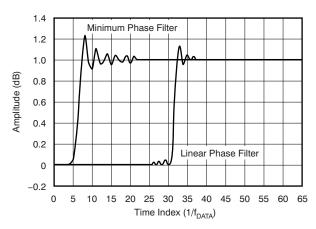

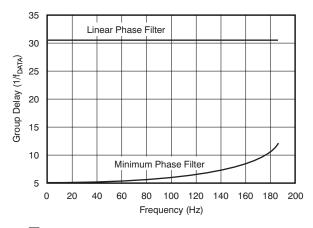

|                     |                              | Minimum phase filter               |            | 5 / f <sub>DATA</sub>       |            |      |

|                     | Group delay                  | Linear phase filter                |            | 31 / f <sub>DATA</sub>      |            | S    |

|                     | 0                            | Minimum phase filter               |            | 62 / f <sub>DATA</sub>      |            |      |

|                     | Settling time (latency)      | Linear phase filter                |            | 62 / f <sub>DATA</sub>      |            | S    |

| DIGITA              | INPUT/OUTPUTS                |                                    |            |                             | <u>"</u>   |      |

| $V_{IL}$            | Logic input level, low       |                                    | DGND       |                             | 0.2 × DVDD | V    |

| V <sub>IH</sub>     | Logic input level, high      |                                    | 0.8 × DVDD |                             | DVDD       | V    |

| V <sub>OL</sub>     | Logic output level, low      | I <sub>OL</sub> = 1 mA             | DGND       |                             | 0.2 × DVDD | V    |

| V <sub>OH</sub>     | Logic output level, high     | I <sub>OH</sub> = 1 mA             | 0.8 × DVDD |                             | DVDD       | V    |

|                     | Input current                | 0 ≤ V <sub>DIGITAL IN</sub> ≤ DVDD | -10        |                             | 10         | μΑ   |

| POWER               | SUPPLY                       |                                    |            |                             |            |      |

|                     |                              | High-resolution mode               |            | 750                         | 1100       |      |

| I <sub>AVDD</sub> , | Analog supply current        | Low-power mode                     |            | 330                         | 480        | μA   |

| I <sub>AVSS</sub>   | Analog supply current        | Standby mode                       |            | 1                           |            | μА   |

|                     |                              | Power-down mode                    |            | 1                           |            |      |

|                     |                              | High-resolution mode               |            | 240                         | 320        |      |

|                     | Digital average              | Low-power mode                     |            | 220                         | 300        |      |

| $I_{DVDD}$          | Digital supply current       | Standby mode <sup>(5)</sup>        |            | 25                          |            | μA   |

|                     |                              | Power-down mode <sup>(5)</sup>     |            | 1                           |            |      |

|                     |                              | High-resolution mode               |            | 4.5                         | 6.6        | m\^/ |

| n                   | Dower discipation            | Low-power mode                     |            | 2.4                         | 3.4        | mW   |

| $P_D$               | Power dissipation            | Standby mode <sup>(5)</sup>        |            | 90                          |            |      |

|                     |                              | Power-down mode <sup>(5)</sup>     |            | 10                          |            | μW   |

<sup>(4)</sup> Input frequencies are in the range of N × f<sub>(CLK)</sub> / 1024 ± f<sub>(DATA)</sub> / 2 (where N = 1, 2, 3, and so forth) intermodulated with the modulator chopper clock. At these frequencies, intermodulation components are -120 dBFS (typ).

<sup>(5)</sup> CLK input stopped.

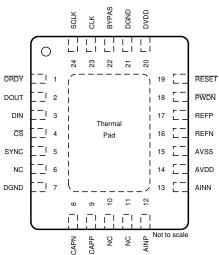

## 7.6 Timing Requirements

over operating ambient temperature range and DVDD = 2.25 V to 3.6 V (unless otherwise noted)

|                                           |                                                                           | MIN      | MAX | UNIT                 |

|-------------------------------------------|---------------------------------------------------------------------------|----------|-----|----------------------|

| SERIAL INTER                              | RFACE                                                                     | <u>.</u> |     |                      |

| t <sub>d(CSSC)</sub>                      | Delay time, $\overline{\text{CS}}$ falling edge to first SCLK rising edge | 40       |     | ns                   |

|                                           | SCLK period                                                               | 250      |     | ns                   |

| t <sub>c(SC)</sub>                        | SCLK period specific to SYNC and RESET commands                           | 2        |     | 1 / f <sub>CLK</sub> |

|                                           | Pulse duration, SCLK high and low <sup>(1)</sup>                          | 100      |     | ns                   |

| $t_{w(SCH)}, t_{w(SCL)}$                  | Pulse duration, SCLK high and low specific to SYNC and RESET commands     | 0.8      |     | 1 / f <sub>CLK</sub> |

| t <sub>su(DI)</sub>                       | Setup time, DIN valid before SCLK rising edge                             | 50       |     | ns                   |

| t <sub>h(DI)</sub>                        | Hold time, DIN valid after SCLK rising edge                               | 50       |     | ns                   |

| t <sub>w(CSH)</sub>                       | Pulse duration, CS high                                                   | 100      |     | ns                   |

| t <sub>d(SCCS)</sub>                      | Delay time, last SCLK rising edge to $\overline{\text{CS}}$ rising edge   | 24       |     | 1 / f <sub>CLK</sub> |

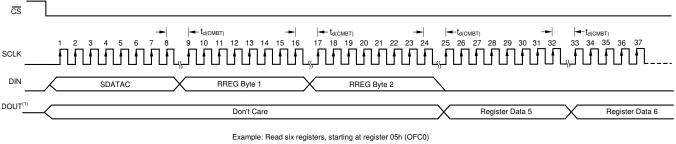

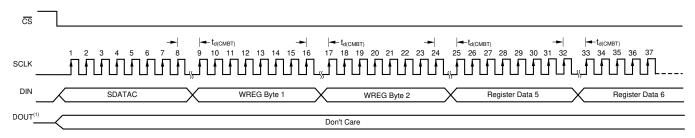

| t <sub>d(CMBT)</sub>                      | Delay time, after each byte within and between command sequences (2)      | 24       |     | 1 / f <sub>CLK</sub> |

| SYNCHRONIZ                                | ATION                                                                     |          | ,,  |                      |

| t <sub>d(CLSY)</sub>                      | Delay time, CLK rising edge to SYNC rising edge <sup>(3)</sup>            | 30       | -30 | ns                   |

| t <sub>w(SYH)</sub> , t <sub>w(SYL)</sub> | Pulse duration, SYNC high or SYNC low                                     | 2        |     | 1 / f <sub>CLK</sub> |

| RESET                                     |                                                                           | ·        |     |                      |

| t <sub>su(RSCL)</sub>                     | Setup time, RESET rising edge to a specific CLK rising edge               | 10       |     | ns                   |

| t <sub>w(RSL)</sub>                       | Pulse duration, RESET low                                                 | 2        |     | 1 / f <sub>CLK</sub> |

# 7.7 Switching Characteristics

over operating ambient temperature range, DVDD = 2.25 V to 3.6 V, and DOUT loading = 20 pF || 100 k $\Omega$  (unless otherwise noted)

|                       | PARAMETER                                                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT                  |

|-----------------------|----------------------------------------------------------------|-----------------|-----|-----|-----|-----------------------|

| SERIAL IN             | TERFACE                                                        |                 |     |     |     |                       |

| t <sub>p(DRDO)</sub>  | Propagation delay time, DRDY falling edge to valid data DOUT   |                 |     |     | 100 | ns                    |

| t <sub>p(CSDOD)</sub> | Propagation delay time, CS falling edge to DOUT driven         |                 |     |     | 60  | ns                    |

| t <sub>p(SCDO1)</sub> | Propagation delay time,<br>SCLK falling edge to valid new DOUT |                 |     |     | 100 | ns                    |

| t <sub>p(SCDO2)</sub> | Propagation delay time,<br>SCLK falling edge to valid old DOUT |                 | 0   |     |     | ns                    |

| t <sub>p(CSDOZ)</sub> | Propagation delay time,<br>CS rising edge to DOUT Hi-z         |                 |     |     | 40  | ns                    |

| t <sub>w(DRH)</sub>   | Pulse duration, DRDY high                                      |                 |     | 4   |     | 1 / f <sub>CLK</sub>  |

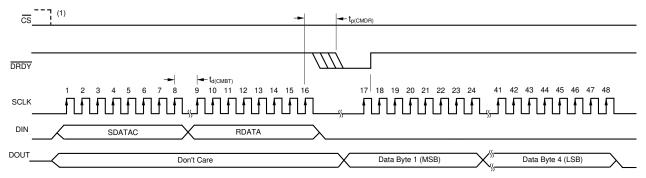

| t <sub>p(CMDR)</sub>  | Propagation delay time, RDATA command to DRDY low (see 図 60)   |                 | 0   |     | 1   | 1 / f <sub>DATA</sub> |

Holding SCLK low for 64 DRDY periods forces a serial interface reset.

When reading conversion data, the byte-to-byte delay is not required (t<sub>d(CMBT)</sub>).

SYNC rising edge to CLK rising edge must not occur within the specified time window.

# **Switching Characteristics (continued)**

over operating ambient temperature range, DVDD = 2.25 V to 3.6 V, and DOUT loading = 20 pF  $\parallel$  100 k $\Omega$  (unless otherwise noted)

|                      | PARAMETER                                                                   | TEST CONDITIONS                                 | MIN TYP MA                                   | X UNIT            |

|----------------------|-----------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------|-------------------|

| SYNCHRO              | NIZATION                                                                    |                                                 |                                              |                   |

|                      |                                                                             | High-resolution mode, 62.5 SPS                  | 1008.145                                     |                   |

|                      |                                                                             | High-resolution mode, 125 SPS                   | 504.301                                      |                   |

|                      |                                                                             | High-resolution mode, 250 SPS                   | 252.379                                      |                   |

|                      |                                                                             | High-resolution mode, 500 SPS                   | 126.419                                      |                   |

|                      |                                                                             | High-resolution mode, 1000 SPS                  | 63.438                                       |                   |

|                      |                                                                             | Low-power mode, 62.5 SPS                        | 1008.390                                     |                   |

|                      |                                                                             | Low-power mode, 125 SPS                         | 504.548                                      |                   |

|                      |                                                                             | Low-power mode, 250 SPS                         | 252.625                                      |                   |

|                      | Propagation delay time, SYNC rising                                         | Low-power mode, 500 SPS                         | 126.665                                      | (4)               |

| $t_{p(SYDR)}$        | edge to DRDY falling edge                                                   | Low-power mode, 1000 SPS                        | 63.684                                       | ms <sup>(1)</sup> |

|                      |                                                                             | Sinc filter and high-resolution mode, 2000 SPS  | 2.755                                        |                   |

|                      |                                                                             | Sinc filter and high-resolution mode, 4000 SPS  | 1.630                                        |                   |

|                      |                                                                             | Sinc filter and high-resolution mode, 8000 SPS  | 0.942                                        |                   |

|                      |                                                                             | Sinc filter and high-resolution mode, 16000 SPS | 0.599                                        |                   |

|                      |                                                                             | Sinc filter and high-resolution mode, 32000 SPS | 0.427                                        |                   |

| RESET                |                                                                             |                                                 |                                              |                   |

| $t_{p(RSDR)}$        | Propagation delay time, RESET pin or reset command to DRDY falling edge     |                                                 | 252.379                                      | ms                |

| POWER-D              | OWN MODE and STANDBY MODE WAKEU                                             | P                                               |                                              |                   |

| $t_{p(PWDR)}$        | Propagation delay time, exit power-down or standby mode to first data ready |                                                 | 252.379 <sup>(2)</sup>                       | ms                |

| POWER-U              | P                                                                           |                                                 |                                              |                   |

| t <sub>p(PUCM)</sub> | Propagation delay time, power-on threshold voltage to communication ready   |                                                 | 2 <sup>16</sup>                              | f <sub>CLK</sub>  |

| $t_{p(PUDR)}$        | Propagation delay time, power-on threshold voltage to first data ready      |                                                 | 2 <sup>16</sup> / f <sub>CLK</sub> + 252.379 | ms <sup>(1)</sup> |

- $f_{CLK}$  = 1.024 MHz. The exit power-down mode default setting is 250 SPS with the FIR filter mode. Subtract two  $f_{CLK}$  cycles for a WAKEUP command. The WAKEUP command is timed from the rising CLK edge after the eighth rising SCLK edge.

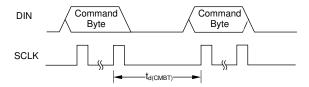

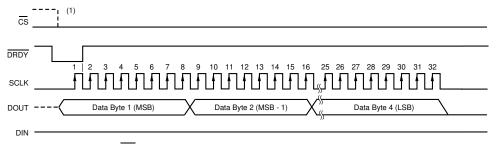

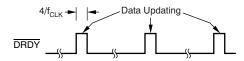

図 1. Serial Interface Timing Requirements

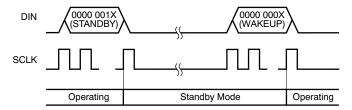

# 図 2. Serial Interface Command Timing Requirements

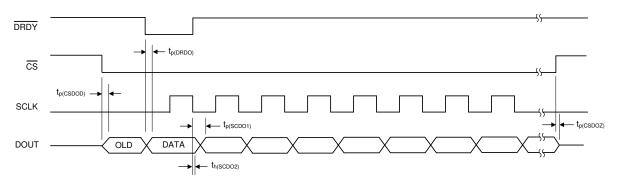

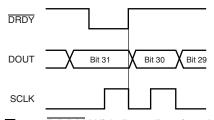

図 3. Serial Interface Switching Characteristics

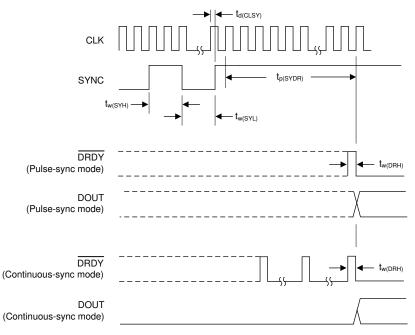

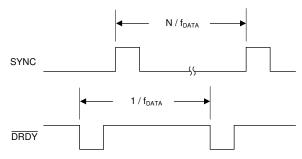

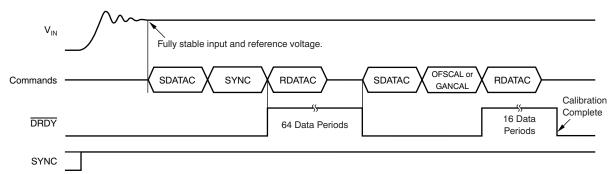

図 4. Synchronization Timing

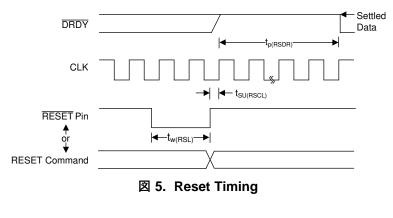

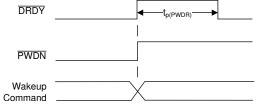

図 6. Power-Down and Standby Wake-Up Timing

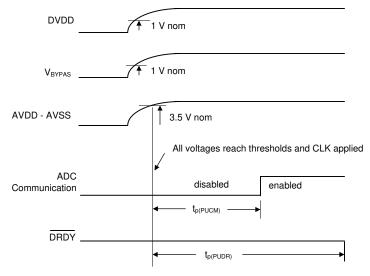

図 7. Power-Up Timing

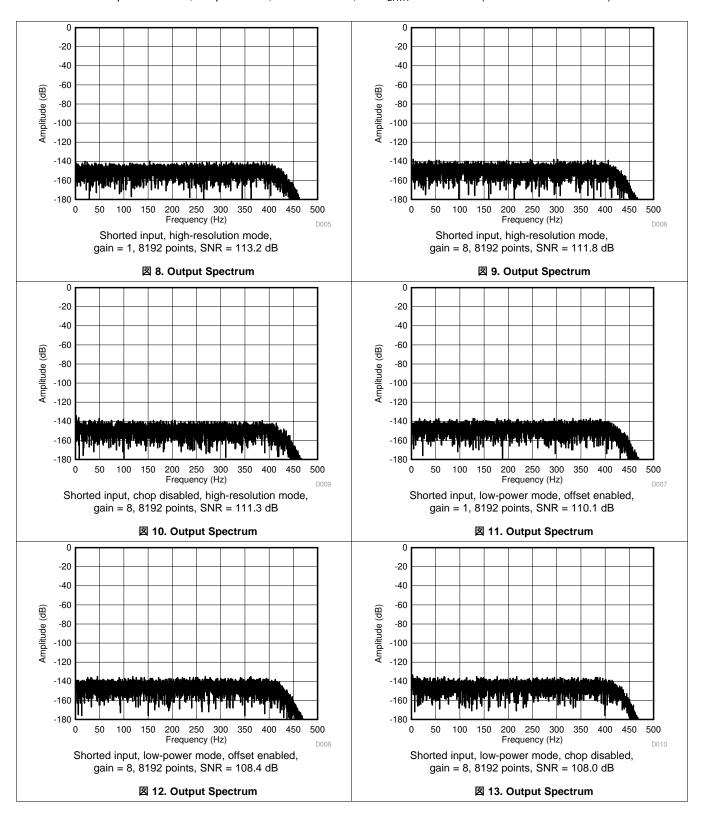

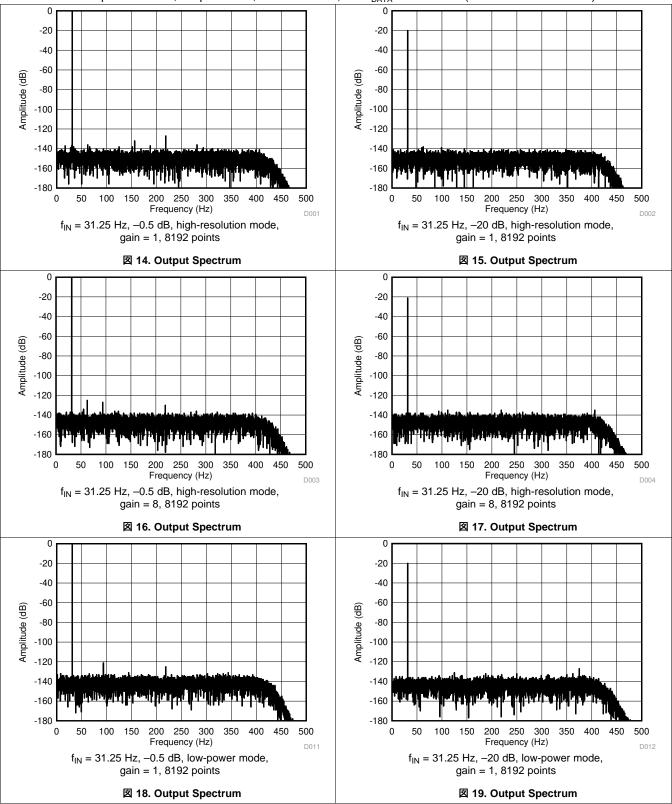

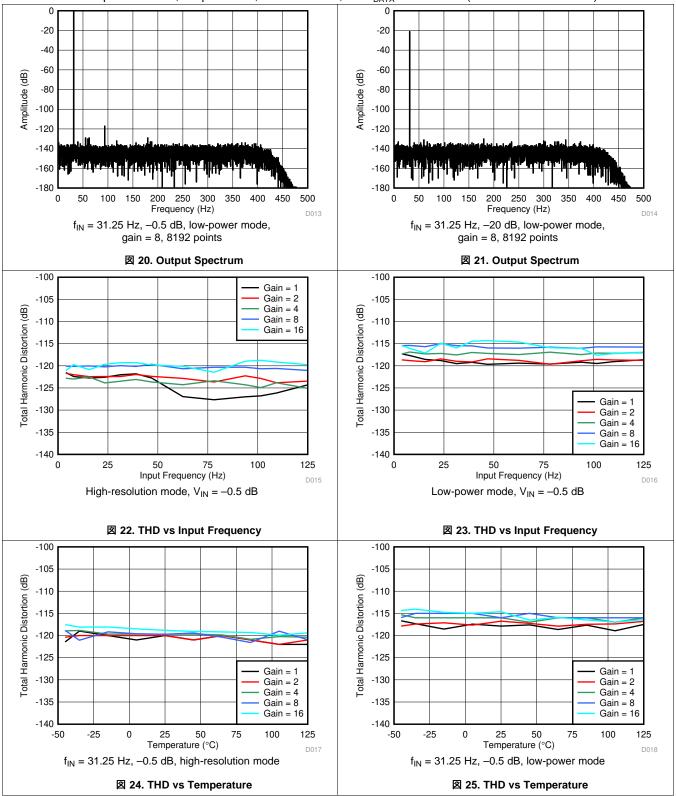

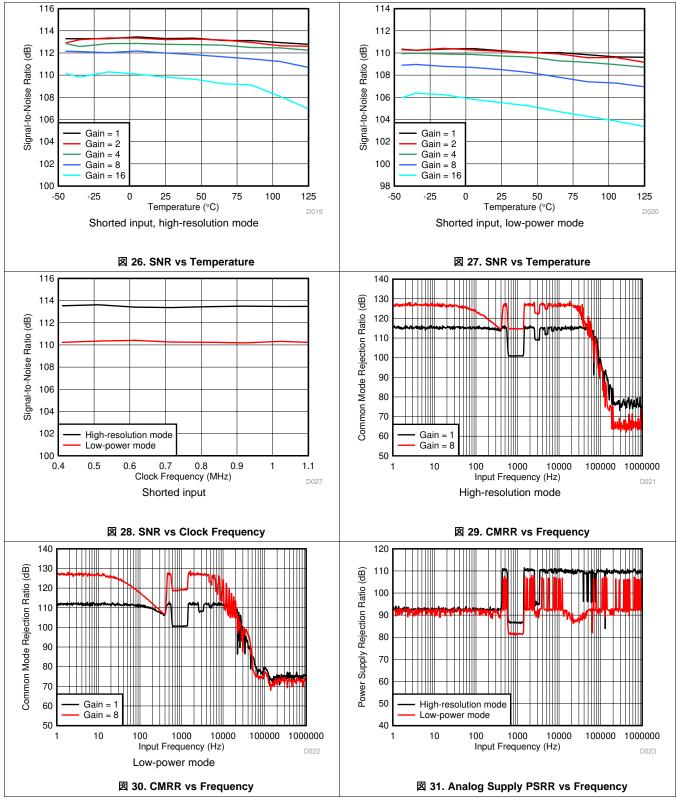

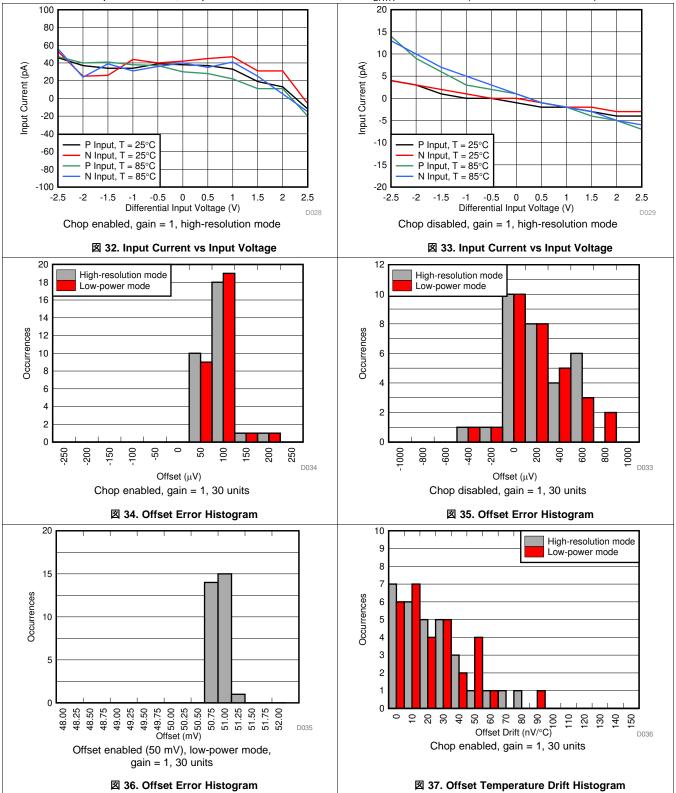

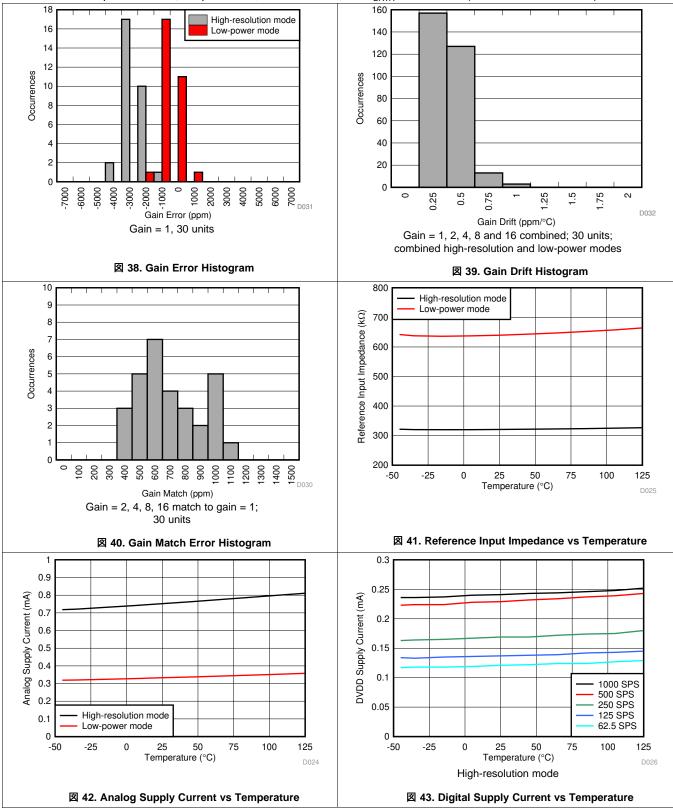

# 7.8 Typical Characteristics

at  $T_A = 25^{\circ}\text{C}$ , AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{\text{CLK}} = 1.024$  MHz,  $V_{(\text{REFP})} = 0$  V,  $V_{(\text{REFN})} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, offset disabled, and  $f_{\text{DATA}} = 1000$  SPS (unless otherwise noted)

# **Typical Characteristics (continued)**

at  $T_A = 25^{\circ}\text{C}$ , AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK} = 1.024$  MHz,  $V_{(REFP)} = 0$  V,  $V_{(REFN)} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, offset disabled, and  $f_{DATA} = 1000$  SPS (unless otherwise noted)

# **Typical Characteristics (continued)**

at  $T_A = 25^{\circ}\text{C}$ , AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{\text{CLK}} = 1.024$  MHz,  $V_{(\text{REFP})} = 0$  V,  $V_{(\text{REFN})} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, offset disabled, and  $f_{\text{DATA}} = 1000$  SPS (unless otherwise noted)

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at  $T_A = 25^{\circ}\text{C}$ , AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK} = 1.024$  MHz,  $V_{(REFP)} = 0$  V,  $V_{(REFN)} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, offset disabled, and  $f_{DATA} = 1000$  SPS (unless otherwise noted)

# **Typical Characteristics (continued)**

at  $T_A = 25^{\circ}\text{C}$ , AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{\text{CLK}} = 1.024$  MHz,  $V_{(\text{REFP})} = 0$  V,  $V_{(\text{REFN})} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, offset disabled, and  $f_{\text{DATA}} = 1000$  SPS (unless otherwise noted)

# **Typical Characteristics (continued)**

at  $T_A = 25^{\circ}\text{C}$ , AVDD = 2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{\text{CLK}} = 1.024$  MHz,  $V_{(\text{REFP})} = 0$  V,  $V_{(\text{REFN})} = -2.5$  V, gain = 1, high-resolution and low-power modes, chop enabled, offset disabled, and  $f_{\text{DATA}} = 1000$  SPS (unless otherwise noted)

#### 8 Parameter Measurement Information

#### 8.1 Noise Performance

SNR and input-referred noise are related parameters that define the ADC effective resolution. Use 式 1 to calculate SNR from the input-referred noise data:

$$SNR = 20log \frac{FSR_{RMS}}{N_{RMS}}$$

where:

$FSR_{RMS}$  = Full-scale range, root-mean-square = 2.5 V / ( $\sqrt{2}$  · Gain)

(1)

表 1 through 表 4 list SNR and noise performance data. Noise performance data are listed for high-resolution and low-power modes, with and without chop enabled. The noise performance data are representative of typical ADC performance at  $T_A = 25$ °C. The data are the standard deviation of consecutive ADC conversion results with the ADC inputs shorted over the signal bandwidth of 0.1 Hz to 0.413  $f_{DATA}$ . Repeated noise measurements can yield higher or lower noise results because of the statistical nature of noise.

Noise performance depends on several ADC operating parameters: high-resolution or low-power mode, data rate, PGA gain, and chop mode. Best noise performance is achieved by operating the ADC in high-resolution mode. Noise performance also depends on the data rate. For example, as the data rate decreases, the ADC bandwidth and thus total noise decreases. Using higher gain factors improves input-referred noise, but the calculated SNR decreases because of a 6-dB decrease of input range for each gain step. Chop mode improves noise performance by removing 1/f noise from the PGA. Chop mode is particularly important for lowest noise operation when used with low data rates or high gain. Chop mode is the recommended mode for geophone sensors.

| 表 1. High-Resolution | <b>Mode Noise</b> | <b>Performance</b> | (Chop | <b>Enabled</b> | ) <sup>(1)</sup> |

|----------------------|-------------------|--------------------|-------|----------------|------------------|

|                      |                   |                    |       |                |                  |

|                         |     |     | SNR (dB) |     |     | INPUT-REFERRED NOISE (μV <sub>RMS</sub> ) |      |      |      | )    |  |

|-------------------------|-----|-----|----------|-----|-----|-------------------------------------------|------|------|------|------|--|

| f <sub>DATA</sub> (SPS) |     |     | GAIN     |     |     | GAIN                                      |      |      |      |      |  |

|                         | 1   | 2   | 4        | 8   | 16  | 1                                         | 2    | 4    | 8    | 16   |  |

| 62.5                    | 125 | 125 | 125      | 124 | 122 | 0.96                                      | 0.49 | 0.25 | 0.14 | 0.09 |  |

| 125                     | 122 | 122 | 122      | 121 | 119 | 1.36                                      | 0.68 | 0.35 | 0.19 | 0.13 |  |

| 250                     | 119 | 119 | 119      | 118 | 116 | 1.90                                      | 0.97 | 0.50 | 0.28 | 0.18 |  |

| 500                     | 116 | 116 | 116      | 115 | 113 | 2.70                                      | 1.36 | 0.71 | 0.39 | 0.25 |  |

| 1000                    | 113 | 113 | 113      | 112 | 110 | 3.85                                      | 1.95 | 1.00 | 0.55 | 0.36 |  |

<sup>(1)</sup> Typical performance data at T<sub>A</sub> = 25°C. SNR data are rounded. Measurement bandwidth: 0.1 Hz to 0.413 f<sub>DATA</sub>.

## 表 2. High-Resolution Mode Noise Performance (Chop Disabled)<sup>(1)</sup>

|                         |     |      | SNR (dB) |     |     | INPUT-REFERRED NOISE (μV <sub>RMS</sub> ) |      |      | )    |      |  |

|-------------------------|-----|------|----------|-----|-----|-------------------------------------------|------|------|------|------|--|

| f <sub>DATA</sub> (SPS) |     | GAIN |          |     |     | GAIN                                      |      |      |      |      |  |

|                         | 1   | 2    | 4        | 8   | 16  | 1                                         | 2    | 4    | 8    | 16   |  |

| 62.5                    | 125 | 125  | 123      | 120 | 114 | 0.99                                      | 0.52 | 0.31 | 0.23 | 0.23 |  |

| 125                     | 122 | 122  | 121      | 119 | 114 | 1.36                                      | 0.70 | 0.39 | 0.26 | 0.22 |  |

| 250                     | 119 | 119  | 118      | 116 | 113 | 1.90                                      | 0.97 | 0.54 | 0.34 | 0.26 |  |

| 500                     | 116 | 116  | 116      | 114 | 111 | 2.70                                      | 1.38 | 0.73 | 0.43 | 0.32 |  |

| 1000                    | 113 | 113  | 113      | 111 | 109 | 3.85                                      | 1.95 | 1.03 | 0.60 | 0.41 |  |

<sup>(1)</sup> Typical performance data at  $T_A = 25$ °C. SNR data are rounded. Measurement bandwidth: 0.1 Hz to 0.413  $f_{DATA}$ .

# 表 3. Low-Power Mode Noise Performance (Chop Enabled, Offset Enabled)<sup>(1)</sup>

|                         |     |     | SNR (dB) |     |     | ı    | NPUT-REF | ERRED NO | ISE (µV <sub>RMS</sub> | )    |

|-------------------------|-----|-----|----------|-----|-----|------|----------|----------|------------------------|------|

| f <sub>DATA</sub> (SPS) |     |     | GAIN     |     |     | GAIN |          |          |                        |      |

|                         | 1   | 2   | 4        | 8   | 16  | 1    | 2        | 4        | 8                      | 16   |

| 62.5                    | 123 | 123 | 122      | 121 | 118 | 1.33 | 0.66     | 0.36     | 0.20                   | 0.14 |

| 125                     | 120 | 119 | 119      | 118 | 115 | 1.86 | 0.96     | 0.50     | 0.29                   | 0.20 |

| 250                     | 117 | 116 | 116      | 115 | 112 | 2.65 | 1.36     | 0.70     | 0.41                   | 0.29 |

| 500                     | 113 | 113 | 113      | 112 | 109 | 3.81 | 1.91     | 1.01     | 0.58                   | 0.40 |

| 1000                    | 110 | 110 | 110      | 109 | 106 | 5.50 | 2.79     | 1.48     | 0.84                   | 0.58 |

<sup>(1)</sup> Typical performance data at  $T_A = 25$ °C. SNR data are rounded. Measurement bandwidth: 0.1 Hz to 0.413  $f_{DATA}$ .

#### 表 4. Low-Power Mode Noise Performance (Chop Disabled, Offset Enabled) (1)

|                         |     |     | SNR (dB) |     |     |      | NPUT-REF | ERRED NO | ISE (µV <sub>RMS</sub> | )    |

|-------------------------|-----|-----|----------|-----|-----|------|----------|----------|------------------------|------|

| f <sub>DATA</sub> (SPS) |     |     | GAIN     |     |     |      |          | GAIN     |                        |      |

|                         | 1   | 2   | 4        | 8   | 16  | 1    | 2        | 4        | 8                      | 16   |

| 62.5                    | 122 | 122 | 121      | 118 | 113 | 1.36 | 0.71     | 0.40     | 0.29                   | 0.24 |

| 125                     | 119 | 119 | 118      | 116 | 112 | 1.90 | 0.97     | 0.53     | 0.36                   | 0.29 |

| 250                     | 116 | 116 | 115      | 114 | 110 | 2.67 | 1.38     | 0.74     | 0.46                   | 0.35 |

| 500                     | 113 | 113 | 113      | 111 | 108 | 3.75 | 1.93     | 1.02     | 0.62                   | 0.46 |

| 1000                    | 110 | 110 | 110      | 108 | 105 | 5.53 | 2.80     | 1.48     | 0.88                   | 0.62 |

<sup>(1)</sup> Typical performance data at T<sub>A</sub> = 25°C. SNR data are rounded. Measurement bandwidth: 0.1 Hz to 0.413 f<sub>DATA</sub>.

# 9 Detailed Description

#### 9.1 Overview

The ADS1287 is a low-power, high-resolution analog-to-digital converter (ADC) intended for energy exploration, low-power seismic-data acquisition nodes, and other exacting applications that require very low power consumption. The converter provides 31-bit resolution over data rates 62.5 SPS to 1000 SPS, and programmable gains of 1 to 16 that expand the measurement resolution; see the *Functional Block Diagram* section.

The ADC consists of an input multiplexer (MUX), a low-noise complementary metal oxide semiconductor (CMOS) programmable gain amplifier (PGA), a fourth order delta-sigma ( $\Delta\Sigma$ ) modulator, an infinite impulse response (IIR) high-pass filter (HPF), a finite-impulse-response (FIR) low-pass filter (LPF), and an SPI-compatible serial interface used for both device configuration and conversion data readback.

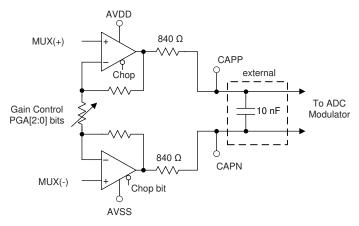

The signal multiplexer selects between the external input or internal short (via  $400-\Omega$  resistors). The internal short is used for offset calibration and to verify the ADC offset and noise performance. The input multiplexer is followed by a programmable-gain, CMOS PGA, featuring low noise. The available PGA gains are 1 V/V, 2 V/V, 4 V/V, 8 V/V, and 16 V/V. The PGA is chopped to reduce 1/f noise and input offset voltage. The PGA output is routed to the modulator and to the CAPP and CAPN pins. An external 10-nF capacitor connected to these pins filters the modulator sampling pulses and provides the ADC antialias filter.

The inherently-stable, fourth-order,  $\Delta\Sigma$  modulator measures the differential input signal  $V_{IN} = V_{(AINP)} - V_{(AINN)}$  against the differential reference  $V_{REF} = V_{(REFP)} - V_{(REFN)}$ . The ADC requires an external 2.5-V voltage reference. The modulator output data are processed by an integrated digital filter to provide the final conversion result.

The digital filter consists of a sinc filter followed by a programmable-phase, FIR low-pass filter and programmable-frequency, IIR high-pass filter. The HPF removes DC and low-frequency components from the conversion result.

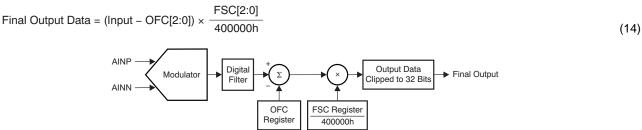

Programmable gain and offset data registers calibrate the conversion result to remove offset and gain errors.

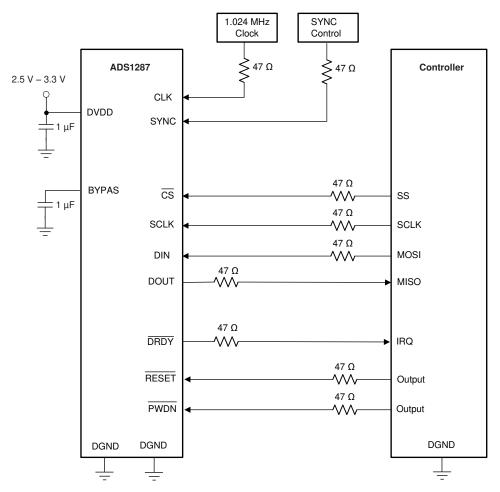

The SYNC input pin synchronizes the ADC. Synchronization has two programable modes of ope<u>ration:</u> pulse-synchronization and continuous-synchronization that accepts a synchronizing-clock input. The RESET input resets the ADC including the register settings.

# Overview (continued)

The PWDN input powers-down the ADC. The low-power STANDBY mode is engaged by software command.

RESET and SYNC control inputs are noise-resistant, Schmitt-trigger inputs to increase reliability in high-noise environments.

The ADC has an SPI-compatible serial interface. The interface is 4-wire and is used to read conversion data and to read and write device registers.

Power to the analog section is provided through AVDD and AVSS. DVDD is the digital and I/O supply. DVDD is sub-regulated to 1.8 V by an integrated, low-dropout regulator (LDO) to supply the digital core. The BYPAS pin is the LDO output and requires a 1-µF bypass capacitor.

#### 9.2 Functional Block Diagram

#### 9.3 Feature Description

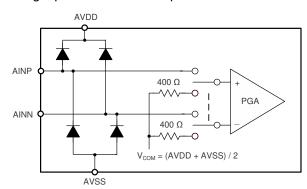

#### 9.3.1 Analog Input and Multiplexer

2 44. Analog Input and Multiplexer

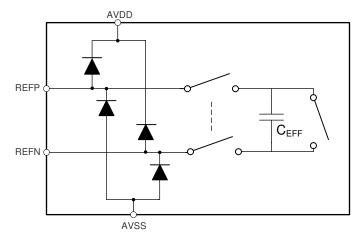

Electrostatic discharge (ESD) diodes are incorporated to protect the ADC inputs from ESD exposure that can occur during device manufacturing and printed circuit board (PCB) assembly process when assembled in an ESD-controlled environment. For system-level ESD protection, external ESD protection devices are recommended to protect device inputs or outputs that may be exposed to ESD events.

If either input is taken below AVSS -0.3 V, or above AVDD +0.3 V, the internal protection diodes can conduct. If these conditions are possible, use external clamp diodes, series resistors, or both to limit the maximum input current to the specified value.

The input multiplexer selects between the external input or the internal (shorted) input. The internal short is via two  $400-\Omega$  resistors to analog mid-supply voltage ( $V_{COM}$ ). The thermal noise of the resistors is equivalent to the noise produced by common geophones. Use the internal short connection to verify the ADC offset voltage and noise performance, and to provide an input to calibrate the ADC offset voltage. 表 5 summarizes the register selections of the multiplexer configurations related to 244.

#### 表 5. Input Multiplexer Modes

| MUX[1:0] REGISTER BITS | DESCRIPTION                                                                                  |