ADS127L11 JAJSLQ5C - APRIL 2021 - REVISED SEPTEMBER 2022

# ADS127L11 400kSPS、広帯域、24 ビット、デルタ・シグマ ADC

## 1 特長

- データ・レートをプログラム可能:

- 最大 400kSPS (広帯域フィルタ)

- 最大 1.067MSPS (低レイテンシ・フィルタ)

- デジタル・フィルタを選択可能:

- 広帯域または低レイテンシ

- AC 精度および DC 精度:

- ダイナミック・レンジ:111.5dB (200kSPS)

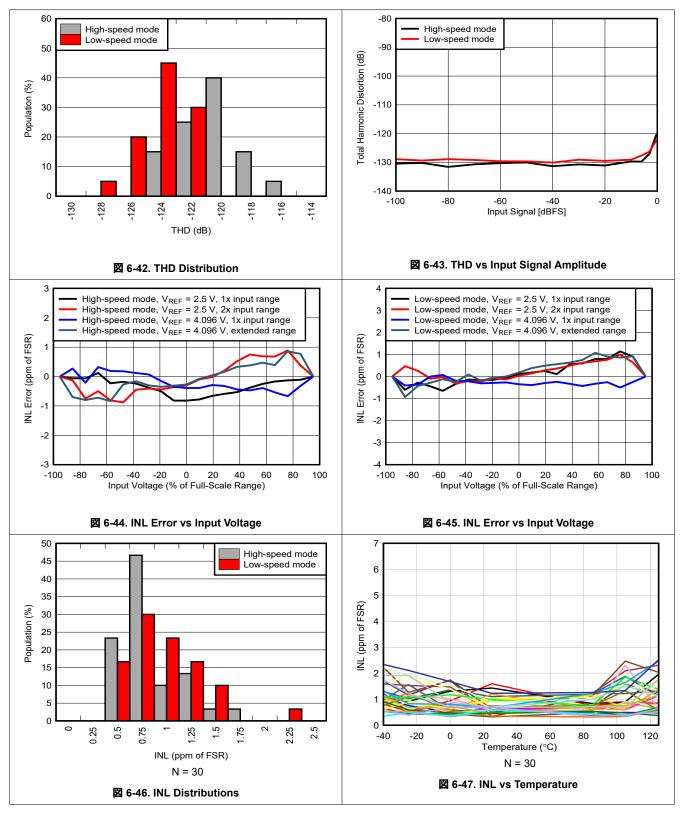

- THD:-120dB

- INL: 0.9ppm FS

- オフセット・ドリフト:50nV/℃

- ゲイン・ドリフト: 0.6ppm/℃

- 消費電力の拡張性が高いアーキテクチャ:

- 高速モード:400kSPS、18.6mW

- 低速モード:50kSPS、3.3mW

- 入力および基準電圧プリチャージ・バッファ

- 内部または外部クロック

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

# 2 アプリケーション

- 試験および測定機器:

- データ・アクイジション (DAQ)

- 衝撃および振動計測器

- 音響および動的歪みゲージ

- ファクトリ・オートメーション / 制御:

- 状況監視

- 航空宇宙/防衛:

- ソナー

- 医療:

- 脳波 (EEG)

- グリッド・インフラ:

- 電力品質分析器

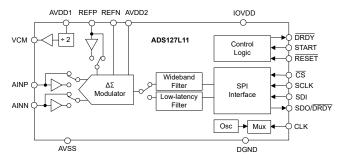

## 3 概要

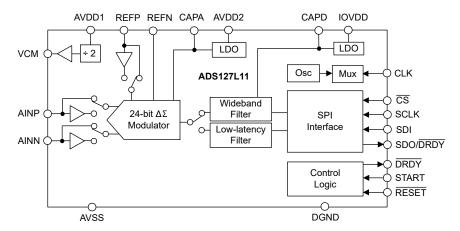

ADS127L11 は 24 ビットのデルタ・シグマ ( $\Delta\Sigma$ ) A/D コン バータ (ADC) で、データ・レートは広帯域フィルタ使用時 に最大 400kSPS、低レイテンシ・フィルタ使用時に最大 1067kSPS です。本デバイスは、低消費電力 (高速モー ドで 18.6mW) で優れた AC 性能と DC 精度を備えてい ます。

このデバイスには、入力バッファと基準電圧バッファが内 蔵されており、信号負荷を減らすことができます。低ドリフト の変調器は、優れた DC 精度を備えており、小さい帯域 内ノイズで AC 性能を向上しています。アーキテクチャ は、消費電力に関する拡張性が高く、データ・レート、分解 能、消費電力を最適化するために、2 つの速度モードを 備えています。

デジタル・フィルタは広帯域または低レイテンシの動作に 構成できるため、1 つのデバイスを広帯域の AC 特性か、 DC 信号のデータ・スループットのどちらかに最適化できま

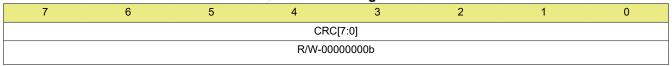

絶縁バリア越しの SPI I/O を簡素化するため、シリアル・イ ンターフェイスはデイジー・チェーン機能を備えています。 通信の信頼性を高めるため、入出力データは巡回冗長検 査 (CRC) で検証されます。

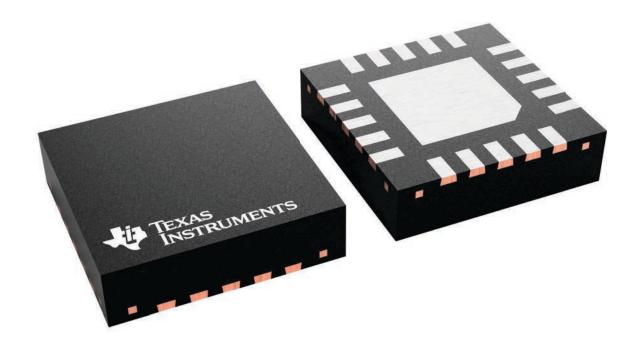

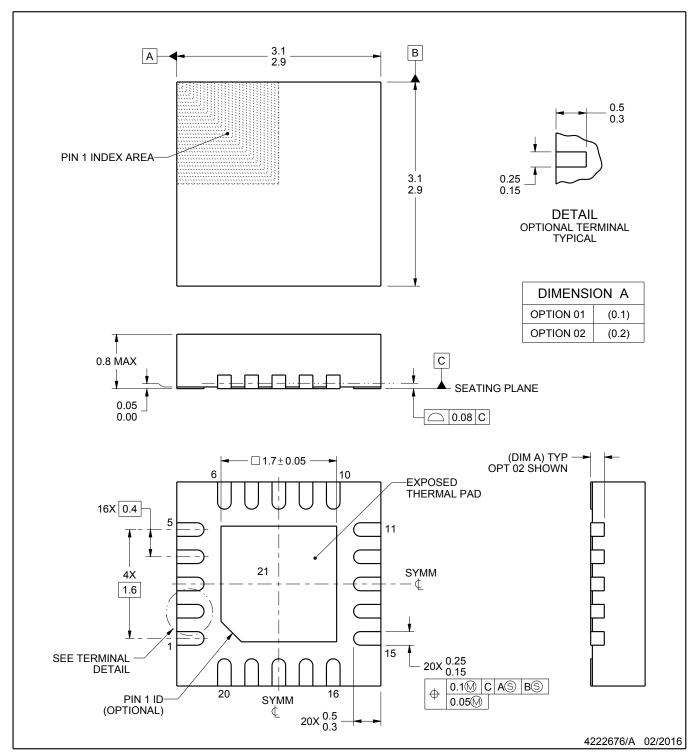

小型の 3mm × 3mm WQFN パッケージと 6.5mm × 4.4mm TSSOP パッケージは省スペースのアプリケーショ ンに適しています。本デバイスは、-40℃~+125℃の温度 範囲について完全に動作が規定されています。

#### パッケージ情報<sup>(1)</sup>

| 部品番号       | 部品番号 パッケージ     |                 |

|------------|----------------|-----------------|

| ADS127I 11 | RUK (WQFN, 20) | 3.00mm × 3.00mm |

|            | PW (TSSOP, 20) | 6.50mm × 4.40mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

概略ブロック図

## **Table of Contents**

| <b>1</b> 特長 1                                           | 7.9 INL Error Measurement25                            |

|---------------------------------------------------------|--------------------------------------------------------|

| 2 アプリケーション1                                             | 7.10 THD Measurement25                                 |

| 3 概要                                                    | 7.11 SFDR Measurement                                  |

| 4 Revision History2                                     | 7.12 Noise Performance26                               |

| 5 Pin Configuration and Functions3                      | 8 Detailed Description29                               |

| 6 Specifications4                                       | 8.1 Overview29                                         |

| 6.1 Absolute Maximum Ratings4                           | 8.2 Functional Block Diagram29                         |

| 6.2 ESD Ratings                                         | 8.3 Feature Description30                              |

| 6.3 Recommended Operating Conditions5                   | 8.4 Device Functional Modes44                          |

| 6.4 Thermal Information5                                | 8.5 Programming49                                      |

| 6.5 Electrical Characteristics6                         | 8.6 Registers60                                        |

| 6.6 Timing Requirements (1.65 V ≤ IOVDD ≤ 2 V) 10       | 9 Application and Implementation72                     |

| 6.7 Switching Characteristics (1.65 V ≤ IOVDD ≤ 2 V) 10 | 9.1 Application Information72                          |

| 6.8 Timing Requirements (2 V < IOVDD ≤ 5.5 V)11         | 9.2 Typical Application73                              |

| 6.9 Switching Characteristics (2 V < IOVDD ≤ 5.5 V) 11  | 9.3 Power Supply Recommendations76                     |

| 6.10 Timing Diagrams12                                  | 9.4 Layout                                             |

| 6.11 Typical Characteristics                            | 10 Device and Documentation Support78                  |

| 7 Parameter Measurement Information23                   | 10.1 Documentation Support78                           |

| 7.1 Offset Error Measurement23                          | 10.2 Receiving Notification of Documentation Updates78 |

| 7.2 Offset Drift Measurement23                          | <b>10.3</b> サポート・リソース                                  |

| 7.3 Gain Error Measurement23                            | 10.4 Trademarks78                                      |

| 7.4 Gain Drift Measurement23                            | 10.5 Electrostatic Discharge Caution78                 |

| 7.5 NMRR Measurement23                                  | 10.6 Glossary                                          |

| 7.6 CMRR Measurement24                                  | 11 Mechanical, Packaging, and Orderable                |

| 7.7 PSRR Measurement24                                  | Information78                                          |

| 7.8 SNR Measurement25                                   |                                                        |

|                                                         |                                                        |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| C | hanges from Revision B (April 2022) to Revision C (September 2022)                                           | Page             |

|---|--------------------------------------------------------------------------------------------------------------|------------------|

| • | RUK (WQFN) パッケージをプレビューから量産データに変更                                                                             | 1                |

| • | Changed AVDD1 to DGND specification in Recommended Operating Conditions section                              |                  |

| • | Changed high-speed mode analog input precharge buffers off current drift specifications in <i>Electrical</i> |                  |

|   | Characterisics section                                                                                       | 6                |

| • | Changed REFP input precharge buffer on current drift specification in Electrical Characterisics section      | 6                |

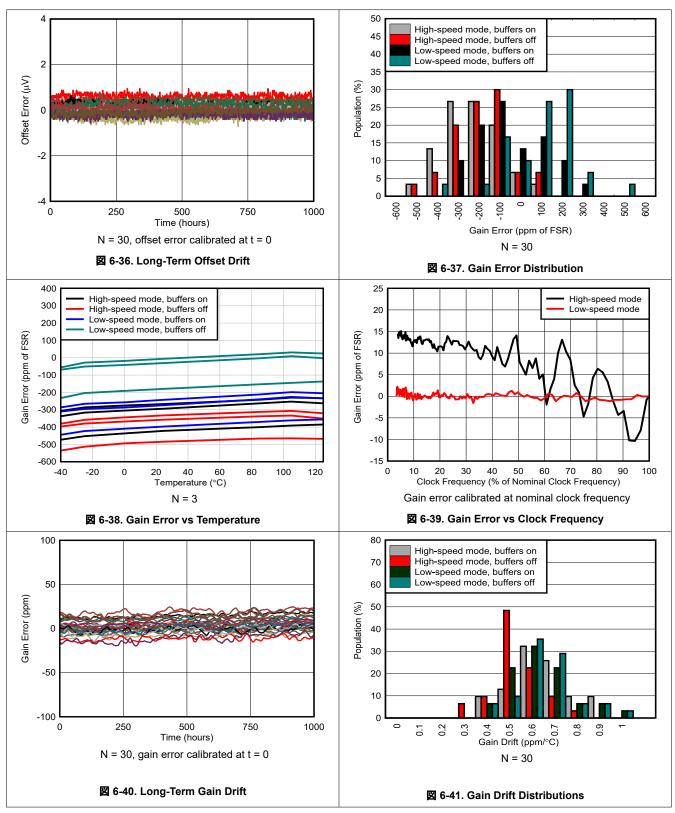

| • | Added Long-Term Offset Drift and Long-Term Gain Drift plots to Typical Characteristics section               | 13               |

| • | Added second paragraph to Internal Oscillator section                                                        | 34               |

| • | Added footnote to Wideband Filter Characteristics table in Wideband Filter section                           | 35               |

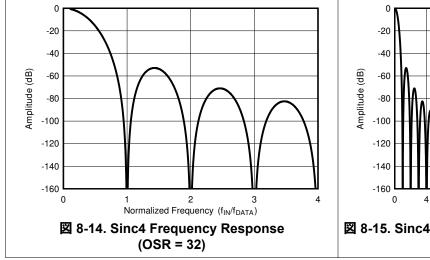

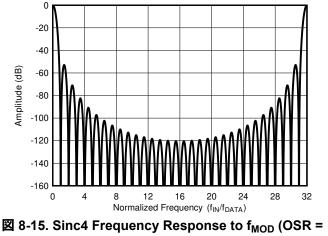

| • | Added footnote to Sinc4 Filter Characteristics table in Sinc4 Filter section                                 | 38               |

| • | Added footnote to Sinc4 + Sinc1 Filter Characteristics table in Sinc4 + Sinc1 Filter section                 | <mark>39</mark>  |

| • | Changed Digital Supply Threshold and Analog Supply Threshold figures in Power-On Reset section               | 43               |

| С | hanges from Revision A (October 2021) to Revision B (April 2022)                                             | Page             |

| • | Changed INL specification in <i>Electrical Characteristics</i> section                                       | 6                |

| • | Changed SPI CRC section                                                                                      | <mark>5</mark> 0 |

# **5 Pin Configuration and Functions**

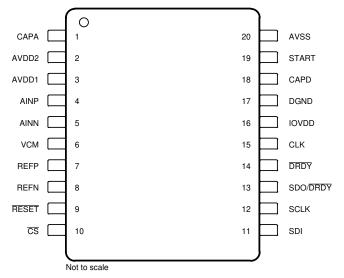

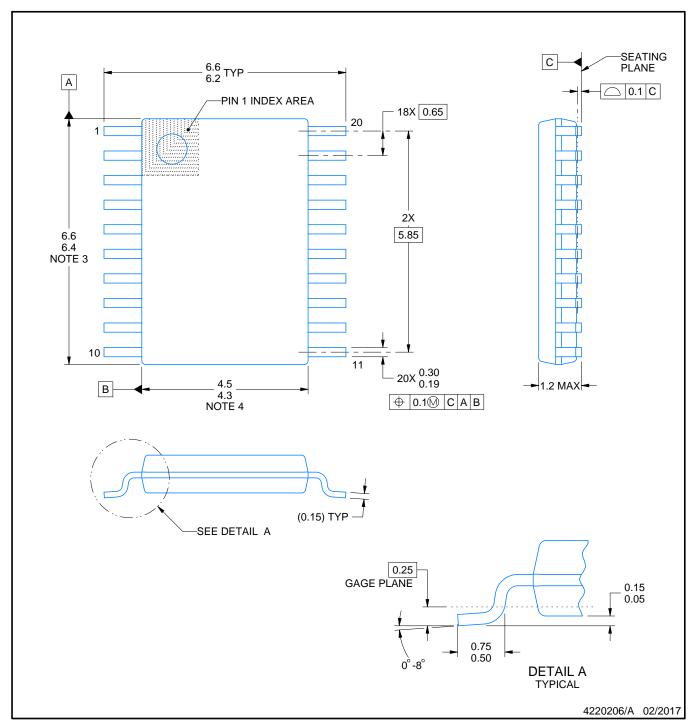

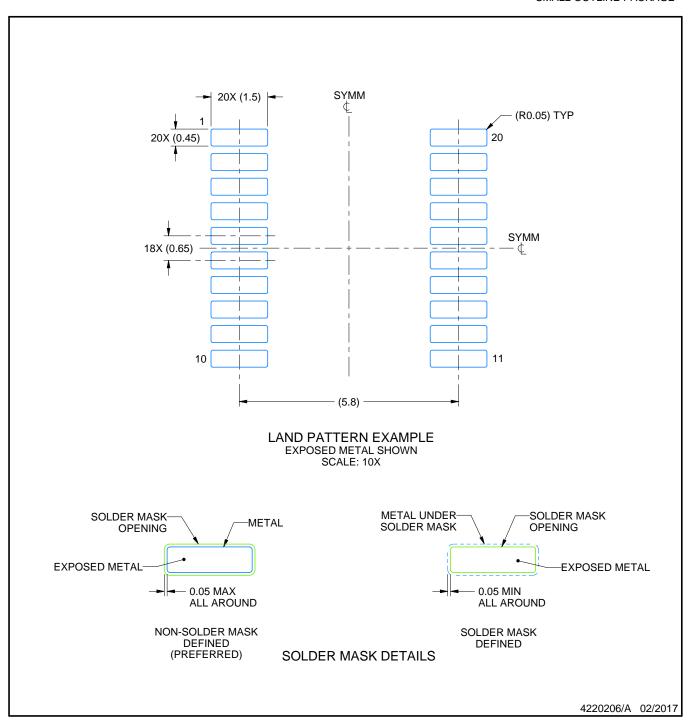

図 5-1. PW Package, 20-Pin TSSOP (Top View)

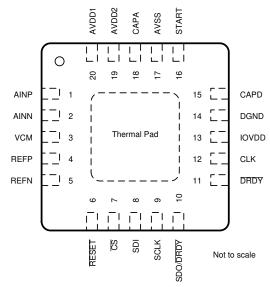

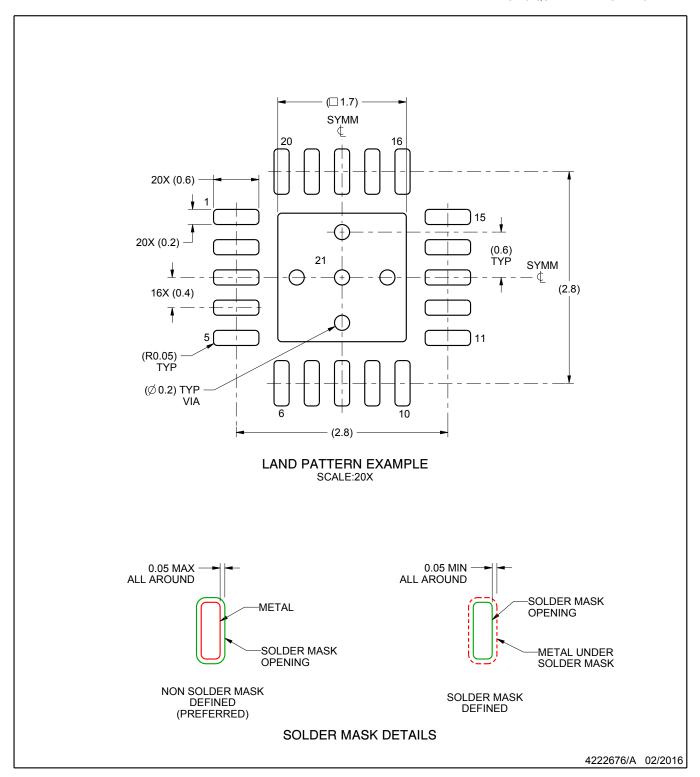

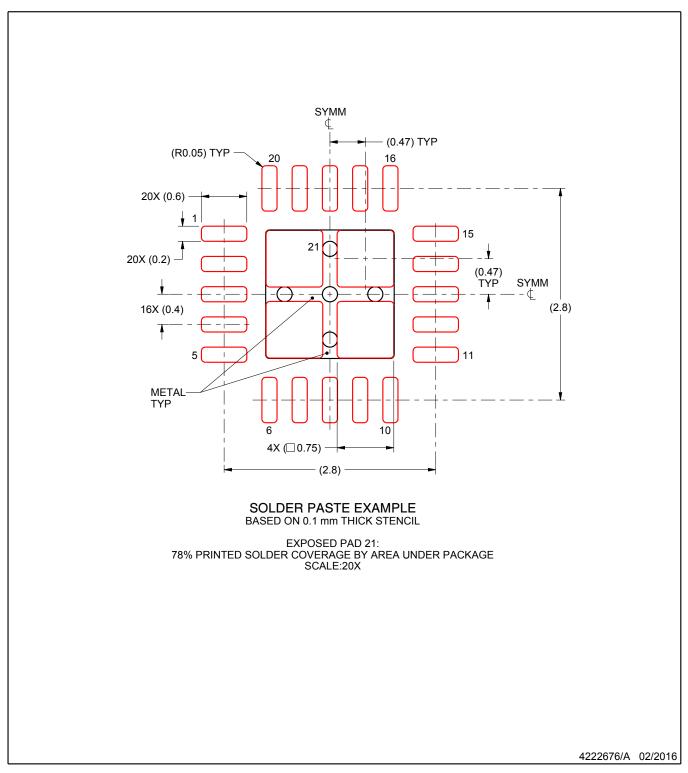

図 5-2. RUK Package, 20-Pin WQFN (Top View)

表 5-1. Pin Functions

| NAME        | PIN NO. |      | 1/0            | DESCRIPTION                                                                         |  |  |  |

|-------------|---------|------|----------------|-------------------------------------------------------------------------------------|--|--|--|

| NAME        | TSSOP   | WQFN | l/O            | DESCRIPTION                                                                         |  |  |  |

| AINN        | 5       | 2    | Analog input   | Negative analog input; see the Analog Input section for details                     |  |  |  |

| AINP        | 4       | 1    | Analog input   | Positive analog input; see the <i>Analog Input</i> section for details              |  |  |  |

| AVDD1       | 3       | 20   | Analog Supply  | ositive analog supply 1; see the <i>Power Supplies</i> section for details          |  |  |  |

| AVDD2       | 2       | 19   | Analog Supply  | Positive analog supply 2; see the <i>Power Supplies</i> section for details         |  |  |  |

| AVSS        | 20      | 17   | Analog Supply  | Negative analog supply; see the <i>Power Supplies</i> section for details           |  |  |  |

| CAPA        | 1       | 18   | Analog output  | nalog voltage regulator output capacitor bypass                                     |  |  |  |

| CAPD        | 18      | 15   | Analog output  | Digital voltage regulator output capacitor bypass                                   |  |  |  |

| CLK         | 15      | 12   | Digital input  | Clock input; see the Clock Operation section for details                            |  |  |  |

| CS          | 10      | 7    | Digital input  | Chip select, active low; see the Chip Select section for details                    |  |  |  |

| DGND        | 17      | 14   | Ground         | Digital ground                                                                      |  |  |  |

| DRDY        | 14      | 11   | Digital output | Data ready, active low; see the Data Ready section for details                      |  |  |  |

| IOVDD       | 16      | 13   | Digital Supply | I/O supply voltage; see the <i>Power Supplies</i> section for details               |  |  |  |

| REFN        | 8       | 5    | Analog input   | Negative reference input; see the Reference Voltage section for details             |  |  |  |

| REFP        | 7       | 4    | Analog input   | Positive reference input; see the Reference Voltage section for details             |  |  |  |

| RESET       | 9       | 6    | Digital input  | Reset, active low; see the <i>Reset</i> section for details                         |  |  |  |

| SCLK        | 12      | 9    | Digital input  | Serial data clock; see the Serial Clock section for details                         |  |  |  |

| SDI         | 11      | 8    | Digital input  | Serial data input; see the Serial Data Input section for details                    |  |  |  |

| SDO/DRDY    | 13      | 10   | Digital output | Serial data output and data ready (optional); see the SDO/DRDY section for details  |  |  |  |

| START       | 19      | 16   | Digital input  | Conversion start; see the <i>Synchronization</i> section for details                |  |  |  |

| VCM         | 6       | 3    | Analog output  | Common-mode voltage buffered output; see the VCM Output Voltage section for details |  |  |  |

| Thermal Pad | _       | Pad  | _              | Thermal power pad; connect to AVSS                                                  |  |  |  |

# **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted) (1)

|                              |                                                             | MIN        | MAX         | UNIT |  |

|------------------------------|-------------------------------------------------------------|------------|-------------|------|--|

|                              | AVDD1 to AVSS                                               | -0.3       | 6.5         |      |  |

|                              | AVDD2 to AVSS                                               | -0.3       | 6.5         |      |  |

| Power supply voltage         | AVSS to DGND                                                | -3         | 0.3         | V    |  |

|                              | IOVDD to DGND                                               | -0.3       | 6.5         |      |  |

|                              | IOVDD to AVSS                                               |            | 8.5         |      |  |

| Analog input voltage         | AINP, AINN, REFP, REFN                                      | AVSS - 0.3 | AVDD1 + 0.3 | V    |  |

|                              | CAPA                                                        | AVSS       | 1.65        |      |  |

| Analog output voltage        | CAPD                                                        | DGND       | 1.65        | V    |  |

|                              | VCM                                                         | AVSS       | AVDD1       |      |  |

| Digital input/autout valtage | SDO/DRDY, DRDY, START                                       | DGND - 0.3 | IOVDD + 0.3 | V    |  |

| Digital input/output voltage | CS, SCLK, SDI, RESET, CLK                                   | DGND - 0.3 | 6.5         | V    |  |

| Input current                | Continuous, any pin except power-supply pins <sup>(2)</sup> | -10        | 10          | mA   |  |

| Tomporatura                  | Junction, T <sub>J</sub>                                    |            | 150         | °C   |  |

| Temperature                  | Storage, T <sub>stg</sub>                                   | -65        | 150         | C    |  |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) Analog input pins AINP, AINN, REFP, and REFN are diode-clamped to AVDD1 and AVSS. Limit the input current to 10 mA in the event the analog input voltage exceeds AVDD1 + 0.3 V or AVSS 0.3 V. Digital input pin START and digital output pins SDO/DRDY and DRDY are diode-clamped to IOVDD and DGND. Digital input pins CS, SCLK, SDI, RESET and CLK are diode-clamped to DGND. Limit the input current to 10 mA in the event the digital input voltage exceeds IOVDD + 0.3 V (for effected pins) or exceeds DGND 0.3 V.

### 6.2 ESD Ratings

|                    |                                            |                                                                       | VALUE | UNIT |

|--------------------|--------------------------------------------|-----------------------------------------------------------------------|-------|------|

| V                  | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | 2000  | V    |

| V <sub>(ESD)</sub> | Liectiostatic discharge                    | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 1000  | '    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# **6.3 Recommended Operating Conditions**

over operating ambient temperature range (unless otherwise noted)

|                                                                 |                                                                                         |                                        | MIN                 | NOM         | MAX                | UNIT  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------|---------------------|-------------|--------------------|-------|

| POWER                                                           | SUPPLY                                                                                  |                                        |                     |             |                    |       |

|                                                                 |                                                                                         | AVDD1 to AVSS, high-speed mode         | 4.5                 |             | 5.5                |       |

|                                                                 |                                                                                         | AVDD1 to AVSS, low-speed mode          | 2.85                |             | 5.5                | V     |

|                                                                 | A = -1 =                                                                                | AVDD1 to DGND                          | 1.65                |             |                    |       |

|                                                                 | Analog power supply                                                                     | Absolute ratio of AVSS / AVDD1 to DGND |                     |             | 1.2                | V/V   |

|                                                                 |                                                                                         | AVDD2 to AVSS                          | 1.74                |             | 5.5                | .,    |

|                                                                 |                                                                                         | AVSS to DGND                           | -2.75               |             | 0                  | V     |

|                                                                 | Digital power supply                                                                    | IOVDD to DGND                          | 1.65                |             | 5.5                | V     |

| ANALO                                                           | G INPUTS                                                                                |                                        |                     |             |                    |       |

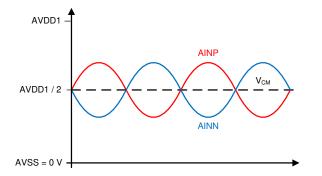

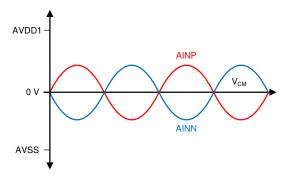

| V <sub>AINP</sub> ,<br>V <sub>AINN</sub> Absolute input voltage |                                                                                         | Precharge buffer off                   | AVSS - 0.05         | AVDD1 + 0.0 |                    | V     |

|                                                                 |                                                                                         | Precharge buffer on                    | AVSS + 0.1          |             | AVDD1 – 0.1        | V     |

| V <sub>IN</sub>                                                 | Differential input voltage                                                              | 1x input range                         | -V <sub>REF</sub>   |             | $V_{REF}$          | V     |

|                                                                 | $V_{IN} = V_{AINP} - V_{AINN}$                                                          | 2x input range                         | -2·V <sub>REF</sub> |             | 2·V <sub>REF</sub> | V     |

| VOLTAC                                                          | SE REFERENCE INPUTS                                                                     |                                        |                     |             |                    |       |

| V <sub>REF</sub>                                                | Differential reference voltage V <sub>REF</sub> = V <sub>REFP</sub> - V <sub>REFN</sub> | Low-reference range                    | 0.5                 | 2.5         | 2.75               | V     |

|                                                                 |                                                                                         | High-reference range                   | 1                   | 4.096       | AVDD1 – AVSS       | V     |

| V <sub>REFN</sub>                                               | Negative reference voltage                                                              |                                        | AVSS - 0.05         |             |                    | V     |

| .,                                                              | Daniti a mafamana a salta na                                                            | REFP precharge buffer off              |                     |             | AVDD1 + 0.05       | V     |

| $V_{REFP}$                                                      | Positive reference voltage                                                              | REFP precharge buffer on               |                     | AVDD1 - 0.7 | V                  |       |

| EXTER                                                           | NAL CLOCK SOURCE                                                                        |                                        |                     |             |                    |       |

| _                                                               | Clock frequency                                                                         | High-speed mode                        | 0.5                 | 25.6        | 26.2               | MHz   |

| f <sub>CLK</sub>                                                | Clock frequency                                                                         | Low-speed mode                         | 0.5                 | 3.2         | 3.28               | IVITZ |

| DIGITAL                                                         | INPUTS                                                                                  |                                        |                     |             |                    |       |

| V <sub>IL</sub>                                                 | Logic input voltage, low                                                                |                                        | DGND                |             | 0.3·IOVDD          | V     |

| V <sub>IH</sub>                                                 | Logic input voltage, high                                                               |                                        | 0.7·IOVDD           |             | IOVDD              | V     |

| TEMPE                                                           | RATURE RANGE                                                                            |                                        |                     |             |                    |       |

| T <sub>A</sub>                                                  | Operating ambient temperature                                                           |                                        | -45                 |             | 125                | °C    |

### **6.4 Thermal Information**

| THERMAL METRIC (1)    |                                              | ADS127L11  |            |      |

|-----------------------|----------------------------------------------|------------|------------|------|

|                       |                                              | WQFN (RUK) | TSSOP (PW) | UNIT |

|                       |                                              | 20 PINS    | 20 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 46.0       | 92.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 43.9       | 32.9       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 19.9       | 44.4       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.7        | 2.2        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 19.9       | 43.9       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.1        | n/a        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD1 = 5 V, AVDD2 = 1.8 V to 5 V, AVSS = 0 V, IOVDD = 1.8 V,  $V_{IN} = 0$  V,  $V_{CM} = 2.5$  V,  $V_{REFP} = 4.096$  V,  $V_{REFN} = 0$  V, high-reference range, 1x input range,  $f_{CLK} = 25.6$  MHz (high-speed mode),  $f_{CLK} = 3.2$  MHz (low-speed mode), input precharge buffers on, and reference precharge buffer on (unless otherwise noted)

|                   | PARAMETER                                       | and reference prech                                         | ONDITIONS                     | MIN          | TYP                   | MAX  | UNIT             |

|-------------------|-------------------------------------------------|-------------------------------------------------------------|-------------------------------|--------------|-----------------------|------|------------------|

| ANALO             | G INPUTS, HIGH-SPEED MODE                       |                                                             |                               |              |                       |      |                  |

|                   |                                                 | Precharge buffers off                                       |                               |              | 95                    |      |                  |

|                   | Input current,                                  | Precharge buffers off, 2x input range                       |                               | 47           |                       |      | μA/V             |

|                   | differential input voltage                      | Precharge buffers on                                        |                               |              | ±3                    |      | μA               |

|                   |                                                 | Precharge buffers off                                       |                               |              | 3                     |      | -                |

|                   | Input current drift,                            | Precharge buffers off, 2x input range                       |                               |              | 1.5                   |      | nA/V/°C          |

|                   | differential input voltage                      | Precharge buffers on                                        |                               |              | 5                     |      | nA/°C            |

|                   |                                                 | Precharge buffers off                                       |                               |              | 5                     |      |                  |

|                   | Input current, common-mode input voltage        | Precharge buffers off, 2:                                   | x input range                 |              | 2.5                   |      | μA/V             |

|                   | common-mode input voltage                       | Precharge buffers on                                        |                               |              | ±3                    |      | μA               |

| ANALO             | G INPUTS, LOW-SPEED MODE                        |                                                             |                               |              |                       |      |                  |

|                   |                                                 | Precharge buffers off                                       |                               |              | 12                    |      |                  |

|                   | Input current,                                  | Precharge buffers off, 2:                                   | x input range                 |              | 6                     |      | μA/V             |

|                   | differential input voltage                      | Precharge buffers on                                        |                               |              | ±0.4                  |      | μA               |

|                   |                                                 | Precharge buffers off                                       |                               |              | 1                     |      |                  |

|                   | Input current drift, differential input voltage | Precharge buffers off 2x input range                        |                               |              | 0.5                   |      | nA/V/°C          |

|                   | umerential input voltage                        | Precharge buffers on                                        | <u> </u>                      |              | 0.2                   |      | nA/°C            |

|                   |                                                 | Precharge buffers off                                       |                               |              | 0.6                   |      |                  |

|                   | Input current,                                  | Precharge buffers off, 2x input range                       |                               |              | 0.3                   |      | μA/V             |

|                   | common-mode input voltage                       | Precharge buffers on                                        |                               |              | ±0.4                  |      | μA               |

| DC PER            | FORMANCE                                        |                                                             |                               |              |                       |      |                  |

|                   | Resolution                                      | OSR ≥ 64                                                    |                               |              | 24                    |      | Bits             |

|                   | Noise                                           |                                                             |                               | See Noise Pe | rformance for details |      |                  |

|                   |                                                 | High-speed mode, low-latency filter                         |                               | 0.08 1067    |                       |      |                  |

|                   |                                                 | High-speed mode, wideband filter                            |                               | 3.125        |                       | 400  |                  |

| † <sub>DATA</sub> | Output data rate                                | Low-speed mode, low-latency filter                          |                               | 0.01         |                       | 133  | kSPS             |

|                   |                                                 | Low-speed mode, wideband filter                             |                               | 0.390625     |                       | 50   |                  |

|                   |                                                 | D 161 11 1                                                  |                               |              | 0.9                   | 5.5  | ppm of           |

| INL               | Integral nonlinearity                           | Best-fit method                                             | T <sub>A</sub> = 25°C to 85°C |              |                       | 4    | FSR              |

|                   | Offset error                                    | T <sub>A</sub> = 25°C                                       |                               | -250         | ±30                   | 250  | μV               |

|                   | Offset drift                                    |                                                             |                               |              | 50                    | 200  | nV/°C            |

|                   | Gain error                                      | T <sub>A</sub> = 25°C                                       |                               | -2000        | ±200                  | 2000 | ppm of<br>FSR    |

|                   | Gain drift                                      |                                                             |                               |              | 0.6                   | 1.9  | ppm of<br>FSR/°C |

| NMRR              | Normal mode rejection ratio                     | f <sub>IN</sub> = 50 Hz (±1 Hz), f <sub>DAT</sub>           | A = 50 SPS                    | 100          |                       |      | dB               |

| INIVIRK           | Normal-mode rejection ratio                     | f <sub>IN</sub> = 60 Hz (±1 Hz), f <sub>DATA</sub> = 60 SPS |                               | 100          |                       |      | uБ               |

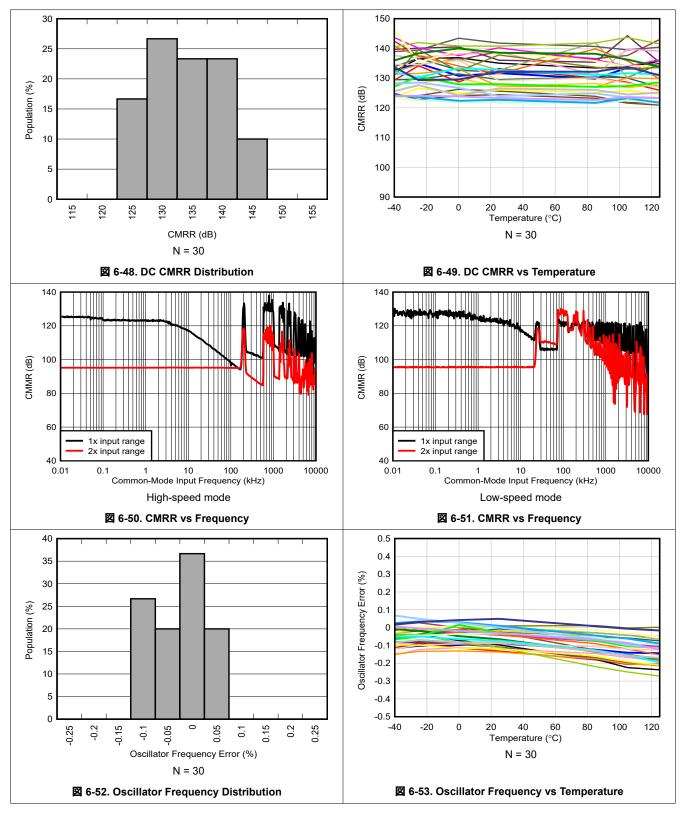

|                   |                                                 | At dc                                                       |                               | 110          | 130                   |      |                  |

| CMRR              | Common-mode rejection ratio                     | Up to 10 kHz                                                |                               |              | 115                   |      | dB               |

|                   |                                                 | At dc, 2x input range                                       |                               |              | 95                    |      |                  |

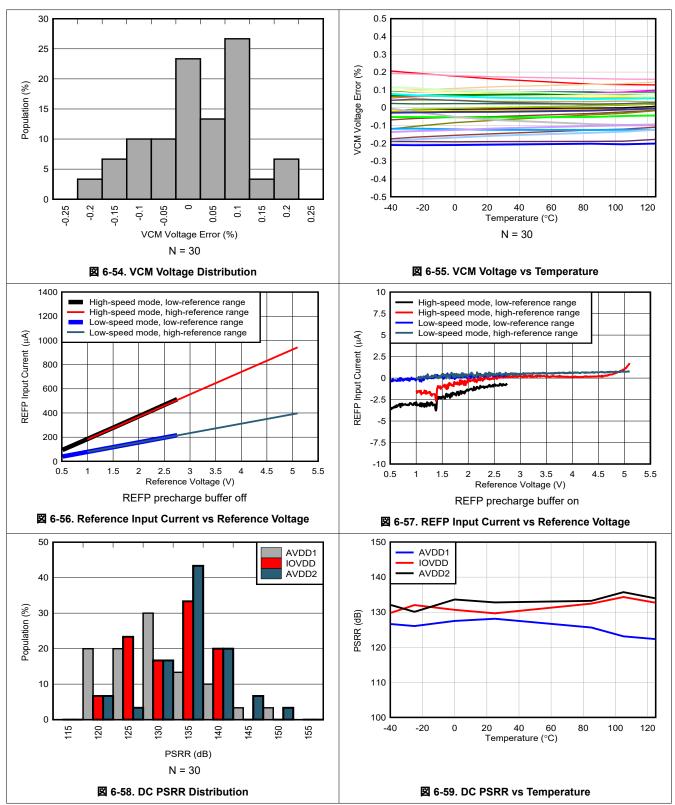

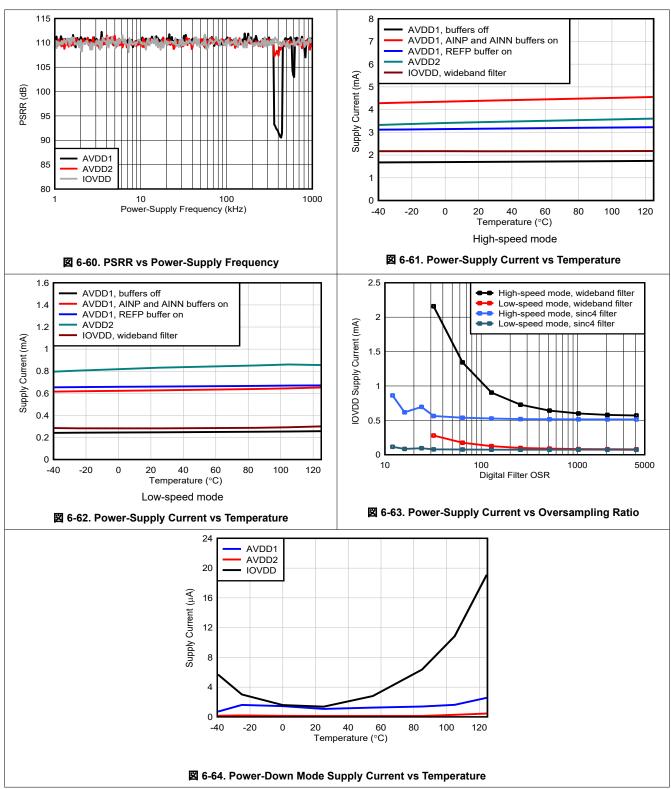

|                   |                                                 | AVDD1, dc                                                   |                               | 100          | 120                   |      |                  |

| PSRR              | Power-supply rejection ratio                    | AVDD2, dc                                                   |                               | 115          | 130                   |      | dB               |

|                   | Tower-supply rejection ratio                    | IOVDD, dc                                                   |                               | 115          | 130                   |      |                  |

# **6.5 Electrical Characteristics (continued)**

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD1 = 5 V, AVDD2 = 1.8 V to 5 V, AVSS = 0 V, IOVDD = 1.8 V,  $V_{IN} = 0$  V,  $V_{CM} = 2.5$  V,  $V_{REFP} = 4.096$  V,  $V_{REFN} = 0$  V, high-reference range, 1x input range,  $f_{CLK} = 25.6$  MHz (high-speed mode),  $f_{CLK} = 3.2$  MHz (low-speed mode), input precharge buffers on, and reference precharge buffer on (unless otherwise noted)

| ,      | input precharge buffers or<br>PARAMETER |                                                                                                                                                                                      | CONDITIONS                                                         | MIN   | TYP   | MAX | UNIT |

|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------|-------|-----|------|

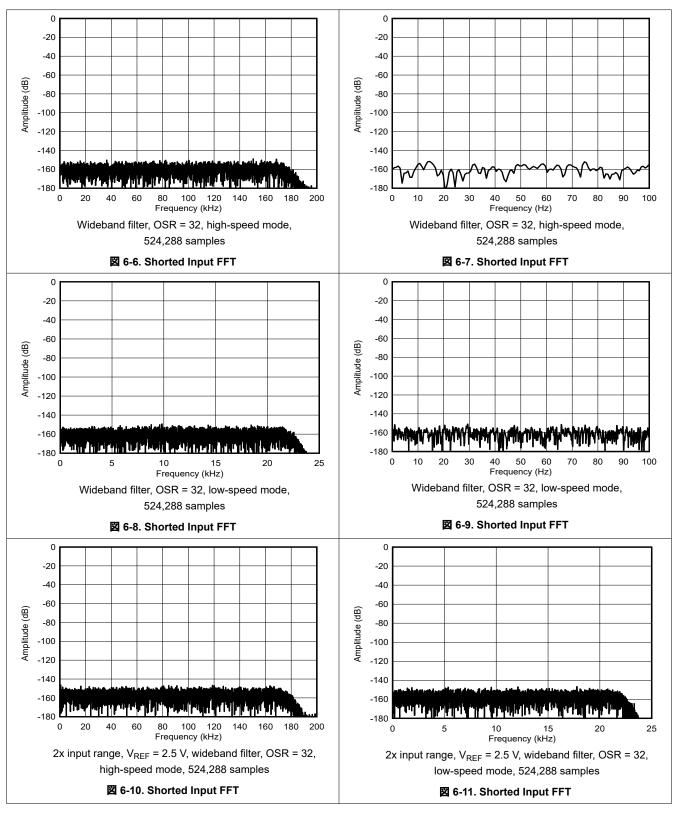

| AC PER | FORMANCE, HIGH-SPEED MOD                | DE                                                                                                                                                                                   |                                                                    |       |       |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter                                                    | 109   | 111.5 |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter,<br>V <sub>REF</sub> = 2.5 V                       |       | 107.5 |     |      |

| DR     | Di marria ranga                         | Inputs shorted,                                                                                                                                                                      | Wideband filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range    |       | 108.5 |     | ٩D   |

| JK     | Dynamic range                           | OSR = 64,<br>f <sub>DATA</sub> = 200 kSPS                                                                                                                                            | Low-latency filter                                                 | 112   | 114   |     | dB   |

|        |                                         |                                                                                                                                                                                      | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V                    |       | 110.5 |     |      |

|        |                                         |                                                                                                                                                                                      | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range |       | 111   |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter                                                    |       | 110   |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter,<br>V <sub>REF</sub> = 2.5 V                       |       | 106   |     |      |

| OND.   | Cinnal to make                          | $f_{IN} = 1 \text{ kHz},$ $V_{IN} = -0.2 \text{ dBFS},$                                                                                                                              | Wideband filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range    |       | 107   |     | ٠ID  |

| SNR    | Signal-to-noise ratio                   | OSR = 64,<br>f <sub>DATA</sub> = 200 kSPS,                                                                                                                                           | Low-latency filter                                                 |       | 112   |     | dB   |

|        |                                         | 9 harmonics                                                                                                                                                                          | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V                    |       | 108.5 |     |      |

|        |                                         |                                                                                                                                                                                      | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range |       | 110   |     |      |

| THD    | Total harmonic distortion               | $\begin{aligned} &f_{\text{IN}} = 1 \text{ kHz,} \\ &V_{\text{IN}} = -0.2 \text{ dBFS,} \\ &OSR = 64, \\ &f_{\text{DATA}} = 200 \text{ kSPS,} \\ &9 \text{ harmonics} \end{aligned}$ | Wideband filter                                                    |       | -120  |     | dB   |

| SFDR   | Spurious-free dynamic range             | f <sub>IN</sub> = 1 kHz, V <sub>IN</sub> = -0.2                                                                                                                                      | 2 dBFS, OSR = 64                                                   |       | 120   |     | dB   |

| AC PER | FORMANCE, LOW-SPEED MOD                 | DE                                                                                                                                                                                   |                                                                    |       |       |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter                                                    | 109   | 112   |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter,<br>V <sub>REF</sub> = 2.5 V                       |       | 107.5 |     |      |

| 20     |                                         | Inputs shorted,                                                                                                                                                                      | Wideband filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range    |       | 108.5 |     | 10   |

| DR     | Dynamic range                           | OSR = 64,<br>f <sub>DATA</sub> = 25 kSPS                                                                                                                                             | Low-latency filter                                                 | 111.5 | 114.5 |     | dB   |

|        |                                         |                                                                                                                                                                                      | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V                    |       | 110.5 |     |      |

|        |                                         |                                                                                                                                                                                      | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range |       | 111.5 |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter                                                    |       | 110   |     |      |

|        |                                         |                                                                                                                                                                                      | Wideband filter,<br>V <sub>REF</sub> = 2.5 V                       |       | 106   |     |      |

| SNID   | Signal-to-noise ratio                   | f <sub>IN</sub> = 1 kHz,<br>V <sub>IN</sub> = -0.2 dBFS,                                                                                                                             | Wideband filter,<br>V <sub>REF</sub> = 2.5 V,<br>2x input range    |       | 108   |     |      |

| SNR    | olynal-to-noise ratio                   | OSR = 64,                                                                                                                                                                            | Low-latency filter                                                 |       | 112   |     | dB   |

|        |                                         | f <sub>DATA</sub> = 25 kSPS                                                                                                                                                          | Low-latency filter,<br>V <sub>REF</sub> = 2.5 V                    |       | 108   |     |      |

|        |                                         |                                                                                                                                                                                      | Low-latency filter, V <sub>REF</sub> = 2.5 V, 2x input range       |       | 110   |     |      |

## 6.5 Electrical Characteristics (continued)

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD1 = 5 V, AVDD2 = 1.8 V to 5 V, AVSS = 0 V, IOVDD = 1.8 V,  $V_{\text{IN}} = 0$  V,  $V_{\text{CM}} = 2.5$  V,  $V_{\text{REFP}} = 4.096$  V,  $V_{\text{REFN}} = 0$  V, high-reference range, 1x input range,  $f_{\text{CLK}} = 25.6$  MHz (high-speed mode),  $f_{\text{CLK}} = 3.2$  MHz (low-speed mode), input precharge buffers on, and reference precharge buffer on (unless otherwise noted)

|                 | PARAMETER                                             | TEST CO                                                                                                                                                                               | ONDITIONS                                 | MIN         | TYP                        | MAX         | UNIT              |

|-----------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------|----------------------------|-------------|-------------------|

| THD             | Total harmonic distortion                             | $\begin{split} f_{\text{IN}} &= 1 \text{ kHz}, \\ V_{\text{IN}} &= -0.2 \text{ dBFS}, \\ \text{OSR} &= 64, \\ f_{\text{DATA}} &= 25 \text{ kSPS}, \\ 9 \text{ harmonics} \end{split}$ | Wideband filter                           |             | -125                       |             | dB                |

| SFDR            | Spurious-free dynamic range                           | $f_{IN} = 1 \text{ kHz}, V_{IN} = -0.2 \text{ c}$                                                                                                                                     | BFS, OSR = 64                             |             | 120                        |             | dB                |

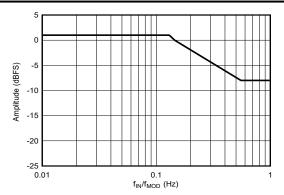

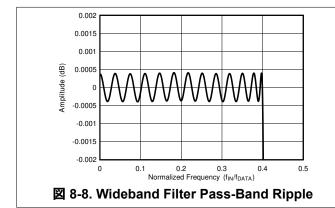

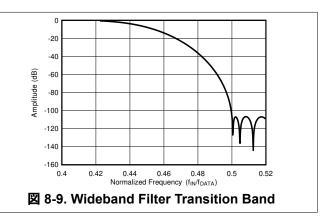

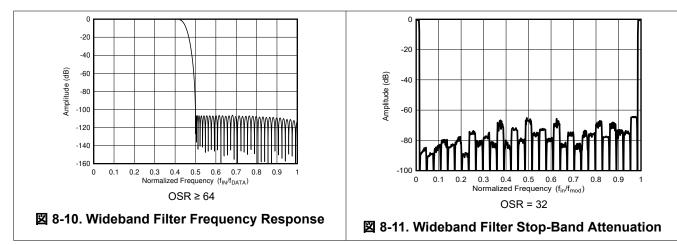

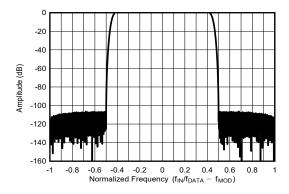

| WIDEBA          | ND FILTER CHARACTERISTICS                             |                                                                                                                                                                                       |                                           |             |                            |             |                   |

|                 |                                                       | Within envelope of pass                                                                                                                                                               | s-band ripple                             |             | 0.4 · f <sub>DATA</sub>    |             |                   |

|                 | Pass-band frequency                                   | -0.1-dB frequency                                                                                                                                                                     |                                           |             | 0.4125 · f <sub>DATA</sub> |             | Hz                |

|                 |                                                       | -3-dB frequency                                                                                                                                                                       |                                           |             | 0.4374 · f <sub>DATA</sub> |             |                   |

|                 | Pass-band ripple                                      |                                                                                                                                                                                       |                                           | -0.0004     |                            | 0.0004      | dB                |

|                 | Stop-band frequency                                   | At stop-band attenuatio                                                                                                                                                               | n                                         |             | 0.5 · f <sub>DATA</sub>    |             | Hz                |

|                 | Stop-band attenuation <sup>(1)</sup>                  |                                                                                                                                                                                       |                                           |             | 106                        |             | dB                |

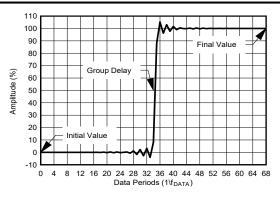

|                 | Group delay                                           |                                                                                                                                                                                       |                                           |             | 34 / f <sub>DATA</sub>     |             | s                 |

|                 | Settling time                                         |                                                                                                                                                                                       |                                           |             | 68 / f <sub>DATA</sub>     |             | s                 |

| VOLTAG          | E REFERENCE INPUTS                                    |                                                                                                                                                                                       |                                           |             |                            |             |                   |

|                 | REFP and REFN input current,                          | REFP precharge buffer                                                                                                                                                                 | off, high-speed mode                      |             | 190                        |             |                   |

|                 | differential reference voltage                        | REFP precharge buffer                                                                                                                                                                 | off, low-speed mode                       |             | 80                         |             | μA/V              |

|                 | REFP input current,<br>differential reference voltage | REFP precharge buffer                                                                                                                                                                 | on                                        |             | ±2                         |             | μA                |

|                 | REFP and REFN                                         | REFP precharge buffer                                                                                                                                                                 | off, high-speed mode                      |             | 10                         |             |                   |

|                 | input current drift                                   | REFP precharge buffer                                                                                                                                                                 | REFP precharge buffer off, low-speed mode |             | 10                         |             | nA/°C             |

|                 | REFP input current drift                              | REFP precharge buffer                                                                                                                                                                 | on                                        | 10          |                            |             |                   |

| INTERN          | AL OSCILLATOR                                         | <u>'</u>                                                                                                                                                                              |                                           |             |                            |             |                   |

|                 | _                                                     | High-speed mode                                                                                                                                                                       |                                           | 25.4        | 25.6                       | 25.8        |                   |

|                 | Frequency                                             | Low-speed mode                                                                                                                                                                        |                                           | 3.17        | 3.2                        | 3.23        | MHz               |

| VCM OU          | TPUT VOLTAGE                                          |                                                                                                                                                                                       |                                           |             |                            |             |                   |

|                 | Output voltage                                        |                                                                                                                                                                                       |                                           | (AVD        | D1 + AVSS) / 2             |             | V                 |

|                 | Accuracy                                              |                                                                                                                                                                                       |                                           | -1%         | ±0.1%                      | 1%          |                   |

|                 | Voltage noise                                         | 1-kHz bandwidth                                                                                                                                                                       |                                           |             | 25                         |             | μV <sub>RMS</sub> |

|                 | Start-up time                                         | C <sub>L</sub> = 100 nF                                                                                                                                                               |                                           |             | 1                          |             | ms                |

|                 | Capacitive load                                       |                                                                                                                                                                                       |                                           |             |                            | 100         | nF                |

|                 | Resistive load                                        |                                                                                                                                                                                       |                                           | 2           |                            |             | kΩ                |

|                 | Short-circuit current limit                           |                                                                                                                                                                                       |                                           |             | 10                         |             | mA                |

| DIGITAL         | INPUTS/OUTPUTS                                        |                                                                                                                                                                                       |                                           |             |                            |             |                   |

|                 | OUT DRV = 0b, I <sub>OL</sub> = 2 mA                  |                                                                                                                                                                                       |                                           |             | 0.2 · IOVDD                |             |                   |

| V <sub>OL</sub> | Logic-low output level                                | OUT_DRV = 1b, I <sub>OL</sub> = 1                                                                                                                                                     |                                           |             |                            | 0.2 · IOVDD | V                 |

|                 |                                                       | OUT_DRV = 0b, I <sub>OH</sub> = -                                                                                                                                                     |                                           | 0.8 · IOVDD |                            |             |                   |

| V <sub>OH</sub> | Logic-high output level                               | OUT_DRV = 1b, I <sub>OH</sub> = -                                                                                                                                                     |                                           | 0.8 · IOVDD |                            |             | V                 |

|                 | Input hysteresis                                      |                                                                                                                                                                                       |                                           |             | 150                        |             | mV                |

|                 | Input current                                         | Excluding RESET pin                                                                                                                                                                   |                                           | -1          |                            | 1           | μA                |

|                 | RESET pin pullup resistor                             |                                                                                                                                                                                       |                                           |             | 20                         |             | kΩ                |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

## 6.5 Electrical Characteristics (continued)

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD1 = 5 V, AVDD2 = 1.8 V to 5 V, AVSS = 0 V, IOVDD = 1.8 V,  $V_{IN} = 0$  V,  $V_{CM} = 2.5$  V,  $V_{REFP} = 4.096$  V,  $V_{REFN} = 0$  V, high-reference range, 1x input range,  $f_{CLK} = 25.6$  MHz (high-speed mode),  $f_{CLK} = 3.2$  MHz (low-speed mode), input precharge buffers on, and reference precharge buffer on (unless otherwise noted)

|                                           | PARAMETER                                               | TEST C                                       | ONDITIONS                              | MIN | TYP  | MAX  | UNIT  |

|-------------------------------------------|---------------------------------------------------------|----------------------------------------------|----------------------------------------|-----|------|------|-------|

| ANALO                                     | S SUPPLY CURRENT                                        |                                              |                                        |     |      |      |       |

|                                           |                                                         | High-speed mode                              |                                        |     | 1.7  | 1.85 | A     |

|                                           | AVDD1 and AVSS current                                  | Low-speed mode                               |                                        |     | 0.25 | 0.3  | mA    |

|                                           | (All buffers off)                                       | Standby mode                                 |                                        |     | 35   |      |       |

|                                           |                                                         | Power-down mode                              |                                        |     | 5    |      | μA    |

| I <sub>AVDD1</sub> ,<br>I <sub>AVSS</sub> |                                                         | AINx precharge buffer,                       | high-speed mode                        |     | 1.35 | 1.9  |       |

| AVSS                                      |                                                         | AINx precharge buffer,                       | low-speed mode                         |     | 0.2  | 0.3  |       |

|                                           | AVDD1 and AVSS additional current (per buffer function) | REFP precharge buffer                        | r, high-speed mode                     |     | 1.5  | 1.6  | mA    |

|                                           | ourient (per buller fullotion)                          | REFP precharge buffer                        | , low-speed mode                       |     | 0.4  | 0.45 |       |

|                                           |                                                         | VCM buffer                                   |                                        |     | 0.1  |      |       |

| I <sub>AVDD2</sub> ,                      |                                                         | High-speed mode                              |                                        |     | 3.5  | 3.8  | A     |

|                                           | AVDD2 and AVSS current                                  | Low-speed mode                               |                                        |     | 0.85 | 0.95 | mA    |

| I <sub>AVSS</sub>                         |                                                         | Standby mode                                 |                                        |     | 60   |      | μΑ    |

|                                           |                                                         | Power-down mode                              |                                        | 1   |      |      |       |

| DIGITAL                                   | SUPPLY CURRENT                                          |                                              | 1                                      |     |      | "    |       |

|                                           |                                                         | High-speed mode, wideband filter, OSR = 32   |                                        | 2.1 | 2.7  |      |       |

|                                           |                                                         | High-speed mode, low-                        | latency filter, OSR = 32               |     | 0.6  | 1    | 4     |

|                                           |                                                         | Low-speed mode, wideband filter, OSR = 32    |                                        |     | 0.3  | 0.4  | mA    |

| $I_{IOVDD}$                               | IOVDD current                                           | Low-speed mode, low-latency filter, OSR = 32 |                                        |     | 0.1  | 0.2  |       |

|                                           |                                                         | Standby mode, external clock                 |                                        |     | 10   |      |       |

|                                           |                                                         | Standby mode, internal                       | l oscillator                           | 40  |      |      | μΑ    |

|                                           |                                                         | Power-down mode                              |                                        |     | 10   |      |       |

| POWER                                     | DISSIPATION                                             |                                              | 1                                      |     |      | "    |       |

|                                           |                                                         |                                              | High-speed mode, wideband filter       |     | 18.6 |      |       |

| D                                         | Dayyar dissination                                      | AVDD2 = 1.8 V,                               | High-speed mode,<br>low-latency filter |     | 15.9 |      | ma\A/ |

| $P_D$                                     | Power dissipation                                       | precharge buffers off                        | Low-speed mode, wideband filter        |     | 3.3  |      | mW    |

|                                           |                                                         |                                              | Low-speed mode,<br>low-latency filter  |     | 3.0  |      |       |

<sup>(1)</sup> Stop-band attenuation as provided by the digital filter. Input frequencies in the stop band intermodulate with the chop frequency beginning at f<sub>MOD</sub> / 32, which results in stop-band attenuation exceeding 106 dB. See the wideband filter stop-band attenuation figure for details.

## 6.6 Timing Requirements (1.65 V ≤ IOVDD ≤ 2 V)

over operating ambient temperature range, unless otherwise noted

|                        |                                                                                                                                       | MIN   | MAX                        | UNIT             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|------------------|

| CLK PIN                |                                                                                                                                       |       | -                          |                  |

|                        | CLK period, high-speed mode                                                                                                           | 38.2  | 2000                       |                  |

| $t_{c(CLK)}$           | CLK period, low-speed mode, CLK_DIV = 1b                                                                                              | 38.2  | 2000                       | ns               |

|                        | CLK period, low-speed mode, CLK_DIV = 0b                                                                                              | 305   | 2000                       |                  |

|                        | Pulse duration, CLK low                                                                                                               | 17    |                            |                  |

| t <sub>w(CLKL)</sub>   | Pulse duration, CLK low, low-speed mode, CLK_DIV = 0b                                                                                 | 128   |                            | ns               |

|                        | Pulse duration, CLK high                                                                                                              |       |                            |                  |

| t <sub>w(CLKH)</sub>   | Pulse duration, CLK high, low-speed mode, CLK_DIV = 0b                                                                                | 128   |                            | ns               |

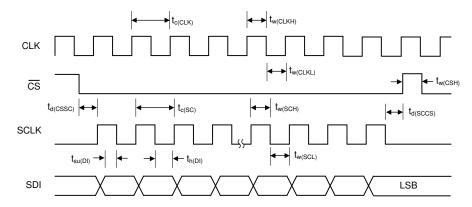

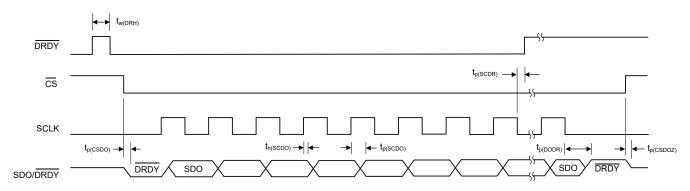

| SERIAL IN              | TERFACE                                                                                                                               |       |                            |                  |

| t <sub>c(SC)</sub>     | SCLK period                                                                                                                           | 25    | 1/(4 · f <sub>DATA</sub> ) | ns               |

| t <sub>w(SCL)</sub>    | Pulse duration, SCLK low                                                                                                              | 10    |                            | ns               |

| t <sub>w(SCH)</sub>    | Pulse duration, SCLK high                                                                                                             | 10    |                            | ns               |

| t <sub>d(CSSC)</sub>   | Delay time, first SCLK rising edge after $\overline{\text{CS}}$ falling edge                                                          | 10    |                            | ns               |

| t <sub>su(DI)</sub>    | Setup time, SDI valid before SCLK falling edge                                                                                        | 4     |                            | ns               |

| t <sub>h(DI)</sub>     | Hold time, SDI valid after SCLK falling edge                                                                                          | 6     |                            | ns               |

| $t_{d(SCCS)}$          | Delay time, $\overline{\text{CS}}$ rising edge after final SCLK falling edge                                                          | 10    |                            | ns               |

| t <sub>w(CSH)</sub>    | Pulse duration, CS high                                                                                                               | 20    |                            | ns               |

| RESET PIN              | ı İ                                                                                                                                   |       |                            |                  |

| t <sub>w(RSL)</sub>    | Pulse duration, RESET low                                                                                                             | 4     |                            | t <sub>CLK</sub> |

| t <sub>d(RSSC)</sub>   | Delay time, communication start after RESET rising edge or after SPI RESET pattern                                                    | 10000 |                            | t <sub>CLK</sub> |

| START PIN              | l                                                                                                                                     |       |                            |                  |

| t <sub>w(STL)</sub>    | Pulse duration, START low                                                                                                             | 4     |                            | t <sub>CLK</sub> |

| t <sub>w(STH)</sub>    | Pulse duration, START high                                                                                                            | 4     |                            | t <sub>CLK</sub> |

| t <sub>su(STCLK)</sub> | Setup time, START high before CLK rising edge (1)                                                                                     | 9     |                            | ns               |

| t <sub>h(STCLK)</sub>  | Hold time, START high after CLK rising edge <sup>(1)</sup>                                                                            | 9     |                            | ns               |

| $t_{su(STDR)}$         | Setup time, START falling edge or STOP bit before $\overline{DRDY}$ falling edge to stop next conversion (start/stop conversion mode) | 8     |                            | t <sub>CLK</sub> |

<sup>(1)</sup> START rising edge should not be applied between the setup and hold time period at the rising edge of CLK

# 6.7 Switching Characteristics (1.65 V ≤ IOVDD ≤ 2 V)

over operating ambient temperature range, OUT\_DRV = 0b,  $C_{LOAD}$  = 20 pF (unless otherwise noted)

|                       | PARAMETER                                                                                                      | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT             |

|-----------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|------------------|

| t <sub>p(CSDO)</sub>  | Propagation delay time, CS falling edge to SDO/DRDY driven state                                               |                                           |     |     | 20  | ns               |

| t <sub>p(CSDOZ)</sub> | Propagation delay time, CS rising edge to SDO/DRDY high impedance state                                        |                                           |     |     | 20  | ns               |

| t <sub>h(SCDO)</sub>  | Hold time, SCLK rising edge to invalid SDO/DRDY                                                                |                                           | 3   |     |     | ns               |

| t <sub>p(SCDO)</sub>  | Propagation delay time, SCLK rising edge to valid SDO/DRDY                                                     |                                           |     |     | 23  | ns               |

| t <sub>w(DRH)</sub>   | Pulse duration, DRDY high                                                                                      |                                           | 2   |     |     | t <sub>CLK</sub> |

| t <sub>p(SCDR)</sub>  | Propagation delay time, 8th SCLK falling edge to DRDY return high                                              | Synchronized and start/stop control modes |     |     | 5   | t <sub>CLK</sub> |

| t <sub>p(DODR)</sub>  | Propagation delay time, last SCLK falling edge of read operation for SDO/DRDY transition from SDO to DRDY mode | SDO_DRDY = 1b                             |     |     | 50  | ns               |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.8 Timing Requirements (2 V < IOVDD ≤ 5.5 V)

over operating ambient temperature range, unless otherwise noted

|                        |                                                                                                                                         | MIN   | MAX                        | UNIT             |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|------------------|

| CLK PIN                |                                                                                                                                         |       | -                          |                  |

|                        | CLK period, high-speed mode                                                                                                             | 38.2  | 2000                       |                  |

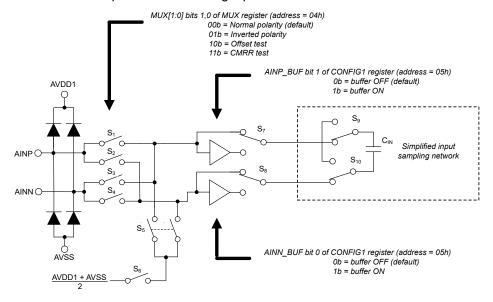

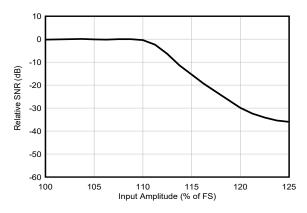

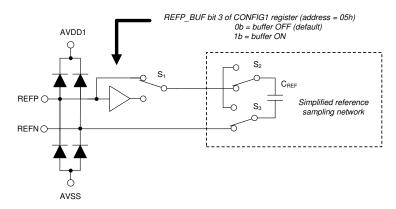

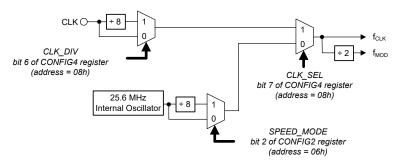

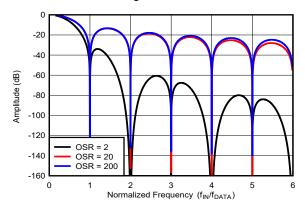

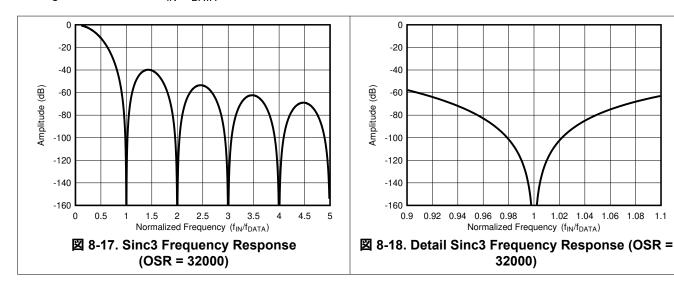

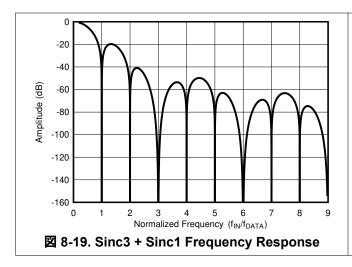

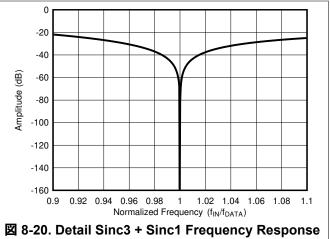

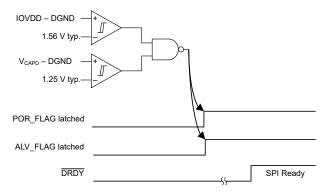

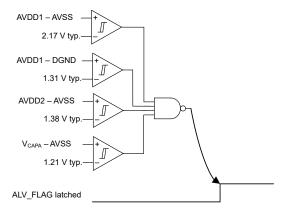

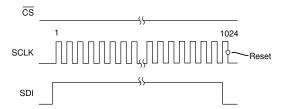

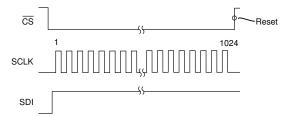

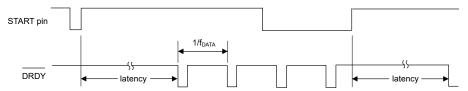

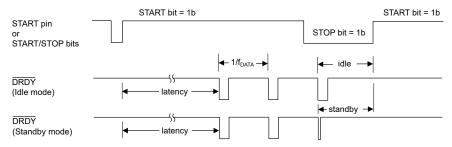

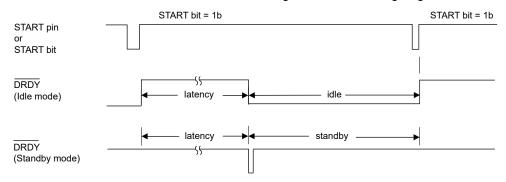

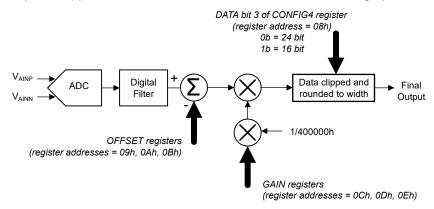

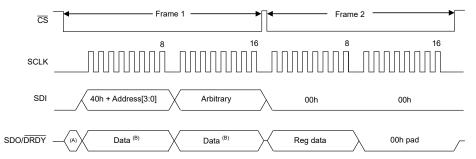

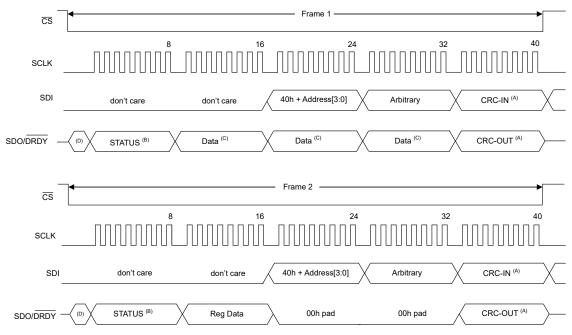

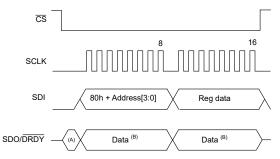

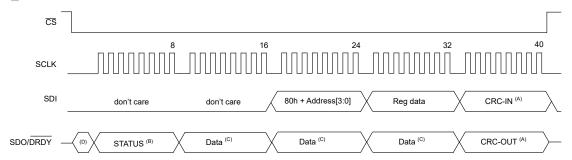

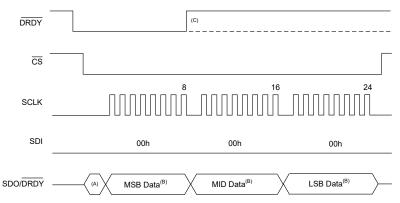

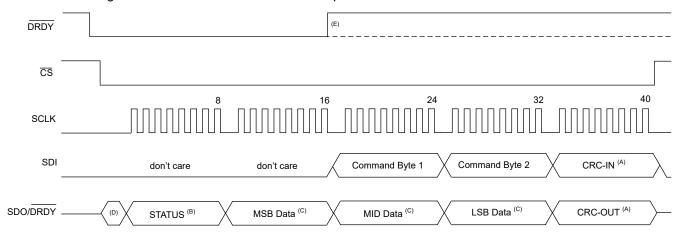

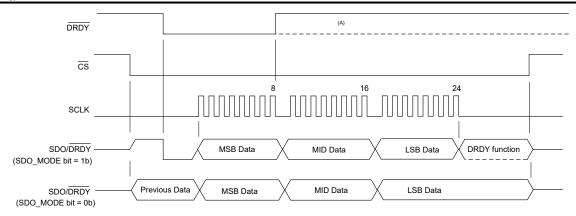

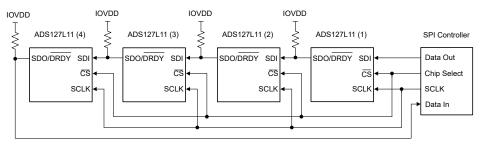

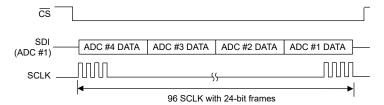

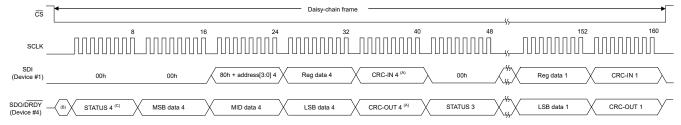

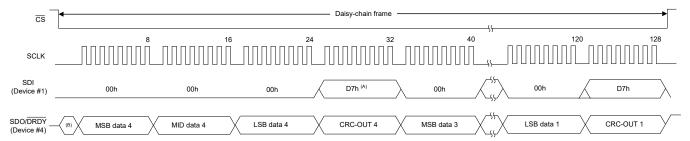

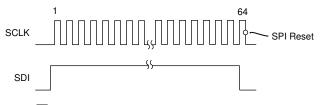

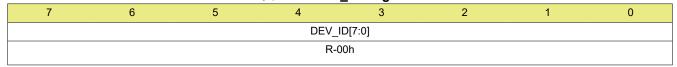

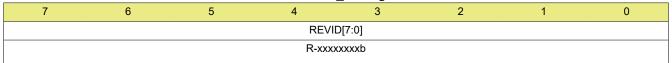

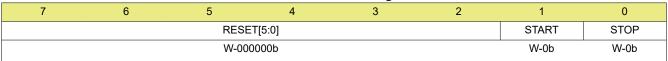

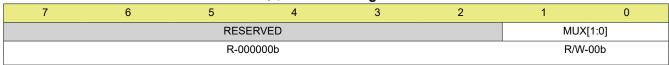

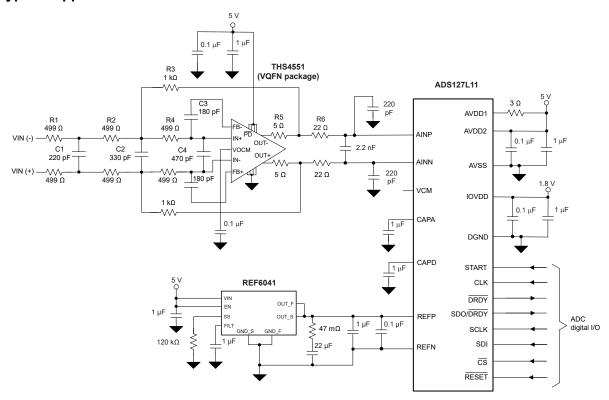

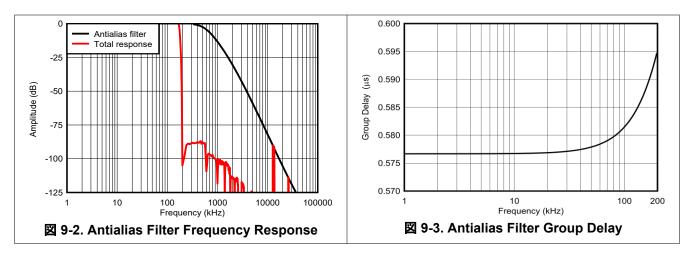

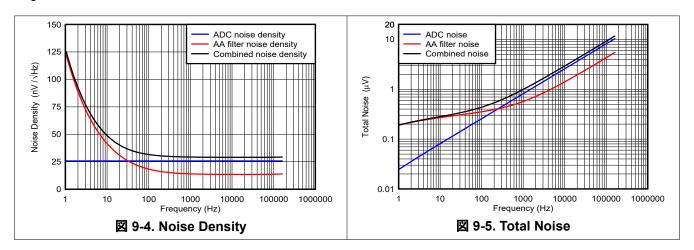

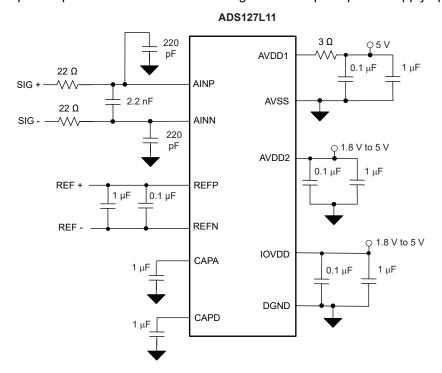

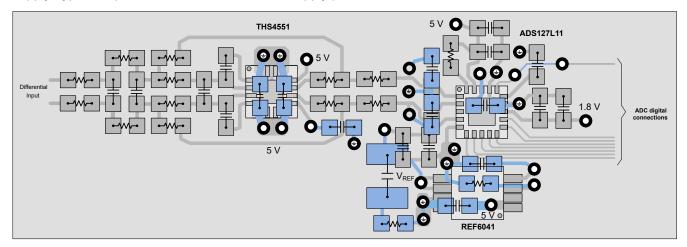

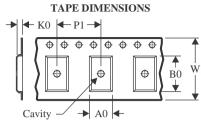

| $t_{c(CLK)}$           | CLK period, low-speed mode, CLK_DIV = 1b                                                                                                | 38.2  | 2000                       | ns               |