**ADS1278-SP**

JAJSG65B - SEPTEMBER 2018 - REVISED DECEMBER 2018

## ADS1278-SP 放射線耐性を強化した8チャネル同時サンプリング、 24ビットのアナログ/デジタル・コンバータ

## 特長

- 放射線耐性を強化

- TID:75krad(Si)

- TID RLAT (Radiation Lot Acceptance Test):未

- 単一イベント・ラッチアップ(SEL)耐性: LET = 68MeV-cm<sup>2</sup>/mg (125°C)

- 8つのチャネルを同時にサンプリング

- 最大128kSPSのデータ・レート

- AC特性

- 帯域幅:63kHz

- SNR:111dB(高分解能モード)

- THD:-108dB

- DC精度

- オフセット・ドリフト:0.8µV/°C

- ゲイン・ドリフト: 1.3ppm/°C

- 動作モードを選択可能

- 高速:128kSPS、SNR 106dB

- 高分解能:52kSPS、SNR 111dB

- 低消費電力:52kSPS、31mW/ch

- 低速:10kSPS、7mW/ch

- 線形位相デジタル・フィルタ

- SPI™またはフレーム同期シリアル・インター フェイス

- 小さいサンプリング・アパーチャ誤差

- 変調器出力オプション(デジタル・フィルタ・バ イパス)

- アナログ電源:5V

- デジタル・コア:1.8V

- I/O電源: 1.8V~3.3V

#### アプリケーション

- 宇宙用システム(人工衛星、シャトル、ステー ション)

- 人工衛星の温度および位置センシング

- 軌道観測システム

- 高精度および科学用アプリケーション

- 高精度の計測機器

### 3 概要

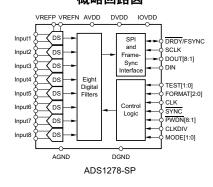

ADS1278-SP( $\forall \Delta P$ ) は24ビット、デルタ-シグマ( $\Delta P$ )ア ナログ/デジタル・コンバータ(ADC)で、最高128kサンプル /秒(SPS)のデータ速度を実現し、8チャネルを同時にサン プリング可能です。

従来、ドリフト性能が優れた産業用デルタ-シグマADCは、 パスバンド・ドループが大きいデジタル・フィルタを使用し ていました。その結果、信号の帯域幅が限られており、主 にDC測定に適していました。オーディオ・アプリケーション の高分解能ADCは、使用可能な帯域幅の点で優れてい ますが、オフセットおよびドリフトの仕様については、対応 する産業用部品より大きく劣っています。ADS1278-SP はこれらのタイプのコンバータを組み合わせることで、優れ たDCおよびAC仕様の高精度産業用計測を可能にしてい ます。

#### 製品情報(1)

|                 | 4X HH ID TIX                                 |                      |

|-----------------|----------------------------------------------|----------------------|

| 型番              | グレード                                         | パッケージ                |

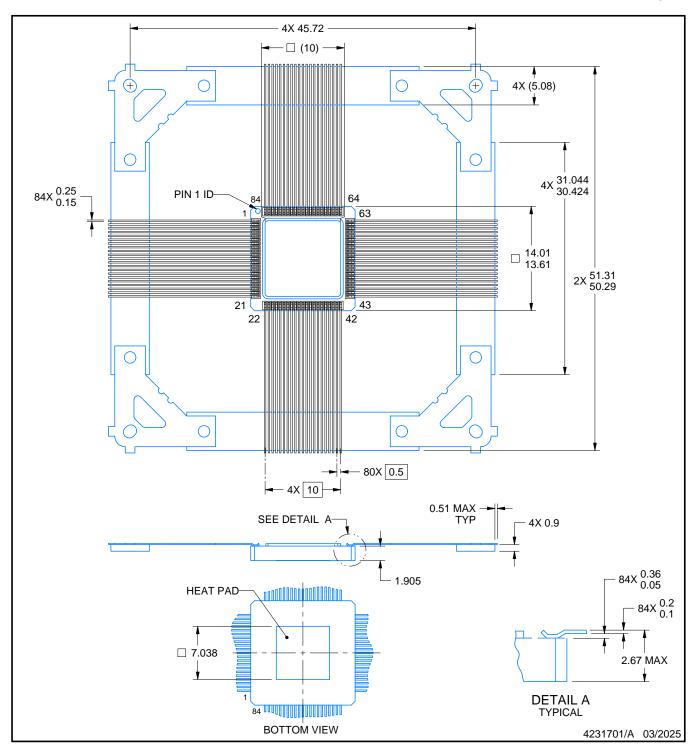

| ADS1278MHFQ-MLS | フライト・グレード: <b>75krad</b><br>(Si)、-55°C~125°C | 84ピンHFQ              |

| ADS1278WHFQ-MLS | フライト・グレード:75krad<br>(Si)、-55°C~115°C         | 重量:                  |

| ADS1278HFQ/EM   | エンジニアリング・サンプル<br>(2)                         | 4.46g <sup>(3)</sup> |

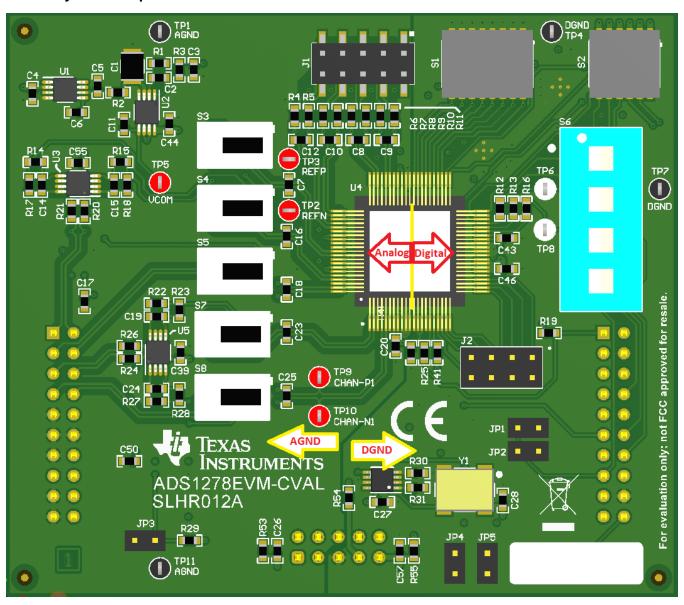

| ADS1278EVM-CVAL | セラミック評価ボード                                   | EVM                  |

- (1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

- これらのユニットは、技術的な評価のみを目的としています。標準と は異なるフローに従って処理されています。これらのユニットは、認 定、量産、放射線テスト、航空での使用には適していません。これら の部品は、MILに規定されている温度範囲-55℃~125℃、または 動作寿命全体にわたる性能を保証されていません。

- (3) 重量の精度は ±10% です。

#### 概略回路図

## 目次

| 1 | 特長1                                           |    | 8.2 Functional Block Diagram   | 23              |

|---|-----------------------------------------------|----|--------------------------------|-----------------|

| 2 | アプリケーション1                                     |    | 8.3 Feature Description        | 23              |

| 3 | 概要1                                           |    | 8.4 Device Functional Modes    | 45              |

| 4 | 改訂履歴2                                         | 9  | Application and Implementation | 46              |

| 5 | 概要(続き)3                                       |    | 9.1 Application Information    | 46              |

| 6 | Pin Configuration and Functions               |    | 9.2 Typical Application        | 46              |

| 7 | Specifications                                | 10 | Power Supply Recommendations   | 49              |

| ' | 7.1 Absolute Maximum Ratings                  | 11 | Layout                         | 50              |

|   | 7.2 ESD Ratings                               |    | 11.1 Layout Guidelines         | <u>50</u>       |

|   | 7.3 Recommended Operating Conditions          |    | 11.2 Layout Example            | <u>5</u> 1      |

|   | 7.4 Thermal Information                       | 12 | デバイスおよびドキュメントのサポート             | <mark>52</mark> |

|   | 7.5 Electrical Characteristics                |    | 12.1 ドキュメントの更新通知を受け取る方法        | <mark>52</mark> |

|   | 7.6 Timing Requirements: SPI Format9          |    | 12.2 コミュニティ・リソース               | <u>52</u>       |

|   | 7.7 Timing Requirements: Frame-Sync Format 11 |    | 12.3 商標                        | 52              |

|   | 7.8 Quality Conformance Inspection            |    | 12.4 静電気放電に関する注意事項             | <u>52</u>       |

|   | 7.9 Typical Characteristics                   |    | 12.5 Glossary                  | 52              |

| 8 | Detailed Description                          | 13 | メカニカル、パッケージ、および注文情報            | 53              |

|   | 8.1 Overview                                  |    |                                |                 |

|   |                                               |    |                                |                 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

## Revision A (December 2018) から Revision B に変更

Page

### 5 概要 (続き)

高次のチョッパ安定化変調器は、小さな帯域内ノイズで非常に小さなドリフトを達成します。オンボードのデシメーション・フィルタは、変調器と信号の帯域外ノイズを抑制します。これらのADCは、使用可能な信号帯域幅がナイキスト・レートの最大90%、リップルは0.005dB未満です。

**4**つの動作モードにより、速度、分解能、消費電力を最適化できます。すべての動作はピンで直接制御でき、レジスタをプログラムする必要はありません。このデバイスは拡張温度範囲の-55℃~125℃で完全に動作が規定されており、84ピンの HFQパッケージで供給されます。

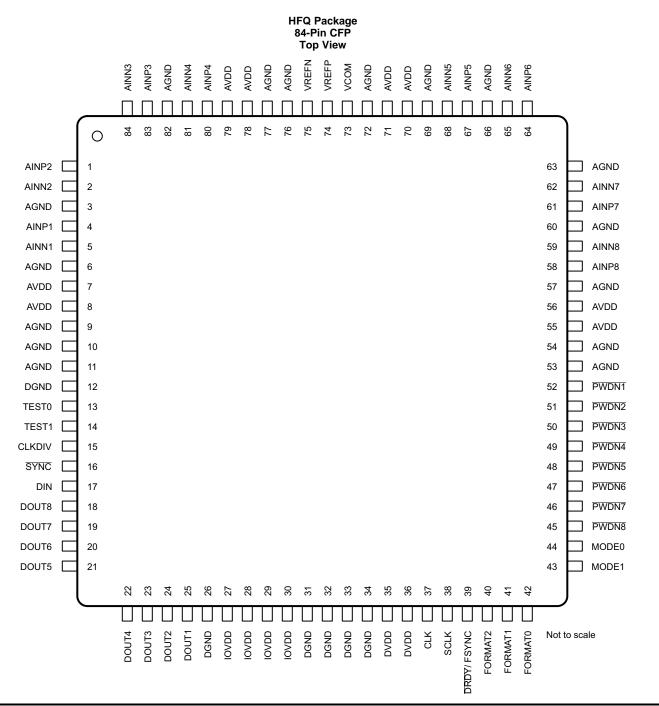

## 6 Pin Configuration and Functions

## **Pin Functions**

| PII            | N                                                                       | 1/0                                                                             | DESCRIPTION                                                                                                               |  |  |

|----------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | NO.                                                                     | 1/0                                                                             | DESCRIF HOW                                                                                                               |  |  |

| AGND           | 3, 6, 9, 10,<br>11, 53, 54,<br>57, 60, 63,<br>66, 69, 72,<br>76, 77, 82 | Analog ground                                                                   | Analog ground; connect to DGND using a single plane.                                                                      |  |  |

| AINP1          | 4                                                                       | Analog input                                                                    |                                                                                                                           |  |  |

| AINP2          | 1                                                                       | Analog input                                                                    |                                                                                                                           |  |  |

| AINP3          | 83                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINP4          | 80                                                                      | Analog input                                                                    | AINDIG:11 Decitive analog input, channels 9 through 1                                                                     |  |  |

| AINP5          | 67                                                                      | Analog input                                                                    | AINP[8:1] Positive analog input, channels 8 through 1.                                                                    |  |  |

| AINP6          | 64                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINP7          | 61                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINP8          | 58                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINN1          | 5                                                                       | Analog input                                                                    |                                                                                                                           |  |  |

| AINN2          | 2                                                                       | Analog input                                                                    |                                                                                                                           |  |  |

| AINN3          | 84                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINN4          | 81                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINN5          | 68                                                                      | Analog input                                                                    | AINN[8:1] Negative analog input, channels 8 through 1.                                                                    |  |  |

| AINN6          | 65                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AINN7          | 3 1                                                                     |                                                                                 |                                                                                                                           |  |  |

| AINN8          | 59                                                                      | Analog input                                                                    |                                                                                                                           |  |  |

| AVDD           | 7, 8, 55, 56,<br>70, 71, 78,<br>79                                      | Analog power supply                                                             | Analog power supply (4.75 V to 5.25 V).                                                                                   |  |  |

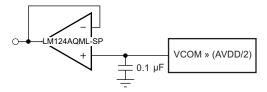

| VCOM           | 73                                                                      | Analog output                                                                   | AVDD / 2 Unbuffered voltage output.                                                                                       |  |  |

| VREFN          | 75                                                                      | Analog input                                                                    | Negative reference input.                                                                                                 |  |  |

| VREFP          | 74                                                                      | Analog input                                                                    | Positive reference input.                                                                                                 |  |  |

| CLK            | 37                                                                      | Digital input                                                                   | Master clock input.                                                                                                       |  |  |

| CLKDIV         | 15                                                                      | Digital input                                                                   | CLK input divider control:  1 = 32.768 MHz (High-Speed mode only) / 27 MHz 0 = 13.5 MHz (low-power) / 5.4 MHz (low-speed) |  |  |

| DGND           | 12, 26, 31,<br>32, 33, 34                                               | Digital ground                                                                  | Digital ground power supply.                                                                                              |  |  |

| DIN            | 17                                                                      | Digital input                                                                   | Daisy-chain data input.                                                                                                   |  |  |

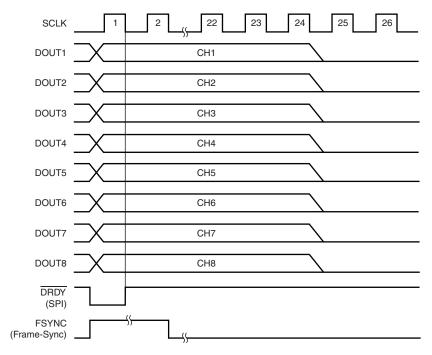

| DOUT1          | 25                                                                      | Digital output                                                                  | DOUT1 is TDM data output (TDM mode).                                                                                      |  |  |

| DOUT2          | 24                                                                      | Digital output                                                                  |                                                                                                                           |  |  |

| DOUT3          | 23                                                                      | Digital output                                                                  |                                                                                                                           |  |  |

| DOUT4          | 22                                                                      | Digital output                                                                  |                                                                                                                           |  |  |

| DOUT5          | 21                                                                      | Digital output                                                                  | DOUT[8:1] Data output for channels 8 through 1.                                                                           |  |  |

| DOUT6          | 20                                                                      | Digital output                                                                  |                                                                                                                           |  |  |

| DOUT7          | 19                                                                      | Digital output                                                                  |                                                                                                                           |  |  |

| DOUT8          | 18                                                                      | Digital output                                                                  |                                                                                                                           |  |  |

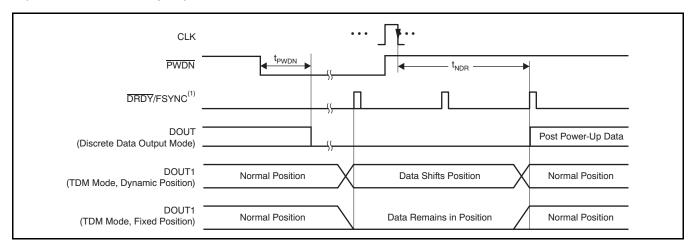

| DRDY/<br>FSYNC | 39                                                                      | Digital input/output                                                            | Frame-Sync protocol: frame clock input; SPI protocol: data ready output.                                                  |  |  |

| DVDD           | 35, 36                                                                  | Digital power supply                                                            | Digital core power supply (+1.65 V to +1.95 V).                                                                           |  |  |

| FORMAT0        | 42                                                                      | Digital input                                                                   | FORMAT[2:0] Selects Frame-Sync/SPI protocol, TDM/discrete data outputs                                                    |  |  |

| FORMAT1        | 41                                                                      | 41 Digital input fixed/dynamic position TDM data, and modulator mode/normal ope |                                                                                                                           |  |  |

| FORMAT2        | 40                                                                      | Digital input                                                                   | mode.                                                                                                                     |  |  |

| IOVDD          | 27, 28, 29,<br>30                                                       | Digital power supply                                                            | I/O power supply (+1.65 V to +3.6 V).                                                                                     |  |  |

## Pin Functions (continued)

| PIN   | ı   | 1/0                  | DESCRIPTION                                                            |

|-------|-----|----------------------|------------------------------------------------------------------------|

| NAME  | NO. | - I/O                | DESCRIPTION                                                            |

| MODE0 | 44  | Digital input        | MODE[1:0] Selects High-Speed, High-Resolution, Low-Power, or Low-Speed |

| MODE1 | 43  | Digital input        | mode operation.                                                        |

| PWDN1 | 52  | Digital input        |                                                                        |

| PWDN2 | 51  | Digital input        |                                                                        |

| PWDN3 | 50  | Digital input        |                                                                        |

| PWDN4 | 49  | Digital input        | DWDNIG.41 Down down control for changels 0 through 1                   |

| PWDN5 | 48  | Digital input        | PWDN[8:1] Power-down control for channels 8 through 1.                 |

| PWDN6 | 47  | Digital input        |                                                                        |

| PWDN7 | 46  | Digital input        |                                                                        |

| PWDN8 | 45  | Digital input        |                                                                        |

| SCLK  | 38  | Digital input/output | Serial clock input, modulator clock output.                            |

| SYNC  | 16  | Digital input        | Synchronize input (all channels).                                      |

| TEST0 | 13  | Digital input        | TEST[1:0] Test mode 00 = Normal operation 01 = Do not use              |

| TEST1 | 14  | Digital input        | select: 11 = Test mode 10 = Do not use                                 |

### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                      | MIN  | MAX        | UNIT |

|---------------------------------------|----------------------|------|------------|------|

| AVDD to AGND                          |                      | -0.3 | 6          | V    |

| AGND to DGND                          |                      | -0.3 | 0.3        | V    |

| DVDD, IOVDD to DGND                   |                      | -0.3 | 3.6        | V    |

| Innest assument                       | Momentary            |      | 100        |      |

| Input current                         | Continuous           |      | 10         | mA   |

| Analog input to AGND                  |                      | -0.3 | AVDD + 0.3 | V    |

| Digital input or output to DGND       |                      | -0.3 | DVDD + 0.3 | V    |

| lunation toner and un                 | HFQ and HKP Packages | -55  | 217        | 00   |

| Junction temperature                  | D Package            | -55  | 175        | °C   |

| Storage temperature, T <sub>stg</sub> |                      | -60  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | TBD   |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | TBD   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|    | · · · · · · · · · · · · · · · · · · · | ·               |     |         |      |

|----|---------------------------------------|-----------------|-----|---------|------|

|    |                                       |                 | MIN | NOM MAX | UNIT |

| _  | Operating innotion temperature        | ADS1278MHFQ-MLS | -55 | 125     | °C   |

| IJ | Operating junction temperature        | ADS1278WHFQ-MLS | -55 | 115     | 10   |

#### 7.4 Thermal Information

|                        |                                              | ADS1278-SP |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | HFQ (CFP)  | UNIT |

|                        |                                              | 84 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 23.7       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 9.6        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 11.5       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 3.0        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 10.9       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 7.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.5 Electrical Characteristics

All specifications at  $T_A = -55$ °C to 125°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

| PA                                        | RAMETER                          | TEST CONDITIONS                              | SUBGROUP |               | C to +125°<br>78MHFQ-I |               |               | C to +115°<br>78WHFQ- |               | UNIT                 |

|-------------------------------------------|----------------------------------|----------------------------------------------|----------|---------------|------------------------|---------------|---------------|-----------------------|---------------|----------------------|

|                                           |                                  |                                              | ( ) ( )  | MIN           | TYP                    | MAX           | MIN           | TYP                   | MAX           |                      |

| ANALOG INPU                               | TS                               |                                              |          |               |                        |               |               |                       |               |                      |

| Full-scale input                          | voltage (FSR <sup>(3)</sup> )    | $V_{IN} = (AINP - AINN)$                     |          |               | $\pm V_{REF}$          |               |               | $\pm V_{REF}$         |               | V                    |

| Absolute input v                          | oltage                           | AINP or AINN to AGND                         | 1, 2, 3  | AGND –<br>0.1 |                        | AVDD<br>+ 0.1 | AGND –<br>0.1 |                       | AVDD<br>+ 0.1 | V                    |

| Common-mode                               | input voltage (V <sub>CM</sub> ) | V <sub>CM</sub> = (AINP + AINN) / 2          |          |               | 2.5                    |               |               | 2.5                   |               | V                    |

|                                           | High-Speed mode                  |                                              |          |               | 14                     |               |               | 14                    |               |                      |

| Differential                              | High-Resolution mode             |                                              |          |               | 14                     |               |               | 14                    |               | 1.0                  |

| input<br>impedance                        | Low-Power mode                   |                                              |          |               | 28                     |               |               | 28                    |               | kΩ                   |

| •                                         | Low-Speed mode                   |                                              |          |               | 140                    |               |               | 140                   |               |                      |

| DC PERFORMA                               | ANCE                             |                                              |          |               |                        |               |               |                       |               |                      |

| Resolution                                |                                  | No missing codes                             | 1, 2, 3  | 24            |                        |               | 24            |                       |               | Bits                 |

|                                           | High County of the               | f <sub>CLK</sub> = 32.768 MHz <sup>(4)</sup> |          |               | 128,000                |               |               | 128,000               |               |                      |

|                                           | High-Speed mode                  | f <sub>CLK</sub> = 27 MHz                    |          |               | 105,469                |               |               | 105,469               |               |                      |

| Maximum data<br>rate (f <sub>DATA</sub> ) | High-Resolution mode             |                                              |          |               | 52,734                 |               |               | 52,734                |               | SPS <sup>(5)</sup>   |

| rate (IDATA)                              | Low-Power mode                   |                                              |          |               | 52,734                 |               |               | 52,734                |               |                      |

|                                           | Low-Speed mode                   |                                              |          |               | 10,547                 |               |               | 10,547                |               |                      |

| Integral nonlinea                         | arity (INL) <sup>(6)</sup>       | Differential input, V <sub>CM</sub> = 2.5 V  | 1, 2, 3  |               | ±0.0003                | ±0.001        |               | ±0.0003               | ±0.001        | % FSR <sup>(3)</sup> |

| Offset error                              |                                  |                                              | 1, 2, 3  |               | 0.25                   | 2             |               | 0.25                  | 2             | mV                   |

| Offset drift                              |                                  |                                              |          |               | 0.8                    |               |               | 0.8                   |               | μV/°C                |

| Gain error                                |                                  |                                              | 1, 2, 3  |               | 0.1                    | 0.5           |               | 0.1                   | 0.5           | % FSR                |

| Gain drift                                |                                  |                                              |          |               | 1.3                    |               |               | 1.3                   |               | ppm/°C               |

|                                           | High-Speed mode                  | Shorted input                                | 1, 2, 3  |               | 8.5                    | 23            |               | 8.5                   | 21            |                      |

|                                           | High-Resolution mode             | Shorted input                                | 1, 2, 3  |               | 5.5                    | 14            |               | 5.5                   | 13            |                      |

| Noise                                     | Low-Power mode                   | Shorted input                                | 1, 2, 3  |               | 8.5                    | 23            |               | 8.5                   | 21            | μV, rms              |

|                                           | Low-Speed mode                   | Shorted input                                | 1, 2, 3  |               | 8.0                    | 23            |               | 8.0                   | 21            |                      |

| Common-mode                               | rejection                        | f <sub>CM</sub> = 60 Hz                      | 1, 2, 3  | 90            | 108                    |               | 90            | 108                   |               | dB                   |

|                                           | AVDD                             |                                              |          |               | 80                     |               |               | 80                    |               |                      |

| Power-supply                              | DVDD                             | f <sub>PS</sub> = 60 Hz                      |          |               | 85                     |               |               | 85                    |               | dB                   |

| rejection                                 | IOVDD                            |                                              |          |               | 105                    |               |               | 105                   |               |                      |

| V <sub>COM</sub> output volt              | age                              | No load                                      |          |               | AVDD /                 |               |               | AVDD /                |               | V                    |

| AC PERFORMA                               | NCE                              | 1                                            | 1        |               |                        | <u> </u>      |               |                       |               |                      |

| Crosstalk                                 |                                  | f = 1 kHz, -0.5 dBFS <sup>(7)</sup>          |          |               | -107                   |               |               | -107                  |               | dB                   |

|                                           | High-Speed mode                  |                                              | 4, 5, 6  | 98            | 106                    |               | 98            | 106                   |               |                      |

| Signal-to-noise                           |                                  | V <sub>REF</sub> = 2.5 V                     | 4, 5, 6  | 101           | 110                    |               | 101           | 110                   |               |                      |

| ratio (SNR)(8)                            | High-Resolution mode             | V <sub>REF</sub> = 3 V                       |          |               | 111                    |               |               | 111                   |               | dB                   |

| (unweighted)                              | Low-Power mode                   |                                              | 4, 5, 6  | 98            | 106                    |               | 98            | 106                   |               |                      |

|                                           | Low-Speed mode                   |                                              | 4, 5, 6  | 98            | 107                    |               | 98            | 107                   |               |                      |

| Total harmonic of                         | distortion (THD) <sup>(9)</sup>  | V <sub>IN</sub> = 1 kHz, -0.5 dBFS           | 4, 5, 6  |               | -108                   | -96           |               | -108                  | -96           | dB                   |

| Spurious-free dy                          |                                  | , , , , , , ,                                | , -, -   |               | 109                    |               |               | 109                   |               | dB                   |

- (1) For subgroup definitions, please see Quality Conformance Inspection table.

- (2) Subgroups apply to -55°C to +125°C column only.

- (3) FSR = full-scale range = 2 V<sub>REF</sub>.

- (4)  $f_{CLK} = 32.768$ -MHz max for High-Speed mode and 27-MHz max for all other modes. When  $f_{CLK} > 27$  MHz, operation is limited to Frame-Sync mode and V<sub>REF</sub> ≤ 2.6 V. SPS = samples per second.

- Best fit method.

- (7) Worst-case channel crosstalk between one or more channels.

- Minimum SNR is ensured by the limit of the DC noise specification.

- THD includes the first nine harmonics of the input signal; Low-Speed mode includes the first five harmonics.

## **Electrical Characteristics (continued)**

All specifications at  $T_A = -55^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ , AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

| PA                    | RAMETER                     | TEST CONDITIONS                              | SUBGROUP |                            | C to +125°<br>278MHFQ-I    |                               |                            | C to +115°<br>278WHFQ-I    |                               | UNIT    |

|-----------------------|-----------------------------|----------------------------------------------|----------|----------------------------|----------------------------|-------------------------------|----------------------------|----------------------------|-------------------------------|---------|

|                       |                             |                                              |          | MIN                        | TYP                        | MAX                           | MIN                        | TYP                        | MAX                           |         |

| Passband ripple       |                             |                                              |          |                            | ±0.005                     |                               |                            | ±0.005                     |                               | dB      |

| Passband              |                             |                                              |          |                            | 0.453<br>f <sub>DATA</sub> |                               |                            | 0.453<br>f <sub>DATA</sub> |                               | Hz      |

| –3-dB bandwidth       | า                           |                                              |          |                            | 0.49<br>f <sub>DATA</sub>  |                               |                            | 0.49<br>f <sub>DATA</sub>  |                               | Hz      |

| Stop band             | High-Resolution mode        |                                              | 4, 5, 6  | 95                         |                            |                               | 95                         |                            |                               | dB      |

| attenuation           | All other modes             |                                              | 4, 5, 6  | 100                        |                            |                               | 100                        |                            |                               | dB      |

| Stop band             | High-Resolution mode        |                                              | 4, 5, 6  | 0.547<br>f <sub>DATA</sub> |                            | 127.45<br>3 f <sub>DATA</sub> | 0.547<br>f <sub>DATA</sub> |                            | 127.45<br>3 f <sub>DATA</sub> | Hz      |

|                       | All other modes             |                                              | 4, 5, 6  | 0.547<br>f <sub>DATA</sub> |                            | 63.453<br>f <sub>DATA</sub>   | 0.547<br>f <sub>DATA</sub> |                            | 63.453<br>f <sub>DATA</sub>   |         |

| Group delay           | High-Resolution mode        |                                              |          |                            | 39/f <sub>DATA</sub>       |                               |                            | 39/f <sub>DATA</sub>       |                               | s       |

| Group delay           | All other modes             |                                              |          |                            | 38/f <sub>DATA</sub>       |                               |                            | 38/f <sub>DATA</sub>       |                               | 3       |

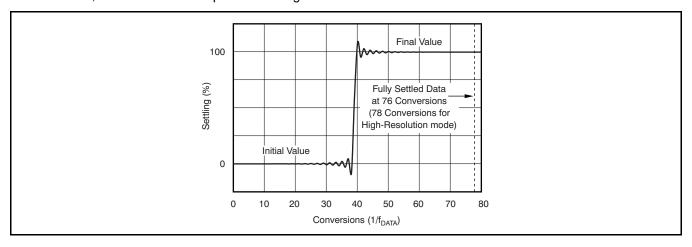

| Settling time         | High-Resolution mode        | Complete settling                            |          |                            | 78/f <sub>DATA</sub>       |                               |                            | 78/f <sub>DATA</sub>       |                               |         |

| (latency)             | All other modes             | Complete settling                            |          |                            | 76/f <sub>DATA</sub>       |                               |                            | 76/f <sub>DATA</sub>       |                               | S       |

| VOLTAGE REF           | ERENCE INPUTS               |                                              |          |                            |                            |                               |                            |                            |                               |         |

| Reference input       | voltage (V <sub>RFF</sub> ) | f <sub>CLK</sub> = 27 MHz                    | 1, 2, 3  | 0.5                        | 2.5                        | 3.1                           | 0.5                        | 2.5                        | 3.1                           | 17      |

| $(V_{REF} = VREFP)$   |                             | f <sub>CLK</sub> = 32.768 MHz <sup>(4)</sup> | 1, 2, 3  | 0.5                        | 2.5                        | 2.6                           | 0.5                        | 2.5                        | 2.6                           | V       |

| Negative referer      | nce input (VREFN)           |                                              | 1, 2, 3  | AGND -<br>0.1              |                            | AGND<br>+ 0.1                 | AGND -<br>0.1              |                            | AGND<br>+ 0.1                 | V       |

| Positive reference    | ce input (VREFP)            |                                              | 1, 2, 3  | VREFN<br>+ 0.5             |                            | AVDD<br>+ 0.1                 | VREFN<br>+ 0.5             |                            | AVDD<br>+ 0.1                 | ٧       |

|                       | High-Speed mode             |                                              |          |                            | 0.65                       |                               |                            | 0.65                       |                               |         |

| Reference             | High-Resolution mode        |                                              |          |                            | 0.65                       |                               |                            | 0.65                       |                               |         |

| Input impedance       | Low-Power mode              |                                              |          |                            | 1.3                        |                               |                            | 1.3                        |                               | kΩ      |

| ·                     | Low-Speed mode              |                                              |          |                            | 6.5                        |                               |                            | 6.5                        |                               |         |

| DIGITAL INPUT         | OUTPUT (IOVDD = 1.8         | V to 3.6 V)                                  |          |                            |                            |                               |                            |                            |                               |         |

| V <sub>IH</sub>       |                             |                                              | 4, 5, 6  | 0.7<br>IOVDD               |                            | IOVDD                         | 0.7<br>IOVDD               |                            | IOVDD                         | V       |

| V <sub>IL</sub>       |                             |                                              | 4, 5, 6  | DGND                       |                            | 0.3<br>IOVDD                  | DGND                       |                            | 0.3<br>IOVDD                  | V       |

| V <sub>OH</sub>       |                             | I <sub>OH</sub> = 4 mA                       | 4, 5, 6  | 0.8<br>IOVDD               |                            | IOVDD                         | 0.8<br>IOVDD               |                            | IOVDD                         | V       |

| V <sub>OL</sub>       |                             | I <sub>OL</sub> = 4 mA                       | 4, 5, 6  | DGND                       |                            | 0.2<br>IOVDD                  | DGND                       |                            | 0.2<br>IOVDD                  | V       |

| Input leakage         |                             | 0 < V <sub>IN DIGITAL</sub> < IOVDD          | 4, 5, 6  |                            |                            | ±11                           |                            |                            | ±10                           | μΑ      |

| Master clock rate     | e (four)                    | High-Speed mode <sup>(4)</sup>               | 4, 5, 6  | 0.1                        |                            | 32.768                        | 0.1                        |                            | 32.768                        | MHz     |

| Waster clock rate     | C (ICLK)                    | Other modes                                  | 1, 2, 3  | 0.1                        |                            | 27                            | 0.1                        |                            | 27                            | 1711 12 |

| POWER SUPPL           | _Y                          |                                              |          |                            |                            |                               |                            |                            |                               |         |

| AVDD                  |                             |                                              | 1, 2, 3  | 4.75                       | 5                          | 5.25                          | 4.75                       | 5                          | 5.25                          | V       |

| DVDD                  |                             |                                              | 1, 2, 3  | 1.65                       | 1.8                        | 1.95                          | 1.65                       | 1.8                        | 1.95                          | V       |

| IOVDD                 | _                           |                                              | 1, 2, 3  | 1.65                       |                            | 3.6                           | 1.65                       |                            | 3.6                           | V       |

|                       | AVDD                        |                                              | 1, 2, 3  |                            | 1                          | 11                            |                            | 1                          | 10                            |         |

| Power-down<br>current | DVDD                        |                                              | 1, 2, 3  |                            | 1                          | 52                            |                            | 1                          | 50                            | μΑ      |

|                       | IOVDD                       |                                              | 1, 2, 3  |                            | 1                          | 12                            |                            | 1                          | 11                            |         |

|                       | High-Speed mode             |                                              | 1, 2, 3  |                            | 97                         | 148                           |                            | 97                         | 145                           |         |

| A)/DD - :             | High-Resolution mode        |                                              | 1, 2, 3  |                            | 97                         | 148                           |                            | 97                         | 145                           |         |

| AVDD current          | Low-Power mode              |                                              | 1, 2, 3  |                            | 44                         | 66                            |                            | 44                         | 64                            | − mA    |

|                       |                             |                                              |          |                            |                            |                               |                            |                            |                               |         |

### **Electrical Characteristics (continued)**

All specifications at  $T_A = -55$ °C to 125°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

| PA            | RAMETER              | TEST CONDITIONS | SUBGROUP |     | to +125°(<br>8MHFQ-N | _   | -55°C<br>(ADS1278 | to +115°(<br>BWHFQ-N |     | UNIT  |

|---------------|----------------------|-----------------|----------|-----|----------------------|-----|-------------------|----------------------|-----|-------|

|               |                      |                 | ( // /   | MIN | TYP                  | MAX | MIN               | TYP                  | MAX |       |

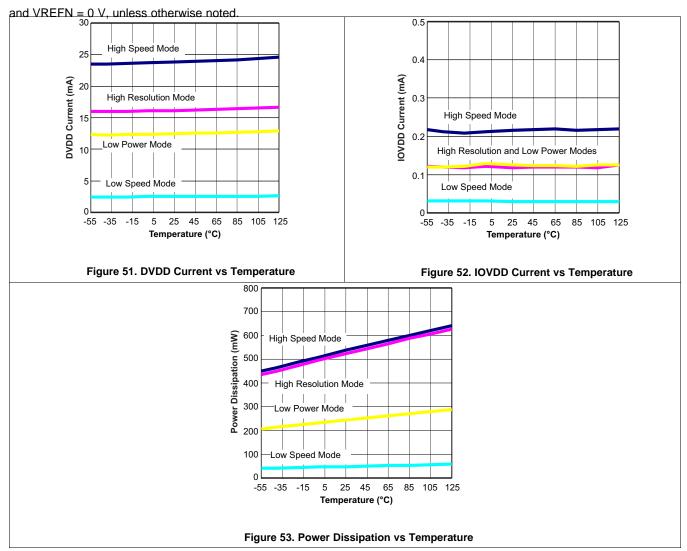

|               | High-Speed mode      |                 | 1, 2, 3  |     | 23                   | 31  |                   | 23                   | 30  |       |

| DVDD current  | High-Resolution mode |                 | 1, 2, 3  |     | 16                   | 21  |                   | 16                   | 20  | mA    |

| DVDD current  | Low-Power mode       |                 | 1, 2, 3  |     | 12                   | 18  |                   | 12                   | 17  | mA    |

|               | Low-Speed mode       |                 | 1, 2, 3  |     | 2.5                  | 5   |                   | 2.5                  | 4.5 |       |

|               | High-Speed mode      |                 | 1, 2, 3  |     | 0.25                 | 1.5 |                   | 0.25                 | 1   |       |

| IOVDD current | High-Resolution mode |                 | 1, 2, 3  |     | 0.125                | 8.0 |                   | 0.125                | 0.6 | mA    |

| IOVDD current | Low-Power mode       |                 | 1, 2, 3  |     | 0.125                | 0.8 |                   | 0.125                | 0.6 | mA    |

|               | Low-Speed mode       |                 | 1, 2, 3  |     | 0.035                | 0.5 |                   | 0.035                | 0.3 |       |

|               | High-Speed mode      |                 | 1, 2, 3  |     | 530                  | 805 |                   | 530                  | 785 |       |

| Power         | High-Resolution mode |                 | 1, 2, 3  |     | 515                  | 785 |                   | 515                  | 765 | mW    |

| dissipation   | Low-Power mode       |                 | 1, 2, 3  |     | 245                  | 370 |                   | 245                  | 355 | IIIVV |

|               | Low-Speed mode       |                 | 1, 2, 3  |     | 50                   | 85  |                   | 50                   | 80  |       |

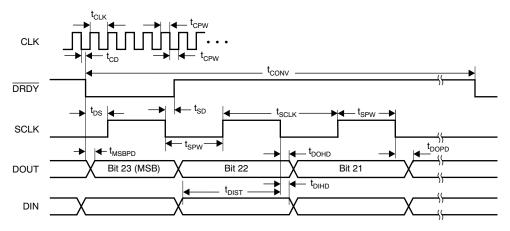

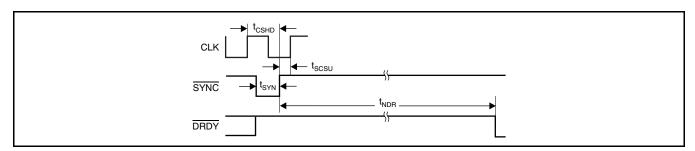

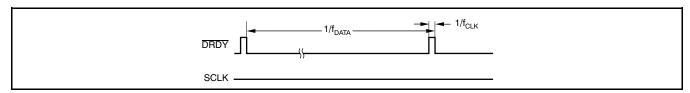

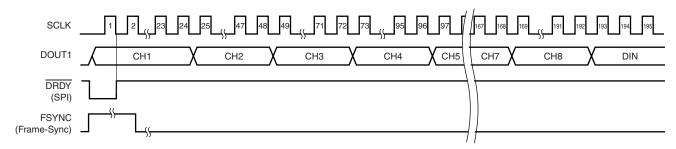

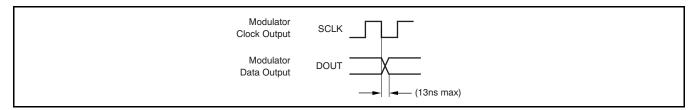

## 7.6 Timing Requirements: SPI Format<sup>(1)</sup>

For  $T_A = -55^{\circ}$ C to 125°C, IOVDD = 1.65 V to 3.6 V, and DVDD = 1.65 V to 1.95 V.

| SYMBOL                         | PARAMETER                                                          | MIN | TYP | MAX    | UNIT             |

|--------------------------------|--------------------------------------------------------------------|-----|-----|--------|------------------|

| t <sub>CLK</sub>               | CLK period (1 / f <sub>CLK</sub> ) <sup>(2)</sup>                  | 37  |     | 10,000 | ns               |

| t <sub>CPW</sub>               | CLK positive or negative pulse width                               | 15  |     |        | ns               |

| t <sub>CONV</sub>              | Conversion period (1 / f <sub>DATA</sub> ) <sup>(3)</sup>          | 256 |     | 2560   | t <sub>CLK</sub> |

| t <sub>CD</sub> <sup>(4)</sup> | Falling edge of CLK to falling edge of DRDY                        |     | 22  |        | ns               |

| t <sub>DS</sub> <sup>(4)</sup> | Falling edge of DRDY to rising edge of first SCLK to retrieve data | 1   |     |        | t <sub>CLK</sub> |

| t <sub>MSBPD</sub>             | DRDY falling edge to DOUT MSB valid (propagation delay)            |     |     | 16     | ns               |

| t <sub>SD</sub> <sup>(4)</sup> | Falling edge of SCLK to rising edge of DRDY                        |     | 18  |        | ns               |

| t <sub>SCLK</sub> (5)          | SCLK period                                                        | 1   |     |        | t <sub>CLK</sub> |

| t <sub>SPW</sub>               | SCLK positive or negative pulse width                              | 0.4 |     |        | t <sub>CLK</sub> |

| t <sub>DOHD</sub> (4) (6)      | SCLK falling edge to new DOUT invalid (hold time)                  | 10  |     |        | ns               |

| t <sub>DOPD</sub> (4)          | SCLK falling edge to new DOUT valid (propagation delay)            |     |     | 32     | ns               |

| t <sub>DIST</sub>              | New DIN valid to falling edge of SCLK (setup time)                 | 6   |     |        | ns               |

| t <sub>DIHD</sub> (6)          | Old DIN valid to falling edge of SCLK (hold time)                  | 6   |     |        | ns               |

- (1) Timing parameters are characterized or assured by design for specified temperature but not production tested.

(2) f<sub>CLK</sub> = 27-MHz maximum.

- Depends on MODE[1:0] and CLKDIV selection. See Table 5 ( $f_{CLK}$  /  $f_{DATA}$ ). Load on  $\overline{DRDY}$  and DOUT = 20 pF.

- For best performance, limit f<sub>SCLK</sub> / f<sub>CLK</sub> to ratios of 1, 1/2, 1/4, 1/8, etc.. t<sub>DOHD</sub> (DOUT hold time) and t<sub>DIHD</sub> (DIN hold time) are specified under opposite worst-case conditions (digital supply voltage and ambient temperature). Under equal conditions, with DOUT connected directly to DIN, the timing margin is > 4 ns.

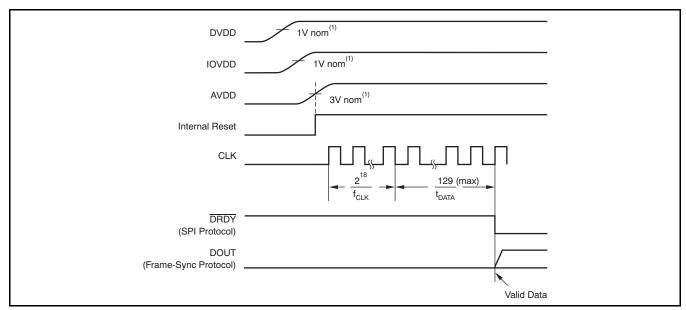

Figure 1. SPI Format Timing Characteristics

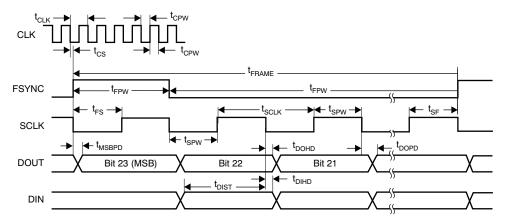

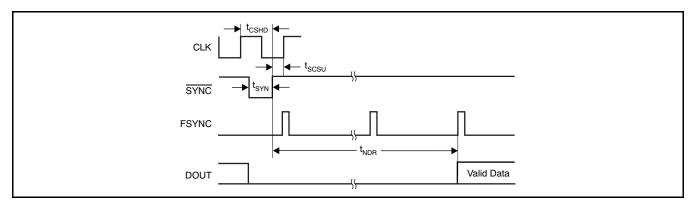

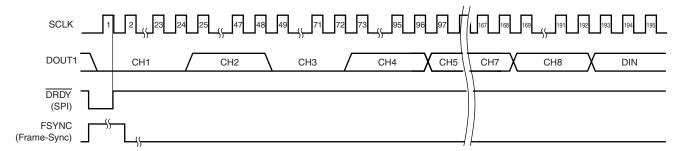

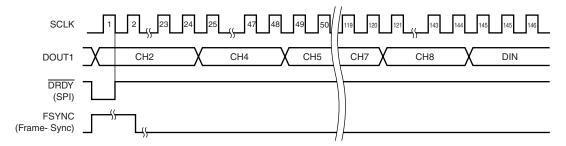

## Timing Requirements: Frame-Sync Format<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

| SYMBOL                | PARAM                                                | IETER                 | MIN   | TYP | MAX    | UNIT              |

|-----------------------|------------------------------------------------------|-----------------------|-------|-----|--------|-------------------|

|                       |                                                      | All modes             | 37    |     | 10,000 | ns                |

| t <sub>CLK</sub>      | CLK period (1 / f <sub>CLK</sub> )                   | High-Speed mode only  | 30.5  |     |        | ns                |

| t <sub>CPW</sub>      | CLK positive or negative pulse width                 |                       | 12    |     |        | ns                |

| t <sub>CS</sub>       | Falling edge of CLK to falling edge of S             | SCLK                  | -0.25 |     | 0.25   | t <sub>CLK</sub>  |

| t <sub>FRAME</sub>    | Frame period (1 / f <sub>DATA</sub> ) <sup>(2)</sup> |                       | 256   |     | 2560   | t <sub>CLK</sub>  |

| t <sub>FPW</sub>      | FSYNC positive or negative pulse widt                | h                     | 1     |     |        | t <sub>SCLK</sub> |

| t <sub>FS</sub>       | Rising edge of FSYNC to rising edge of               | of SCLK               | 5     |     |        | ns                |

| t <sub>SF</sub>       | Rising edge of SCLK to rising edge of FSYNC          |                       | 5     |     |        | ns                |

| t <sub>SCLK</sub>     | SCLK period <sup>(3)</sup>                           |                       | 1     |     |        | t <sub>CLK</sub>  |

| t <sub>SPW</sub>      | SCLK positive or negative pulse width                |                       | 0.4   |     |        | t <sub>CLK</sub>  |

| t <sub>DOHD</sub> (4) | SCLK falling edge to old DOUT invalid                | (hold time)           | 10    |     |        | ns                |

| t <sub>DOPD</sub> (5) | SCLK falling edge to new DOUT valid                  | (propagation delay)   |       |     | 31     | ns                |

| t <sub>MSBPD</sub>    | FSYNC rising edge to DOUT MSB vali                   | d (propagation delay) |       |     | 31     | ns                |

| t <sub>DIST</sub>     | New DIN valid to falling edge of SCLK                | (setup time)          | 6     |     |        | ns                |

| t <sub>DIHD</sub> (4) | Old DIN valid to falling edge of SCLK (              | hold time)            | 6     |     |        | ns                |

- Timing parameters are characterized or assured by design for specified temperature but not production tested.

- (2)

- Depends on MODE[1:0] and CLKDIV selection. See Table 5 ( $f_{CLK}$  /  $f_{DATA}$ ). SCLK must be continuously running and limited to ratios of 1, 1/2, 1/4, and 1/8 of  $f_{CLK}$ .

- t<sub>DOHD</sub> (DOUT hold time) and t<sub>DIHD</sub> (DIN hold time) are specified under opposite worst-case conditions (digital supply voltage and ambient temperature). Under equal conditions, with DOUT connected directly to DIN, the timing margin is > 4 ns.

- Load on DOUT = 20 pF.

Figure 2. Frame-Sync Format Timing Characteristics

## 7.8 Quality Conformance Inspection

MIL-STD-883, Method 5005 - Group A

| SUBGROUP | DESCRIPTION         | TEMP (°C)   |

|----------|---------------------|-------------|

| 1        | Static tests at     | 25          |

| 2        | Static tests at     | 125         |

| 3        | Static tests at     | <b>–</b> 55 |

| 4        | Dynamic tests at    | 25          |

| 5        | Dynamic tests at    | 125         |

| 6        | Dynamic tests at    | <b>–</b> 55 |

| 7        | Functional tests at | 25          |

## **Quality Conformance Inspection (continued)**

| SUBGROUP | DESCRIPTION         | TEMP (°C)  |

|----------|---------------------|------------|

| 8A       | Functional tests at | 125        |

| 8B       | Functional tests at | <b>-55</b> |

| 9        | Switching tests at  | 25         |

| 10       | Switching tests at  | 125        |

| 11       | Switching tests at  | <b>-55</b> |

| 12       | Setting time at     | 25         |

| 13       | Setting time at     | 125        |

| 14       | Setting time at     | -55        |

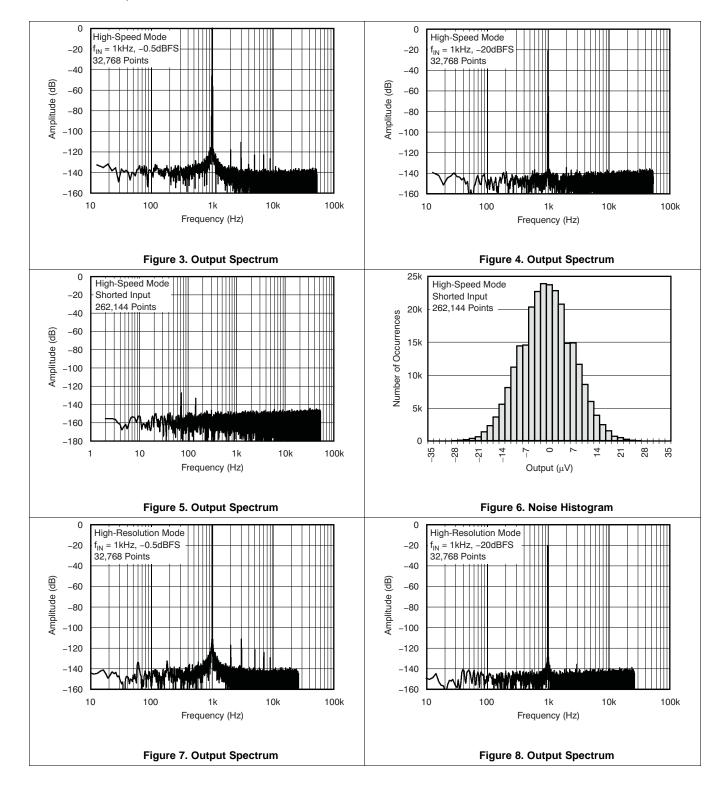

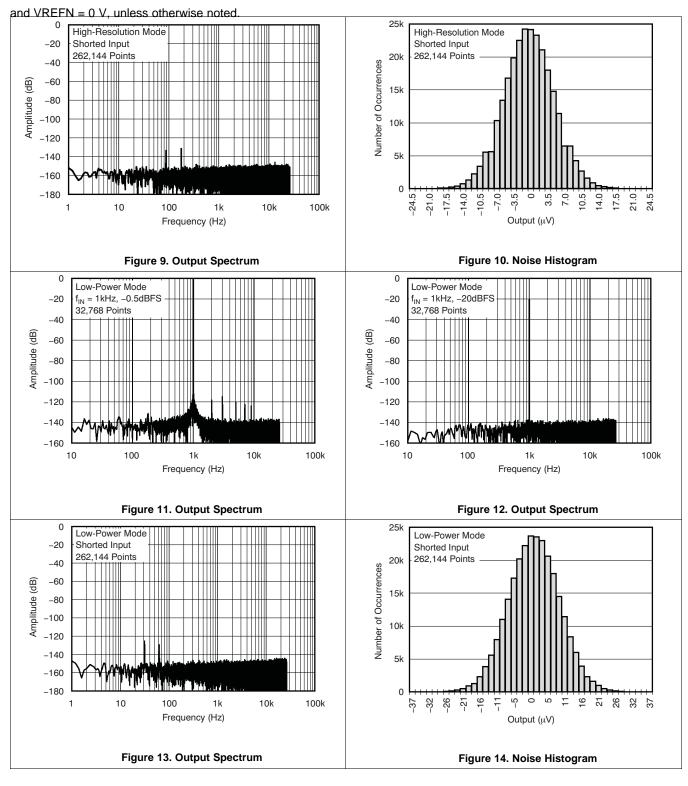

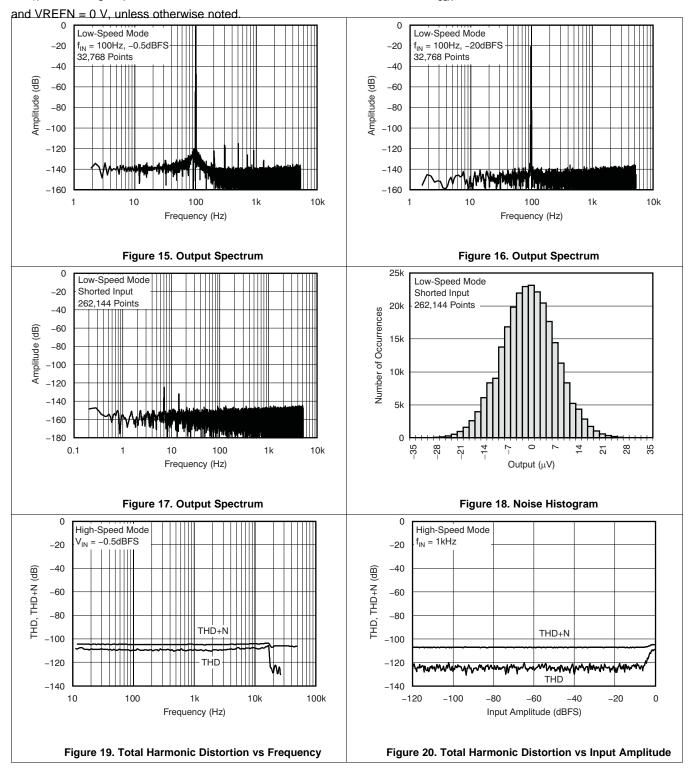

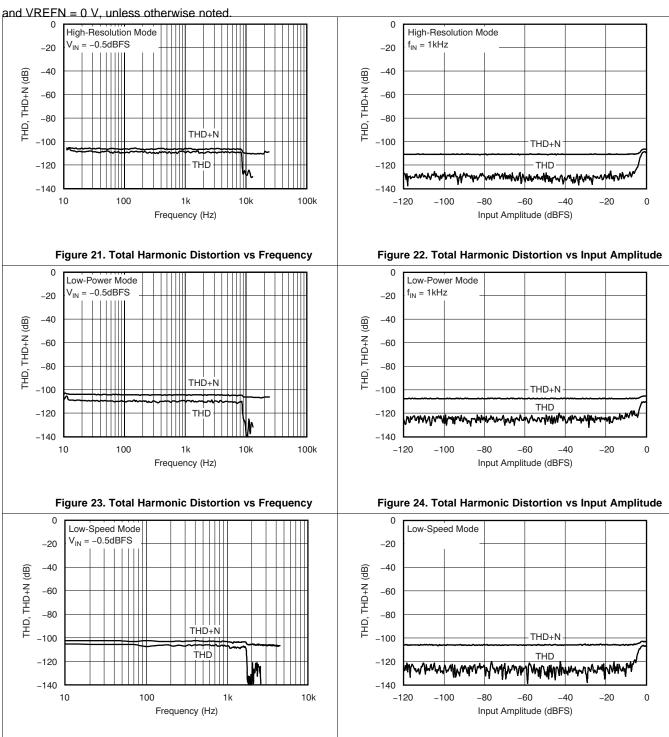

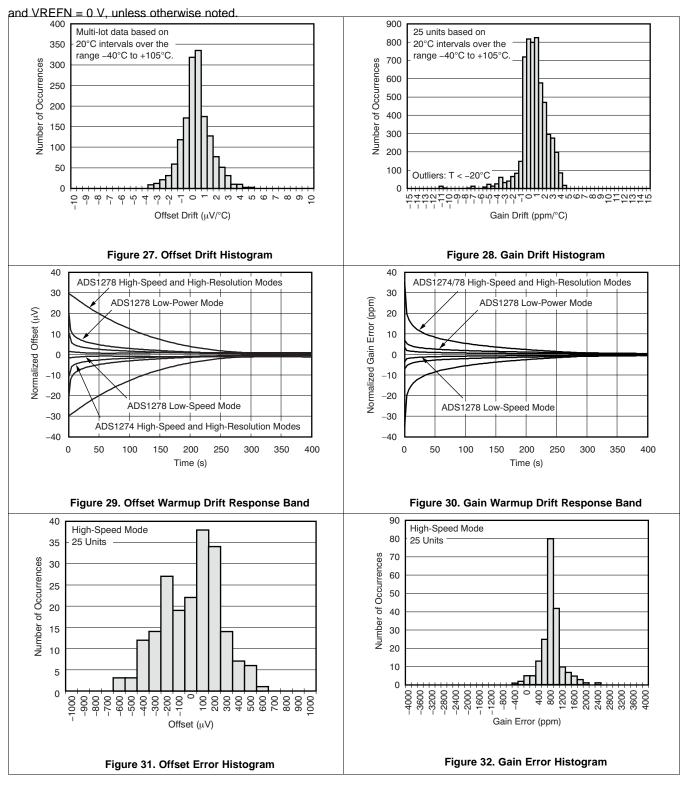

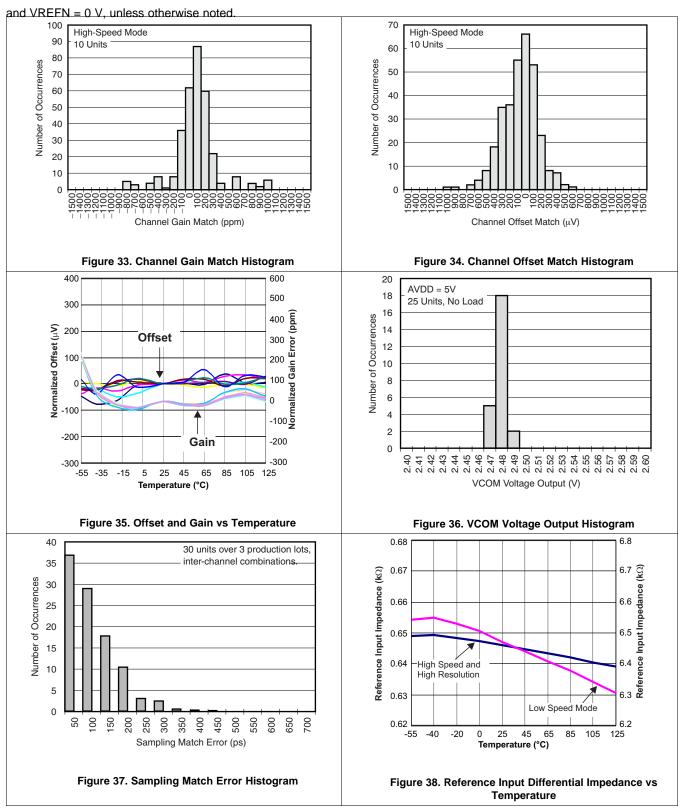

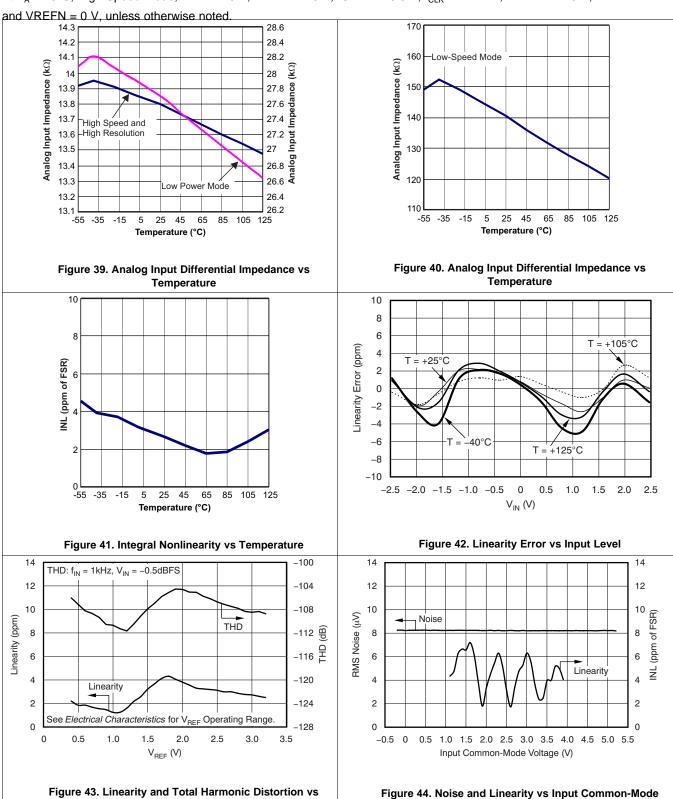

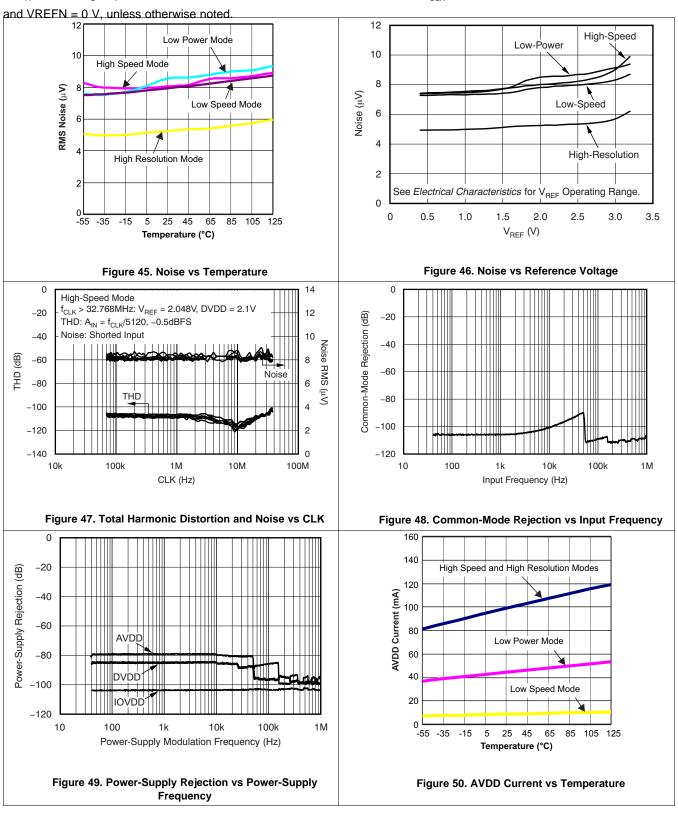

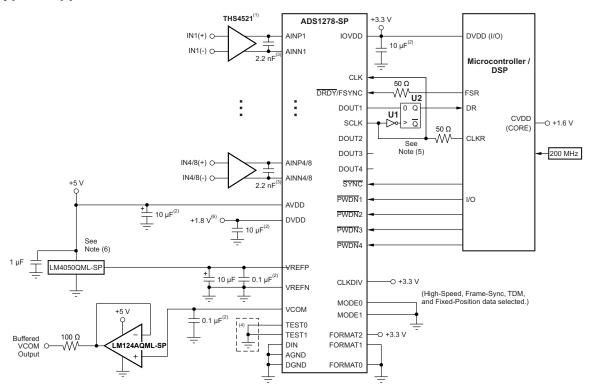

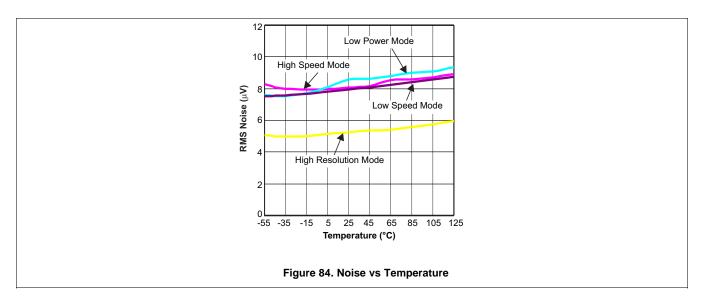

### 7.9 Typical Characteristics

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and VREFN = 0 V, unless otherwise noted.

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

Figure 25. Total Harmonic Distortion vs Frequency

Figure 26. Total Harmonic Distortion vs Input Amplitude

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

Reference Voltage

Voltage

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V,

### 8 Detailed Description

#### 8.1 Overview

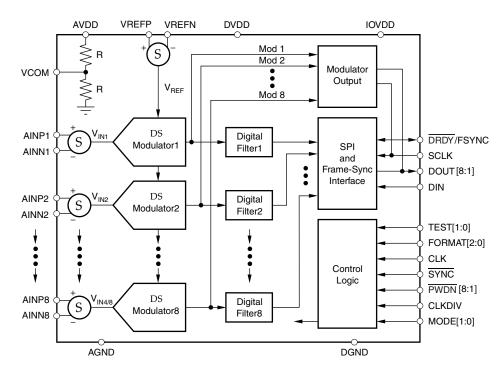

The ADS1278-SP is a delta-sigma ADC consisting of eight independent converters that digitize eight input signals in parallel.

The converter is composed of two main functional blocks to perform the ADC conversions: the modulator and the digital filter. The modulator samples the input signal together with sampling the reference voltage to produce a 1-s density output stream. The density of the output stream is proportional to the analog input level relative to the reference voltage. The pulse stream is filtered by the internal digital filter where the output conversion result is produced.

In operation, the input signal is sampled by the modulator at a high rate (typically 64x higher than the final output data rate). The quantization noise of the modulator is moved to a higher frequency range where the internal digital filter removes it. Oversampling results in very low levels of noise within the signal passband.

Since the input signal is sampled at a very high rate, input signal aliasing does not occur until the input signal frequency is at the modulator sampling rate. This architecture greatly relaxes the requirement of external antialiasing filters because of the high modulator sampling rate.

The ADS1278-SP is an octal 24-bit, delta-sigma ADC. It offers the combination of outstanding dc accuracy and superior ac performance. *Functional Block Diagram* section shows the block diagram. The converter is comprised of eight advanced, 6th-order, chopper-stabilized, delta-sigma modulators followed by low-ripple, linear phase FIR filters. The modulators measure the differential input signal,  $V_{IN} = (AINP - AINN)$ , against the differential reference,  $V_{REF} = (VREFP - VREFN)$ . The digital filters receive the modulator signal and provide a low-noise digital output. To allow tradeoffs among speed, resolution, and power, four operating modes are supported:

High-Speed, High-Resolution, Low-Power, and Low-Speed. Table 15 summarizes the performance of each mode.

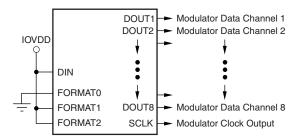

In High-Speed mode, the maximum data rate is 128 kSPS (when operating at 128 kSPS, Frame-Sync format must be used). In High-Resolution mode, the SNR = 111 dB ( $V_{REF}$  = 3.0 V); in Low-Power mode, the power dissipation is 31 mW/channel; and in Low-Speed mode, the power dissipation is only 7 mW/channel at 10.5 kSPS. The digital filters can be bypassed, enabling direct access to the modulator output.

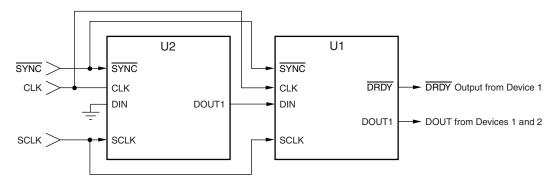

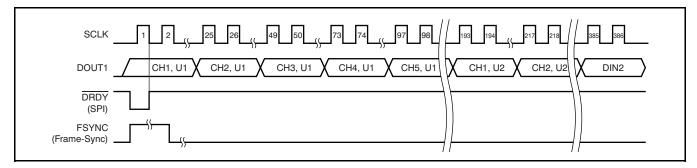

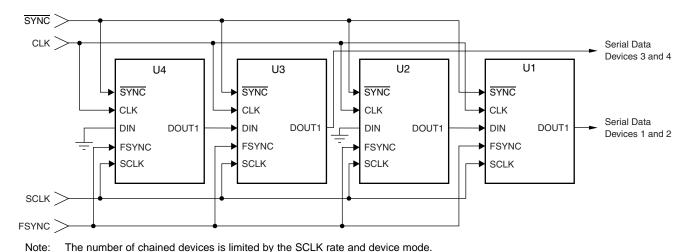

The ADS1278-SP is configured by simply setting the appropriate I/O pins—there are no registers to program. Data are retrieved over a serial interface that supports both SPI and Frame-Sync formats. The ADS1278-SP has a daisy-chainable output and the ability to synchronize externally, so it can be used conveniently in systems requiring more than eight channels.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Sampling Aperture Matching

The ADS1278-SP converter operates from the same CLK input. The CLK input controls the timing of the modulator sampling instant. The converter is designed such that the sampling skew, or modulator sampling aperture match between channels, is controlled. Furthermore, the digital filters are synchronized to start the convolution phase at the same modulator clock cycle. This design results in excellent phase match among the ADS1278-SP channels.

Figure 37 shows the inter-device channel sample matching for the ADS1278-SP.

#### 8.3.2 Frequency Response

The digital filter sets the overall frequency response. The filter uses a multi-stage FIR topology to provide linear phase with minimal passband ripple and high stop band attenuation. The filter coefficients are identical to the coefficients used in the ADS1271. The oversampling ratio of the digital filter (that is, the ratio of the modulator sampling to the output data rate, or  $f_{MOD}/f_{DATA}$ ) is a function of the selected mode, as shown in Table 1.

Table 1. Oversampling Ratio vs Mode

| MODE SELECTION  | OVERSAMPLING RATIO (f <sub>MOD</sub> /f <sub>DATA</sub> ) |

|-----------------|-----------------------------------------------------------|

| High-Speed      | 64                                                        |

| High-Resolution | 128                                                       |

| Low-Power       | 64                                                        |

| Low-Speed       | 64                                                        |

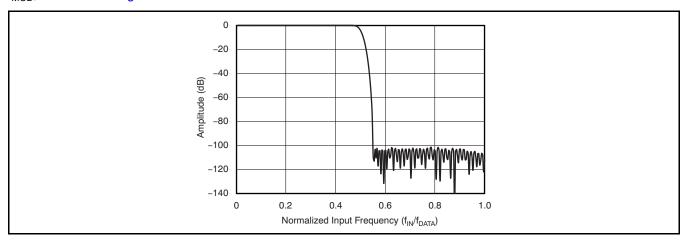

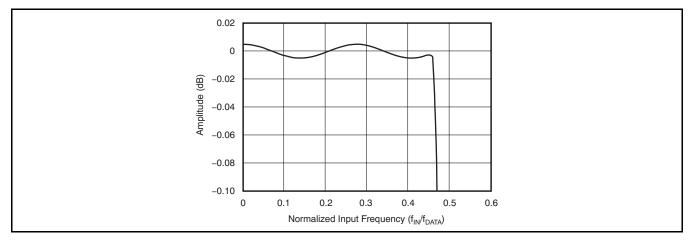

#### 8.3.2.1 High-Speed, Low-Power, And Low-Speed Modes

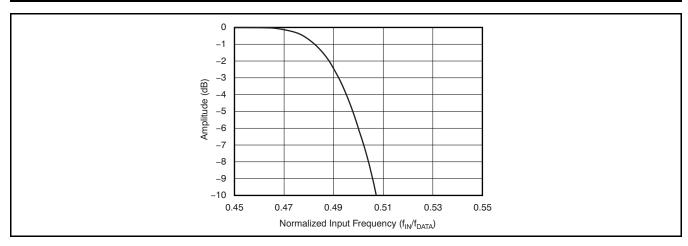

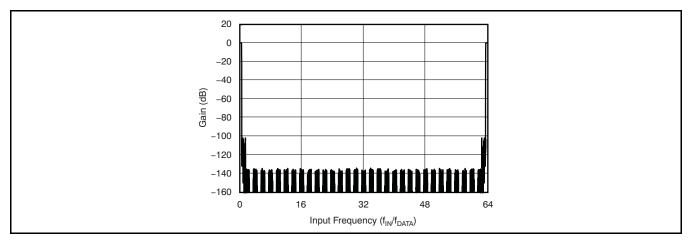

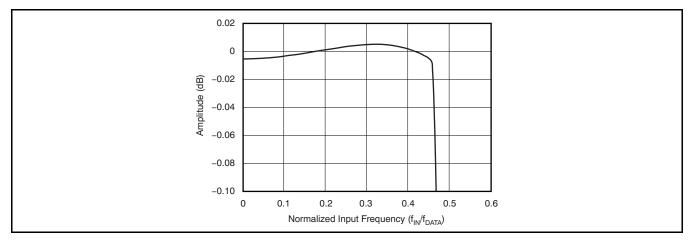

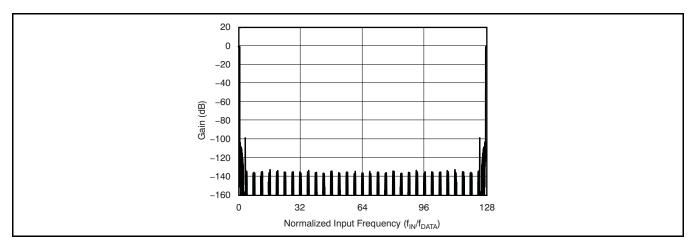

The digital filter configuration is the same in High-Speed, Low-Power, and Low-Speed modes with the oversampling ratio set to 64. Figure 54 shows the frequency response in High-Speed, Low-Power, and Low-Speed modes normalized to  $f_{DATA}$ . Figure 55 shows the passband ripple. The transition from passband to stop band is shown in Figure 56. The overall frequency response repeats at 64x multiples of the modulator frequency  $f_{MOD}$ , as shown in Figure 57.

Figure 54. Frequency Response For High-Speed, Low-Power, And Low-Speed Modes

Figure 55. Passband Response For High-Speed, Low-Power, And Low-Speed Modes

Figure 56. Transition Band Response For High-Speed, Low-Power, and Low-Speed Modes

Figure 57. Frequency Response Out To F<sub>MOD</sub> For High-Speed, Low-Power, And Low-Speed Modes

These image frequencies, if present in the signal and not externally filtered, will fold back (or alias) into the passband, causing errors. The stop band of the ADS1278-SP provides 100-dB attenuation of frequencies that begin just beyond the passband and continue out to  $f_{MOD}$ . Placing an anti-aliasing, low-pass filter in front of the ADS1278-SP inputs is recommended to limit possible high-amplitude, out-of-band signals and noise. Often, a simple RC filter is sufficient. Table 2 lists the image rejection versus external filter order.

Table 2. Antialiasing Filter Order Image Rejection

| ANTIALIASING FILTER ORDER | IMAGE REJECTION (dB) (f <sub>-3dB</sub> at f <sub>DATA</sub> ) |     |  |  |

|---------------------------|----------------------------------------------------------------|-----|--|--|

|                           | HS, LP, LS                                                     | HR  |  |  |

| 1                         | 39                                                             | 45  |  |  |

| 2                         | 75                                                             | 87  |  |  |

| 3                         | 111                                                            | 129 |  |  |

#### 8.3.2.2 High-Resolution Mode

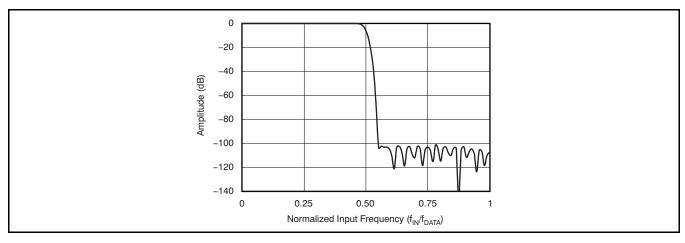

The oversampling ratio is 128 in High-Resolution mode. Figure 58 shows the frequency response in High-Resolution mode normalized to  $f_{DATA}$ . Figure 59 shows the passband ripple, and the transition from passband to stop band is shown in Figure 60. The overall frequency response repeats at multiples of the modulator frequency  $f_{MOD}$  (128 ×  $f_{DATA}$ ), as shown in Figure 61. The stop band of the ADS1278-SP provides 100-dB attenuation of frequencies that begin just beyond the passband and continue out to  $f_{MOD}$ . Placing an antialiasing, low-pass filter in front of the ADS1278-SP inputs is recommended to limit possible high-amplitude out-of-band signals and noise. Often, a simple RC filter is sufficient. Table 2 lists the image rejection versus external filter order.

Figure 58. Frequency Response For High-Resolution Mode

Figure 59. Passband Response For High-Resolution Mode

Figure 60. Transition Band Response For High-Resolution Mode

Figure 61. Frequency Response Out To  $F_{\text{MOD}}$  For High-Resolution Mode

#### 8.3.3 Phase Response

The ADS1278-SP incorporates a multiple stage, linear phase digital filter. Linear phase filters exhibit constant delay time versus input frequency (constant group delay). This characteristic means the time delay from any instant of the input signal to the same instant of the output data is constant and is independent of input signal frequency. This behavior results in essentially zero phase errors when analyzing multi-tone signals.

#### 8.3.4 Settling Time

As with frequency and phase response, the digital filter also determines settling time. Figure 62 shows the output settling behavior after a step change on the analog inputs normalized to conversion periods. The X-axis is given in units of conversion. Note that after the step change on the input occurs, the output data change very little prior to 30 conversion periods. The output data are fully settled after 76 conversion periods for High-Speed and Low-Power modes, and 78 conversion periods for High-Resolution mode.

Figure 62. Step Response

#### 8.3.5 Data Format

The ADS1278-SP outputs 24 bits of data in two complement format.

A positive full-scale input produces an ideal output code of 7FFFFh, and the negative full-scale input produces an ideal output code of 800000h. The output clips at these codes for signals exceeding full-scale. Table 3 summarizes the ideal output codes for different input signals.

Table 3. Ideal Output Code Versus Input Signal

| INPUT SIGNAL V <sub>IN</sub> (AINP – AINN)               | IDEAL OUTPUT CODE <sup>(1)</sup> |

|----------------------------------------------------------|----------------------------------|

| ≥ +V <sub>REF</sub>                                      | 7FFFFh                           |

| $\frac{+ V_{REF}}{2^{23} - 1}$                           | 000001h                          |

| 0                                                        | 000000h                          |

| $\frac{-V_{REF}}{2^{23}-1}$                              | FFFFFFh                          |

| $\leq -V_{REF} \left( \frac{2^{23}}{2^{23} - 1} \right)$ | 800000h                          |

(1) Excludes effects of noise, INL, offset, and gain errors.

#### 8.3.6 Analog Inputs (AINP, AINN)

The ADS1278-SP measures each differential input signal  $V_{IN}$  = (AINP – AINN) against the common differential reference  $V_{REF}$  = (VREFP – VREFN). The most positive measurable differential input is + $V_{REF}$ , which produces the most positive digital output code of 7FFFFFh. Likewise, the most negative measurable differential input is - $V_{REF}$ , which produces the most negative digital output code of 800000h.

For optimum performance, the inputs of the ADS1278-SP are intended to be driven differentially. For single-ended applications, one of the inputs (AINP or AINN) can be driven while the other input is fixed (typically to AGND or 2.5 V). Fixing the input to 2.5 V permits bipolar operation, thereby allowing full use of the entire converter range.

While the ADS1278-SP measures the differential input signal, the absolute input voltage is also important. This value is the voltage on either input (AINP or AINN) with respect to AGND. The range for this voltage is:

$$-0.1 \text{ V} < (AINN \text{ or AINP}) < AVDD + 0.1 \text{ V}$$

If either input is taken below -0.4 V or above (AVDD + 0.4 V), ESD protection diodes on the inputs may turn on. If these conditions are possible, external Schottky clamp diodes or series resistors may be required to limit the input current to safe values (see the *Absolute Maximum Ratings* table).

The ADS1278-SP is a very high-performance ADC. For optimum performance, it is critical that the appropriate circuitry be used to drive the ADS1278-SP inputs. See the *Application Information* section for several recommended circuits.

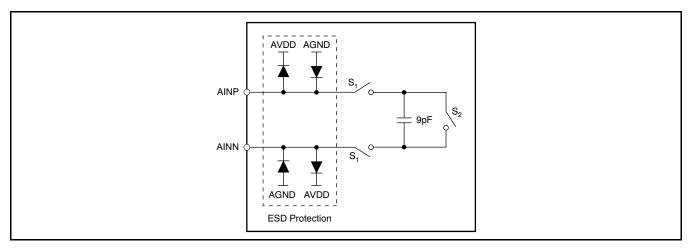

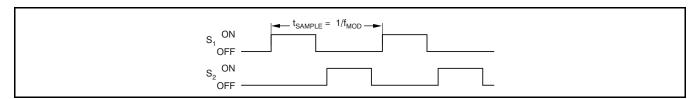

The ADS1278-SP uses switched-capacitor circuitry to measure the input voltage. Internal capacitors are charged by the inputs and then discharged. Figure 63 shows a conceptual diagram of these circuits. Switch  $S_2$  represents the net effect of the modulator circuitry in discharging the sampling capacitor; the actual implementation is different. The timing for switches  $S_1$  and  $S_2$  is shown in Figure 64. The sampling time ( $t_{SAMPLE}$ ) is the inverse of modulator sampling frequency ( $t_{MOD}$ ) and is a function of the mode, the CLKDIV input, and CLK frequency, as shown in Table 4.

Figure 63. Equivalent Analog Input Circuitry

Figure 64. S<sub>1</sub> and S<sub>2</sub> Switch Timing for Figure 63

| Table 4   | Modulator  | Frequency    | (F)   | Mode   | Selection |

|-----------|------------|--------------|-------|--------|-----------|

| I able 4. | Wiodulator | I I EUUEIICV | U MOD | IVIOUE | SCICCIOII |

| MODE SELECTION  | CLKDIV | f <sub>MOD</sub>      |

|-----------------|--------|-----------------------|

| High-Speed      | 1      | f <sub>CLK</sub> / 4  |

| High-Resolution | 1      | f <sub>CLK</sub> / 4  |

| Lew Pewer       | 1      | f <sub>CLK</sub> / 8  |

| Low-Power       | 0      | f <sub>CLK</sub> / 4  |

| Law Craad       | 1      | f <sub>CLK</sub> / 40 |

| Low-Speed       | 0      | f <sub>CLK</sub> / 8  |

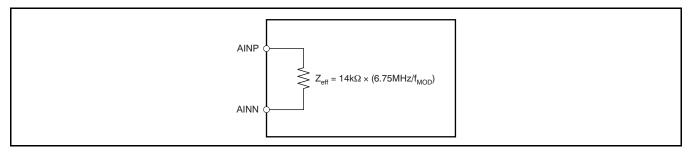

The average load presented by the switched capacitor input can be modeled with an effective differential impedance, as shown in Figure 65. Note that the effective impedance is a function of  $f_{\text{MOD}}$ .

Figure 65. Effective Input Impedances

# 8.3.7 Voltage Reference Inputs (VREFP, VREFN)

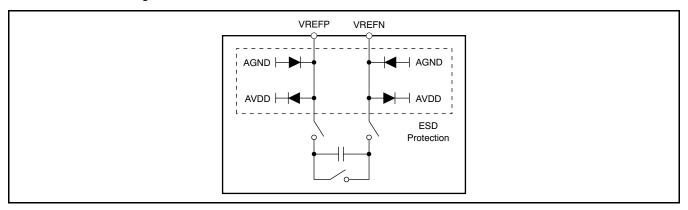

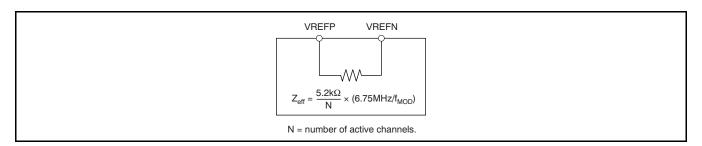

The voltage reference for the ADS1278-SP ADC is the differential voltage between VREFP and VREFN:  $V_{REF} = (VREFP - VREFN)$ . The voltage reference is common to all channels. The reference inputs use a structure similar to that of the analog inputs with the equivalent circuitry on the reference inputs shown in Figure 66. As with the analog inputs, the load presented by the switched capacitor can be modeled with an effective impedance, as shown in Figure 67. However, the reference input impedance depends on the number of active (enabled) channels in addition to  $f_{MOD}$ . As a result of the change of reference input impedance caused by enabling and disabling channels, the regulation and setting time of the external reference should be noted, so as not to affect the readings.

Figure 66. Equivalent Reference Input Circuitry

Figure 67. Effective Reference Impedance

ESD diodes protect the reference inputs. To keep these diodes from turning on, make sure the voltages on the reference pins do not go below AGND by more than 0.4 V, and likewise do not exceed AVDD by 0.4 V. If these conditions are possible, external Schottky clamp diodes or series resistors may be required to limit the input current to safe values (see the *Absolute Maximum Ratings* table).

Note that the valid operating range of the reference inputs is limited to the following parameters:

$-0.1 \text{ V} \leq \text{VREFN} \leq +0.1 \text{ V}$

VREFN + 0.5 V ≤ VREFP ≤ AVDD + 0.1 V

#### 8.3.8 Clock Input (CLK)

The ADS1278-SP requires a clock input for operation. The individual converters of the ADS1278-SP operate from the same clock input. At the maximum data rate, the clock input can be either 27 MHz or 13.5 MHz for Low-Power mode, or 27MHz or 5.4 MHz for Low-Speed mode, determined by the setting of the CLKDIV input. For High-Speed mode, the maximum CLK input frequency is 32.768 MHz. For High-Resolution mode, the maximum CLK input frequency is 27 MHz. The selection of the external clock frequency ( $f_{CLK}$ ) does not affect the resolution of the ADS1278-SP. Use of a slower  $f_{CLK}$  can reduce the power consumption of an external clock buffer. The output data rate scales with clock frequency, down to a minimum clock frequency of  $f_{CLK}$  = 100 kHz. Table 5 summarizes the ratio of the clock input frequency ( $f_{CLK}$ ) to data rate ( $f_{DATA}$ ), maximum data rate and corresponding maximum clock input for the four operating modes.

As with any high-speed data converter, a high-quality, low-jitter clock is essential for optimum performance. Crystal clock oscillators are the recommended clock source. Make sure to avoid excess ringing on the clock input; keeping the clock trace as short as possible, and using a  $50-\Omega$  series resistor placed close to the source end, often helps.

**Table 5. Clock Input Options**

| MODE SELECTION  | MAX f <sub>CLK</sub> (MHz) | CLKDIV | f <sub>CLK</sub> /f <sub>DATA</sub> | DATA RATE (SPS) |  |

|-----------------|----------------------------|--------|-------------------------------------|-----------------|--|

| High-Speed      | 32.768                     | 1      | 256                                 | 128,000         |  |

| High-Resolution | 27                         | 1      | 512                                 | 52,734          |  |

| Law Dawer       | 27                         | 1      | 512                                 | 50.704          |  |

| Low-Power       | 13.5                       | 0      | 256                                 | 52,734          |  |

| Law Speed       | 27                         | 1      | 2,560                               | 10.547          |  |

| Low-Speed       | 5.4                        | 0      | 512                                 | 10,547          |  |

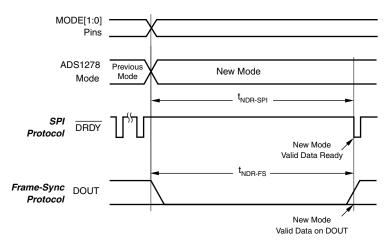

#### 8.3.9 Mode Selection (MODE)