JAJS168H - JUNE 2005 - REVISED JUNE 2025

# ADS123x、2 および4 チャネル、24 ビット、デルタ・シグマ ADC、ブリッジ・ センサ用

### 1 特長

- ブリッジ センサ用の包括的なフロントエンド

- ゲイン= 1 で 23.5 ビットの実効分解能

- ゲイン=64で19.2ビットのノイズフリー分解能

- 低ノイズ PGA

- 1、2、64、128 のゲインを選択可能

- RMS ノイズ:

- ゲイン 128、10SPS 動作時のノイズは 17nV

- ゲイン 128、80SPS 動作時のノイズは 44nV

- 50Hz と 60Hz を同時に除去時に 100dB

- 柔軟性の高いクロッキング:

- 高精度内部発振回路

- 外付け水晶振動子 (オプション)

- 10SPS または 80SPS のデータレートを選択可能

- 容易なレシオメトリック測定:

- 広い入力電圧範囲 (最大 5V)

- 2 チャネル差動入力、温度センサ内蔵 (ADS1232)

- 4 チャネル差動入力 (ADS1234)

- 2線式シリアルインターフェイス

- 電源電圧範囲:2.7V ~ 5.3V

- 温度範囲:-40℃ ~ +105℃

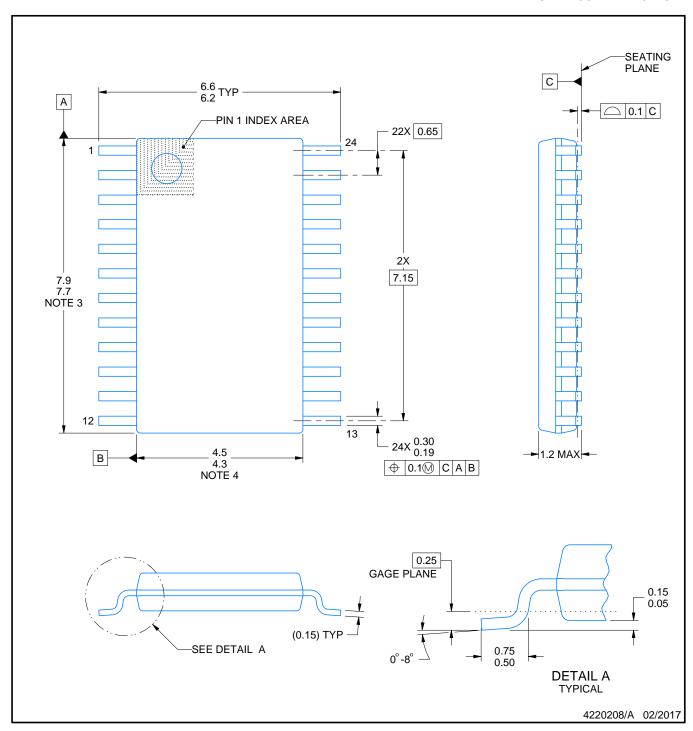

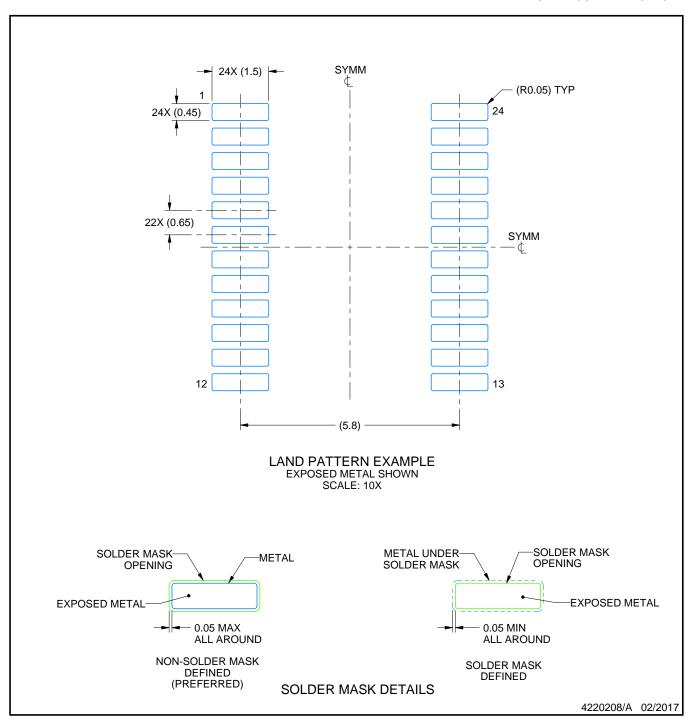

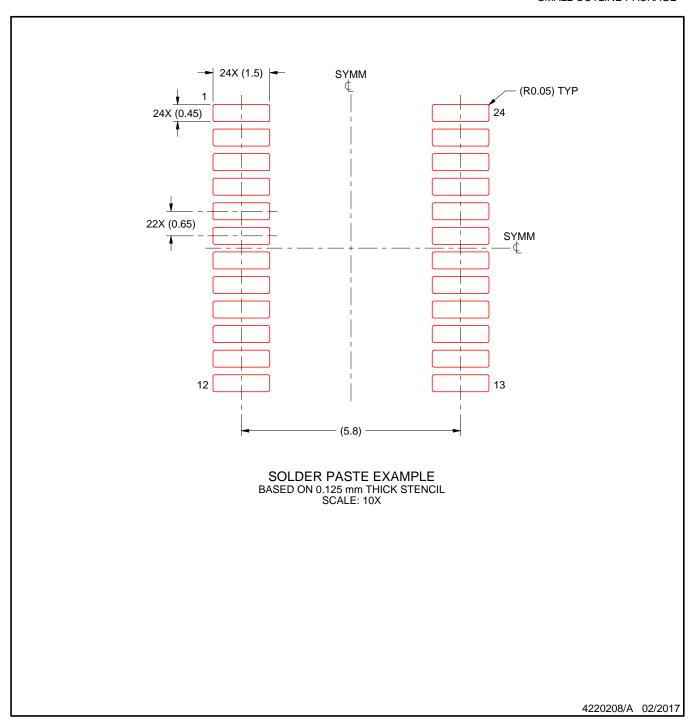

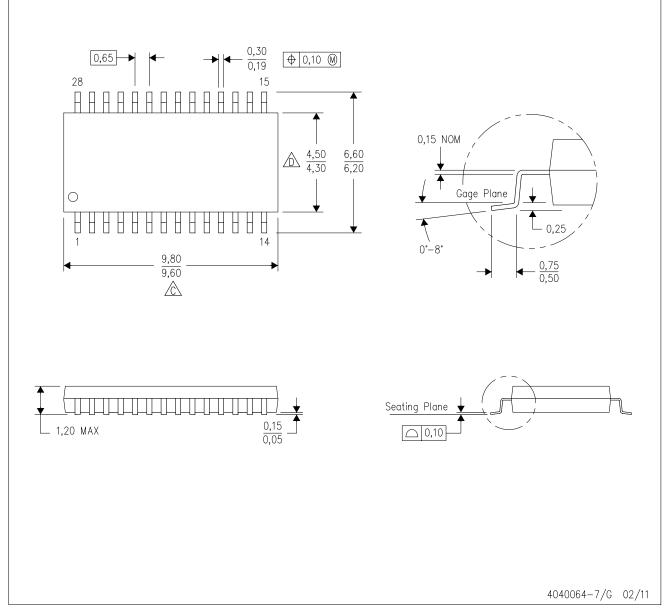

- パッケージ:TSSOP-24 (ADS1232) または TSSOP-28 (ADS1234)

## 2 アプリケーション

- 計量器

- PLC 重量計モジュール

- 圧力センサ

### 3 説明

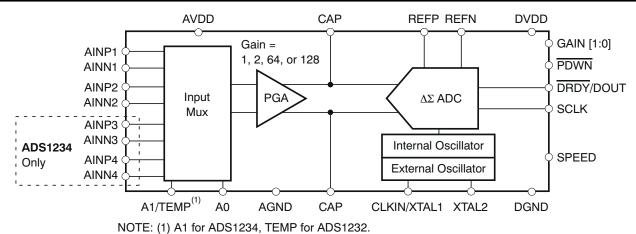

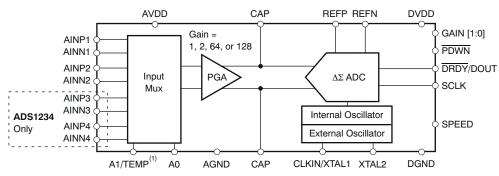

ADS1232 および ADS1234 (ADS123x) は、高精度の 24 ビット A/D コンバータ (ADC) です。 低ノイズのプログラ マブル ゲイン アンプ (PGA)、高精度デルタ シグマ ADC、内部発振器を搭載しています。ADS123x は、重量 計、歪みゲージ、圧力センサなどのブリッジ センサ アプリ ケーション用の包括的なフロントエンドソリューションを提 供します。

入力マルチプレクサ (MUX) は、2 つ (ADS1232) または 4 つ (ADS1234) の差動入力を受け入れます。ADS1232 には、周囲温度を監視する温度センサも搭載されていま す。低ノイズ PGA は、1、2、64、128 のゲインを選択で き、±2.5V、±1.25V、±39mV、±19.5mV のフルスケール 差動入力をサポートします。

デルタ シグマ ADC は、最大 23.5 ビットの有効分解能を 実現し、次の 2 つのデータ レートをサポートします。 10SPS (50Hz および 60Hz 除去) および 80SPS。 ADS123x は、発振器または水晶振動子、または内部発 振器を使用して、外部からクロックを供給できます。

オフセットキャリブレーションは、オンデマンドで実行され、 ADS123x は、低消費電力のスタンバイ モードにするか、 電源オフモードで完全にシャットオフすることができます。 ADS123x は、シンプルなピン駆動制御で動作します。プ ログラムするためのデジタルレジスタはありません。

データは 2 線式のシリアル インターフェイスを経由して出 力され、MSP430 や他のマイクロコントローラに直接接続 できます。

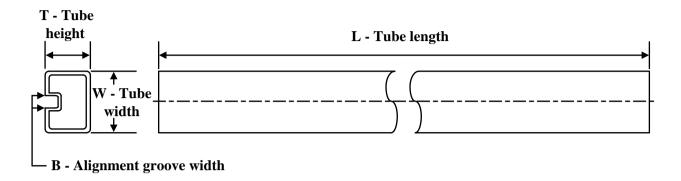

#### パッケージ情報

| 部品番号    | パッケージ (1)      | パッケージ サイズ <sup>(2)</sup> |  |  |  |  |

|---------|----------------|--------------------------|--|--|--|--|

| ADS1232 | PW (TSSOP, 24) | 7.8mm × 6.4mm            |  |  |  |  |

| ADS1234 | PW (TSSOP, 28) | 9.7mm × 6.4mm            |  |  |  |  |

- 詳細については、メカニカル、パッケージ、および注文情報をご覧 (1)

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ (2) ンを含みます。

51E. (1) AT 101 AD01204, TEMIT 101 AD0120.

ブロック図

## **Table of Contents**

| 1 特長                                 | 1  | 7.3 Feature Description                 | 16              |

|--------------------------------------|----|-----------------------------------------|-----------------|

| 2アプリケーション                            |    | 7.4 Device Functional Modes             | <mark>25</mark> |

| 3 説明                                 |    | 8 Application and Implementation        | 29              |

| 4 Pin Configuration and Functions    |    | 8.1 Application Information             | 29              |

| 5 Specifications                     |    | 8.2 Typical Application                 |                 |

| 5.1 Absolute Maximum Ratings         |    | 8.3 Power Supply Recommendations        | 31              |

| 5.2 ESD Ratings                      |    | 8.4 Layout                              | 31              |

| 5.3 Recommended Operating Conditions |    | 9 Device and Documentation Support      | 34              |

| 5.4 Thermal Information              |    | 9.1ドキュメントの更新通知を受け取る方法                   | 34              |

| 5.5 Electrical Characteristics       |    | 9.2 サポート・リソース                           | 34              |

| 5.6 Typical Characteristics          |    | 9.3 Trademarks                          | 34              |

| 6 Parameter Measurement Information  |    | 9.4 静電気放電に関する注意事項                       | 34              |

| 6.1 Noise Performance                | 15 | 9.5 用語集                                 | 34              |

| 7 Detailed Description               | 16 | 10 Revision History                     |                 |

| 7.1 Overview                         |    | 11 Mechanical, Packaging, and Orderable |                 |

| 7.2 Functional Block Diagram         | 16 | Information                             | 35              |

| •                                    |    |                                         |                 |

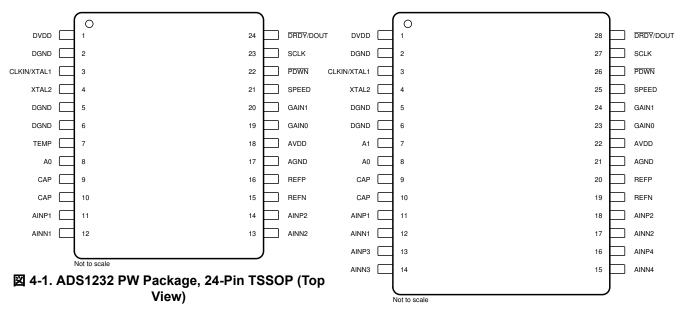

## 4 Pin Configuration and Functions

図 4-2. ADS1234 PW Package, 28-Pin TSSOP (Top View)

表 4-1. Pin Functions

|             | PIN     |         |                |                                                                                                                                                                  |  |  |

|-------------|---------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | ADS1232 | ADS1234 | TYPE           | DESCRIPTION                                                                                                                                                      |  |  |

| A0          | 8       | 8       | Digital input  | Input MUX select pins. See 表 7-1 and 表 7-2 for more information.                                                                                                 |  |  |

| A1          | _       | 7       | Digital input  | Input MUX select pins. See 表 7-1 and 表 7-2 for more information.                                                                                                 |  |  |

| AGND        | 17      | 21      | Analog         | Analog ground                                                                                                                                                    |  |  |

| AINN1       | 12      | 12      | Analog input   | Negative analog input channel 1                                                                                                                                  |  |  |

| AINN2       | 13      | 17      | Analog input   | Negative analog input channel 2                                                                                                                                  |  |  |

| AINN3       | _       | 14      | Analog input   | Negative analog input channel 3                                                                                                                                  |  |  |

| AINN4       | _       | 15      | Analog input   | Negative analog input channel 4                                                                                                                                  |  |  |

| AINP1       | 11      | 11      | Analog input   | Positive analog input channel 1                                                                                                                                  |  |  |

| AINP2       | 14      | 18      | Analog input   | Positive analog input channel 2                                                                                                                                  |  |  |

| AINP3       | _       | 13      | Analog input   | Positive analog input channel 3                                                                                                                                  |  |  |

| AINP4       | _       | 16      | Analog input   | Positive analog input channel 4                                                                                                                                  |  |  |

| AVDD        | 18      | 22      | Analog         | Analog power supply: 2.7V to 5.3V                                                                                                                                |  |  |

| CAP         | 9, 10   | 9, 10   | Analog         | PGA bypass, connect a 0.1µF capacitor across pins 9 and 10                                                                                                       |  |  |

| CLKIN/XTAL1 | 3       | 3       | Digital input  | External crystal connection 1, or external clock input, or tie low to activate internal oscillator. See the <i>Clock Sources</i> section for more information.   |  |  |

| DGND        | 2, 5, 6 | 2, 5, 6 | Digital        | Digital ground                                                                                                                                                   |  |  |

| DRDY/DOUT   | 24      | 28      | Digital output | Dual-purpose output:  Data ready indicates valid data by going low.  Data output outputs data, MSB first, on the first rising edge of SCLK.                      |  |  |

| DVDD        | 1       | 1       | Digital        | Digital power supply: 2.7V to 5.3V                                                                                                                               |  |  |

| GAIN0       | 19      | 23      | Digital input  | Gain select pins. See the Low-Noise PGA section for more information.                                                                                            |  |  |

| GAIN1       | 20      | 24      | Digital input  | Gain select pins. See the Low-Noise PGA section for more information.                                                                                            |  |  |

| REFN        | 15      | 19      | Analog input   | Negative reference input                                                                                                                                         |  |  |

| REFP        | 16      | 20      | Analog input   | Positive reference input                                                                                                                                         |  |  |

| PDWN        | 22      | 26      | Digital input  | Power-down: hold this pin low to power down and reset the ADC. Toggle the pin at device power-up. See the <i>Power-Up Sequence</i> section for more information. |  |  |

Copyright © 2025 Texas Instruments Incorporated

1

## 表 4-1. Pin Functions (続き)

| PIN   |         |         |               |                                                                                                                                                                                                                                    |

|-------|---------|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | ADS1232 | ADS1234 | TYPE          | DESCRIPTION                                                                                                                                                                                                                        |

| SCLK  | 23      | 27      | Digital input | Serial clock: clock out data on the rising edge. Also used to initiate offset calibration and standby modes. See the <i>Offset Calibration Mode</i> and <i>Standby Mode With Offset-Calibration</i> sections for more information. |

| SPEED | 21      | 25      | Digital input | Data rate select. See the <i>Data Rate</i> section for more information.                                                                                                                                                           |

| TEMP  | 7       | _       | Digital input | Temperature sensor select. See 表 7-1 for more information.                                                                                                                                                                         |

| XTAL2 | 4       | 4       | Digital       | External crystal connection 2                                                                                                                                                                                                      |

### **5 Specifications**

### 5.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                       |                                                                        | MIN        | MAX        | UNIT |

|-----------------------|------------------------------------------------------------------------|------------|------------|------|

|                       | AVDD to AGND                                                           | -0.3       | 6          |      |

| Power-supply voltage  | DVDD to DGND                                                           | -0.3       | 6          | V    |

|                       | AGND to DGND                                                           | -0.3       | 0.3        |      |

| Analog input voltage  | AINNx, AINPx, REFP, REFN                                               | AGND - 0.3 | AVDD + 0.3 | V    |

| Digital input voltage | A0, A1, CLKIN/XTAL1, XTAL2, DRDY/DOUT, GAIN0, GAIN1, PWDN, SCLK, SPEED | DGND - 0.3 | DVDD + 0.3 | V    |

| Input current         | Continuous, all pins except power-supply pins <sup>(2)</sup>           | -10        | 10         | mA   |

| Tommoratura           | Junction, T <sub>J</sub>                                               |            | 150        | °C   |

| Temperature           | Storage, T <sub>stg</sub>                                              | -60        | 150        | C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 5.2 ESD Ratings

|                              |                                                                                |                                                                   | VALUE | UNIT |

|------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|------|

|                              | Electrostatic                                                                  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±750  | V    |

| V <sub>(ESD)</sub> discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500                                                              | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Input and output pins are diode-clamped to the internal power supplies. Limit the input current to 10mA in the event the analog input voltage exceeds AVDD + 0.3V or AGND – 0.3V, or if the digital input voltage exceeds DVDD + 0.3V or DGND – 0.3V.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

over operating ambient temperature range (unless otherwise noted)

|                     |                               |                                     | MIN                       | NOM MAX                   | UNIT |

|---------------------|-------------------------------|-------------------------------------|---------------------------|---------------------------|------|

| POWER S             | UPPLY                         |                                     | <u> </u>                  |                           |      |

|                     | Analog power supply           | AVDD to AGND                        | 2.7                       | 5.3                       | V    |

|                     | Digital power supply          | DVDD to DGND                        | 2.7                       | 5.3                       | V    |

| ANALOG              | INPUTS                        |                                     | '                         | -                         |      |

|                     | Full-scale input voltage      | $V_{(AINPx)} - V_{(AINNx)}$         | ±0.5                      | 5 V <sub>REF</sub> / Gain | V    |

|                     | Common model in muture no     | Gain = 1 and 2                      | AGND - 0.1                | AVDD + 0.1                | V    |

|                     | Common-mode input range       | Gain = 64 and 128                   | AGND + 1.5                | AVDD – 1.5                | V    |

| VOLTAGE             | REFERENCE INPUTS              |                                     | '                         |                           |      |

| V <sub>REF</sub>    | Voltage reference input       | $V_{REF} = V_{(REFP)} - V_{(REFN)}$ | 1.5                       | AVDD AVDD + 0.1           | V    |

| V <sub>(REFN)</sub> | Negative reference input      |                                     | AGND - 0.1                | V <sub>(REFP)</sub> – 1.5 | V    |

| V <sub>(REFP)</sub> | Positive reference input      |                                     | V <sub>(REFN)</sub> + 1.5 | AVDD + 0.1                | V    |

| EXTERNA             | L CLOCK INPUT                 |                                     | '                         |                           |      |

| f <sub>CLK</sub>    | External clock frequency      |                                     | 0.2                       | 4.9152 8                  | MHz  |

| SERIAL IN           | ITERFACE CLOCK INPUT          |                                     | 1                         | 1                         |      |

| f <sub>(SCLK)</sub> | Serial clock frequency        |                                     |                           | 5                         | MHz  |

| DIGITAL II          | NPUTS                         |                                     | '                         |                           |      |

|                     | Input voltage                 |                                     | DGND                      | DVDD + 0.1                | V    |

| TEMPERA             | TURE                          | 1                                   | 1                         | I                         |      |

| T <sub>A</sub>      | Operating ambient temperature | 1                                   | -40                       | 105                       | °C   |

## **5.4 Thermal Information**

|                       |                                              | ADS1232    | ADS1234    |      |

|-----------------------|----------------------------------------------|------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | PW (TSSOP) | UNIT |

|                       |                                              | 24 PINS    | 28 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 82.4       | 74.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 25.5       | 21.9       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 38.1       | 32.9       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.3        | 1.1        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 37.6       | 32.4       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

1

#### 5.5 Electrical Characteristics

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +105°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD = DVDD =  $V_{(REFP)} = 5V$ ,  $V_{(REFN)} = AGND$ , and  $f_{CLK} = 4.9152MHz$  (unless otherwise noted)

|                   |                                   | , , , ,                                                                                | JEIK        |                           |          |                         |

|-------------------|-----------------------------------|----------------------------------------------------------------------------------------|-------------|---------------------------|----------|-------------------------|

|                   | PARAMETER                         | TEST CONDITIONS                                                                        | MIN         | TYP                       | MAX      | UNIT                    |

| ANALOG II         | NPUTS                             |                                                                                        |             |                           |          |                         |

|                   |                                   | Gain = 1                                                                               |             | ±3                        |          |                         |

|                   | Differential input current        | Gain = 2                                                                               |             | ±6                        |          | nA                      |

|                   |                                   | Gain = 64, 128                                                                         |             | ±3.5                      |          |                         |

| SYSTEM P          | ERFORMANCE                        | ·                                                                                      |             |                           |          |                         |

|                   | Resolution                        | No missing codes                                                                       | 24          |                           |          | Bits                    |

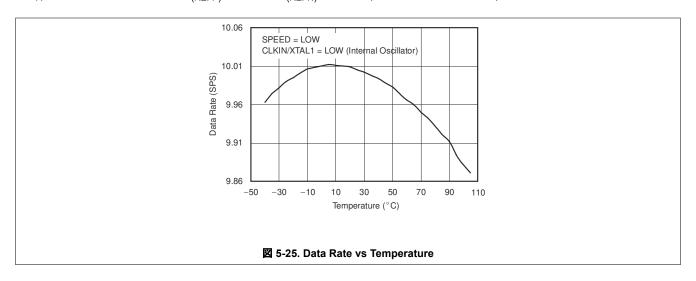

|                   |                                   | Internal oscillator, SPEED = high                                                      | 78          | 80                        | 82.4     |                         |

| £                 | Deta rata                         | Internal oscillator, SPEED = low                                                       | 9.75        | 10                        | 10.3 SPS |                         |

| f <sub>data</sub> | Data rate                         | External oscillator, SPEED = high                                                      |             | f <sub>CLK</sub> / 61,440 |          | 373                     |

|                   |                                   | External oscillator, SPEED = low                                                       | f           | <sub>CLK</sub> / 491,520  |          |                         |

|                   | Digital filter settling time      | Full settling, readings synchronized with A0, A1 pins                                  |             | 4                         |          | Conversions             |

|                   |                                   | Differential input, end-point fit, gain = 1, 2                                         | -0.001      | ±0.0002                   | 0.001    |                         |

| INL               | Integral nonlinearity             | Differential input, end-point fit, gain = 64, 128                                      |             | ±0.0004                   |          | % of FSR <sup>(1)</sup> |

|                   | (2)                               | Gain = 1                                                                               | -5          | ±0.2                      | 5        | 150                     |

|                   | Input offset error <sup>(2)</sup> | Gain = 128                                                                             | -1          | ±0.02                     | 1        | ppm of FS               |

|                   |                                   | Gain = 1                                                                               |             | ±0.3                      |          | μV/°C                   |

|                   | Input offset drift                | Gain = 128                                                                             |             | ±10                       |          | nV/°C                   |

|                   | - (2)                             | Gain = 1                                                                               | -0.02       | ±0.001                    | 0.02     |                         |

|                   | Gain error <sup>(3)</sup>         | Gain = 128                                                                             | -0.1        | ±0.01                     | 0.1      | %                       |

|                   |                                   | Gain = 1                                                                               |             | ±0.2                      |          | ppm/°C                  |

|                   | Gain drift                        | Gain = 128                                                                             |             | ±2.5                      |          |                         |

|                   |                                   | Internal oscillator, f <sub>DATA</sub> = 10SPS<br>f <sub>IN</sub> = 50Hz or 60Hz, ±1Hz | 100         | 110                       |          |                         |

| NMRR              | Normal-mode rejection ratio (4)   | External oscillator, f <sub>DATA</sub> = 10SPS<br>f <sub>IN</sub> = 50Hz or 60Hz, ±1Hz | 120         | 130                       |          | dB                      |

|                   |                                   | At DC, gain = 1, $\Delta$ V = 1V, $V_{CM}$ = AVDD / 2                                  | 95          | 110                       |          |                         |

| CMRR              | Common-mode rejection ratio       | At DC, gain = 128, $\Delta$ V = 0.1V, $V_{CM}$ = AVDD / 2                              | 95          | 110                       |          | dB                      |

| e <sub>n</sub>    | Input-referred noise              |                                                                                        | See the Noi | se Performance s          | ection   |                         |

| DCDD              | D                                 | AVDD, at DC, gain = 1, ΔV = 1V                                                         |             | 85                        |          | ٦D                      |

| PSRR              | Power-supply rejection            | AVDD, at DC, gain = 128, ΔV = 0.1V                                                     | 100         | 120                       |          | dB                      |

| VOLTAGE           | REFERENCE INPUT                   | '                                                                                      |             |                           |          |                         |

|                   | Input current                     |                                                                                        |             | 10                        |          | nA                      |

| DIGITAL LO        | OGIC LEVELS                       |                                                                                        |             |                           |          |                         |

| V <sub>IH</sub>   | High-level input voltage          |                                                                                        | 0.7 DVDD    |                           |          | V                       |

| V <sub>IL</sub>   | Low-level input voltage           |                                                                                        |             |                           | 0.2 DVDD | V                       |

| V <sub>OH</sub>   | High-level output voltage         | I <sub>OH</sub> = 1mA                                                                  | DVDD - 0.4  |                           |          | V                       |

| V <sub>OL</sub>   | Low-level output voltage          | I <sub>OL</sub> = 1mA                                                                  |             |                           | 0.2 DVDD | V                       |

|                   | Input leakage current             | 0V < V <sub>IN</sub> < DVDD                                                            | -10         |                           | 10       | μA                      |

## 5.5 Electrical Characteristics (続き)

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +105°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD = DVDD =  $V_{(REFP)} = 5V$ ,  $V_{(REFN)} = AGND$ , and  $f_{CLK} = 4.9152MHz$  (unless otherwise noted)

|                     | PARAMETER                | TEST CONDITIONS                               | MIN TYP | MAX  | UNIT |

|---------------------|--------------------------|-----------------------------------------------|---------|------|------|

| POWER SU            | UPPLY                    |                                               |         | '    |      |

|                     |                          | Normal mode, AVDD = 3V, gain = 1, 2           | 600     | 1300 |      |

|                     |                          | Normal mode, AVDD = 3V, gain = 64, 128        | 1350    | 2500 |      |

| (AVDD)              | Analog supply current    | Normal mode, AVDD = 5V, gain = 1, 2           | 650     | 1300 |      |

| I <sub>(AVDD)</sub> | Analog supply current    | Normal mode, AVDD = 5V, gain = 64, 128        | 1350    | 2500 | μA   |

|                     |                          | Standby mode                                  | 0.1     | 1    |      |

|                     |                          | Power-down                                    | 0.1     | 1    |      |

|                     |                          | Normal mode, DVDD = 3V, gain = 1, 2           | 60      | 95   |      |

|                     |                          | Normal mode, DVDD = 3V, gain = 64, 128        | 75      | 120  | μΑ   |

|                     |                          | Normal mode, DVDD = 5V, gain = 1, 2           | 95      | 130  |      |

| $I_{(DVDD)}$        | Digital supply current   | Normal mode, DVDD = 5V, gain = 64, 128        | 75      | 120  |      |

|                     |                          | Standby mode, SCLK = high, DVDD = 3V          | 45      | 80   |      |

|                     |                          | Standby mode, SCLK = high, DVDD = 5V          | 65      | 80   |      |

|                     |                          | Power-down                                    | 0.2     | 1.3  |      |

|                     |                          | Normal mode, AVDD = DVDD = 3V, gain = 1, 2    | 2       | 4.2  |      |

|                     |                          | Normal mode, AVDD = DVDD = 5V, gain = 1, 2    | 3.7     | 7.2  |      |

| $P_D$               | Power dissipation, total | Normal mode, AVDD = DVDD = 3V, gain = 64, 128 | 4.3     | 7.9  | mW   |

|                     |                          | Normal mode, AVDD = DVDD = 5V, gain = 64, 128 | 7.1     | 13.1 |      |

|                     |                          | Standby mode, AVDD = DVDD = 5V                | 0.3     | 0.4  |      |

<sup>(1)</sup> FSR = full-scale range =  $V_{REF}$  / Gain.

<sup>(2)</sup> Input offset error specified after calibration. Recalibration minimizes these errors to the level of noise at any temperature.

Gain errors are calibrated at the factory (AVDD = 5V, all gains,  $T_A = 25$ °C).

<sup>(4)</sup> Specification is verified by the combination of design and final production test.

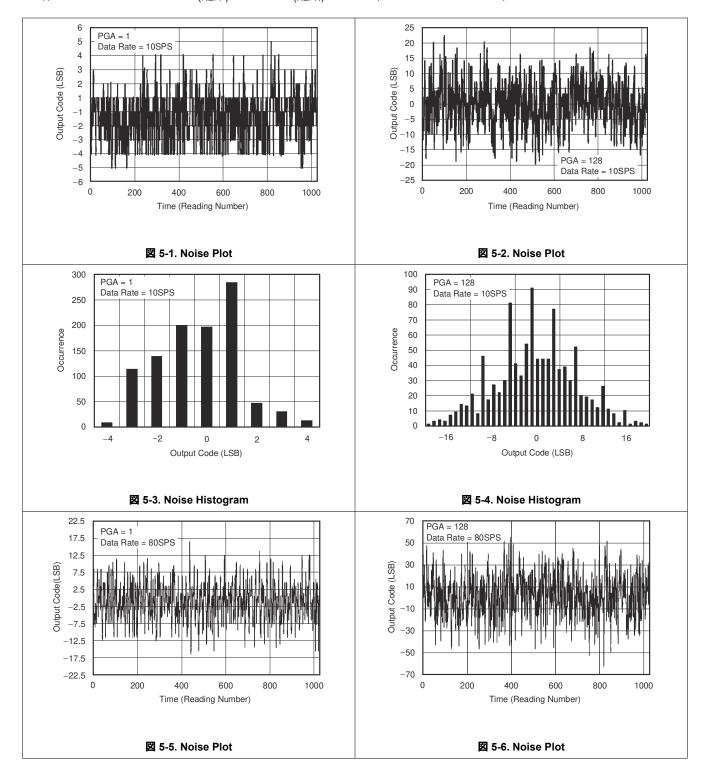

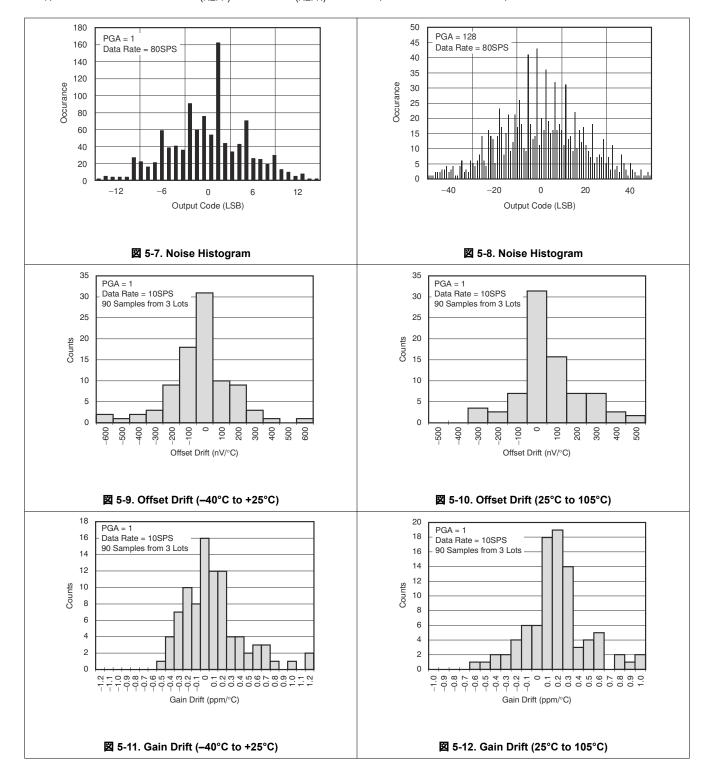

## **5.6 Typical Characteristics**

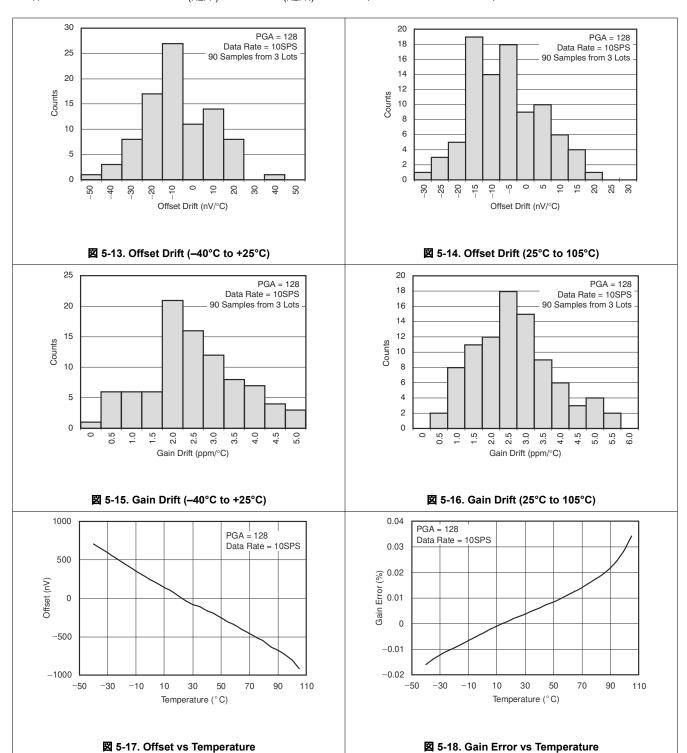

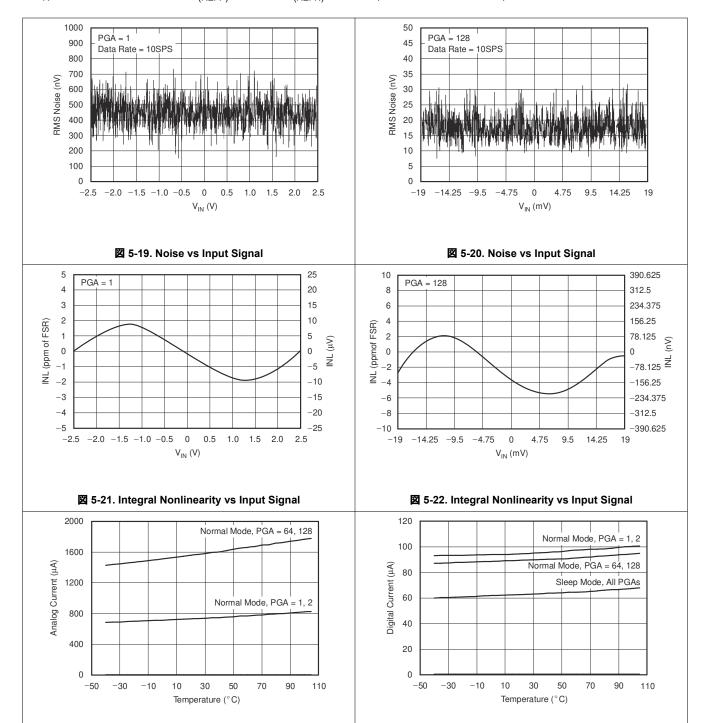

at  $T_A = 25$ °C, AVDD = DVDD =  $V_{(REFP)} = 5V$ , and  $V_{(REFN)} = AGND$  (unless otherwise noted)

図 5-23. Analog Supply Current vs Temperature

☑ 5-24. Digital Supply Current vs Temperature

### **6 Parameter Measurement Information**

#### **6.1 Noise Performance**

The ADS123x offer outstanding noise performance that can be optimized for a given full-scale range using the programmable gain amplifier (PGA). AVDD = 5V, V<sub>REF</sub> = 5V, Data Rate = 10SPS through AVDD = 3V, V<sub>REF</sub> = 3V, Data Rate = 80SPS summarize the typical noise performance with inputs shorted externally for different gains, data rates, and voltage reference values. The RMS and peak-to-peak noise data are referred to the input.

The effective resolution of the ADC is defined as:

The noise-free resolution of the ADC is defined as:

#### where

FSR = full-scale range = V<sub>REF</sub> / gain

表 6-1. AVDD = 5V, V<sub>RFF</sub> = 5V, Data Rate = 10SPS

| GAIN | RMS NOISE | PEAK-TO-PEAK NOISE <sup>(1)</sup> | EFFECTIVE<br>RESOLUTION (Bits) | NOISE-FREE<br>RESOLUTION (Bits) |

|------|-----------|-----------------------------------|--------------------------------|---------------------------------|

| 1    | 420nV     | 1.79µV                            | 23.5                           | 21.4                            |

| 2    | 270nV     | 900nV                             | 23.1                           | 21.4                            |

| 64   | 19nV      | 125nV                             | 22.0                           | 19.2                            |

| 128  | 17nV      | 110nV                             | 21.1                           | 18.4                            |

(1) Peak-to-peak noise data are based on direct measurement.

### 表 6-2. AVDD = 5V, V<sub>REF</sub> = 5V, Data Rate = 80SPS

| GAIN | RMS NOISE | PEAK-TO-PEAK NOISE <sup>(1)</sup> | EFFECTIVE<br>RESOLUTION (Bits) | NOISE-FREE<br>RESOLUTION (Bits) |

|------|-----------|-----------------------------------|--------------------------------|---------------------------------|

| 1    | 1.36µV    | 8.3µV                             | 21.8                           | 19.2                            |

| 2    | 850nV     | 5.5µV                             | 21.5                           | 18.8                            |

| 64   | 48nV      | 307nV                             | 20.6                           | 18                              |

| 128  | 44nV      | 247nV                             | 19.7                           | 17.2                            |

(1) Peak-to-peak noise data are based on direct measurement.

## 表 6-3. AVDD = 3V, $V_{REF}$ = 3V, Data Rate = 10SPS

| GAIN | RMS NOISE | PEAK-TO-PEAK NOISE(1) | EFFECTIVE<br>RESOLUTION (Bits) | NOISE-FREE<br>RESOLUTION (Bits) |

|------|-----------|-----------------------|--------------------------------|---------------------------------|

| 1    | 450nV     | 2.8µV                 | 22.6                           | 20                              |

| 2    | 325nV     | 1.8µV                 | 22.1                           | 19.7                            |

| 64   | 20nV      | 130nV                 | 21.2                           | 18.5                            |

| 128  | 18nV      | 115nV                 | 20.3                           | 17.6                            |

(1) Peak-to-peak noise data are based on direct measurement.

### 表 6-4. AVDD = 3V, V<sub>REF</sub> = 3V, Data Rate = 80SPS

| GAIN | RMS NOISE | PEAK-TO-PEAK NOISE <sup>(1)</sup> | EFFECTIVE<br>RESOLUTION (Bits) | NOISE-FREE<br>RESOLUTION (Bits) |

|------|-----------|-----------------------------------|--------------------------------|---------------------------------|

| 1    | 2.2µV     | 12µV                              | 20.4                           | 17.9                            |

| 2    | 1.2µV     | 6.8µV                             | 20.2                           | 17.8                            |

| 64   | 54nV      | 340nV                             | 19.7                           | 17.1                            |

| 128  | 48nV      | 254nV                             | 18.9                           | 16.5                            |

(1) Peak-to-peak noise data are based on direct measurement of 1024 samples.

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

## 7 Detailed Description

#### 7.1 Overview

The ADS1232 and ADS1234 (ADS123x) are highly integrated, 24-bit ADCs that include an input multiplexer, low-noise PGA, third-order delta-sigma ( $\Delta\Sigma$ ) modulator, and fourth-order digital filter. With input-referred RMS noise down to 17 nV, the ADS123x are ideally suited for measuring the very low signals produced by bridge sensors in applications such as weigh scales, strain gauges, and pressure sensors.

Clocking can be supplied by an external oscillator, an external crystal, or by a precision internal oscillator. Data can be output at 10 SPS for excellent 50-Hz and 60-Hz rejection, or at 80 SPS when higher speeds are needed. The ADS123x are easy to configure, and all digital control is accomplished through dedicated pins; there are no registers to program. A simple two-wire serial interface retrieves the data.

### 7.2 Functional Block Diagram

NOTE: (1) A1 for ADS1234, TEMP for ADS1232

### 7.3 Feature Description

#### 7.3.1 Analog Inputs (AINPX, AINNX)

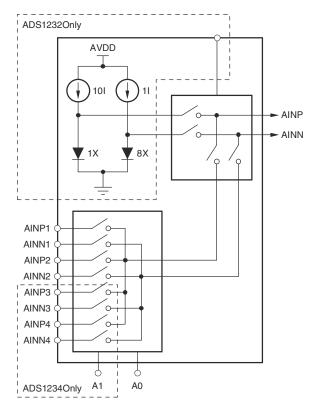

The input signal to be measured is applied to the input pins AINPx and AINNx. The positive internal input is generalized as AINP, and the negative internal input generalized as AINN. The signal is selected through the input MUX, which is controlled by pins A0 and TEMP (ADS1232) and pins A0 and A1 (ADS1234), as shown in 表 7-1 and 表 7-2.

The ADS123x accepts differential input signals, but can also accept single-ended signals. When measuring single-ended signals, it is permissible to connect the negative input (AINNx) to ground only for gain = 1 or 2. When using gain = 64 or 128, connect AINNx to a level-shift voltage equal to mid-AVDD supply to comply with the input range requirement. Connect the signal to the positive input (AINPx). When the ADS123x are configured this way, only half of the converter full-scale range is used because only positive digital output codes are produced.

The analog and reference inputs are protected by ESD diodes. See 🗵 7-3 for the similar connection of the ESD diodes for the analog inputs.

**SELECTED ANALOG INPUTS MUX PINS TEMP** Α0 **POSITIVE INPUT NEGATIVE INPUT** 0 0 AINP1 AINN1 0 1 AINP2 AINN2 1 Temperature sensor Temperature sensor х

表 7-1. ADS1232 Input Channel Selection With A0 and TEMP

| MUX PINS |    | SELECTED ANALOG INPUTS |                |  |

|----------|----|------------------------|----------------|--|

| A1       | A0 | POSITIVE INPUT         | NEGATIVE INPUT |  |

| 0        | 0  | AINP1                  | AINN1          |  |

| 0        | 1  | AINP2                  | AINN2          |  |

| 1        | 0  | AINP3                  | AINN3          |  |

| 1        | 1  | AINP4                  | AINN4          |  |

### 7.3.2 Temperature Sensor (ADS1232 Only)

On-chip diodes provide temperature-sensing capability. By setting the TEMP pin high, the selected analog inputs are disconnected and the inputs to the ADC are connected to the anodes of two diodes scaled to 1x and 80x in current and size, as shown in  $\boxtimes$  7-1. By measuring the difference in voltage of these diodes, temperature changes can be inferred from a baseline temperature. Typically, the difference in diode voltage is 111.7 mV at 25°C with a temperature coefficient of 379  $\mu$ V/°C. With PGA gain = 1 and 2, the difference voltage output from the PGA is 111.7 mV and 223.4 mV, respectively. The temperature sensor function is impossible to use with PGA gain = 64 and 128.

☑ 7-1. Measurement of the Temperature Sensor in the Input Multiplexer

#### 7.3.3 Low-Noise PGA

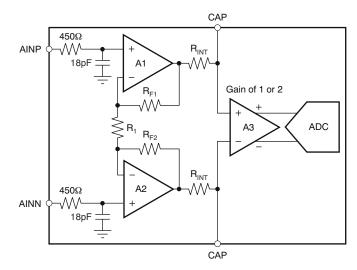

The ADS123x feature a low-drift, low-noise PGA that provides a complete front-end solution for bridge sensors. A simplified diagram of the PGA is shown in  $\boxtimes$  7-2. The PGA consists of two chopper-stabilized amplifiers (A1 and A2) and three accurately matched resistors (R<sub>1</sub>, R<sub>F1</sub>, and R<sub>F2</sub>), which construct a differential front-end stage with a gain of 64, followed by gain stage A3. The PGA inputs are equipped with an EMI filter, as shown in  $\boxtimes$  7-2. The cut-off frequency of the EMI filter is 19.6 MHz. If the PGA gain is set to 1 or 2, the gain-of-64 stage is bypassed and shut down to save power. With the combination of both gain stages, the PGA gain can be set to 64 or 128. The PGA gain of the ADS123x is set to 1, 2, 64, or 128 by pins GAIN1 (MSB) and GAIN0 (LSB).  $\bigstar$  7-3 shows the gain setting of the PGA.

表 7-3. PGA Gain

| GAIN[1:0] INPUT PINS | PGA GAIN |

|----------------------|----------|

| 00                   | 1        |

| 01                   | 2        |

| 10                   | 64       |

| 11                   | 128      |

By using AVDD as the reference input, the bipolar input ranges from  $\pm 2.5$  V to  $\pm 19.5$  mV, while the unipolar ranges from 2.5 V to 19.5 mV. When the PGA gain is set to 1 or 2, the absolute inputs can go rail-to-rail without significant performance degradation. However, the inputs of the ADS123x are protected with internal diodes connected to the power-supply rails. These diodes clamp the applied signal to prevent damage to the input circuitry. On the other hand, when the PGA gain is set to 64 or 128, the operating input range is limited to (AGND + 1.5 V) to (AVDD - 1.5 V), in order to prevent saturating the differential front-end circuitry and degrading performance.

図 7-2. Simplified Diagram of the PGA

#### 7.3.3.1 PGA Bypass Capacitor

By applying a  $0.1\mu F$  external capacitor ( $C_{EXT}$ ) across two PGA output pins (pins 9 and 10 and the combination of the internal  $2k\Omega$  resistor ( $R_{INT}$ ), a low-pass filter with a corner frequency of 720Hz is created to band limit the signal path prior to the modulator input. This low-pass filter serves two purposes. First, the input signal is band-limited to prevent aliasing, as well as to filter high-frequency noise. Second, the low-pass filter attenuates the chopping residue from the PGA (for gains of 64 and 128 only) to improve temperature drift performance. High-quality capacitors (such as high-k ceramic or tantalum capacitors) are not required for a general application. However, high-quality capacitors, such as C0G dielectric ceramic or poly, are recommended for high-linearity applications.

資料に関するフィードバック (ご意見やお問い合わせ) を送信 Copyright

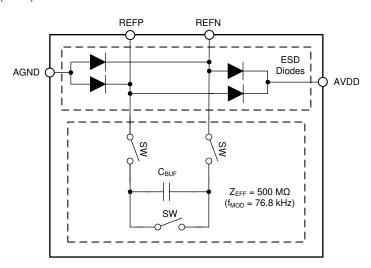

#### 7.3.4 Voltage Reference Inputs (REFP, REFN)

The voltage reference used by the modulator is generated from the voltage difference between pins REFP and REFN:  $V_{REF} = V_{(REFN)} - V_{(REFN)}$ . The reference inputs use a structure similar to that of the analog inputs. In order to increase the reference input impedance, a switching buffer circuitry is used to reduce the input equivalent capacitance. The reference drift and noise impact ADC performance. In order to achieve best results, pay close attention to the reference noise and drift specifications. A simplified diagram of the circuitry on the reference inputs is shown in  $\boxtimes$  7-3. The switches and capacitors can be modeled with an effective impedance of:

$$Z_{EFF} = \frac{1}{2f_{MOD}C_{BUF}}$$

#### where

- f<sub>MOD</sub> = modulator sampling frequency = f<sub>CLK</sub> / 64 = (76.8 kHz)

- C<sub>BUF</sub> = input capacitance of the buffer

For the ADS123x:

$$Z_{EFF} = \frac{1}{(2)(76.8kHz)(13fF)} = 500M\Omega$$

☑ 7-3. Simplified Reference Input Circuitry

ESD diodes protect the reference inputs. To prevent these diodes from turning on, make sure the voltages on the reference pins do not go below AGND by more than 100 mV; and likewise, do not exceed AVDD by 100 mV:

AGND – 100 mV

$$<$$

V<sub>(REFP)</sub> or V<sub>(REFN)</sub>  $<$  AVDD + 100 mV

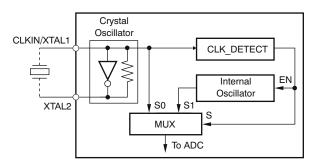

#### 7.3.5 Clock Sources

The ADS123x can use an external clock source, external crystal, or internal oscillator to accommodate a wide variety of applications. Z 7-4 shows the equivalent circuitry of the clock source. The CLK\_DETECT block determines whether a crystal oscillator or external clock signal is applied to the CLKIN/XTAL1 pin so that the internal oscillator is bypassed or activated. When the CLKIN/XTAL1 pin frequency is above approximately 200 kHz, the CLK\_DETECT output goes low and shuts down the internal oscillator. When the CLKIN/XTAL1 pin frequency is below approximately 200 kHz, the CLK\_DETECT output goes high and activates the internal oscillator. Connect the CLKIN/XTAL1 pin to ground when the internal oscillator is chosen.

図 7-4. Equivalent Circuitry of the Clock Source

For crystal operation, connect the 4.9152-MHz crystal across the CLKIN/XTAL1 and XTAL2 pins. 表 7-4 shows the recommended crystal part numbers. As a result of the low-power design of the internal parallel-resonant circuit, both the CLKIN/XTAL1 and XTAL2 pins are only for use with the external crystal; do not use these pins as clock output drivers for external circuitry. No external capacitors are used with the crystal. Place the crystal as close as possible to the device pins in order to reduce board stray capacitance and in order to help ensure proper crystal operation.

表 7-4. Recommended Crystals

| MANUFACTURER | FREQUENCY  | PART NUMBER |

|--------------|------------|-------------|

| ECS          | 4.9152 MHz | ECS-49-20-1 |

| ECS          | 4.9152 MHz | ECS-49-20-4 |

An external clock oscillator can be used by driving the CLKIN/XTAL1 pin from the oscillator output and leave XTAL2 disconnected.

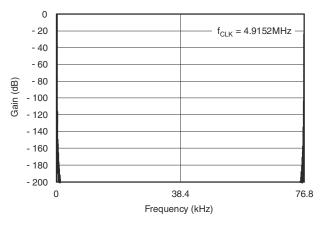

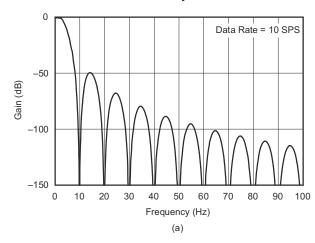

#### 7.3.6 Digital Filter Frequency Response

The ADS123x use a  $sinc^4$  digital filter with the frequency response ( $f_{CLK}$  = 4.9152 MHz) shown in  $\boxtimes$  7-5. The frequency response repeats at multiples of the modulator sampling frequency of 76.8 kHz. The overall response is that of a low-pass filter with a -3-dB cutoff frequency of 2.4 Hz with the SPEED pin tied low (10-SPS data rate) and 19 Hz with the SPEED pin tied high (80-SPS data rate).

図 7-5. Digital Filter Frequency Response

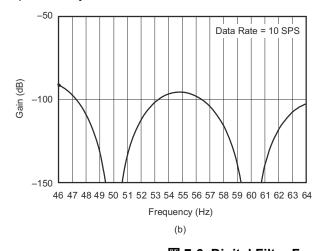

To better demonstrate the response at lower frequencies,  $\boxtimes$  7-6(a) illustrates the response out to 100 Hz, when the data rate = 10 SPS. Notice that signals at multiples of 10 Hz are rejected, and therefore, simultaneous rejection of 50 Hz and 60 Hz interference is achieved.

The benefit of using a sinc<sup>4</sup> filter is that every frequency notch has four zeros at the same location. This response, combined with the low-drift internal oscillator, provides an excellent normal-mode rejection of line-cycle interference.

☑ 7-6(b) shows the plot enlarged for both 50-Hz and 60-Hz notches with the SPEED pin tied low (10-SPS data rate). With only a ±3% variation of the internal oscillator, over 100 dB of normal-mode rejection is achieved.

図 7-6. Digital Filter Frequency Response to 100 Hz

The ADS123x data rate and frequency response scale directly with clock frequency. For example, if  $f_{CLK}$  increases from 4.9152 MHz to 6.144 MHz when the SPEED pin is tied high, the data rate increases from 80 SPS to 100 SPS, while filter notches also increase from 80 Hz to 100 Hz. Frequency scaling is only possible when the external clock source is applied.

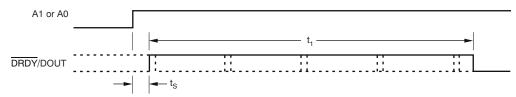

#### 7.3.7 Settling Time

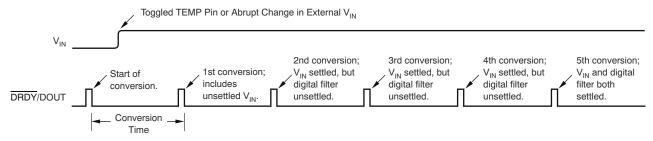

After changing the input multiplexer, the first data are fully settled. In both ADS123x devices, the digital filter is allowed to settle after toggling either the A1 or A0 pin. Toggling any of these digital pins holds the  $\overline{DRDY}/DOUT$  line high until the digital filter is fully settled. For example, if A0 changes from low to high, selecting a different input channel,  $\overline{DRDY}/DOUT$  immediately goes high, and  $\overline{DRDY}/DOUT$  goes low when fully settled data are ready for retrieval. There is no need to discard any data.  $\overline{\boxtimes}$  7-7 shows the timing of the  $\overline{DRDY}/DOUT$  line as the input multiplexer changes.

In certain instances, large or abrupt input changes require four data cycles to settle. One example of such a change is an external multiplexer in front of the ADS123x, which can cause large changes in input voltage simply by switching input channels. Another example is toggling the TEMP pin, which switches the internal AINP, AINN signals to connect to either the external AINPx, AINNx pins or to the TEMP diode (see  $\boxtimes$  7-1).

To acquire fully settled data after an input step change, five readings are required. Five readings are required because if the change in input occurs in the middle of the first conversion, four additional full conversions of the fully settled input are required to get fully settled data. Discard the first four readings because they contain only partially settled data. 27-8 illustrates the settling time for the ADS123x in continuous conversion mode.

図 7-7. Example of Settling Time After Changing the Input Multiplexer

表 7-5. Timing Requirements for 図 7-7

| PARAMETER <sup>(1)</sup> |                                           |           | MIN | MAX | UNIT |

|--------------------------|-------------------------------------------|-----------|-----|-----|------|

| t <sub>S</sub>           | Setup time for changing the A1 or A0 pins |           | 40  | 50  | μs   |

|                          | Settling time (DRDY/DOUT                  | SPEED = 1 | 51  | 51  | ms   |

|                          | held high)                                | SPEED = 0 | 401 | 401 | ms   |

(1) Values given for f<sub>CLK</sub> = 4.9152 MHz. For different f<sub>CLK</sub> frequencies, scale proportional to CLK period. Expect a ±3% variation when an internal oscillator is used.

図 7-8. Settling Time in Continuous Conversion Mode

#### 7.3.8 Data Rate

The ADS123x data rate is set by the SPEED pin, as shown in 表 7-6. When SPEED is low, the data rate is nominally 10 SPS. This data rate provides the lowest noise, and also has excellent rejection of both 50-Hz and 60-Hz line-cycle interference. For applications requiring fast data rates, setting SPEED high selects a data rate of 80 SPS.

表 7-6. Data Rate Settings

|              | DATA RATE                                    |                            |  |  |  |

|--------------|----------------------------------------------|----------------------------|--|--|--|

| SPEED<br>PIN | INTERNAL OSCILLATOR<br>OR 4.9152-MHz CRYSTAL | EXTERNAL<br>OSCILLATOR     |  |  |  |

| 0            | 10 SPS                                       | f <sub>CLK</sub> / 491,520 |  |  |  |

| 1            | 80 SPS                                       | f <sub>CLK</sub> / 61,440  |  |  |  |

#### 7.3.9 Data Format

The ADS123x output 24 bits of data in binary two's complement format. The least significant bit (LSB) has a weight of  $0.5 \, V_{REF} / (2^{23} - 1)$ . The positive full-scale input produces an output code of 7FFFFh and the negative full-scale input produces an output code of 800000h. The output clips at these codes for signals exceeding full-scale. 表 7-7 summarizes the ideal output codes for different input signals.

表 7-7. Ideal Output Code Versus Input Signal (1)

| INPUT SIGNAL V <sub>IN</sub> (AINP – AINN)             | IDEAL OUTPUT CODE |

|--------------------------------------------------------|-------------------|

| ≥ 0.5 V <sub>REF</sub> / Gain                          | 7FFFFh            |

| (0.5 V <sub>REF</sub> / Gain) / (2 <sup>23</sup> – 1)  | 000001h           |

| 0                                                      | 000000h           |

| (-0.5 V <sub>REF</sub> / Gain) / (2 <sup>23</sup> - 1) | FFFFFFh           |

| ≤ –0.5 V <sub>REF</sub> / Gain                         | 800000h           |

<sup>(1)</sup> Excludes effects of noise, INL, offset, and gain errors.

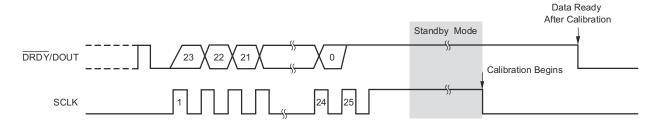

#### 7.3.10 Data Ready and Data Output (DRDY/DOUT)

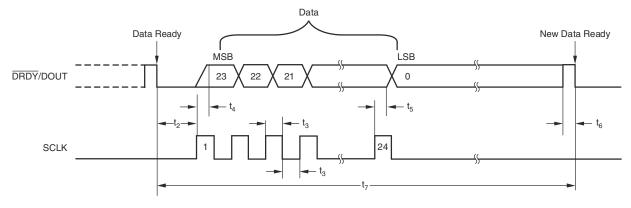

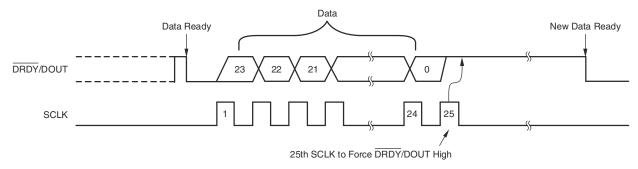

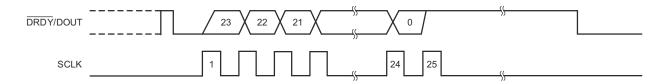

This digital output pin serves two purposes. First, DRDY/DOUT indicates when new data are ready by going low. Afterwards, on the first rising edge of SCLK, the DRDY/DOUT pin changes function and begins outputting the conversion data, most significant bit (MSB) first. Data are shifted out on each subsequent SCLK rising edge. After all 24 bits have been retrieved, the pin can be forced high with an additional SCLK. DRDY/DOUT then remains high until new data are ready. This configuration is useful when polling on the status of DRDY/DOUT to determine when to begin data retrieval.

#### 7.3.11 Serial Clock Input (SCLK)

This digital input shifts serial data out with each rising edge. This input has built-in hysteresis, but care must be taken to ensure a clean signal. Glitches or slow-rising signals can cause unwanted additional shifting. For this reason, make sure the rise-and-fall times of SCLK are less than 50 ns.

23

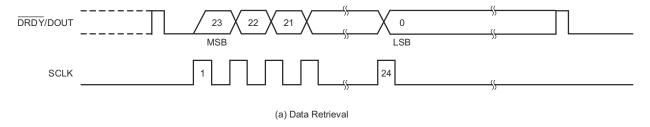

#### 7.3.12 Data Retrieval

The ADS123x continuously converts the analog input signal. To retrieve data, wait until  $\overline{DRDY}/DOUT$  goes low, as shown in  $\overline{\boxtimes}$  7-9. After  $\overline{DRDY}/DOUT$  goes low, begin shifting out the data by applying SCLKs. Data are shifted out MSB first. Not all 24 bits of data are required to be shifted out, but the data must be retrieved before new data are updated (within  $t_7$ ) or else the data are overwritten. Avoid data retrieval during the update period ( $t_6$ ).  $\overline{DRDY}/DOUT$  remains at the state of the last bit shifted out until taken high (see  $t_6$ ), indicating that new data are being updated. To avoid having  $\overline{DRDY}/DOUT$  remain in the state of the last bit, the user can shift SCLK to force  $\overline{DRDY}/DOUT$  high, as shown in  $\overline{\boxtimes}$  7-10. This technique is useful when a host controlling the device is polling  $\overline{DRDY}/DOUT$  to determine when data are ready.

図 7-9. Data Retrieval Timing

表 7-8. Timing Requirements for 図 7-9

|                    | PARAMETER                                                 |           |     | TYP  | MAX | UNIT |

|--------------------|-----------------------------------------------------------|-----------|-----|------|-----|------|

| t <sub>2</sub>     | DRDY/DOUT low to first SCLK rising edge                   |           | 0   |      |     | ns   |

| t <sub>3</sub>     | SCLK positive or negative pulse width                     |           | 100 |      |     | ns   |

| t <sub>4</sub>     | SCLK rising edge to new data bit valid: propagation delay |           |     |      | 50  | ns   |

| t <sub>5</sub>     | SCLK rising edge to old data bit valid: hold time         |           | 0   |      |     | ns   |

| t <sub>6</sub> (1) | Data updating: no readback allowed                        |           | 39  |      |     | μs   |

| t <sub>7</sub> (1) |                                                           | SPEED = 1 |     | 12.5 |     | ms   |

| 17 17              | Conversion time (1/data rate)  SPEED = 0                  |           |     | 100  |     | 1115 |

(1) Values given for f<sub>CLK</sub> = 4.9152 MHz. For different f<sub>CLK</sub> frequencies, scale proportional to the CLK period.

図 7-10. Data Retrieval With DRDY/DOUT Forced High Afterwards

#### 7.4 Device Functional Modes

In addition to the active conversion mode, the device has other functional modes: offset calibration mode (to calibrate the ADC internal offset), standby mode (saving power when not converting), and a power-down mode (for complete device shutdown).

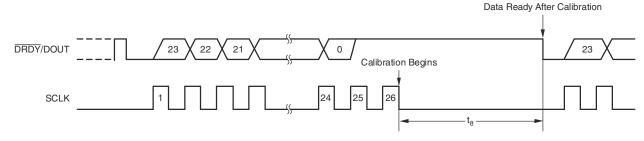

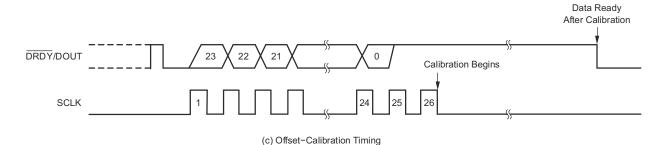

#### 7.4.1 Offset Calibration Mode

Offset calibration can be initiated at any time to remove the ADS123x offset error. To initiate offset calibration, apply at least two additional SCLKs after retrieving 24 bits of data. Z 7-11 shows the timing pattern. The 25th SCLK sends DRDY/DOUT high. The falling edge of the 26th SCLK begins the calibration cycle. Additional SCLK pulses can be sent after the 26th SCLK; however, minimize activity on SCLK during offset calibration for best results. The analog input pins are disconnected within the ADC and the appropriate signal is applied internally to perform the calibration.

When the calibration is completed, DRDY/DOUT goes low, indicating that new data are ready. The first conversion after a calibration is fully settled and valid for use. The offset calibration takes exactly the same time as specified in (t<sub>8</sub>) right after the falling edge of the 26th SCLK.

図 7-11. Offset-Calibration Timing

表 7-9. Timing Requirements for 図 7-11

| PARAMETER                                                        |                                     |                    | MIN    | MAX    | UNIT |

|------------------------------------------------------------------|-------------------------------------|--------------------|--------|--------|------|

| t <sub>8</sub> <sup>(1)</sup> First data ready after calibration |                                     | SPEED = 1 (80 SPS) | 101.28 | 101.29 | ms   |

| t <sub>8</sub> (1)                                               | I list data ready after calibration | SPEED = 0 (10 SPS) | 801.02 | 801.03 |      |

<sup>(1)</sup> Values given for f<sub>CLK</sub> = 4.9152 MHz. For different f<sub>CLK</sub> frequencies, scale proportional to the CLK period. Expect a ±3% variation when the internal oscillator is used.

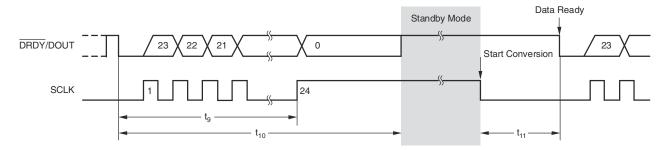

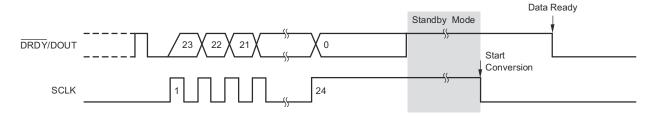

### 7.4.2 Standby Mode

Standby mode dramatically reduces power consumption by shutting down most of the circuitry. In standby mode, the entire analog circuitry is powered down and only the clock source circuitry is awake to reduce the wake-up time from the standby mode. To enter standby mode, simply hold SCLK high after DRDY/DOUT goes low; see Z 7-12. Standby mode can be initiated at any time during readback; all 24 bits of data are not required to be retrieved beforehand.

When  $t_{10}$  has passed with SCLK held high, standby mode activates.  $\overline{DRDY}/DOUT$  stays high when standby mode begins. SCLK must remain high to stay in standby mode. To exit standby mode (wakeup), set SCLK low. The first data after exiting standby mode is valid.

図 7-12. Standby Mode Timing (Can be Used for Single Conversions)

表 7-10. Timing Requirements for 図 7-12

|                                | PARAMETER                             |           |       | MAX   | UNIT |

|--------------------------------|---------------------------------------|-----------|-------|-------|------|

| t <sub>9</sub> (1)             | SCLK high after DRDY/DOUT goes        | SPEED = 1 | 0     | 12.44 | ms   |

| 19 1                           | low to activate standby mode          | SPEED = 0 | 0     | 99.94 |      |

| t <sub>10</sub> <sup>(1)</sup> | Standby mode activation time          | SPEED = 1 | 12.46 |       | ms   |

|                                |                                       | SPEED = 0 | 99.96 |       |      |

| t <sub>11</sub> <sup>(1)</sup> | Data ready after exiting standby mode | SPEED = 1 | 52.51 | 52.51 | ms   |

| 411 17                         | Data ready after exiting standby mode | SPEED = 0 | 401.8 | 401.8 |      |

<sup>(1)</sup> Values given for f<sub>CLK</sub> = 4.9152 MHz. For different f<sub>CLK</sub> frequencies, scale proportional to the CLK period. Expect a ±3% variation when an internal oscillator is used.

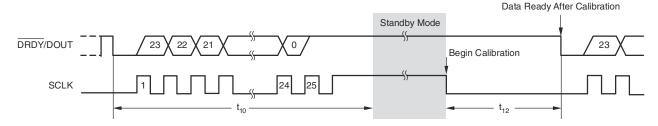

#### 7.4.3 Standby Mode With Offset-Calibration

Offset-calibration can be set to run immediately after exiting standby mode. This feature is useful when the ADS123x is put in standby mode for long periods of time, and offset-calibration is desired afterwards to compensate for temperature or supply voltage changes.

To force an offset-calibration with standby mode, shift 25 SCLKs and take the SCLK pin high to enter standby mode. Offset-calibration then begins after wake-up;  $\boxtimes$  7-13 shows the appropriate timing. Note the extra time needed after wake-up for calibration before data are ready. The first data after standby mode with offset-calibration is fully settled and can be used right away.

図 7-13. Standby Mode With Offset-Calibration Timing (Can be Used for Single Conversions)

表 7-11. Timing Requirements for 🗵 7-13

|                                | PARAMETER                             | MIN       | MAX | UNIT |    |

|--------------------------------|---------------------------------------|-----------|-----|------|----|

| t <sub>12</sub> <sup>(1)</sup> | Data ready after exiting standby mode | SPEED = 1 | 103 | 103  | ms |

| 12 '                           | and calibration                       | SPEED = 0 | 803 | 803  |    |

(1) Values given for f<sub>CLK</sub> = 4.9152 MHz. For different f<sub>CLK</sub> frequencies, scale proportional to CLK period. Expect a ±3% variation when an internal oscillator is used.

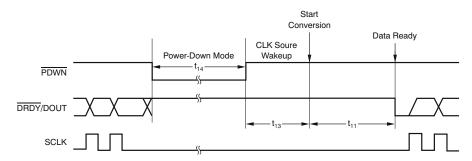

#### 7.4.4 Power-Down Mode

Power-down mode shuts down the entire ADC circuitry and reduces the total power consumption close to zero. To enter power-down mode, hold the  $\overline{\text{PDWN}}$  pin low. Power-down mode also resets the entire circuitry to free the ADC circuitry from locking up to an unknown state. Power-down mode can be initiated at any time during readback; not all 24 bits of data must be retrieved beforehand.  $\boxtimes$  7-14 shows the wake-up timing from power-down mode.

図 7-14. Wake-Up Timing From Power-Down Mode

表 7-12. Timing Requirements for 図 7-14

|                     |                     | <u> </u>                          |         |      |

|---------------------|---------------------|-----------------------------------|---------|------|

|                     | PARAMET             | ER                                | MIN TYP | UNIT |

|                     |                     | Internal clock                    | 7.95    | μs   |

| t <sub>13</sub>     | ' '                 | External clock                    | 0.16    | μs   |

|                     |                     | Crystal oscillator <sup>(1)</sup> | 5.6     | ms   |

| t <sub>14</sub> (2) | PDWN pulse duration |                                   | 26      | μs   |

- (1) No capacitors on CLKIN/XTAL1 or XTAL2 outputs.

- (2) Value given for f<sub>CLK</sub> = 4.9152 MHz. For different f<sub>CLK</sub> frequencies, the scale is proportional to the CLK period except for a ±3% variation when an internal oscillator is used.

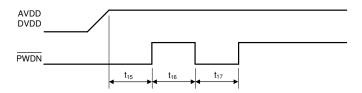

#### 7.4.5 Power-Up Sequence

When powering up the ADS123x, follow the prescribed  $\overline{PWDN}$  pin sequence as shown in  $\boxtimes$  7-15. At power-up, hold the  $\overline{PWDN}$  pin low until after AVDD and DVDD have stabilized above the minimum specified voltage levels. After an initial delay where  $\overline{PWDN}$  must be held low ( $t_{15}$ ), take  $\overline{PWDN}$  high then toggle  $\overline{PWDN}$  low to high with pulse durations ( $t_{16}$  and  $t_{17}$ ) as shown in  $\boxtimes$  7-15 and 7-13. The ADC then begins operation as shown in  $\boxtimes$  7-14 and 8 7-12. Control  $\overline{PDWN}$  by the host processor to provide the required power-on timing.

図 7-15. Power-Up Timing Sequence

表 7-13. Power-up Timing Requirements for 図 7-15

|                 | PARAMETER                                     |    |    |  |  |  |

|-----------------|-----------------------------------------------|----|----|--|--|--|

| t <sub>15</sub> | Delay time, PWDN high after AVDD, DVDD stable | 10 | μs |  |  |  |

| t <sub>16</sub> | Pulse duration, PWDN high                     | 26 | μs |  |  |  |

| t <sub>17</sub> | Pulse duration, PWDN low                      | 26 | μs |  |  |  |

(1)  $f_{CLK} = 4.9152$  MHz. For  $f_{CLK} < 4.9152$  MHz, adjust the  $\overline{PWDN}$  delay time and pulse duration accordingly.

### 7.4.6 Summary of Serial Interface Waveforms

## ▼ 7-16 summarizes the serial interface waveforms.

(b) Data Retrieval with DRDY/DOUT Forced High Afterwards

(d) Standby Mode/Single Conversions

(e) Standby Mode/Single Conversions with Offset Calibration

図 7-16. Summary of Serial Interface Waveforms

## 8 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 Application Information

The ADS123x devices are high-resolution, 24-bit ADCs with an integrated low-noise PGA. Best performance is achieved by following the guidelines and recommendations described in the *Typical Application* section.

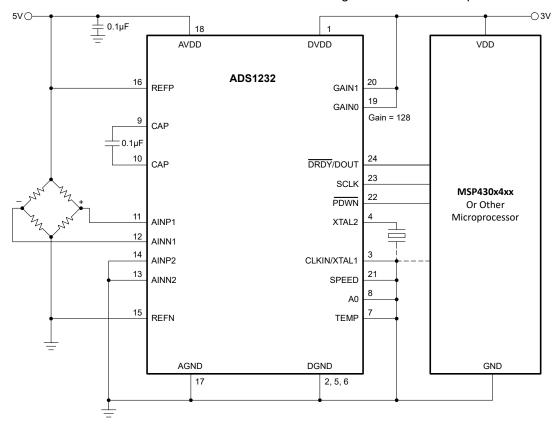

### 8.2 Typical Application

⊠ 8-1 shows a circuit diagram of the ADS1232 as part of a weigh scale system. In this setup, the ADS1232 is configured to channel 1 input, gain = 128, and 10SPS data rate. Gain = 128 is selected by tying the GAIN[1:0] pins to logic high (3V in this example). Input channel 1 and data rate = 10SPS are selected by tying input channel select pins A0 and TEMP to ground, and by tying the data rate select pin SPEED to ground. The unused channel 2 inputs are tied to ground.

The internal oscillator is selected by grounding the CLKIN/XTAL1 pin. The other clock options are 1) 4.9152MHz crystal across the CLKIN/XTAL1 and XTAL2 pins, or 2) apply a clock to the CLKIN/XTAL1 pin (pin XTAL2 unconnected). The PWDN pin of the ADC is routed to the controller because this pin must be toggled after the ADC is powered. The bridge excitation voltage is connected to the ADC reference input pins (REFP, REFN). Not shown in  $\boxtimes$  8-1 are R-C input filters for the signal and reference inputs. If these filters are used, match the filter time constants to maintain cancellation of noise common to both signal and reference inputs.

図 8-1. Weigh-Scale Application

#### 8.2.1 Design Requirements

表 8-1 summarizes the design performance goals. 表 8-2 summarizes the system design parameters.

#### 表 8-1. Design Goals

| <u>-                               </u> |                                                 |  |  |  |  |  |  |  |

|-----------------------------------------|-------------------------------------------------|--|--|--|--|--|--|--|

| DESIGN GOAL                             | VALUE                                           |  |  |  |  |  |  |  |

| Noise-free resolution                   | 80,000 counts / 130,000 counts (post averaging) |  |  |  |  |  |  |  |

| Sample rate                             | 10 SPS                                          |  |  |  |  |  |  |  |

| Input step settling time                | 500 ms / 900 ms (post averaging)                |  |  |  |  |  |  |  |

| 50-Hz and 60-Hz noise rejection         | >100 dB                                         |  |  |  |  |  |  |  |

表 8-2. Design Parameters

| DESIGN PARAMETERS                            | DESIGN VALUE |

|----------------------------------------------|--------------|

| Bridge resistance                            | 1 kΩ         |

| Bridge excitation voltage                    | 5 V          |

| Load cell sensitivity                        | 2 mV/V       |

| Bridge full-scale output                     | 10 mV        |

| ADC analog power supply                      | 5 V          |

| Host controller and ADC digital power supply | 3 V          |

### 8.2.2 Detailed Design Procedure

Common performance metrics of a weigh scale are noise-free resolution (or counts) and offset and gain stability (drift) after calibrating the weigh scale. 表 6-1 to 表 6-4 illustrate ADC noise performance expressed as an input-referred quantity over gain, data rate, and analog supply voltage.

In this design example, the ADC analog supply voltage (5 V) is used as the bridge excitation voltage. 5-V excitation optimizes the bridge signal output compared to 3-V excitation and also has the benefit of optimizing the ADC conversion noise. Gain = 128 is selected because it also provides optimal noise performance. The front end circuitry of the ADC easily accommodates the 10-mV bridge output. In summary, the ADC configuration that yields the highest resolution while achieving the sample rate and settling time requirements is AVDD = 5 V, bridge excitation = 5 V, gain = 128, and sample rate = 10 SPS.

Signal-to-noise performance is improved by using a higher gauge-factor bridge (example 3 mV/V bridge), or by increasing the excitation voltage. If the excitation voltage > 5 V, a voltage divider is required to reduce the voltage at the ADC reference inputs.

Noise-free counts are improved by post averaging the data (for example, a moving-average filter performed in the microcontroller). A moving average filter reduces noise by a factor of  $\sqrt{N}$ , where N is the number of readings averaged. However, a moving average filter increases the input step settling time due to the latency caused by averaging.

The other key performance attributes are DC offset and gain drift, and 50-Hz and 60-Hz noise rejection. Solution 5-14 and 5-16 illustrate the distributions of offset and gain drift performance. 50-Hz and 60-Hz noise rejection is described in 7-6. The ADC provides over 100-dB rejection with ±3% variation of the ADC clock frequency.

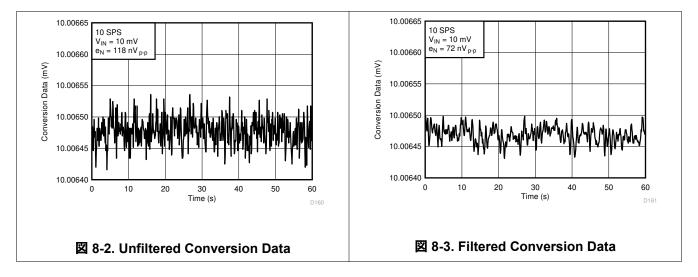

#### 8.2.3 Application Curves

To evaluate the ADC's noise performance, four fixed-value,  $1-k\Omega$  low-drift precision resistors are connected in a bridge arrangement to simulate a bridge sensor. The simulator provides the same thermal noise generated by a physical bridge. One of the four bridge resistors is modified to  $1.008~k\Omega$  in order to provide a 10-mV output signal. The 10-mV signal is typical of a 2-mV/V load cell using 5-V excitation.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

As shown in the noise plots, the moving average filter reduces noise by approximately one-half. As a consequence of the post filter operation, the input step settling time increases from 500 ms to 900 ms (500 ms because of the ADC settling response time, 400 ms because of the post-averaging filter).

### 8.3 Power Supply Recommendations

At device power-on, follow the PWDN pin toggle sequence as detailed in the Power-Up Sequence section.

The ADC has an analog power supply (AVDD) and digital power supply (DVDD). The supply range is 2.7V to 5.25V. The analog and digital supplies can be tied together, however the digital power supply must be clean and free of glitches and transients, which can be generated by the operation of LEDs, relays, and so forth. The bridge excitation voltage is often the same as the ADC supply voltage, so the supply voltage must be free of transients.

Voltage ripple produced by switching power supplies can also degrade ADC performance. The use a low-dropout regulator (LDOs) can reduce voltage ripple caused by switching power supplies.

### 8.3.1 Power-Supply Decoupling

Good power-supply decoupling is important in order to achieve rated performance. The power supplies must be decoupled close to the power-supply pins using short, direct connections to ground. For both analog and digital power supplies, connect a 0.1-µF capacitor (X7R-dielectric ceramic) from the power-supply pins to the ground plane.

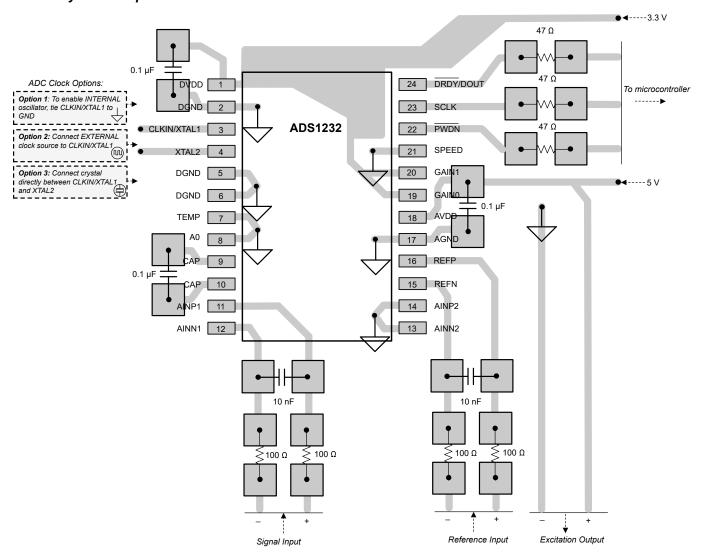

#### 8.4 Layout

Good layout practices are crucial to realize the full-performance of the ADC. Poor grounding can quickly degrade the noise performance. The following layout guidelines help provide the best results.

#### 8.4.1 Layout Guidelines

For best performance, dedicate a PCB layer to a ground plane and do not route any other signal traces on this layer. However, depending on space limitations, a dedicated ground plane may not be practical. If a continuous ground plane is not possible, connect the individual plane segments in one place at the ADC.

Route digital traces away from the PGA output pins (CAP) and away from all analog inputs and associated components to minimize interference. Maintain differential trace routing for the input signal and reference signal to minimize RFI susceptibility.

Use C0G capacitors for analog and reference input filters and the PGA output capacitors in high-linearity applications. High-K type capacitors (such as Y5V and X7R) should be avoided. Place supply bypass and the PGA bypass capacitors as close as possible to the device pins using short, direct traces. For optimum performance, use low-impedance connections (such as multiple vias) on the ground-side connections of the bypass capacitors.

Avoid long traces on DRDY/DOUT, because high trace capacitance can lead to increased ADC noise. Use a series resistor or a local buffer if long traces are used. When applying an external clock, be sure the clock is free of overshoot and glitches. A source-termination resistor placed at the clock buffer helps control reflections and overshoot. Glitches present on the clock signal can lead to increased noise and possible mis-operation and must be avoided.

図 8-4 illustrates a PCB layout example. Separate 5V analog and a 3.3V digital supplies are shown. The ADC configuration is through hard-tie of the control pins as shown in 表 8-3.

MODE

PIN CONTROL

VOLTAGE

Data rate = 10 SPS

SPEED

0V

Gain = 128

GAIN[1:0]

3.3V

表 8-3. Layout Example Pin Connections

A0, TEMP

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Input = channel 1

Copyright © 2025 Texas Instruments Incorporated

0V

### 8.4.2 Layout Example

図 8-4. ADS1232 Layout Example

## 9 Device and Documentation Support

## 9.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.3 Trademarks

テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

### 9.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.5 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

### 10 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision G (January 2021) to Revision H (June 2025)                                                                                 | Page         |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Changed ESD (HBM) rating from ±1000V to ±750V                                                                                                    | 6            |

| Changed AINN3 to AINN4 in ADS1234 Input Channel Selection With A0 and A1 table.                                                                  | 16           |

| Changes from Revision F (February 2008) to Revision G (January 2021)                                                                             | Page         |

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新                                                                                                                  | 1            |

| • 「製品情報」および「ESD 定格」表、「推奨動作条件」および「熱に関する情報」表、「詳細説明<br>ーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デ<br>のサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加 | バイスおよびドキュメント |

| • Deleted Ordering Information section; all ordering information available in package opt                                                        |              |

| at end of data sheet                                                                                                                             |              |

| Added analog input voltage specification to Absolute Maximum Ratings                                                                             |              |

| Added digital input voltage specification to Absolute Maximum Ratings                                                                            |              |

| <ul> <li>Deleted momentary input current specification from Absolute Maximum Ratings</li> </ul>                                                  |              |

| Added input current note to Absolute Maximum Ratings                                                                                             |              |

| Added common-mode voltage condition to Common-Mode Rejection specification in E table                                                            | _            |

| • Deleted power-supply rejection (gain = 1) MIN specification from <i>Electrical Characteris</i>                                                 | stics table8 |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated