# ADS117L1x 512kSPS、クワッドおよびオクタル、同時サンプリング、16 ビット $\Delta\Sigma$ ADCs

## 1 特長

- 4つまたは8つのチャネルを同時に測定

- 広帯域フィルタモード: 最大 512kSPS

- 線形位相応答

- $\pm 0.0004\text{dB}$  パスバンドリップル

- 106dB ストップバンド減衰

- 低レイテンシフィルタモード: 最大 1365kSPS

- 3.9 $\mu\text{s}$  変換レイテンシ

- 電力スケーラブルな速度モード:

- 最高速度: 21mW/ch (512kSPS/1365kSPS)

- 高速度: 16mW/ch (400kSPS/1067kSPS)

- 中速度: 9mW/ch (200kSPS/533kSPS)

- 低速度: 3mW/ch (50kSPS/133kSPS)

- 高精度:

- 200kSPS での SNR: 97.7dB (標準値)

- THD: -115dB (標準値)

- INL: 0.5LSB (標準値)

- オフセットドリフト: 60nV/ $^{\circ}\text{C}$  (標準値)

- ゲインドリフト: 1ppm/ $^{\circ}\text{C}$  の FSR (標準値)

- プリチャージバッファ付き信号入力

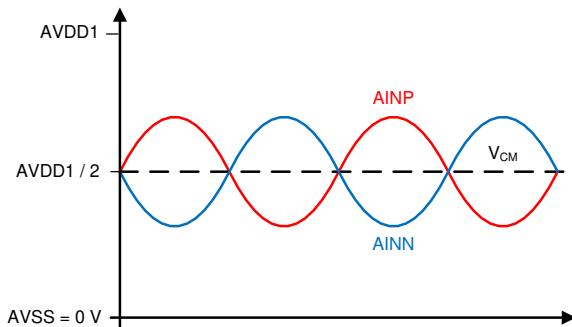

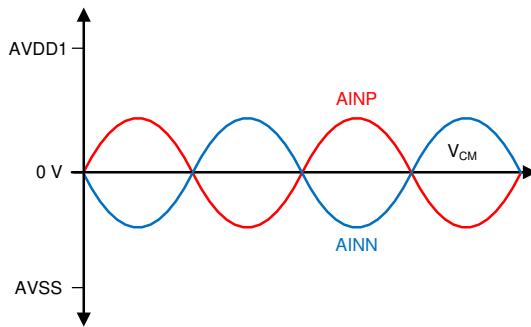

- バイポーラまたはユニポーラの電源動作

- $\pm V_{\text{REF}}$  または  $\pm 2V_{\text{REF}}$  入力範囲

- ピン設定または SPI でプログラム可能

- 出力データ用のフレーム同期ポート

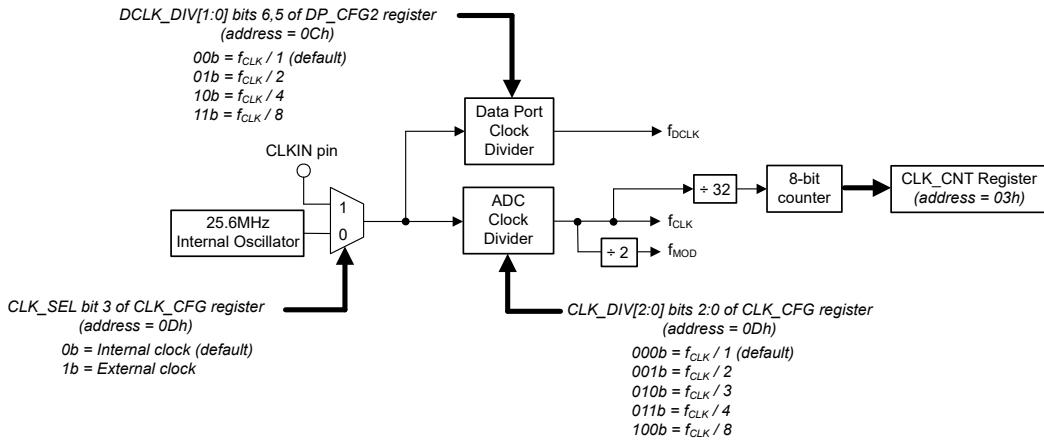

- 内部または外部クロック動作

- アナログ電源電圧: 2.85V ~ 5.5V

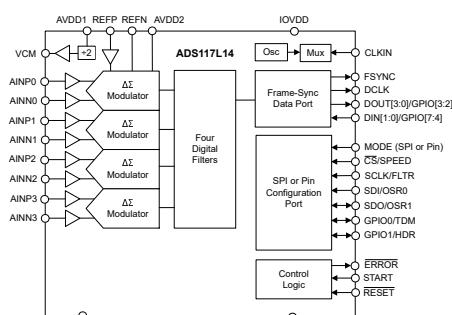

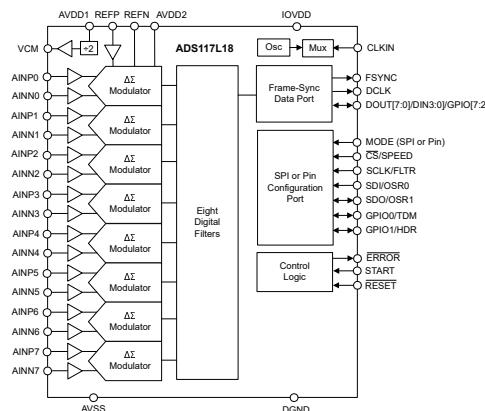

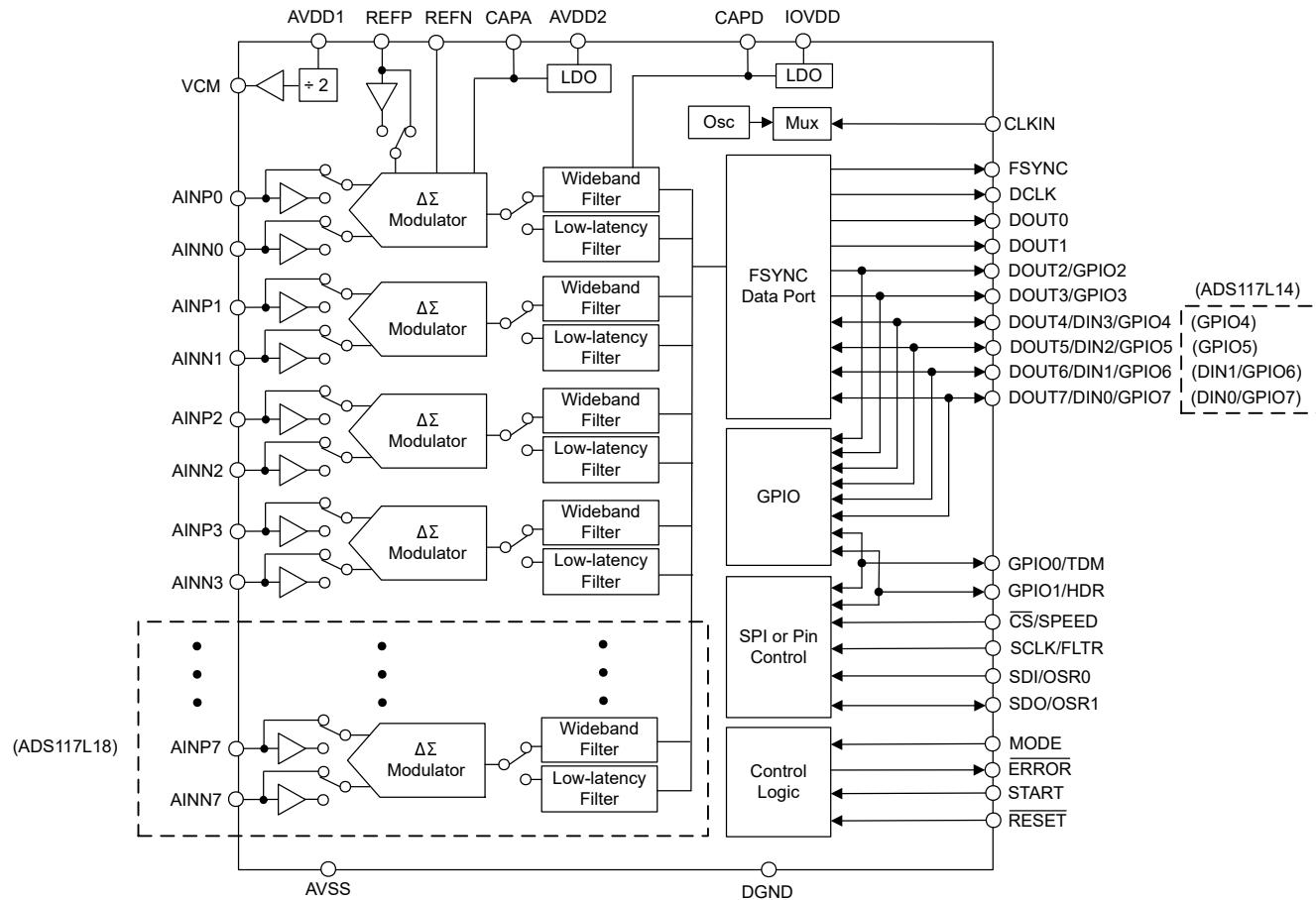

機能ブロック図

## 2 アプリケーション

- 試験および測定機器:

- データアクイジョン (DAQ)

- 衝撃および振動計測器

- 音響および動的歪みゲージ

- ファクトリオートメーション / 制御:

- 状況監視

- 航空宇宙 / 防衛:

- ソナー

- 医療:

- 脳波 (EEG)

- グリッドインフラ:

- 電源品質アナライザ

## 3 説明

ADS117L14 (クワッド) および ADS117L18 (オクタル) は、16ビットのデルタシグマ ( $\Delta\Sigma$ ) アナログ - デジタルコンバーター (ADC) です。これらのデバイスは、4または8チャネルの同時サンプリングを、512kSPS (広帯域フィルタモード) および 1365kSPS (低レイテンシフィルタモード) までのデータレートで実現します。24ビットの ADS127L14 (クワッド) および ADS127L18 (オクタル) ADC は、解像度を向上させるピン互換デバイスです。

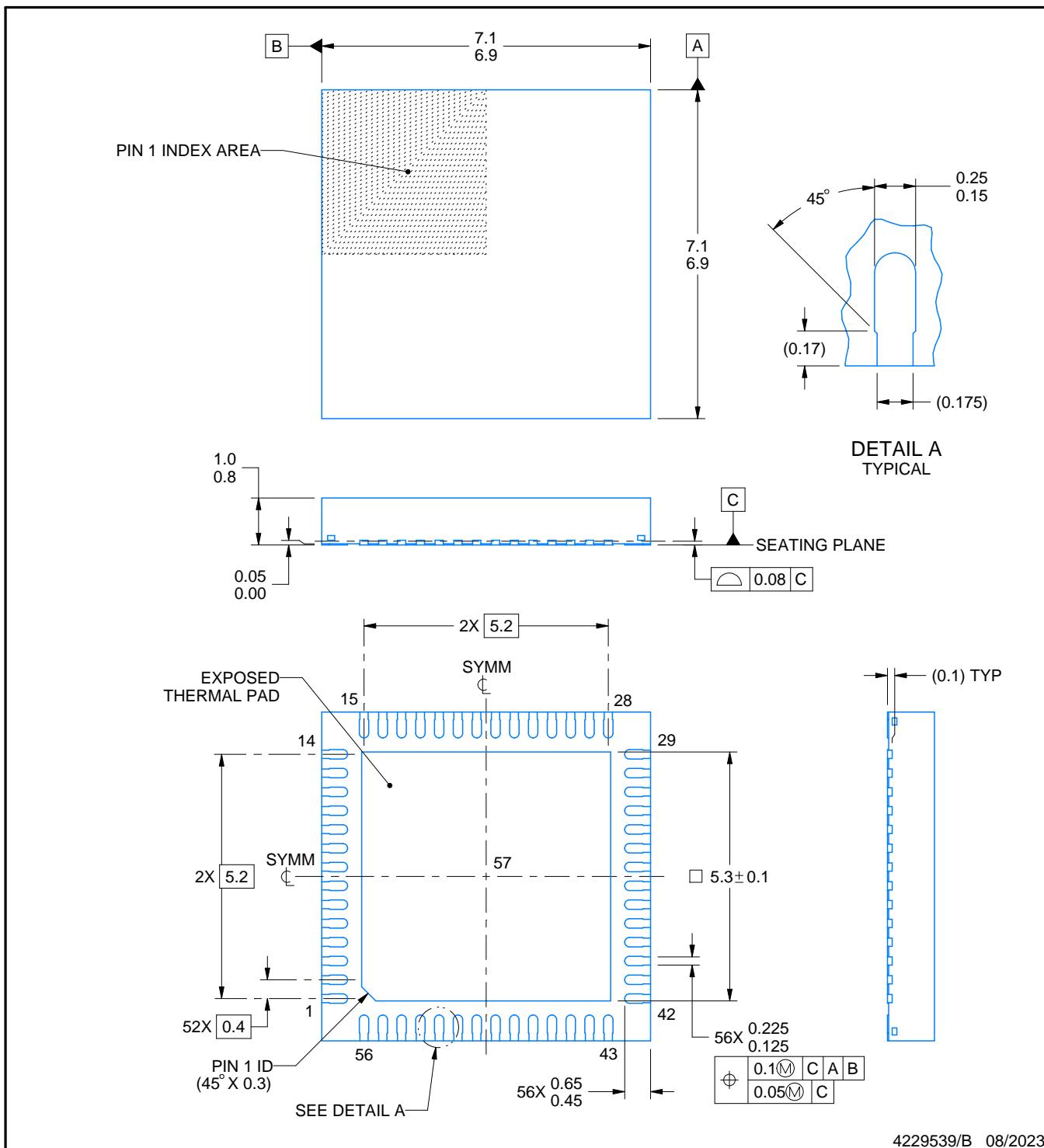

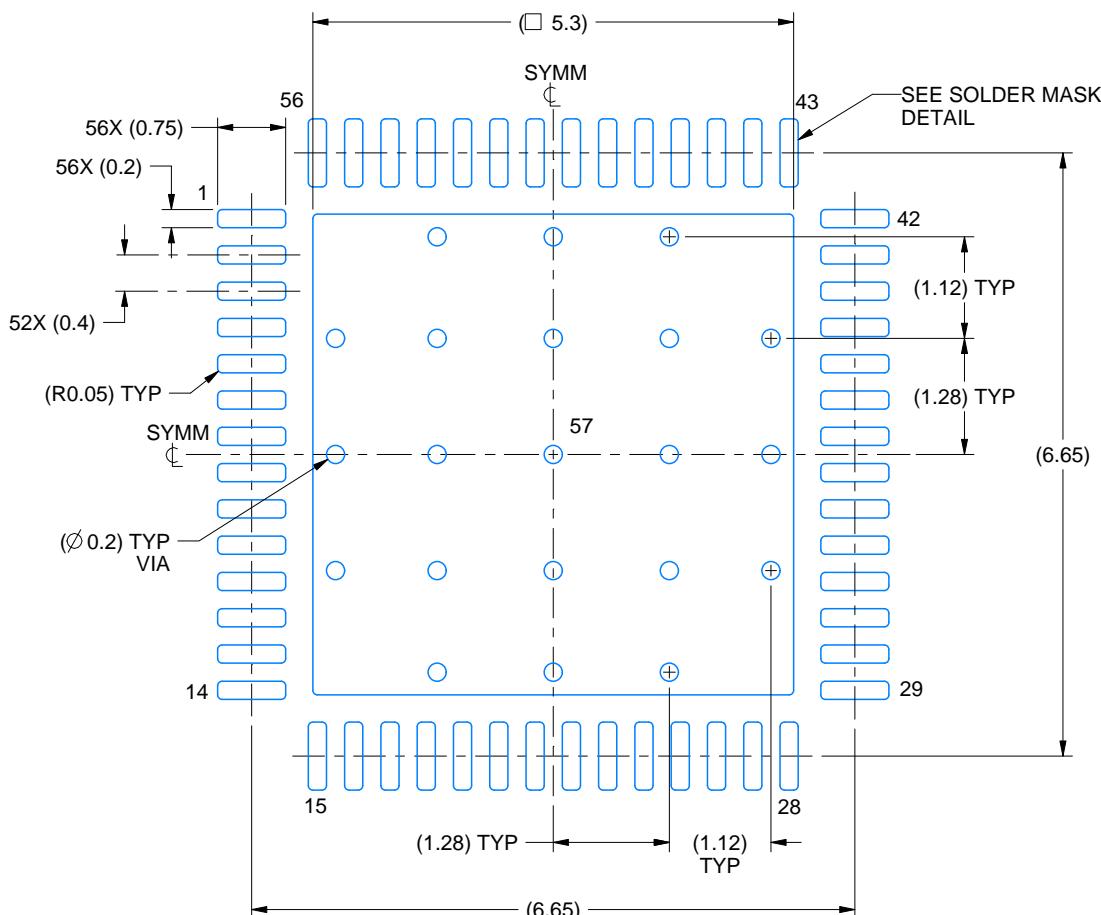

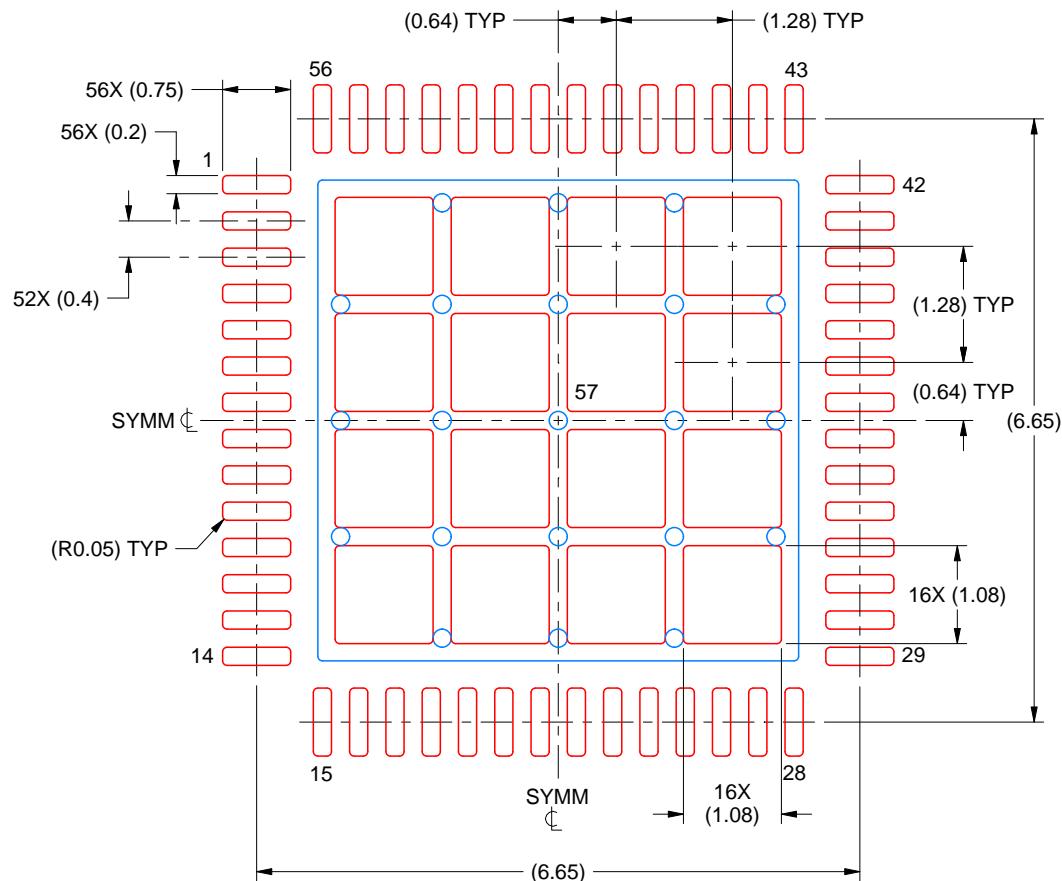

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ  |

|-----------|----------------------|-----------|

| ADS117L1x | RSH (VQFN, 56)       | 7mm × 7mm |

(1) 詳細については、[メカニカル、パッケージ、および注文情報](#)をご覧ください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

電力スケーラブルな速度モードにより、データレート、帯域幅、消費電力の間でトレードオフを最適化できます。広帯域フィルタおよび低レイテンシフィルタにより、AC信号の性能またはDC信号のデータスループットをすべて1つのデバイスで最適化します。

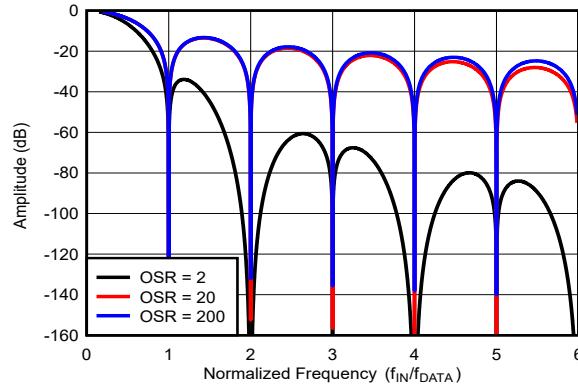

プログラム可能なオーバーサンプリング比(OSR)によって、データレートと信号帯域幅が決まります。線形位相の広帯域フィルタにより、使用可能帯域幅はナイキスト周波数の80%、パスバンドリップルは $\pm 0.0004\text{dB}$ です。低レイテンシフィルタは、 $3.9\mu\text{s}$ の変換レイテンシでデータを供給します。

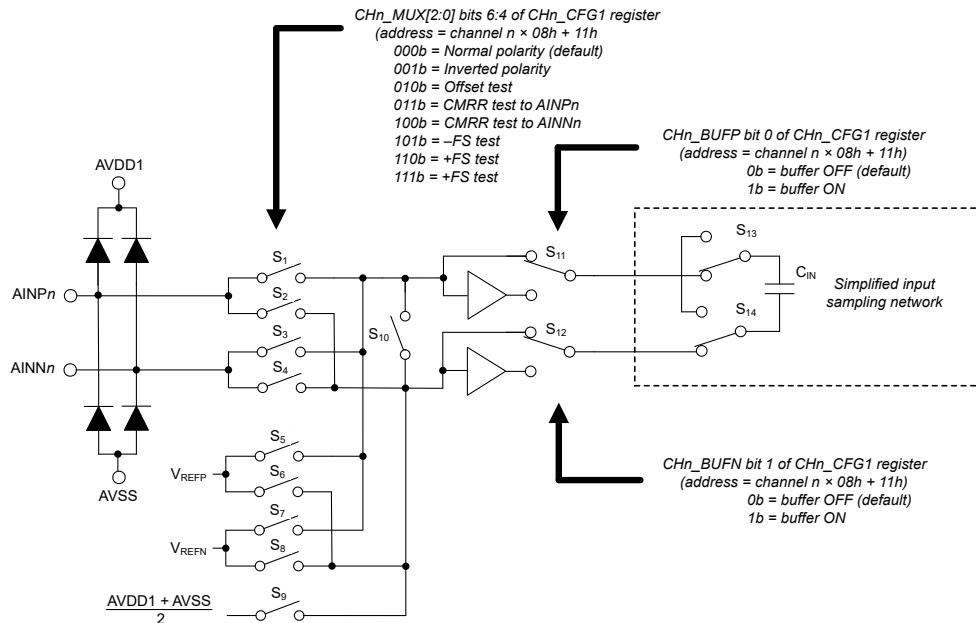

各入力チャネルのプリチャージバッファは、アナログ入力電流とサンプリングノイズを低減し、精度を向上させます。リファレンス入力バッファは、リファレンス負荷を低減して精度を向上させます。

低ドリフトの変調器は、優れたDC精度を備えており、小さいノイズで卓越した16ビット性能を実現します。クロストーク誤差が小さいため、チャネル間の信号結合が減少し、データ絶縁が向上します。

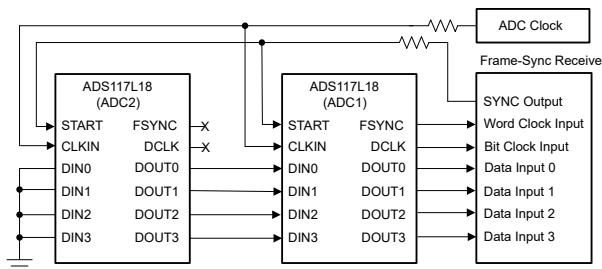

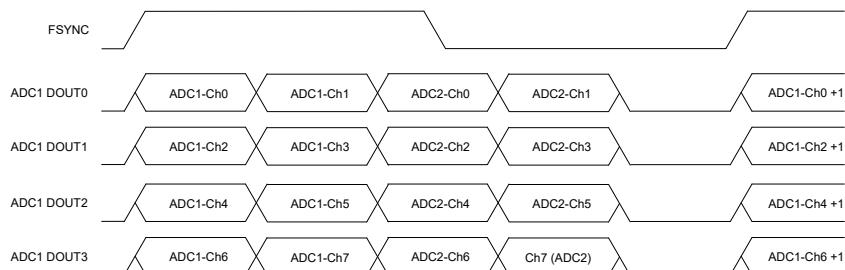

これらのデバイスは、単純なピン接続またはSPIポートを使用してプログラムされます。データレーン数を選択可能なフレーム同期データポートにより、並列または時分割多重形式で変換データが得られます。デイジーチェーン動作では、同じデータレーン数を使用してシステムのチャネル数を拡張します。

これらのデバイスは、同一の7mm × 7mm VQFNパッケージで供給され、ドロップイン拡張機能が可能で、-40°C～+125°C温度範囲での動作が完全に規定されています。

## 目次

|                  |    |                         |    |

|------------------|----|-------------------------|----|

| 1 特長             | 1  | 6.11 IMD の測定            | 30 |

| 2 アプリケーション       | 1  | 6.12 SFDR の測定           | 30 |

| 3 説明             | 1  | 6.13 ノイズ性能              | 31 |

| 4 ピン構成および機能      | 4  | 7 詳細説明                  | 35 |

| 5 仕様             | 8  | 7.1 概要                  | 35 |

| 5.1 絶対最大定格       | 8  | 7.2 機能ブロック図             | 36 |

| 5.2 ESD 定格       | 8  | 7.3 機能説明                | 36 |

| 5.3 推奨動作条件       | 9  | 7.4 デバイスの機能モード          | 54 |

| 5.4 熱に関する情報      | 9  | 7.5 プログラミング             | 67 |

| 5.5 電気的特性        | 10 | 8 レジスタマップ               | 74 |

| 5.6 タイミング要件      | 15 | 9 アプリケーションと実装           | 90 |

| 5.7 スイッチング特性     | 16 | 9.1 アプリケーション情報          | 90 |

| 5.8 タイミング図       | 16 | 9.2 代表的なアプリケーション        | 91 |

| 5.9 代表的特性        | 19 | 9.3 電源に関する推奨事項          | 94 |

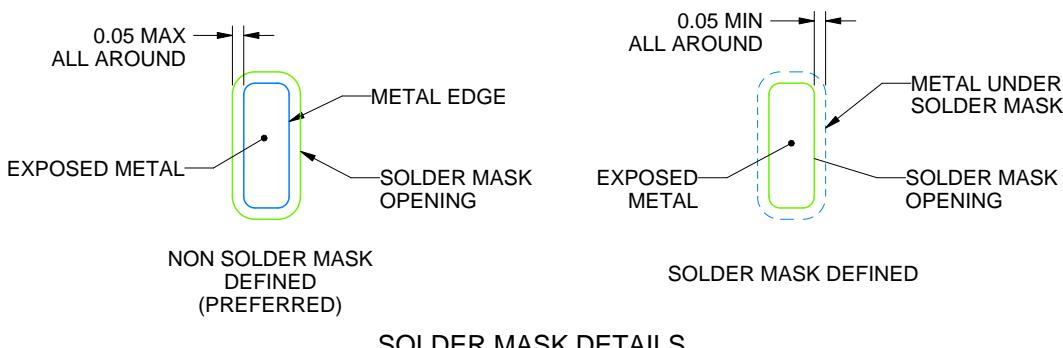

| 6 パラメータ測定情報      | 27 | 9.4 レイアウト               | 95 |

| 6.1 オフセット誤差の測定   | 27 | 10 デバイスおよびドキュメントのサポート   | 97 |

| 6.2 オフセットドリフトの測定 | 27 | 10.1 ドキュメントのサポート        | 97 |

| 6.3 ゲイン誤差の測定     | 27 | 10.2 ドキュメントの更新通知を受け取る方法 | 97 |

| 6.4 ゲインドリフトの測定   | 27 | 10.3 サポート・リソース          | 97 |

| 6.5 NMRR の測定     | 27 | 10.4 商標                 | 97 |

| 6.6 CMRR の測定     | 28 | 10.5 静電気放電に関する注意事項      | 97 |

| 6.7 PSRR の測定     | 28 | 10.6 用語集                | 97 |

| 6.8 SNR の測定      | 29 | 11 改訂履歴                 | 97 |

| 6.9 INL 誤差の測定    | 29 | 12 メカニカル、パッケージ、および注文情報  | 98 |

| 6.10 THD の測定     | 29 |                         |    |

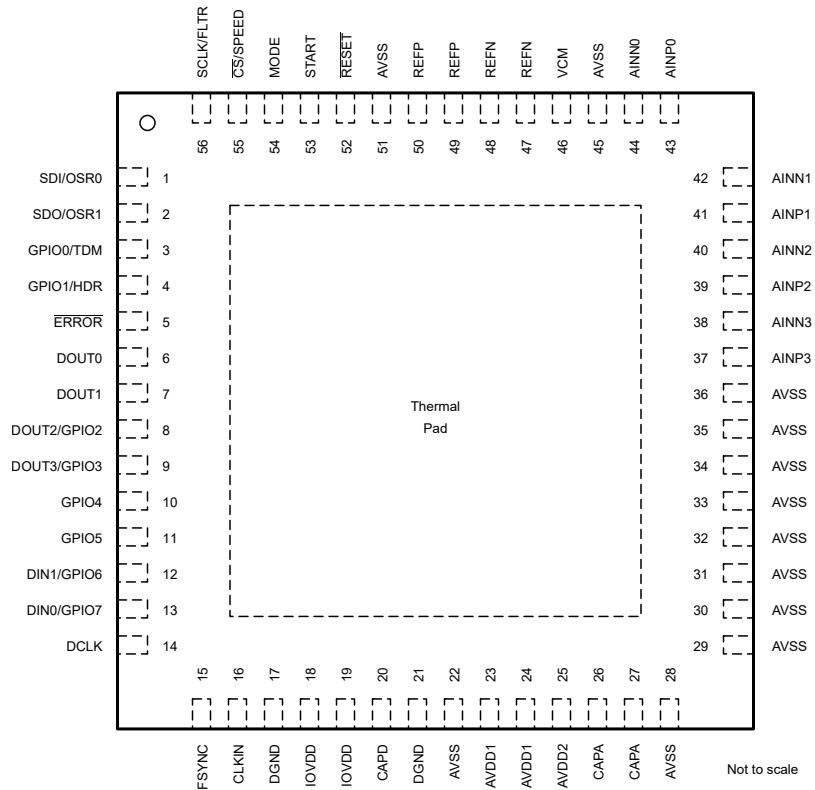

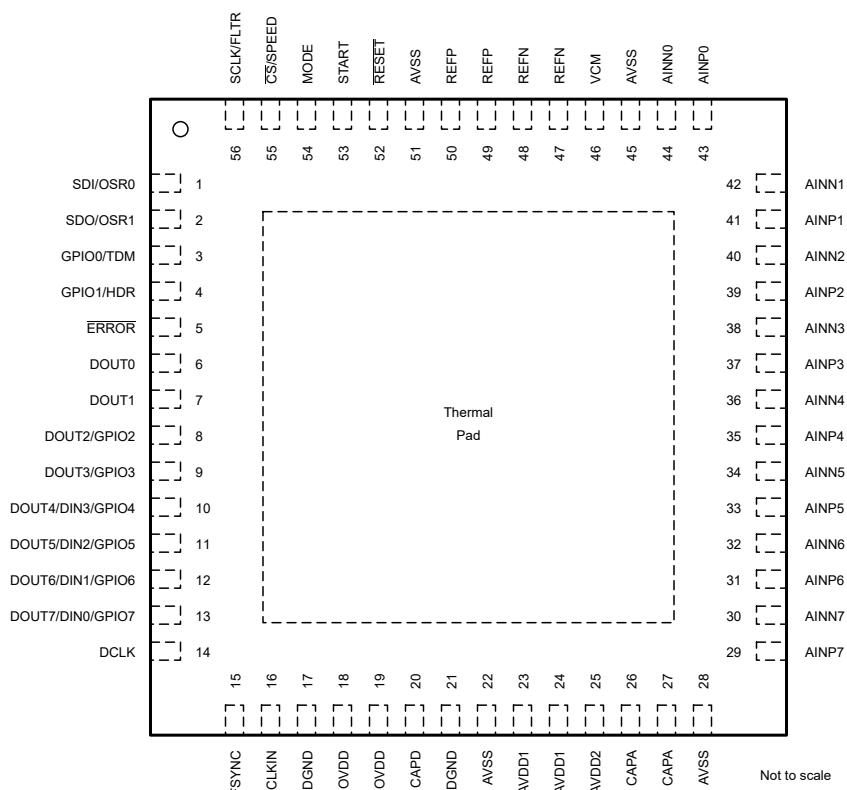

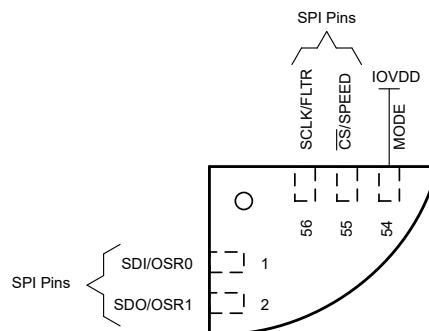

## 4 ピン構成および機能

図 4-1. ADS117L14 RSH パッケージ、56 ピン VQFN (上面図)

図 4-2. ADS117L18 RSH パッケージ、56 ピン VQFN (上面図)

表 4-1. ピンの機能

| 名称    | ADS117L14 ピン | ADS117L18 ピン | TYPE <sup>(1)</sup> | 説明                                                                |

|-------|--------------|--------------|---------------------|-------------------------------------------------------------------|

| AINN0 | 44           | 44           | I                   | チャネル 0 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN1 | 42           | 42           | I                   | チャネル 1 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN2 | 40           | 40           | I                   | チャネル 2 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN3 | 38           | 38           | I                   | チャネル 3 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN4 | —            | 36           | I                   | チャネル 4 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN5 | —            | 34           | I                   | チャネル 5 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN6 | —            | 32           | I                   | チャネル 6 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINN7 | —            | 30           | I                   | チャネル 7 の負アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

| AINP0 | 43           | 43           | I                   | チャネル 0 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。 |

**表 4-1. ピンの機能 (続き)**

| 名称               | ADS117L14 ピン                                         | ADS117L18 ピン   | TYPE <sup>(1)</sup> | 説明                                                                                                                                                                               |

|------------------|------------------------------------------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AINP1            | 41                                                   | 41             | I                   | チャネル 1 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AINP2            | 39                                                   | 39             | I                   | チャネル 2 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AINP3            | 37                                                   | 37             | I                   | チャネル 3 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AINP4            | —                                                    | 35             | I                   | チャネル 4 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AINP5            | —                                                    | 33             | I                   | チャネル 5 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AINP6            | —                                                    | 31             | I                   | チャネル 6 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AINP7            | —                                                    | 29             | I                   | チャネル 7 の正アナログ入力。詳細については、「 <a href="#">アナログ入力</a> 」セクションを参照してください。                                                                                                                |

| AVDD1            | 23, 24                                               | 23, 24         | P                   | 正のアナログ電源 1。詳細については、 <a href="#">電源に関する推奨事項</a> セクションを参照してください。                                                                                                                   |

| AVDD2            | 25                                                   | 25             | P                   | 正のアナログ電源 2。詳細については、 <a href="#">電源に関する推奨事項</a> セクションを参照してください。                                                                                                                   |

| AVSS             | 22, 28, 29, 30、<br>31, 32, 33, 34、<br>35, 36, 45, 51 | 22, 28, 45, 51 | P                   | 負のアナログ電源。詳細については、 <a href="#">電源に関する推奨事項</a> セクションを参照してください。                                                                                                                     |

| CAPA             | 26, 27                                               | 26, 27         | P                   | アナログ電圧レギュレータの出力バイパス。詳細については、 <a href="#">CAPA および CAPD</a> セクションを参照してください。                                                                                                       |

| CAPD             | 20                                                   | 20             | P                   | デジタル電圧レギュレータの出力のバイパス。詳細については、 <a href="#">CAPA および CAPD</a> セクションを参照してください。                                                                                                      |

| CLKIN            | 16                                                   | 16             | I                   | クロック入力。詳細については、 <a href="#">クロック動作</a> セクションを参照してください。                                                                                                                           |

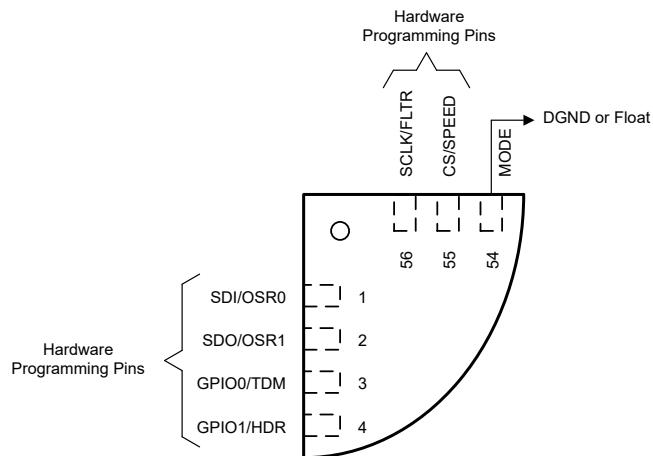

| CS/速度            | 55                                                   | 55             | I                   | SPI モード: アクティブ low チップ セレクト。詳細については、 <a href="#">SPI のプログラミング</a> セクションを参照してください。<br>ハードウェア モード (トライステート入力): 速度範囲の選択。<br>詳細については、 <a href="#">ハードウェア プログラミング</a> セクションを参照してください。 |

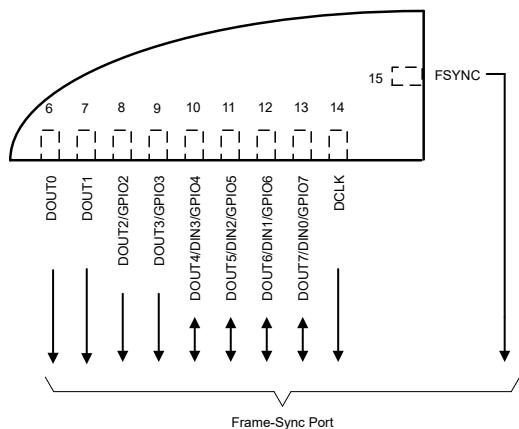

| DCLK             | 14                                                   | 14             | O                   | フレーム同期ビット クロック出力。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。                                                                                                           |

| DGND             | 17, 21                                               | 17, 21         | GND                 | デジタル グランド。                                                                                                                                                                       |

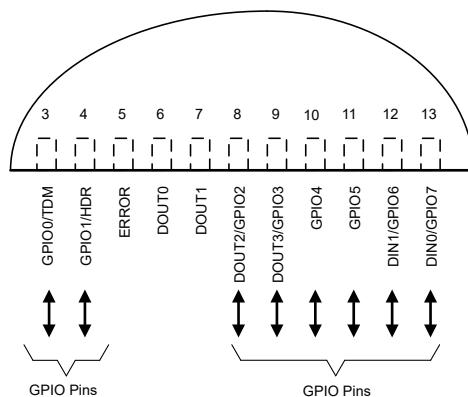

| DIN0/GPIO7       | 13                                                   | —              | I/O                 | デイジー チェーン データ入力 0。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 7。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                                 |

| DIN1/GPIO6       | 12                                                   | —              | I/O                 | デイジー チェーン データ入力 1。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 6。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                                 |

| DOUT0            | 6                                                    | 6              | O                   | データ出力 0。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。                                                                                                                    |

| DOUT1            | 7                                                    | 7              | O                   | データ出力 1。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。                                                                                                                    |

| DOUT2/GPIO2      | 8                                                    | 8              | I/O                 | データ出力 2。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 2。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                                           |

| DOUT3/GPIO3      | 9                                                    | 9              | I/O                 | データ出力 3。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 3。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                                           |

| DOUT4/DIN3/GPIO4 | —                                                    | 10             | I/O                 | データ出力 4 とデイジー チェーン データ入力 3。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 4。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                        |

| DOUT5/DIN2/GPIO5 | —                                                    | 11             | I/O                 | データ出力 5 とデイジー チェーン データ入力 2。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 5。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                        |

| DOUT6/DIN1/GPIO6 | —                                                    | 12             | I/O                 | データ出力 6 とデイジー チェーン データ入力 1。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 6。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                        |

| DOUT7/DIN0/GPIO7 | —                                                    | 13             | I/O                 | データ出力 7 とデイジー チェーン データ入力 0。詳細については、 <a href="#">フレーム同期データポート</a> セクションを参照してください。<br>汎用入出力 7。詳細については、 <a href="#">GPIO</a> セクションを参照してください。                                        |

**表 4-1. ピンの機能 (続き)**

| 名称        | ADS117L14 ピン | ADS117L18 ピン | TYPE <sup>(1)</sup> | 説明                                                                                                                                                                          |

|-----------|--------------|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

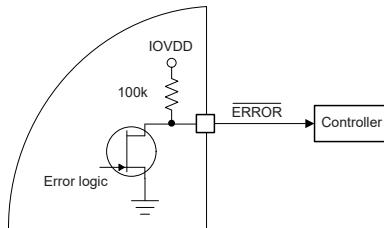

| エラー       | 5            | 5            | O                   | オープンドレイン出力誤差信号。詳細については、 <a href="#">ERROR ピンとERR_FLAG ビットセクション</a> を参照してください。                                                                                               |

| FSYNC     | 15           | 15           | O                   | フレーム同期ワードクロック出力。詳細については、 <a href="#">フレーム同期データポートセクション</a> を参照してください。                                                                                                       |

| GPIO0/TDM | 3            | 3            | I/O                 | 汎用入出力 0。詳細については、 <a href="#">GPIO セクション</a> を参照してください。<br>ハードウェアモード(トライステート入力):TDM 比の選択。<br>詳細については、 <a href="#">ハードウェアプログラミングセクション</a> を参照してください。                          |

| GPIO1/HDR | 4            | 4            | I/O                 | 汎用入出力 1。詳細については、 <a href="#">GPIO セクション</a> を参照してください。<br>ハードウェアモード(tri 状態入力):データヘッダーの選択。<br>詳細については、 <a href="#">ハードウェアプログラミングセクション</a> を参照してください。                         |

| GPIO4     | 10           | —            | I/O                 | 汎用入出力 4。詳細については、 <a href="#">GPIO セクション</a> を参照してください。                                                                                                                      |

| GPIO5     | 11           | —            | I/O                 | 汎用入出力 5。詳細については、 <a href="#">GPIO セクション</a> を参照してください。                                                                                                                      |

| IOVDD     | 18, 19       | 18, 19       | P                   | デジタル I/O 電源電圧。詳細については、 <a href="#">電源に関する推奨事項</a> セクションを参照してください。                                                                                                           |

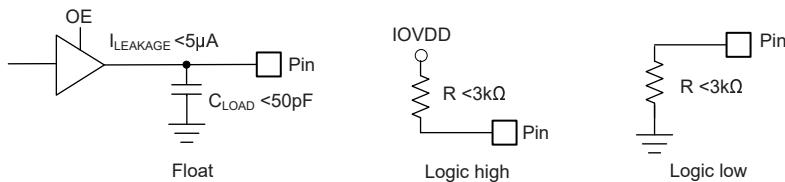

| モード       | 54           | 54           | I                   | トライステート入力。構成モードの選択<br>1 = SPI プログラムモード<br>0 または float = ハードウェアプログラムモード                                                                                                      |

| REFN      | 47, 48       | 47, 48       | I                   | 負のリファレンス電圧入力。詳細については、「 <a href="#">リファレンス電圧</a> 」セクションを参照してください。                                                                                                            |

| REFP      | 49, 50       | 49, 50       | I                   | 正のリファレンス電圧入力。詳細については、「 <a href="#">リファレンス電圧</a> 」セクションを参照してください。                                                                                                            |

| RESET     | 52           | 52           | I                   | リセット入力、アクティブ low。詳細については、 <a href="#">RESET ピンセクション</a> を参照してください。                                                                                                          |

| SCLK/FLTR | 56           | 56           | I                   | SPI モード:シリアルクロック入力。詳細については、 <a href="#">SPI のプログラミング</a> セクションを参照してください。<br>ハードウェアモード(トライステート入力):フィルタモードの選択。<br>詳細については、 <a href="#">ハードウェアプログラミングセクション</a> を参照してください。      |

| SDI/OSR0  | 1            | 1            | I                   | SPI モード:シリアルデータ入力。詳細については、 <a href="#">SPI のプログラミング</a> セクションを参照してください。<br>ハードウェアモード(トライステート入力):フィルタ OSR0 を選択します。<br>詳細については、 <a href="#">ハードウェアプログラミングセクション</a> を参照してください。 |

| SDO/OSR1  | 2            | 2            | I/O                 | SPI モード:シリアルデータ出力。詳細については、 <a href="#">SPI のプログラミング</a> セクションを参照してください。<br>ハードウェアモード(トライステート入力):フィルタ OSR1 を選択します。<br>詳細については、 <a href="#">ハードウェアプログラミングセクション</a> を参照してください。 |

| START     | 53           | 53           | I                   | 変換制御。詳細については、 <a href="#">同期</a> セクションを参照してください。                                                                                                                            |

| VCM       | 46           | 46           | O                   | 同相電圧出力。詳細については、 <a href="#">VCM の出力電圧</a> セクションを参照してください。                                                                                                                   |

| サーマルパッド   | —            | —            | —                   | サーマルパワーパッド。サーマルパッドを AVSS に接続。                                                                                                                                               |

(1) I: 入力、O: 出力、I/O: 双方向入出力、P: 電源、G ND: グラウンド

## 5 仕様

### 5.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|           |                                | 最小値        | 最大値         | 単位 |

|-----------|--------------------------------|------------|-------------|----|

| 電源電圧      | AVDD1 から AVSS へ                | -0.3       | 6.5         | V  |

|           | AVDD2 から AVSS へ                | -0.3       | 6.5         |    |

|           | AVSS から DGND へ                 | -3         | 0.3         |    |

|           | IOVDD から DGND へ                | -0.3       | 2.2         |    |

| アナログ入力電圧  | AINPx, AINNx, REFP, REFN       | AVSS - 0.3 | AVDD1 + 0.3 | V  |

| アナログ出力電圧  | CAPA から AVSS へ                 | AVSS       | 1.65        | V  |

|           | CAPD から DGND へ                 | DGND       | 1.65        |    |

|           | VCM から AVSS へ                  | AVSS       | AVDD1       |    |

| デジタル入出力電圧 | DGND へ                         | DGND - 0.3 | 2.2         | V  |

| 入力電流      | 連続、電源ピンを除く任意のピン <sup>(2)</sup> | -10        | 10          | mA |

| 温度        | 接合部、T <sub>J</sub>             |            | 150         | °C |

|           | 保存、T <sub>stg</sub>            | -65        | 150         |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。絶対最大定格の範囲内であっても推奨動作条件の範囲外で短時間動作させると、デバイスは損傷を受けないかもしれません、完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) アナログ入力ピン AINPx, AINNx, REFP、および REFN は、AVDD1 および AVSS にダイオード クランプされています。アナログ入力電圧が AVDD1 + 0.3V 以上か、AVSS - 0.3V 以下の場合、入力電流を 10mA に制限します。デジタル I/O ピンは、DGND のみにダイオード クランプされます。デジタルピンの電圧が DGND-0.3V を下回った場合は、入力電流を 10mA に制限します。

### 5.2 ESD 定格

|                    |      |                                                          | 値    | 単位 |

|--------------------|------|----------------------------------------------------------|------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | 2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | 1000 |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

動作時周辺温度範囲内 (特に記述のない限り)

|                              |                                               |                      | 最小値          | 公称値          | 最大値          | 単位  |

|------------------------------|-----------------------------------------------|----------------------|--------------|--------------|--------------|-----|

| <b>電源</b>                    |                                               |                      |              |              |              |     |

| アナログ電源                       |                                               | AVDD1 から AVSS へ      | 最高速度モード      | 4.5          | 5.5          | V   |

|                              |                                               |                      | 高速度モード       | 4.5          | 5.5          |     |

|                              |                                               |                      | 中速度モード       | 3            | 5.5          |     |

|                              |                                               |                      | 低速度モード       | 2.85         | 5.5          |     |

|                              |                                               | AVDD1 から DGND へ      |              | 1.65         |              | V   |

|                              |                                               | バイポーラ電源 AVSS/AVDD1 比 |              |              | 1.2          | V/V |

|                              |                                               | AVDD2 から AVSS へ      |              | 1.74         | 5.5          | V   |

|                              |                                               | AVSS から DGND へ       |              | -2.75        | 0            | V   |

|                              | デジタル電源                                        | IOVDD から DGND へ      |              | 1.65         | 1.95         | V   |

| <b>アナログ入力</b>                |                                               |                      |              |              |              |     |

| $V_{AINPn}$ ,<br>$V_{AINNn}$ | 絶対入力電圧                                        | 入力バッファがオフ            | AVSS - 0.05  | AVDD1 + 0.05 |              | V   |

|                              |                                               | 入力バッファがオン            | AVSS + 0.1   | AVDD1 - 0.1  |              |     |

| $V_{INn}$                    | 差動入力電圧<br>$V_{IN} = V_{AINP} - V_{AINN}$      | 1x の入力範囲             | - $V_{REF}$  | $V_{REF}$    |              | V   |

|                              |                                               | 2x の入力範囲             | -2 $V_{REF}$ | 2 $V_{REF}$  |              |     |

| <b>電圧リファレンス入力</b>            |                                               |                      |              |              |              |     |

| $V_{REF}$                    | 差動リファレンス電圧<br>$V_{REF} = V_{REFP} - V_{REFN}$ | Low のリファレンス範囲        | 0.5          | 2.5          | 2.75         | V   |

|                              |                                               | High のリファレンス範囲       | 1            | 4.096        | AVDD1 - AVSS |     |

| $V_{REFN}$                   | 負のリファレンス電圧                                    |                      | AVSS - 0.05  |              |              | V   |

| $V_{REFP}$                   | 正のリファレンス電圧                                    | REFP バッファがオフ         |              |              | AVDD1 + 0.05 | V   |

|                              |                                               | REFP バッファがオン         |              |              | AVDD1 - 0.7  |     |

| <b>クロック信号</b>                |                                               |                      |              |              |              |     |

| $f_{CLK}$                    | クロック周波数                                       | 最高速度モード              | 0.5          | 32.768       | 33.66        | MHz |

|                              |                                               | 高速度モード               | 0.5          | 25.6         | 26.3         |     |

|                              |                                               | 中速度モード               | 0.5          | 12.8         | 13.15        |     |

|                              |                                               | 低速度モード               | 0.5          | 3.2          | 3.29         |     |

| <b>デジタル入力</b>                |                                               |                      |              |              |              |     |

|                              | 入力電圧                                          |                      | 0            |              | IOVDD        | V   |

| <b>温度範囲</b>                  |                                               |                      |              |              |              |     |

| $T_A$                        | 周囲温度                                          | 動作中                  | -50          |              | 125          | °C  |

|                              |                                               | 仕様                   | -40          |              | 125          |     |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     |  | ADS117L14、ADS117L18 | 単位   |

|-----------------------------|---------------------|--|---------------------|------|

|                             |                     |  | VQFN (RSH)          |      |

|                             |                     |  | 56 ピン               |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        |  | 23.5                | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 |  | 11.5                | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        |  | 6.3                 | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    |  | 0.1                 | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    |  | 6.2                 | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗 |  | 1.1                 | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$  です。すべての仕様は AVDD1 = 5V, AVDD2 = 1.8V ~ 5V, AVSS = 0V, IOVDD = 1.8V,  $V_{IN} = 0\text{V}$ ,  $V_{CM} = 2.5\text{V}$ ,  $V_{REFP} = 4.096\text{V}$ ,  $V_{REFN} = 0\text{V}$ , 高リファレンス範囲、1倍の入力範囲、すべての速度モード、すべてのチャンネルがアクティブ、入力プリチャージバッファがオン、リファレンスプリチャージバッファがオン時のものです（特に記述のない限り）

| パラメータ                 | テスト条件             | 最小値       | 標準値 | 最大値 | 単位                                  |

|-----------------------|-------------------|-----------|-----|-----|-------------------------------------|

| <b>アナログ入力、最大速度モード</b> |                   |           |     |     |                                     |

| 入力電流、差動入力電圧           | 入力バッファがオフ         | 125       |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 60        |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 2$   |     |     | $\mu\text{A}$                       |

| 入力電流ドリフト、差動入力電圧       | 入力バッファがオフ         | 5         |     |     | $\text{nA}/\text{V}/^\circ\text{C}$ |

|                       | 入力バッファがオフ、2倍の入力範囲 | 2         |     |     |                                     |

|                       | 入力バッファがオン         | 20        |     |     | $\text{nA}/^\circ\text{C}$          |

| 入力電流、同相入力電圧           | 入力バッファがオフ         | 6.5       |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 3         |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 2$   |     |     | $\mu\text{A}$                       |

| <b>アナログ入力、高速度モード</b>  |                   |           |     |     |                                     |

| 入力電流、差動入力電圧           | 入力バッファがオフ         | 95        |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 47        |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 1.5$ |     |     | $\mu\text{A}$                       |

| 入力電流ドリフト、差動入力電圧       | 入力バッファがオフ         | 3         |     |     | $\text{nA}/\text{V}/^\circ\text{C}$ |

|                       | 入力バッファがオフ、2倍の入力範囲 | 1.5       |     |     |                                     |

|                       | 入力バッファがオン         | 5         |     |     | $\text{nA}/^\circ\text{C}$          |

| 入力電流、同相入力電圧           | 入力バッファがオフ         | 5         |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 2.5       |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 1.5$ |     |     | $\mu\text{A}$                       |

| <b>アナログ入力、中速度モード</b>  |                   |           |     |     |                                     |

| 入力電流、差動入力電圧           | 入力バッファがオフ         | 47        |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 25        |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 1.5$ |     |     | $\mu\text{A}$                       |

| 入力電流ドリフト、差動入力電圧       | 入力バッファがオフ         | 2         |     |     | $\text{nA}/\text{V}/^\circ\text{C}$ |

|                       | 入力バッファがオフ、2倍の入力範囲 | 1         |     |     |                                     |

|                       | 入力バッファがオン         | 5         |     |     | $\text{nA}/^\circ\text{C}$          |

| 入力電流、同相入力電圧           | 入力バッファがオフ         | 2.5       |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 1.3       |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 1.5$ |     |     | $\mu\text{A}$                       |

| <b>アナログ入力、低速度モード</b>  |                   |           |     |     |                                     |

| 入力電流、差動入力電圧           | 入力バッファがオフ         | 12        |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 6         |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 0.4$ |     |     | $\mu\text{A}$                       |

| 入力電流ドリフト、差動入力電圧       | 入力バッファがオフ         | 1         |     |     | $\text{nA}/\text{V}/^\circ\text{C}$ |

|                       | 入力バッファがオフ、2倍の入力範囲 | 0.5       |     |     |                                     |

|                       | 入力バッファがオン         | 0.2       |     |     | $\text{nA}/^\circ\text{C}$          |

| 入力電流、同相入力電圧           | 入力バッファがオフ         | 0.6       |     |     | $\mu\text{A}/\text{V}$              |

|                       | 入力バッファがオフ、2倍の入力範囲 | 0.3       |     |     |                                     |

|                       | 入力バッファがオン         | $\pm 0.4$ |     |     | $\mu\text{A}$                       |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$  です。すべての仕様は AVDD1 = 5V、AVDD2 = 1.8V ~ 5V、AVSS = 0V、IOVDD = 1.8V、 $V_{IN} = 0V$ 、 $V_{CM} = 2.5V$ 、 $V_{REFP} = 4.096V$ 、 $V_{REFN} = 0V$ 、高リファレンス範囲、1 倍の入力範囲、すべての速度モード、すべてのチャンネルがアクティブ、入力プリチャージバッファがオン、リファレンス プリチャージバッファがオン時のものです (特に記述のない限り)

| パラメータ             | テスト条件                 | 最小値                                                                              | 標準値                                           | 最大値                     | 単位                             |

|-------------------|-----------------------|----------------------------------------------------------------------------------|-----------------------------------------------|-------------------------|--------------------------------|

| <b>DC 特性</b>      |                       |                                                                                  |                                               |                         |                                |

|                   | 分解能                   | ミッシング コードなし                                                                      | 16                                            |                         | ビット                            |

| $e_n$             | DC ノイズ                |                                                                                  | 詳細については、「ノイズ性能」を参照してください                      |                         |                                |

|                   | オフセット エラー             | $T_A = 25^\circ\text{C}$                                                         | -250                                          | $\pm 60$                | $\mu\text{V}$                  |

|                   | オフセットのドリフト            |                                                                                  | 50                                            | 200                     | $\text{nV}/^\circ\text{C}$     |

|                   | ゲイン誤差                 | $T_A = 25^\circ\text{C}$                                                         | -2500                                         | $\pm 200$               | 2500 ppm (対 FSR)               |

|                   | ゲインドリフト               |                                                                                  | 1                                             | 3                       | ppm (対 FSR) / $^\circ\text{C}$ |

| INL               | 積分非直線性 <sup>(1)</sup> |                                                                                  | 0.5                                           | 1                       | LSB                            |

| CMRR              | 同相除去比                 | DC                                                                               | 90                                            | 115                     | dB                             |

|                   |                       | 最高 10kHz                                                                         |                                               | 110                     |                                |

|                   |                       | DC 時、2 倍の入力範囲                                                                    |                                               | 105                     |                                |

| PSRR              | 電源除去比                 | AVDD1、DC                                                                         | 98                                            |                         | dB                             |

|                   |                       | AVDD2、DC                                                                         | 130                                           |                         |                                |

|                   |                       | IOVDD、DC                                                                         | 108                                           |                         |                                |

| <b>AC 特性</b>      |                       |                                                                                  |                                               |                         |                                |

| $f_{DATA}$        | データレート                | 最高速度モード                                                                          | 広帯域フィルタ                                       | 4                       | 512 kSPS                       |

|                   |                       |                                                                                  | 低レイテンシ フィルタ                                   | 0.1024                  | 1365.3                         |

|                   |                       | 高速度モード                                                                           | 広帯域フィルタ                                       | 3.125                   | 400                            |

|                   |                       |                                                                                  | 低レイテンシ フィルタ                                   | 0.08                    | 1067                           |

|                   |                       | 中速度モード                                                                           | 広帯域フィルタ                                       | 1.5625                  | 200                            |

|                   |                       |                                                                                  | 低レイテンシ フィルタ                                   | 0.08                    | 533.3                          |

|                   |                       | 低速度モード                                                                           | 広帯域フィルタ                                       | 0.390625                | 50                             |

|                   |                       |                                                                                  | 低レイテンシ フィルタ                                   | 0.01                    | 133.3                          |

| SNR               | 信号対雑音比                | $f_{IN} = 1\text{kHz}$ ,<br>$V_{IN} = -0.2\text{dBFS}$ ,<br>OSR = 64             | 広帯域フィルタ                                       | 97.0                    | 97.7 dB                        |

|                   |                       |                                                                                  | 広帯域フィルタ、<br>$V_{REF} = 2.5V$ 、<br>2 倍の入力範囲    |                         | 97.5                           |

|                   |                       |                                                                                  | 低レイテンシ フィルタ                                   | 97.0                    | 97.9                           |

|                   |                       |                                                                                  | 低レイテンシ フィルタ<br>$V_{REF} = 2.5V$ 、<br>2 倍の入力範囲 |                         | 97.8                           |

|                   |                       |                                                                                  |                                               |                         |                                |

| THD               | 全高調波歪                 | $f_{IN} = 1\text{kHz}$ , $V_{IN} = -0.2\text{dBFS}$                              |                                               | -115                    | -105 dB                        |

|                   |                       | 最高速度モード                                                                          |                                               | -105                    | -100                           |

| IMD               | 相互変調歪み                | $f_{IN} = 9.7\text{kHz}$ および<br>10.3kHz,<br>$V_{IN} = -6.5\text{dBFS}$           | 2 次項                                          | -120                    | dB                             |

|                   |                       |                                                                                  | 3 次項                                          | -110                    |                                |

| SFDR              | スプリアスフリー ダイナミック レンジ   | $f_{IN} = 1\text{kHz}$ , $V_{IN} = -0.2\text{dBFS}$                              |                                               | 110                     | dB                             |

|                   | クロストーク                | $f_{IN} = 1\text{kHz}$ , $V_{IN} = -0.2\text{dBFS}$ <sup>(3)</sup>               |                                               | -120                    | dB                             |

| NMRR              | ノーマル モード除去比           | $f_{IN} = 50\text{Hz} (\pm 1\text{Hz})$ , $f_{DATA} = 50\text{SPS}$ , sinc3 フィルタ |                                               | 100                     | dB                             |

|                   |                       | $f_{IN} = 60\text{Hz} (\pm 1\text{Hz})$ , $f_{DATA} = 60\text{SPS}$ , sinc3 フィルタ |                                               | 100                     |                                |

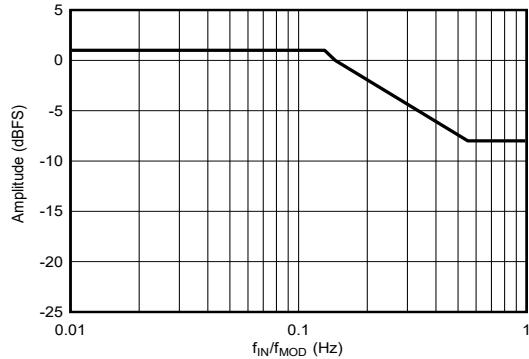

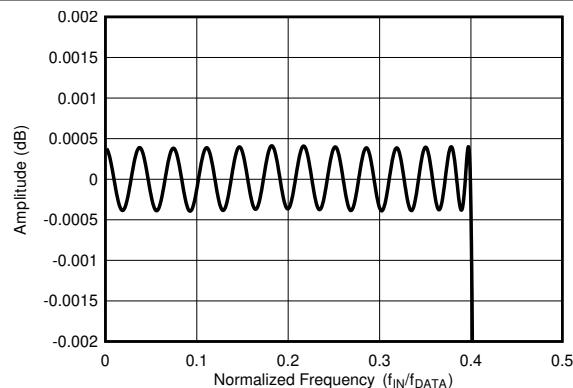

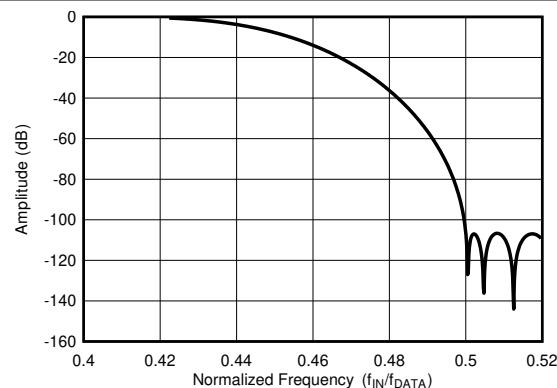

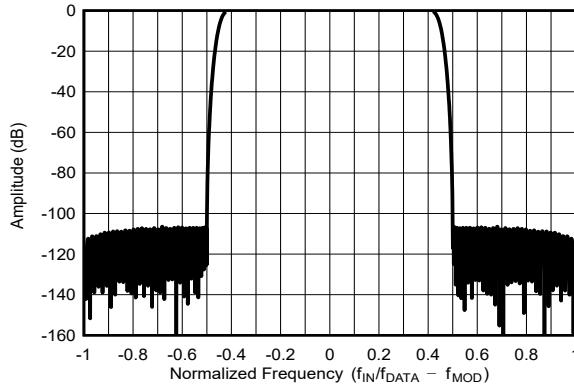

| <b>広帯域フィルタの特性</b> |                       |                                                                                  |                                               |                         |                                |

|                   | パス バンド周波数             | パス バンドリップルのエンベロープ内                                                               |                                               | $0.4 \cdot f_{DATA}$    | Hz                             |

|                   |                       | -0.1dB 周波数                                                                       |                                               | $0.4125 \cdot f_{DATA}$ |                                |

|                   |                       | -3dB 周波数                                                                         |                                               | $0.4374 \cdot f_{DATA}$ |                                |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$  です。すべての仕様は AVDD1 = 5V, AVDD2 = 1.8V ~ 5V, AVSS = 0V, IOVDD = 1.8V,  $V_{IN} = 0V$ ,  $V_{CM} = 2.5V$ ,  $V_{REFP} = 4.096V$ ,  $V_{REFN} = 0V$ , 高リファレンス範囲、1倍の入力範囲、すべての速度モード、すべてのチャンネルがアクティブ、入力プリチャージバッファがオン、リファレンス プリチャージバッファがオン時のものです (特に記述のない限り)

| パラメータ                     | テスト条件       | 最小値     | 標準値                  | 最大値 | 単位 |

|---------------------------|-------------|---------|----------------------|-----|----|

| バス バンドリップル                |             | -0.0004 | 0.0004               | dB  |    |

| ストップ バンド周波数               | ストップ バンド減衰時 |         | $0.5 \cdot f_{DATA}$ | Hz  |    |

| ストップ バンド減衰 <sup>(2)</sup> |             |         | 106                  | dB  |    |

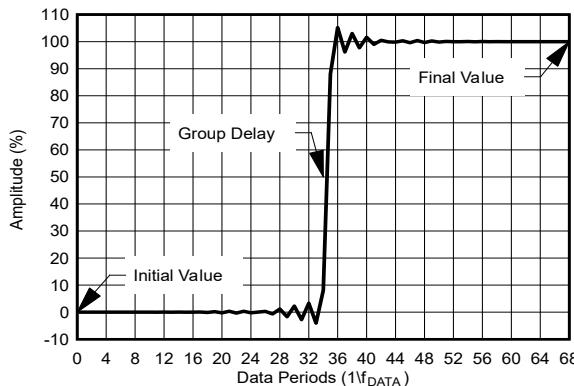

| 群遅延                       |             |         | $34 / f_{DATA}$      | s   |    |

| セトリング タイム                 |             |         | $68 / f_{DATA}$      | s   |    |

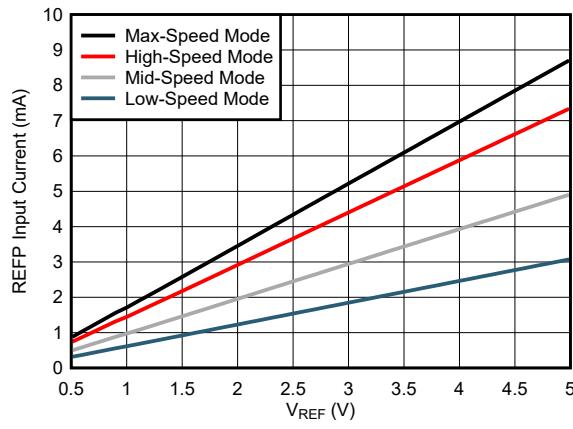

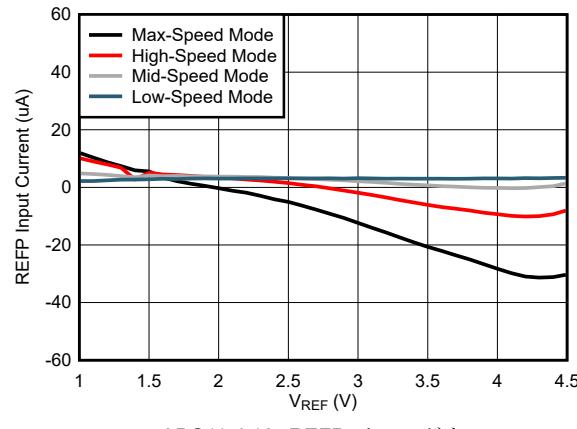

### 電圧リファレンス入力

|                           |              |         |         |                                  |

|---------------------------|--------------|---------|---------|----------------------------------|

| REFP および REFN 入力電流        | REFP バッファがオフ | 最高速度モード | 225     | $\mu\text{A}/\text{V}/\text{ch}$ |

|                           |              | 高速度モード  | 190     |                                  |

|                           |              | 中速度モード  | 130     |                                  |

|                           |              | 低速度モード  | 80      |                                  |

| REFP 入力電流                 | REFP バッファがオン |         | $\pm 3$ | $\mu\text{A}/\text{ch}$          |

| REFP および REFN<br>入力電流ドリフト | REFP バッファがオフ |         | 20      | nA/ $^\circ\text{C}/\text{ch}$   |

| REFP 入力電流ドリフト             | REFP バッファがオン |         | 10      | nA/ $^\circ\text{C}/\text{ch}$   |

### 内部発振器

|           |           |      |      |      |     |

|-----------|-----------|------|------|------|-----|

| $f_{OSC}$ | オシレータの周波数 | 25.4 | 25.6 | 25.8 | MHz |

|-----------|-----------|------|------|------|-----|

### VCM 出力電圧

|            |                      |                      |                     |

|------------|----------------------|----------------------|---------------------|

| 出力電圧       |                      | $(AVDD1 + AVSS) / 2$ | V                   |

| 精度         |                      | $\pm 1\%$            | $\pm 0.1\%$         |

| 電圧ノイズ      | 1kHz の帯域幅            | 25                   | $\mu\text{V}_{RMS}$ |

| 起動時間       | $C_L = 100\text{nF}$ | 1                    | ms                  |

| 容量性負荷      |                      | 100                  | nF                  |

| 抵抗性負荷      |                      | 2                    | k $\Omega$          |

| 回路短絡時の電流制限 |                      | 10                   | mA                  |

### デジタル入出力

|            |                 |                                      |                   |               |

|------------|-----------------|--------------------------------------|-------------------|---------------|

| $V_{IL}$   | ロジック Low 入力レベル  |                                      | 0.3 IOVDD         | V             |

| $V_{IH}$   | ロジック High 入力レベル | 0.7 IOVDD                            |                   | V             |

| $I_{LEAK}$ | 外部リーケージ電流       | トライステートビン、フローティング入力状態                | -5                | $\mu\text{A}$ |

| $C_{LOAD}$ | 容量性負荷           | トライステートビン、フローティング入力状態                | 50                | pF            |

| $R_{EXT}$  | プルアップまたはプルダウン抵抗 | トライステートビン:論理 low または high 状態         | 0                 | k $\Omega$    |

| $V_{OL}$   | ロジック Low 出力レベル  | OUT_DRV = 0b, $I_{OL} = 2\text{mA}$  | $0.2 \cdot IOVDD$ | V             |

|            |                 | OUT_DRV = 1b, $I_{OL} = 1\text{mA}$  | $0.2 \cdot IOVDD$ |               |

| $V_{OH}$   | ロジック High 出力レベル | OUT_DRV = 0b, $I_{OH} = -2\text{mA}$ | $0.8 \cdot IOVDD$ | V             |

|            |                 | OUT_DRV = 1b, $I_{OH} = -1\text{mA}$ | $0.8 \cdot IOVDD$ |               |

|            |                 | エラー ピン, $I_{OH} = -2\mu\text{A}$     | $0.8 \cdot IOVDD$ |               |

| 入力ヒステリシス   |                 |                                      | 150               | mV            |

| 入力電流       |                 | -1                                   | 1                 | $\mu\text{A}$ |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$  です。すべての仕様は AVDD1 = 5V、AVDD2 = 1.8V ~ 5V、AVSS = 0V、IOVDD = 1.8V、 $V_{IN} = 0V$ 、 $V_{CM} = 2.5V$ 、 $V_{REFP} = 4.096V$ 、 $V_{REFN} = 0V$ 、高リファレンス範囲、1倍の入力範囲、すべての速度モード、すべてのチャンネルがアクティブ、入力プリチャージバッファがオン、リファレンス プリチャージバッファがオン時のものです (特に記述のない限り)

| パラメータ                 | テスト条件                      |                           | 最小値     | 標準値  | 最大値  | 単位            |  |

|-----------------------|----------------------------|---------------------------|---------|------|------|---------------|--|

| <b>アナログ電源電流</b>       |                            |                           |         |      |      |               |  |

| $I_{AVDD1}, I_{AVSS}$ | AVDD1、AVSS 電流<br>(バッファ オフ) | 1 チャネル                    | 最高速度モード | 1.9  | 2.1  | mA            |  |

|                       |                            | 各追加チャネル                   |         | 1.7  | 2.0  | mA/ch         |  |

|                       |                            | 1 チャネル                    | 高速度モード  | 1.5  | 1.7  | mA            |  |

|                       |                            | 各追加チャネル                   |         | 1.3  | 1.6  | mA/ch         |  |

|                       |                            | 1 チャネル                    | 中速度モード  | 0.9  | 1.0  | mA            |  |

|                       |                            | 各追加チャネル                   |         | 0.7  | 0.85 | mA/ch         |  |

|                       |                            | 1 チャネル                    | 低速度モード  | 0.3  | 0.35 | mA            |  |

|                       |                            | 各追加チャネル                   |         | 0.2  | 0.21 | mA/ch         |  |

|                       |                            | スタンバイ モード                 |         | 110  |      | $\mu\text{A}$ |  |

|                       |                            | パワーダウン モード                |         | 5    |      | $\mu\text{A}$ |  |

| $I_{AVDD2}, I_{AVSS}$ | AVDD1、AVSS バッファ電流          | 入力バッファ                    | 最高速度モード | 1.78 | 2.1  | mA/バッフ<br>ア   |  |

|                       |                            |                           | 高速度モード  | 1.36 | 1.6  |               |  |

|                       |                            |                           | 中速度モード  | 0.7  | 0.85 |               |  |

|                       |                            |                           | 低速度モード  | 0.2  | 0.25 |               |  |

|                       |                            | REFP バッファ                 | 最高速度モード | 1.6  | 1.7  | mA/バッフ<br>ア   |  |

|                       |                            |                           | 高速度モード  | 1.5  | 1.65 |               |  |

|                       |                            |                           | 中速度モード  | 0.9  | 1.0  |               |  |

|                       |                            |                           | 低速度モード  | 0.4  | 0.5  |               |  |

|                       |                            | VCM (同相電圧) バッファ           |         | 0.1  |      | mA            |  |

|                       |                            | AVDD2、AVSS 電流             |         | 4.6  | 5.1  | mA/ch         |  |

|                       |                            | 最高速度モード                   |         | 3.6  | 4.0  |               |  |

|                       |                            | 高速度モード                    |         | 2.3  | 2.55 |               |  |

|                       |                            | 中速度モード                    |         | 0.85 | 0.96 |               |  |

|                       |                            | 低速度モード                    |         | 60   |      | $\mu\text{A}$ |  |

|                       |                            | スタンバイ モード                 |         | 1    |      | $\mu\text{A}$ |  |

| <b>デジタル電源電流</b>       |                            |                           |         |      |      |               |  |

| $I_{IOVDD}$           | IOVDD 電流                   | 広帯域フィルタ<br>$OSR = 32$     | 最高速度モード | 2.1  | 2.5  | mA/ch         |  |

|                       |                            |                           | 高速度モード  | 1.6  | 2.0  |               |  |

|                       |                            |                           | 中速度モード  | 0.8  | 1    |               |  |

|                       |                            |                           | 低速度モード  | 0.2  | 0.35 |               |  |

|                       |                            | 低レイテンシ フィルタ<br>$OSR = 32$ | 最高速度モード | 0.6  | 0.8  | $\mu\text{A}$ |  |

|                       |                            |                           | 高速度モード  | 0.5  | 0.7  |               |  |

|                       |                            |                           | 中速度モード  | 0.20 | 0.35 |               |  |

|                       |                            |                           | 低速度モード  | 0.05 | 0.15 |               |  |

|                       |                            | スタンバイ モード                 | 外部クロック  | 15   |      |               |  |

|                       |                            |                           | 内部発振器   | 50   |      |               |  |

|                       |                            | パワーダウン モード                |         | 35   |      | $\mu\text{A}$ |  |

## 5.5 電気的特性 (続き)

最小値および最大値の仕様は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$  で適用されます。標準値の仕様は  $T_A = 25^\circ\text{C}$  です。すべての仕様は AVDD1 = 5V、AVDD2 = 1.8V ~ 5V、AVSS = 0V、IOVDD = 1.8V、 $V_{IN} = 0V$ 、 $V_{CM} = 2.5V$ 、 $V_{REFP} = 4.096V$ 、 $V_{REFN} = 0V$ 、高リファレンス範囲、1倍の入力範囲、すべての速度モード、すべてのチャンネルがアクティブ、入力プリチャージバッファがオン、リファレンス プリチャージバッファがオン時のものです (特に記述のない限り)

| パラメータ       | テスト条件                                                 | 最小値     | 標準値 | 最大値 | 単位 |

|-------------|-------------------------------------------------------|---------|-----|-----|----|

| <b>消費電力</b> |                                                       |         |     |     |    |

| $P_D$       | ADS117L14<br>広帯域フィルタ、<br>AVDD2 = 1.8V、<br>バッファがオフ     | 最高速度モード | 83  | 95  | mW |

|             |                                                       | 高速度モード  | 64  | 76  |    |

|             |                                                       | 中速度モード  | 37  | 43  |    |

|             |                                                       | 低速度モード  | 12  | 14  |    |

|             | ADS117L14<br>低レイテンシ フィルタ、<br>AVDD2 = 1.8V、<br>バッファがオフ | 最高速度モード | 72  | 83  |    |

|             |                                                       | 高速度モード  | 57  | 66  |    |

|             |                                                       | 中速度モード  | 33  | 39  |    |

|             |                                                       | 低速度モード  | 11  | 13  |    |

|             | ADS117L18<br>広帯域フィルタ、<br>AVDD2 = 1.8V、<br>バッファがオフ     | 最高速度モード | 165 | 190 |    |

|             |                                                       | 高速度モード  | 128 | 151 |    |

|             |                                                       | 中速度モード  | 74  | 86  |    |

|             |                                                       | 低速度モード  | 24  | 28  |    |

|             | ADS117L18<br>低レイテンシ フィルタ、<br>AVDD2 = 1.8V、<br>バッファがオフ | 最高速度モード | 144 | 165 |    |

|             |                                                       | 高速度モード  | 112 | 132 |    |

|             |                                                       | 中速度モード  | 65  | 77  |    |

|             |                                                       | 低速度モード  | 21  | 25  |    |

- (1) ベストフィット方式。

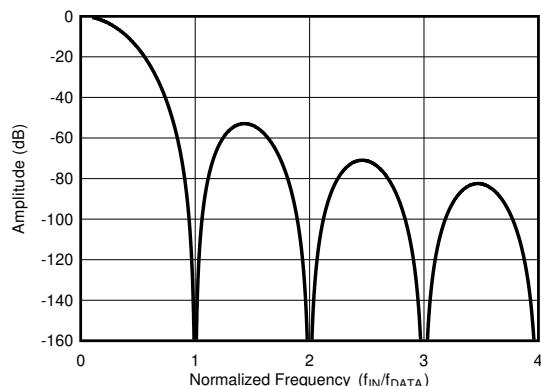

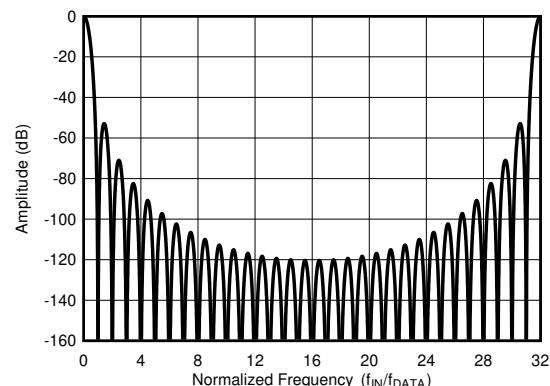

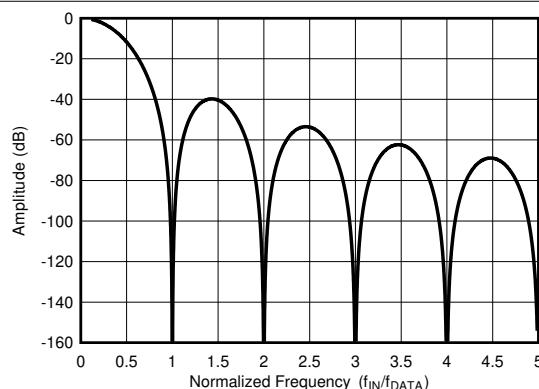

- (2) デジタル フィルタによって提供されるストップバンド減衰。ストップ バンドの入力周波数は、 $f_{MOD} / 32$  で始まるチョップ周波数と相互変調し、106dB 以上のストップ バンド減衰をもたらします。詳細については、「[ストップ バンドの減衰](#)」の図を参照してください。

- (3) 3つ(ADS117L14)と7つ(ADS117L18)のアクティブ チャンネルで、1つの短絡した入力チャネルでクロストークを測定。

## 5.6 タイミング要件

1.65V ≤ IOVDD ≤ 1.95V、動作時周囲温度範囲全体 (特に記述のない限り)

|                         |                                                                                       | 最小値  | 最大値  | 単位               |

|-------------------------|---------------------------------------------------------------------------------------|------|------|------------------|

| <b>クロック</b>             |                                                                                       |      |      |                  |

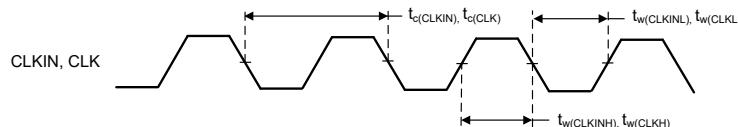

| $t_c(\text{CLKIN})$     | CLKIN 周期                                                                              | 15   | 2000 | ns               |

| $t_w(\text{CLKINL})$    | パルス幅、CLKIN low                                                                        | 6.5  |      | ns               |

| $t_w(\text{CLKINH})$    | パルス幅、CLKIN high                                                                       | 6.5  |      | ns               |

| $t_c(\text{CLK})^{(1)}$ | ADC クロック周期、最大速度モード                                                                    | 29.7 | 2000 | ns               |

|                         | ADC クロック周期、高速度モード                                                                     | 38   | 2000 |                  |

|                         | ADC クロック周期、中速度モード                                                                     | 76   | 2000 |                  |

|                         | ADC クロック周期、低速度モード                                                                     | 304  | 2000 |                  |

| $t_w(\text{CLKL})$      | パルス幅、CLK Low、最大速度モード                                                                  | 13.2 |      | ns               |

|                         | パルス幅、CLK Low、高速度モード                                                                   | 17   |      |                  |

|                         | パルス幅、CLK Low、中速度モード                                                                   | 34   |      |                  |

|                         | パルス幅、CLK Low、低速度モード                                                                   | 128  |      |                  |

| $t_w(\text{CLKH})$      | パルス幅、CLK High、最大速度モード                                                                 | 13.2 |      | ns               |

|                         | パルス幅、CLK High、高速度モード                                                                  | 17   |      |                  |

|                         | パルス幅、CLK High、中速度モード                                                                  | 34   |      |                  |

|                         | パルス幅、CLK High、低速度モード                                                                  | 128  |      |                  |

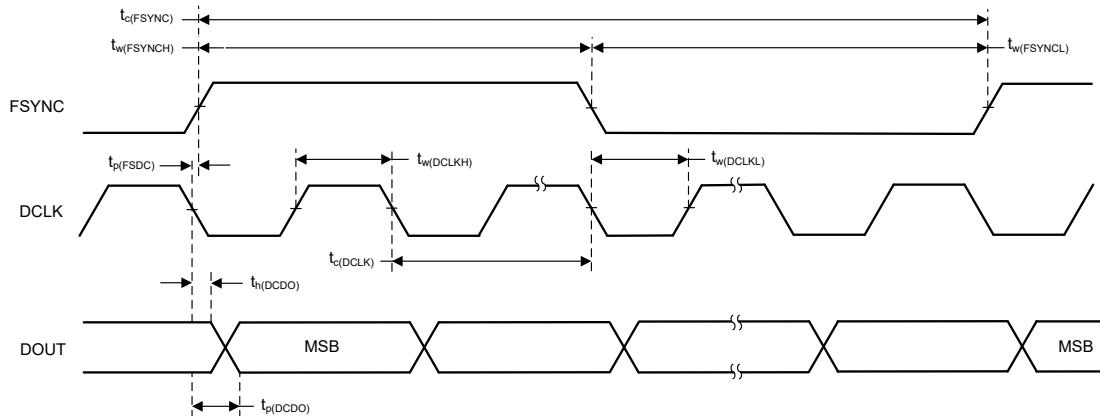

| <b>フレーム同期 (データポート)</b>  |                                                                                       |      |      |                  |

| $t_c(\text{DCLK})$      | DCLK 期間、スタンダードアロン動作                                                                   | 15   |      | ns               |

|                         | DCLK 周期、デイジーチェーン動作                                                                    | 29.7 |      | ns               |

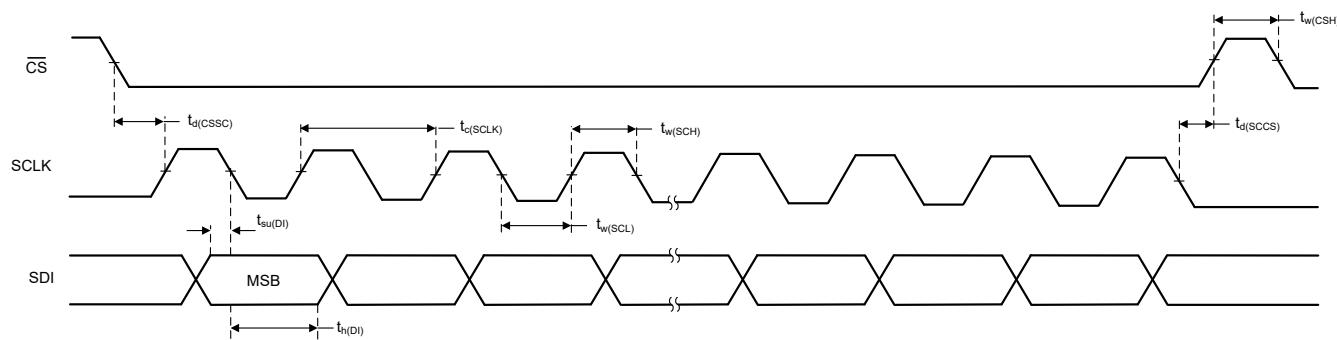

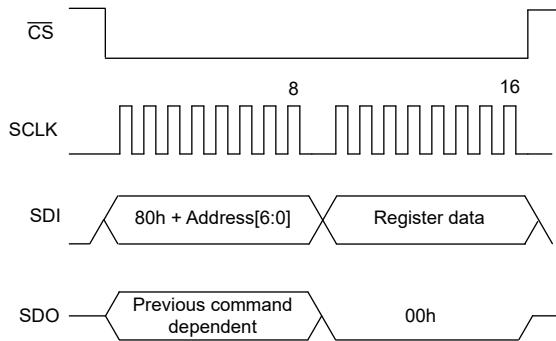

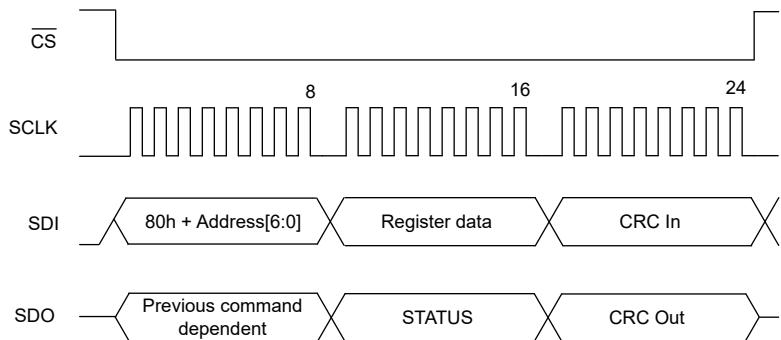

| <b>SPI (構成ポート)</b>      |                                                                                       |      |      |                  |

| $t_c(\text{SCLK})$      | SCLK 周期                                                                               | 75   |      | ns               |

| $t_w(\text{SCL})$       | パルス幅、SCLK low                                                                         | 25   |      | ns               |

| $t_w(\text{SCH})$       | パルス幅、SCLK high                                                                        | 25   |      | ns               |

| $t_d(\text{CSSC})$      | 遅延時間、 $\overline{\text{CS}}$ 立ち下がりエッジから最初の SCLK 立ち上がりエッジまで                            | 20   |      | ns               |

| $t_{su(\text{DI})}$     | セットアップ時間、SDI 有効から SCLK 立ち下がりエッジまで                                                     | 6    |      | ns               |

| $t_h(\text{DI})$        | ホールド時間、SCLK 立ち下がりエッジから SDI 有効まで                                                       | 8    |      | ns               |

| $t_d(\text{SCCS})$      | 遅延時間、最後の SCLK 立ち下がりエッジから $\overline{\text{CS}}$ 立ち上がりエッジまで                            | 20   |      | ns               |

| $t_w(\text{CSH})$       | パルス幅、 $\overline{\text{CS}}$ High                                                     | 20   |      | ns               |

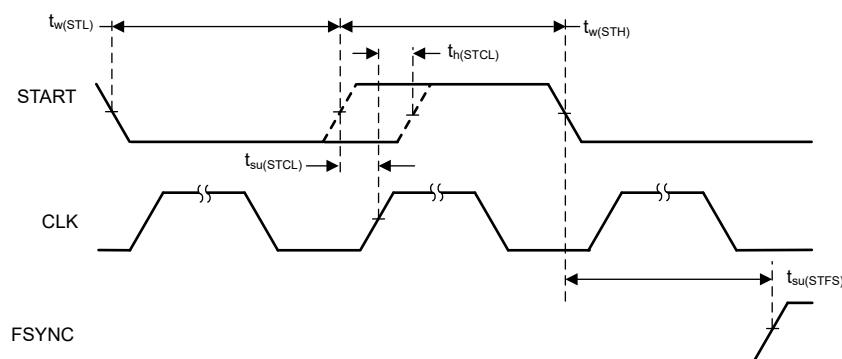

| <b>START ピン</b>         |                                                                                       |      |      |                  |

| $t_w(\text{STL})$       | パルス幅、START low                                                                        | 4    |      | $t_{\text{CLK}}$ |

| $t_w(\text{STH})$       | パルス幅、START high                                                                       | 4    |      | $t_{\text{CLK}}$ |

| $t_{su(\text{STCL})}$   | セットアップ時間、START 立ち上がりエッジから CLKIN 立ち上がりエッジまで <sup>(2)</sup>                             | 4    |      | ns               |

| $t_h(\text{STCL})$      | ホールド時間、CLKIN 立ち上がりエッジから START 立ち上がりエッジまで <sup>(2)</sup>                               | 6    |      | ns               |

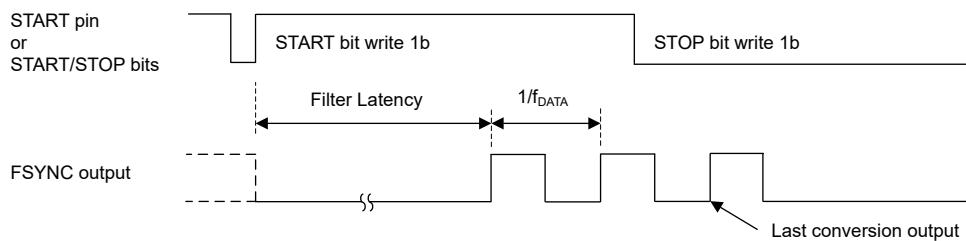

| $t_{su(\text{STFS})}$   | セットアップ時間、START 立ち上がりエッジまたは STOP ビットから FSYNC 立ち下がりエッジにより次の変換を停止するまで (スタート / ストップ変換モード) | 24   |      | $t_{\text{CLK}}$ |

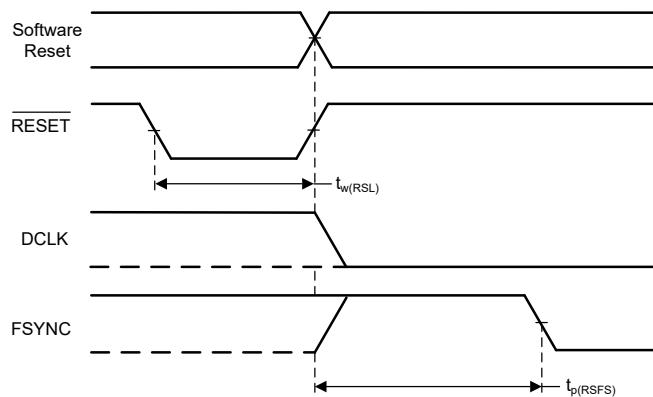

| <b>RESET ピン</b>         |                                                                                       |      |      |                  |

| $t_w(\text{RSL})$       | パルス幅、RESET Low                                                                        | 4    |      | $t_{\text{CLK}}$ |

(1)  $f_{\text{CLK}}$  はメイン ADC クロックです。

(2) 同期の不確実性を回避するため、セットアップ時間とホールド時間の仕様の間に START を high に駆動しないようにします。

## 5.7 スイッチング特性

1.65V ≤ IOVDD ≤ 1.9V、動作時周囲温度範囲全体、OUT\_DRV = 0b、C\_LOAD = 20pF (特に記述のない限り)

| パラメータ                  |                                                       | テスト条件 | 最小値                                                    | 標準値                       | 最大値 | 単位               |

|------------------------|-------------------------------------------------------|-------|--------------------------------------------------------|---------------------------|-----|------------------|

| <b>クロック</b>            |                                                       |       |                                                        |                           |     |                  |

| t <sub>C(CLK)</sub>    | ADC クロック周期 (プログラマブル) <sup>(1)</sup>                   |       | 1、2、3、4 または 8/f <sub>CLKIN</sub> または /f <sub>OSC</sub> |                           |     |                  |

| <b>フレーム同期 (データポート)</b> |                                                       |       |                                                        |                           |     |                  |

| t <sub>c(FSYNC)</sub>  | FSYNC 周期                                              |       | 1 / f <sub>DATA</sub>                                  | ns                        |     |                  |

| t <sub>w(FSYNCH)</sub> | パルス幅、FSYNC high                                       |       | 0.5 / f <sub>DATA</sub>                                | ns                        |     |                  |

| t <sub>w(FSYNCL)</sub> | パルス幅、FSYNC low                                        |       | 0.5 / f <sub>DATA</sub>                                | ns                        |     |                  |

| t <sub>p(FSDC)</sub>   | 伝搬遅延時間、FSYNC 立ち下がりエッジから DCLK 立ち上がりエッジまで               |       | -1                                                     | 1                         | ns  |                  |

| t <sub>c(DCLK)</sub>   | DCLK 周期 (プログラマブル) <sup>(1)</sup>                      |       | 1、2、4、または 8/f <sub>CLKIN</sub> または /f <sub>OSC</sub>   |                           |     |                  |

| t <sub>w(DCLKH)</sub>  | パルス幅、DCLK low                                         |       | 0.5 · t <sub>c(DCLK)</sub>                             | ns                        |     |                  |

| t <sub>w(DCLKL)</sub>  | パルス幅、DCLK high                                        |       | 0.5 · t <sub>c(DCLK)</sub>                             | ns                        |     |                  |

| t <sub>h(DCDO)</sub>   | ホールド時間、DCLK 立ち下がりエッジから前の DOUT 無効まで                    |       | -2                                                     | ns                        |     |                  |

| t <sub>p(DCDO)</sub>   | 伝搬遅延時間、DCLK の立ち下がりエッジから新しい DOUT が有効になるまでの時間           |       | 7                                                      | ns                        |     |                  |

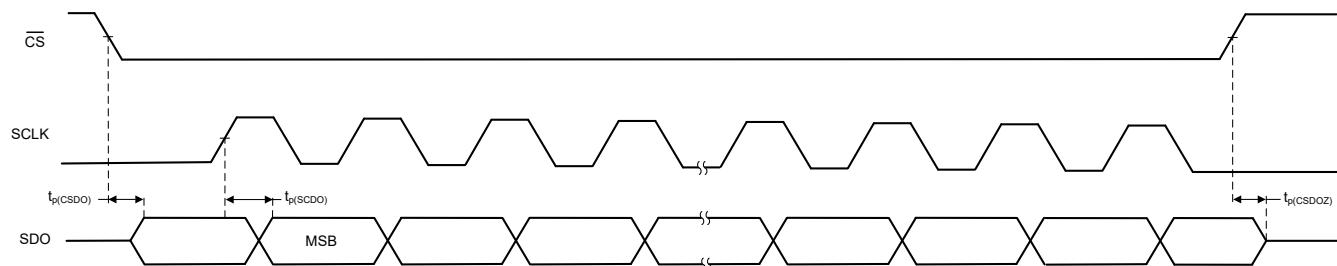

| <b>SPI (構成ポート)</b>     |                                                       |       |                                                        |                           |     |                  |

| t <sub>p(CSDO)</sub>   | 伝搬遅延時間、CS 立ち下がりエッジから SDO 駆動状態まで                       |       |                                                        | 16                        | ns  |                  |

| t <sub>p(CSDOZ)</sub>  | 伝搬遅延時間、CS 立ち上がりエッジから SDO トライステートまで                    |       |                                                        | 16                        | ns  |                  |

| t <sub>p(SCDO)</sub>   | 伝搬遅延時間、SCLK 立ち上がりエッジから有効な SDO まで                      |       |                                                        | 20                        | ns  |                  |

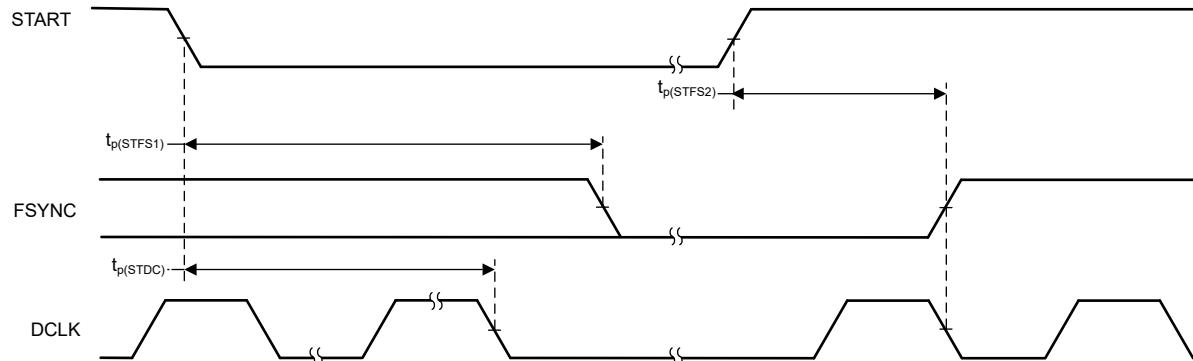

| <b>START ピン</b>        |                                                       |       |                                                        |                           |     |                  |

| t <sub>p(STFS1)</sub>  | 伝搬遅延時間、START 立ち下がりエッジから FSYNC 信号停止まで (スタート/ストップ モード)  |       |                                                        | 11                        | ns  | t <sub>CLK</sub> |

| t <sub>p(STDC)</sub>   | 伝搬遅延時間、START 立ち下がりエッジから DCLK 信号停止まで (スタート/ストップ モード)   |       |                                                        | 7                         | ns  | t <sub>CLK</sub> |

| t <sub>p(STFS2)</sub>  | 伝搬遅延時間、START 立ち上がりエッジから FSYNC 立ち上がりエッジ (最初の変換準備完了) まで |       |                                                        | 「デジタル フィルタ」セクションを参照してください |     |                  |

| <b>RESET ピン</b>        |                                                       |       |                                                        |                           |     |                  |

| t <sub>p(RSFS)</sub>   | 伝搬遅延時間、RESET 立ち上がりエッジから FSYNC 立ち下がりエッジまで (ADC 準備完了)   |       |                                                        | 10 <sup>4</sup>           | ns  | t <sub>CLK</sub> |

(1) デイジー チェーン接続には外部クロック動作が必要で、CLK\_DIV[2:0]、DCLK\_DIV[1:0]= 1 分周が必要です。

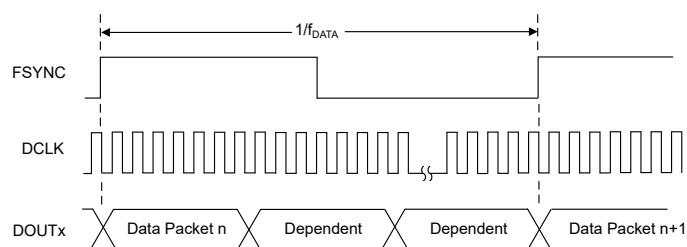

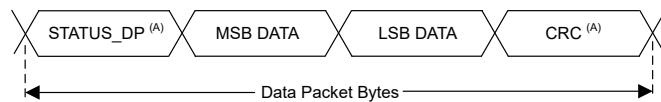

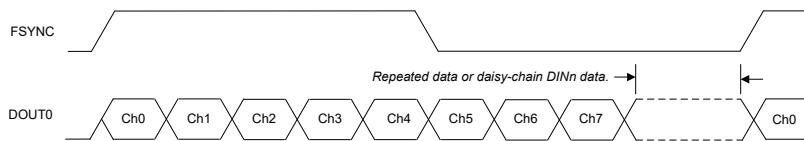

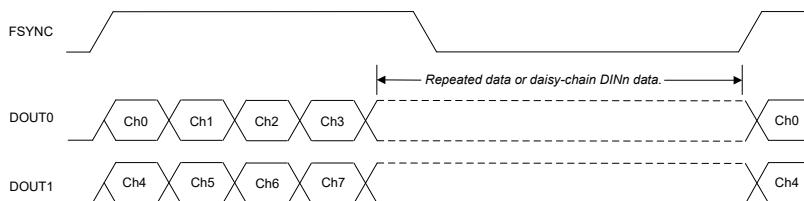

## 5.8 タイミング図

図 5-1. クロックのタイミング要件

図 5-2. フレーム同期ポートのスイッチング特性

図 5-3. SPI のタイミング要件

図 5-4. SPI スイッチング特性

図 5-5. START ピンのタイミング要件

図 5-6. START ピンのスイッチング特性

図 5-7. RESET ピンのタイミング要件およびスイッチング特性

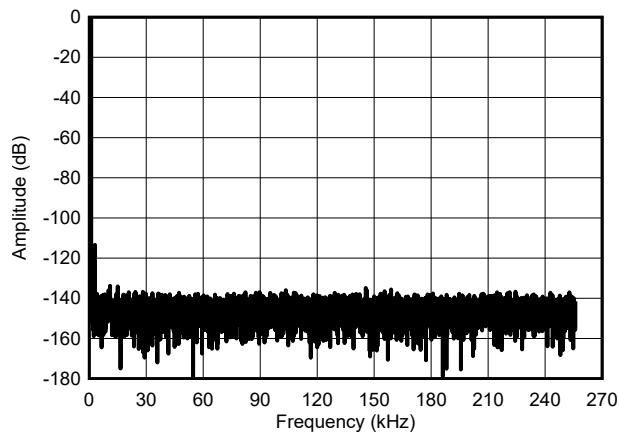

## 5.9 代表的特性

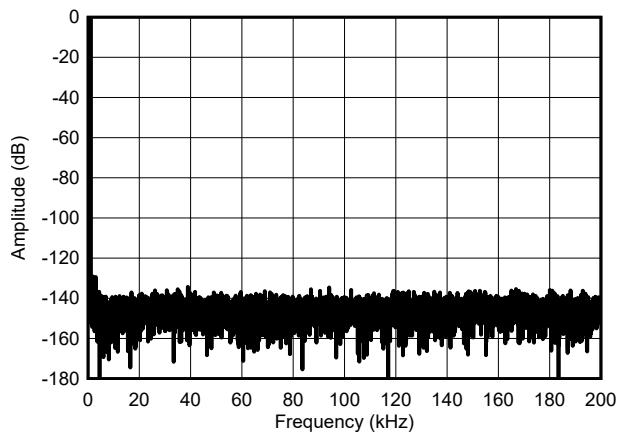

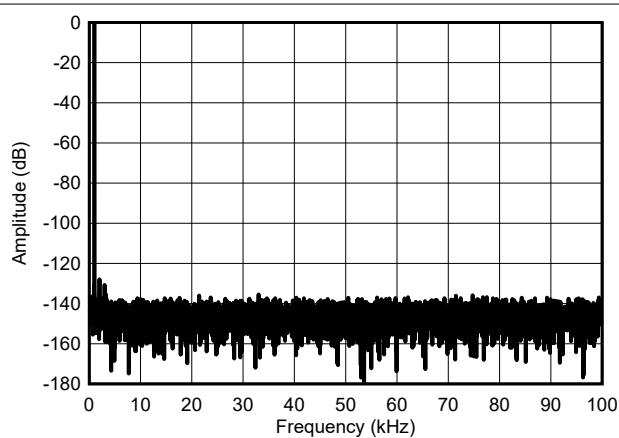

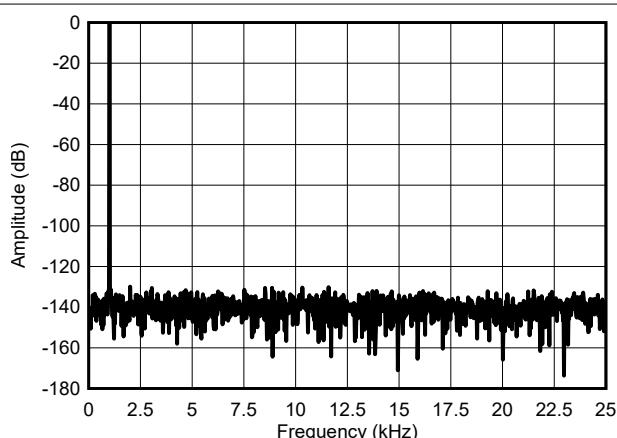

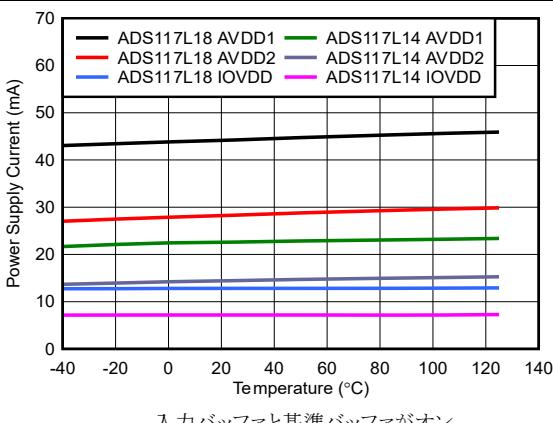

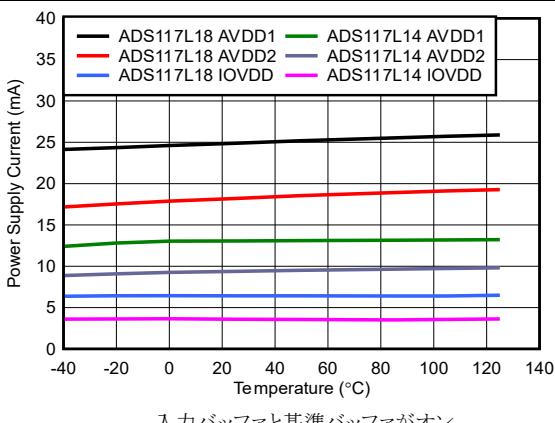

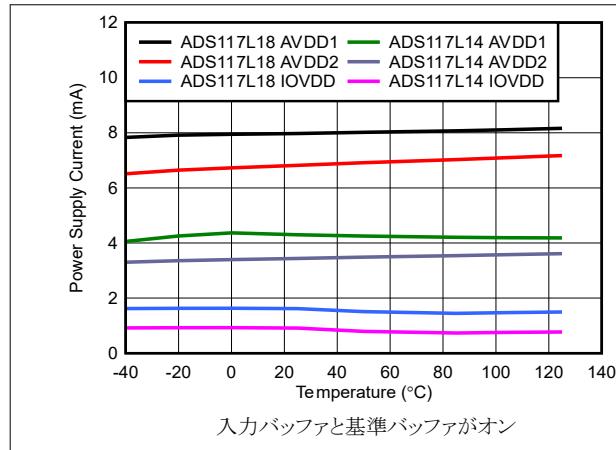

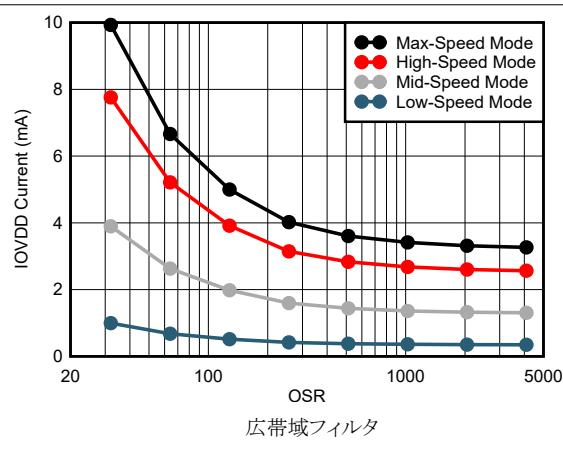

AVDD1 = AVDD2 = 1.8V、AVSS = 0V、IOVDD = 1.8V、 $V_{REF} = 4.096V$ 、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージ バッファがオフ、 $T_A = 25^{\circ}\text{C}$ 、データは典型的なチャネルパフォーマンスを表すとき (特に記述のない限り)。

図 5-8. 最高速度モード、フルスケール FFT

図 5-9. 高速度モード、フルスケール FFT

図 5-10. 中速度モード、フルスケール FFT

図 5-11. 低速度モード、フルスケール FFT

## 5.9 代表的特性 (続き)

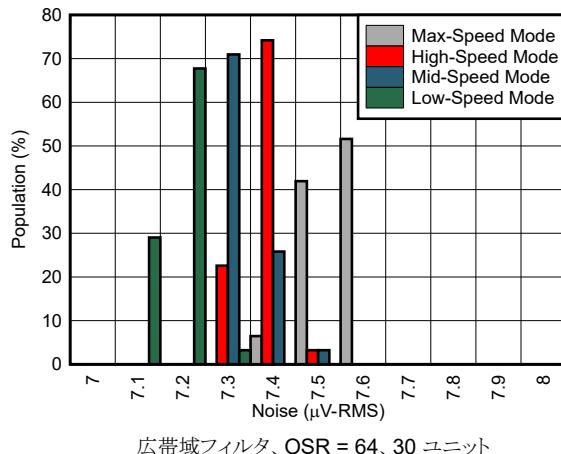

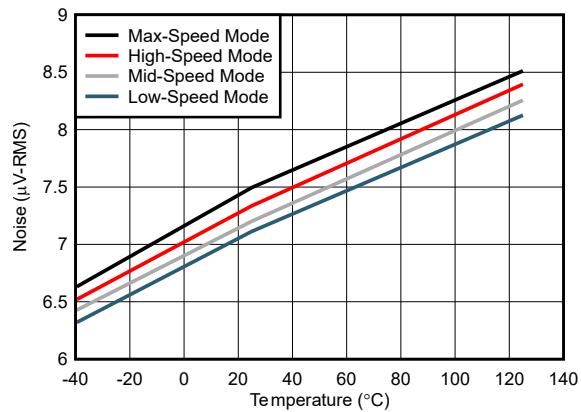

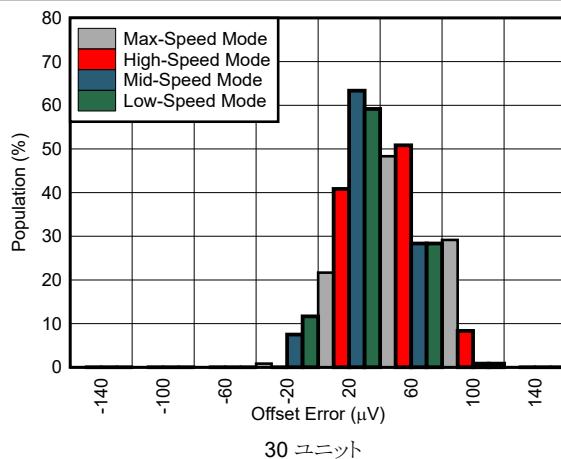

AVDD1 = AVDD2 = 1.8V、AVSS = 0V、IOVDD = 1.8V、 $V_{REF} = 4.096V$ 、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージ バッファがオフ、 $T_A = 25^{\circ}\text{C}$ 、データは典型的なチャネルパフォーマンスを表すとき (特に記述のない限り)。

図 5-12. ノイズヒストグラム

図 5-13. ノイズと温度との関係

図 5-14. オフセット電圧のヒストグラム

図 5-15. オフセット電圧ドリフトのヒストグラム

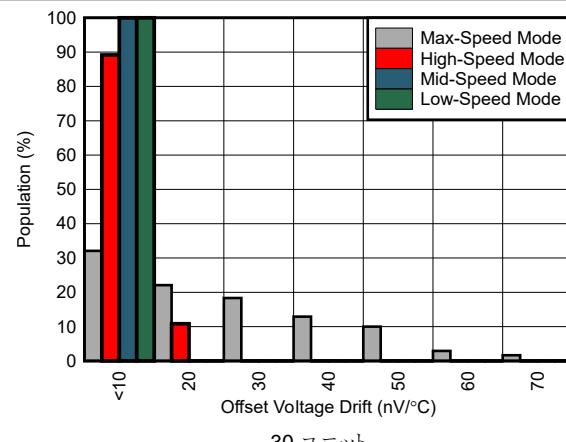

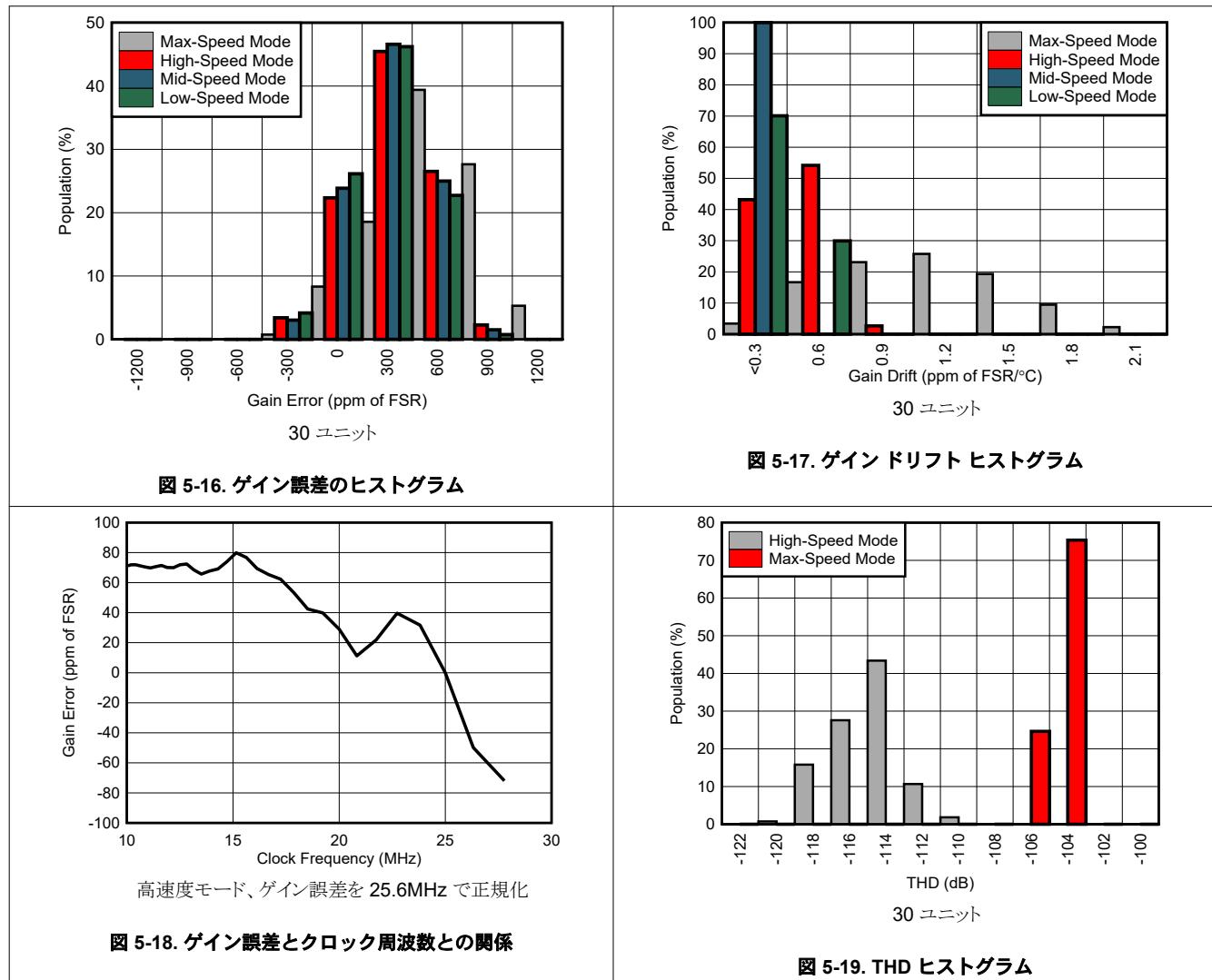

## 5.9 代表的特性 (続き)

AVDD1 = AVDD2 = 1.8V、AVSS = 0V、IOVDD = 1.8V、 $V_{REF} = 4.096V$ 、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージ バッファがオフ、 $T_A = 25^\circ C$ 、データは典型的なチヤネルパフォーマンスを表すとき (特に記述のない限り)。

## 5.9 代表的特性 (続き)

AVDD1 = AVDD2 = 1.8V、AVSS = 0V、IOVDD = 1.8V、 $V_{REF} = 4.096V$ 、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージ バッファがオフ、 $T_A = 25^{\circ}\text{C}$ 、データは典型的なチヤネルパフォーマンスを表すとき (特に記述のない限り)。

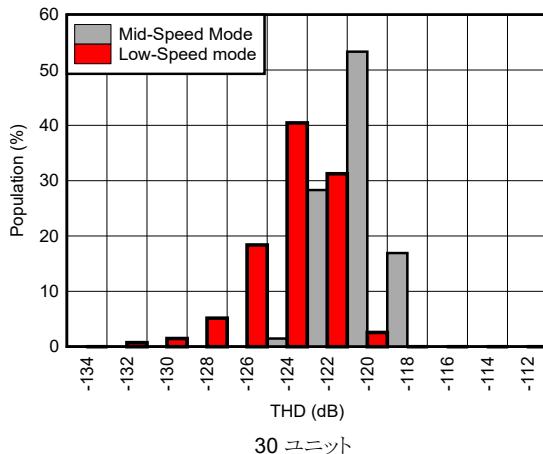

図 5-20. THD ヒストグラム

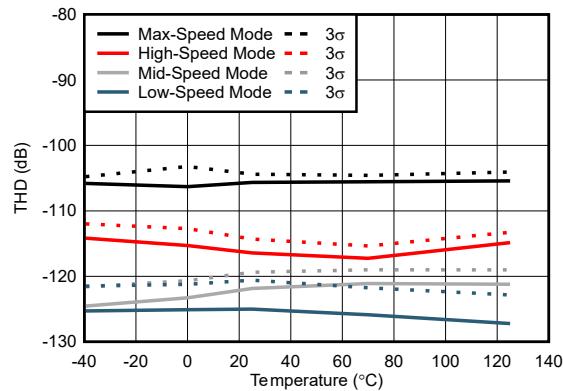

図 5-21. THD と温度との関係

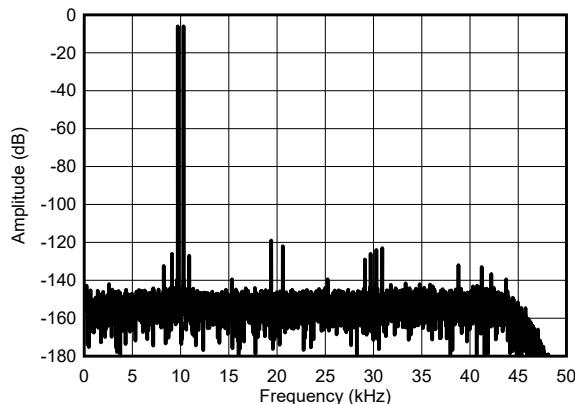

図 5-22. IMD FFT

図 5-23. INL と入力電圧との関係

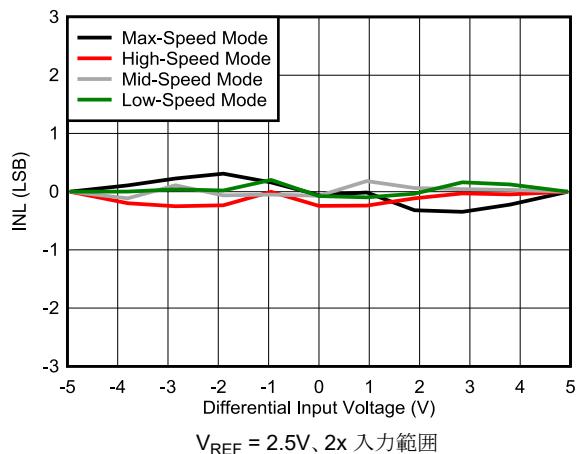

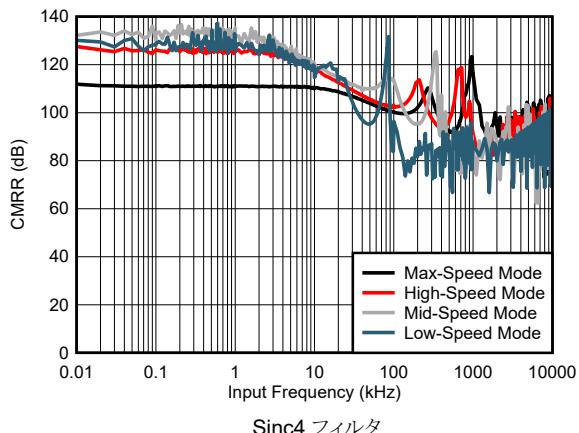

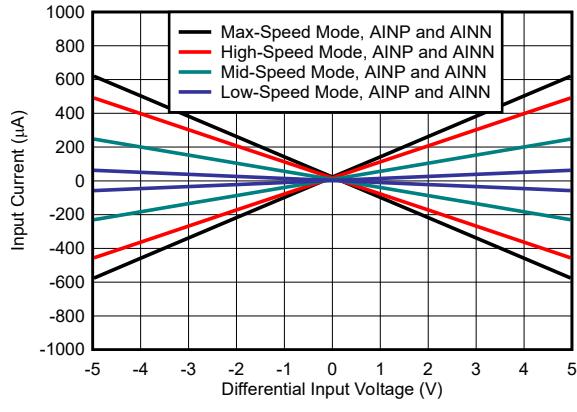

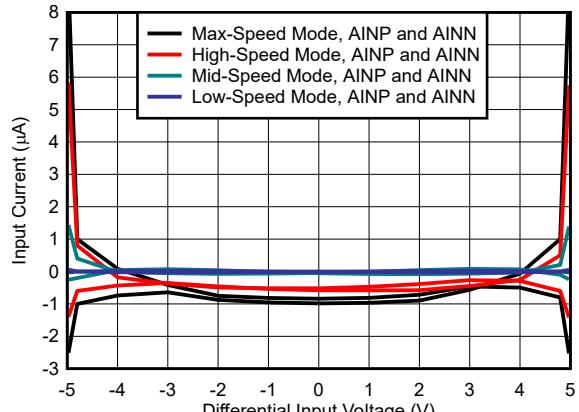

## 5.9 代表的特性 (続き)

AVDD1 = AVDD2 = 1.8V, AVSS = 0V, IOVDD = 1.8V,  $V_{REF} = 4.096V$ , 高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージ バッファがオフ、 $T_A = 25^\circ C$ 、データは典型的なチャネルパフォーマンスを表すとき (特に記述のない限り)。

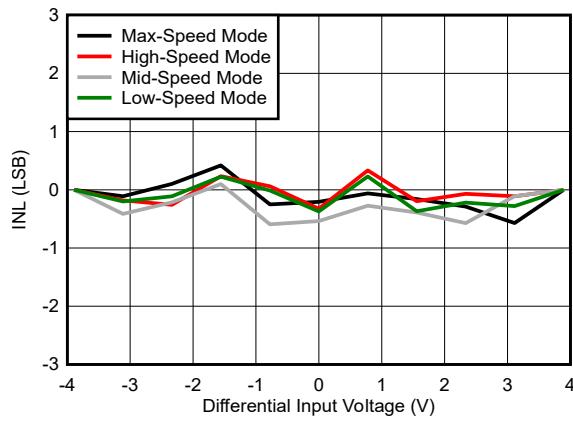

図 5-24. INL と入力電圧との関係

図 5-25. CMRR と周波数との関係

図 5-26. 入力電流と入力電圧との関係

図 5-27. 入力電流と入力電圧との関係

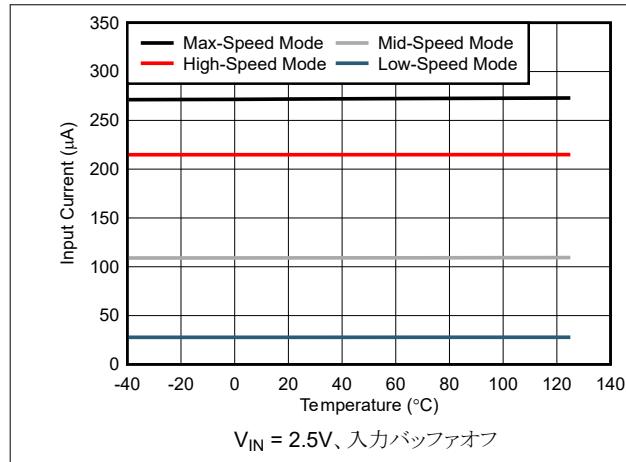

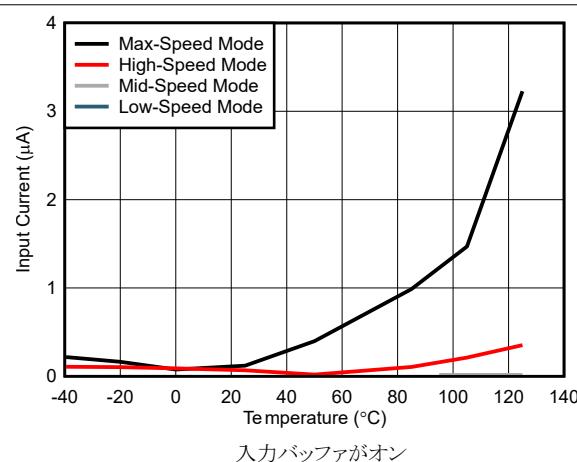

## 5.9 代表的特性 (続き)

AVDD1 = AVDD2 = 1.8V、AVSS = 0V、IOVDD = 1.8V、 $V_{REF} = 4.096V$ 、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンスプリチャージバッファがオフ、 $T_A = 25^{\circ}\text{C}$ 、データは典型的なチヤネルパフォーマンスを表すとき (特に記述のない限り)。

図 5-28. 入力電流と温度の関係

図 5-29. 入力電流と温度の関係

図 5-30. REFP 入力電流とリファレンス電圧との関係

図 5-31. REFP 入力電流とリファレンス電圧との関係

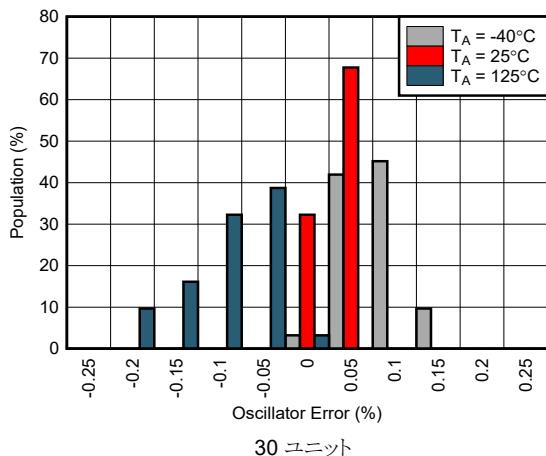

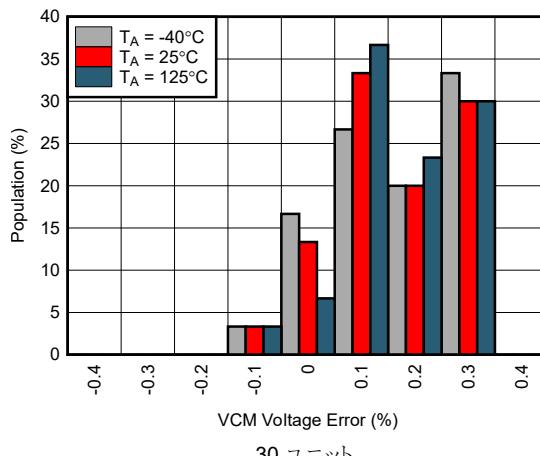

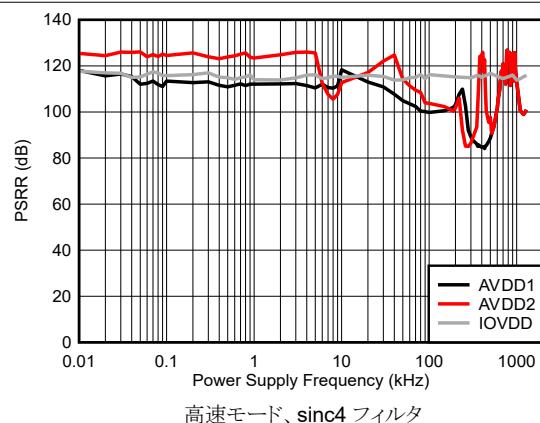

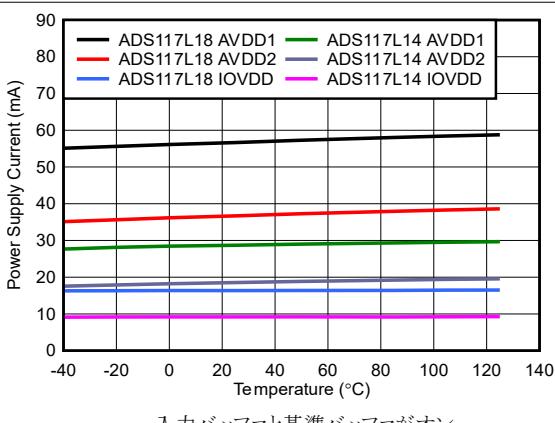

## 5.9 代表的特性 (続き)

AVDD1 = AVDD2 = 1.8V, AVSS = 0V, IOVDD = 1.8V, V<sub>REF</sub> = 4.096V、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージバッファがオフ、T<sub>A</sub> = 25°C、データは典型的なチャネルパフォーマンスを表すとき (特に記述のない限り)。

図 5-32. 発振器の周波数ヒストグラム

図 5-33. VCM 出力電圧ヒストグラム

図 5-34. PSRR と電源周波数との関係

図 5-35. 最高速度モード電源電流と温度との関係

図 5-36. 高速モード電源電流と温度との関係

図 5-37. 中速度モード電源電流と温度との関係

## 5.9 代表的特性 (続き)

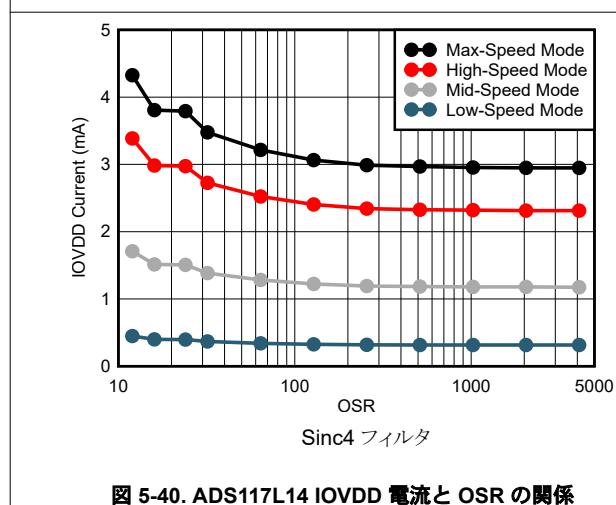

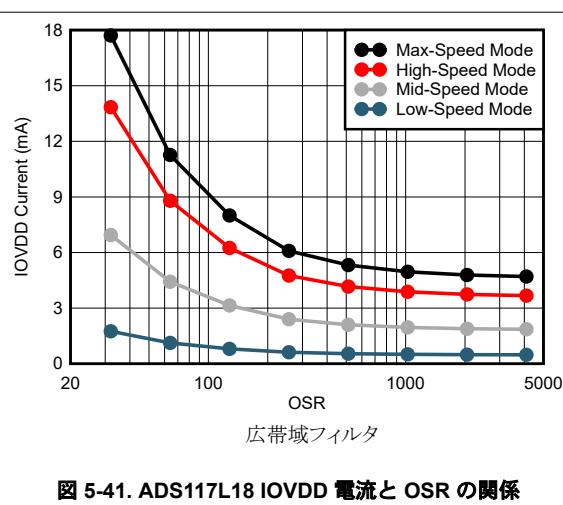

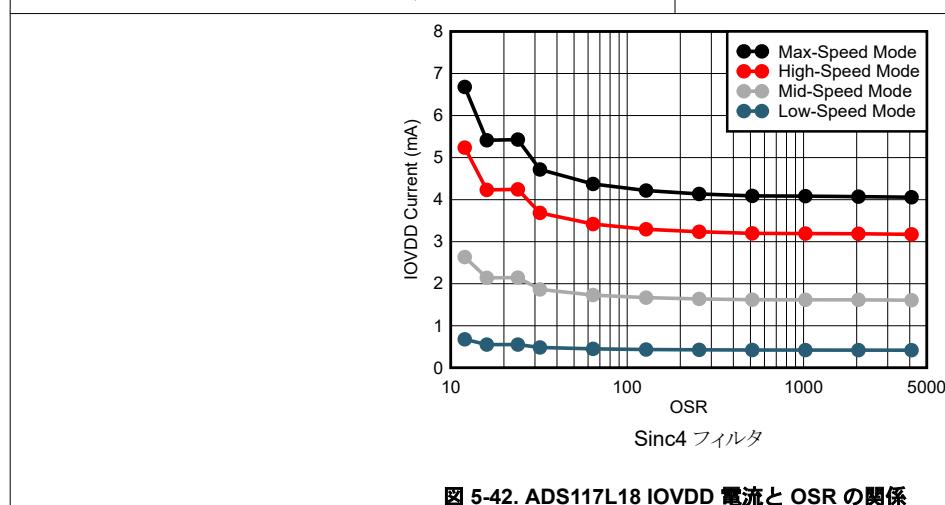

AVDD1 = AVDD2 = 1.8V、AVSS = 0V、IOVDD = 1.8V、 $V_{REF} = 4.096V$ 、高リファレンス範囲、高速度モード、広帯域フィルタ、OSR = 32、1x の入力範囲、入力プリチャージバッファがオン、リファレンス プリチャージ バッファがオフ、 $T_A = 25^{\circ}\text{C}$ 、データは典型的なチャネルパフォーマンスを表すとき (特に記述のない限り)。

図 5-38. 低速モード電源電流と温度との関係

図 5-39. ADS117L14 IOVDD 電流と OSR の関係

図 5-40. ADS117L14 IOVDD 電流と OSR の関係

図 5-41. ADS117L18 IOVDD 電流と OSR の関係

図 5-42. ADS117L18 IOVDD 電流と OSR の関係

## 6 パラメータ測定情報

### 6.1 オフセット誤差の測定

オフセット誤差は、ADC 入力が外部で短絡した状態で測定されます。入力同相電圧は、AVDD1 および AVSS 電源電圧範囲の中間点に固定されています。オフセット誤差は、 $T_A = 25^\circ\text{C}$ で規定されています。

### 6.2 オフセット ドリフトの測定

オフセットドリフトは、指定された温度範囲全体にわたって複数のポイントで測定される、オフセット電圧の変化として定義されます。オフセットドリフトは ボックス方式を使用して計算され、指定された温度範囲内で最大と最小のオフセット電圧を囲むボックスが形成されます。このボックス方式では、温度誤差の限界が規定されますが、テスト対象となるデバイスの測定結果について、正確な形状とスロープは規定されません。ボックス方式を使用したオフセットドリフトの計算を、式 1 に示します。

$$\text{Offset Drift (nV/}^\circ\text{C)} = 10^9 \cdot (V_{\text{OFSMAX}} - V_{\text{OFSMIN}}) / (T_{\text{MAX}} - T_{\text{MIN}}) \quad (1)$$

ここで

- $V_{\text{OFSMAX}}$  および  $V_{\text{OFSMIN}}$ =指定された温度範囲内での最大と最小のオフセット電圧

- $T_{\text{MAX}}$  と  $T_{\text{MIN}}$ =最高と最低の温度

### 6.3 ゲイン誤差の測定

ゲイン誤差は、ADC 伝達関数の実際のスロープと理想的なスロープとの差として定義されます。ゲイン誤差は、DC テスト電圧を FSR の -95% と 95% で印加して測定します。誤差は、DC テスト電圧 (理想的なスロープ) の変化を、ADC 出力電圧 (実際のスロープ) の変化から減算して計算されます。スロープの差を理想的なスロープで除算し、 $10^6$  を掛けて、誤差を FSR の ppm に変換します。ADC リファレンス電圧に起因する誤差は、ゲイン誤差の測定から除外されます。ゲイン誤差は、 $T_A = 25^\circ\text{C}$ で規定されます。ゲイン誤差の計算を、式 2 に示します。

$$\text{Gain Error (ppm of FSR)} = 10^6 \cdot (\Delta V_{\text{OUT}} - \Delta V_{\text{IN}}) / \Delta V_{\text{IN}} \quad (2)$$

ここで

- $\Delta V_{\text{OUT}}$ =2 つの ADC 出力電圧の差

- $\Delta V_{\text{IN}}$ =2 つの入力テスト電圧の差

### 6.4 ゲイン ドリフトの測定

ゲインドリフトは、指定された温度範囲全体にわたって複数のポイントで測定される、ゲイン誤差の変化として定義されます。ボックス方式が使用され、指定された温度範囲内で最大と最小のゲイン誤差を囲むボックスが形成されます。このボックス方式では、温度誤差の限界が規定されますが、テスト対象となるデバイスの測定結果について、正確な形状とスロープは規定されません。ボックス方式を使用したオフセットドリフトの計算を、式 3 に説明されます。

$$\text{Gain Drift (ppm/}^\circ\text{C)} = (G_{\text{E}}_{\text{MAX}} - G_{\text{E}}_{\text{MIN}}) / (T_{\text{MAX}} - T_{\text{MIN}}) \quad (3)$$

ここで

- $G_{\text{E}}_{\text{MAX}}$  と  $G_{\text{E}}_{\text{MIN}}$ =指定された温度範囲における最大と最小のゲイン誤差

- $T_{\text{MAX}}$  と  $T_{\text{MIN}}$ =最高と最低の温度

### 6.5 NMRR の測定

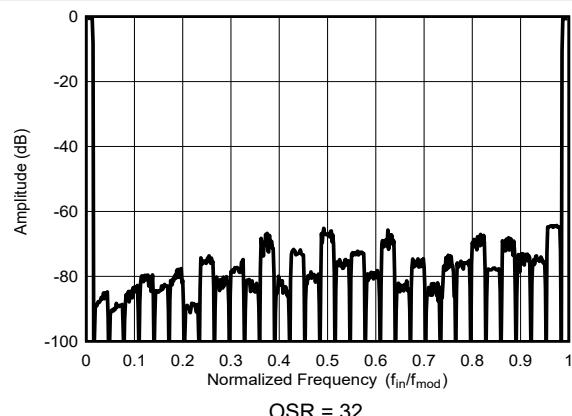

ノーマル モード除去比 (NMRR) は、ADC が特定の周波数でノーマル モードの入力信号を除去する能力を規定しています。これらの出力周波数は、通常、50Hz および 60Hz について示されます。ノーマル モード除去は、デジタル フィルタの周波数応答によって一意に決定されます。この場合、低レイテンシの sinc3 フィルタ オプションの周波数応答のヌルは 50Hz と 60Hz に配置され、これらの周波数で除去を行います。

## 6.6 CMRR の測定

CMRR (同相除去比) は、ADC が同相入力信号をどの程度除去できるのかを示すものです。CMRR は、DC および AC パラメータとして表されます。CMRR (DC) を測定するには、外部で互いに短絡した入力に 3 つの同相テスト電圧を印加します。これらのテスト電圧は、AVSS + 50mV、(AVDD1 + AVSS)/2、および AVDD1 - 50mV と等しくなります。同相テスト電圧の変化に対する、ADC オフセット電圧の最大の変化を記録します。CMRR (DC) の計算方法を、式 4 に示します。

$$\text{CMRR (dc) (dB)} = 20 \cdot \log(\Delta V_{\text{CM}} / \Delta V_{\text{OS}}) \quad (4)$$

ここで

- $\Delta V_{\text{CM}}$  = DC 同相テスト電圧の変化

- $\Delta V_{\text{OS}}$  = 対応するオフセット電圧の変化

CMRR (AC) を測定するには、フルスケール範囲の 95% のさまざまなテスト周波数で AC 同相信号を印加します。FFT は、同相信号が印加されたときの ADC データから計算されます。式 5 は、周波数スペクトル内で振幅の大きい 9 つのスプリアス周波数について、電力の合計を示しています。これらの周波数は、同相テスト信号の振幅に関係しています。

$$\text{CMRR (ac) (dB)} = 20 \cdot \log(V_{\text{CM}} / V_{\text{O}}) \quad (5)$$

ここで

- $V_{\text{CM}} (\text{RMS})$  = 同相入力信号の振幅

- $V_{\text{O}} (\text{RMS})$  = スプリアス周波数の 2 乗和平方根の振幅 =  $\sqrt{(V_0^2 + V_1^2 + \dots + V_8^2)}$

## 6.7 PSRR の測定

電源除去比 (PSRR) は、ADC が電源との干渉をどの程度除去できるかを示します。PSRR は AC および DC パラメータとして表されます。PSRR (DC) を測定するには、外部で入力を短絡させた状態で、電源電圧を最小、公称、最大の規定電圧範囲で変化させます。電源電圧の変化に対する、ADC オフセット電圧の最大の変化を記録します。PSRR (DC) は、式 6 に示すように、電源電圧ステップの変化とオフセット電圧の変化との比率として計算されます。

$$\text{PSRR (dc) (dB)} = 20 \cdot \log(\Delta V_{\text{PS}} / \Delta V_{\text{OS}}) \quad (6)$$

ここで

- $\Delta V_{\text{PS}}$  = 電源電圧の変化

- $\Delta V_{\text{OS}}$  = オフセット電圧の変化

PSRR (AC) を測定するため、電源電圧がさまざまなテスト周波数で、100mVpp (35mVRMS) 信号によって変調されます。電源変調による ADC データの FFT が実行されます。式 7 は、周波数スペクトル内で振幅の大きい 9 つのスプリアス周波数について、電力の合計を示しています。これらの周波数は、電源変調信号の振幅にも関係しています。

$$\text{PSRR (ac) (dB)} = 20 \cdot \log(V_{\text{PS}} / V_{\text{O}}) \quad (7)$$

ここで

- $V_{\text{PS}} (\text{RMS})$  = 35mV の AC 電源変調信号

- $V_{\text{O}} (\text{RMS})$  = スプリアス周波数の 2 乗和平方根の振幅 =  $\sqrt{(V_0^2 + V_1^2 + \dots + V_8^2)}$

## 6.8 SNR の測定

信号対雑音比 (SNR) は、フルスケールの AC 入力信号でのノイズ性能の測定値です。SNR の測定では、 $V_{CM}$  = 中間電源電圧で、-0.2dBFS、1kHz のテスト信号を使用します。[式 8](#) に示すように、SNR は入力信号の RMS 値と、ADC 出力サンプルの FFT 結果から求められた、他のすべての周波数成分の 2 乗和平方根との比です。元の信号の DC および高調波は、SNR 計算から除外されます。非コヒーレント サンプリングのために FFT ウィンドウ関数が使用される場合、元の信号の周囲のスペクトル漏れビンが削除され、SNR が計算されます。

$$\text{SNR (dB)} = 20 \cdot \log(V_{IN} / e_n) \quad (8)$$

ここで

- $V_{IN}$  = 入力テスト信号

- $e_n$  = DC および信号高調波を除く周波数成分の 2 乗和平方根

## 6.9 INL 誤差の測定

積分非直線性 (INL) 誤差は、ADC の DC 伝達関数の直線性を示します。INL は、ADC の入力範囲全体にわたって一連の DC テスト電圧を印加することで測定されます。INL は、DC テスト電圧  $[V_{IN(N)}]$  の組と、ADC のスロープおよびオフセット伝達関数から計算された対応する出力電圧  $[V_{OUT(N)}]$  の組との差です。INL 誤差を計算するエンドポイント方式を、[式 9](#) に示します。

$$\text{INL (LSB)} = \text{Maximum of test voltage series } [2^{16} \cdot |V_{IN(N)} - V_{OUT(N)}| / \text{FSR}] \quad (9)$$

ここで

- $N$  = DC テスト電圧のインデックス

- $[V_{IN(N)}]$  = 入力範囲の -95%~95% にわたるテスト電圧の組

- $[V_{OUT(N)}]$  = 対応する ADC 出力電圧の組

- FSR (フルスケール範囲) =  $2 \cdot V_{REF}$  (1x 入力範囲) または  $4 \cdot V_{REF}$  (2x 入力範囲)

INL の最適化手法では、最小 2 乗誤差 (LSE) の計算を使用して新しい直線を決定します。この線により、元のエンドポイント線の上下にある INL 誤差の 2 乗和平方根を最小化できます。

## 6.10 THD の測定

全高調波歪み (THD) は、AC 入力信号を使用する ADC の動的直線性を規定します。THD の測定では、 $V_{CM}$  = 中間電源電圧で、-0.2dBFS、1kHz 差動の入力信号が適用されます。十分な数のデータ ポイントを収集して、周波数ビンの幅が 5Hz 以下の FFT 結果を生成します。5Hz のビン幅により、高調波ビンのノイズが低減され、一貫した THD 測定が可能になります。[式 10](#) に示すように、THD は入力信号振幅に対する高調波の 2 乗和平方根振幅の比として計算されます。

$$\text{THD (dB)} = 20 \cdot \log(V_H / V_{IN}) \quad (10)$$

ここで

- $V_H$  = 高調波の 2 乗和平方根:  $\sqrt{(V_2^2 + V_3^2 + \dots + V_n^2)}$ 、ここで  $V_n$  = 9 次高調波電圧

- $V_{IN}$  = 入力信号の基本波

## 6.11 IMD の測定

相互変調歪み (IMD) は、2つの入力信号の混合効果を規定します。信号の混合は ADC の非直線性に起因し、元の信号にはない新しい和および差の周波数が発生することがあります。IMD の 2 次項は、 $(f_1 + f_2)$  および  $(f_1 - f_2)$  です。IMD の 3 次項は、 $(2f_1 + f_2)$ 、 $(2f_1 - f_2)$ 、 $(f_1 + 2f_2)$ 、および  $(f_1 - 2f_2)$  です。テスト信号  $f_1 = 9.7\text{kHz}$  および  $f_2 = 10.3\text{kHz}$  は、-6.5dBFS です。[式 11](#) に、IMD 計算を示します。

$$\begin{aligned} \text{IMD}_2 (\text{dB}) &= 20 \cdot \log(V_2 / V_{\text{IN}}) \\ \text{IMD}_3 (\text{dB}) &= 20 \cdot \log(V_3 / V_{\text{IN}}) \end{aligned} \quad (11)$$

ここで

- $\text{IMD}_2$  = 2 次 IMD

- $\text{IMD}_3$  = 3 次 IMD

- $V_2$  = 2 次項の二乗和平方根

- $V_3$  = 3 次項の二乗和平方根

- $V_{\text{IN}}$  = 入力テスト信号の合計振幅

## 6.12 SFDR の測定

スプリアス フリー ダイナミック レンジ (SFDR) は、シングルトーン AC 入力の RMS 値と、ADC 周波数スペクトル内で最大のスプリアス信号との比です。SFDR の測定結果には、元の信号の高調波が含まれます。SFDR の測定では、 $V_{\text{CM}}$  = 中間電源電圧で、-0.2dBFS、1kHz の入力信号を印加します。[式 12](#) に示すように、SFDR は、入力信号の RMS 値と、元の信号の高調波を含む、单一の最も大きいスプリアス信号との比です。

$$\text{SFDR} (\text{dB}) = 20 \cdot \log(V_{\text{IN}} / V_{\text{SPUR}}) \quad (12)$$

ここで

- $V_{\text{IN}}$  = 入力テスト信号

- $V_{\text{SPUR}}$  = 単一の最大スプリアスのレベル

## 6.13 ノイズ性能

ADC にはプログラム可能な OSR 付きの 4 つの速度モードがあり、消費電力と帯域幅の間でトレードオフを選択できます。モードには最高速度、高速度、中速度、低速度があり、このレベルにデバイスの消費電力と信号帯域幅が減少します。

ADC 入力が短絡した場合、出力コードは単一の値、または 2 つ以上の値の間のフリッカー コードになります。コードフリッカーは、選択した OSR 値に対応する ADC ノイズと、次のコード遷移に対する DC 信号に依存します。ADC のピークツーピークノイズ値は通常、RMS ノイズ値の 6.6 倍です。コードフリッカーは、ノイズの振幅がコード遷移を引き起こすのに十分な大きさである場合に発生します。

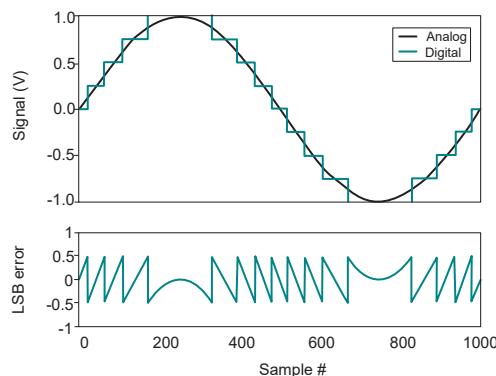

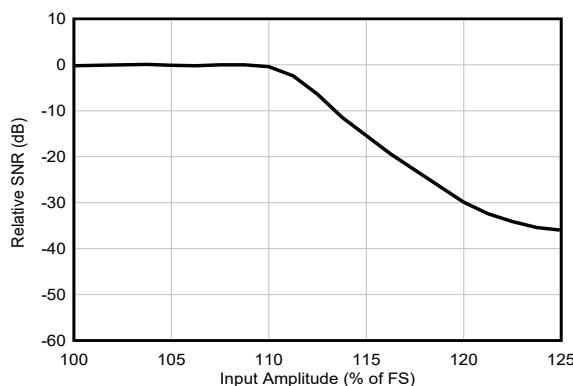

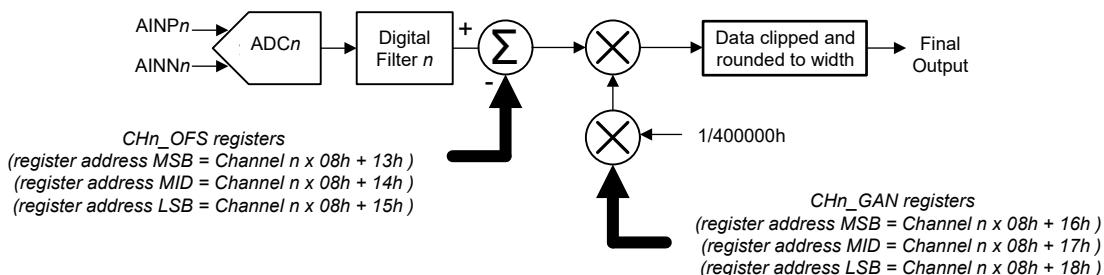

ADC の量子化誤差は  $\pm 0.5 \text{ LSB}$  です。ac 信号の場合、量子化誤差は量子化ノイズになります。**図 6-1** に、信号が変化すると、ノイズへの変換時量子化誤差 (LSB 誤差プロット) を示します。非コヒーレントサンプリングの場合、この量子化ノイズはホワイトノイズとして近似され、周波数帯域全体に均等に拡散されます。N ビット ADC の場合、信号対量子化ノイズ比 (SQNR) は次のとおりです。SQNR (dB) =  $6.02 \times N + 1.76$ 。16 ビット ADC の場合、SQNR は 98.1dB です。

**図 6-1. 正弦波入力の量子化ノイズ**

ノイズ特性の要約を、**表 6-1** から **表 6-5** までに示します。表の SNR 値は、RMS フルスケール範囲と、ADC 热ノイズおよび 16 ビット量子化ノイズの結果の 2 乗和平方根の比で計算されます。このデバイスでは、量子化ノイズの値は通常、熱ノイズより大きいため、OSR 値が大きくなると SNR は 98.1dB に制限されます。

**表 6-1. 広帯域フィルタのノイズ性能 ( $V_{REF} = 4.096\text{V}$ 、1x の入力範囲)**

| モード  | $f_{CLK}$ (MHz) | OSR | データレート (kSPS) | ノイズ ( $e_n, \mu V_{RMS}$ ) | SNR (dB) |

|------|-----------------|-----|---------------|----------------------------|----------|

| 最高速度 | 32.768          | 32  | 512           | 10.9                       | 97.7     |

| 高速   | 25.6            |     | 400           | 10.8                       | 97.7     |

| 中速度  | 12.8            |     | 200           | 10.5                       | 97.8     |

| 低速度  | 3.2             |     | 50            | 10.4                       | 97.8     |

| 最高速度 | 32.768          | 64  | 256           | 7.48                       | 97.9     |

| 高速   | 25.6            |     | 200           | 7.33                       | 97.9     |

| 中速度  | 12.8            |     | 100           | 7.21                       | 97.9     |

| 低速度  | 3.2             |     | 25            | 7.17                       | 97.9     |

| 最高速度 | 32.768          | 128 | 128           | 5.17                       | 98.0     |

| 高速   | 25.6            |     | 100           | 5.14                       | 98.0     |

| 中速度  | 12.8            |     | 50            | 5.02                       | 98.0     |

| 低速度  | 3.2             |     | 12.5          | 5.02                       | 98.0     |

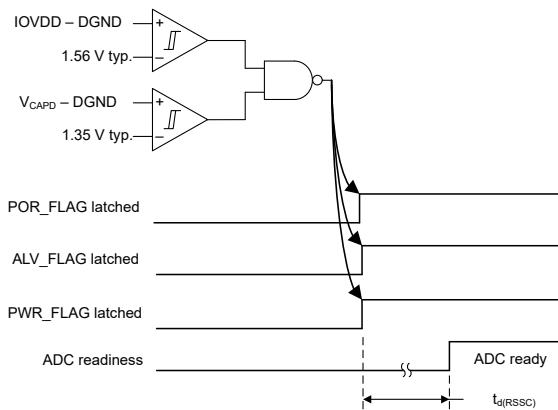

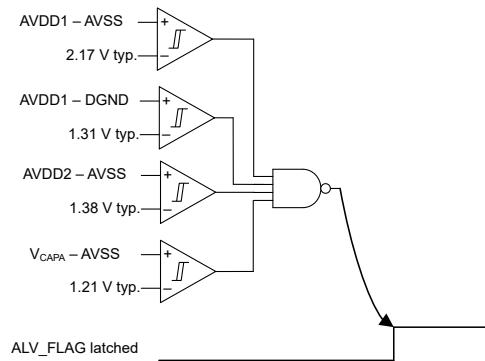

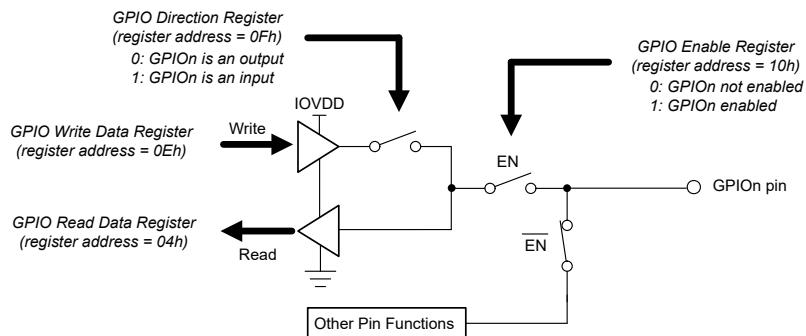

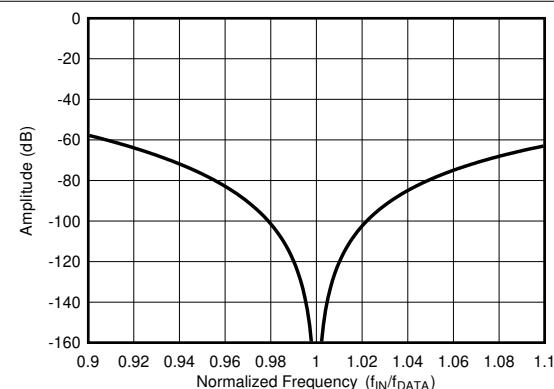

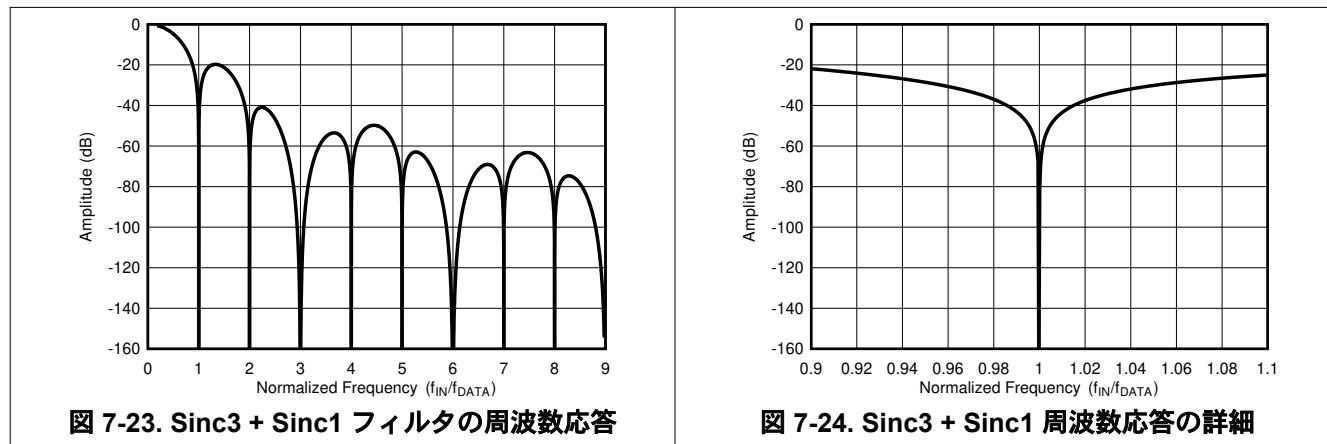

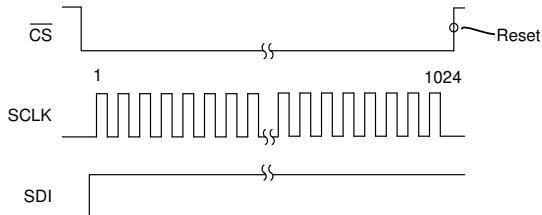

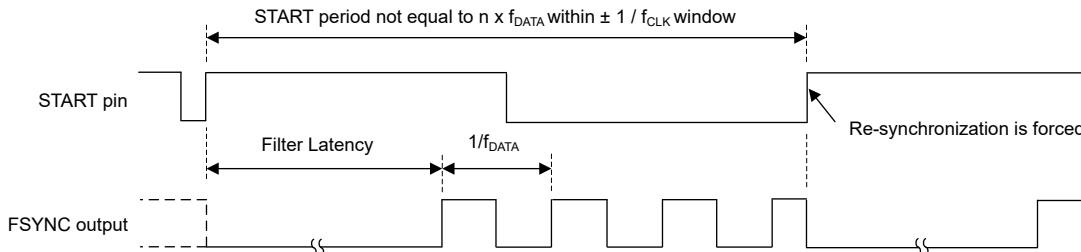

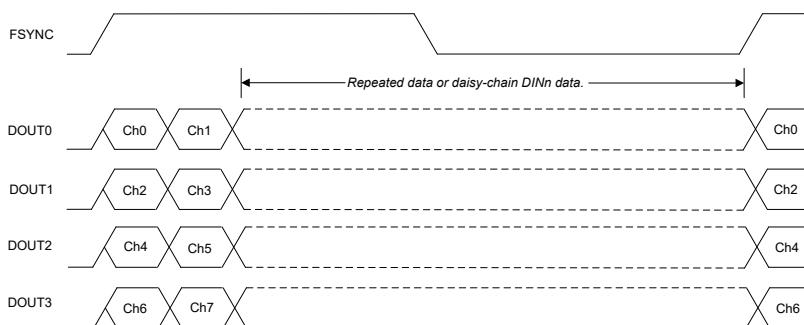

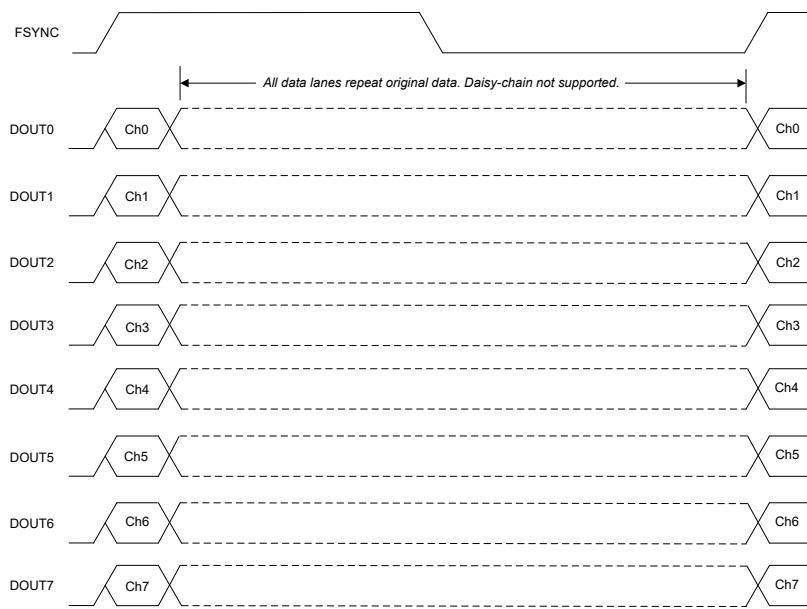

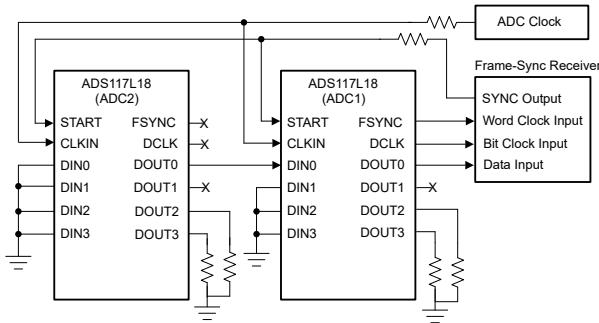

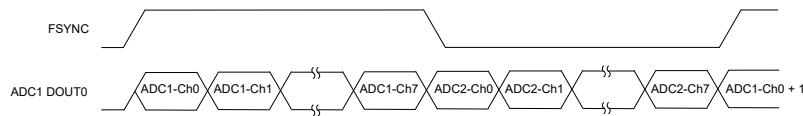

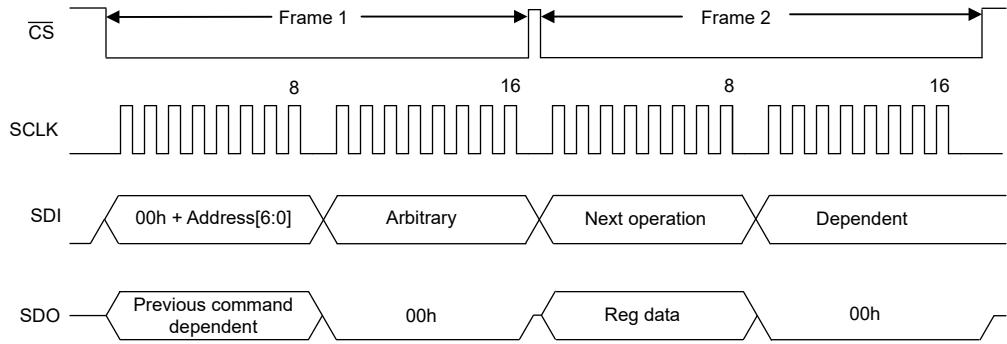

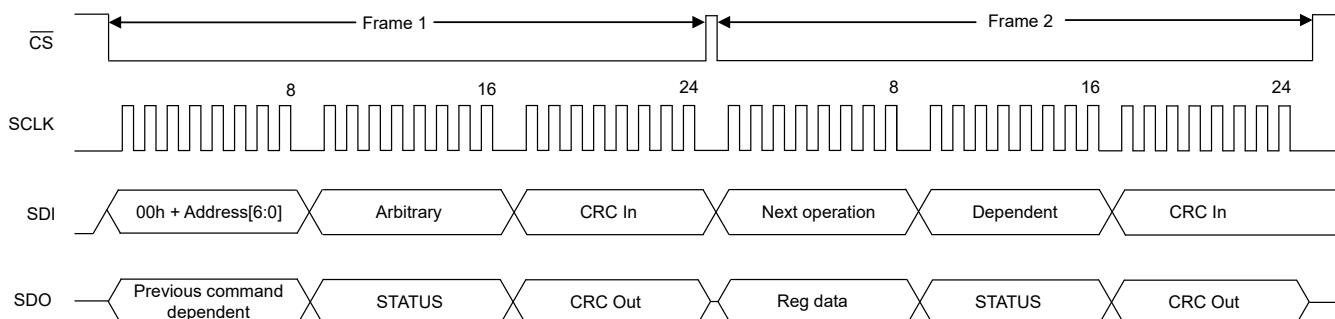

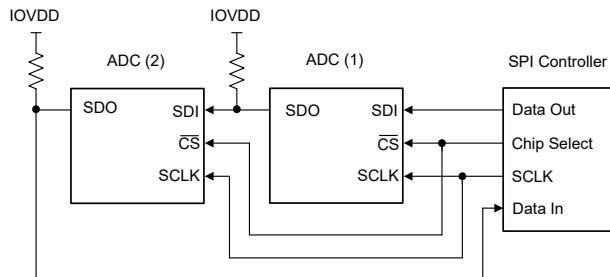

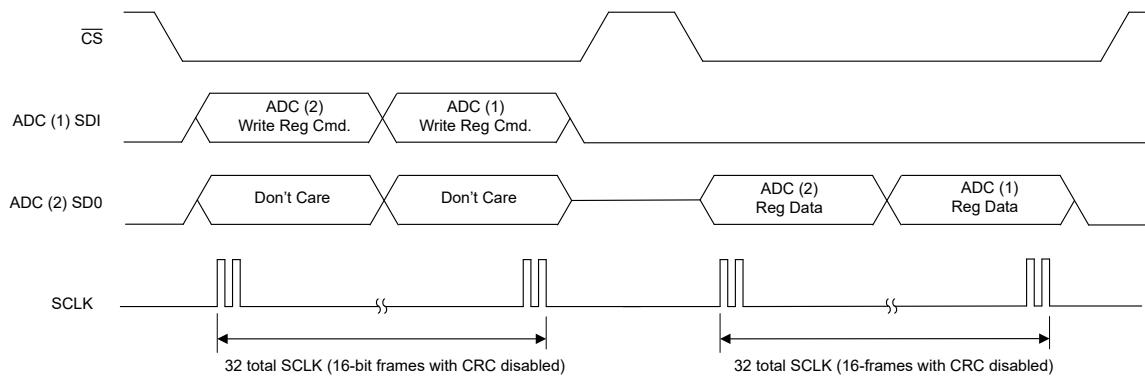

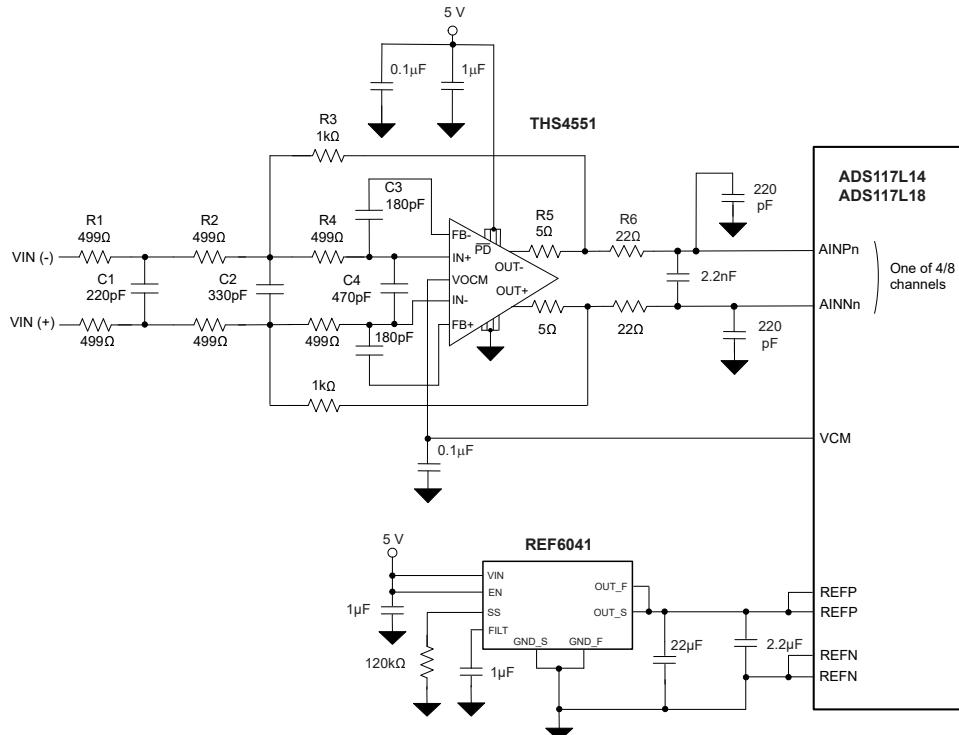

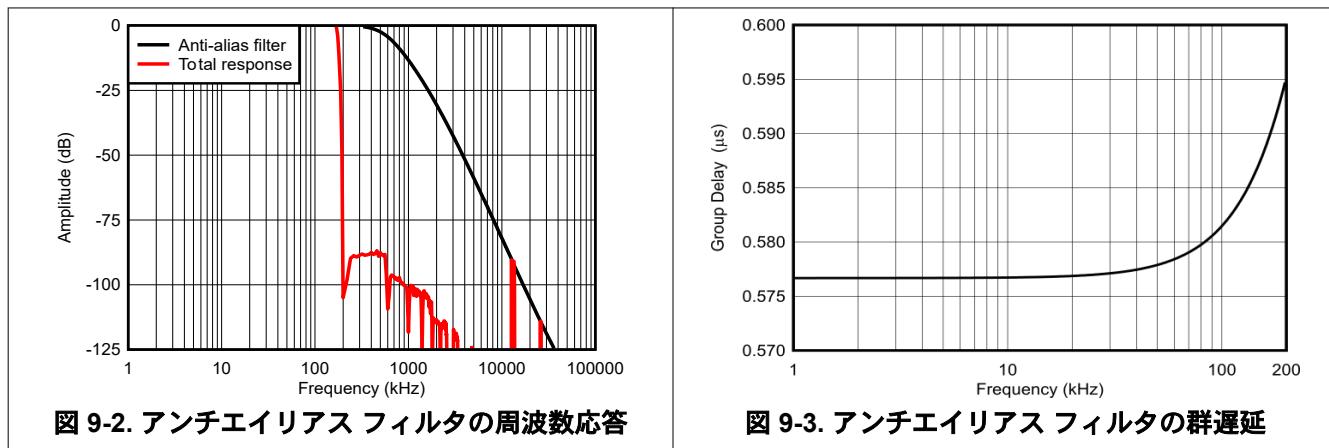

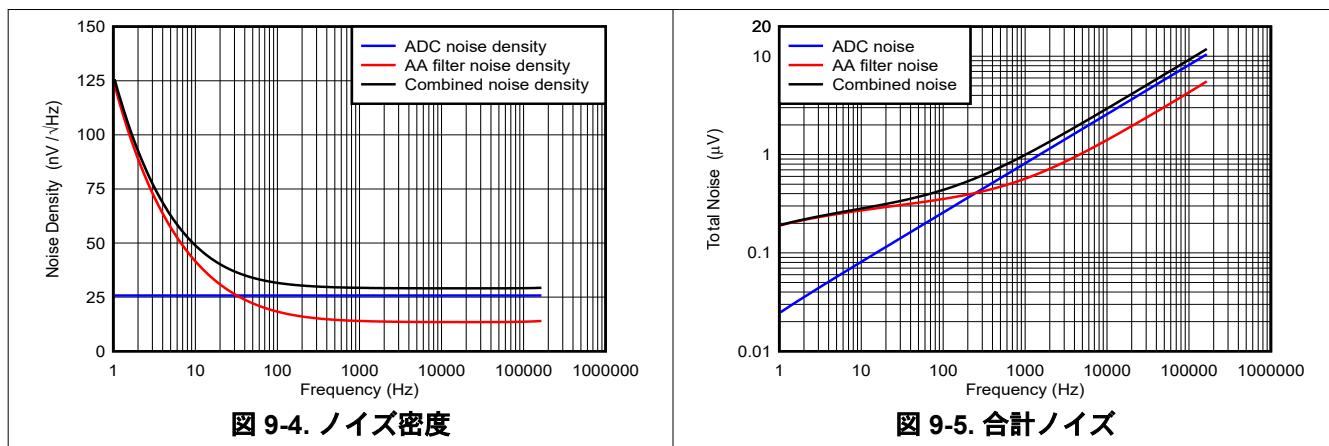

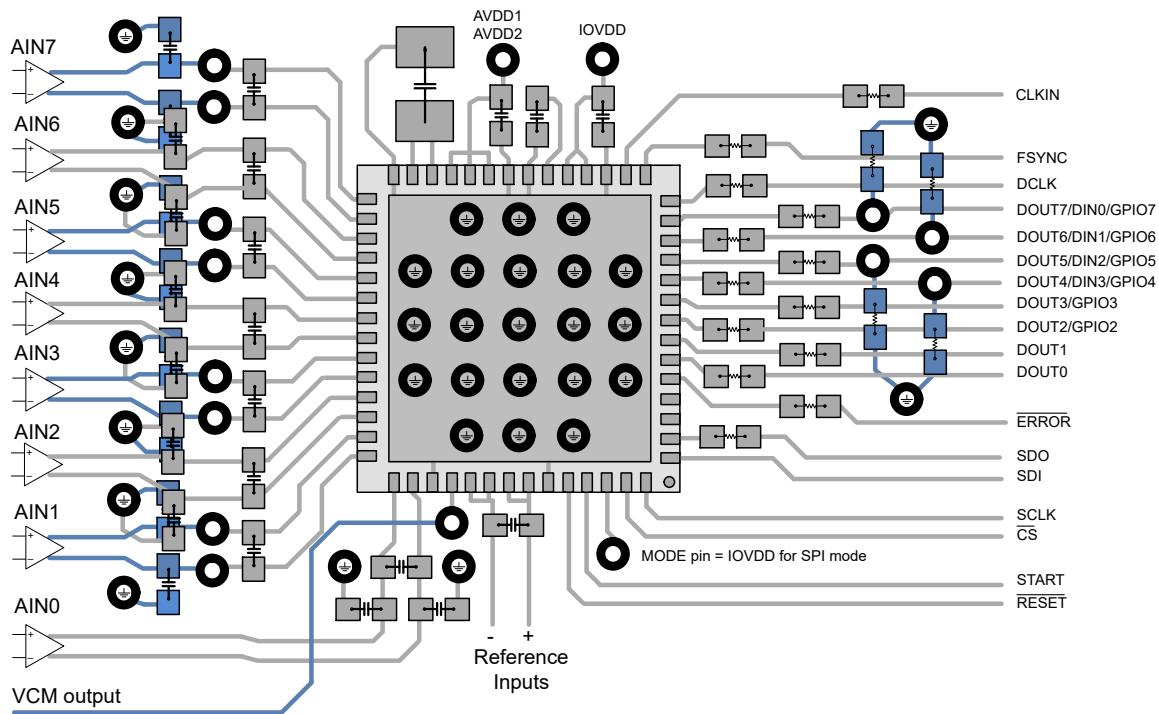

**表 6-1. 広帯域フィルタのノイズ性能 ( $V_{REF} = 4.096V$ 、 $1x$  の入力範囲) (続き)**