**ADC3664-SP**

#### JAJSVW8A - DECEMBER 2024 - REVISED APRIL 2025

# ADC3664-SP 放射線耐性保証、14 ビット、デュアル チャネル、1~125MSPS、 低レイテンシ、低ノイズ、超低消費電力の A/D コンバータ (ADC)

### 1 特長

- スクリーニングと耐放射線特性

- QMLV スクリーニングと信頼性保証

- 吸収線量 (TID): 300krad (Si)

- シングル イベントラッチアップ (SEL):75MeVcm<sup>2</sup>/mg

- 周囲温度範囲:-55℃~105℃

- デュアル チャネル ADC

- 14 ビット 125MSPS

- ノイズ・フロア: -156.9dBFS/Hz

- 低消費電力:100mW/チャネル

- レイテンシ:2 クロック サイクル

- クロックレートと電圧リファレンスとの関係:

- 外部リファレンス:1MSPS~125MSPS

- 内部リファレンス:100MSPS~125MSPS

- 14 ビット、ミッシングコードなし

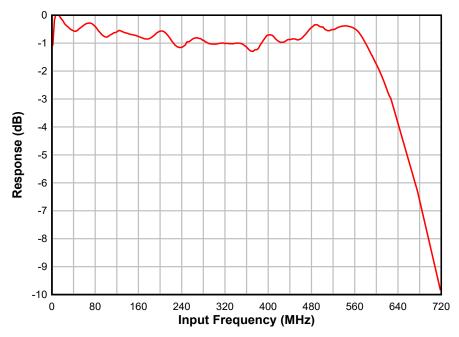

- 入力帯域幅:200MHz (-3dB)

- INL: ±2.6LSB, DNL: ±0.9LSB

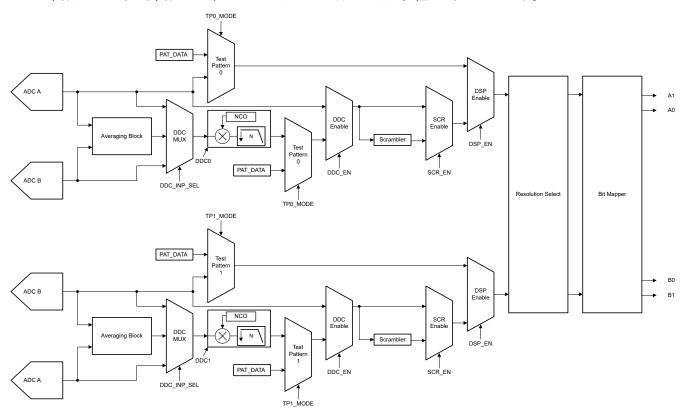

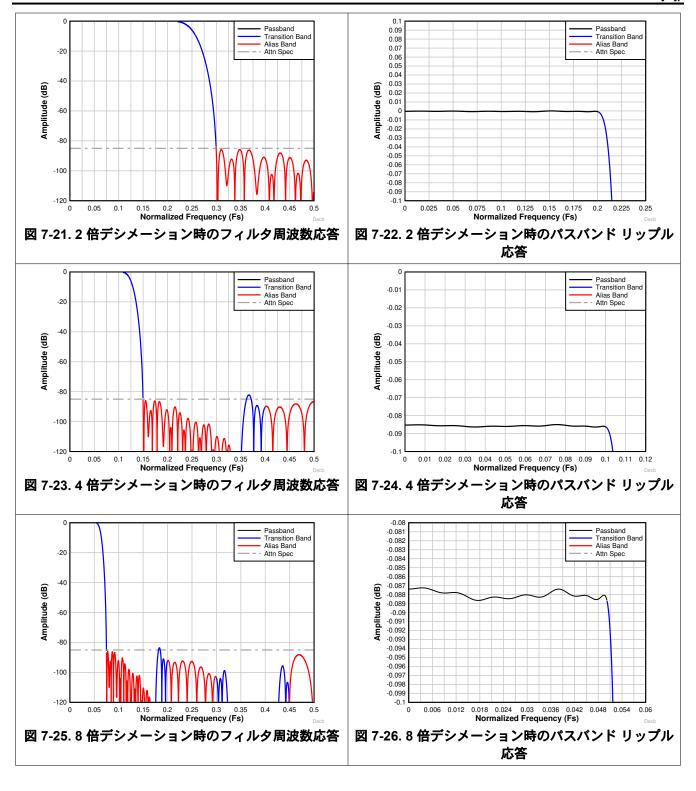

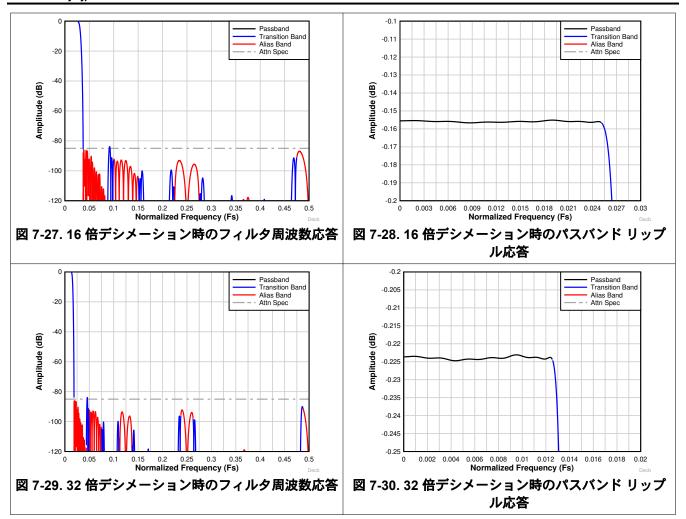

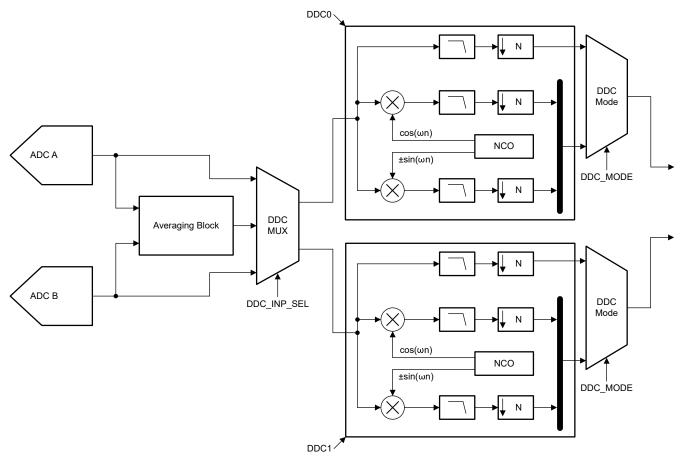

- オプションのデジタル降圧コンバータ (DDC):

- 実数または複素数のデシメーション

- デシメーション比:2、4、8、16、32

- 32 ビット NCO

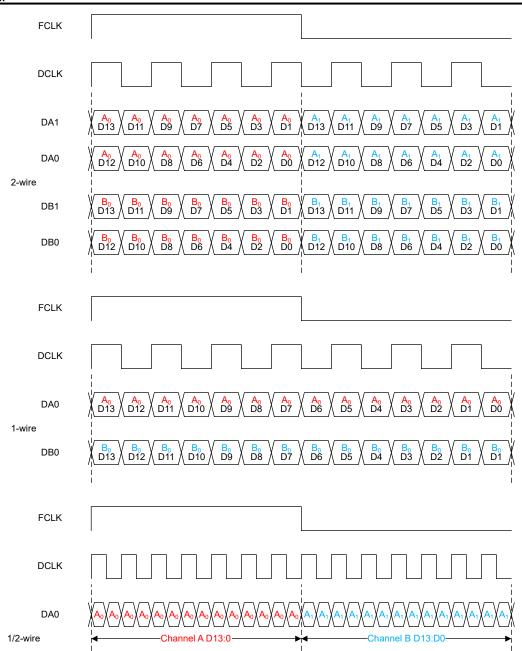

- シリアル LVDS (SLVDS) インターフェイス (2 線式、1 線式、

- 1/2 線式)

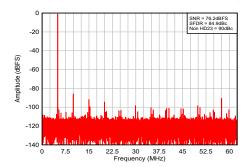

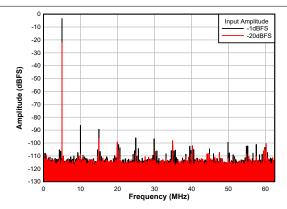

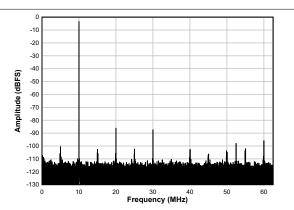

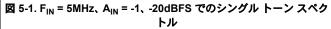

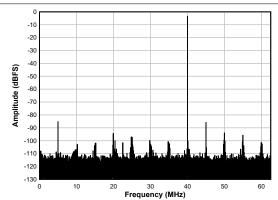

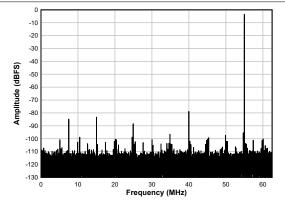

- スペクトル性能 (F<sub>IN</sub> = 5MHz):

- 信号対雑音比:77.5dBFS

- SFDR:84dBc HD2, HD3

- HD23 以外:91dBc

## 2 アプリケーション

- 光学画像処理ペイロード

- レーダー画像処理ペイロード

- 衛星通信ペイロード

#### 3 説明

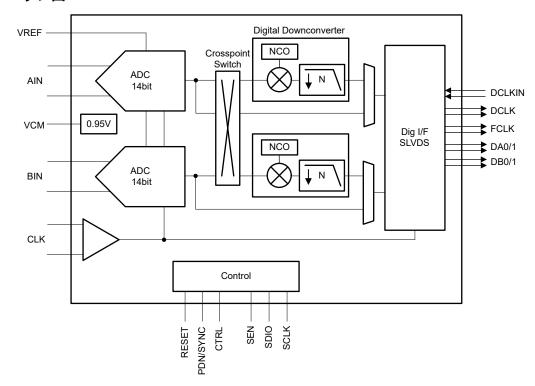

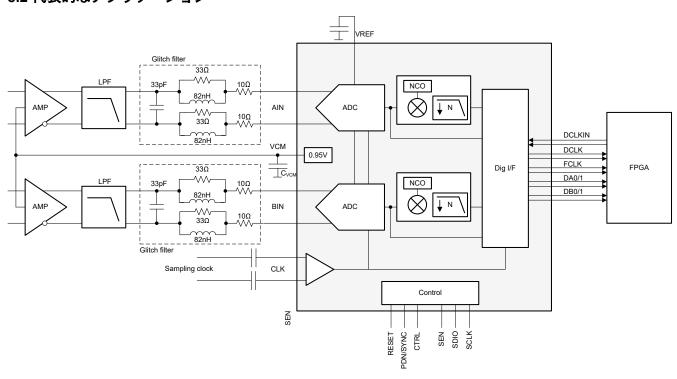

ADC3664-SP は、低レイテンシ、低ノイズ、超低消費電 力、14 ビット、125MSPS の高速デュアル チャネル A/D コンバータ (ADC) です。最善のノイズ性能を実現するよう に設計されており、このデバイスは、ノイズスペクトル密度 -156.9dBFS/Hz で、優れた直線性とダイナミック レンジを 備えています。ADC3664-SP は IF サンプリングをサポー トすると共に DC 精度を達成しているため、幅広いアプリ ケーションの設計が可能になります。低レイテンシアーキ テクチャ (最小 1 クロック サイクル レイテンシ) と高いサン プル レートにより、高速な制御ループも実現できます。こ の ADC の消費電力は 1 チャネルあたりわずか 100mW (125MSPS 時) であり、サンプリング レートにより、消費電 力を良好に増減できます。

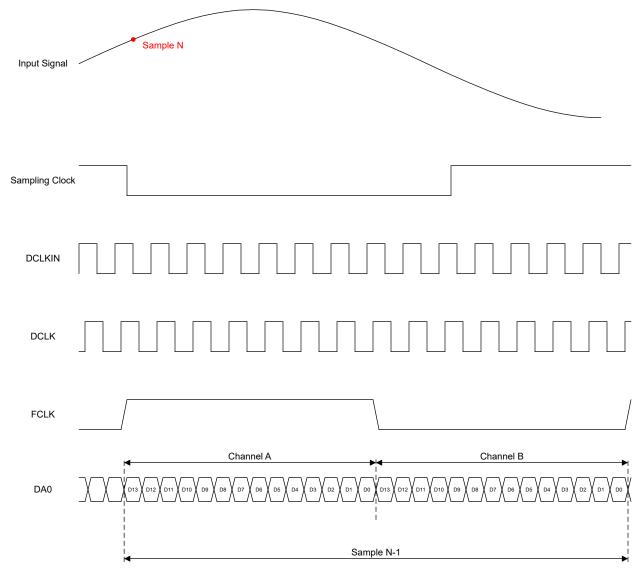

このデバイスは、シリアル LVDS (SLVDS) インターフェイ スを使用してデータを出力し、デジタル相互接続の数を最 小限に抑えます。このデバイスは、デジタル降圧コンバー タ (DDC) も内蔵しており、データレートの低減とシステム の消費電力の低減に役立ちます。このデバイスは、18 ビ ット、65MSPS ADC3683-SP とピン互換です。 本デバイ スは 64 ピンの CFP パッケージ (10.9mm x 10.9mm) で 供給され、-55℃~+105℃の温度範囲をサポートしてい

#### 製品情報

| 部品番号                         | グレード                               | パッケージ <sup>(1)</sup>    |

|------------------------------|------------------------------------|-------------------------|

| 5962F2320501VXC              | 放射線耐性保証 QML-V                      | 10.9mm x 10.9mm 64 ピン   |

| ADC3664HBP/EM <sup>(2)</sup> | エンジニアリング モデル、ノン<br>フライト プロトタイプ 作業用 | セラミック フラット パック<br>(HBP) |

- (1) 詳細については、セクション 12 を参照してください。

- これらのユニットは、技術的な評価のみを目的としています。規格 に準拠したフローを実施していません (そのため、バーンインはな く、25℃テストのみなど)。 さらにこれらのユニットは、認定、量産、 放射線テスト、航空での使用には適していません。部品は、温度ま たは動作寿命全体にわたる性能を保証されていません。

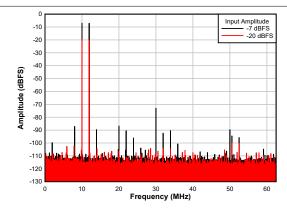

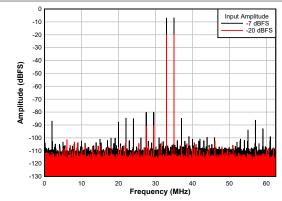

シングル トーン スペクトル、 $F_s = 125MSPS$ 、 $F_{in} =$ 5MHz

## 目次

| 1 特長              | 1        |

|-------------------|----------|

| 2 アプリケーション        |          |

| 3 説明              | 1        |

| 4 ピン構成および機能       |          |

| 5 仕様              |          |

| 5.1 絶対最大定格        |          |

| 5.2 ESD 定格        |          |

| 5.3 推奨動作条件        | <u>5</u> |

| 5.4 熱に関する情報       |          |

| 5.5 電気的特性 - 消費電力  | <b>7</b> |

| 5.6 電気的特性 - DC 仕様 | 8        |

| 5.7 電気的特性 - AC 仕様 | 10       |

| 5.8 タイミング要件       |          |

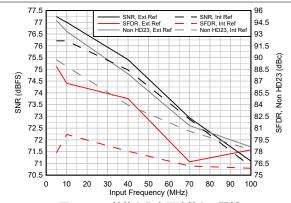

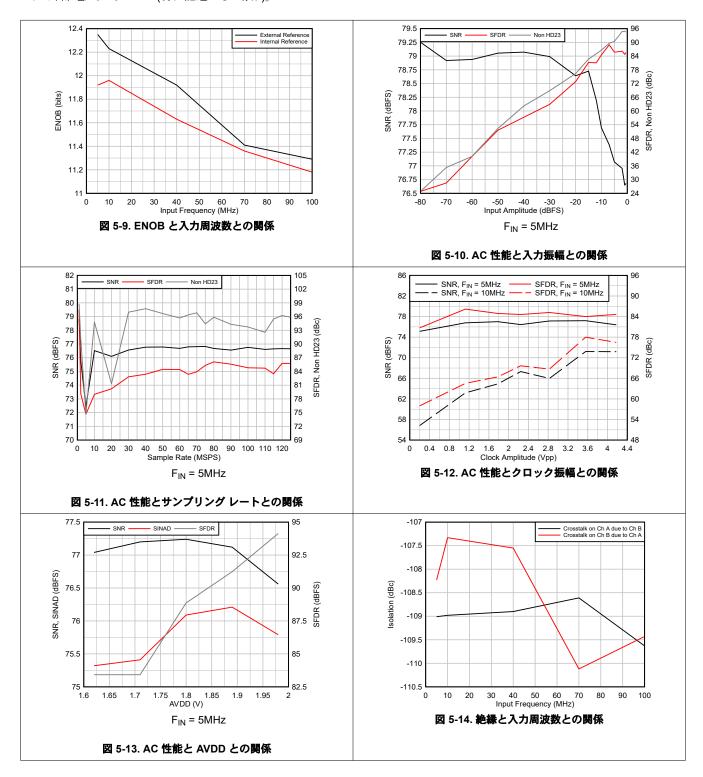

| 5.9 代表的特性         | 13       |

| 6 パラメータ測定情報       | 18       |

| 7 詳細説明            | 21       |

| 7.1 概要            | 21       |

| 7.2 機能ブロック図       | 21       |

|   | 7.3 機能説明              | .22 |

|---|-----------------------|-----|

|   | 7.4 デバイスの機能モード        | 44  |

|   | 7.5 プログラミング           | 45  |

| 8 | アプリケーション情報に関する免責事項    | 63  |

|   | 8.1 アプリケーション情報        | .63 |

|   | 8.2 代表的なアプリケーション      | 63  |

|   | 8.3 初期化セットアップ         | .64 |

|   | 8.4 電源に関する推奨事項        |     |

|   | 8.5 レイアウト             | 66  |

| 9 | デバイスおよびドキュメントのサポート    | .68 |

|   | 9.1ドキュメントの更新通知を受け取る方法 | 68  |

|   | 9.2 サポート・リソース         | 68  |

|   | 9.3 商標                | .68 |

|   | 9.4 静電気放電に関する注意事項     | 68  |

|   | 9.5 用語集               |     |

| 1 | 0 改訂履歴                | 68  |

| 1 | 1 メカニカル、パッケージ、および注文情報 | .68 |

|   | 11.1 メカニカル データ        | .69 |

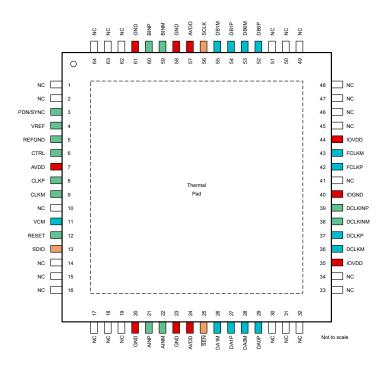

## 4 ピン構成および機能

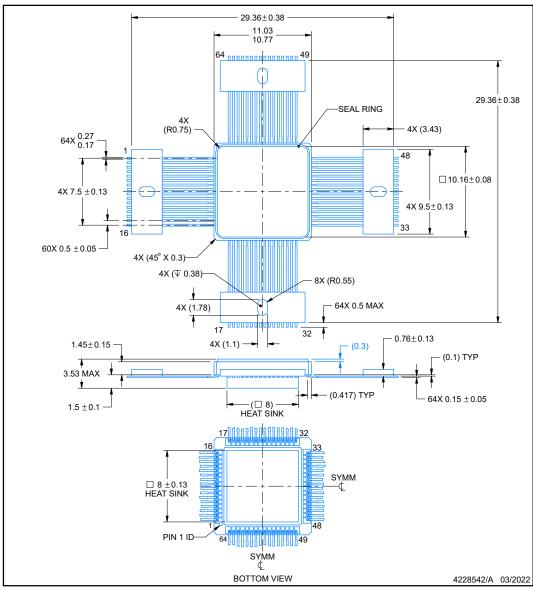

図 4-1. HBP パッケージ、64 ピン CFP (上面図)

表 4-1. ピンの機能

|         | ピン | هــد دد | aw no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号 | タイプ     | 説明<br>  The state of the state |

| 入力      |    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AINP    | 21 | I       | ADC A の正アナログ入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AINM    | 22 | I       | ADC A の負アナログ入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BINP    | 60 | I       | ADC B の正アナログ入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BINM    | 59 | I       | ADC B の負アナログ入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLKP    | 8  | I       | ADC A と B の正のサンプリング クロック入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKM    | 9  | I       | ADC A および B の負のサンプリング クロック入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

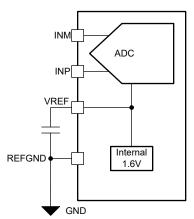

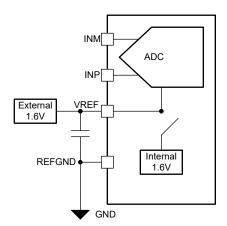

| VREF    | 4  | I       | 外部、1.6V、電圧リファレンス入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| REFGND  | 5  | I       | 電圧リファレンス グランド。このピンは、内部リファレンス モードでも外部リファレンス モードでも、<br>VREF 入力の近くにデカップリング コンデンサを近接配置できるようにします。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CTRL    | 6  | ı       | このビンを使用して、電源投入時にデフォルトのサンプリング クロック タイプと電圧リファレンス ソースを構成します (セクション 7.5.1 を参照)。 AVDD に対して内部に 100kΩ のプルアップ抵抗があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PDN/同期  | 3  | I       | デュアル目的、アクティブ High、ピン。このピンは、デバイスのパワーダウン状態または同期入力を<br>制御するように構成できます。このピン機能は SPI により構成できます (デフォルトの機能は<br>PDN)。このピンには、内部に 21kΩ プルダウン抵抗があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| リセット    | 12 | I       | アクティブ High リセット ピン。このピンには、内部に 21kΩ プルダウン抵抗があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DCLKINP | 39 | 1       | インターフェイス クロックの正入力。このピンは、内部の 100Ω 終端抵抗を経由して DCLKINM に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DCLKINM | 38 | ı       | インターフェイス クロックの負入力。このピンは、100Ω の内部終端抵抗を経由して DCLKINP に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 出力      |    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## 表 4-1. ピンの機能 (続き)

|       | ピン                                                                                                           |     | TILL OF TAKER (NOLC)                                                 |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------|--|--|--|--|

| 名称    | 番号                                                                                                           | タイプ | 説明                                                                   |  |  |  |  |

| DA0P  | 29                                                                                                           | 0   | インターフェイス レーン AO の正の出力。                                               |  |  |  |  |

| DA0M  | 28                                                                                                           | 0   | インターフェイス レーン AO の負の出力。                                               |  |  |  |  |

| DA1P  | 27                                                                                                           | 0   | インターフェイス レーン <b>A1</b> の正の出力。                                        |  |  |  |  |

| DA1M  | 26                                                                                                           | 0   | インターフェイス レーン A1 の負の出力。                                               |  |  |  |  |

| DB0P  | 52                                                                                                           | 0   | インターフェイス レーン B0 の正の出力。                                               |  |  |  |  |

| DB0M  | 53                                                                                                           | 0   | インターフェイス レーン B0 の負出力                                                 |  |  |  |  |

| DB1P  | 54                                                                                                           | 0   | インターフェイス レーン B1 の正の出力。                                               |  |  |  |  |

| DB1M  | 55                                                                                                           | 0   | インターフェイス レーン B1 の負の出力。                                               |  |  |  |  |

| DCLKP | 37                                                                                                           | 0   | インターフェイスクロックの正の出力。                                                   |  |  |  |  |

| DCLKM | 36                                                                                                           | 0   | インターフェイスクロックの負の出力。                                                   |  |  |  |  |

| FCLKP | 42                                                                                                           | 0   | インターフェイスフレームクロックの正の出力。                                               |  |  |  |  |

| FCLKM | 43                                                                                                           | 0   | インターフェイスフレームクロックの負の出力。                                               |  |  |  |  |

| VCM   | 11                                                                                                           | 0   | アナログ入力への同相電圧出力 (通常 0.95V)。                                           |  |  |  |  |

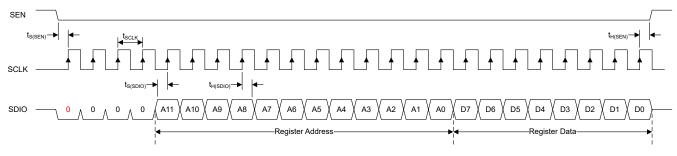

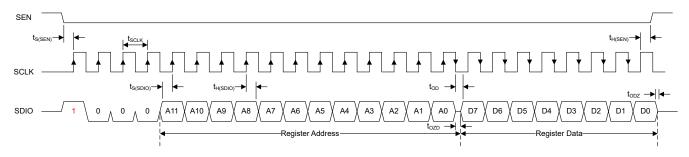

| SPI   |                                                                                                              |     |                                                                      |  |  |  |  |

| SEN   | 25                                                                                                           | 1   | アクティブ Low の SPI をイネーブル。このピンには、内部に AVDD への $21k\Omega$ プルアップ抵抗が あります。 |  |  |  |  |

| SCLK  | 56                                                                                                           | I   | SPI クロック入力。このピンには、内部に 21kΩ プルダウン抵抗があります。                             |  |  |  |  |

| SDIO  | 13                                                                                                           | I/O | SPI データ入力または出力。このピンには、内部に 21kΩ プルダウン抵抗があります。                         |  |  |  |  |

| 電源    |                                                                                                              |     |                                                                      |  |  |  |  |

| AVDD  | 7、24、57                                                                                                      | I   | アナログ電源入力、1.8V。                                                       |  |  |  |  |

| GND   | 20、23、58、61                                                                                                  | I   | グランド電源入力、OV。                                                         |  |  |  |  |

| IOVDD | 35、44                                                                                                        | I   | インターフェイス電源入力、1.8V。                                                   |  |  |  |  |

| IOGND | 40                                                                                                           | I   | インターフェイス グランド電源入力、OV。                                                |  |  |  |  |

| その他   |                                                                                                              |     |                                                                      |  |  |  |  |

| DAP   | DAP                                                                                                          | -   | ダイ取り付けパッド (サーマル パッド)、GND に接続。                                        |  |  |  |  |

| NC    | 1, 2, 10, 14, 15, 16,<br>17, 18, 19, 30, 31, 32,<br>33, 34, 41, 45, 46, 47,<br>48, 49, 50, 51, 62, 63,<br>64 | -   | 接続の無いピン。グランドに接続するか、フローティングのまま。(1)                                    |  |  |  |  |

<sup>(1)</sup> サーマル パッドと上部金属製リッドをピン 17 に接続します。グランドに接続するか、未接続にすることができます。

4

Product Folder Links: ADC3664-SP

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)(1)

| パラメータ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | テスト条件                            | 最小値  | 最大値                 | 単位 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|---------------------|----|

| 電源電圧の範囲、AVDD、IOVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  | -0.3 | 2.1                 | V  |

| 電源電圧の範囲、GND、IOGND、REFGND -0.3 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  | V    |                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AINP/M、BINP/M、CLKP/M、VREF、CTRL   | -0.3 | MIN(2.1, AVDD+0.3)  |    |

| 入力ピンに印加され   る電圧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PDN/SYNC, RESET, SCLK, SEN, SDIO | -0.3 | MIN(2.1, AVDD+0.3)  | V  |

| المراجع المراج | DCLKINP / M                      | -0.3 | MIN(2.1, IOVDD+0.3) |    |

| 接合部温度、TJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |      | 125                 | °C |

| 保管温度、T <sub>stg</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  | -65  | 150                 | °C |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、 *推奨動作条件*に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありませ ん。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

|                    |      |                                                              | 値    | 単位 |

|--------------------|------|--------------------------------------------------------------|------|----|

| V                  | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup> | 1000 | \/ |

| V <sub>(ESD)</sub> |      | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン (2)          | 250  | '  |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

#### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                      | 最小値  | 公称值 | 最大値                | 単位 |

|----------------|----------------------|------|-----|--------------------|----|

| <b>電源電圧公田</b>  | AVDD <sup>(1)</sup>  | 1.75 | 1.8 | 1.85               | V  |

| 電源電圧範囲         | IOVDD <sup>(1)</sup> | 1.75 | 1.8 | 1.85               | V  |

| T <sub>A</sub> | 自由空気での動作温度           | -55  |     | 105                | °C |

| T <sub>J</sub> | 動作時接合部温度             |      |     | 105 <sup>(2)</sup> | °C |

- (1) GND を基準として測定されます。

- (2) この接合部温度を超えて長時間使用すると、デバイスの時間あたりの故障回数 (FIT) レートが上昇する可能性があります。

## 5.4 熱に関する情報

|                       |                             | ADC3664-SP |      |

|-----------------------|-----------------------------|------------|------|

|                       | <b>熱評価基準</b> <sup>(1)</sup> | HBP (CFP)  | 単位   |

|                       |                             | 64 ピン      |      |

| $R_{\Theta JA}$       | 接合部から周囲への熱抵抗                | 28.4       | °C/W |

| R <sub>OJC(top)</sub> | 接合部からケース (上面) への熱抵抗         | 12.0       | °C/W |

| $R_{\Theta JB}$       | 接合部から基板への熱抵抗                | 14.1       | °C/W |

| $\Psi_{JT}$           | 接合部から上面への特性パラメータ            | 7.8        | °C/W |

| $\Psi_{JB}$           | 接合部から基板への特性パラメータ            | 13.8       | °C/W |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## 5.4 熱に関する情報 (続き)

|                             |                     | ADC3664-SP |      |

|-----------------------------|---------------------|------------|------|

| <b>熱評価基準</b> <sup>(1)</sup> |                     | HBP (CFP)  | 単位   |

|                             |                     |            |      |

| R <sub>OJC(bot)</sub>       | 接合部からケース (底面) への熱抵抗 | 7.0        | °C/W |

(1) 従来および新しい熱特性の詳細については、『半導体および IC パッケージの熱測定値』アプリケーション レポート、SPRA953 を参照してください。

## 5.5 電気的特性 - 消費電力

標準値は、 $T_A$  = 25°C、全温度範囲は  $T_{MIN}$  = -55°C~ $T_{MAX}$  = 105°C、ADC サンプリング レート= 125MSPS、50% クロック デューティ サイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

|                    | パラメータ                 | テスト条件                  | 最小値 標準値 | 最大値 | 単位   |

|--------------------|-----------------------|------------------------|---------|-----|------|

| ADC3664-           | SP:125MSPS            |                        |         | '   |      |

| 1                  | マナロゲ最近最近              | 内部基準電圧                 | 72      |     |      |

| I <sub>AVDD</sub>  | アナログ電源電流              | 外部リファレンス               | 66      | 82  | mA   |

| I <sub>IOVDD</sub> | I/O 電源電流              | 2線式                    | 45      | 72  | 2    |

| P <sub>DIS</sub>   | 消費電力                  | 外部リファレンス、2線式           | 200     | 277 | mW   |

|                    |                       | 2 線式、1/2 スイング          | 45      |     | mA   |

|                    |                       | 4 倍の実数デシメーション、1 線式     | 54      |     |      |

|                    |                       | 4 倍の実数デシメーション、1/2 線式   | 55      |     |      |

| ı                  | 110 是被争冰              | 16 倍の実数デシメーション、1 線式    | 49      |     |      |

| IOVDD              | I/O 電源電流              | 16 倍の実数デシメーション、1/2 線式  | 49      |     |      |

|                    |                       | 4 倍の複素数デシメーション、1 線式    | 58      |     |      |

|                    |                       | 16 倍の複素数デシメーション、1 線式   | 51      |     |      |

|                    |                       | 16 倍の複素数デシメーション、1/2 線式 | 51      |     |      |

| P <sub>DIS</sub>   | グローバル パワー ダウン モードでの消費 | デフォルトのマスク設定、内部リファレンス   | 11      |     | m\/\ |

|                    | 電力                    | デフォルトのマスク設定、外部リファレンス   | 13      |     | mW   |

## 5.6 電気的特性 - DC 仕様

標準値は、 $T_A$  = 25°C、全温度範囲は  $T_{MIN}$  = -55°C~ $T_{MAX}$  = 105°C、ADC サンプリング レート= 125MSPS、50% クロック デューティ サイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

|                       | パラメータ                      | テスト条件                  | 最小値 | 標準値   | 最大値   | 単位       |

|-----------------------|----------------------------|------------------------|-----|-------|-------|----------|

| DC 精度                 |                            |                        |     |       |       |          |

| ミッシング コー              | ードなし                       |                        | 14  |       |       | ビット      |

| PSRR                  | 電源除去比                      | F <sub>IN</sub> = 1MHz |     | 35    |       | dB       |

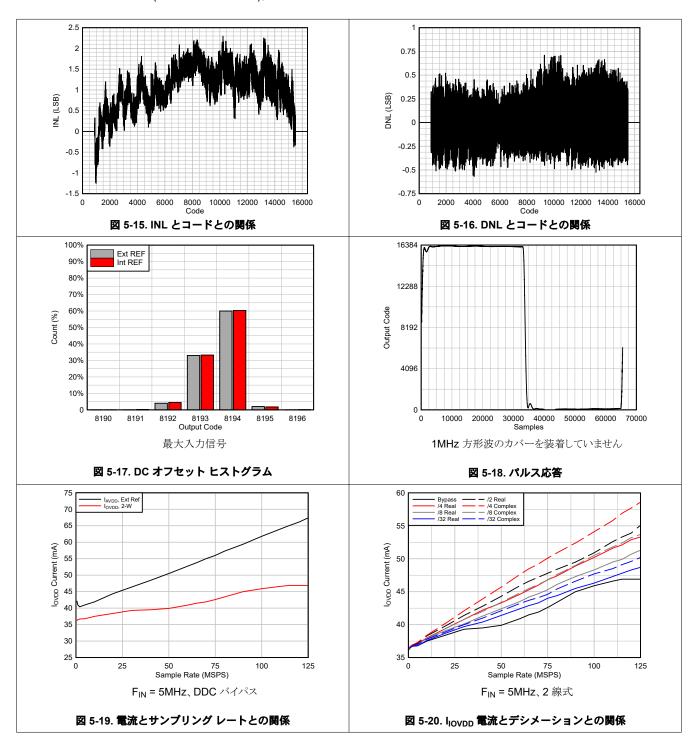

| DNL                   | 微分非直線性                     | F <sub>IN</sub> = 5MHz |     | ±0.9  | ±0.97 | LSB      |

| INL                   | 積分非直線性                     | F <sub>IN</sub> = 5MHz |     | ±2.6  | ±9.5  | LSB      |

| V <sub>OS</sub>       | 入力オフセット                    |                        |     | ±30   | ±50   | LSB      |

| V <sub>OS_DRIFT</sub> | オフセットのドリフト                 |                        |     | ±0.06 |       | LSB/°C   |

| エラー                   | ゲイン誤差と内部リファレンスの組み合わ<br>せ誤差 | 両方のチャネルに電源が投入されます      |     | ±2    |       | %FSR     |

|                       | ゲイン誤差                      | 両方のチャネルに電源が投入されます      |     | ±1.8  |       | %FSR     |

|                       | <i>よ</i> かっぱけつし            | 1.6V 外部リファレンス。         |     | ±57   |       | ppm/°C   |

|                       | ゲイン ドリフト                   | 内部基準電圧                 |     | 106   |       | ppm/°C   |

| 変換ノイズ                 |                            |                        |     | 0.7   |       | LSB      |

| ADC アナログ              | ブ入力 (AINP/M、BINP/M)        |                        |     |       |       |          |

| FS                    | 入力フル スケール                  | 差動                     |     | 3.2   |       | $V_{pp}$ |

| V <sub>CM</sub>       | 入力同相電圧                     |                        |     | 0.95  |       | V        |

| R <sub>IN</sub>       | 入力抵抗                       | DC で差動                 |     | 8     |       | kΩ       |

| C <sub>IN</sub>       | 入力容量                       | DC で差動                 |     | 5.4   |       | pF       |

| V <sub>OCM</sub>      | 出力同相電圧                     |                        |     | 0.95  |       | V        |

| BW                    | フルパワー アナログ入力帯域幅 (-3dB):    |                        |     | 200   |       | MHz      |

| 内部基準電圧                | E                          |                        | ·   |       |       |          |

| V <sub>REF</sub>      | 内部リファレンス電圧                 |                        |     | 1.6   |       | V        |

| V <sub>REF</sub> 出力イン |                            |                        |     | 8     |       | Ω        |

| 外部電圧リフ                | ァレンス                       |                        |     | ,     |       |          |

| V <sub>REF</sub>      | 外部電圧リファレンス                 |                        |     | 1.6   |       | V        |

| 入力電流                  |                            |                        |     | 1     |       | mA       |

| 入力インピー                | ダンス                        |                        |     | 5.3   |       | kΩ       |

| クロック入力                | (CLKP/M)                   |                        |     |       |       |          |

| 1 + 2 2 F             | FI Suth Wife               | 外部リファレンス               | 1   |       | 125   | MHz      |

| 入力クロック原               | 可仅数                        | 内部基準電圧                 | 100 |       | 125   | MHz      |

| V <sub>ID</sub>       | 差動入力電圧                     |                        | 0.5 | 1     |       | $V_{pp}$ |

| V <sub>CM</sub>       | 入力同相電圧                     |                        |     | 0.9   |       | V        |

| R <sub>IN</sub>       | 同相へのシングル エンド入力抵抗           |                        |     | 5     |       | kΩ       |

| C <sub>IN</sub>       | シングル エンド入力容量               |                        |     | 1.5   |       | pF       |

| クロック デュー              | ーティ サイクル                   |                        | 45  | 50    | 60    | %        |

## 5.6 電気的特性 - DC 仕様 (続き)

標準値は、 $T_A = 25$ °C、全温度範囲は  $T_{MIN} = -55$ °C~ $T_{MAX} = 105$ °C、ADC サンプリング レート= 125MSPS、50% クロック デューティサイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

|                 | パラメータ                         | テスト条件                      | 最小値            | 標準値   | 最大値      | 単位        |

|-----------------|-------------------------------|----------------------------|----------------|-------|----------|-----------|

| デジタル入フ          | (RESET, PDN, SCLK, SEN, SDIO) |                            |                |       |          |           |

| V <sub>IH</sub> | High レベル入力電圧                  |                            | 1.5            |       |          | V         |

| V <sub>IL</sub> | Low レベル入力電圧                   |                            |                |       | 0.3      | V         |

| I <sub>IH</sub> | High レベル入力電流                  |                            |                | 90    | 150      | μA        |

| I <sub>IL</sub> | Low レベル入力電流                   |                            | -150           | -90   |          | μA        |

| Cı              | 入力容量                          |                            |                | 1.5   |          | pF        |

| デジタル出フ          | th (SDOUT)                    |                            |                |       |          |           |

| V <sub>OH</sub> | High レベル出力電圧                  | I <sub>LOAD</sub> = -400uA | IOVDD -<br>0.1 | IOVDD |          | V         |

| V <sub>OL</sub> | Low レベル出力電圧                   | I <sub>LOAD</sub> = 400uA  |                |       | 0.1      |           |

| LVDS レーン        | /速度                           |                            |                |       | 1        | Gbps      |

| V <sub>ID</sub> | DCLKIN 差動入力電圧                 |                            | 200            | 350   |          | $mV_{pp}$ |

| V <sub>CM</sub> | DCLKIN 入力同相モード電圧最大値           |                            | 1.1            | 1.2   | 1.3      | V         |

| SLVDS イン        | ターフェイス                        | <u> </u>                   | '              |       | <u>'</u> |           |

| V <sub>OD</sub> | 差動出力電圧                        |                            | 0.585          | 700   | 0.785    | $mV_{pp}$ |

| V <sub>CM</sub> | 出力同相電圧                        |                            | 0.85           | 1.0   | 1.15     | V         |

## 5.7 電気的特性 - AC 仕様

標準値は、 $T_A$  = 25°C、全温度範囲は  $T_{MIN}$  = -55°C~ $T_{MAX}$  = 105°C、ADC サンプリング レート= 125MSPS、50% クロック デューティ サイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

|           | パラメータ                                   | テスト条件                                                  | 最小値                                                                                                                                                                                                                                                                                                                                                         | 標準値    | 最大値 | 単位      |  |  |  |

|-----------|-----------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---------|--|--|--|

| NSD       | ノイズスペクトル密度                              | F <sub>IN</sub> = 5MHz, A <sub>IN</sub> = -20dBFS      |                                                                                                                                                                                                                                                                                                                                                             | -156.9 |     | dBFS/Hz |  |  |  |

|           |                                         | F <sub>IN</sub> = 5MHz                                 | 70                                                                                                                                                                                                                                                                                                                                                          | 77.5   |     | dBFS    |  |  |  |

|           |                                         | F <sub>IN</sub> = 5MHz, A <sub>IN</sub> = -20dBFS      |                                                                                                                                                                                                                                                                                                                                                             | 78.9   |     |         |  |  |  |

| CND       | <i>□</i> □ □ ± 1,146 → 11.              | F <sub>IN</sub> = 10MHz                                |                                                                                                                                                                                                                                                                                                                                                             | 77.6   |     |         |  |  |  |

| SNR       | 信号対雑音比                                  | F <sub>IN</sub> = 40MHz                                |                                                                                                                                                                                                                                                                                                                                                             | 76.9   |     | dBFS    |  |  |  |

|           |                                         | F <sub>IN</sub> = 70MHz                                |                                                                                                                                                                                                                                                                                                                                                             | 75.5   |     |         |  |  |  |

|           |                                         | F <sub>IN</sub> = 100MHz                               |                                                                                                                                                                                                                                                                                                                                                             | 74.1   |     |         |  |  |  |

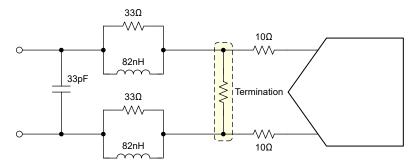

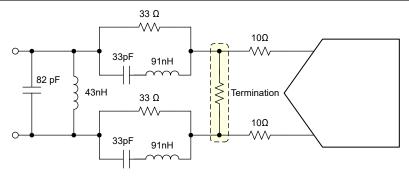

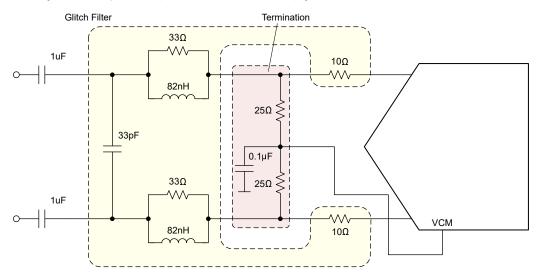

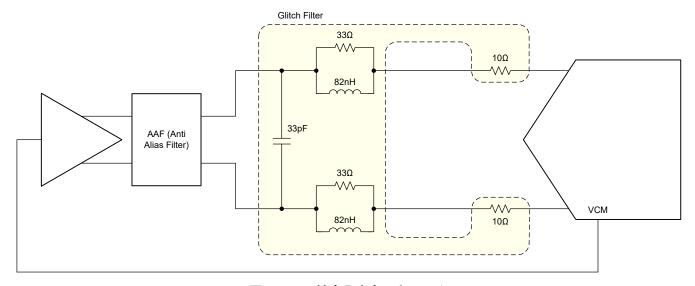

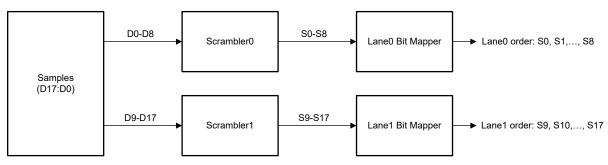

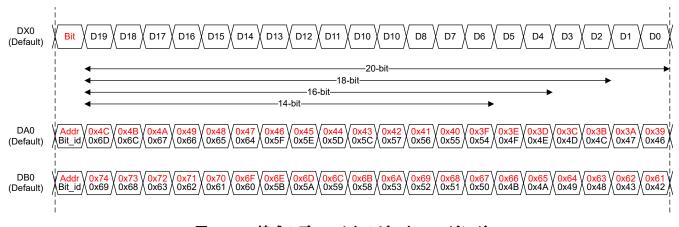

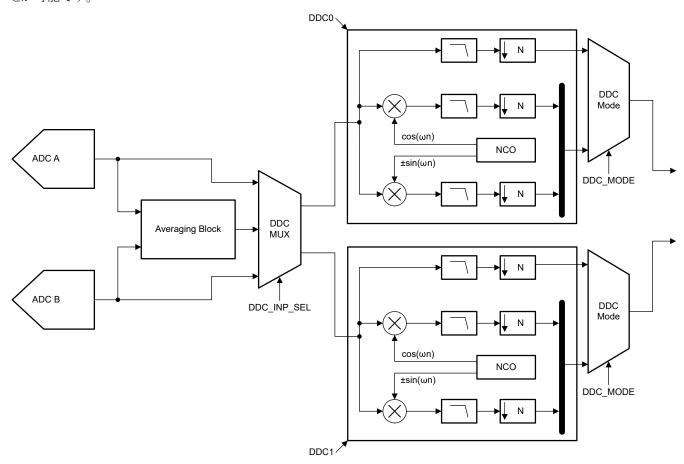

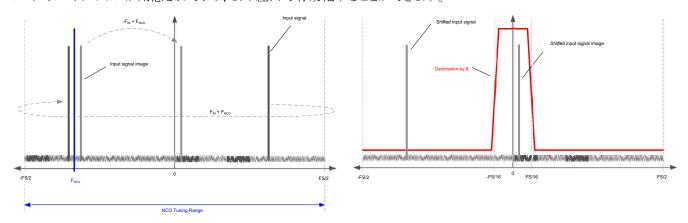

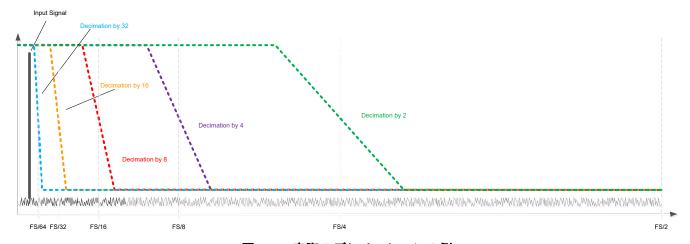

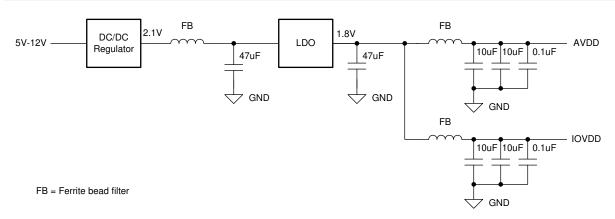

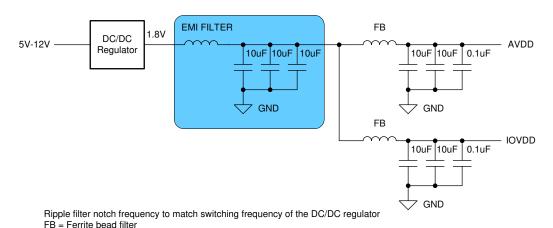

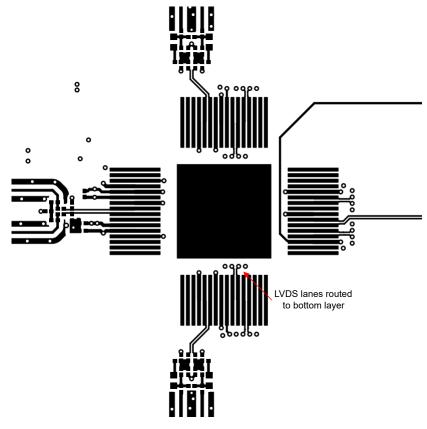

|           |                                         | F <sub>IN</sub> = 5MHz                                 |                                                                                                                                                                                                                                                                                                                                                             | 75.7   |     |         |  |  |  |