# ADC3664-SEP ADC3664-EP 14 ビット、125MSPS、低ノイズ、低消費電力デュアルチャネル ADC

## 1 特長

- 耐放射線特性 (-SEP のみ):

- 単一イベントラッチアップ (SEL) 耐性 (最大):

$LET = 43 \text{ MeV}\cdot\text{cm}^2/\text{mg}$

- $LET = 43\text{MeV}\cdot\text{cm}^2/\text{mg}$  まで、SEFI (Single-Event Functional Interrupt) 特性を評価済み

- 吸収線量 (TID): 30krad(Si)

- エンハンスト製品 (- EP と -SEP):

- ASTM E595 アウトガス仕様に適合

- ベンダー品目の図面 (VID)

- 温度範囲:  $-55^\circ\text{C} \sim 105^\circ\text{C}$

- 単一の製造、アセンブリ、テスト施設

- 金ボンドワイヤ、NiPdAu リード仕上げ

- ウエハー ロットをトレース可能

- 長期にわたる製品ライフ サイクル

- デュアルチャネル、125MSPS ADC

- 14 ビットの分解能 (ミッシング コードなし)

- ノイズ・フロア:  $-156.9\text{dBFS}/\text{Hz}$

- 低消費電力: 100mW/ チャネル (125MSPS 時)

- レイテンシ: 2 クロック サイクル

- 電圧リファレンス オプション:

- 外部: 1 ~ 125MSPS

- 内部: 100 ~ 125MSPS

- 入力帯域幅: 200MHz (3dB)

- INL:  $\pm 2.6\text{LSB}$ 、DNL:  $\pm 0.9\text{LSB}$  (標準値)

- オンチップ DSP (オプション / バイパス可能)

- デシメーション比: 2、4、8、16、32

- 32 ビット NCO

- シリアル LVDS デジタル インターフェイス (2 線式、1 線式、1/2 線式)

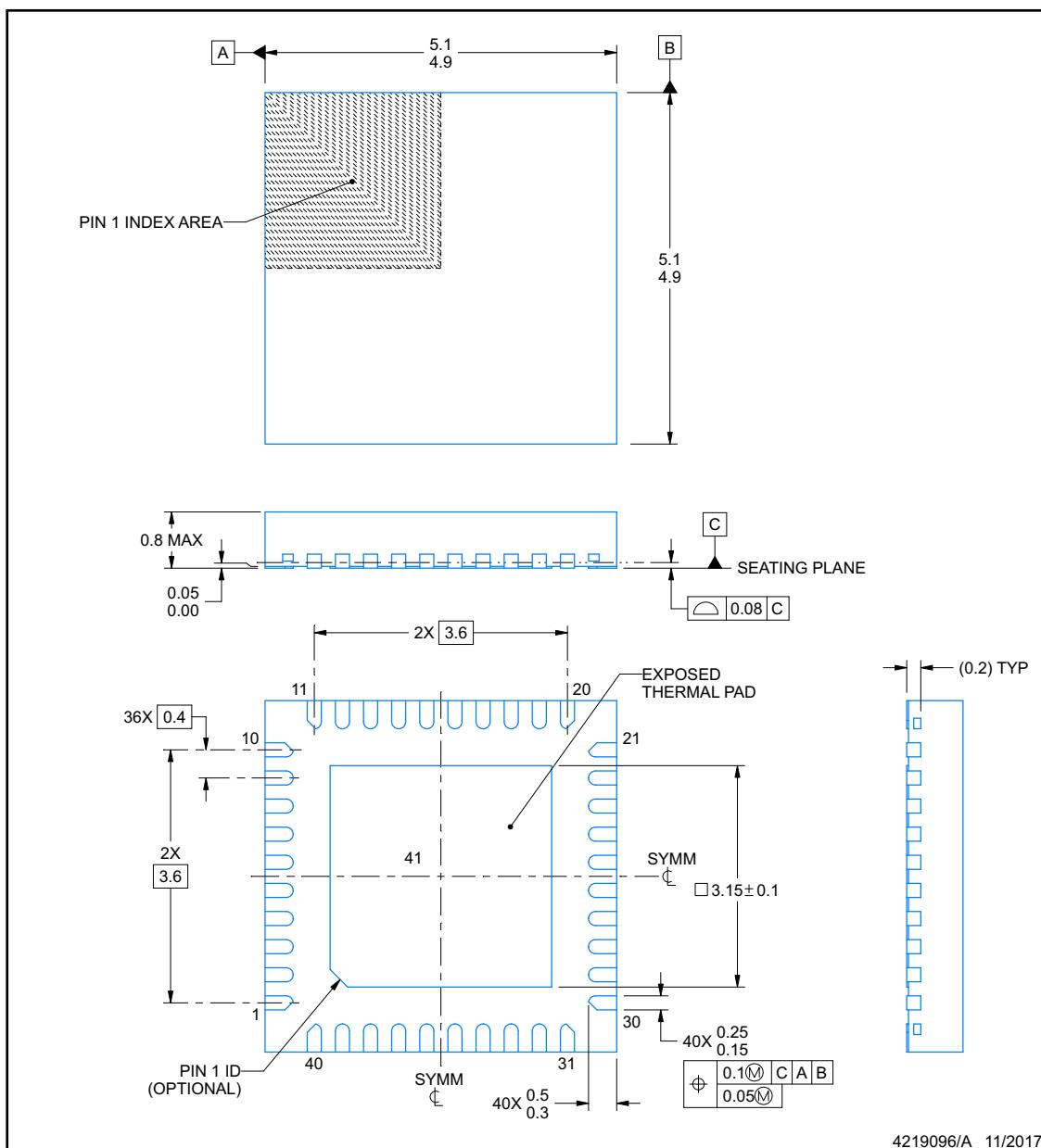

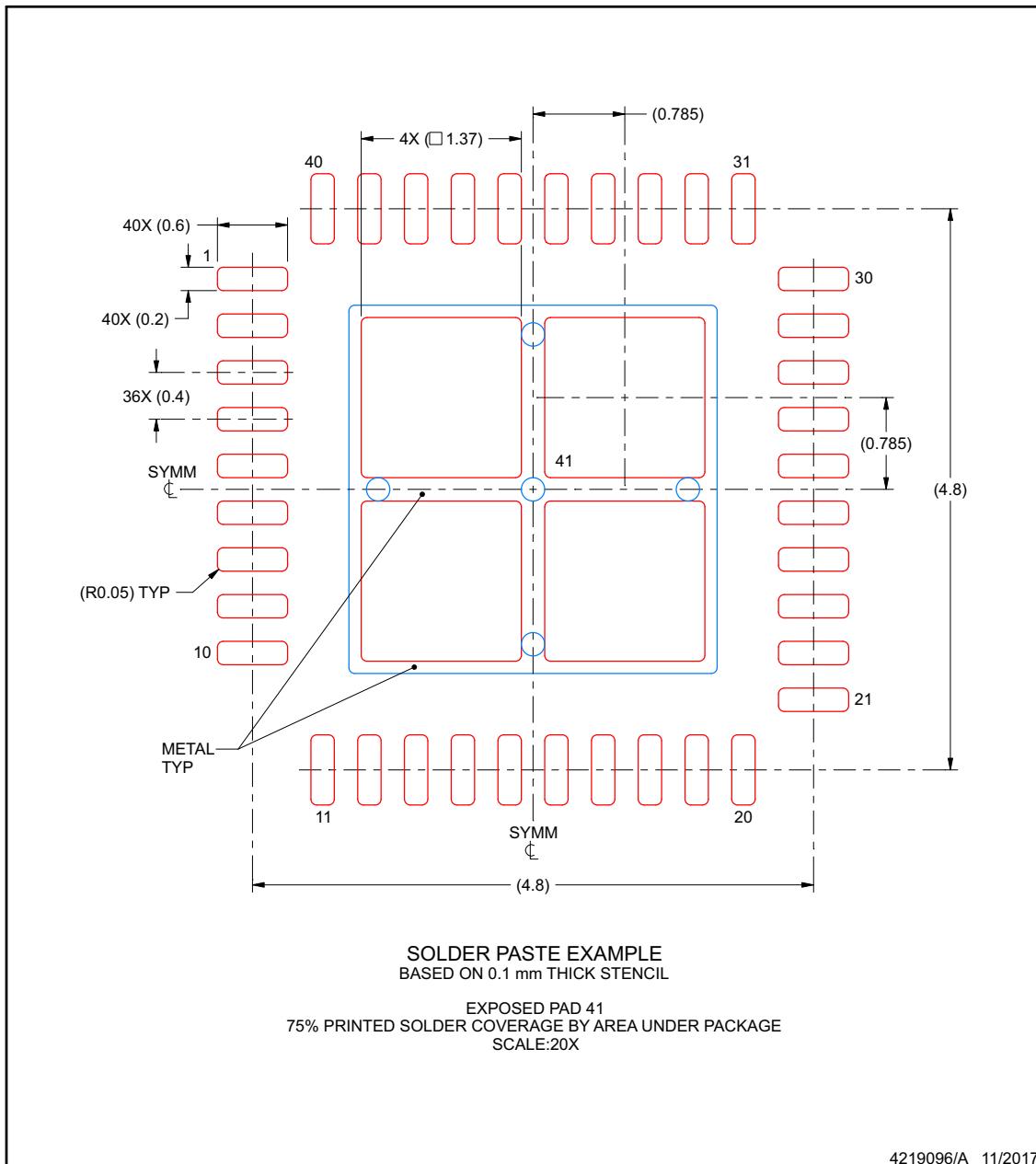

- 小型サイズ: 40QFN ( $5 \times 5\text{mm}$ ) パッケージ

- スペクトル性能 ( $f_{IN} = 5\text{MHz}$ ):

- 信号対雑音比: 77.5dBFS

- SFDR: 84dBc HD2、HD3

- SFDR: 92dBFS の最大スプリアス

## 2 アプリケーション

- 高速データ アクイジション

- 衛星光通信ペイロード

- 衛星画像処理ペイロード

- 衛星通信ペイロード

- 衛星レーダーおよび LIDAR ペイロード

## 3 概要

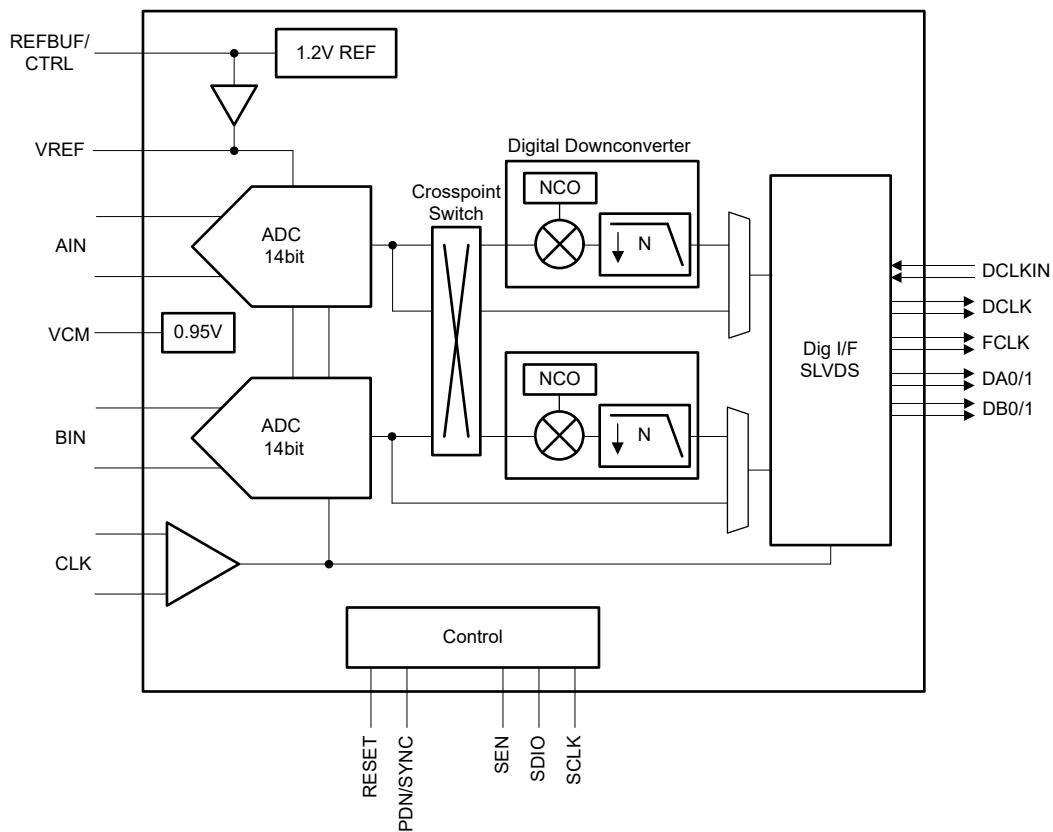

ADC3664-xEP デバイスは、低ノイズ、超低消費電力、14 ビット、125MSPS のデュアルチャネル高速 A/D コンバータ (ADC) です。きわめて低いノイズ性能を実現するように設計されており、デバイスのノイズ スペクトル密度は  $-156.9\text{dBFS}/\text{Hz}$  となり、直線性とダイナミックレンジを備えています。ADC3664-xEP は IF サンプリングをサポートしており、広範なアプリケーション向けに設計されたデバイスです。レイテンシがわずか 1 クロック サイクルと短いため、高速な制御ループを実現できます。この ADC の消費電力は 1 チャネルあたりわずか 100mW (125MSPS 時) であり、サンプリング レートを下げることで、消費電力を良好に低減できます。

ADC3664-xEP は、シリアル LVDS (SLVDS) インターフェイスを使用してデータを出力し、デジタル相互接続の数を最小限に抑えます。このデバイスは、2 レーン、1 レーン、およびハーフ レーンのオプションをサポートしています。このデバイスは、 $-55 \sim +105^\circ\text{C}$  の拡張温度範囲をサポートしています。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| ADC3664-SEP | VQFN (40)            | 5mm × 5mm                |

| ADC3664-EP  |                      |                          |

(1) 詳細については、[セクション 12](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合、これにはビンも含まれます。

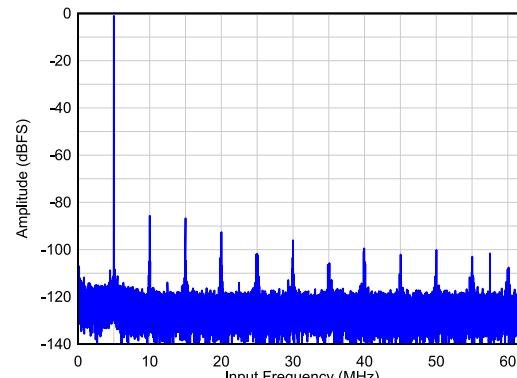

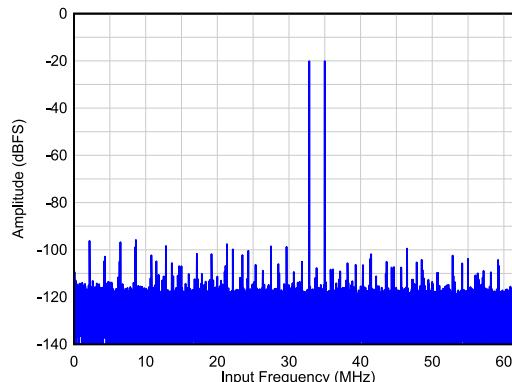

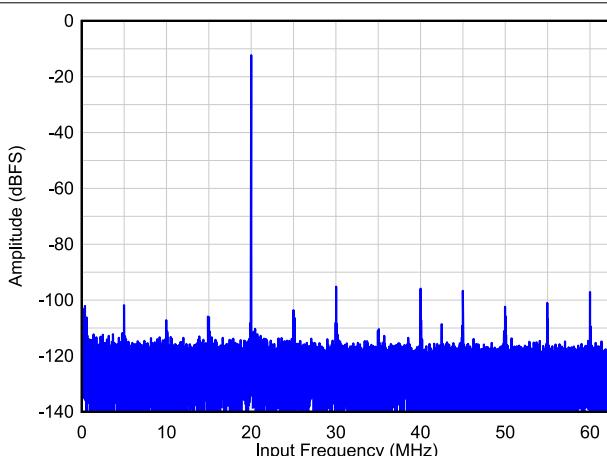

$F_{IN} = 5\text{MHz}$  でのシングル トーン FFT

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><b>1 特長</b>.....<br/> <b>2 アプリケーション</b>.....<br/> <b>3 概要</b>.....<br/> <b>4 ピン構成および機能</b>.....<br/> <b>5 仕様</b>.....<br/>       5.1 絶対最大定格.....<br/>       5.2 ESD 定格.....<br/>       5.3 推奨動作条件.....<br/>       5.4 熱に関する情報.....<br/>       5.5 電気的特性 - 消費電力.....<br/>       5.6 電気的特性 - DC 仕様.....<br/>       5.7 電気的特性 - AC 仕様.....<br/>       5.8 タイミング要件.....<br/>       5.9 代表的特性.....<br/> <b>6 パラメータ測定情報</b>.....<br/> <b>7 詳細説明</b>.....<br/>       7.1 概要.....<br/>       7.2 機能ブロック図.....<br/>       7.3 機能説明.....<br/> </p> | <p><b>1</b> .....<br/> <b>1</b> .....<br/> <b>1</b> .....<br/> <b>3</b> .....<br/> <b>5</b> .....<br/>       5 .....<br/>       5 .....<br/>       5 .....<br/>       5 .....<br/>       7 .....<br/>       8 .....<br/>       10 .....<br/>       11 .....<br/>       13 .....<br/>       18 .....<br/>       20 .....<br/>       20 .....<br/>       21 .....<br/> </p> | <p><b>7.4 デバイスの機能モード</b>.....<br/> <b>7.5 プログラミング</b>.....<br/> <b>8 アプリケーション情報に関する免責事項</b>.....<br/>       8.1 アプリケーション情報.....<br/>       8.2 代表的なアプリケーション.....<br/>       8.3 初期化セットアップ.....<br/>       8.4 電源に関する推奨事項.....<br/>       8.5 レイアウト.....<br/> <b>9 レジスタ マップ</b>.....<br/>       9.1 レジスタの詳細説明.....<br/> <b>10 デバイスおよびドキュメントのサポート</b>.....<br/>       10.1 ドキュメントの更新通知を受け取る方法.....<br/>       10.2 サポート・リソース.....<br/>       10.3 商標.....<br/>       10.4 静電気放電に関する注意事項.....<br/>       10.5 用語集.....<br/> <b>11 改訂履歴</b>.....<br/> <b>12 メカニカル、パッケージ、および注文情報</b>.....<br/>       12.1 メカニカル データ.....<br/> </p> | <p><b>44</b> .....<br/> <b>45</b> .....<br/> <b>47</b> .....<br/> <b>47</b> .....<br/> <b>47</b> .....<br/> <b>50</b> .....<br/> <b>52</b> .....<br/> <b>53</b> .....<br/> <b>55</b> .....<br/> <b>56</b> .....<br/> <b>71</b> .....<br/> <b>72</b> .....<br/> </p> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

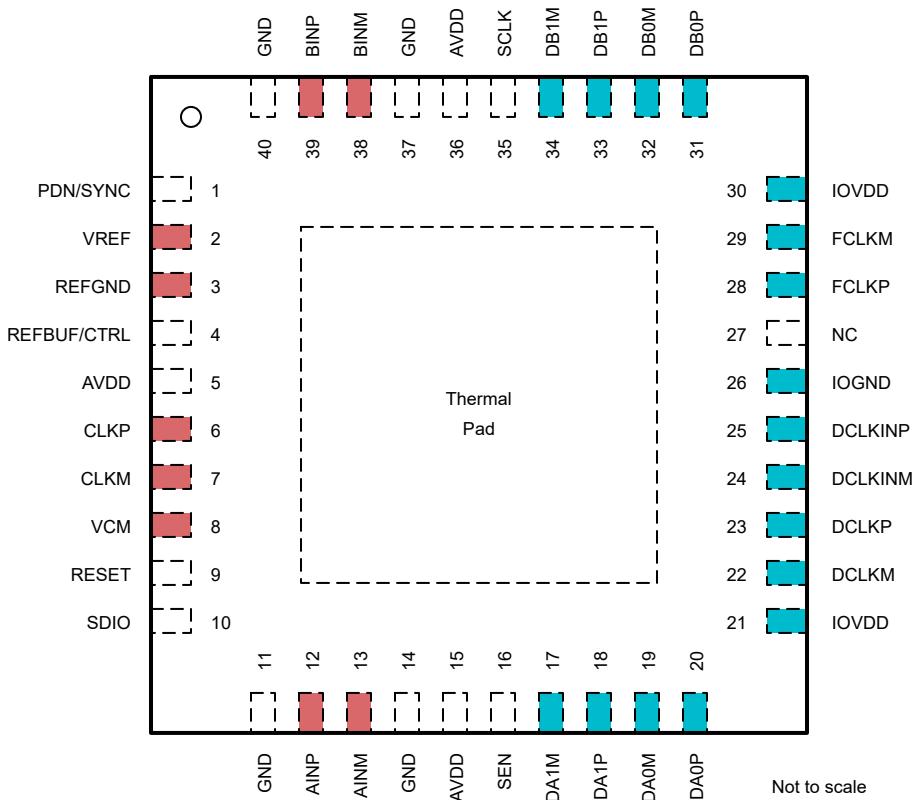

## 4 ピン構成および機能

**図 4-1. RSB (WQFN) パッケージ、40 ピン

(上面図)**

**表 4-1. ピンの機能**

| ピン           |    | タイプ | 概要                     |

|--------------|----|-----|------------------------|

| 名称           | 番号 |     |                        |

| <b>入力/換算</b> |    |     |                        |

| AINM         | 13 | I   | 負アナログ入力、チャネル A         |

| AINP         | 12 | I   | 正アナログ入力、チャネル A         |

| BINP         | 39 | I   | 正アナログ入力、チャネル B         |

| BINM         | 38 | I   | 負アナログ入力、チャネル B         |

| REFGND       | 3  | I   | 基準グランド入力、0V            |

| VCM          | 8  | O   | アナログ入力への同相電圧出力、0.95V   |

| VREF         | 2  | I   | 外部電圧リファレンス入力           |

| <b>クロック</b>  |    |     |                        |

| CLKM         | 7  | I   | ADC の負の差動サンプリング クロック入力 |

| CLKP         | 6  | I   | ADC の正の差動サンプリング クロック入力 |

| <b>構成</b>    |    |     |                        |

**表 4-1. ピンの機能 (続き)**

| ピン                  |                               | タイプ | 概要                                                                                                       |

|---------------------|-------------------------------|-----|----------------------------------------------------------------------------------------------------------|

| 名称                  | 番号                            |     |                                                                                                          |

| PDN/同期              | 1                             | I   | パワーダウン/同期入力。このピンは、SPI インターフェイスにより構成します。アクティブ HIGH。このピンには、内部に $21\text{k}\Omega$ ブルダウン抵抗があります。            |

| REFBUF/<br>CTRL     | 4                             | I   | このピンを使用して、電源投入時にデフォルトのサンプリング クロック タイプと電圧リファレンス ソースを構成します。AVDD に対して内部に $100\text{k}\Omega$ のプルアップ抵抗があります。 |

| リセット                | 9                             | I   | ハードウェア リセットアクティブ HIGH。このピンには、内部に $21\text{k}\Omega$ ブルダウン抵抗があります。                                        |

| SCLK                | 35                            | I   | シリアル インターフェース クロック入力。このピンには、内部に $21\text{k}\Omega$ ブルダウン抵抗があります。                                         |

| SDIO                | 10                            | I   | シリアル インターフェース データ入出力。このピンには、内部に $21\text{k}\Omega$ ブルダウン抵抗があります。                                         |

| SEN                 | 16                            | I   | シリアル インターフェースのイネーブル。アクティブ Low。このピンには、内部に AVDD への $21\text{k}\Omega$ プルアップ抵抗があります。                        |

| NC                  | 27                            | -   | 接続しない                                                                                                    |

| <b>デジタルインターフェイス</b> |                               |     |                                                                                                          |

| DA0P                | 20                            | O   | レーン 0、チャネル A の正の差動シリアル LVDS 出力。                                                                          |

| DA0M                | 19                            | O   | レーン 0、チャネル A の負の差動シリアル LVDS 出力。                                                                          |

| DA1P                | 18                            | O   | レーン 1、チャネル A の正の差動シリアル LVDS 出力。                                                                          |

| DA1M                | 17                            | O   | レーン 1、チャネル A の負の差動シリアル LVDS 出力。                                                                          |

| DB0P                | 31                            | O   | レーン 0、チャネル B の正の差動シリアル LVDS 出力。                                                                          |

| DB0M                | 32                            | O   | レーン 0、チャネル B の負の差動シリアル LVDS 出力。                                                                          |

| DB1P                | 33                            | O   | レーン 1、チャネル B の正の差動シリアル LVDS 出力。                                                                          |

| DB1M                | 34                            | O   | レーン 1、チャネル B の負の差動シリアル LVDS 出力。                                                                          |

| DCLKP               | 23                            | O   | 正の差動シリアル LVDS ビットクロック出力。                                                                                 |

| DCLKM               | 22                            | O   | 負の差動シリアル LVDS ビットクロック出力。                                                                                 |

| FCLKP               | 28                            | O   | 正の差動データ LVDS フレーム クロック出力。                                                                                |

| FCLKM               | 29                            | O   | 負の差動シリアル LVDS フレーム クロック出力。                                                                               |

| DCLKINP             | 25                            | I   | 正の差動シリアル LVDS ビットクロック入力。内部に $100\Omega$ の差動終端                                                            |

| DCLKINM             | 24                            | I   | 負の差動シリアル LVDS ビットクロック入力。内部に $100\Omega$ の差動終端                                                            |

| <b>電源</b>           |                               |     |                                                                                                          |

| AVDD                | 5,15,36                       | I   | アナ 1.8V のアナログ電源                                                                                          |

| GND                 | 11、14、37、<br>40、<br>PowerPAD™ | I   | グランド、0V                                                                                                  |

| IOGND               | 26                            | I   | デジタル インターフェース用のグランド、0V                                                                                   |

| IOVDD               | 21.30                         | I   | デジタル インターフェイス用 1.8V 電源                                                                                   |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                    | テスト条件                            | 最小値  | 最大値                | 単位 |

|--------------------------|----------------------------------|------|--------------------|----|

| 電源電圧の範囲、AVDD、IOVDD       |                                  | -0.3 | 2.1                | V  |

| 電源電圧の範囲、GND、IOGND、REFGND |                                  | -0.3 | 0.3                | V  |

| 入力ピンに印加される電圧             | AINP/M、BINP/M、CLKP/M、VREF、REFBUF | -0.3 | MIN(2.1、AVDD+0.3)  | V  |

|                          | PDN / SYNC、RESET、SCLK、SEN、SDIO   | -0.3 | MIN(2.1、AVDD+0.3)  |    |

|                          | DCLKINP / M                      | -0.3 | MIN(2.1、IOVDD+0.3) |    |

| 接合部温度、T <sub>J</sub>     |                                  |      | 125                | °C |

| 保管温度、T <sub>stg</sub>    |                                  | -65  | 150                | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、推奨動作条件に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

|                    |      |                                                                | 値    | 単位 |

|--------------------|------|----------------------------------------------------------------|------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | 2500 | V  |

|                    |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | 1000 |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                      | 最小値  | 公称値 | 最大値                | 単位 |

|----------------|----------------------|------|-----|--------------------|----|

| 電源電圧範囲         | AVDD <sup>(1)</sup>  | 1.75 | 1.8 | 1.85               | V  |

|                | IOVDD <sup>(1)</sup> | 1.75 | 1.8 | 1.85               | V  |

| T <sub>A</sub> | 自由空気での動作温度           |      | -55 | 105                | °C |

| T <sub>J</sub> | 動作時接合部温度             |      |     | 105 <sup>(2)</sup> | °C |

- (1) GND に対して測定。

(2) この接合部温度を超えて長時間使用すると、デバイスの時間あたりの故障回数 (FIT) レートが上昇する可能性があります。

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | ADC3664-SEP | 単位   |

|-----------------------|---------------------|-------------|------|

|                       |                     | RSB (QFN)   |      |

|                       |                     | 40 ピン       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 30.7        | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 16.4        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 10.5        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.2         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 10.5        | °C/W |

## 5.4 热に関する情報 (続き)

| 热評価基準 <sup>(1)</sup>  |                     | ADC3664-SEP | 単位   |

|-----------------------|---------------------|-------------|------|

|                       |                     | RSB (QFN)   |      |

|                       |                     | 40 ピン       |      |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への热抵抗 | 2.0         | °C/W |

- (1) 従来および新しい热特性の詳細については、『半導体および IC パッケージの热測定値』アプリケーション レポート、SPRA953 を参照してください。

## 5.5 電気的特性 - 消費電力

標準値は、 $T_A = 25^\circ\text{C}$ 、全温度範囲は  $T_{\text{MIN}} = -55^\circ\text{C} \sim T_{\text{MAX}} = 105^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、50% クロック デューティサイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

| パラメータ                      |                                                                                            | テスト条件                         | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------------|--------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-----|----|

| <b>ADC3664-SEP:125MSPS</b> |                                                                                            |                               |     |     |     |    |

| I <sub>AVDD</sub>          | アナログ電源電流                                                                                   | 外部リファレンス                      | 64  | 80  |     |    |

| I <sub>IOVDD</sub>         | I/O 電源電流                                                                                   | SLVDS 2 線式                    | 47  | 72  |     | mA |

| P <sub>DIS</sub>           | 消費電力                                                                                       | 外部リファレンス、2 線式                 | 200 | 274 |     | mW |

| I <sub>IOVDD</sub>         | I/O 電源電流                                                                                   | 2 線式、1/2 スイング                 | 35  |     |     | mA |

|                            |                                                                                            | 4 倍の実数デシメーション、16 ビット、1 線式     | 50  |     |     |    |

|                            |                                                                                            | 16 倍の実数デシメーション、16 ビット、1 線式    | 45  |     |     |    |

|                            |                                                                                            | 16 倍の実数デシメーション、16 ビット、1/2 線式  | 41  |     |     |    |

|                            |                                                                                            | 4 倍の複素数デシメーション、16 ビット、1 線式    | 57  |     |     |    |

|                            |                                                                                            | 8 倍の複素数デシメーション、16 ビット、1 線式    | 54  |     |     |    |

|                            |                                                                                            | 8 倍の複素数デシメーション、16 ビット、1/2 線式  | 50  |     |     |    |

|                            |                                                                                            | 16 倍の複素数デシメーション、16 ビット、1 線式   | 50  |     |     |    |

|                            |                                                                                            | 16 倍の複素数デシメーション、16 ビット、1/2 線式 | 47  |     |     |    |

|                            |                                                                                            | 32 倍の複素数デシメーション、16 ビット、1 線式   | 48  |     |     |    |

| I <sub>AVDD</sub>          | 内部リファレンス、追加のアナログ電源電流<br>1.2V 外部リファレンス (REFBUF)、追加のアナログ電源電流<br>シングルエンドクロック入力により、アナログ電源電流を低減 | SPI 経由でイネーブル                  | 4   |     |     | mA |

|                            |                                                                                            |                               | 0.5 |     |     |    |

|                            |                                                                                            |                               | 1   |     |     |    |

| P <sub>DIS</sub>           | グローバル パワー ダウン モードでの消費電力                                                                    | デフォルトのマスク設定                   | 12  |     |     | mW |

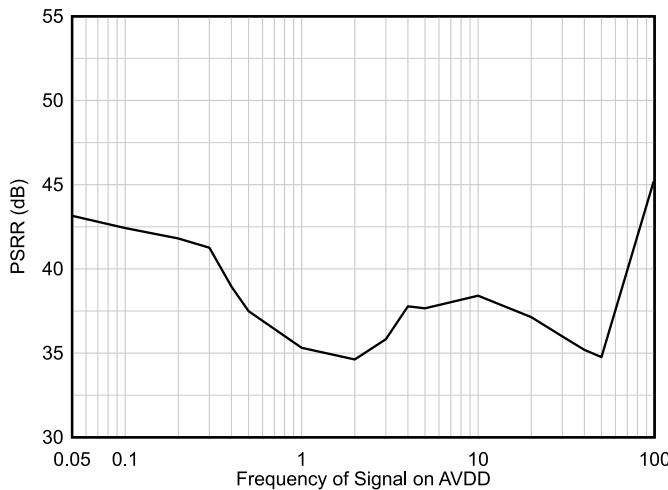

## 5.6 電気的特性 - DC 仕様

標準値は、 $T_A = 25^\circ\text{C}$ 、全温度範囲は  $T_{\text{MIN}} = -55^\circ\text{C} \sim T_{\text{MAX}} = 105^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、50% クロック デューティサイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

| パラメータ                              | テスト条件                         | 最小値           | 標準値        | 最大値      | 単位     |

|------------------------------------|-------------------------------|---------------|------------|----------|--------|

| <b>DC 精度</b>                       |                               |               |            |          |        |

| ミッキング コードなし                        |                               | 14            |            |          | ビット    |

| PSRR                               | $f_{\text{IN}} = 1\text{MHz}$ | 35            |            |          | dB     |

| DNL                                | 微分非直線性                        | -1.8          | $\pm 0.9$  | +1.8     | LSB    |

| INL                                | 積分非直線性                        | -7.5          | $\pm 2.6$  | +7.5     | LSB    |

| $V_{\text{OS\_ERR}}$               | オフセットエラー                      | -55           | $\pm 30$   | 55       | LSB    |

| $V_{\text{OS\_DRIFT}}$             | 温度範囲でのオフセットドリフト               |               | $\pm 0.06$ |          | LSB/°C |

| $GAIN_{\text{ERR}}$                | ゲイン誤差                         | 1.6V 外部リファレンス |            | $\pm 2$  | %FSR   |

| $GAIN_{\text{DRIFT}}$              | 温度範囲でのゲインドリフト                 | 1.6V 外部リファレンス |            | $\pm 57$ | ppm/°C |

| $GAIN_{\text{ERR}}$                | ゲイン誤差                         | 内部リファレンス      |            | $\pm 3$  | %FSR   |

| $GAIN_{\text{DRIFT}}$              | 温度範囲でのゲインドリフト                 | 内部リファレンス      |            | 106      | ppm/°C |

| 変換ノイズ                              |                               |               |            | 0.7      | LSB    |

| <b>ADC アナログ入力 (AINP/M, BINP/M)</b> |                               |               |            |          |        |

| FS                                 | 入力フル スケール                     | 差動            | 3.2        |          | Vpp    |

| $V_{\text{CM}}$                    | 入力同相電圧                        |               | 0.9        | 0.95     | 1.0    |

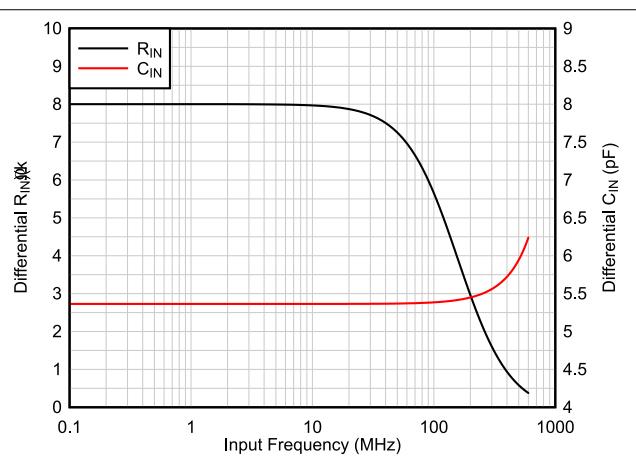

| $R_{\text{IN}}$                    | 入力抵抗                          | DC で差動        | 8          |          | kΩ     |

| $C_{\text{IN}}$                    | 入力容量                          | DC で差動        | 5.4        |          | pF     |

| $V_{\text{OCM}}$                   | 出力同相電圧                        |               | 0.95       |          | V      |

| BW                                 | アナログ入力帯域幅 (-3dB)              |               | 200        |          | MHz    |

| <b>内部基準電圧</b>                      |                               |               |            |          |        |

| $V_{\text{REF}}$                   | 内部リファレンス電圧                    |               | 1.6        |          | V      |

| $V_{\text{REF}}$ 出力インピーダンス         |                               |               | 8          |          | Ω      |

| <b>リファレンス入力バッファ (REFBUF)</b>       |                               |               |            |          |        |

| 外部基準電圧                             |                               |               | 1.2        |          | V      |

| <b>外部基準電圧 (VREF)</b>               |                               |               |            |          |        |

| $V_{\text{REF}}$                   | 外部基準電圧                        |               | 1.6        |          | V      |

| 入力電流                               |                               |               | 1          |          | mA     |

| 入力インピーダンス                          |                               |               | 5.3        |          | kΩ     |

| <b>クロック入力 (CLKP / M)</b>           |                               |               |            |          |        |

| 入力クロック周波数                          | 外部リファレンス                      | 1             | 125        |          | MHz    |

|                                    | 内部リファレンス                      | 100           | 125        |          | MHz    |

| $V_{\text{ID}}$                    | 差動入力電圧                        | 0.5           | 1          | 3.6      | Vpp    |

| $V_{\text{CM}}$                    | 入力同相電圧                        |               | 0.9        |          | V      |

| $R_{\text{IN}}$                    | 同相へのシングル エンド入力抵抗              |               | 5          |          | kΩ     |

| $C_{\text{IN}}$                    | シングル エンド入力容量                  |               | 1.5        |          | pF     |

| クロック デューティ サイクル                    |                               | 45            | 50         | 60       | %      |

## 5.6 電気的特性 - DC 仕様 (続き)

標準値は、 $T_A = 25^\circ\text{C}$ 、全温度範囲は  $T_{\text{MIN}} = -55^\circ\text{C} \sim T_{\text{MAX}} = 105^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、50% クロック デューティサイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

| パラメータ                                       |              | テスト条件                      | 最小値         | 標準値   | 最大値 | 単位            |

|---------------------------------------------|--------------|----------------------------|-------------|-------|-----|---------------|

| <b>デジタル入力 (RESET, PDN, SCLK, SEN, SDIO)</b> |              |                            |             |       |     |               |

| $V_{IH}$                                    | High レベル入力電圧 |                            | 1.4         |       |     |               |

| $V_{IL}$                                    | Low レベル入力電圧  |                            |             | 0.4   |     | V             |

| $I_{IH}$                                    | High レベル入力電流 |                            | 90          | 150   |     | $\mu\text{A}$ |

| $I_{IL}$                                    | Low レベル入力電流  |                            | -150        | -90   |     | $\mu\text{A}$ |

| $C_I$                                       | 入力容量         |                            |             | 1.5   |     | $\text{pF}$   |

| <b>デジタル出力 (SDOUT)</b>                       |              |                            |             |       |     |               |

| $V_{OH}$                                    | High レベル出力電圧 | $I_{LOAD} = -400\text{uA}$ | IOVDD - 0.1 | IOVDD |     |               |

| $V_{OL}$                                    | Low レベル出力電圧  | $I_{LOAD} = 400\text{uA}$  |             |       | 0.1 | V             |

| <b>SLVDS インターフェイス</b>                       |              |                            |             |       |     |               |

| $V_{ID}$                                    | 差動入力電圧       | DCLKIN                     | 200         | 350   | 650 | $\text{mVpp}$ |

| $V_{CM}$                                    | 入力同相電圧       |                            | 1           | 1.2   | 1.3 | V             |

| 出力データ レート                                   |              | 差動 SLVDS 出力ペアごと            |             | 1000  |     | Mbps          |

| $V_{OD}$                                    | 差動出力電圧       |                            | 500         | 700   | 850 | $\text{mVpp}$ |

| $V_{CM}$                                    | 出力同相電圧       |                            |             | 1.0   |     | V             |

## 5.7 電気的特性 - AC 仕様

標準値は、 $T_A = 25^\circ\text{C}$ 、全温度範囲は  $T_{\text{MIN}} = -55^\circ\text{C} \sim T_{\text{MAX}} = 105^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、50% クロック デューティサイクル、AVDD = IOVDD = 1.8V、1.6V 外部リファレンス、-1dBFS 差動入力 (特に記述のない限り)

| パラメータ     |                                      | テスト条件                                                                                | 最小値  | 標準値    | 最大値 | 単位      |

|-----------|--------------------------------------|--------------------------------------------------------------------------------------|------|--------|-----|---------|

| NSD       | ノイズ スペクトル密度                          | $f_{\text{IN}} = 5\text{MHz}, A_{\text{IN}} = -20\text{dBFS}$                        |      | -156.9 |     | dBFS/Hz |

| SNR       | 信号対雑音比                               | $f_{\text{IN}} = 5\text{MHz}$                                                        | 72   | 77.5   |     | dBFS    |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}, A_{\text{IN}} = -20\text{dBFS}$                        |      | 78.9   |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 77.6   |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 76.9   |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 75.5   |     |         |

| SINAD     | 信号対雑音歪み比                             | $f_{\text{IN}} = 100\text{MHz}$                                                      |      | 74.1   |     | dBFS    |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}$                                                        |      | 75.7   |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 74.2   |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 72.6   |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 71.3   |     |         |

| ENOB      | 有効ビット数                               | $f_{\text{IN}} = 100\text{MHz}$                                                      |      | 72.4   |     | ビット     |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}$                                                        |      | 12.6   |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 12.6   |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 12.5   |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 12.3   |     |         |

| THD       | 全高調波歪み (最初の 5 つの高調波)                 | $f_{\text{IN}} = 100\text{MHz}$                                                      |      | 12.0   |     | ビット     |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}$                                                        | 71.5 | 80     |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 76     |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 74     |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 72     |     |         |

| HD2       | 2 次高調波歪み                             | $f_{\text{IN}} = 100\text{MHz}$                                                      |      | 76     |     | dBc     |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}$                                                        | 77   | 84     |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 78     |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 75     |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 77     |     |         |

| HD3       | 3 次高調波歪み                             | $f_{\text{IN}} = 100\text{MHz}$                                                      |      | 79     |     | dBc     |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}$                                                        | 73.5 | 84     |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 81     |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 88     |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 76     |     |         |

| Non HD2,3 | スプリアス フリー ダイナミック レンジ (HD2 と HD3 を除く) | $f_{\text{IN}} = 100\text{MHz}$                                                      |      | 81     |     | dBFS    |

|           |                                      | $f_{\text{IN}} = 5\text{MHz}$                                                        | 84   | 92     |     |         |

|           |                                      | $f_{\text{IN}} = 10\text{MHz}$                                                       |      | 93     |     |         |

|           |                                      | $f_{\text{IN}} = 40\text{MHz}$                                                       |      | 89     |     |         |

|           |                                      | $f_{\text{IN}} = 70\text{MHz}$                                                       |      | 84     |     |         |

| IMD3      | 2 トーンの相互変調歪み                         | $f_1 = 10\text{MHz}, f_2 = 12\text{MHz}, A_{\text{IN}} = -7\text{dBFS} / \text{トーン}$ |      | 86     |     | dBc     |

|           |                                      |                                                                                      |      | 88     |     |         |

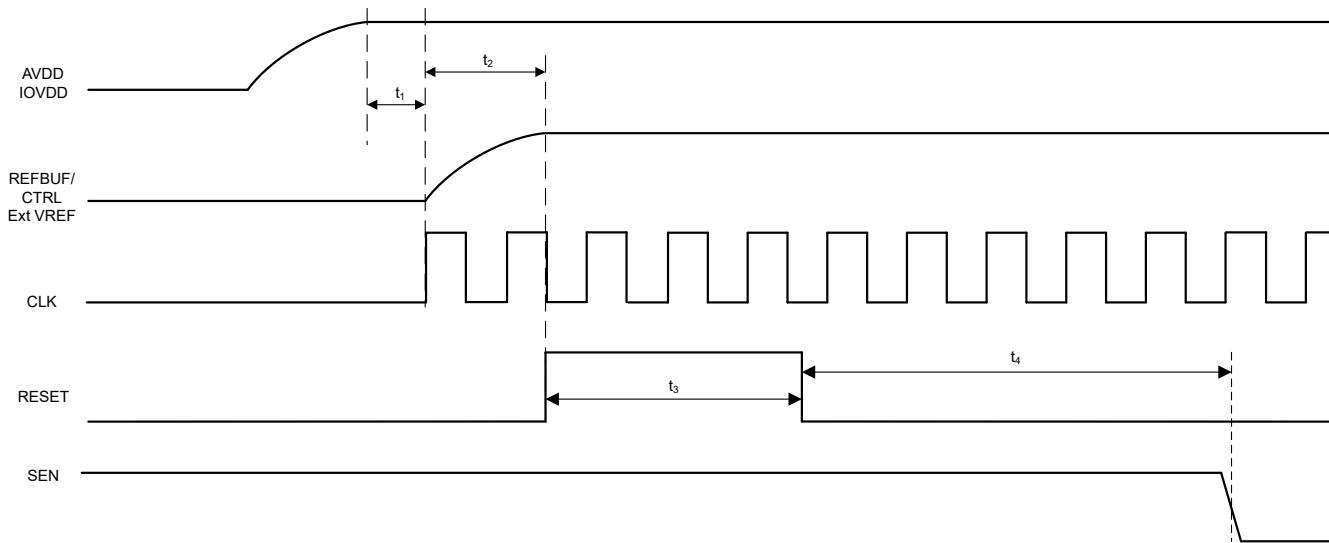

## 5.8 タイミング要件

特に記述のない限り、 $T_A = 25^\circ\text{C}$  における標準値、最小および最大のタイミング値は、 $T_{\text{MIN}} = -55^\circ\text{C} \sim T_{\text{MAX}} = 105^\circ\text{C}$  の全温度範囲で特性評価されていますが、生産試験は行われていません。その他の条件として、ADC サンプリング レート = 125MSPS、クロック デューティ比 = 50%、AVDD = IOVDD = 1.8V、外部リファレンス = 1.6V、入力信号 = -1dBFS の差動入力

| パラメータ                                    | テスト条件                                         | 最小値                                                                                                                                                                            | 公称値                                      | 最大値                    | 単位        |

|------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------|-----------|

| <b>ADC タイミング仕様</b>                       |                                               |                                                                                                                                                                                |                                          |                        |           |

| $t_{\text{AD}}$                          | アパーーチャ遅延                                      |                                                                                                                                                                                | 0.85                                     |                        | ns        |

| $t_A$                                    | アパーーチャジッタ                                     | 高速エッジ付き方形波クロック                                                                                                                                                                 | 250                                      |                        | fs        |

| $t_J$                                    | DCLKIN でのジッタ                                  |                                                                                                                                                                                |                                          | $\pm 50$               | ps pk-pk  |

| +6dB 過負荷状態からの復帰時間                        | SNR が予測値から 1dB 以内                             |                                                                                                                                                                                | 1                                        |                        | クロック サイクル |

| $t_{\text{ACQ}}$                         | 信号アクイジョン期間                                    | サンプリング クロックの立ち下がりエッジを基準                                                                                                                                                        | $-T_S/4$                                 | サンプリング クロック 周期         |           |

| $t_{\text{CONV}}$                        | 信号変換期間                                        |                                                                                                                                                                                |                                          |                        |           |

| ウェークリップ時間                                | パワー ダウンから出た後の有効なデータに対する時間。内部リファレンス。           | バンドギャップ リファレンスがイネーブル、シングル エンド クロック                                                                                                                                             | 13                                       | us                     |           |

|                                          |                                               | バンドギャップ リファレンスがイネーブル、差動クロック                                                                                                                                                    | 15                                       |                        |           |

|                                          |                                               | バンドギャップ リファレンスがディセーブル、シングル エンド クロック                                                                                                                                            | 2.4                                      | ms                     |           |

|                                          |                                               | バンドギャップ リファレンスがディセーブル、差動クロック                                                                                                                                                   | 2.3                                      |                        |           |

|                                          | パワー ダウンから出た後の有効なデータに対する時間<br>外部 1.6V リファレンス。  | バンドギャップ リファレンスがイネーブル、シングル エンド クロック                                                                                                                                             | 13                                       | us                     |           |

|                                          |                                               | バンドギャップ リファレンスがイネーブル、差動クロック                                                                                                                                                    | 14                                       |                        |           |

|                                          |                                               | バンドギャップ リファレンスがディセーブル、シングル エンド クロック                                                                                                                                            | 2.0                                      | ms                     |           |

|                                          |                                               | バンドギャップ リファレンスがディセーブル、差動クロック                                                                                                                                                   | 2.2                                      |                        |           |

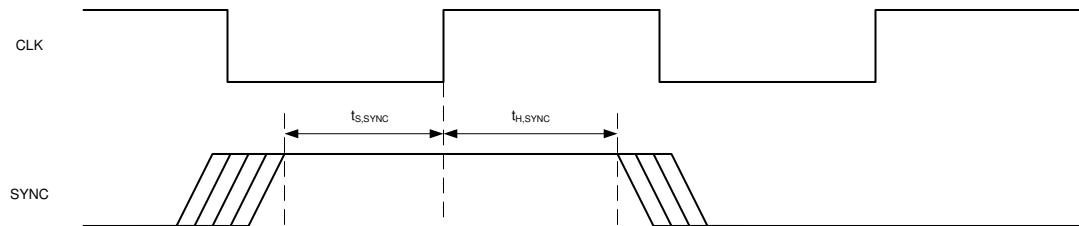

| $t_{S,\text{SYNC}}$                      | 同期入力信号のセットアップ時間                               | サンプリング クロックの立ち上がりエッジを基準                                                                                                                                                        | 500                                      | ps                     |           |

| $t_{H,\text{SYNC}}$                      | 同期入力信号のホールド時間                                 |                                                                                                                                                                                | 600                                      |                        |           |

| ADC レイテンシ                                | データ出力への信号入力                                   | 1/2 線式 SLVDS                                                                                                                                                                   | 1                                        | クロック サイクル              |           |

|                                          |                                               | 1 線式 SLVDS                                                                                                                                                                     | 1                                        |                        |           |

|                                          |                                               | 2 線式 SLVDS                                                                                                                                                                     | 2                                        |                        |           |

| 追加。レイテンシ                                 | 2 倍による実数のデシメーション                              |                                                                                                                                                                                | 21                                       | 出力クロック サイクル            |           |

|                                          | 2 倍による複素数デシメーション                              |                                                                                                                                                                                | 22                                       |                        |           |

|                                          | 4 倍、8 倍、16 倍、32 倍による実数または複素数のデシメーション          |                                                                                                                                                                                | 23                                       |                        |           |

| <b>インターフェイス タイミング:シリアル LVDS インターフェイス</b> |                                               |                                                                                                                                                                                |                                          |                        |           |

| $t_{PD}$                                 | 伝搬遅延:サンプリング クロックの立ち下がりエッジから DCLKIN 立ち上がりエッジまで | サンプリング クロックの立ち下がりエッジから DCLKIN 立ち下がりエッジまでの遅延 < 2.5ns。<br>$T_{\text{DCLK}} = \text{DCLK}$ 期間<br>$t_{\text{CDCLK}} = \text{サンプリング クロック立ち下がりエッジから DCLKIN 立ち下がりエッジまで}$              | $2 + T_{\text{DCLK}} + t_{\text{CDCLK}}$ | $3 + +$                | ns        |

|                                          |                                               | サンプリング クロックの立ち下がりエッジから DCLKIN 立ち下がりエッジまでの遅延 $\geq 2.5\text{ns}$ 。<br>$T_{\text{DCLK}} = \text{DCLK}$ 期間<br>$t_{\text{CDCLK}} = \text{サンプリング クロック立ち下がりエッジから DCLKIN 立ち下がりエッジまで}$ | $2 + t_{\text{CDCLK}}$                   | $3 + t_{\text{CDCLK}}$ |           |

## 5.8 タイミング要件 (続き)

特に記述のない限り、 $T_A = 25^\circ\text{C}$  における標準値、最小および最大のタイミング値は、 $T_{\text{MIN}} = -55^\circ\text{C} \sim T_{\text{MAX}} = 105^\circ\text{C}$  の全温度範囲で特性評価されていますが、生産試験は行われていません。その他の条件として、ADC サンプリング レート = 125MSPS、クロック デューティ比 = 50%、AVDD = IOVDD = 1.8V、外部リファレンス = 1.6V、入力信号 = -1dBFS の差動入力

| パラメータ                                        |                                                                    | テスト条件                             | 最小値  | 公称値  | 最大値 | 単位 |

|----------------------------------------------|--------------------------------------------------------------------|-----------------------------------|------|------|-----|----|

| $t_{\text{CD}}$                              | DCLK 立ち上がりエッジから出力データまでの遅延<br>2 線式 SLVDS、14 ビット                     | Fout = 65MSPS、DA/B0,1 = 455MBPS   | 0    | 0.1  |     | ns |

|                                              |                                                                    | Fout = 80MSPS、DA/B0,1 = 560MBPS   | 0    | 0.1  |     |    |

|                                              |                                                                    | Fout = 125MSPS、DA/B0,1 = 875MBPS  | -0.2 | 0.1  |     |    |

|                                              | DCLK 立ち上がりエッジから出力データまでの遅延<br>1 線式 SLVDS、14 ビット                     | Fout = 65MSPS、DA/B0 = 910MBPS     | 0    | 0.1  |     |    |

|                                              |                                                                    | FOUT = 10MSPS、DA / B0 = 160MBPS   | 0    | 0.1  |     |    |

|                                              |                                                                    | FOUT = 25MSPS、DA / B0 = 400MBPS   | 0    | 0.1  |     |    |

|                                              |                                                                    | FOUT = 62.5MSPS、DA / B0= 1000MBPS | -0.6 | 0.1  |     |    |

|                                              | DCLK 立ち上がりエッジから出力データまでの遅延<br>1/2 線式 SLVDS、16 ビット                   | FOUT = 5MSPS、DAO = 160MBPS        | 0    | 0.1  |     |    |

|                                              |                                                                    | FOUT = 10MSPS、DAO = 320MBPS       | 0    | 0.1  |     |    |

|                                              |                                                                    | FOUT = 25MSPS、DAO = 800MBPS       | 0    | 0.1  |     |    |

| $t_{\text{DV}}$                              | データ有効、2 線式 SLVDS、14 ビット                                            | Fout = 65MSPS、DA/B0,1 = 455MBPS   | 1.8  | 1.9  |     | ns |

|                                              |                                                                    | Fout = 80MSPS、DA/B0,1 = 560MBPS   | 1.4  | 1.5  |     |    |

|                                              |                                                                    | Fout = 125MSPS、DA/B0,1 = 875MBPS  | 0.6  | 0.8  |     |    |

|                                              | データ有効、1 線式 SLVDS、14 ビット                                            | Fout = 65MSPS、DA/B0 = 910MBPS     | 0.6  | 0.8  |     |    |

|                                              |                                                                    | FOUT = 10MSPS、DA / B0 = 160MBPS   | 5.7  | 5.8  |     |    |

|                                              |                                                                    | FOUT = 25MSPS、DA / B0 = 400MBPS   | 2.0  | 2.1  |     |    |

|                                              |                                                                    | FOUT = 62.5MSPS、DA / B0= 1000MBPS | 0.5  | 0.6  |     |    |

|                                              | データ有効、1/2 線式 SLVDS、16 ビット                                          | FOUT = 5MSPS、DAO = 160MBPS        | 5.7  | 5.8  |     |    |

|                                              |                                                                    | FOUT = 10MSPS、DAO = 320MBPS       | 2.7  | 2.8  |     |    |

|                                              |                                                                    | FOUT = 25MSPS、DAO = 800MBPS       | 0.8  | 0.9  |     |    |

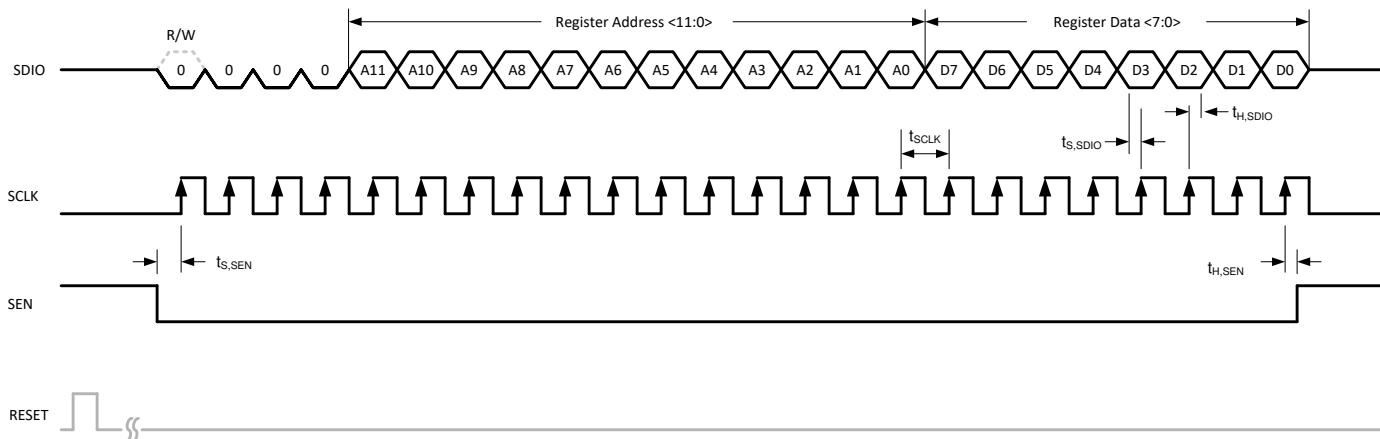

| シリアル プログラミング インターフェイス (SCLK, SEN, SDIO) - 入力 |                                                                    |                                   |      |      |     |    |

| $f_{\text{CLK,SCLK}}$                        | シリアル クロック周波数                                                       |                                   | 20   |      | MHz |    |

| $t_{\text{S,SEN}}$                           | SEN 立ち下がりエッジから SCLK 立ち上がりエッジまで                                     |                                   | 10   |      |     | ns |

| $t_{\text{H,SEN}}$                           | SCLK 立ち上がりエッジから SEN 立ち上がりエッジまで                                     |                                   | 9    |      |     |    |

| $t_{\text{S,SDIO}}$                          | SCLK の立ち上がりエッジからの SDIO セットアップ時間                                    |                                   | 17   |      |     |    |

| $t_{\text{H,SDIO}}$                          | SCLK の立ち上がりエッジからの SDIO ホールド時間                                      |                                   | 9    |      |     |    |

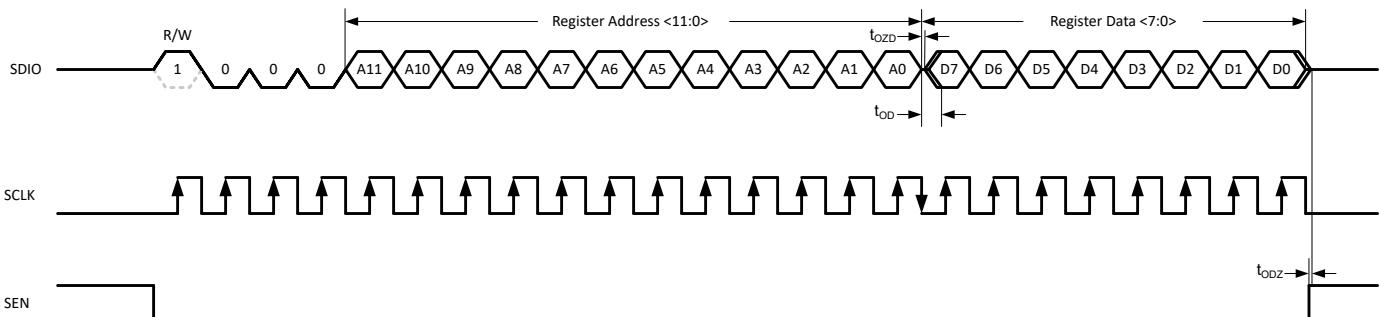

| シリアル プログラミング インターフェイス (SDIO) - 出力            |                                                                    |                                   |      |      |     |    |

| $t_{\text{OZD}}$                             | SDIO がトライステートから有効なデータに遷移するための読み出し動作中の、第 16 SCLK サイクルの立ち下がりエッジからの遅延 |                                   | 3.9  | 10.8 |     | ns |

| $t_{\text{ODZ}}$                             | SDIO がトライステートから有効なデータに遷移するための SEN 立ち上がりエッジからの遅延                    |                                   | 3.4  | 14   |     |    |

| $t_{\text{OD}}$                              | 読み出し動作中の 16 番目の SCLK サイクルの立ち下がりエッジから有効な SDIO までの遅延                 |                                   | 3.9  | 10.8 |     |    |

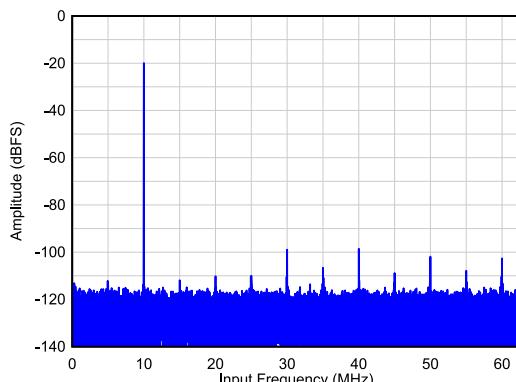

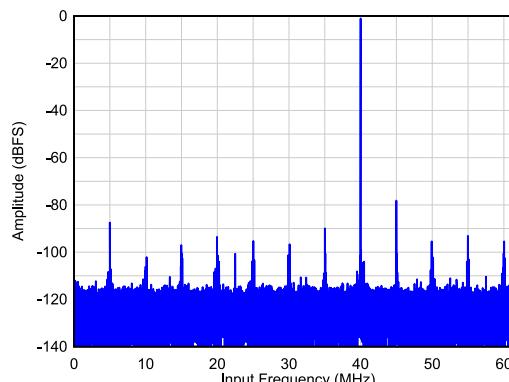

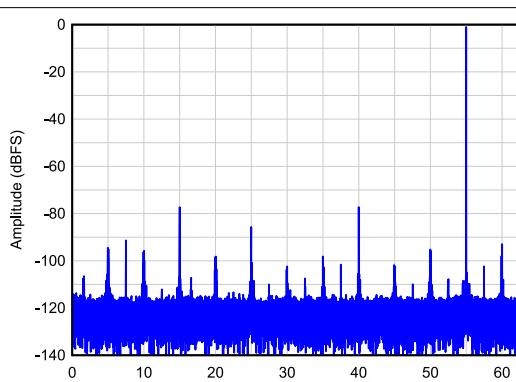

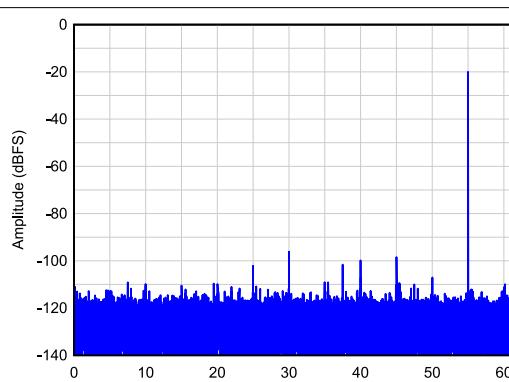

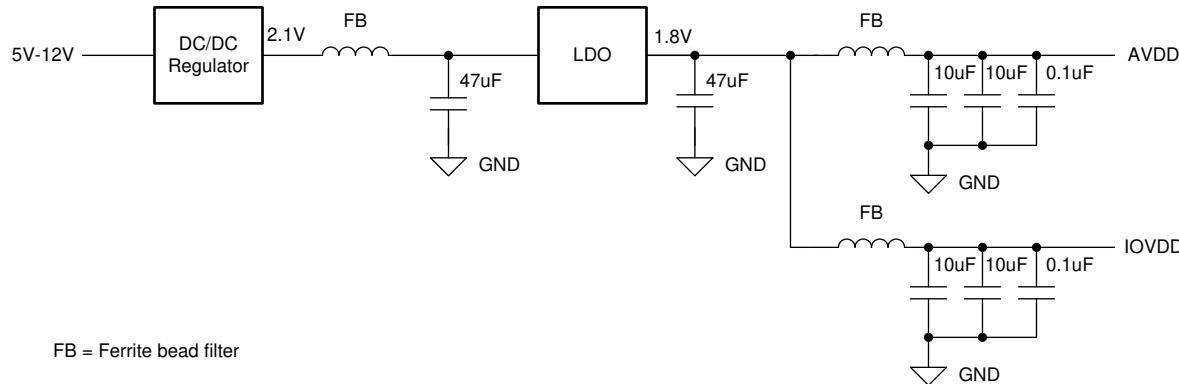

## 5.9 代表的特性

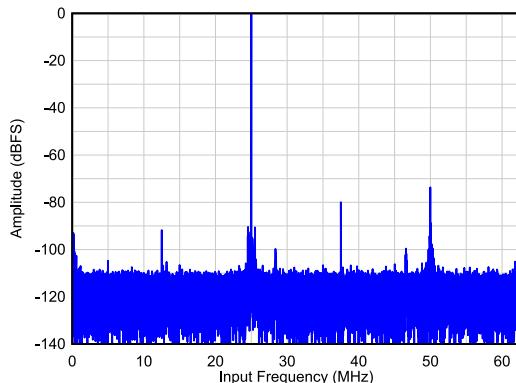

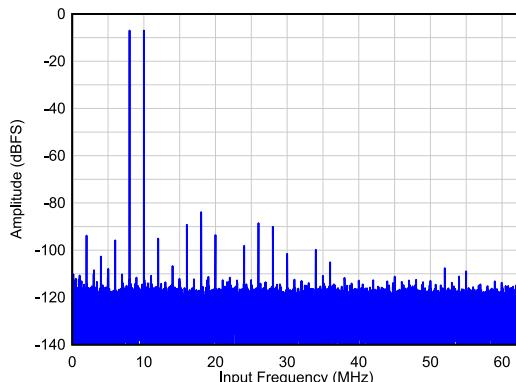

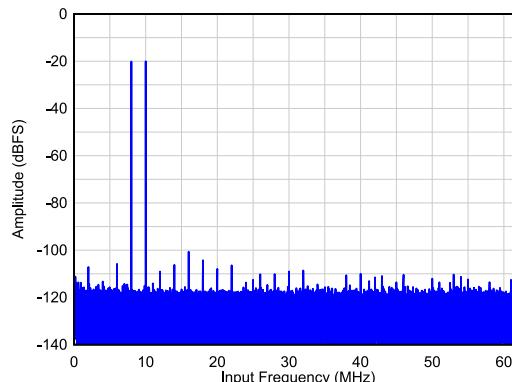

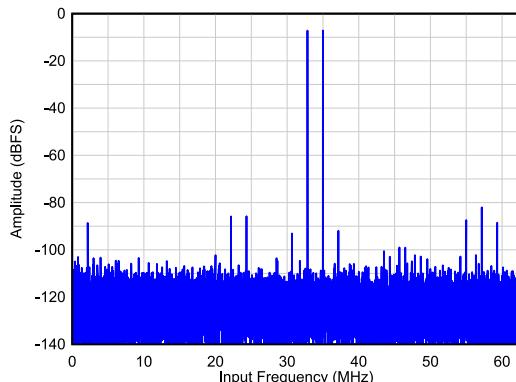

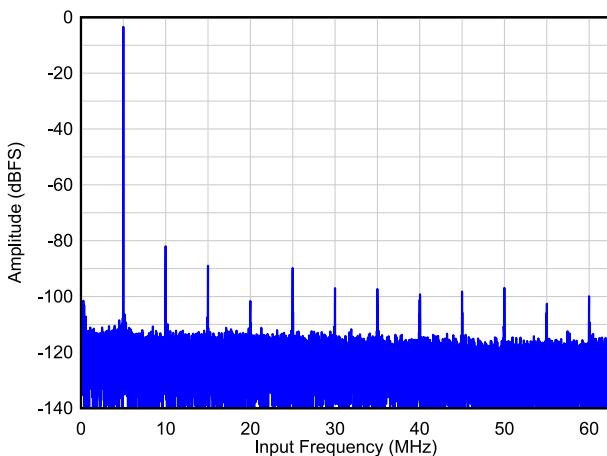

$T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、 $A_{IN} = -1\text{dBFS}$  差動入力、AVDD = IOVDD = 1.8V、1.6V 外部電圧リファレンス (特に記述のない限り)。

SNR = 77.5dBFS, HD2,3 = 85dBc, Non HD23 = 92dBFS

図 5-1.  $F_{IN} = 5\text{MHz}$  でのシングル トーン FFT

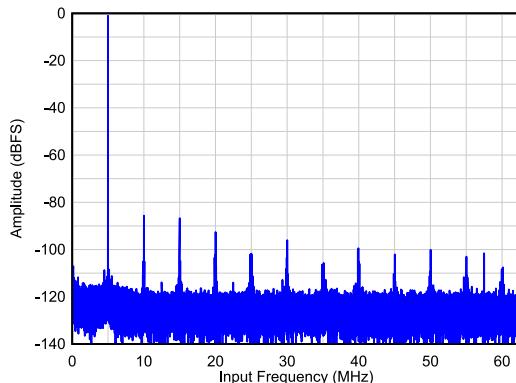

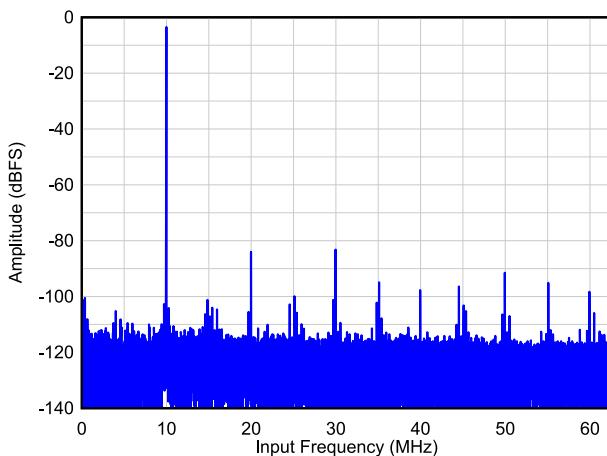

SNR = 77.5dBFS, HD2,3 = 78dBc, Non HD23 = 93dBFS

図 5-2.  $F_{IN} = 10\text{MHz}$  でのシングル トーン FFT

$A_{IN} = -20\text{dBFS}$ , SNR = 78.9dBFS, HD2,3 = 78dBc,

Non HD23 = 102dBFS

図 5-3.  $F_{IN} = 10\text{MHz}$  でのシングル トーン FFT

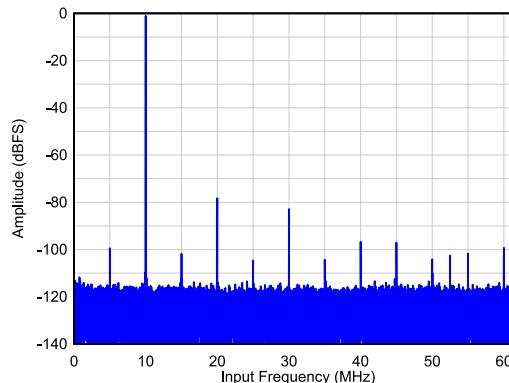

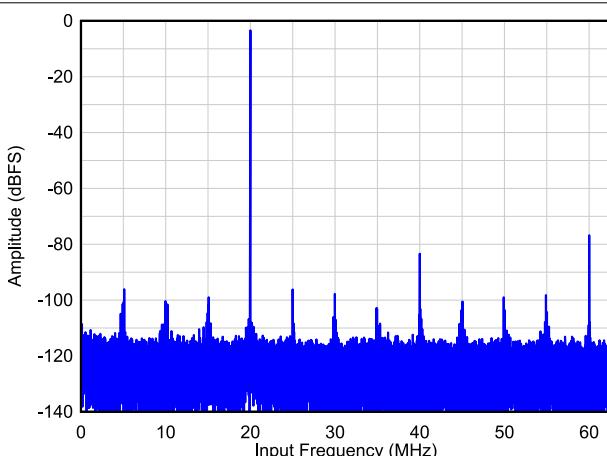

SNR = 76.9dBFS, HD2,3 = 78dBc, Non HD23 = 94dBFS

図 5-4.  $F_{IN} = 40\text{MHz}$  でのシングル トーン FFT

SNR = 75.5dBFS, HD2,3 = 77dBc, Non HD23 = 85dBFS

図 5-5.  $F_{IN} = 70\text{MHz}$  でのシングル トーン FFT

$A_{IN} = -20\text{dBFS}$ , SNR = 77.5dBFS, HD2,3 = 77dBc,

Non HD23 = 98dBFS

図 5-6.  $F_{IN} = 70\text{MHz}$  でのシングル トーン FFT

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、 $A_{\text{IN}} = -1\text{dBFS}$  差動入力、AVDD = IOVDD = 1.8V、1.6V 外部電圧リファレンス (特に記述のない限り)。

SNR = 71dBFS、HD2,3 = 73dBc、Non HD23 = 90dBFS

図 5-7.  $F_{\text{IN}} = 150\text{MHz}$  でのシングル トーン FFT

SNR = 69.5dBFS、HD2,3 = 61dBc、Non HD23 = 78dBc

図 5-8.  $F_{\text{IN}} = 190\text{MHz}$  でのシングル トーン FFT

$A_{\text{IN}} = -7\text{dBFS/tone}$ 、IMD3 = 88dBc

図 5-9.  $F_{\text{IN}} = 10/12\text{MHz}$  での 2 トーン FFT

$A_{\text{IN}} = -2\text{dBFS/tone}$ 、IMD3 = 85dBc

図 5-10.  $F_{\text{IN}} = 10/12\text{MHz}$  での 2 トーン FFT

$A_{\text{IN}} = -7\text{dBFS/tone}$ 、IMD3 = 85dBc

図 5-11.  $F_{\text{IN}} = 90/92\text{MHz}$  での 2 トーン FFT

$A_{\text{IN}} = -20\text{dBFS/tone}$ 、IMD3 = 80dBc

図 5-12.  $F_{\text{IN}} = 90/92\text{MHz}$  での 2 トーン FFT

## 5.9 代表的特性 (続き)

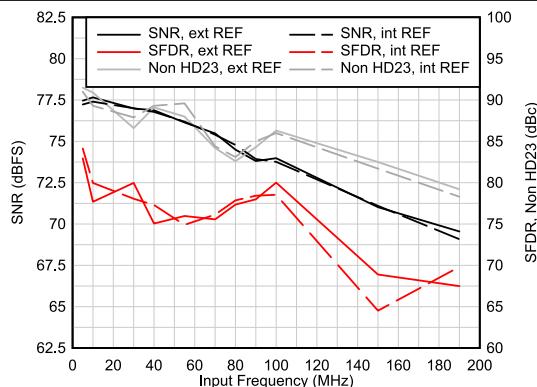

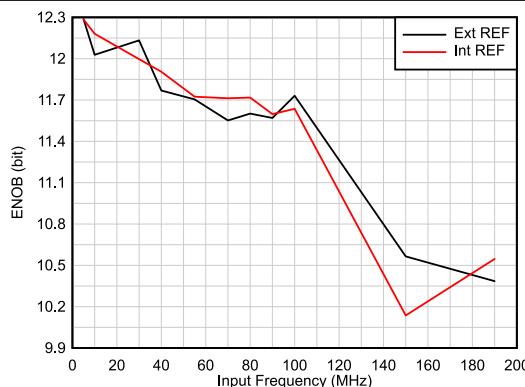

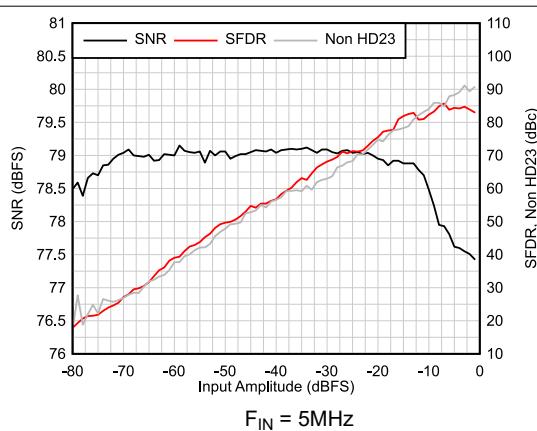

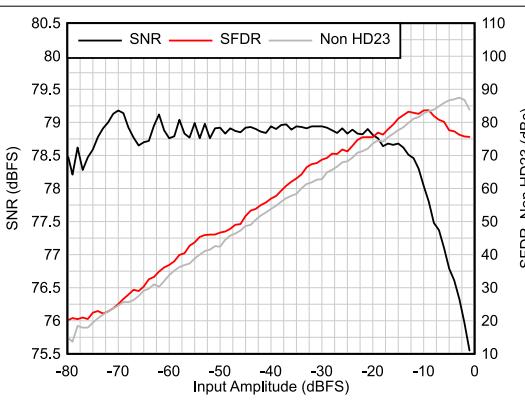

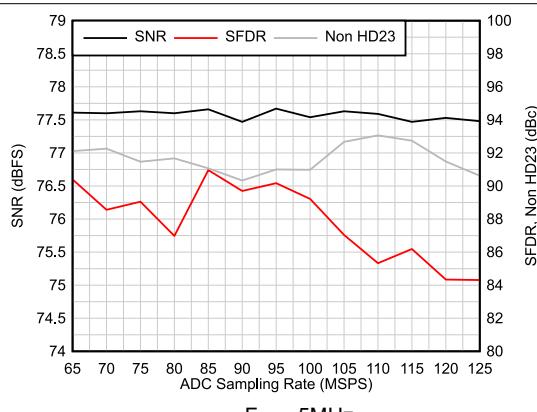

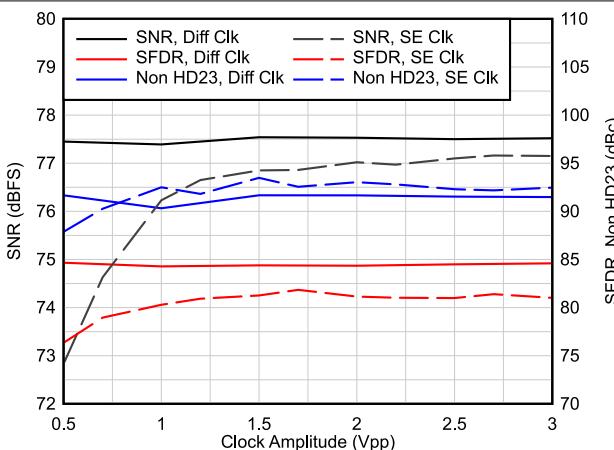

$T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、 $A_{IN} = -1\text{dBFS}$  差動入力、AVDD = IOVDD = 1.8V、1.6V 外部電圧リファレンス (特に記述のない限り)。

図 5-13. AC 性能と入力周波数との関係

図 5-14. ENOB と入力周波数との関係

図 5-15. SNR、SFDR と入力振幅との関係

図 5-16. AC 性能と入力振幅との関係

図 5-17. AC 性能とサンプリング レートとの関係

図 5-18. AC 性能とクロック振幅との関係

## 5.9 代表的特性 (続き)

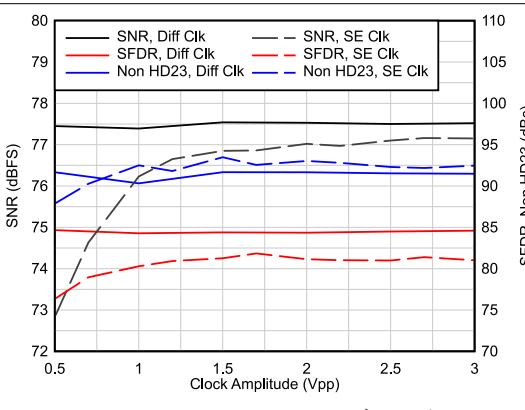

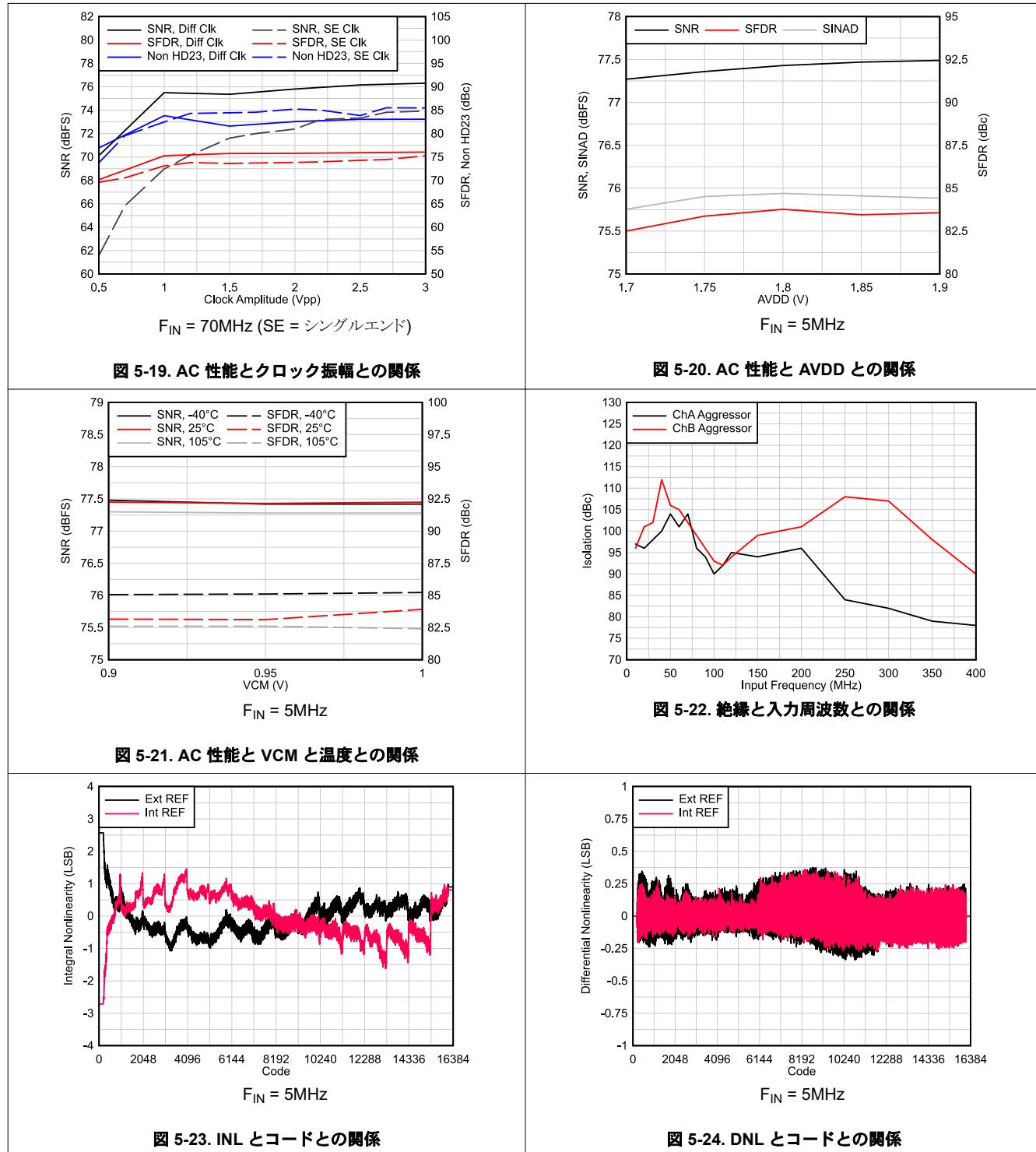

$T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、 $A_{IN} = -1\text{dBFS}$  差動入力、AVDD = IOVDD = 1.8V、1.6V 外部電圧リファレンス (特に記述のない限り)。

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 125MSPS、 $A_{IN} = -1\text{dBFS}$  差動入力、AVDD = IOVDD = 1.8V、1.6V 外部電圧リファレンス (特に記述のない限り)。

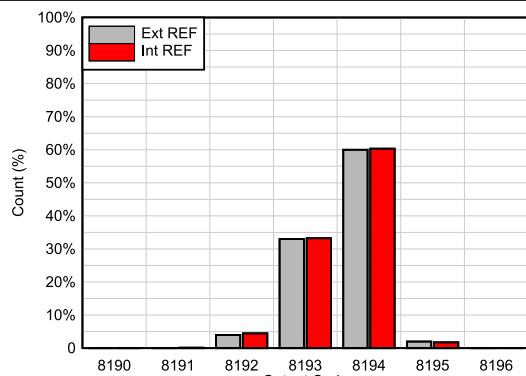

図 5-25. DC オフセットヒストグラム

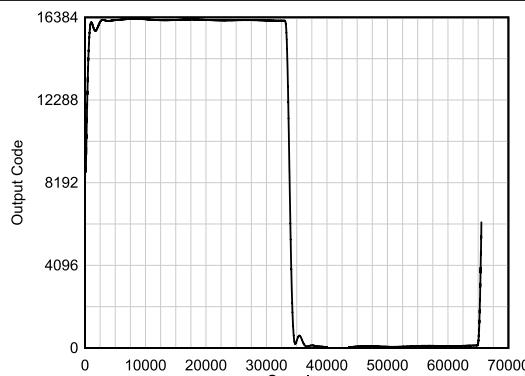

パルス入力 = 1MHz

図 5-26. パルス応答

F<sub>IN</sub> = 5MHz

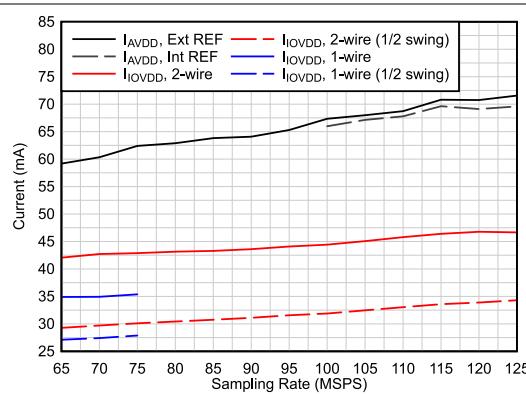

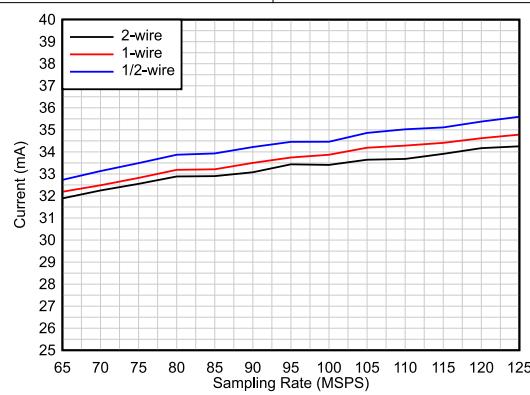

図 5-27. 消費電力とサンプリング レートとの関係

F<sub>IN</sub> = 5MHz, 2 線式

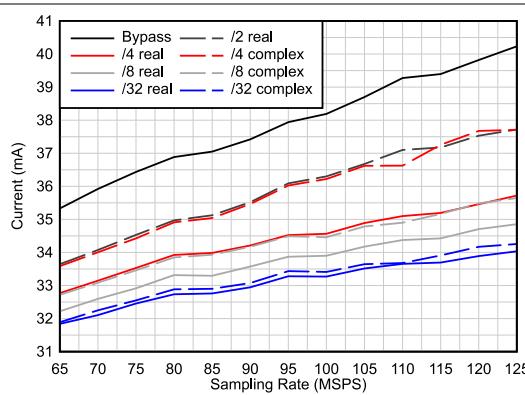

図 5-28. 消費電力とデシメーションとの関係

F<sub>IN</sub> = 5MHz, 32 による複素数デシメーション

図 5-29. 消費電力と出力インターフェイスとの関係

## 6 パラメータ測定情報

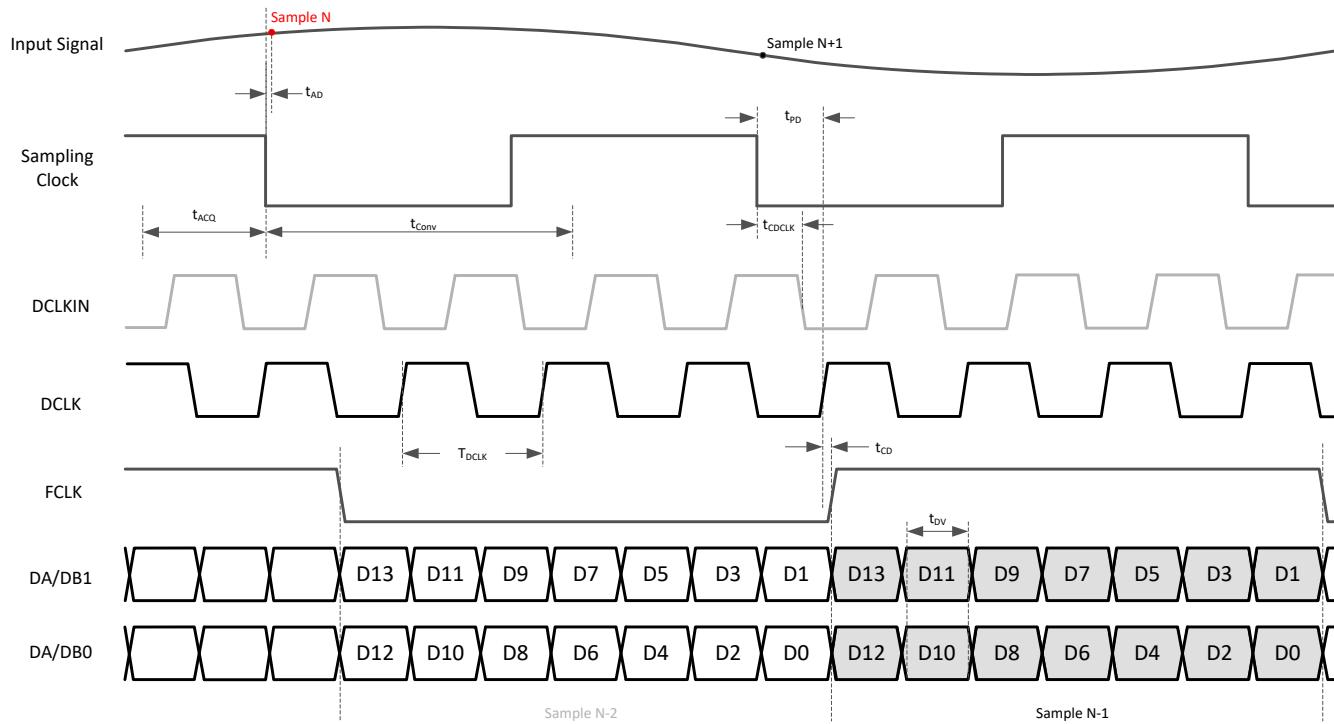

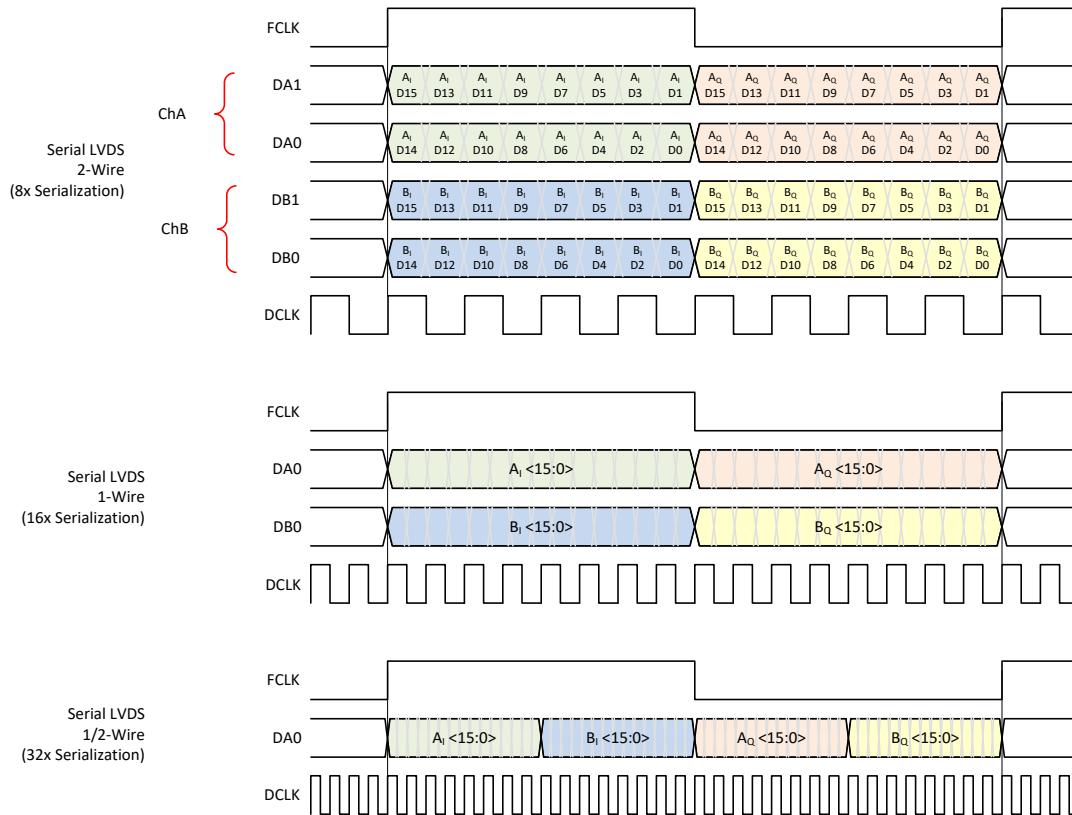

図 6-1. タイミング図：2 線式 SLVDS

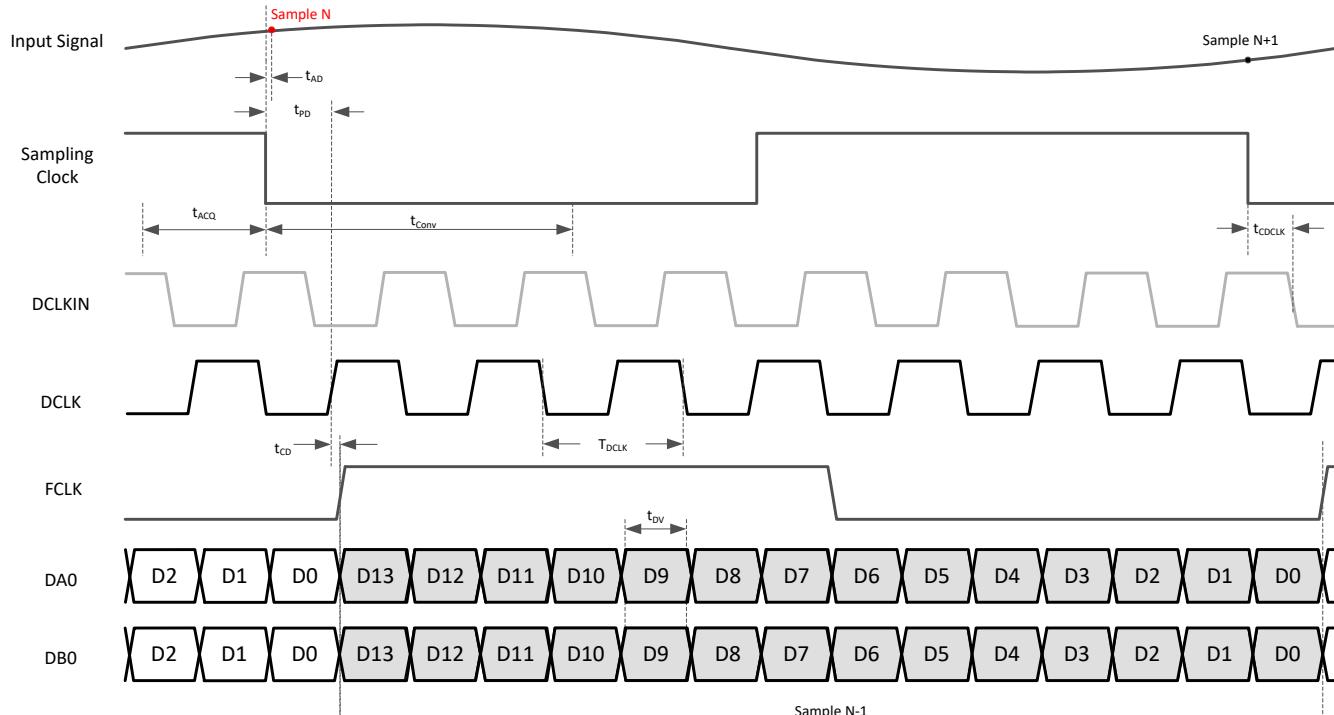

図 6-2. タイミング図：1 線式 SLVDS

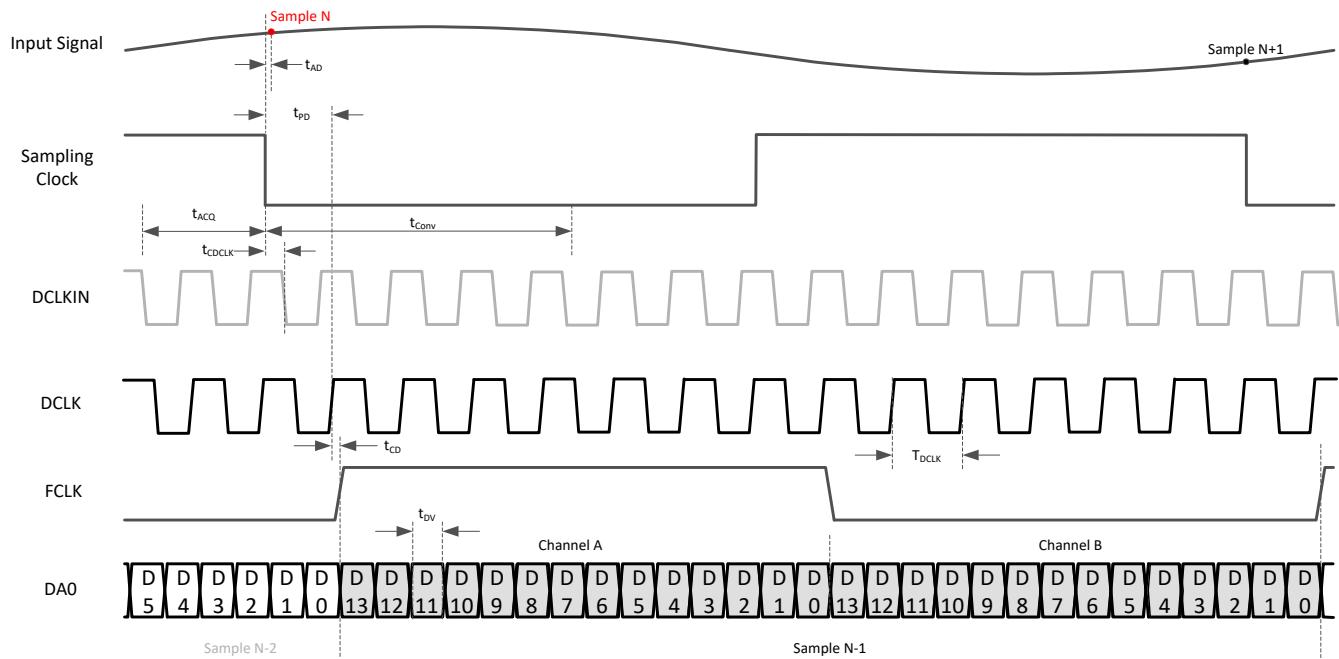

図 6-3. タイミング図 : 1/2 線式 SLVDS

## 7 詳細説明

### 7.1 概要

ADC3664-xEP は、最大 125MSPS のサンプリング レートに対応した、低ノイズ・超低消費電力の 14 ビット高速デュアル チャネル ADC です。このデバイスは、優れた直流精度と IF サンプリングへの対応を兼ね備えています。多様なアプリケーションに合わせて設計されたデバイスを作成できます。ADC3664-xEP にはオンチップの内部リファレンス機能が搭載されていますが、外部の高精度な 1.6V リファレンスや、外部 1.2V リファレンス (内部でバッファされ、ゲインがかけられる) にも対応しています。このデバイスは本質的に低レイテンシなアーキテクチャを採用しているため、デジタル出力インターフェイス上では、最短で 1 クロック サイクル後にデジタル出力結果を取得できます。

#### 注

ADC3664-xEP は、以下のサンプリング レートをサポートしています。

- 外部リファレンス: 1 ~ 125MSPS

- 内部リファレンス: 100 ~ 125MSPS

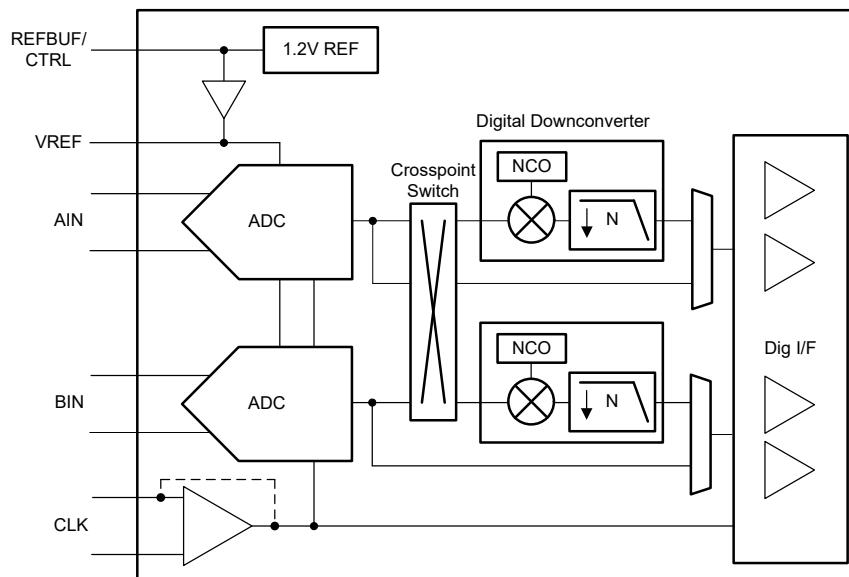

オプションのプログラマブルなデジタル ダウンコンバータにより、外部アンチエイリアス フィルタの設計を緩和できるほか、出力データ レートの低減も可能になります。デジタル フィルタは 32 ビット プログラマブル NCO を内蔵しており、実数または複素数の両方のデシメーションをサポートしています。

ADC3664-xEP は、シリアル LVDS (SLVDS) インターフェイスを使用してデータを出力し、デジタル相互接続の数を最小限に抑えます。このデバイスは、2 レーン (2 線式)、1 レーン (1 線式)、ハーフレーン (1/2 線式) のオプションをサポートしています。ADC3664-xEP は、14 ~ 20 ビットの出力分解能をサポートするデジタル出力フォーマッタを搭載しています。

デバイスの機能と制御オプションは、ピン構成または SPI レジスタ書き込みにより設定できます。

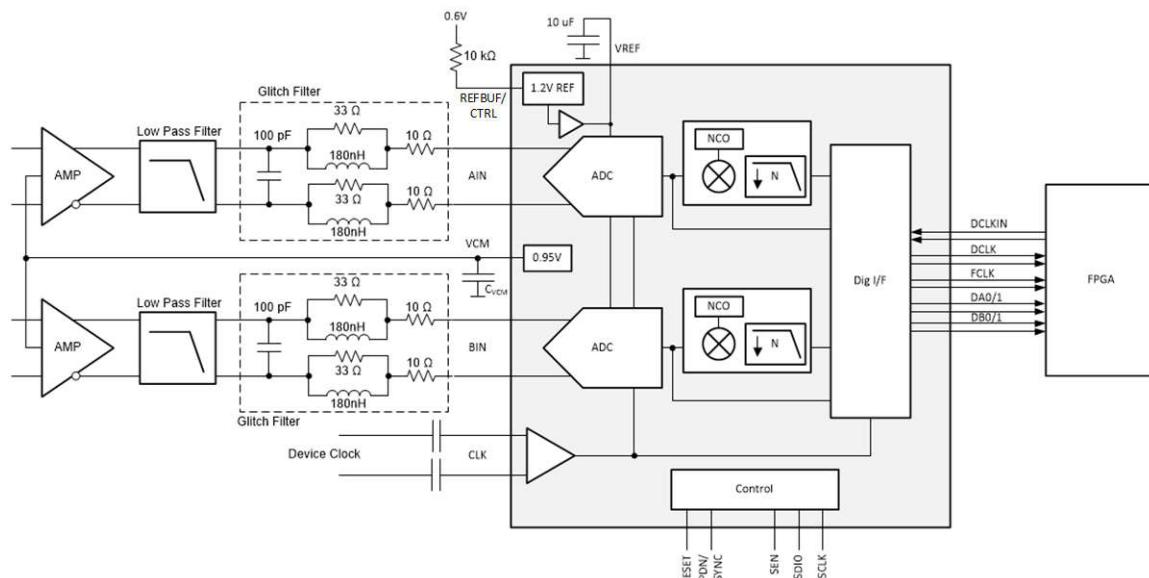

### 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 アナログ入力

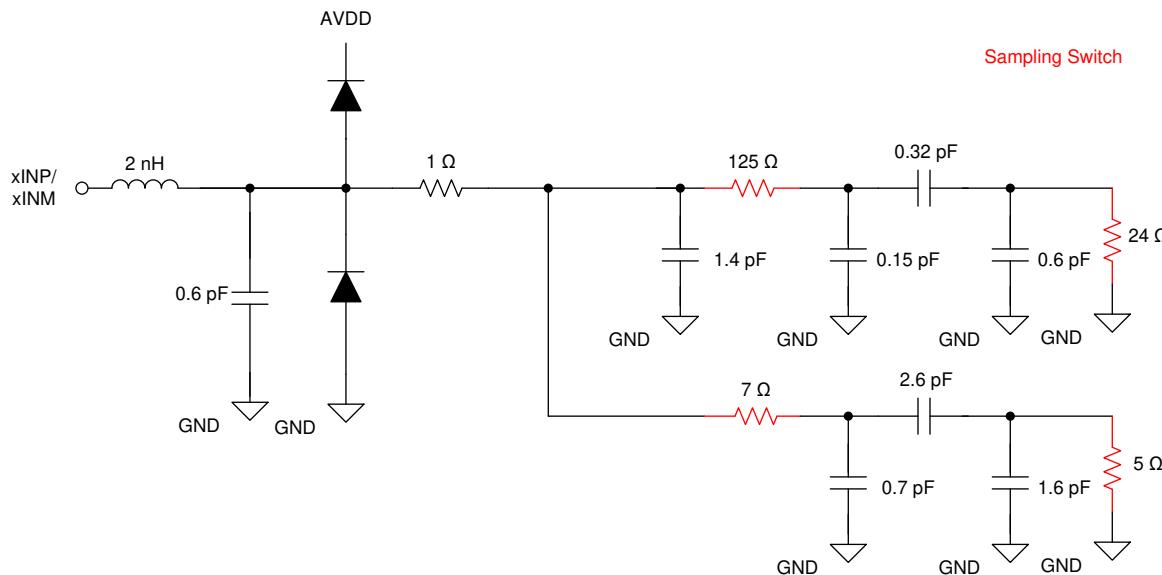

ADC3664-xEP のアナログ入力は、差動駆動することを目的としています。アナログ入力の AC 結合と DC 結合の両方がサポートされています。アナログ入力は、各入力ピンに外部から供給される 0.95V の入力同相電圧になるように設計されています。DC 結合入力信号は、デバイスの入力同相電圧範囲を満たす同相モード電圧を持つ必要があります。

等価入力回路のネットワーク表を 図 7-1 に示します。4 つのサンプリング スイッチすべてで、赤色で示したオン抵抗は同じ位置（開閉）に同時に存在します。

図 7-1. 等価入力ネットワーク

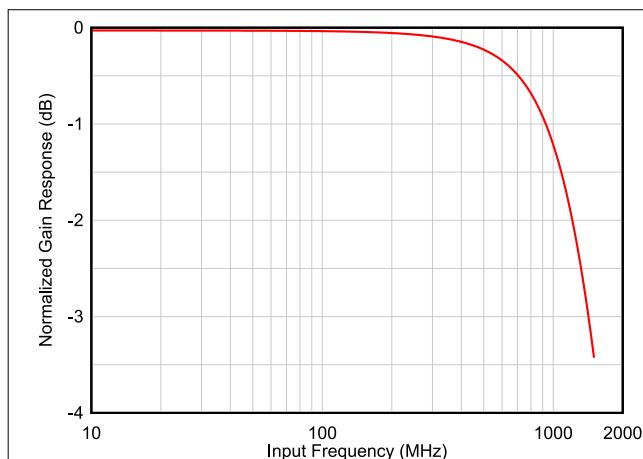

#### 7.3.1.1 アナログ入力帯域幅

図 7-2 に、50Ω の差動終端を使用した ADC3664-xEP のアナログ全電力入力帯域幅を示します。-3dB 帯域幅はおよそ 1.4GHz であり、良好な交流性能を保った実用的な入力帯域幅はおよそ 200MHz です。

等価差動入力抵抗  $R_{IN}$  および入力容量  $C_{IN}$  対周波数を図 7-3 に示します。

図 7-2. ADC アナログ入力帯域幅応答

図 7-3. 等価  $R_{IN}/C_{IN}$  と入力周波数との関係

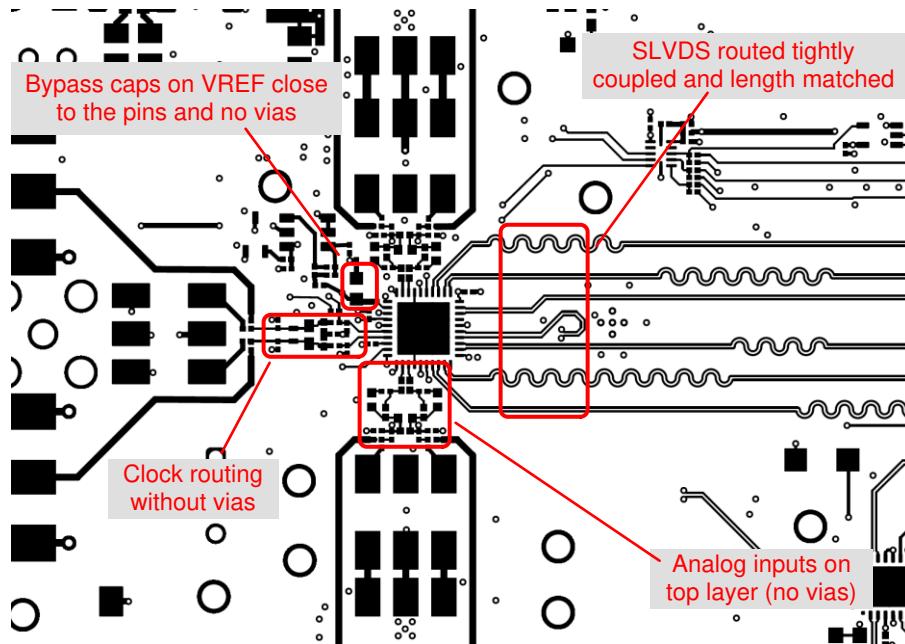

### 7.3.1.2 アナログ フロント エンド設計

ADC3664-xEP はバッファされていない ADC であるため、サンプリング動作によるグリッチを吸収するため、パッシブ キックバック フィルタを推奨します。入力がバランによって駆動されるか、低出力インピーダンスの差動アンプによって駆動されるかによって、終端ネットワークが必要になります。さらに、AC カップリング構成で使用する場合には、終端ネットワークと組み合わせた受動型の直流バイアス回路が必要です。

#### 7.3.1.2.1 サンプリング グリッチ フィルタ設計

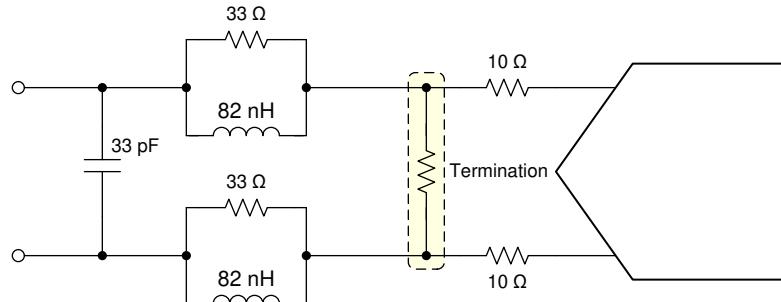

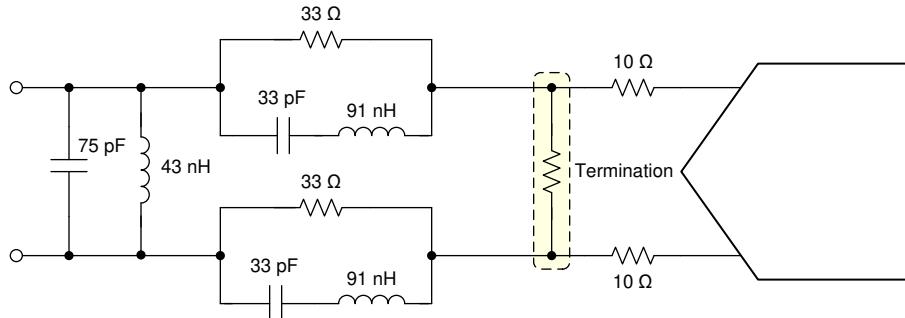

フロント エンドのサンプリング グリッチ フィルタは、ADC の SNR および HD3 性能を最適化するように設計されています。フィルタの性能は入力周波数に依存するため 図 7-5 および 図 7-4 に示すような異なる入力周波数範囲に対して、以下のフィルタ設計を推奨します（ソース インピーダンスが  $50\Omega$  と仮定）。

図 7-4. DC から 60MHz までの入力周波数のサンプリング グリッチ フィルタの例

図 7-5. 入力周波数が 60 ~ 120MHz のサンプリング グリッチ フィルタの例

### 7.3.1.2.2 アナログ入力終端およびDCバイアス

入力駆動回路によっては、終端ネットワークや DC バイアスを供給する必要があります。

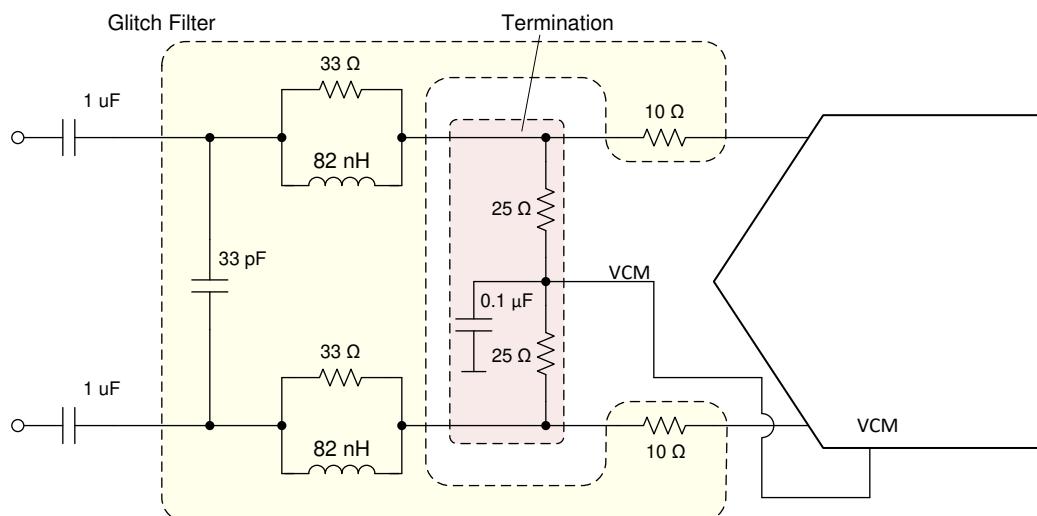

#### 7.3.1.2.2.1 AC 結合

ADC3664-xEP には、図 7-6 に示すように、ADC の同相出力電圧 (VCM) と終端回路を使用して、外部 DC バイアスが必要です。終端はグリッヂ フィルタ ネットワーク内に配置されています。入力でバランを使用する場合は、トランスの巻線比を考慮して終端インピーダンスを調整する必要があります。アンプを使用する場合は、終端インピーダンスが調整され、アンプ性能が最適化されます。

図 7-6. AC 結合: 終端ネットワークは DC バイアスを供給します(60MHz までのグリッヂ フィルタの例)

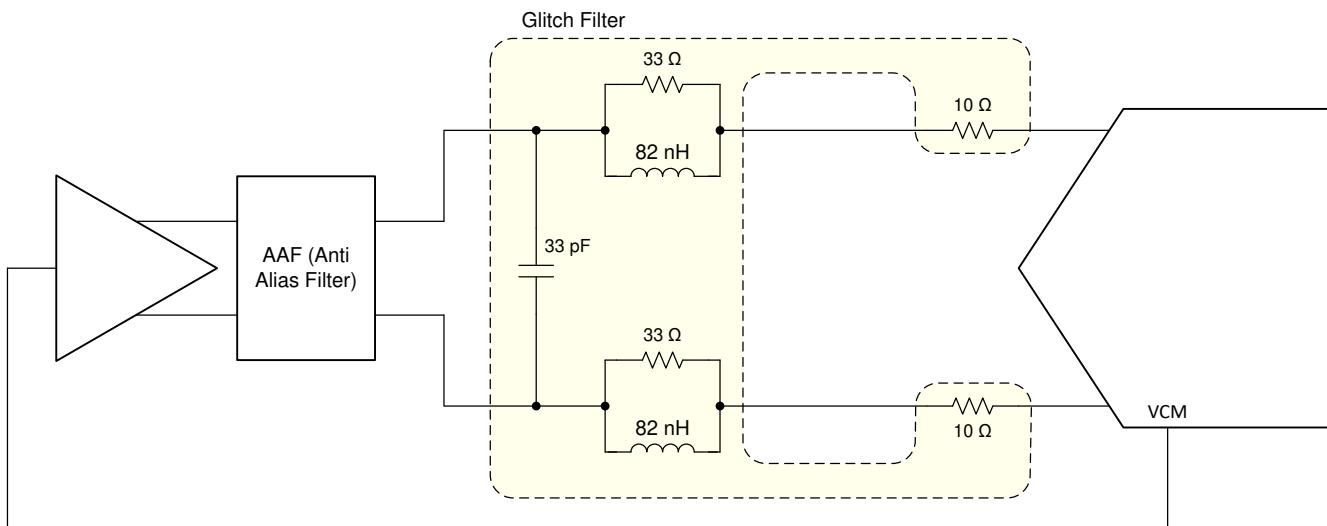

#### 7.3.1.2.2.2 DC 結合

DC 結合アプリケーションでは、図 7-7 に示すように ADC の VCM 出力を使用して、完全差動アンプ (FDA) から DC バイアスを供給する必要があります。この場合、グリッヂ フィルタは、アンチエイリアスフィルタと ADC の間に配置します。アンプが ADC の近くに配置されている場合、または終端がアンチエイリアスフィルタの一部である場合、終端は不要です。

図 7-7. DC 結合 : FDA から供給される直流バイアス (60MHz 向けのグリッヂ フィルタ例)

### 7.3.2 クロック入力

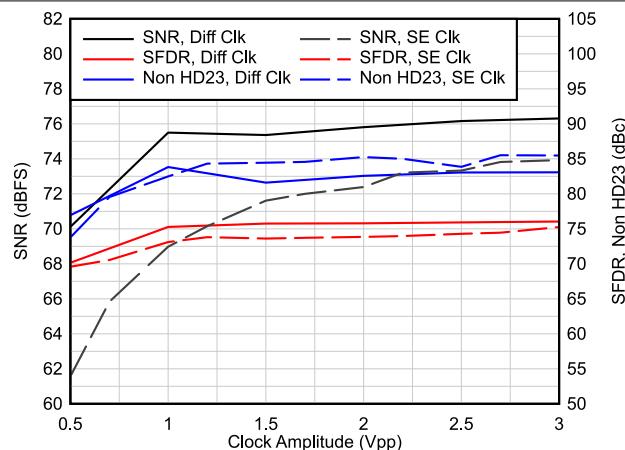

ADC の SNR 性能を最大化するには、外部サンプリング クロックを低ジッタかつ高スルーレートの差動信号伝送にする必要があります。これは、IF サンプリング アプリケーション（図 7-8 および 図 7-9）で特に重要です。ジッタの影響を受けにくいアプリケーション向けに、ADC3664-xEP ではシングルエンド信号処理で動作させるオプションを備えており、消費電力をさらに削減できます。

図 7-8.  $F_{IN} = 5\text{MHz}$  の AC 性能とクロック振幅との関係

図 7-9.  $F_{IN} = 70\text{MHz}$  の AC 性能とクロック振幅との関係

#### 7.3.2.1 シングルエンド入力 対 差動クロック入力

ADC3664-xEP は差動またはシングルエンドクロック入力で動作し、シングルエンドクロックの消費電力が小さくなります。しかしながら、クロック振幅は ADC のアペーチャジッタに影響し、結果として SNR にも影響を与えます。最大の SNR 性能を得るには、高速スルーレートの大規模クロック信号を供給する必要があります。

- 差動クロック入力: クロック入力は、外部で AC 結合されています。このデバイスには、その使用事例用の内部バイアスがあります。

- シングルエンドクロック入力このモードは、SPI レジスタ (0x0E, D2, D0) または REFBUF/CTRL ピンを使用して構成する必要があります。このモードでは、内部クロックのバイアスが存在しないため、クロック入力を 0.9V の中心付近で DC 結合する必要があります。未使用の入力はグランドに AC 結合する必要があります。

図 7-10. 差動 (左) クロック入力とシングルエンド (右) クロック入力を使用した外部と内部接続

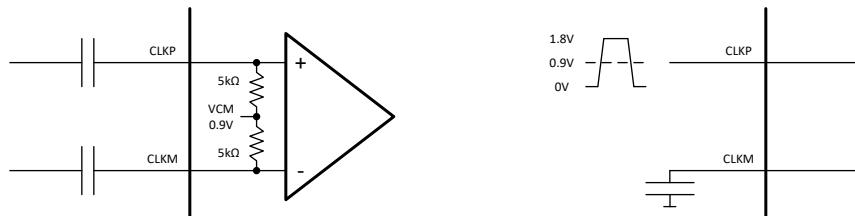

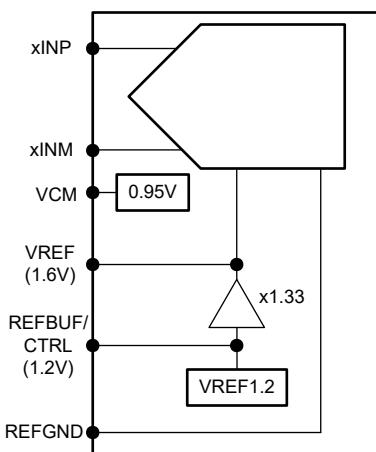

### 7.3.3 電圧リファレンス

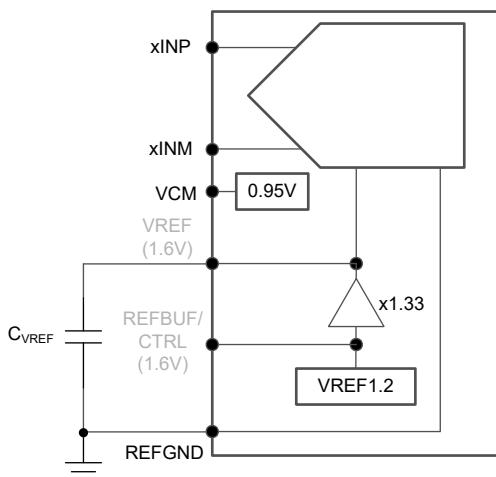

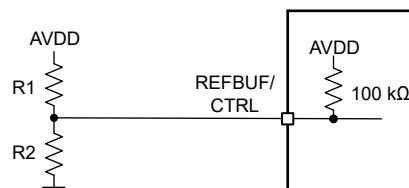

ADC3664-xEP には、ADC に電圧リファレンスを供給するための 3 種類のオプションがあります。外部の 1.6V リファレンスは VREF 入力に直接接続されます。1.2V のリファレンス電圧は、内部ゲイン バッファを使用して REFBUF/CTRL 入力に接続されるか、または内部の 1.2V リファレンスを有効にして 1.6V のリファレンス電圧を生成することもできます。最高の性能を得るために、VREF ピンには  $10\mu\text{F}$  と  $0.1\mu\text{F}$  のセラミック バイパス コンデンサを接続してリファレンス ノイズをフィルタリングする必要があります。図 7-11 に ADC3664-xEP の内部リファレンス回路を示します。

#### 注

電圧リファレンス モードは、SPI 書き込みを使用して、または REFBUF/CTRL ピン（デフォルト）を制御ピン（セクション 7.5.1）として使用して選択します。REFBUF/CTRL ピンを設定用に使用しない場合でも、このピンは AVDD に接続する必要があります（REFBUF/CTRL ピンには AVDD への弱い内部ブルアップがあります）。また、電圧リファレンスの選択は SPI インターフェイスを使用して行う必要があります。

図 7-11. ADC3664-xEP の電圧リファレンスのオプション

#### 7.3.3.1 内部基準電圧

ADC 用の 1.6V リファレンスは、オンチップの 1.2V リファレンスと内部のゲインバッファを用いて内部的に生成されます。 $10\mu\text{F}$  および  $0.1\mu\text{F}$  のセラミック バイパス コンデンサ ( $C_{VREF}$ ) を、VREF ピンと REFGND ピンの間に、できる限りピンの近くに接続する必要があります。

図 7-12. 内部リファレンス

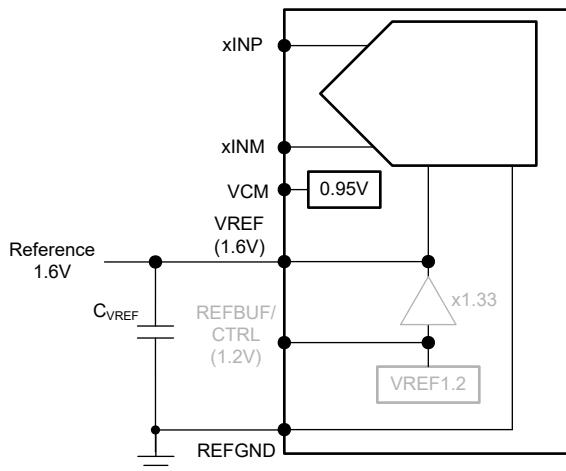

### 7.3.3.2 外部基準電圧 (VREF)

最高の精度と最小の温度ドリフトを得るために、VREF 入力を外部の 1.6V リファレンスに直接接続します。10 $\mu$ F および 0.1 $\mu$ F セラミック バイパス コンデンサ ( $C_{VREF}$ ) を VREF ピンと REFGND ピンの間に接続し、可能な限りこれらのピンの近くに配置することが推奨します。外部リファレンスからの負荷電流は約 1mA です。

注

内部リファレンスはデバイス内の他の機能にも使用されているため、リファレンス アンプは電源オフ状態のときにのみ停止させる必要があり、通常動作中には停止させないようにします。

図 7-13. 1.6V 外部リファレンス

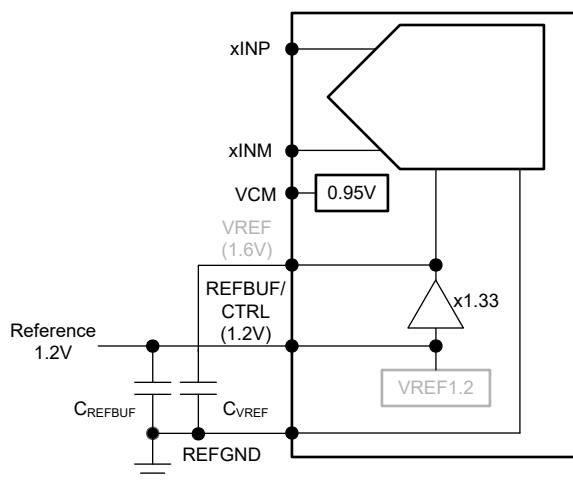

### 7.3.3.3 内部バッファ付き外部基準電圧 (REFBUF/CTRL)

ADC3664-xEP は、外部の 1.2V リファレンスから 1.6V のリファレンス電圧を生成するためのゲインも備えたオンチップのリファレンスバッファが搭載されています。VREF ピンと REFGND ピンの間に 10 $\mu$ F および 0.1 $\mu$ F のセラミック バイパス コンデンサ ( $C_{VREF}$ ) を、また REFBUF/CTRL ピンと REFGND ピンの間に 10 $\mu$ F および 0.1 $\mu$ F のセラミック バイパス コンデンサを接続することが推奨されています。バイパスコンデンサはピンにできるだけ近付けて配置します。外部リファレンスからの負荷電流は 100 $\mu$ A 未満です。

図 7-14. 内部リファレンス バッファを使用した外部 1.2V リファレンス

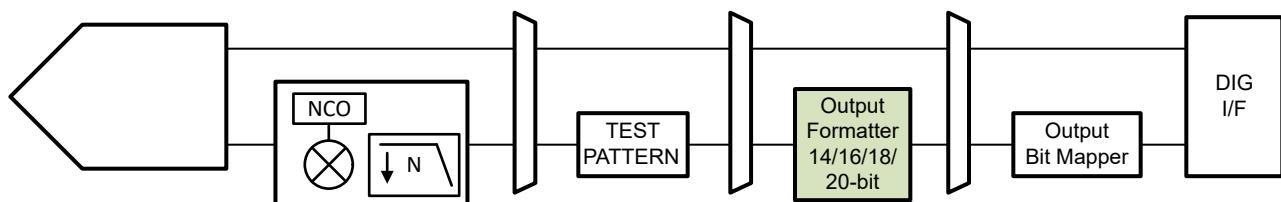

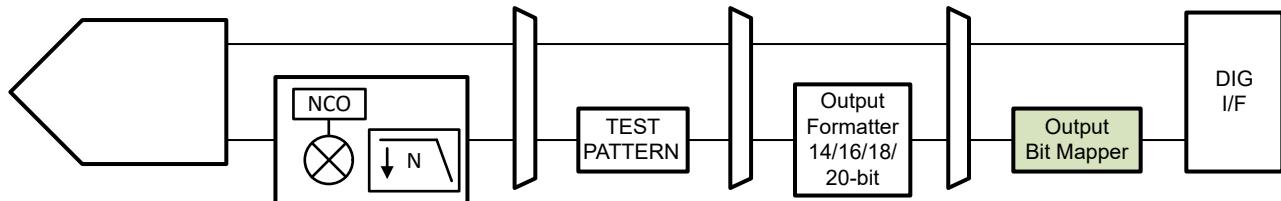

### 7.3.4 デジタルダウンコンバータ

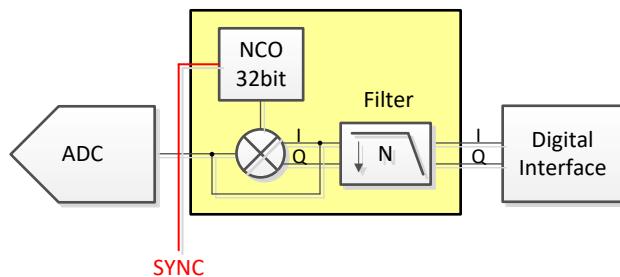

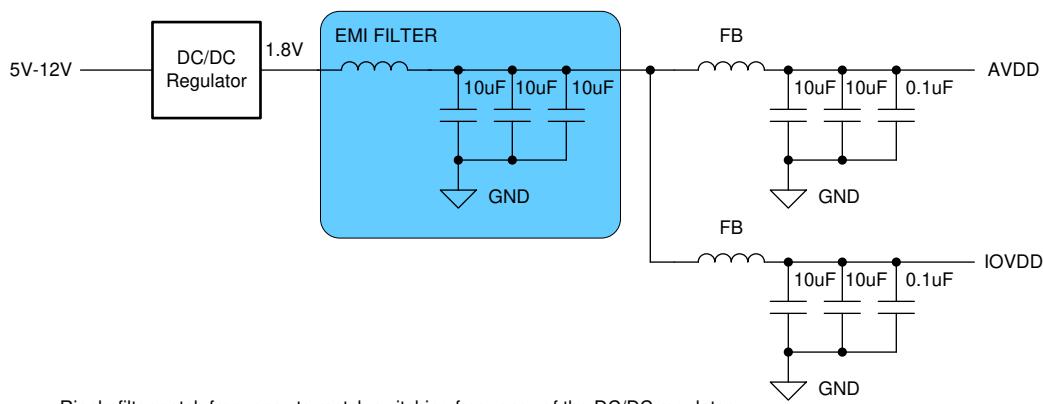

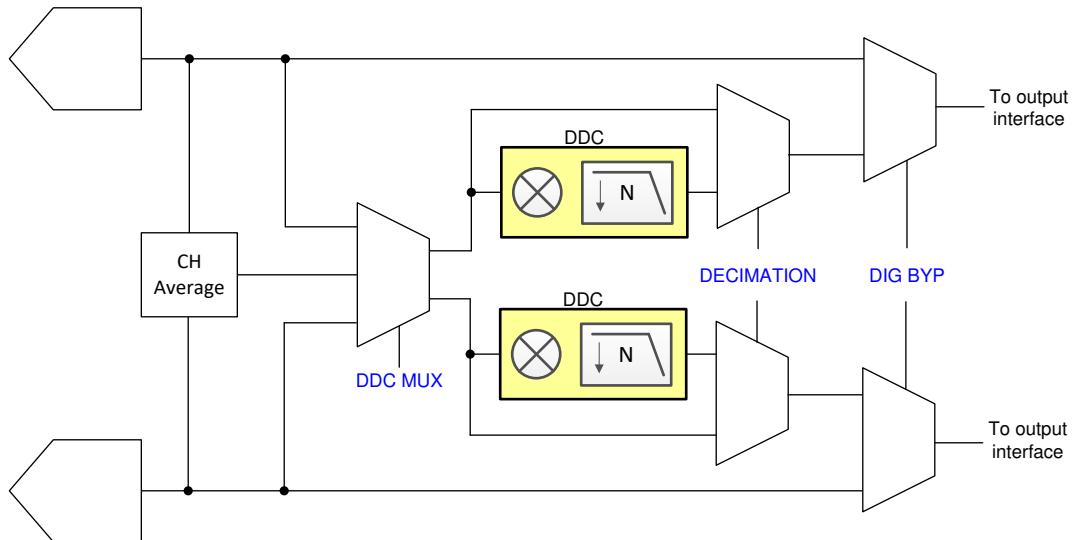

ADC3664-xEP は、オプションのオンチップ デジタル ダウン変換 (DDC) デシメーション フィルタを内蔵しており、SPI レジスタ設定によりこのフィルタを有効化できます。図 7-15 に示すように、デジタル ミキサと 32 ビット数値制御発振器 (NCO) を使用した、2, 4, 8, 16, 32 による複素数デシメーションをサポートしています。さらに、デバイスは実数デシメーション モードをサポートしており、このモードではコンプレックス ミキサがバイパスされます (最低消費電力を得るために NCO を 0 に設定する必要があります)。この場合、デジタル フィルタはロー パス フィルタとして動作します。

内部では、デシメーション フィルタの演算は 20 ビットの解像度で実行されており、量子化ノイズによる SNR の劣化を防いでいます。出力フォーマット は、デジタル インターフェイスにデータを出力する前に、選択した解像度に切り捨てられます。

図 7-15. 内部デジタル デシメーション フィルタ

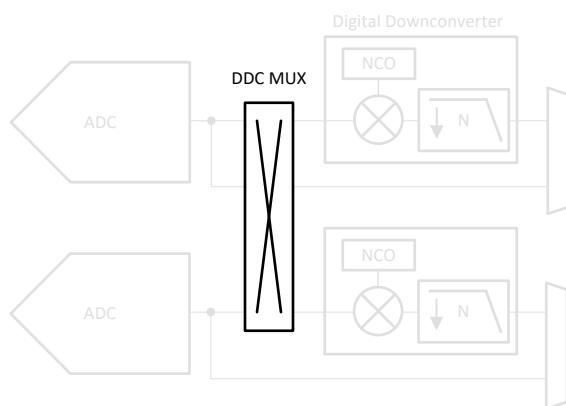

#### 7.3.4.1 DDC MUX

ADC3664-xEP はデジタル デシメーション フィルタの前に MUX を内蔵しており、ADC チャネル A 入力をチャネル B の DDC に接続できます

図 7-16. DDC MUX

### 7.3.4.2 デジタル フィルタ動作

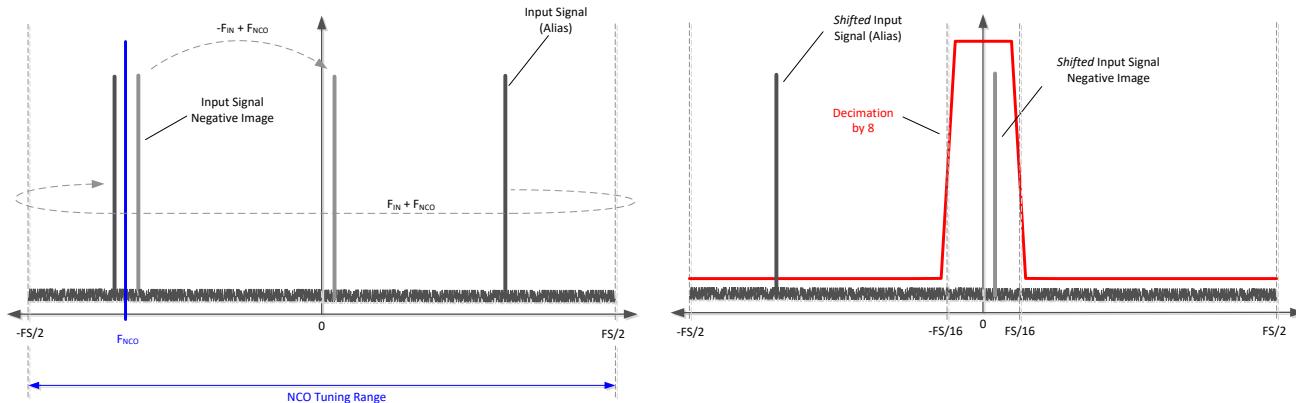

複素数デシメーション動作を、図 7-17 に示します。まず、入力信号（およびその負のイメージ信号）は、左図に示されているように、NCO 周波数によって周波数がシフトされます。次に、0Hz を中心としたデジタル フィルタが適用され、出力データレートがデシメートされます。この例では、出力データレート  $F_{S,OUT} = F_S/8$  と、ナイキストゾーン  $F_S/16$  を使用しています。複素ミキシングの過程で、スペクトル（信号およびノイズ）は実部と虚部に分割されるため、振幅は 6dB 低下します。この損失を補償するために、デシメーション フィルタ ブロックには 6dB のデジタル ゲイン オプションが用意されており、SPI 書き込みによって有効にできます。

図 7-17. 複雑なデシメーションの説明図

実際のデシメーション動作を、図 7-18 の例に示します。周波数シフトは発生せず、複素デジタル フィルタの実数部分のみが実行されます。出力データレートはデシメーションされます。デシメーション率を 8 に設定すると、出力データレート  $F_{S,OUT} = F_S/8$  が得られ、ナイキストゾーン  $F_S/16$  が得られます。

実数ミキシングの過程では、スペクトル（信号およびノイズ）の振幅が 3dB 低下します。この損失を補償するために、デシメーション フィルタ ブロックには 3dB のデジタル ゲイン オプションが用意されており、SPI 書き込みによって有効にできます。

図 7-18. 実数デシメーションのイラスト

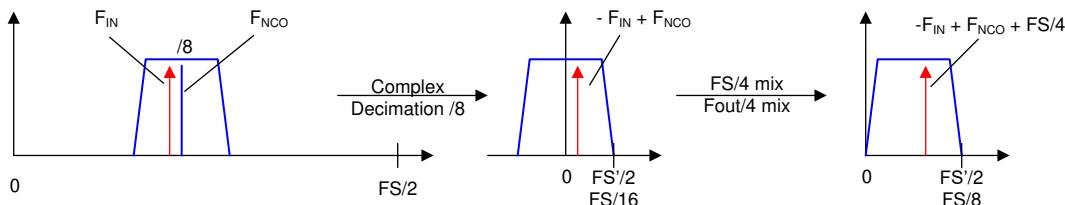

### 7.3.4.3 FS/4 ミキシングと実数出力

このモードでは、複素数デシメーション後の出力が  $FS/4$  (ここでの  $FS$  は出力データレート) とミキシングされます。入力信号が  $0\text{Hz}$ を中心とした複素出力として送信される代わりに、図 7-19 に示すように、このモードでは出力は実数出力として 2 倍のデータレートで送信され、信号は  $FS/4$  ( $F_{out}/4$ ) を中心とした周波数に配置されます。

この例では、8 による複素数デシメーションを使用しています。出力データは、実際の出力として、出力レート  $F_{out} = FS'/4$  ( $FS' = \text{ADC サンプリング レート}$ ) で送信されます。入力信号は  $FS/4$  ( $F_{out}/4$ ) または  $FS'/16$  を中心としました。

図 7-19. FS/4 ミキシングと実数出力

### 7.3.4.4 数値制御発振器 (NCO) およびデジタルミキサ

デシメーション ブロックには 32 ビットの NCO とデジタルミキサが搭載されており、デジタル フィルタ処理の前に周波数位置を細かく調整できます。発振器は、次のような複素指数関数列を生成します。

$e^{j\omega n}$  (default) or  $e^{-j\omega n}$

ここで、周波数 ( $\omega$ ) は 32 ビット レジスタ設定により符号付き数値として指定されます

複素指数関数列に ADC からの実数入力を乗算し、目的のキャリアを  $f_{IN} + f_{NCO}$  に等しい周波数にミックスします。NCO 周波数は  $-FS/2$  から  $+FS/2$  の範囲で調整でき、符号付き 2 の補数として処理されます。新しい NCO 周波数をプログラムした後、その周波数を有効にするには、MIXER RESTART レジスタ ビットまたは SYNC ピンをトグルさせる必要があります。さらに、ADC3664-xEP では、SPI を使用してミキサ位相を反転させるオプションを利用できます。

NCO 周波数の設定は、32 ビットのレジスタ値によって設定され、次のように計算されます。

$$\text{NCO frequency} = 0 \text{ to } +FS/2: \text{NCO} = f_{NCO} \times 2^{32} / FS \quad (1)$$

$$\text{NCO frequency} = -FS/2 \text{ to } 0: \text{NCO} = (f_{NCO} + FS) \times 2^{32} / FS \quad (2)$$

ここで

- NCO = NCO レジスタ設定 (10 進値)

- $f_{NCO}$  = 目標とする NCO 周波数 (MHz)

- $FS$  = ADC サンプリング レート (MSPS)

NCO プログラミングをこの例で説明します。

- ADC サンプリング レート  $FS = 125\text{MSPS}$

- 入力信号  $f_{IN} = 10\text{MHz}$

- 目的の出力周波数  $f_{OUT} = 0\text{MHz}$

この例では、NCO をプログラムして目的の出力周波数を実現する方法は実際には 4 つあります(表 7-1 を参照)。

表 7-1. NCO 値の計算例

| エイリアスまたはネガティブイメージ        | $f_{NCO}$                 | NCO 値      | ミキサ段階 | $f_{OUT}$ の周波数変換                                                            |

|--------------------------|---------------------------|------------|-------|-----------------------------------------------------------------------------|

| $f_{IN} = -10\text{MHz}$ | $f_{NCO} = 10\text{MHz}$  | 343597384  | そのまま  | $f_{OUT} = f_{IN} + f_{NCO} = -10\text{MHz} + 10\text{MHz} = 0\text{MHz}$   |

| $f_{IN} = 10\text{MHz}$  | $f_{NCO} = -10\text{MHz}$ | 4638564680 |       | $f_{OUT} = f_{IN} + f_{NCO} = 10\text{MHz} + (-10\text{MHz}) = 0\text{MHz}$ |

表 7-1. NCO 値の計算例 (続き)

| エイリアスまたはネガティブイメージ        | f <sub>NCO</sub>          | NCO 値      | ミキサ段階 | f <sub>OUT</sub> の周波数変換                                                          |

|--------------------------|---------------------------|------------|-------|----------------------------------------------------------------------------------|

| f <sub>IN</sub> = 10MHz  | f <sub>NCO</sub> = 10MHz  | 343597384  | 反転    | f <sub>OUT</sub> = f <sub>IN</sub> - f <sub>NCO</sub> = 10MHz - 10MHz = 0MHz     |

| f <sub>IN</sub> = -10MHz | f <sub>NCO</sub> = -10MHz | 4638564680 |       | f <sub>OUT</sub> = f <sub>IN</sub> - f <sub>NCO</sub> = -10MHz - (-10MHz) = 0MHz |

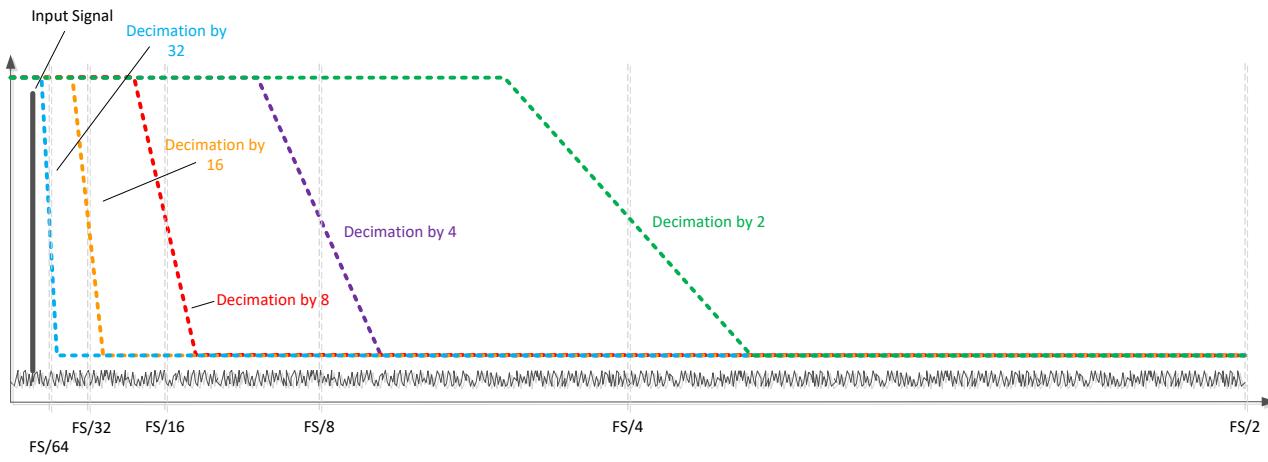

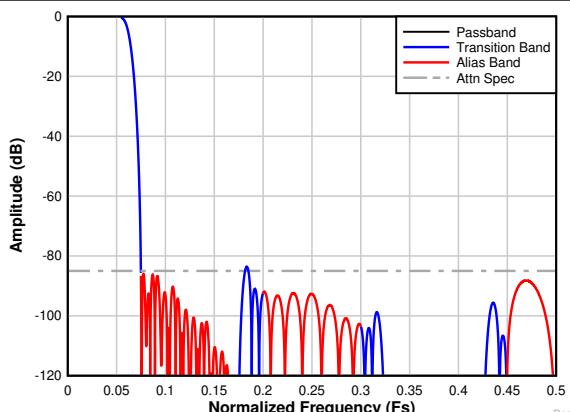

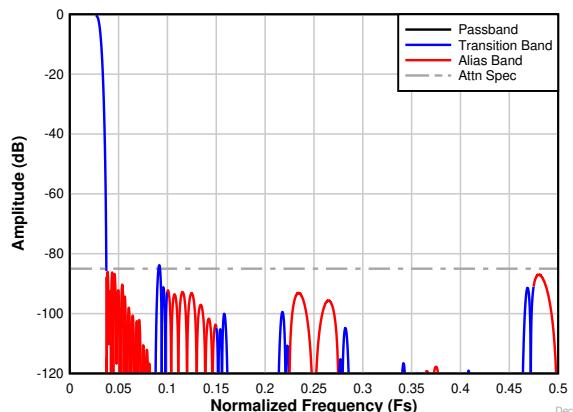

#### 7.3.4.5 デシメーション フィルタ

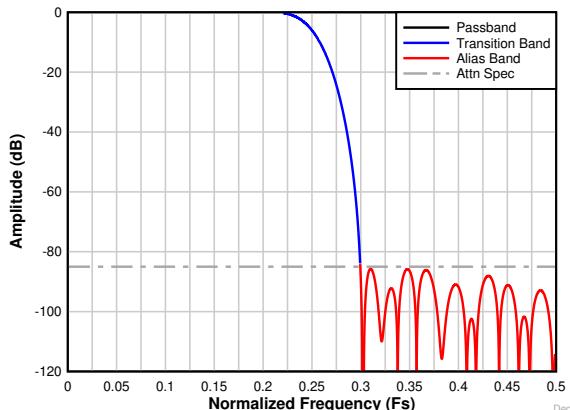

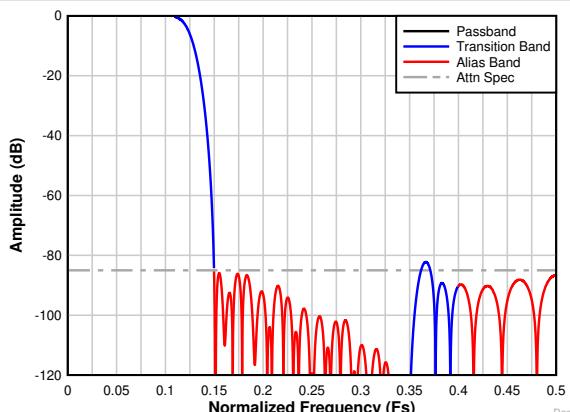

ADC3664-xEP は、パスバンド帯域幅が約 80%、85dB 以上のストップバンド除去で、2、4、8、16、32 による複素数デシメーションをサポートしています。ADC サンプリング レート  $F_S$  に対する各種デシメーション設定でのパスバンド帯域幅の概要を、表 7-2 に示します。実数デシメーション モードでは、出力帯域幅は複素数帯域幅の半分です。

表 7-2. デシメーション フィルタの概要と使用可能な最大出力帯域幅

| 実数または複素数の<br>デシメーション | デシメーション設<br>定 N | 出力レート         | 出力帯域幅                 | 出力レート<br>( $F_S = 125\text{MSPS}$ ) | 出力帯域幅<br>( $F_S = 125\text{MSPS}$ ) |

|----------------------|-----------------|---------------|-----------------------|-------------------------------------|-------------------------------------|

| 複雑                   | 2               | $F_S / 2$ 複素数 | $0.8 \times F_S / 2$  | 62.5MSPS 複素                         | 50MHz                               |

|                      | 4               | $F_S / 4$ 複雑  | $0.8 \times F_S / 4$  | 31.25MSPS 複素                        | 25MHz                               |

|                      | 8               | $F_S / 8$ 複雑  | $0.8 \times F_S / 8$  | 15.625MSPS 複素                       | 12.5MHz                             |

|                      | 16              | $F_S / 16$ 複雑 | $0.8 \times F_S / 16$ | 7.8125MSPS 複素                       | 6.25MHz                             |

|                      | 32              | $F_S / 32$ 複雑 | $0.8 \times F_S / 32$ | 3.90625MSPS 複素                      | 3.125MHz                            |

| 実数                   | 2               | $F_S / 2$ 実数  | $0.4 \times F_S / 2$  | 62.5MSPS                            | 25MHz                               |

|                      | 4               | $F_S / 4$ 実数  | $0.4 \times F_S / 4$  | 31.25MSPS                           | 12.5MHz                             |

|                      | 8               | $F_S / 8$ 実数  | $0.4 \times F_S / 8$  | 15.625MSPS                          | 6.25MHz                             |

|                      | 16              | $F_S / 16$ 実数 | $0.4 \times F_S / 16$ | 7.8125MSPS                          | 3.125MHz                            |

|                      | 32              | $F_S / 32$ 実数 | $0.4 \times F_S / 32$ | 3.90625MSPS                         | 1.5625MHz                           |

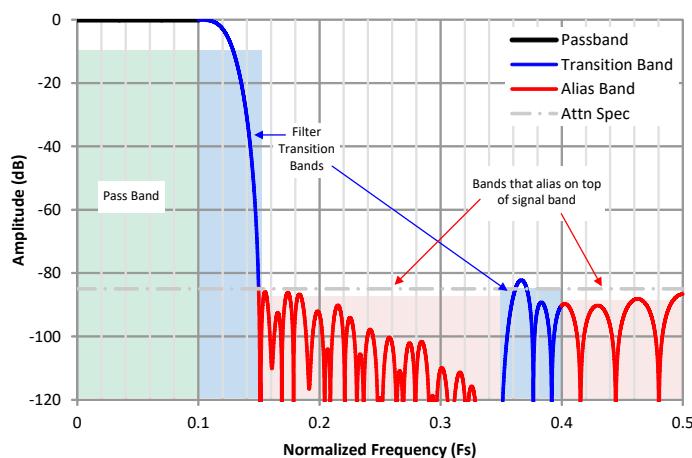

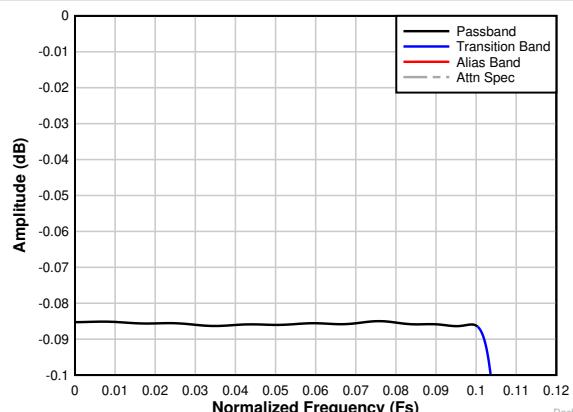

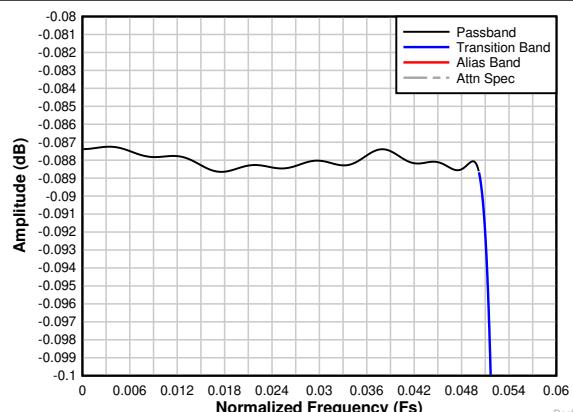

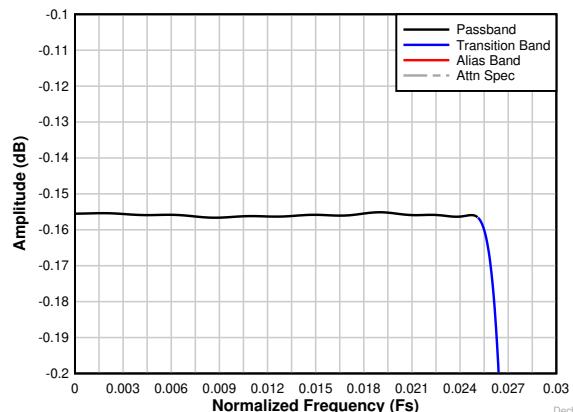

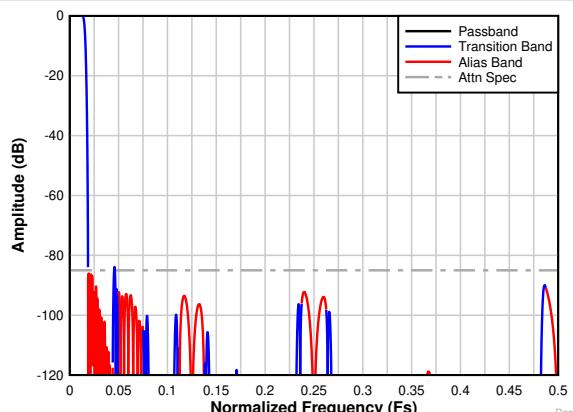

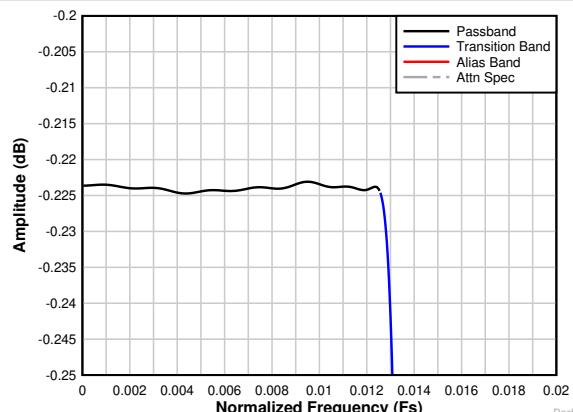

デシメーション フィルタの応答である ADC サンプリング クロック周波数に正規化されたものが、図 7-21 から 図 7-30 に示されます。次のように解釈されます。

各図には、図 7-20 に示すように、フィルタのパスバンド、遷移バンド、エイリアスまたはストップバンドが含まれています。X 軸は、(NCO 周波数シフト後の) オフセット周波数を ADC サンプリング レート  $F_S$  に正規化したものを示します。

たとえば、1/4 の複素セットアップでは、出力データ レートは  $F_S / 4$  複素、ナイキスト ゾーンは  $F_S / 8$  すなわち  $0.125 \times F_S$  です。遷移バンド (青色) は  $0.125 \times F_S$  を中心にしており、エイリアス遷移バンドは  $0.375 \times F_S$  を中心にしています。ストップ バンド (赤色) は、パスバンドの上側にエイリアスがあり、 $0.25 \times F_S$  および  $0.5 \times F_S$  を中心にして配置されています。ストップバンド減衰は、85dB を超えています。

図 7-20. デシメーション フィルタ プロットの解釈

図 7-21. 2 倍デシメーション時の複素数周波数応答

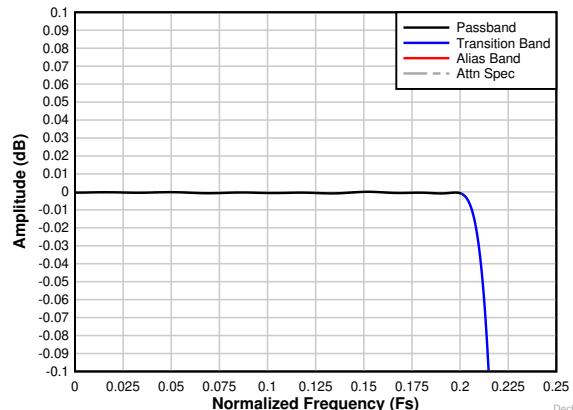

図 7-22. 2 倍デシメーション時の複素数バスバンド リップル応答

図 7-23. デシメーションにより、4 つの複素周波数応答 を実現

図 7-24. 4 倍デシメーション時の複素数バスバンド リップル応答

図 7-25. デシメーションにより、8 つの複素周波数応答 を実現

図 7-26. 8 倍デシメーション時の複素数バスバンド リップル応答

図 7-27. デシメーションにより、16 つの複素周波数応答を実現

図 7-28. 16 倍デシメーション時の複素数バスバンドリップル応答

図 7-29. デシメーションにより、32 つの複素周波数応答を実現

図 7-30. 32 倍デシメーション時の複素数バスバンドリップル応答

### 7.3.4.6 SYNC

PDN/SYNC ピンは、外部の SYNC 信号を使用して複数のデバイスを同期させるために使用されます。PDN/SYNC ピンは、SPI (SYNC EN ビット) を介して構成され、パワーダウン機能から同期機能へと切り替わります。この設定は、図 7-31 に示すようにサンプリング クロックの立ち上がりエッジでラッチされます。

図 7-31. 外部 SYNC タイミング図

同期信号が必要となるのは、デシメーション フィルタを使用する場合のみであり、その際は SPI の SYNC レジスタまたは PDN/SYNC ピンのいずれかを使用します。デシメーション フィルタで使用される内部クロック分周器をリセットし、内部クロックおよび I/Q データを同じサンプル内で整列させます。SYNC 信号が与えられない場合、内部のクロック分周器は同期されず、複数のデバイス間で分数遅延が発生する可能性があります。SYNC 信号は、NCO の位相をリセットし、新しい NCO 周波数を読み込む役割も果たします（これは MIXER RESTART ビットと同じ動作です）。

動作中に再同期を試みる場合、SYNC のトグルは  $64 \times K$  クロック サイクルごとに発生します（K は整数）。この場合、クロック分周器の位相連続性が示されます。

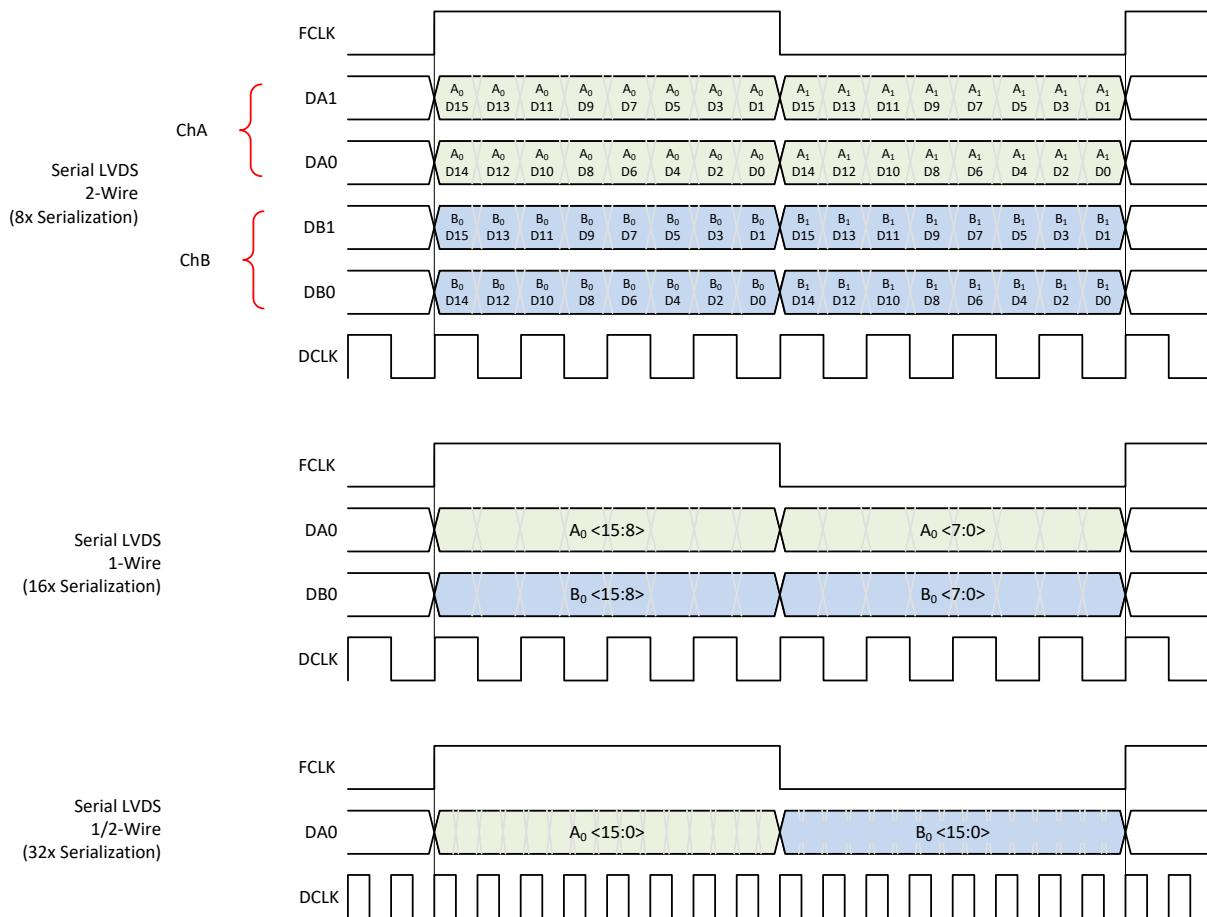

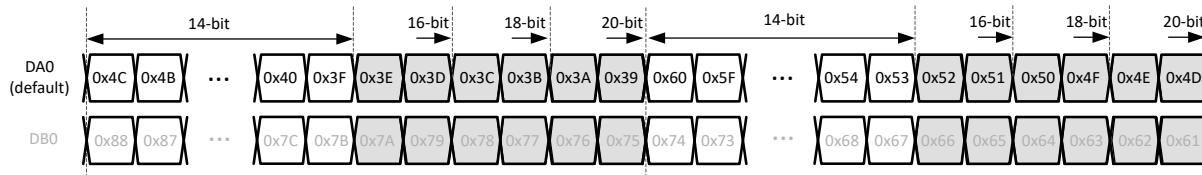

#### 7.3.4.7 デシメーションを使用した出力フォーマット

デシメーションを使用する場合、出力データは 図 7-32 および 図 7-33 に示すような形式になります。以下の例では、16 ビット出力における 2 線式 (8 倍直列化)、1 線式 (16 倍直列化)、および 1/2 線式 (32 倍直列化) の構成が示されています。

図 7-32. 複素デシメーションにおける出力データ フォーマット

表 7-3 は、出力インターフェイスのデータレートを示しており、出力解像度 ( $R$ )、SLVDS レーン数 ( $L$ )、および複素デシメーション設定 ( $N$ ) に基づく DCLK/DCLKIN および FCLK の周波数もあわせて示しています。

この表は、2 線式、1 線式、および 1/2 線式インターフェイスにおいて、16 ビット出力解像度および 4 倍の複素デシメーションを使用した場合の実際のレーンレートの例を示しています。

表 7-3. 複素デシメーションおよび 16 ビット出力解像度におけるシリアル LVDS レーン レートの例

| デシメーション設定 | ADC のサンプリングレート | 出力分解能 | 配線数 | FCLK      | DCLKIN, DCLK   | DA/B0, 1                        |

|-----------|----------------|-------|-----|-----------|----------------|---------------------------------|

| N         | $F_S$          | $R$   | $L$ | $F_S / N$ | [DA/B0, 1] / 2 | $F_S \times 2 \times R / L / N$ |

|           |                |       |     |           | 250MHz         | 500MHz                          |

|           |                |       |     |           | 500MHz         | 1000MHz                         |

|           |                |       |     |           | 15.625MHz      | 50MHz                           |

| 4         | 125MSPS        | 16    | 2   | 31.25MHz  | 500MHz         | 1000MHz                         |

|           |                |       | 1   |           | 1000MHz        | 1000MHz                         |

|           | 55MSPS         |       | 1/2 |           |                |                                 |

図 7-33. 実数デシメーションを使用した出力データ フォーマット

表 7-4 に、出力解像度 (R)、SLVDS レーン数 (L)、および実数デシメーション設定 (M) に基づいて、出力インターフェイスのデータレートと、それに対応する DCLK/DCLKIN および FCLK の周波数を示します。

この表は、2 線式、1 線式、1/2 線式インターフェイス、16 ビット出力分解能、実数デシメーションを 4 倍にする実際のレーンレートの例を示しています。

表 7-4. 実数デシメーションと 16 ビット出力分解能を使用するシリアル LVDS レーン レートの例

| デシメーション設定 | ADC のサンプリングレート | 出力分解能 | 配線数 | FCLK                                                    | DCLKIN, DCLK     | DA/B0, 1               |

|-----------|----------------|-------|-----|---------------------------------------------------------|------------------|------------------------|

| M         | $F_S$          | R     | L   | $F_S / M / 2$ ( $L = 2$ )<br>$F_S / M$ ( $L = 1, 1/2$ ) | $[DA/B0, 1] / 2$ | $F_S \times R / L / M$ |

| 4         | 125MSPS        | 16    | 2   | 15.625MHz                                               | 125MHz           | 250MHz                 |

|           |                |       | 1   | 31.25MHz                                                | 250MHz           | 500MHz                 |

|           |                |       | 1/2 |                                                         | 500MHz           | 1000MHz                |

### 7.3.5 デジタルインターフェイス

シリアル LVDS インターフェイスは、2 線式、1 線式、1/2 線式の動作を使用するデータ出力をサポートしています。実際のデータ出力レートは、使用する出力分解能とレーン数によって異なります。

ADC3664-xEP には外部シリアル LVDS クロック入力 (DCLKIN) が必要で、ADC からデータをデータクロック (DCLK) とともに送信するために使用されます。DCLKIN とサンプリングクロックの位相関係は無関係ですが、両方のクロックを周波数ロックする必要があります。SLVDS インターフェイスは、SPI レジスタへの書き込みを使用して構成されます。

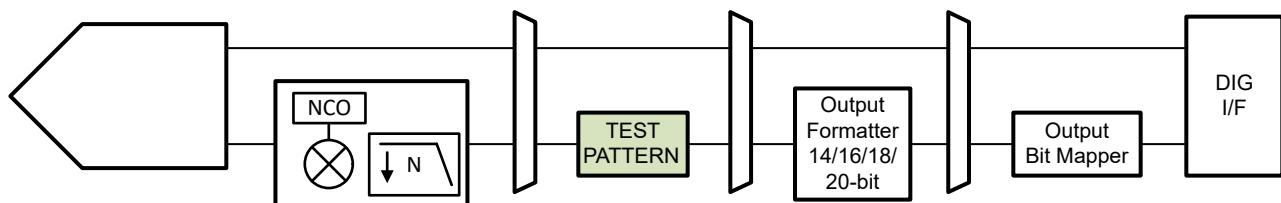

#### 7.3.5.1 出力 フォーマッタ

デジタル出力インターフェイスは、柔軟な出力ビットマッパー (図 7-34) を使用します。ビットマッパーは、ADC から直接 14 ビットの出力を取得するか、デジタルフィルタブロックから 14 ビット、16 ビット、18 ビット、20 ビットの分解能に再フォーマットします。出力シリアルライゼーション係数は、2 線式、1 線式、および 1/2 線式のインターフェイスモードに応じて調整されます。最大出力データレートは、出力解像度とシリアルライゼーション係数とは無関係に超えることはできません。

非デシメーションモードで 16 ビット以上の出力分解能を使用する場合、2LSB は 0 に設定されます。

図 7-34. インターフェース出力ビットマッパー

表 7-5 は出力解像度と出力モードに応じて、結果のシリアルライゼーションファクタの概要を示します。注:DCLKIN 周波数もそれに応じて調整する必要があります。たとえば、出力分解能を 16 ビット、2 線式モードに変更すると、 $F_s * 4$  から  $DCLKIN = F_s * 4$  となります。

出力ビットマッパーは、バイパスフィルタおよびデシメーションフィルタに使用されます。

表 7-5. さまざまな出力モードでのシリアル化係数と出力分解能の対比

| 出力分解能          | インターフェイス | シリアル化 | FCLK    | DCLKIN      | DCLK        | D0/D1      |

|----------------|----------|-------|---------|-------------|-------------|------------|

| 14 ビット (デフォルト) | 2 線式     | 7x    | $F_s/2$ | $F_s * 3.5$ | $F_s * 3.5$ | $F_s * 7$  |

|                | 1 線式     | 14x   | $F_s$   | $F_s * 7$   | $F_s * 7$   | $F_s * 14$ |

|                | 1/2 線式   | 28x   | $F_s$   | $F_s * 14$  | $F_s * 14$  | $F_s * 28$ |

| 16 ビット         | 2 線式     | 8x    | $F_s/2$ | $F_s * 4$   | $F_s * 4$   | $F_s * 8$  |

|                | 1 線式     | 16x   | $F_s$   | $F_s * 8$   | $F_s * 8$   | $F_s * 16$ |

|                | 1/2 線式   | 32x   | $F_s$   | $F_s * 16$  | $F_s * 16$  | $F_s * 32$ |

| 18 ビット         | 2 線式     | 9x    | $F_s/2$ | $F_s * 4.5$ | $F_s * 4.5$ | $F_s * 9$  |

|                | 1 線式     | 18x   | $F_s$   | $F_s * 9$   | $F_s * 9$   | $F_s * 18$ |

|                | 1/2 線式   | 36x   | $F_s$   | $F_s * 18$  | $F_s * 18$  | $F_s * 36$ |

| 20 ビット         | 2 線式     | 10x   | $F_s/2$ | $F_s * 5$   | $F_s * 5$   | $F_s * 10$ |

|                | 1 線式     | 20x   | $F_s$   | $F_s * 10$  | $F_s * 10$  | $F_s * 20$ |

|                | 1/2 線式   | 40x   | $F_s$   | $F_s * 20$  | $F_s * 20$  | $F_s * 40$ |

出力インターフェイス、または分解能をデフォルト設定から変更するプログラミングシーケンスを、[出力インターフェイス/モード構成](#) に示します。

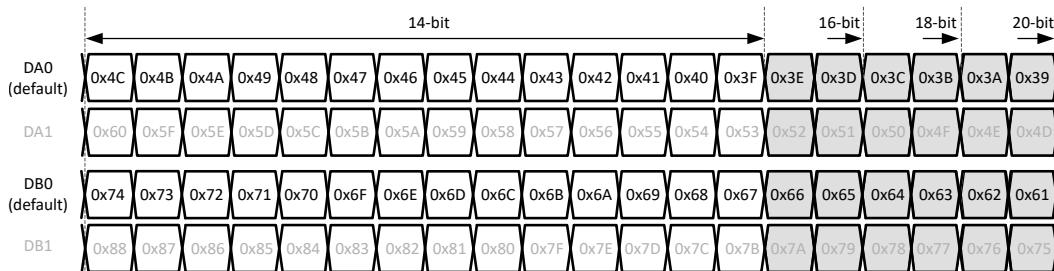

### 7.3.5.2 出力ビットマッパー

出力ビットマッパーを使用すると、任意の選択されたインターフェイスモードにおいて出力ビットの順序を変更することができます。

図 7-35. 出力ビットマッパー

出力ビットマッピングを変更し、出力データバスを構成するには、2段階のプロセスが使用されます。

1. 出力チャネル A および B の両方は、最大 20 ビットの出力が可能です。表 7-6 に示すように、いずれかのチャネルの各出力ビットには一意の識別子ビットがあります。MSB はビット D19 から始まり、選択された出力分解能に応じて、LSB は D6 (14 ビット) から D0 (20 ビット) までです。前のサンプルは、2W モードでのみ必要です。

2. 次に、ビットマッパーを使用して出力サンプルをアセンブルします。次のセクションでは、シリアル出力フォーマットを再マッピングする方法について詳しく説明します。

表 7-6. 各データビットの固有の識別子

| ビット       | チャネル A          |         | チャネル B          |         |

|-----------|-----------------|---------|-----------------|---------|

|           | 以前のサンプル (2W のみ) | 現在のサンプル | 以前のサンプル (2W のみ) | 現在のサンプル |

| D19 (MSB) | 0x2D            | 0x6D    | 0x29            | 0x69    |

| D18       | 0x2C            | 0x6C    | 0x28            | 0x68    |

| D17       | 0x27            | 0x67    | 0x23            | 0x63    |

| D16       | 0x26            | 0x66    | 0x22            | 0x62    |

| D15       | 0x25            | 0x65    | 0x21            | 0x61    |

| D14       | 0x24            | 0x64    | 0x20            | 0x60    |

| D13       | 0x1F            | 0x5F    | 0x1B            | 0x5B    |

| D12       | 0x1E            | 0x5E    | 0x1A            | 0x5A    |

| D11       | 0x1D            | 0x5D    | 0x19            | 0x59    |

| D10       | 0x1C            | 0x5C    | 0x18            | 0x58    |

| D9        | 0x17            | 0x57    | 0x13            | 0x53    |

| D8        | 0x16            | 0x56    | 0x12            | 0x52    |

| D7        | 0x15            | 0x55    | 0x11            | 0x51    |

| D6        | 0x14            | 0x54    | 0x10            | 0x50    |

| D5        | 0x0F            | 0x4F    | 0x0B            | 0x4B    |

| D4        | 0x0E            | 0x4E    | 0x0A            | 0x4A    |

| D3        | 0x0D            | 0x4D    | 0x09            | 0x49    |

| D2        | 0x0C            | 0x4C    | 0x08            | 0x48    |

| D1        | 0x07            | 0x47    | 0x03            | 0x43    |

| D0 (LSB)  | 0x06            | 0x46    | 0x02            | 0x42    |

シリアル出力モードでは、シリアル出力ストリーム内の各位置にデータビット(固有の識別子を持つ)を割り当てる必要があります。チャネルごとに合計 40 個のアドレスが使用できます。チャネル A はアドレス 0x39 ~ 0x60、チャネル B はアドレス 0x61 ~ 0x88 に及びます。複素デシメーションを使用する場合、出力ビットマッパーは「I」サンプルと「Q」サンプルの両方に適用されます。

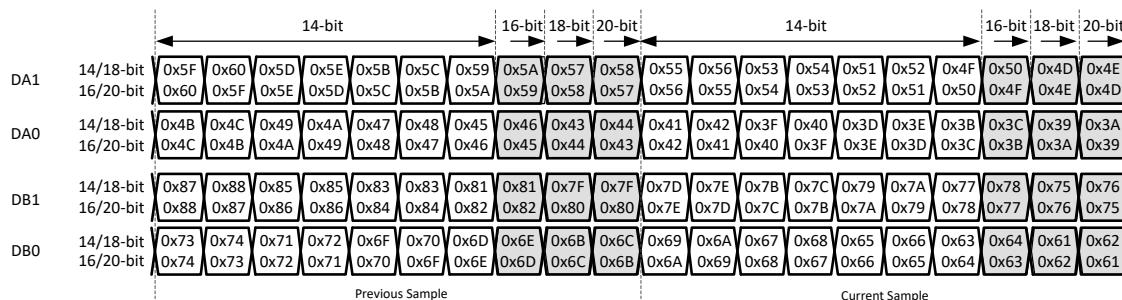

### 7.3.5.2.1.2 線式モード

このモードでは、図 7-36 に示すように、現在のサンプルと前のサンプルの両方をアドレス空間で使用する必要があります。アドレス順序は、14/18 ビットと 16/20 ビットで異なります。

注

サンプル間には 20 ビット未満 (グレーのバック グラウンド) の分解能については未使用のアドレスがありますが、未使用の場合はスキップされます。

図 7-36. 2 線式出力ビットマッパー

次の例(図7-37)では、16ビット2線式シリアル出力がリオーダされています。ここで、レーンDA1/DB1は8MSB、レーンDA0/DB0は8LSBを传送します。