# ADC3568、ADC3569 シングルチャネル、16 ビット、250MSPS および 500MSPS A/D コンバータ (ADC)

## 1 特長

- 16 ビット、シングルチャネル 250 / 500MSPS ADC

- ノイズスペクトル密度:-160.4dBFS/Hz

- 熱ノイズ:76.4dBFS

- シングルコア(非インターリーブ)ADC アーキテクチャ

- 消費電力:

- 435mW (500MSPS)

- 369mW (250MSPS)

- アーチャジッタ:75fs

- バッファ付きアナログ入力

- プログラム可能な 100Ω および 200Ω 終端

- 入力フルスケール:2V<sub>pp</sub>

- フルパワー入力帯域幅(-3dB):1.4GHz

- スペクトル性能( $f_{IN} = 70\text{MHz}$ , -1dBFS 時):

- 信号対雑音比:75.6dBFS

- SFDR HD2, 3:80dBc

- SFDR の最大スプリアス:94dBFS

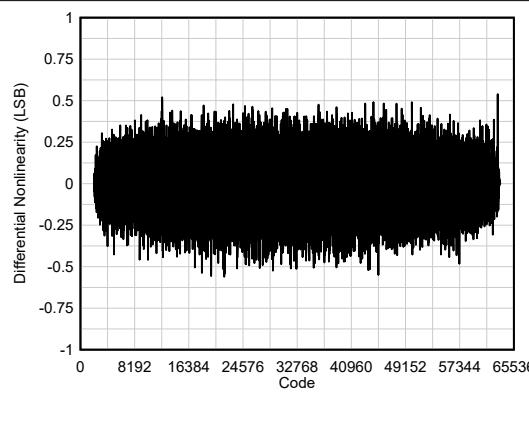

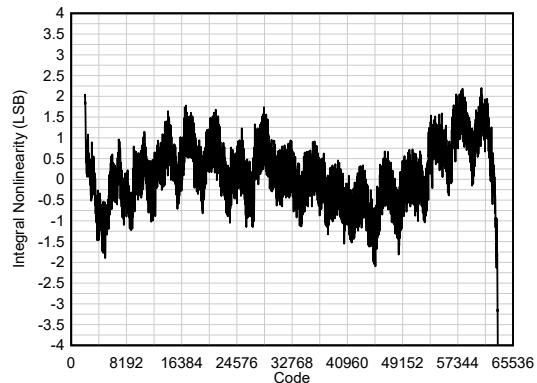

- INL:±2LSB (標準値)

- DNL:±0.5LSB (標準値)

- デジタルダウンコンバータ(DDC)

- 最大 4 つの独立した DDC

- 複素数と実数のデシメーション

- デシメーション:1/2, 1/4 ~ 1/32768 のデシメーション

- 48 ビット NCO による位相コヒーレント周波数ホッピング

- パラレル / シリアル LVDS インターフェイス

- DDC バイパス用の 16 ビットパラレル SDR、DDR LVDS

- デシメーション用のシリアル LVDS

- 高比率デシメーション用の 32 ビット出力オプション

## 2 アプリケーション

- ソフトウェア無線

- スペクトルアナライザ

- レーダー

- 分光器

- パワーアンプ直線化

- 通信インフラ

## 3 概要

ADC3568 と ADC3569 (ADC356x) は、16 ビット、250MSPS および 500MSPS、シングルチャネル A/D コンバータ(ADC)です。これらのデバイスは高い信号対雑音比(SNR)を実現するよう設計されており、-160dBFS/Hz(500MSPS)のノイズスペクトル密度を実現します。

電力効率の優れた ADC アーキテクチャは、500MSPS で 435mW の消費電力を実現し、低サンプリングレートで電力スケーリングを実現します(250MSPS で 369mW)。

ADC356x は、オプションのクワッドバンドデジタルダウンコンバータ(DDC)を搭載しており、比率 2 の広帯域デシメーションから、比率 32768 の狭帯域デシメーションまでサポートしています。DDC では、位相コヒーレントと位相連続の周波数ホッピングをサポートする 48 ビット NCO を使用しています。

ADC356x には、フレキシブルな LVDS インターフェイスが装備されています。デシメーションバイパスモードでは、パラレル SDR または DDR LVDS インターフェイスを使用します。デシメーションを使用するときは、シリアル LVDS インターフェイスを使用して出力データが送信され、デシメーションの増加に応じて必要なレーン数が少くなります。デシメーション比が高い場合、出力分解能を 32 ビットに増やすことができます。

### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | 最大サンプリングレート |

|---------|----------------------|-------------|

| ADC3569 | 64QFN                | 500MSPS     |

| ADC3568 | 64QFN                | 250MSPS     |

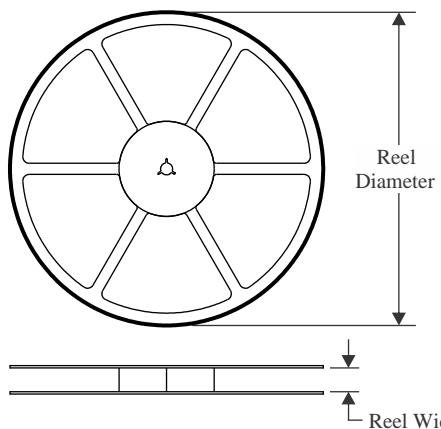

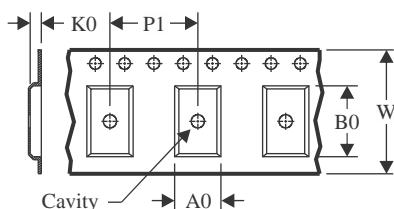

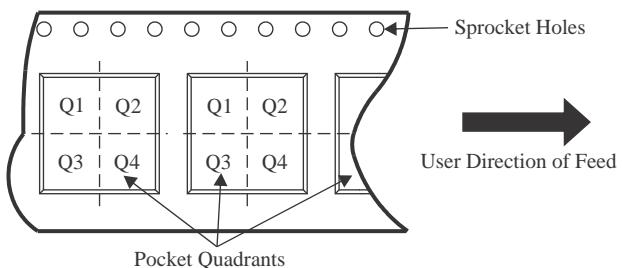

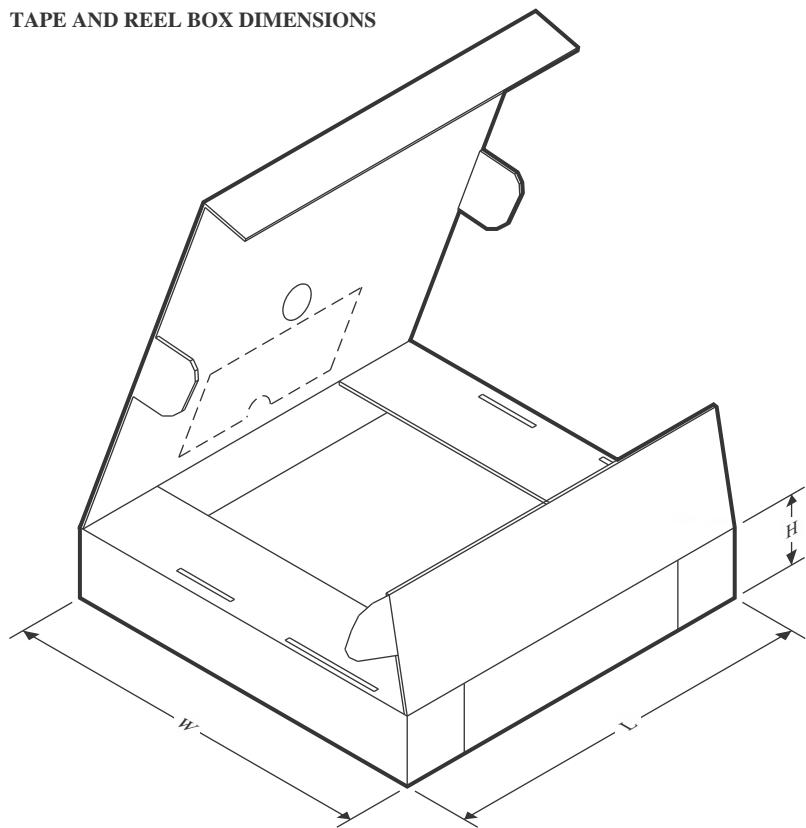

(1) 詳細については、[セクション 12](#)を参照してください。

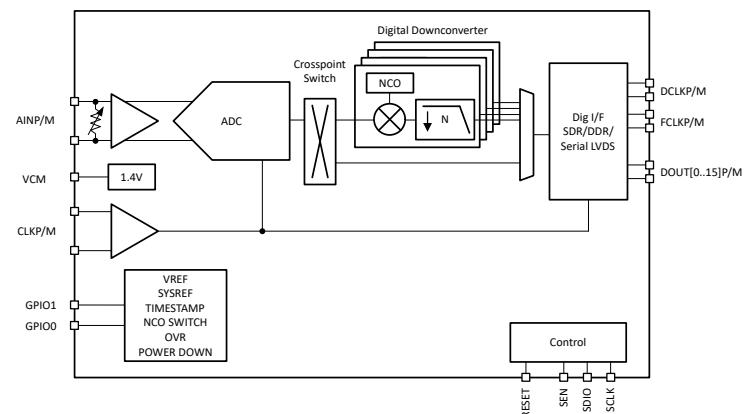

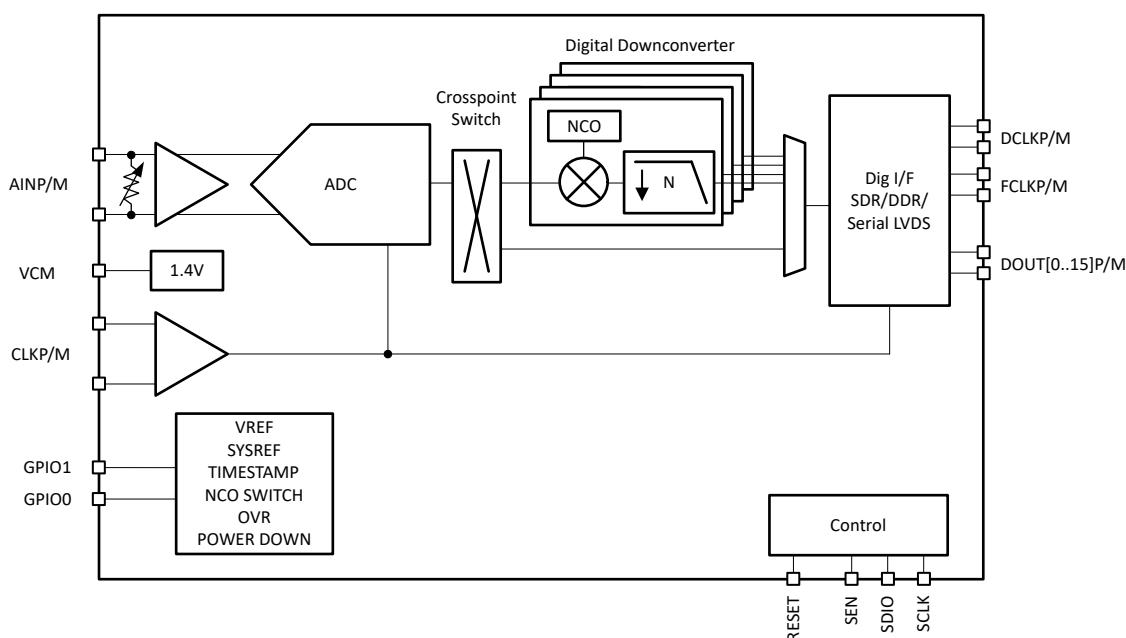

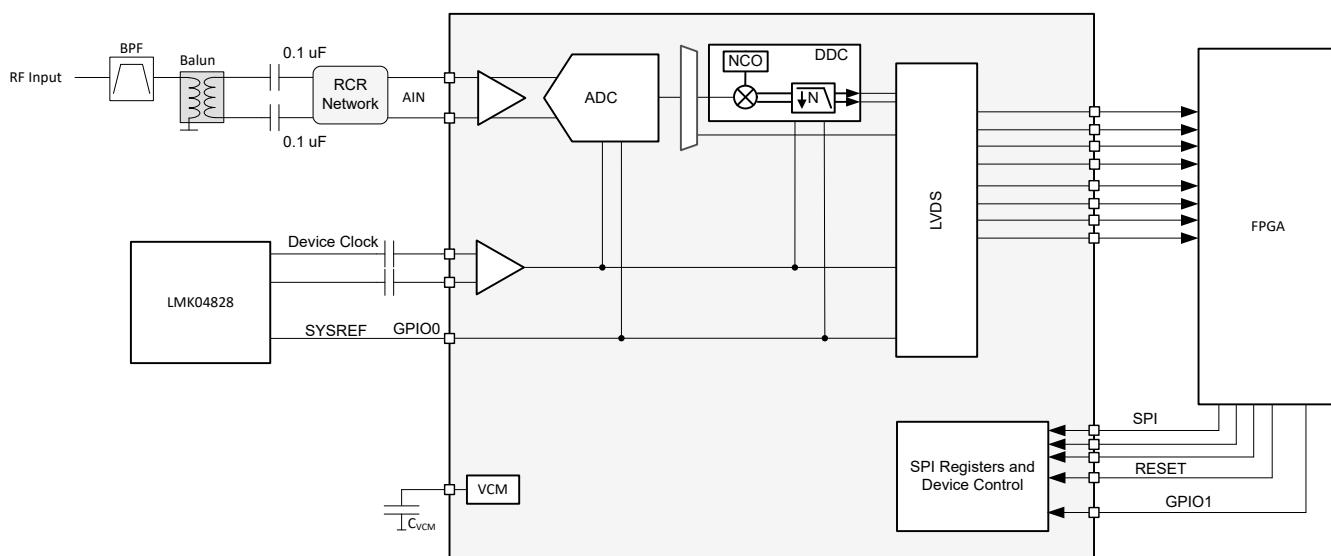

ブロック図

**⚠️** このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SBASA04

## 目次

|                                       |    |                         |    |

|---------------------------------------|----|-------------------------|----|

| 1 特長                                  | 1  | 8.1 概要                  | 27 |

| 2 アプリケーション                            | 1  | 8.2 機能ブロック図             | 27 |

| 3 概要                                  | 1  | 8.3 機能説明                | 28 |

| 4 デバイスの比較                             | 2  | 8.4 デバイスの機能モード          | 53 |

| 5 ピン構成および機能                           | 3  | 8.5 プログラミング             | 54 |

| 6 仕様                                  | 5  | 9 アプリケーションと実装           | 73 |

| 6.1 絶対最大定格                            | 5  | 9.1 アプリケーション情報          | 73 |

| 6.2 ESD 定格                            | 5  | 9.2 代表的なアプリケーション        | 73 |

| 6.3 推奨動作条件                            | 5  | 9.3 電源に関する推奨事項          | 78 |

| 6.4 熱に関する情報                           | 6  | 9.4 レイアウト               | 79 |

| 6.5 電気的特性 - 消費電力                      | 6  | 10 デバイスおよびドキュメントのサポート   | 80 |

| 6.6 電気的特性 - DC 仕様                     | 6  | 10.1 ドキュメントのサポート        | 80 |

| 6.7 電気的特性 - AC 仕様 (ADC3568 - 250MSPS) | 9  | 10.2 ドキュメントの更新通知を受け取る方法 | 80 |

| 6.8 電気的特性 - AC 仕様 (ADC3569 - 500MSPS) | 11 | 10.3 サポート・リソース          | 80 |

| 6.9 タイミング要件                           | 13 | 10.4 商標                 | 80 |

| 6.10 代表的特性、ADC3568                    | 14 | 10.5 静電気放電に関する注意事項      | 80 |

| 6.11 代表的特性、ADC3569                    | 19 | 10.6 用語集                | 80 |

| 7 パラメータ測定情報                           | 25 | 11 改訂履歴                 | 80 |

| 8 詳細説明                                | 27 | 12 メカニカル、パッケージ、および注文情報  | 81 |

## 4 デバイスの比較

表 4-1. デバイス比較表

| 部品番号    | 最大サンプリングレート | 分解能    | チャネル数 |

|---------|-------------|--------|-------|

| ADC3669 | 500MSPS     | 16 ビット | 2     |

| ADC3668 | 250MSPS     | 16 ビット | 2     |

| ADC3569 | 500MSPS     | 16 ビット | 1     |

| ADC3568 | 250MSPS     | 16 ビット | 1     |

| ADC3649 | 500MSPS     | 14 ビット | 2     |

| ADC3648 | 250MSPS     | 14 ビット | 2     |

| ADC3549 | 500MSPS     | 14 ビット | 1     |

| ADC3548 | 250MSPS     | 14 ビット | 1     |

## 5 ピン構成および機能

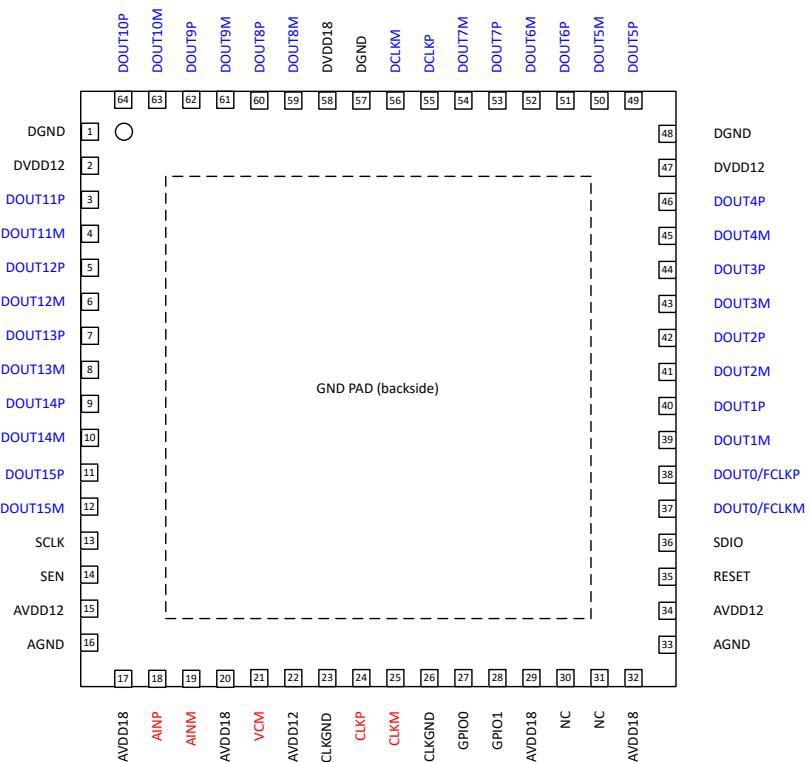

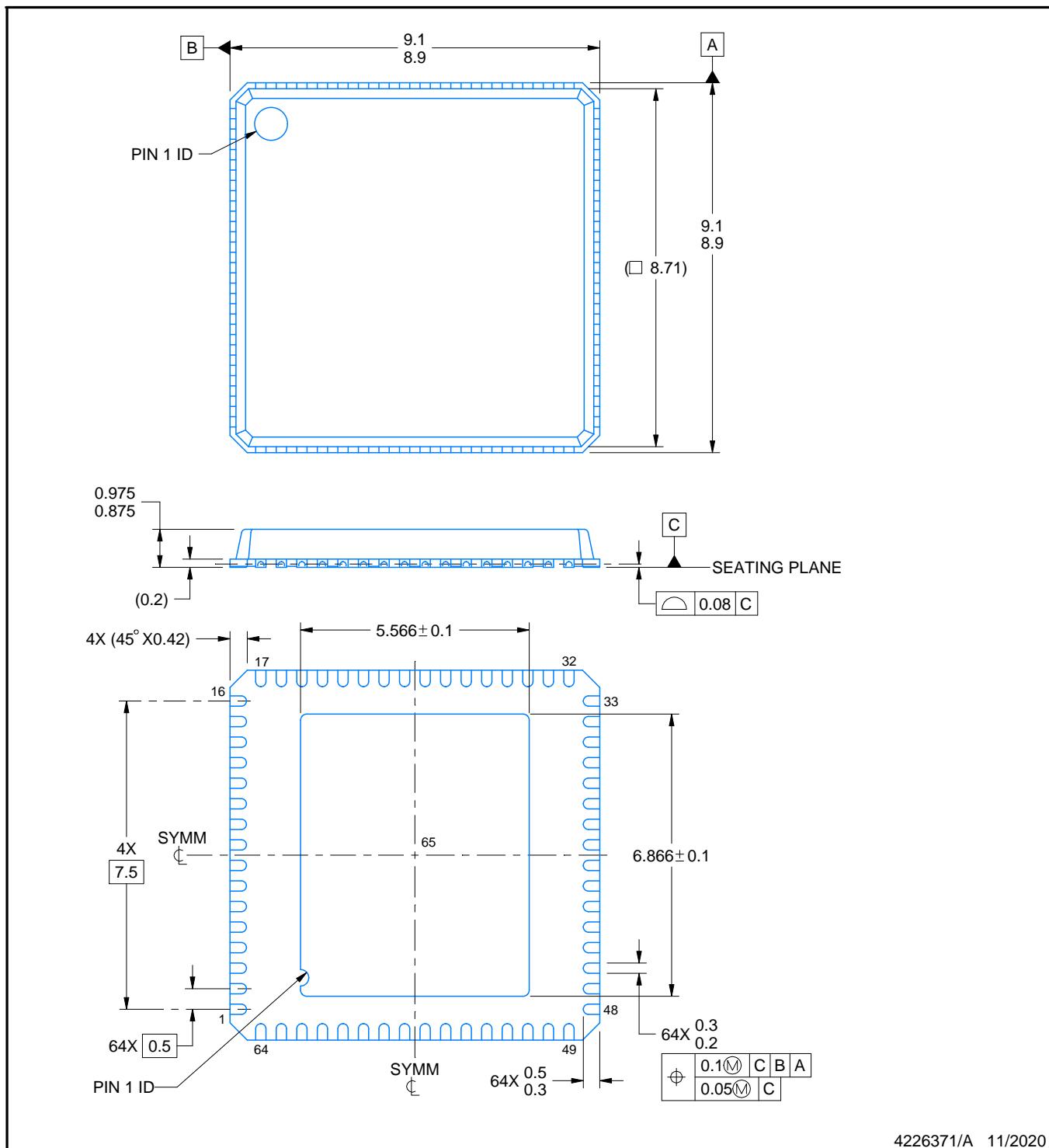

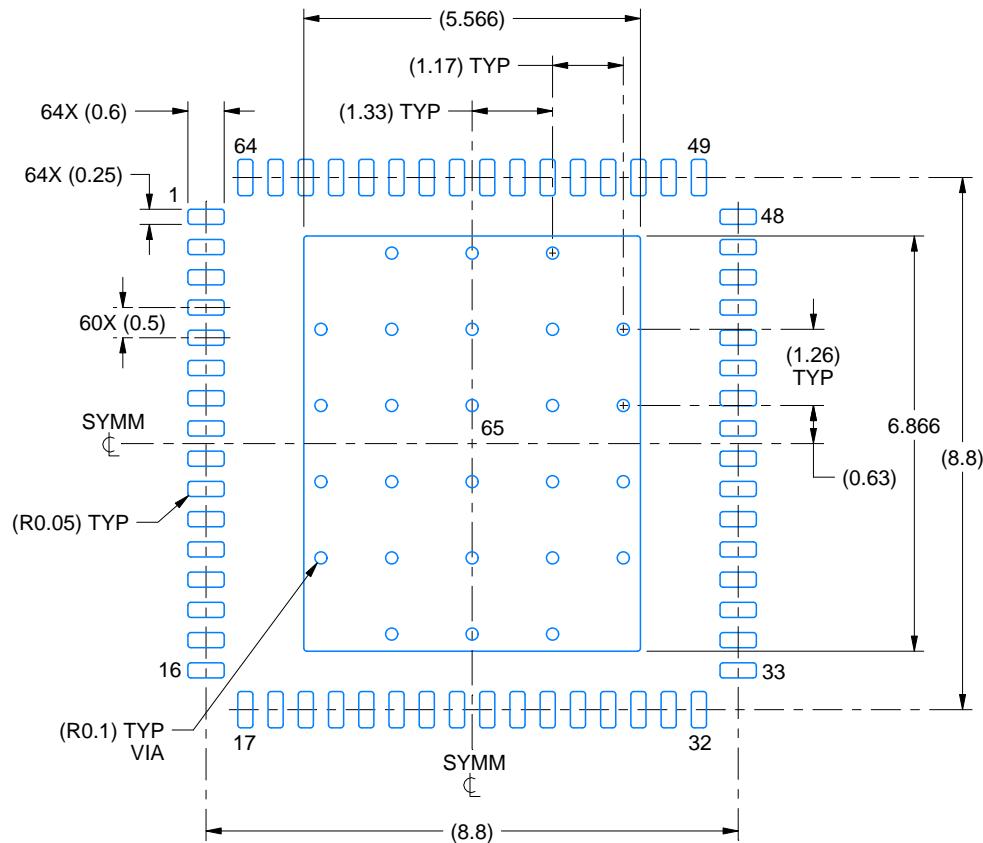

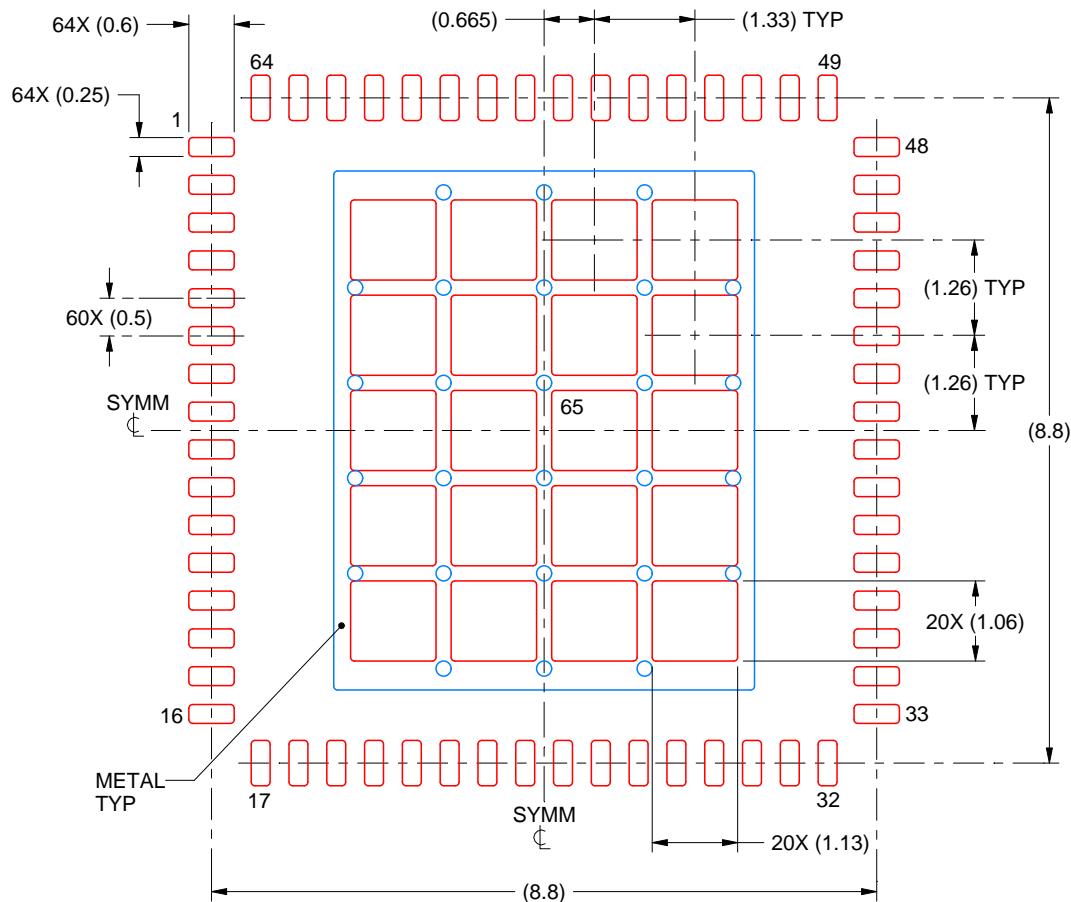

図 5-1. RTD パッケージ、64 ピン VQFN

(上面図)

表 5-1. ピンの機能

| ピン          |                | タイプ <sup>(1)</sup> | 説明                                                                                                       |

|-------------|----------------|--------------------|----------------------------------------------------------------------------------------------------------|

| 名称          | 番号             |                    |                                                                                                          |

| AGND        | 16, 33         | I                  | アナログ グランド、0V                                                                                             |

| AINM        | 19             | I                  | チャネル A 差動信号入力、負接続。差動入力は、プログラム可能な内部終端 (100Ω または 200Ω) を備えており、自己バイアスされています。                                |

| AINP        | 18             | I                  | チャネル A 差動信号入力、正接続。                                                                                       |

| AVDD12      | 15, 22, 34     | I                  | アナログ 1.2V 電源                                                                                             |

| AVDD18      | 17, 20, 29, 32 | I                  | アナログ 1.8V 電源                                                                                             |

| CLKGND      | 23, 26         | I                  | クロック グランド、0V                                                                                             |

| CLKP        | 24             | I                  | デバイス サンプリング クロック差動入力。最高の AC 性能を得るために、クロック信号は AC 結合し、外部で終端することを推奨します。差動入力は、入力同相電圧 (0.75V) に対して自己バイアスされます。 |

| CLKM        | 25             | I                  |                                                                                                          |

| DCLKP       | 55             | O                  | 差動 LVDS データビットクロック出力。                                                                                    |

| DCLKM       | 56             | O                  |                                                                                                          |

| DGND        | 1, 48, 57      | I                  | デジタル グランド、0V                                                                                             |

| DOUT0/FCLKM | 37             | O                  | 差動 LVDS データビット出力レーン 0。デシメーション モードでは、このピンは、差動 SLVDS フレームクロック出力となり、LSB と置き換えられます。                          |

| DOUT0/FCLKP | 38             | O                  |                                                                                                          |

| DOUT1M      | 39             | O                  | 差動 LVDS データビット出力レーン 1。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                                            |

| DOUT1P      | 40             | O                  |                                                                                                          |

| DOUT2M      | 41             | O                  | 差動 LVDS データビット出力レーン 2。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                                            |

| DOUT2P      | 42             | O                  |                                                                                                          |

表 5-1. ピンの機能 (続き)

| ピン      |       | タイプ <sup>(1)</sup> | 説明                                                                                |

|---------|-------|--------------------|-----------------------------------------------------------------------------------|

| 名称      | 番号    |                    |                                                                                   |

| DOUT3M  | 43    | O                  | 差動 LVDS データビット出力レーン 3。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT3P  | 44    | O                  |                                                                                   |

| DOUT4M  | 45    | O                  | 差動 LVDS データビット出力レーン 4。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT4P  | 46    | O                  |                                                                                   |

| DOUT5P  | 49    | O                  | 差動 LVDS データビット出力レーン 5。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT5M  | 50    | O                  |                                                                                   |

| DOUT6P  | 51    | O                  | 差動 LVDS データビット出力レーン 6。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT6M  | 52    | O                  |                                                                                   |

| DOUT7P  | 53    | O                  | 差動 LVDS データビット出力レーン 7。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT7M  | 54    | O                  |                                                                                   |

| DOUT8M  | 59    | O                  | 差動 LVDS データビット出力レーン 8。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT8P  | 60    | O                  |                                                                                   |

| DOUT9M  | 61    | O                  | 差動 LVDS データビット出力レーン 9。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                     |

| DOUT9P  | 62    | O                  |                                                                                   |

| DOUT10M | 63    | O                  | 差動 LVDS データビット出力レーン 10。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                    |

| DOUT10P | 64    | O                  |                                                                                   |

| DOUT11P | 3     | O                  | 差動 LVDS データビット出力レーン 11。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                    |

| DOUT11M | 4     | O                  |                                                                                   |

| DOUT12P | 5     | O                  | 差動 LVDS データビット出力レーン 12。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                    |

| DOUT12M | 6     | O                  |                                                                                   |

| DOUT13P | 7     | O                  | 差動 LVDS データビット出力レーン 13。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                    |

| DOUT13M | 8     | O                  |                                                                                   |

| DOUT14P | 9     | O                  | 差動 LVDS データビット出力レーン 14。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                    |

| DOUT14M | 10    | O                  |                                                                                   |

| DOUT15P | 11    | O                  | 差動 LVDS データビット出力レーン 15。使用しない場合は、フローティングのままにして、SPI 経由で電源オフできます。                    |

| DOUT15M | 12    | O                  |                                                                                   |

| DVDD12  | 2, 47 | I                  | デジタル 1.2V 電源                                                                      |

| DVDD18  | 58    | I                  | デジタル 1.8V 電源                                                                      |

| GPIO0   | 27    | I/O                | 同期または制御入力またはステータス出力。未使用時は、フローティングにできます。                                           |

| GPIO1   | 28    | I/O                | 制御入力またはステータス出力または外部電圧リファレンス (1.2V)。未使用時は、フローティングにできます。                            |

| NC      | 30.31 | -                  | 接続しない                                                                             |

| リセット    | 35    | I                  | ハードウェアリセットアクティブ HIGH。このピンには、内部に DGND への 21kΩ プルダウン抵抗があります。                        |

| SCLK    | 13    | I                  | シリアル インターフェイス プログラミング用のシリアル インターフェイス クロック。このピンには、内部に DVDD18 への 21kΩ プルアップ抵抗があります。 |

| SDIO    | 36    | I/O                | シリアル インターフェイス データ入出力。このピンには、内部に DVDD18 への 21kΩ プルアップ抵抗があります。                      |

| SEN     | 14    | I                  | シリアル インターフェイス チップ セレクト。このピンには、内部に DVDD18 への 21kΩ プルアップ抵抗があります。                    |

| VCM     | 21    | O                  | 同相電圧出力 (1.4V)                                                                     |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                 | テスト条件                           | 最小値  | 最大値          | 単位  |

|-----------------------|---------------------------------|------|--------------|-----|

| 電源電圧範囲、AVDD18         |                                 | -0.3 | 2.1          | V   |

| 電源電圧範囲、AVDD12         |                                 | -0.3 | 1.4          | V   |

| 電源電圧範囲、DVDD18         |                                 | -0.3 | 2.1          | V   |

| 電源電圧範囲、DVDD12         |                                 | -0.3 | 1.4          | V   |

| 入力ピンに印加される電圧          | AINP/M                          | -0.3 | 2.1          | V   |

|                       | CLKP/M                          | -0.3 | 1.4          | V   |

|                       | GPIO0/1, RESET, SCLK, SEN, SDIO | -0.3 | DVDD18 + 0.2 | V   |

| ピーク RF 入力電力 (AINP/M)  | 100Ω 差動終端                       |      | 10           | dBm |

| 接合部温度、T <sub>J</sub>  |                                 |      | 125          | °C  |

| 保管温度、T <sub>stg</sub> |                                 | -65  | 150          |     |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、「推奨動作条件」に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 6.2 ESD 定格

| V <sub>(ESD)</sub> | 静電放電                                                                                                              | 値    | 単位 |

|--------------------|-------------------------------------------------------------------------------------------------------------------|------|----|

|                    |                                                                                                                   | 1500 | V  |

| V <sub>(ESD)</sub> | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup><br>デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | 750  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |             | 最小値  | 公称値 | 最大値                | 単位 |

|----------------|-------------|------|-----|--------------------|----|

| AVDD18         | 1.8V アナログ電源 | 1.75 | 1.8 | 1.85               | V  |

| AVDD12         | 1.2V アナログ電源 | 1.15 | 1.2 | 1.225              |    |

| DVDD18         | 1.8V デジタル電源 | 1.75 | 1.8 | 1.85               |    |

| DVDD12         | 1.2V デジタル電源 | 1.15 | 1.2 | 1.225              |    |

| T <sub>A</sub> | 自由空気での動作温度  | -40  |     | 105                | °C |

| T <sub>J</sub> | 動作時接合部温度    |      |     | 115 <sup>(1)</sup> |    |

- (1) この接合部温度を超えて長時間使用すると、デバイスの時間あたりの故障回数 (FIT) レートが上昇する可能性があります。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | ADC3568/69 | 単位   |

|-----------------------------|---------------------|------------|------|

|                             |                     | RTD (QFN)  |      |

|                             |                     | 64 ピン      |      |

| $R_{\Theta JA}$             | 接合部から周囲への熱抵抗        | 22.3       | °C/W |

| $R_{\Theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 11.4       | °C/W |

| $R_{\Theta JB}$             | 接合部から基板への熱抵抗        | 7.4        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.1        | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 7.3        | °C/W |

| $R_{\Theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗 | 1.1        | °C/W |

(1) 热評価基準の詳細については、『半導体および IC パッケージの热評価基準』アプリケーション レポート、SPRA953 を参照してください。

## 6.5 電気的特性 - 消費電力

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ                    | テスト条件                        | 最小値           | 標準値 | 最大値 | 単位 |

|--------------------------|------------------------------|---------------|-----|-----|----|

| <b>ADC3568 - 250MSPS</b> |                              |               |     |     |    |

| $I_{AVDD18}$             | 電源電流、1.8V アナログ電源<br>DDR LVDS | 60            | 85  |     | mA |

| $I_{AVDD12}$             |                              | 45            | 90  |     |    |

| $I_{DVDD18}$             |                              | 75            | 105 |     |    |

| $I_{DVDD12}$             |                              | 60            | 126 |     |    |

| $P_{\text{DIS}}$         |                              | 369           |     |     | mW |

| <b>ADC3569 - 500MSPS</b> |                              |               |     |     |    |

| $I_{AVDD18}$             | 電源電流、1.8V アナログ電源<br>DDR LVDS | 66            | 85  |     | mA |

| $I_{AVDD12}$             |                              | 65            | 115 |     |    |

| $I_{DVDD18}$             |                              | 76            | 105 |     |    |

| $I_{DVDD12}$             |                              | 85            | 155 |     |    |

| $P_{\text{DIS}}$         |                              | 435           |     |     | mW |

| パワーダウン モード               |                              |               |     |     |    |

| $P_{\text{DIS}}$         | パワー ダウン モードの消費電力             | グローバル パワー ダウン | 31  |     | mW |

## 6.6 電気的特性 - DC 仕様

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ                   | テスト条件            | 最小値                            | 標準値  | 最大値       | 単位  |

|-------------------------|------------------|--------------------------------|------|-----------|-----|

| <b>DC 精度</b>            |                  |                                |      |           |     |

| ミッキング コードなし             |                  | 16                             |      |           | ビット |

| <b>ADC3568:250 MSPS</b> |                  |                                |      |           |     |

| DNL                     | 微分非直線性           | $F_{\text{IN}} = 70\text{MHz}$ | -0.9 | $\pm 0.5$ | LSB |

| INL                     | 積分非直線性           | $F_{\text{IN}} = 70\text{MHz}$ |      | $\pm 2$   | LSB |

| $V_{\text{OS\_ERR}}$    | オフセット エラー        |                                | 10   |           | LSB |

| $V_{\text{OS\_DRIFT}}$  | 温度に対するオフセット ドリフト |                                | 10   |           | LSB |

## 6.6 電気的特性 - DC 仕様 (続き)

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ                                                |                   | テスト条件                      | 最小値            | 標準値    | 最大値   | 単位   |

|------------------------------------------------------|-------------------|----------------------------|----------------|--------|-------|------|

| GAIN <sub>ERR</sub>                                  | ゲイン誤差             | 外部リファレンス                   |                | ±1     |       | %FSR |

|                                                      |                   | 内部リファレンス                   |                | ±3     |       |      |

| GAIN <sub>DRIFT</sub>                                | 温度範囲でのゲインドリフト     | 外部リファレンス                   |                | ±0.5   |       | %FSR |

|                                                      |                   | 内部リファレンス                   |                | ±1     |       |      |

| <b>ADC3569:500 MSPS</b>                              |                   |                            |                |        |       |      |

| DNL                                                  | 微分非直線性            | $F_{IN} = 70\text{MHz}$    | -0.9           | ±0.5   |       | LSB  |

| INL                                                  | 積分非直線性            | $F_{IN} = 70\text{MHz}$    |                | ±2     |       | LSB  |

| V <sub>OS_ERR</sub>                                  | オフセット エラー         |                            |                | 10     |       | LSB  |

| V <sub>OS_DRIFT</sub>                                | 温度に対するオフセット ドリフト  |                            |                | 10     |       | LSB  |

| GAIN <sub>ERR</sub>                                  | ゲイン誤差             | 外部リファレンス                   |                | ±1     |       | %FSR |

|                                                      |                   | 内部リファレンス                   |                | ±3     |       |      |

| GAIN <sub>DRIFT</sub>                                | 温度範囲でのゲインドリフト     | 外部リファレンス                   |                | ±0.5   |       | %FSR |

|                                                      |                   | 内部リファレンス                   |                | ±1     |       |      |

| <b>ADC アナログ入力 (AINP/M)</b>                           |                   |                            |                |        |       |      |

| FS                                                   | 入力フル スケール         | 差動                         |                | 2.0    |       | Vpp  |

| V <sub>ICM</sub>                                     | 入力同相電圧            |                            | 1.3            | 1.4    | 1.5   | V    |

| Z <sub>IN</sub>                                      | 差動入力インピーダンス       | 差動、100MHz                  |                | 100    |       | Ω    |

| V <sub>CM</sub>                                      | 出力同相電圧            |                            |                | 1.4    |       | V    |

| BW                                                   | アナログ入力帯域幅 (-3dB)  |                            |                | 1.4    |       | GHz  |

| <b>クロック入力 (CLKP/M)</b>                               |                   |                            |                |        |       |      |

| 入力クロック周波数                                            |                   | ADC3569                    | 100            | 500    |       | MHz  |

|                                                      |                   | ADC3568                    | 100            | 250    |       | MHz  |

| V <sub>ID</sub>                                      | 差動入力電圧            |                            | 0.5            | 2      | 2.4   | Vpp  |

| V <sub>ICM</sub>                                     | 入力同相電圧            |                            |                | 0.75   |       | V    |

| Z <sub>IN</sub>                                      | 差動入力インピーダンス       | 差動、500MHz                  |                | 5      |       | kΩ   |

| クロック デューティ サイクル                                      |                   |                            | 35             | 50     | 65    | %    |

| <b>外部リファレンス入力 (GPIO1)</b>                            |                   |                            |                |        |       |      |

| V <sub>REF</sub>                                     | 外部基準電圧            |                            | 1.175          | 1.2    | 1.225 | V    |

| I <sub>VREF</sub>                                    | 入力電流、外部電圧リファレンス入力 |                            |                | 10     |       | μA   |

| <b>デジタル入力 (GPIO0, GPIO1, RESET, SCLK, SEN, SDIO)</b> |                   |                            |                |        |       |      |

| V <sub>IH</sub>                                      | High レベル入力電圧      |                            | 1.4            | 1.8    |       | V    |

| V <sub>IL</sub>                                      | Low レベル入力電圧       |                            | 0              | 0.4    |       | V    |

| I <sub>IH</sub>                                      | High レベル入力電流      |                            | 90             | 150    |       | μA   |

| I <sub>IL</sub>                                      | Low レベル入力電流       |                            | -150           | -90    |       | μA   |

| C <sub>I</sub>                                       | 入力容量              |                            |                | 1.5    |       | pF   |

| <b>デジタル出力 (GPIO0, GPIO1, SDIO)</b>                   |                   |                            |                |        |       |      |

| V <sub>OH</sub>                                      | High レベル出力電圧      | I <sub>LOAD</sub> = -400uA | AVDD18<br>-0.1 | AVDD18 |       | V    |

| V <sub>OL</sub>                                      | Low レベル出力電圧       | I <sub>LOAD</sub> = 400uA  |                |        | 0.1   | V    |

| <b>LVDS/SLVDS インターフェイス (DOUT[0..15]P/M, DCLKP/M)</b> |                   |                            |                |        |       |      |

| 出力データ フォーマット (デフォルト)                                 |                   |                            | 2 の補数          |        |       |      |

## 6.6 電気的特性 - DC 仕様 (続き)

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ     |        | テスト条件        | 最小値  | 標準値  | 最大値  | 単位   |

|-----------|--------|--------------|------|------|------|------|

| $V_{OD}$  | 差動出力電圧 | 差動ピーク ツー ピーク | 500  | 700  | 850  | mVpp |

| $V_{OCM}$ | 出力同相電圧 |              | 0.96 | 1.02 | 1.08 | V    |

## 6.7 電気的特性 - AC 仕様 (ADC3568 - 250MSPS)

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ        |                                      | テスト条件                                                | 最小値 <sup>(1)</sup> | 標準値  | 最大値 | 単位               |

|--------------|--------------------------------------|------------------------------------------------------|--------------------|------|-----|------------------|

| <b>AC 精度</b> |                                      |                                                      |                    |      |     |                  |

| NSD          | ノイズ スペクトル密度                          | $f_{IN} = 100\text{MHz}$ 、 $A_{IN} = -20\text{dBFS}$ | -157.4             |      |     | $\text{dBFS/Hz}$ |

| NF           | ノイズ指数:                               | $f_{IN} = 100\text{MHz}$ 、 $A_{IN} = -20\text{dBFS}$ | 23.6               |      |     | $\text{dB}$      |

| SNR          | 信号対雑音比                               | $f_{IN} = 10\text{MHz}$                              | 75.5               |      |     | $\text{dBFS}$    |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 70                 | 75.2 |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             |                    | 74.6 |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             |                    | 72.9 |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             |                    | 71.4 |     |                  |

| SINAD        | 信号対雑音歪み比                             | $f_{IN} = 10\text{MHz}$                              | 73.6               |      |     | $\text{dBFS}$    |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 74.1               |      |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 72.2               |      |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 68.5               |      |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 64.7               |      |     |                  |

| ENOB         | 有効ビット数                               | $f_{IN} = 10\text{MHz}$                              | 11.9               |      |     | $\text{ビット}$     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 12.0               |      |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 11.7               |      |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 11.1               |      |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 10.4               |      |     |                  |

| THD          | 全高調波歪み (最初の 5 つの高調波)                 | $f_{IN} = 10\text{MHz}$                              | 77                 |      |     | $\text{dBc}$     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 80                 |      |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 75                 |      |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 71                 |      |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 65                 |      |     |                  |

| HD2          | 2 次高調波歪み                             | $f_{IN} = 10\text{MHz}$                              | 79                 |      |     | $\text{dBc}$     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 69                 | 85   |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 78                 |      |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 76                 |      |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 68                 |      |     |                  |

| HD3          | 3 次高調波歪み                             | $f_{IN} = 10\text{MHz}$                              | 83                 |      |     | $\text{dBc}$     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 71                 | 81   |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 81                 |      |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 79                 |      |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 74                 |      |     |                  |

| Non HD2,3    | スプリアス フリー ダイナミック レンジ (HD2 と HD3 を除く) | $f_{IN} = 10\text{MHz}$                              | 96                 |      |     | $\text{dBFS}$    |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 96                 |      |     |                  |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 95                 |      |     |                  |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 88                 |      |     |                  |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 81                 |      |     |                  |

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ | テスト条件        | 最小値 <sup>(1)</sup>                                                             | 標準値 | 最大値 | 単位  |

|-------|--------------|--------------------------------------------------------------------------------|-----|-----|-----|

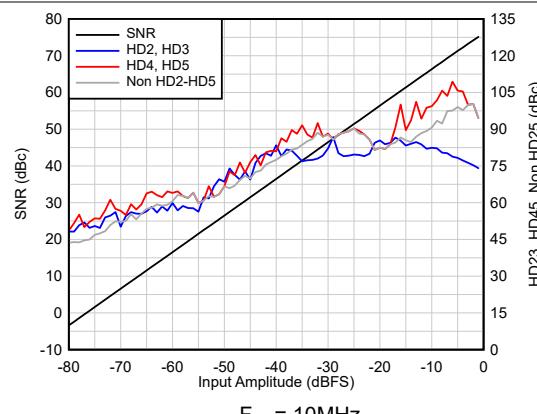

| IMD3  | 2 トーンの相互変調歪み | $f_1 = 100\text{MHz}$ , $f_2 = 120\text{MHz}$ , $A_{IN} = -7\text{dBFS}$ / トーン | 83  |     | dBc |

(1) SNR と HD3 の最小値は ATE で規定されています。HD2 はベンチ特性評価により規定されています。

## 6.8 電気的特性 - AC 仕様 (ADC3569 - 500MSPS)

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ        |                                      | テスト条件                                                | 最小値 <sup>(1)</sup> | 標準値  | 最大値 | 単位      |

|--------------|--------------------------------------|------------------------------------------------------|--------------------|------|-----|---------|

| <b>AC 精度</b> |                                      |                                                      |                    |      |     |         |

| NSD          | ノイズ スペクトル密度                          | $f_{IN} = 100\text{MHz}$ 、 $A_{IN} = -20\text{dBFS}$ | -160.4             |      |     | dBFS/Hz |

| NF           | ノイズ指数:                               | $f_{IN} = 100\text{MHz}$ 、 $A_{IN} = -20\text{dBFS}$ | 20.6               |      |     | dB      |

| SNR          | 信号対雑音比                               | $f_{IN} = 10\text{MHz}$                              | 75.8               |      |     | dBFS    |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 70                 | 75.6 |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             |                    | 74.9 |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             |                    | 72.6 |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             |                    | 71.5 |     |         |

| SINAD        | 信号対雑音歪み比                             | $f_{IN} = 10\text{MHz}$                              | 72.6               |      |     | dBFS    |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 73.7               |      |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 72.4               |      |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 68.2               |      |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 64.4               |      |     |         |

| ENOB         | 有効ビット数                               | $f_{IN} = 10\text{MHz}$                              | 11.8               |      |     | ビット     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 11.9               |      |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 11.7               |      |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 11.0               |      |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 10.4               |      |     |         |

| THD          | 全高調波歪み (最初の 5 つの高調波)                 | $f_{IN} = 10\text{MHz}$                              | 74                 |      |     | dBc     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 77                 |      |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 74                 |      |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 68                 |      |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 63                 |      |     |         |

| HD2          | 2 次高調波歪み                             | $f_{IN} = 10\text{MHz}$                              | 76                 |      |     | dBc     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 69                 | 82   |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 77                 |      |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 81                 |      |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 76                 |      |     |         |

| HD3          | 3 次高調波歪み                             | $f_{IN} = 10\text{MHz}$                              | 88                 |      |     | dBc     |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 71                 | 80   |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 83                 |      |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 71                 |      |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 65                 |      |     |         |

| Non HD2,3    | スプリアス フリー ダイナミック レンジ (HD2 と HD3 を除く) | $f_{IN} = 10\text{MHz}$                              | 94                 |      |     | dBFS    |

|              |                                      | $f_{IN} = 70\text{MHz}$                              | 94                 |      |     |         |

|              |                                      | $f_{IN} = 170\text{MHz}$                             | 90                 |      |     |         |

|              |                                      | $f_{IN} = 300\text{MHz}$                             | 86                 |      |     |         |

|              |                                      | $f_{IN} = 450\text{MHz}$                             | 87                 |      |     |         |

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力、内部リファレンスで規定されています。

| パラメータ | テスト条件        | 最小値 <sup>(1)</sup>                                                             | 標準値 | 最大値 | 単位  |

|-------|--------------|--------------------------------------------------------------------------------|-----|-----|-----|

| IMD3  | 2 トーンの相互変調歪み | $f_1 = 100\text{MHz}$ , $f_2 = 120\text{MHz}$ , $A_{IN} = -7\text{dBFS}$ / トーン | 86  |     | dBc |

(1) SNR と HD3 の最小値は ATE で規定されています。HD2 はベンチ特性評価により規定されています。

## 6.9 タイミング要件

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ                                                 | テスト条件                                           | 最小値                                         | 公称値           | 最大値           | 単位          |

|-------------------------------------------------------|-------------------------------------------------|---------------------------------------------|---------------|---------------|-------------|

| <b>ADC タイミング仕様</b>                                    |                                                 |                                             |               |               |             |

| $t_{AD}$                                              | アパーーチャ遅延                                        |                                             | 200           |               | ps          |

| $T_A$                                                 | アパーーチャジッタ                                       |                                             | 75            |               | fs          |

| CER                                                   | コード エラー レート                                     | $F_S = 500\text{MSPS}$ 、エラー > 64 コード        | 1E-10         | エラー / サンプル    |             |

|                                                       |                                                 | $F_S = 500\text{MSPS}$ 、エラー > 128 コード       | 3E-13         |               |             |

|                                                       |                                                 | $F_S = 250\text{MSPS}$ 、エラー > 64 コード        | 1E-11         |               |             |

| ウェークアップ時間                                             | グローバル パワー ダウン モード終了から有効データまでの時間 (内部電圧リファレンス オフ) |                                             | 3             |               | ms          |

| <b>レイテンシ: <math>t_{PD} + t_{ADC} + t_{DIG}</math></b> |                                                 |                                             |               |               |             |

| $t_{PD}$                                              | 伝搬遅延:サンプリング クロックの立ち下がりエッジから DCLK 立ち上がりエッジまで     | 伝搬遅延:サンプリング クロックの立ち下がりエッジから DCLK 立ち上がりエッジまで | $1.4 + T_S/4$ | $1.7 + T_S/4$ | $2 + T_S/4$ |

| $t_{ADC}$                                             | ADC レイテンシ                                       | SDR/DDR LVDS、通常モード                          | 38            | ADC クロック サイクル |             |

|                                                       |                                                 | DDR LVDS、低レイテンシ モード                         | 4             |               |             |

|                                                       | タイムスタンプ:入力から LVDS 出力まで                          | SDR/DDR LVDS                                | 8             |               |             |

| $t_{DIG}$                                             | デジタル レイテンシ:インターフェイスおよびデシメーション                   | DDC バイパス                                    | 5             | 出力クロック サイクル   |             |

|                                                       |                                                 | 1/2 のデシメーション (実数または複素数)                     | 24            |               |             |

|                                                       |                                                 | 1/4、1/8 のデシメーション (実数または複素数)                 | 49            |               |             |

|                                                       |                                                 | 1/16~1/32768 のデシメーション (実数または複素数)            | 50            |               |             |

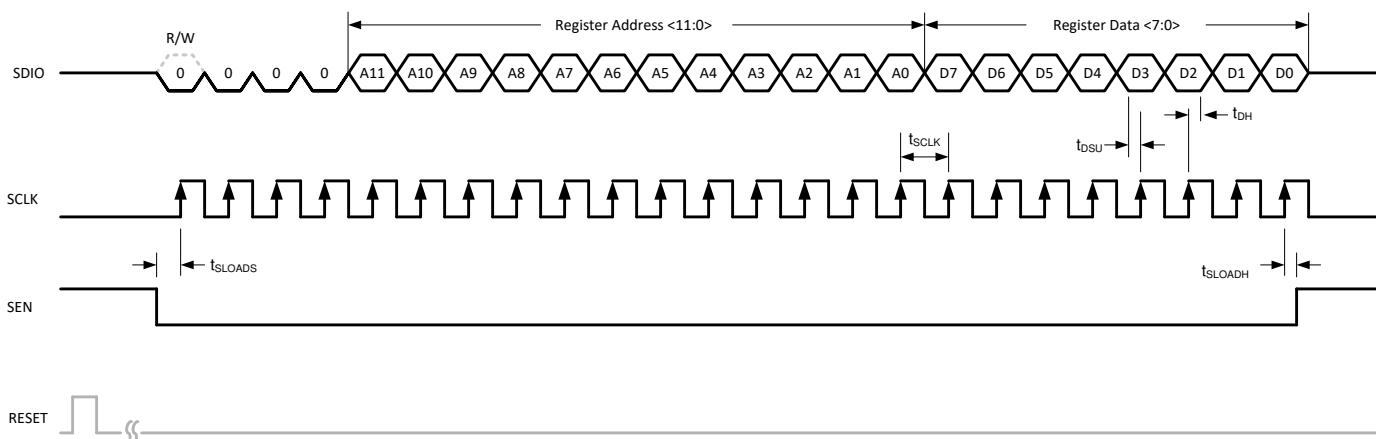

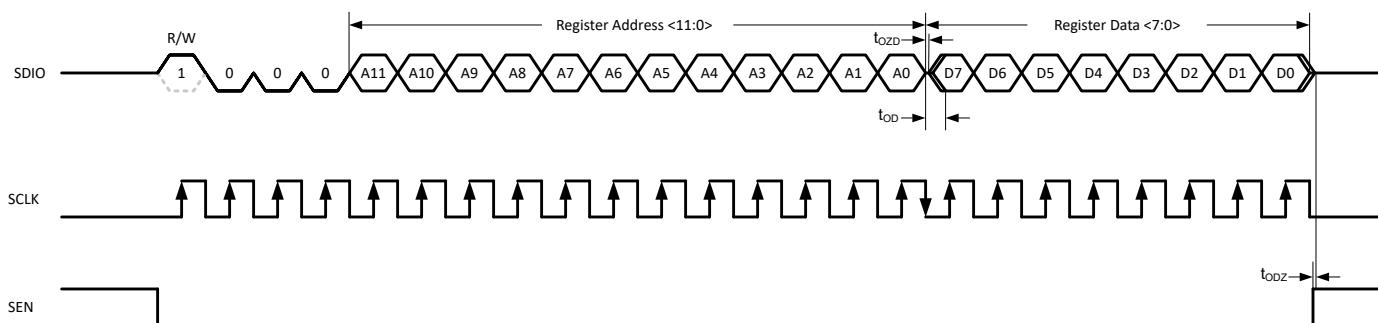

| <b>シリアル プログラミング インターフェイス (SCLK, SEN, SDIO) - 入力</b>   |                                                 |                                             |               |               |             |

| $f_{CLK(SCLK)}$                                       | シリアル クロック周波数                                    |                                             | 1             | 20            | MHz         |

| $t_{SLOADS}$                                          | SEN 立ち下がりエッジから SCLK 立ち上がりエッジまでのセットアップ時間         |                                             | 10            |               | ns          |

| $t_{SLOADH}$                                          | SCLK 立ち上がりエッジから SEN 立ち上がりエッジまでのホールド時間           |                                             | 10            |               | ns          |

| $t_{DSU}$                                             | SDIO から SCLK 立ち上がりエッジまでのセットアップ時間                |                                             | 10            |               | ns          |

| $t_{DH}$                                              | SCLK 立ち上がりエッジから SDIO までのホールド時間                  |                                             | 10            |               | ns          |

| <b>シリアル プログラミング インターフェイス (SDIO) - 出力</b>              |                                                 |                                             |               |               |             |

| $t_{(OZD)}$                                           | SDIO トライステートから駆動へ                               |                                             |               | 10            | ns          |

| $t_{(ODZ)}$                                           | SDIO データからトライステートへ                              |                                             |               | 14            | ns          |

| $t_{(OD)}$                                            | SDIO は SCLK の立ち下がりエッジから有効                       |                                             |               | 10            | ns          |

| <b>タイミング: SYSREF</b>                                  |                                                 |                                             |               |               |             |

| $t_{s(SYSREF)}$                                       | セットアップ時間:SYSREF 有効から CLKP/M 立ち上がりエッジまで          |                                             | 100           |               | ps          |

| $t_{h(SYSREF)}$                                       | ホールド時間:CLKP/M 立ち上がりエッジから SYSREF 無効まで            |                                             | 100           |               | ps          |

| <b>インターフェイス タイミング: SDR LVDS</b>                       |                                                 |                                             |               |               |             |

| $t_{DV}$                                              | データ有効時間:データ遷移から DCLK 立ち上がりエッジまで                 | $F_S = 500\text{MSPS}$                      | 0.465         | 0.68          | 0.905       |

|                                                       |                                                 | $F_S = 250\text{MSPS}$                      | 0.905         | 1.16          | 1.415       |

| $t_{DI}$                                              | データ無効時間:DCLK 立ち上がりエッジからデータ遷移まで                  | $F_S = 500\text{MSPS}$                      | 1.095         | 1.32          | 1.495       |

|                                                       |                                                 | $F_S = 250\text{MSPS}$                      | 2.615         | 2.84          | 3.015       |

| <b>インターフェイス タイミング: DDR および SLVDS</b>                  |                                                 |                                             |               |               |             |

| $t_{DV}$                                              | データ有効時間:データ遷移から DCLK 遷移まで                       | $F_S = 500\text{MSPS}$                      | 0.465         | 0.68          | 0.905       |

|                                                       |                                                 | $F_S = 250\text{MSPS}$                      | 0.905         | 1.16          | 1.415       |

## 6.9 タイミング要件 (続き)

最大値と最小値は、自由気流での動作温度範囲および公称電源電圧について規定されています。特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

| パラメータ           |                          | テスト条件                  | 最小値   | 公称値  | 最大値   | 単位 |

|-----------------|--------------------------|------------------------|-------|------|-------|----|

| $t_{\text{DI}}$ | データ無効時間:DCLK 遷移からデータ遷移まで | $F_S = 500\text{MSPS}$ | 0.095 | 0.32 | 0.535 | ns |

|                 |                          | $F_S = 250\text{MSPS}$ | 0.615 | 0.84 | 1.065 | ns |

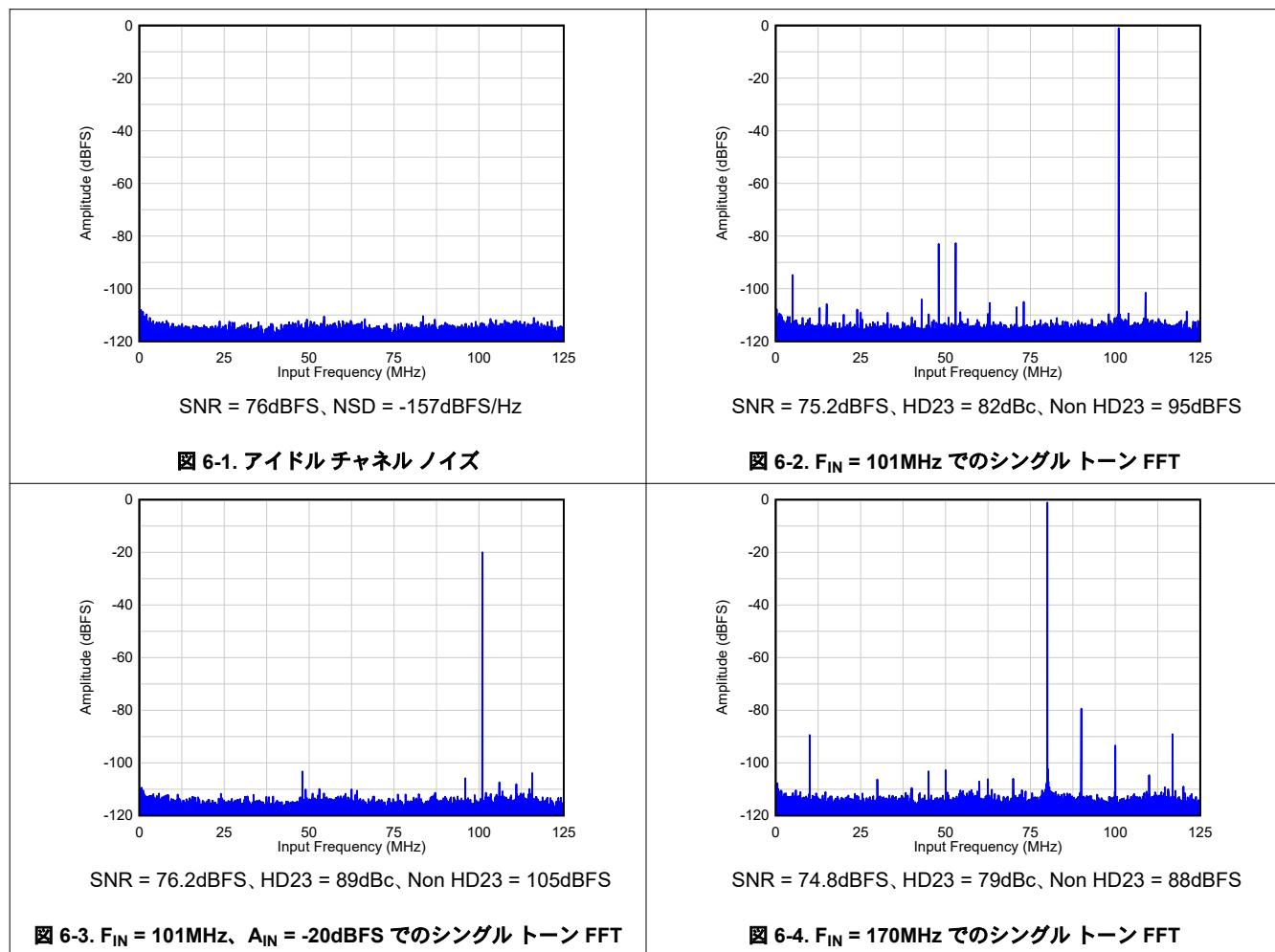

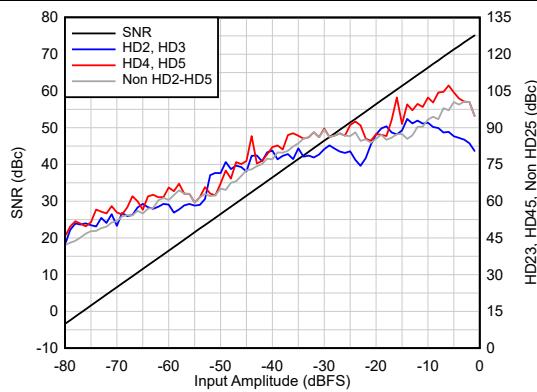

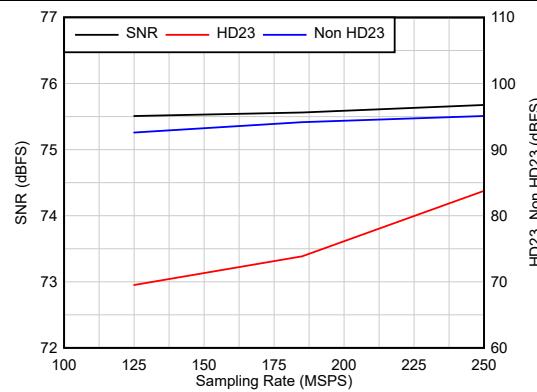

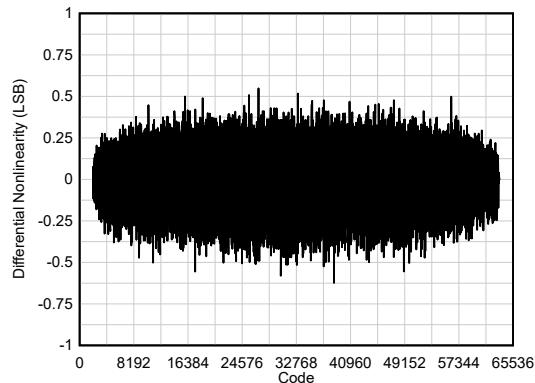

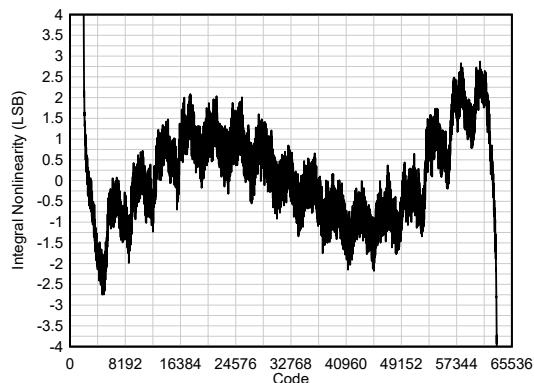

## 6.10 代表的特性、ADC3568

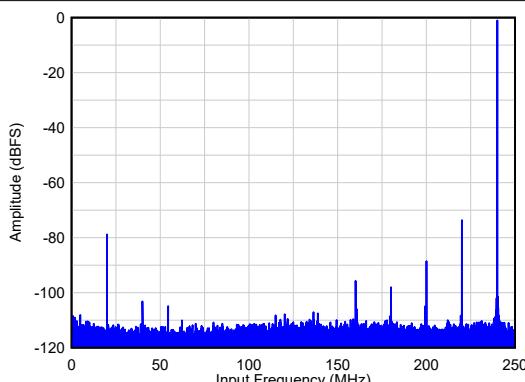

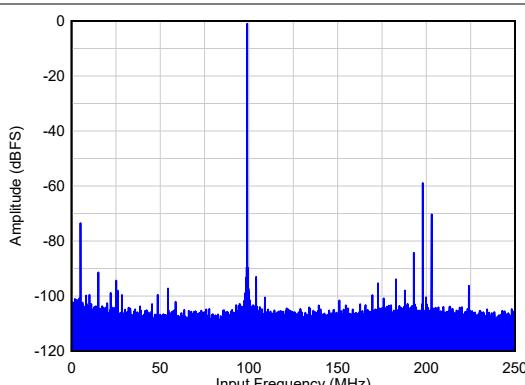

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

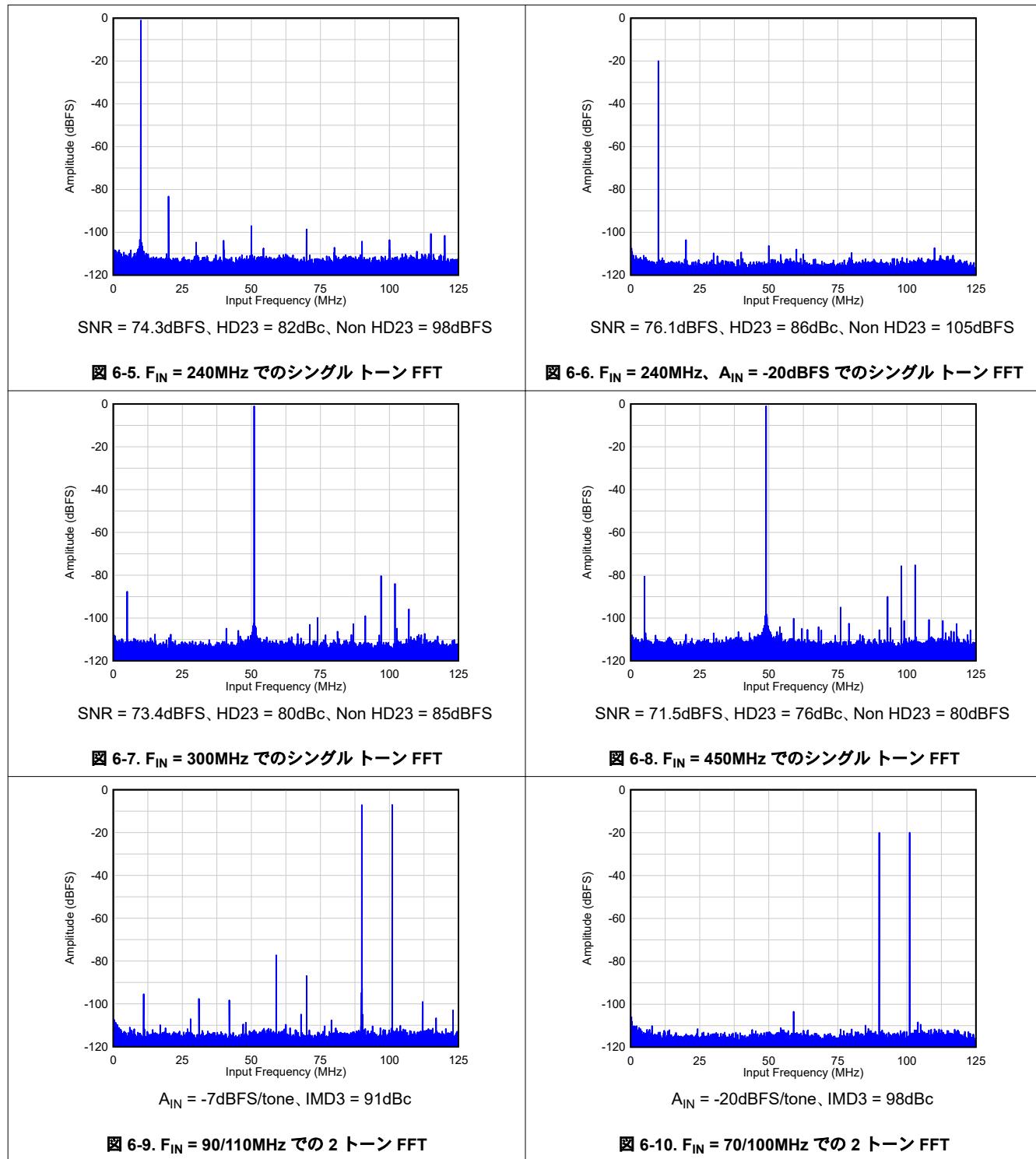

## 6.10 代表的特性、ADC3568 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

## 6.10 代表的特性、ADC3568 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

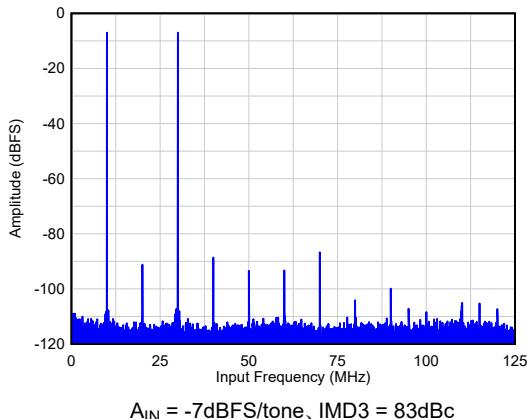

図 6-11.  $F_{IN} = 220/240\text{MHz}$  での 2 トーン FFT

図 6-12.  $F_{IN} = 220/240\text{MHz}$  での 2 トーン FFT

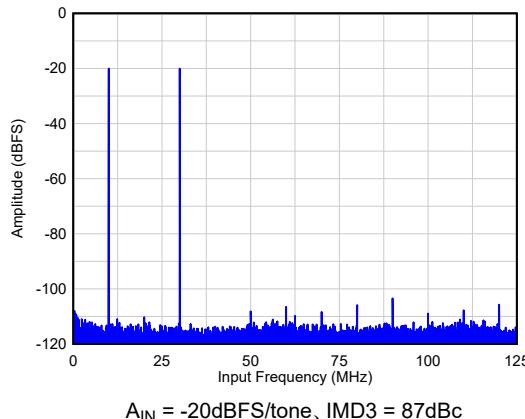

図 6-13. AC 性能と  $F_{IN}$  との関係

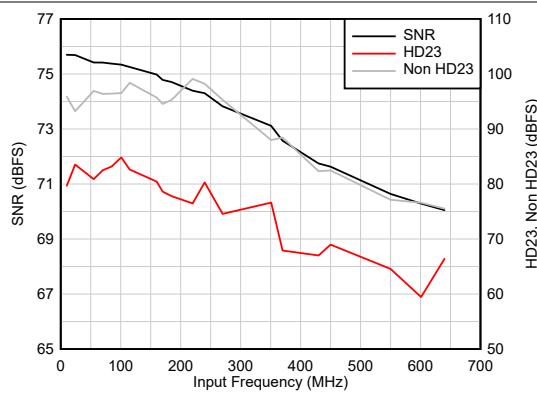

図 6-14. AC 性能と  $A_{IN}$  との関係

図 6-15. AC 性能と  $A_{IN}$  との関係

図 6-16. AC 性能と  $F_S$  との関係

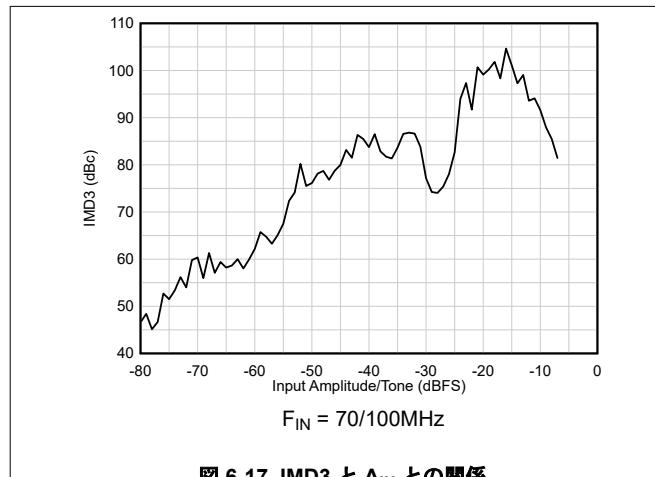

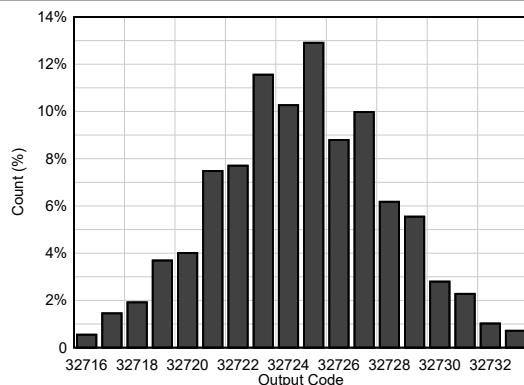

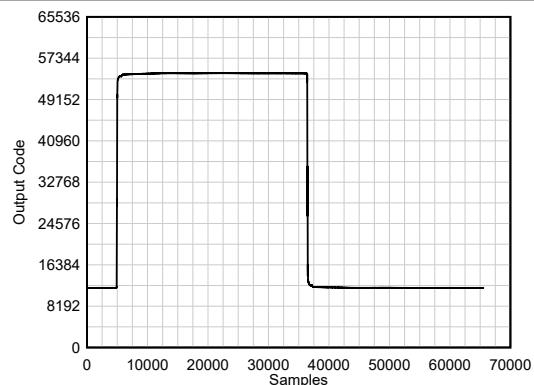

## 6.10 代表的特性、ADC3568 (続き)

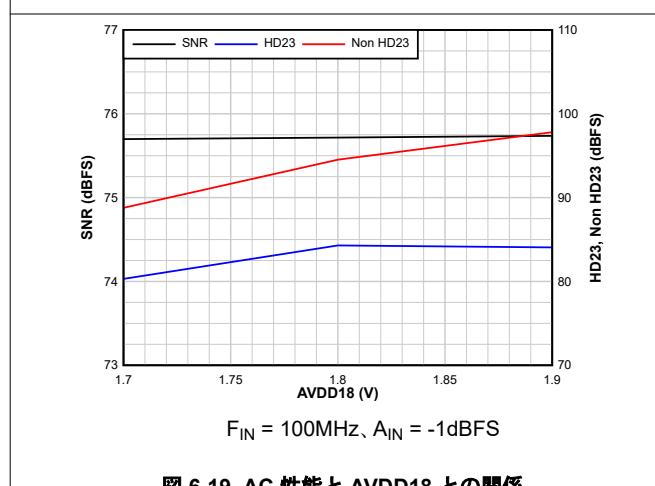

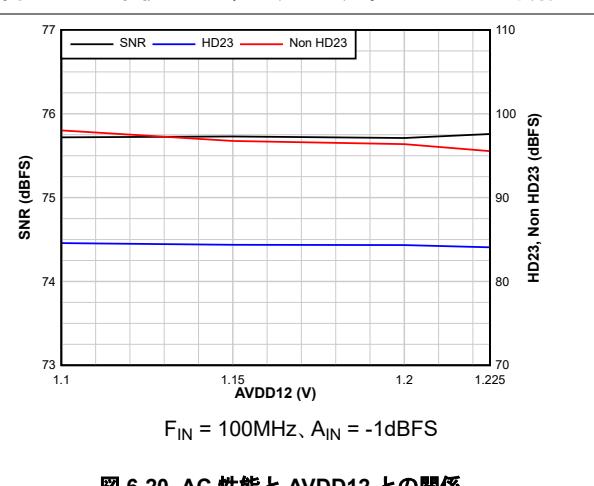

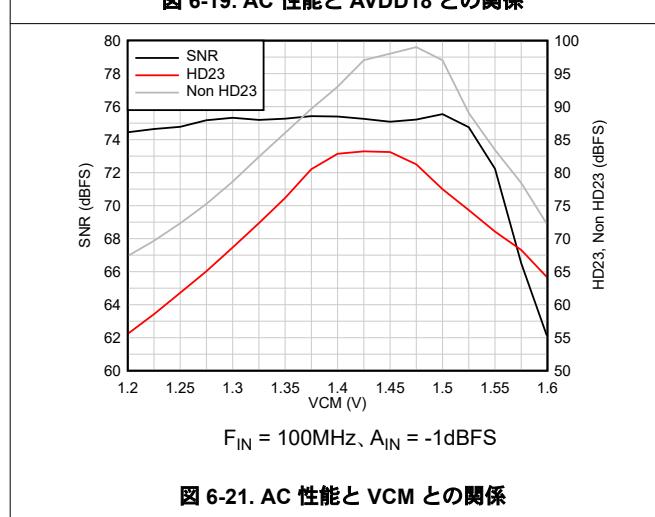

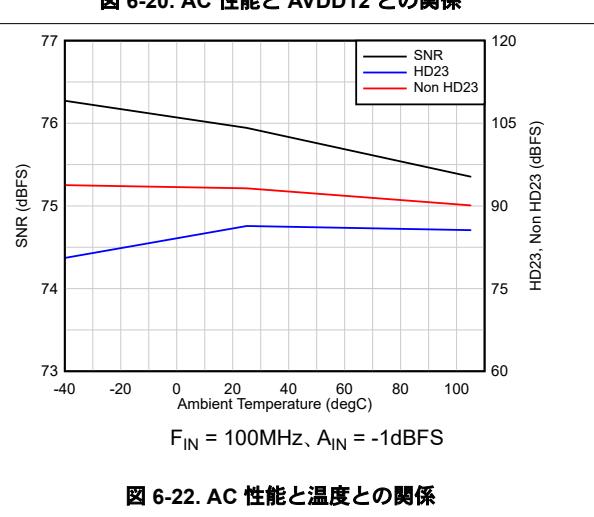

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

図 6-17. IMD3 と  $A_{IN}$  との関係

図 6-18. AC 性能とクロック デューティ サイクルとの関係

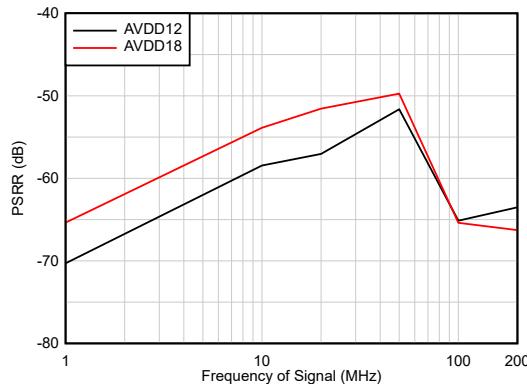

図 6-19. AC 性能と AVDD18 との関係

図 6-20. AC 性能と AVDD12 との関係

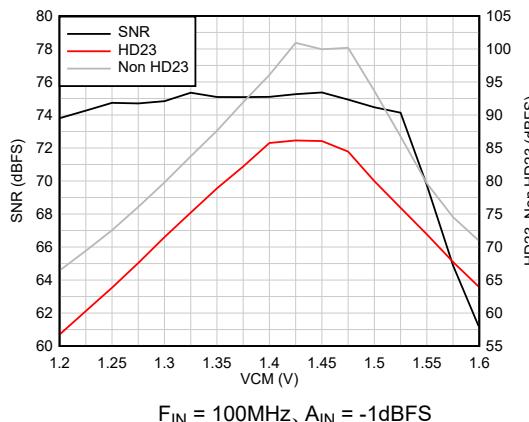

図 6-21. AC 性能と VCM との関係

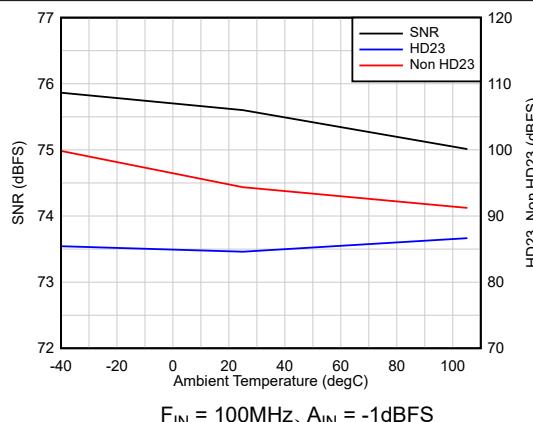

図 6-22. AC 性能と温度との関係

## 6.10 代表的特性、ADC3568 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 250MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

図 6-23. DNL

図 6-24. INL

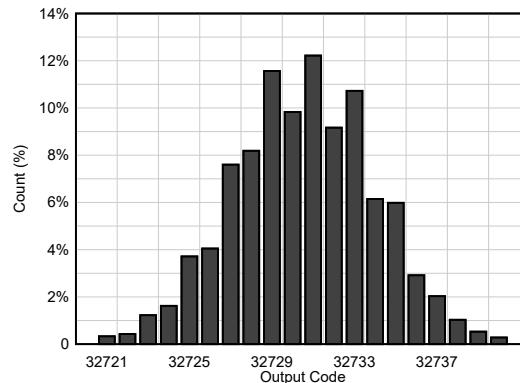

図 6-25. DC オフセット ヒストグラム

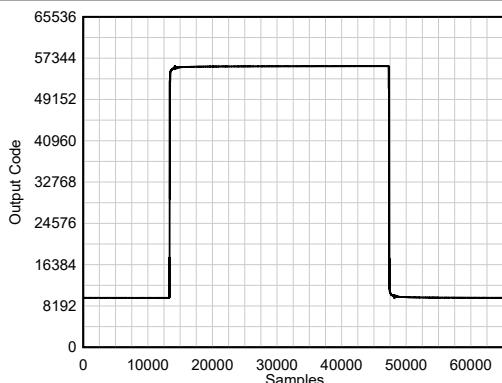

図 6-26. パルス応答

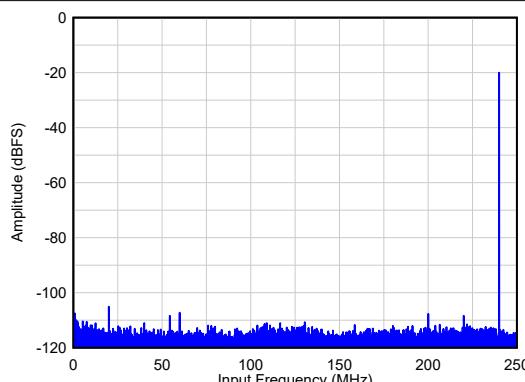

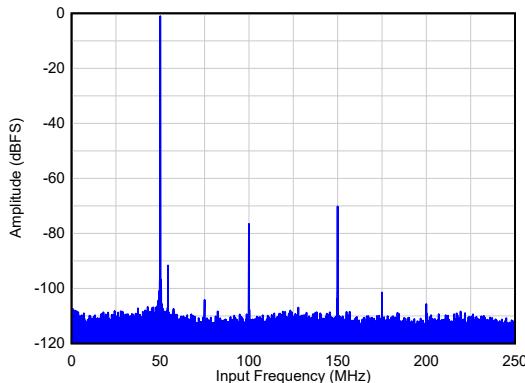

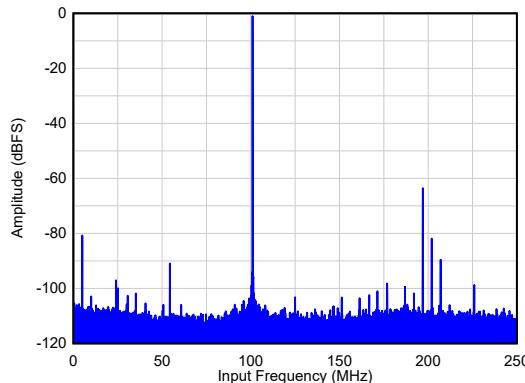

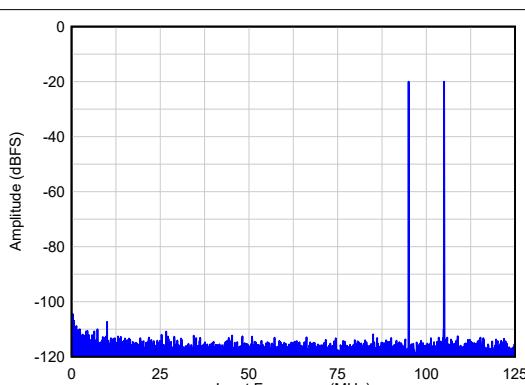

## 6.11 代表的特性、ADC3569

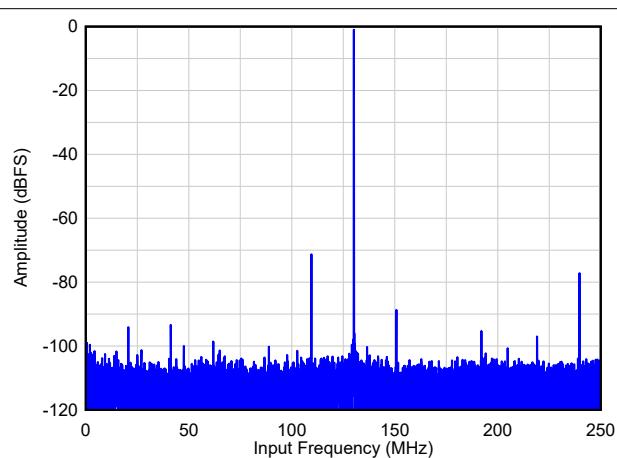

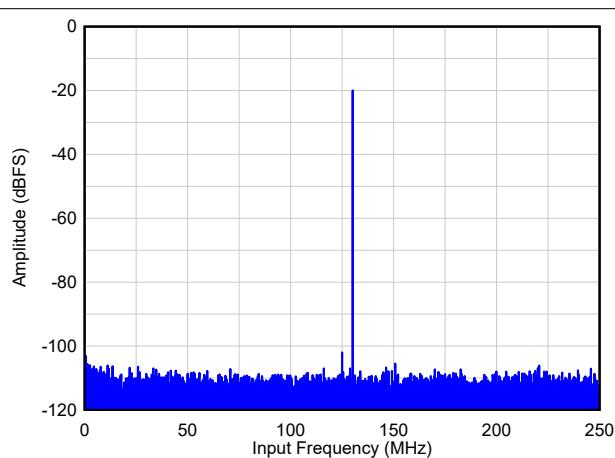

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

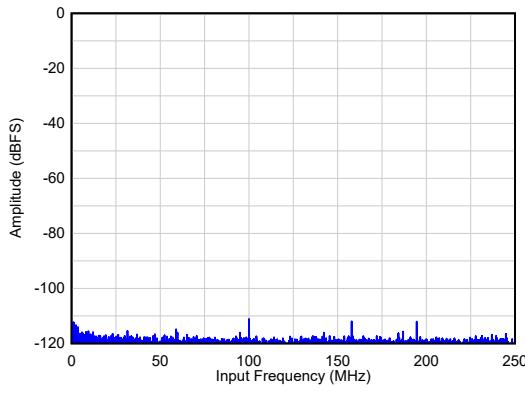

図 6-27. アイドル チャネル ノイズ

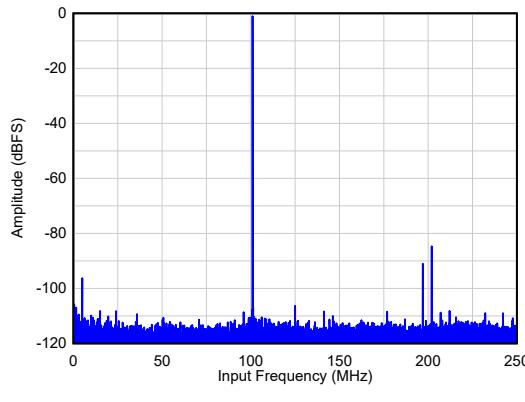

図 6-28.  $F_{\text{IN}} = 101\text{MHz}$  でのシングル トーン FFT

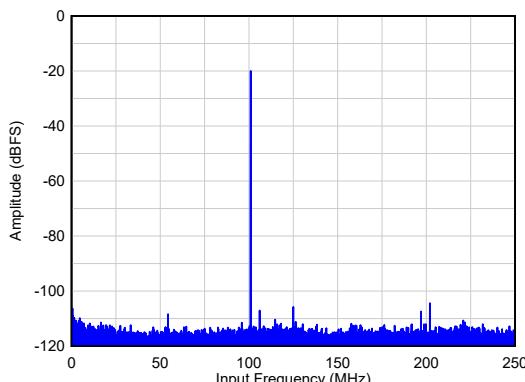

図 6-29.  $F_{\text{IN}} = 101\text{MHz}$ 、 $A_{\text{IN}} = -20\text{dBFS}$  でのシングル トーン FFT

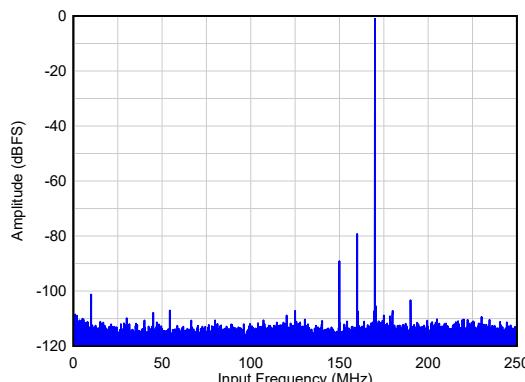

図 6-30.  $F_{\text{IN}} = 170\text{MHz}$  でのシングル トーン FFT

図 6-31.  $F_{\text{IN}} = 240\text{MHz}$  でのシングル トーン FFT

図 6-32.  $F_{\text{IN}} = 240\text{MHz}$ 、 $A_{\text{IN}} = -20\text{dBFS}$  でのシングル トーン FFT

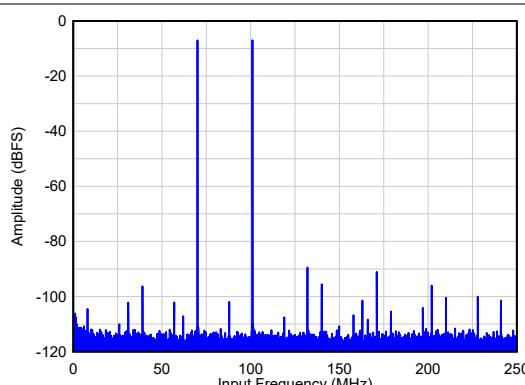

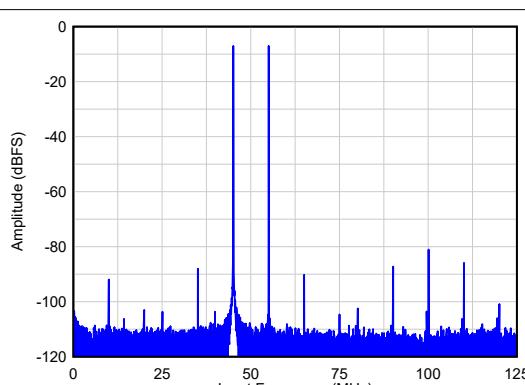

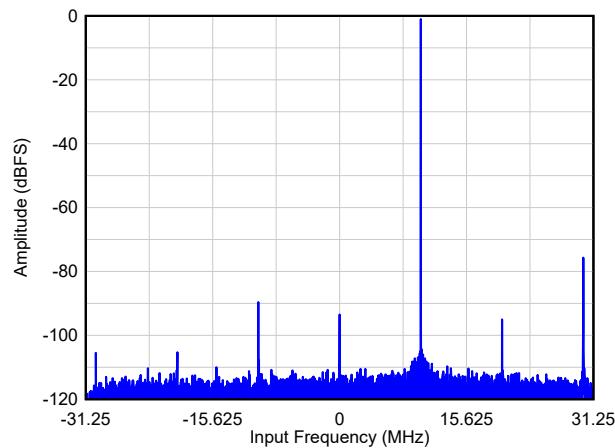

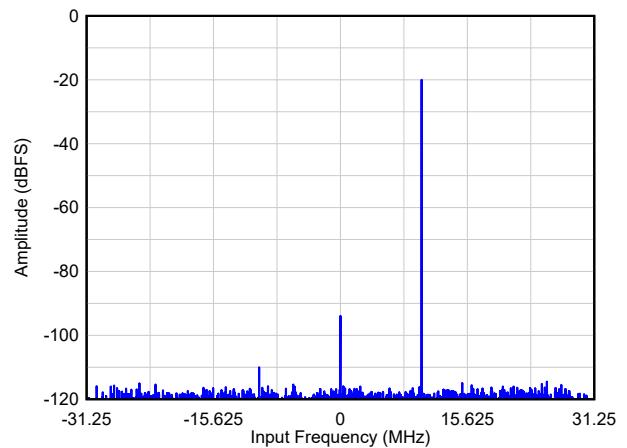

## 6.11 代表的特性、ADC3569 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

図 6-33.  $F_{\text{IN}} = 450\text{MHz}$  でのシングル トーン FFT

図 6-34.  $F_{\text{IN}} = 605\text{MHz}$  でのシングル トーン FFT

図 6-35.  $F_{\text{IN}} = 905\text{MHz}$  でのシングル トーン FFT

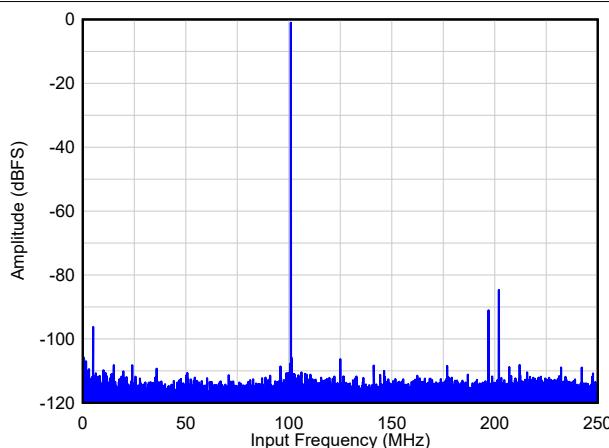

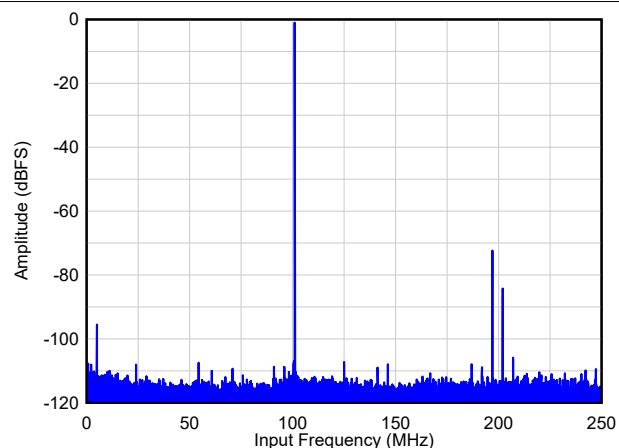

図 6-36.  $F_{\text{IN}} = 70/100\text{MHz}$  での 2 トーン FFT

$A_{\text{IN}} = -20\text{dBFS/tone}$ 、IMD3 = 92dBc

$A_{\text{IN}} = -7\text{dBFS/tone}$ 、IMD3 = 81dBc

図 6-37.  $F_{\text{IN}} = 70/100\text{MHz}$  での 2 トーン FFT

図 6-38.  $F_{\text{IN}} = 401/450\text{MHz}$  での 2 トーン FFT

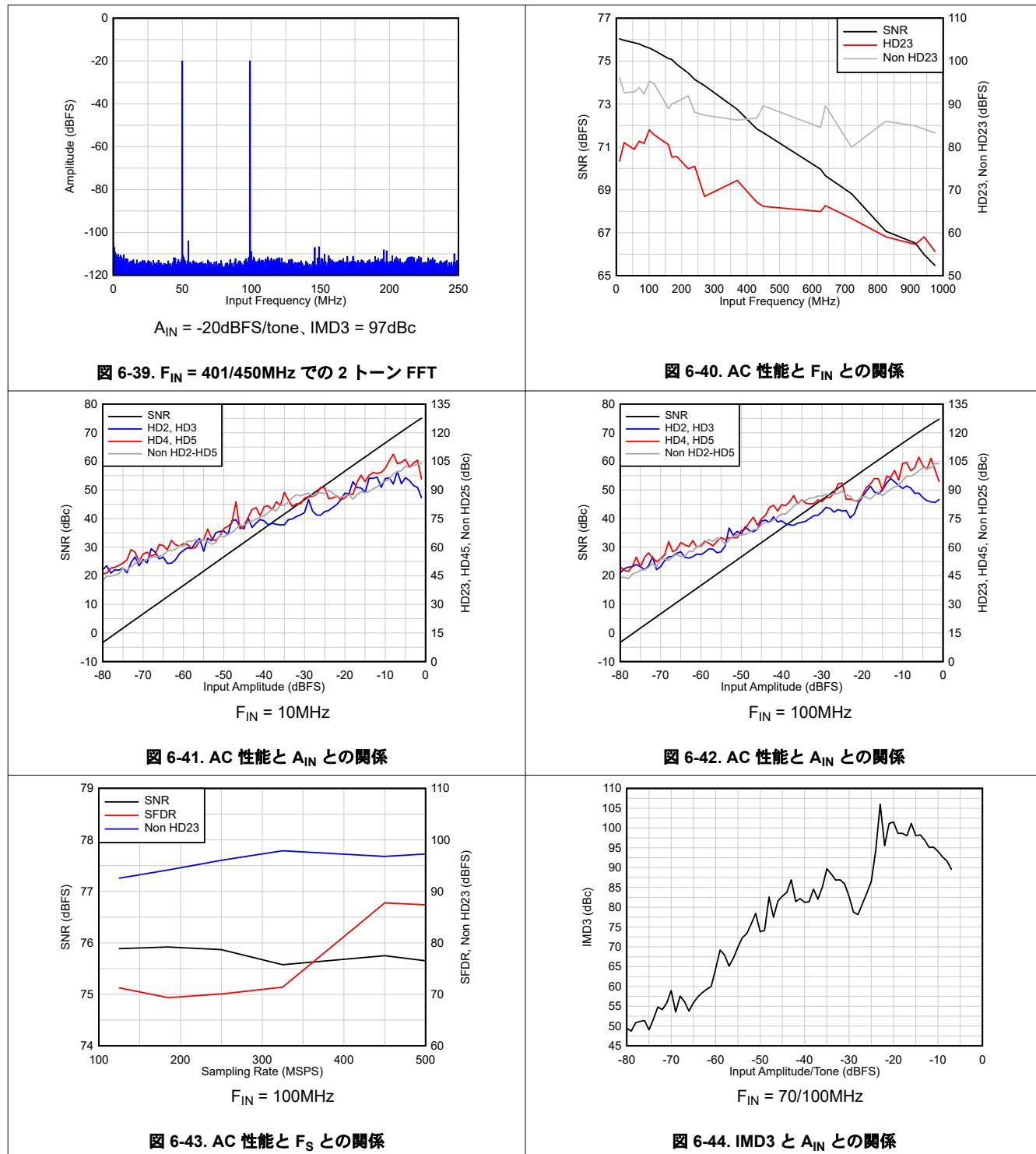

## 6.11 代表的特性、ADC3569 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

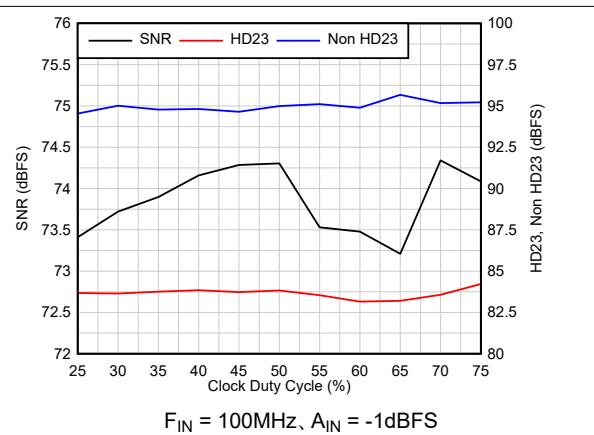

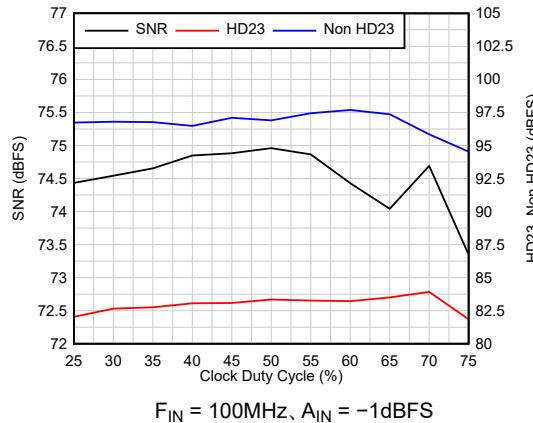

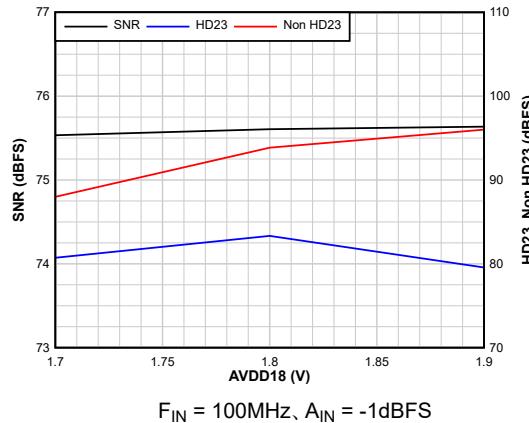

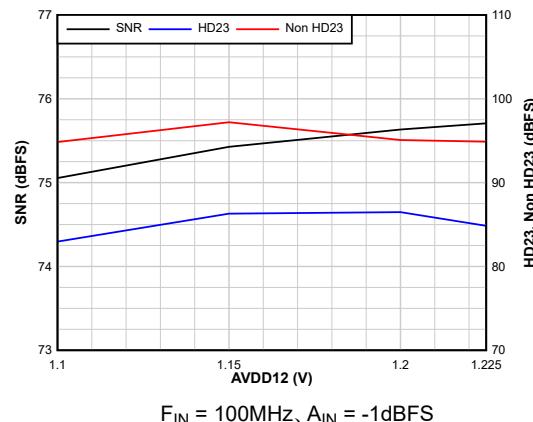

## 6.11 代表的特性、ADC3569 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

図 6-45. AC 性能とクロック デューティ サイクルとの関係

図 6-46. AC 性能と AVDD18 との関係

図 6-47. AC 性能と AVDD12 との関係

図 6-48. AC 性能と VCM との関係

図 6-49. AC 性能と温度との関係

図 6-50. DNL

## 6.11 代表的特性、ADC3569 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

図 6-51. INL

図 6-52. DC オフセットヒストグラム

図 6-53. パルス応答

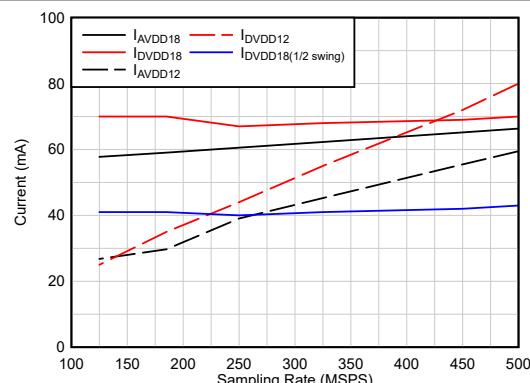

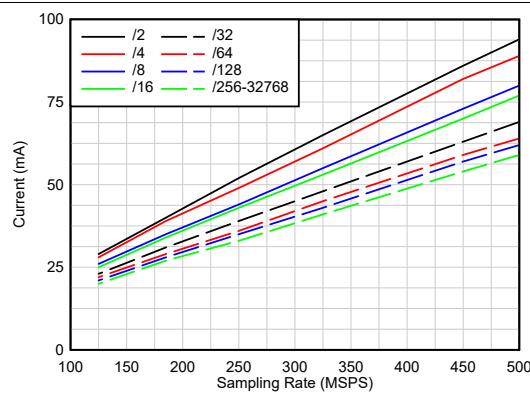

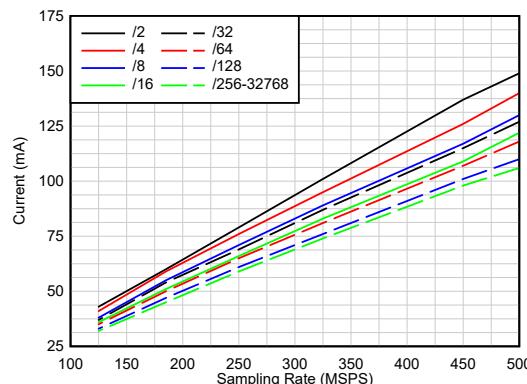

図 6-54. 電流とサンプリング レートとの関係

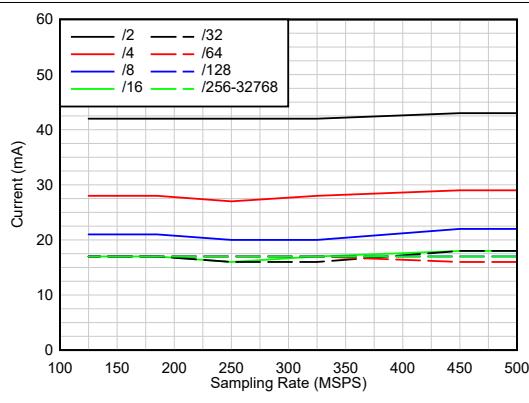

図 6-55. 電流とサンプリング レートとの関係

図 6-56. 電流とサンプリング レートとの関係

## 6.11 代表的特性、ADC3569 (続き)

特に記述のない限り、標準値は  $T_A = 25^\circ\text{C}$ 、ADC サンプリング レート = 500MSPS、DDC バイパス モード、50% クロック デューティ サイクル、公称電源電圧、-1dBFS 差動入力で規定されています。

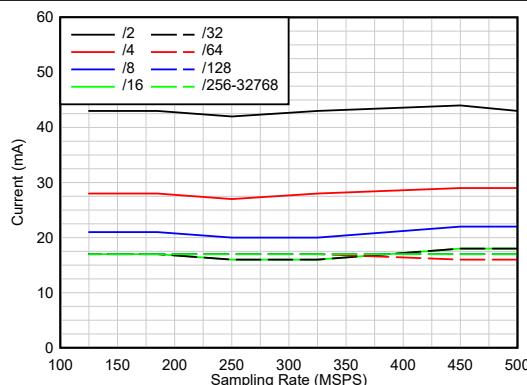

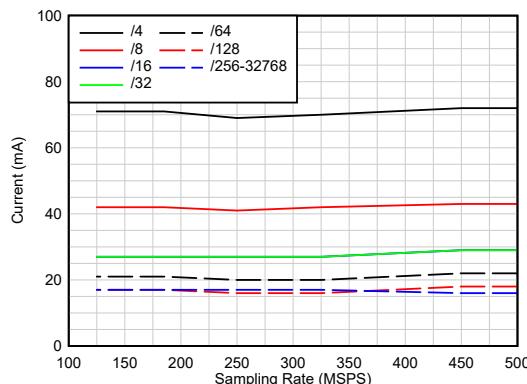

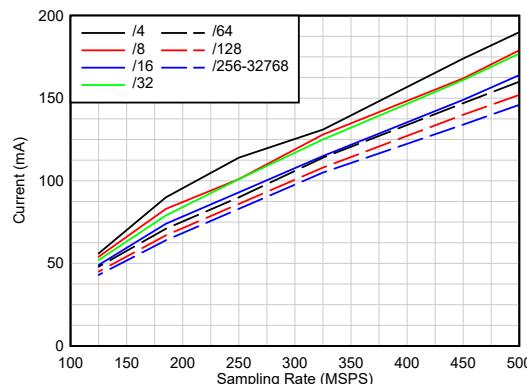

複素デシメーション、シングル バンド、DVDD18

図 6-57. 電流とサンプリング レートとの関係

複素デシメーション、シングル バンド、DVDD12

図 6-58. 電流とサンプリング レートとの関係

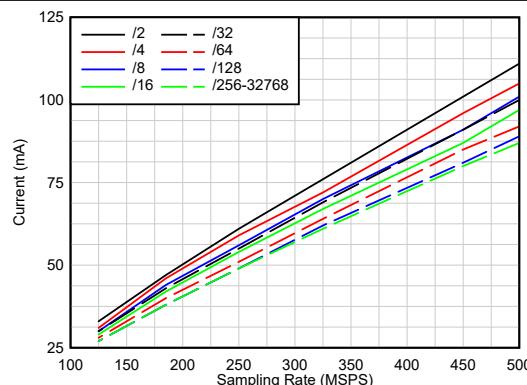

複素デシメーション、デュアル バンド、DVDD18

図 6-59. 電流とサンプリング レートとの関係

複素デシメーション、デュアル バンド、DVDD12

図 6-60. 電流とサンプリング レートとの関係

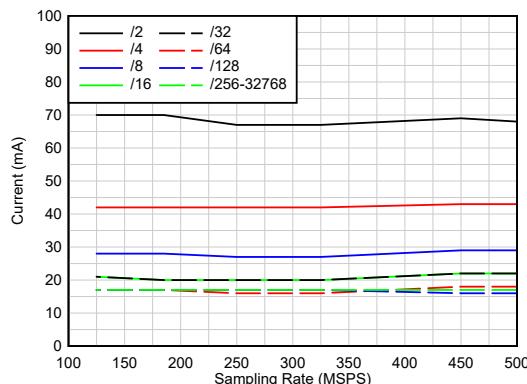

複素デシメーション、クワッド バンド、DVDD18

図 6-61. 電流とサンプリング レートとの関係

複素デシメーション、クワッド バンド、DVDD12

図 6-62. 電流とサンプリング レートとの関係

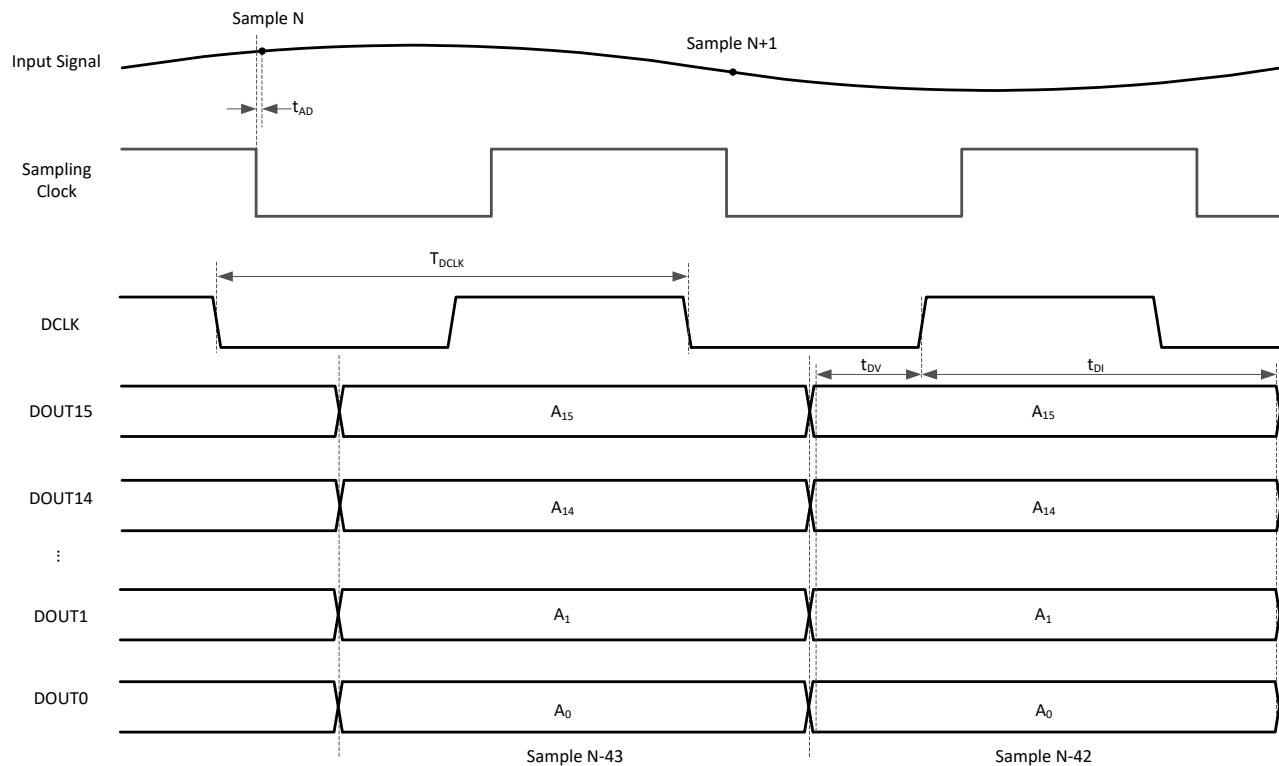

## 7 パラメータ測定情報

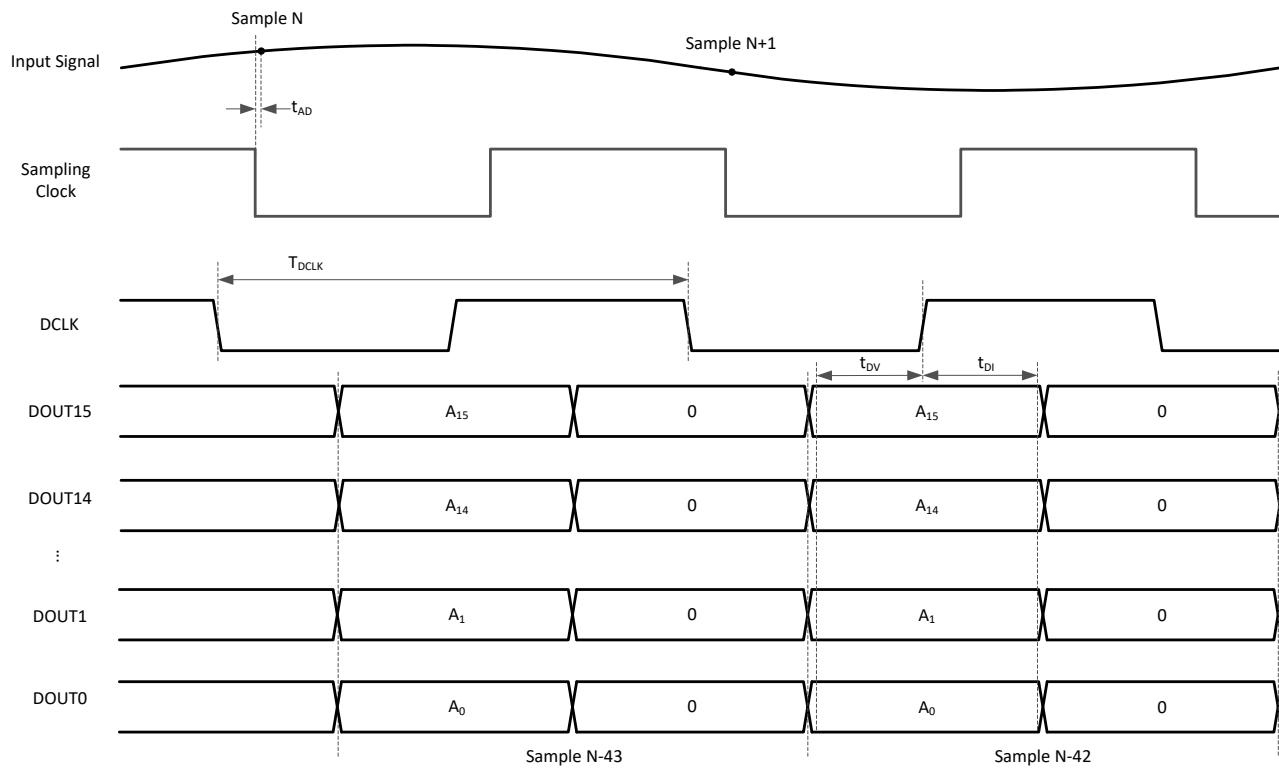

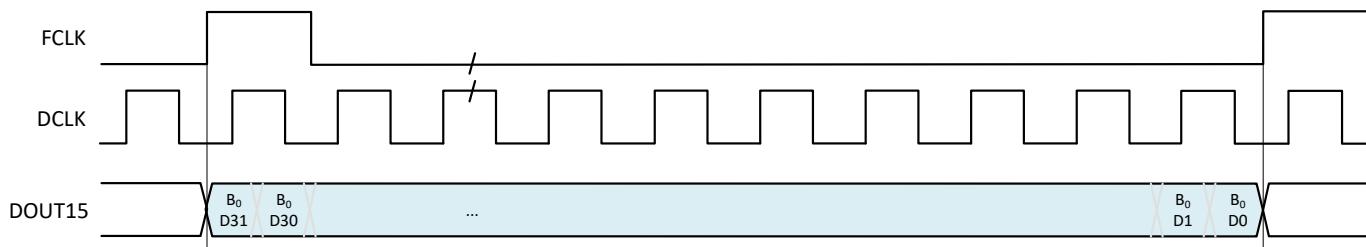

図 7-1. タイミング図 - パラレル SDR LVDS (デフォルト)

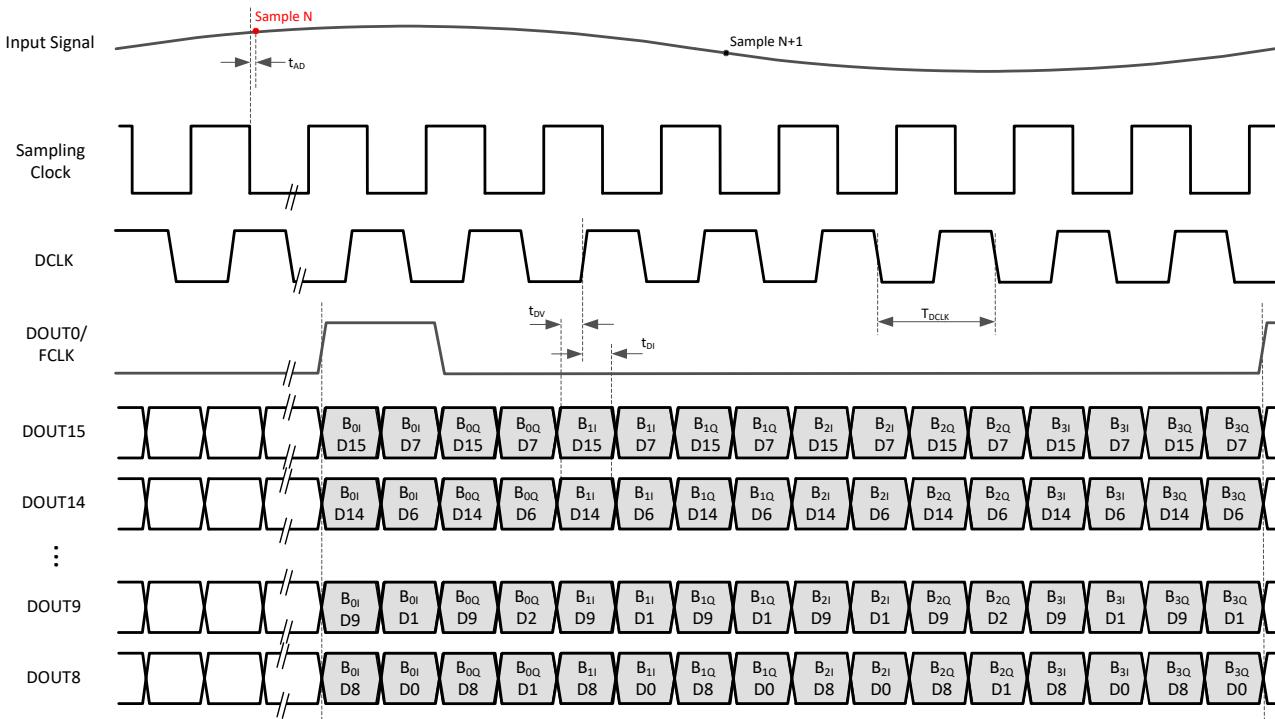

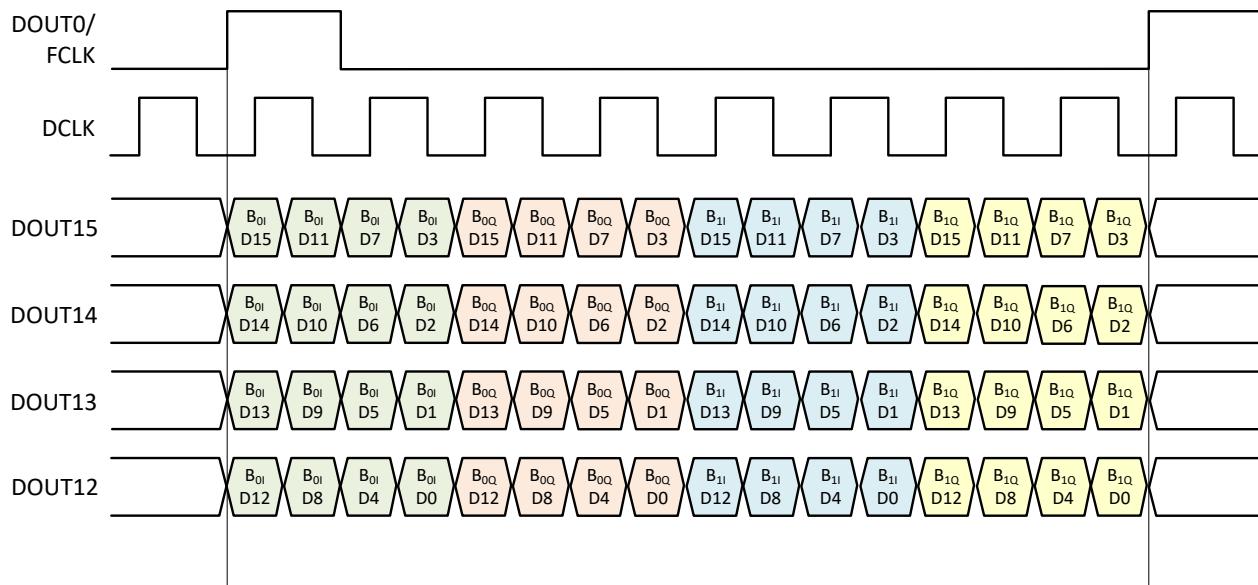

図 7-2. タイミング図 - パラレル DDR LVDS (レジスタ 0x110 のレジスタ書き込みを使用)

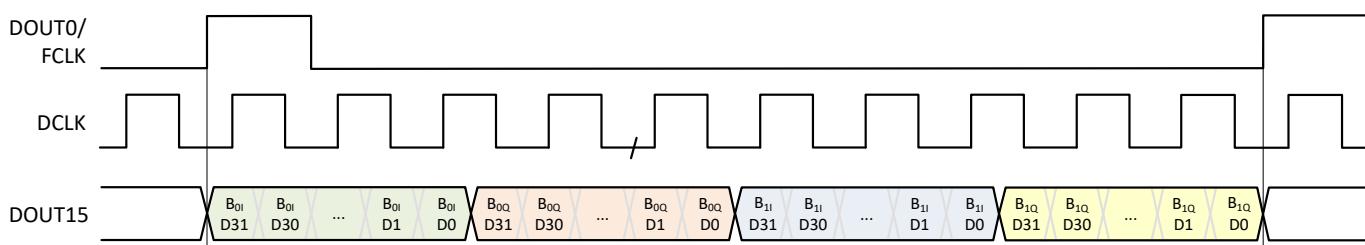

図 7-3. タイミング図 - シリアル LVDS (例 : クワッド バンド、16 ビット、1/8 の複素デシメーション)

## 8 詳細説明

### 8.1 概要

ADC356x は、16 ビット、250MSPS および 500MSPS のシングル チャネル A/D コンバータ (ADC) です。このデバイスは、高い信号対雑音比 (SNR) を実現するよう設計されており、-160dBFS/Hz という低いソイズ スペクトル密度を備えています。バッファ付きアナログ入力は、1.4GHz (-3dB) のフルパワー入力帯域幅で、100Ω および 200Ω のプログラム可能な内部終端インピーダンスをサポートしています。

ADC356x は、クワッド バンド デジタル ダウンコンバータ (DDC) を搭載しており、比率 2 の広帯域デシメーションから、比率 32768 の狭帯域デシメーションまでサポートしています。DDC では、位相コヒーレントと位相連続の周波数ホッピングをサポートする 48 ビット NCO を使用しています。

ADC356x には、フレキシブルな LVDS インターフェイスが装備されています。デシメーション バイパス モードでは、出力データは、SDR または DDR クロックにより、16 組の LVDS ペアを介して送信されます。実数または複素数のデシメーションを使用する場合、出力データは、シリアル LVDS インターフェイスを使って送信されます。デシメーションが増加すると、使用されるレーン数が減少します。

電力効率の優れた ADC アーキテクチャは、500MSPS で 435mW の消費電力を実現し、低サンプリング レートで電力スケーリングを実現します (250MSPS で 369mW)。

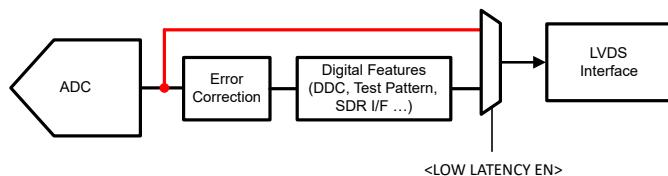

### 8.2 機能ブロック図

図 8-1. ブロック図

## 8.3 機能説明

### 8.3.1 アナログ入力

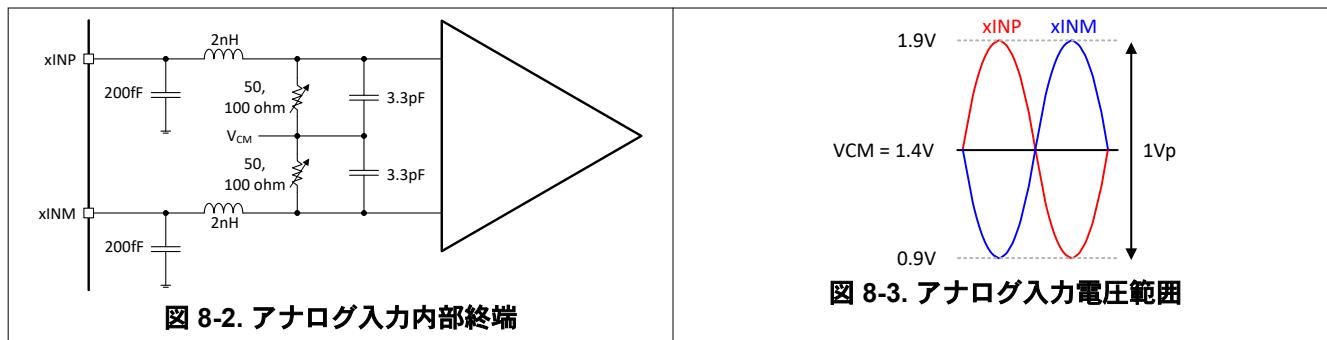

ADC366x のアナログ入力には内部バッファがあり、サンプリングコンデンサを外部入力回路のグリッチノイズから絶縁します。アナログ入力には、 $100\Omega$  の差動分割終端があり、 $V_{CM}$  への内部バイアスを備えています (図 8-2 の代表的な入力モデルを参照)。これは、SPI レジスタへの書き込みにより差動  $200\Omega$  終端に変更できます。

入力フルスケールは  $2V_{pp}$ 、 $V_{CM}$  は  $1.4V$  なので、アナログ入力の電圧は  $0.9\sim1.9V$  の範囲で変動します。ADC 入力は、通常動作で  $1.9V$  をサポートするように、信頼性の高い設計を採用しています。

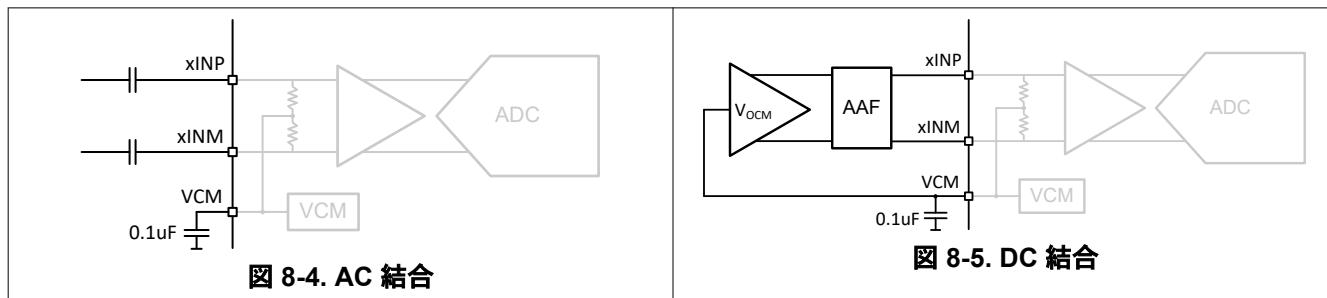

このデバイスは、図 8-4 および図 8-5 に示すように、アナログ入力の AC 結合と DC 結合の両方をサポートしています。

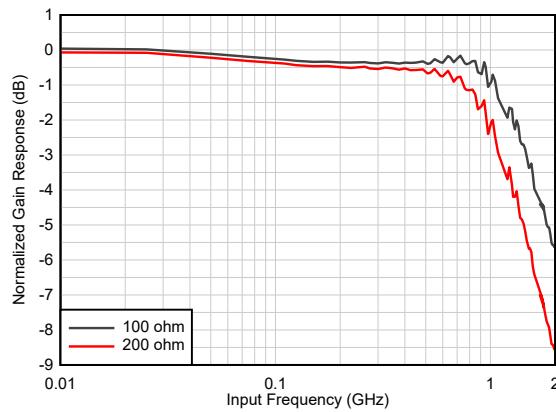

図 8-6 に、内部終端  $100\Omega$  および  $200\Omega$  に対する入力帯域幅 (-3dB) を示します。

**図 8-6. 内部終端  $100\Omega$  および  $200\Omega$  に対するフルパワー入力帯域幅**

### 8.3.1.1 ナイキスト ゾーン選択

この ADC は、目的の信号がどのナイキスト ゾーンにあるかに基づいて最適化されるデジタル誤り訂正を備えています。最適な性能を得るには、SPI レジスタ マップで正しい入力周波数範囲 (レジスタ 0x132) およびナイキスト ゾーン (レジスタ 0x16B) を選択する必要があります。デフォルトでは、1 次ナイキスト ゾーンが選択されています。

### 8.3.1.2 アナログ フロント エンド設計

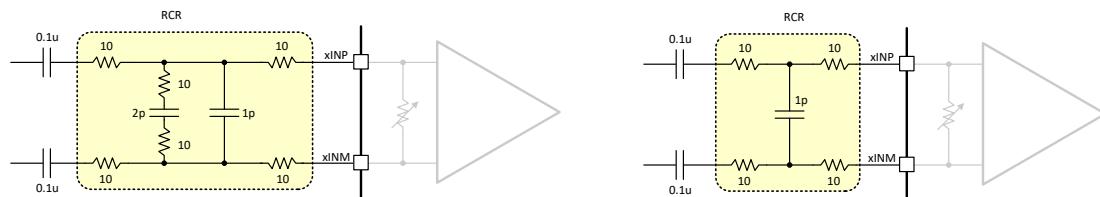

ADC の SNR と HD3 性能を最適化するため、アナログ入力のすぐ前に RCR 回路を追加することを推奨します。図 8-7 に、入力周波数が 500MHz より低い場合と高い場合に推奨される RCR 回路を示します (この例は AC 結合を示していますが、DC 結合でも同じように適用できます)。ソース インピーダンスは  $50\Omega$  と想定しています。ADC が外部アンプによって駆動される場合は、RCR 回路が不要になることもあります。

図 8-7.  $F_{IN} < 500\text{MHz}$  (左) および  $F_{IN} > 500\text{MHz}$  (右) の外部 RCR

### 8.3.2 サンプリング クロック

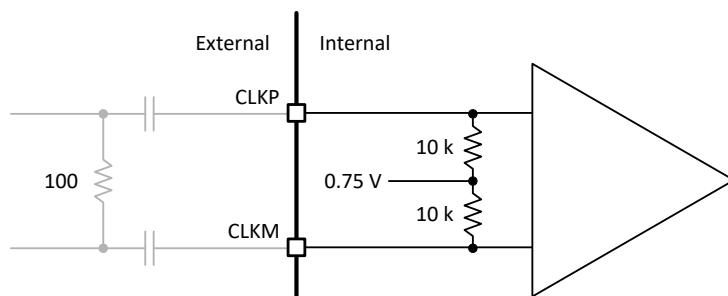

サンプリング クロック入力は、外部 AC 結合および終端を備えており、差動で駆動されるよう設計されています。この ADC には、図 8-8 に示すように、内部同相電圧バイアスがあります。

図 8-8. サンプリング クロック入力回路

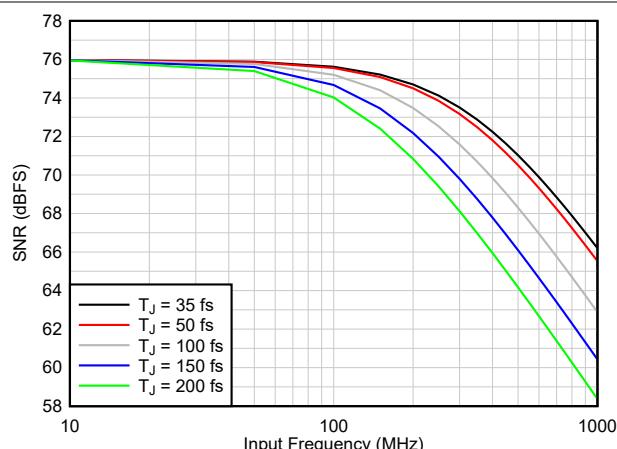

内部サンプリング クロック パスは、残留位相ノイズへの影響が小さくなるように設計されています。サンプリング クロック回路には、最高の位相ノイズとジッタ性能を得るために、専用の低ノイズ電源が必要です。内部残留クロックの位相ノイズは、クロックの振幅にも影響を受けます。

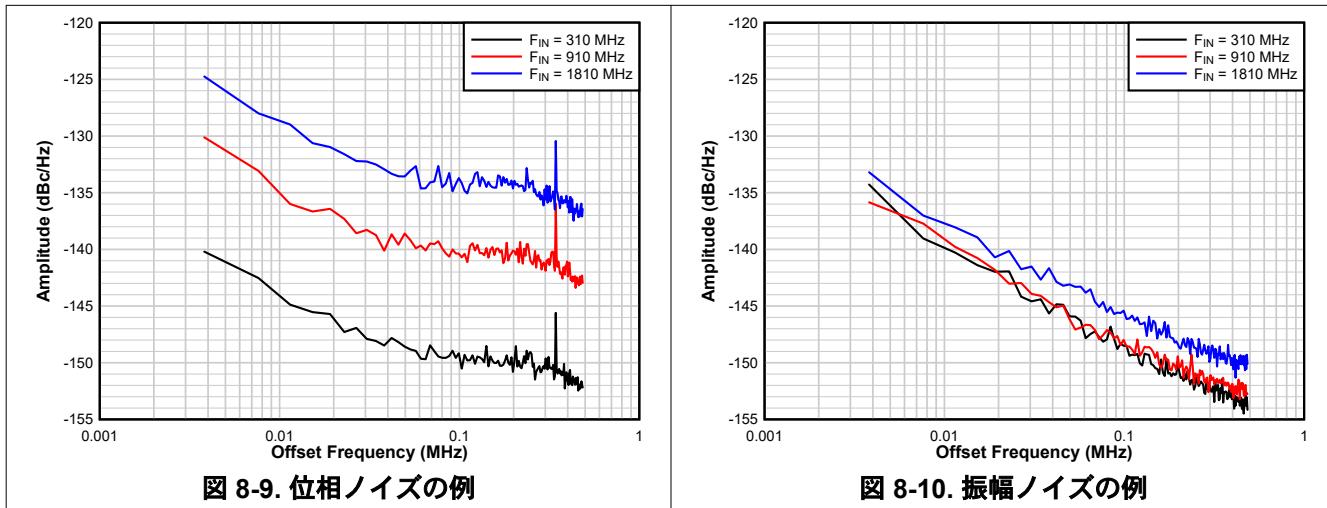

表 8-1 に示すように、内部残留クロック ノイズは、位相ノイズと振幅ノイズという 2 つの成分で構成されます。位相ノイズは、入力周波数およびサンプリング レート ( $20 * \log(f_{IN}/F_S)$ ) に応じてスケーリングされますが、振幅ノイズはスケーリングされません。

表 8-1.  $F_S = 500\text{MHz}$  での位相ノイズと振幅ノイズ

| 周波数オフセット (MHz) | 位相ノイズ (dbc/Hz) | 振幅ノイズ (dbc/Hz) |

|----------------|----------------|----------------|

| 0.001          | -130           | -129           |

| 0.01           | -140           | -139           |

| 0.1            | -150           | -149           |

| 1              | -160           | -159           |

| 3              | -165           | -164           |

| 10             | -165           | -164           |

図 8-9 および 図 8-10 に、3 つの異なる入力周波数での位相ノイズと振幅ノイズを示します。

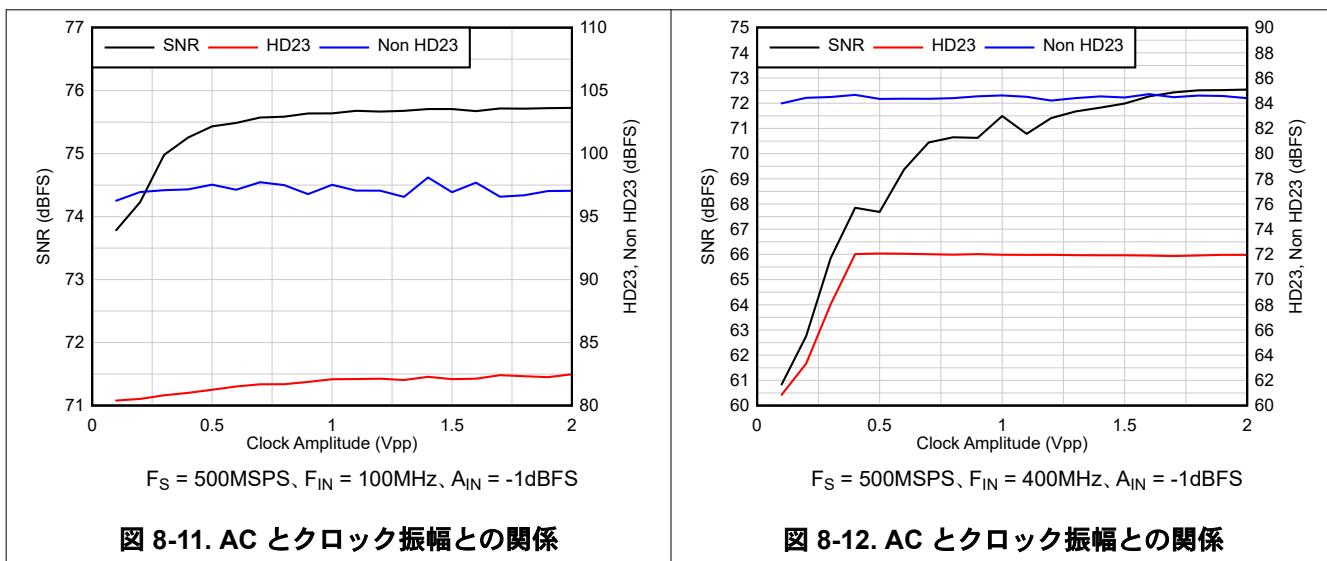

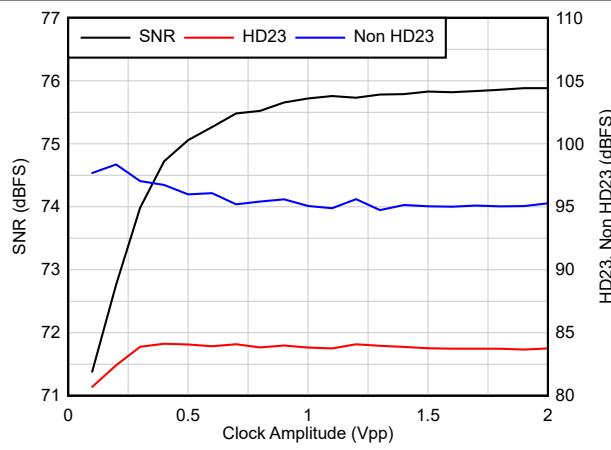

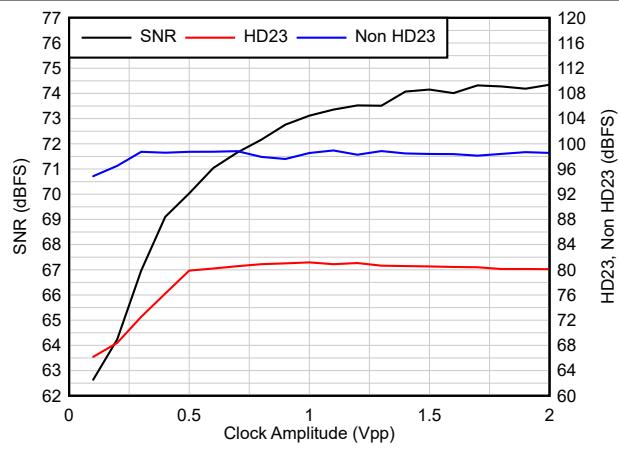

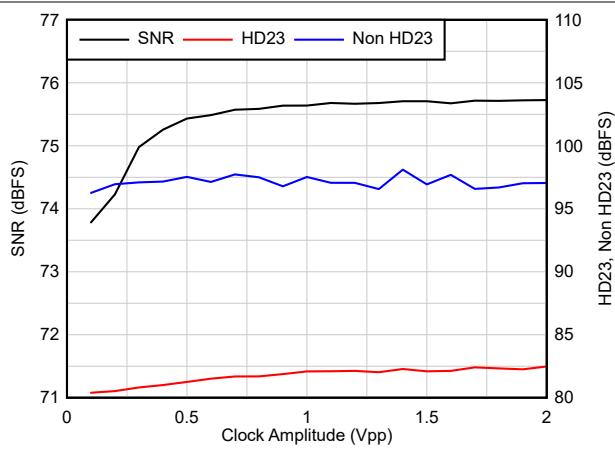

内部クロックのノイズも、外部クロックの振幅に依存します。図 8-11～図 8-14 に、クロック振幅に対してさまざまな入力周波数で想定される AC 性能を示します。

図 8-13. AC とクロック振幅との関係

図 8-14. AC とクロック振幅との関係

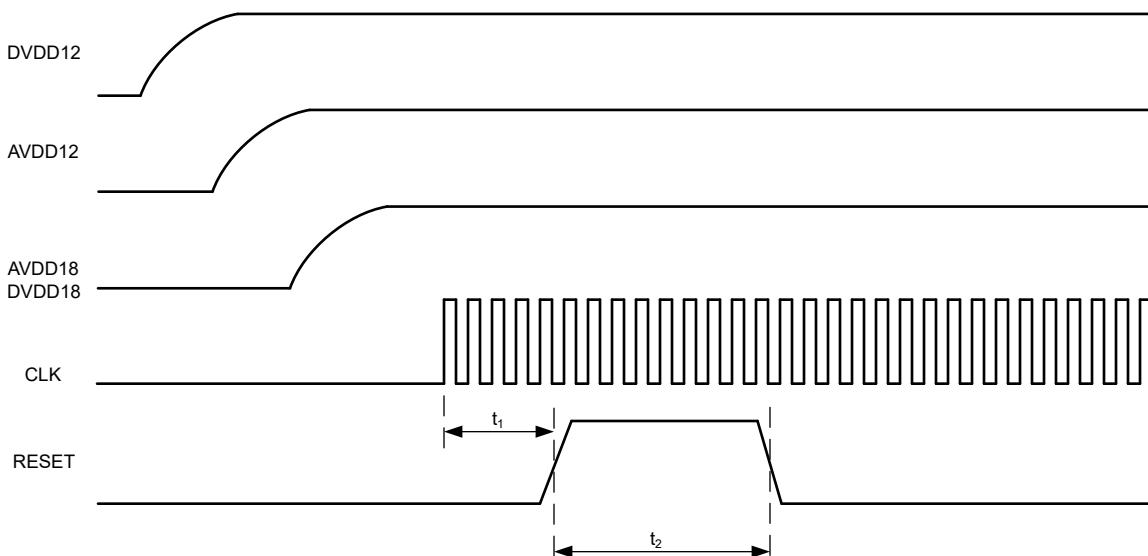

### 8.3.3 複数チップの同期

このデバイスでは、オプションとして確定的レイテンシを実現できるので、動作モードに応じて複数のデバイス間での同期が容易になります。

- **DDC バイパス モード:** このデバイスは、もともと本質的にレイテンシが確定的です。外部マルチチップ同期は、デバイス間のクロックの配線パターンを一致させることによって実現されます。ただし、内部ランプ テスト パターンは、SYSREF 信号を使用してリセットできます。

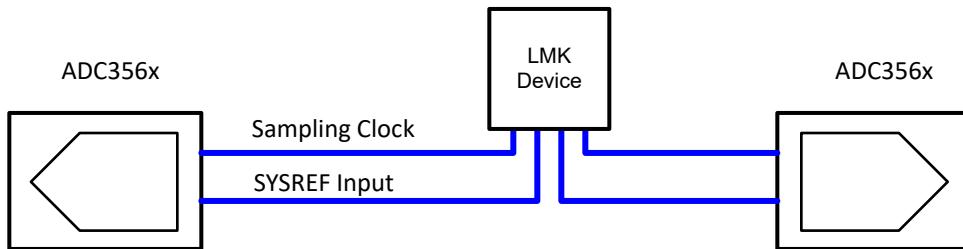

- **DDC モード:** デシメーション フィルタに関連する内部ブロック (クロック分周器、NCO 位相など) は、SYSREF 信号を使用して確定的状態にリセットされます。図 8-15 に示すように、デバイス間のクロックおよび SYSREF 信号の配線 (青色の線) を一致させることで、外部マルチチップ同期を実現します。

図 8-15. 2 つのデバイスの同期例

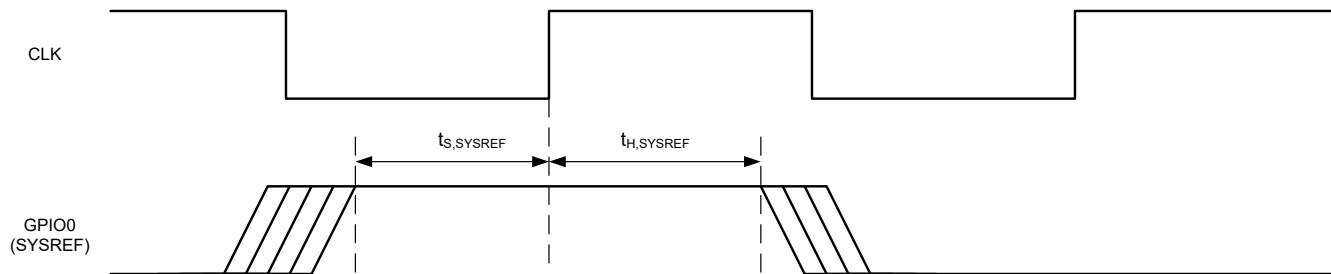

GPIO0 ピンは、同期入力として構成できます。図 8-16 に示すように、マルチチップ同期に单一のパルスを適用できます。

図 8-16. タイミング：外部同期入力

SPI レジスタ マップには、NCO 位相など特定のブロックのみをリセットするための複数の異なる同期マスクがあります。

表 8-2. 外部 SYSREF 構成のためのレジスタ書き込み例

| ADDR  | データ  | 説明                           |

|-------|------|------------------------------|

| 0x146 | 0x00 | ピン GPIO0 を SYSREF 入力として構成します |

### 8.3.3.1 SYSREF モニタ

セットアップ時間とホールド時間を最大化するため、SYSREF 入力信号の立ち上がりエッジは、サンプリング クロックの立ち下がりエッジとエッジをそろえる必要があります。SYSREF 信号は、サンプリング クロックの立ち上がりエッジから 60ps 後に内部的にサンプリングされます。

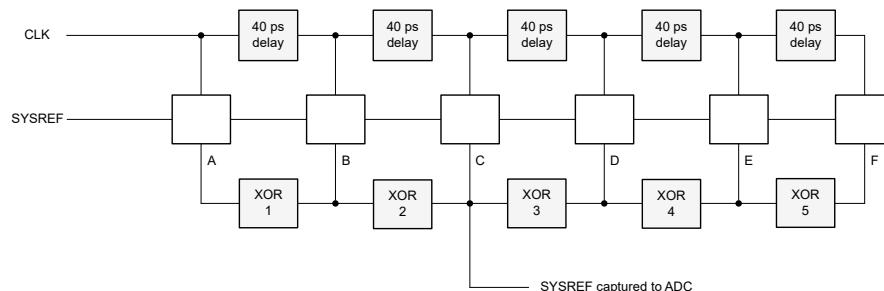

ADC356x には、内部 SYSREF 監視回路が搭載されており、SYSREF のサンプリングの瞬間付近での起こりうる SYSREF ロジック レベルの準安定性を検出します。この準安定性は、デバイス間の不整合につながる可能性があります。SYSREF 監視回路は、SYSREF ロジック状態の遷移が、サンプリング クロックの立ち上がりエッジから -60~+140ps の範囲内であるかどうかを検出することにより、SYSREF / クロックの不整合に関する情報を提供します。この回路は、以下に示す SYSREF ウィンドウに対する SYSREF XOR フラグの 1 つを検出してフラグを立てます。

- ウィンドウ XOR1:SYSREF がサンプル クロックより 20~60ps 先行

- ウィンドウ XOR2:SYSREF がサンプル クロックより 20ps~0ps 先行、または SYSREF がサンプル クロックより 0~20ps 遅延

- ウィンドウ XOR3:SYSREF がサンプル クロックより最大 20~60ps 遅延

- ウィンドウ XOR4:SYSREF がサンプル クロックより 60~100ps 遅延

- ウィンドウ XOR5:SYSREF がサンプル クロックより 100~140ps 遅延

SYSREF モニタ レジスタは、SYSREF の立ち上がりエッジごとに更新されます。<SYSREF DET> レジスタ (D6) はステイッキー (SYSREF エッジが検出されたことを通知) であり、手動でクリアする必要があります。

図 8-17. SYSREF 検出回路

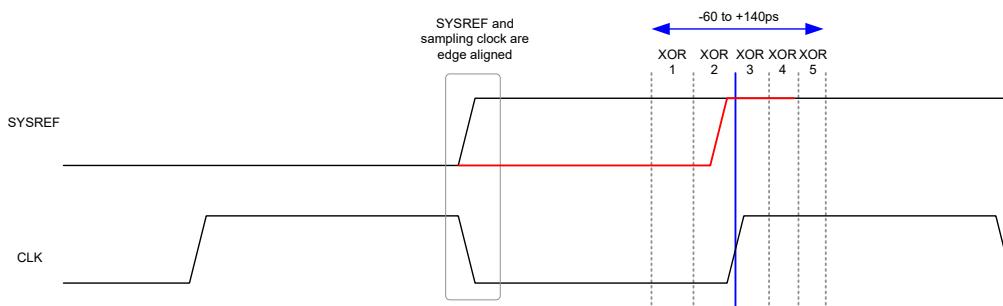

図 8-18 の例では、SYSREF 信号の整列がずれており、サンプリング クロックの立ち下がりエッジよりもはるかに後で SYSREF 信号が到着した状況を示しています。この例では、遅延した SYSREF 信号は「B」と「C」のフリップフロップの間に遷移し、XOR2 フラグを発生させます。この XOR フラグは、レジスタ 0x140 で通知されます。この例では、表 8-3 に示すように、レジスタ 0x140 を読み出すと 0x62 が得られます。

図 8-18. キャプチャ ウィンドウ内での SYSREF 遷移の検出

表 8-3. SYSREF ウィンドウ レジスタの例 (0x140)

| ADDR  | D7 | D6         | D5        | D4        | D3        | D2        | D1        | D0        |

|-------|----|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0x140 | 0  | SYSREF DET | SYSREF OR | SYSREF X5 | SYSREF X4 | SYSREF X3 | SYSREF X2 | SYSREF X1 |

|       | 0  | 1          | 1         | 0         | 0         | 0         | 1         | 0         |

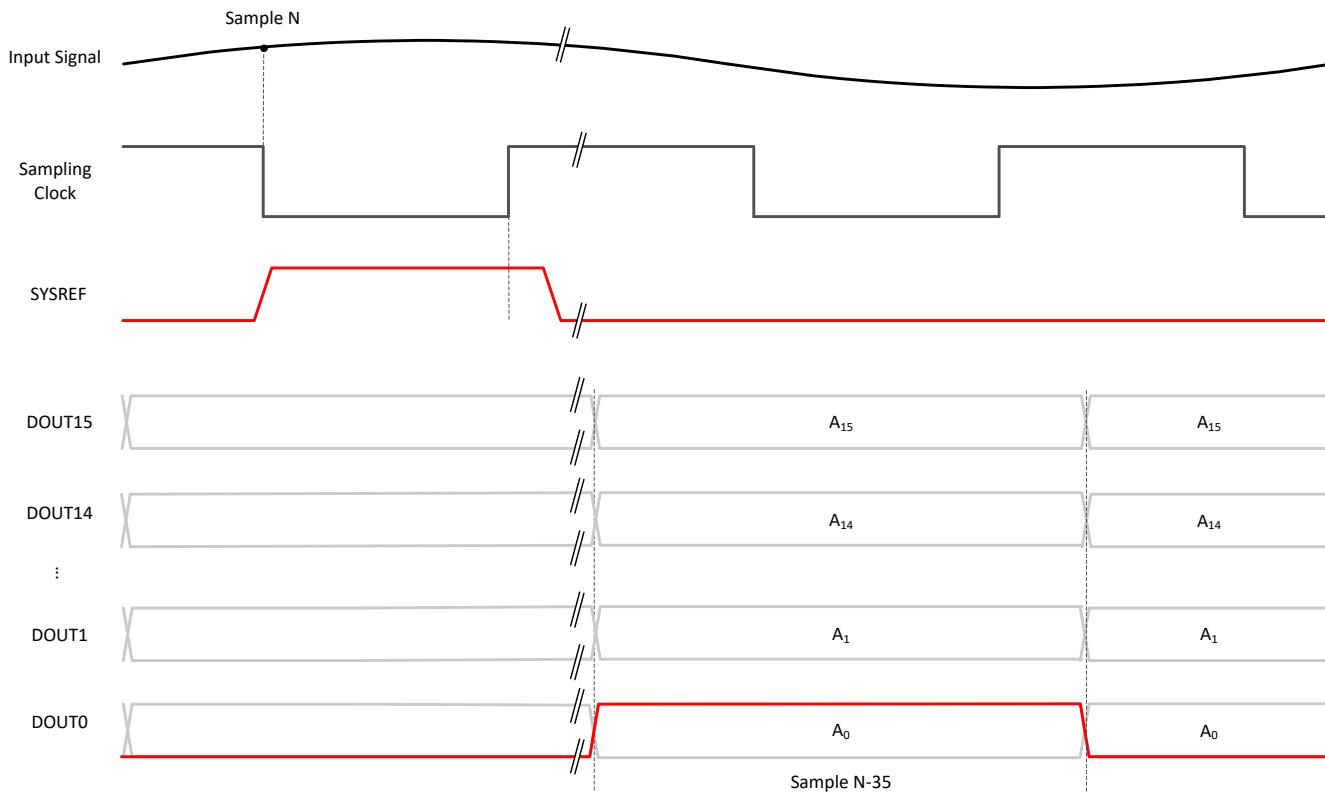

### 8.3.4 タイムスタンプ

ADC356x はタイムスタンプ機能を備えており、DDC バイパス モードで、アナログ入力の特定のサンプルにタグを付けることができます。この機能を (SPI 書き込みにより) イネーブルにすると、GPIO/SYSREF ピンのロジック Low から High への遷移が、サンプリング クロックの立ち上がりエッジで記録されます。タイムスタンプ信号は、レーン DOUT0 (LSB) に出力されますが、この信号は、レイテンシが出力データと一致していません。タイムスタンプ機能は、SDR および DDR LVDS で利用できます。

図 8-19 に示すように、タイムスタンプ信号は、出力データの 35 クロック サイクル前に示されます。

- レイテンシ出力データ: 43 クロック サイクル

- レイテンシ タイムスタンプ出力: 8 クロック サイクル

図 8-19. タイミング図 - SDR LVDS によるタイムスタンプ出力

表 8-4. ピン GPIO0 のタイムスタンプをイネーブルするためのレジスタ書き込みの例

| ADDR  | データ  | 説明                             |

|-------|------|--------------------------------|

| 0x146 | 0x00 | ピン GPIO0 で SYSREF をイネーブルします。   |

| 0x162 | 0xC0 | LSB を置き換えるタイムスタンプ機能をイネーブルにします。 |

### 8.3.5 オーバーレンジ

信号が表現可能なデジタル範囲を超えると、デバイスはオーバーレンジ インジケータをトリガします。オーバーレンジ出力は、レジスタ 0x10A/0x10B で設定できます。OVR 通知のレイテンシは、データ レイテンシと等しいかそれ以下です。

OVR は、次の 2 つの方法で通知できます。

- GPIO ピン: レジスタ 0x146 を使用して設定できます

- LSB データ: 出力データ (レジスタ 0x116) の LSB が OVR 信号に置き換えられます。デシメーション モードでは、OVR 信号がすべての DDC 出力ストリームの LSB を置き換えます。

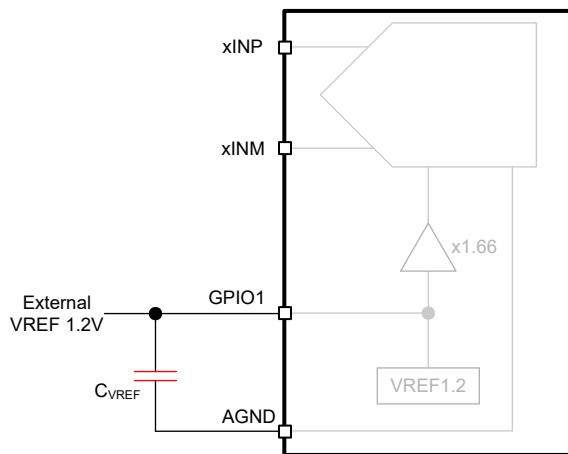

### 8.3.6 外部電圧リファレンス

最高の精度と最小の温度ドリフトを得るために、ADC に外部 1.2V 電圧リファレンスを供給できます。外部リファレンスは、GPIO1 ピンから供給することができます (SPI により構成)。10 $\mu$ F および 0.1 $\mu$ F セラミック バイパス コンデンサ (CVREF) を GPIO0/1 ピンと AGND ピンの間に接続し、できるだけピンの近くに配置することを推奨します。

図 8-20. 外部電圧リファレンス

### 8.3.7 デジタル ゲイン

このデバイスは、プログラム可能なデジタル ゲインを備えています。このゲインはレジスタ 0x15B でプログラマれます。8 ビット レジスタ フィールドは、符号ビット付きの 7 ビット (2 の補数) です。

実際のゲイン (dB) は次のとおりです。 $20 \times \log (1 + (7 \text{ ビット ゲイン} / 128))$

たとえば、レジスタ値 0x7F は 6dB のデジタル ゲインに対応し、0xC0 は -6dB のデジタル ゲインに対応します。

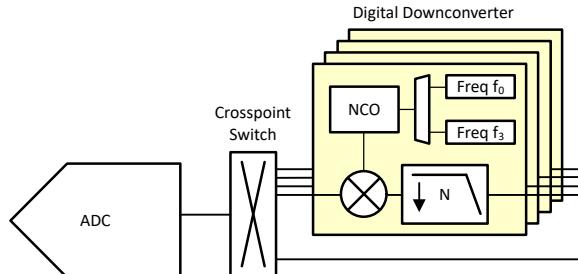

### 8.3.8 デシメーションフィルタ

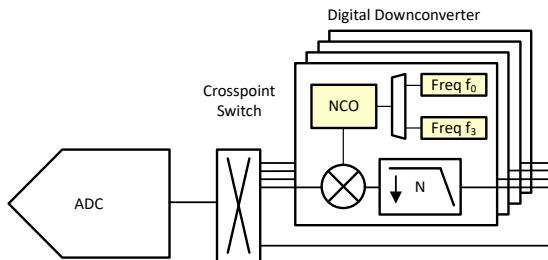

ADC3568 と ADC3569 は、図 8-21 に示すように、最大 4 つのデジタル降圧コンバータを実現します。クロスポイントスイッチを SPI レジスタへの書き込みと組み合わせると、4 つの DDC のいずれかを接続できます。シングル バンド モード (1 DDC) では、/2～/32768 のデシメーションがサポートされています。4 DDC モードでは、表 8-5 に示すように、可能な最小のデシメーションは /8 です。実数 (シングル バンドのみ) および複素数のデシメーションがサポートされています。実数デシメーションでは、パスバンドは約 40% であり、複素数デシメーションでは、パスバンドは約 80% です (表 8-6 を参照)。

図 8-21. 内蔵デジタル ダウン コンバータ

表 8-5. さまざまなデシメーション フィルタの帯域オプションの概要

| DDC の数 | 最小デシメーション | 最大デシメーション |

|--------|-----------|-----------|

| 1      | /2        | /32768    |

| 2      | /4        | /32768    |

| 4      | /8        | /32768    |

表 8-6. 複素数デシメーションおよび実数デシメーションと出力帯域幅との関係

| デシメーション係数 (複素数) | DDC ごとの複素数出力帯域幅      | DDC ごとの実数出力帯域幅       |

|-----------------|----------------------|----------------------|

| N               | $0.8 \times F_S / N$ | $0.4 \times F_S / N$ |

デシメーションは、<COMMON DECIMATION> SPI レジスタ (0x169、D3～D0) をセットすることでイネーブルになります。デフォルトでは、このレジスタは「実数」デシメーションに設定されています。「複素数」デシメーションは、レジスタ <COMPLEX EN> (0x162、D2) でイネーブルになります。

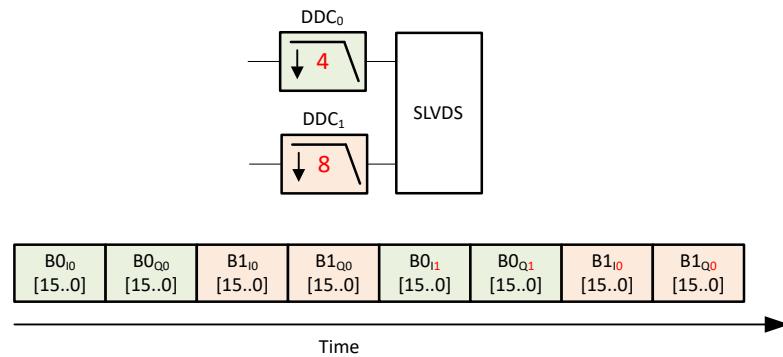

#### 8.3.8.1 特長あるデシメーション比

DDC は、それぞれ異なる個別のデシメーション比を持つようにプログラム可能です。出力データ レートは、最小のデシメーション比を持つデシメーション フィルタに基づいて決まります。デシメーション係数の大きい DDC の出力サンプルは、出力データ ストリームで繰り返されます。たとえば、DDC0 を /4 に、DDC1 を /8 に設定すると、DDC0 の出力データ レートは DDC1 の 2 倍になります ( $F_{out0} = F_S/4$  と  $F_{out1} = F_S/8$  との関係)。したがって、DDC1 の出力サンプルは、図 8-22 に示すように 1 回繰り返されます。

図 8-22. 異なるデシメーション係数

### 8.3.8.2 デシメーション フィルタ応答

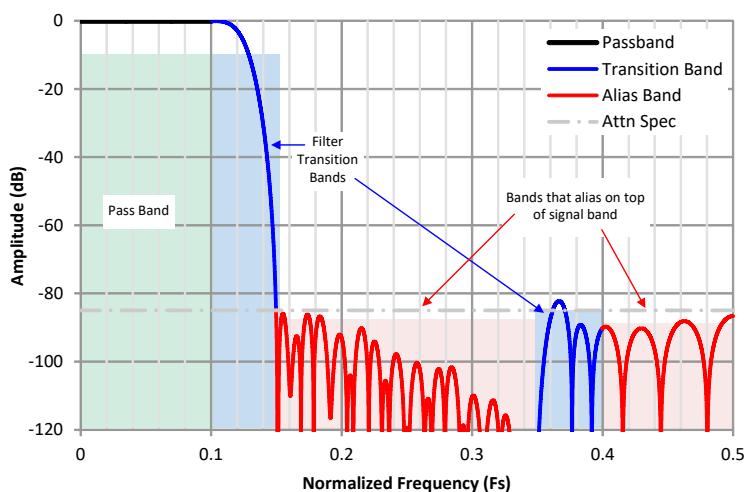

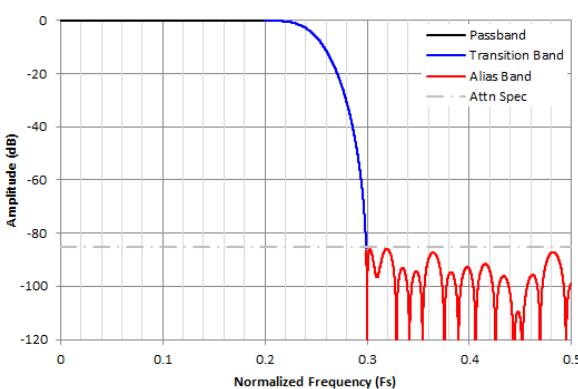

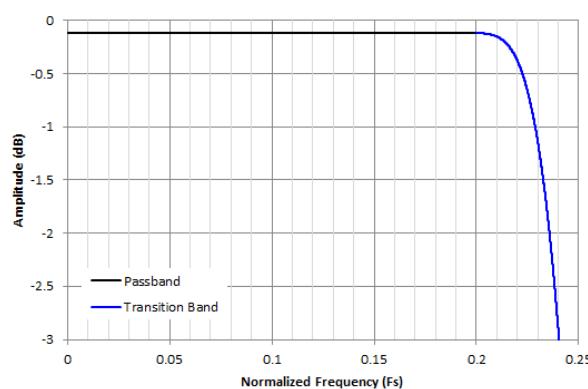

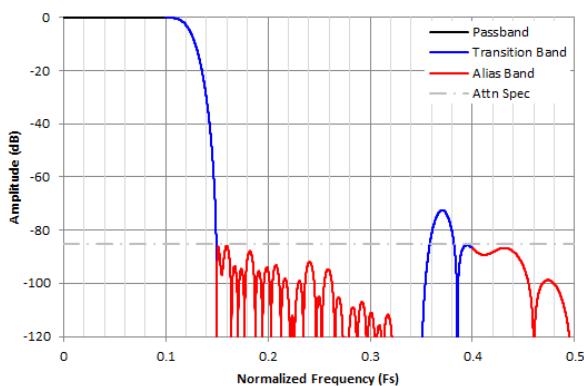

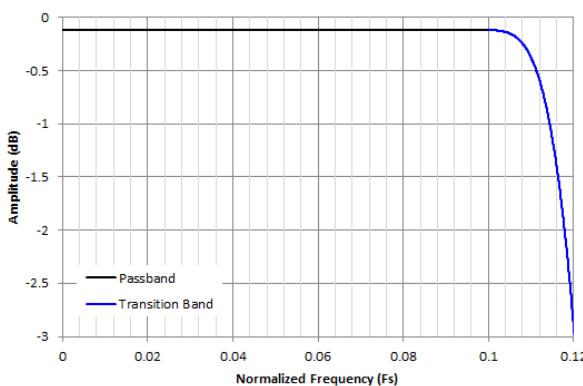

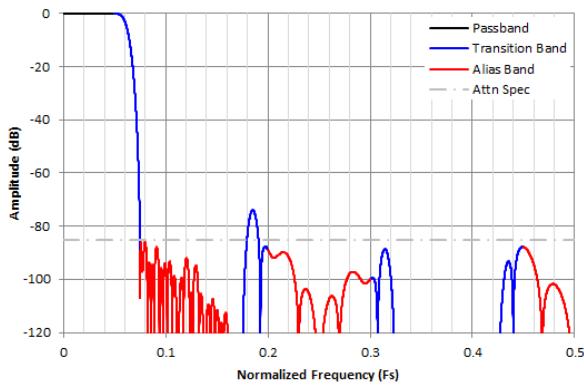

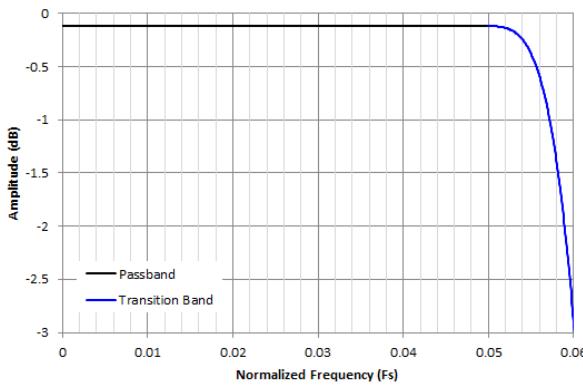

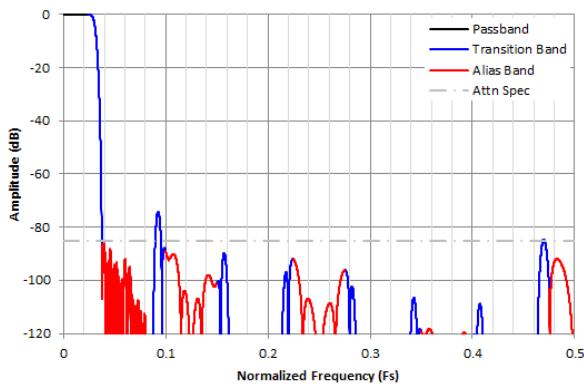

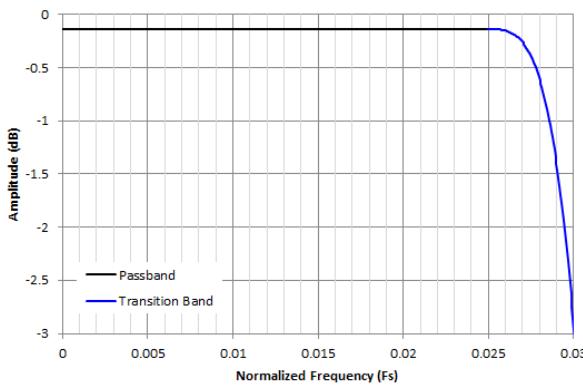

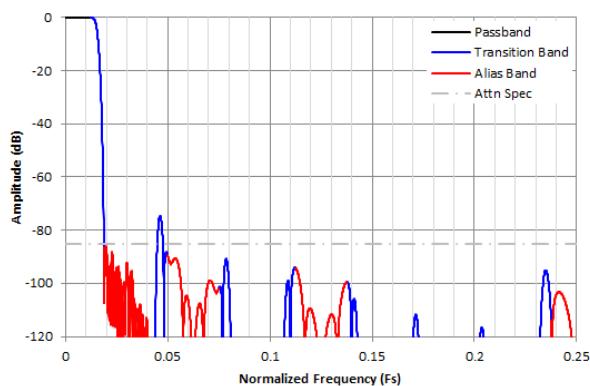

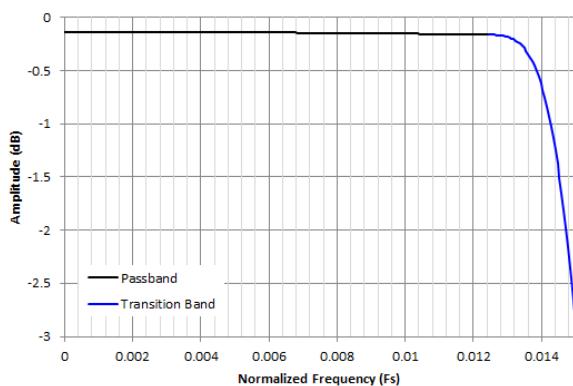

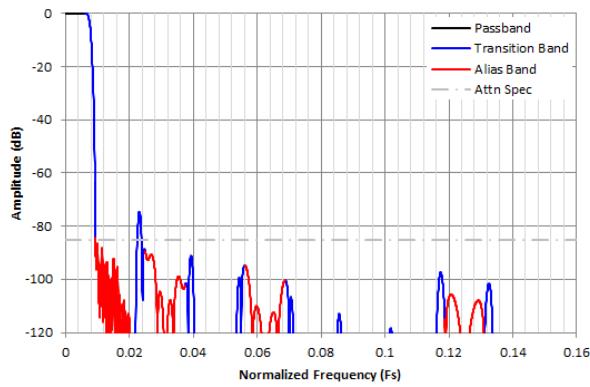

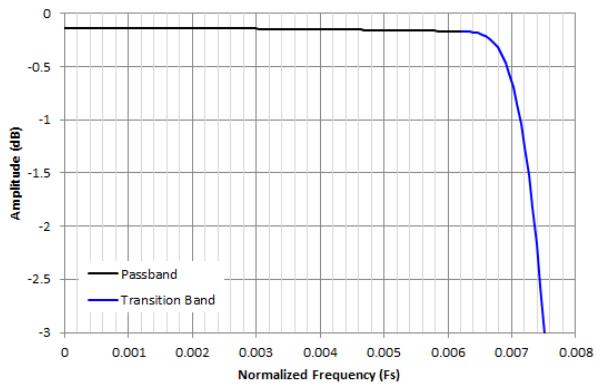

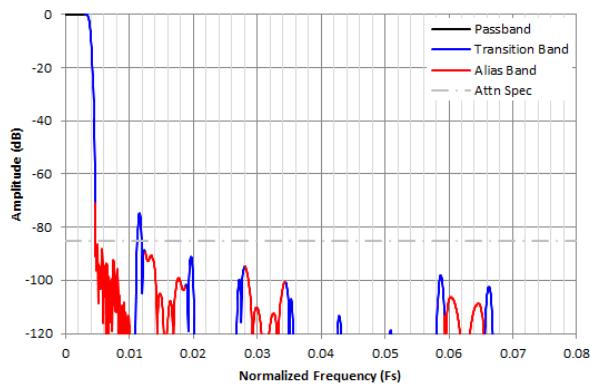

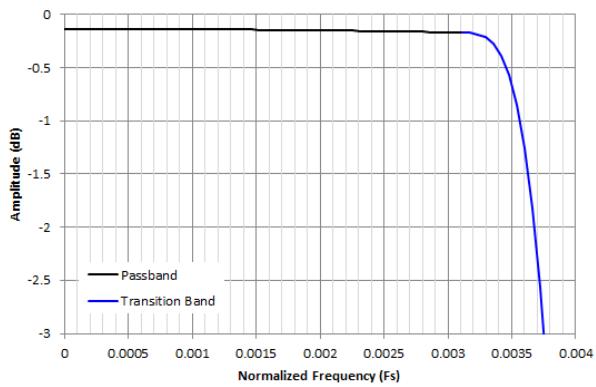

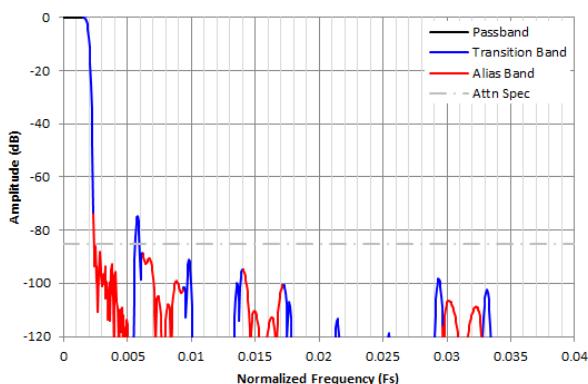

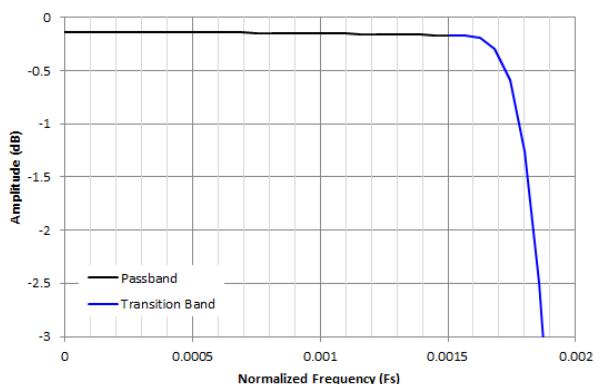

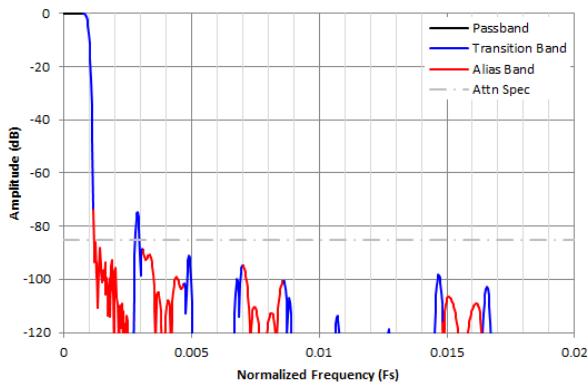

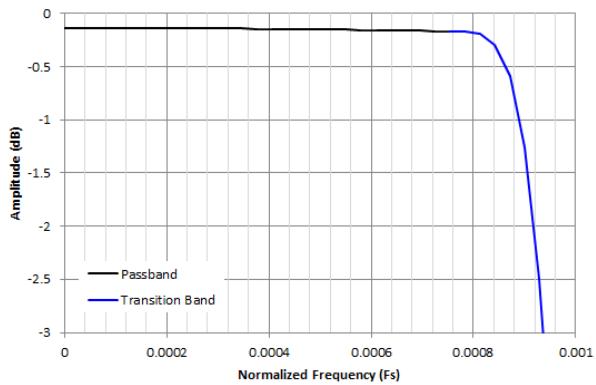

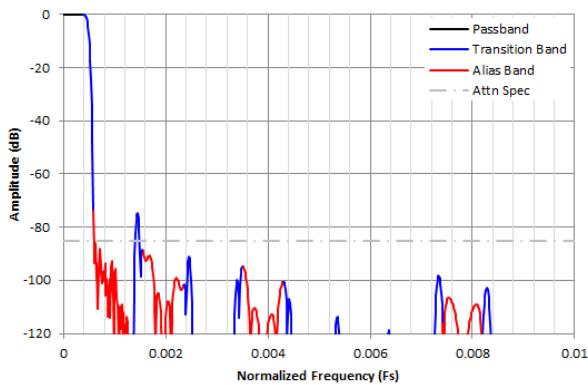

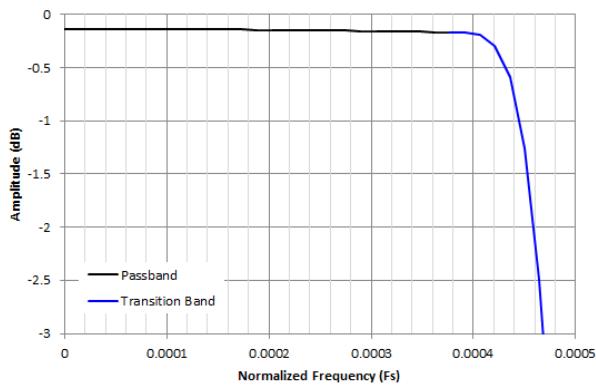

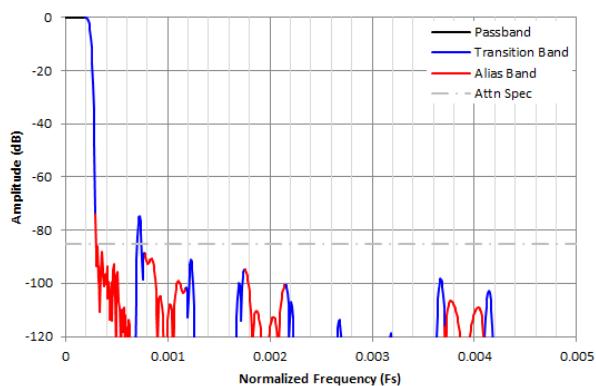

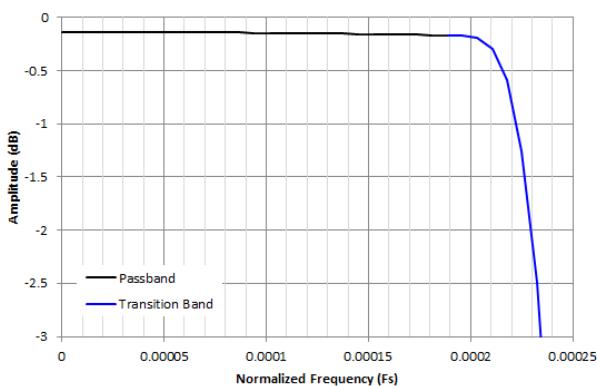

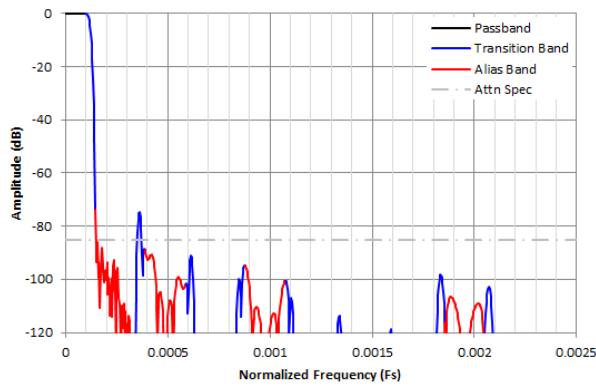

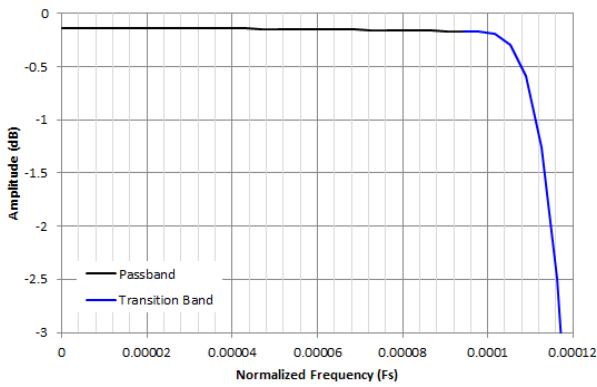

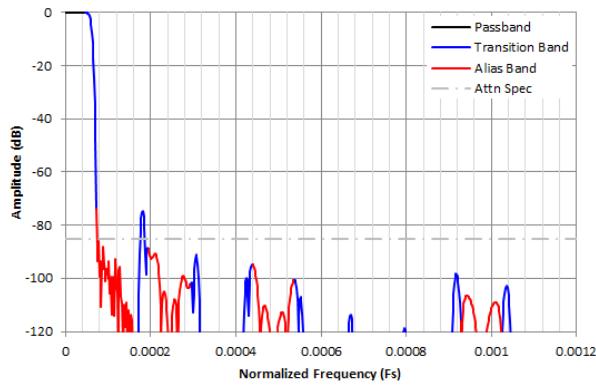

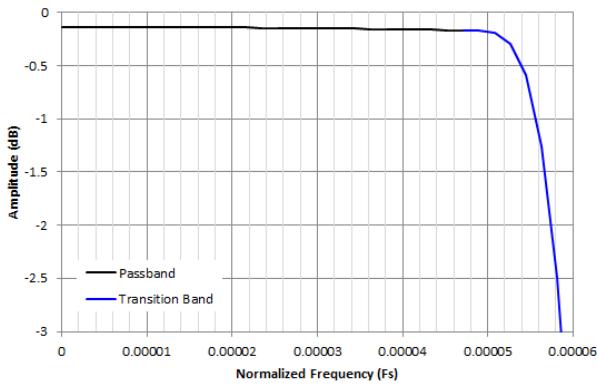

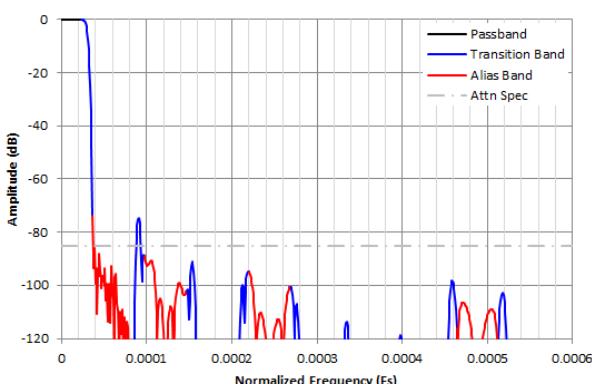

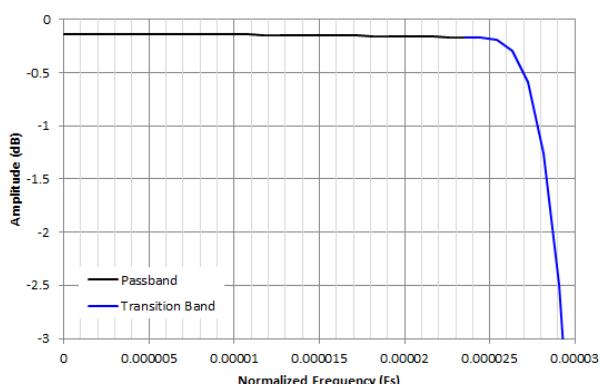

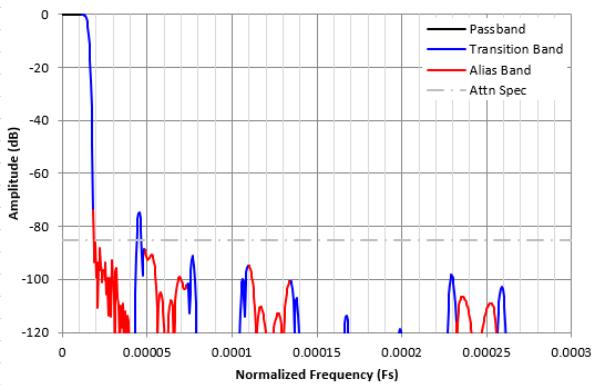

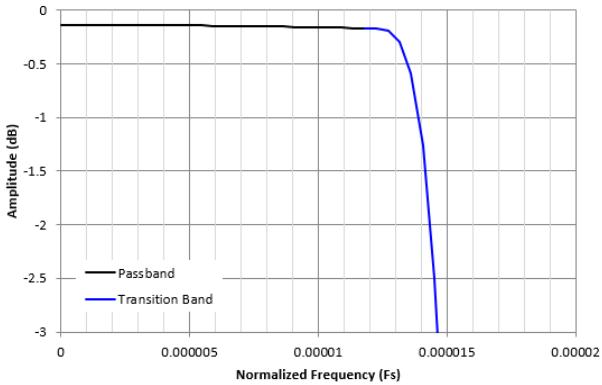

このセクションでは、正規化された ADC サンプリング レートでのさまざまなデシメーション フィルタ応答について説明します。複素フィルタのパス バンドは約 80% (-1dB) であり、最小 85dB のストップ バンド除去を実現しています。

デシメーション フィルタの応答を ADC サンプリング クロック周波数  $F_S$  に正規化して、図 8-24～図 8-52 に示します。各図には、図 8-23 に示すように、フィルタのパスバンド、遷移バンド、エイリアスまたはストップバンドが含まれています。X 軸は、(NCO 周波数シフト後の) オフセット周波数を ADC サンプリング レート  $F_S$  に正規化したものを示します。

たとえば、1/4 の複素セットアップでは、出力データ レートは  $F_S/4$  複素、ナイキスト ゾーンは  $F_S/8$  すなわち  $0.125 \times F_S$  です。遷移バンド (青色) は  $0.125 \times F_S$  を中心にしており、エイリアス遷移バンドは  $0.375 \times F_S$  を中心にしています。ストップ バンド (赤色) は、パスバンドの上側にエイリアスがあり、 $0.25 \times F_S$  および  $0.5 \times F_S$  を中心にして配置されています。ストップバンド減衰は、85dB を超えています。

#### 注

より高いデシメーション比 (/32 以降) の場合、ファーアウト遷移とストップバンドは -120dB を上回るため、デシメーション フィルタ プロットは、-120dB 未満の減衰を持つ応答に近い該当のもののみを示します。

図 8-23. デシメーション フィルタ プロットの解釈

図 8-24. 1/2 複素デシメーションのフィルタ応答

図 8-25. 1/2 デシメーションのパスバンド リップル応答

図 8-26. 1/4 複素デシメーションのフィルタ応答

図 8-27. 1/4 デシメーションのパスバンド リップル応答

図 8-28. 1/8 複素デシメーションのフィルタ応答

図 8-29. 1/8 デシメーションのパスバンド リップル応答

図 8-30. 1/16 複素デシメーションのフィルタ応答

図 8-31. 1/16 デシメーションのパスバンド リップル応答

図 8-32. 1/32 複素デシメーションのフィルタ応答

図 8-33. 1/32 デシメーションのバスバンド リップル応答

図 8-34. 1/64 複素デシメーションのフィルタ応答

図 8-35. 1/64 複素デシメーションのフィルタ リップル応答

図 8-36. 1/128 複素デシメーションのフィルタ応答

図 8-37. 1/128 デシメーションのバスバンド リップル応答

図 8-38. 1/256 複素デシメーションのフィルタ応答

図 8-39. 1/256 デシメーションのバスバンド リップル応答

図 8-40. 1/512 複素デシメーションのフィルタ応答

図 8-41. 1/512 デシメーションのバスバンド リップル応答

図 8-42. 1/1024 複素デシメーションのフィルタ応答

図 8-43. 1/1024 デシメーションのバスバンド リップル応答

図 8-44. 1/2048 複素デシメーションのフィルタ応答

図 8-45. 1/2048 デシメーションのパスバンド リップル応答

図 8-46. 1/4096 複素デシメーションのフィルタ応答

図 8-47. 1/4096 デシメーションのパスバンド リップル応答

図 8-48. 1/8192 複素デシメーションのフィルタ応答

図 8-49. 1/8192 デシメーションのパスバンド リップル応答

図 8-50. 1/16384 複素デシメーションのフィルタ応答

図 8-51. 1/16384 デシメーションのパスバンド リップル応答

図 8-52. 1/32768 複素デシメーションのフィルタ応答

図 8-53. 1/32768 デシメーションのパスバンド リップル応答

### 8.3.8.3 デシメーション フィルタ構成

デジタル デシメーション フィルタの動作は、レジスタ 0x163~0x169 を使用して制御できます。NCO 周波数は、レジスタ 0x200..0x2DF にマップされます。DDC は多用途で、多くの動作モードをサポートできます。

表 8-7. DDC の構成

| ADDR      | 説明                                                      |

|-----------|---------------------------------------------------------|

| 0x163     | ADC ChA を目的の DDC に接続します。デフォルトでは、ADC は 2 つの DDC に接続されます。 |

| 0x164     | NCO モードを選択し、NCO 周波数を更新します                               |

| 0x165     | NCO 周波数の更新を構成します                                        |

| 0x166     | NCO 周波数 0~3 を各 NCO に割り当てます                              |

| 0x167/168 | 異なるデシメーション係数を使用する場合は、各 DDC に対するデシメーションを選択します            |

| 0x169     | DDC の数および共通のデシメーション係数を構成します                             |

以下のシーケンスを使用して、DDC を静的動作モード (固定 NCO / 低速変化 NCO 周波数のいずれか) に設定できます。複素デシメーション /1024、クワッド バンド 32 ビット出力

表 8-8. DDC の構成例

| ADDR  | データ  | 説明                                             |

|-------|------|------------------------------------------------|

| 0x162 | 0x06 | 複素デシメーション、32 ビット出力分解能を選択します。                   |

| 0x169 | 0x1A | 4x DDC (クワッド バンド) に構成し、共通デシメーションを 1024 に設定します。 |

### 8.3.8.4 数値制御発振器 (NCO)

各デジタル ダウンコンバータ (DDC) は、48 ビットの数値制御発振器 (NCO) を使用して、デジタル フィルタリングの前に周波数の配置を微調整します。SPI レジスタ書き込みを使用して、各 DDC に対して最大 4 種類の NCO 周波数をプログラミます。デジタル NCO は、少なくとも 100dB の SFDR を達成するように設計されています。

図 8-54. NCO のブロック図

NCO 動作モードには、位相連続および無限位相コヒーレントの 2 つの異なるモードがあります。

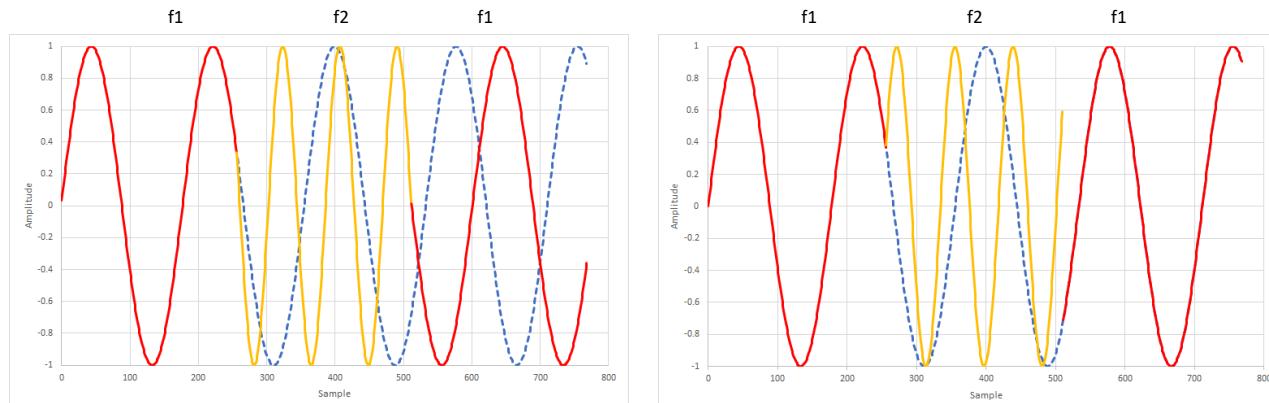

1. 位相連続 NCO:NCO 周波数が変化する際には、図 8-55 (左) に示すように、NCO 位相は新しい周波数に徐々に調整されます。「破線」は、元の  $f_1$  周波数の位相を示しています。

2. 無限位相コヒーレント NCO:位相コヒーレント NCO では、SYSREF を使用して、すべての周波数が 1 つのイベントに同期します。これにより、周波数ホッピングの間で位相コヒーレンシが維持されるため、NCO をリセットする必要なしに、無限回の周波数ホッピングを実現できます。これを 図 8-55 (右) に示します。元の周波数  $f_1$  に戻ると、NCO 位相は NCO が周波数を一度も変えなかつたかのように見えます。

図 8-55. 位相連続 (左) と無限位相コヒーレント (右) NCO 周波数スイッチング

発振器は、次のような複素指数関数列を生成します。

$$e^{j\omega n} \text{ (default) or } e^{-j\omega n} \quad (1)$$

ここで、周波数 ( $\omega$ ) は 48 ビットレジスタ設定により符号付き数値として指定されます

複素指数関数列に ADC からの実数入力を乗算し、目的のキャリアを  $f_{IN} + f_{NCO}$  に等しい周波数にミックスします。NCO 周波数は  $-F_S/2$  から  $+F_S/2$  の範囲で調整でき、符号付き 2 の補数として処理されます。

NCO 周波数の設定は、48 ビットのレジスタ値によって設定され、次のように計算されます。

$$\text{NCO frequency (0 to } + F_S/2\text{): } NCO = f_{NCO} \times 2^{48} / F_S \quad (2)$$

$$\text{NCO frequency } (-F_S/2 \text{ to } 0): NCO = (f_{NCO} + F_S) \times 2^{48} / F_S \quad (3)$$

ここで

- NCO = NCO レジスタ設定 (10 進値)

- $f_{NCO}$  = 目標とする NCO 周波数 (MHz)

- $F_S$  = ADC サンプリング レート (MSPS)

NCO プログラミングをこの例で説明します。

- ADC サンプリング レート  $F_S = 500$ MSPS

- 目標とする NCO 周波数 = 120MHz

$$\text{NCO frequency setting} = f_{NCO} \times 2^{48} / F_S = 120\text{MHz} \times 2^{48} / 500 \text{ MSPS} = 67,553,994,410,557 \quad (4)$$

表 8-9 に、DDC0 の NCO の周波数 0 を、その周波数に設定するためのレジスタ書き込みを示します。

**表 8-9. NCO 周波数を変更するためのレジスタ書き込みの例**

| ADDR  | データ  | 説明                                                                                              |

|-------|------|-------------------------------------------------------------------------------------------------|

| 0x200 | 0x3D | NCO0 の周波数を 120MHz (67,553,994,410,557) に設定します。<br>これは 0x3D70 A3D7 0A3D であり、LSB が 0x200 から始まります。 |

| 0x201 | 0x0A |                                                                                                 |

| 0x202 | 0xD7 |                                                                                                 |

| 0x203 | 0xA3 |                                                                                                 |

| 0x204 | 0x70 |                                                                                                 |

| 0x205 | 0x3D |                                                                                                 |

| 0x165 | 0x00 | すべての NCO を新しい周波数でロードおよび更新します。                                                                   |

| 0x165 | 0x01 |                                                                                                 |

| 0x165 | 0x00 |                                                                                                 |

| 0x160 | 0x00 | NCO 周波数を更新するために、手動で SYSREF (ピン経由または SPI SYSREF) を発行します。                                         |

| 0x160 | 0x04 |                                                                                                 |

| 0x160 | 0x00 |                                                                                                 |

### 8.3.9 デジタルインターフェイス

ADC356x は、動作モードに応じて 3 種類の LVDS インターフェイスをサポートしています。

1. **SDR LVDS (デフォルト):** データは、16 ビット幅の LVDS バスを使用して出力され、各ビットは出力クロックの立ち上がりエッジで 1 つの出力レーンを使用します。

2. **DDR LVDS:** データは、出力クロックの立ち上がりエッジと立ち下がりエッジの両方を使用して、16 ビット幅の LVDS バスを使用して出力されます。データはクロックの立ち上がりエッジで出力され、0 はクロックの立ち下がりエッジで出力されます。

3. **シリアル LVDS (SLVDS):** デシメーション (実数または複素数) を使用する場合、出力データはシリアル化され、少ないレーンで出力されます。

#### 8.3.9.1 パラレル LVDS (SDR) - デフォルト

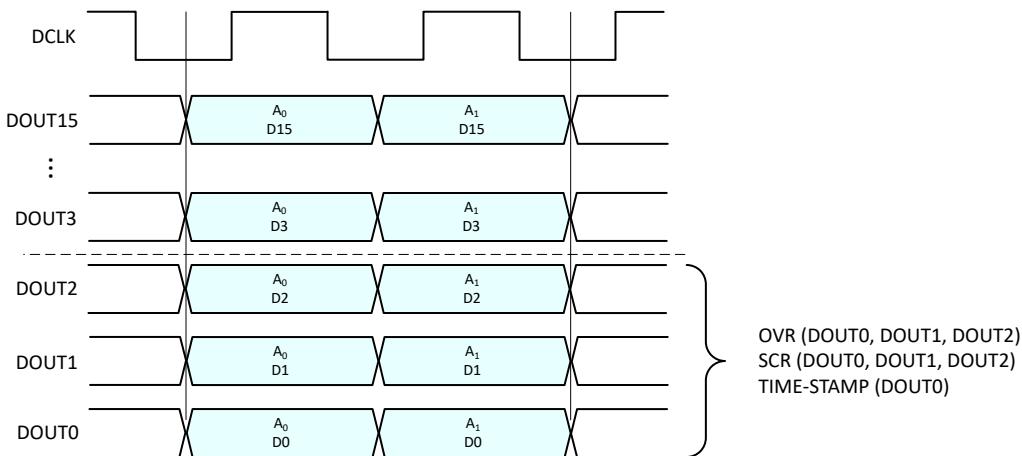

パラレル LVDS は、デシメーション バイパス モードで使用します。SDR LVDS では、図 8-56 に示すように、DCLK の立ち上がりエッジを使用して 16 の LVDS レーンで 16 ビットすべてが送信されます。

レーン DOUT0/1/2 の出力データは、次のように置き換えられます。

- レジスタ 0x116 で設定されたレーン DOUT0/1/2 でのオーバーレンジ出力 OVR

- レジスタ 0x116 で設定されたレーン DOUT0/1/2 での出力スクランブル モードの PRBS ビット

- レジスタ 0x162 で設定されたレーン DOUT0 のみのタイムスタンプ。DOUT0 に設定すると、OVR および SCR よりもタイムスタンプが優先されます。

図 8-56. SDR LVDS モードでの出力データ フォーマット

#### 8.3.9.2 パラレル LVDS (DDR)

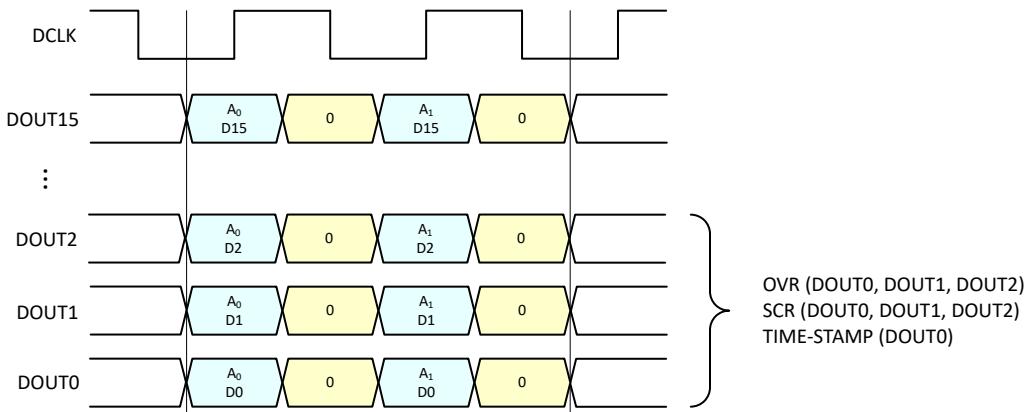

パラレル LVDS は、デシメーション バイパス モードで使用します。図 8-57 に示すように、データは DCLK の立ち上がりエッジで送信され、0 は DCLK の立ち下がりエッジで送信されます。

レーン DOUT0/1/2 のチャネル A の出力データは、次のように置き換えることができます。

- レジスタ 0x116 で設定されたレーン DOUT0/1/2 でのオーバーレンジ出力 OVR

- レジスタ 0x116 で設定されたレーン DOUT0/1/2 での出力スクランブル モードの PRBS ビット

- レジスタ 0x162 で設定されたレーン DOUT0 のみのタイムスタンプ。DOUT0 に設定すると、OVR および SCR よりもタイムスタンプが優先されます。

図 8-57. DDR LVDS モードでの出力データ フォーマット

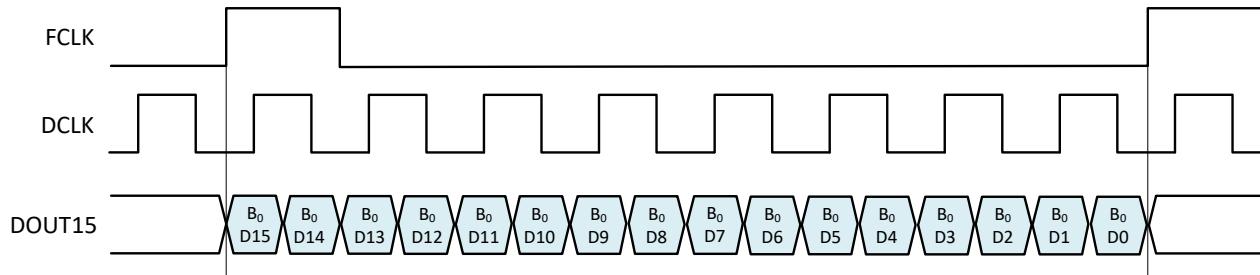

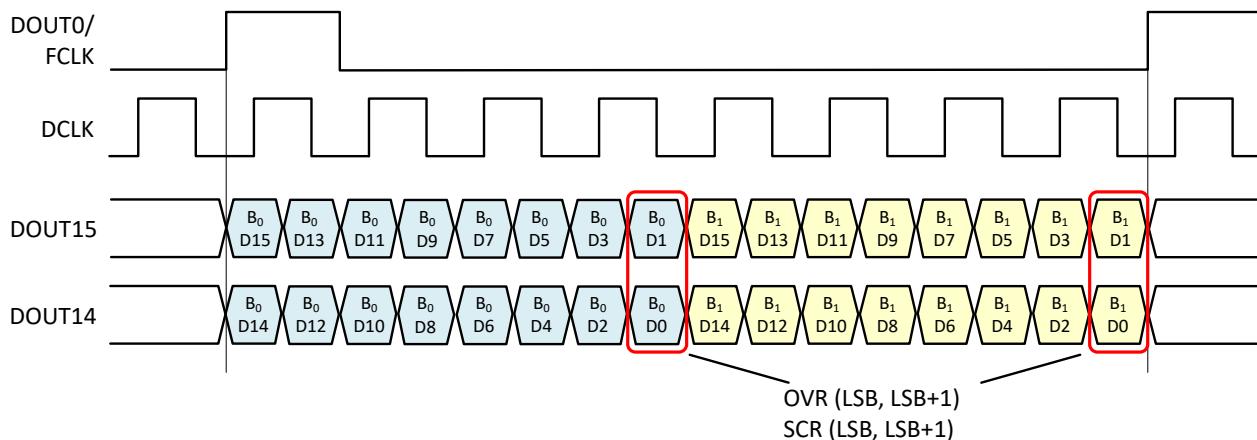

### 8.3.9.3 デシメーション付き SLVDS

実数または複素数のデシメーションを使用する場合、出力データをシリアル化して送信します。これにより、LVDS トランスマッタの使用個数が少なくなります。フレーム クロック (FCLK) は、サンプルの開始と停止を示します。データ ビットは、データ クロック (DCLK) の立ち上がりエッジおよび立ち下がりエッジでクロック出力されます。フレーム クロックは、DOUT0 に出力され、データ出力に使用できる LVDS レーン数は最大 15 です。出力インターフェイスのマッピングは、常にレーン DOUT15 で開始します。

実数デシメーションでは、1 つのバンドだけがサポートされます。

レーン数と出力データレートは、次のパラメータで計算できます。

- R: 出力分解能: 16 ビット = 1, 32 ビット = 2

- B: バンドの合計数

- C: 実数または複素数のデシメーション: 実数 = 1, 複素数 = 2

- D: デシメーション係数

- FS: ADC サンプリング クロック周波数

- K = R x B x C

- L = 8 x K / D

$L < 1$  の場合、DCLK 出力分周器 (0x590, D1) をイネーブルにする必要があります。

表 8-10. SLVDS クロックおよびデータレートの計算

| パラメータ                        | $L \geq 1$ | $L < 1$         |

|------------------------------|------------|-----------------|

| フレーム クロック (FCLK) 周波数         | FS / D     |                 |

| データ ビット クロック (DCLK) 周波数      | FS         | DOU / 2         |

| レーンあたりのデータ出力レート DOUT (DOU/L) | FS x 2     | FS / D x 16 x K |

SLVDS フレームの組み立ては、ADC によって自動的に実行され、ここに示す方式に従います。レーン DOUT0 から始まって、各チャネルの MSB を使用します。

表 8-11. SLVDS フレームの組み立て

| デシメーション | 出力分解能  | バンド順序                                                                                                                                         |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 実数      | 16 ビット | B                                                                                                                                             |

|         | 32 ビット |                                                                                                                                               |

| 複雑      | 16 ビット | B <sub>0I</sub> , B <sub>0Q</sub> , B <sub>1I</sub> , B <sub>1Q</sub> , B <sub>2I</sub> , B <sub>2Q</sub> , B <sub>2I</sub> , B <sub>2Q</sub> |

|         | 32 ビット |                                                                                                                                               |

以下に、4 つの異なる例について、フレームの組み立てと計算の詳細を示します。

事例 1: シングル バンド、1/8 の実数デシメーション、16 ビット出力分解能、 $FS = 500\text{Msps}$

- $K = 1$  ( $R = 1$ 、 $B = 1$ 、 $C = 1$ )

- $L = 8 \times K / D = 8 \times 1 / 8 = 1$

- $FCLK = FS / D = 500\text{MSPS} / 8 = 62.5\text{MHz}$

- $DCLK = 500\text{MHz}$

- $DOUT / レーン = 1\text{Gbps}$

図 8-58 に、例 1 の SLVDS フレームの組み立てを示します。1 つのレーンを使用してデータを出力します。

図 8-58. 例 1 の SLVDS フレームの組み立て

事例 2: シングル バンド、1/128 の実数デシメーション、32 ビット出力分解能、 $FS = 500\text{Msps}$

- $K = 2$  ( $R = 2$ 、 $B = 1$ 、 $C = 1$ )

- $L = 8 \times K / D = 8 \times 2 / 128 = 1/8 \Rightarrow 1$  レーンを使用。

- $FCLK = FS / D = 500\text{MSPS} / 128 = 3.91\text{MHz}$

- $DCLK = 62.5\text{MHz}$

- $DOUT / レーン = 125\text{Mbps}$

図 8-59 に、例 2 の SLVDS フレームの組み立てを示します。1 つのレーンを使用して 32 ビットを送信します。

図 8-59. 例 2 の SLVDS フレームの組み立て

事例 3: デュアル バンド、1/8 の複素数デシメーション、16 ビット出力分解能、FS = 500Msps

- $K = 4$  ( $R = 1$ ,  $B = 2$ ,  $C = 2$ )

- $L = 8 \times K / D = 8 \times 4 / 8 = 4$

- $FCLK = FS / D = 500\text{MSPS} / 8 = 62.5\text{MHz}$

- $DCLK = 500\text{MHz}$

- $DOUT / レーン = 1\text{Gbps}$

図 8-60 に、例 3 の SLVDS フレームの組み立てを示します。このフレームの組み立てでは、DOUT15 においてバンド 0 の「I」サンプルの 4 MSB で始まります。各サンプルは 4 つのレーンに分散されます。

図 8-60. 例 3 の SLVDS フレームの組み立て

事例 4: デュアル バンド、1/256 の複素数デシメーション、32 ビット出力分解能、FS = 500Msps

- $K = 8$  ( $R = 2$ ,  $B = 2$ ,  $C = 2$ )

- $L = 8 \times K / D = 8 \times 8 / 256 = 1/4 \Rightarrow 1$  レーンを使用。

- $FCLK = FS / D = 500\text{MSPS} / 256 = 1.95\text{MHz}$

- $DOUT/レーン = FS / D \times 16 \times K = 500\text{MSPS} / 256 \times 16 \times 8 = 250\text{Mbps}$

- $DCLK = 125\text{MHz}$

図 8-61 に、例 4 の SLVDS フレームの組み立てを示します。このフレームの組み立てでは、バンド 0 の 32 ビット「I」サンプルからバンド 1 の 32 ビット「Q」サンプルまでの DOUT15 のみを使用します。

図 8-61. 例 4 の SLVDS フレームの組み立て

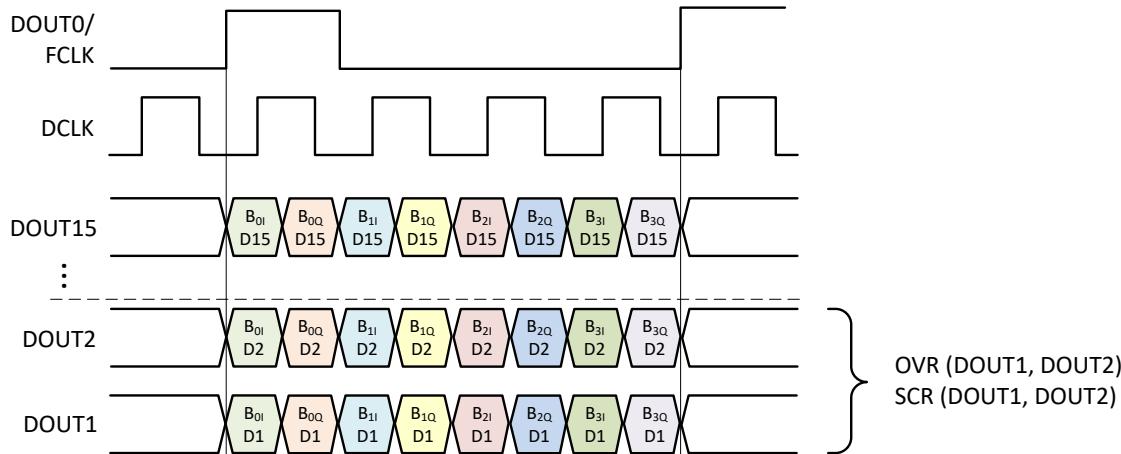

### 8.3.9.3.1 SLVDS - ステータス ビットの挿入

デシメーション機能付きシリアル LVDS では、出力データをオーバーレンジまたは PRBS スクランブルビット (SCR) に置き換えることもできます。FCLK はすでに出力レーン DOUT0 を使用していることに注意してください。

16 の SLVDS レーンを使用する場合、図 8-62 のクワッド バンドの例に示すように、OVR または PRBS (SCR) ビットを LSB+1 (DOUT1) および/または LSB+2 (DOUT2) に置き換えることができます。

16 未満の SLVDS レーンを使用する場合、図 8-63 のデュアル バンドの例に示すように、OVR または PRBS (SCR) ビットを LSB および/または LSB+1 に置き換えることができます。

図 8-62. 出力データ置換 : 16 つの SLVDS レーン

図 8-63. 出力データ置換 : 16 未満の SLVDS レーン

### 8.3.9.4 出力データ フォーマット

出力データは、2 の補数 (デフォルト) またはオフセット バイナリ形式に構成することができます。後者の場合は、SPI レジスタへの書き込み (レジスタ 0x162) を使用します。表 8-12 に、2 つのフォーマット オプションと 16 または 32 ビットの出力分解能に対する、出力コードの最小値と最大値の概要を示します。

**表 8-12. 最小出力コードと最大出力コードの概要、および各種フォーマットでの分解能の比較**

| 分解能 (ビット)    | 2 の補数 (デフォルト) |             | オフセット バイナリ |             |

|--------------|---------------|-------------|------------|-------------|

|              | 16            | 32          | 16         | 32          |

| $V_{IN,MAX}$ | 0x7FFF        | 0x7FFF FFFF | 0xFFFF     | 0xFFFF FFFF |

| 0            | 0x0000        | 0x0000 0000 | 0x8000     | 0x8000 0000 |

| $V_{IN,MIN}$ | 0x8000        | 0x8000 0000 | 0x0000     | 0x0000 0000 |

### 8.3.9.5 32 ビット出力分解能

ADC356x は、16 ビットおよび 32 ビットの出力分解能をサポートしています。表 8-13 に示すように、量子化ノイズの制限による SNR の低下を回避するために、大きいデシメーション係数 (実数の場合 16、複素数の場合 32 以上のデシメーション) を使用する場合には、32 ビット出力分解能を推奨します。

出力分解能は、レジスタ 0x162 への SPI レジスタへの書き込みにより変更できます。

**表 8-13. 出力 SNR : デシメーションと出力分解能との関係**

| ベースライン<br>SNR (dBFS) | 実数デシメーション | 3dB PER /2 での SNR (dBFS) | 16 ビット出力分解能での SNR (dBFS) | 32 ビット出力分解能での SNR (dBFS) |

|----------------------|-----------|--------------------------|--------------------------|--------------------------|

| 76                   | /16       | 88.0                     | 87.6                     | 88.0                     |

| 76                   | /32       | 91.1                     | 90.3                     | 91.1                     |

| 76                   | /256      | 100.1                    | 96.0                     | 100.1                    |

| 76                   | /32768    | 121.1                    | 98.0                     | 121.1                    |

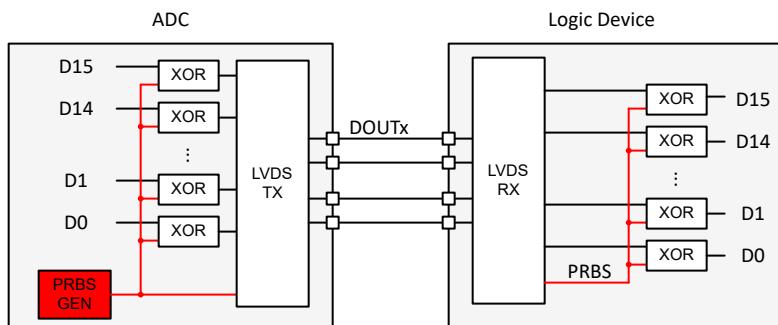

### 8.3.9.6 出力スクランブル

ADC には、オプションの出力スクランブルが含まれています。ADC では、内部 PRBS ジェネレータが PRBS パターンを生成します。各データビットは、PRBS ビットストリームと XOR 処理されます。スクランブル処理された出力データは、(0x146 で構成されている LSB、LSB-1、または LSB-2 出力データを置き換える) PRBS ビットとともに (パラレルまたはシリアル LVDS で) 送信されます。

受信ロジックデバイスは PRBS ビットストリームを抽出し、回復した PRBS ビットを使用して各データビットを XOR 処理することで受信データにデコードします。

**図 8-64. 出力スクランブル**

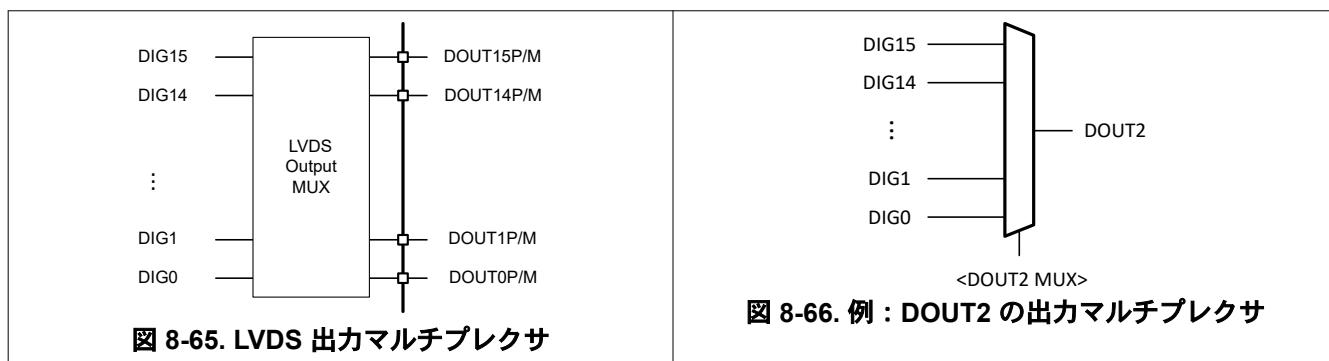

### 8.3.9.7 出力 MUX

LVDS 出力インターフェイスには出力マルチプレクサが含まれており、図 8-65 に示すように、任意の内部デジタル レーンを任意の LVDS 出力レーンに再ルーティングできます。これにより、リンクの冗長性またはリンクの修復に使用できるレーン マッピングの柔軟性が向上します。LVDS 出力マルチプレクサは、<LVDS MUX EN> (レジスタ 0x116、ビット 7) を設定することによりイネーブルにできます。マルチプレクサ構成は、<DOUTxMUX> レジスタ (0x117~0x11E) へ書き込むことで制御できます。マルチプレクサ構成は、数学的には  $DOUT_k = \text{DIG}[DOUT_k\_MUX]$  として記述できます。ここで、 $k$  はレーン番号を示します。たとえば、<DOUT2 MUX> の値を 2 に設定すると、DIG2 が DOUT2 にリダイレクトされます。図 8-66 に、すべての DOUT ピンに使用されるマルチプレクサ構造の例を示します。

さらに、シリアル LVDS (デシメーションのみ) を使用する場合、同じ内部デジタル レーンを複数の LVDS 出力レーンに接続することで、この出力マルチプレクサを使用して重複した冗長出力を生成できます。

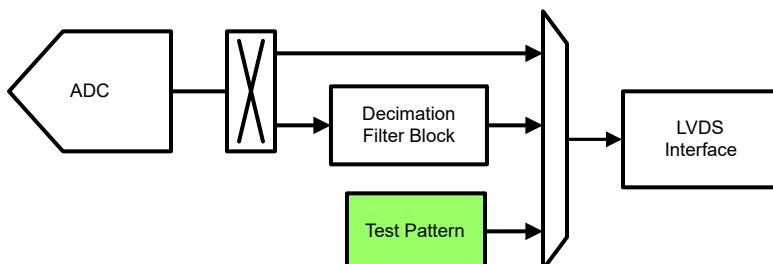

### 8.3.9.8 テスト・パターン

このデバイスには、テスト パターン ジェネレータが内蔵されているため、LVDS 出力のデバッグやキャリブレーションを簡単に行えます。テスト パターン ジェネレータは、図 8-67 に示すように DDC の後に配置されています。

図 8-67. テスト パターン ジェネレータ

テスト パターン ジェネレータ (0x14A のレジスタ <TEST PATTERN>) をイネーブルにすると、通常の ADC またはデシメーション データなど、現在の出力データ サンプルをすべて置き換えます。テスト パターンはすべてのチャネルで同じです。テスト パターン ブロックは、20 ビットのテスト パターンを生成します。パターン自体は <TEST PATTERN> フィールドの値によって制御されます。

デシメーションでは、テスト パターン ブロックは、デフォルトでデシメーションされたクロックで動作します。レジスタ 0x14A の <PATTERN CLK> フィールドをセットすることにより、Fs クロックで動作するように切り替えることもできます。テスト パターン 機能は、低レイテンシ動作モードではイネーブルにできません。

以下のレジスタ書き込みを使用すると、16 ビットの出力分解能でステップ サイズ 1 のランプ パターンを構成できます。

表 8-14. カスタム ステップ サイズを使用したランプ パターンの設定例

| ADDR  | データ  | 説明                                                        |

|-------|------|-----------------------------------------------------------|

| 0x14A | 0x02 | カスタム ステップ サイズでランプ パターンを有効化します                             |

| 0x14B | 0x10 | ステップ サイズは 16LSB (20 ビット分解能の場合) であり、16 ビット分解能の 1LSB に相当します |

## 8.4 デバイスの機能モード

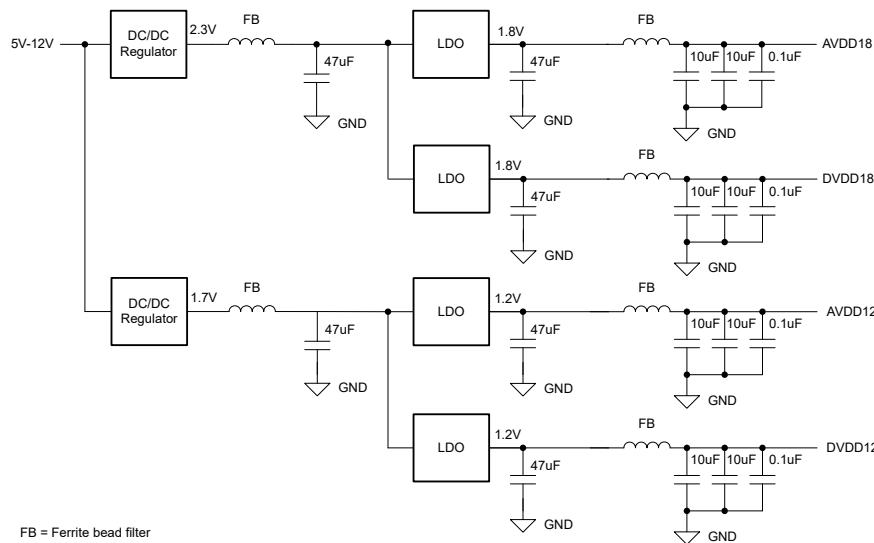

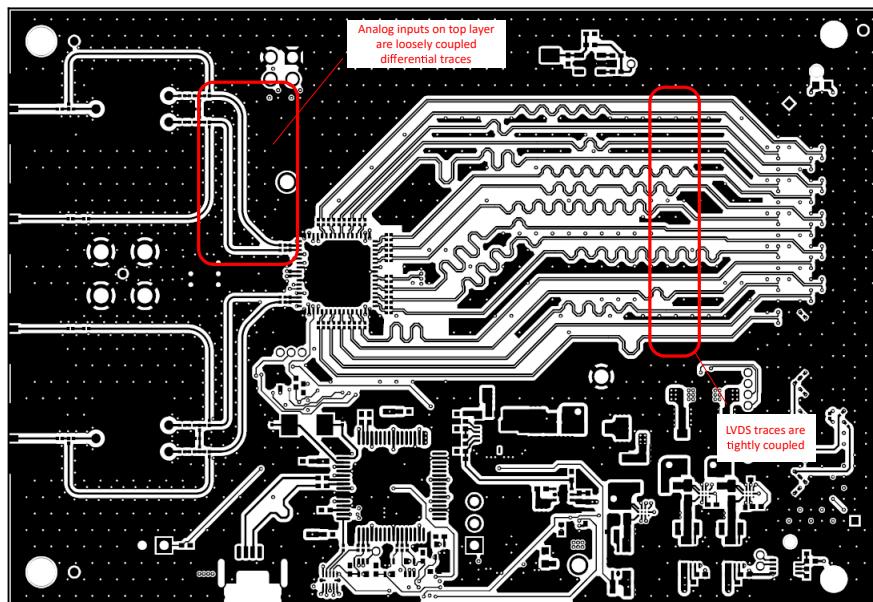

通常動作 (DDC バイパスおよび DDC) のほかに、このデバイスは複数の追加動作モードをサポートしています。