ADC168M102R-SEP 放射線耐性、8 チャネル、1MSPS、16 ビット ADC

## 1 特長

- 放射線耐性:

- シングル イベント ラッチアップ (SEL) 耐性: LET = 43MeV-cm<sup>2</sup>/mg (125°C) まで

- LET = 43MeV-cm<sup>2</sup>/mg まで、シングル イベント機 能割り込み (SEFI) 特性を評価済み

- 30krad (Si) まで、総吸収線量 (TID) RLAT/RHA 特性を評価済み

- 宇宙用強化プラスチック (宇宙用 EP):

- 防衛および航空宇宙アプリケーションをサポート

- 管理されたベースライン

- 単一のアセンブリ/テスト施設

- 長期にわたる製品ライフ サイクル

- 製品のトレーサビリティ

- ASTM E595 に準拠した気体排出試験実施済み

- VID (Vendor Item Drawing) V62/24631

- 軍用温度範囲:-55℃~+125℃

- 金ボンドワイヤ、NiPdAuリード仕上げ

- 8 つの擬似差動入力または 4 つの完全差動入力

- 2 チャネルの同時サンプリング

- 優れた AC 特性:

- 信号対雑音比:93 dB

- THD:-98 dB

- デュアル プログラマブルおよびデュアル バッファ 2.5V 基準電圧により次のことが可能:

- 2種類の入力電圧範囲設定

- 2 レベル PGA 実装

- プログラマブル自動シーケンサ

- オーバーサンプリング アプリケーション向けの内蔵デ ータストレージ (チャネルごとに最大4つ)

- 安全アプリケーション用の2ビットカウンタ

# 2 アプリケーション

- 衛星用電源システム (EPS)

- コマンドとデータの処理 (C&DH)

- 光学画像処理ペイロード

- モータ制御

- 電圧、電流、温度の監視

- 加速度計

## 3 概要

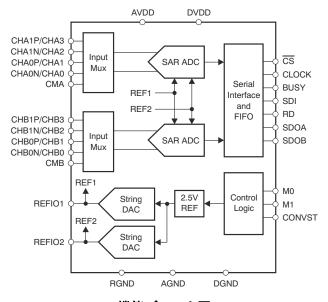

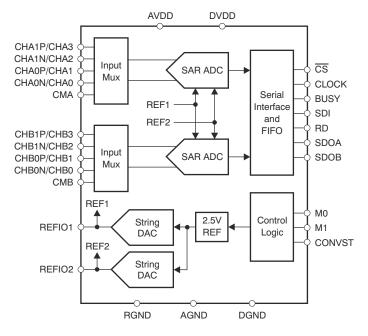

ADC168M102R-SEP はデュアル、16 ビット、1MSPS の A/D コンバータ (ADC) です。この ADC には、8 つの擬 似差動入力チャネルまたは 4 つの完全差動入力チャネ ルがあり、同時に信号を収集するために、2 つのペアにグ ループ化されています。アナログ入力は、ADC の入力に 対して差動で維持されます。入力マルチプレクサは、疑似 差動モードまたは完全差動モードのいずれかで使用しま す。疑似差動モードでは、ADC ごとに最大 4 つのチャネ ル (4x2) をサポートし、完全差動モードでは ADC ごとに 最大 2 つの入力 (2x2) を変換します。

ADC168M102R-SEP は 2 つのプログラマブル リファレ ンス出力、フレキシブルな電源電圧範囲、プログラマブル 自動シーケンサ、複数のパワーダウン機能を備えていま す。また、このデバイスには、チャネルごとに最大4つの 変換結果がデータ保存されます。

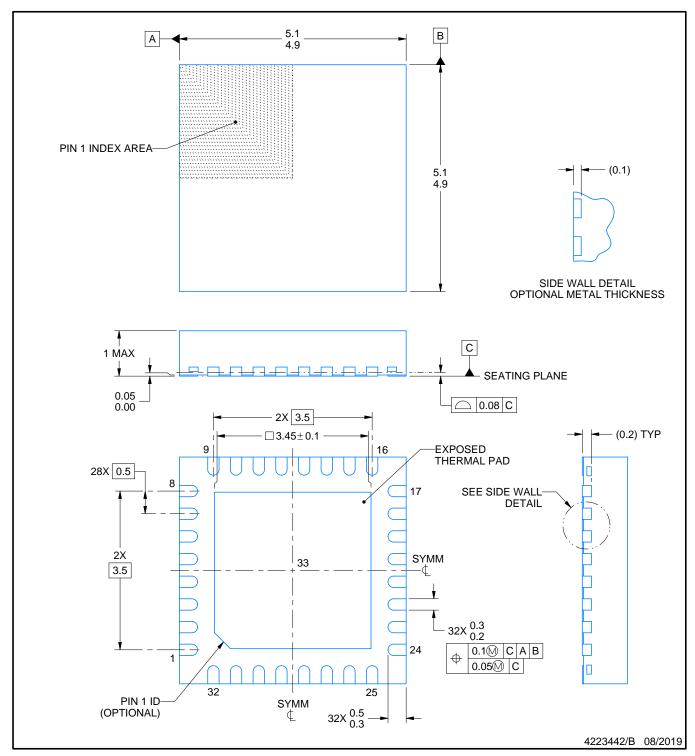

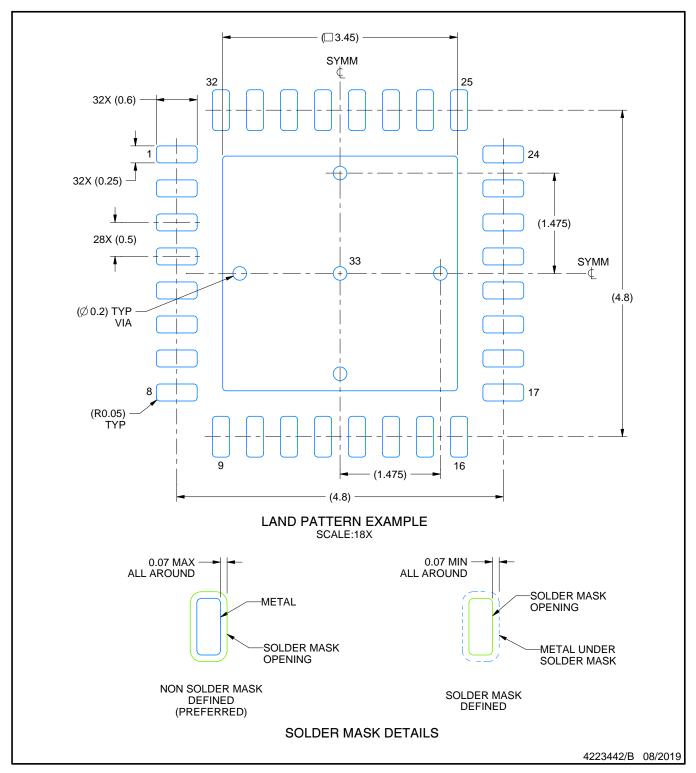

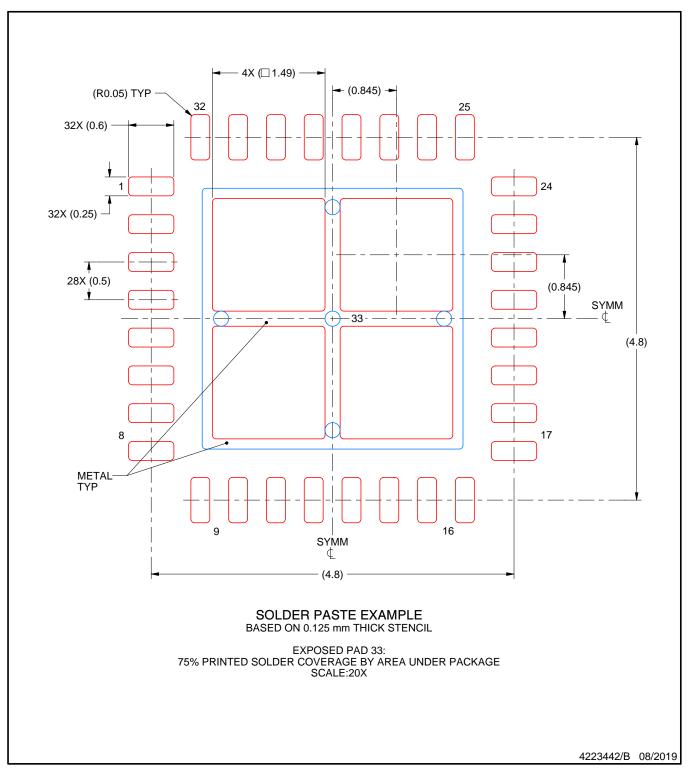

## パッケージ情報

| 部品番号            | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------------|----------------------|--------------------------|

| ADC168M102R-SEP | RHB (VQFN, 32)       | 5mm × 5mm                |

- 詳細については、「メカニカル、パッケージ、および注文情報」を参 照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

機能ブロック図

## **Table of Contents**

| 1 特長                                 | 1 | 6.4 Device Functional Modes             | 22 |

|--------------------------------------|---|-----------------------------------------|----|

| 2 アプリケーション                           |   | 6.5 Programming                         | 24 |

| 3 概要                                 |   | 7 Register Map                          | 32 |

| 4 Pin Configuration and Functions    |   | 8 Application and Implementation        | 42 |

| 5 Specifications                     |   | 8.1 Application Information             | 42 |

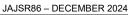

| 5.1 Absolute Maximum Ratings         |   | 8.2 Typical Application                 | 42 |

| 5.2 ESD Ratings                      |   | 8.3 Power Supply Recommendations        | 44 |

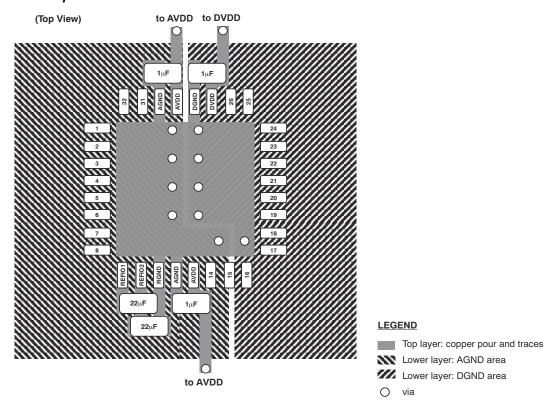

| 5.3 Recommended Operating Conditions |   | 8.4 Layout                              | 44 |

| 5.4 Thermal Information              |   | 9 Device and Documentation Support      | 47 |

| 5.5 Electrical Characteristics       |   | 9.1 Documentation Support               | 47 |

| 5.6 Timing Requirements              |   | 9.2 静電気放電に関する注意事項                       | 47 |

| 5.7 Switching Characteristics        |   | 9.3 用語集                                 | 47 |

| 5.8 Timing Diagrams                  |   | 9.4 Trademarks                          |    |

| 5.9 Typical Characteristics          |   | 9.5ドキュメントの更新通知を受け取る方法                   | 47 |

| 6 Detailed Description               |   | 9.6 サポート・リソース                           | 47 |

| 6.1 Overview                         |   | 10 Revision History                     |    |

| 6.2 Functional Block Diagram         |   | 11 Mechanical, Packaging, and Orderable |    |

| 6.3 Feature Description              |   | Information                             | 47 |

|                                      |   |                                         |    |

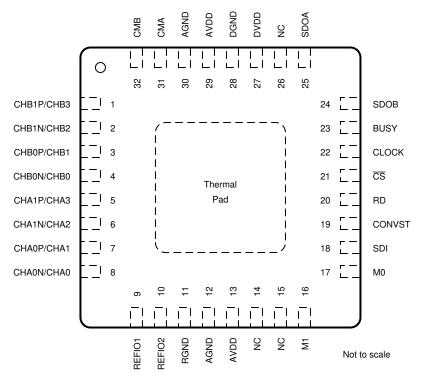

# 4 Pin Configuration and Functions

図 4-1. RHB Package, 32-Pin VQFN (Top View)

表 4-1. Pin Functions

| PIN        | 1      |                     |                                                                                                                                                                           |

|------------|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                               |

| AGND       | 12, 30 | Р                   | Analog ground. Connect to analog ground plane.                                                                                                                            |

| AVDD       | 13, 29 | Р                   | Analog power supply, 2.7V to 5.5V. Decouple to AGND with a 1µF ceramic capacitor.                                                                                         |

| BUSY       | 23     | DO                  | Converter busy indicator. BUSY goes high when the inputs are in hold mode and returns to low after the conversion is complete.                                            |

| CHA0N/CHA0 | 8      | Al                  | Fully differential inverting analog input channel A1 or pseudo-differential input A0                                                                                      |

| CHA0P/CHA1 | 7      | Al                  | Fully differential noninverting analog input channel A1 or pseudo-differential input A1                                                                                   |

| CHA1N/CHA2 | 6      | Al                  | Fully differential inverting analog input channel A1 or pseudo-differential input A2                                                                                      |

| CHA1P/CHA3 | 5      | Al                  | Fully differential noninverting analog input channel A1 or pseudo-differential input A3                                                                                   |

| CHB0N/CHB0 | 4      | Al                  | Fully differential inverting analog input channel B0 or pseudo-differential input B0                                                                                      |

| CHB0P/CHB1 | 3      | Al                  | Fully differential noninverting analog input channel B0 or pseudo-differential input B1                                                                                   |

| CHB1N/CHB2 | 2      | Al                  | Fully differential inverting analog input channel B1 or pseudo-differential input B2                                                                                      |

| CHB1P/CHB3 | 1      | Al                  | Fully differential noninverting analog input channel B1 or pseudo-differential input B3                                                                                   |

| CLOCK      | 22     | DI                  | External clock input. The range is 0.5MHz to 20MHz in half-clock mode, or 1MHz to 40MHz in full-clock mode.                                                               |

| CMA        | 31     | Al                  | Common-mode voltage input for channels Ax (in pseudo-differential mode only).                                                                                             |

| СМВ        | 32     | Al                  | Common-mode voltage input for channels Bx (in pseudo-differential mode only).                                                                                             |

| CONVST     | 19     | DI                  | Conversion start. The ADC switches from sample into hold mode on the rising edge of CONVST. Thereafter, the conversion starts with the next rising edge of the CLOCK pin. |

| CS         | 21     | DI                  | Chip select. When this pin is low, the SDOx, SDI, and RD pins are active. When this pin is high, the SDOx outputs are tri-stated, and the SDI and RD inputs are ignored.  |

| DGND       | 28     | Р                   | Digital ground. Connect to digital ground plane.                                                                                                                          |

| DVDD       | 27     | Р                   | Digital supply, 2.3V to 5.5V. Decouple to DGND with a 1µF ceramic capacitor.                                                                                              |

| MO         | 17     | DI                  | Mode pin 0. Selects analog input channel mode (see 表 6-5).                                                                                                                |

| M1         | 16     | DI                  | Mode pin 1. Selects the digital output mode (see 表 6-5).                                                                                                                  |

# 表 4-1. Pin Functions (続き)

| PIN                          |            |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------------------------------|------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO. TYPE <sup>(1)</sup> |            | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| NC                           | 14, 15, 26 | NC                  | This pin is not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| RD                           | 20         | DI                  | Read data. Synchronization pulse for the SDOx outputs and SDI input. RD only triggers when $\overline{\text{CS}}$ is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| REFIO1                       | 9          | AIO                 | ence voltage input/output 1. Connect 22µF ceramic capacitor is connected to RGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| REFIO2                       | 10         | AIO                 | rence voltage input/output 2. Connect 22μF ceramic capacitor is connected to RGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RGND                         | 11         | Р                   | Reference ground. Connect this pin to analog ground plane with a dedicated via.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SDI                          | 18         | DI                  | Serial data input. This pin sets up the internal registers. The data on SDI are ignored when $\overline{\text{CS}}$ is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| SDOA                         | 25         | DO                  | al data output for converter A. This pin is in tri-state when $	extstyle 	extstyle $ |  |

| SDOB                         | 24         | DO                  | Serial data output for converter B. Active only if M1 is low. This pin is in tri-state when $\overline{CS}$ is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

(1) Al = analog input, AlO = analog input/output, DI = digital input, DO = digital output, DIO = digital input/output, P = power supply, NC = not connected.

## **5 Specifications**

### 5.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                         | MIN        | MAX                       | UNIT |

|---------------------------------------------------------|------------|---------------------------|------|

| Supply voltage, AVDD to AGND or DVDD to DGND            | -0.3       | 6                         | V    |

| Supply voltage, DVDD to AVDD                            | -0.3       | 1.2 x AVDD <sup>(2)</sup> | V    |

| Analog and reference input voltage with respect to AGND | AGND - 0.3 | AVDD + 0.3                | V    |

| Digital input voltage with respect to DGND              | DGND - 0.3 | DVDD + 0.3                | V    |

| Ground voltage difference, AGND – DGND                  | -0.3       | 0.3                       | V    |

| Input current to any pin except supply pins             | -10        | 10                        | mA   |

| Junction temperature, T <sub>J</sub>                    |            | 150                       | °C   |

| Storage temperature, T <sub>stg</sub>                   | -65        | 150                       | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) Exceeding the specified limit causes an increase of the DVDD leakage current and leads to malfunction of the device.

### 5.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Floatroatatia diagharma | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                     | TEST CONDITIONS                 | MIN               | NOM | MAX        | UNIT |

|---------------------------|-------------------------------|---------------------------------|-------------------|-----|------------|------|

| A) (DD                    | Analog nower supply           | AVDD to AGND, half-clock mode   | 2.7               | 5.0 | 5.5        | V    |

| AVDD                      | AVDD Analog power supply      | AVDD to AGND, full-clock mode   | 4.5               | 5.0 | 5.5        | V    |

| DVDD Digital newer cumbly | 3V and 3.3V levels            | 2.3                             | 2.5               | 3.6 | V          |      |

|                           | DVDD Digital power supply     | 5V levels, half-clock mode only | 4.5               | 5.0 | 5.5        | V    |

| FSR                       | Full-scale analog input range | (CHxxP – CHxxN) or CHxx to CMx  | -V <sub>REF</sub> |     | $V_{REF}$  | V    |

| V <sub>IN</sub>           | Absolute input voltage        | CHxxx to AGND                   | -0.1              |     | AVDD + 0.1 | V    |

| T <sub>A</sub>            | Ambient temperature           |                                 | -55               | 25  | 125        | °C   |

### **5.4 Thermal Information**

|                       |                                              | ADC168M102R-SEP |      |

|-----------------------|----------------------------------------------|-----------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN)      | UNIT |

|                       |                                              | 32 PINS         | _    |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 33.3            | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.5            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.3             | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2             | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 7.4             | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (bottom) thermal resistance | 0.9             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

### 5.5 Electrical Characteristics

at AVDD and DVDD supply voltage ranges specified in *Recommended Operating Conditions*, VREF = 2.5V (internal), and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -55$ °C to 125°C; typical values at  $T_A = 25$ °C. AVDD = 5V, and DVDD = 3.3V

|                      | PARAMETER                                   | TEST CONDITIONS                           | MIN                 | TYP                      | MAX          | UNIT   |

|----------------------|---------------------------------------------|-------------------------------------------|---------------------|--------------------------|--------------|--------|

| ANALOG               | INPUTS                                      |                                           |                     |                          | I            |        |

| I <sub>DCL</sub>     | Input leakage current                       |                                           | -16                 |                          | 16           | nA     |

| C <sub>IN</sub>      | Input capacitance                           | CHxxx to AGND                             |                     | 45                       |              | pF     |

| C <sub>ID</sub>      | Differential input capacitance              | CHxxx to AGND                             |                     | 22.5                     |              | pF     |

| DC PERFO             | DRMANCE                                     |                                           |                     |                          | I.           |        |

|                      | Resolution                                  | No missing codes                          |                     | 16                       |              | Bits   |

| 5                    | D                                           | Half-clock mode                           | -2                  | ±0.6                     | 2            |        |

| DNL                  | Differential nonlinearity                   | Full-clock mode                           | -2                  | ±0.8                     | 4            | LSB    |

|                      |                                             | Half-clock mode                           | -4                  | ±1.2                     | 4            |        |

| INL                  | Integral nonlinearity                       | Full-clock mode                           | -5                  | ±1.5                     | 5            | LSB    |

| V <sub>OS</sub>      | Input offset error                          |                                           | -2.5                | ±0.2                     | 2.5          | mV     |

|                      | V <sub>OS</sub> match                       | ADC to ADC                                | -1.5                | ±0.1                     | 1.5          | mV     |

| dV <sub>OS</sub> /dT | Input offset error thermal drift            |                                           |                     | 1                        |              | μV/°C  |

| G <sub>ERR</sub>     | Gain error                                  |                                           | -0.15               | 0.01                     | 0.15         | %FSR   |

|                      | G <sub>ERR</sub> match                      | ADC to ADC                                | -0.15               | 0.01                     | 0.15         | %FSR   |

| G <sub>ERR</sub> /dT | G <sub>ERR</sub> thermal drift              |                                           |                     | 1                        |              | ppm/°C |

| AC PERFO             | DRMANCE                                     |                                           |                     |                          | <u>l</u>     |        |

| SINAD                | Signal-to-noise + distortion ratio          | $V_{IN} = 5V_{PP}$ , $f_{IN} = 10$ kHz    | 88                  | 92                       |              | dB     |

| SNR                  | Signal-to-noise ratio                       | $V_{IN} = 5V_{PP}, f_{IN} = 10kHz$        | 89                  | 93                       |              | dB     |

| THD                  | Total harmonic distortion                   | $V_{IN} = 5V_{PP}, f_{IN} = 10kHz$        |                     | -98                      | -90          | dB     |

| SFDR                 | Spurious-free dynamic range                 | $V_{IN} = 5V_{PP}, f_{IN} = 10kHz$        | 89                  | 100                      |              | dB     |

| CMRR                 | Common-mode rejection ratio                 | Both ADCs, f <sub>IN</sub> = dc to 100kHz |                     | 92                       |              | dB     |

| PSRR                 | Power-supply rejection ratio                |                                           |                     | 75                       |              | dB     |

| VOLTAGE              | REFERENCE INPUT                             |                                           |                     | -                        |              |        |

| V <sub>REF</sub>     | Reference input voltage range               |                                           | 2.485               | 2.5                      | 2.525        | V      |

| I <sub>REF</sub>     | Reference input current                     |                                           |                     | 50                       |              |        |

| C <sub>REF</sub>     | External decoupling capacitor               |                                           |                     | 22                       |              | μF     |

| INTERNAL             | VOLTAGE REFERENCE                           | ,                                         |                     |                          |              |        |

|                      | Reference output DAC resolution             |                                           | 10                  |                          |              | Bits   |

|                      |                                             | >20% to 100% of DAC range                 | 0.2 x               |                          | $V_{REFOUT}$ |        |

| V <sub>REFOUT</sub>  | Reference output voltage                    | -                                         | V <sub>REFOUT</sub> |                          |              | V      |

| * REFOUT             | reference output voltage                    | REFIO1, DAC = 3FFh                        | 2.485               | 2.500                    | 2.515        | v      |

|                      |                                             | REFIO2, DAC = 3FFh                        | 2.485               | 2.500                    | 2.515        |        |

| DNL <sub>DAC</sub>   | DAC DNL                                     |                                           | -5                  | ±1                       | 5            | LSB    |

| INL <sub>DAC</sub>   | DAC INL                                     |                                           | -5                  | ±0.5                     | 5            | LSB    |

| PSRR <sub>DAC</sub>  | Power-supply rejection ratio                |                                           |                     | 73                       |              | dB     |

| I <sub>REFOUT</sub>  | Output DC current                           |                                           |                     | ±2                       |              | mA     |

| I <sub>REFSC</sub>   | Output short-circuit current <sup>(1)</sup> |                                           |                     | 50                       |              | mA     |

| DIGITAL II           |                                             |                                           |                     |                          |              |        |

|                      | Input current <sup>(2)</sup>                | V <sub>IN</sub> = DVDD to DGND            | -50                 | -                        | 50           | nA     |

|                      | Digital input capacitance                   |                                           |                     | 5                        |              | pF     |

|                      | Logic family                                |                                           |                     | MOS with Schmitt Trigger |              |        |

| V <sub>IH</sub>      | Input high logic level                      | DVDD = 4.5V to 5.5V                       | 0.7 x DVDD          |                          | DVDD + 0.3   | V      |

| V <sub>IL</sub>      | Input low logic level                       | DVDD = 4.5V to 5.5V                       | -0.3                |                          | 0.3 x DVDD   | V      |

|                      | Logic family                                |                                           |                     | VCMOS                    |              |        |

| $V_{IH}$             | Input high logic level                      | DVDD = 2.3V to 3.6V                       | 2                   |                          | DVDD + 0.3   | V      |

## 5.5 Electrical Characteristics (続き)

at AVDD and DVDD supply voltage ranges specified in *Recommended Operating Conditions*, VREF = 2.5V (internal), and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -55^{\circ}C$  to  $125^{\circ}C$ ; typical values at  $T_A = 25^{\circ}C$ , AVDD = 5V, and DVDD = 3.3V

|                   | PARAMETER               | TEST CONDITIONS                         | MIN        | TYP    | MAX      | UNIT |

|-------------------|-------------------------|-----------------------------------------|------------|--------|----------|------|

| V <sub>IL</sub>   | Input low logic level   | DVDD = 2.3V to 3.6V                     | -0.3       |        | 0.8      | V    |

| DIGITAL           | OUTPUTS                 |                                         |            |        | <u> </u> |      |

| C <sub>OUT</sub>  | Output capacitance      |                                         |            | 5      |          | pF   |

| C <sub>LOAD</sub> | Load capacitance        |                                         |            |        | 30       | pF   |

|                   | Logic family            |                                         |            | CMOS   |          |      |

| V <sub>IH</sub>   | Output high logic level | DVDD = 4.5V, I <sub>LOAD</sub> = -100uA | 4.44       |        |          | V    |

| V <sub>IL</sub>   | Output low logic level  | DVDD = 4.5V, I <sub>LOAD</sub> = 100uA  |            |        | 0.5      | V    |

|                   | Logic family            |                                         | I          | LVCMOS |          |      |

| V <sub>IH</sub>   | Output high logic level | DVDD = 2.3V, I <sub>LOAD</sub> = -100uA | DVDD - 0.2 |        |          | V    |

| V <sub>IL</sub>   | Output low logic level  | DVDD = 2.3V, I <sub>LOAD</sub> = 100uA  |            |        | 0.2      | V    |

| POWER             | SUPPLY                  |                                         |            |        | <u> </u> |      |

|                   |                         | AVDD = 3.6V                             |            | 12     | 18       |      |

|                   |                         | AVDD = 5.5V                             |            | 15     | 25       |      |

| AIDD              | Analog supply current   | AVDD = 3.6V, sleep and auto-sleep modes |            | 0.8    | 2        | mA   |

|                   |                         | AVDD = 5.5V, sleep and auto-sleep modes |            | 0.9    | 6.2      |      |

|                   |                         | Power-down mode                         |            |        | 0.15     |      |

| D.D.D.            | Disit-Lawrence -        | DVDD = 3.6V, C <sub>LOAD</sub> = 10pF   |            | 1.1    |          | ^    |

| DIDD              | Digital supply current  | DVDD = 5.5V, C <sub>LOAD</sub> = 10pF   |            | 3      | 13       | mA   |

| <b>D</b>          | Power-dissipation       | AVDD = DVDD = 3.6V                      |            | 47.2   | 66.6     | \^/  |

| $P_D$             | (normal operation)      | AVDD = 5.5V, DVDD = 3.6V                |            | 86.5   | 135      | mW   |

<sup>(1)</sup> Reference output current is not internally limited.

<sup>(2)</sup> Digital pins input and output characteristics specified by design; not production tested.

## 5.6 Timing Requirements

at AVDD and DVDD supply voltage ranges specified in *Recommended Operating Conditions*, VREF = 2.5V (internal), and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -55$ °C to 125°C; typical values at  $T_A = 25$ °C. AVDD = 5V, and DVDD = 3.3V

|                                      |                                                   |                                              | MIN   | TYP MA | Х  | UNIT             |  |

|--------------------------------------|---------------------------------------------------|----------------------------------------------|-------|--------|----|------------------|--|

| SAMPLI                               | NG DYNAMICS                                       |                                              |       |        |    |                  |  |

| ı                                    | Carial alask francisco                            | Half-clock mode                              |       | 2      | 20 | MHz              |  |

| f <sub>CLK</sub>                     | Serial clock frequency                            | Full-clock mode                              |       | 4      | 10 | IVITZ            |  |

| t <sub>CLK</sub> Serial clock period | Sorial alook period                               | Half-clock mode                              | 50    |        |    | no               |  |

|                                      | Serial clock period                               | Full-clock mode                              | 25    |        |    | ns               |  |

| f <sub>DATA</sub>                    | ADC sampling frequency                            |                                              | 25    | 100    | 00 | kSPS             |  |

| t <sub>DATA</sub>                    | ADC sampling period (1/f <sub>DATA</sub> )        |                                              | 1     |        |    | μs               |  |

| SPI INTE                             | RFACE TIMINGS                                     |                                              |       |        |    |                  |  |

| t <sub>CLKL</sub>                    | Clock low time                                    |                                              | 11.25 |        |    | ns               |  |

| t <sub>CLKH</sub>                    | Clock high time                                   |                                              | 11.25 |        |    | ns               |  |

| t <sub>1</sub>                       | CONVST rising to first CLOCK rising               | edge                                         | 12    |        |    | ns               |  |

|                                      |                                                   |                                              | 10    |        |    | ns               |  |

| t <sub>2</sub>                       | CONVST high time                                  | Half-clock mode: timing modes II and IV only |       |        | 1  | t <sub>CLK</sub> |  |

| 13                                   | RD high time, half-clock mode: timing             | g modes II, IV, SII, and SIV only            |       |        | 1  | t <sub>CLK</sub> |  |

| S1                                   | RD high to CLOCK falling edge setup time          |                                              | 5     |        |    | ns               |  |

| H1                                   | RD high to CLOCK falling edge hold time           |                                              | 5     |        |    | ns               |  |

| S2                                   | Input data valid to CLOCK falling edge setup time |                                              | 5     |        |    | ns               |  |

| H2                                   | Input data valid to CLOCK falling edg             | ge hold time                                 | 4     |        |    | ns               |  |

## 5.7 Switching Characteristics

at AVDD and DVDD supply voltage ranges specified in *Recommended Operating Conditions*, VREF = 2.5V (internal), and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -55$ °C to 125°C; tvoical values at  $T_A = 25$ °C. AVDD = 5V. and DVDD = 3.3V

|                   | PARAMETER                                                        | TEST CONDITIONS    | MIN  | TYP | MAX | UNIT             |

|-------------------|------------------------------------------------------------------|--------------------|------|-----|-----|------------------|

| SAMPLING          | DYNAMICS                                                         |                    |      |     |     |                  |

|                   | Companying times and ADC                                         | Half-clock mode    | 17.5 |     |     | +                |

| t <sub>CONV</sub> | Conversion time per ADC                                          | Full-clock mode    | 35   |     |     | t <sub>CLK</sub> |

| +                 | A aquicition time                                                | Half-clock mode    | 2    |     |     |                  |

| t <sub>ACQ</sub>  | Acquisition time                                                 | Full-clock mode    | 4    |     |     | t <sub>CLK</sub> |

| t <sub>A</sub>    | Aperture delay                                                   |                    |      |     | 6   | ns               |

|                   | t <sub>A</sub> match                                             |                    |      | 50  |     | ps               |

|                   | Aperture jitter                                                  |                    |      | 50  |     | ps               |

| SPI INTER         | FACE TIMINGS                                                     |                    |      |     |     |                  |

| +                 | CONVST rising edge to BUSY high delay <sup>(1)</sup>             | 2.3V ≤ DVDD ≤ 3.6V |      |     | 19  | no               |

| t <sub>D1</sub>   | CONVOT TISING edge to BOOT High delay                            | 4.5V ≤ DVDD ≤ 5.5V |      |     | 16  | ns               |

|                   | CLOCK 18th falling edge (half-clock mode) or                     | 2.3V ≤ DVDD ≤ 3.6V |      |     | 25  |                  |

| t <sub>D2</sub>   | 24 <sup>th</sup> rising edge (full-clock mode) to BUSY low delay | 4.5V ≤ DVDD ≤ 5.5V |      |     | 20  | ns               |

| +                 | CLOCK rising edge to next data valid delay in                    | 2.3V ≤ DVDD ≤ 3.6V |      |     | 14  | ns               |

| t <sub>D3</sub>   | half-clock mode                                                  | 4.5V ≤ DVDD ≤ 5.5V |      |     | 12  | 115              |

| t <sub>H3</sub>   | Output data to CLOCK rising edge hold time, half-clock mode      |                    | 3    |     |     | ns               |

| t <sub>D4</sub>   | CLOCK falling edge to next data valid delay, full                | -clock mode        |      |     | 19  | ns               |

## 5.7 Switching Characteristics (続き)

at AVDD and DVDD supply voltage ranges specified in *Recommended Operating Conditions*, VREF = 2.5V (internal), and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -55^{\circ}C$  to  $125^{\circ}C$ ; typical values at  $T_A = 25^{\circ}C$ , AVDD = 5V, and DVDD = 3.3V

|                    | PARAMETER                                  | MIN                                                          | TYP | MAX | UNIT |    |  |  |  |

|--------------------|--------------------------------------------|--------------------------------------------------------------|-----|-----|------|----|--|--|--|

| t <sub>H4</sub>    | Output data to CLOCK falling edge hold tin | Output data to CLOCK falling edge hold time, full-clock mode |     |     |      |    |  |  |  |

| t <sub>D5</sub>    | PD falling adge to first date valid        | 2.3V ≤ DVDD ≤ 3.6V                                           |     |     | 16   | ns |  |  |  |

|                    | RD falling edge to first data valid        | 4.5V ≤ DVDD ≤ 5.5V                                           |     |     | 12   | ns |  |  |  |

| t <sub>D6</sub>    | CS rising edge to SDOx tristate delay      | •                                                            |     |     | 6    | ns |  |  |  |

| INTERNAL V         | INTERNAL VOLTAGE REFERENCE                 |                                                              |     |     |      |    |  |  |  |

| t <sub>REFON</sub> | Reference output settling time             |                                                              | 8   |     | ms   |    |  |  |  |

Not applicable in auto-sleep power-down mode.

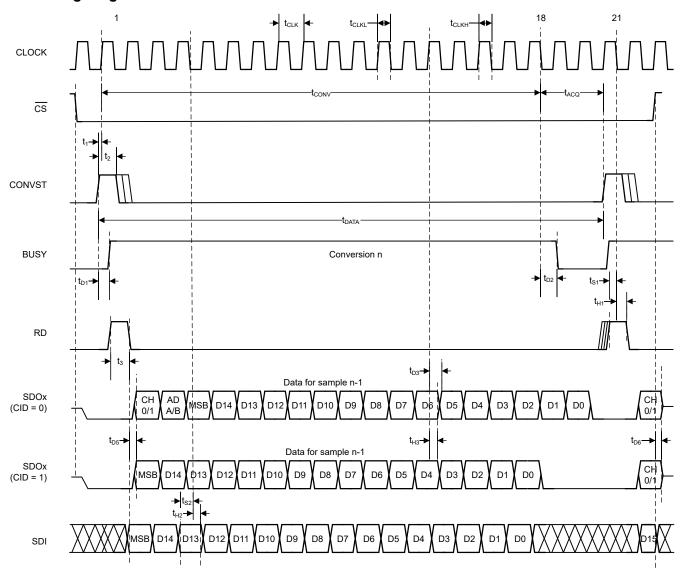

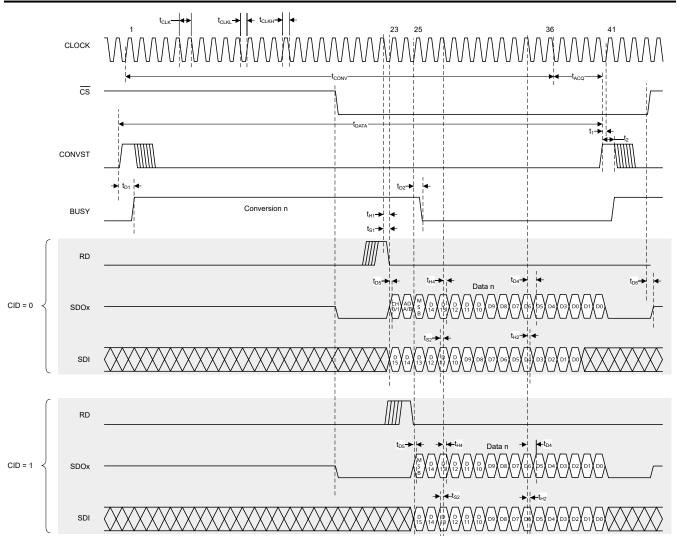

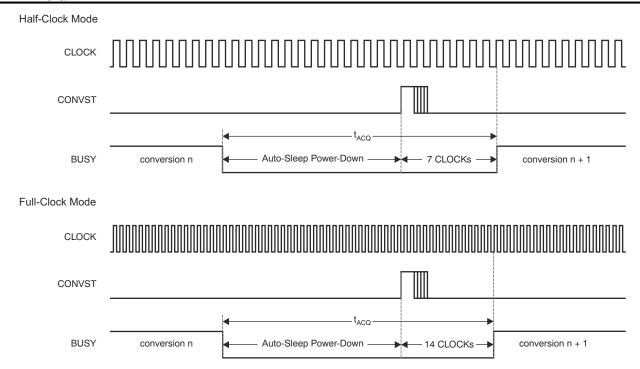

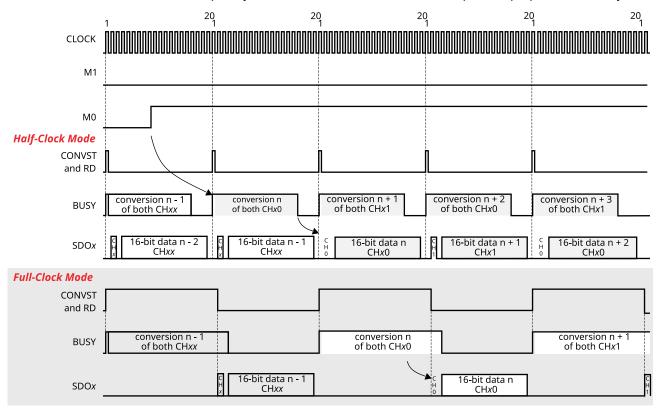

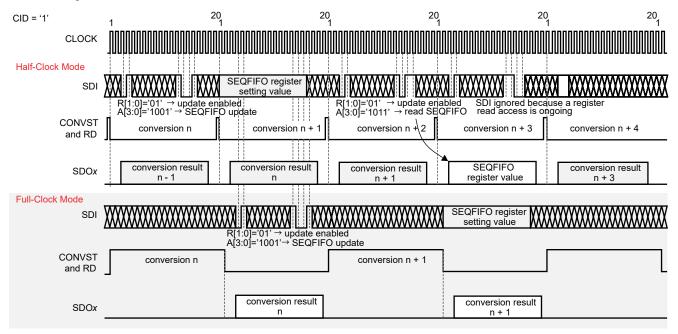

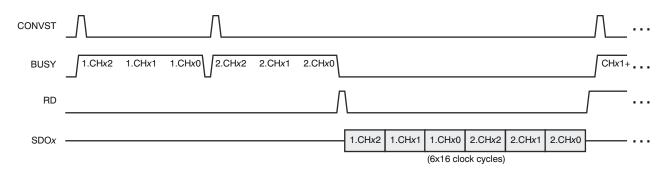

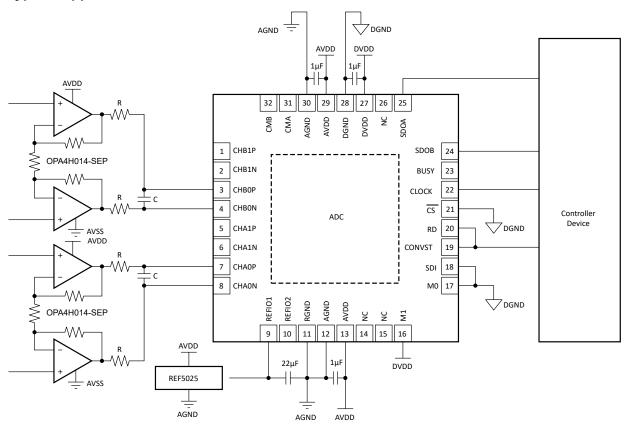

### 5.8 Timing Diagrams

図 5-1. Detailed Timing Diagram: Half-Clock Mode

図 5-2. Detailed Timing Diagram: Full-Clock Mode

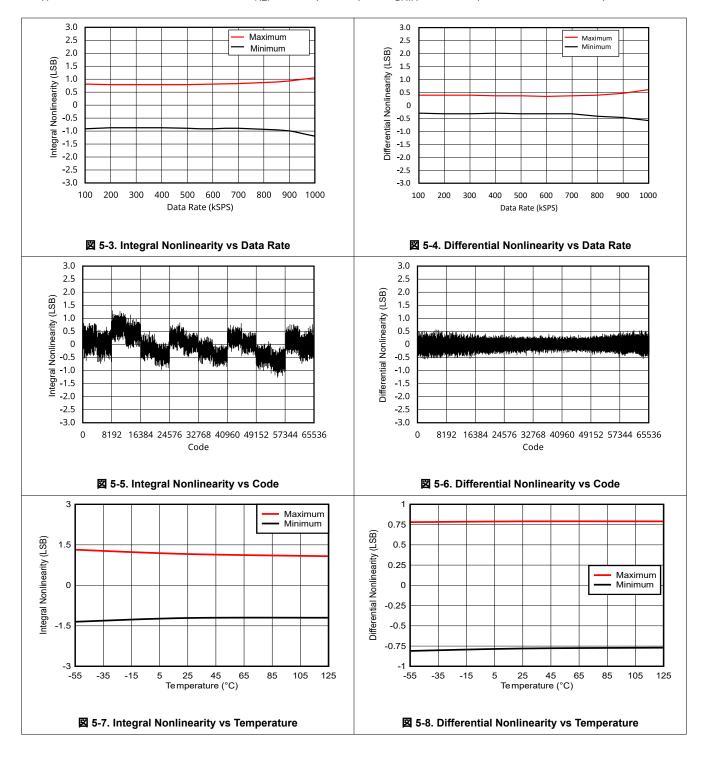

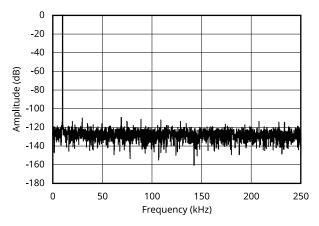

### 5.9 Typical Characteristics

at  $T_A$  = +25°C, AVDD = 5V, DVDD = 3.3V,  $V_{REF}$  = 2.5V (internal), and  $f_{DATA}$  = 1MSPS (unless otherwise noted)

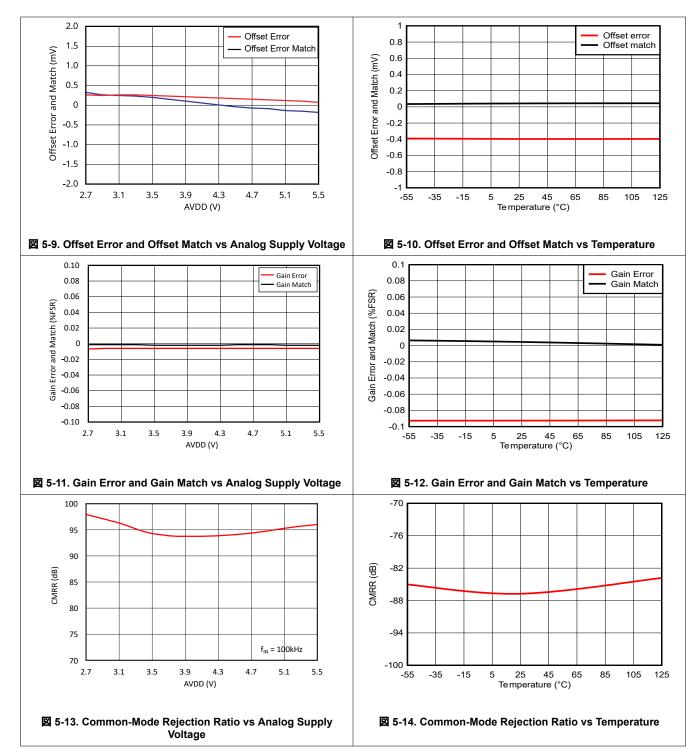

## **5.9 Typical Characteristics (continued)**

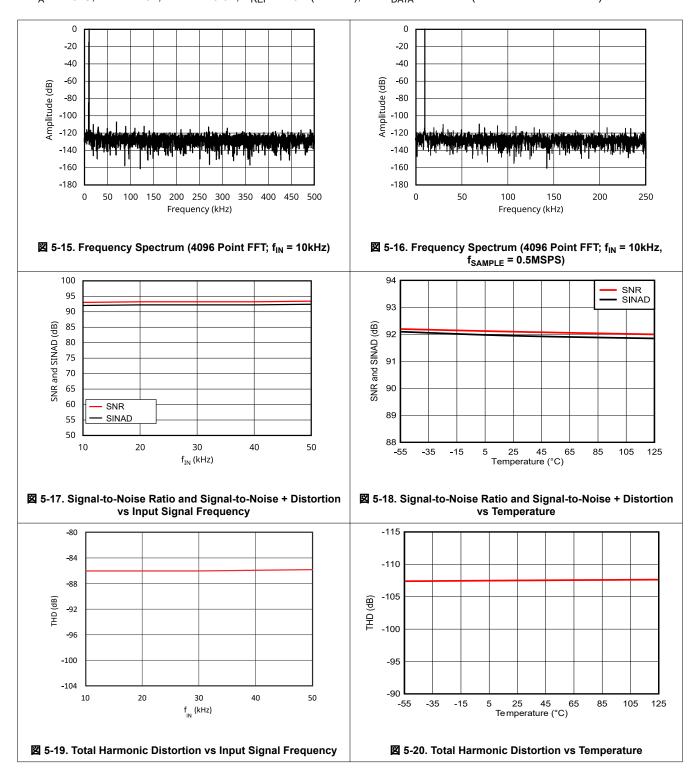

at  $T_A$  = +25°C, AVDD = 5V, DVDD = 3.3V,  $V_{REF}$  = 2.5V (internal), and  $f_{DATA}$  = 1MSPS (unless otherwise noted)

### 5.9 Typical Characteristics (continued)

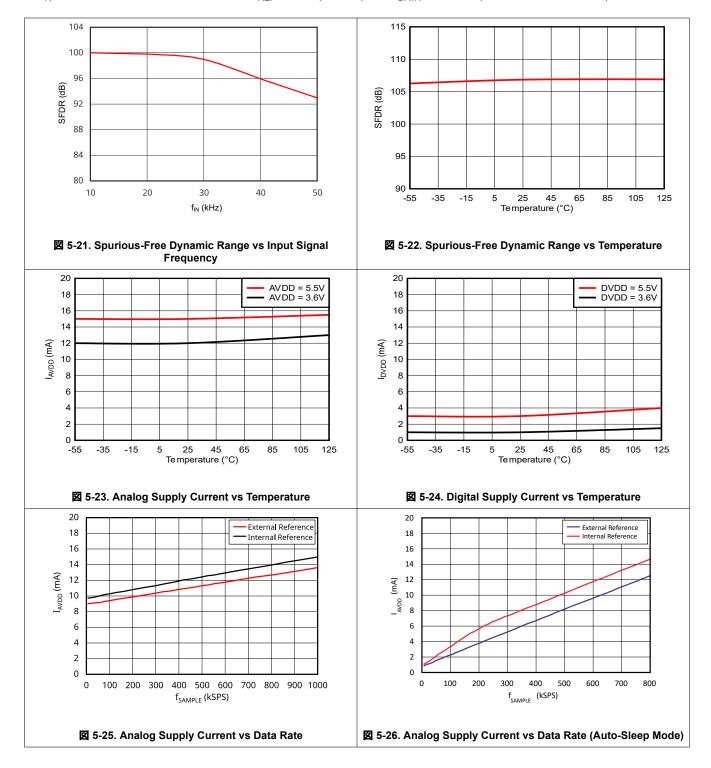

at T<sub>A</sub> = +25°C, AVDD = 5V, DVDD = 3.3V, V<sub>REF</sub> = 2.5V (internal), and f<sub>DATA</sub> = 1MSPS (unless otherwise noted)

## **5.9 Typical Characteristics (continued)**

at  $T_A$  = +25°C, AVDD = 5V, DVDD = 3.3V,  $V_{REF}$  = 2.5V (internal), and  $f_{DATA}$  = 1MSPS (unless otherwise noted)

English Data Sheet: SBASAW9

## **6 Detailed Description**

### 6.1 Overview

The ADC168M102R-SEP contains two 16-bit analog-to-digital converters (ADCs), that operate based on the successive approximation register (SAR) principle. These ADCs sample and convert simultaneously. Conversion time is potentially as low as 875ns. Adding a 100ns acquisition time, and a 25ns margin for propagation delay and CONVST pulse generation, results in a 1MSPS maximum conversion rate.

Each ADC has a fully differential 2:1 multiplexer front-end. In many common applications, all negative input signals remain at the same constant voltage (for example, 2.5V). For these applications, use the multiplexer in a pseudo-differential 4:1 mode. In this mode, the CMx pins function as common-mode pins and all four analog inputs are referred to the corresponding CMx pin.

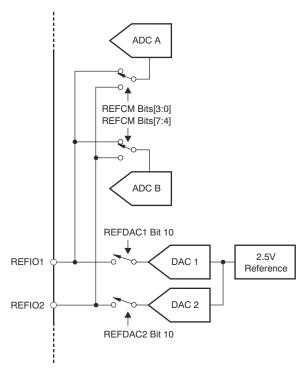

The ADC168M102R-SEP also includes a 2.5V internal reference. This reference drives two independently programmable, 10-bit digital-to-analog converters (DACs). Thus, allowing the voltage at each REFIOx pin to be adjusted through the internal REFDACx registers in 2.44mV steps. A low-noise, unity-gain operational amplifier buffers each DAC output and drives the REFIOx pin.

## 6.2 Functional Block Diagram

### **6.3 Feature Description**

### 6.3.1 Analog

This section discusses the analog input circuit, the ADCs, and the reference design of the device.

### 6.3.1.1 Analog Inputs

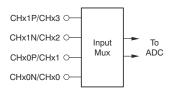

As shown in 図 6-1, each ADC is fed by an input multiplexer. Each multiplexer is used in either a fully differential 2:1 configuration (表 6-1) or a pseudo-differential 4:1 configuration (表 6-2).

**図 6-1. Input Multiplexer Configuration**

Use either the external M0 pin or the C[1:0] bits in the Configuration (CONFIG) register for channel selection in fully differential mode. In pseudo-differential mode, channel selection is performed with the SEQFIFO register. In either mode, changing the multiplexer settings impacts the conversion started with the next CONVST pulse.

表 6-1. Fully Differential 2:1 Multiplexer Configuration

|    |    | . •   |       |

|----|----|-------|-------|

| C1 | C0 | ADC+  | ADC-  |

| 0  | X  | CHx0P | CHx0N |

| 1  | x  | CHx1P | CHx1N |

表 6-2. Pseudo-Differential 4:1 Multiplexer Configuration

| C0 | ADC+             | ADC-                 |

|----|------------------|----------------------|

| 0  | CHx0             | CMx/REFIOx           |

| 1  | CHx1             | CMx/REFIOx           |

| 0  | CHx2             | CMx/REFIOx           |

| 1  | CHx3             | CMx/REFIOx           |

|    | 0<br>1<br>0<br>1 | 0 CHx0 1 CHx1 0 CHx2 |

The input path for the converter is fully differential and provides a good common-mode rejection of 92dB at 100kHz. The high CMRR also helps suppress noise in harsh industrial environments.

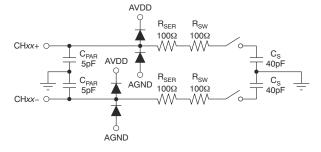

Each 40pF sample-and-hold capacitor ( $C_S$  in  $\boxtimes$  6-2) is connected through switches to the multiplexer output. Opening the switches holds the sampled data during the conversion process. After the conversion completes, both capacitors are precharged for the duration of one clock cycle to the voltage present at the REFIOx pin. After precharging, the multiplexer outputs are connected to the sampling capacitors again. The voltage at the analog input pin is usually different from the reference voltage. Therefore, charge the sample capacitors to within one-half LSB for 16-bit accuracy during the acquisition time  $t_{ACO}$  (see  $\boxtimes$  5-1 and  $\boxtimes$  5-2).

図 6-2. Equivalent Analog Input Circuit

Acquisition is indicated with the BUSY signal low. Acquisition starts by closing the input switches (after finishing the previous conversion and precharging) and finishes with the rising edge of the CONVST signal. If the device operates at full speed, the acquisition time is typically 100ns.

As shown in,  $\pm$  1 calculate the minimum –3dB bandwidth of the driving operational amplifier with n = 16 for the resolution of the ADC168M102R-SEP:

$$f_{-3dB} = \frac{\ln(2)(n+1)}{2\pi t_{ACQ}}$$

(1)

With  $t_{ACQ}$  = 100ns, the minimum bandwidth of the driving amplifier is 19MHz for the ADC168M102R-SEP. The required bandwidth is potentially lower if the application allows a longer acquisition time.

A gain error occurs if a given application does not fulfill the settling requirement in 式 1. However, linearity and THD are not directly affected as a result of precharging the capacitors.

The OPA365 from Texas Instruments is recommended as a driver. In addition to offering the required bandwidth, the OPA365 also provides a low offset and excellent THD performance (see the *Application and Implementation* section).

The phase margin of the driving operational amplifier is usually reduced by the ADC sampling capacitor. A resistor placed between the capacitor and the amplifier limits this effect. Therefore, place an internal  $100\Omega$  resistor (R<sub>SER</sub>) in series with the switch. The switch resistance (R<sub>SW</sub>) is typically  $100\Omega$ ; see  $\boxtimes$  6-2).

An input driver is not required if the impedance of the signal source (R<sub>SOURCE</sub>) fulfills the requirement of  $\gtrsim 2$ :

$$R_{SOURCE} < \frac{t_{ACQ}}{C_S ln(2)(n+1)} - (R_{SER} + R_{SW})$$

(2)

#### where:

- n = 16 is the ADC168M102R-SEP resolution

- C<sub>S</sub> = 40pF sample capacitance

- R<sub>SFR</sub> = 100Ω input resistor value

- $R_{SW} = 100\Omega$  switch resistance value

With  $t_{ACQ}$  = 100ns, make sure the maximum source impedance is less than  $12\Omega$  for the ADC168M102R-SEP. The source impedance is potentially higher if the ADC is used at a lower data rate.

The differential input voltage range of the ADC is ±V<sub>RFF</sub>, the voltage at the selected REFIOx pin.

Keep the voltage for all inputs within the 0.3V limit below AGND and above AVDD. Do not allow dc current to flow through the inputs. Exceeding these limits causes the internal ESD diodes to conduct, leading to increased leakage current that potentially damages the device. Current is only necessary to recharge the sample-and-hold capacitors.

Directly tie any unused inputs to AGND or RGND without the need of a pulldown resistor.

#### 6.3.1.2 Analog-to-Digital Converters (ADCs)

The ADC168M102R-SEP includes two 1MSPS, 16-bit SAR ADCs that include sample-and-hold, respectively; see the *Functional Block Diagram*.

#### **6.3.1.3 CONVST**

The analog inputs are held with the CONVST rising edge (conversion start) signal. The setup time of CONVST referred to the next CLOCK rising edge (system clock) is 12ns (minimum). The conversion automatically starts with the rising CLOCK edge. Do not issue a rising CONVST edge during a conversion (that is, when BUSY is high).

RD (read data) and CONVST are shorted to minimize necessary software and wiring. The RD signal is triggered by the device on the falling CLOCK edge. Therefore, activate the combined signals with the rising CLOCK edge. The conversion then starts with the subsequent rising CLOCK edge. In modes with only SDOA active, the maximum length of the combined RD and CONVST signal is one clock cycle if half-clock timing is used. These modes are II, IV, SII, and SIV.

If CONVST and RD are combined, make sure  $\overline{\text{CS}}$  is low whenever a new conversion starts. However, this condition is not required if RD and CONVST are controlled separately. If the first-in, first-out (FIFO) is used, control CONVST separately from RD.

After completing a conversion, the sample capacitors are automatically precharged to the reference voltage value used to significantly reduce crosstalk among the multiplexed input channels.

#### 6.3.1.4 CLOCK

The ADC168M102R-SEP uses an external clock with an allowable frequency range that depends on the mode being used. By default (after power-up), the ADC operates in half-clock mode that supports a clock ranging from 0.5MHz to 20MHz. In full-clock mode, the ADC requires a clock ranging from 1MHz to 40MHz. For maximum data throughput, keep the clock signal continuously running. However, when using the device in burst mode, keep the clock held static low or high when read access completes and before starting a new conversion.

Keep the CLOCK duty cycle at 50%. However, the device functions properly with a duty cycle between 30% and 70%.

#### 6.3.1.5 RESET

The ADC168M102R-SEP features an internal power-on reset (POR) function. A user-controlled reset is also issued using the SDI register bits A[3:0] (see the *Digital* section).

#### 6.3.1.6 REFIOx

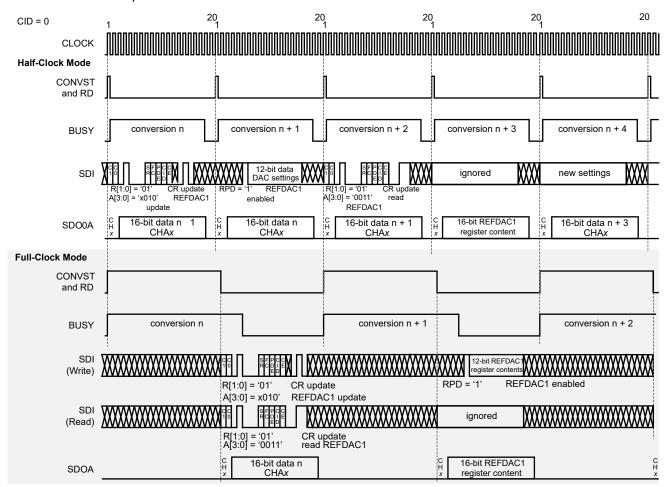

The ADC168M102R-SEP includes a low-drift, 2.5V internal reference source. This source feeds two, 10-bit string DACs that are controlled through registers. As a result of this architecture, the reference voltages at REFIOx are programmable in 2.44mV steps and adjusted to application requirements without additional external components. The actual output voltage is calculated using \$\frac{1}{2}\$, with code being the decimal value of the REFDACx register content:

$$V_{REF} = \frac{2.5V(\text{code } + 1)}{1024}$$

(3)

The reference DAC has a fixed transition at code 508 (0x1FC). At this code, the DAC shows a jump of up to 10mV in the transfer function. 表 6-3 lists some examples of internal reference DAC settings. However, to provide proper performance, do not program the REFDACx output voltage below 0.5V.

表 6-3. REFDACx Setting Examples

| VREFOUT (NOM) | DECIMAL CODE | BINARY CODE  | HEXADECIMAL<br>CODE |

|---------------|--------------|--------------|---------------------|

| 0.5000V       | 205          | 00 1100 1101 | 0CDh                |

| 1.2429V       | 507          | 01 1111 1100 | 1FBh                |

| 1.2427V       | 508          | 01 1111 1101 | 1FCh                |

| 2.5000V       | 1023         | 11 1111 1111 | 3FFh                |

A minimum of  $22\mu F$  capacitance is required on each REFIOx output to keep the references stable. The settling time is 8ms (maximum) with the reference capacitor connected. Smaller reference capacitance values reduce the DNL, INL, and ac performance of the device. By default, both reference outputs are disabled and the respective values are set to 2.5V after power-up.

For applications that use an external reference source, the internal reference is disabled (default) using the RPD bit in the CONFIG register (see the *Digital* section). The REFIOx pins are directly connected to the ADC; therefore, the internal switching generates spikes at this pin. Thus, use an external 22µF capacitor to the analog ground (AGND) to stabilize the reference input voltage.

Leave disabled REFIOx pins floating or directly tied to AGND or RGND.

Each reference DAC output is individually selected as a source for each channel input using the Rxx bits in the REFCM register.  $\boxtimes$  6-3 shows a simplified block diagram of the internal circuit.

図 6-3. Reference Selection Circuit

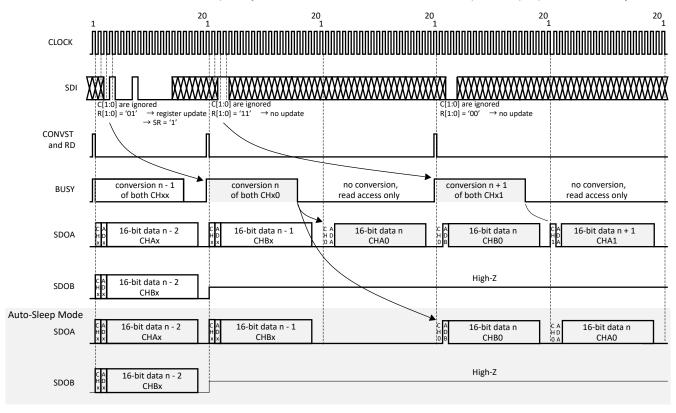

### 6.3.2 Digital

This section reviews the timing and control of the serial interface.

The ADC168M102R-SEP offers a set of internal registers that allows the control of several device features and modes. See the *Register Map* section for details. 表 6-4 lists the supported device operating modes.

| St 0 4. Supported Operating modes    |                                                                                                                                |                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| INPUT SIGNAL TYPE                    | MANUAL CHANNEL SELECTION                                                                                                       | AUTOMATIC CHANNEL SELECTION                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Fully differential<br>(PDE bit = 0)  | Operating modes: I, II, and special mode II<br>Channel information is selectable through the CID<br>bit<br>FIFO: Not available | Operating modes: III, IV and special mode IV Channel information is selectable through the CID bit. FIFO: Available in mode III and special mode IV. When used, a single read pulse allows reading of all data.  |  |  |  |  |  |  |  |  |  |

| Pseudo-differential<br>(PDE bit = 1) | Operating modes: I, II and special mode II<br>Channel information is selectable through the CID<br>bit<br>FIFO: Not available  | Operating modes: III and special mode IV Channel information is not available (CID bit forced to 1). FIFO: Available in mode III and special mode IV. When used, a single read pulse allows reading of all data. |  |  |  |  |  |  |  |  |  |

表 6-4. Supported Operating Modes

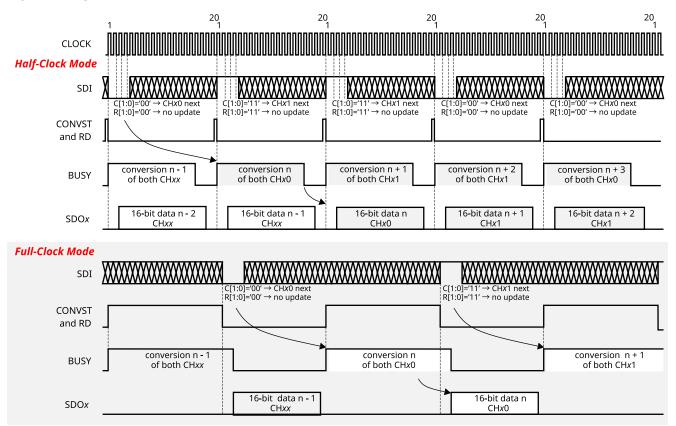

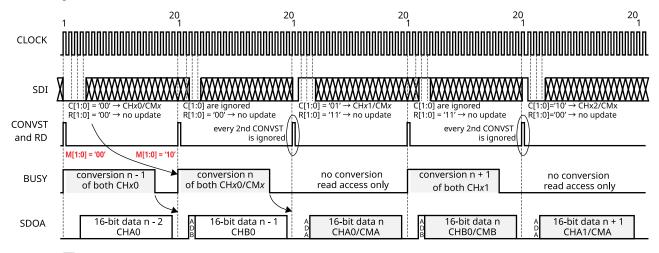

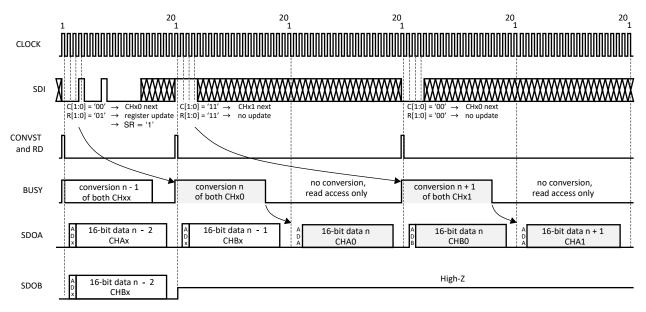

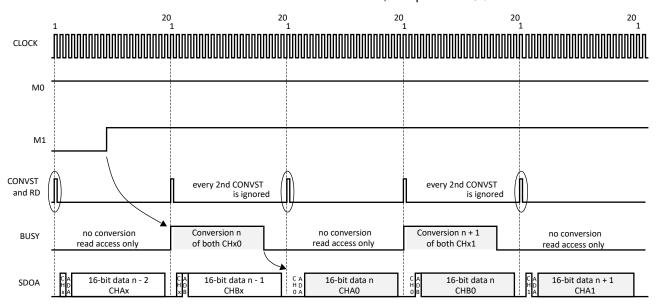

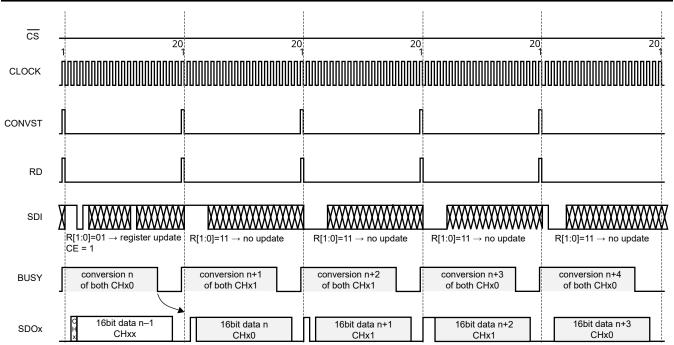

#### 6.3.2.1 Mode Selection Pins M0 and M1

As shown in 表 6-5, configure the ADC168M102R-SEP to four different operating modes using the M0 and M1 mode pins.

表 6-5. M0, M1 Truth Table

| MO | M1 | CHANNEL SELECTION    | SDOx USED     |

|----|----|----------------------|---------------|

| 0  | 0  | Manual (through SDI) | SDOA and SDOB |

| 0  | 1  | Manual (through SDI) | SDOA only     |

| 1  | 0  | Automatic            | SDOA and SDOB |

| 1  | 1  | Automatic            | SDOA only     |

The M0 pin sets either manual or automatic channel selection. In manual mode, the CONFIG register bits C[1:0] select between channels CHx0 and CHx1. In automatic mode, the CONFIG register bits C[1:0] are ignored and channel selection is controlled by the device after each conversion. The automatic channel selection is only performed on fully differential inputs in this case. For pseudo-differential inputs, the internal sequencer controls the input multiplexer.

The M1 pin selects how serial data are transmitted. Serial data are transmitted simultaneously on both SDOA and SDOB outputs for each channel (respectively), or only the SDOA output transmitts data from both channels. See 🗵 6-5 through 🗵 6-10 and the associated text for more information.

Additionally, the SDI pin controls device functionality through the internal register; see the *Register Map* section for details.

#### 6.3.2.2 Half-Clock Mode (Default Mode After Power-Up and Reset)

The ADC168M102R-SEP powers up in half-clock mode. In this mode, the ADC requires at least 20 CLOCKs for a complete conversion cycle, including the acquisition phase. The conversion result is only read during the next conversion cycle. The first output bit is available with the falling RD edge, and the following output data bits are refreshed with the CLOCK rising edge.

### 6.3.2.3 Full-Clock Mode (Allowing Conversion and Data Readout Within 1µs, Supported In Dual Output Modes)

The full-clock mode allows converting data and reading the result within 1µs. The entire cycle requires 40 CLOCKs. The first output bit is available with the falling RD edge. The following output data bits are refreshed with the falling edge of the CLOCK in this mode.

Use the full-clock mode with a 4.5V to 5.5V AVDD power supply range and a 2.3V to 3.6V DVDD digital supply range. The internal FIFO is disabled in full-clock mode.

#### 6.3.2.4 2-Bit Counter

This device offers a selectable 2-bit counter (activated using the CE bit in the CONFIG register) that is a useful feature in safety applications. The counter value automatically increments whenever a new conversion result is stored in the output register, indicating a new value. The counter default value after power-up is 01 (followed by 10, 11, 00, 01, and so on); see  $\boxtimes$  7-3. The counter value increments only when new conversion results are transferred to the output register. Thus, this counter verifies the ADC performed a conversion and the data read are the new conversion result (not an old result read multiple times).

#### 6.4 Device Functional Modes

#### 6.4.1 Power-Down Modes and Reset

This device has a comprehensive built-in power-down feature. There are three power-down modes: power-down, sleep, and auto-sleep. All three power-down modes are activated by write access completion, during which the related bits are asserted (PD[1:0]). All modes are deactivated by deasserting the respective bits in the CONFIG register. The content of the CONFIG register is not affected by any of the power-down modes. Any ongoing conversion is finished before entering any of the power-down modes. 表 6-6 summarizes the differences among the three power-down modes.

表 6-6. Power-Down Modes

| POWER-<br>DOWN MODE | POWER-<br>DOWN<br>CURRENT | POWER-<br>DOWN<br>ENABLED BY | POWER-<br>DOWN START<br>BY | DELAY TIME<br>TO POWER-<br>DOWN | NORMAL<br>OPERATION<br>BY | WAKEUP TIME          | POWER-<br>DOWN<br>DISABLED BY |

|---------------------|---------------------------|------------------------------|----------------------------|---------------------------------|---------------------------|----------------------|-------------------------------|

| Power-down          | 5μΑ                       | PD[1:0] = 01                 | Write access completed     | 20µs                            | PD[1:0] = 00              | 8ms                  | PD[1:0] = 00                  |

| Sleep               | 1.2mA (3.6V)              | PD[1:0] = 10                 | Write access completed     | 10µs                            | PD[1:0] = 00              | 7 or 14 CLOCK cycles | PD[1:0] = 00                  |

| Auto-sleep          | 1.2mA (3.6V)              | PD[1:0] = 11                 | Each end of conversion     | 10µs                            | CONVST pulse              | 7 or 14 CLOCK cycles | PD[1:0] = 00                  |

#### 6.4.1.1 Power-Down Mode

In power-down mode (PD[1:0] = 01), all functional blocks except the digital interface are disabled. In this mode, the current demand is reduced to  $5\mu A$  within  $20\mu s$ . The wakeup time from power-down mode is 8ms when using a reference capacitor of  $22\mu F$ . The device goes into power-down mode after completing any ongoing conversions.

#### 6.4.1.2 Sleep Mode

In sleep mode (PD[1:0] = 10), the device reduces the current demand to approximately 0.9mA within  $10\mu s$ . The device goes into sleep mode after completing any ongoing conversions.

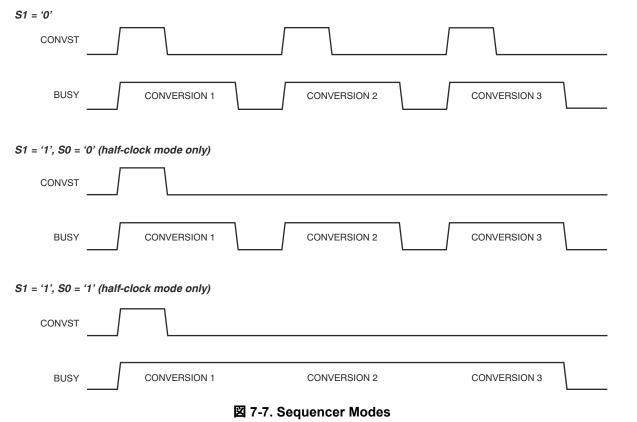

### 6.4.1.3 Auto-Sleep Mode

Auto-sleep mode is almost identical to sleep mode. The only differences are the method of activating the mode and waking up the device. The CONFIG register bits PD[1:0] = 11 only enable or disable this feature. If auto-sleep mode is enabled, the device automatically turns off the biasing after finishing a conversion; thus, the end of conversion actually activates auto-sleep mode. If sequencer mode is used and individual conversion start pulses are chosen (S1 = 0), the device automatically powers down after each conversion. If a single CONVST pulse starts the sequence (S1 = 1), power-down is activated when the entire sequence completes.

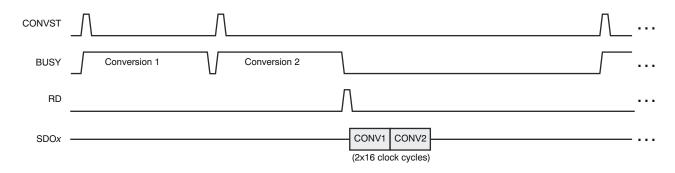

The device wakes up with the next CONVST pulse. However, the analog input is held in sample mode for another seven clock cycles in half-clock mode, or 14 clock cycles in full-clock mode. Thereafter (see 🗵 6-4), the actual conversion starts (BUSY goes high). This time is required to settle the internal circuitry to the required voltage levels. The conversion result is delayed in auto-sleep mode; see 🗵 6-10.

In this mode, the current demand is reduced to approximately 1.2mA within 10µs.

図 6-4. Actual Conversion Start In Auto-Sleep Mode

### 6.4.1.4 Reset