SN65HVS883

JAJSCH3-SEPTEMBER 2016

# SN65HVS883 24V、8チャネル・デジタル入力シリアライザ

## 1 特長

- 8つのセンサ入力

- 最大34Vの高い入力電圧

- 0ms~3msのデバウンス・フィルタを選択可能

- 0.2mA~5.2mAまで可変の電流制限

- フィールド入力および電源ラインに対する 15kV HBMまでの保護

- 外部のステータスLED用の出力ドライバ

- カスケード接続により、入力を8個単位で増やす ことが可能

- SPI互換のインターフェイス

- 外部デジタル・アイソレータへの、レギュレート された5V出力

- 低電源電圧インジケータ

## 2 アプリケーション

- 産業自動化およびプロセス制御用のセンサ入力

- IEC61131-2タイプ1、2、3スイッチ

- EN60947-5-2近接スイッチ

- PCおよびPLCシステム用の、チャネル数の多いデジタル入力モジュール

- 非集中化I/Oモジュール

## 3 概要

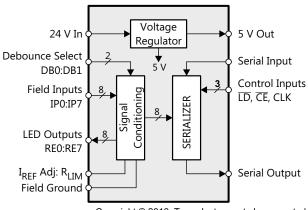

SN65HVS883は24V、8チャネルのデジタル入力シリアライザで、産業自動化において、PCおよびPLCベースのシステム用の、チャネル密度の高いデジタル入力モジュールとして使用されます。ガルバニー絶縁体と組み合わせることで、デバイスはフィールド側の24Vセンサ出力と、制御側の低電圧コントローラ入力との間で、完全なインターフェイスになります。

EN60947-5-2準拠の2線および3線の近接スイッチから供給される入力信号は、電流制限されてから、内部のデバウンス・フィルタにより検証されます。入力のスイッチング特性は、IEC61131-2のタイプ1、2、3センサ・スイッチに準拠しています。

負荷およびクロック信号を印加すると、入力データが並列にラッチされてシフト・レジスタに送られ、後段のアイソレータによりクロックに合わせて直列に、シリアルPLC入力へ送られます。

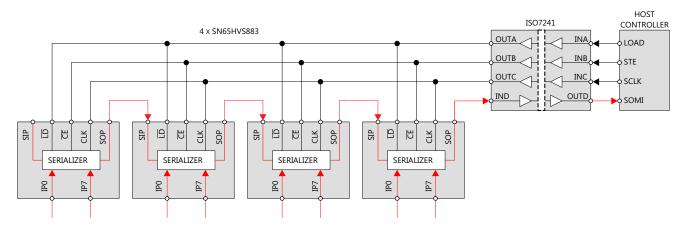

前段のデバイスのシリアル出力を後段のデバイスのシリアル入力へ接続することによって、複数のSN65HVS883をカスケード接続すると、チャネル数の多い入力モジュールの設計が可能になります。入力の状態は、3mAの定電流LED出力により示されます。内部の基準電流を設定するため、高精度の外付け抵抗が必要です。内蔵の電圧レギュレータにより、低消費電力アイソレータへ5Vの電源が供給されます。内部の電源電圧モニタにより、チップOK(CHOK)信号が出力されます。

SN65HVS883は28ピンのPWP PowerPAD™パッケージ で供給され、効率的な放熱が可能です。このデバイスは、 -40 $^{\circ}$ ~85 $^{\circ}$ の温度範囲で動作が規定されています。

#### 製品情報(1)

| 型都       | <b>F</b> | パッケージ       | 本体サイズ(公称)     |

|----------|----------|-------------|---------------|

| SN65HVS8 | 83       | HTSSOP (28) | 9.70mm×4.40mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

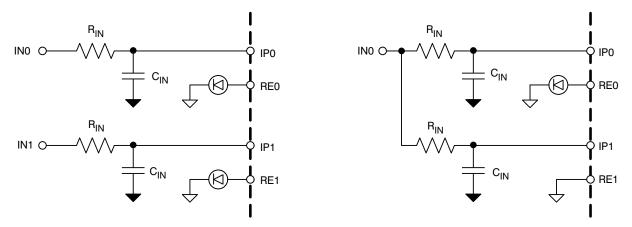

## I/O構造の簡略図

Copyright © 2016, Texas Instruments Incorporated

# 目次

| 1      | 特長1                                       |    | 8.1 Overview                         | 10 |

|--------|-------------------------------------------|----|--------------------------------------|----|

| 2      | アプリケーション1                                 |    | 8.2 Functional Block Diagram         | 10 |

| 3      | 概要1                                       |    | 8.3 Feature Description              |    |

| 4      | 改訂履歴                                      |    | 8.4 Device Functional Modes          | 14 |

| 5      | Pin Configuration and Functions           | 9  | Application and Implementation       | 15 |

| ა<br>6 | _                                         |    | 9.1 Application Information          |    |

| 0      | Specifications                            |    | 9.2 Typical Application              |    |

|        | 6.1 Absolute Maximum Ratings              | 10 | Power Supply Recommendations         |    |

|        | 6.2 ESD Ratings                           | 11 | Layout                               |    |

|        | 6.3 Recommended Operating Conditions      |    | 11.1 Layout Guidelines               |    |

|        | 6.4 Thermal Information                   |    | 11.2 Layout Example                  |    |

|        | 6.6 Timing Requirements                   | 12 | デバイスおよびドキュメントのサポート                   |    |

|        | 6.7 Switching Characteristics             |    | 12.1 Third-Party Products Disclaimer |    |

|        | 6.8 Typical Input Characteristics         |    | 12.2 ドキュメントの更新通知を受け取る方法              |    |

|        | 6.9 Typical Voltage Regulator Performance |    | 12.3 コミュニティ・リソース                     |    |

|        | Characteristics 8                         |    | 12.4 商標                              |    |

| 7      | Parameter Measurement Information9        |    | 12.5 静電気放電に関する注意事項                   |    |

| •      | 7.1 Waveforms                             |    | 12.6 Glossary                        |    |

|        | 7.2 Signal Conventions                    | 13 | メカニカル、パッケージ、および注文情報                  |    |

| 8      | Detailed Description                      |    | ///・/// // // // V (40&0 仕入旧刊        | 22 |

| J      | Detailed Description10                    |    |                                      |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2016年9月 | *    | 初版 |

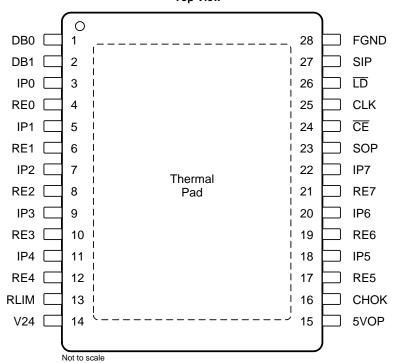

# 5 Pin Configuration and Functions

PWP Package 28 Pin (HTSSOP) With Exposed Thermal Pad Top View

## **Pin Functions**

| PIN                            |          | DESCRIPTION                              |  |

|--------------------------------|----------|------------------------------------------|--|

| PIN NO.                        | NAME     | DESCRIPTION                              |  |

| 1, 2                           | DB0, DB1 | Debounce select inputs                   |  |

| 3, 5, 7, 9,<br>11, 18, 20, 22  | IPx      | Input channel x                          |  |

| 4, 6, 8, 10,<br>12, 17, 19, 21 | REx      | Return path x (LED drive)                |  |

| 13                             | RLIM     | Current limiting resistor                |  |

| 14                             | V24      | 24 VDC field supply                      |  |

| 15                             | 5VOP     | 5 V output to supply low-power isolators |  |

| 16                             | CHOK     | Chip okay indicator output               |  |

| 23                             | SOP      | Serial data output                       |  |

| 24                             | CE       | Clock enable input                       |  |

| 25                             | CLK      | Serial clock input                       |  |

| 26                             | D        | Load pulse input                         |  |

| 27                             | SIP      | Serial data input                        |  |

| 28                             | FGND     | Field ground                             |  |

# TEXAS INSTRUMENTS

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

|                  |                                    |                                                                     |     | MIN       | MAX    | UNIT       |

|------------------|------------------------------------|---------------------------------------------------------------------|-----|-----------|--------|------------|

| V24              | Field power input                  | V24                                                                 |     | -0.3      | 36     | V          |

| $V_{IPx}$        | Field digital inputs               | IPx                                                                 |     | -0.3      | 36     | V          |

| $V_{ID}$         | Voltage at any logic input         | DB0, DB1, CLK, SIP, $\overline{\text{CE}}$ , $\overline{\text{LD}}$ |     | -0.5      | 6      | V          |

| Io               | Output current                     | CHOK, SOP                                                           |     |           | ±8     | mA         |

| P <sub>TOT</sub> | Continuous total power dissipation |                                                                     | See | Thermal I | nforma | tion table |

| TJ               | Junction temperature               |                                                                     |     |           | 170    | °C         |

## 6.2 ESD Ratings

|  |                                                                     |          |        | VALUE | UNIT |

|--|---------------------------------------------------------------------|----------|--------|-------|------|

|  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-                     | All pins | ±4000  |       |      |

|  | 001 <sup>(1)</sup>                                                  | IPx,V24  | ±15000 | V     |      |

|  | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | All pins | ±1000  |       |      |

|  | Machine Mode <sup>(3)</sup>                                         | All pins | ±100   |       |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) JEDEC Standard 22, Method A115-A.

# 6.3 Recommended Operating Conditions

|                  |                                          | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------------|-----|-----|-----|------|

| V <sub>24</sub>  | Field supply voltage                     | 10  | 24  | 34  | V    |

| $V_{IPL}$        | Field input low-state input voltage (1)  | 0   |     | 4   | V    |

| V <sub>IPH</sub> | Field input high-state input voltage (1) | 10  |     | 34  | V    |

| V <sub>IL</sub>  | Logic low-state input voltage            | 0   |     | 0.8 | V    |

| $V_{IH}$         | Logic high-state input voltage           | 2   |     | 5.5 | V    |

| R <sub>LIM</sub> | Current limiter resistor                 | 17  | 25  | 500 | kΩ   |

| $f_{IP}$         | Input data rate <sup>(2)</sup>           | 0   |     | 1   | Mbps |

| TJ               |                                          |     |     | 150 | °C   |

| T <sub>A</sub>   |                                          | -40 |     | 85  | °C   |

- (1) Field input voltages correspond to an input resistor of  $R_{IN}$  = 1.2 k $\Omega$

- 2) Maximum data rate corresponds to 0 ms debounce time, (DB0 = open, DB1 = FGND), and  $R_{IN} = 0 \Omega$

#### 6.4 Thermal Information

|                      |                                                                                                                                                                                                                         |              | SN65HVS883 |      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------|

|                      | THERM                                                                                                                                                                                                                   | PWP (HTSSOP) | UNIT       |      |

|                      |                                                                                                                                                                                                                         |              | 28 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance                                                                                                                                                                                  |              |            | °C/W |

| $R_{\theta JC(top)}$ | BJC(top) Junction-to-case (top) thermal resistance                                                                                                                                                                      |              |            | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                                                                                                                                                                                    |              | 15         | °C/W |

| PD                   | $ \begin{array}{c} I_{LOAD} = 50 \text{ mA}, \ R_{IN} = 0, \ IPO-IP7 = V24 = 30 \ V, \\ RE7 = FGND, \ f_{CLK} = 100 \ MHz, \\ I_{IP-LIM} \ and \ I_{CC} = worst \ case \ with \ R_{LIM} = 25 \ k\Omega \\ \end{array} $ |              | 2591       | mW   |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

JAJSCH3-SEPTEMBER 2016 www.ti.com

# 6.5 Electrical Characteristics

all voltages measured against FGND unless otherwise stated, see Figure 12

| SYMBOL                     | PARAMETER                                                        | PIN                                       | TEST CONDITIONS                                                                                                                           | MIN  | TYP       | MAX | UNIT |  |

|----------------------------|------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-----|------|--|

| V <sub>TH-(IP)</sub>       | Low-level device input threshold voltage                         |                                           | 18 V< V24 < 34 V,                                                                                                                         | 4    | 4.3       |     | V    |  |

| V <sub>TH+(IP)</sub>       | High-level device input threshold voltage                        | IP0-IP7                                   | $R_{IN} = 0 \Omega$ ,                                                                                                                     |      | 5.2       | 5.5 | V    |  |

| V <sub>HYS(IP)</sub>       | Device input hysteresis                                          |                                           | $R_{LIM} = 25 \text{ k}\Omega$                                                                                                            |      | 0.9       |     | V    |  |

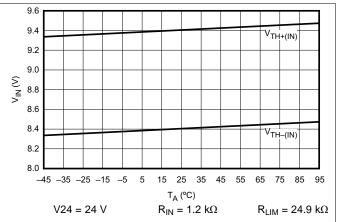

| V <sub>TH-(IN)</sub>       | Low-level field input threshold voltage                          |                                           | 18 V < V24 < 34 V,                                                                                                                        | 6    | 8.4       |     | V    |  |

| V <sub>TH+(IN)</sub>       | High-level field input threshold voltage                         | measured at field side of R <sub>IN</sub> | $R_{IN} = 1.2 \text{ k}\Omega \pm 5\%,$                                                                                                   |      | 9.4       | 10  | V    |  |

| V <sub>HYS(IN)</sub>       | Field input hysteresis                                           | TICIA SIAC OF TAIN                        | $R_{LIM} = 25 \text{ k}\Omega$                                                                                                            |      | 1         |     | V    |  |

| V <sub>TH-(V24)</sub>      | Low-level V24-monitor threshold voltage                          |                                           |                                                                                                                                           | 15   | 16.05     |     | V    |  |

| V <sub>TH+(V24)</sub>      | High-level V24-monitor threshold voltage                         | V24                                       |                                                                                                                                           |      | 16.8      | 18  | V    |  |

| V <sub>HYS(V24)</sub>      | V24-monitor hysteresis                                           |                                           |                                                                                                                                           |      | 0.75      |     | V    |  |

| R <sub>IP</sub>            | Input resistance                                                 | IP0–IP7                                   | $3 \text{ V} < \text{V}_{\text{IPx}} < 6 \text{ V},$ $R_{\text{IN}} = 1.2 \text{ k}\Omega \pm 5\%,$ $R_{\text{LIM}} = 25 \text{ k}\Omega$ | 1.4  | 1.83      | 2.3 | kΩ   |  |

| I <sub>IP-LIM</sub>        | Input current limit                                              |                                           | $10~V < V_{IPx} < 34~V,$ $R_{LIM} = 25~k\Omega$                                                                                           | 3.15 | 3.6       | 4   | mA   |  |

| V <sub>OL</sub>            | Logic low-level output voltage                                   | SOD CHOK                                  | I <sub>OL</sub> = 20 μA                                                                                                                   |      |           | 0.4 | V    |  |

| V <sub>OH</sub>            | Logic high-level output voltage                                  | SOP, CHOK                                 | I <sub>OH</sub> = -20 μA                                                                                                                  | 4    |           |     | V    |  |

| I <sub>IL</sub>            | Logic input leakage current                                      | DB0, DB1, SIP,<br>LD, CE, CLK             |                                                                                                                                           | -50  |           | 50  | μΑ   |  |

| I <sub>RE-on</sub>         | RE on-state current                                              | RE0-RE7                                   | $R_{LIM} = 25 \text{ k}\Omega,$<br>$RE_X = FGND$                                                                                          | 2.8  | 3.15      | 3.5 | mA   |  |

| I <sub>CC(V24)</sub>       | Supply current                                                   | V24                                       | IP0 to IP7 = V24,<br>5VOP = open,<br>RE <sub>X</sub> = FGND,<br>All logic inputs open                                                     |      |           | 8.7 | mA   |  |

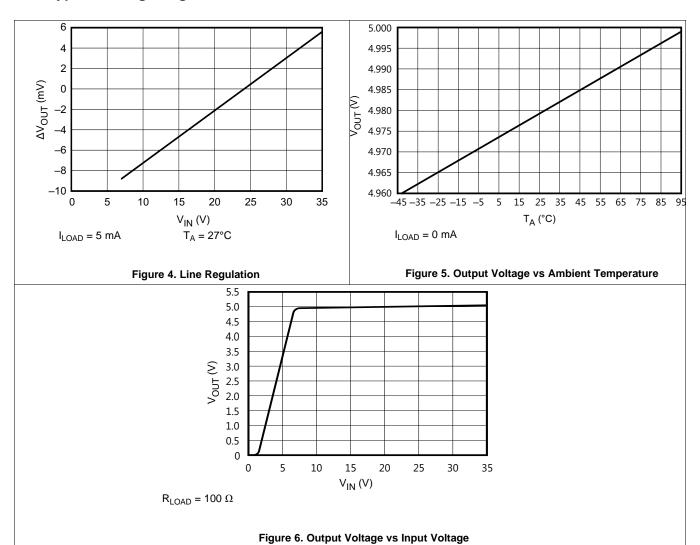

| V                          | Linear regulator output valtage                                  |                                           | 18 V < V24 < 34 V,<br>no load                                                                                                             | 4.5  | 5         | 5.5 | V    |  |

| V <sub>O(5V)</sub>         | Linear regulator output voltage                                  | 5VOP                                      | 18 V < V24 < 34 V,<br>I <sub>L</sub> = 50 mA                                                                                              | 4.5  | 4.5 5 5.5 |     | V    |  |

| I <sub>LIM(5V)</sub>       | Linear regulator output current limit                            |                                           |                                                                                                                                           |      | 115       |     | mA   |  |

| $\Delta V_5/\Delta V_{24}$ | Line regulation                                                  | 5VOP, V24                                 | 18 V < V24 < 34 V,<br>I <sub>L</sub> = 5 mA                                                                                               |      |           | 2   | mV/V |  |

|                            |                                                                  |                                           | DB0 = open,<br>DB1 = FGND                                                                                                                 |      | 0         |     |      |  |

| t <sub>DB</sub>            | Debounce times of input channels                                 | IP0-IP7                                   | DB0 = FGND,<br>DB1 = open                                                                                                                 |      | 1         |     | ms   |  |

|                            |                                                                  |                                           | DB0 = DB1 = open                                                                                                                          |      | 3         |     | 1    |  |

| t <sub>DB-HL</sub>         | Voltage monitor debounce time after V24 < 15 V (CHOK turns low)  | V04 CUCK                                  |                                                                                                                                           |      | 1         |     | ms   |  |

| t <sub>DB-LH</sub>         | Voltage monitor debounce time after V24 > 18 V (CHOK turns high) | V24, CHOK                                 |                                                                                                                                           |      | 6         |     | ms   |  |

| T <sub>SHDN</sub>          | Shutdown temperature                                             |                                           |                                                                                                                                           |      | 170       |     | °C   |  |

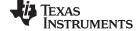

# 6.6 Timing Requirements

over operating free-air temperature range (unless otherwise noted)

| SYMBOL           | PARAMETER                                          |               | MIN | TYP N | /IAX | UNIT |

|------------------|----------------------------------------------------|---------------|-----|-------|------|------|

| t <sub>W1</sub>  | CLK pulse width                                    | See Figure 9  | 4   |       |      | ns   |

| t <sub>W2</sub>  | LD pulse width                                     | See Figure 7  | 6   |       |      | ns   |

| t <sub>SU1</sub> | SIP to CLK setup time                              | See Figure 10 | 4   |       |      | ns   |

| t <sub>H1</sub>  | SIP to CLK hold time                               | See Figure 10 | 2   |       |      | ns   |

| t <sub>SU2</sub> | Falling edge to rising edge (CE to CLK) setup time | See Figure 11 | 4   |       |      | ns   |

| t <sub>REC</sub> | LD to CLK recovery time                            | See Figure 8  | 2   |       |      | ns   |

| f <sub>CLK</sub> | Clock pulse frequency (50% duty cycle)             | See Figure 9  | DC  |       | 100  | MHz  |

# 6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| SYMBOL                                | PARAMETER           | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|---------------------------------------|---------------------|--------------------------------------|-----|-----|-----|------|

| t <sub>PLH1</sub> , t <sub>PHL1</sub> | CLK to SOP          | C <sub>L</sub> = 15 pF, see Figure 9 |     |     | 10  | ns   |

| t <sub>PLH2</sub> , t <sub>PHL2</sub> | LD to SOP           | C <sub>L</sub> = 15 pF, see Figure 7 |     |     | 14  | ns   |

| t <sub>r</sub> , t <sub>f</sub>       | Rise and fall times | C <sub>L</sub> = 15 pF, see Figure 9 |     |     | 5   | ns   |

www.ti.com JAJSCH3 – SEPTEMBER 2016

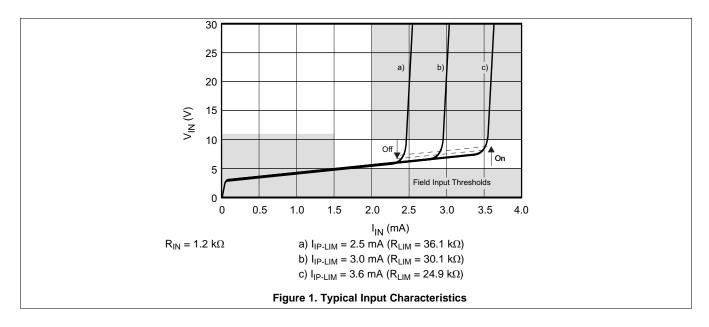

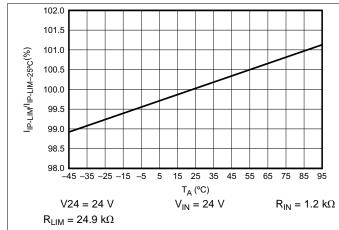

# 6.8 Typical Input Characteristics

**STRUMENTS**

Figure 2. Typical Current Limiter Variation vs Ambient Temperature

Figure 3. Typical Limiter Threshold Voltage Variation vs

Ambient Temperature

www.ti.com

# 6.9 Typical Voltage Regulator Performance Characteristics

# 7 Parameter Measurement Information

# 7.1 Waveforms

For the complete serial interface timing, refer to Figure 21.

# 7.2 Signal Conventions

Copyright © 2016, Texas Instruments Incorporated

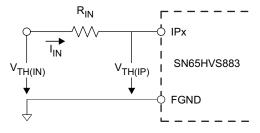

Figure 12. On/Off Threshold Voltage Measurements

# TEXAS INSTRUMENTS

# 8 Detailed Description

#### 8.1 Overview

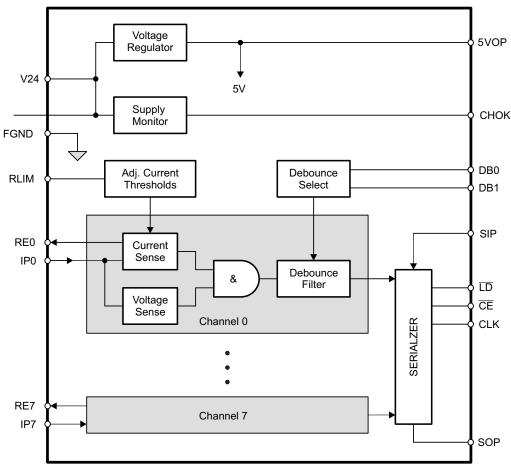

The SN65HVS883 is an 8 channel, digital input serializer which operates from a 24 V supply and accepts digital inputs of up to 34 V on the 8 channels (IP0-IP7). The device provides a serially shifted digital output with reduced voltage ranges of 0-5 V for applications in industrial and building automation systems. The SN65HVS883 meets JEDEC standards for ESD protection (refer to *ESD Ratings*), and is SPI compatible for interfacing with standard microcontrollers. The serializer operates in 2 fundamental modes: Load Mode and Shift mode. In Load mode, information from the field inputs is allowed to latch into the shift register. In Shift mode, the information stored in the parallel shift register can be serially shifted to the serial output (SOP). A detailed description of the functional modes is available in the *Device Functional Modes* section.

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 Digital Inputs

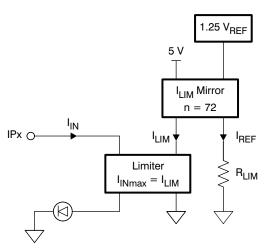

Each digital input operates as a controlled current sink limiting the input current to a maximum value of  $I_{LIM}$ . The current limit is derived from the reference current via  $I_{LIM} = n \times I_{REF}$ , and  $I_{REF}$  is determined by  $I_{REF} = V_{REF}/R_{LIM}$ . Thus, changing the current limit requires the change of  $R_{LIM}$  to a different value via:  $R_{LIM} = n \times V_{REF}/I_{LIM}$ .

Inserting the actual values for n and  $V_{REF}$  gives:  $R_{LIM} = 90 \text{ V} / I_{LIM}$ .

While the device is specified for a current limit of **3.6 mA**, (via  $R_{LIM} = 25 \text{ k}\Omega$ ), it is easy to lower the current limit to further reduce the power consumption. For example, for a current limit of **2.5 mA** simply calculate:

$$R_{LIM} = \frac{90 \text{ V}}{I_{LIM}} = \frac{90 \text{ V}}{2.5 \text{ mA}} = 36 \text{ k}\Omega$$

(1)

Figure 13. Digital Input Stage

#### 8.3.2 Debounce Filter

The HVS883 applies a simple analog/digital filtering technique to remove unintended signal transitions due to contact bounce or other mechanical effects. Any new input (either low or high) must be present for the duration of the selected debounce time to be latched into the shift register as a valid state.

The logic signal levels at the control inputs, DB0 and DB1 of the internal Debounce-Select logic determine the different debounce times listed in the following truth table.

**Table 1. Debounce Times**

| DB1       | DB0  | FUNCTION                        |

|-----------|------|---------------------------------|

| Open      | Open | 3 ms delay                      |

| Open      | FGND | 1 ms delay                      |

| FGND Open |      | 0 ms delay<br>(Filter bypassed) |

| FGND      | FGND | Reserved                        |

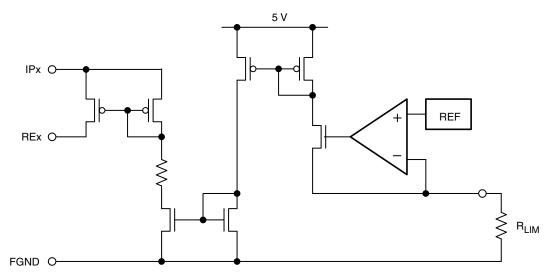

Figure 14. Equivalent Input Diagram

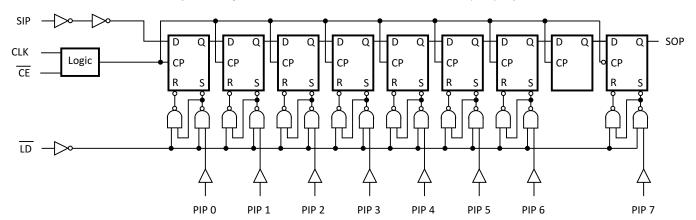

## 8.3.3 Shift Register

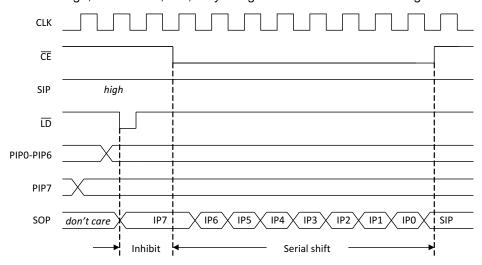

The conversion from parallel input to serial output data is performed by an eight-channel, parallel-in serial-out shift register. Parallel-in access is provided by the internal inputs, PIP0–PIP7, that are enabled by a low level at the load input (LD). When clocked, the latched input data shift towards the serial output (SOP). The shift register also provides a clock-enable function.

Clocking is accomplished by a low-to-high transition of the clock (CLK) input while  $\overline{LD}$  is held high and the clock enable (CE) input is held low for all registers in the shift register except the last register which is latched by a high-to-low transition. Parallel loading is inhibited when LD is held high. The parallel inputs to the register are enabled while  $\overline{LD}$  is low independently of the levels of the CLK,  $\overline{CE}$ , or serial (SIP) inputs.

Figure 15. Shift Register Logic Structure

JAJSCH3-SEPTEMBER 2016 www.ti.com

**Table 2. Function Table**

| FUNCTION      | INPUTS |     |    |  |

|---------------|--------|-----|----|--|

| FUNCTION      | CE     | CLK | LD |  |

| Parallel load | Y      | Y   | ı  |  |

| INPUTS |     |    | FUNCTION             |

|--------|-----|----|----------------------|

| LD     | CLK | CE | FUNCTION             |

| L      | X   | X  | Parallel load        |

| Н      | X   | Н  | No change            |

| Н      | 1   | L  | Shift <sup>(1)</sup> |

| Н      | 1   | L  | Shift <sup>(2)</sup> |

- Shift = content of each internal register, except the last register, shifts towards serial output.

- Shift = content of the last register shifts towards serial output.

## 8.3.4 Voltage Regulator

The on-chip linear voltage regulator provides a 5 V supply to the internal- and external circuitry, such as digital isolators, with an output drive capability of 50 mA and a typical current limit of 115 mA. The regulator accepts input voltages from 34 V down to 10 V. Because the regulator output is intended to supply external digital isolator circuits proper output voltage decoupling is required. For best results connect a 1 μF and a 0.1 μF ceramic capacitor as close as possible to the 5VOP-output. For longer traces between the SN65HVS883 and isolators of the ISO72xx family use additional 0.1 μF and 10 pF capacitors next to the isolator supply pins. Make sure, however, that the total load capacitance does not exceed 4.7 µF.

For good stability the voltage regulator requires a minimum load current, I<sub>L-MIN</sub>. Ensure that under any operating condition the ratio of the minimum load current in mA to the total load capacitance in µF is larger than 1:

$$\frac{I_{L-MIN}}{C_L} > \frac{1}{1} \frac{mA}{\mu F} \tag{2}$$

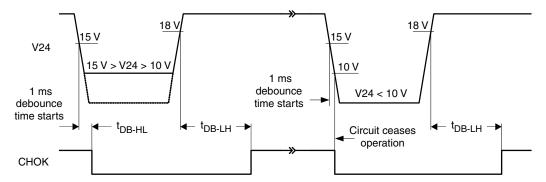

#### 8.3.5 Supply Voltage Monitor

The integrated supply voltage monitor senses the supply voltage of the SN65HVS883 at the V24-pin. If this voltage drops below 15 V but stays within the regulator's operating range, i.e., 15 V > V24 > 10 V, the output CHOK goes low 1 ms later. When the supply voltage returns to 24 V, the CHOK output turns logic high after 6 ms. Should the supply voltage drop below 10 V, the device ceases operation. Upon the supply returning to above 18 V, the CHOK output turns high again after 6 ms.

Figure 16. CHOK Output Timing as a Function of Supply Voltage Drop at V24

#### 8.4 Device Functional Modes

The 2 functional modes of operation are Load mode and Shift mode.

Load mode enables information from the field inputs to latch into the shift register. To enter load mode, the  $\overline{\text{LD}}$  pin must be held low, and the device remains in load mode regardless of the CLK,  $\overline{\text{CE}}$ , or serial (SIP) input levels. A high level at the  $\overline{\text{LD}}$  pin switches the device into Shift mode.

When the device is in Shift mode, a low level at the  $\overline{\text{CE}}$  pin causes the data stored in all registers of the parallel shift register except for the last register, to be serially shifted toward the serial output (SOP) on the rising edge of CLK. The final register in the shift register will be shifted toward the serial output (SOP) on the falling edge of CLK. A high level at the  $\overline{\text{CE}}$  pin inhibits the serial shifting, which is demonstrated in Figure 21. After 8 consecutive CLK cycles, the serial output (SOP) remains at the level of the serial input (SIP) which is internally pulled to logic high. A logic high at the  $\overline{\text{CE}}$  pin is required to signify the end of the serial data output. For of a daisy chained configuration, the serial output (SOP) of the SN65HVS883 can be connected to the serial input (SIP) of a following device, and additional clock cycles are required to shift the additional data out of the chain. The number of consecutive clock cycles will equal 8 times the number of devices in the chain. See Figure 22 for an example of a cascaded chain of 4x SN65HVS883.

# 9 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

#### 9.1.1 System-Level EMC

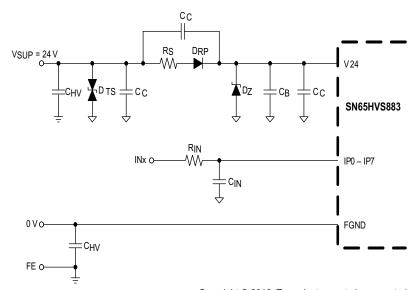

The SN65HVS883 must operate reliably in harsh industrial environments. At a system level, the device is tested according to several international electromagnetic compatibility (EMC) standards.

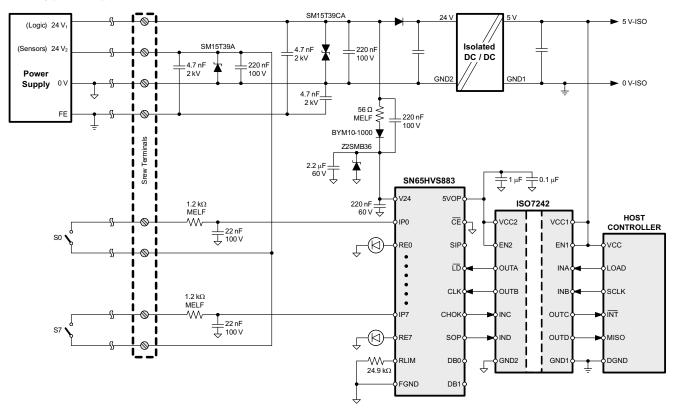

In addition to the device internal ESD structures, external protection circuitry, such as the one in Figure 17, can be used to absorb as much energy from burst- and surge-transients as possible.

Copyright © 2016, Texas Instruments Incorporated

Figure 17. Typical EMC Protection Circuitry for Supply and Signal Inputs

**Table 3. Components**

| DESIGNATOR      | DESCRIPTION                                                       |  |  |  |  |

|-----------------|-------------------------------------------------------------------|--|--|--|--|

| D <sub>TS</sub> | 39 V Transient Voltage Suppressor: SM15T39CA                      |  |  |  |  |

| D <sub>RP</sub> | Super Rectifier: BYM10-1000, or General Purpose rectifier: 1N4007 |  |  |  |  |

| $D_Z$           | 33 V – 36 V fast Zener Diode, Z2SMB36                             |  |  |  |  |

| R <sub>S</sub>  | 56 $\Omega$ , 1/3 W MELF Resistor                                 |  |  |  |  |

| R <sub>IN</sub> | 1.2 kΩ, 1/4 W MELF Resistor                                       |  |  |  |  |

| C <sub>IN</sub> | 22 nF, 60 V Ceramic Capacitor                                     |  |  |  |  |

| $C_HV$          | 4.7 nF, 2 kV Ceramic Capacitor                                    |  |  |  |  |

| C <sub>C</sub>  | n x 220 nF, 60 V Ceramic Capacitors                               |  |  |  |  |

| C <sub>B</sub>  | 1 μF - 10 μF, 60 V Ceramic Capacitor                              |  |  |  |  |

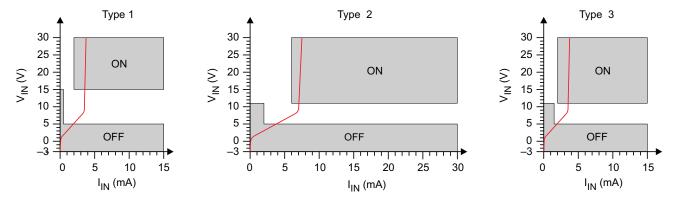

#### 9.1.2 Input Channel Switching Characteristics

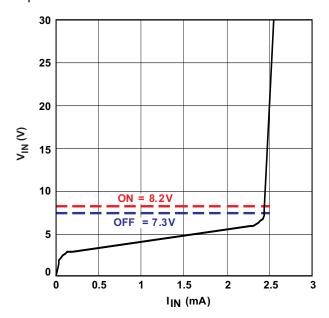

The input stage of the SN65HVS883 is so designed, that for an input resistor  $R_{IN}$  = 1.2 k $\Omega$  the trip point for signalling an ON-condition is at 9.4 V at 3.6 mA. This trip point satisfies the switching requirements of IEC61131-2 Type 1 and Type 3 switches.

Figure 18. Switching Characteristics for IEC61131-2 Type 1, 2, and 3 Proximity Switches

For a Type 2 switch application, two inputs are connected in parallel. The current limiters then add to a total maximum current of 7.2 mA. While the return-path (RE-pin), of one input might be used to drive an indicator LED, the RE-pin of the other input channel should be connected to ground (FGND).

Paralleling input channels reduces the number of available input channels from an octal Type 1 or Type 3 input to a quad Type 2 input device. Note, that in this configuration output data of an input channel is represented by two shift register bits.

Figure 19. Paralleling Two Type 1 or Type 3 Inputs Into One Type 2 Input

www.ti.com

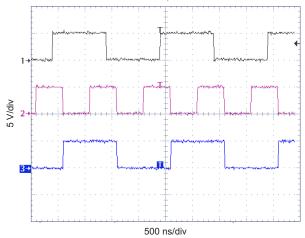

#### 9.1.3 Digital Interface Timing

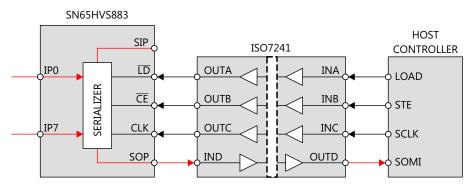

The digital interface of the SN65HVS883 is SPI compatible and interfaces, isolated or non-isolated, to a wide variety of standard micro controllers.

Figure 20. Simple Isolation of the Shift Register Interface

Upon a low-level at the load input,  $\overline{LD}$ , the information of the field inputs, IP0 to IP7 is latched into the shift register. Taking  $\overline{LD}$  high again blocks the parallel inputs of the shift register from the field inputs. A low-level at the clock-enable input,  $\overline{CE}$ , enables the clock signal, CLK, to serially shift the data to the serial output, SOP. Data is clocked into the shift register at the rising edge of CLK and out of the shift register on the falling edge of CLK. Thus after eight consecutive clock cycles all field input data have been clocked out of the shift register and the information of the serial input, SIP, appears at the serial output, SOP.

The  $\overline{\text{CE}}$  signal should only be transitioned low while the CLK signal is low which ensures that a rising edge of CLK occurs before a falling edge of CLK. This shifts the data into and through the shift register up until the final register before the first bit that was loaded into the final register is shifted out the serial output, SOP. If a falling edge of CLK is seen first following the transition of  $\overline{\text{CE}}$  to low, the final register outputs the first bit, IPO, on the serial output, SOP, before shifting the rest of the bits through the shift register. The previous value of the second to last register prior to the  $\overline{\text{LD}}$  event will then be shifted into the final register on the next rising CLK edge and output on the serial output, SOP, before the next valid bit, IP1, is output on the serial output, SOP. This appears as an erroneous bit in the serial data. Also, depending on how many falling CLK edges were seen before the  $\overline{\text{CE}}$  signal is transitioned back high, the final bit, IP7, may not get shifted out of the shift register.

Figure 21. Interface Timing for Parallel-Load and Serial-Shift Operation of the Shift Register

JAJSCH3 – SEPTEMBER 2016 www.ti.com

# TEXAS INSTRUMENTS

#### 9.1.4 Cascading for High Channel Count Input Modules

Designing high-channel count modules require cascading multiple SN65HVS883 devices. Simply connect the serial output (SOP) of a leading device with the serial input (SIP) of a following device without changing the processor interface.

Figure 22. Cascading Four SN65HVS883 for a 32-Channel Input Module

#### **NOTE**

When daisy-chaining multiple devices, the maximum operating rate (CLK pulse width) may need to be restricted in order to maintain minimum set-up/hold timing relationships between the serial data (SIP/SOP) and the CLK line.

## 9.2 Typical Application

Copyright © 2016, Texas Instruments Incorporated

Figure 23. Typical Digital Input Module Application

www.ti.com JAJSCH3 – SEPTEMBER 2016

#### **Typical Application (continued)**

#### 9.2.1 Design Requirements

The simplified schematic in Figure 23 demonstrates a typical application of the SN65HVS883 for sensing the state of digital switches with 24-V high logic levels. In this application, a 5-V host controller must receive the state of 8 switches as a serial input, while remaining isolated from the high voltage power supply.

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Input Stage

Selection of the current limiting resistor R<sub>LIM</sub> sets the input current limit I<sub>LIM</sub> for the device. *Digital Inputs* includes necessary equations for choosing the limiting resistor.

The On/Off voltage thresholds at the device pin  $V_{TH(IP+)}$  and  $V_{TH(IP+)}$  are fixed to 5.2 V and 4.3 V respectively, however the On/Off voltage thresholds of the field input  $V_{TH(IN+)}$  and  $V_{TH(IN+)}$  are determined by the value of the series resistor RIN placed between the field input and the device. The threshold voltage  $V_{TH(IN+)}$  is determined with the following equation:

$$V_{TH(IN+)} = I_{IN} \times R_{IN} + V_{TH(IP+)}$$

(3)

Substituting Equation 1 and solving for R<sub>IN</sub> produces an equation for R<sub>IN</sub> given a desired on-threshold.

$$R_{IN} = \frac{(V_{TH(IN+)} - 5.2V) \times R_{LIM}}{90V}$$

(4)

The following equation can be used to calculate the off-threshold voltage given a value for R<sub>IN</sub>

$$V_{\text{TH(IN-)}} = \frac{90V \times R_{\text{IN}}}{R_{\text{LIM}}} + V_{\text{TH(IP-)}}$$

(5)

Figure 24 contains an example input characteristic:

Figure 24. SN65HVS883 Example Input Characteristic

# TEXAS INSTRUMENTS

# **Typical Application (continued)**

#### 9.2.2.2 Setting Debounce Time

The logic signals at the DB0 and DB1 pins determine the denounce times for the device according to the table in section 6.5. The DB0 and DB1 pins are internally pulled high. Connecting the pins to GND in different configurations allows for selection of 0, 1, or 3 ms debounce times. In noisy environments, it is recommended that unused DB pins should be connected externally to a 5 V supply.

#### 9.2.2.3 Example: High-Voltage Sensing Application

For the high-voltage sensing application in Figure 23, inputs from each switch (S0-S7) are connected to the 8 parallel inputs (IP0-IP7) of the SN65HVS883 through 1.2 k $\Omega$  MELF resistors. Small capacitors (22 nF) are tied to ground at each input to provide noise protection for the signals. A resistor is added between the R<sub>LIM</sub> pin and GND to provide a device current limit according to the equation I<sub>LIM</sub> = 90 V / R<sub>LIM</sub>. In this example, with a 24.9 k $\Omega$  resistor, the current limit for the device is set to 3.6 mA. LEDs are placed between pins RE0-RE7 to allow for external status observation of the parallel inputs. Finally the SN65HVS883 is connected through a digital isolation device to the host controller to provide galvanic isolation to the external interfaces and to allow for communication between the 5 V SN65HVS883 logic and the 5-V host controller. The host controller manages mode switching and clocking of the SN65HVS883 through the digital isolation device.

#### 9.2.3 Application Curve

The application traces acquired in Figure 25 demonstrates the typical behavior of the SN65HVD883 when in shift mode (Load Pulse Input pulled high and Clock Enable Input pulled low). Channel 1 shows the SIP input, Channel 2 shows the CLK input, and Channel 3 shows the SOP output.

Figure 25. SN65HVS883 Serial Input and Output Timing

www.tij.co.jp

## 10 Power Supply Recommendations

The SN65HVS883 operates within a recommended supply voltage range from 4.5 V to 5.5 V. A 0.1  $\mu$ F or larger capacitor should be placed between V<sub>CC</sub> and ground to improve power supply noise immunity. A current limiting resistor can be used to reduce overall power consumption as described in *Digital Inputs*. The high voltage parallel field inputs can accept voltages ranging from 0 V to 34 V, however all other inputs must remain between 0 V to 5 V. Refer to the *Recommended Operating Conditions* table for more detailed voltage suggestions. High voltage field inputs should be buffered as shown in Figure 23 to improve input noise immunity.

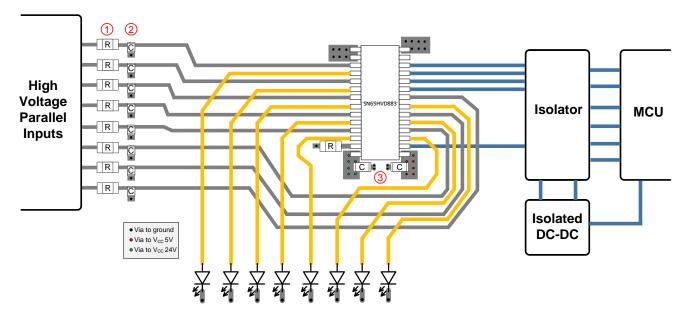

### 11 Layout

#### 11.1 Layout Guidelines

- 1. Place series MELF resistors between the field inputs and the device input pins.

- 2. Place small ~22 nF capacitors close to the field input pins to reduce noise.

- 3. Place a supply buffering 0.1-µF capacitor around as close to the V<sub>CC</sub> pin as possible.

## 11.2 Layout Example

# 12 デバイスおよびドキュメントのサポート

#### 12.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 12.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 12.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.4 商標

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 12.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 12.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins    | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| SN65HVS883PWPR        | Active | Production    | HTSSOP (PWP)   28 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | HVS883           |

| SN65HVS883PWPR.A      | Active | Production    | HTSSOP (PWP)   28 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | HVS883           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated