-

DS110DF111 Low-Power, Multirate, 2-Channel Retimer

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5

Programming

- 7.5.1

SMBus Interface

- 7.5.1.1 Address Lines

- 7.5.1.2 Device Configuration in SMBus Slave Mode

- 7.5.1.3 Bit Fields in the Register Set

- 7.5.1.4 Writing to and Reading From the Control/Shared Registers

- 7.5.1.5 SMBus Strap Observation

- 7.5.1.6 Interrupt Channel Flag Bits

- 7.5.1.7 Control/Shared Register Reset

- 7.5.1.8 Device Revision and Device ID

- 7.5.1.9 Channel Select Register

- 7.5.1.10 Resetting Individual Channels of the Retimer

- 7.5.1.11 Rate and Subrate Setting

- 7.5.1.12 Overriding the CTLE Boost Setting

- 7.5.1.13 Overriding the Output Multiplexer

- 7.5.1.14 Overriding the VCO Divider Selection

- 7.5.1.15 Using the Internal Eye Opening Monitor

- 7.5.1.16 Overriding the DFE Tap Weights and Polarities

- 7.5.1.17 Enabling Slow Rise/Fall Time on the Output Driver

- 7.5.1.18 Using the PRBS Generator

- 7.5.1.19 Inverting the Output Polarity

- 7.5.1.20 Overriding the Figure of Merit Adaption

- 7.5.1.21 Setting the Rate and Subrate for Lock Acquisition

- 7.5.1.22 Setting the Adaption/Lock Mode

- 7.5.1.23 Initiating Adaption

- 7.5.1.24 Overriding the CTLE Settings used for CTLE Adaption

- 7.5.1.25 Setting the Output Differential Voltage

- 7.5.1.26 Setting the Output De-Emphasis Setting

- 7.5.1.27 CTLE Setting for Divide by 4 and Divide by 8 VCO Ranges

- 7.5.1

SMBus Interface

- 7.6 Register Maps

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

DS110DF111 Low-Power, Multirate, 2-Channel Retimer

1 Features

-

Pin-Compatible Retimer Family

- DS110DF111 With DFE: 8.5 to 11.3 Gbps

- DS125DF111 With DFE: 9.8 to 12.5 Gbps

- Adaptive CTLE Up to 34 dB Boost at 5.65 GHz

- Self-Tuning 5-Tap DFE

- Raw Equalized and Retimed Data Loopback

- Adjustable Transmit VOD: 600 to 1300 mVp-p

- Settable TX De-Emphasis Driver 0 to –12 dB

- Low Power Consumption: 200 mW/Channel

- Locks to Half, Quarter, and Eighth Data Rates for Legacy Support

- On-Chip Eye Monitor (EOM), PRBS Generator

- Input Signal Detection, CDR Lock Detection/Indicator

- Single 3.3-V or 2.5-V ±5% Power Supply

- SMBus, EEPROM, or Pin-Based Configuration

- 4.0-mm × 4.0-mm, 24-Pin QFN Package

- Operating Temp Range: –40°C to 85°C

2 Applications

- Front Port Optical Interconnects

- SFF-8431

- 10G/1G Ethernet

- CPRI

3 Description

The DS110DF111 is a dual-channel (1-lane bidirectional) retimer with integrated signal conditioning. The DS110DF111 includes an input Continuous-Time Linear Equalizer (CTLE), clock and data recovery (CDR), and transmit driver on each channel.

The DS110DF111 with its on-chip Decision Feedback Equalizer (DFE) can enhance the reach and robustness of long, lossy, cross-talk-impaired high speed serial links to achieve BER < 1x10-15. For less-demanding applications and interconnects, the DFE can be switched off and achieve the same BER performance. The DS125DF111 and DS110DF111 devices are pin-compatible.

Each channel of the DS110DF111 independently locks to serial data at data rates from 8.5 to 11.3 Gbps or to any supported subrate of these data rates. This simplifies system design and lowers overall cost.

Programmable transmit de-emphasis driver offers precise settings to meet the SFF-8431 output eye template. The fully adaptive receive equalization (CTLE and DFE) enables longer distance transmission in lossy copper interconnect and backplanes with multiple connectors. The CDR function is ideal for use in front port parallel optical module applications to reset the jitter budget and retime high-speed serial data.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| DS110DF111 | WQFN (24) | 4.0 mm × 4.0 mm |

- For all available packages, see the orderable addendum at the end of the datasheet.

Simplified Schematic

4 Revision History

Changes from * Revision (May 2013) to A Revision

- Added Pin Configuration and Functions section, Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section Go

5 Pin Configuration and Functions

Pin Functions

| PIN | TYPE | DESCRIPTION | |

|---|---|---|---|

| NAME | NUMBER | ||

| HIGH SPEED DIFFERENTIAL I/OS | |||

| OUTA± | 7, 8 | O, CML | Inverting and noninverting CML-compatible differential outputs. Outputs require AC coupling |

| OUTB± | 20, 19 | O, CML | Inverting and noninverting CML-compatible differential outputs. Outputs require AC coupling |

| INA± | 24, 23 | I, CML | Inverting and noninverting CML-compatible differential inputs. An on-chip 100 Ohm terminating resistor connects INA+ to INA- Inputs require AC coupling. TI recommends 100 nF capacitors. Note that for SFP+ applications, AC coupling is included as part of the SFP+ module. |

| INB± | 11, 12 | I, CML | Inverting and noninverting CML-compatible differential inputs. An on-chip 100 Ohm terminating resistor connects INB+ to INB- Inputs require AC coupling. TI recommends 100 nF capacitors. Note that for SFP+ applications, AC coupling is included as part of the SFP+ module. |

| LOOP FILTER CONNECTION PIN | |||

| LPF_CP_A, LPF_REF_A | 2, 1 | I/O, analog | Loop filter connection, place a 22 nF capacitor in series between LPF_CP_A and LPF_REF_A |

| LPF_CP_B, LPF_REF_B | 17, 18 | I/O, analog | Loop filter connection, place a 22 nF capacitor in series between LPF_CP_B and LPF_REF_B |

| Reference Clock I/O | |||

| REFCLK_IN | 14 | I, LVCMOS | 25 MHz ±100 ppm clock from external Oscillator |

| INDICATOR PINS | |||

| LOCK | 16 | O, LVCMOS | Goes high when CDR lock is attained on the corresponding channel. Note that this terminal is shared with strap input functions read at startup |

| LOS/INT# | 13 | O, OD | Output is driven LOW when a valid signal is present on CH A. Output is released when signal on CH A is lost (LOS). This output can be redefined as an INT# signal which will be driven LOW if the EOM check returns a value below the HEO/VEO interrupt threshold(2) |

| SMBus MODE PINS | |||

| ENSMB | 3 | I, 4-Level | System Management Bus (SMBus) enable terminal HIGH = Register Access, SMBus Slave mode FLOAT = SMBus Master read from External EEPROM LOW = External Pin Control Mode |

| SDA | 4 | I, SMBus O, OD |

Data Input / Open Drain Output External pull-up resistor is required. Terminal is 3.3 V LVCMOS tolerant(3) |

| SCL | 5 | I, SMBus O, OD |

Clock input in SMBus slave mode. Can also be an open drain output in SMBus master mode Pin is 3.3 V LVCMOS Tolerant(3) |

| TX_DIS | 6 | I, 4-Level | Disable the OUTB transmitter HIGH = OUTA Enabled/OUTB Disabled FLOAT = Reserved 20K to GND = Reserved LOW = OUTA/OUTB Enabled (normal operation) |

| ADDR0 | 16 | I, LVCMOS | This pin sets the SMBus address for the retimer. This pin is a strap input. The state is read on power-up to set the SMBus address in SMBus control mode(3) |

| ADDR1/DONE# | 10 | IO, LVCMOS | This pin sets the SMBus address for the retimer in SMBus Slave Mode. Goes low to indicate that the SMBus master EEPROM read has been completed in SMBus Master Mode(3) |

| READEN# | 9 | I, 4-Level | Initiates SMBus master EEPROM read. When multiple DS110DS111 are connected to a single EEPROM, the READEN# input can be daisy chained to the DONE# output. In SMBus Slave Mode, pull low to Logic 0 proper register operation(3) |

| PIN CONTROL (ENSMB = LOW)(1) | |||

| DEMA | 4 | I, 4-Level | Set CHA output de-emphasis level in pin control mode(3) |

| DEMB | 5 | I, 4-Level | Set CHB output de-emphasis level in pin control mode(3) |

| LBK | 6 | I, 4-Level | HIGH = INA goes to OUTA, INB goes to OUTB FLOAT = INB goes to OUTA and OUTB 20K to GND = INA goes to OUTA and OUTB LOW = INA goes to OUTB, INB goes to OUTA(3) |

| VODA | 9 | I, 4-Level | Set CHA output launch amplitude in pin control mode(3) |

| VODB | 10 | I, 4-Level | Set CHB output launch amplitude in pin control mode(3) |

| POWER | |||

| VDD | 21, 22 | Power | VDD = 2.5 V ±5% 3.3 V Mode Operation: VDD Supply Output = 2.5 V ±5% 2.5 V Mode Operation: VDD Supply Input = 2.5 V ±5% |

| VIN | 15 | Power | Regulator Input with Integrated Supply Mode Control 3.3 V Mode Operation: VIN Supply Input = 3.3 V ±10% 2.5 V Mode Operation: VIN Supply Input = 2.5 V ±5% |

| DAP | PAD | Power | Ground reference The exposed pad at the center of the package must be connected to ground plane of the board with at least 4 vias to lower the ground impedance and improve the thermal performance of the package |

6 Specifications

6.1 Absolute Maximum Ratings(1)

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Supply Voltage (VDD) | –0.5 | +2.75 | V | ||

| Supply Voltage (VIN) | –0.5 | +4.0 | V | ||

| LVCMOS Input/Output Voltage | –0.5 | +4.0 | V | ||

| 4-Level Input Voltage (2.5 V mode) | –0.5 | +2.75 | V | ||

| 4-Level Input Voltage (3.3 V mode) | –0.5 | 4.0 | V | ||

| SMBus Input/Output Voltage | –0.5 | 4.0 | V | ||

| CML Input Voltage | –0.5 | VDD + 0.5 | V | ||

| CML Input Current | –30 | +30 | mA | ||

| Storage Temperature Tstg | –40 | +125 | °C | ||

6.2 ESD Ratings

| VALUE | UNIT | ||

|---|---|---|---|

| ESD Rating(1) | HBM, STD - JESD22-A114F(2) | ±2500 | V |

| CDM, STD - JESD22-C101-D(3) | ±1000 | V | |

6.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| Supply Voltage | 2.5 V Mode | 2.375 | 2.5 | 2.625 | V |

| 3.3 V Mode | 3.0 | 3.3 | 3.6 | ||

| Ambient Temperature | –40 | 25 | +85 | °C | |

| SMBus (SDA, SCL) | 3.0 | 3.3 | 3.6 | V | |

6.4 Thermal Information

| THERMAL METRIC(1) | DS110DF111 | UNIT | |

|---|---|---|---|

| WQFN (RTW) | |||

| 24 PINS | |||

| θJA | Junction-to-ambient thermal resistance | 35.0 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 34.0 | °C/W |

| RθJB | Junction-to-board thermal resistance | 13.4 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.3 | °C/W |

| ψJB | Junction-to-board characterization parameter | 13.4 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 3.3 | °C/W |

6.5 Electrical Characteristics

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| R_baud | Input baud rate | Full Rate: DS110DF111 | 8.5 | 11.3 | Gbps | |

| FSDC | SMBus Clock Rate | Slave Mode Clock Rate | 100 | 400 | kHz | |

| Master Mode Clock Rate | 280 | 400 | 520 | |||

| REFCLK | Clock Rate | ± 100 ppm | 25.0 | MHz | ||

| POWER SUPPLY CURRENT | ||||||

| IDD | Current Consumption (Whole Device) |

11.3 Gbps : DS110DF111 | 170 | mA | ||

| 11.3 Gbps : DS110DF111 DFE Disabled |

150 | mA | ||||

| Maximum Transient Supply Current Default Settings: CHA and CHB valid input signal detected CHA and CHB acquiring LOCK |

235 | 300 | mA | |||

| NTps | Supply Noise Tolerance | 50 Hz to 100 Hz | 100 | mVp-p | ||

| 100 Hz to 10 MHz | 40 | mVp-p | ||||

| 10 MHz to 5.0 GHz | 10 | mVp-p | ||||

| LVCMOS (LBK, READEN#, DONE#, LOCK) | ||||||

| VIH | High level input voltage | 2.5 V or 3.3 V Supply Modes | 1.7 | VIN | V | |

| VIL | Low level input voltage | 2.5 V or 3.3 V Supply Modes | 0.7 | |||

| VOH | High level output voltage | IOH = –3 mA | 2.0 | VIN | V | |

| VOL | Low level output voltage | IOL = 3 mA | 0.4 | |||

| IIN | Input leakage current | VINPUT = GND or VIN | –15 | +15 | μA | |

| 4-LEVEL INPUTS (ENSMB, DEMA, DEMB, TX_DIS, VODA, VODB) | ||||||

| IIN-R | Input leakage current | VINPUT = GND or VIN | –160 | +80 | μA | |

| OPEN DRAIN (LOS/INT#) | ||||||

| VOL | Low level output voltage | IOL = 3 mA | 0.4 | V | ||

| SIGNAL DETECT | ||||||

| SDH | Signal Detect: ON Threshold Level |

Default level to assert Signal Detect, 10.3125 Gbps |

20 | mVp-p | ||

| SDL | Signal Detect: OFF Threshold Level |

Default level to de-assert Signal Detect, 10.3125 Gbps |

15 | mVp-p | ||

| CML RX INPUTS | ||||||

| R_Rd | DC Input differential Resistance | 100 | Ω | |||

| RLRX-IN | Input Return-Loss | SDD11 10 MHz | –19 | dB | ||

| SDD11 2.0 GHz | –14 | |||||

| SDD11 6.0 - 11.1 GHz | –8 | |||||

| VRX-LAUNCH | Source Transmit Signal Level | 600 | 1600 | mVp-p | ||

| CML TX OUTPUTS | ||||||

| T_VDIFF0 | Output differential voltage | Default setting, PRBS31 | 400 | 550 | 675 | mVp-p |

| T_VDIFF7 | Output differential voltage | Maximum setting, PRBS31 Requires SMBus Control |

1000 | 1250 | mVp-p | |

| VOD_DE | De-emphasis Level | Maximum setting, VOD and DE Requires SMBus Control Input: 10.3125Gbps, 64T pattern |

–12 | dB | ||

| T_Rd | DC Output Differential Resistance | 100 | Ω | |||

| TR/TF | Output Rise/Fall Time | Full Slew Rate 20% - 80% Input: 10.3125 Gbps, 8T Pattern |

36 | ps | ||

| TRS/TFS | Output Rise/Fall Time | Limited Slew Rate (Reg 0x18) 20% - 80% Input: 10.3125 Gbps, 8T Pattern |

50 | ps | ||

| TSDD22 | Output differential mode return loss | SDD22 10 MHz - 2 GHz | –19 | dB | ||

| SDD22 5.5GHz | –15 | |||||

| SDD22 11.1GHz | –11 | |||||

| TPD | Propagation Delay | Retimed Data 10.3125 Gbps | 350 | ps | ||

| TPD-RAW | Propagation Delay | Raw Data | 200 | ps | ||

| TRANSMIT JITTER SPECS(1) | ||||||

| TTJ | Total Jitter (1E-12) | PRBS7, 10.3125 Gbps | 7.5 | ps | ||

| TRJ | Random Jitter | PRBS7, 10.3125 Gbps | 0.33 | ps (RMS) | ||

| TDJ | Deterministic Jitter | PRBS7, 10.3125 Gbps | 3.6 | ps | ||

| CLOCK AND DATA RECOVERY | ||||||

| BWPLL | PLL Bandwidth –3 dB | Measured at 10.3125 Gbps | 5 | MHz | ||

| JTOL | Total jitter tolerance | Jitter per SFF-8431 Appendix D.11 Combination of Dj, Pj, and Rj |

> 0.70 | UI | ||

| TLOCK1 | CDR Lock Time | Standards Based(2) | 10 - 30 | ms | ||

| TEMPLOCK | CDR Lock | Lock Temperature Range –40°C to 85°C operating range |

125 | °C | ||

| SERIAL BUS INTERFACE CHARACTERISTICS(3) | ||||||

| VIL | Data, Clock Input Low Voltage (SDA / SCL) |

0.8 | V | |||

| VIH | Data, Clock Input High Voltage (SDA / SCL) |

2.1 | 3.6 | V | ||

| VHY | Input Hystersis | >50 | mV | |||

| VOL | Output Low Voltage | SDA or SCL, IOL = 1.25 mA | 0 | 0.36 | V | |

| IIN | Input Current | SDA or SCL, VINPUT = VIN, VDD, GND | –15 | +15 | μA | |

| TR | SDA Rise Time, Read Operation | SDA, RPU = 10K, Cb < 400 pF | 430 | ns | ||

| TF | SDA Fall Time, Read Operation | SDA, RPU = 10K, Cb < 400 pF | 20 | ns | ||

| TSU;DAT | Setup Time, Read Operation | 560 | ns | |||

| THD;DAT | Hold Time, Read Operation | 615 | ns | |||

| TSP | Input Filter | 50 | ns | |||

| CIN | Input Capacitance | SDA or SCL | < 5 | pF | ||

| RECOMMENDED TIMING FOR THE SERIAL BUS INTERFACE | ||||||

| FSCL | SCL Clock Frequency | 400 | kHz | |||

| TLOW | SCL Low Period | 1300 | ns | |||

| THIGH | SCL High Period | 600 | ns | |||

| THD;STA | Hold Time, Start Operation | 600 | ns | |||

| TSU;STA | Setup Time, Start Operation | 600 | ns | |||

| THD;DAT | Data Hold Time | 0 | 900 | ns | ||

| TSU;DAT | Data Set Up Time | 100 | ns | |||

| TSU;STO | Set Up Time, Stop Condition | 600 | ns | |||

| TBUF | Bus Free Time Between Stop - Start |

1300 | ns | |||

| TF | SCL and SDA, Fall Time | 300 | ns | |||

| TR | SCL and SDA, Rise Time | 1000 | ns | |||

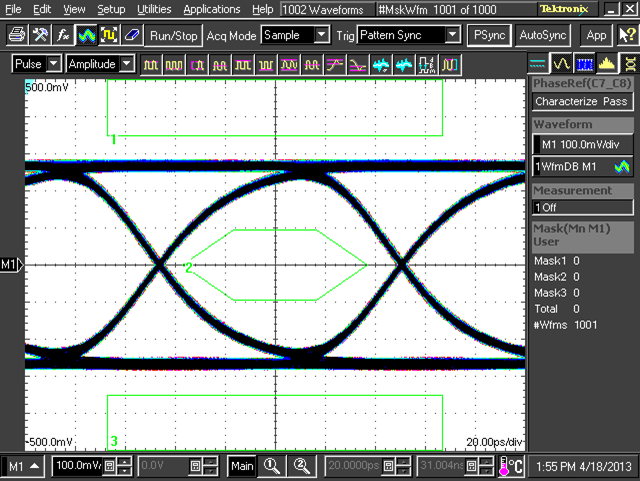

Figure 1. Output Edge Rate

Figure 1. Output Edge Rate

Figure 2. Propagation Delay

Figure 2. Propagation Delay

Figure 3. SMBus Timing Diagram

Figure 3. SMBus Timing Diagram

6.6 Typical Characteristics

| Test Conditions | ||

| Datarate: 10.3125 Gbps with a PRBS7 pattern | ||

| VOD Setting: 1000mV | ||

| Temperature: 25°C and VDD = 2.5V |

| Jitter Measurements | ||

| Rj (RMS): 315 fs | Dj: 3.74 ps | Tj (1E-12): 7.33 ps |