*Errata***AWR2544 器件勘误表****内容**

|                  |    |

|------------------|----|

| 1 简介             | 2  |

| 2 器件命名规则         | 2  |

| 3 器件标识           | 3  |

| 4 器件型号/修订版对应关系公告 | 4  |

| 5 功能规范的已知设计异常    | 5  |

| 6 修订历史记录         | 40 |

## 1 简介

本文档介绍了德州仪器 (TI) CMOS 雷达器件 (AWR2544) 的功能和性能规范的已知异常

## 2 器件命名规则

为了标示所处的产品开发周期阶段，德州仪器 (TI) 为所有雷达/毫米波传感器器件的零件号分配了前缀。每个雷达器件具有以下两种前缀之一：XA<sub>x</sub> 或 AWR2<sub>x</sub> (例如：XA2E44BGALTX)。这些前缀代表了产品开发的发展阶段，即从工程原型 (XA<sub>x</sub>) 直到完全合格的生产器件 (AWR2<sub>x</sub>)。

器件开发进化流程：

**XA<sub>x</sub>** — 试验器件不一定代表最终器件的电气规格，并且可能不使用生产封装流程。

**AWR2<sub>x</sub>** — 完全合格的器件芯片量产版本。

XA<sub>x</sub> 器件在供货时附带如下免责声明：

“开发中的产品用于内部评估用途。”

由于这些器件的预期最终使用故障率仍未确定，德州仪器 (TI) 建议不要将这些器件用于任何生产系统。

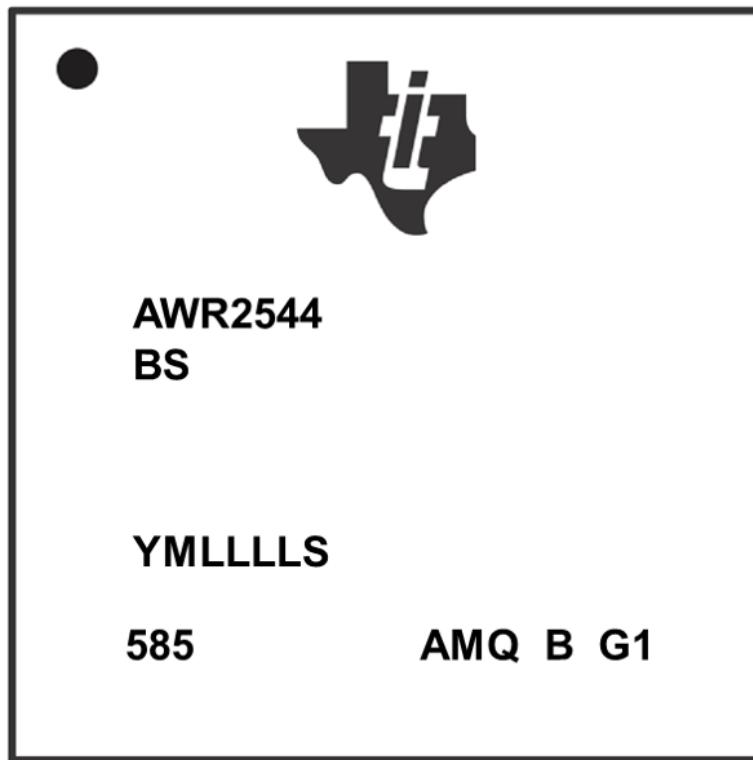

### 3 器件标识

图 3-1 展示了 AWR2544 雷达器件的封装符号示例。

图 3-1. 器件产品标识示例

此标识编号包含以下信息：

- 第 1 行：器件型号

- 第 2 行：安全级别和安全等级

- 第 3 行：批次追踪代码

- YM = 年/月日期代码

- Z = 次要产地代码

- LLLL = 组装批次代码

- S = 主站点代码

- 第 4 行：

- 585 = 器件标识符

- AMQ = 封装标识符

- G1 = “绿色”封装版本 ( 必须带下划线 )

## 4 器件型号/修订版对应关系公告

表 4-1. 器件型号/修订版对应关系

| 公告编号                    | 公告标题                                                                     | AWR2544 |

|-------------------------|--------------------------------------------------------------------------|---------|

| <b>主子系统</b>             |                                                                          |         |

| <a href="#">MSS#25</a>  | 系统复位时调试器可能在内存浏览器窗口显示不可预测的数据                                              | X       |

| <a href="#">MSS#27</a>  | 在慢速 SPICLK 频率和时钟相位 = 1 的情况下，外设模式 MibSPI 的 3 或 4 引脚通信传输数据不正确              | X       |

| <a href="#">MSS#28</a>  | 启用 IO 环回时，外设模式下反复生成数据长度错误                                                | X       |

| <a href="#">MSS#29</a>  | 外设模式 MibSPI 的虚假 RX DMA REQ                                               | X       |

| <a href="#">MSS#30</a>  | 读取后 MibSPI RX RAM RXEMPTY 位不清除                                           | X       |

| <a href="#">MSS#33</a>  | DIAG 模式下无法正确读取 MibSPI RAM ECC                                            | X       |

| <a href="#">MSS#40</a>  | 所有跨硬件加速器的 ACCEL_MEM1 和 ACCEL_MEM2 内存的 EDMA 传输均有可能导致数据损坏，而 SoC 不会发出任何错误通知 | X       |

| <a href="#">MSS#49</a>  | 在 Aurora 64B/66B 协议中，在溢出消息传输期间，支持严格对齐用户流控制剥离的接收器的潜在互操作性可能存在问题            | X       |

| <a href="#">MSS#52</a>  | DSS L2 奇偶校验问题：当 DSP 发送超出配置的内存大小的访问时                                      | X       |

| <a href="#">MSS#53</a>  | 在 HWA 2.0 中的最后一个参数集发生上下文切换时会出现错误行为                                       | X       |

| <a href="#">MSS#54</a>  | Aurora TX UDP 大小 <= 4 时无效                                                | X       |

| <a href="#">MSS#55</a>  | 不支持线性调频脉冲间阶梯模式下的 PMIC CLKOUT 抖动                                          | X       |

| <a href="#">MSS#56</a>  | CR4 STC 引导监控器故障                                                          | X       |

| <a href="#">MSS#57</a>  | 在 MDO 接口上，执行 Flush/Marker 操作时或数据包传输完成后，观察到数据丢失现象。                        | X       |

| <a href="#">MSS#58</a>  | ePWM：斩波运行模式期间存在干扰                                                        | X       |

| <a href="#">MSS#59</a>  | CRC：不支持 CRC 8 位数据宽度以及 CRC8-SAE-J1850 和 CRC8-H2F 在 CAN 模块中的潜在用途           | X       |

| <a href="#">MSS#60</a>  | PCR 的 6 个内部寄存器存在读写地址不匹配问题                                                | X       |

| <a href="#">MSS#61</a>  | 当对配置的 MPU 区域的最后 24 个字节进行访问并启用缓存时，出现数据中止                                  | X       |

| <a href="#">MSS#62</a>  | 连续使用 FFT3X 参数集时，出现 HWA 挂起                                                | X       |

| <a href="#">MSS#63</a>  | 块一致性操作期间可能出现 L2 缓存损坏问题                                                   | X       |

| <a href="#">MSS#64</a>  | 单条 MFENCE 指令问题                                                           | X       |

| <a href="#">MSS#65</a>  | 块和全局一致性操作期间的 L2 缓存损坏问题                                                   | X       |

| <a href="#">MSS#68</a>  | HWA 的 Real2X FFT 模式下，第 0 个 BCNT 的 FFT 数据可能损坏                             | X       |

| <a href="#">MSS#71</a>  | 单比特 ECC ( 错误校正 ) 机制可能会导致内存更新错误                                           | X       |

| <b>模拟/毫米波</b>           |                                                                          |         |

| <a href="#">ANA#12A</a> | 接收器中存在二次谐波 (HD2)                                                         | X       |

| <a href="#">ANA#37A</a> | 在本振频率范围内 RX 增益大幅下降                                                       | X       |

| <a href="#">ANA#39</a>  | HPF 截止频率 2800kHz 配置可能会导致不正确的 RX IFA 增益和滤波器转角频率                           | X       |

| <a href="#">ANA#43</a>  | 合成器频率实时监控中出现错误                                                           | X       |

| <a href="#">ANA#44</a>  | 在 3.3V IO 模式下，观察到 1.8V 电源轨存在来自 3.3V 电源轨的反向供电                             | X       |

| <a href="#">ANA#45</a>  | 数字活动导致的杂散信号                                                              | X       |

| <a href="#">ANA#47</a>  | 空闲信道场景下，各 RX 均观察到 RX 杂散信号                                                | X       |

| <a href="#">ANA#59</a>  | OSC_CLK_OUT_ETH 活动导致的杂散信号                                                | X       |

## 5 功能规范的已知设计异常

### MSS#25

系统复位时调试器可能在内存浏览器窗口显示不可预测的数据

受影响的修订版：

AWR2544

说明：

如果在调试器使用系统视图对系统资源执行访问时发生系统复位 ( nRST 变为低电平 )，则应向调试器回复外设错误。如果访问是读取操作，则响应可能错误地指示访问成功并返回不可预测的数据。

在以下情况下会发生该问题：当调试器正通过系统视图完成对系统的一次访问操作时，系统复位信号 ( nRST 为低电平 ) 恰好在某个特定周期有效。例如，当调试器 ( 如 CCS-IDE 内存浏览器窗口 ) 通过系统视图刷新内容时。仅 CPU 复位时无此问题，上电复位 (nPORRST) 期间也无此问题。

权变措施：

避免在器件可能处于复位状态时执行调试读写操作。

**MSS#27**

在慢速 **SPICLK** 频率和时钟相位 = 1 的情况下，外设模式 **MibSPI** 的 3 或 4 引脚通信传输数据不正确

## 受影响的修订版：

AWR2544

## 说明：

MibSPI 模块通过 3 个功能引脚 (CLK、SIMO、SOMI) 或 4 个功能引脚 (CLK、SIMO、SOMI、nENA) 配置为多缓冲外设模式时，可能在满足以下所有条件时发送不正确的数据：

- MibSPI 模块配置为多缓冲模式，

- 模块配置为 SPI 通信中的外设，

- SPI 通信配置为 3 引脚模式或 4 引脚模式 ( 通过 nENA ) ，

- SPICLK 的时钟相位为 1，并且

- SPICLK 频率为 MSS\_VCLK 频率 / 12 或更低

## 权变措施：

可以通过设置 TX RAM ( 多缓冲区 RAM 传输数据寄存器 ) 控制字段中的 CSHOLD 位来避免该问题。在该通信中 nCS 不用作功能信号；因此，设置 CSHOLD 位不会对 SPI 通信造成任何其他影响。

**MSS#28**

启用 IO 环回时，外设模式下反复生成数据长度错误

受影响的修订版：

AWR2544

说明：

在 SPI 的外设模式下使用 nSCS 引脚在 IO 环回测试模式下生成 DLEN 错误时，SPI 模块重新传输包含 DLEN 错误的数据，而非中止正在进行的传输并停止。这只是模拟环回配置中 IOLPBK 模式外设的问题，在使用 CTRLDLENERR (IOLPBKTSTCR.16) 触发有意的错误生成功能时出现。

权变措施：

在 IOLPBK 模式中检测到 DLEN\_ERR 中断后，清除 SPIGCR1 寄存器中的 SPIEN ( 位 24 ) 禁用传输，然后复位 SPIEN 位重新启用传输。

**MSS#29****外设模式 MibSPI 的虚假 RX DMA REQ****受影响的修订版：**

AWR2544

**说明：**

即便 SPI 外设未按以下条件序列传输数据，仍有可能生成虚假的 DMA 请求：

- MIBSPI 在标准（非多缓冲）SPI 模式下配置为外设

- 将 DMAREQEN 位 (SPIINT0.16) 设置为启用 DMA 请求

- 芯片选择 (nSCS) 引脚处于活动状态，但传输未处于活动状态

- 将 SPIEN (SPIGCR1.24) 位从“1”清除为“0”来禁用 SPI

SPIEN 位从“1”清除为“0”后，以上序列在接收 DMA 请求时触发错误的请求脉冲。

**权变措施：**

每当通过清除 SPIEN 位 (SPIGCR1.24) 禁用 SPI 时，先将 DMAREQEN 位 (SPIINT0.16) 清除为“0”，然后再清除 SPIEN 位。

**MSS#30**

读取后 **MibSPI RX RAM RXEMPTY 位不清除**

受影响的修订版：

AWR2544

说明：

满足以下条件时，CPU 或 DMA 读取后 RXEMPTY 标志可能不自动清除：

- 序列器从当前活动传输组的发送 RAM 中读取的最新缓冲区 TXFULL 标志为 0，

- 较高优先级的传输组中断当前传输组，序列器开始读取发送 RAM 新传输组的第一个缓冲区，以及

- 同时，主机 (CPU/DMA) 读取接收 RAM 位置，其中包含先前传输的有效接收数据。

权变措施：

避免传输组之间相互中断。

如果较低优先级传输组中使用虚拟缓冲区，为虚拟缓冲区选择适当的“BUFMODE”（例如跳过/禁用），根据特定需求使用“暂停”模式的情况除外。

**MSS#33*****DIAG 模式下无法正确读取 MibSPI RAM ECC***

受影响的修订版：

AWR2544

说明：

如果实施扩展缓冲区支持，但针对特定 MibSPI 实例禁用扩展模式，则在 **DIAG** 模式下对 MibSPI RAM 的 ECC 地址空间的读取操作不会返回前 128 个缓冲区的正确 ECC 值。

权变措施：

无

**MSS#40**

所有跨硬件加速器的 ACCEL\_MEM1 和 ACCEL\_MEM2 内存的 EDMA 传输均有可能导致数据损坏，而 SoC 不会发出任何错误通知

**受影响的修订版：**

AWR2544

**说明：**

根据 TPTC IP 规范，传输请求 (TR) 应访问单个外设端点。HWA 的 ACCEL\_MEM0/ACCEL\_MEM1 内存库可通过单个外设点使用，HWA 的 ACCEL\_MEM2/ACCEL\_MEM3 内存库可用作另一个外设点（不同于 ACCEL\_MEM0/ACCEL\_MEM1）使用。因此，如果使用单个 TR 访问跨 HWA ACCEL\_MEM1 和 ACCEL\_MEM2 内存的缓冲器（即跨 2 个不同外设点的单个缓冲器），不符合规范的要求。本勘误表明确强调该规范要求。

**备注**

在 SoC 层面，ACCEL\_MEM1 和 ACCEL\_MEM2 内存分别称为 DSS\_HWA\_DMA0 和 DSS\_HWA\_DMA1。

**权变措施：**

将访问拆分为 2 个 TR，避免单个 TR 跨越 ACCEL\_MEM1 + ACCEL\_MEM2。可以将 2 个 TR 连接起来。

**MSS#49**

在 Aurora 64B/66B 协议中，在溢出消息传输期间，支持严格对齐用户流控制剥离的接收器的潜在互操作性可能存在问题。

**受影响版本**

AWR2544

**详细信息**

测量数据输出 (MDO) 用于捕获器件不同接口连接的总线上的事务并通过 Aurora LVDS 接口 (4 个数据信道) 在外部进行传输。MDO 由监听器、FIFO 和聚合器组成。MDO 监听器模块负责监控芯片中的硬件接口并捕获总线上配置目标寻址区域内的事务。

监听器上可能因溢出导致数据丢失。溢出信息作为中断发送至 CPU 和 Aurora Tx IP。如果出现数据溢出情况，Aurora TX IP 生成用户流控制 (UFC) 数据包，以便将此错误情况通知用户。这是一个错误场景，预计不会在正常传输功能中发生。在此阶段，数据完整性已经受到损害。

Aurora IP 仅支持根据 Aurora 64B/66B 协议规范第 6.6 节生成 UFC 数据包，即 UFC 报头块位于 UFC 数据块之前。目前不支持严格对齐用户流控制剥离 (请参阅 Aurora 64B/66B 协议规范第 6.7 节)。

**权变措施**

对于 MDO，输入数据速率应小于输出数据速率，以确保有效数据速率处于合理范围内，从而完全避免溢出情况。

**备注**

对于 Aurora 64B/66B 协议，不建议使用

`TOP_AURORA_TX:AURORA_TX_UFC_MSG_REQ` 寄存器来发送 UFC 数据包，否则可能发生溢出。

**MSS#52**

**DSS L2 奇偶校验问题：当 DSP 发送超出配置的内存大小的访问时**

**受影响的修订版：**

AWR2544

**说明：**

DSP IP 发出对其 L2 存储器的访问，访问超出配置的 DSP L2 内存大小 384KB ( 保留空间访问 )，即超过 0x8085 FFFC。

如果启用奇偶校验，读取超过 0x80860000 -0x8087FFFC 的保留位置时会出现 L2 奇偶校验错误

**备注**

0x80860000 到 0x8087FFFC 的保留存储器位置可以读取和写入。0x80860000 到 0x8087FFFC 的存储器位置在 0x80840000 到 0x8085FFFC 赋予别名，而 0x80850000 到 0x8085FFFC 在 0x80870000 到 0x8087FFFC 复制，因此实际 L2RAM 仅为 384KB。

**权变措施：**

**配置 MPU：(L2MPPA24 - L2MPPA31) 设置为 0。**

可阻止对保留空间的写入访问。无别名且无 L2 奇偶校验错误。这可确保有效 L2 区域的数据完整性。

对保留空间的读取访问仍会导致 L2 奇偶校验错误 ( 如果启用奇偶校验 )。

不阻止调试访问 ( 读取和写入 )：仍然导致别名 + L2 奇偶校验错误：即便将 MPPA 寄存器配置为启用保护，阻止调试访问仍不可行

存储器保护故障地址寄存器 (0184 A000h:: L2MPFAR/0184 AC00h:: L1DMPFAR) 中填充阻止 ( 本例中超出 384KB 边界 ) 但仍被访问的地址

下次读取时，需要使用值为 1 的清除寄存器 (L2MPFCR/L1DMPFCR) 清除地址 (L2MPFSR/L1DMPFSR) 和状态 (L2MPFSR/L1DMPFSR) 寄存器

观察结果 ( 启用/禁用 L1D 缓存时 )

读取：在 L1D 上观察到 MPU 保护错误，其中 L1MPFAR 寄存器填充阻止的地址访问

写入：在 L2 上观察到 MPU 保护错误，其中 L2MPFAR 寄存器填充阻止的地址访问

**MSS#53****在硬件加速器 (HWA 2.1) 中的最后一个参数集发生上下文切换时出现错误行为****受影响的修订版：**

仅限 AWR2544

**说明：**

在低优先级上下文的最后一个循环的最后一个参数集结束时，若发生向高优先级的上下文切换，则返回低优先级时会出现异常行为。这种错误行为可能表现为低优先级循环完成后，（意外）重新启动。错误条件如下：

- 在低优先级线程的最后一个参数集中设置了 CONTEXT\_SW\_EN 或 FORCED\_CONTEXT\_SW\_EN。

同理，在高优先级线程的最后一个参数集中不应启用强制上下文切换 (FORCED\_CONTEXT\_SW\_EN)。

**权变措施：**

建议不要在上述条件的最后一个参数集中启用上下文切换。如果最后一个参数集必须启用上下文切换，用户可添加一个禁用上下文切换的虚拟参数集作为最后一个参数集。

**MSS#54**

***Aurora TX UDP 大小 <= 4 时无效***

---

受影响的版本：

AWR2544

说明：

传输期间，Aurora TX UDP 大小 <= 4 时无效。

Aurora 8b/10b 和 Aurora 64b/66b 的有效 UDP 大小为：

1. AURORA\_TX\_UDP\_CONFIG\_PACK\_MODE\_SEL = 0 (字节)：有效的 Udp 大小 - AURORA\_TX\_UDP\_SIZE = 8、12、16、20……

2. AURORA\_TX\_UDP\_CONFIG\_PACK\_MODE\_SEL = 1 (TWP)：有效的 Udp 大小 - AURORA\_TX\_UDP\_SIZE = 5、6、7、8……

权变措施：

建议仅使用上述有效的 UDP 大小。

**MSS#55****不支持线性调频脉冲间阶梯模式下的 PMIC CLKOUT 抖动**

受影响的修订版：

AWR2544

说明：

PMIC CLKOUT 具备向时钟频率添加抖动的选项，以降低时钟杂散的影响。支持连续抖动模式，但不支持线性调频脉冲间阶梯抖动模式。这是因为 DFE 复位未到达 PMIC CLKOUT 块。

权变措施：

建议在 PMIC CLKOUT 中使用连续抖动模式。

**MSS#56****CR4 STC 引导监控器故障****受影响的修订版：**

仅限 AWR2544

**说明：**

在器件中观察到 Cortex CR4 STC 引导监控器故障。

**权变措施：**

建议在次级引导加载程序 (SBL) 中开始 CR4 (BSS) 执行之前执行一个序列 (MSS\_CTRL:MSS\_PBIST\_KEY\_RST[3:0] = 0) 以清除 PBIST 寄存器。请参阅 TI 提供的 SBL 示例代码。

**MSS#57**

在 MDO 接口上，执行 **Flush/Marker** 操作时或数据包传输完成后，观察到数据丢失现象。

## 受影响的修订版：

AWR2544

## 说明：

421-24008：通过 MDO 发送的数据帧会丢弃帧末尾的最后 6 个字节

已观察到：通过 MDO 传输的、数据大小为 6 字节的数据传输会被丢弃。为确保数据完整传输，数据大小需满足 4 字节和 8 字节对齐。如果不满足对齐要求，在触发 **Flush/Marker** 或数据包完成时，可能会丢失最后 6 字节数据。

数据流：EDMA -> SNIFFER -> FIFO --> AGGREGATOR -> STM -> TPIU -> AURORA TX。

使用 **MSS\_TPCC** 向 **MDO\_DSS\_FIFO** 传输 6 字节数据时，该 6 字节会被丢弃。STM 模块包含 **cxstm500\_axislvif\_write** 块，该块根据 **WSTRB** 对数据进行采样。STM 内部无法处理 6 字节的输入数据。

**STM 模块在设计上存在无法处理 6 字节数据的限制。**

1、2、4、8 字节的数据可以得到处理。但 6 字节数据会被丢弃。

## 权变措施：

建议在传输期间包含 2 个虚拟字节，使 **WSTRB** 能够处理 8 个字节。

**MSS#58****ePWM : 斩波运行模式期间存在干扰****受影响的修订版**

AWRL6432 AWR2544

**详细信息**

在斩波模式下运行期间，可能会在来自 ePWM 模块的 ePWMA 和 ePWMB 输出信号上观察到干扰。

**权变措施**

如果用例受到干扰，建议将 LPRADAR:APP\_PWM:PCCTL:CHPEN 寄存器位设置为 0，以禁用 PWM 斩波控制功能。

下表列出了上述权变措施的寄存器地址。

| 位 | 名称                              | 地址          |

|---|---------------------------------|-------------|

| 0 | LPRADAR:APP_PWM:PCCTL:CHP<br>EN | 0X57F7 FC3C |

**MSS#59**

**CRC : 不支持 CRC 8 位数据宽度以及 CRC8-SAE-J1850 和 CRC8-H2F 在 CAN 模块中的潜在用途**

---

**受影响的修订版**

AWR2544

**详细信息**

1. 不支持 8 位数据宽度。支持的最小数据宽度为 16 位。

2. 不支持 CRC 类型 CRC8-SAE-J1850 和 CRC8-H2F。

**权变措施**

1. 支持 16/32/64 位数据宽度。

2. 建议不要使用上述不受支持的多项式。

**MSS#60**

**PCR 的 6 个内部寄存器存在读写地址不匹配问题**

**受影响的修订版**

AWR2544

**详细信息**

以下是器件中所有 PCR 的通用寄存器集及其对应的读取地址偏移和写入地址偏移

| 寄存器        | 写入地址偏移      | 读取地址偏移       |

|------------|-------------|--------------|

| PPROTSET_2 | 0x0000 0028 | 0x0000 002C  |

| PPROTSET_3 | 0x0000 002C | 0x0000 0040  |

| PPROTCLR0  | 0x0000 0040 | 0x0000 0044  |

| PPROTCLR1  | 0x0000 0044 | 0x0000 0048  |

| PPROTCLR2  | 0x0000 0048 | 0x0000 004C  |

| PPROTCLR3  | 0x0000 004C | 0x0000 00260 |

**权变措施**

对这些特定的寄存器组执行任何读取-修改-写入或读回检查时，需使用上述映射关系。

**MSS#61**

当对配置的 **MPU** 区域的最后 24 个字节进行访问并启用缓存时，出现数据中止。

**受影响的修订版**

AWR2544

**详细信息**

当 R5F 访问可缓存区域中的一个字节或字时，缓存的访问长度为 32 字节（一个缓存行大小），起始地址为正在读取的关键字地址。

**MPU**（错误地）假定当前事务的结束地址为“关键字地址 + 32 字节”，并将其与 **MPU** 中已编程的结束地址进行比较。**MPU** 将此判定为访问违规，并使该事务失败（例如： $0x701FFFF8 + 32$  字节 =  $0x7020\ 0018 > 0x70FF\ FFFF$ ）。

如果 **MPU** 区域被标记为不可缓存，则无此问题。

**权变措施**

如果启用了缓存，请勿在 **MPU** 区域的最后 32 字节中放置任何数据。

**MSS#62**

**连续使用 FFT3X 参数集时，出现 HWA 挂起**

**受影响的修订版**

AWR2544

**详细信息**

如果在连续的参数集中，或在循环的首个和最后一个参数集中启用 FFT3X，则 HWA 状态机在执行完第一个 FFT3X 参数集后会挂起，且不触发任何参数完成中断。

**权变措施**

在使用启用 FFT3X 的参数集之前，先使用任何禁用 FFT3X 的参数集（用户也可选用 ACCEL\_MODE = 0b111 的无操作参数集）

**MSS#63****块一致性操作期间可能出现 L2 缓存损坏问题****受影响的修订版：**

AWR2544

**说明：**

在块一致性操作过程中发现了潜在的 L2 缓存损坏问题。在一组特定的情况下，L1D 或 L2 的块一致性操作可能导致 L2 缓存损坏。当同一 L2 组中连续发生以下四个操作时，会引发该问题：

1. L1D 写缺失

2. 因块一致性操作导致的受害者写回

3. 对某个地址的写分配

4. 对某个地址的读分配或写分配

此问题适用于下面列出的所有块一致性操作：

- L1D 写回

- L1D 失效

- L1D 写回并失效

- L2 写回

- L2 失效

- L2 写回并失效

**权变措施：**

此权变措施要求内存系统在块一致性操作期间保持空闲。因此，程序必须等待块一致性操作完成后才能继续执行。这适用于 L1D 和 L2 内存的块一致性操作。要发出块一致性操作，请按照以下顺序操作。

1. 禁用中断。

2. 将起始地址写入相应的 BAR 寄存器。

3. 将字计数写入相应的 WC 寄存器。

4. 通过以下任一方式等待操作完成：

- a. 发出 MFENCE 指令 (首选)。

- b. 轮询 WC 寄存器，直到字计数字段读数为 0。

5. 执行 16 个 NOP。

6. 恢复中断。

有关缓存控制寄存器 (BAR 和 WC) 的更多信息，请参阅《TMS320C66x DSP CorePac 用户指南》(SPRUGW0)。MFENCE 指令是 C66x DSP 的新增指令。该指令会使 DSP 暂停，直至所有未完成的内存操作执行完毕。有关 MFENCE 指令的更多信息，请参阅《C66x DSP 和指令集参考指南》(SPRUGHT)。

## MSS#64

## 块和全局一致性操作期间的 L2 缓存损坏问题

### 受影响的修订版：

AWR2544

### 说明：

在一组特定的情况下，L1D 或 L2 的块和全局一致性操作可能导致 L2 缓存损坏。当同一 L2 组中连续发生以下四个操作时，会引发该问题：

1. L1D 写缺失

2. 因块和全局一致性操作导致的失效或带失效的写回

3. 对某个地址的写分配

4. 对某个地址的读分配或写分配

该问题适用于所有块和全局一致性操作，但以下操作除外：

- L1D 块写回

- L1D 全局写回

- L2 块写回

- L2 全局写回

另请参见：[公告 63 — 块一致性操作期间的潜在 L2 缓存损坏问题](#)

### 权变措施：

#### 通用权变措施：

以下权变措施具有通用性，但可能影响性能。建议客户理解应用场景，然后选择更适合的方案。

#### 权变措施 1：

此权变措施要求内存系统在块和全局一致性操作期间保持空闲状态。因此，程序必须等待块和全局一致性操作完成后才能继续执行。这适用于 L1D 和 L2 内存块以及全局一致性操作。

要发出块一致性操作，请按照以下顺序操作：

1. 禁用中断。

2. 将起始地址写入相应的 BAR 寄存器。

3. 将字计数写入相应的 WC 寄存器

4. 通过以下任一方式等待操作完成：

- a. 发出 MFENCE 指令 (首选)

- b. 轮询 WC 寄存器，直到字计字段读数为 0

5. 执行 16 个 NOP

6. 恢复中断

要发出全局一致性操作，请按照以下顺序操作：

1. 禁用中断。

2. 向相应的全局一致性寄存器 (L1DINV、L1DWBINV、L2DINV 和 L2DWBINV) 写入 1

3. 通过以下任一方式等待操作完成

- a. 发出 MFENCE 指令 (首选)

- b. 轮询相应的全局一致性寄存器 (L1DINV、L1DWBINV、L2DINV 和 L2DWBINV)，直到位 [0] 字段读取为 0

4. 执行 16 个 NOP

5. 恢复中断

**MSS#64 (续)****块和全局一致性操作期间的 L2 缓存损坏问题****权变措施 2：**

此变通办法同样具有通用性，但允许 CPU 事务与缓存一致性操作并行执行。要发出块一致性操作，请按照以下顺序操作：

1. 发出 MFENCE 命令。

2. 冻结 L1D 缓存

3. 启动 L1D WBINV

4. 重新启动 CPU 事务 (CPU 操作与 WBINV 并行执行，无需等待缓存一致性操作完成)

5. 轮询 WC 寄存器，直到字计字段读数为 0。

6. 当字数统计字段读数为 0 时，WBINV 完成

7. 发出 MFENCE 命令。

8. 解冻 L1D 缓存。

有关缓存控制寄存器 (BAR、WC、L1DINV、L1DWBINV、L2DINV 和 L2DWBINV) 的更多信息，请参阅《TMS320C66x DSP CorePac 用户指南》([SPRUGW0](#))。MFENCE 指令是 C66x DSP 的新增指令。该指令会使 DSP 暂停，直至所有未完成的内存操作执行完毕。有关 MFENCE 指令的更多信息，请参阅《C66x DSP 和指令集参考指南》([SPRUGH7](#))。

## MSS#65

### 单条 MFENCE 指令问题

受影响的修订版：

AWR2544

说明：

MFENCE 指令用于暂停指令取指流水线，直至所有 CPU 触发的内存事务完成。

在极特殊情况下，MFENCE 可能允许其后续事务在前面的 STORE 操作完成前执行。

例如，

1. STORE\_A

2. MFENCE

3. TRANSACTION\_B

MFENCE 的实现机制是：暂停 CPU 直至内存系统确认无“进行中”事务，即处于空闲状态。这可防止 CPU 在 STORE\_A 完成之前执行 TRANSACTION\_B。存在一个很小的窗口期：当 STORE\_A 从 L1D 移至 L2 且内存系统处于空闲状态时，内存系统可能过早声明自身为空闲状态。如果 TRANSACTION\_B 必须严格在 STORE\_A 之后执行，这可能导致程序行为异常。例如：假设 STORE\_A 向 DDR3 写入数据，而 TRANSACTION\_B 触发 EDMA 读取 STORE\_A 写入的地址。MFENCE 应确保 STORE\_A 在 EDMA 执行前提交，以便 EDMA 读取更新后的值。由于本公告所述问题，TRANSACTION\_B 可能在 STORE\_A 提交前触发 EDMA，导致 EDMA 读取到陈旧数据。

权变措施：

将单条 MFENCE 指令替换为连续两条 MFENCE 指令。当 STORE\_A 从 L1D 传至 L2 时，如果内存系统过早指示空闲，此方案可通过恢复暂停状态来解决该问题。

1. STORE\_A

2. MFENCE

3. MFENCE

4. TRANSACTION\_B

关于一致性操作的说明：对于以下公告，除已列出的权变措施外，也可使用双 MFENCE 作为权变措施：

- [公告 63 — 块一致性操作期间的潜在 L2 缓存损坏问题](#)

- [公告 64 — 块和全局一致性操作期间的 L2 缓存损坏问题](#)

请注意，上述第二条公告不涵盖 L1D 和 L2 的块及全局写回操作。如果 L1D 和 L2 的块及全局写回操作后紧跟 MFENCE 和依赖于写回完成的事务，则应使用双 MFENCE 权变措施。

另请注意，当前版本的 MCSDK 软件包未包含此权变措施。该方案将在未来版本中提供

#### 备注

跟踪功能的特殊注意事项。如果通过包含 MFENCE 的软件生成跟踪信息，该权变措施有额外要求。MFENCE 的跟踪生成要求每条 MFENCE 指令后紧跟一条 NOP 和一条 MARK 指令。该权变措施详见本白皮书。

**MSS#68*****HWA 的 Real2X FFT 模式下，第 0 个 BCNT 的 FFT 数据可能损坏***

受影响的修订版：

AWR2544

说明：

如果 FFT 参数集中启用 Real2X FFT 模式，且该 FFT 参数集与禁用动态时钟门控的其他参数集组合使用，则可能导致第 0 个 BCNT 生成错误数据。

权变措施：

在 HWA MMR 空间中启用动态时钟门控以降低数据损坏概率，或禁用 Real2X 模式并在 Real1X 模式下运行。

## MSS#71

## 单比特 ECC ( 错误校正 ) 机制可能会导致内存更新错误

受影响的修订版：

AWR2544

说明：

### 备注

在仿真中调试错误的内存访问序列期间发现了该问题。截至目前，尚未收到任何客户反馈在实际应用/部署场景中出现此类问题。

在 SoC 中，当以下表格所列的内存范围内发生罕见的单比特翻转事件时，若同时存在特定的内存访问序列组合，单比特错误校正机制可能导致内存数据更新错误。

AWR294x 上的 RAM 存储器采用 ECC 保护，具备单比特错误校正、双比特错误检测 (SECDED) 机制。当特定事件序列发生时，单比特错误校正机制可能导致内存更新错误。

该问题若要对应用产生影响，必须同时满足以下所有条件

- 因环境条件或其他因素导致的随机硬件故障引发单比特翻转事件；并且

- 单比特翻转事件影响受影响的内存范围；并且

- 对存在单比特错误的内存地址执行读操作或部分写操作（触发单比特错误校正机制）；并且

- 单比特错误校正后出现特定的内存访问序列组合；并且

- 错误校正机制导致的内存更新错误足以影响应用程序流程，且不会被其他安全机制检测到。

单比特错误校正后，对受影响内存范围执行以下访问组合（上述条件 3 和 4）可能引发该问题。

- 读取/部分写入访问（针对存在 SEC 的 A 地址）→（随后）全写（至同一内存范围内的一个或多个地址）→（随后）部分写（至同一内存范围内的任意其他地址）：会导致最后一次全写的地址出现更新错误。

- 部分写入访问（针对存在 SEC 的 A 地址）→（随后）部分写（至同一内存范围内的其他地址）：会导致 A 地址出现更新错误。

### 备注

其他所有内存访问序列组合均不会引发该问题。

权变措施：

单比特翻转事件属于罕见情况，发生概率较低。

- 该场景仅会导致单比特错误。双比特错误仅能被检测；发生双比特错误时，器件会根据严重程度进入安全状态。

- ( 可能引发该问题的 ) 部分写内存访问受到以下限制

- 缓存内存范围不会产生部分写入访问，因为缓存行写入始终为全写操作。

- 例如：MSS L2 内存

- 代码段为只读（因此整个代码段访问均不满足引发该问题的条件）。

- 例如：MSS L2 内存

- 存在部分写访问的受影响内存可能具备其他安全机制，可检测或规避此类随机错误。

- 雷达数据立方的高级处理算法因具备跟踪功能（时间和逻辑监控），内置异常值剔除能力。

- 例如，DSS L3

- 可在邮箱等受影响内存上采用信息冗余技术检测错误。

**MSS#71 (续)****单比特 ECC (错误校正) 机制可能会导致内存更新错误**

- 例如，邮箱内存

在受影响的内存范围内，确定是否可能进行部分内存写入访问。针对已确认存在部分写入操作的内存范围，评估其风险等级以确定是否需要采取措施。以下是可行的应对措施：

- 当操作环境中单比特翻转事件发生的可能性极低时。

- 当存在其他安全机制可检测或规避此类虚假随机错误时。

- 操作：可考虑采取以下一项或多项措施

- 避免对这些内存范围采用部分写入访问模式。

- 发生单比特内存校正事件时，重新初始化受影响的内存库。

- 将单比特内存校正事件视为不可校正错误，并进入安全状态。

- 这不会影响功能安全的可检测性声明，但在发生此类单比特翻转时可能影响可用性。

如果需要执行操作 (2-b-ii)，请参阅下表中的内存范围及其对应的 ESM 线路和 ECC 聚合器位。

此表仅包含受影响的内存列表和有关的相应详细信息

| 内存名称         | 起始地址       | 终止地址       | ESM 行                          | ECC 聚合器状态位                                                        |

|--------------|------------|------------|--------------------------------|-------------------------------------------------------------------|

| DSS L3 Bank0 | 0x88000000 | 0x880BFFFF | DSS_ESM::<br>GROUP1 Line No-92 | DSS_ECC_AGG::SE<br>C_STATUS_REG0::<br>DSS_L3RAM0_PEN<br>D         |

| DSS L3 Bank1 | 0x8800C000 | 0x8817FFFF | DSS_ESM::<br>GROUP1 Line No-92 | DSS_ECC_AGG::SE<br>C_STATUS_REG0::<br>DSS_L3RAM1_PEN<br>D         |

| DSS L3 Bank2 | 0x88180000 | 0x881FFFFF | DSS_ESM::<br>GROUP1 Line No-92 | DSS_ECC_AGG::SE<br>C_STATUS_REG0::<br>DSS_L3RAM2_PEN<br>D         |

| DSS L3 Bank3 | 0x88200000 | 0x8827FFFF | DSS_ESM::<br>GROUP1 Line No-92 | DSS_ECC_AGG::SE<br>C_STATUS_REG0::<br>DSS_L3RAM3_PEN<br>D         |

| MSS L2 Bank0 | 0xC0200000 | 0xC027FFFF | MSS_ESM::<br>GROUP1 Line No-18 | MSS_ECC_AGG_M<br>SS::SEC_STATUS_<br>REG0::<br>MSS_L2SLV0_PEN<br>D |

| MSS L2 Bank1 | 0xC0280000 | 0xC02EFFFF | MSS_ESM::<br>GROUP1 Line No-18 | MSS_ECC_AGG_M<br>SS::SEC_STATUS_<br>REG0::<br>MSS_L2SLV1_PEN<br>D |

| MSS 邮箱       | 0xC5000000 | 0xC5001FFF | MSS_ESM::<br>GROUP1 Line No-18 | MSS_ECC_AGG_M<br>SS::SEC_STATUS_<br>REG0::<br>MSS_MBOX_PEND       |

| MSS_RETRAM   | 0xC5010000 | 0xC50107FF | MSS_ESM::<br>GROUP1 Line No-18 | MSS_ECC_AGG_M<br>SS::SEC_STATUS_<br>REG0::<br>MSS_RETRAM_PE<br>ND |

| DSS 邮箱       | 0x83100000 | 0x83100FFF | DSS_ESM::<br>GROUP1 Line No-92 | DSS_ECC_AGG::SE<br>C_STATUS_REG0::<br>DSS_MAILBOX_PEN<br>D        |

**MSS#71 (续)**

**单比特ECC(错误校正)机制可能会导致内存更新错误**

**备注**

上述 MSS\_L2 地址基于 DSS 和 EDMA 的寻址视角。从 MSS-R5 视角来看，

MSS\_L2\_BANK0 和 MSS\_L2\_BAK1 的地址范围分别为

0x10200000-0x1027FFFF 和 0x10280000-0x102EFFFF

其他未被应用程序使用但被 BSS 使用的内存模块 (如 BSS\_Mailbox 和

BSS\_Static\_RAM) 也受此勘误影响

- BSS 邮箱主要用于通过 mmWaveLink 在 BSS 和 MSS/DSS 之间进行通信，其采用的消息协议通过 CRC 确保数据完整性。在通过 BSS 邮箱进行消息交换期间使用 CRC 可降低与该内存相关的风险。

- 当发生故障 (本例中为 ECC SEC) 时，BSS 会向 MSS/DSS 发送 ESM 故障异步事件消息作为通知。应用程序必须从 BSS 的 AWR\_AE\_RF\_ADV\_ESMFAULT\_STATUS\_SB 异步事件中读取 b20:ECC\_AGGR\_SEC\_ERROR。将此单比特内存校正事件视为不可校正错误，并进入安全状态。

- 此权变措施仅在应用程序使用 DFP 2.4.14 版本或更早版本的 BSS 补丁时有效

**ANA#12A****接收器中存在二次谐波 (HD2)****受影响的修订版：**

AWR2544

**说明：**

射频引脚/封装和 FMCW 合成器之间的隔离有限。这可能会在合成器输出端产生杂散频率分量，并导致 RX ADC 输出端出现二次谐波，以及预期中频频率的互调产物。以 LNA 输入端目标信号的功率水平为基准，二次谐波的振幅可高达  $-55\text{dBc}$ 。

**权变措施：**

目前无可用权变措施。但在许多典型雷达应用场景中，HD2 不会影响系统性能，原因有二：

1. 由于 HD2 源于与 LO 信号的耦合，自混频效应（即混频器处的相位噪声和相位杂散抑制效应）会固有地抑制 HD2 电平。

2. 在实际场景中，雷达信号从目标反射时通常存在双反射效应，这会导致在实际目标距离两倍处出现虚假目标。这种效应通常与 HD2 自身效应难以区分。

**ANA#37A**

在本振频率范围内 RX 增益大幅下降

受影响版本

AWR2544

详细信息

在该器件的整个工作频率范围内，RX 增益衰减约为 4.5dB。

权变措施

由于增益衰减对噪声系数的影响极小，因此对系统性能的影响可忽略不计。

**ANA#39**

**HPF 截止频率 2800kHz 配置可能会导致不正确的 RX IFA 增益和滤波器转角频率。**

---

**受影响版本**

AWR2544

**详细信息**

模拟中频级包括一个二阶高通滤波器，可配置为以下 -6dB 转角频率：

300、350、700、1400、2800kHz。

在这些情况下，HPF 截止频率 2800kHz 配置可能会导致不正确的 RX IFA 增益和滤波器转角频率。

**权变措施**

建议不要使用 2800kHz 截止频率配置。

**ANA#43**

**合成器频率实时监控中出现错误**

受影响的修订版：

AWR2544

说明：

当温度超过 100°C 时，对于斜率  $> 50\text{MHz}/\text{us}$ 、频率在 80.5GHz 至 81GHz 之间的斜坡配置，合成器频率实时监控中会出现超过 20MHz 的较大误差。

权变措施：

对于斜率  $> 50\text{MHz}/\text{us}$  的情况，建议使用低于 80.5GHz 的线性调频脉冲。

**ANA#44**

在 3.3V IO 模式下，观察到 1.8V 电源轨存在来自 3.3V 电源轨的反向供电

## 受影响的修订版：

AWR2544

## 说明：

当 3.3V 电源轨上电而 1.8V 电源轨尚未供电时，由于 IO 单元内部的泄漏路径，1.8V VIOIN 轨会出现电压上升。

## 权变措施：

建议采用以下权变措施：

1. 使用适当的电源时序：首先提供 1.8V 电压，然后再提供 3.3V 电压。

2. 如果 PMIC 因检测到输出端存在电压而无法上电，应禁用 PMIC 中的该电压检测机制。

**ANA#45**

**数字活动导致的杂散信号**

受影响的修订版：

AWR2544

说明：

数字滤波活动可能耦合到模拟电路，导致本振中出现杂散，这也可以在 Rx 数据中看到。

Rx 数据中的此类杂散会出现在强目标附近的杂散频率偏移处。

可能观察到的各类杂散如下：

1. 采样率在 20Msps 附近 +/-0.5Msps 时，在 (2Fs-40) MHz 中频处出现杂散。

2. 采样率在 30Msps 附近 +/-0.5Msps 时，在 (2Fs-60) MHz 中频处出现杂散。

3. 采样率在 35Msps 附近 +/-0.3Msps 时，在 (4Fs-140) MHz 的中频处出现杂散。

4. 采样率在 22 至 23.5Msps 和 26.5 至 28Msps 范围时，在 (4Fs-100) MHz 中频处出现杂散

[Fs = 配置文件采样率]

权变措施：

用户应避免使用上述范围内的采样率，或精确使用采样率范围的中心值（使杂散位于 0 Hz 处）。

**ANA#47****空闲信道场景下，各 RX 均观察到 RX 杂散信号****受影响的修订版：**

AWR2544

**说明：**

在无目标存在或附近存在极弱目标的场景中， $\Sigma-\Delta$  ADC 输出的 RX 频谱中可能存在杂散。仅在低 RX 增益设置下观察到此现象。杂散频率在各 RX 通道间可能不同。存在真实目标时，不会观察到此现象。

**权变措施：**

- 权变措施 1：在这些情况下，请使用更高的 Rx 增益 ( $>40$ dB)。

- 权变措施 2：空闲信道杂散在 2DFFT 的杂散距离仓中分布于所有多普勒仓。在 2D FFT 中检测峰值时，用户可采用二维邻域峰值搜索（如 2D CFAR-CA），将信号电平与所有周围仓进行比较。这有助于避免将空闲信道杂散检测为虚假目标。

ANA#59

**OSC\_CLK\_OUT\_ETH 活动导致的杂散信号**

受影响的修订版：

AWR2544

说明：

使用 XTAL/2 频率选项启用 OSC\_CLK\_OUT\_ETH 可能会因以太网时钟信号与 LO 信号耦合而导致 XTAL/2 中频处出现弱杂散。如果存在强的真实目标，RX 数据中可能在中频 = ( XTAL/2 — 真实目标中频 ) 处出现虚假目标。

权变措施：

可考虑采取以下一项或多项权变措施：

1. 避免 OSC\_CLK\_OUT\_ETH = XTAL/2 选项，改用 XTAL/1 选项。如果有相关选项，在 AWR2544 芯片外部（例如以太网 PHY 芯片内部）实现任何必要的 2 分频。

2. 使用中频带宽  $< XTAL/4$ ，以避免在强真实目标存在时出现带内虚假目标。

3. 如果使用中频带宽  $> XTAL/4$ ，在检测到强真实目标后，在中频偏移 ( XTAL/2 - 实际目标中频 ) 处采用更严格的检测阈值，以避免检测到这些由 OSC\_CLK\_OUT\_ETH 引起的虚假目标。

4. 降低 OSC\_CLK\_OUT\_ETH 的驱动强度以降低杂散电平。驱动强度为 0.5 倍时，杂散电平预计降低 3dB。

5. 使用 OSC\_CLK\_OUT，而非 OSC\_CLK\_OUT\_ETH

## 商标

所有商标均为其各自所有者的财产。

## 6 修订历史记录

### Changes from DECEMBER 24, 2024 to OCTOBER 1, 2025 (from Revision \* (December 2024) to Revision A (October 2025))

Page

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| • 器件型号/修订版对应关系公告 : 在“主子系统”中添加了 MSS#68 和 MSS#71 公告.....                                    | 4  |

| • 器件型号/修订版对应关系公告 : 删除了 ANA#46.....                                                        | 4  |

| • CRC : 不支持 CRC 8 位数据宽度以及 CRC8-SAE-J1850 和 CRC8-H2F 在 CAN 模块中的潜在用途 : 重新表述了详细信息和权变措施。..... | 20 |

| • MSS#68 : HWA 的 Real2X FFT 模式下, 第 0 个 BCNT 的 FFT 数据可能损坏.....                             | 28 |

| • MSS#71 : 单比特 ECC ( 错误校正 ) 机制可能会导致内存更新错误。.....                                           | 29 |

| • ANA#59 : 将受影响的器件更新为 AWR2544。将 ANA48 更改为 ANA59 以保持一致性。.....                              | 39 |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月