*Errata***AM62Ax Sitara™ 处理器器件勘误表，器件版本 1.0****摘要**

本文档介绍了功能规格的已知例外情况（公告）。本文档也包含了使用说明。在使用说明中介绍了器件行为可能与假定或记录的行为不匹配的情况。这可能包括影响器件性能或功能正确性的行为。

**内容**

|                          |           |

|--------------------------|-----------|

| <b>1 使用说明和公告模型</b> ..... | <b>2</b>  |

| <b>2 器件使用说明和公告</b> ..... | <b>4</b>  |

| <b>修订历史记录</b> .....      | <b>25</b> |

## 1 使用说明和公告模型

使用说明汇总表 列出了所有使用说明和适用的器件修订版本。公告汇总表 列出了所有公告、受影响的模块以及适用的器件修订版本。

**表 1-1. 使用说明汇总表**

| 模块   | 说明                                   | 受影响的器件修订版<br>本 |

|------|--------------------------------------|----------------|

|      |                                      | AM62Ax 1.0     |

| 引导   | i2372 — ROM 不支持串行 NAND 引导中选定的多平面寻址方案 | 是              |

| DDR  | i2330 — DDRSS 寄存器配置工具更新              | 是              |

| OSPI | i2351 — OSPI：控制器不支持带 NAND 闪存的连续读取模式  | 是              |

| PLL  | i2424 — PLL：PLL 编程序列可能会导致 PLL 不稳定    | 是              |

**表 1-2. 公告汇总表**

| 模块       | 说明                                                            | 受影响的器件修订版<br>本 |

|----------|---------------------------------------------------------------|----------------|

|          |                                                               | AM62Ax 1.0     |

| BCDMA    | i2431 — BCDMA : RX 通道在某些情况下可能锁定                               | 是              |

| BCDMA    | i2436 — BCDMA : RX CHAN CFG 寄存器中的 BCDMA_RX_IGNORE_LONG 设置不起作用 | 是              |

| 引导       | i2366 — 引导：ROM 不理解 8D-8D-8D 操作使用的特定 JEDEC SDFP 特性             | 是              |

| 引导       | i2371 — 引导：数据传输过程中，UART 引导模式下的 ROM 代码可能出现挂起                   | 是              |

| 引导       | i2410 — 引导：由于 i2409，ROM 可能无法引导                                | 是              |

| 引导       | i2413 — 引导：HS-FS ROM 引导时加载的 ROM 引导镜像已损坏                       | 是              |

| 引导       | i2414 — 引导：以太网 PHY 扫描和启动流程不适用于不支持自动协商的 PHY                    | 是              |

| 引导       | i2419 — 引导：禁用偏斜消除校准时，ROM 不会检查是否启用了偏斜消除校准                      | 是              |

| 引导       | i2420 — 引导：SDFP 模式下的 XSPI 引导时间不一致                             | 是              |

| 引导       | i2421 — 引导：fatTiny GPT 处理导致数据中止                               | 是              |

| 引导       | i2422 — 引导：MMCSD 文件系统引导时，ROM 的超时时间过长                          | 是              |

| 引导       | i2423 — 引导：HS-FS ROM 对电子保险丝控制器防火墙覆盖的所有地址空间应用调试访问限制            | 是              |

| 引导       | i2435 — 引导：eMMC 引导的 ROM 超时过长                                  | 是              |

| 引导       | i2482 — 引导：ROM 在 SD 卡初始化期间未提供足够的时钟                            | 是              |

| 引导       | i2464 — 引导：ROM 无法从格式化错误的 SD 卡引导                               | 是              |

| C7x      | i2199 — C71x：在非对齐的转置流跨越 AM1 循环缓冲区边界时 SE 返回错误数据                | 是              |

| C7x      | i2120 — C71x：在非对齐的转置流跨越 AM1 循环缓冲区边界时 SE 返回错误数据                | 是              |

| C7x      | i2087 — C7x MMA HWA_STATUS 在应用程序启动前报告错误                       | 是              |

| C7x      | i2376 — C7x：执行两条连续的 VPUT/MVC 指令后，SE/SA/HWAOPEN 接收到损坏的模板       | 是              |

| C7x      | i2399 — C7x：CPU NLC 模块在中断时未清除状态                               | 是              |

| CSI_RX   | i2190 — CSI_RX_IF 在接收不完整的帧后可能进入未知状态                           | 是              |

| CPSW     | i2208 — CPSW : ALE IET 高速数据包丢失                                | 是              |

| CPSW     | i2401 — CPSW：主机时间戳导致 CPSW 端口锁定                                | 是              |

| DDR      | i2160 — DDR：在 LPDDR4 命令总线训练期间必须定义有效的 VRef 范围                  | 是              |

| DSS      | i2097 — DSS：禁用与叠加层相连的层可能会导致下一帧期间出现同步丢失                        | 是              |

| ECC_AGGR | i2049 — ECC_AGGR：由于出现挂起的 ECC 聚合器中断，IP 时钟停止/复位序列可能挂起           | 是              |

| 中断聚合器    | i2196 — IA : IA 中可能出现的死锁情况                                    | 是              |

| LPM      | i2487 — LPM：低功耗模式可能会意外损坏 DDR 内容                               | 是              |

| MCAN     | i2278 — MCAN：当从配置有相同报文 ID 的专用 Tx 缓冲区发送时，无法确保报文发送顺序            | 是              |

| MCAN     | i2279 — MCAN：配置有相同报文 ID 的专用 Tx 缓冲区和 Tx 队列的规范更新                | 是              |

| MMCHS    | i2312 — MMCHS HS200 和 SDR104 命令超时窗口太小                         | 是              |

| MMCHS    | i2493 — MMCSD : HS200 写入失败                                    | 是              |

| OSPI     | i2189 — OSPI：控制器 PHY 调优算法                                     | 是              |

| OSPI     | i2249 — OSPI：未通过 OSPI DDR PHY 内部焊盘环回和无环回时序模式测试                | 是              |

表 1-2. 公告汇总表 (续)

| 模块    | 说明                                                      | 受影响的器件修订版<br>本 |

|-------|---------------------------------------------------------|----------------|

|       |                                                         | AM62Ax 1.0     |

| OSPI  | i2383 — OSPI : PHY DDR 模式不支持 2 字节地址                     | 是              |

| PRG   | i2253 — PRG : CTRL_MMR_STAT 寄存器是 POK 阈值失效的不可靠指示器        | 是              |

| PSIL  | i2137 — PSIL : 时钟停止操作可能会导致异常行为                          | 是              |

| RAT   | i2062 — RAT : 即使设置了“错误记录禁用”，仍会触发错误中断                    | 是              |

| 复位    | i2407 — RESET : : MCU_RESETZ 置位为低电平时 MCU_RESETSTATZ 不可靠 | 是              |

| USART | i2310 — USART : 错误地触发超时中断                               | 是              |

| USART | i2311 — USART 虚假 DMA 中断                                 | 是              |

| USB   | i2134 — USB : 2.0 合规性接收灵敏度测试限制                          | 是              |

| USB   | i2409 — USB : USB2 PHY 由于短暂挂起而锁定                        | 是              |

| VPU   | i2373 — VPU : VPU 的中断未路由到 A53                           | 是              |

## 1.1 支持的器件

本文档支持以下器件：

- AM62Ax

有关所支持器件的参考文档如下：

- AM62Ax 处理器技术参考手册 (SPRUJ16)

- AM62Ax 处理器数据表 (SPRSP77)

## 2 器件使用说明和公告

本节列出了此器件修订版本的使用说明和公告。

### 2.1 器件使用说明

*i2351*

#### **OSPI : 直接访问控制器 (DAC) 不支持带 NAND 闪存的连续读取模式**

**详细信息：**

OSPI 直接访问控制器 (DAC) 不支持带 NAND 闪存的连续读取模式，因为 OSPI 控制器可以在发送到 OSPI 控制器的内部 DMA 总线请求之间，将向闪存存储器发送的 CSn 信号置为无效 ( 根据设计意图 ) 。

发生此问题的原因是，一些 OSPI/QSPI NAND 闪存存储器提供的“连续读取”模式要求片选输入在整个突发事务中持续置为有效状态。

SoC 内部 DMA 控制器和其他启动器限制用于 1023 B 或更小的事务，并且仲裁/排队可以在各种 DMA 控制器内部进行，也可以在任何 DMA 控制器与 OSPI 外设之间的互连中进行。这会导致到 OSPI 控制器的总线请求延迟，进而导致外部 CSn 信号被置为无效。

NOR 闪存存储器不受 CSn 置为无效的影响，连续读取模式正常运行。

**权变措施：**

软件可以使用页面/缓冲读取模式来访问 NAND 闪存。

*i2330*

#### **DDRSS 寄存器配置工具更新**

**详细信息：**

DDR 寄存器配置工具根据系统级详细信息提供自定义寄存器设置，例如 DDR 器件的架构 ( 密度、数据宽度、列数 ) 、工作频率以及通过电路板仿真确定的 IO 设置。经过一段时间，可能会对该工具进行更新，以支持新的器件和/或特性，修复该工具中发现的问题，最重要的是，详细解释勘误表中的权变措施或寄存器计算的最新更新，从而提升性能、信号完整性或信号之间的时序关系。

**权变措施：**

为了确保根据经验教训正确设置参数并降低出现功能故障的风险，应始终使用最新的 DDR 寄存器配置工具生成寄存器值。由于 DDR 寄存器配置工具可以定期更新，因此应查看和评估该工具的修订历史记录，以确定工具更改是否适用于现有系统。如果适用，应适当更新现有系统的配置。可以在 <http://dev.ti.com/sysconfig> 上找到该工具的最新版本，并且对于正在使用的适用器件，选择“Software Product”下拉列表中的“DDR Configuration”。

*i2372*

#### **引导 : ROM 不支持串行 NAND 引导中的所选多层平面寻址方案**

**详细信息：**

ROM 引导加载程序不支持某些多层平面串行 SPI NAND 闪存存储器，因为它们要求从缓存/缓冲区读取命令理解如何更改缓存/缓冲区/平面编号以访问正确的数据。

**权变措施：**

请仔细查看候选闪存存储器的寻址要求，以作为特殊位在从缓存/缓冲区读取命令中选择平面/缓冲区/缓存的参考。不要使用具有此类要求的存储器。

i2424

## PLL : PLL 编程序列可能会导致 PLL 不稳定

### 详细信息：

PLL 编程序列已经更改，以确保如果使用它，在启用 PLL 校准前，所有校准字段都已配置。除了更改对校准逻辑的控制之外，还实现了其他更改，以便在启用 PLL 时 PLL 参数保持不变。

在整数模式下时，软件会在支持校准的 PLL 上启用 PLL 校准功能。之前的软件在 **CAL\_LOCK** 置为有效后调整校准模式。已经看到，这些写入操作会导致某些器件上的 PLL 锁定丢失。此外，即使在易受影响的器件上，锁定丢失也是间歇性的，但是当丢失发生时，相关电路以不正确的频率运行；这种错误频率可能表现为算法执行缓慢或通信故障。

限制影响：当 PLL 处于小数模式时，不能使用校准逻辑。因此，被编程为使用分数模式的 PLL 不应出现与校准编程相关的故障。然而，由于对完整 PLL 序列的更改，建议所有用户使用新软件。

### 权变措施：

请勿将 `clk_pll_16fft_cal_option4()` 用于 SYSFW。执行任何 PLL 配置更改时，确保使用 SDK v10.0 或更高版本中更新后的 PLL 编程序列。

## 2.2 器件公告

i2049

**ECC\_AGGR : 由于出现挂起的 ECC 聚合器中断，IP 时钟停止/复位序列可能挂起**

### 详细信息：

ECC 聚合器模块用于聚合发生的安全错误（这种情况很少见）并产生中断以通知软件。ECC 聚合器通过软件控制安全错误中断的启用/禁用和清除。

当软件对 IP 执行时钟停止/复位序列时，该序列可能无法完成，因为该 IP 关联的 ECC 聚合器实例不是空闲的。ECC 聚合器空闲状态取决于挂起的任何安全错误中断，这些中断要么启用，要么禁用，并且未被软件清除。因此，如果有任何挂起的安全错误中断未被清除，IP 的时钟停止/复位序列可能永远不会完成（挂起）。

受影响的 ECC\_AGGR 可通过技术参考手册 (TRM) 中为其 REV 寄存器（寄存器偏移 0h）列出的值来确定。REV 寄存器在其字段中对 ECC\_AGGR 版本进行编码，如下所示：

v[REVMAJ].[REVMIN].[REVRTL]

v2.1.1 之前的 ECC\_AGGR 版本会受到影响。ECC\_AGGR 版本 V2.1.1 和更高版本不受影响。

受影响的示例：

REVMAJ = 2

REVMIN = 1

REVRTL = 0

上述值会解码为受到影响的 ECC\_AGGR 版本 v2.1.0。

不受影响示例：

REVMAJ = 2

REVMIN = 1

REVRTL = 1

上述值会解码为不受影响的 ECC\_AGGR 版本 V2.1.1。

### 权变措施：

一般说明：

功能安全用例中不支持对 ECC 聚合器执行时钟停止。

对于非功能安全用例，软件应使用以下权变措施：

1. 为 IP 启用所有 ECC 聚合器中断

2. 处理并清除所有挂起的中断

3. 第 3 步：

- a. 禁用 ECC 聚合器的所有中断源，然后执行时钟停止/复位序列。

- b. 执行时钟停止/复位序列，同时继续处理/清除挂起的中断。

由于中断属于外部刺激，软件为第 3 步提供了两种选项：

1. 在执行时钟停止/复位序列之前，禁用所有可以产生挂起 ECC\_AGGR 中断的中断源（EDC CTRL 校验器）

2. 继续处理/清除发生的挂起中断，同时执行时钟停止/复位序列。当清除完所有中断除时，该序列将继续进行。

**i2049 ( 续 )**

**ECC\_AGGREGATOR : 由于出现挂起的 ECC 聚合器中断，IP 时钟停止/复位序列可能挂起**

通常，软件可能需要检测在整个这一序列期间持续触发的挂起中断（例如，在卡滞故障情况下），并禁用其关联的 EDC CTRL 安全校验器，使得时钟停止/复位序列可以继续进行直到完成。

**i2062**

**RAT : 即使设置了“错误记录禁用”，仍会触发错误中断**

**详细信息：**

如果对 RAT 错误记录进行编程以禁用记录并启用中断，则错误将错误地触发中断，但错误日志寄存器不会正确更新。错误中断不应产生。

**权变措施：**

如果禁用 RAT 错误记录，则错误中断也应由软件禁用。

**i2087**

**C71x : MMA\_HWA\_STATUS 在应用程序启动之前报告错误**

**详细信息：**

由于内部状态未初始化，C71x 处理器所搭载的矩阵数学加速器 (MMA) 在上电后，可能会在 HWA\_STATUS 寄存器的 FirstErrorCode 与 LastErrorCode 字段中上报错误。由于这些字段是粘滞字段，任何后续的 HWARCV 指令都可能会引发 C71x 异常。

**权变措施：**

上电后，在首次执行正常 MMA 操作前，可通过 C71x 处理器运行一段简短指令序列，完成 MMA 内部状态初始化。仅需执行一次该指令序列。

该序列会生成有效的 HWA\_CONFIG 和 HWA\_OFFSET 值并将其加载到 MMA 中，随后清除粘性错误码。

以下为 C71x 汇编语言编写的指令序列：

```

PROT

MVK32 .M2 0x0,B0 ; clear low word of VBO

VDUPW .C2 B0,VBO ; duplicate word across VBO

HWAOPEN .L2 VBO,VBO,0 ; clear HWA_CONFIG and HWA_OFFSET

HWACLOSE .S1 0 ; clear any error conditions

```

**i2097**

**DSS : 禁用连接到重叠区的层可能会导致下一帧期间出现同步丢失**

**详细信息：**

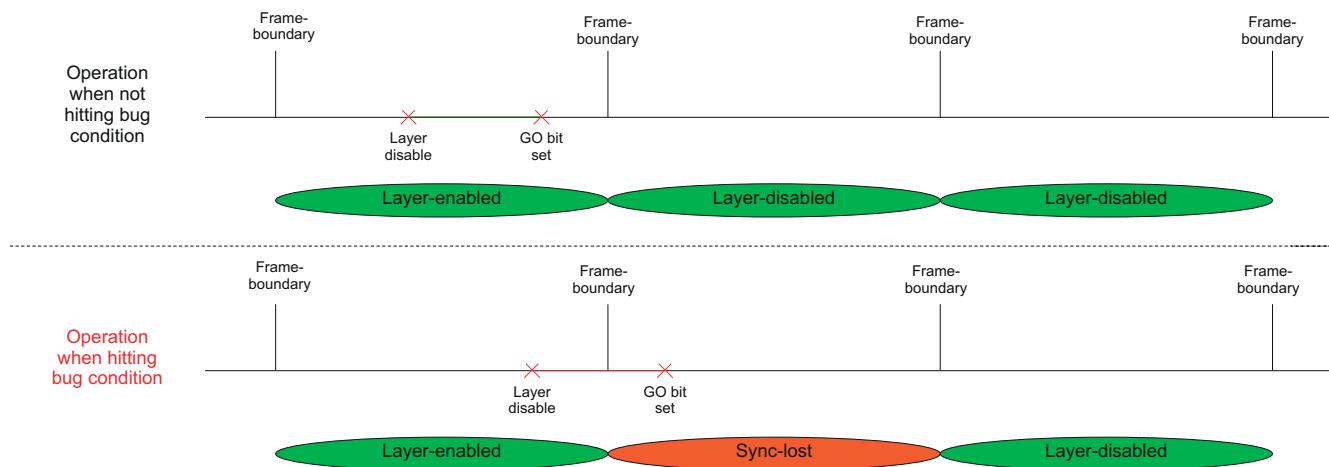

禁用连接到重叠区（它将 DSS\_VID\_ATTRIBUTES[0] ENABLE 从 1 切换到 0）的层（例如 VID1）可能会导致下一帧期间出现同步丢失。同步丢失可能导致出现损坏帧或空白帧（该帧期间从 DSS 发出的所有像素数据为 0x0）。同步丢失出现与否取决于设置和禁用该层有关的 GO 位的时序（即 DSS\_VP\_CONTROL[5] GOBIT 为 1）。如果“禁用层”MMR 写入操作和“设置 GO 位”MMR 写入操作发生在同一帧边界之内，同步丢失不会发生。如果这些操作跨越帧边界发生，则会发生同步丢失（对于一个帧）。设置 GO 位后，该设计将从下一帧开始自动恢复并恢复正常运行，请参见图 2-1。

i2097 (续)

**DSS : 禁用连接到重叠区的层可能会导致下一帧期间出现同步丢失**

图 2-1. 错误条件

**权变措施：**

有一种简单的软件权变措施。在该权变措施中，在禁用重叠区上的层之前，该层会移动到重叠区的“不可见”区域（例如：DSS\_OVR\_ATTRIBUTES\_x[17-6] POSX = **max\_value\_of\_posx** 或 DSS\_OVR\_ATTRIBUTES\_x[30-19] POSY = **max\_value\_of\_posy**）。这就避免了禁用层时发生同步丢失。

示例软件权变措施的伪代码如图 2-2 所示。在这种情况下，常规的“禁用层” MMR 写入操作和“设置 GO 位设置” MMR 写入操作被执行软件权变措施的宏取代。

```

macro disable_layer (overlay n , layer m)

set OVR[n].ATTRIBUTES2[m].POSX = posx_max;

set OVR[n].ATTRIBUTES2[m].POSY = posy_max;

global_ovr_layer_disable_tracker[n][m] = 1;

endmacro

macro set_go_bit (vp n)

if((global_ovr_layer_disable_tracker[n])//any bit set

{

set VP[n].CONTROL.GOBIT = 1;

Wait for 10 DSS FUNC CLK cycles;

for (i=0;i<NUM_LAYERS;i++)

{

if(global_ovr_layer_disable_tracker[n][i])

{

Clear OVR[n].ATTRIBUTES[i].ENABLE = 0;

global_ovr_layer_disable_tracker[n][i] = 0;

}

}

set VP[n].CONTROL.GOBIT = 1;

endmacro

```

- Replace layer disable MMR write operation with a macro which positions the layer to the non-visible area of the OVR

- Track which layers are disabled. This will be used while GO bit is set

- Replace GO bit set MMR write operation with this macro

- First, set GO Bit for the changes in “disable\_layer” macro (and any other earlier changes) to take effect

- After the first GO bit set, few idle\_cycles (10 DSS functional clock cycles) are necessary before we move to the second step

- In the second step, actually disable the layers based on the previously tracked information

- Set the GO bit for the second time for the disable of the layers to take effect

图 2-2. 权变措施伪代码

i2134

**USB : 2.0 合规性接收灵敏度测试限制****详细信息：**

按照《USB-IF USB 2.0 电气合规性测试规范》中的规定执行接收灵敏度测试（EL\_16 和 EL\_17）可能会引发公告 i2091 中描述的问题。

该问题最初是在使用自动化软件执行这些测试时发现的，该软件会在发送数据包时增加 USB 信号的振幅。在验证被测器件 (DUT) 在振幅低于 100mV 时否定应答所有数据包并在振幅高于 150mV 时不否定答应任何数据包期间，该软件一直从低于 100mV 的振幅扫描到高于 150mV 的振幅。但是，如公告 i2091 中所述，在发送有效数据包时，增加振幅超过静噪阈值可能会锁定 PHY。

**i2134 (续)****USB : 2.0 合规性接收灵敏度测试限制****权变措施：****i2189****OSPI : 控制器 PHY 调优算法****详细信息：**

启用 PHY 模块后，OSPI 控制器使用 DQS 信号对数据进行采样。但是，该模块中存在一个问题，要求这种采样必须在内部时钟定义的窗口内进行。读取操作会受到外部延迟的影响，该外部延迟会随温度变化而变化。要确保在任何温度下都能有效读取，必须实施一种特殊调优算法来选择最稳健的 TX、RX 和读取延迟值。

**权变措施：**

此错误的权变措施在 [SPRACT2](#) 中进行了详细介绍。要在某些 PVT 条件下对数据进行采样，必须调高读取延迟字段，以改变内部时钟采样窗口。这样就可以在数据眼图内的任何位置对数据进行采样。但是，这会带来以下副作用：

1. 必须为所有读取操作启用 PHY 流水线模式。由于必须要对写入操作禁用 PHY 流水线模式，因此读取和写入操作必须分开进行。

2. 当权变措施实施后，BUSY 位的硬件轮询中断，因此必须改用软件轮询。写入必须在页边界内通过 DMA 访问进行，以防主机或闪存器件发起的中断。软件必须在页写入操作间隙轮询 BUSY 位。或者，在启用硬件轮询时，写入可以在非 PHY 模式下执行。

3. STIG 读取必须填充额外的字节，并且接收到的数据必须右移。

**i2196****IA : IA 中可能出现的死锁情况****详细信息：**

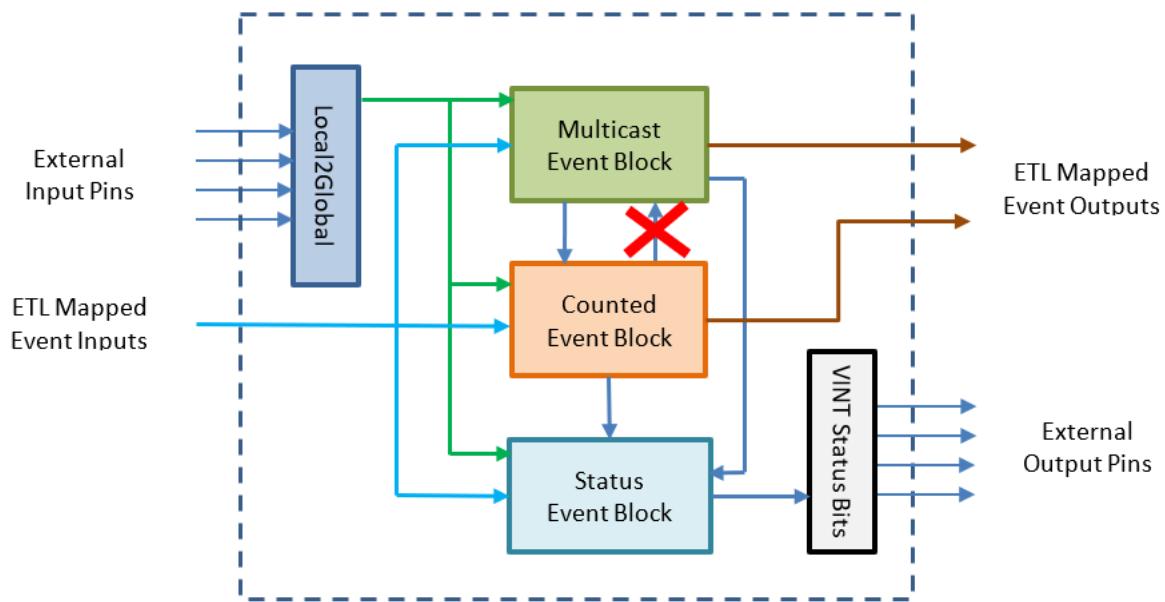

中断聚合器 (IA) 的一个主要功能是转换到达事件传输通道 (ETL) 总线的事件，它可以将事件转换为用于产生电平中断的中断状态位。在 IA 1.0 版中执行此功能的块称为状态事件块。

除了状态事件块外，还有另外两个主处理块：多播事件块和计数事件块。多播块实际上用作事件分离器。对于它接收的每个事件，多播块都可以生成两个输出事件。计数事件块用于将高频事件转换为可读计数。它对输入事件进行计数，并在计数从 0 转换到非零计数值/从非零读数值转换到 0 时生成输出事件。与状态事件块不同，多播和计数事件块生成输出 ETL 事件，然后将这些事件映射到其他处理块。

在设计后，发现了一个可能导致 IA 死锁的问题。当事件“循环”在这三个处理块之间发生时，就会出现该问题。有可能出现一种情况：由于路径阻塞，处理块无法输出事件，并且由于它无法输出事件，因此不能接收任何新的输入事件。无法接受输入事件这种情况会阻止输出路径展开，因此两条路径都被阻塞阻止。

**权变措施：**

[图 2-3](#) 展示了 IA 1.0 的概念方框图。通过采用不允许计数事件块向多播块发送事件的策略，可以避免可能出现的循环。选择此方法是因为更常见的做法是先拆分一个事件，然后对其中一个事件进行计数，同时将另一个事件发送到其他位置。由于该路径由于约定被阻塞，单个事件无法多次访问任何块，因此只要输出保持未阻塞状态，路径就无法被阻塞。

**i2196 ( 续 )****IA : IA 中可能出现的死锁情况****图 2-3. 中断聚合器 1.0 版**

通过遵循此处概述的约定，系统不会出现可能产生死锁情况的危险循环。

**i2199****C71x : 在非对齐的转置流跨越 AM1 循环缓冲区边界时 SE 返回错误数据****详细信息：**

当 AM1 指比 AM0 大的循环缓冲区大小时，SE 可能会在非对齐转置流期间重复使用错误的 64B 数据行。当转置行中的其中一行跨越 AM1 循环缓冲区边界而不是 AM0 边界时，便会出现这种情况。

**权变措施：**

将转置流完全对齐（这意味着起始地址和所有调整后的 DIM 值是 64B 的倍数），或者不要将 AM1 配置为比 AM0 大的循环寻址缓冲区大小。

**i2208****CPSW : ALE IET 高速数据包丢失****详细信息：**

此问题影响以下模块：

[AM62A/D] 3 端口 CPSW

ALE 出现问题的原因是简短高速流量和抢占数据包的 CPSW 频率和 IET 操作，在不支持 10G 的端口上这些数据包在 60-69 个字节之间被抢占。

如果 IET 抢占数据包在 60-69 个字节处中断，则在下一个块到达时进行查找。CPSW 仅提供可抢占 MAC 中的 ALE 64 个字节。

因此，简短高速流量查找将在 64 字节高速流量结束时开始，但当抢占队列继续时，抢占队列将完成 64 个字节的流量并尝试查找抢占数据包。然而，从高速查找开始，该查找操作少于 64 个时钟，因此高速查找将中止（高速流量丢失）并开始新的查找以获取抢占流量。

引发此问题的规则：

**i2208 ( 续 )**

**CPSW : ALE IET 高速数据包丢失**

1. 您在不支持 5/10G 操作的端口上处于 IET ( 穿插快速流量 ) 模式

2. 远程高速数据包可以是小至 60 个字节的抢占数据包

3. 抢占 128 字节或更多字节的数据包流量。

4. 中断 60-69 个字节的抢占流量的高速流量。

5. 一个简短高速流量，然后继续是抢占流量。

- a. 高速帧与抢占帧之间的间隔是最小的。

6. CPSW 频率在所需速度下处于最低等级性能。

**权变措施 :**

在 IET 协商过程中，指示远程器件在 128 字节处分段。

**i2249**

**OSPI : 具有 DDR 时序的内部 PHY 环回和内部焊盘环回时钟模式无法运行**

**详细信息**

OSPI 内部 PHY 环回模式和内部焊盘环回模式采用“启动沿作为捕获沿”（相同的边沿捕获或 0 周期时序）。

可编程接收延迟线 (Rx PDL) 用于补偿往返延迟 ( Tx 时钟至闪存器件、闪存时钟至输出以及闪存数据至控制器 )。

在内部环回模式和 IO 环回模式的情况下，Rx PDL 的总延迟不足以补偿往返延迟，因此不能使用这些模式。

下表介绍了 OSPI 控制器中推荐的时钟拓扑。在 DDR 模式下，此处未描述的所有其他模式都受本公告的影响，不推荐作为时钟拓扑。

**表 2-1. OSPI 时钟拓扑**

| 时钟模式术语          | CONFIG_REG.PHY_MODE_ENABLE | READ_DATA_CAPTURE.BYPASS | READ_DATA_CAPTURE.DQS_EN | 电路板实现                               |

|-----------------|----------------------------|--------------------------|--------------------------|-------------------------------------|

| 无环回、无 PHY       | 0 ( PHY 禁用 )               | 1 ( 禁用调整后的环回时钟 )         | X                        | 无。依靠内部时钟。最大频率 50MHz。                |

| 具有 PHY 的外部电路板环回 | 1 ( PHY 启用 )               | 0 ( 启用调整后的环回时钟 )         | 0 ( DQS 禁用 )             | 外部电路板环回 (OSPI_LOOPBACK_CLK_SEL = 0) |

| 具有 PHY 的 DQS    | 1 ( PHY 启用 )               | x ( DQS 启用具有优先级 )        | 1 ( DQS 启用 )             | 连接到 SOC DQS 引脚的存储器选通                |

**权变措施**

无。请根据介绍的表格，使用未受影响的时钟模式之一

**i2278**

**MCAN : 当从配置有相同报文 ID 的专用 Tx 缓冲区发送时，无法确保报文发送顺序**

**详细信息**

此勘误表仅限于多个 Tx 缓冲区配置有相同报文 ID (TXBC.NDTB > 1) 的情况。

在以下情况下，消息可能会不按顺序发送：

- 多个 Tx 缓冲区配置有相同的报文 ID

- 这些 Tx 缓冲区的 Tx 请求按顺序提交，且每个请求之间存在延迟

**权变措施**

权变措施 1 :

**i2278 ( 续 )****MCAN : 当从配置有相同报文 ID 的专用 Tx 缓冲区发送时 , 无法确保报文发送顺序**

将具有相同报文 ID 的 Tx 报文写入消息 RAM 后 , 通过对 TXBAR 进行一次写访问 , 同时请求发送所有这些报文。在同时发出请求之前 , 确保所有这些报文中都没有挂起的 Tx 请求。

权变措施 2 :

使用 Tx FIFO 而不是专用 Tx 缓冲区 ( 设置位 MCAN\_TXBC[30] TFQM = 0 以使用 Tx FIFO ) 按特定顺序发送多条具有相同报文 ID 的报文。

**i2279****MCAN : 配置有相同报文 ID 的专用 Tx 缓冲区和 Tx 队列的规范更新****详细信息**

此勘误表更新了 M\_CAN 用户手册中第 3.5.2 节专用 Tx 缓冲区和第 3.5.4 节 Tx 队列中的说明 , 该说明与配置有相同报文 ID 的多个专用 Tx 缓冲区的报文发送有关。

**权变措施**

权变措施 1 :

将具有相同报文 ID 的 Tx 报文写入消息 RAM 后 , 通过对 TXBAR 进行一次写访问 , 同时请求发送所有这些报文。在同时发出请求之前 , 确保所有这些报文中都没有挂起的 Tx 请求。

权变措施 2 :

使用 Tx FIFO 而不是专用 Tx 缓冲区 ( 设置位 MCAN\_TXBC[30] TFQM = 0 以使用 Tx FIFO ) 按特定顺序发送多条具有相同报文 ID 的报文。

**i2310****USART: 错误地清除/触发超时中断****详细信息 :**

在 RHR/MSR/LSR 寄存器读取期间 , USART 可能会错误地清除或触发超时中断。

**权变措施 :****CPU 用例**

- 如果超时中断被错误地清除 :

- 清除是有效的 , 因为 FIFO 中的挂起数据会重触发超时中断

- 如果错误地设置了超时中断 , 并且 FIFO 为空 , 请使用以下软件权变措施来清除中断 :

- 在 TIMEOUTH 和 TIMEOUTL 寄存器中设置超时计数器的高值

- 将 EFR2 第 6 位设置为 1 以将超时模式更改为周期性模式

- 读取 IIR 寄存器以清除此中断

- 将 EFR2 第 6 位设置回 0 以将超时模式改回原始模式

**DMA 用例**

- 如果超时中断被错误地清除 :

- 清除是有效的 , 因为下一个周期性事件会重触发超时中断

- 用户必须通过将 EFR2 第 6 位设置为 1 来确保 RX 超时行为处于周期性模式

- 如果超时中断被错误地设置 :

- 这会导致 DMA 被软件驱动程序关闭

- 有效 , 因为下一个传入数据将导致软件再次设置 DMA

**i2311****USART 虚假 DMA 中断****详细信息：**

当在 TLR 寄存器中出现非 2 的乘幂触发级别的情况下，使用 DMA 访问 TX/RX FIFO 时，可能会发生虚假 DMA 中断。

**权变措施：**

为 TX/RX FIFO 触发级别使用 2 的乘幂值 ( 1、2、4、8、16 和 32 )。

**i2312****MMCSD : HS200 和 SDR104 命令超时窗口太小****详细信息：**

在高速 HS200 和 SDR104 模式下，MMC 模块的功能时钟将达到 192 MHz。在此频率下，通过 MMC 主机控制器使用 MMCSD\_SYSCTL[19:16] DTO = 0xE 可获得的最大超时为  $(1/192\text{MHz}) \times 2^{27} = 700\text{ms}$ 。超过 700ms 的命令可能会受到这一较小窗口时间范围帧的影响。

**权变措施：**

如果命令需要超过 700ms 的超时，则可以禁用 MMC 主机控制器命令超时 (MMCSD\_CON[6] MIT=0x1) 并可以使用软件实现代替它。详细步骤如下所示 ( 在 Linux 中 ) :

1. 在 MMC 主机控制器探测函数 (omap\_hsmmc.c:omap\_hsmmc\_probe()) 执行期间，通知处理器主机控制器无法支持所有必需的超时。

2. 修改 MMC 核心软件层功能，以便在底层 MMC 主机控制器无法支持所需超时的情况下，内核自行超时。

**i2366****引导 : ROM 不理解 8D-8D-8D 操作使用的特定 JEDEC SFDP 特性****详细信息：**

JEDEC 规范 JESD216 - 串行闪存可发现参数 (SFDP) 详细说明了在某些串行闪存器件中使用的参数表，用于描述特性以及如何与器件通信/配置器件。ROM 可以解释 SFDP 中适用于器件特性的相关部分 ( 例如，如何从 1S-1S-1S 模式更改为 8D-8D-8D 模式 )，但不能正确理解有以下需要的闪存器件：

- 与 1S-1S-1S 模式相比，8D-8D-8D 模式下的交换的字节顺序

- 8D-8D-8D 模式下的命令扩展，它需要使用与发送的第一个字节不同的命令 ( 例如，操作码反转或其他唯一字节 )

**权变措施：**

查看符合 JEDEC JESD216 的任何候选闪存存储器的 SFDP 表；大多数情况下，供应商不会发布该表，但可以向闪存供应商索取。如果 JEDEC 基本闪存参数表的第 18 个 DWORD 的第 31 位的值为 “1b”，则必须在出厂时以交换的字节顺序对存储器进行编程，或使用 SoC 进行编程。如果 [30:29] 位的值不是 “00b”，则它不能在 8D-8D-8D 模式下用于任何引导模式。因此，避免对该闪存器件使用任何 8D-8D-8D 引导模式。

**i2371****引导 : 数据传输过程中, UART 引导模式下的 ROM 代码可能出现挂起****详细信息 :**

由于公告 i2310 , UART 引导过程中可能出现 ROM 代码执行挂起的情况。i2310 公告中提及的软件权变措施未在 ROM 中实现 , 因此在非预期状态下可能触发错误的超时中断。这可能会导致 ROM 无法清除此中断 , 进而出现挂起。

只要使用 UART 引导模式或将 UART 用作引导接口以启用生产流程 ( 例如 UniFlash 或者使用 OTP Keywriter 对电子保险丝进行编程 ) , 就可能会出现此问题。

**权变措施 :**

无。应使用其他引导接口。

**i2120****C71x : 在转置流中对 LEZR 进行非奇偶校验错误检测时 SE 挂起****详细信息 :**

C71x 流引擎 (SE) 用于返回格式化数据和返回报告内部错误信息的管道始终监控其正在处理的数据的标签。当检测到用于格式化返回 CPU 的数据的数据行出错时 , 所有用于将命令排队进入 UMC 、 uTLB 以及返回 CPU 的格式化管道的提取端执行都将停止。

在一般操作中 , 仅进行错误监控的标签是用于当前命令的标签。对于转置模式 , 是指受到当前数组列影响的所有标签。抑制内部标签监控时出现的间隙会导致格式化管道监控其当前未处理的标签 , 同时为 LEZR 特性创建零矢量。如果 SE 的提取端遇到并记录了未来列的错误 , 格式化端可能会注意到它 , 并在该列的命令提交进行格式化之前停止提取端。

仅仅对于在内部提交进行格式化的命令 , 才将错误报告给 CPU , 因此在提交该列之前停止内部执行导致不向 CPU 报告任何错误。因为 SE 已经停止提取操作而没有报告错误 , 所以 CPU 继续挂起 , 等待 SE 返回数据或发出错误 , 直到发生一个不相关的外部事件或中断。

**权变措施 :**

唯一的 100% 权变措施是在同时启用了 LEZR 和转置模式的情况下不使用流模板。

**i2137****PSIL : 时钟停止操作可能会导致异常行为****详细信息 :**

时钟停止接口是一个请求/确认接口 , 用于协调正确停止的主时钟和模块之间的握手。如果不首先执行通道清理或清除全局启用位 , 而尝试对在模块执行时钟停止 , 将导致模块特定的异常行为。

受影响的模块包括 PDMA 、 SA2UL 、以太网交换机、 CSI 、 UDMAP 、 ICSS 和 CAL 。

**权变措施 :**

在尝试进行时钟停止操作之前 , 需要使用软件清理所有活动通道 ( 通过 UDMAP 中的 UDMAP “实时”寄存器或 PSIL 模块中的 PSIL 寄存器 0x408 ) , 并且在完成此操作后 , 还要清除所有通道的全局启用位 ( 通过 UDMAP 和 PSIL 模块中的 PSIL 寄存器 0x2 ) 。

**i2190****CSI : CSI\_RX\_IF 在接收不完整的帧后可能进入未知状态****详细信息 :**

当 CSI2 接口接收到可能存在 CRC 错误的不完整帧时 , 该模块可能进入未知状态。在这种情况下 , 将不会捕获所有后续图像帧。

**权变措施 :**

复位 CSI\_RX\_IF 模块。

i2253

**PRG : CTRL\_MMR STAT 寄存器是 POK 阈值失效的不可靠指示器**

详细信息

CTRL\_MMR PRG STAT 寄存器中的 POK 过压和欠压标志是用于指示 POK 是否失效的不可靠指示器。因此，在器件技术参考手册 (TRM) 中将它们标记为“保留”。

权变措施

滤波后的 POK 输出会更新 ESM 标志。

在 POK 初始化 (即启用) 时，应该清除 ESM 标志 (根据带隙和/或 POK 趋稳时间内进行的比较)。在该初始清除之后，ESM 标志可用作 POK 失效 (或未失效) 的可靠指示器。

**i2373****VPU : VPU 的中断未路由到 A53****详细信息**

视频加速器 (VPU) 的 CODEC0\_VPU\_WAVE512CL 中断未路由至 A53 核心。VPU 中断只路由到 DM R5 和 MCU R5。

**权变措施**

A53 需要轮询 VPU 状态来管理 VPU 中断。

### i2383

### **OSPI : PHY DDR 模式不支持 2 字节地址**

#### 详细信息：

当 OSPI 控制器配置为在 PHY DDR 模式中进行 2 字节寻址时，内部状态机将发送的地址字节数失配为值 1 (而不是 2)。这会导致状态机在地址阶段锁定，使 PHY DDR 模式不可运行。

使用任何 Tap 模式或 PHY SDR 模式时，不会发生此问题。在 PHY DDR 模式下使用 4 字节寻址时，也不会出现此问题。

#### 权变措施：

对于具有可编程地址字节设置的兼容 OSPI 存储器，请将闪存上所需的地址字节数从 2 设置为 4。这可能涉及发送一条特定命令以更改地址字节和/或在闪存上写入配置寄存器。完成后，将在控制器设置中发送的地址字节数从 2 更新为 4。

对于仅支持 2 字节寻址且无法重新编程的兼容 OSPI 存储器，PHY DDR 模式将与该存储器不兼容。替代模式包括：

- PHY SDR 模式

- TAP (无 PHY) DDR 模式

- TAP (无 PHY) SDR 模式

### i2401

### **CPSW : 主机时间戳导致 CPSW 端口锁定**

#### 详细信息：

CPSW 提供两种机制，将数据包入站时间戳信息传递给主机。

第一种机制是通过 CPTS 事件 FIFO 实现的，该机制在由特定事件触发时记录时间戳。这类事件包括接收到包含指定 EtherType 字段的以太网数据包。这种机制最常用于捕获 PTP 数据包的入站时间戳。通过这种机制，主机必须将时间戳（来自 CPTS FIFO）和 DMA 提供的数据包有效载荷分开读取。这种模式受支持并且不受此勘误表影响。

第二种机制是为所有数据包启用接收时间戳，而不仅仅是 PTP 数据包。采用这种机制时，时间戳会通过 DMA 与数据包有效载荷一起传送。第二种机制是本勘误表的主题。

当启用 CPTS 主机时间戳时，每个传送到内部 CPSW 端口 FIFO 的数据包都需要来自 CPTS 的时间戳。当数据包前导码由于 EMI 或任何其他损坏机制而损坏时，可能不会向 CPTS 发送时间戳请求。在这种情况下，CPTS 将不会生成时间戳，这会导致 CPSW 端口 FIFO 中出现锁定状况。当通过清除 CPTS\_CONTROL 寄存器中的 tstamp\_en 位来禁用 CPTS 主机时间戳时，将阻止发生锁定状况。

#### 权变措施：

必须禁用以太网到主机的时间戳。

可以使用 CPTS 事件 FIFO 时间戳来代替 CPTS 主机时间戳。

### i2407

### **复位 : MCU\_RESETz 置位为低电平时 MCU\_RESETSTATz 不可靠**

#### 详细信息：

MCU\_RESETSTATz 在较短的一段时间内周期性地变为高电平，然后再次变为低电平，同时 MCU\_RESETz 仍被置为低电平。仅当 MCU\_RESETz 置位为低电平的时间超过 100us 时，才会出现此问题。当 MCU\_RESETz 为低电平时，器件保持复位状态；本公告仅适用于信号 MCU\_RESETSTATz。

#### 权变措施：

以下任何一项都可以用作本公告的权变措施

- 请勿在功能系统中使用 MCU\_RESETz。MCU\_RESETz 仍可用于调试，以实现勘误表中的限制。

**i2407 ( 续 )****复位 : MCU\_RESETz 置位为低电平时 MCU\_RESETSTATz 不可靠**

- 将 MCU\_RESETz 的最大低电平持续时间限制为小于 100us。

- 使用主域 RESETSTATz 而不是 MCU\_RESETSTATz。MCU\_RESETz 也会导致主复位，因此主域 RESETSTATz 可用于观察器件复位。有关 RESETSTATz 时序规范，请参阅数据表。

- 在新设计中，产生主域复位和 MCU 域复位的电路应与“与”门结合使用，作为 RESETz 的输入。还应将 MCU 域复位电路连接到 MCU\_RESETz 输入。这将提供 MCU 热复位的完整功能，使用 MCU\_RESETz 和 MCU\_RESETSTATz 指示 MCU 域复位的状态。RESETz 将在主域复位或 MCU 域复位时使用“与”门触发。

**i2409****USB : USB2 PHY 由于短暂挂起而锁定****详细信息 :**

当 USB 2.0 PHY 可能挂起，以响应在 USB 控制器进入挂起状态的 3 微秒内发生的 USB 唤醒事件时。这种 PHY 挂起只能通过电源重启恢复，因为热复位无效。

**权变措施 :**

注意：此权变措施仅在 USB 不是主引导模式时适用。如果 USB 是主引导模式，则没有可用的权变措施。

为防止该问题发生，在 USB 控制器初始化过程中必须遵循特定的操作顺序：

1. 通过 LPSC 移除 USB 控制器复位。

2. 将 PHY2 区域中的 PLL\_REG12 pll\_ldo\_ref\_en 字段（第 5 位）设置为“1”。

3. 将 PHY2 区域中的 PLL\_REG12 pll\_ldo\_ref\_en\_en 字段（第 4 位）设置为“1”。

4. 继续进行正常的 USB 控制器初始化。

**i2410****引导 : 由于 i2409 , ROM 可能无法引导****详细信息 :**

由于 i2409，在热复位后 ROM 可能无法在 USB 引导模式下引导。如果 USB 2.0 PHY 锁定，ROM 未实现 i2409 中列出的任何权变措施，因此 ROM 将挂起且无法引导。

**权变措施 :**

应通过在软件公告中描述的其中一种权变措施来避免 i2409 中描述的公告。

**i2376****C7x : 执行两条连续的 VPUT/MVC 指令后，SE/SA/HWAOPEN 接收到损坏的模板****详细信息**

在 C7604 CPU 上，编程信息通过 SEOPEN 发送到流引擎，通过 SAOPEN 发送到流地址生成器，并通过 HWAOPEN 指令发送到 MMA。该编程信息来源于 CPU 中的 CUCR 寄存器，这些寄存器通过 MVC 和 VPUT 系列指令进行填充与更新。如果在三个 CPU 周期序列中，前两个周期更新了某个 CUCR 寄存器，第三个周期该寄存器被 SEOPEN、SAOPEN 或 HWAOPEN 指令使用，则写入这些 CUCR 寄存器的数据可能会错误地转发至上述指令。

**i2376 ( 续 )**

**C7x : 执行两条连续的 VPUT/MVC 指令后，SE/SA/HWAOPEN 接收到损坏的模板**

例如，以下序列会导致 SAOPEN 指令执行时出现转发错误，进而破坏 SA0 的编程配置：

```

MVC .C2 VBO, CUCR0

VPUTD .C2 B1, 0, CUCR0

SAOPEN .C2 CUCR1:CUCR0, 0

```

**权变措施**

避免以下三个执行包序列即可规避该问题：前两个执行包包含向同一 CUCR 写入数据的 MVC/VPUT 指令，第三个执行包包含从同一 CUCR 读取数据的 SE/SA/HWAOPEN 指令。编译器在编译 C7504 代码时，会自动纳入该问题的权变措施。

**i2399**

**C7x : CPU NLC 模块在中断时未清除状态**

**详细信息：**

在以下情况下将会发生数据损坏：

1. 一个应用程序正在运行，并涉及任务切换。在这种情况下，至少有 2 个任务可能使用 NLC。

2. 当为任务 A 提供中断时，发出了一条 NLCINIT，然后是 TICK。此操作最终会设置 NLC 模块中的一些内部状态，说明我们需要在下一条 TICK 时将 ILCNT\_INIT 值重新加载到 ILCNT，因为它计算出的转发用例已刷新。在接到中断时，该状态未被正确清除。

3. ISR 执行任务切换并切换到任务 B，任务 B 也在运行 NLC 代码。要返回到的 NLC 代码需要继续进行，并且其 ILCNT\_INIT 值与原任务中的 NLC 循环不同。

4. 从 ISR 返回后，下一条 TICK 会因状态损坏最终将 ILCNT 设置为错误的值 (ILCNT\_INIT - 2)。

此时 ILCNT 已损坏，NLC 循环将执行错误次数的迭代，从而导致数据损坏。

**权变措施：**

在保存上下文的过程中，在 ISR 中发出 NLCINIT ( 参数无关紧要，随后无需发出 TICK/BNL )。权变措施不会影响性能。

**i2413**

**引导 : HS-FS ROM 引导时加载的 ROM 引导镜像已损坏**

**详细信息：**

ROM 支持一种镜像格式，该格式中同时包含引导加载程序镜像与 TIFS 镜像。这种格式被称为组合镜像。

在 HS-FS 器件上，当使用 RSA 密钥对组合镜像签名后，ROM 应执行以下操作：

- 跳过对引导加载程序组件的完整性检查

- 在 TIFS 组件上执行完整性检查和签名验证。

由于 ROM 存在漏洞，在 HS-FS 器件上使用非退化 RSA 密钥时，ROM 会跳过对 TIFS 组件的完整性校验。

**权变措施：**

使用退化 RSA 密钥对 X509 证书进行签名，以启用对所有组件 ( 引导加载程序与 TIFS ) 的完整性校验

**i2414****引导 : 以太网 PHY 扫描和启动流程不适用于不支持自动协商的 PHY****详细信息 :**

ROM 以太网 ( RGMII 或 RMII ) 引导模式需要 PHY 自动协商完成后，才会检查链路状态。因此，不支持自动协商的 PHY 无法使用此引导模式。

**权变措施 :**

无，需要支持自动协商的 PHY。

**i2419****引导 : 禁用偏斜消除校准时，ROM 不会检查是否启用了偏斜消除校准****详细信息 :**

如果禁用了 PLL 偏斜消除校准，ROM 驱动程序代码往往会检查偏斜消除校准是否已启用以及锁定是否失效。但是，当前代码在 IF 条件下有赋值。因此，在清除配置位之前，它不会检查偏斜消除校准是否启用。不存在功能问题。

**权变措施 :**

无

**i2420****引导 : SFDP 模式下的 xSPI 引导时间不一致****详细信息 :**

当在启用 SFDP 的情况下使用 xSPI 引导 ( 即以 25Mhz 在 DDR 模式下引导 ) 时，冷启动与热启动的引导时间存在差异。该问题与 OSPI 子系统中的异步桥接有关，会导致以下两者之间出现竞争条件：

1. OSPI IP 完成数据预取

2. 下一个读取事务由 TI OSPI 封装器提交到 OSPI IP。

这会产生相当长的延迟，导致 OSPI 控制器将片选置为无效，从而减慢整体传输速度。

**权变措施 :**

无

**i2421****引导 : fatTiny GPT 处理会导致数据中止****详细信息 :**

尝试从 GPT 格式的文件系统引导会导致公共 ROM (R5) 进入数据中止。此时引导将挂起，直到看门狗计时器启动。

**权变措施 :**

不支持此 GPT 分区表类型，请确保分区表为 MBR，且引导分区类型为 FAT。

**i2422****引导 : MMCSD 文件系统引导时, ROM 的超时时间过长****详细信息 :**

由于 ROM 存在漏洞, 如果尝试从空或已擦除 (或出厂全新状态) 的 eMMC 器件通过 SD/MMC 引导 (文件系统模式) 进行引导, 正常的引导超时切换至备份引导模式功能将失效, 因为引导过程会陷入无限循环, 直至看门狗计时器触发复位。

**权变措施 :**

需要从另一个主引导模式引导才能对 eMMC 闪存进行编程。

**i2423****引导 : HS-FS ROM 对电子保险丝控制器防火墙覆盖的所有地址空间应用调试访问限制****详细信息 :**

在 HS-FS 器件 ROM 上, ROM 对包含安全资产的 FWL 33 和 FWL 66 应用调试限制。调试访问限制应用于整个防火墙区域, 而不仅仅是应用于安全资产所在的区域。例如, 在无需 TIFS 软件参与的情况下, 这会导致无法使用外部仿真器执行初始闪存编程操作。

**权变措施 :**

需借助 TIFS 软发起请求, 才能打开所需的防火墙。

**i2431****BCDMA : RX 通道在某些情况下可能锁定****详细信息 :**

如果没有任何 TR 在配置特定的标志字段中设置 EOP 标志, BCDMA RX chan Teardown 可以锁定通道并且无法在随后的传送中使用。随后, 当通道重新启用时, 传送将不会完成并将终止, 并且 TR 响应中会出现各种错误。

**权变措施 :**

- 从 PSIL/PDMA 外设接收数据时, 需要在每个 TR 的配置的特定标志字段中设置 EOP 标志, 并应将 PDMA 的 1 X-Y FIFO 模式静态 TR “Z” 参数设置为非零值, 以便通道清理正常进行并清理内部状态存储器。否则, 会导致在随后后续运行时通道锁定。PDMA Z 计数也应与 TR 大小匹配, 以便 PDMA 将每次传送描述为单个数据包。这在一些情况下尤其会造成问题, 例如, TRPD 设置了无限重新加载计数, 以便在流模式下使用单组 TR 执行循环传送, 在这种情况下, 每个 TR 都可能是最后一个。

- 如果用例不允许提前设置 PDMA Z 计数或者无法设置数据包 EOP, 则替代方法是在单缓冲模式下使用 PKTDMA 而不是 BCDMA。

**i2435****引导 : eMMC 引导的 ROM 超时过长****详细信息 :**

由于 ROM 中存在错误, 如果尝试从空的或已擦除 (即, 恢复出厂设置) 的 eMMC 器件以 eMMC 引导模式 (即从 eMMC 引导分区进行引导, 有时称为 eMMC 替代模式) 进行引导, 切换至备份引导模式的正常引导超时时间可长达 10 秒。

**权变措施 :**

如果系统认为此超时时间过长, 则需要从另一种引导模式引导。

**i2160****DDR : 必须在 LPDDR4 命令总线训练期间定义有效 VRef 范围****详细信息：**

DDR PHY 会在 LPDDR4 命令总线训练 (CBT) 期间更新命令/地址总线的 VREF (ca)。如果 VREF (ca) 搜索范围设置为无效值，因而在 CBT 期间无法找到工作设置，则培训过程可能失败或挂起。

**权变措施：**

在启用 CBT 之前，将以下字段设置为已知的有效工作值。

对于频率集 0 : PI\_CALVL\_VREF\_INITIAL\_START\_POINT\_F0 和

PI\_CALVL\_VREF\_INITIAL\_STOP\_POINT\_F0

对于频率集 1 : PI\_CALVL\_VREF\_INITIAL\_START\_POINT\_F1 和

PI\_CALVL\_VREF\_INITIAL\_STOP\_POINT\_F1

对于频率集 2 : PI\_CALVL\_VREF\_INITIAL\_START\_POINT\_F2 和

PI\_CALVL\_VREF\_INITIAL\_STOP\_POINT\_F2

建议使用标称 Vref 值 ( 基于处理器上驱动强度的器件编程和存储器终端 ) +/- 4%。请使用 <http://dev.ti.com/sysconfig> 上的在线 DDR 寄存器配置工具对这些寄存器进行编程并检查修订历史记录，以确保所使用的工具版本已采用此权变措施。

**i2436****BCDMA : RX CHAN CFG 寄存器中的 BCDMA\_RX\_IGNORE\_LONG 设置不起作用****详细信息：**

当远程端点未发送 EOP 以匹配 TR 边界时，BCDMA 的 RXCHAN CFG 寄存器中的 RX\_IGNORE\_LONG 标志被忽略，并且 BCDMA 报告 TR 响应中存在错误。

**权变措施：**

RX\_IGNORE\_LONG 不可用，因此 PDMA 之类的远程端点应通过发送 EOP 来关闭数据包，以匹配 TR 边界 ( PDMA X\*Y\*Z 应匹配 TR ICNT0\*ICNT1\*ICNT2\*ICNT3 )

如果需要无限流 (PDMA Z=0)，则切换到 PKTDMA 并使用单缓冲模式

**i2482****引导 : ROM 在 SD 卡初始化期间未提供足够的时钟****详细信息：**

ROM 代码未按《SD 卡物理层规范 2.00.》这可能导致 SD 卡引导失败，然而在受影响的器件上尚未因该勘误观察到引导失败。

**权变措施：**

无

**i2464****引导 : ROM 无法从格式化错误的 SD 卡引导****详细信息：**

如果在创建文件系统期间对文件系统进行了错误的格式化，MMCSD 引导模式可能无法从该 SD 卡引导。

**权变措施：**

从 Ubuntu 22.04 系统创建 SD 时，在 mkfs.vfat 命令中添加 “-a” 参数以生成正确的引导分区。

**i2487****LPM : 低功耗模式可能会意外损坏 DDR 内容****详细信息：**

在进入深度休眠或 RTC+IO+DDR 低功耗模式期间，该器件可能无法将连接的 DDR 正确转换到保留模式，这会导致 DDR 数据损坏。

如果没有应用软件权变措施，受影响的器件不应使用这些低功耗模式。

**权变措施：**

SDK 11.1 版及更高版本中提供了此问题的权变措施。该权变措施可确保控制 DDR 自刷新的内部保持锁存器在各种复位情况下均处于正确状态。

**i2493****MMCSD : HS200 写入失败****详细信息：**

当 MMC0 接口在 HS200 模式下执行多块写入操作且 IO 电源噪声过大时，可能会出现写入失败的情况。

为最大限度降低 IO 电源噪声，请遵循以下最佳实践并参阅链接的应用手册：

- 在接地层附近使用宽电源平面/覆铜，并在两者之间采用较薄的电介质。

- 使电源平面/覆铜和相邻的接地平面尽可能靠近供电元件表面。

- 使用各种容值的去耦电容器，并将低 ESL 电容器放置在尽可能靠近去耦器件的位置。

- 每个电源引脚配置一个去耦电容器。

- 使用短而宽的布线去耦电容器和电源/接地过孔。

- [Sitara™ 处理器配电网络：实施与分析](#)

**权变措施：**

实现软件恢复机制，对失败的多块写入操作进行重发，块与块之间至少保持  $5 \mu s$  的延迟以降低噪声。实现此延迟的一种方法是，将失败的多块写入操作改为单块写入操作。

**商标**

所有商标均为其各自所有者的财产。

## 修订历史记录

### Changes from DECEMBER 11, 2024 to OCTOBER 31, 2025 (from Revision B (December 2024) to Revision C (October 2025))

|                                                                            | Page |

|----------------------------------------------------------------------------|------|

| • 增加了使用说明 i2330 : DDRSS 寄存器配置工具更新.....                                     | 4    |

| • 增加了公告 i2087 ; C7x : C7x MMA HWA_STATUS 在应用启动之前报告错误.....                  | 7    |

| • 增加了公告 i2160 ; DDR : 必须在 LPDDR4 命令总线训练期间定义有效 VRef 范围.....                 | 22   |

| • 增加了公告 i2436 ; BCDMA : RX CHAN CFG 寄存器中的 BCDMA RX_IGNORE_LONG 设置不起作用..... | 22   |

| • 增加了公告 i2482 ; 引导 : ROM 在 SD 卡初始化期间未提供足够的时钟.....                          | 22   |

| • 增加了公告 i2464 ; 引导 : ROM 无法从格式化错误的 SD 卡引导.....                             | 22   |

| • 增加了公告 i2487 ; LPM : 低功耗模式可能会意外损坏 DDR 内容.....                             | 23   |

| • 增加了公告 i2493 ; MMCSD : HS200 写入失败.....                                    | 23   |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月