*Errata***IWRL6432 器件勘误表

器件修订版本 1.0 和 2.0****摘要**

本文档介绍了功能规格的已知例外情况（公告）。本文档也包含了使用说明。使用说明中介绍了器件行为可能与假定或记录的行为不匹配的情况。这可能包括影响器件性能或功能正确性的行为。

**内容**

|                                          |           |

|------------------------------------------|-----------|

| <b>1 简介</b>                              | <b>2</b>  |

| <b>2 器件命名规则</b>                          | <b>2</b>  |

| <b>3 器件标识</b>                            | <b>3</b>  |

| <b>4 使用说明</b>                            | <b>5</b>  |

| 4.1 低功耗拓扑中的上电序列                          | 5         |

| 4.2 符合 BOM 优化型拓扑中 1.2V 数字 LDO 输出路径的数据表规格 | 5         |

| <b>5 器件型号/修订版对应关系公告</b>                  | <b>7</b>  |

| <b>6 功能规范的已知设计异常</b>                     | <b>8</b>  |

| <b>7 商标</b>                              | <b>25</b> |

| <b>修订历史记录</b>                            | <b>25</b> |

## 1 简介

本文档介绍了德州仪器 (TI) CMOS 雷达器件 (IWRL6432) 的功能和性能规范的已知异常

## 2 器件命名规则

为了标示所处的产品开发周期阶段，德州仪器 (TI) 为所有雷达/毫米波传感器器件的零件号分配了前缀。每个雷达器件具有以下两种前缀之一：XIx 或 IWRLx (例如：**XI6432 BGABL**)。这些前缀代表了产品开发的发展阶段，即从工程原型 (XI) 直到完全合格的量产器件 (IWRL)。

器件开发进化流程：

**XI** — 试验器件不一定代表最终器件的电气规格，并且可能不使用生产封装流程。

**IWRL** — 完全合格的器件芯片量产版本。

XI 器件在供货时附带如下免责声明：

“开发中的产品用于内部评估用途。”

由于这些器件的预期最终使用故障率仍未确定，德州仪器 (TI) 建议不要将这些器件用于任何生产系统。

### 3 器件标识

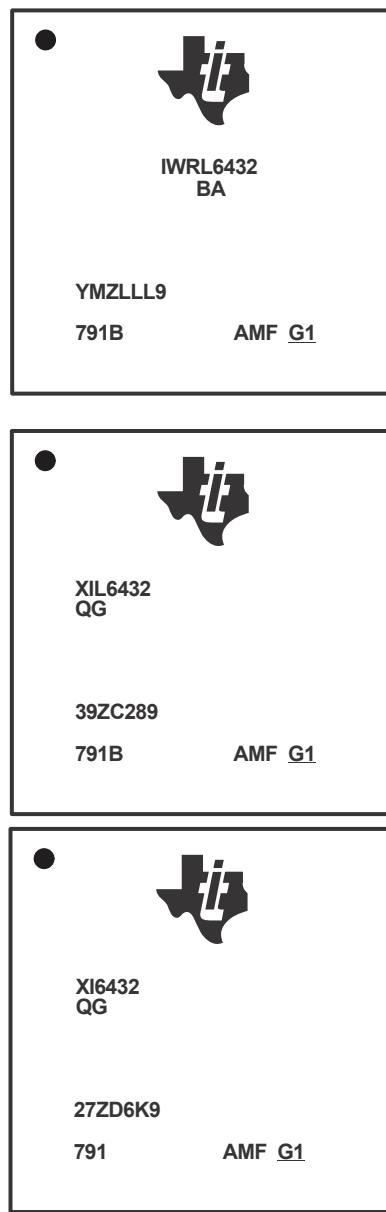

图 3-1 展示了 IWRL6432 雷达器件的封装符号示例。

图 3-1. 器件产品标识示例

此标识编号包含以下信息：

- 第 1 行：TI 标识

- 第 1 行：器件型号

- 第 2 行：安全级别和安全等级

- Q = 非功能安全

- B = SIL 2

- G = 通用

- A = 经认证的引导

- 第 3 行：批次追踪代码

- YM = 年/月代码

## 器件标识

- Z = 组装地点代码

- LLL = 组装批次

- 9 = 主站点代码

- 第 4 行：

- 791 = IWRL6432 标识符

- B = 裸片修订版本

- AMF = 封装标识符

- G1 = “绿色” 封装版本 ( 必须带下划线 )

## 4 使用说明

### 4.1 低功耗拓扑中的上电序列

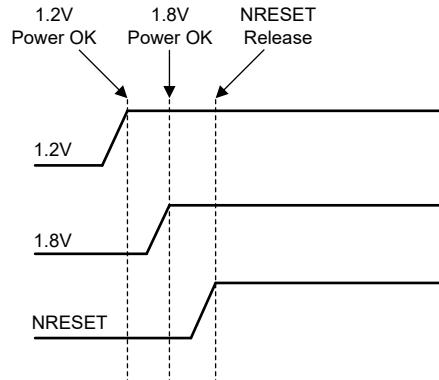

当器件处于低功耗拓扑，且 1.8V 在 1.2V 之前上电时，仅在器件上电期间，在 NRESET 释放之前，在 1.2V 电源轨上可以看到瞬时大电流。为避免这种情况，请在 1.8V 之前上电 1.2V ( VDDIN、VDD\_SRAM 和 VNWA )。

图 4-1. 建议的加电序列

#### 备注

1. 本使用说明仅适用于 1.2V 电源轨。对于 1.2V 电源以外的信号，请参阅数据表中的“器件唤醒序列”图。

2. TI EVM/参考设计中的配电网络遵循数据表中的“器件唤醒序列”，并支持额外电流，而无需先上电 1.2V。

### 4.2 符合 BOM 优化型拓扑中 1.2V 数字 LDO 输出路径的数据表规格

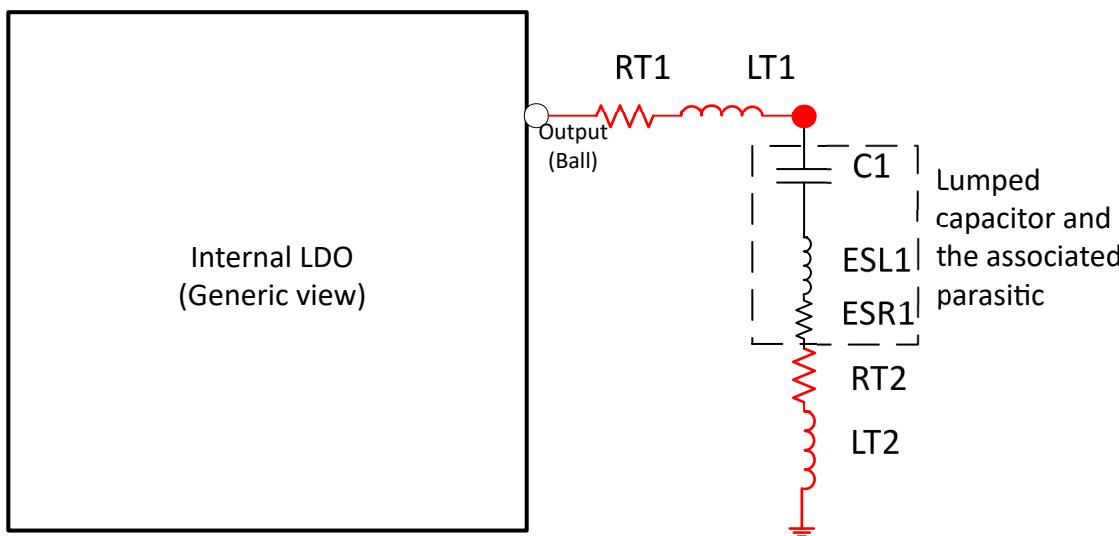

如器件数据表所示，1.2V 数字 LDO 需要一个典型值为  $4.7 \mu F$  的去耦电容器。输出路径不同部分提供的寄生效应如图 4-2 所示。“RT1”和“RT2”分别是焊球到电容器引线走线和接地走线提供的寄生电阻。同样，“LT1”和“LT2”分别是焊球到电容器引线走线和接地走线提供的寄生电感。“ESL1”和“ESR1”是去耦电容器的有效串联电感和电阻。表 4-1 给出了电容和寄生电阻/电感的最小值、最大值和典型值。

图 4-2. 与单个去耦电容器相关的 PCB 寄生元件

表 4-1. 1.2V 数字 LDO 输出

|                 | 最小值 | 典型值 | 最大值 | 单位               |

|-----------------|-----|-----|-----|------------------|

| C 的建议值          | 3.6 | 4.7 | 5.2 | $\mu\text{F}$    |

| 允许的输出寄生电感 $L_p$ | 1   | 1.5 | 2   | nH               |

| 允许的输出寄生电阻 $R_p$ | 15  | 20  | 35  | $\text{m}\Omega$ |

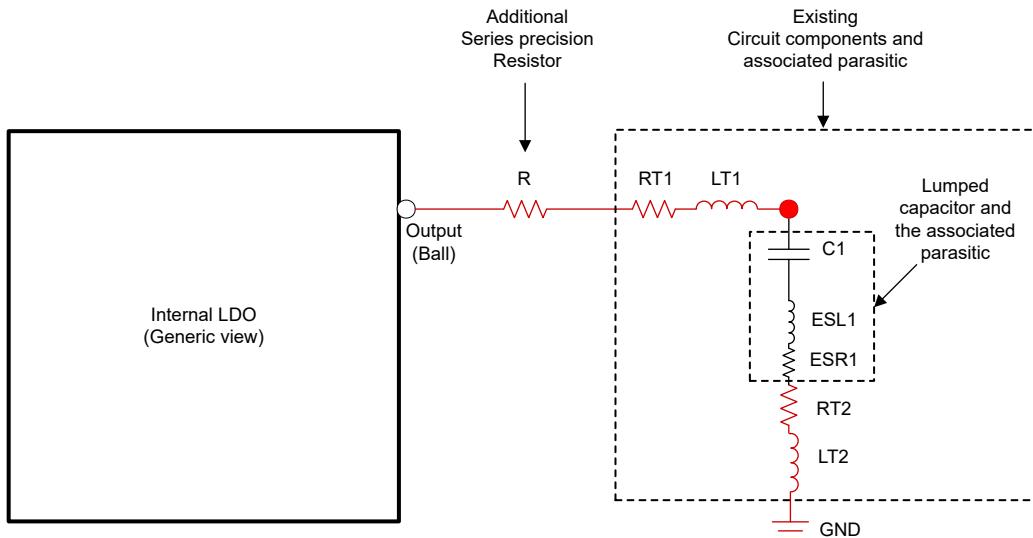

如果在 PCB 设计中无法实现  $R_p$ ，则可以考虑以下权变措施：

在 VDD 输出路径中添加一个串联精密电阻器以及去耦电容器，以获得数据表限制范围内输出路径的等效有效串联电阻。

示例器件型号：PA0402FRL570R02L、20m $\Omega$ 、1% 容差；MFL0603R0200FA、20m $\Omega$ 、1% 总容差；

图 4-3. 解决方法示例

## 5 器件型号/修订版对应关系公告

表 5-1. 器件型号/修订版对应关系公告

| 公告编号    | 公告标题                                                           | IWRL6432 | IWRL6432 |

|---------|----------------------------------------------------------------|----------|----------|

|         |                                                                | ES1.0    | ES2.0    |

| 模拟/毫米波  |                                                                |          |          |

| ANA #48 | 缩小支持的射频频率范围                                                    | x        |          |

| ANA #49 | 模拟温度传感器：在高温下不可用                                                | x        |          |

| ANA #50 | 不支持基于 GPADC 的外部信号监控器                                           | x        |          |

| ANA #51 | 连续波流 CZ 模式：RX 输出代码每 20.97152 毫秒突然跳变一次                          | x        | x        |

| ANA #52 | 启动后未禁用限幅器 LDO 测试负载 (TLOAD)                                     | x        |          |

| ANA #57 | 在存在强近距离反射源的情况下，在 60GHz 出现 SNR 劣化                               | x        | x        |

| 数字子系统   |                                                                |          |          |

| DIG #1  | ePWM：斩波运行模式期间存在干扰                                              | x        | x        |

| DIG #2  | 无法使用 UART A 将序列发生器从深度睡眠低功耗模式唤醒                                 | x        |          |

| DIG #3  | 限制了 UART 波特率                                                   | x        | x        |

| DIG #4  | RS232 自动波特率功能不支持修整后的 ROCSC 差异。                                 | x        | x        |

| DIG #5  | 启用 SPI 智能空闲模式后，不支持通过内部总线访问 SPI 来传输数据。                          | x        | x        |

| DIG #6  | CRC：不支持 CRC 8 位数据宽度以及 CRC8-SAE-J1850 和 CRC8-H2F 在 CAN 模块中的潜在用途 | x        | x        |

| DIG #7  | 在低功耗深度睡眠断电状态下访问集群 3 保留存储器时，APPSS Cortex-M4 无法获得正确的错误响应         | x        |          |

| DIG #8  | 共享 RAM 时钟门控默认值                                                 | x        | x        |

| DIG #9  | 无法从 RS232 访问 TOP_IO_MUX 寄存器空间来进行调试。                            | x        | x        |

| DIG #10 | 帧停止 API 出现错误行为                                                 | x        | x        |

| DIG #14 | 共享存储器中的部分写入导致数据存储损坏                                            | x        | x        |

| DIG #15 | 如果 metainimage 为 2K 的倍数，引导将会失败                                 |          | x        |

| DIG #16 | 通过 SPI 传输小于 8k 的映像时引导失败                                        | x        | x        |

## 6 功能规范的已知设计异常

### ANA #48 缩小支持的射频频率范围

---

受影响的修订版 : IWRL6432 ES1.0

说明 : 此器件版本支持的频率范围为 58-62.5GHz。将在未来进行增强。

权变措施 运行时的线性调频脉冲频率应限制在 58GHz 至 62.5GHz 之间。

受影响的修订版 : IWRL6432 ES2.0

说明 : 此器件版本支持的频率范围为 57-63.9GHz。

权变措施 运行时的线性调频脉冲频率应限制在 57GHz 至 63.9GHz 之间。

**ANA #49**

**模拟温度传感器：在高温下不可用**

**受影响的修订版**

IWRL6432 ES1.0

**详细信息**

在沿通往 GPADC 的布线路径上发现泄漏电流路径。

由于此问题，模拟温度传感器在高温下不可用。

**权变措施**

使用数字温度传感器读数来估算裸片温度。

此问题已在 ES2.0 中修复

**ANA #50****不支持基于 GPADC 的外部信号监控器****受影响的修订版**

IWRL6432 ES1.0

**详细信息**

在沿通往 GPADC 的布线路径上发现泄漏电流路径。

由于此问题，基于 GPADC 的外部信号监控功能无法使用。

**权变措施**

仅对低于 0.4V 的电压使用外部监控功能

此问题已在 ES2.0 中修复

**ANA #51****连续波流 CZ 模式 : RX 输出代码每 20.97152 毫秒突然跳变一次****受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

在连续波流 CZ 模式下，Rx 数据显示输出代码每 20.97152 毫秒突然跳变一次。

使用线性调频脉冲时，这在雷达功能模式下不会导致问题。但是，在实验室中使用连续流模式测试 Rx 链时，会出现此问题。

**权变措施**

要使用连续流 (CW) 模式进行测试，TI 建议从第一个样本开始采集数据，以确保在确定性的样本上发生干扰。请按照以下顺序实现此目的：

- 配置 RDIF ( 雷达数据接口 )

- 装备 DCA1000 ( 数据采集卡 )

- 启用连续流模式。

按此顺序操作不会出现干扰。例如，如果用户分析前 20ms 或 21 到 41ms 间的数据。

**ANA #52****启动后未禁用限幅器 LDO 测试负载 (TLOAD)****受影响版本**

IWRL6432 ES1.0

**详细信息**

出于稳定性目的，默认情况下，启动期间会启用限幅器 LDO TLOAD。启用振荡器后，应自动禁用电流负载，以便降低功耗并提高可靠性。

由于当前未自动关闭负载，因此观察到高于预期的电流 ( $\approx 8\text{mA}$ )。

**权变措施**

建议设置以下字段来显式禁用负载位，以避免不必要的功率烧毁：

TOP\_PRCM : CLK\_CTRL\_REG1\_LDO\_CLKTOP = 0x1

此问题已在 ES2.0 中修复

**ANA #57****在存在强近距离反射源的情况下，在 60GHz 出现 SNR 劣化****受影响的修订版**

IWRL6432 ES1.0, ES2.0

**详细信息**

超过 60GHz 时，合成器存在非线性问题，这会导致在存在强近距离反射源的情况下 RX 输出的本底噪声增加。

**权变措施**

射频带宽较大 ( $>1.5\text{GHz}$ ) 的线性调频脉冲的本底噪声影响可以忽略不计。对于带宽较小的线性调频脉冲，避免使用 60GHz。

**DIG #1****ePWM : 斩波运行模式期间存在干扰****受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

在斩波模式下运行期间，可能会在来自 ePWM 模块的 ePWMA 和 ePWMB 输出信号上观察到干扰。

**权变措施**

如果用例受到干扰，TI 建议将 LPRADAR:APP\_PWM:PCCTL:CHPEN 寄存器位设置为 0，以禁用 PWM 斩波控制功能。

下表列出了上述权变措施的寄存器地址。

| 位 | 名称                          | 地址          |

|---|-----------------------------|-------------|

| 0 | LPRADAR:APP_PWM:PCCTL:CHPEN | 0X57F7 FC3C |

**DIG #2**

**UART : 无法使用 UARTA 将序列发生器从深度睡眠低功耗模式唤醒**

**受影响的修订版**

IWRL6432 ES1.0

**详细信息**

无法使用通用异步接收器/发送器 A (UART A) 将处理器内核从深度睡眠模式唤醒。目前，UART B 中断连接到唤醒中断控制器线路。

**权变措施**

建议使用其他唤醒源 ( 控制器局域网 — 灵活数据速率 (CAN-FD)/UARTB/串行外设接口 (SPI) )

此问题已在 ES2.0 中修复。

**DIG #3****UART : 限制了 UART 波特率****受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

由于设计限制（与时钟方案有关），UART 不支持高于 115200 比特每秒的标准波特率。可支持最高 1.25Mbps 的更高波特率，但波特率是非标准的。

需要 UART 的应用无法使用高于 115200 比特每秒的标准波特率

支持的标准波特率：

| XTAL (MHz)  | 40        |      |

|-------------|-----------|------|

| 理想波特率 (bps) | 实际波特率     | 误差 % |

| 115200      | 113636.36 | 1.36 |

| 76800       | 75757.58  | 1.36 |

支持的非标准波特率：

| XTAL (MHz)  | 40      |

|-------------|---------|

| 最大波特率 (bps) | 1250k   |

|             | 833.33k |

|             | 625k    |

|             | 500k    |

|             | 416.66k |

|             | 357.14k |

|             | 312.5k  |

**权变措施**

TI 建议根据应用需求使用以下权变措施：

- 如果外部 MCU 可支持相同的非标准波特率，使用非标准波特率可提供最高 1.25Mbps 的吞吐量。

- 如果用例需要更高的吞吐量，则改用 SPI。

**DIG #4**

**RS232 : 自动波特率功能不支持修整后的 RCOSC 差异**

**受影响版本**

IWR6432 ES1.0, ES2.0

**详细信息**

修整 RCOSC 后，预期的时钟频率和观察到的频率差异 ( RC 时钟的容差 ) 不支持 RS232 所需的自动波特率设置。

目前，对于 64xx ES2.0，默认会禁用自动波特率

**DIG #5**

启用 SPI 智能空闲模式后，不支持通过内部总线访问 SPI 来传输数据。

**受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

在第一次触发以进行数据传输访问之前，需要禁用 SPI 智能空闲模式。如果需要启用 SPI 智能空闲模式，该模式必须在访问完成后再次启用该模式。

**权变措施**

TI 建议遵循以下操作顺序：

自动唤醒 = 1 且在控制器模式下

1. 根据需要配置 McSPI

2. 在确保没有来自/到 SPI 的待处理事务，且 CPU 或 DMA 不会再访问 McSPI 之后，启用“智能空闲”模式（对于 SPI1，设置 LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE；对于 SPI 2，设置 LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE）

3. 如果需要对 McSPI 进行寄存器或存储器访问，禁用“智能空闲”模式（对于 SPI 1，设置 LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE=0；对于 SPI 2，设置 LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE=0）

4. 在控制器模式下，外部主机不会切换 SPI\_CS，因此不会发生任何唤醒操作 =>（对于 SPI 1，设置 LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_AUTO\_EN 为 1 或 0，以及设置 LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_AUTO\_EN 为 1 或 0）没有任何区别

自动唤醒 = 1 且在外设模式下

1. 根据需要配置 McSPI

2. 在确保没有来自/到 SPI 的待处理事务，且 CPU 或 DMA 不会再访问 McSPI 之后，启用“智能空闲”模式（对于 SPI1，设置 LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE；对于 SPI 2，设置 LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE）

3. 如果任何控制器(DMA/CPU)需要对 McSPI 进行寄存器或存储器访问，禁用“智能空闲”模式（对于 SPI 1，设置 LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE=0；对于 SPI 2，设置 LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE=0）

4. 如果有来自 McSPI 的唤醒信号（由于某个 SPI\_CS 切换操作），则会自动启用时钟。

5. 禁用“智能空闲”配置（对于 SPI 1，设置 LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE=0；对于 SPI 2，设置 LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE=0），以访问寄存器。

下表列出了针对上述权变措施的寄存器地址。

| 位 | 名称                                       | 地址         |

|---|------------------------------------------|------------|

| 0 | LPRADAR:APP_CTRL:SPI1_SMART_IDLE_ENABLE  | 0x560603A8 |

| 2 | LPRADAR:APP_CTRL:SPI1_SMART_IDLE_AUTO_EN | 0x560603A8 |

| 0 | LPRADAR:APP_CTRL:SPI2_SMART_IDLE_ENABLE  | 0x560603AC |

| 2 | LPRADAR:APP_CTRL:SPI2_SMART_IDLE_AUTO_EN | 0x560603AC |

|        |                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------|

| DIG #6 | <b>CRC</b> : 不支持 CRC 8 位数据宽度以及 <b>CRC8-SAE-J1850</b> 和 <b>CRC8-H2F</b> 在 CAN 模块中的潜在用途                                            |

| 受影响版本  | IWRL6432 ES1.0, ES2.0                                                                                                            |

| 详细信息   | <ol style="list-style-type: none"><li>1. 不支持 8 位数据宽度。支持的最小数据宽度为 16 位。</li><li>2. 不支持 CRC 类型 CRC8-SAE-J1850 和 CRC8-H2F。</li></ol> |

| 权变措施   | <ol style="list-style-type: none"><li>1. 支持 16/32/64 位数据宽度。</li><li>2. TI 建议不要使用上述不受支持的多项式。</li></ol>                            |

|                |                                                                      |

|----------------|----------------------------------------------------------------------|

| <b>DIG #7</b>  | 在低功耗深度睡眠断电状态下访问集群 3 保留存储器时，APPSS Cortex-M4F 无法获得正确的错误响应              |

| <b>受影响的修订版</b> | IWRL6432 ES1.0                                                       |

| <b>详细信息</b>    | Cortex-M4F 在断电状态下尝试访问集群 3 存储器时，生成错误的逻辑不正确，导致 Cortex-M4F 无法获得正确的错误响应。 |

| <b>权变措施</b>    | 在低功耗深度睡眠断电状态下，软件不应尝试访问集群 3 保留存储器<br>此问题已在 ES2.0 中修复。                 |

**DIG #8**

**共享 RAM 时钟门控默认值**

**受影响的修订版**

IWRL6432 ES1.0, ES2.0

**详细信息**

在未对时钟门控寄存器重新编程的情况下，退出深度睡眠模式时可能会损坏共享 RAM 数据。

前端控制器子系统 (FECSS)、应用子系统 (APPSS) 和硬件加速器子系统 (HWASS) 共享存储器时钟门控的复位值为 1。时钟 ICG 控制信号来自以下寄存器。

| 位 | 名称                                                                                   | 地址         |

|---|--------------------------------------------------------------------------------------|------------|

| 0 | LPRADAR:FEC_CTRL:FECSS_SHARED_MEM_CLK_GATE:FECSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE | 0x5200002C |

| 0 | LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE | 0x56060398 |

| 2 | LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM1_HWA_ENABLE | 0x56060398 |

当 FECSS 通过 AHB 访问共享存储器时，若 APPSS 试图通过 VBUSM SCR 访问共享存储器组 0，会观察到 APPSS 从共享 RAM 中读取到错误的零值。

如果根据分配情况仅启用其中一个时钟门 ( HWA 或 FEC/APP )，则可以正确读取数据。由于时钟门控控制信号来自控制信号寄存器空间，因此每次退出深度睡眠模式后，这些值会再次被复位，需要重新编程。

**权变措施**

根据不同的共享存储器配置，对到达共享存储器的时钟 ICG 控制信号进行编程。每次退出深度睡眠模式后，都需要对 ICG 控制信号进行重新编程。

| 配置              | 软件注意事项                                                                                                                                                                                                                                                            |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 存储器与 M3 共享      | 禁用以下 ICG 控制信号：-<br>LPRADAR:FEC_CTRL:FECSS_SHARED_MEM_CLK_GATE:<br>FECSS_SHARED_MEM_CLK_GATE_HWA_ENABLE                                                                                                                                                            |

| 前 128KB 与 M4 共享 | 禁用以下 ICG 控制信号：-<br>LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:<br>APPSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE                                                                                                                                                       |

| 256KB 与 M4 共享   | 禁用以下 ICG 控制信号：-<br><ul style="list-style-type: none"> <li>LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:<br/>APPSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE</li> <li>LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:<br/>APPSS_SHARED_MEM_CLK_GATE_MEM1_HWA_ENABLE</li> </ul> |

**DIG #9**

无法从 RS232 访问 **TOP\_IO\_MUX** 寄存器空间来进行调试

**受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

RS232 无法写入 **TOP\_IO\_MUX** 寄存器，除非该空间已针对用户模式访问进行了编程。

**权变措施**

TI 建议按以下顺序操作：

1. 从处理器或 DAP：解锁 **TOP\_IO\_MUX** 寄存器（通过编程

`LPRADAR:TOP_IO_MUX:IOCFGKICK0 = 83E7 0B13h` 和

`LPRADAR:TOP_IO_MUX:IOCFGKICK1 = 95A4 F1E0h`）

2. 从处理器或 DAP：写入 **TOP\_IO\_MUX** 寄存器，

`LPRADAR:TOP_IO_MUX:USERMODEEN` 应设置为 `0xADADADAD`

3. 现在可以从 RS232 访问 **TOP\_IO\_MUX** 寄存器了。

下表列出了针对上述权变措施的寄存器地址。

| 位    | 名称                            | 地址         |

|------|-------------------------------|------------|

| 0:31 | LPRADAR:TOP_IO_MUX:IOCFGKICK0 | 0x5A000068 |

| 0:31 | LPRADAR:TOP_IO_MUX:IOCFGKICK1 | 0x5A00006C |

| 0:31 | LPRADAR:TOP_IO_MUX:USERMODEEN | 0x5A000060 |

**DIG #10**

**帧停止 API 出现错误行为**

**受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

帧定时器将帧停止命令锁存在硬件寄存器中，该命令在当前帧结束时生效。由于锁存的停止位，在帧定时器已经停止时发出帧停止 API，导致下一帧触发意外停止。

**权变措施**

1. 避免非必要的传感器停止 API。

2. 该应用可能必须等待一个帧周期完成，然后才能停止帧。

3. 应用等待 FECSS 在收到帧停止确认后，完成突发结束和帧结束活动。

**DIG #14****共享存储器中的部分写入导致数据存储损坏****受影响的修订版**

IWRL6432 ES1.0, ES2.0

**详细信息**

内部共享存储器具有 ODD 和 EVEN 存储体结构。对于特定地址范围，对 EVEN 存储体进行部分写入（小于 32 位）时，会通过总线上的下一个数据损坏 ODD 存储体中相同地址的内容。当共享存储器分配给 M4/M3 时，若先对地址 A 进行连续全字写入访问，再对地址 B 进行子字写入访问，将导致地址 A 的数据损坏。

当存储器与 M4/M3 共享时，以下地址范围会出现问题：

| 内存                 | 地址范围                      |

|--------------------|---------------------------|

| APP_CPU_SHARED_RAM | 0x0048 0000 - 0x004B FFFC |

| FEC_CPU_SHARED_RAM | 0x2120 8000 - 0x2121 FFFC |

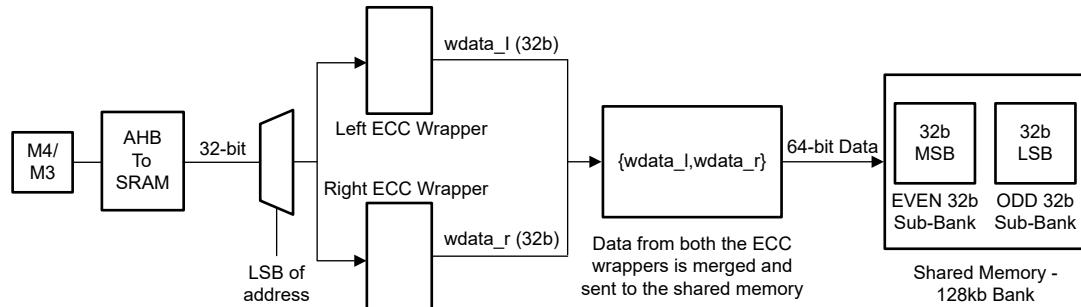

图 6-1. 与 M4/M3 共享时的共享存储器逻辑图

与 M3/M4 共享时，输入数据位宽为 32 位，如图所示。因此，根据地址的 LSB，信号会发送到左侧或右侧 ECC 包装器。

**权变措施**

1. 与处理器共享时，使用共享存储器作为代码存储器。

2. 对非功能安全器件禁用 ECC – 在非功能安全器件的 RBL 中，禁用共享存储器的 ECC。

**DIG #15**

如果 **metaimage** 为 2K 的倍数，引导将会失败

**受影响版本**

IWR6432 ES2.0

**详细信息**

如果 **metaimage** 为 2048 字节的倍数，引导会失败。

**权变措施**

1. 添加一个固定的非易失性变量，以增加 **metaimage** 的大小，使其不与 2048 字节对齐。

2. 将 MMWAVE-L-SDK 更新到 5.4 或更高版本；毫米波 LSDK 5.4 及更高版本对 **metaimage** 进行了更改，在映像为 2048 字节的倍数时会添加一个最小配置文件（约 64 字节）。

**DIG #16****通过 SPI 传输小于 8k 的映像时引导失败****受影响版本**

IWRL6432 ES1.0, ES2.0

**详细信息**

在少数情况下 ( 在 SPI 连续下载期间 ) 不会进行 EDMA 地址链接 , 因此对于下表中提到的特定 metaimage 大小范围 , 通过 SPI 引导连续下载映像会失败 :

| 映像大小 ( 字节 )           | 是否存在问题 |

|-----------------------|--------|

| <2048                 | 否      |

| >2048 且 <4096         | 否      |

| $\geq 4096$ 且 $<6144$ | 是      |

| $\geq 6144$ 且 $<8192$ | 是      |

| $\geq 8192$           | 否      |

**权变措施**

通过 SPI 引导时使用大于 8KB 的映像。如果映像较小 , 在编译期间附加常量数据来创建大于 8KB 的映像。

## 7 商标

所有商标均为其各自所有者的财产。

## 修订历史记录

### Changes from JULY 25, 2025 to DECEMBER 15, 2025 (from Revision B (July 2025) to Revision C (December 2025))

|                                       | Page |

|---------------------------------------|------|

| • ( 使用说明 ) : 已添加该章节.....              | 5    |

| • 器件型号/修订版对应关系公告 : 新增了 ANA#57 公告..... | 7    |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月