*Errata***CC2340R5-Q1 SimpleLink™ 无线 MCU 器件修订版本 B****摘要**

本文档介绍了 CC2340R5-Q1 和 CC2340R53-Q1 SimpleLink™ 器件功能规格的已知例外情况（公告）。

**内容**

|                                  |           |

|----------------------------------|-----------|

| <b>1 公告汇总表</b> .....             | <b>2</b>  |

| <b>2 命名规则、封装编号法和修订版本标识</b> ..... | <b>2</b>  |

| 2.1 器件和开发支持工具命名规则.....           | 2         |

| 2.2 支持的器件.....                   | 3         |

| 2.3 封装编号法和修订版本标识.....            | 3         |

| <b>3 公告</b> .....                | <b>3</b>  |

| <b>4 修订历史记录</b> .....            | <b>10</b> |

**商标**

SimpleLink™ and 德州仪器 (TI)™ are trademarks of Texas Instruments.

所有商标均为其各自所有者的财产。

## 1 公告汇总表

表 1-1 列出了所有公告、受影响的模块以及适用的器件修订版本。

表 1-1. 公告汇总表

| 模块     | 说明                                             | 受影响的器件修订版本  |              |

|--------|------------------------------------------------|-------------|--------------|

|        |                                                | CC2340R5-Q1 | CC2340R53-Q1 |

|        |                                                | 受影响版本       |              |

| SPI    | 公告 SPI_04 - SPI 永久等待 CPU 干预导致的挂起场景             | B           | B            |

| ADC    | 公告 ADC_08 - 在重复单次、序列和重复序列转换模式下不会清除 ADC BUSY 位。 | B           | B            |

| ADC    | 公告 ADC_09 - ADC 可能存在随机转换错误。                    | B           | B            |

| BATMON | 公告 BATMON_01 - 温度测量不正确                         | B           | B            |

| BATMON | 公共 BATMON_02 - 待机时来自 BATMON 的虚假温度更新中断          | B           | B            |

| CKM    | 公告 CKM_01 - 待机唤醒期间的跟踪环路问题                      | 不受影响        | B            |

| CKM    | 公告 CLK_01 - 仅使用 LFOSC 时，无法维持蓝牙低耗能链路            | B           | B            |

| I2C    | 公告 I2C_02 - SDA 和 SCL 漏极开路输出缓冲器问题              | B           | B            |

| GPIO   | 公告 GPIO_01 - 漏极开路配置可以驱动短高电平脉冲                  | B           | B            |

| PMU    | 公告 PMU_01 - 欠压检测 (BOD) 阈值转换缓慢可能会导致器件挂起         | B           | B            |

| UART   | 公告 UART_01 - UART 可能会发出虚假的 μ DMA 写入突发请求        | B           | B            |

表 1-2. 按器件型号列出的最新修订版本

| 器件型号         | 修订版本 |

|--------------|------|

| CC2340R5-Q1  | B    |

| CC2340R53-Q1 | B    |

## 2 命名规则、封装编号法和修订版本标识

### 2.1 器件和开发支持工具命名规则

为了标示产品开发周期所处的阶段，德州仪器 (TI)<sup>TM</sup> 为所有器件和支持工具提供了阶段标识符。为器件分配了以下两个标识符中的一个：X 或 P，表示硅片的非生产版本（例如 CC2340Q/R53/TI X）。完全合格的生产版本不带标识符。德州仪器 (TI) 为其支持工具推荐使用两种可能的标识符：TMDX 和 TMDS。这些标识符代表了产品开发的发展阶段，即从工程原型 (X/TMDX) 直到完全合格的生产器件工具 (TMDS)。

器件开发进化流程：

**X** 试验器件不一定代表最终器件的电气规格，并且可能不使用生产封装流程

**P** 原型器件不一定是最终的器件芯片，并且不一定符合最终电气规格

**无标识符** 完全合格的器件芯片生产版本

支持工具开发演变流程：

**TMDX** 尚未完成德州仪器 (TI) 内部合格性测试的开发支持工具

**TMDS** 完全合格的开发支持产品

X 和 P 器件和 TMDX 开发支持工具在供货时附带如下免责条款：

“开发中的产品用于内部评估用途。”

生产器件和 TMDS 开发支持工具已进行完全特性描述，并且器件的质量和可靠性已经完全论证。TI 的标准保修证书对该器件适用。

原型器件（标记为 X 或者 P）的故障率大于完全合格生产器件。由于其长期可靠性尚未完全确定，德州仪器 (TI) 建议不要将其用于生产系统。终端产品中只应使用完全合格的生产器件。

## 2.2 支持的器件

本文档支持以下器件：

- [CC2340R5-Q1](#)

- [CC2340R53-Q1](#)

## 2.3 封装编号法和修订版本标识

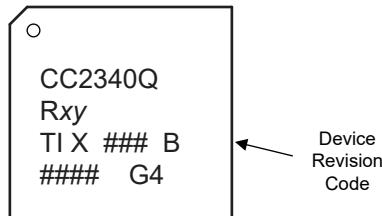

图 2-1 和 表 2-1 介绍了封装编号法和器件修订版代码。

图 2-1. 封装符号

**xy** 表示闪存和 RAM 规格

表 2-1. 版本标识

| 器件修订版本代码 | 硅片版本  |

|----------|-------|

| B        | PG2.0 |

## 3 公告

### SPI\_04

#### SPI 永久等待 CPU 干预导致的挂起场景

受影响版本

B

详细信息

当 CPU 读取或写入 SPI FIFO 时，如果使用 FIFO 电平触发器来生成中断，系统可能会发生挂起。在处理第一个中断后，FIFO 电平可能会永久低于或高于配置的阈值，并且不会生成后续 CPU 中断。这可能会导致 SPI 永久等待 CPU 干预，因此导致挂起的场景。

权变措施

1. 在 SPI 中使用 FIFO 状态轮询，而不依赖于 FIFO 电平配置的中断，或

2. 仅使用空/溢出中断，而不使用 FIFO 电平配置的中断，或

3. 使用 FIFO 电平配置的中断以及空（适用于 TXFIFO）和溢出（适用于 RXFIFO）作为失效防护，以避免挂起的场景。

### ADC\_08

#### 在重复单次、序列和重复序列转换模式下，ADC 繁忙位不会被清除。

受影响版本

B

说明

当 ADC 在 MEMCTLx 寄存器中配置为重复单次、序列或重复序列转换模式且触发策略为“触发下一个”时，尝试通过清零 ENC 位来停止转换序列的软件不会清除 STATUS 寄存器中的 BUSY 位。对于具有触发下一个策略的序列转换模式，BUSY 位在转换序列结束时清零。

权变措施

在上述 ADC 操作场景中，若要停止转换并清除 BUSY 位，可以执行以下软件序列。

1. 写入 CTL0.ENC = 0

2. 将 CTL1.TRIGSRC 更改为 SOFTWARE

3. 写入 CTL1.SC=1

**ADC\_09****ADC 可能具有随机转换错误****受影响版本**

B

**说明**

ADC 在 4 亿次 ADC 转换中的误差率可能高达 1。转换误差时，该误差会导致 ADC 的数字输出发生跳变，而 ADC 输入电压没有相应的变化，否则称为“闪码”。当 ADC 用于 12 位分辨率设置时，跳变幅度为 64 LSB，高于或低于预期的 ADC 输出。对于 10 位分辨率，跳变的幅度降至  $\pm 16$  LSB；而当设置为 8 位分辨率时，则降至  $\pm 4$  LSB。

**权变措施**

通过将 ADC.DEBUG1:CTRL[10:9] 位设置为高电平，可以在 100 亿个 ADC 转换中将错误率降至 1。

还可以考虑其他软件权变措施，例如三选一，即在三个连续样本中丢弃标准偏差最高的样本，并对另外两个样本取平均值以生成 ADC 输出。

通过软件对 16 个连续的 ADC 输出求平均值，可在设置为 12 位分辨率时将 ADC 输出的偏差降至  $\pm 4$  LSB。

这些权变措施将整合到 SimpleLink™ 低功耗 F3 软件开发套件 (SDK) 的未来版本中。

**BATMON\_01****温度测量值不正确****受影响版本**

B

**说明**

启用迟滞时，BATMON 可以报告不正确的温度。为了防止报告的温度可能不正确，用户必须始终禁用 BATMON 迟滞。

**权变措施**

迟滞由 PMUD.CLT[2] HYST\_EN 位控制。

默认启用迟滞（复位值=1），因此必须在启动期间主动禁用迟滞。

可以使用以下命令清除 PMUD.CLT[2] HYST\_EN 位来禁用迟滞：

`HWREG( PMUD_BASE + PMUD_O_CTL ) = ( PMUD_CTL_CALC_EN | PMUD_CTL_MEAS_EN )`

此权变措施已集成到 SimpleLink™ 低功耗 F3 软件开发套件 (SDK) 版本 8.10 和更高版本中。

**BATMON\_02****待机时 BATMON 产生虚假温度更新中断****受影响版本**

B

**说明**

当 PMUD.EVENT.TEMP\_UPDATE 用作从待机状态唤醒源时，BATMON 可能会发出虚假温度更新中断。

**权变措施**

不使用 PMUD.EVENT.TEMP\_UPDATE 作为唤醒源，而是考虑 PMUD.EVENT.TEMP\_OVER\_UL（当前温度超过设定的上限）或 PMUD.EVENT.TEMP\_BELOW\_LL（当前温度低于设定的下限）。

当使用 PMUD.EVENT.TEMP\_OVER\_UL 或 PMUD.EVENT.TEMP\_BELOW\_LL 作为唤醒中断时，必须启用的其他设置，包括：

- 通过将 PMCTL.VDDRCTL.SELECT 设置为 0x0，选择 GLDO 作为 VDDR 调节的源。

**备注**

这会导致待机功耗略有增加。有关确切的详细信息，请查看数据表的“功耗 - 电源模式”部分。

- 将 SYS0.TMUTE4.RECHCOMPREFLVL 设为 0x2。

- 将 SYS0.TMUTE5.GLDOISET 设为 0x1E。

此权变措施可集成到 SimpleLink™ 低功耗 F3 软件开发套件 (SDK) 的未来版本中。

**CKM\_01****待机唤醒期间的跟踪环路问题****受影响版本**

CC2340R53-Q1 修订版 B

**详细信息**

在少数极端情况下，HFOSC 跟踪环路会在从待机状态恢复时停止工作，并设置 TRACKREFLOSS，指示跟踪环路所选的基准时钟丢失。

**权变措施**

待机进入序列包括禁用软件覆盖和清除 CKM LDO 控制位。这些写入必须按顺序进行，以便首先清除软件覆盖，然后再将 LDOCTL 位全部设置为零。

如果这些设置并行发生，则跟踪环路在某些情况下可能会卡住。

该权变措施已在电源驱动程序中实施，是 9.10 SDK 版本的一部分。

**CLK\_01****仅使用 LFOSC 时，无法维持蓝牙低耗能链路。****受影响版本**

B

**说明**

如果将 LFOSC 用作睡眠时钟，由于随机时序误差高于 500PPM，一小部分器件无法维持蓝牙低耗能链路。

**权变措施**

SimpleLink F3 SDK >= 8.10.xx 中提供了一种软件权变措施，当仅使用 LFOSC 时，允许器件以广播者、观察者和外设角色运行。使用软件权变措施时，如果出现时序误差，器件可能会出现短时间的吞吐量降低和功耗增加。此软件权变措施不支持中央角色。为完全避免功耗和连接吞吐量增加的后果或支持中央角色，TI 建议使用外部 32.768kHz 晶体。

## I<sup>2</sup>C\_01

## SDA 和 SCL 漏极开路输出缓冲器问题

### 受影响版本

B

### 说明

SDA 和 SCL 输出通过推挽三态输出缓冲器而非 I<sup>2</sup>C 要求的漏极开路输出缓冲器来实现。虽然推挽三态输出缓冲器可以用作漏极开路输出，但内部时序偏斜问题会导致输出在禁用前驱动逻辑高电平约 1ns 至 2ns 的持续时间。仅当 SCL 或 SDA 输出从驱动的低电平状态转换为高阻抗状态时，才会出现意外的高电平脉冲。

这一短暂的高电平脉冲会在 I<sup>2</sup>C 信号走线中注入能量，导致 I<sup>2</sup>C 信号由于多次传输线路反射而持续一段时间的振铃。这种振铃不会导致 SDA 信号出现问题，因为它仅在预计 SDA 会改变逻辑电平时发生，并且振铃在接收器件锁存的数据之前有时间衰减。振铃幅度可能足以在此振铃期间的前几纳秒内多次超过 SCL 输入缓冲器开关阈值，从而导致时钟毛刺。如果振铃幅度在前 50ns 内衰减，则不会造成问题，因为系统会要求 I<sup>2</sup>C 器件对 SCL 输入进行滤波以消除时钟毛刺。因此，设计 PCB 信号走线以将振铃的持续时间限制在 50ns 以内非常重要。减少振铃的一种可能方法是，在 SCL 和 SDA 端子附近插入串联端接电阻器，以衰减传输线路反射。

目标开始 ACK 周期时，此问题还可能导致 SDA 输出在意外高电平脉冲的持续时间内与目标 SDA 输出发生争用。发生这种情况是因为在发生意外的高电平脉冲之前，目标可能已经将 SDA 驱动为低电平。由于这段短暂的争用期而在 SDA 上产生的毛刺不会导致任何 I<sup>2</sup>C 协议问题，但峰值电流会对两个 I<sup>2</sup>C 器件施加不必要的应力，并可能导致电源噪声增加。因此，需要在相应的 SDA 端子附近放置一个串联端接电阻器，以限制短暂争用期间的电流。

当连接到支持时钟延展的 I<sup>2</sup>C 目标器件时，SCL 上也可能会出现类似的争用问题。发生这种情况是因为在发生意外的高电平脉冲之前，目标已将 SCL 驱动为低电平。由于这段短暂的争用期而在 SCL 上产生的毛刺不会导致任何 I<sup>2</sup>C 协议问题，因为 I<sup>2</sup>C 器件需要在其 SCL 输入端应用毛刺滤波器。但是，峰值电流会对两个 I<sup>2</sup>C 器件施加不必要的应力，并可能导致电源噪声增加。因此，需要在相应的 SCL 端子附近放置一个串联端接电阻器，以限制短暂争用期间的电流。

如果连接了另一个控制器，SCL 和 SDA 输出端的意外高电平脉冲可能会导致在时钟同步和仲裁期间发生争用。上面介绍的串联端接电阻器也可限制此用例中的争用电流，而不会产生任何 I<sup>2</sup>C 协议问题。

### 权变措施

在 SCL 和 SDA 信号端插入串联端接电阻器，并将其放在 SCL 和 SDA 端子附近，与 SCL 和 SDA 上拉电阻器一起布置。

通过控制输出以使用最小驱动强度和降低的压摆率，也可以减少振铃。这些选项只能在支持高驱动输出的引脚上进行配置。标准驱动引脚没有配置选项。

**GPIO\_01****漏极开路配置可以驱动短高电平脉冲****受影响版本****B****说明**

每个 DIO 都可以使用 IOC<sub>x</sub> 寄存器配置为漏极开路模式。

但是，内部器件时序问题可能会导致 GPIO 在进入或退出高阻抗状态期间驱动逻辑高电平约 1ns-2ns。如果另一个驱动器同步驱动低电平，这种不必要的高电平可能会导致 GPIO 与线路上的另一个漏极开路驱动器发生争用。我们不希望出现此争用，因为它会对两个器件施加应力，并导致信号上出现短暂的中间电压电平。如果接收器逻辑中没有足够的逻辑滤波来滤除此短暂脉冲，则该中间电压电平可能会被错误地解读为高电平。

**权变措施**

如果存在争用问题，请勿使用 GPIO 的漏极开路功能；请改为在软件中仿真漏极开路模式。通过将 GPIO 数据 (DOUT31\_0.DIO<sub>x</sub>) 设置为静态 0 并驱动 GPIO 输出启用 (DOE31\_0.DIO<sub>x</sub>) 以启用或禁用驱动低电平，可以实现漏极开路仿真。有关实现示例，请参阅以下代码。

```

#include <ti/devices/cc23x0r5/driverlib/gpio.h>

/* Call driver init functions */

GPIO_init();

//Set GPIO data (DOUT31_0.DIOx) to static 0

GPIOClearDio(CONFIG_GPIO_LED_0);

while(1) //loop below toggles the LED on and off every 1 second

{

GPIOSetOutputEnableDio(CONFIG_GPIO_LED_0, 1);

sleep(1);

GPIOSetOutputEnableDio(CONFIG_GPIO_LED_0, 0);

sleep(1);

}

```

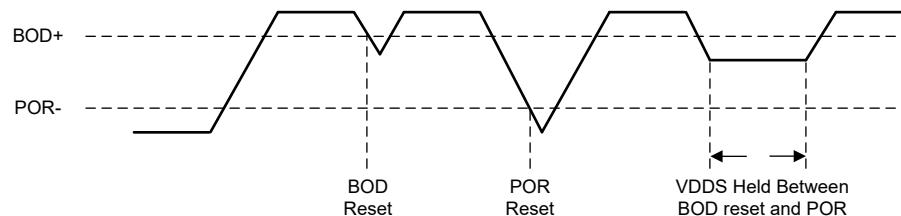

**PMU\_01****欠压检测 (BOD) 阈值转换缓慢可能会导致器件挂起****受影响版本****B****详细信息**

如果 VDDS 电源电压保持在 BOD 阈值区域内（约 1.68V），器件在极少数情况下可能会进入锁定状态。在此状态下，器件会消耗约 2.25mA 的电流，并且即使 VDDS 电源电压随后增加到 BOD 阈值以上也不会恢复。从此状态恢复需要引脚复位或将 VDDS 电源电压降至上电复位 (POR) 阈值 (1.0V) 以下，从而触发 POR 复位。

如果在引导代码执行的特定阶段发生欠压检测 (BOD) 事件，则会触发锁定状态。有两个关键的窄时间窗口，每个窗口的持续时间约为 10ns，这两个时间窗口都在启动引导代码的复位事件后 100 μs 到 1ms 内出现。当电源电压缓慢斜升至超过 BOD 阈值时，通常会出现此问题。在这种情况下，电源电阻与器件启动电流相结合可能会导致 VDDS 电压在器件复位时反复降至 BOD 阈值以下，使进入锁定状态的可能性提高。

对于锂离子和镍氢可充电电池，一级保护机制（断开芯片 VDDS 电源）通常可阻止器件在电池放电期间进入此状态，因为器件电源会降至 POR 阈值以下。

即使使用不可充电（主）电池，仍可能出现此问题，尤其是在电池接近使用寿命终止且电压缓慢下降时。在这些情况下，可能并不一定需要采取权变措施，因为器件最终需要更换电池，这也会触发上电复位。但是，不能排除锁定的风险。

图 3-1. 显示发生情况的图表

**权变措施**

必须实现以下权变措施：

该器件指定的工作电源电压范围是 1.72V 至 3.8V。使用可充电电池时，电池保护系统必须确保满足以下条件之一：

- 上电后器件电源电压保持等于或高于最小工作电源电压 (1.72V)，或

- 如果器件电源放电至低于最低工作电源电压 (1.72V)，则电源充电至再次高于最低工作电源电压 (1.72V) 时，该器件必须复位（引脚或上电复位）。

**UART\_01****UART 可能会发出虚假的  $\mu$ DMA 写入突发请求****受影响版本**

B

**详细信息**

当 FIFO 中的条目数小于或等于配置的突发 FIFO 阈值时，UART 会发出  $\mu$ DMA 突发写入请求。如果总 FIFO 条目数仍低于配置的阈值，则会发出后续的  $\mu$ DMA 写入突发请求。与  $\mu$ DMA 发出结束其突发活动状态的信号相比，UART 需要一个额外的 SVT 时钟周期来更新内部 FIFO 电平。在极端情况下，根据初始 UART FIFO 电平、为突发请求配置的 FIFO 阈值、互连延迟等，UART 内的这种额外时钟延迟可能会导致生成向  $\mu$ DMA 发出的虚假写入突发请求，这可能会导致  $\mu$ DMA 响应此请求的最后一次或几次写入操作丢失。此问题在 UART 读取突发请求时不会发现，因为  $\mu$ DMA 会等待读取完成，然后再发出读取突发结束信号。

**权变措施**

与 UART 配合使用时，必须将  $\mu$ DMA SETBURST 配置为用于突发请求。

$\mu$ DMA 仲裁数必须为 2。

对于写入突发触发器，TX FIFO 电平触发必须设置为  $\leq 1/4$  空

## 4 修订历史记录

注：以前版本的页码可能与当前版本的页码不同

**Changes from SEPTEMBER 30, 2024 to JULY 16, 2025 (from Revision A (September 2024) to Revision B (July 2025))**

|                                                | Page |

|------------------------------------------------|------|

| • 添加了 CC2340R53-Q1.....                        | 1    |

| • 添加了公告 CKM_01、BATMON_02、PMU_01 和 UART_01..... | 2    |

| • 更新了说明.....                                   | 3    |

| • 增加了公告 ADC_09.....                            | 4    |

| • 更新了说明.....                                   | 5    |

| • 更新了说明.....                                   | 5    |

**Changes from DECEMBER 1, 2023 to SEPTEMBER 30, 2024 (from Revision \* (December 2023) to Revision A (September 2024))**

|                      | Page |

|----------------------|------|

| • 修正了整个文档中的拼写错误..... | 1    |

| • 增加了公告 CLK_01.....  | 2    |

| • 增加了公告 I2C_02.....  | 2    |

| • 增加了公告 GPIO_01..... | 2    |

| • 增加了公告 ADC_09.....  | 2    |

| • 更新了说明.....         | 3    |

| • 增加了公告 ADC_09.....  | 4    |

| • 更新了说明.....         | 5    |

| • 更新了说明.....         | 5    |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025 , 德州仪器 (TI) 公司