*Errata*

# ***MSPM0G351x、MSPM0G151x、MSPM0G351x-Q1、 MSPM0G3529-Q1 微控制器***

**摘要**

本文档介绍了功能规格的已知例外情况（公告）。

**内容**

|                           |           |

|---------------------------|-----------|

| <b>1 功能公告</b> .....       | <b>1</b>  |

| <b>2 预编程的软件公告</b> .....   | <b>2</b>  |

| <b>3 仅调试公告</b> .....      | <b>2</b>  |

| <b>4 已通过编译器公告修复</b> ..... | <b>3</b>  |

| <b>5 器件命名规则</b> .....     | <b>3</b>  |

| 5.1 器件编号法和修订版本标识.....     | 3         |

| <b>6 公告说明</b> .....       | <b>5</b>  |

| <b>7 商标</b> .....         | <b>23</b> |

| <b>8 修订历史记录</b> .....     | <b>23</b> |

**1 功能公告**

影响器件运行、功能或参数的公告。

✓ 复选标记表示指定版本中存在该问题。

| 勘误编号         | 修订版 A<br>( 原型 X 标<br>记产品 ) | 修订版 C |

|--------------|----------------------------|-------|

| ADC_ERR_06   | ✓                          | ✓     |

| ADC_ERR_10   | ✓                          | ✓     |

| AES_ERR_01   | ✓                          | ✓     |

| CPU_ERR_02   | ✓                          | ✓     |

| CPU_ERR_03   | ✓                          | ✓     |

| FLASH_ERR_01 | ✓                          | ✓     |

| FLASH_ERR_03 | ✓                          | ✓     |

| FLASH_ERR_04 | ✓                          | ✓     |

| FLASH_ERR_05 | ✓                          | ✓     |

| FLASH_ERR_08 | ✓                          | ✓     |

| GPIO_ERR_04  | ✓                          | ✓     |

| I2C_ERR_04   | ✓                          | ✓     |

| I2C_ERR_05   | ✓                          | ✓     |

| I2C_ERR_06   | ✓                          | ✓     |

| I2C_ERR_07   | ✓                          | ✓     |

| I2C_ERR_08   | ✓                          | ✓     |

| I2C_ERR_09   | ✓                          | ✓     |

| I2C_ERR_10   | ✓                          | ✓     |

| 勘误编号            | 修订版 A<br>( 原型 X 标<br>记产品 ) | 修订版 C |

|-----------------|----------------------------|-------|

| I2C_ERR_13      | ✓                          | ✓     |

| KEYSTORE_ERR_01 | ✓                          | ✓     |

| MATHACL_ERR_01  | ✓                          | ✓     |

| MATHACL_ERR_02  | ✓                          | ✓     |

| PMCU_ERR_09     | ✓                          | ✓     |

| PMCU_ERR_10     | ✓                          |       |

| PMCU_ERR_11     | ✓                          | ✓     |

| RST_ERR_01      | ✓                          | ✓     |

| RTC_ERR_01      | ✓                          | ✓     |

| SPI_ERR_02      | ✓                          | ✓     |

| SPI_ERR_04      | ✓                          | ✓     |

| SPI_ERR_05      | ✓                          | ✓     |

| SPI_ERR_06      | ✓                          | ✓     |

| SPI_ERR_07      | ✓                          | ✓     |

| SRAM_ERR_03     | ✓                          |       |

| SYSCTL_ERR_01   | ✓                          | ✓     |

| SYSCTL_ERR_02   | ✓                          | ✓     |

| SYSCTL_ERR_03   | ✓                          | ✓     |

| SYSCTL_ERR_04   | ✓                          | ✓     |

| SYSOSC_ERR_01   | ✓                          | ✓     |

| SYSOSC_ERR_02   | ✓                          | ✓     |

| SYSOSC_ERR_04   | ✓                          | ✓     |

| SYSPLL_ERR_01   | ✓                          | ✓     |

| TIMER_ERR_04    | ✓                          | ✓     |

| TIMER_ERR_06    | ✓                          | ✓     |

| TIMER_ERR_07    | ✓                          | ✓     |

| UART_ERR_01     | ✓                          | ✓     |

| UART_ERR_02     | ✓                          | ✓     |

| UART_ERR_04     | ✓                          | ✓     |

| UART_ERR_05     | ✓                          | ✓     |

| UART_ERR_06     | ✓                          | ✓     |

| UART_ERR_07     | ✓                          | ✓     |

| UART_ERR_08     | ✓                          | ✓     |

| UART_ERR_10     | ✓                          | ✓     |

| UART_ERR_11     | ✓                          | ✓     |

## 2 预编程的软件公告

影响出厂编程软件的公告。

✓ 复选标记表示问题存在于指定的版本中。

## 3 仅调试公告

仅影响调试操作的公告。

✓ 复选标记表示指定版本中存在该问题。

| 勘误编号        | 修订版 A | 修订版 B |

|-------------|-------|-------|

| GPIO_ERR_03 | ✓     | ✓     |

## 4 已通过编译器公告修复

使用编译器解决方法解决的公告。请参阅每个公告，了解 IDE 和编译器版本及解决方法。

✓ 复选标记表示问题存在于指定的版本中。

## 5 器件命名规则

为了标示产品开发周期所处的阶段，TI 为所有 MSP MCU 器件的器件型号分配了前缀。每个 MSP MCU 商用系列产品都具有以下两个前缀之一：MSP 或 XMS。这些前缀代表了产品开发的发展阶段，即从工程原型 (XMS) 直到完全合格的生产器件 (MSP)。

**XMS** - 实验器件，不一定代表最终器件的电气规格

**MSP** - 完全合格的生产器件

支持工具命名前缀：

**X**：还未经德州仪器 (TI) 完整内部质量测试的开发支持产品。

**null**：完全合格的开发支持产品。

**XMS** 器件和 **X** 开发支持工具在供货时附带如下免责条款：

“开发中的产品用于内部评估用途。”

**MSP** 器件的特性已经全部明确，并且器件的质量和可靠性已经完全论证。TI 的标准保修证书对该器件适用。

预测显示原型器件 (XMS) 的故障率大于标准生产器件。由于这些器件的预计最终使用故障率尚不确定，德州仪器 (TI) 建议不要将它们用于任何生产系统。请仅使用合格的生产器件。

TI 的器件命名规则还包含具有器件产品系列名称的后缀。此后缀表示温度范围、封装类型和配送形式。

### 5.1 器件编号法和修订版本标识

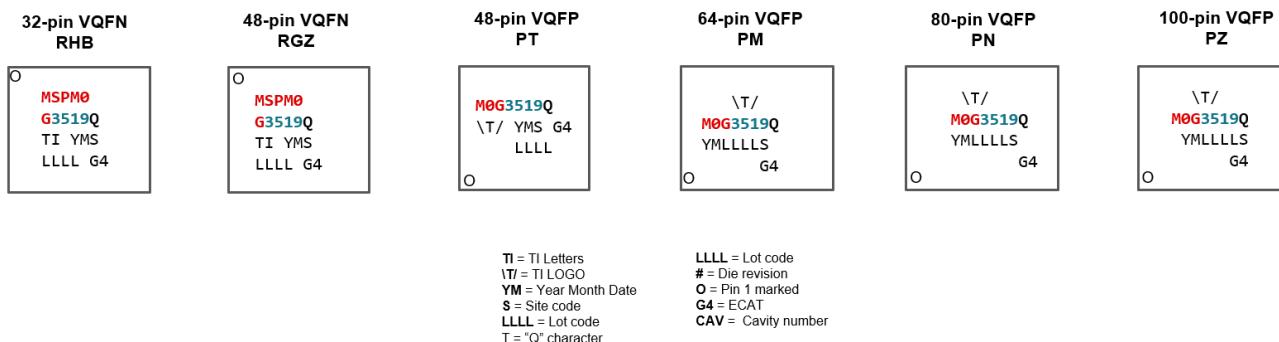

下面的封装图展示了封装编号法方案，表 5-1 定义了器件修订版到版本 ID 的映射。

图 5-1. 封装符号

表 5-1. 芯片修订版本

| 修订版字母 | 版本 (在器件的出厂常量存储器中) |

|-------|-------------------|

| A     | 1                 |

| C     | 2                 |

修订版字母表示产品硬件修订版本。根据修订字母，本文档中的公告标记为“适用于”或“不适用于”给定器件。该字母映射到器件存储器中存储的整数，可用于使用应用软件或已连接的调试探针来查找修订版本。

## 6 公告说明

### ADC\_ERR\_06

#### ADC 模块

##### 类别

功能

##### 功能

ADC 输出代码跳变，从而使 DNL/INL 规格降低

##### 说明

当发生转换错误时，ADC 数字输出代码会出现固定的 +/- 64LSB 跳变，而 ADC 输入电压并未发生相应变化。

在 -40°C 的最恶劣工况下，12 位模式下每转换 2,400 万个样本就会出现 1 次此类错误。

( 使用的 VDD 电压和基准对错误率没有影响 )

##### 权变措施

根据具体应用需求，适用的权变措施可能会有所不同，但建议在软件中采用以下权变措施。适用的权变措施的选择应由系统设计人员根据实际情况自行判断。

权变措施 1：当 ADC 结果超出应用阈值（通过 ADC 窗口比较器或软件阈值）时，触发或等待另一个 ADC 结果，然后再做出关键的系统决策

权变措施 2：在后处理过程中，剔除与中值或预期值相差太大的 ADC 值。预期值应基于系统中实际采样的平均值，剔除阈值应基于测量的系统噪声大小。

权变措施 3：使用 ADC 样本平均法，以尽可能降低任何单次错误转换结果的影响。

### ADC\_ERR\_10

#### ADC 模块

##### 类别

功能

##### 功能

当 PA15/PA18/PA22/PA21 切换时，会出现 ADCMEMRES 交换

##### 说明

设置条件：

1. ADC 处于重复序列模式 2. ADC 可以使用任何通道序列来读取数据 3. PA15/PA18/PA22/PA21 由外部器件或 MCU 本身（如 PWM）切换。

观察结果：

当软件开始 ADC 转换时，MEMRES 数据有时会发生交换。本应位于 MEMRES0 中的数据将进入 MEMRES1，MEMRES1 数据将进入 MEMRES2，以此类推。在重复模式下，当出现此错误时，最后一个 MEMRES 的数据将出现在 MEMRES0 中。

PA15/PA18/PA22/PA21 上的切换信号可能会影响 ADC 的转换时钟。这会使 ADC 在正确的通道数据传入之前存储先前的结果。

##### 权变措施

避免 PA15/PA18/PA22/PA21 上出现快速开关信号（12kHz 或更快）。

**AES\_ERR\_01****AES 模块****类别**

功能

**功能**

AES 保存的上下文就绪中断未按预期生成

**说明**

未生成已保存的上下文就绪中断。如果对任何 AES 寄存器进行了访问（读取或写入），则会生成中断。

**权变措施**

使用基于轮询的机制，检查 CTRL 寄存器中已保存的上下文就绪的状态位，而不是中断。

**CPU\_ERR\_02****CPU 模块****类别**

功能

**功能**

禁用 CPUSS 预取具有限制

**说明**

如果存在待处理的闪存访问，CPU 预取禁用将不会生效。

**权变措施**

禁用预取器，然后发出对 SYSTCL 中的关断存储器 (SHUTDNSTORE) 的存储器访问权限，这可以通过 SYSTCL.SOCLOCK.SHUTDNSTORE0; 来完成存储器访问完成后，将禁用预取器。

**示例：**

```

CPUSS.CTL.PREFETCH = 0x0; //禁用预取器

SYSTCL.SOCLOCK.SHUTDNSTORE0; //对关断存储器的存储器访问

```

**CPU\_ERR\_03****CPU 模块****类别**

功能

**功能**

在转换到低功耗模式时，预取器可能会获取错误的指令

**说明**

转换到低功耗模式且存在待处理的预取时，预取器可能会错误地获取不正确的数据（全 0）。当器件唤醒时，如果预取器和高速缓存未被 ISR 代码覆盖，则从闪存执行的主代码可能会损坏。例如，如果 ISR 位于 SRAM 中，则从闪存预取的不正确的数据不会被覆盖。当 ISR 返回损坏的数据时，CPU 可能会提取预取器中的数据，从而导致指令不正确。硬件事件唤醒是将唤醒器件但不刷新预取器的进程的另一个示例。

**权变措施**

进入低功耗模式之前禁用预取器。

**示例：**

```

CPUSS->CTL &= 0x6; // 禁用预取器，保持其他设置

SYSTCL.SOCLOCK.SHUTDNSTORE0 // 从 SHUTDOWN 存储器读取

```

## CPU\_ERR\_03

(续)

### CPU 模块

`__WFI(); // or __WFE();` 该函数调用转换到低功耗模式

`CPUSS->CTL |= 0x1;` // 启用预取器

## FLASH\_ERR\_01

### FLASH 模块

#### 类别

功能

#### 功能

访问 **FACTORY** 区域将导致在闪存等待状态等于 2 时出现硬故障。

#### 说明

当闪存等待状态设置为 2 时，访问 **FACTORY** 区域将触发硬故障。当 **MCLK** 设置为超出 32MHz 时，闪存等待状态需要为 2。

#### 权变措施

以较低的频率设置 **MCLK** ( 闪存等待状态为 0 或 1 ) 以访问 **FACTORY** 区域。在闪存等待状态小于 2 时访问 **FACTORY** 区域 ( 要求 **MCLK** 为 32MHz 或更低 )。如果应用程序需要在运行时访问这些值，则缓存 **SRAM**、**MAIN** 闪存或 **DATA** 闪存中的数据。温度传感器的校准值是一个典型值。

## FLASH\_ERR\_03

### FLASH 模块

#### 类别

功能

#### 功能

在 2 个等待状态下访问闪存，然后访问无效引导代码，将导致下一次闪存访问也出现违规

#### 说明

在 2 个等待状态下访问闪存，然后访问 **BOOTCODE**，将导致下一次闪存访问也出现违规。

#### 权变措施

请勿尝试在启动阶段后访问引导代码区域。否则，在引导代码违规和下一次正确闪存访问之间需要间隔 4 个时钟周期。

## FLASH\_ERR\_04

### FLASH 模块

#### 类别

功能

#### 功能

如果错误位于 **NONMAIN** 或 **Factory** 区域，则 **SYSCTL\_DEDERRADDR** 中会报告错误地址

#### 说明

当出现 **FLASHDED** 错误时，数据会截断最高有效字节。在器件的存储器限制范围内，最高有效字节对 **MAIN** 闪存的返回地址没有影响。对于 **NONMAIN** 闪存或 **Factory** 区域，**MSB** 应列出为 **0x41xx.xxxx**

**FLASH\_ERR\_04**

(续)

**FLASH 模块****权变措施**

如果 `SYSCTL_DEDERRADDR` 的返回地址返回 `0x00Cxxxxx`，请使用 `0x41000000` 进行“OR”操作，以获取 `NONMAIN` 或 `Factory` 区域返回地址的正确地址。例如，如果 `SYSCTL_DEDERRADDR = 0x00C4013C`，则实际地址为 `0x41C4013C`。

对于主闪存 DED，可按原样使用 `SYSCTL_DEDERRADDR`。

**FLASH\_ERR\_05****FLASH 模块****类别**

功能

**功能**

`DEDERRADDR` 可能具有不正确的复位值

**说明**

`SYSCTL->DEDERRADDR` 的复位值可能返回 `0x00C4013C`，而不是正确的 `0x00000000`。错误发生在出厂微调区域，并不表示出现故障，可适当忽略。在器件上对 `NONMAIN` 进行编程后，复位值通常会发生变化。

**权变措施**

接受 `0x00C4013C` 作为另一个复位值，因此引导后的默认值可能为 `0x00000000` 或 `0x00C4013C`。返回值超出了器件 `MAIN` 闪存的范围，因此该返回值不可能来自实际的 FLASH DED 状态。

**FLASH\_ERR\_08****FLASH 模块****类别**

功能

**功能**

不会为典型的无效存储器区域生成硬故障

**说明**

在尝试访问如下所示的非法存储器地址空间时，不会生成硬故障：1. `0x010053FF - 0x20000000` 2. `0x40BFFFFF - 0x41C00000` 3. `0x41C007FF - 0x41C40000`

**权变措施**

否

**GPIO\_ERR\_03****GPIO 模块****类别**

功能

**功能**

调试器读取 `GPIO EVENT0 IIDX` 时，中断被清除。

**说明**

在调试器读取 `GPIO EVENT0` 的 `IIDX` 时，被视为 CPU 读取，中断被清除。

**权变措施**

在调试期间，可通过软件读取 `RIS` 来读取 `event0` 的 `IIDX`。

## GPIO\_ERR\_04

### GPIO 模块

#### 类别

功能

#### 功能

配置全局快速唤醒不允许焊盘数据传输到 DIN 寄存器

#### 说明

当配置 CTL 寄存器中的“仅快速唤醒”位并在运行模式下强制将数据传输到焊盘时，焊盘中的数据不会反映在 DIN 寄存器中。这是因为 CTL 寄存器配置会阻断任何数据从焊盘流向 DIN 寄存器。

#### 权变措施

当需要焊盘上的数据传输到 DIN 寄存器时，避免使用 GPIO 快速唤醒功能。

## I2C\_ERR\_04

### I2C 模块

#### 类别

功能

#### 功能

当 SCL 为低电平且 SDA 为高电平时，目标 i2c 无法释放延展。

#### 说明

1 : SCL 线路接地并释放，器件不限期将 SCL 拉至低电平。

2 : 时钟后延展、超时和释放；如果线路上存在另一个时钟低电平，器件会不限期地将 SCL 拉至低电平。

#### 权变措施

如果 I2C 目标应用在低功耗模式下不需要使用异步快速时钟请求进行数据接收，则建议默认禁用 SWUEN，包括在复位或功率周期期间也是一样。在这种情况下，不会出现错误描述 1 和 2。

如果 I2C 目标应用需要使用异步快速时钟请求在低功耗模式下接收数据，请在进入低功耗模式之前启用 SWUEN，并在退出低功耗模式后清除 SWUEN。即使在这种情况下，当 I2C 目标处于低功耗模式时，也可能会出现错误描述 1 和 2，如果总线上的另一个器件引发连续时钟延展或超时，它也会不限期延长 SCL 线路。为了从这种情况中恢复，请在 I2C 目标器件上启用低电平超时中断，在低电平超时 ISR 内复位并重新初始化 I2C 模块。

## I2C\_ERR\_05

### I2C 模块

#### 类别

功能

#### 功能

如果我们在正在进行的事务期间切换 ACTIVE 位，I2C SDA 可能会卡在零的位置

#### 说明

如果在正在进行的传输期间切换 ACTIVE 位，则状态机将复位。但是，由控制器驱动的 SDA 和 SCL 输出将不会复位。存在 SDA 为 0 且控制器已进入 IDLE 状态的情况下，在这种情况下，控制器将无法从 IDLE 状态向前移动或更新 SDA 值。设置目标的 BUSBUSY ( 切换 ACTIVE 位会导致在线路上开始检测到开始 )，并且 BUSBUSY 不会被清除，因为控制器将无法驱动 STOP 来将其清除。

**I2C\_ERR\_05 (续) I2C 模块****权变措施**

在事务正在进行期间不要切换 ACTIVE 位。

**I2C\_ERR\_06****I2C 模块****类别**

功能

**功能**

当 I2C 时钟低于 24kHz 及更低时，SMBus 高电平超时功能会失败

**说明**

当 I2C 时钟速率低于 24kHz 及更低 ( 20kHz、10kHz ) 时，SMBus 高电平超时功能会失败。根据 SMBUS 规格，活动事务期间 SCL 高电平时间的上限为 50us。从将 START MMR 位写入 SCL 低电平所需的总时间为 60us，即 >50us。它将触发超时事件，并使 I2C 控制器进入 IDLE 状态，而不会在传输本身开始时完成事务。以下是详细说明。对于 SCL 配置为 20kHz 的情况，SCL 低电平周期和高电平周期分别为 30us 和 20us。首先，在高电平超时计数器开始递减的同时开始 MMR 位写入。然后，从开始 MMR 位写入到 SDA 变为低电平 ( 启动条件 ) 需要一个 SCL 低电平 (30us)。接下来，从 SDA 变为低电平 ( 启动条件 ) 到 SCL 变为低电平 ( 数据传输开始 ) 需要另一个 SCL 低电平周期 (30us)，此时应该停止高电平超时计数器。从计数器开始到结束总共需要 60us 的时间。但是，由于高电平超时计数器的上限 (50us)，尽管 I2C 事务会正常工作，而且不出现问题，但仍将触发超时事件。

**权变措施**

当 I2C 时钟低于 24kHz 及更低时，请勿使用 SMBus 高电平超时功能。

**I2C\_ERR\_07****I2C 模块****类别**

功能

**功能**

背对背控制器控制寄存器的写入将导致 I2C 无法启动。

**说明**

背对背 CTR 寄存器写入将导致后续的 CTR.START 不会正确地引起启动条件。

**权变措施**

以单次写入方式写入所有 CTR 位 ( 包括 CTR.START )，或者在 CTR 写入和 CTR.START 写入之间等待一个时钟周期。

**I2C\_ERR\_08****I2C 模块****类别**

功能

**功能**

RXDONE 中断后直接读取 FIFO 会导致读取错误数据

**说明**

发生 RXDONE 中断时，FIFO 并不总是会更新为最新数据。

## I2C\_ERR\_08 (续) I2C 模块

### 权变措施

等待 2 个 I2C CLK 周期，让 FIFO 确保获得最新数据。I2C CLK 基于 I2C 寄存器中的 CLKSEL 寄存器。

## I2C\_ERR\_09

### I2C 模块

#### 类别

功能

#### 功能

如果以低速运行 I2C，则 ISR 读取时可能不会及时更新起始地址匹配状态。

#### 说明

如果以低于 100kHz 的 I2C 速度运行，可能无法及时将 ADDRMATCH 位 ( TSR 寄存器中的地址匹配 ) 置位来通过中断读取。

### 权变措施

如果在 I2C 上以低于 100kHz 的速度运行，请等待至少 1 个 I2C CLK 周期，然后再读取 ADDRMATCH 位。

## I2C\_ERR\_10

### I2C 模块

#### 类别

功能

#### 功能

启用 I2C 忙碌状态，防止进入低功耗模式

#### 说明

在 I2C 目标模式下，如果没有 STOP 位，I2C 忙碌状态会在事务后保持高电平。

### 权变措施

对 I2C 控制器进行编程，以发送 STOP 位并且不为最后一个字节发送 NACK。通过 STOP 条件终止任何 I2C 传输，以保持正确的 BUSY 状态和异步时钟请求行为 ( 用于重新进入低功耗模式 ) 。

## I2C\_ERR\_13

### I2C 模块

#### 类别

功能

#### 功能

轮询 I2C BUSY 位可能无法保证控制器传输完成

#### 说明

在设置 CCTR.BURSTRUN 位来启动 I2C 控制器传输后，大约需要 3 个 I2C 功能时钟周期才能将 BUSY 状态置为有效。如果在设置 CCTR.BURSTRUN 后立即轮询 BUSY 位以等待传输完成，可能会在 BUSY 状态尚未置位时就完成状态检查。在 CLKDIV 值较高 ( 导致 I2C 功能时钟较慢 ) 或编译器优化级别较高的情况下，更有可能发生该问题。

### 权变措施

在轮询 BUSY 状态之前添加软件延迟。软件延迟 =  $3 \times \text{CPU CLK}/\text{I2C 功能时钟} = 3 \times \text{CPU CLK}/(\text{CLKSEL}/\text{CLKDIV})$  例如，时钟分频器 (CLKDIV) 为 8、时钟源为 4MHz(MFCLK)，CPU CLK 为 32MHz 时：软件延迟 =  $3 \times 32\text{MHz}/(4\text{MHz}/8) = 192$  个 CPU 周期

**KEYSTORE\_ERR\_****01****密钥库模块****类别**

功能

**功能**

STATUS.STATUS 值可以是 0 或 1，无需密钥访问

**说明**

STATUS.STATUS 的复位值为 1 并在以下条件下变为 0：1. 复位后，调试器通过寄存器窗口访问将返回 0x00。2. 复位后，第一次 CPU 读取将返回 0x01，后续 CPU 读取将返回 0x00。3) 复位后，首先读取任何其他密钥库寄存器，然后读取 STATUS.STATUS 将返回 0x00。

**权变措施**

STATUS.STATUS = 0x0 表示“无错误”。要检查插槽是否有效（是否有密钥），请检查 STATUS.VALID。

**MATHACL\_ERR\_0****1****MATHACL 模块****类别**

功能

**功能**

MATHACL 状态错误位不会被清除

**说明**

如果 mathacl 生成状态错误（例如，除以 0），则状态寄存器永远不会被清除。

**权变措施**

复位外设以清除状态位。

**MATHACL\_ERR\_0****2****MATHACL 模块****类别**

功能

**功能**

MATHACL COS (-180) 返回 1，而不是 -1，SIN (-90) 返回 1，而不是 -1

**说明**

在执行 COS (-180) 或 SIN (-90) 时，MATHACL 将返回 1，而不是 -1

**权变措施**

没有解决方法，在软件中使结果为负。

**PMCU\_ERR\_09****PMCU 模块****类别**

功能

**功能**

在 POR (NRST>1s) 复位后，RSTCAUSE 错误地更新为 0xC

## PMCU\_ERR\_09

(续)

### PMCU 模块

#### 说明

当使用 NRST 触发 POR (NRST>1s) 复位时，RSTCAUSE 会错误地更新为 0xC，而预期值为 0x2。

#### 权变措施

如果需要检查复位原因，请使用一个可用的关断存储器字节 (SHUTDNSTOREx) 来在获取 RSTCAUSE 状态后存储非零数据。当 RSTCAUSE 返回 0xC 时，如果 SHUTDNSTOREx 数据被清除，则会发生 POR；如果 SHUTDNSTOREx 数据被保留，则会发生 BOR。

## PMCU\_ERR\_10

### PMCU 模块

#### 类别

功能

#### 功能

在某些工作条件下，VBOOST 可能会存在更高的延迟

#### 说明

模拟多路复用的 VBOOST 在 VDD < 1.8V 时具有较大的延迟，这会延迟 HFXT、COMP、SYSOSC (FCL 外部 R)、OPA 和 GPAMP 等其他模块的稳定时间。

#### 权变措施

使用 GENCLKCFG[23:22]=0x2，保持 VDD >= 1.8V 并在 ONALWAYS 模式下使用 VBOOST。

## PMCU\_ERR\_11

### PMCU 模块

#### 类别

功能

#### 功能

在关断模式下，NRST<1sec 脉冲提供错误的 rstcause

#### 说明

在以下情况下，rstcause 值错误。但预期的 rstcause 为 0x05。

- (i) 器件配置为 SHUTDOWN 模式

- (ii) WFI() 被调用

- (iii) 提供 NRST<1sec 的脉冲以使器件退出关断模式

#### 权变措施

无权变措施。

## RST\_ERR\_01

### RST 模块

#### 类别

功能

#### 功能

当 LFCLK\_IN 是 LFCLK 源且 LFCLK\_IN 被禁用时，不会检测到 NRST 释放

**RST\_ERR\_01**

(续)

**RST 模块****说明**

当 **LFCLK = LFCLK\_IN** 且禁用 **LFCLK\_IN** 时，会出现一种边界场景：**NRST** 脉冲边沿检测失效，且器件不会退出复位。如果 **NRST** 脉冲宽度低于 **608us**，则会出现此问题。**NRST** 脉冲超过 **608us** 时，复位可正常显示。

**权变措施**

保持 **NRST** 脉冲宽度高于 **608us** 即可以避免此问题。

**RTC\_ERR\_01****RTC 模块****类别**

功能

**功能**

某些 **RTC** 中断在 **STANDBY1** 中不可用

**说明**

在 **STANDBY1** 下，**RTCRDY** 和 **RTC\_PRESCALER1** 中断无法唤醒器件。

**权变措施**

使用 **RTC** 从 **STANDBY1** 唤醒器件时，请使用其他可用中断，例如 **RTC\_ALARM** 和 **RTC\_PRESCALER0**。

**SPI\_ERR\_02****SPI 模块****类别**

功能

**功能**

从低功耗模式 (**LPM**) 唤醒后 **SPI** 时钟和数据字节缺失

**说明**

器件从低功耗状态唤醒后，**SPI** 模块无法正确传播发送出的第一个字节的前几个时钟周期和数据位。

**权变措施**

为了在唤醒后保持 **SPI** 数据完整性，请在进入和退出 **LPM** 时使用以下序列：

1. 禁用 **SPI** 模块

2. 等待中断 (**WFI**) - 进入 **LPM**

3. 从 **LPM** 唤醒 (任何源)。

4. 启用 **SPI** 模块。

**SPI\_ERR\_04****SPI 模块****类别**

功能

**功能**

当 **SPI** 外设处于仅接收模式时，在每个帧接收后进行 **IDLE/BUSY** 状态切换。

## SPI\_ERR\_04 (续) SPI 模块

### 说明

如果 SPI 外设处于仅接收模式，则在 SPI 连续接收数据 (SPI\_PHASE=1) 时，每个帧接收后都会切换 IDLE 中断和 BUSY 状态。此处没有数据加载到外设 TXFIFO，TXFIFO 为空。

### 权变措施

不要使用 SPI 外设的仅接收模式。将 SPI 外设设置为传输和接收模式。您无需在 TX FIFO 中为 SPI 设置任何数据。

## SPI\_ERR\_05

### SPI 模块

### 类别

功能

### 功能

无论 RXFIFO 数据如何，都将设置 SPI 外设接收超时中断

### 说明

当使用 SPI 超时中断时，即使在接收到最终 SPI CLK 后，RXTIMEOUT 也可以继续递减，这可能会导致错误的 RXTIMEOUT。

### 权变措施

接收到最后一个数据包后禁用 RXTIMEOUT (可以在 ISR 中完成) 并在 SPI 通信再次开始时重新启用。

## SPI\_ERR\_06

### SPI 模块

### 类别

功能

### 功能

调试暂停置为有效时，IDLE/BUSY 状态不反映 SPI IP 的正确状态

### 说明

IDLE/BUSY 与暂停无关，它仅控制 RXFIFO/TXFIFO 写入/读取选通。因此，如果控制器正在发送数据，尽管未在 FIFO 中为其设置闩锁，但正在设置 BUSY。在暂停期间，POCI 线路会在线路上传输先前传输的数据

### 权变措施

当 SPI IP 暂停时，请勿使用 IDLE/BUSY 状态。

## SPI\_ERR\_07

### SPI 模块

### 类别

功能

### 功能

如果同时在 SPI 外设对 TXFIFO 进行读取/写入，则可能不会生成 SPI 下溢事件

### 说明

当 SPI.CTL0.SPH = 0 且器件配置为 SPI 外设时。

如果在从 SPI 控制器发出读取请求时对 TXFIFO 进行了写入，则由于同时发生读取/写入请求，可能不会生成下溢事件。

## **SPI\_ERR\_07 (续) SPI 模块**

### 权变措施

当 SPI 控制器对器件寻址时，确保 TXFIFO 不为空，这可以通过预加载数据来实现，以避免对同一 TXFIFO 地址进行写入和读取。或者，可以使用数据检查策略（如 CRC）来验证数据包是否已正确发送，在 CRC 不匹配时，可以重新发送数据。

## **SRAM\_ERR\_03 SRAM 模块**

### 类别

功能

### 功能

修订版 A 器件不支持 SRAM 奇偶校验和 ECC 功能

### 说明

修订版 A 器件不支持 SRAM 奇偶校验和 ECC 功能。请勿在修订版 A 器件上使用 SRAM 奇偶校验和 ECC 功能。

### 权变措施

无。

## **SYSCTL\_ERR\_01 SYSCTL 模块**

### 类别

功能

### 功能

SW-POR 功能与 HW-POR 结合使用

### 说明

当用户使用正确的密钥写入 LFSSRST 寄存器以生成软件触发的 POR 时，RSTCAUSE 寄存器将显示 0x2（指示 NRST 触发的 POR），而不是预期的 0x3（软件触发的 POR）。这是因为 SW-POR 功能是与 HW-POR 路径结合使用的。

### 权变措施

否

## **SYSCTL\_ERR\_02 SYSCTL 模块**

### 类别

功能

### 功能

SYSSTATUS.FLASHSEC 在 BOOTRST 之后为非零

### 说明

在 BOOTRST/ 引导代码运行完成之后，SYSSTATUS.FLASHSEC 为非零。客户将在引导代码运行完成后看到此情况。

### 权变措施

否

## SYSCTL\_ERR\_03 SYSCTL 模块

### 类别

功能

### 功能

在执行 **SYSRESET** 或对 **SYSSTATUSCLR** 进行写入后, **DEDERRADDR** 仍然存在

### 详细信息

在执行 **SYSRESET** 或对 **SYSSTATUSCLR** 进行写入后, **DEDERRADDR** 寄存器仍然存在。仅当发生新的 **FLASHDED** 错误时, 才会覆盖其值。这种行为不符合技术参考手册 (TRM), 手册中规定其初始复位值为零。

### 权变措施

无权变措施

## SYSCTL\_ERR\_04 SYSCTL 模块

### 类别

功能

### 功能

**SYSRESET** 之后不会清除 **SYSSTATUS.FLASHSEC**

### 说明

**SYSRESET** 之后不会清除 **SYSSTATUS.FLASHSEC**, 只能通过写入 **SYSSTATUSCLR** 寄存器来清除。

### 权变措施

否

## SYSOSC\_ERR\_01 SYSOSC 模块

### 类别

功能

### 功能

将 **SYSOSC FCL** 与 **STOP1** 模式一起使用时的 **MFCLK** 漂移

### 说明

如果启用了 **MFCLK** 并且 **SYSOSC** 使用频率改正环路 (FCL) 模式并使用 **STOP1** 低功耗工作模式, 则当 **SYSOSC** 从 4MHz 转换回 32MHz 时 (在退出 **STOP1** 进入 **RUN** 模式时或发生强制 **SYSOSC** 进入 32MHz 的异步快速时钟请求时), **MFCLK** 可能会漂移两个周期。

### 权变措施

使用 **STOP0** 模式而不是 **STOP1** 模式, 使用 **STOP0** 模式时没有 **MFCLK** 漂移。

或

在使用 **STOP1** 时, 在 **FCL** 模式下不使用 **SYSOSC** (使 **FCL** 保持禁用状态)。

## SYSOSC\_ERR\_02 SYSOSC 模块

## 类别

功能

## 功能

在 LPM 下接收到异步时钟请求 ( 在 FCL 模式下禁用了 SYSOSC ) 时 , MFCLK 不工作

## 说明

在以下情况下 , MFCLK 不会开始切换 :

1. 启用 FCL 模式 , 然后启用 MFCLK

2. 进入禁用 SYSOSC 的低功耗模式 (SLEEP2/STOP2/STANDBY0/STANDBY1)。

3. 从一些使用 MFCLK 作为功能时钟的外设接收到异步请求。

接收到异步请求时 , SYSOSC 将被启用 , ulpclk 将变为 32MHz。但 MFCLK 会断开 , 并且它根本不会切换 , 因为器件的设置仍然为 LPM。

## 权变措施

如果 SYSOSC 正在使用 FCL 模式 - 当您进入 LPM 模式 ( 通常会关闭 SYSOSC ) 时 , 请勿启用外设的 MFCLK。

## SYSOSC\_ERR\_04 SYSOSC 模块

## 类别

功能

## 功能

使用 SYSPLL 时 , SYSOSC 精度在 FCL ON 模式下会降低

## 说明

当将 FCLON 用于内部振荡器时 , 在使用 SYSPLL 的情况下 , SYSOSC 精度可能会降低多达  $+/- 3\%$ 。精度下降是由于 4MHz SYSOSC 采样时钟与系统噪声之间的同步所致。

## 权变措施

如果使用 SYSPLL FCL ON 模式 , 请为 SYSPLL 频率选择一个非 4MHz 整数倍的值 , 例如 : 78MHz、79MHz、81MHz

请勿将 SYSPLL 频率设为 16、32、48、40、64、80MHz 等

对于 78MHz :

请将 SYSPLLCFG1.PDIV 设为 0x3 , SYSPLLCFG1.QDIV 设为 38。

## SYSPLL\_ERR\_01 SYSPLL 模块

## 类别

功能

## 功能

启用后 , SYSPLL 频率可能无法锁定到正确的频率。

## 说明

当在 SYSCTL HSCLKEN 寄存器中将 SYSPLLEN 位设置为 1 时 , SYSPLL 将运行锁相环搜索。如果频率不会设置为正确的值 , 搜索可能会失败 , 相反 , 生成的频率将与配置的频率大不相同。

## SYSPLL\_ERR\_01

(续)

### SYSPLL 模块

#### 权变措施

只要 **SYSPLEN** 位设置为 1，就会使用频率时钟计数器 (FCC) 检查 **SYSPLL** 的频率输出。一旦频率正确，它将保持正确的值，直到禁用和重新启用 (**SYSPLEN** 设置为 0 然后设置为 1)，一旦重新启用，PLL 将重新运行搜索，并且需要重新检查 **SYSPLL** 输出。

权变措施 1：将 FCC 设置为 **SYSPLLCLK0** 作为 CLK 输入、**LFCLK** 作为触发源。运行 FCC 并参考 **LFCLK** 检查所配置的 **SYSPLL** 频率的值；例如，当 **SYSPLL** = 80MHz 且 **LFCLK** = 32kHz 时，生成的 FCC 计数应为  $80,000,000/32,768 = \sim 2441$ 。计数将因组合时钟精度而异，因此建议在允许的范围内增加  $\pm 5\%$ 。FCC 的估计时间为 30us。

FCC 设置：

**SYSCTL.GENCLKCFG.FCCTRIGCNT** = 0,

**SYSCTL.GENCLKCFG.FCCTRIGSRC** = 1, **SYSCTL.GENCLKCFG.FCCSELCLK** = 4;

如果 FCC 值不正确，请通过将 **SYSPLEN** 设置为 0 然后设置为 1 来禁用并重新启用 **SYSPLL**。重新运行 FCC 检查。

权变措施 2：从 **CLK\_OUT** 引脚输出 **SYSOSC/2** 并将信号路由到 **FCC\_IN**。将 **SYSPLLCLK0** 用作 FCC CLK，将 **FCC\_IN** 用作触发源。运行 FCC 16 个时钟周期，并参考 **SYSOSC** 检查所配置 **SYSPLL** 频率的值；例如，当 **SYSPLL** = 80MHz 且 **SYSOSC/2** = 16MHz 时，生成的 FCC 计数应为  $80,000,000/16,000,000 * 16 = \sim 80$ 。计数将因组合时钟精度而异，因此建议在允许的范围内增加  $\pm 5\%$ 。FCC 的估计时间为 1us。

FCC 设置：

**SYSCTL.GENCLKCFG.FCCTRIGCNT** = 0x0F,

**SYSCTL.GENCLKCFG.FCCTRIGSRC** = 0, **SYSCTL.GENCLKCFG.FCCSELCLK** = 4;

如果 FCC 值不正确，请通过将 **SYSPLEN** 设置为 0 然后设置为 1 来禁用并重新启用 **SYSPLL**。重新运行 FCC 检查。

## TIMER\_ERR\_04

### TIMER 模块

#### 类别

功能

#### 功能

如果接近零事件，则可能会错过计时器的重新启用

#### 说明

在单次模式下使用计时器时，如果接近零事件，则可能会错过计时器的重新启用。对计时器使能位进行硬件更新将需要一个功能时钟周期。例如，如果计时器的时钟源为 32.768kHz，时钟分频器为 3，则需要  $\sim 100\mu s$  才能将使能位正确设置为 0。

#### 权变措施

在重新启用计时器之前等待 1 个功能时钟周期，或者可以先禁用计时器，然后再重新启用。

通过 **CTRCTL.EN** = 0 禁用计数器，然后通过 **CTRCTL.EN** = 1 重新启用

**TIMER\_ERR\_06** *TIMA 和 TIMG 模块*

---

**类别**

功能

**功能**

向 CLKEN 位写入 0 不会禁用计数器

**说明**

向计数器时钟控制寄存器 (CCLKCTL) 时钟使能位 (CLKEN) 写入 0 不会停止计时器。

**权变措施**

通过向计数器控制 (CTRCTL) 使能 (EN) 位写入 0 来停止计时器。

**TIMER\_ERR\_07**

*初始重复计数器的周期比下一个重复模块少 1 个*

---

**类别**

功能

**功能**

计时器

**说明**

使用计时器重复计数器模式时，第一次重复的计数将比后续重复的计数少 1，因为以下重复计数器将包括 0 和加载值之间的转换。例如，如果  $\text{TIMx.RCLD} = 0x3$ ，则第一个重复计数器上将出现 3 个可观察到的零事件，并在以下重复计数器序列上显示 4 个可观察到的零事件。

**权变措施**

将初始 RCLD 值设置为比预期的 RCLD 大 1，然后在重复计数器归零事件 (REPC) 的 ISR 中将 RCLD 设置为预期的 RCLD 值。例如，如果打算重复 4 次，请将初始 RCLD 值设置为  $\text{RCLD} = 0x5$ ，然后在 REPC 中断的计时器 ISR 中设置  $\text{RCLD} = 0x4$ 。现在，所有计时器重复将具有相同数量的零/加载事件。

**UART\_ERR\_01**

*UART 模块*

---

**类别**

功能

**功能**

在切换到 STANDBY1 模式时，未检测到 UART 启动条件

**说明**

器件处于 STANDBY1 模式时，由 UART 传输启动的异步快速时钟请求提供服务后，器件将返回 STANDBY1 模式。如果在转换回 STANDBY1 模式期间开始另一次 UART 传输，则器件无法正确检测到并接收数据。

**权变措施**

当预计存在重复的 UART 启动条件时，使用 STANDBY0 模式或更高的低功耗模式。

**UART\_ERR\_02**

*UART 模块*

---

**类别**

功能

**功能**

仅启用 TXE 时，不设置 UART 传输结束中断

## UART\_ERR\_02

(续)

### UART 模块

#### 说明

当器件设置为仅传输 ( CTL0.TXE = 1 , CTL0.RXE = 0 ) 时 , 不会触发 UART 传输结束 (EOT) 中断。当器件设置为传输和接收 ( CTL0.TXE = 1 , CTL0.RXE = 1 ) 时 , EOT 会成功触发

#### 权变措施

当使用 UART 传输结束中断时 , 设置 CTL0.TXE 和 CTL0.RXE 位。请注意 , 您不需要将引脚分配为 UART 接收。

## UART\_ERR\_04

### UART 模块

#### 类别

功能

#### 功能

当时钟从 SYSOSC 转换到 LFOSC 时 , 通过快速时钟请求接收到的错误 UART 数据会被禁用

#### 说明

场景 :

1. 已选择 LFCLK 作为 UART 的功能时钟。

2. 波特率为 9600 , 配置了 3 倍过采样

3. UART 快速时钟请求已被禁用

- 。如果在 UART RX 传输过程中 ULPCLK 从 SYSOSC 更改为 LFOSC , 则会观察到一个位读取不正确

#### 权变措施

在 LPM 模式下使用 UART 时启用 UART 快速时钟请求。

## UART\_ERR\_05

### UART 模块

#### 类别

功能

#### 功能

UART 模块中调试暂停功能的限制

#### 说明

所有 Tx FIFO 元素都在通信进入暂停状态之前发出 , 预计完成现有帧并暂停。

#### 权变措施

调试暂停置为有效后 , 请确保数据不会写入 TX FIFO 。

## UART\_ERR\_06

### UART 模块

#### 类别

功能

#### 功能

UART 9 位模式下的 RTOUT/忙碌/异步异常行为

**UART\_ERR\_06**

(续)

**UART 模块****说明**

在多节点场景中，UART 接收超时 (RTOUT) 无法正常工作，其中一个 UART 将用作控制器，其他 UART 节点作为外设，在 9 位 UART 模式下为每个外设配置不同的地址。

第一个 UART 控制器与 UART 外设 1 通信，通过发送外设 1 的地址作为第一个字节，然后发送数据，外设 1 已看到地址匹配并接收到数据。控制器处理好外设 1 后，外设 1 在配置的超时期间后不设置 RTOUT、如果控制器立即开始与另一个 UART 外设 ( 外设 2 ) 的通信，该外设在总线上配置了不同的地址。外设 1 RTOUT 计数器在与外设 2 和外设 1 通信过程中复位，仅在 UART 控制器完成与外设 2 的通信后才设置其 RTOUT。

在 BUSY 和异步请求中观察到类似行为。即使与总线上的其他外设的通信时地址不匹配，控制器也正在设置忙碌和 Async 请求。

**权变措施**

请勿在单个控制器连接到多个外设的多节点 UART 通信中使用 RTOUT/ BUSY / 异步时钟请求行为。

**UART\_ERR\_07****UART 模块****类别**

功能

**功能**

在 IDLE LINE MODE 下，RTOUT 计数器不会按预期计数

**说明**

在 UART 中的 IDLE LINE MODE 下，RTOUT 计数器会卡住，即使线路处于 IDLE 状态且 FIFO 有一些元素也是如此。这意味着 RTOUT 中断在 IDLE LINE MODE 下将不起作用。

如果地址不匹配，当在 Rx 线上看到切换时，将重新加载 RTOUT 计数器。

在多响应器场景中，当命令发出位置和其他某个响应器之间正在通信时，这可能会导致产生 RTOUT 事件的无限延迟。

**权变措施**

在 IDLELINE 模式/多节点 UART 应用中使用 UART 模块时，请勿启用 RTOUT 功能。

**UART\_ERR\_08****UART 模块****类别**

功能

**功能**

STAT BUSY 并不代表 UART 模块的正确状态

**说明**

即使 UART 模块被禁用并且 TXFIFO 中有可用数据，STAT BUSY 也会保持高电平。

**权变措施**

轮询 TXFIFO 状态和 CTL0.ENABLE 寄存器位以识别 BUSY 状态。

**UART\_ERR\_10****UART 模块****类别**

功能

**UART\_ERR\_10**

(续)

**UART 模块****功能**

对于 UART IrDA 模式，BUSY 位设置会延迟

**说明**

在 IrDA 模式下，UART.STAT.BUSY 位会在 IrDA 启动脉冲的第二个边沿设置；这意味着整个位传输将在正确设置 BUSY 状态之前完成。在此期间，如果软件轮询 BUSY 位，即使 IrDA 启动脉冲正在进行，也会出现 UART 不繁忙的错误指示。BUSY 状态将受到 UART 波特率的影响，UART 传输速度越慢，正确设置 BUSY 之前的时间就越长。

**权变措施**

检查 BUSY 状态之前位传输长度的延迟。或者，依次检查 `UART.STAT.BUSY == 0x0` 和 `UART.STAT.BUSY == 0x1` 是另一种使动态延迟独立于波特率或其他 ISR 的权变措施。

**UART\_ERR\_11****UART 模块****类别**

功能

**功能**

在 STOP 位事务期间，UART 接收超时比预期更早开始计数

**说明**

在 STOP 位事务期间，接收超时将在 STOP 位事务的中间开始计数，如果 RXTOSEL 设置太小，这可能会导致意外的 RTOUT 中断。例如，如果波特率为 1Mbps 且 RXTOSEL 设置为 1，则预期的 RTOUT 应该在 STOP 位事务后 1us 发生，而不是 RTOUT 中断设置为 0.5us。

**权变措施**

UART.IFLS.RXTOSEL 寄存器选择在接收超时 (RTOUT) 中断触发之前的位时间。RXTOSEL 值需要大于 1 才能防止提前中断。接收超时时间的计算公式如下：接收超时 =  $(RXTOSEL - 0.5)/\text{波特率}$

**7 商标**

所有商标均为其各自所有者的财产。

**8 修订历史记录**

注：以前版本的页码可能与当前版本的页码不同

**Changes from NOVEMBER 30, 2025 to DECEMBER 31, 2025 (from Revision C (November 2025) to Revision D (December 2025))****Page**

|                               |    |

|-------------------------------|----|

| • 已更新 ADC_ERR_10 功能.....      | 5  |

| • 已更新 ADC_ERR_10 说明.....      | 5  |

| • 已更新 ADC_ERR_10 权变措施.....    | 5  |

| • 已更新 CPU_ERR_03 权变措施.....    | 6  |

| • 已更新 SYSOSC_ERR_04 功能.....   | 18 |

| • 已更新 SYSOSC_ERR_04 说明.....   | 18 |

| • 已更新 SYSOSC_ERR_04 权变措施..... | 18 |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月