# 提高 GaN 器件电源转换器效率和密度的设计注意事项

#### Salil Chellappan

Systems Manager, Power Delivery Industrial Systems Texas Instruments

# 随着许多制造商发布通用器件,用于电源转换的氮化镓 (GaN) 器件供应能力逐渐提高。

这些器件的应用引起了全球电源系统设计人员的高度关注。尽管采取了大量研究来了解 GaN 器件的属性,但是对于如何根据其属性来选择适用于各种电源转换应用的 GaN 器件,仍然还不清楚。

# 引言

在对使用 GaN 来替代电源开关中的硅进行大量专门研究后,现在有多家制造商提供用于电源转换应用的 GaN 开关器件。但是,在评估 GaN 器件的适用性和优势之前,您必须详细查看它们的属性。本白皮书将研究影响电源转换器性能的一些最重要的设计注意事项。

#### 器件架构

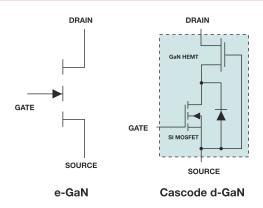

GaN 开关器件根据其内部架构分为两种不同的类型:增强模式 (e-GaN) 和共源共栅耗尽模式 (d-GaN)。尽管 e-GaN 开关降低了栅源电压电平,但其工作方式与普通硅金属氧化物半导体场效应晶体管 (MOSFET) 相似。e-GaN 器件还具有更简单的架构和封装、低导通电阻以及零体二极管反向恢复功能(不存在体二极管,但通道本身是双向的,其工作原理类似于体二极管)。

这种器件的第一个(也是主要的)问题是其栅极驱动设计的关键特性。问题在于该设备的完全增强型栅极驱动电压非常接近其击穿电压,安全裕度通常仅为 1V。这可能会在发生电压尖峰或寄生振铃的情况下导致器件故障。其次,相对较低的栅极阈值电压会降低噪声裕度。这些器件的第三个问题(尽管不是非常严重)是较高的栅极漏电流,这会增加栅极驱动器的耗散。

耗尽模式 GaN 器件既能提供出色的性能,还具有制造优势。但是,在加电和其他异常工作条件下,其通常的"接通"特性会成为一个问题。它还需要使用负电源。通过将耗尽模式 GaN 高电子迁移率晶体管 (HEMT) 与共源共栅 d-GaN 结构中的低压硅 MOSFET 串联连接,可以克服此问题。HEMT 的栅极短接到 MOSFET 的源极,而 HEMT 的源极连接到 MOSFET 的源极 [1]。图 1 如 所示,HEMT 的栅源电压是 MOSFET 的源漏

图 1. e-GaN 和共源共栅 d-GaN 器件的符号突显了结构差异。

电压。因此,硅 MOSFET 可以控制 GaN HEMT 的接通和关断。

这种结构的主要优点是,完整的共源共栅 d-GaN 开关具有低压硅 MOSFET 的栅极特性。所以,现有的商用MOSFET 栅极驱动器可以轻松驱动共源共栅 d-GaN 开关。另外,硅 MOSFET 的栅极特性是众所周知的,因此没有未知特性需要解决。

由于存在附加的串联硅开关,您将不得不在总体性能上做出一些妥协。可以说,对性能影响最大的是与硅 MOSFET 的体二极管相关的反向恢复能力。因为共源共栅 d-GaN 开关是串联组合,所以与 e-GaN 开关不同,它在反向导电时将具有反向恢复能力。下一个重大影响是,由于两个串联器件的漏源电容之间的电荷不平衡,关断期间有发生硅MOSFET 雪崩的可能性。这可能会增加开关损耗并降低可靠性。

由于存在附加的串联硅开关,共源共栅 d-GaN 增加了封装的复杂性和成本。更多的器件和互连增加了可靠性相关的问题。硅开关和 GaN HEMT 之间的寄生电感和电容会在开关瞬变期间引起延迟和振荡,并影响电气性能。

d-GaN 器件的另一个不利影响是,硅 MOSFET 的导通电阻增加,导致器件导通电阻增加。对于较低电压 (<200V)的共源共栅 d-GaN 器件,增加的幅度会非常显著。因此,对于低电压,e-GaN 开关是更好的选择。对于高压 (600V)共源共栅 d-GaN 器件,额外的电阻可能仅占总导通电阻的

5%左右 [2];在此电压电平下,共源共栅 d-GaN 仍然是可行的选择。

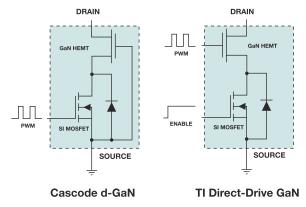

## TI 直接驱动 GaN

比较 e-GaN 和 d-GaN 结构可以很明显地发现,与共源共栅 d-GaN 相关的大多数问题都来自硅 MOSFET 和 GaN HEMT 的同时开关操作。TI 的直接驱动技术仅使用硅 MOSFET 来启用器件,进而克服了这一问题。图 2 对配置进行了比较。

图 2. 共源共栅 d-GaN 与直接驱动 GaN 之间的配置差异。

如前所述,在共源共栅 GaN 中,硅器件和 GaN 器件一起打开和关闭。但是,在 TI 直接驱动 GaN 中,硅 MOSFET 仅用于克服加电击穿的问题。硅 MOSFET 不进行开关;它会在加电期间打开,并一直保持打开状态直到断电为止,而且只在存在关闭 GaN HEMT 的负偏压时才会施加使能信号 [3]。将负电压电源和栅极驱动器与电源开关集成在一起,可确保对硅 MOSFET 和 GaN HEMT 的开关操作进行可靠且精确的控制。直接驱动 GaN 栅极可显著降低栅极电荷。此外,将体二极管的反向恢复和硅开关雪崩完全消除后,开关损耗大大降低。

将驱动电路集成到功率器件所带来的其他优势包括:可控制开关压摆率,通过感应硅 MOSFET 压降进行逐周期过流保护,以及过热保护。

# 器件封装

由于 GaN 器件能够非常快速地进行开关,因此与封装相关 的寄生效应非常重要。在某些情况下,它们会严重限制器 件性能。 在所有寄生元件中,共源电感 (CSI) 最为重要,因为它会影响电气性能。总体 CSI 是封装内部的源电感和封装本身的引线电感之和。在漏源极电路中存在高 di/dt 的情况下, CSI 有可能在漏源电压和栅源电压之间产生振铃,从而导致损耗增加 [4] 和开关错误 [5]。在 e-GaN 器件中,由于安全裕度有限,VGS 中的振铃甚至可能导致栅极击穿。

在硅 MOSFET 中,通常的做法是通过增加栅极电阻并减慢 开关速度来抑制这种振铃。这对于 GaN 器件是不可取的, 因为它们将失去固有的快速开关能力。另一个解决方案是 提供开尔文源连接,以从栅极驱动电路中消除 CSI。尽管 这可以解决开关错误问题,但漏源振铃可能仍然存在。对 于 GaN 器件而言,TO-220 之类的穿孔封装并不是很好的 选择,因为显著的引线电感会妨碍对快速开关功能进行有 效利用。此外,TO-220 封装的中心漏极布置也并非快速 开关器件布局的理想选择。对于靠近栅极引脚的开尔文源 引脚,最好使用表面贴装器件 (SMD) 封装。使用将栅极驱动器与 GaN 开关本身集成在一起的器件(如 TI 的直接驱动器件)更好,因为它可以避免外部布局问题。

热管理是与封装相关的另一个考虑因素。大多数 SMD 封装依赖于印刷电路板 (PCB) 热传递来进行散热。为了提高热性能,TI GaN 子卡的用户指南介绍了如何将散热器连接到 PCB [6]。将其放置在封装的散热焊盘下方会降低对连接在 PCB 另一侧的散热器的热阻。尽管 TO-220 封装具有金属片可用于散热,因而更适合进行热管理,但在考虑使用它之前,请注意本文中讨论的问题。

与封装相关的另一个考虑因素与电磁干扰 (EMI) 有关。大多数开关电源电路都以漏极作为开关节点。但是将散热焊盘连接到漏极会导致较高的共模和辐射 EMI。所以,从EMI 的角度来看,与源连接的散热焊盘是更好的选择。

在某些应用中,源极可以是开关节点。在此类情况下,将 散热器(直接或通过电容器)连接至安静节点(直流总线 正极或回路)有助于降低 EMI。

## 漏极电压额定值

根据设计,大多数实用的 GaN 器件都不具备雪崩能力。因此,足够的额定电压非常重要。即使发生瞬态事件时,也要注意不得超过击穿电压额定值。对于降压、升压和桥拓扑(包括半桥和全桥、电感器-电感电-容器 [LLC]、相移全

桥 [PSFB] 等),在高达 480V 的总线电压下,600V 的额 定电压通常情况下是足够的。

# 输出电容

开关电源器件有两种不同的输出电容参数:一个与时间有关,另一个与能量有关。与时间相关的输出电容 CO(tr) 在软开关拓扑中更为重要,因为它确定了零电压开关 (ZVS) 所需的死区时间。对于 GaN 器件,此参数大大低于(5 至10 倍)硅超结 MOSFET。您可能还会看到此参数以电荷(QOSS) 形式指定。在 ZVS 拓扑中,与硅 MOSFET 相比,降低的 CO(tr) 具有明显优势,因为死区时间缩短可降低循环电流。

尽管 GaN 器件的 CO(tr) 明显较低,但与能量相关的输出电容 CO(er) 却并非如此。您可能会看到以能量 (EOSS) 表示的相同参数。与性能卓越的硅超结 MOSFET 相比,共源共栅 d-GaN 器件的 CO(er) 稍高,但 e-GaN 器件的 CO(er) 几乎相等,因为 GaN 器件的输出电容 (COSS) 随电压变化不大,而硅超结 MOSFET 的输出电容具有非常明显的非线性特征。由于超结 MOSFET 在较低电压下的电容要高得多,而在较高电压下的电容要低得多,因此总电荷的能量含量可能相似。但是,由于 GaN 器件的 COSS 具有明显更高的线性度,因此与类似 EOSS 的硅超结 MOSFET 相比,与存储在其中的能量相关的磁滞较低,从而可以在软开关应用中恢复更多的能量。

#### 栅极电荷

栅极电荷是指示器件快速开关功能的参数。QGS2 + QGD 之和的值较低表示该器件能够实现较高的 dV/dt,从而降低开关损耗。通常,GaN 器件在这方面具有显著的优势。与硅超结 MOSFET 相比,e-GaN 器件的栅极电荷低约 10 倍,d-GaN 器件的栅极电荷低约 2 至 5 倍。您还可以查看RON x QG 品质因数,以了解足够低的导通损耗是否伴随着低开关损耗。

#### dV/dt 和 di/dt 灵敏度

先前在"器件封装"部分中提到了由高 di/dt 导致的与 CSI 相关的错误开关。由于该问题主要与封装和布局有关,因此通过适当的封装选择和适当的布局来减少 CSI 可以解决与 di/dt 相关的问题。

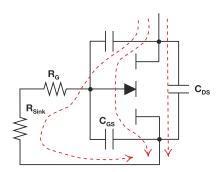

电源开关器件的 dV/dt 灵敏度是由各种寄生电容和栅极驱动电路阻抗之间的相互作用引起的。GaN 器件也是如此。图 3 显示了在漏源极上发生正向 dV/dt 事件期间,各种寄生电容和通过它们的电流。

在 dV/dt 事件期间,漏源极电容 (CDS) 进行充电;同时,栅漏极 (CGD) 和栅源极 (CGS) 电容器也

图 3. GaN 电源器件中的寄生电容和电流。

以串联的形式进行充电。如果未解决,则流过 CGD 电容器的充电电流将流过 CGS 并对 CGS 充电,使其超过栅极阈值电压 (VTH),并将器件打开。该事件有时被称为米勒导通,在 MOSFET 开关中众所周知,可能会非常耗散。为了确定电源开关器件的 dV/dt 灵敏度,可以使用称为米勒电荷比 (QGD/QGS1) 的品质因数。小于 1 的米勒电荷比将保证达到理论上的 dV/dt 抗扰度。但是,该比率可能并不总是能够低于 1,特别是对于高电压器件。在此类情况下,通过栅极驱动电路分流 CGD 电容器充电电流的有效性将决定电路的 dV/dt 抗扰度。图 3 尽管在中,栅极驱动电路仅显示电阻,但驱动电路可能会因布局而包含电感,这可能会对充电电流的有效分流产生重大影响。因此,栅极驱动电路布局成为提高 dV/dt 抗扰度的关键因素。由于使用共同封装的栅极驱动器可以实现更低阻抗的栅极驱动,因此可以产生显著的积极影响。

栅极阈值电压 VTH 在确保 dV/dt 抗扰度方面也非常重要。 尽管最好使用较高的 VTH,但 e-GaN 开关的结构会导致 较低的栅源电压电平。共源共栅 d-GaN 器件比 e-GaN 器 件要好一些,因为其栅极结构是硅,并且栅源电压电平与 硅 MOSFET 的电平相同。

## 反向导通

在使用图腾柱(半桥)功率级的许多开关拓扑中,电源开 关器件的反向导通特性至关重要。虽然硅 MOSFET 中体二 极管的正向压降很低,可确保较低的导通损耗,但其反向恢复却非常缓慢,导致开关损耗极高。

尽管 GaN 器件没有反向体二极管,但由于它们本身是双向 器件,因此也能够反向导通。只要它们的反向电压超过栅 极阀值电压,它们就可以开始进行导通。这种导通类似于 反向体二极管的效果,其切入正向压降等于栅极阈值电 压,动态电阻等于导通电阻。由于这种反向导通是多数载 流子效应,因此没有相关的反向恢复。但是,栅极阈值电 压远高于结二极管的正向电压,因此导通损耗会很大。所 以,在大多数需要反向导通的应用中,您可能需要仔细进 行优化死区时间的同步整流。

共源共栅 d-GaN 器件串联了低压硅 MOSFET,因此具有 反向恢复能力,不过 Qrr 明显低于同类硅超结 MOSFET 的 反向体二极管。

TI 的直接驱动架构完全消除了硅 MOSFET 的反向恢复,因为在开关过程中通道始终处于导通状态,而二极管绝不会进入工作状态。但是,就像在 e-GaN FET 中一样,您应该使用可靠的同步整流方案来解决反向运行期间的较高压降。

# 是否选择软开关

许多电源系统设计人员普遍认为,GaN 电源开关具有非常快速的开关能力,因此能够使软开关或谐振开关拓扑变得不再重要。假设快速开关功能可以实现与硬开关拓扑相同甚至更高的效率,那么,软开关可能变得不再重要。虽然目前借助硅 MOSFET 确实可以实现如此高的开关频率,但正如本文其他部分所讨论的,GaN 器件存在很大的 EOSS 损耗。随着开关频率增加,EOSS 损耗会成为更为主要的损耗因素。由于与硅超结 MOSFET 相比,GaN 器件输出电容中存储的能量更容易恢复,因此采用软开关或谐振开关非常有必要,特别是在数兆赫兹的开关频率下。

# 结论

d-GaN 和 e-GaN 器件的器件架构、封装和性能参数不断 发展,目标是在电源转换器中作为硅 MOSFET 的高效、稳

健且具有成本效益的替代品。毫无疑问,本白皮书中讨论的许多性能参数都将在未来得到显著改善。半桥器件和具有保护电路的集成式栅极驱动器等 GaN 器件具有更高的集成水平,使得它们在电源转换器中的运用变得轻松很多。在软开关拓扑中采用 GaN 器件可以将电源转换器的功率密度提高到硅开关技术领域尚未达到的水平。

## 参考文献

- W. Liu, H. Zhou and E. Persson. "Switching Characteristics of Cascode GaN Switches," PCIM Europe, 2015.

- A. Lidow, M. de Rooij, J. Strydom and D. Reusch. "GaN Transistors for Efficient Power Conversion," Efficient Power Conversion Corp., APEC 2013 Educational Seminar S7, p. 16.

- P. Brohlin、Y.K. Ramadass 和 C. Kaya。《GaN 器件的直接驱动配置》,德州仪器 (TI) 白皮书 (SLPY008),2016 年 10 月。

- 4. D. Jauregui、B. Wang 和 R. Chen。《同步降压转换器的功率损耗计算和共源电感注意事项》,德州仪器 (TI) 应用报告 (SLPA009A), 2011 年 7 月。

- J. Wang and H. Shu-Hung Chung. "Impact of Parasitic Elements on the Spurious Triggering Pulse in Synchronous Buck Converter," IEEE Transactions on Power Electronics, Vol. 29, Issue 12, December 2014, p. 6672-6685.

- 《使用 LMG3410-HB-EVM 半桥和 LMG34XXBB-EVM 分线板 EVM》,德州仪器 (TI) 用户指南 (SNOU140A),2017 年 5 月。

**重要声明:**本文所提及德州仪器 (TI) 及其子公司的产品和服务均依照 TI 标准销售条款和条件进行销售。建议客户在订购之前获取有关 TI 产品和服务的最新和完整信息。TI 对应用帮助、客户的应用或产品设计、软件性能或侵犯专利不负任何责任。有关任何其它公司产品或服务的发布信息均不构成 TI 因此对其的认可、保证或授权。

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司