*User's Guide***LP8752x-Q1 配置指南****摘要**

本配置指南旨在帮助用户了解如何使用微控制器单元 (MCU) 配置 LP8752x-Q1 PMIC。对于每个设计，无需新的一次性可编程配置 (OTP)，可以在启动时通过内部集成电路 (I2C) 总线配置本配置指南中描述的特定 LP8752x-Q1 型号，以满足设计要求。

**内容**

|                                                  |           |

|--------------------------------------------------|-----------|

| <b>1 简介</b> .....                                | <b>2</b>  |

| <b>2 设置</b> .....                                | <b>2</b>  |

| 2.1 SCL/SDA 引脚.....                              | 2         |

| 2.2 NRST 引脚.....                                 | 3         |

| 2.3 EN <sub>x</sub> (GPIO <sub>x</sub> ) 引脚..... | 3         |

| 2.4 nINT.....                                    | 3         |

| <b>3 配置</b> .....                                | <b>4</b>  |

| 3.1 配置序列.....                                    | 4         |

| 3.2 默认 OTP 配置.....                               | 5         |

| 3.3 通过 I2C 来配置寄存器的建议顺序.....                      | 8         |

| <b>4 修订历史记录</b> .....                            | <b>10</b> |

**插图清单**

|                                            |    |

|--------------------------------------------|----|

| 图 2-1. 用于启动配置的与 LP8752x-Q1 的典型 MCU 连接..... | 2  |

| 图 3-1. 启动期间的配置序列 (RESET_REG_MASK = 0)..... | 4  |

| 图 3-2. 启动期间的配置序列 (RESET_REG_MASK = 1)..... | 5  |

| 图 3-3. 复位期间的配置序列.....                      | 5  |

| 图 3-4. 启动和关断序列时序图.....                     | 10 |

**表格清单**

|                                      |   |

|--------------------------------------|---|

| 表 3-1. BUCK <sub>x</sub> OTP 设置..... | 6 |

| 表 3-2. EN、CLKIN 和 GPIO 引脚设置.....     | 6 |

| 表 3-3. PGOOD OTP 设置.....             | 7 |

| 表 3-4. 保护 OTP 设置.....                | 7 |

| 表 3-5. 器件标识和 I2C 设置.....             | 7 |

| 表 3-6. 中断屏蔽设置.....                   | 7 |

| 表 3-7. 稳压器控制设置寄存器.....               | 8 |

**商标**

所有商标均为其各自所有者的财产。

## 1 简介

LP8752x-Q1 包含四个降压直流/直流转换器内核，这些内核配置为 4 相单输出、3 相和单相输出、一个双相和两个单相输出、四个单相输出或两个双相输出。该器件由 I<sup>2</sup>C 兼容串行接口和启用信号进行控制。通常，LP8752x-Q1 PMIC 的输出电压、启动/关断序列等设置在 IC 制造期间由一次性可编程存储器 (OTP) 进行编程。但是，对于 MCU，也可以在每次启动后配置该器件以满足不同的设计要求。配置寄存器（易失性存储器）的默认值在器件上电期间从 OTP 加载，并且通过 I<sup>2</sup>C 总线可以将寄存器更新为所需值。

本文档说明了如何设置在启动时要配置的 LP8752x-Q1 PMIC，以便其可以在不同的设计中使用，而无需新的 OTP。本文档中介绍的特定 OTP 版本旨在允许于每次上电时轻松配置 PMIC。有关器件规格和详细功能，请参阅器件特定数据表。

## 2 设置

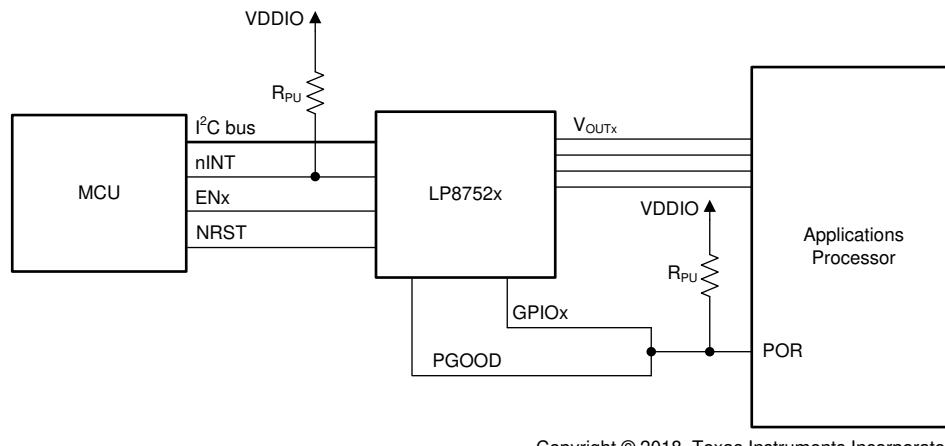

有几个重要的连接可确保 LP8752x-Q1 已正确配置，本节对每个连接进行了介绍。图 2-1 中显示了如何将 MCU 连接到 LP8752x-Q1 PMIC 的一个很好的示例。

Copyright © 2018, Texas Instruments Incorporated

图 2-1. 用于启动配置的与 LP8752x-Q1 的典型 MCU 连接

### 2.1 SCL/SDA 引脚

SCL 和 SDA 线路（分别为引脚 5 和 6）用于通过 I<sup>2</sup>C 兼容接口在 MCU 和 LP8752x-Q1 PMIC 之间进行通信。可通过与 I<sup>2</sup>C 兼容的同步串行接口来访问器件上的可编程功能和寄存器。该协议使用两线制接口在连接到总线的 IC 之间进行双向通信。两条接口线是串行数据线 (SDA) 和串行时钟线 (SCL)。总线上的每个器件都分配有一个唯一的地址，并根据它是产生还是接收串行时钟 (SCL) 来充当主机或从机。SCL 和 SDA 线必须各自在线路上放置一个上拉电阻器，即使在总线空闲时也保持高电平。LP8752x-Q1 支持标准模式 (100kHz)、快速模式 (400kHz)、快速模式增强版 (1MHz) 和高速模式 (3.4MHz)。有关所有 I<sup>2</sup>C 协议详细信息，请参阅器件特定数据表。

## 2.2 NRST 引脚

NRST 引脚 ( 引脚 20 ) 用于复位器件逻辑/启用器件内部逻辑和 I/O 接口。当 NRST 电压低于阈值电平时，LP8752x-Q1 器件的所有电源开关、基准、控制和偏置电路都会关闭。当 NRST 设置为高电平 ( 并且 VANA 高于 UVLO 电平 ) 时，这将启动上电复位 (POR)、OTP 读取并启用系统 I/O 接口。在向 LP8752x-Q1 写入或从中读取数据之前，I2C 主机必须至少留出 1.2ms 的时间。器件在内部启动序列后进入 STANDBY 模式。如果需要，主机可以通过 I2C 更改默认寄存器设置。可以通过 ENx 引脚或 I2C 接口启用/禁用稳压器。

## 2.3 ENx (GPIOx) 引脚

启用引脚 EN1 (GPIO1)、EN2 (GPIO2)、EN3 (GPIO3) ( 引脚 7、15、2 ) 是 I2C 可配置的通用输入/输出 (GPIO) 引脚。可针对 GPIO 就方向、功能和输出类型 ( 开漏或推挽 ) 进行编程。当配置为 EN 引脚时，这些引脚可用于根据编程的时序启动降压转换器启动序列。也可以针对关断时间进行编程。建议将 ENx 引脚驱动为低电平，直到将器件配置为所需设置。当编程为启用信号时，将这些引脚驱动为低电平以禁用，或驱动为高电平以启用相关的降压转换器。

## 2.4 nINT

nINT 引脚 ( 引脚 19 ) 是来自 LP8752x-Q1 PMIC 的开漏、低电平有效输出。将此引脚连接至一个外部上拉电阻器。如果 RESET\_REG\_MASK 位未被屏蔽，则只要 RESET\_REG\_INT 位设置为高电平，就会在该引脚上生成中断。当 VANA 电源电压降至欠压阈值电平以下或主机已使用 RESET 寄存器中的 SW\_RESET 位请求复位或器件由 NRST 复位时，RESET\_REG\_INT 位被设置为高电平。通过监测 nINT 引脚，MCU 知道 PMIC 寄存器何时复位为 OTP 确定的默认值，并采取必要的操作以确保根据需要配置 PMIC。

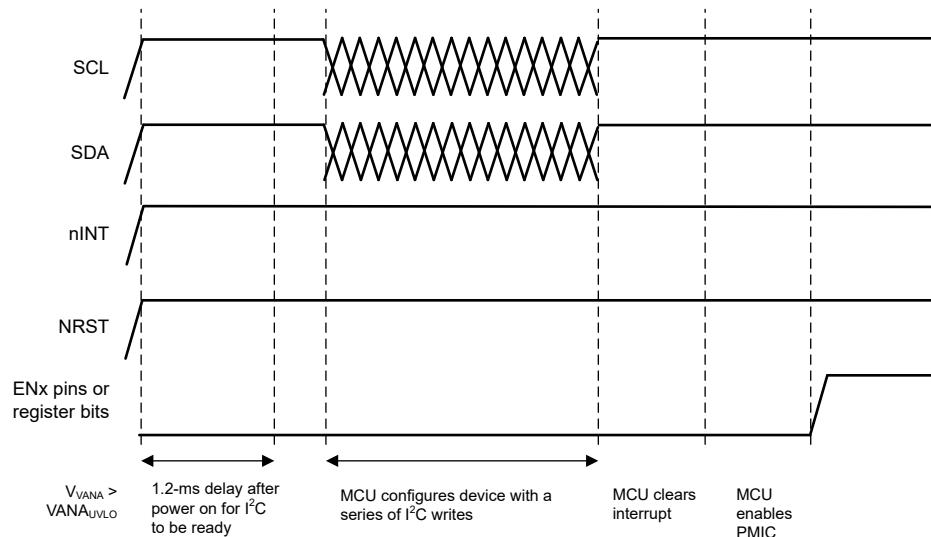

上电复位后，LP8752x-Q1 PMIC 需要 1.2ms 的延迟，然后才能通过 I2C 接口进行任何通信。当 RESET\_REG\_MASK 位未屏蔽时，可以通过 nINT 引脚监测此所需延迟。上电复位后，nINT 引脚会驱动为高电平，同时寄存器复位并读取 OTP 以将寄存器设置为其初始值。在 1.2ms 后，nINT 引脚被驱动为低电平，表明寄存器已复位并通过配置来满足设计要求。

否则，当 RESET\_REG\_MASK 位被屏蔽时，nINT 对上电复位没有任何反应。

---

### 备注

为了正确监控 nINT 引脚，MCU 必须清除所有中断，然后才能启用 LP8752x-Q1 PMIC 上的所有输出。将 1 写入 INT\_TOP2 寄存器中的 RESET\_REG 位，以清除此中断。如果在启用 LP8752x-Q1 PMIC 输出之前未清除所有中断，则当生成中断并且 MCU 无法检测到寄存器复位时，nINT 引脚上没有变化。确保 TOP\_MASK2 寄存器中的 RESET\_REG\_MASK 位未屏蔽，以便在 nINT 上生成中断。

---

### 3 配置

本节介绍了默认 OTP 设置，以及如何配置这些设置来满足设计要求。

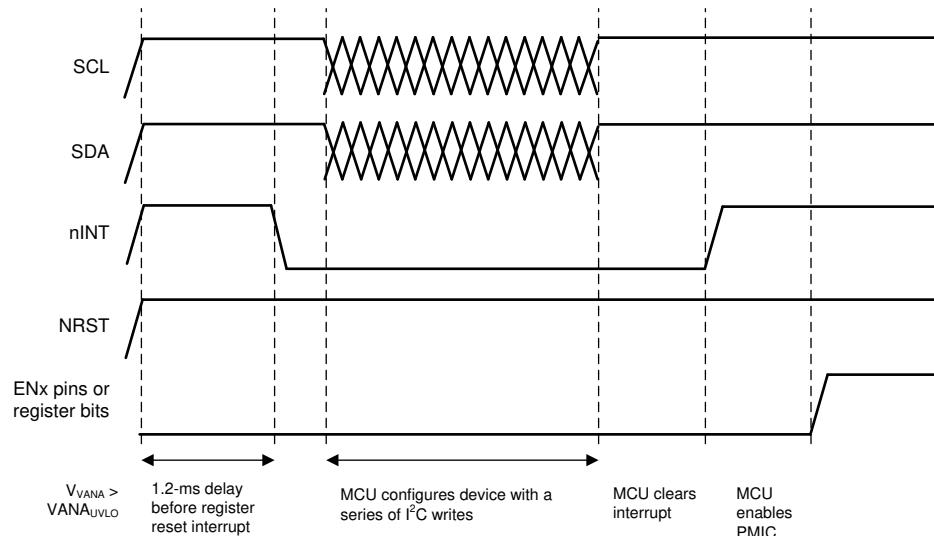

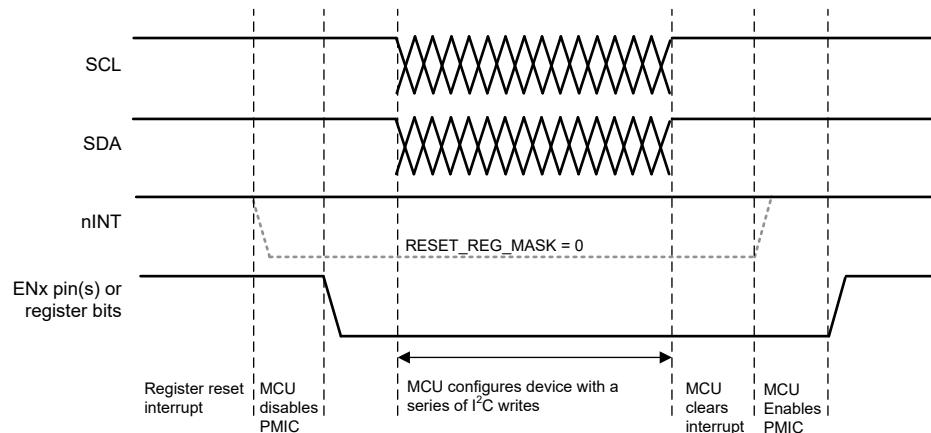

#### 3.1 配置序列

使用[节 2](#)中介绍的设置允许 MCU 在上电复位后或在任何导致寄存器复位的事件之后，轻松配置 LP8752x-Q1 PMIC。为了确保正确完成此操作，请按照本节中所述的顺序进行操作。以下列表示出了确保正确配置 LP8752x-Q1 PMIC 需要执行的操作。这些操作必须在上电复位或寄存器复位之后执行。

1. 将 PMIC 上电。 $(V_{VANA} > V_{ANA\_UVLO})$

2. 将 NRST 设置为高电平

3. 等待 1.2ms ( 或如果  $\text{RESET\_REG\_MASK} = 0$ ，则 nINT 线路设置为低电平 )

4. 按照建议的顺序使用 I<sup>2</sup>C 通信设置新配置。请参阅[节 3.3](#)。

- a. 电压设置

- b. 稳压器设置

- c. GPIO 设置

- d. 时钟同步功能

- e. PGOOD 设置

- f. 中断设置

- g. 启动/关闭设置

- h. 设置 EN<sub>x</sub> 引脚控制位

- i. 设置 EN\_BUCK<sub>x</sub> 位

5. 清除中断。

6. 将 EN<sub>x</sub> 引脚设置为高电平以启动序列。

上电复位时，等待 nINT 线路设置为低电平可确保 PMIC 已为 I<sup>2</sup>C 通信做好准备。通过等待 nINT 线路在任何其他时间设置为低电平，PMIC 可以知道何时发生了寄存器复位。[图 3-1](#)、[图 3-2](#) 和 [图 3-3](#) 中的时序图显示了发生上电复位或寄存器复位后如何配置 LP8752x-Q1 PMIC。所有 I<sup>2</sup>C 写入完成后，MCU 会清除中断并启用 PMIC。MCU 可以通过向 RESET\_REG 位写入 1 来清除中断，并通过将 EN<sub>x</sub> 引脚拉至高电平来打开 PMIC 输出以实现该目的。

图 3-1. 启动期间的配置序列 (RESET\_REG\_MASK = 0)

图 3-2. 启动期间的配置序列 (RESET\_REG\_MASK = 1)

图 3-3. 复位期间的配置序列

### 3.2 默认 OTP 配置

所有 LP8752x-Q1 PMIC 资源设置都以易失性寄存器的形式存储。这些设置定义了降压输出电压、GPIO 功能，以及上电和断电序列。有关设置寄存器的完整列表，请参阅器件特定的数据表。对于每种可能的相位配置，都需要不同的 OTP。相位配置不可通过 I<sup>2</sup>C 来配置。

每个器件都在 OTP 中存储了预定义值，用于控制器件的默认配置。有关每个器件的默认 OTP 编程值，请参阅特定于器件的技术参考手册 (TRM)。本节中的表格列出了每个位的可配置性。

表 3-1 显示了 BUCK0、BUCK1、BUCK2、BUCK3 的器件设置。BUCKx 允许的最大压摆率取决于输出电容。有关输出电容边界条件，请参阅器件特定数据表。

表 3-1. BUCKx OTP 设置

|         | 说明                                                                                         | 位名称                     | 可配置                                                                                                        |

|---------|--------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------|

| 常规设置    | 降压相位配置（例如，四个单相表示为 1+1+1+1，四个相位单相输出表示为 4 ph）。对于多相配置，主降压转换器定义了输出电压、启动/关断时间等。更多信息，请参阅器件专用数据表。 | -                       | 不涉及以下器件型号：<br>LP87521x - 4 相<br>LP87522x - 3+1<br>LP87523x - 2+1+1<br>LP87524x - 1+1+1+1<br>LP87525x - 2+2 |

|         | 开关频率                                                                                       | -                       | 否                                                                                                          |

|         | 展频                                                                                         | EN_SPREAD_SPEC          | 是                                                                                                          |

|         | 启动和关断延迟范围，0...4.8ms / 0... 10ms / 0...15ms / 0...30ms                                      | DOUBLE_DELAY、HALF_DELAY | 是                                                                                                          |

| BUCK 设置 | 输出电压                                                                                       | BUCKx_VSET              | 是                                                                                                          |

|         | 启用，ENx 引脚或 I2C 寄存器                                                                         | EN_PIN_CTRLx            | 是                                                                                                          |

|         | BUCK0 的控制                                                                                  | EN_BUCKx                | 是                                                                                                          |

|         | 强制使用 PWM 模式或自动模式                                                                           | BUCKx_FPWM              | 是                                                                                                          |

|         | 强制使用多相模式或自动模式                                                                              | BUCKx_FPWM_MP           | 是                                                                                                          |

|         | 峰值电流限值                                                                                     | ILIMx                   | 否                                                                                                          |

|         | 压摆率                                                                                        | SLEW_RATEx              | 是                                                                                                          |

|         | 启动延迟                                                                                       | BUCKx_STARTUP_DELAY     | 是                                                                                                          |

|         | 关断延迟                                                                                       | BUCKx_SHUTDOWN_DELAY    | 是                                                                                                          |

表 3-2 列出了 GPIO 的器件设置。

表 3-2. EN、CLKIN 和 GPIO 引脚设置

|                | 说明                                | 位名称                                   | 可配置 |

|----------------|-----------------------------------|---------------------------------------|-----|

| EN1 (GPIO1) 引脚 | EN1 (GPIO1) 引脚下拉电阻器启用或禁用          | EN1_PD                                | 是   |

| EN2 (GPIO2) 引脚 | EN2 (GPIO2) 引脚下拉电阻器启用或禁用          | EN2_PD                                | 是   |

| EN3 (GPIO3) 引脚 | EN3 (GPIO3) 引脚下拉电阻器启用或禁用          | EN3_PD                                | 是   |

| CLKIN 引脚       | CLKIN 引脚下拉电阻器启用或禁用                | CLKIN_PD                              | 是   |

|                | 连接到 CLKIN 时外部时钟的频率                | EXT_CLK_FREQ                          | 是   |

|                | 内部 PLL 的模式。当 PLL 禁用时，会使用内部 RC OSC | PLL_MODE                              | 是   |

| EN1 (GPIO) 控制  | 启用或 GPIO                          | GPIO1_SEL                             | 是   |

|                | GPIO 模式下的输入或输出                    | GPIO1_DIR                             | 是   |

|                | 输出类型开漏或推挽                         | GPIO1_OD                              | 是   |

|                | GPIO 输出的默认状态                      | GPIO1_OUT                             | 是   |

| EN2 (GPIO) 控制  | 启用或 GPIO                          | GPIO2_SEL                             | 是   |

|                | GPIO 模式下的输入或输出                    | GPIO2_DIR                             | 是   |

|                | 输出类型开漏或推挽                         | GPIO2_OD                              | 是   |

|                | GPIO 输出的默认状态                      | GPIO2_OUT                             | 是   |

|                | GPIO、EN2 或 EN3 的引脚控制              | EN_PIN_CTRL_GPIO2、EN_PIN_SELECT_GPIO2 | 是   |

|                | 启动延迟                              | GPIO2_STARTUP_DELAY                   | 是   |

|                | 关断延迟                              | GPIO2_SHUTDOWN_DELAY                  | 是   |

**表 3-2. EN、CLKIN 和 GPIO 引脚设置 (续)**

|               | 说明                   | 位名称                                   | 可配置 |

|---------------|----------------------|---------------------------------------|-----|

| EN3 (GPIO) 控制 | 启用或 GPIO             | GPIO3_SEL                             | 是   |

|               | GPIO 模式下的输入或输出       | GPIO3_DIR                             | 是   |

|               | 输出类型开漏或推挽            | GPIO3_OD                              | 是   |

|               | GPIO 输出的默认状态         | GPIO3_OUT                             | 是   |

|               | GPIO、EN2 或 EN3 的引脚控制 | EN_PIN_CTRL_GPIO3、EN_PIN_SELECT_GPIO3 | 是   |

|               | 启动延迟                 | GPIO3_STARTUP_DELAY                   | 是   |

|               | 关断延迟                 | GPIO3_SHUTDOWN_DELAY                  | 是   |

表 3-3 示出了 PGOOD 的器件设置。

**表 3-3. PGOOD OTP 设置**

|               | 说明                                   | 位名称             | 可配置 |

|---------------|--------------------------------------|-----------------|-----|

| 信号通过 PGOOD 监控 | BUCKx 输出电压/电压和电流 ( 主降压转换器 )          | PGx_SEL         | 是   |

| PGOOD 模式选择    | BUCKx 的 PGOOD 阈值 ( 欠压/窗口 ( 欠压和过压 ) ) | PGOOD_WINDOW    | 是   |

|               | PGOOD 有效去抖动时间                        | PGOOD_SET_DELAY | 是   |

|               | PGOOD 信号模式 ( 状态/在读取故障源前锁存 )          | EN_PGFLT_STAT   | 是   |

|               | PGOOD 输出模式 ( 推挽或开漏 )                 | PGOOD_OD        | 是   |

|               | PGOOD 极性 ( 高电平有效/低电平有效 )             | PGOOD_POL       | 是   |

表 3-4 列出了热警告的器件设置。有关中断设置，请参阅表 3-6。

**表 3-4. 保护 OTP 设置**

|      | 说明                      | 位名称             | 可配置 |

|------|-------------------------|-----------------|-----|

| 保护功能 | 热警告级别 ( 125°C 或 137°C ) | TDIE_WARN_LEVEL | 是   |

|      | 输入过压保护                  | -               | 否   |

表 3-5 展示了 I2C 和 OTP 修订版 ID 值的器件设置。

**表 3-5. 器件标识和 I2C 设置**

|                    | 说明        | 位名称 | 可配置                    |

|--------------------|-----------|-----|------------------------|

| I2C 从器件 ID ( 7 位 ) | 器件 I2C 地址 | -   | 否<br>请参阅<br>TRM 了解默认值。 |

表 3-6 列出了中断的器件设置。如果未屏蔽事件的中断，则会向 nINT 引脚生成中断。

**表 3-6. 中断屏蔽设置**

|       | 中断事件                | 位名称               | 可配置 |

|-------|---------------------|-------------------|-----|

| 通用    | 同步时钟出现或消失           | SYNC_CLK_MASK     | 是   |

|       | 热警告                 | TDIE_WARN_MASK    | 是   |

|       | 负载测量就绪              | I_LOAD_READY_MASK | 是   |

|       | 寄存器复位               | RESET_REG_MASK    | 是   |

| BUCK0 | Buck0 PGOOD 已达到阈值电平 | BUCK0_PG_MASK     | 是   |

|       | Buck0 电流限制已触发       | BUCK0_ILIM_MASK   | 是   |

| BUCK1 | Buck1 PGOOD 已达到阈值电平 | BUCK1_PG_MASK     | 是   |

|       | Buck1 电流限制已触发       | BUCK1_ILIM_MASK   | 是   |

| BUCK2 | Buck2 PGOOD 已达到阈值电平 | BUCK2_PG_MASK     | 是   |

|       | Buck2 电流限制已触发       | BUCK2_ILIM_MASK   | 是   |

| BUCK3 | Buck3 PGOOD 已达到阈值电平 | BUCK3_PG_MASK     | 是   |

|       | Buck3 电流限制已触发       | BUCK3_ILIM_MASK   | 是   |

### 3.3 通过 I<sup>2</sup>C 来配置寄存器的建议顺序

本节按照建议的顺序介绍了经配置可适配特定设计的主要设置。有关所有这些设置及其相应的位/寄存器，请参阅器件特定数据表和 [节 3.2](#)。

#### 3.3.1 电压设置

降压转换器的默认电压设置取决于 OTP。请参阅器件 TRM 以了解默认值。通过写入下面所列相应字段来更改默认电压设置。要了解这些寄存器的值与不同的电压之间的对应关系，请参阅器件特定数据表。根据相位配置，只需设置主降压电压。

- BUCK0\_VOUT 寄存器中的 BUCK0\_VSET 字段

- BUCK1\_VOUT 寄存器中的 BUCK1\_VSET 字段

- BUCK2\_VOUT 寄存器中的 BUCK2\_VSET 字段

- BUCK3\_VOUT 寄存器中的 BUCK3\_VSET 字段

#### 3.3.2 其他稳压器设置

每个降压转换器都有 2 个 CTRL 寄存器，可用于设置其、压摆率以及启用其输出放电电阻器或设置自动/强制 PWM 模式和自动/强制多相模式。这些寄存器中包含每个稳压器的 EN\_PIN\_CTRLx、EN\_BUCKx 和 BUCKx\_EN\_PIN\_SELECT[1:0] 位。建议最后设置 EN\_PIN\_CTRLx、EN\_BUCKx 和 BUCKx\_EN\_PIN\_SELECT[1:0] 位，以避免任何稳压器在配置完成之前打开。这些调节器设置字段在 [图 2-1](#) 中进行了汇总。有关所有寄存器及其设置的完整说明，请参阅器件特定的数据表。

**表 3-7. 稳压器控制设置寄存器**

| 稳压器   | 寄存器          | 预期应当已经配置的字段                                      | 用于在 PMIC 准备好上电时配置的字段 ( <a href="#">节 3.3.8</a> )    |

|-------|--------------|--------------------------------------------------|-----------------------------------------------------|

| BUCK0 | BUCK0_CTRL_1 | EN_ROOF_FLOOR0、EN_RDIS0、BUCK0_FPWM、BUCK0_FPWM_MP | BUCK0_EN_PIN_CTRL、EN_BUCK0、BUCK0_EN_PIN_SELECT[1:0] |

|       | BUCK0_CTRL_2 | SLEW_RATE0[1:0]                                  |                                                     |

| BUCK1 | BUCK1_CTRL_1 | EN_ROOF_FLOOR1、EN_RDIS1、BUCK1_FPWM               | BUCK1_EN_PIN_CTRL、EN_BUCK1、BUCK1_EN_PIN_SELECT[1:0] |

|       | BUCK1_CTRL_2 | SLEW_RATE1[1:0]                                  |                                                     |

| BUCK2 | BUCK2_CTRL_1 | EN_ROOF_FLOOR2、EN_RDIS2、BUCK2_FPWM、BUCK2_FPWM_MP | BUCK2_EN_PIN_CTRL、EN_BUCK2、BUCK2_EN_PIN_SELECT[1:0] |

|       | BUCK2_CTRL_2 | SLEW_RATE2[1:0]                                  |                                                     |

| BUCK3 | BUCK3_CTRL_1 | EN_ROOF_FLOOR3、EN_RDIS3、BUCK3_FPWM               | BUCK3_EN_PIN_CTRL、EN_BUCK3、BUCK3_EN_PIN_SELECT[1:0] |

|       | BUCK3_CTRL_2 | SLEW_RATE3[1:0]                                  |                                                     |

#### 3.3.3 GPO 设置

LP8752x-Q1 器件最多支持三个 GPIO 信号。GPIO 信号与启用信号进行多路复用。可以通过 PIN\_FUNCTION 寄存器中的 GPIOx\_SEL 位来设置启用和 GPIO 功能之间的选择。当为 GPIO 功能选择引脚时，其他位定义 GPIO 的工作方式：

- GPIOx\_DIR 定义 GPIO、输入或输出的方向 ( GPIO\_CONFIG 寄存器 )

- GPIOx\_OD 定义 GPIO 设置为输出时的输出类型，可以是具有 VANA 电平的推挽或开漏 ( GPIO\_CONFIG 寄存器 )

当 GPIO<sub>x</sub> 定义为输出时，引脚的逻辑电平由 GPIO<sub>x\_OUT</sub> 位（在 GPIO\_OUT 寄存器中）设置。当 GPIO<sub>x</sub> 定义为输入时，从 GPIO<sub>x\_IN</sub> 位（在 GPIO\_IN 寄存器中）读取引脚的逻辑电平。可包括配置为输出的 GPIO 控制以启动和关断序列。具有 EN<sub>x</sub> 信号的序列的 GPIO 控制通过 EN\_PIN\_CTRL\_GPIO<sub>x</sub> 和 EN\_PIN\_SELECT\_GPIO<sub>x</sub> 位（在 PIN\_FUNCTION 寄存器中）来选择。启动和关断期间的延迟由 GPIO<sub>x\_STARTUP\_DELAY[3:0]</sub> 和 GPIO<sub>x\_SHUTDOWN\_DELAY[3:0]</sub> 位（在 GPIO\_DELAY 寄存器中）进行设置，设置方式与稳压器的控制相同。GPIO<sub>x</sub> 信号具有可选的下拉电阻器。下拉电阻通过 EN<sub>x\_PD</sub> 位（在 CONFIG 寄存器中）选择。有关 GPIO 寄存器中每个字段的更多信息，请参阅器件特定数据表。

### 3.3.4 时钟同步功能

LP8752x-Q1 器件包含一个 CLKIN 输入，用于将降压稳压器的开关时钟与外部时钟同步。根据 PLL\_MODE[1:0] 位（在 PLL\_CTRL 寄存器中）和外部时钟可用性，选择外部时钟并生成中断。或者，使用 TOP\_MASK1 寄存器中的 SYNC\_CLK\_MASK 位屏蔽此中断。外部输入时钟的标称频率由 EXT\_CLK\_FREQ[4:0] 位设置（在 PLL\_CTRL 寄存器中），范围为 1MHz 至 24MHz，具有 1MHz 阶跃。外部时钟必须在精度限制范围（-30%/+10%）内才能实现有效时钟检测。更多有关此功能的信息，请参阅器件特定数据表。

### 3.3.5 PGOOD 设置

PGOOD 输出可用于监控多个信号，并具有多种要配置的设置，如下所示。

- 监控稳压器输出电压（各个稳压器都是可选的）

- 仅欠压或欠压及过压监控

- 监控输出电流

- 去抖动时间设置

- 推挽或开漏输出

- 选通或连续工作模式

- 可调节的极性

更多有关 PGOOD 信号功能的信息，请参阅器件特定数据表。

### 3.3.6 中断设置

LP8752x-Q1 PMIC 具有许多中断信号，用于指示不同的事件，包括稳压器过流事件、稳压器 PGOOD 事件、稳压器短路事件和时钟事件。包含所有这些中断的寄存器如下面所列：

- INT\_TOP1 寄存器

- INT\_TOP2 寄存器

- INT\_BUCK\_0\_1 寄存器

- INT\_BUCK\_2\_3 寄存器

可以使用下面的寄存器屏蔽或取消屏蔽这些中断。有关默认的屏蔽设置，请参阅器件特定 TRM。当 RESET\_REG\_INT 位未被屏蔽时，MCU 可以知道 PMIC 寄存器何时复位为 OTP 确定的值，因此 MCU 会根据需要采取必要的操作来验证 PMIC 是否已配置。根据需要来取消屏蔽其他中断。如果多个中断未被屏蔽，则读取中断寄存器以确定在 nINT 线路上生成中断时的具体原因。

- TOP\_MASK1 寄存器

- TOP\_MASK2 寄存器

- BUCK\_0\_1\_MASK 寄存器

- BUCK\_2\_3\_MASK 寄存器

### 3.3.7 启动和关断序列

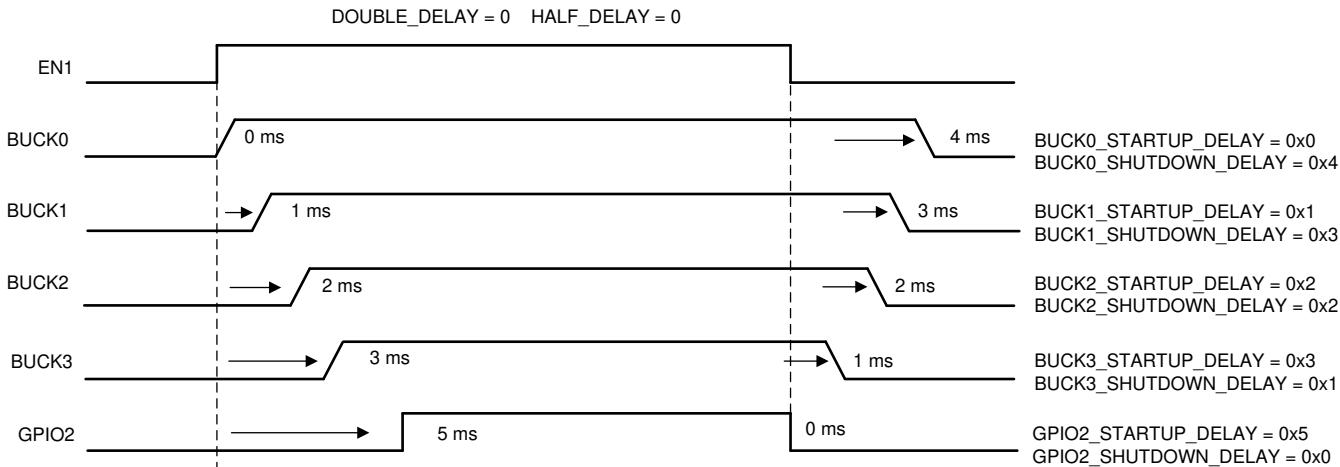

LP8752x-Q1 上的每个降压转换器和 GPO 都可以设置为按特定序列启动和关断。要配置所需序列，需要将每个输出的 STARTUP\_DELAY 和 SHUTDOWN\_DELAY 字段设置为 0x0 和 0xF 之间的值。此值对应的延迟时间取决于位于 CONFIG 寄存器中的 DOUBLE\_DELAY 位和 HALF\_DELAY 位。这两个位上的值均为 0 时，可以 1ms 的步长实现 0ms 至 15ms 的延迟范围。图 3-4 显示了一个示例，说明如何使用这些延迟来配置启动和关断序列，在本例中使用 EN1 信号。有关所有寄存器及其设置的完整说明，请参阅器件特定的数据表。

图 3-4. 启动和关断序列时序图

### 3.3.8 设置 EN<sub>x</sub> 引脚控制位

每个输出都可以由 I2C 通信或者 EN<sub>x</sub> 引脚的组合进行控制，具体取决于每个输出的 EN\_PIN\_CTRL<sub>x</sub> 和 BUCK<sub>x</sub>\_EN\_PIN\_SELECT[1:0] 位。通过 I2C (EN\_PIN\_CTRL<sub>x</sub> = 0) 进行控制时，会使用相应的 EN\_BUCK<sub>x</sub> 位打开所选输出。请注意，在这种情况下，时序控制延迟设置无效。当使用 I2C 和 EN<sub>x</sub> 引脚的组合 (EN\_PIN\_CTRL<sub>x</sub> = 1) 进行控制时，EN<sub>x</sub> 引脚 (通过 BUCK<sub>x</sub>\_EN\_PIN\_SELECT[1:0] 进行设置) 和相应的 EN\_BUCK<sub>x</sub> 位都必须设置为高电平才能开启输出。

设置所有其他器件设置后，针对需要在设计中打开的每个输出，将 EN\_PIN\_CTRL<sub>x</sub> 位设置为高电平，从而允许 EN<sub>x</sub> 引脚控制每个所需的输出。

### 3.3.9 设置 EN\_BUCK<sub>x</sub> 位

一旦针对需要在设计中打开的每个输出将 EN\_PIN\_CTRL<sub>x</sub> 位设置为高电平，每个相应输出的 EN\_BUCK<sub>x</sub> 位也可以设置为高电平。重要的是在 EN\_BUCK<sub>x</sub> 位之前设置 EN\_PIN\_CTRL<sub>x</sub> 位，以便不会意外打开任何输出。当 EN\_BUCK<sub>x</sub> 位设置为高电平时，MCU 必须完成所需的 I2C 命令，并可以继续清除中断并将 EN<sub>x</sub> 引脚设置为高电平以将启动序列启动，如节 3.1 中所述。

## 4 修订历史记录

注：以前版本的页码可能与当前版本的页码不同

| Changes from Revision * (October 2018) to Revision A (July 2025) | Page |

|------------------------------------------------------------------|------|

| • 阐明了 nINT 行为取决于 RESET_REG_MASK 位.....                           | 3    |

| • 添加了图 3-2 .....                                                 | 4    |

| • 以掩码相关的 nINT 响应更新了 图 3-3 .....                                  | 4    |

| • 将 LP8752x-Q1 特定引用更改为一般配置设置.....                                | 5    |

| • 从表中删除了 LP8752x-Q1 列.....                                       | 5    |

| • 将电压设置更改成与 OTP 相关.....                                          | 8    |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025 , 德州仪器 (TI) 公司