# User's Guide

# DLP2021-Q1 和 DLP3021-Q1 FPGA

#### 摘要

本文档定义了为 Spartan 7 (XA7S15-1CPGA196Q) 实现的 DLP® 汽车动态地面投影 FPGA 设计的接口和功能。 某些规格基于 Spartan 7 硬件模块和非设计特定限制。在这些情况下,如果存在冲突值,则认为 Xilinx Spartan 7 文档是更准确的信息来源。

# 内容

| 1 | 简介                           | 3              |

|---|------------------------------|----------------|

|   | 1.1 用途和范围                    | 3              |

| 2 | : FPGA 引脚配置和功能               | 4              |

|   | 2.1 DMD 接口                   | 4              |

|   | 2.2 光控制                      | 5              |

|   | 2.3 通信                       | <mark>5</mark> |

|   | 2.4 支持                       | 6              |

|   | 2.5 FPGA 专用引脚                | 6              |

|   | 2.6 电源和接地                    | <mark>7</mark> |

|   | 2.7 未使用的引脚                   | 7              |

| 3 | 规格                           | 9              |

|   | 3.1 建议运行条件                   | 9              |

|   | 3.2 FPGA 功耗                  | 9              |

|   | 3.3 主机 SPI 接口时序              | 9              |

|   | 3.4 电源和复位时序                  | 10             |

|   | 3.5 DMD 接口时序                 | 12             |

|   | 3.6 闪存存储器接口时序                | 12             |

|   | 3.7 基准时钟时序                   | 12             |

|   | 3.8 I2C 接口时序                 | 13             |

| 4 | 特性描述                         | 13             |

|   | 4.1 视频控制器                    | 13             |

|   | 4.2 温度测量                     | 17             |

|   | 4.3 PWM 输出                   | 17             |

|   | 4.4 主机 IRQ 中断信号              | 18             |

|   | 4.5 视频和图像压缩                  | 18             |

| 5 | ;布局                          | 19             |

| 6 | 5 主机命令协议                     | 19             |

|   | 6.1 SPI 规格                   | 19             |

|   | 6.2 SPI 写入命令                 | 20             |

|   | 6.3 SPI 读取命令                 | 20             |

| 7 | ' FPGA 寄存器定义                 | 21             |

| 8 | 修订历史记录                       | 29             |

|   |                              |                |

|   | 插图清单                         |                |

| E | <b>3 1-1</b> . 动态地面投影电子产品方框图 | 3              |

|   | 图 3-1. 主机 SPI 接口时序图          |                |

|   | 图 3-2. 上电时序图                 |                |

|   | 图 3-3. 断电时序图                 |                |

| E | 图 4-1. 典型 PWM 电路             | 18             |

| E | 图 6-1. SPI 写入命令格式            | 20             |

|   |                              |                |

| 图 6-2. SPI 读取命令格式                                    | 20 |

|------------------------------------------------------|----|

| <del>하</del> 사수 가는 수수                                |    |

| 表格清单                                                 |    |

| 表 2-1. DMD 接口引脚说明                                    |    |

| 表 2-2. 光控制引脚说明                                       |    |

| 表 2-3. 通信引脚说明                                        |    |

| 表 2-4. 支持引脚说明                                        |    |

| 表 2-5. FPGA 专用引脚说明                                   |    |

| 表 2-6. 电源和接地引脚说明                                     |    |

| 表 2-7. 未使用的引脚                                        |    |

| 表 3-1. 建议运行条件                                        |    |

| 表 3-2. FPGA 功耗规格                                     |    |

| 表 3-3. 主机 SPI 接口时序                                   |    |

| 表 3-4. 上电时序规格                                        |    |

| 表 3-5. 断电时序规格                                        |    |

| 表 3-6. 欠压检测规格                                        |    |

| 表 3-7. DMD 接口时序规格                                    |    |

| 表 3-8. 闪存存储器接口时序                                     |    |

| 表 3-9. 基准时钟时序规格                                      |    |

| 表 3-10. I <sup>2</sup> C 接口时序 <sup>(1)</sup> (2)     |    |

| 表 4-1. 视频控制寄存器配置                                     |    |

| 表 4-2. PWM 选择配置                                      |    |

| 表 4-3. DLP3021-Q1 的典型存储能力                            |    |

| 表 4-4. DLP2021-Q1 的典型存储能力                            |    |

| 表 6-1. SPI 规格                                        |    |

| 表 6-2. SPI MOSI 写入命令信息                               |    |

| 表 6-3. SPI MISO 写入命令信息                               |    |

| 表 6-4. SPI MOSI 读取命令信息                               |    |

| 表 6-5. SPI MISO 读取命令信息                               |    |

| 表 7-1. FPGA SPI 寄存器                                  |    |

| 表 7-2. 器件访问类型代码                                      |    |

| 表 7-3. FPGA_INTERRUPT_CLEAR 寄存器字段说明                  |    |

| 表 7-4. FPGA_INTERRUPT_SET 寄存器字段说明                    |    |

| 表 7-5. FPGA_INTERRUPT_ENABLE 寄存器字段说明                 |    |

| 表 7-6. FPGA_VERSION 寄存器字段说明                          |    |

| 表 7-7. FMT_FLIP 寄存器字段说明                              |    |

| 表 7-8. RSC_SEQBUF_SELECT 寄存器字段说明                     |    |

| 表 7-9. PWM_CONTROL 寄存器字段说明                           | 24 |

| 表 7-10. VCM_FRAME_RATE 寄存器字段说明                       |    |

| 表 7-11. VCM_START_ADDR1 寄存器字段说明                      |    |

| 表 7-12. VCM_CONFIG1 寄存器字段说明                          |    |

| 表 7-13. VCM_START_ADDR2 寄存器字段说明                      |    |

| 表 7-14. VCM_CONFIG2 寄存器字段说明                          |    |

| 表 7-15. VCM_CONTROL 寄存器字段说明                          |    |

| 表 7-16. VCM_STATUS 寄存器字段说明                           |    |

| 表 7-17. TMP_CTRL 寄存器字段说明                             |    |

| 表 7-18. TMP_STATUS 寄存器字段说明                           |    |

| 表 7-19. FAULT_STATUS 寄存器字段说明                         |    |

| 表 7-20. TMP_LOCAL_TEMP 寄存器字段说明                       | 29 |

| 商标                                                   |    |

| DLP® is a registered trademark of Texas Instruments. |    |

| 所有商标均为其各自所有者的财产。                                     |    |

| // · · · · · · · · · · · · · · · · · ·               |    |

# 1 简介

# 1.1 用途和范围

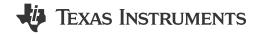

在此应用中,FPGA 直接从闪存存储器中读取要在 DMD 上显示的视频数据。FPGA 还可以协调照明时序,以与显示的视频内容相协调。

图 1-1. 动态地面投影电子产品方框图

# 2 FPGA 引脚配置和功能

本节详细介绍了 FPGA 的引脚配置,并描述了每个引脚的功能和 I/O 类型。

# 2.1 DMD 接口

表 2-1. DMD 接口引脚说明

| 表 2-1. DMD 接口引         |           | 脚说明<br> |    |                                                                                                              |

|------------------------|-----------|---------|----|--------------------------------------------------------------------------------------------------------------|

|                        | <b> 脚</b> | I/O     |    |                                                                                                              |

| 名称                     | 编号        | 电源      | 类型 | 说明                                                                                                           |

| D0                     | L14       | 1.8V    | 0  | DMD 数据引脚                                                                                                     |

| D1                     | L13       | 1.8V    | 0  |                                                                                                              |

| D2                     | J14       | 1.8V    | 0  |                                                                                                              |

| D3                     | K12       | 1.8V    | 0  |                                                                                                              |

| D4                     | H12       | 1.8V    | 0  |                                                                                                              |

| D5                     | K13       | 1.8V    | 0  |                                                                                                              |

| D6                     | G14       | 1.8V    | 0  |                                                                                                              |

| D7                     | H14       | 1.8V    | 0  |                                                                                                              |

| D8                     | H13       | 1.8V    | 0  |                                                                                                              |

| D9                     | G12       | 1.8V    | 0  |                                                                                                              |

| D10 <sup>(1)</sup>     | F14       | 1.8V    | 0  |                                                                                                              |

| D11 <sup>(1)</sup>     | E12       | 1.8V    | 0  |                                                                                                              |

| D12 <sup>(1)</sup>     | E13       | 1.8V    | 0  |                                                                                                              |

| D13 <sup>(1)</sup>     | F13       | 1.8V    | 0  |                                                                                                              |

| D14 <sup>(1)</sup>     | D14       | 1.8V    | 0  |                                                                                                              |

| DCLK                   | B14       | 1.8V    | 0  | DMD 数据时钟 (DDR)                                                                                               |

| TRC                    | C14       | 1.8V    | 0  | DMD 数据切换速率控制                                                                                                 |

| LOADB                  | C13       | 1.8V    | 0  | DMD 数据加载信号(低电平有效)                                                                                            |

| SAC 总线                 | M14       | 1.8V    | 0  | DMD SAC 总线数据                                                                                                 |

| SAC 时钟                 | N13       | 1.8V    | 0  | DMD SAC 总线时钟                                                                                                 |

| DAD 总线                 | N14       | 1.8V    | 0  | DMD DAD 总线数据                                                                                                 |

| DMD TDO <sup>(1)</sup> | P12       | 1.8V    | I  | DMD 接口测试数据输入。连接到 DMD JTAG 接口的信号,以便允许验证接口。此信号连接到 DMD JTAG TDO。包括一个内部上拉电阻器。DMD 设计中未实现 FPGA JTAG 功能。此引脚可保持断开状态。 |

| DMD TDI <sup>(1)</sup> | P10       | 1.8V    | 0  | DMD 接口测试数据输出。连接到 DMD JTAG 接口的信号,以便允许验证接口。此信号连接到 DMD JTAG TDI。<br>DMD 设计中未实现 FPGA JTAG 功能。此引脚可保持断开状态。         |

| DMD TCK <sup>(1)</sup> | P11       | 1.8V    | 0  | DMD 接口测试数据输入。连接到 DMD JTAG 接口的信号,以便允许验证接口。此信号连接到 DMD JTAG TDO。<br>DMD 设计中未实现 FPGA JTAG 功能。此引脚可保持断开状态。         |

| DMD TMS <sup>(1)</sup> | M10       | 1.8V    | 0  | DMD 接口测试模式。连接到 DMD JTAG 接口的信号,以便允许验证接口。<br>DMD 设计中未实现 FPGA JTAG 功能。此引脚可保持断开状态。                               |

| 复位 OEZ                 | P13       | 1.8V    | 0  | DMD DAD 输出启用(低电平有效)。当处于三态时,需要连接至 DMD 接口的 1.8V 电源轨的上拉电阻器,以使此信号保持非活动状态。                                        |

| SCTRL                  | A13       | 1.8V    | 0  | DMD 数据串行控制信号                                                                                                 |

| 复位选通                   | M12       | 1.8V    | 0  | DMD DAD 总线选通                                                                                                 |

<sup>(1)</sup> 此引脚不适用于 DLP2021-Q1。

# 2.2 光控制

# 表 2-2. 光控制引脚说明

| 引        | 引脚 I/O |      |    |            |

|----------|--------|------|----|------------|

| 名称       | 编号     | 电源   | 类型 | 说明         |

| S_EN     | A2     | 3.3V | 0  | 照明驱动器的分流启用 |

| R_EN     | A3     | 3.3V | 0  | 照明驱动器的红色选择 |

| G_EN     | A4     | 3.3V | 0  | 照明驱动器的绿色选择 |

| B_EN     | A5     | 3.3V | 0  | 照明驱动器的蓝色选择 |

| LED_EN   | B6     | 3.3V | 0  | 启用照明驱动器    |

| PWM0     | N2     | 3.3V | 0  | 红色 PWM 输出  |

| PWM1     | N3     | 3.3V | 0  | 绿色 PWM 输出  |

| PWM2     | P3     | 3.3V | 0  | 蓝色 PWM 输出  |

| PWM_SEL0 | P4     | 3.3V | 0  | 编码 PWM 选择  |

| PWM_SEL1 | N4     | 3.3V | 0  | 编码 PWM 选择  |

# 2.3 通信

# 表 2-3. 通信引脚说明

| 引脚 I/O                |         | F 90 73 |    |                                                                                 |

|-----------------------|---------|---------|----|---------------------------------------------------------------------------------|

|                       | 编号      | 电源      | 类型 | <br>说明                                                                          |

| 主机时钟                  | H3      | 3.3V    | I  | SPI 端口(从机)时钟                                                                    |

| 主机 MOSI               | H1      | 3.3V    | I  | SPI 端口(从器件)数据输入                                                                 |

| 主机 MISO               | J1      | 3.3V    | 0  | SPI 端口(从器件)数据输出                                                                 |

| 主机 CS                 | M1      | 3.3V    | I  | SPI 端口(从器件)芯片选择                                                                 |

| 主机 IRQ                | N1      | 3.3V    | 0  | 主机中断                                                                            |

| 温度 SDA <sup>(1)</sup> | L2      | 3.3V    | В  | I <sup>2</sup> C 端口(控制器)数据<br>需要外部上拉电阻器。此 I <sup>2</sup> C 端口通常用于与温度感测器件<br>通信。 |

| 温度 SCL <sup>(1)</sup> | К3      | 3.3V    | 0  | I2C 端口(控制器)时钟<br>需要外部上拉电阻器。此 I <sup>2</sup> C 端口通常用于与温度感测器件<br>通信。              |

| 闪存 DQ0                | C10、F12 | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ1                | C11、E11 | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ2                | B11     | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ3                | A12     | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ4                | B12     | 1.8 V   | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ5                | A10     | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ6                | A9      | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 DQ7                | D11     | 1.8V    | В  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。                                               |

| 闪存 CS                 | C12、D13 | 1.8V    | 0  | SPI 端口(控制器)<br>闪存器件、发送和接收数据的控制接口。<br>需要外部上拉电阻器(≤10kΩ)。                          |

| 闪存 DQS                | H11     | 1.8V    | I  | 闪存数据选通                                                                          |

## 表 2-3. 通信引脚说明 (续)

| 引脚   |       | I/O  |    |      |

|------|-------|------|----|------|

| 名称   | 编号    | 电源   | 类型 | 说明   |

| 闪存时钟 | B9、A7 | 1.8V | 0  | 闪存时钟 |

(1) 该引脚不由 FPGA 直接支持,必须在外部 MCU 支持下读取。例如,在 DLP2021LEQ1EVM 上,TMP411 I2C 路由至 MSP430。

#### 2.4 支持

表 2-4. 支持引脚说明

| 引脚       |         | I/O  |          |                                                  |  |

|----------|---------|------|----------|--------------------------------------------------|--|

| 名称       | 编号      | 电源   | 类型       | 说明                                               |  |

| TSTPT_0  | B1      | 3.3V | 0        | 保留用于测试输出。在最终产品设计中,这些 I/O 应保持开<br>路或未连接状态,以便正常运行。 |  |

| TSTPT_1  | B2      | 3.3V | 0        |                                                  |  |

| TSTPT_2  | C1      | 3.3V | 0        |                                                  |  |

| TSTPT_3  | C2      | 3.3V | 0        |                                                  |  |

| TSTPT_4  | D1      | 3.3V | 0        |                                                  |  |

| TSTPT_5  | D3      | 3.3V | 0        |                                                  |  |

| TSTPT_6  | E1      | 3.3V | 0        |                                                  |  |

| TSTPT_7  | E2      | 3.3V | 0        |                                                  |  |

| 振荡器输入    | G2      | 3.3V | I        | 基准时钟输入                                           |  |

| 欠压检测     | F2      | 1.8V | I (HSTL) | 欠压检测                                             |  |

| DMD 放电启用 | M5      | 3.3V | 0        | DMD 放电启用                                         |  |

| 时钟环回     | J11、J13 |      |          | 保留                                               |  |

# 2.5 FPGA 专用引脚

以下引脚是 Spartan 7 FPGA 上的硬件专用引脚。有关主要指南,请参阅 Xilinx 文档。表 2-5 中的说明是针对应用特定注意事项的建议。

表 2-5. FPGA 专用引脚说明

| 引脚                 |       | 1/0   |                                                                |  |

|--------------------|-------|-------|----------------------------------------------------------------|--|

| 名称                 | 编号    | 1/0   | 说明                                                             |  |

| PUDC               | B10   | I     | 配置期间的上拉电阻器<br>直接(或通过 1kΩ 或更小的电阻器)连接到 GND。这将在配置期间<br>启用引脚上拉电阻器。 |  |

| PROGRAMZ           | N8    | I     | 异步复位至配置逻辑(低电平有效)                                               |  |

| INITZ              | N7    | B(开漏) | 指示配置存储器的初始化(低电平有效)                                             |  |

| DONE               | M9    | В     | 指示配置成功完成(高电平有效)                                                |  |

| CFGBVS_0           | N9    | I     | 接地                                                             |  |

| DXN_0              | J7    | 不适用   | FPGA 的温度感测二极管引脚。不使用时接地。                                        |  |

| DXP_0              | J8    | 不适用   | FPGA 的温度感测二极管引脚。不使用时接地。                                        |  |

| M0_0               | L10   | I     | 配置模式选择<br>连接至 1.8V。                                            |  |

| M1_0               | L8    | I     | 配置模式选择 接地。                                                     |  |

| M2_0               | L9    | I     | 配置模式选择<br>接地。                                                  |  |

| HSTL VREF          | C4、L3 | REF   | HSTL 1.8V 输入的电压基准                                              |  |

| TDO <sup>(1)</sup> | M6    | I     | JTAG 数据输出                                                      |  |

| TDI <sup>(1)</sup> | M7    | I     | JTAG 数据输入                                                      |  |

www.ti.com.cn FPGA 引脚配置和功能

# 表 2-5. FPGA 专用引脚说明 (续)

| 引脚                 |    | I/O |           |  |

|--------------------|----|-----|-----------|--|

| 名称                 | 编号 |     | 说明        |  |

| TCK <sup>(1)</sup> | A8 | 0   | JTAG 时钟   |  |

| TMS <sup>(1)</sup> | L7 | I   | JTAG 模式选择 |  |

(1) 此引脚不适用于 DLP2021-Q1。

# 2.6 电源和接地

表 2-6. 电源和接地引脚说明

| 引脚      |                                                                                                                                                                                                                                            | I/O |                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|

| 名称      | 编号                                                                                                                                                                                                                                         |     | 说明                       |

| VCCAUX  | D6、D8、D10                                                                                                                                                                                                                                  | PWR | 辅助电路的 1.8V 电源引脚          |

| VCCBRAM | C7、C9                                                                                                                                                                                                                                      | PWR | FPGA 逻辑块 RAM 的 1.0V 电源引脚 |

| VCCINT  | E7、E9、F6、G9、<br>H6、J9、K6、K8                                                                                                                                                                                                                | PWR | 内部内核逻辑的 0.9V/1.0V 电源引脚   |

| VCCO_0  | N6、P8                                                                                                                                                                                                                                      | PWR | 组0的电源引脚                  |

| VCCO_14 | F10、H10、K10                                                                                                                                                                                                                                | PWR | 组 14 的电源引脚               |

| VCCO_34 | E5、G5、J5                                                                                                                                                                                                                                   | PWR | 组 34 的电源引脚               |

| GND     | A1、H5、H9、J2、<br>J6、J10、J12、K4、<br>K5、K7、K9、K14、<br>L1、L5、L6、L11、<br>M3、M8、M13、<br>N5、N10、P1、P5、<br>P6、P7、P9、P14、<br>A6、A11、A14、<br>B3、B8、B13、C6、<br>C8、D2、D5、D7、<br>D9、D12、E4、E6、<br>E8、E10、E14、<br>F1、F5、F9、F11、<br>G3、G6、G10、<br>G11、G13 | RTN | 接地                       |

# 2.7 未使用的引脚

所有 NC 引脚都有内部上拉电阻器,在原理图设计中应保留未连接状态。

表 2-7. 未使用的引脚

| 引                | <b>类型</b> |          |

|------------------|-----------|----------|

| 名称               | 编号        | <b>一</b> |

| IO_L2P_T0_34     | B4        | NC       |

| IO_L3N_T0_DQS_34 | B5        | NC       |

| IO_L3P_T0_DQS_34 | C5        | NC       |

| IO_L5N_T0_34     | B1        | NC       |

| IO_L5P_T0_34     | B2        | NC       |

| IO_L6P_T0_34     | D4        | NC       |

| IO_L7N_T1_34     | C1        | NC       |

| IO_L7P_T1_34     | C2        | NC       |

| IO_L8N_T1_34     | D3        | NC       |

| IO_L8P_T1_34     | E3        | NC       |

| IO_L9N_T1_DQS_34 | D1        | NC       |

| IO_L9P_T1_DQS_34 | E1        | NC       |

# 表 2-7. 未使用的引脚 (续)

| 引                  | No mai |    |

|--------------------|--------|----|

| 名称                 | 编号     |    |

| IO_L10N_T1_34      | E2     | NC |

| IO_L11N_T1_SRCC_34 | F3     | NC |

| IO_L11P_T1_SRCC_34 | F4     | NC |

| IO_L12N_T1_MRCC_34 | G1     | NC |

| IO_L13N_T2_MRCC_34 | G4     | NC |

| IO_L13P_T2_MRCC_34 | H4     | NC |

| IO_L14N_T2_SRCC_34 | H2     | NC |

| IO_L16N_T2_34      | J3     | NC |

| IO_L16P_T2_34      | J4     | NC |

| IO_L17N_T2_34      | K1     | NC |

| IO_L18N_T2_34      | K2     | NC |

| IO_L19P_T3_34      | L4     | NC |

| IO_L20P_T3_34      | M2     | NC |

| IO_L23N_T3_34      | P2     | NC |

| IO_0_34            | C3     | NC |

| IO_L16P_T2_CSI_14  | K11    | NC |

| IO_L18P_T2_D28_14  | L12    | NC |

| IO_L23P_T3_D19_14  | N11    | NC |

| IO_L23N_T3_D18_14  | N12    | NC |

| IO_L24N_T3_D16_14  | M11    | NC |

| TCK_0              | A8     | NC |

| TDI_0              | M7     | NC |

| TDO_0              | M6     | NC |

| TMS_0              | L7     | NC |

| NC1                | В7     | NC |

| NC2                | F7     | NC |

| NC3                | F8     | NC |

| NC4                | G7     | NC |

| NC5                | G8     | NC |

| NC6                | H7     | NC |

| NC7                | H8     | NC |

|                    |        |    |

# 3 规格

# 3.1 建议运行条件

表 3-1. 建议运行条件

| ·· /=//-////           |      |      |      |    |  |  |  |

|------------------------|------|------|------|----|--|--|--|

|                        | 最小值  | 标称值  | 最大值  | 单位 |  |  |  |

| VCCO_0                 | 1.71 | 1.8  | 1.89 | V  |  |  |  |

| VCCO_14                | 1.71 | 1.8  | 1.89 | V  |  |  |  |

| VCCO_34                | 3.14 | 3.3  | 3.46 | V  |  |  |  |

| VCCAUX <sup>(1)</sup>  | 1.71 | 1.80 | 1.89 | V  |  |  |  |

| VCCBRAM <sup>(1)</sup> | 0.95 | 1.00 | 1.05 | V  |  |  |  |

| VCCINT <sup>(1)</sup>  | 0.95 | 1.00 | 1.05 | V  |  |  |  |

<sup>(1)</sup> 值基于撰写本文时的可用 FPGA 文档。请参阅 FPGA 数据表,将其作为主要来源规格。

# 3.2 FPGA 功耗

表 3-2. FPGA 功耗规格

| 元件       | 最小值 | 标称值 | 最大值 | 单位 |

|----------|-----|-----|-----|----|

| 1.0V 电源轨 |     |     | 127 | mW |

| 1.8V 电源轨 |     |     | 308 | mW |

| 3.3V 电源轨 |     |     | 45  | mW |

| FPGA 总功率 |     | 363 | 480 | mW |

# 3.3 主机 SPI 接口时序

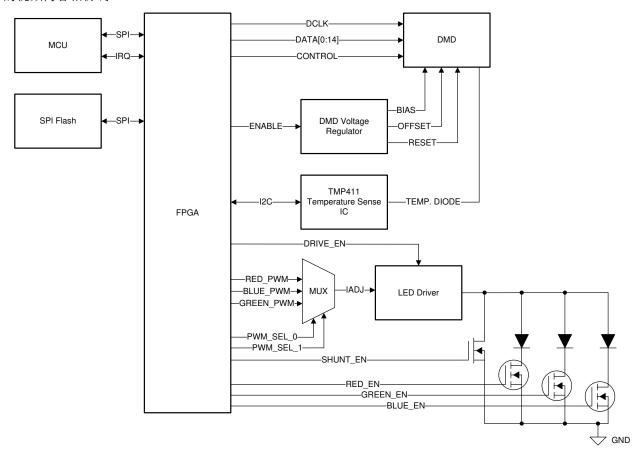

#### 表 3-3. 主机 SPI 接口时序

| 次 0 0: <u>工</u> // 0: 1 次 7 7/1 |                                                        |     |     |     |  |  |

|---------------------------------|--------------------------------------------------------|-----|-----|-----|--|--|

|                                 | 说明                                                     | 最小值 | 最大值 | 单位  |  |  |

| f <sub>clock</sub>              | 时钟频率,HOST CLK<br>(50% 基准点)                             |     | 5   | MHz |  |  |

| t <sub>su</sub>                 | 建立时间 - 在 HOST CLK 捕获边沿之前,<br>HOST MOSI 有效<br>(50% 基准点) | 0   |     | ns  |  |  |

| t <sub>h</sub>                  | 保持时间 - 在 HOST CLK 捕获边沿之前,<br>HOST MOSI 有效<br>(50% 基准点) | 20  |     | ns  |  |  |

| t <sub>out</sub>                | 时钟到数据输出 - 来自 HOST CLK 转换边沿的 HOST MISO (50% 基准点)        | 40  | 60  | ns  |  |  |

图 3-1. 主机 SPI 接口时序图

#### 3.4 电源和复位时序

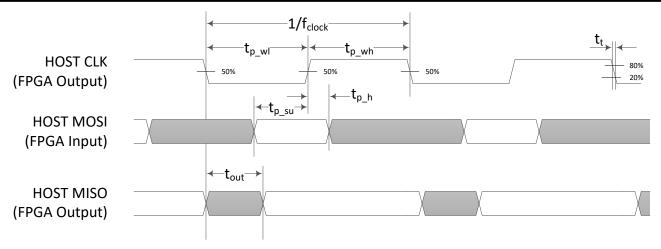

#### 3.4.1 上电时序

表 3-4 指定了 FPGA 启动期间的配置和初始化时序。HOST\_IRQ 设置为高电平后,FPGA 经配置并准备好在 SPI 接口上接收命令。但是,第一个命令将不会多执行 10ms。

| <b>次 3-4.</b> 工电明                |                                             |     |      |     |    |  |

|----------------------------------|---------------------------------------------|-----|------|-----|----|--|

|                                  |                                             | 最小值 | 标称值  | 最大值 | 单位 |  |

| t <sub>init</sub> (2)            | FPGA 配置初始化。1.8V 电源至 DONE 上升沿                |     | 230  |     | ms |  |

| t <sub>oez</sub>                 | DONE 上升沿至 DMD RESET OEZ 低电平                 |     | 8.5  |     | ms |  |

| t <sub>irq</sub> (3)             | RESET OEZ 低电平至 HOST IRQ 高电平                 |     | 1.15 |     | ms |  |

| t <sub>ramp</sub> <sup>(1)</sup> | 每个电源的斜坡时间: 1.0V、1.8V 和 3.3V (GND 至 90% 基准点) | 0.2 |      | 50  | ms |  |

表 3-4. 上电时序规格

- (1) 值基于撰写本文时的可用 FPGA 文档。作为主要来源规格,请参阅特定于器件的 FPGA 数据表。

- (2) INITZ 应上拉至 1.8V 以实现最短的启动时间。如果 INITZ 上升沿延迟,则配置将延迟。

- (3) HOST IRQ 就绪位将指示 FPGA 已为来自主机的 SPI 通信做好准备。为了实现在启动时将 HOST IRQ 设置为高电平的条件,必须在中断启用屏蔽中设置此位。在启动时,可通过默认配置来自动配置中断启用屏蔽。

图 3-2. 上电时序图

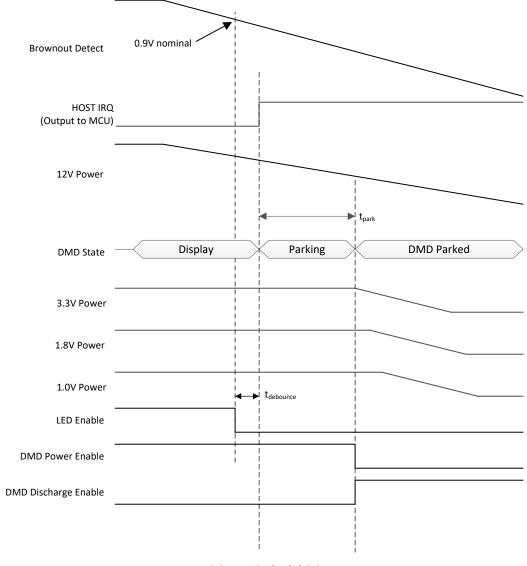

#### 3.4.2 断电时序

#### 表 3-5. 断电时序规格

|                       | The state of the s |     |     |     |    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 最小值 | 标称值 | 最大值 | 单位 |

| t <sub>park</sub>     | DMD 正确停止所需时间 <sup>(1)</sup> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |     | 500 | μs |

| t <sub>debounce</sub> | 在停止序列开始之前,输入电压保持低于欠压检测<br>阈值所需时间。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100 |     |     | μs |

- (1) DMD 电压 (2.5V、1.8V、8.5V、16V、-10V) 在 DLP3021-Q1 上停止之前必须保持有效

- (2) DMD 电压 (1.8V、8.5V、16V、-10V) 在 DLP2021-Q1 上停止之前必须保持有效

图 3-3. 断电时序图

## 3.4.3 欠压检测

DLP3021-Q1 FPGA 配置包括欠压检测功能,可在输入电压开始下降时发出警报并正确关断系统。FPGA 引脚 F2 配置为欠压检测引脚。该引脚配置为数字输入,将在高电平到低电平转换时触发欠压中断。输入电压应分压为该引脚的输入,以便该引脚的标称电压不会超过 1.8V。当输入下降到低于 0.9V 的标称电压时,将出现欠压情况。当触发欠压条件并且输入电压在 100µs 去抖周期内保持低于欠压电压阈值时,FPGA 将自动开始停止 DMD,以便实现正确的断电时序。欠压检测使 DMD 停止之后,系统必须在重新启动之前完全断电,从而确保重新启动时具有正确的上电时序。

#### 表 3-6. 欠压检测规格

|                |             | 最小值                | 标称值                | 最大值                | 单位 |

|----------------|-------------|--------------------|--------------------|--------------------|----|

| $V_{Brownout}$ | 触发欠压条件的输入电压 | 0.8 <sup>(1)</sup> | 0.9 <sup>(1)</sup> | 1.0 <sup>(1)</sup> | V  |

(1) 对 V<sub>REF</sub> = 0.9V 有效的电压。

# 3.5 DMD 接口时序

表 3-7. DMD 接口时序规格

|                     |                                                                 | 最小值  | 标称值 | 最大值 | 单位  |

|---------------------|-----------------------------------------------------------------|------|-----|-----|-----|

| f <sub>clock</sub>  | 时钟频率,DCLK 和 SAC CLK                                             |      | 80  | 82  | MHz |

| t <sub>wh</sub>     | 脉冲宽度高电平, DCLK 和 SAC CLK ( 50% 基准<br>点 )                         | 5    |     |     | ns  |

| t <sub>wl</sub>     | 脉冲宽度低电平, DCLK 和 SAC CLK ( 50% 基准<br>点 )                         | 5    |     |     | ns  |

| t <sub>t</sub>      | 转换时间,所有信号(20%至80%基准点)                                           | 0.5  |     | 2.5 | ns  |

| t <sub>su</sub>     | 输出建立时间 - 相对于 DCLK 的上升沿和下降沿 (50% 基准点)的 D(14:0)、SCTRL、LOADB 和 TRC | 1.5  |     |     | ns  |

| t <sub>h</sub>      | 输出保持时间 - 相对于 DCLK 的上升沿和下降沿 (50% 基准点)的 D(14:0)、SCTRL、LOADB 和 TRC | 1.5  |     |     | ns  |

| t <sub>clkdat</sub> | 时钟到数据输出延迟                                                       | -1.5 |     | 1.5 | ns  |

# 3.6 闪存存储器接口时序

#### 表 3-8. 闪存存储器接口时序

|            |                         | 最小值 | 标称值 | 最大值 | 单位  |

|------------|-------------------------|-----|-----|-----|-----|

| DLP2021-Q1 | f <sub>clock</sub> 时钟频率 |     |     | 140 | MHz |

|            | 跟踪延迟                    |     |     | 100 | ps  |

| DLP3021-Q1 | f <sub>clock</sub> 时钟频率 |     |     | 130 | MHz |

|            | 跟踪延迟                    |     |     | 100 | ps  |

#### 3.7 基准时钟时序

此设计利用 FPGA 内的 MMCM 模块。

表 3-9. 基准时钟时序规格

|                     |                    | 最小值           | 标称值 | 最大值  | 单位  |

|---------------------|--------------------|---------------|-----|------|-----|

| f <sub>clock</sub>  | 时钟频率,振荡器输入         | 39.5          | 40  | 40.5 | MHz |

| t <sub>wh</sub>     | 脉冲持续时间,振荡器输入高电平(1) | f_clock 的 25% |     |      |     |

| t <sub>wl</sub>     | 脉冲持续时间,振荡器输入低电平(1) | f_clock 的 25% |     |      |     |

| t <sub>clkjit</sub> | 时钟周期抖动,振荡器输入(1)    |               |     | 50   | ps  |

(1) 值基于撰写本文时的可用 FPGA 文档。请参阅 FPGA 数据表,将其作为 MMCM 规格的主要来源。

### 3.8 I2C 接口时序

#### 表 3-10. I2C 接口时序(1)(2)

|                    | 说明   | 最小值 | 标称值 | 最大值 | 单位  |

|--------------------|------|-----|-----|-----|-----|

| f <sub>clock</sub> | 时钟频率 |     | 51  |     | kHz |

- (1) 符合 I2C 总线规范指定的所有 I2C 时序。

- (2) I2C 接口时序仅适用于 DLP3021-Q1, 因为 DLP2021-Q1 固件不支持 TMP411 的 I2C 连接。

#### 4 特性描述

## 4.1 视频控制器

FPGA 能够从外部闪存存储器读取视频数据并将其显示在 DMD 上。视频数据在存储到闪存存储器中之前,必须使用 DLP Composer 工具进行转换和压缩。生成闪存二进制文件时,DLP Composer 将指定存储器内视频内容的地址位置。

两组寄存器用于两种视频配置。如果需要,这可实现两个视频之间的无缝切换。也可以无缝显示两个以上的视频,但需要主机控制器在播放期间进行干预。可以在播放一种配置的同时修改另一种配置。当视频配置开始播放时,配置会锁存。中断信号可用于在一种配置完成时通知主机控制器,以便在下一种配置播放时将这一种配置的值修改为所需的另一个视频。

在运行期间,以下寄存器可用于配置 FPGA,以显示闪存存储器中的视频内容:

- 视频帧速率

- 视频起始地址 1

- 视频配置 1

- 视频起始地址 2

- 视频配置 2

- 视频控制器

- 视频状态

显示视频的步骤如下:

- 写入视频帧速率 设置帧速率以匹配 DMD 序列。

- 写入起始地址 X 设置所需视频在闪存中的起始地址。

- 写入配置 X 设置视频中的帧数和循环视频的次数。

- (可选)写入起始地址Y 设置第二个所需视频在闪存中的起始地址。

- (可选)写入配置Y 设置下一个视频中的帧数和循环视频的次数。

- **写入视频控制** 选择播放选项,然后播放视频。

#### 4.1.1 视频选项

视频控制寄存器用于设置使用哪种视频配置以及如何在两种视频配置之间切换。

表 4-1. 视频控制寄存器配置

| 循环配置(位4) | 切换配置(位 5) | 配置指针(位3) |                  |

|----------|-----------|----------|------------------|

|          | 视频控制寄存器   |          | 结果               |

| 0        | 0         | 0        | 播放配置 1 一次        |

| 0        | 0         | 1        | 播放配置 2 一次        |

| 0        | 1         | 0        | 播放(配置1,然后配置2)一次  |

| 0        | 1         | 1        | 播放(配置2,然后配置1)一次  |

| 1        | 0         | 0        | 持续重复配置 1         |

| 1        | 0         | 1        | 持续重复配置 2         |

| 1        | 1         | 0        | 持续重复(先配置1,然后配置2) |

| 1        | 1         | 1        | 持续重复(先配置2,然后配置1) |

如果"循环配置"=0,则结束操作由"自动停止"(位2)确定。自动停止位允许完全关闭视频(1)或冻结视频中的最后一个图像(0)。如果"循环配置"=1,则没有结束操作,因为视频会一直循环,直到通过命令停止。

#### 4.1.2 示例 1: 显示静态图像

下面的步骤可用于在 DMD 上显示单个图像。

- 1. 写入视频帧速率寄存器。

- a. 时钟计数应与所使用的 DMD 序列的长度相匹配。

- 2. 写入视频起始地址 1 寄存器。

- a. 起始地址应与图像在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 3. 写入视频配置 1 寄存器。

- a. 帧计数= 1

- b. 循环计数 = 1

- 4. 写入视频控制寄存器。

- a. 循环配置 = 1

- b. 切换配置 = 0

- c. 配置指针=0

- d. 播放 = 1

- e. 停止 = 0

此配置将始终显示图像,或直到设置了"停止"位。由于设置了"循环配置"位,将在每次完成时连续执行此配置。

#### 4.1.3 示例 2: 重复显示 1 个视频

下面的步骤可用于在 DMD 上重复显示单个视频。

- 1. 写入视频帧速率寄存器。

- a. 时钟计数应与所使用的 DMD 序列的长度相匹配。

- 2. 写入视频起始地址 1 寄存器。

- a. 起始地址应与视频在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 3. 写入视频配置 1 寄存器。

- a. 帧计数 = 视频中的帧数

- b. 循环计数 = 1

- 4. 写入视频控制寄存器。

- a. 循环配置 = 1

- b. 切换配置 = 0

- c. 配置指针=0

- d. 播放 = 1

- e. 停止 = 0

此配置将播放视频,然后继续重复该视频,直到设置"停止"位。由于设置了"循环配置"位,将在每次完成时继续执行此配置。

#### 4.1.4 示例 3:显示两个视频,然后停止

下面的步骤可用于连续显示两个视频,然后停止显示。

- 1. 写入视频帧速率寄存器。

- a. 时钟计数应与所使用的 DMD 序列的长度相匹配。

- 2. 写入视频起始地址 1 寄存器。

- a. 起始地址应与视频在闪存存储器中的位置相匹配。

- 3. 写入视频配置 1 寄存器。

- a. 帧计数 = 视频中的帧数

www.ti.com.cn 特性描述

- b. 循环计数 = 1

- 4. 写入视频起始地址 2 寄存器。

- a. 起始地址应与视频在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 5. 写入视频配置 2 寄存器。

- a. 帧计数 = 视频中的帧数

- b. 循环计数 = 1

- 6. 写入视频控制寄存器。

- a. 循环配置 = 0

- b. 切换配置 = 1

- c. 配置指针 = 0

- d. 播放 = 1

- e. 停止 = 0

- f. 自动停止 = 1

由于"配置指针"=0,此配置将从配置1开始。将播放此视频的一个循环,然后切换到配置2。在第二个视频播放一个循环后,显示将自动停止。这意味着灯会关闭,不再显示图像。

#### 4.1.5 示例 4:显示一次 VIdeo, 然后一直显示图像

下面的步骤可用于显示视频,然后显示静态图像:

- 1. 写入视频帧速率寄存器。

- a. 时钟计数应与所使用的 DMD 序列的长度相匹配。

- 2. 写入视频起始地址 1 寄存器。

- a. 起始地址应与视频在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 3. 写入视频配置 1 寄存器。

- a. 帧计数 = 视频中的帧数

- b. 循环计数 = 1

- 4. 4. 写入视频起始地址 2 寄存器。

- a. 起始地址应与视频在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 5. 写入视频配置 2 寄存器。

- a. 帧计数 = 1

- b. 循环计数 = 1

- 6. 写入视频控制寄存器。

- a. 循环配置 = 0

- b. 切换配置 = 1

- c. 配置指针 = 0

- d. 播放 = 1

- e. 停止 = 0

- f. 自动停止 = 0

由于"配置指针"=0,该配置将从配置1开始。将播放所需视频的一个循环,然后切换到配置2。在这种情况下,将配置2设置为一个帧(图像)。由于自动停止设置为0,显示将重复配置2的最后一帧,而不是停止。配置2设置为所需图像的一帧,因此会重复显示该图像,直到收到停止命令。

#### 4.1.6 示例 5: 无缝显示 3 个以上视频图像

由于只有两组配置寄存器,因此在不暂停的情况下显示两个以上视频需要主机干预。HOST IRQ 信号包括中断事件,其可帮助无缝切换到其他视频内容。

- 1. 写入 FPGA 中断启用寄存器"视频配置完成"位。

- 2. 读取 FPGA 中断设置寄存器并写入 FPGA 中断清除寄存器。

- a. 向 FPGA 中断清除寄存器写入 1,以便清除可将 HOST IRQ 信号保持为高电平的任何活动中断。

- 3. 写入视频帧速率寄存器。

- a. 时钟计数应与所使用的 DMD 序列的长度相匹配。

- 4. 写入视频起始地址 1 寄存器。

- a. 起始地址应与第一个视频在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 5. 写入视频配置 1 寄存器。

- a. 帧计数 = 视频中的帧数

- b. 循环计数 = 1

- 6. 写入视频起始地址 2 寄存器。

- a. 起始地址应与第二个视频在闪存存储器中的位置相匹配。这可以在 DLP Composer 工具的构建日志输出中查找。

- 7. 写入视频配置 2 寄存器。

- a. 帧计数 = 视频中的帧数

- b. 循环计数 = 1

- 8. 写入视频控制寄存器。

- a. 循环配置 = 0

- b. 切换配置 = 1

- c. 配置指针=0

- d. 播放 = 1

- e. 停止 = 0

- f. 自动停止 = 0

- 9. 等待 HOST IRQ 信号中断主机 MCU, 然后读取 FPGA 中断设置寄存器,以确认"视频配置完成"是中断的来源。

- 10. 写入视频起始地址 1 寄存器。

- a. 起始地址应与**第三个**视频在闪存存储器中的位置相匹配。

- 11. 写入视频配置 1 寄存器。

- a. 帧计数 = 视频中的帧数

- b. 循环计数 = 1

- 12. 12. 等待 HOST IRQ 信号中断主机 MCU, 然后读取 FPGA 中断设置寄存器,以确认"视频配置完成"是中断的来源。

- 13. 写入视频控制寄存器。

- a. 循环配置 = 0

- b. 切换配置 = 1

- c. 配置指针=0

- d. 播放 = 1

- e. 停止 = 0

- f. 自动停止 = 0

www.ti.com.cn 特性描述

在视频配置 1 和 2 中设置前两个视频。然后,主机 MCU 应一直等待,直到"视频配置完成"中断触发指示 FPGA 已交换到显示配置 2。发生这种情况后,主机 MCU 可以修改配置 1,而不会影响所显示的视频内容。然后,它应在视频 2 完成之前将第三个视频的设置存储在配置 1 中。视频 2 完成后,FPGA 将循环回到配置 1,现在应将该配置设置为显示视频 3。可以针对任何所需数量的视频或图像重复此过程。在 HOST IRQ 中断切换到最终视频配置后,可将视频控制寄存器设置为在完成之后自动停止。写入该寄存器时,请勿设置播放位。如果此时设置了播放位,视频配置将在下一个视频帧上的指定配置指针处重新启动,而不是等待当前配置完成。

#### 4.2 温度测量

FPGA 可以选择从通过 I2C 连接的外部 TMP411 温度传感器读取温度测量。这允许使用 DMD 内置的二极管来读取 TMP411 本地温度和 DMD 远程温度。

FPGA 以大约 8Hz 的频率从 TMP411 读取两个温度,并将最新值存储在主机控制器可以读回的寄存器中。

FPGA 中的温度值以 TMP411 12 位格式返回。八个 MSB 为整数部分。四个 LSB 为小数部分,应将其除以 16 并添加到整数部分。

#### 各注

DLP2021-Q1 固件不支持 TMP411 的 I2C 连接。这需要针对 TMP411 数据的外部 MCU 处理程序。 DLP2021-Q1 的 FPGA 固件绝不会看到温度数据,只有主要主机能看到。

#### 4.3 PWM 输出

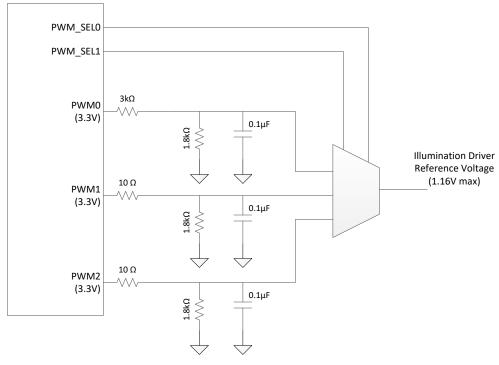

FPGA 有三路 PWM 输出,通常对应红色、绿色和蓝色照明颜色。可根据需要调整 PWM 占空比,将基准电压设置为外部照明驱动器电路,从而平衡颜色并调整输出亮度。

图 4-1 展示了典型 PWM 电路。在本例中,每个 PWM 都经过低通滤波,并且输出连接到 4:1 模拟多路复用器。如所展示的,每个滤波器的电容器并联有一个可选电阻器,以在需要时作为分压器,从而匹配所需的照明驱动器基准电压范围。在最大占空比时,PWM 输出频率为 40kHz。

PWM\_SELx 信号可用于选择在执行 DMD 序列时将哪个输出 PWM 多路复用到照明驱动器。表 4-2 说明了 PWM SELx 输出和多路复用器输出之间的预期关系。

PWM\_SEL0 PWM\_SEL1 多路复用器输出 典型序列颜色 0 0 无 0 1 PWM1 红色 PWM2 1 0 绿色 PWM3 1 1 蓝色

表 4-2. PWM 选择配置

图 4-1. 典型 PWM 电路

# 4.4 主机 IRQ 中断信号

HOST IRQ 是 FPGA 的电平中断输出。多个内部中断源可触发外部中断信号。如果信号为低电平,则清除所有已启用的中断源。如果信号为高电平,则其中一个源是启用的,并且已经触发。三个寄存器用于处理中断源:

- FPGA 中断启用

- FPGA 中断设置

- FPGA 中断清除

FPGA 中断启用用于屏蔽哪个中断源将触发外部 HOST IRQ 信号。例如,如"视频循环完成"启用位设置为 1,则此源将在触发时将 HOST IRQ 设置为高电平。如果设置为 0,则 HOST IRQ 将不会由于此源而设置为高电平。

FPGA 中断设置用于读回当前设置的中断。一旦设置了内部中断源,其将保持设置状态,直到通过写入 FPGA 中断清除寄存器将其清除。

FPGA 中断清除用于在处理后清除中断源。通常情况下,FPGA 中断设置寄存器可以直接写入 FPGA 中断清除寄存器,以便清除所有当前活动中断。然后,主机 MCU 可以根据所设置的中断来确定要采取的操作。

如果触发多个已启用的中断源,则 HOST IRQ 将保持高电平。

#### 4.5 视频和图像压缩

构建闪存二进制文件后,DLP Composer 工具会自动压缩闪存中存储的视频和图像。这些视频帧和图像将进行格式化,以显示在 DLP3021-Q1 上,并使用简化的行程编码 (RLE) 进行压缩,以实现无损压缩。所有黑色或所有白色图像的最大压缩比为 16:1,但典型的图像压缩系数约为 2:1。压缩比取决于内容,因此可存储的图像总数或视频长度将取决于视频内容和所选闪存芯片的大小。

#### 表 4-3 列出了典型的存储能力。

#### 表 4-3. DLP3021-Q1 的典型存储能力

| 闪存大小  | 大约图像数/帧数 <sup>(1)</sup> | 视频长度 (s)25Hz 视频 |

|-------|-------------------------|-----------------|

| 512Mb | 150                     | 6               |

| 1GB   | 300                     | 12              |

| 2Gb   | 600                     | 24              |

(1) 存储在闪存中的帧数将取决于视频和图像数据的压缩系数。实际帧数将取决于各个内容。

#### 表 4-4. DLP2021-Q1 的典型存储能力

| 闪存大小  | 大约图像数/帧数(1) | 视频长度 (s) 25Hz 视频 |

|-------|-------------|------------------|

| 512Mb | 300         | 12               |

| 1GB   | 600         | 24               |

| 2Gb   | 1200        | 48               |

(1) 存储在闪存中的帧数将取决于视频和图像数据的压缩系数。实际帧数将取决于各个内容。

#### 5 布局

对于新电路板设计,请确保 FPGA 与闪存存储器接口和 DMD 接口的布线长度正确匹配。

- DMD 时钟和数据

- 这包括 FPGA 和 DMD 之间与 DCLK 同步的信号,包括 D0-D14、LOADB、SCTRL、RESET\_STROBE 和 TRC。这些信号的布线长度匹配要求为 ±50mil。

- DAD\_BUS 和 SAC\_BUS 是与 SAC\_CLK 同步的。这些信号应彼此在 20mm 以内匹配,但对前一组信号没有匹配要求。

- DMD\_TMS、DMD\_TDO、DMD\_TDI 与 DMD\_TCK 同步,且应彼此在 20mm 以内匹配,但对前一组信号 没有匹配要求。

- 闪存时钟和数据

- 这包括 FPGA 和闪存存储器之间的八个数据信号、时钟、芯片选择和数据选通。这些信号的布线长度匹配要求是 ±15mm。

有关 FPGA 特定布局指南,请参阅 Xilinx 7 系列 FPGA PCB 设计指南。

#### 6 主机命令协议

#### 6.1 SPI 规格

表 6-1. SPI 规格

| 参数          | 值                           |  |  |  |

|-------------|-----------------------------|--|--|--|

| 时钟频率        | 5 MHz                       |  |  |  |

| 模式(时钟相位和极性) | 0(在上升沿捕捉数据,在下降沿转换。时钟空闲低电平。) |  |  |  |

| 位顺序         | 一个字节内的最高有效位优先               |  |  |  |

| 字节顺序        | 最低有效字节优先                    |  |  |  |

| 芯片选择极性      | 低电平有效                       |  |  |  |

# 6.2 SPI 写入命令

# MOSI(主输出,从输入):

#### 表 6-2. SPI MOSI 写入命令信息

| DATA | 说明                                       |

|------|------------------------------------------|

| CMD  | 命令字节。0表示写入                               |

| 地址   | 2 字节寄存器地址                                |

| 数据   | 4 字节寄存器数据                                |

| 校验码  | 所有传输的字节(包括命令、地址、数据)的总和。如果总和超过 255,则丢弃溢出。 |

# MISO(主输入,从输出):

#### 表 6-3. SPI MISO 写入命令信息

| DATA      | 说明           |  |  |  |

|-----------|--------------|--|--|--|

| CMD (ACK) | 回显从主器件接收到的命令 |  |  |  |

| 地址 (ACK)  | 回显接收到的地址     |  |  |  |

| 数据        | 回显接收到的数据     |  |  |  |

| MOSI | CMD = 0 | Address (LSB) | Address (MSB) | ddress (MSB) Data (LSB) |            | Data | Data (MSB) | Checksum   |

|------|---------|---------------|---------------|-------------------------|------------|------|------------|------------|

|      |         |               |               |                         |            |      |            |            |

| MISO | Dummy   | CMD = 0       | Address (LSB) | Address (MSB)           | Data (LSB) | Data | Data       | Data (MSB) |

#### 图 6-1. SPI 写入命令格式

# 6.3 SPI 读取命令

MOSI(主输出,从输入):

#### 表 6-4. SPI MOSI 读取命令信息

| At a second state of March 4 IM-9. |             |  |  |  |  |  |

|------------------------------------|-------------|--|--|--|--|--|

| DATA                               | 说明          |  |  |  |  |  |

| CMD                                | 命令字节。1 表示读取 |  |  |  |  |  |

| 地址                                 | 2 字节寄存器地址   |  |  |  |  |  |

# MISO(主输入,从输出):

#### 表 6-5. SPI MISO 读取命令信息

| DATA      | 说明                     |  |  |  |

|-----------|------------------------|--|--|--|

| CMD (ACK) | 回显从主器件接收到的命令           |  |  |  |

| 地址 (ACK)  | 回显接收到的地址               |  |  |  |

| 数据        | 所请求寄存器中的数据             |  |  |  |

| 校验码       | 命令、地址和数据字节的总和。不包括虚拟字节。 |  |  |  |

| MOSI | CMD = 1 | Address (LSB) | Address (MSB) | Dummy         | Dummy      | Dummy | Dummy | Dummy      | Dummy    |

|------|---------|---------------|---------------|---------------|------------|-------|-------|------------|----------|

|      |         |               |               |               |            |       |       |            |          |

| MISO | Dummy   | CMD = 1       | Address (LSB) | Address (MSB) | Data (LSB) | Data  | Data  | Data (MSB) | Checksum |

图 6-2. SPI 读取命令格式

# 7 FPGA 寄存器定义

本节定义了可通过 SPI 访问的 FPGA 寄存器。

表 7-1 列出了器件寄存器的存储器映射寄存器。表 7-1 中未列出的所有寄存器偏移地址都应视为保留的位置,并且不应修改寄存器内容。

表 7-1. FPGA SPI 寄存器

| 地址    | 首字母缩写词                         | 寄存器名称                | 部分                                              |

|-------|--------------------------------|----------------------|-------------------------------------------------|

| 0x0   | FPGA_INTERRUPT_CLEAR           | FPA 中断清除             | 转到                                              |

| 0x4   | FPGA_INTERRUPT_SET             | FPGA 中断设置            | 转到                                              |

| 0x8   | FPGA_INTERRUPT_ENABLE          | FPGA 中断启用            | 转到                                              |

| 0xC   | FPGA_MAIN_STATUS               | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x10  | FPGA_VERSION                   | FPGA 版本              | 转到                                              |

| 0x14  | FPGA_CONTROL                   | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x20  | FMT_FLIP                       | 格式翻转                 | 转到                                              |

| 0x24  | FMT_CONTROL                    | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x28  | FMT_CMB_STATUS。                | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x2C  | FMT_FRB_STATUS                 | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x30  | RSC_SW_DMD_UNPARK              | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x34  | RSC_PARK_WAVEFORM_CTRL         | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x38  | RSC_UNUSED                     | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x3C  | RSC_MISC_CONTROL               | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x40  | RSC_SEQ_CONTROL                | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x44  | RSC_SEQBUF_SELECT              | 序列缓冲器选择              | —————————————————————————————————————           |

| 0x50  | PWM_CONTROL                    | PWM 控制               | 转到                                              |

| 0x60  | VCM_FRAME_RATE                 | 帧速率                  | <del>************************************</del> |

| 0x64  | VCM_START_ADDR1                | 视频 1 起始地址            | 转到                                              |

| 0x68  | VCM_CONFIG1                    | 视频配置 1               | <b>转</b> 到                                      |

| 0x6C  | VCM_START_ADDR2                | 视频 2 起始地址            | 转到                                              |

| 0x70  | VCM_CONFIG2                    | 视频配置 2               | <b>专</b>                                        |

| 0x74  | VCM_CONTROL                    | 视频控制                 | <del>************************************</del> |

| 0x78  | VCM_STATUS                     | 视频状态                 | 转到                                              |

| 0x7C  | VCM_SEQABORT                   | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x80  | VCM_TMSEL                      | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x90  | TMP_CTRL <sup>(1)</sup>        | 温度控制                 | 转到                                              |

| 0x94  | TMP_STATUS <sup>(1)</sup>      | 温度状态                 | 转到                                              |

| 0x98  | TMP_REMOTE_TEMP <sup>(1)</sup> | 远程温度测量               | 转到                                              |

| 0x9C  | TMP_LOCAL_TEMP <sup>(1)</sup>  | 本地温度测量               | 转到                                              |

| 0xDC  | DESTOP_TIMEOUT_DEBUG_INFO_REG  | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0xE0  | DESTOP_MBOX0_SAPTR_REG         | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0xE4  | DESTOP_MBOX0_CTRL_REG          | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0xF0  | DESTOP_MBOX0_DATA_REG          | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x100 | DESTOP_MBOX1_SAPTR_REG         | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x104 | DESTOP_MBOX1_CTRL_REG          | TI 内部使用。未定义的读取/写入行为。 |                                                 |

| 0x110 | DESTOP_MBOX1_DATA_REG          | TI 内部使用。未定义的读取/写入行为。 |                                                 |

|       | 4                              |                      |                                                 |

<sup>(1)</sup> 此寄存器不适用于 DLP2021-Q1。

复杂的位访问类型经过编码可适应小型表单元。节7展示了适用于此部分中访问类型的代码。

#### 表 7-2. 器件访问类型代码

| 访问类型   | 代码 | 说明        |  |  |  |

|--------|----|-----------|--|--|--|

| 读取类型   |    |           |  |  |  |

| R      | R  | 读取        |  |  |  |

| 写入类型   |    |           |  |  |  |

| W      | W  | 写入        |  |  |  |

| 复位或默认值 |    |           |  |  |  |

| -n     |    | 复位后的值或默认值 |  |  |  |

# 7.1 FPGA\_INTERRUPT\_CLEAR 寄存器(地址 = 0x0)[复位 = 0x0]

节 7 展示了 FPGA\_INTERRUPT\_CLEAR。

返回汇总表。

向任何位写1可以清除中断事件。

表 7-3. FPGA INTERRUPT CLEAR 寄存器字段说明

|      | • •                 | _   | _   | * ** *** * ** ** * * * * * * * * * * * *                        |

|------|---------------------|-----|-----|-----------------------------------------------------------------|

| 位    | 字段                  | 类型  | 复位  | 说明                                                              |

| 31-5 | RESERVED            | R   | 0x0 | 保留                                                              |

| 4    | VID_CONFIG_COMP_IRQ | R/W | 0x0 | 视频配置已完成,包括所有请求的循环。这在视频的所有循环都完成后触发一次。如果请求使用这两种视频配置,则会在每次配置完成后触发。 |

| 3    | VID_LOOP_COMP_IRQ   | R/W | 0x0 | 视频循环已完成。如果请求了视频的多个循环,则在每次完成<br>循环后都会触发此中断。                      |

| 2    | BROWNOUT_IRQ        | R/W | 0x0 | 检测到欠压                                                           |

| 1    | INIT_DONE_IRQ       | R/W | 0x0 | 初始化完成                                                           |

| 0    | RESERVED            | R   | 0x0 | 保留                                                              |

|      |                     |     |     |                                                                 |

# 7.2 FPGA\_INTERRUPT\_SET 寄存器 (地址 = 0x4) [复位 = 0x0]

表 7-4 展示了 FPGA\_INTERRUPT\_SET。

返回汇总表。

读取中断事件的状态。

表 7-4. FPGA\_INTERRUPT\_SET 寄存器字段说明

| 位    | 字段                  | 类型  | 复位  | 说明                                                              |  |  |  |

|------|---------------------|-----|-----|-----------------------------------------------------------------|--|--|--|

| 31-5 | RESERVED            | R   | 0x0 | 保留                                                              |  |  |  |

| 4    | VID_CONFIG_COMP_IRQ | R/W | 0x0 | 视频配置已完成,包括所有请求的循环。这在视频的所有循环都完成后触发一次。如果请求使用这两种视频配置,则会在每次配置完成后触发。 |  |  |  |

| 3    | VID_LOOP_COMP_IRQ   | R/W | 0x0 | 视频循环已完成。如果请求了视频的多个循环,则在每次完成<br>循环后都会触发此中断。                      |  |  |  |

| 2    | BROWNOUT_IRQ        | R/W | 0x0 | 检测到欠压                                                           |  |  |  |

| 1    | INIT_DONE_IRQ       | R/W | 0x0 | 初始化完成                                                           |  |  |  |

| 0    | RESERVED            | R   | 0x0 | 保留                                                              |  |  |  |

#### 7.3 FPGA\_INTERRUPT\_ENABLE 寄存器 (地址 = 0x8) [复位 = 0x0]

表 7-5 展示了 FPGA\_INTERRUPT\_ENABLE。

返回汇总表。

中断事件屏蔽。向任何位写入1以使能该中断事件,从而将HOSTIRQ设置为高电平。

#### 表 7-5. FPGA INTERRUPT ENABLE 寄存器字段说明

| W. C. |                     |     |     |                                                                         |  |

|-------------------------------------------|---------------------|-----|-----|-------------------------------------------------------------------------|--|

| 位                                         | 字段                  | 类型  | 复位  | 说明                                                                      |  |

| 31-5                                      | RESERVED            | R   | 0x0 | 保留                                                                      |  |

| 4                                         | VID_CONFIG_COMP_IRQ | R/W | 0x0 | 视频配置已完成,包括所有请求的循环。这在视频的所有循环<br>都完成后触发一次。如果请求使用这两种视频配置,则会在每<br>次配置完成后触发。 |  |

| 3                                         | VID_LOOP_COMP_IRQ   | R/W | 0x0 | 视频循环已完成。如果请求了视频的多个循环,则在每次完成<br>循环后都会触发此中断。                              |  |

| 2                                         | BROWNOUT_IRQ        | R/W | 0x0 | 检测到欠压                                                                   |  |

| 1                                         | INIT_DONE_IRQ       | R/W | 0x0 | 初始化完成                                                                   |  |

| 0                                         | RESERVED            | R   | 0x0 | 保留                                                                      |  |

# 7.4 FPGA\_VERSION 寄存器 (地址 = 0x10) [复位 = 0x10000000]

FPGA VERSION 寄存器字段说明 展示了 FPGA VERSION。

返回汇总表。

FPGA 位流版本

# 表 7-6. FPGA\_VERSION 寄存器字段说明

| 位     | 字段                 | 类型 | 复位  | 说明              |

|-------|--------------------|----|-----|-----------------|

| 31-28 | FPGA_BUILD_LEVEL   | R  | 0x1 | FPGA 位流构建级别     |

|       |                    |    |     | 0x0 = 调试版本,不可重现 |

|       |                    |    |     | 0x1+=版本控制版本,可复制 |

| 27-20 | FPGA_VERSION_MINOR | R  | 0x0 | FPGA 位流次要修订     |

| 19-12 | FPGA_VERSION_MAJOR | R  | 0x0 | FPGA 位流主要修订     |

| 11-0  | FPGA_BUILD_NUMBER  | R  | 0x0 | FPGA 位流内部版本号    |

#### 7.5 FMT\_FLIP 寄存器 (地址 = 0x20) [复位 = 0x0]

FMT\_FLIP 寄存器字段说明 展示了 FMT\_FLIP。

返回汇总表。

DMD 翻转控制寄存器

#### 表 7-7. FMT\_FLIP 寄存器字段说明

| 位    | 字段               | 类型  | 复位  | 说明                                               |

|------|------------------|-----|-----|--------------------------------------------------|

| 31-5 | RESERVED         | R   | 0x0 | 保留                                               |

| 4    | FMT_CTL_DMDLFLIP | R/W |     | DMD 长边翻转<br>0x0 = 无长边翻转<br>0x1 = 启用沿 DMD 长边的图像翻转 |

| 3-1  | RESERVED         | R   | 0x0 | 保留                                               |

| 0    | FMT_CTL_DMDSFLIP | R/W | 0x0 | DMD 短边翻转<br>0x0 = 无短边翻转<br>0x1 = 启用沿 DMD 短边的图像翻转 |

#### 7.6 RSC SEQBUF SELECT 寄存器 (地址 = 0x44) [复位 = 0x0]

RSC\_SEQBUF\_SELECT 寄存器字段说明 展示了 RSC\_SEQBUF\_SELECT。

返回汇总表。

序列缓冲选择

## 表 7-8. RSC\_SEQBUF\_SELECT 寄存器字段说明

| 位    | 字段                | 类型  | 复位  | 说明                                                  |

|------|-------------------|-----|-----|-----------------------------------------------------|

| 31-1 | RESERVED          | R   | 0x0 | 保留                                                  |

| 0    | RSC_SEQBUF_SELECT | R/W |     | 序列缓冲器选择<br>0x0 = 选择序列发生器缓冲器 0<br>0x1 = 选择序列发生器缓冲器 1 |

#### 7.7 PWM\_CONTROL 寄存器 (地址 = 0x50) [复位 = 0x46419064]

PWM CONTROL 寄存器字段说明 展示了 PWM CONTROL。

返回汇总表。

PWM 控制寄存器

#### 表 7-9. PWM\_CONTROL 寄存器字段说明

| 位     | 字段           | 类型  | 复位   | 说明         |

|-------|--------------|-----|------|------------|

| 31    | RESERVED     | R   | 0x0  | 保留         |

| 30    | PWM_EN       | R/W | 0x1  | PWM 使能     |

| 29-20 | PWM_BPWM_DC  | R/W | 0x64 | 蓝色 PWM 占空比 |

| 19-10 | PWM_GPWM_DC  | R/W | 0x64 | 绿色 PWM 占空比 |

| 9-0   | PWM_RRPWM_DC | R/W | 0x64 | 红色 PWM 占空比 |

#### 7.8 VCM\_FRAME\_RATE 寄存器 (地址 = 0x60) [复位 = 0x00186A00]

VCM\_FRAME\_RATE 寄存器字段说明 展示了 VCM\_FRAME\_RATE。

返回汇总表。

帧速率选择

#### 表 7-10. VCM\_FRAME\_RATE 寄存器字段说明

| 位     | 字段             | 类型  | 复位  | 说明                                                                  |

|-------|----------------|-----|-----|---------------------------------------------------------------------|

| 31-24 | RESERVED       | R   | 0x0 | 保留                                                                  |

| 23-0  | VCM_FRAME_RATE | R/W | 0   | 40MHz 时钟计数中的视频帧时间。<br>值应与序列时间相匹配<br>25Hz = 1600000<br>60Hz = 666666 |

#### 7.9 VCM\_START\_ADDR1 寄存器 (地址 = 0x64) [复位 = 0x0]

表 7-11 展示了 VCM\_START\_ADDR1。

返回汇总表。

视频 1 起始地址

www.ti.com.cn FPGA 寄存器定义

#### 表 7-11. VCM START ADDR1 寄存器字段说明

| 位    | 字段          | 类型  | 复位  | 说明            |

|------|-------------|-----|-----|---------------|

| 31-0 | START_ADDR1 | R/W | 0x0 | 闪存中的视频 1 起始地址 |

#### 7.10 VCM\_CONFIG1 寄存器 (地址 = 0x68) [复位 = 0x1001]

表 7-12 展示了 VCM\_CONFIG1。

返回汇总表。

视频配置 1

#### 表 7-12. VCM CONFIG1 寄存器字段说明

|       | 次 i i i voiii_ootti ioi n ii ii i i i i i i i i i i i i i |     |     |                                                    |  |  |

|-------|-----------------------------------------------------------|-----|-----|----------------------------------------------------|--|--|

| 位     | 字段                                                        | 类型  | 复位  | 说明                                                 |  |  |

| 31-24 | RESERVED                                                  | R   | 0x0 | 保留                                                 |  |  |

| 23-12 | LOOP_CNT1                                                 | R/W | 0x1 | 循环视频 1 的次数<br>0x0 = 无效<br>0x1 = 1 循环<br>0x2 = 2 循环 |  |  |

| 11-0  | FRAME_CNT1                                                | R/W | 0x1 | 视频 1 中的帧数<br>0x0 = 无效<br>0x1 = 1 帧<br>0x2 = 2 帧    |  |  |

# 7.11 VCM\_START\_ADDR2 寄存器 (地址 = 0x6C) [复位 = 0x0]

表 7-13 展示了 VCM\_START\_ADDR2。

返回汇总表。

视频 2 起始地址

#### 表 7-13. VCM\_START\_ADDR2 寄存器字段说明

| 位    | 字段          | 类型  | 复位  | 说明            |

|------|-------------|-----|-----|---------------|

| 31-0 | START_ADDR2 | R/W | 0x0 | 闪存中的视频 2 起始地址 |

# 7.12 VCM\_CONFIG2 寄存器 (地址 = 0x70) [复位 = 0x1001]

表 7-14 展示了 VCM\_CONFIG2。

返回汇总表。

视频配置 2

#### 表 7-14. VCM\_CONFIG2 寄存器字段说明

| 位     | 字段        | 类型  | 复位  | 说明         |

|-------|-----------|-----|-----|------------|

| 31-24 | RESERVED  | R   | 0x0 | 保留         |

| 23-12 | LOOP_CNT2 | R/W | 0x1 | 循环视频 2 的次数 |

|       |           |     |     | 0x0 = 无效   |

|       |           |     |     | 0x1 = 1 循环 |

|       |           |     |     | 0x2 = 2 循环 |

# 表 7-14. VCM\_CONFIG2 寄存器字段说明 (续)

| 位    | 字段         | 类型  | 复位 | 说明        |

|------|------------|-----|----|-----------|

| 11-0 | FRAME_CNT2 | R/W |    | 视频 2 中的帧数 |

|      |            |     |    | 0x0 = 无效  |

|      |            |     |    | 0x1 = 1 帧 |

|      |            |     |    | 0x2 = 2 帧 |

www.ti.com.cn FPGA 寄存器定义

# 7.13 VCM\_CONTROL 寄存器 (地址 = 0x74) [复位 = 0x10]

表 7-15 展示了 VCM\_CONTROL。

返回汇总表。

# 表 7-15. VCM\_CONTROL 寄存器字段说明

| 位    | 字段                 | 类型  | 复位  | 说明                                                        |

|------|--------------------|-----|-----|-----------------------------------------------------------|

| 31-6 | RESERVED           | R   | 0x0 | 保留                                                        |

| 5    | VCM_TOGGLE_CONFIGS | R/W | 0x0 | 视频缓冲器切换选择 0x0 = 播放将仅使用所选缓冲器 0x1 = 播放将使用两个缓冲器              |

| 4    | VCM_LOOP_CONFIGS   | R/W | 0x1 | 循环配置<br>0x1 = 重复配置                                        |

| 3    | VCM_BUF_PTR        | R/W | 0x0 | 视频配置指针<br>0x0 = 播放视频 1<br>0x1 = 播放视频 2                    |

| 2    | VCM_AUTOSTOP       | R/W | 0x0 | 播放后自动停止 0x0 = 重复视频播放的最后一帧,直到收到其他命令 0x1 = 视频完成后停止,并且停止 DMD |

| 1    | VCM_STOP           | R/W | 0x0 | 停止视频/停止 DMD                                               |

| 0    | VCM_PLAY           | R/W | 0x0 | 播放视频。自清除                                                  |

# 7.14 VCM\_STATUS 寄存器 (地址 = 0x78) [复位 = 0x0]

表 7-16 展示了 VCM\_STATUS。

返回汇总表。

视频状态寄存器

# 表 7-16. VCM\_STATUS 寄存器字段说明

| 位    | 字段                  | 类型 | 复位  | 说明             |

|------|---------------------|----|-----|----------------|

| 31-3 | RESERVED            | R  | 0x0 | 保留             |

| 2    | VCM_SEQABORT_ERR    | R  | 0x0 | 序列中止错误在视频播放时清除 |

| 1    | VCM_CURR_CONFIG_PTR | R  | 0x0 | 当前视频配置指针       |

| 0    | VCM_VID_IN_PROGRESS | R  | 0x0 | 设置时视频正在进行      |

# 7.15 TMP\_CTRL 寄存器 (地址 = 0x90) [复位 = 0x00010003]

表 7-17 展示了 TMP\_CTRL。

返回汇总表。

温度控制寄存器

## 表 7-17. TMP\_CTRL 寄存器字段说明

| 位     | 字段            | 类型  | 复位  | 说明                                           |

|-------|---------------|-----|-----|----------------------------------------------|

| 31-17 | RESERVED      | R   | 0x0 | 保留                                           |

| 16    | TMP_CTRLEN    | R/W | 0x1 | 温度功能启用<br>0x0 = 禁用<br>0x1 = 启用               |

| 15-8  | TMP_I2CSLADDR | R/W | 0x0 | TMP411 I2C 从器件地址(有关详细信息,请参阅 TMP411 数据表)      |

| 7-0   | TMP_NFACTOR   | R/W | 0x3 | 补偿 TMP411 测量的 N 因子 ( 有关详细信息, 请参阅 TMP411 数据表) |

# 7.16 TMP\_STATUS 寄存器 (地址 = 0x94) [复位 = 0x0]

表 7-18 展示了 TMP\_STATUS。

返回汇总表。

温度状态寄存器

#### 表 7-18. TMP\_STATUS 寄存器字段说明

| 位    | 字段        | 类型 | 复位  | 说明                                                  |

|------|-----------|----|-----|-----------------------------------------------------|

| 31-2 | RESERVED  | R  | 0x0 | 保留                                                  |

| 1    | TMP_VALID | R  |     | 温度状态有效<br>0x0 = I2C 温度读取失败或尚未完成<br>0x1 = I2C 温度读取成功 |

| 0    | TMP_PASS  | R  |     | 温度状态通过 0x0 = 选择序列发生器缓冲器 0 0x1 = 选择序列发生器缓冲器 1        |

#### 7.17 TMP\_REMOTE\_TEMP 寄存器 (地址 = 0x98) [复位 = 0x0]

表 7-19 展示了 TMP\_REMOTE\_TEMP。

返回汇总表。

DMD 温度测量

#### 表 7-19. FAULT\_STATUS 寄存器字段说明

| 位     | 字段                  | 类型 | 复位  | 说明              |

|-------|---------------------|----|-----|-----------------|

| 31-28 | RESERVED            | R  | 0x0 | 保留              |

| 27-16 | TMP_REMOTE_FILTERED | R  | 0x0 | TMP411 远程温度滤波测量 |

|       |                     |    |     | 滤波后的 DMD 温度测量   |

| 15-12 | RESERVED            | R  | 0x0 | 保留              |

| 11-0  | TMP_REMOTE_RAW      | R  | 0x0 | TMP411 远程温度原始测量 |

|       |                     |    |     | 单个 DMD 温度测量     |

www.ti.com.cn 修订历史记录

#### 7.18 TMP\_LOCAL\_TEMP 寄存器 (地址 = 0x9C) [复位 = 0x0]

表 7-20 展示了 TMP\_LOCAL\_TEMP。

返回汇总表。

TMP411 温度测量

#### 表 7-20. TMP\_LOCAL\_TEMP 寄存器字段说明

| 位     | 字段                 | 类型 | 复位  | 说明                                  |

|-------|--------------------|----|-----|-------------------------------------|

| 31-28 | RESERVED           | R  | 0x0 | 保留                                  |

| 27-16 | TMP_LOCAL_FILTERED | R  | 0x0 | TMP411 本地温度滤波测量<br>滤波后的 TMP411 温度测量 |

| 15-12 | RESERVED           | R  | 0x0 | 保留                                  |

| 11-0  | TMP_LOCAL_RAW      | R  | 0x0 | TMP411 本地温度原始测量<br>单个温度测量           |

# 8 修订历史记录

注:以前版本的页码可能与当前版本的页码不同

# Changes from Revision A (April 2024) to Revision B (June 2024)Page● 更新了节 519

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司