## User's Guide

# 将 AFE7769DEVM 与 Hitek Agilex eSOM7 FPGA 连接

### 摘要

本用户指南概述了硬件和软件设置,并提供了补充图片作为直观展示,然后介绍了启动步骤、环回示例和使用 LTE 信号的环回测试。

# 内容

| 1 引言                                    | 2               |

|-----------------------------------------|-----------------|

| 2 硬件设置                                  | <mark>2</mark>  |

| 3 软件设置                                  | 3               |

| 4 启动步骤                                  | 4               |

| 5 带有 DDR 的 TX 到 FB 环回示例                 | 13              |

| A 设置以太网端口 IP 地址                         | 15              |

|                                         |                 |

| 插图清单                                    |                 |

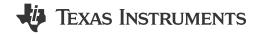

| 图 2-1. 硬件设置,AFE7769DEVM 和 Agilex eSOM7  | 3               |

| 图 3-1. 第一次更改代码行,AFE77xxD GUI            |                 |

| 图 3-2. 第二次更改代码行, AFE77xxD GUI           |                 |

| 图 4-1. 打开 Teraterm 中的串行端口窗口             | 4               |

| 图 4-2. 串行端口设置和连接                        | 4               |

| 图 4-3. IP 地址获取                          | 5               |

| 图 4-4. 启动 AFE77xxD Latte GUI            | 5               |

| 图 4-5. 导航至 AFE77xxD-Params              | 6               |

| 图 4-6. AFE77xxD-Params 显示视图             | 6               |

| 图 4-7. 将 AFE77xxD 配置文件加载到 Latte         | <mark>7</mark>  |

| 图 4-8. Quartus Prime Programmer 中的自动检测  | <mark>7</mark>  |

| 图 4-9. 器件选择                             | 8               |

| 图 4-10. 文件更改                            | 8               |

| 图 4-11. 程序/配置                           | 9               |

| 图 4-12. 器件启动,AFE77xxD-Params            | 9               |

| 图 4-13. 在 AFE77xxD Latte GUI 中确认 LMK 配置 | <mark>9</mark>  |

| 图 4-14. 点击开始按钮对 Agilex FPGA 进行编程        | 10              |

| 图 4-15. 在 Agilex FPGA 中初始化 JESD IP      | 11              |

| 图 4-16. AFE 配置完成说明器件 JESD RX 的链路接通      | <mark>11</mark> |

| 图 4-17. 完成 JESD204C 链路并显示链路的状态报告        | 12              |

| 图 4-18. Eth0 接口                         |                 |

| 图 4-18. 确认 eth0 接口有正确的 IP 地址            | 12              |

| 图 4-20. TX 到 RX 测试的 TDD 配置              | 13              |

| 图 4-21. TX 到 FB 测试的 TDD 配置              | 13              |

| 图 5-1. 运行环回命令后的预期输出                     | 13              |

| 图 5-2. 显示环回 TM3.1a 波形的 FFT              |                 |

| 图 5-3. FFT 放大显示环回 TM3.1a 波形             |                 |

| 图 A-1. 以太网设置                            |                 |

| 图 A-2. 手动设置 IP 地址                       |                 |

| 图 A-3. 在控制面板中打开网络                       |                 |

| 图 A-4. 打开显示以太网连接的属性选项卡                  |                 |

| 图 A-5. 打开 IPv4 属性                       |                 |

| 图 A-6. 手动设置 IP 地址                       | 17              |

## 商标

Intel Agilex® is a registered trademark of Intel Corporation or its subsidiaries.

Arm® is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

所有商标均为其各自所有者的财产。

## 1 引言

本用户指南介绍了与 Hitek Systems 协作开发、使用德州仪器 (TI) AFE7769D 评估模块 (EVM) 的无线开发平台。Hitek Systems 是一家硬件公司以及 Intel 合作伙伴,为通信行业内的公司提供基于现场可编程门控阵列 (FPGA) 的评估模块。据 Hitek Systems 介绍,该参考解决方案旨在帮助客户提升模拟前端 (AFE) 的系统集成能力,并提供"用于 5G ORAN 和无线解决方案的快速评估和原型设计平台"。

AFE7769D 是一款具有集成数字预失真 (DPD) 的 4T4R2F 射频采样收发器,可用于线性化功率放大器 (PA),以提高终端客户的无线覆盖范围。无线开发平台采用器件的 EVM 版本,该器件通过 FPGA 夹层卡 (FMC+) 连接器与 Hitek 的解决方案元件相连。Agilex 嵌入式模块上系统 (eSOM7) 是一个 FPGA 模块,可通过 FMC+ 连接器与 AFE7769DEVM 交互。该硬件基于使用 Intel 10nm SuperFin 工艺技术构建的 Intel Agilex® 7 SoC FPGA。

在文档的以下部分中,命令以**粗体**显示,文件路径、文件夹和名称以*斜体*显示,用户界面中的标题用引号括起来。

## 2 硬件设置

以下部分从硬件 (HW) 角度分步介绍了参考设计的设置,并在最后提供了该设置的直观展示。

#### 步骤:

- 1. 将 Agilex 嵌入式 SOM7 (eSOM7) 安装到 TI 载板上。

- 2. 将 AFE7769DEVM 安装在 TI 载板的 FMC+ 插槽上。

- 3. 将 +12V 6 引脚 ATX PCIe 电源连接器插入 TI 载体中。

- 4. 将 Micro USB 从主机 PC 连接到 TI 载体的 USB 连接器 J23,以便对 HPS(Arm® 节点)进行 UART 访问。

- 5. 将 Micro USB 从主机 PC 连接到 TI 载体的 USB 连接器 J24,以便通过 JTAG 对包含 RF 接口框架的 Agilex FPGA 图像进行编程。

- 6. 将以太网电缆连接到 TI 载体的 RJ45 端口 (J21),以通过网络传输文件。

- 7. 将 5.5V、5A 电源连接到 TI AFE7769DEVM。

- 8. 在主机 PC (Windows) 与 TI AFE7769D 评估卡上的 mini-USB 端口之间连接 mini-USB 电缆,用于使用定制 的 TI AFE77xxD Latte 软件(版本 0.4.0)和提供的配置文件配置评估卡上的芯片。

- 9. 从 TX RF 端口连接到 RX/FB RF 端口的 SMA 电缆。

- a. 对于 TX 到 RX RF 端口,连接应如下所示:

- i. TX1 (J7) 至 RX1 (J1)

- ii. TX2 (J8) 至 RX2 (J2)

- iii. TX3 (J9) 至 RX3 (J3)

- iv. TX4 (J10) 至 RX4 (J4)

- b. 对于 TX 到 FB RF 端口,连接应如下所示:

- i. TX1 (J7) 至 FB1 (J5)

- ii. TX2 (J8) 至 FB2 (J6)

为硬件设置加电时,请在为 TI AFE7769DEVM 加电之前为 Agilex eSOM7 TI 载体加电。关闭硬件设置的电源时,请先关闭 TI AFE7769DEVM 的电源,然后再关闭 Agilex eSOM7 TI 载体的电源。有关硬件设置的最终结果,请参阅图 2-1。

#### 备注

Agilex eSOM7 附带 Skyworks Si5518 时序模块(ASY-00-00048 版本 2)。就本指南而言,这不是必需的。

图 2-1. 硬件设置, AFE7769DEVM 和 Agilex eSOM7

## 3 软件设置

以下部分从软件 (SW) 角度分步介绍了参考设计的设置,以及整个过程的屏幕截图。包含所需文件的文件夹可在以下链接 <> 中找到。Quartus Programmer、Teraterm 和 PowerShell 的安装程序可在线获取。

#### 步骤:

安装以下软件元素:

- 1. AFE77xxD 图形用户界面 (GUI) 0.4.0 版

- a. 对 Documents\Texas Instruments\AFE77xxDLatte 文件夹中的文件进行以下更改:

- i. 图 3-1 (lib\Afe77xxDLibraries\AFE77xxDLibraryPG1p0\resourceFiles\mLmk.py) 和图 3-2 (lib\Afe77xxDLibraries\AFE77xxDLibraryPG1p0\resourceFiles\mSetupParams.py) 分别显示了如何将下面以红色编写的代码行更改为以绿色编写的代码行,从而更改某些 LMK 分频器,以便为此应用输出正确的 FPGA 时钟。

- lmk.head.page.DCLK12\_SDCLK13\_controls.Out\_control.dclkout\_DIV\_lt\_4\_0\_gt\_= 12

+ lmk.head.page.DCLK12\_SDCLK13\_controls.Out\_control.dclkout\_DIV\_lt\_4\_0\_gt\_= int(round(divInputClk/setupParams.fpgaRefClk)

图 3-1. 第一次更改代码行, AFE77xxD GUI

- fpgaRefClk = 245.76

+ fpgaRefClk = 368.64

图 3-2. 第二次更改代码行, AFE77xxD GUI

- 2. Teraterm 版本 4.106

- a. 安装任何串行端口终端(Minicom 或 Gtkterm)以连接到 Agilex HPS(Arm 节点)。在本指南中,使用 Teraterm。

- 3. PowerShell

- 4. Intel Quartus Programmer 版本 22.3

- a. 仅在附加软件下安装 "Intel® Quartus® Prime Pro Edition Programmer and Tools": https://www.intel.com/content/www/us/en/software-kit/746667/intel-quartus-prime-pro-edition-design-software-version-22-3-for-windows.html

- b. Intel 网站上还有一个补丁,可以修复此版本存在的问题:https://www.intel.com/content/www/us/en/support/programmable/articles/000092460.html。

- 5. IP 地址设置

#### 4 启动步骤

以下部分从启动的角度分步介绍了参考设计的设置,以及整个过程的相关屏幕截图。

#### 步骤:

- 1. 首先,为 Agilex eSOM7 TI 载板上电,然后为 TI AFE7769DEVM 上电。

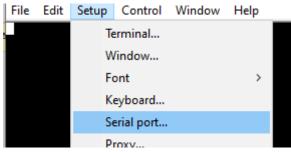

- 2. 打开 Teraterm,点击"Serial",然后点击"OK"。

- 3. 依次点击 "Setup > Serial port",请参阅图 4-1。

图 4-1. 打开 Teraterm 中的串行端口窗口

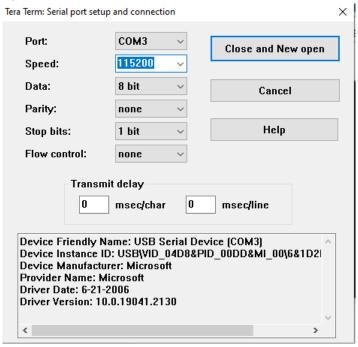

4. 此时将显示一个新窗口。选择连接 eSOM7 的 COM 端口(不是 COM1)。将速度更改为"115200",然后点击"Close and New open",请参阅图 4-2。

图 4-2. 串行端口设置和连接

5. 您现在应该会看到"agilex login:",如果您没有看到任何文本,请按 Enter 键,屏幕上将出现"agilex login"。

- 6. 键入 **root** 并按 Enter 键登录。

- 7. 使用 ifconfig 命令获取 Arm 节点的 IP 地址。如果在 eth0 接口下看不到"inet4" IP 地址,请使用命令 ifconfig eth0 192.168.0.1 netmask 255.255.255.0 为 eth0 接口分配 192.168.0.1 IP 地址,请参阅图 4-3。

图 4-3. IP 地址获取

- 8. 在 PowerShell 上,使用 cd < Hitek RF INTF release archive path> 命令将您的目录移至 Hitek RF INTF 版本归档。在我们的设置中,命令为 cd C:\Users\a0503061\Documents\Hitek\AG\_eSOM\_AFE77XX\_RF\_INTF\_DEMO\_Release\_v3\_3\_2023-04-2

- 9. 使用 **scp -r software/arm\_ag/tools/ root@192.168.0.1:~/jesd\_tools/** 命令将 *software/arm\_ag\_/tools* 文件 夹从 *AG\_eSOM\_AFE77XX\_RF\_INTF\_DEMO\_Release\_v3\_3\_2023-04-25* 文件夹复制到文件夹名为 "jesd\_tools"的 Arm 节点。

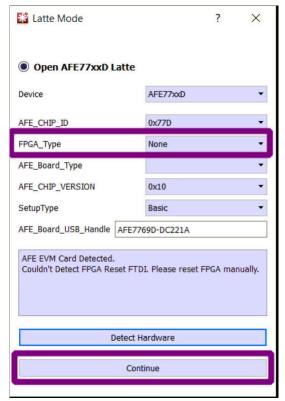

- 10. 启动 TI AFE77xxD Latte GUI 软件,在标题为"Latte Mode"的第一个对话框窗口中,确保"FPGA\_Type"设置为"None",并显示"AFE EVM Card Detected"消息。应该会显示"Couldn't Detect FPGA Reset FTDI.Reset FPGA manually"。然后按"Continue"按钮打开 Latte 主 GUI。要正确导航到"Latte Mode"窗口,请参阅图 4-4。

图 4-4. 启动 AFE77xxD Latte GUI

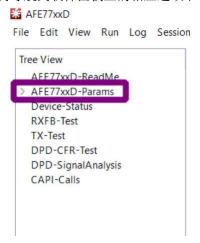

11. 在 Latte 软件完成初始化步骤后,点击软件窗口左面板上的"AFE77xxD-Params",转到"AFE77xxD Params"选项卡。图 4-5 显示了如何导航到软件面板上的相应选项卡。

图 4-5. 导航至 AFE77xxD-Params

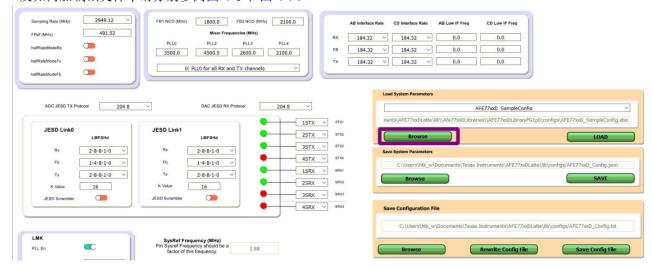

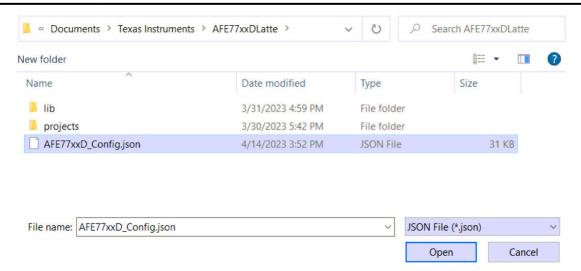

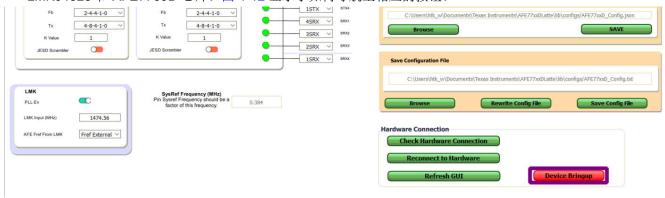

12. 在 "Load System Parameters" 框中,点击 "Browse" 以搜索 AG\_eSOM\_AFE77XX\_RF\_INTF\_DEMO\_Release\_v3\_3\_2023-04-25\software\x64\_64\utilities\AFE77xxDLat te\_v0p4 中提供的 AFE77xxD\_Config.json 配置文件,并将其打开。有关 "AFE77xxD-Params"显示视图以及如何加载该文件,请分别参阅图 4-6 和图 4-7。

图 4-6. AFE77xxD-Params 显示视图

图 4-7. 将 AFE77xxD 配置文件加载到 Latte

- 13. 选择配置文件后,请点击"LOAD"按钮将此配置加载到 GUI 中。GUI 应更改为所需配置,以便能够与 Agilex FPGA 中的 JESD IP 建立 JESD 链路。

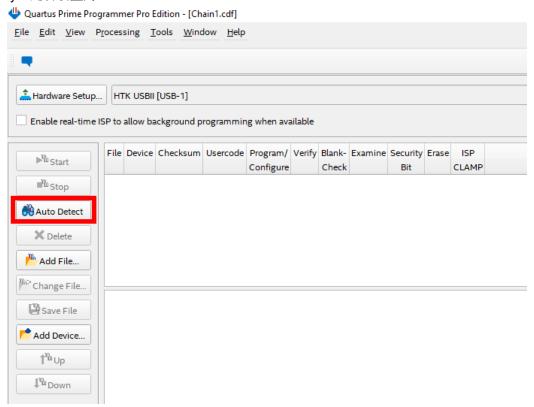

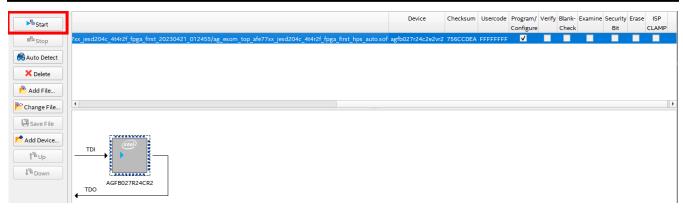

- 14. 打开 Quartus Prime Programmer 并点击 "Auto Detect" 按钮。有关如何导航至相应功能的信息,请参阅图 4-8。如果这是 eSOM7 首次连接到 PC,而"Auto Detect"按钮为灰色,请点击"Hardware Setup..."按钮,在"Currently selected hardware"旁边的下拉菜单中选择"HTK USBII",然后检查"Hardware frequency"是否设置为 24000000Hz。

图 4-8. Quartus Prime Programmer 中的自动检测

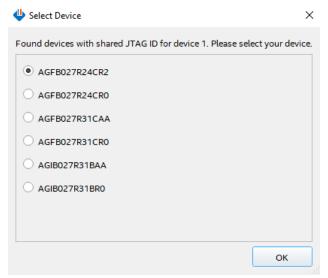

15. 点击 "Auto Detect"后,将出现一个窗口;选择"AGFB027R24CR2"选项并点击"OK"。图 4-9 显示了选择器件时的典型视图。

图 4-9. 器件选择

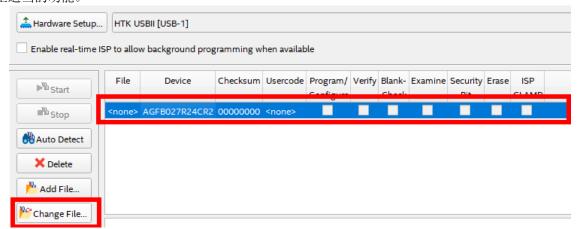

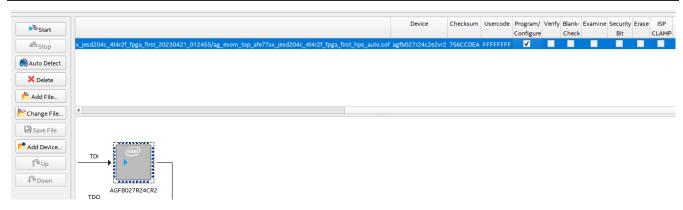

16. 选择 "File"下的唯一行,然后点击 "Change File"。选择 AG\_eSOM\_AFE77XX\_RF\_INTF\_DEMO\_Release\_v3\_3\_2023-04-25\snapshots\hardware\fpga\agfb027\_r24 c\_asyXX\ag\_esom\_top\_afe77xx\_jesd204c\_4t4r2f\_fpga\_first\_20230421\_012455 目录中提供的名为 ag\_esom\_top\_afe77xx\_jesd204c\_4t4r2f\_fpga\_first\_hps\_auto.sof 的 FPGA 图像,其中"XX"应与 eSOM7 板上的"ASY-XX-00047"标签匹配。压缩的 .tar.gz 文件夹中有这些文件的额外副本。图 4-10 显示了如何导航至适当的功能。

图 4-10. 文件更改

17. 接下来,选中"Program/Configure"下的框,请参阅图 4-11。

图 4-11. 程序/配置

18. 在 AFE77xxD GUI 上,应点击"AFE77xxD-Params"页面底部的"Device Bringup"按钮,开始配置 LMK04828 和 AFE7769D 芯片。图 4-12 显示了如何导航至相应的按钮。

图 4-12. 器件启动, AFE77xxD-Params

19. TI AFE77xxD Latte 软件日志窗口中出现"LMK Configured"消息后,说明 LMK04828 芯片配置完成,通过点击 Quartus Prime Programmer 上的"Start"按钮,对 Agilex FPGA 图像进行编程。图 4-13 和图 4-14 提供了器件编程步骤的直观参考。

图 4-13. 在 AFE77xxD Latte GUI 中确认 LMK 配置

启动步骤 www.ti.com.cn

图 4-14. 点击开始按钮对 Agilex FPGA 进行编程

20. 等待 Arm 节点的 Linux 引导显示在 Teraterm 控制台上,并使用 **root** 用户名登录。然后,使用命令 **source jesd\_tools/init\_term.sh** 执行 jesd\_tools 文件夹中的 init\_term.sh 脚本,然后运行 Arm 节点上的 **run\_jesd\_init\_afe77xx\_jesd204c\_4t4r2f\_board.sh** 脚本。先不要按 Enter 键。图 4-15 显示了一个示例代码 块。

```

Poky (Yocto Project Reference Distro) 3.4.2 agilex tty81

agilex login: root

Nov 19 17:19:43 agilex authpriv.notice login[201]: ROOT LOGIN on '/dev/tty81'

root@agilex:~# source jesd_tools/init_term.sh

Setting I2C Device Environment Variables...

root@agilex:~# run_jesd_init_afe?7xx_jesd204c_4t4r2f_board.sh

Checking F-Tile System PLL Lock Status

Reset ACKs are deasserted

Reset ACKs are asserted

Reset ACKs are deasserted

Press Enter to recalibrate FPGA XCURs (Rx only) once AFE?7XX eval. board bringup is complete

```

## 图 4-15. 在 Agilex FPGA 中初始化 JESD IP

21. 等到 TI AFE77xxD Latte 软件中的 AFE7769D 配置完成,它应该会在"Log"窗口中报告 AFE7769D 芯片上的 JESD204C 链路成功(请注意,预计会出现与 FPGA 复位故障相关的 2 个错误)。图 4-16 显示了"Log"窗口,其中显示了器件能够为器件的 JESD RX 接通链路。

```

AFE DPD Block configuration Complete

AFE RX IQMC configuration Complete

AFE RX AGC configuration Complete

Setting RBD to: 9

############Device DAC JESD-RX 0 Link Status##########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

BUF State TX0: 0b11111111 . It is expected to be 0b11111111

Could get the link up for device RX: 0

**********

###########Device DAC JESD-RX 0 Link Status##########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

BUF State TX0: 0b11111111 . It is expected to be 0b11111111

Could get the link up for device RX: 0

***************

Setting RBD to: 6

##########Device DAC JESD-RX 0 Link Status#########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

BUF State TX0: 0b11111111 . It is expected to be 0b11111111

Could get the link up for device RX: 0

************

AFE configuration Complete

#======= ERRORS:2, WARNINGS:0 =========#

```

图 4-16. AFE 配置完成说明器件 JESD RX 的链路接通

启动步骤 www.ti.com.cn

22. 在 TI AFE77xxD Latte 软件中完成 AFE7769D 配置后,在 Arm 节点 (Teraterm) 上按 Enter 键以重新校准 FPGA XCVR(仅限 Rx),从而完成 FPGA 上的 JESD204C 链路。图 4-17 显示了 FPGA 中的链路状态报告。

```

root@agilex:~# run_jesd_init_afe77xx_jesd204c_4t4r2f_board.s

:hecking F-Tile System PLL Lock Status

:eset ACKs are deasserted

:esst ACKs

Reset ACKs are asserted

Reset ACKs are deasserted

ress Enter to recalibrate FPGA XCVRs (Rx only) once AFE77XX eval. board bringup is complete

Reset ACKs are deasserted

Reset ACKs are asserted

Reset ACKs are deasserted

Thecking JESD Link Status ...

JESD Common Status

= Locked

JESD TX Status

## + TX Link Ready

## + TX Interrupt

= Ready

= Not asserted

JESD RX/FB Status

= Ready

## + FB Link Ready

## + RX Interrupt

= Ready

Asserted

## + FB Interrupt

## + RX J204C Sync Header

= Asserted

##

##

Locked

## + FB J204C Sync Header

## + RX J204C EMB

##

##

Locked

= Locked

## + FB J204C EMB

## + RX/FB J204C CRC Errors

.......

root@agilex:~#

```

图 4-17. 完成 JESD204C 链路并显示链路的状态报告

23. 运行 ifconfig 命令查看 eth0 接口的 IP 地址。图 4-18 显示了一个示例代码块。

- a. 如果 eth0 接口与上图中的不符,请使用 ifconfig eth0 192.168.0.1 up 命令启动接口。然后,使用 ifconfig eth0 192.168.0.1 netmask 255.255.255.0 命令设置接口的 IP 地址

- b. 然后,您可以使用 ifconfig 命令检查该接口是否分配了 IP 地址,请参阅图 4-18 作为参考。

图 4-18. 确认 eth0 接口有正确的 IP 地址

#### 图 4-18. Eth0 接口

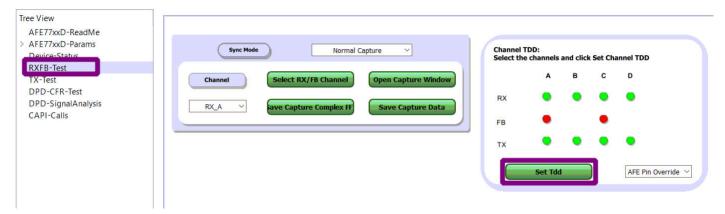

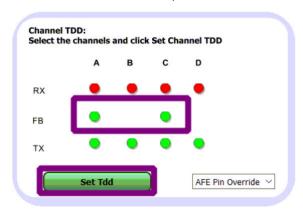

24. 为了能够从 TX RF 端口输出信号以及从 RX 和 FB RF 端口输入信号,需要为所需的被测通道设置 "Channel TDD"。为此,请点击软件窗口左侧的"RXFB-Test",转到 AFE77xxD GUI 中的"RXFB-Test"页面。在此页面的"Channel TDD"框中,点击红点使其变为绿色,最后点击"Set Tdd"按钮,请参阅图 4-20。

图 4-20. TX 到 RX 测试的 TDD 配置

请注意,在测试 FB 通道时,不应设置 RX 通道的 TDD(因此, RX 通道的点不是绿色的),请参阅图 4-21。

图 4-21. TX 到 FB 测试的 TDD 配置

#### 5 带有 DDR 的 TX 到 FB 环回示例

#### 步骤:

- 确保 SMA 电缆已连接,使前两个 TX RF 端口 (TX1-TX2) 连接到两个 FB RF 端口(分别为 FB1-FB2)。

- 2. 在 PowerShell 中使用命令 scp <path to the waveform file> root@192.168.0.1:/home/root/jesd\_tools/data/,将波形文件从主机 PC 复制到 Arm 节点。对于此设置,我们使用了scp .\jesd\TM3.1a\_FDD\_737.28MHz\_eSOM\_ACLRver.txt root@192.168.0.1:/home/root/jesd\_tools/data/命令。

- a. 波形文件的格式是,每个样本占据一行,第一列中的 I 部分和第二列中的 Q 部分均为 16 位十六进制值。

- 3. 在 Arm 节点 (Teraterm) 上,运行下面的命令来同时将波形样本播放到 FPGA 前两个 TX 通道中的每一个通道上,并以 4T4R2F 模式采集两个 FB 通道中每个通道的样本。

- a. run\_jesd\_cw\_lpbk\_tests\_with\_ddr.sh -s=8 -n=2 -f=jesd\_tools/data/ TM3.1a\_FDD\_737.28MHz\_eSOM\_ACLRver.txt

- b. 预期的输出如图 5-1 所示。

rootĕagilex:~# run\_jesd\_cw\_lpbk\_tests\_with\_ddr.sh -s=8 -n=2 -f=jesd\_tools/data/TM3.1a\_FDD\_737.28MHz\_eSOM\_ACLRver.txt

Using /home/root/jesd\_tools/data/TM3.1a\_FDD\_737.28MHz\_eSOM\_ACLRver.txt for looping playback of 7372800 samples from

DDR-A to TX0,TX1,TX2,TX3 channels

Greated /home/root/jesd\_tools/log/cw\_capture\_fb0.txt after capture of 65536 samples from FB0 channel to DDR-B

Greated /home/root/jesd\_tools/log/cw\_capture\_fb1.txt after capture of 65536 samples from FB1 channel to DDR-B

root@agilex:~#

#### 图 5-1. 运行环回命令后的预期输出

4. 执行结束时,Arm 节点上的 *jesd\_tools/log* 文件夹中应该会创建两个名为 *cw\_capture\_fb[0-1].txt* 的捕获文件。使用 **scp root@192.168.0.1:/home/root/jesd\_tools/log/cw\_capture\_fb0.txt <location to copy>** 命令将其中一个文件复制到主机 PC 的

Hitek\_RF\_INTF\_Common\_Files\_2023-06-07\software\x64\_64\analysis\jesd 文件夹中。在我们的设置中,使用了 scp root@192.168.0.1:/home/root/jesd\_tools/log/cw\_capture\_fb0.txt jesd/ 命令。

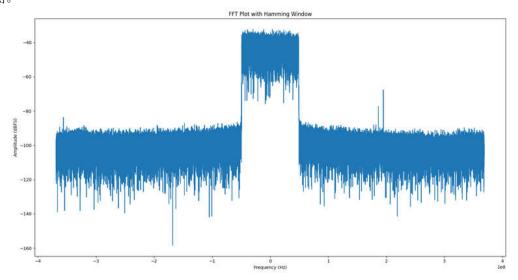

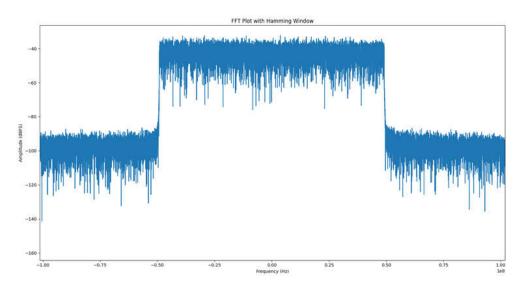

5. 从 Hitek\_RF\_INTF\_Common\_Files\_2023-06-07\software\x64\_64\analysis\jesd 目录运行 .\run\_freq\_plot.exe 2 .\\cw\_capture\_fb0.txt 737280000 命令,以显示具有 FB 捕获汉明窗的快速傅里叶变换 (FFT)。FB 在 4T4R2F 模式下以 737.28Msps 的频率进行采样,如图 5-2 所示。您可以放大以调整图像中的视图。

图 5-2. 显示环回 TM3.1a 波形的 FFT

图 5-3. FFT 放大显示环回 TM3.1a 波形

## A 设置以太网端口 IP 地址

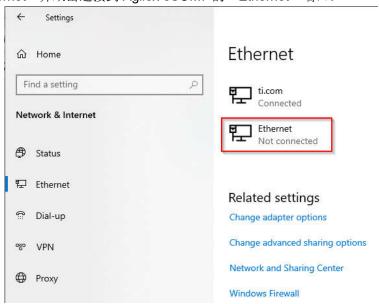

1. 进入设置下的"Ethernet"并双击连接到 Agilex eSOM7 的"Ethernet"端口。

图 A-1. 以太网设置

2. 在 IP 设置下方,点击"Edit"按钮并在下拉列表中选择"Manual",以手动设置 IP 地址,如图 A-2 所示。 更改"IP address"、"Subnet prefix length"和"Gateway"字段后,点击"Save"。

图 A-2. 手动设置 IP 地址

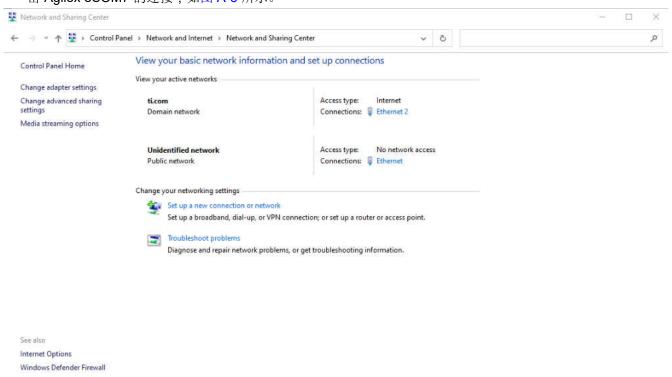

3. 之后,打开控制面板并转至"Control Panel\Network and Internet\Network and Sharing Center"。然后,点击 Agilex eSOM7 的连接,如图 A-3 所示。

图 A-3. 在控制面板中打开网络

4. 此时会显示如图 A-4 所示的窗口。点击"Properties"按钮。

图 A-4. 打开显示以太网连接的属性选项卡

5. 之后,将打开一个如图 A-5 中所示的窗口。双击"Internet Protocol Version 4 (TCP/IPv4)"选项以打开其"Properties"选项卡。

图 A-5. 打开 IPv4 属性

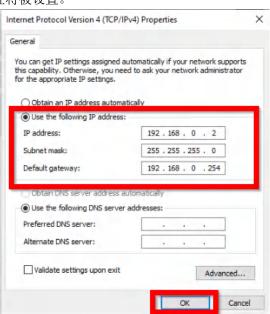

6. 在随即打开的窗口中,选择"Use the following IP address"选项,然后填写图 A-6 中所示的字段。填写完相应字段后,点击"OK",地址将被设置。

图 A-6. 手动设置 IP 地址

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司