TI Designs: TIDA-00835

采用 **24** 位  $\Delta$ -Σ **ADC** 的高精度 **±0.5%** 电流和隔离式电压测量参考设计

# TEXAS INSTRUMENTS

#### 说明

此参考设计允许在宽动态范围内使用四通道、24 位同步采样差分输入 Δ-Σ ADC 实现精准电压和电流测量。 ADC 配置为测量 ±2.5V 双极输入,可测量 ±4V。使用固定增益放大器可将输入缩放到 ±2.5V 的 ADC 输入范围。该 AFE 采用通用外部时钟和缓冲器连接两个ADC,以将输入通道数量扩展至 8 个,同时对所有输入通道进行同步采样。通过每个模块采用更多测量通道,从而降低了总体系统成本。此外,还可将诊断整合到TIDA-00810 所示的设计中。

#### 资源

| TIDA-00835   | 设计文件夹 |

|--------------|-------|

| ADS131A04    | 产品文件夹 |

| ADS131A02    | 产品文件夹 |

| CDCLVC1102PW | 产品文件夹 |

| OPA4180ID    | 产品文件夹 |

| AMC1301      | 产品文件夹 |

| ISO224       | 产品文件夹 |

| SN6501       | 产品文件夹 |

| TPS60403DBVR | 产品文件夹 |

| TPS72325DBVT | 产品文件夹 |

| TPS71733DCKR | 产品文件夹 |

| TLV70450DBVR | 产品文件夹 |

| LM27762      | 产品文件夹 |

| MSP432P401R  | 产品文件夹 |

| REF3425      | 产品文件夹 |

| REF3440      | 产品文件夹 |

| TLV9061      | 产品文件夹 |

| OPA4171      | 产品文件夹 |

| TVS0500      | 产品文件夹 |

|              |       |

咨询我们的 E2E 专家

#### 特性

- 数据采集

- 四通道、同步采样、基于 24 位 Δ-Σ

(ADS131A04) ADC 的 AFE,用于精确测量 ±0.5% 内的宽输入

- 两个 ADC 之间实现同步,从而扩展输入通道 (共八个)

- 模拟输入

- 使用板载负载电阻器和外部电流互感器进行电流 输入测量

- 使用活动硬件积分器连接到 TIDA-00777 Rogowski 的输出

- 使用带 AMC1301 增强型隔离放大器(替代传统电压互感器)或不带隔离的分压器进行电压测量

- AMC1301 输出与配置为双极性的 ADC 兼容 (±2.5V)

- 为主机接口提供 ±2.5V AVDD 电源和 3.3V DVDD 电源

- 在双极模式下提供 2.5V 或 4V 的外部基准,以增加 动态范围

- 与基于 ARM® Cortex®-M4F 的低功耗 MCU (MSP432P401R) 相连

#### 应用

- 保护继电器

- 远程终端装置,数据终端装置

- 电能质量分析仪

- ACB、MCCB

System Overview www.ti.com.cn

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

## 1 System Overview

## 1.1 Protection Relay

Protection relays installed along power systems protect the primary equipment and customer loads (motors and busbar). Protection relays are used during generation, transmission, distribution, and at consumer locations. The features and complexities vary depending on the installation. Protection relays detect defective lines, apparatus, and other power system conditions of an abnormal or dangerous nature. Protection relays also initiate appropriate control over circuit action. Relays detect and locate faults by measuring electrical quantities in the power system, which are different during normal and intolerable conditions. The most important role of protection relays is to protect individuals first and then equipment.

Protection relays also minimize the damage and expense caused by insulation breakdowns (above overloads) called faults. These faults can occur as a result of deteriorated insulation or unforeseen events such as lightning strikes or power trips, caused by contact with trees and foliage. Protection relays are not required to operate during normal operation, but must immediately activate to handle intolerable system conditions. This immediate availability criterion is necessary to avoid serious outages and damages to portions of or the entire power network. In theory, a relay system must be able to respond to an infinite number of abnormalities that may occur within the network.

Protection relays are intelligent electronic devices (IEDs) that receive measured signals from the secondary side of current transformers (CTs) and voltage transformers (VTs). The relays detect whether or not the protected unit is in a stressed condition (based on the type and configuration of the unit). The protective relays send a trip signal to the circuit breakers to disconnect the faulty components from the power system if necessary.

www.ti.com.cn System Overview

## 1.2 Introduction to Protection Relay and Subsystems for Grid Applications

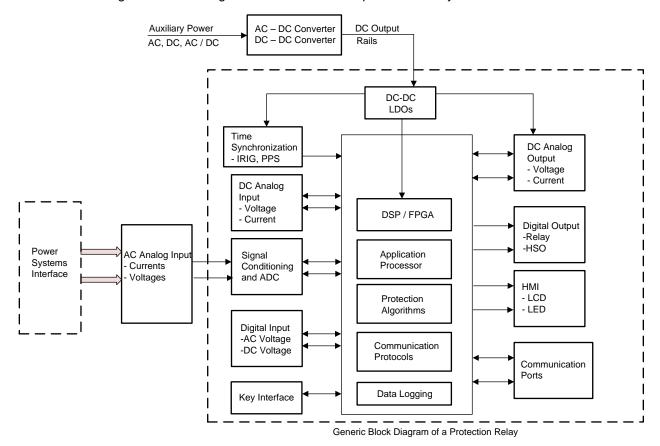

1 shows a generic block diagram for a multifunction protection relay.

Copyright © 2016, Texas Instruments Incorporated

图 1. General Block Diagram of Protection Relay

System Overview www.ti.com.cn

Protective relays are categorized based on the equipment type protected such as generators, transmission lines, transformers, and loads. The protection relay, or IED, used in grid applications has the following generic subsystems, which are based on functionality:

- CPU or DSP module: This module handles all protection functions and logic, as well as the HMI and communication functions.

- Power supply

- Nominal auxiliary voltage: 24-V DC, 48- to 60-V DC, 110- to 125-V DC, 220-V DC, and 230-V AC, 50 or 60 Hz, ±20%, and 40-W maximum admissible consumption

- Stored energy for up to 50-ms power supply interruption

- AC measurement inputs

- Nominal frequency (FNOM): 50 Hz or 60 Hz

- Operating range: 45 Hz to 66 Hz

- Accuracy: 0.2% F<sub>s</sub> at FNOM

- CT measurements inputs

- Nominal current: 1 or 5 A (IN)

- Nominal consumption per phase: < 0.15 A at IN</li>

- Load rating: 20 A in continuous, 30 A for 3 sec, and 100 A for 1 sec

- VT measurements inputs

- Nominal voltage: 57.7 to 500 V

- Nominal consumption per phase: < 0.1 VA at 130 V</li>

- Maximum measurable voltage: 577 V<sub>RMS</sub>

- DC analog input range (independently configurable)

- ±1.25, ±2.5, ±5, and ±10 V

- ±1, ±5, ±10, and ±20 mA

- 0 to 1, 0 to 5, 0 to 10, 0 to 20, and 4 to 20 mA

- DC analog output range (independently configurable): ±5, ±10, ±20 mA, and 4 to 20 mA

- Digital inputs

- Nominal voltage: 24-V DC, 48- to 60-V DC, 110- to 125-V DC or AC, 220-V DC or AC, ±20% or multi-voltage (24- to 250-V DC or AC)

- Groups of 4, 8, 12, 16, or 32

- Digital output relays Continuous current: 5 A

- Control output relays Continuous current: 5 A

- Time synchronization by:

- IRIG-B GPS clock (through the IRIG-B input)

- Ethernet SNTP server

- Time telegram message issued by remote SCADA (DNP3.0, IEC 60870-5-101, or IEC 60870-5-104)

- Communication capabilities Ethernet communication

- 10BASE-TX and 100BASE-TX, auto-crossing, or 100BASE-FX

www.ti.com.cn System Overview

- Protocols include UCA2 or IEC 61850, IEC 60870-5-104 (multi-client), or DNP3.0 IP

- Embedded Ethernet switch module with up to six ports (permitting a compact connection of various devices or I/O extensions) – Serial communication

- Up to two SCADA or four IED links per device

- SCADA protocol can be switched between DNP3.0, IEC 60870-5-101, and MODBUS

- IED protocol can be switched between DNP3.0, IEC 60870-5-103, MODBUS, and IEC 60870-5-101

This TI Design focuses on voltage and current input measurement using a high-resolution delta-sigma ADC.

System Overview www.ti.com.cn

## 1.3 Voltage, Current, and Power Measurement of AFE

The AFE for measurement of AC voltage and current inputs consists of the following:

- Voltage input circuit with potential divider, signal conditioning, and interface to the ADC

- Current input circuit consists of burden resistors, signal conditioning, and interface to the ADC

- Signal condition circuit provides fixed or variable gain to the AC inputs and a common-mode DC level shift based on application to interface to the ADC.

- ADC for sampling the analog inputs includes multichannel inputs and high-resolution capable of sampling at > 80 samples (80 samples for protection and 256 samples for measurement as per IEC61850-9-2) per cycle.

- Interface to the MCU to process the sampled values includes an 32-bit ARM Cortex-M4F MCU and interconnection to the AFE.

- Power supply subsystem includes generation of required positive and negative power supplies.

Additional features of the AFE include:

- · Measurement of a wide range of input currents and voltages

- Accurate measurement of AC parameters over the entire input range

- Isolated measurement of voltages using isolation amplifiers

- Measurement of increased number of channels

## 1.4 Accurate Measurement of AC Voltage, Current, and Power

Most of the current generation of multifunction protection relays provides power-measurement features. Protection relays are specified to measure wide input voltage and currents within a specified range of accuracy. To achieve wide dynamic input measurement within specified accuracy, ADC with PGA or a high-resolution ADC are used. In this design a 24-bit delta-sigma ADC is used.

## 1.5 Increasing Analog Input Channels

Depending on the protection relay configuration and application, the number of current and voltage channels varies from 4 to 16 channels. These 4 to 16 channels are realized by using multiple ADCs. If each ADC has separate interfaces, the complexity increases. Also, it may be necessary to synchronize multiple ADCs to ensure accuracy. The simplest way to interface multiple ADCs are daisy-chaining and using a common clock. In this design two ADCs are used. Each ADC has four channels. The ADCs are chained as a single interface and share a common clock.

#### 1.6 Measurement of Voltages and Currents

Protection relay is used in HV, MV, and LV applications. Depending on the application the voltage levels are high, and during fault conditions high voltage levels damage the protection relay. The solution to this problem is isolating the voltage and current inputs. Voltages are isolated to provide user safety. The inputs can be isolated using analog isolation amplifiers or digitally using modulators. In this design, isolation amplifiers are used and the output of the isolation amplifiers is interfaced to the delta-sigma ADC.

www.ti.com.cn System Overview

#### 1.6.1 Current Transformer or Rogowski Inputs

Primary current is reduced to measurable secondary current by an external CT and applied to the protection relay. The protection relay has an internal CT to transform the secondary current to a measurable input current level. The advantage to using CTs is that they provide isolation, and no additional isolation is required on the protection relay when an internal CT is used.

#### 1.6.2 Voltage Inputs

High-voltage inputs are connected to a PT and the secondary is connected to the input of the protection relay. Internally the protection relays have a potential transformer that can transform the input AC voltage into a measurable value. Potential transformers are large and have inherent nonlinearity, which is overcome by using a resistor divider. Resistor dividers do not provide isolation, as provided by the PT. Isolation amplifiers provide the required isolation when resistor dividers are used. Isolation amplifiers with either basic or reinforced isolation can be used based on the application. The solution using the resistor divider and isolation amplifier can be considered an alternative to the conventional potential transformer.

#### 1.6.3 Alternative Methods for Interfacing Analog Inputs to ADC

ADS131A04 is a differential input. In applications where differential measurement is preferred consider the following solutions:

- THS4551: Low-noise, precision, 150-MHz, fully differential amplifier

- THS4541High-Speed Differential I/O Amplifier

- THS4531A: Ultra-low-power, RRO, fully differential amplifier

For cost-sensitive applications, sensor output can be directly interfaced to the differential input of the ADC. The performance must be evaluated with specific sensors for accuracy.

## 1.7 Key System Specifications

表 1 lists the key system specifications.

## 表 1. Specifications for Data Acquisition AFE

| SERIAL NUMBER | PARAMETERS                                                 | DESCRIPTION                                                    | COMMENTS                                        |

|---------------|------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|

| 1             | ADC for measurement of analog inputs:  • Type • resolution | Delta-sigma, 24-bit                                            | Measurement accuracy ±0.5%                      |

| 2             | Number of analog inputs                                    | Eight, two-chained, 4-channel ADCs                             | Both ADCs are synchronized with a common clock. |

| 3             | Non-isolated voltage input range                           | 5 to 300 V with resistor divider and fixed-<br>gain amplifier  | Measurement accuracy ±0.5%                      |

| 4             | looloted voltage input range                               | 10- to 270-V AC AMC1301 isolation (reinforced) amplifier based | Measurement accuracy ±0.5%                      |

| 4             | Isolated voltage input range                               | 10- to 270-V AC AMC1200 isolation (basic) amplifier based      | Measurement accuracy ±0.5%                      |

| 5             | Current input measurement range                            | 0.25- to 100-A AC with fixed-gain amplifier                    | Measurement accuracy<br>±0.5%                   |

| 6             | ADC clock                                                  | 16.384-MHz oscillator with two output clock buffer             | _                                               |

System Overview www.ti.com.cn

## 表 1. Specifications for Data Acquisition AFE (continued)

| SERIAL NUMBER | PARAMETERS                       | DESCRIPTION                                        | COMMENTS                                                                                                              |

|---------------|----------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 7             | Reference                        | Internal:                                          | On power up, ADC defaults to external reference.                                                                      |

| 8             | Power supply for AFE             | Positive     Digital: 3.3 V     Analog: 5 V, 2.5 V | Analog input voltage: VAVDD to VAVSS +5 V is used for unipolar input. VAVDD to VGND +2.5 V is used for bipolar input. |

|               |                                  | Negative • Analog: -5 V, -2.5 V                    | VAVSS to VGND -2.5 V is used for bipolar input.                                                                       |

| 9             | Isolated power                   | Positive • Analog : 5 V                            | _                                                                                                                     |

| 10            | Interface to MCU for delta-sigma | SPITM                                              | See 3 节 for connection details.                                                                                       |

## 1.8 Block Diagram

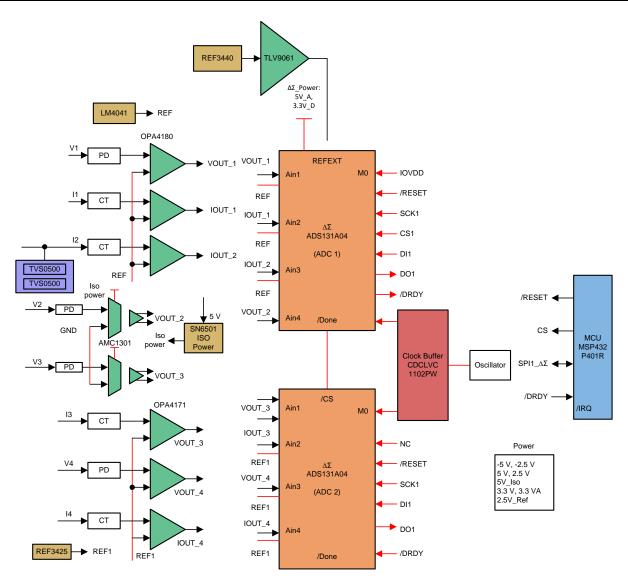

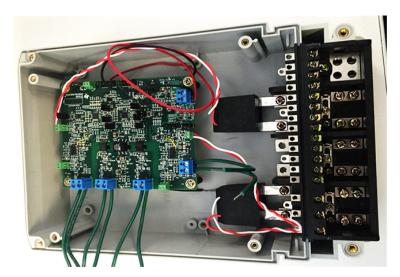

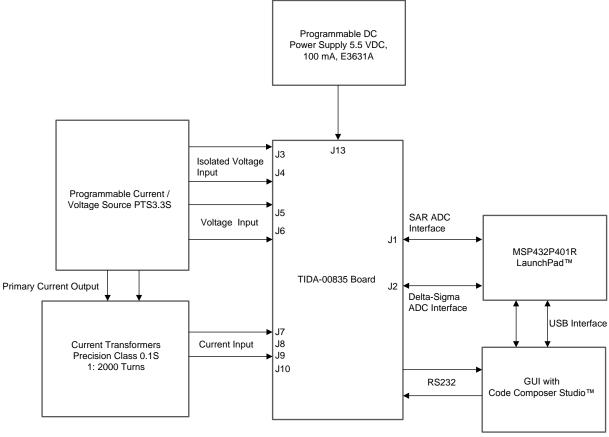

The high-performance AC analog input data acquisition AFE (see ②) has two 24-bit, delta-sigma ADCs chained to measure up to eight analog inputs. Potential dividers are provided to directly connect the AC voltage up to 300 V. Using isolation amplifiers provides the option to measure isolated voltage. The current and isolated voltage inputs have a fixed-gain front-end amplifier for adjusting the current measurement range, and the output of the amplifier is connected to the ADCs. The voltage and current inputs are measured as pseudo-differential inputs, and the voltage inputs from the isolation amplifier are measured as differential input. The positive and negative power supply required for the ADCs operation is generated from a single DC input, and provision to configure the power supply based on the input configuration is provided. Isolated power required for the operation of the isolation amplifier is also generated onboard.

www.ti.com.cn System Overview

图 2. TIDA-00835 Block Diagram

#### 1.8.1 Delta-Sigma ADC for Measurement

ADS131A04 is a 24-bit, four-channel, simultaneous-sampling differential ADC, used for measuring the analog input accurately over a wide range. Two ADCs are chained to be able to measure up to eight channels. A common clock oscillator of 16.384-MHz frequency and clock buffer CDCLVC1102PW are used for synchronizing the chained ADCs. The ADC analog power input is configurable from 0 to 5 V or ±2.5 V, based on the application and the input configuration. The isolated voltage output is connected differentially to the ADC. The current and non-isolated voltage gain amplifier outputs are connected in a pseudo-differential input configuration to the ADCs.

#### 1.8.1.1 ADC Interface to MCU—MSP432P401R

Provision to interface the ADS131A04 to the MSP432P401R LaunchPad<sup>™</sup> is provided onboard. The SPI signals the ADC reset, and the ADC data ready signals are interfaced to the MSP432<sup>™</sup> LaunchPad. The ADC IOVDD is configured as asynchronous interrupt mode for communicating with the MSP432 MCU.

System Overview www.ti.com.cn

In applications requiring higher memory for processing, MSP432P411Y SimpleLink Ultra-Low-Power 32-Bit Arm Cortex-M4F MCU with Precision ADC, 1MB Flash and 256KB RAM or MSP432P4011 SimpleLink Ultra-Low-Power 32-Bit Arm Cortex-M4F MCU with Precision ADC, 2MB Flash and 256KB RAM can be considered.

## 1.8.2 Signal Conditioning

#### 1.8.2.1 Current and Non-Isolated Voltage Inputs (With Potential Divider)

The current inputs are connected to an external current transformer of accuracy class 0.1, and the secondary output is connected to the AFE. The transformer has a turns ration of 2000. The secondary of the current transformer is differentially connected to the signal conditioning circuit. The gain is provided using an accurate op amp OP4180 or OPA4171. The output of the gain amplifier is a single-ended output connected to the delta-sigma ADC.

AC voltage input up to 300 V can be directly connected to the AFE. The AFE has an onboard potential divider which divides the 300-V AC input into less than 1.5 V. An amplifier is used to provide a fixed gain and the output of the amplifier is connected to the ADC.

#### 1.8.2.2 Isolated Voltage Input Using AMC1301

In applications which need reinforced isolation, TI recommends the AMC1301. The voltage input is applied across a potential divider and the potential divider output is connected to the AMC1301. The AMC1301 has an input range of ±250 mV. The output has a common-mode shift of 1.42 V with a 5-V supply and ×8.2 gain. The output of the AMC1301 is differentially connected to the ADC. The AMC1301 can be used in any of the ADS131A04 ADC configurations as follows:

- 0- to 5-V analog input

- ±2.5-V analog input

The AMC1301 output can also be interfaced to the MSP432 differential ADC input for cost optimized applications.

Alternatively in application with requirement for measuring higher input voltages, ISO224 ±12V Reinforced Isolated Amplifier for Voltage Sensing can be considered.

Find more information at the device's product page: http://www.ti.com/product/ISO224

#### 1.8.2.3 Reference

The ADC internal reference is 2.442 V or 4 V. The ADC provides a reference output, which can be used for the AFE signal conditioning. The ADC reference is by default configured for external reference. The device must be configured to internal reference for the reference output to be active. Alternatively, for improved performance, an external 2.5-V or 4-V reference can be used to maximize dynamic range.

#### 1.8.2.4 Analog Inputs Protection

The current inputs are protected against sensor opening by using two parallel resistors and TVS. Two of the TVS0500 connected back-to-back are used for overvoltage protection. The voltage inputs are protected for overvoltage, and multiple resistors are used as potential dividers for improved reliability. The potential divide input to the isolation amplifier is also protected for overvoltage. Additionally, the isolation amplifiers are protected for overvoltage.

www.ti.com.cn System Overview

## 1.8.3 Power Supply

#### 1.8.3.1 Non-Isolated Power

The ADS131A04 has flexible analog power-supply input options for operation as follows:

Unipolar supply: 3.3 to 5.5 V

Bipolar supply: ±2.5 V

Digital supply: 1.65 to 3.6 V

The required power supplies are generated from a single 5.5-V input. The positive voltages generated are 5 V, 3.3 V, and 2.5 V, and the negative voltages generated are –5 V and –2.5 V. These voltages provide flexibility to operate the ADC in any required input configurations.

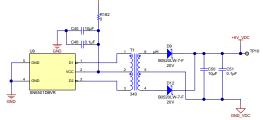

#### 1.8.3.2 Isolated Power

The isolation amplifier operates with 5 V on the analog input side. The isolated power supply required is generated from 5 V on the digital side. The required isolated power is generated using the SN6501 transformer driver and LDO. The transformer for the isolated power has also been chosen with a dielectric voltage of  $> 5 \text{ kV}_{\text{RMS}}$ .

Alternatively DCH010505S or DCH010505D Miniature, 1W, 3kVDC Isolated DC/DC Converters can be considered which simplifies the isolated power supply design.

Find more information at the device's product page: http://www.ti.com/product/DCH010505S

## 2 System Design Theory

## 2.1 Delta-Sigma ADC for Analog Input Measurement

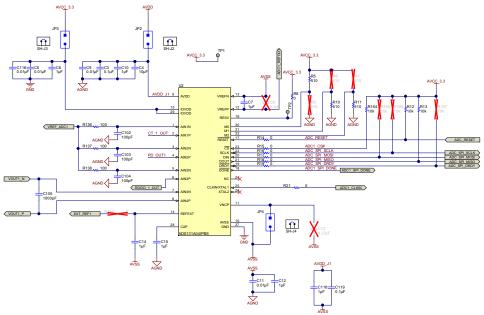

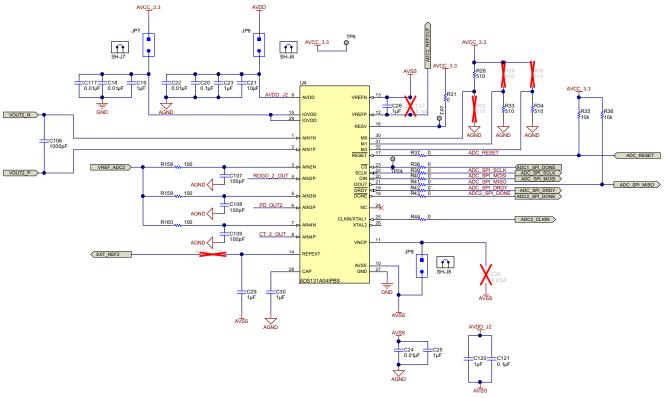

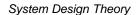

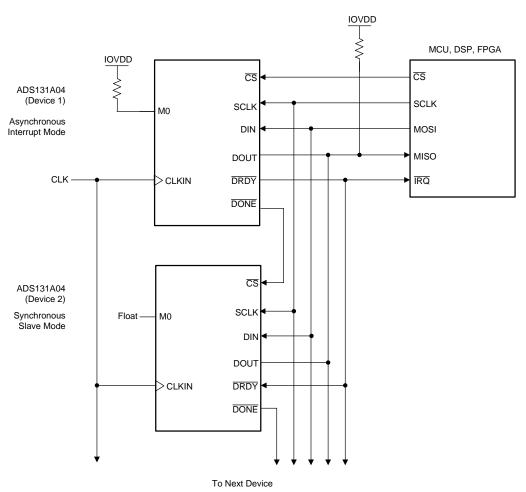

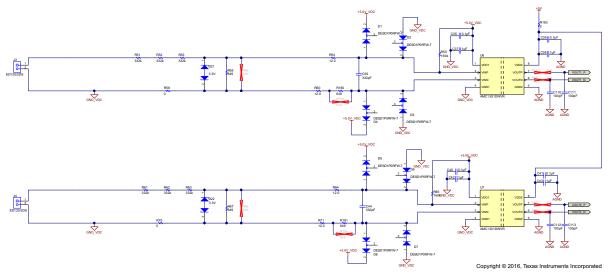

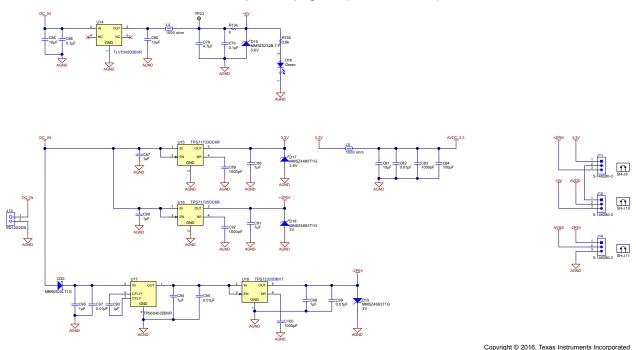

图 3 and 图 4 show two ADS131A04 devices in a chain configuration interfaced to the MCU.

Copyright © 2016, Texas Instruments Incorporated

## 图 3. Delta-Sigma ADC1 Configuration

Copyright © 2016, Texas Instruments Incorporated

图 4. Delta-Sigma ADC2 Configuration

www.ti.com.cn System Design Theory

Two ADS131A04 ADCs are chained in this TI Design. The following inputs are connected:

- Current input

- Non-isolated voltage inputs

- Isolated amplifier output (isolated voltage)

The current inputs and the non-isolated voltage inputs are applied in a pseudo-differential configuration. The isolated voltage inputs are applied as differential inputs to the ADC. The ADC has an internal reference. The ADC is configured to use the internal ADC, and an external clock input is applied for operation.

Jumpers are provided for the following:

AVDD: JP2 and JP6AVCC: JP7 and JP3

Charge pump disable: JP4 and JP8

In the current design configuration the charge pump is disabled by mounting the jumpers. The power supply jumpers must also be mounted for proper operation.

For unipolar mode operation, an input of 0 to 5 V can be applied, and for bipolar input an ±2.5-V input can be applied. The M0, M1, and M2 pins are used to configure the ADC. The ADC is configured in asynchronous Interrupt mode in this design. Two devices have been chained to achieve eight inputs.

## 2.1.1 Delta-Sigma ADC—ADS131A04

The ADS131A04 is a four-channel, simultaneously sampling, 24-bit, delta-sigma ADC. The wide dynamic range, scalable data rates and internal fault monitors make the ADS131A04 ideally-suited for energy monitoring, protection, and control applications. Flexible power-supply options are available to maximize the effective number of bits (ENOB) for high dynamic range applications. Asynchronous and synchronous master and slave interface options are available, providing ADC configuration flexibility when chaining multiple devices in a single system.

#### Features:

- · Four simultaneously sampling differential inputs

- Data rates up to 128 kSPS

- Noise performance

- Single-channel accuracy better than 0.1% at 10000:1 dynamic range

- ENOB: 19.1 bits at 8 kSPS

- THD: –100 dB at 50 Hz and 60 Hz

- Integrated negative charge pump

- Flexible analog power-supply operation

- Using negative charge pump: 3.0 to 3.45 V

- Unipolar supply: 3.3 to 5.5 V

- Bipolar supply: ±2.5 V

- Digital supply: 1.65 to 3.6 V

- Low-drift internal voltage reference: 4 ppm/°C

- ADC self checks

- Cyclic redundancy check (CRC) and hamming code error correction on communications

- Multiple SPI data interface modes

- Asynchronous interrupt

- Synchronous master and slave

- Package: 32-pin TQFP

- Operating temperature range: –40°C to 125°C

Find more information at the device's product page: http://www.ti.com/product/ADS131A04

注: The ADS131A02 2-Channel AFE can be considered in single-phase applications.

#### 2.1.2 Clock Buffer CDCLVC1102PW

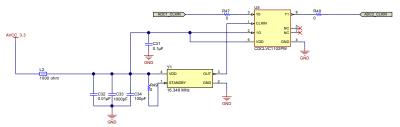

Two ADCs are used in this TI Design. To synchronize the sampling of the two ADCs the same clock is applied to both. A 16.348-MHz oscillator is to generate the clock. The clock output is buffered using a clock buffer (see § 5).

Copyright © 2016, Texas Instruments Incorporated

图 5. Clock Buffer for Delta-Sigma ADCs

The CDCLVC11xx is a modular, high-performance, low-skew, general-purpose clock buffer family from TI. Seven different fan-out variations, 1:2 to 1:12, are available. All of the devices are pin compatible to each other for easy handling. All family members share the same high-performing characteristics such as low-additive jitter, low skew, and wide operating temperature range.

#### Features:

- High-performance LVCMOS clock buffer family

- Very low pin-to-pin skew < 50 ps</li>

- Very low additive jitter < 100 fs</li>

- Supply voltage: 3.3 V or 2.5 V

- f<sub>max</sub> = 250 MHz for 3.3 V

- f<sub>max</sub> = 180 MHz for 2.5 V

- Operating temperature range: –40°C to 85°C

表 2 lists the CDCLVC1102PWR features.

## 表 2. CDCLVC1102PWR Features

| PARAMETER                 | DETAILS                             |

|---------------------------|-------------------------------------|

| Part number               | CDCLVC1102PWR                       |

| Description               | IC CLK BUFFER 1:2 250-MHZ<br>8TSSOP |

| Туре                      | Fan-out buffer (distribution)       |

| Number of circuits        | 1                                   |

| Ratio—input:output        | 1:2                                 |

| Differential—input:output | No / no                             |

| Input                     | LVCMOS                              |

| Output                    | LVCMOS                              |

| Voltage supply            | 2.3 to 3.6 V                        |

| Mounting type             | Surface mount                       |

| Supplier device package   | 8-TSSOP                             |

Find more information at the device's product page: http://www.ti.com/product/CDCLVC1102

## 2.1.3 Delta-Sigma to ADC Interface to MCU—MSP432P401R

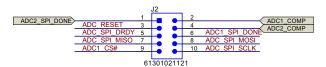

Delta-sigma ADCs are interfaced to the MCU MSP432F401R through the SPI. The interface signals required from the ADC are terminated to connector J2. Resetting the ADC is critical. Follow the instructions in Section 9.4.5 Reset (RESET) of the data sheet (SBAS590B) to reset the ADC during initialization. 8 6 shows the Delta-Sigma ADC to MSP432 interface connector.

Copyright © 2016, Texas Instruments Incorporated

## 图 6. Delta-Sigma ADC to MSP432 Interface Connector

The MSP432P401x device family is TI's latest addition to its portfolio of efficient ultra-low-power mixed-signal MCUs. The MSP432P401x family features the ARM Cortex-M4 processor in a wide configuration of device options, including a rich set of analog, timing, and communication peripherals, thereby catering to a large number of application scenarios where both efficient data processing and enhanced low-power operation are paramount.

#### Features:

- Core

- ARM 32-bit Cortex-M4F CPU with floating-point unit and memory protection unit

- Frequency up to 48 MHz

- Performance benchmark:

- 1.196 DMIPS/MHz (Dhrystone 2.1)

- 3.41 CoreMark/MHz

- Energy Benchmark: 167.4 ULPBench score

- Memory

- Up to 256KB of flash main memory (simultaneous read and execute during program or erase)

- 16KB of flash information memory

- Up to 64KB of SRAM (including 8KB of backup memory)

- 32KB of ROM with MSPWare driver libraries

- · Operating Characteristics

- Wide supply voltage range: 1.62 to 3.7 V

- Temperature range (ambient): –40°C to 85°C

- Serial communication

- Up to four eUSCI\_A modules

- UART with automatic baud-rate detection

- · IrDA encode and decode

- SPI (up to 16 Mbps)

- Flexible I/O features

- Ultra-low-leakage I/Os (±20-nA maximum)

- Up to four high-drive I/Os (20-mA capability)

- All I/Os have capacitive touch capability

- Up to 48 I/Os with interrupt and wake-up capability

- Up to 24 I/Os with port mapping capability

- Eight I/Os with glitch filtering capability

- Advanced low-power analog features

- 14-bit, 1-MSPS SAR ADC

- Internal voltage reference with 10-ppm/°C typical stability

- Two analog comparators

Find more information at the device's product page: http://www.ti.com/product/MSP432P401R

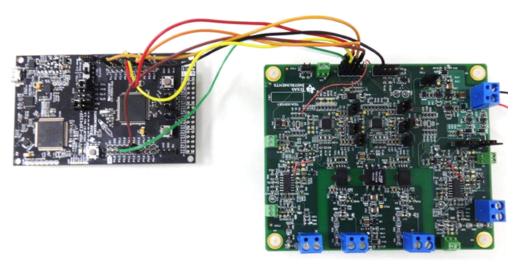

#### 2.1.3.1 MSP432P401R LaunchPad

The MSP432P401R LaunchPad lets users develop high-performance applications which benefit from low-power operation. The LaunchPad features the MSP432P401R, which includes the following:

- 48-MHz ARM Cortex-M4F

- 95 µA/MHz active power

- 850-nA RTC operation

- 14-bit 1-MSPS differential SAR ADC

- AES256 accelerator

This LaunchPad includes an onboard emulator with EnergyTrace<sup>™</sup>+ technology, which means users can program and debug their projects without the need for additional tools, while also measuring total system energy consumption. All pins of the MSP-EXP432P401R device are fanned out for easy access.

## 2.1.4 Chaining of Multiple Delta-Sigma ADCs

In this TI Design, two ADS131A04 devices have been chained to increase the number of analog channels. The ADS131A04 lets the designer add channels by adding an additional device to the bus. The first device in the chain can be configured using any of the interface modes. All subsequent devices must be configured in synchronous slave mode. In all cases, however, the chain of ADS131A04 devices appear as a single device with extra channels, with the exception that each device sends individual status and data integrity words. In this manner, no additional pins on the host are required for an additional device on the chain. The only special provisions required in the interface is to extend the frame to the appropriate length.

The first device is configured in asynchronous interrupt mode.

7 shows a multiple-device configuration where the first device is configured in asynchronous interrupt mode as noted by the state of the M0 pin. The second ADS131A0x device and any additional devices are configured in synchronous slave mode.

www.ti.com.cn System Design Theory

Copyright © 2016, Texas Instruments Incorporated

## 图 7. Multiple Device Configuration Using Asynchronous Interrupt Mode

See Section 10.1.3 of the data sheet Chaining for Multiple Device Configuration (SBAS590) for more information on chaining multiple devices.

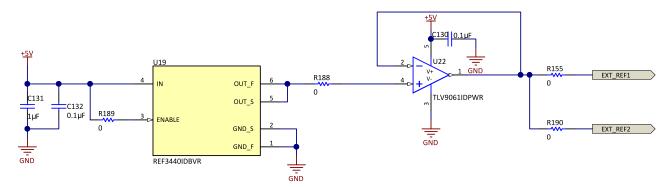

#### 2.1.5 Connecting External Reference to ADC1 and ADC2

External reference of 2.5 V or 4 V can be connected to the ADC based on the required input range. Provision to connect REF3425 or REF3440 has been provided in the design. The output of the reference is buffered using TLV9061 operational amplifiers and connected to ADC1 and ADC2.

图 8. External Reference for ADC1 and ADC2

The REF34xx is a low temperature drift (6 ppm/°C), low-power, high-precision CMOS voltage reference, featuring  $\pm 0.05\%$  initial accuracy, low operating current with power consumption less than 95  $\mu$ A. This device also offers very low output noise of 3.8  $\mu$ Vp-p /V, which enables its ability to maintain high signal integrity with high-resolution data converters in noise critical systems. Stability and system reliability are further improved by the low output-voltage hysteresis of the device and low long-term output voltage drift.

Find more information at the device's product page: http://www.ti.com/product/REF3440 and http://www.ti.com/product/REF3425

TLV9061, is a single (1.8 V to 5.5 V) 10MHz operational amplifiers (op amps) with rail-to-rail input- and output-swing capabilities. These devices are highly cost-effective solutions for applications where low-voltage operation, a small footprint, and high capacitive load drive are required.

Find more information at the device's product page: http://www.ti.com/product/TLV9061

#### 2.2 Signal Conditioning With Op-amp OPA4180 or OPA4171

The Signal condition for the voltage and current inputs can be implemented using OPA4180 or OPA4171.

The OPA4180 operational amplifiers use zero-drift techniques to simultaneously provide low-offset voltage (75  $\mu$ V), and near zero-drift over time and temperature. These miniature, high-precision, low-quiescent current amplifiers provide high-input impedance and rail-to-rail output swing within 18 mV of the rails. The input common-mode range includes the negative rail. Either single or dual supplies can be used in the range of 4 to 36 V ( $\pm$ 2 to  $\pm$ 18 V). The quad is offered in SOIC-14 and TSSOP-14 packages. All versions are specified for operation from  $-40^{\circ}$ C to  $105^{\circ}$ C.

#### Features:

Low offset voltage: 75 μV (maximum)

Zero-drift: 0.1 µV / °C

Low noise: 10 nV / √Hz

Very low 1 / f noise

Excellent DC precision:

PSRR: 126 dBCMRR: 114 dB

Open-loop gain (AOL): 120 dB

Quiescent current: 525 µA (maximum)

www.ti.com.cn System Design Theory

- Wide supply range: ±2 to ±18 V

- Rail-to-rail output: input includes negative rail

- Low bias current: 250 pA (typical)

- · RFI filtered inputs

Find more information at the device's product page: http://www.ti.com/product/OPA4180

Alternatively, for cost-sensitive applications, the OPA4171 can be used. The OPA4171 is a 36-V, single-supply, low-noise operational amplifier with the ability to operate on supplies ranging from 2.7 V (±1.35 V) to 36 V (±18 V). These devices offer low offset, drift, and bandwidth with low quiescent current. The OPA4171 family is specified from 2.7 to 36 V. Input signals beyond the supply rails do not cause phase reversal.

Find more information at the device's product page: http://www.ti.com/product/OPA4171

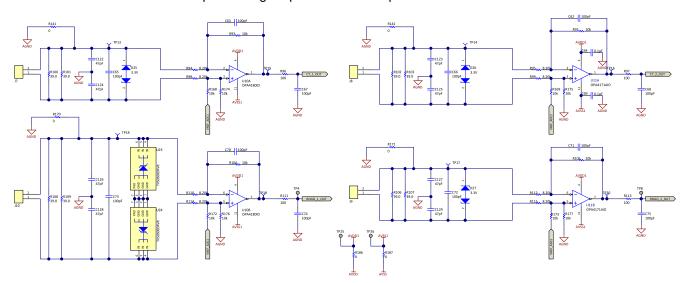

#### 2.2.1 Current Inputs

图 9 shows the current input scaling amplifiers for four input currents.

图 9. Current Input Connectors with Gain Amplifiers and Flat clamp TVS protection

This design provides provision to measure up to four current inputs. Two current channels are provided for each ADC. An external CT is used to step down the primary current. The CT ratio used in this design is 1:2000. The secondary current is connected as input to a fixed-gain amplifier. The amplifier is configured in differential mode and depending on the application and the input voltage range the gain can be configured. The output of the amplifier is connected to the delta-sigma ADC for measurement. The burden required for converting the current input to voltage is provided onboard.

表 3 lists the current input range calculation.

表 3. Calculation of Current Input Range

| CURRENT MEASUREMENT | VALUE   | UNIT         |

|---------------------|---------|--------------|

| Burden              | 19.5000 | Ω            |

| Gain                | 1.2195  | <del>-</del> |

| RF                  | 10.0000 | ΚΩ           |

| CURRENT MEASUREMENT | VALUE     | UNIT    |

|---------------------|-----------|---------|

| RI                  | 8.2000    | ΚΩ      |

| Op amp rail         | 2300.0000 | mV      |

| Op amp output       | 1886.0000 | mV (PK) |

| CT sec current      | 68.4002   | mA      |

| CT ratio            | 2000      | _       |

| Primary current     | 136.8005  | A       |

表 3. Calculation of Current Input Range (continued)

The output of the TIDA-00777 can be connected to the current inputs designated Rogo\_1\_out and Rogo2\_Out. The TIDA-00777 output is compatible to the ADS131A04 output when configured for a 2.442-V reference. To connect the Rogowski inputs, make the following changes:

- 1. Remove R111, R113, C74, and C75.

- 2. Connect current inputs to TP4 and TP6.

注: Ensure the ground of the two boards are connected together.

The current transformer inputs are protected against overvoltage using a TVS diode. An alternative approach for protection is to use the flat-clamp TVS diode TVS0500 connected in back-to-back configuration for bi-directional protection.

Find more information at the device's product page: http://www.ti.com/product/TVS0500

#### 2.2.2 Non-Isolated Voltage Inputs (With Potential Divider)

10 shows voltage input scaling amplifiers for two non-isolated voltage inputs.

Copyright © 2016, Texas Instruments Incorporated

图 10. Voltage Input Signal Conditioning

This design provides the option to measure two non-isolated voltage inputs. One input is provided on each ADC. The AC input can be directly applied across the potential divider provided onboard. The output of the potential divider is connected to a fixed-gain amplifier. The amplifier is configured in differential mode and depending on the application and the input voltage range, the gain can be configured. The output of the gain amplifier is connected to the ADC input.

表 4 lists the input range calculation for the non-isolated voltage input.

表 4. Input Range for Non-Isolated Voltage Input

| VOLTAGE MEASUREMENT _PD | VALUE    | UNIT |

|-------------------------|----------|------|

| PD                      | 993.3000 | ΚΩ   |

| Gain                    | 1.2195   | _    |

www.ti.com.cn System Design Theory

| VOLTAGE MEASUREMENT _PD | VALUE     | UNIT     |

|-------------------------|-----------|----------|

| RF                      | 10.0000   | ΚΩ       |

| RI                      | 8.2000    | ΚΩ       |

| Op amp rail             | 2300.0000 | mV       |

| Op amp input            | 1886.0000 | mV (PK)  |

| Op amp input            | 1333.8048 | mV (RMS) |

| Voltage division ratio  | 301.0000  | _        |

| Primary voltage         | 401.4752  | V        |

表 4. Input Range for Non-Isolated Voltage Input (continued)

注: The OPA4188 can be consider for applications requiring improved accuracy performance.

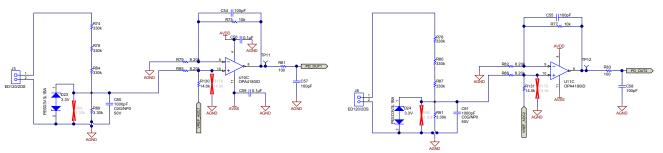

#### 2.2.3 Isolated Voltage Input Using AMC1301

图 11 shows the isolation amplifiers for voltage input.

图 11. Isolation Amplifier With Input Protection and Potential Divider

The AMC1301 is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 7 kV $_{PEAK}$  according to VDE-V 0884-10 and UL1577. Used with isolated power supplies, this device prevents noise currents on a high common-mode voltage line from entering the local ground and interfering with or damaging sensitive circuitry. The integrated common-mode overvoltage and missing high-side supply voltage detection features of the AMC1301 simplify system-level design and diagnostics. The AMC1301 is fully specified over the extended industrial temperature range of  $-40^{\circ}$ C to  $125^{\circ}$ C and is available in a wide-body, 8-pin, SOIC (DWV) package.

#### Features:

- ±250-mV input voltage range optimized for current measurement using shunt resistors

- Low offset error and drift:

- ±200 µV (maximum) at 25°C

- ±3  $\mu$ V/°C (maximum)

- Fixed gain: 8.2

- Very low gain error and drift:

- ±0.3% (maximum) at 25°C

- ±50 ppm/°C (maximum)

- · Very low nonlinearity and drift:

- 0.03% (maximum)

- 1 ppm/°C (typical)

- 3.3-V operation on high-side and low-side

- System-level diagnostic features

- Safety and regulatory approvals:

- 7000-V<sub>PK</sub> reinforced isolation per DIN V VDE-V 0884-10 (VDE-V 0884-10): 2006-12

- 5000-V<sub>RMS</sub> isolation for 1 minute per UL1577

- CAN/CSA No. 5A-component acceptance service notice, IEC 60950-1, and IEC 60065 end equipment standards

- Fully specified over the extended industrial temperature range

Find more information at the device's product page: http://www.ti.com/product/AMC1301

www.ti.com.cn System Design Theory

This design provides the option to measure two isolated voltage inputs. The isolation amplifier is used to provide the required analog isolation. The isolator provides reinforced isolation with a fixed gain of  $\times 8.2$ . The common-mode output of the isolation amplifier is 1.44 V. The advantage of the AMC1301 is that it can be used with the ADC configured for unipolar inputs (0 to 5 V) and bipolar inputs  $\pm 2.5$  V. The AMC1301 can also be used with a 2.442-V and 4-V reference. The AC input is specified to be linear up to a  $\pm 250$ -mV input. The output of isolation amplifier is differentially connected to the ADC. The required protection for input overvoltage is provided.

表 5 lists the input range calculation for the AMC1301.

| VOLTAGE MEASUREMENT_ISO Amp_AMC1301 | VALUE     | UNIT |

|-------------------------------------|-----------|------|

| PD                                  | 996.6500  | ΚΩ   |

| Gain                                | 8.2000    | _    |

| Output Peak                         | 2.0500    | _    |

| Output RMS                          | 1.4498    | V    |

| Input                               | 0.1768    | V    |

| Voltage division ratio              | 1533.0000 | _    |

| Primary voltage                     | 271.0396  | V    |

表 5. Input Voltage Range Calculation for AMC1301

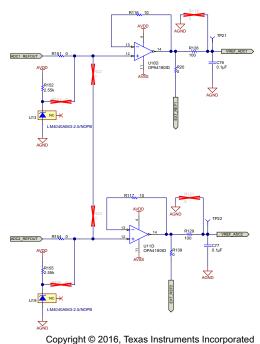

### 2.2.4 Reference—LM4040 and Buffer (For Common-Mode DC Level Shift)

The reference and buffers are used to provide the required DC common-mode level shifting for using the ADC range (see 3 12).

图 12. Reference With Buffer for Gain Amplifiers

The LM4040-N precision voltage reference is available in an SOT-23 surface-mount package. The advanced design of the LM4040-N eliminates the need for an external stabilizing capacitor while ensuring stability with any capacitive load, making the LM4040-N easy to use. The minimum operating current increases from 60  $\mu$ A for the 2.5-V LM4040-N to 100  $\mu$ A for the 10-V LM4040-N. All versions have a maximum operating current of 15 mA. The LM4040-N uses a fuse and Zener-zap reverse breakdown voltage trim during wafer sort to ensure that the prime parts have an accuracy of better than ±0.1% (A grade) at 25°C. Curvature correction for bandgap reference temperature drift and low dynamic impedance ensure stable reverse breakdown voltage accuracy over a wide range of operating temperatures and currents.

#### Features:

- No output capacitor required

- Tolerates capacitive loads

- Key specifications (2.5-V LM4040-N)

- Output voltage tolerance (A grade, 25°C): ±0.1% (maximum)

- Low output noise (10 Hz to 10 kHz): 35 μV<sub>RMS</sub> (typical)

- Wide operating current range: 60 μA to 15 mA

- Low temperature coefficient: 100 ppm/°C (maximum)

- 表 6 lists the LM4040 external reference specifications.

表 6. LM4040 Features

| PARAMETER                        | DETAILS               |

|----------------------------------|-----------------------|

| Part number                      | LM4040AIM3-2.5 / NOPB |

| Reference type                   | Shunt                 |

| Output type                      | Fixed                 |

| Voltage output (minimum / fixed) | 2.5 V                 |

| Current output                   | 15 mA                 |

| Tolerance                        | ±0.1%                 |

| Temperature coefficient          | 100 ppm/°C            |

| Noise: 10 Hz to 10 kHz           | 35 μVrms              |

| Current cathode                  | 65 µA                 |

| Supplier device package          | SOT-23-3              |

The delta-sigma ADC operates with unipolar input or bipolar inputs. For bipolar inputs the reference is zero, and for unipolar input the reference must be shifted—typically, the input range is 2. The amplifier outputs are level shifted depending on the input configuration. The references can be configured as follows:

- ADC REFP out for DC level shifting the analog input

- R151 and R154 mounted

- R153 and R156 not mounted

- External reference for DC level shifting the analog input

- R153 and R156 mounted

- R151 and R154 not mounted

Based on the power supply configuration, the reference output to the op amp gain amplifier can be selected as follows:

www.ti.com.cn

- 0-V reference

- R118 and R121 mounted

- R126 and R129 not mounted

- 2.5-V reference

- R126 and R129 mounted

- R118 and R121 not mounted

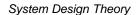

## 2.3 Power Supply

The delta-sigma ADC has flexible analog power-supply options for operation as follows:

Unipolar supply: 3.3 to 5.5 V

Bipolar supply: ±2.5 V

Digital supply: 1.65 to 3.6 V

The power supply required to operate the ADC is provided onboard (see 🖺 13). The power supply operates from a single positive input voltage. The required negative power supply is generated using higherficiency input inverters and negative LDOs. The required overvoltage protection has been provided using Zener diodes. Jumpers J11, J12, and J14 are used to configure the ADC analog supply input range.

Alternatively LM27762 Low-Noise Positive- and Negative-Output Charge Pump With Integrated LDO can be considered simplifying power supply design.

Find more information at the device's product page: http://www.ti.com/product/LM27762

图 13. Onboard Positive and Negative Power Supply With Protection

#### 2.3.1 Non-Isolated Power

## 2.3.1.1 +5 V (U14)

The TLV704 series of LDO regulators are ultra-low quiescent current devices designed for extremely power-sensitive applications. Quiescent current is virtually constant over the complete load current and ambient temperature range. These devices are an ideal power-management attachment for low-power MCUs, such as the MSP430. The TLV704 operates over a wide operating input voltage of 2.5 to 24 V. Therefore, the device is an excellent choice for battery-powered systems and industrial applications that undergo large line transients.

#### Features:

- Wide input voltage range: 2.5 to 24 V

- Low 3.2-µA quiescent current

- Ground pin current: 3.4 μA at 100-mA I<sub>OUT</sub>

- Stable with a low-ESR, 1-μF, typical output capacitor

www.ti.com.cn System Design Theory

#### 表 7 lists the TLV70450 features.

表 7. TLV70450 LDO Features

| PARAMETER                 | DETAILS          |

|---------------------------|------------------|

| Part number               | TLV70450DBVR     |

| Regulator topology        | Positive fixed   |

| Voltage output            | 5 V              |

| Current output            | 150 mA           |

| Voltage dropout (typical) | 0.85 V at 100 mA |

| Number of regulators      | 1                |

| Voltage input             | Up to 24 V       |

| Current limit (minimum)   | 160 mA           |

| Operating temperature     | -40°C to 125°C   |

| Supplier device package   | SOT-23-5         |

## 2.3.1.2 +3.3 V (U15)

The TPS717xx family of LDOs, low-power linear regulators, offers very high-power supply rejection (PSRR) while maintaining very low 45- $\mu$ A ground current in an ultra-small, 5-pin, SOT package. The family uses an advanced BiCMOS process and a PMOS pass device to achieve fast start-up, very low noise, excellent transient response, and excellent PSRR performance. The TPS717xx is stable with a 1- $\mu$ F ceramic output capacitor and uses a precision voltage reference and feedback loop to achieve a worst-case accuracy of 3% overall load, line, process, and temperature variations.

#### Features:

- Input voltage: 2.5 to 6.5 V

- Available in multiple output versions:

- Fixed output with voltages from 0.9 to 5 V

- Adjustable output voltage from 0.9 to 6.2 V

- · Ultra-high PSRR:

- 70 dB at 1 kHz

- 67 dB at 100 kHz

- 45 dB at 1 MHz

- Excellent load and line transient response

- Very LDO: 170 mV typical at 150 mA

- Low noise: 30 μV<sub>RMS</sub> typical (100 Hz to 100 kHz)

表 8 lists the TPS71733 LDO features.

表 8. TPS71733 LDO Features

| PARAMETER                 | DETAILS          |

|---------------------------|------------------|

| Part number               | TPS71733DCKR     |

| Regulator topology        | Positive fixed   |

| Voltage output            | 3.3 V            |

| Current output            | 150 mA           |

| Voltage dropout (typical) | 0.17 V at 150 mA |

表 8. TPS71733 LDO Features (continued)

| PARAMETER               | DETAILS        |

|-------------------------|----------------|

| Number of regulators    | 1              |

| Voltage input           | Up to 6.5 V    |

| Current limit (minimum) | 200 mA         |

| Operating temperature   | -40°C to 125°C |

| Supplier device package | SC-70-5        |

## 2.3.1.3 +2.5 V (U16)

The TPS717xx family of LDO, low-power linear regulators offers very high-power supply rejection (PSRR) while maintaining very low 45-µA ground current in an ultra-small, 5-pin SOT package. The family uses an advanced BiCMOS process and a PMOS pass device to achieve fast start-up, very low noise, excellent transient response, and excellent PSRR performance. The TPS717xx is stable with a 1-µF ceramic output capacitor and uses a precision voltage reference and feedback loop to achieve a worst-case accuracy of 3% over all load, line, process, and temperature variations.

#### **Features**

- Input voltage: 2.5 to 6.5 V

- Available in multiple output versions:

- Fixed output with voltages from 0.9 to 5 V

- Adjustable output voltage from 0.9 to 6.2 V

- Ultra-high PSRR:

- 70 dB at 1 kHz

- 67 dB at 100 kHz

- 45 dB at 1 MHz

- · Excellent load and line transient response

- Very LDO: 170 mV typical at 150 mA

- Low noise: 30 μV<sub>RMS</sub> typical (100 Hz to 100 kHz)

表 9 lists the TPS71725 LDO features.

表 9. TPS71725 LDO Features

| PARAMETERS              | DETAILS        |

|-------------------------|----------------|

| Part number             | TPS71725DCKR   |

| Regulator topology      | Positive fixed |

| Voltage output          | 2.5 V          |

| Current output          | 150 mA         |

| Number of regulators    | 1              |

| Voltage input           | 2.5 to 6.5 V   |

| Current limit (minimum) | 200 mA         |

| Operating temperature   | -40°C to 125°C |

| Mounting type           | Surface mount  |

## 2.3.1.4 -5 V (U17)

The TPS6040x family of devices generates an unregulated negative output voltage from an input voltage ranging from 1.6 to 5.5 V. The devices are typically supplied by a pre-regulated supply rail of 5 V or 3.3 V. Only three external 1- $\mu$ F capacitors are required to build a complete DC-DC charge pump inverter. The TPS6040x can deliver a maximum output current of 60 mA with a typical conversion efficiency of greater than 90% over a wide output current range.

#### Features:

- Inverts input supply voltage

- Up to 60-mA output current

- Only three small 1-µF ceramic capacitors needed

- Input voltage range from 1.6 to 5.5 V

- Device quiescent current typical 65 μA

- Integrated active Schottky diode for start-up into load

表 10 lists the TPS60403 features.

表 10. TPS60403 Inverter (Charge Pump) Features

| PARAMETERS                       | DETAILS                          |

|----------------------------------|----------------------------------|

| Part number                      | TPS60403DBVR                     |

| Function                         | Ratiometric                      |

| Output configuration             | Positive or negative             |

| Topology                         | Charge pump                      |

| Output type                      | Fixed                            |

| Number of outputs                | 1                                |

| Voltage input (minimum)          | 1.8 V                            |

| Voltage input (maximum)          | 5.25 V                           |

| Voltage output (minimum / fixed) | –Vin, 2Vin, Vin / 2              |

| Current output                   | 60 mA                            |

| Frequency switching              | 250 kHz                          |

| Synchronous rectifier            | No                               |

| Operating temperature            | -40°C to 125°C (T <sub>J</sub> ) |

## 2.3.1.5 -2.5 V ( U18)

The TPS723xx family of LDO negative voltage regulators offers an ideal combination of features to support low noise applications. These devices are capable of operating with input voltages from -10 to -2.7 V, and support outputs from -10 to -1.2 V. These regulators are stable with small, low-cost ceramic capacitors, and include enable (EN) and noise reduction (NR) functions. Thermal short circuit and overcurrent protections are provided by internal detection and shutdown logic. High PSRR (65 dB at 1 kHz) and low noise (60  $\mu$ V<sub>RMS</sub>) make the TPS723xx ideal for low-noise applications.

#### Features:

Ultra-low noise: 60 μV<sub>RMS</sub> typical

High PSRR: 65 dB typical at 1 kHz

LDO voltage: 280 mV typical at 200 mA, 2.5 V

Available in –2.5 V

Stable with a 2.2-μF ceramic output capacitor

Less than 2-μA typical quiescent current in shutdown mode

2% overall accuracy (line, load, and temperature)

Thermal and overcurrent protection

SOT23-5 (DBV) package

表 11 lists the TPS72325 features.

表 11. TPS72325 Features

| PARAMETERS                | DETAILS          |

|---------------------------|------------------|

| Part number               | TPS72325DBVT     |

| Regulator topology        | Negative fixed   |

| Voltage output            | -2.5 V           |

| Current output            | 200 mA           |

| Voltage dropout (typical) | 0.28 V at 200 mA |

www.ti.com.cn System Design Theory

| 表 11. TPS72325 Features (continued) | 表 11. | <b>TPS72325</b> | <b>Features</b> | (continued) |

|-------------------------------------|-------|-----------------|-----------------|-------------|

|-------------------------------------|-------|-----------------|-----------------|-------------|

| PARAMETERS              | DETAILS        |

|-------------------------|----------------|

| Number of regulators    | 1              |

| Voltage Input           | −10 to −1.2 V  |

| Current limit (minimum) | 300 mA         |

| Operating temperature   | -40°C to 125°C |

## 2.3.1.6 Power Supply Jumper Options

表 12 lists the power supply jumper options.

表 12. Power Supply Jumper Options

| CONNECTOR | 1-2           | 3-2        |

|-----------|---------------|------------|

| J11       | 3.3 V         | +2 P 5 V   |

| J12       | AVDD = 2.5 V  | AVDD = 5 V |

| J14       | AVSS = −2.5 V | AVSS = 0 V |

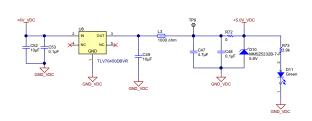

#### 2.3.1.7 Isolated Power

Copyright © 2016, Texas Instruments Incorporated

图 14. Isolated Power Supply for Isolation Amplifiers

The SN6501 is a monolithic oscillator and power-driver, specifically designed for small form factor, isolated power supplies in isolated interface applications. The device drives a low-profile, center-tapped transformer primary from a 3.3- or 5-V DC power supply. The secondary can be wound to provide any isolated voltage based on transformer turns ratio. The SN6501 consists of an oscillator followed by a gate drive circuit that provides the complementary output signals to drive the ground referenced N-channel power switches. The internal logic ensures break-before-make action between the two switches.

#### Features:

- Push-pull driver for small transformers

- Single 3.3- or 5-V supply

- High primary-side current drive:

- 5-V supply: 350 mA (maximum)

- 3.3-V supply: 150 mA (maximum)

- Low ripple on rectified output permits

- Small output capacitors

#### Small 5-pin SOT-23 package

Find more information at the device's product page: http://www.ti.com/product/SN6501

#### 2.4 Design Enhancements

#### 2.4.1 Sampling Rate

This TI design has been tested with the ADC configured to sample the analog input at 80 samples per cycle. ADC is capable of providing data rates up to 128 kSPS. There are 16 selectable oversampling ratio (OSR) options to optimize the converter for a specific data rate. Higher data rates are typically used in grid infrastructure applications that implement software re-sampling techniques to help with channel-to-channel phase adjustment for voltage and current. See Section 9.3.1, *Clock*, of the data sheet for more details.

## 2.4.2 Using External Reference With ADS131A04

The delta-sigma ADC has an internal reference of 2.442 V. The dynamic range can be increased by using an external reference of 2.5 V. Provision to provide an external reference input to the delta-sigma ADC is provided. In the ADS131A04 by default, the external reference is selected (INT\_REFEN = 0). If reference output is required for testing before interfacing to the MCU, a low cost reference can be used.

#### 2.4.3 Using 4-V Reference for Analog Input Measurement

The differential input voltage range for the ADS131A04 is –VREF / Gain to VREF / Gain. The internal reference can be programmed to either 2.442 V or 4 V. The dynamic range of the ADC can be improved by configuring VREF = 4 V, the VREF\_4 V bit can be set to 1 when VAVDD – VAVSS > 4.5 V. In this design the reference has been programmed to 2.442 V and tested. To use the 4 V reference the ADC must be configured to measure bipolar input.

By configuring VREF = 4 V the input range can be increased from  $\pm 2.442$  to  $\pm 4$  V which increases the AC input range by  $\times 1.65$  compared to VREF = 2.442 V. This configuration can be used when wider current ranges are required to be measured. The op amps used in the design can work for  $\pm 5$  V. In this design,  $\pm 5$ -V rails are available onboard. By making these simple changes in the design the input measurement range can be extended.

表 13 provides information to configure the power supply for different reference voltage configuration.

## 表 13. Changes for Reference Configuration

| REFERENCE | POPULATE                                                 | DEPOPULATE    |

|-----------|----------------------------------------------------------|---------------|

| 2.442 V   | R186 and R187                                            | _             |

| 4 V       | Use TP25 and TP26 to connect external voltage up to ±5 V | R186 and R187 |

#### 2.5 Board Design Guideline

## 2.5.1 Delta-Sigma ADC

Recommendations

- Partition the analog, digital, and power-supply circuitry into separate sections on the PCB.

- Use a single ground plane for analog and digital grounds.

- Place the analog components close to the ADC pins using short, direct connections.

- Keep the SCLK pin free of glitches and noise.

www.ti.com.cn System Design Theory

Verify that the analog input voltages are within the specified voltage range under all input conditions.

- Tie unused analog input pins to GND.

- Provide current limiting to the analog inputs in case overvoltage faults occur.

- Use a LDO regulator to reduce ripple voltage generated by switch-mode power supplies. This

reduction is especially true for AVDD where the supply noise can affect performance.

- Keep the input series resistance low to maximize THD performance.

- · Do not cross analog and digital signals.

- Do not allow the analog power supply voltages (AVDD AVSS) to exceed 3.6 V under any conditions, including during power up and power down when the negative charge pump is enabled.

- Do not allow the analog power supply voltages (AVDD AVSS) to exceed 6 V under any conditions, including during power up and power down when the negative charge pump is disabled.

- Do not allow the digital supply voltage to exceed 3.9 V under any conditions, including during power up

## 2.5.2 AMC1301

See the following sections in the data sheet for design and layout guidelines:

- Section 10 Power Supply Recommendations

- Section 11 Layout

#### 2.5.3 CDCLVC1102PW

See the following sections in the data sheet for

- Section 11 Power Supply Recommendations

- Section 12 Layout

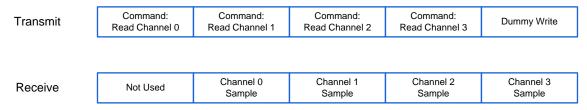

#### 2.6 Software Implementation

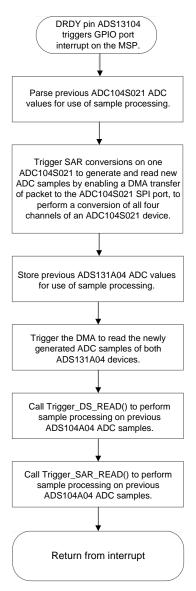

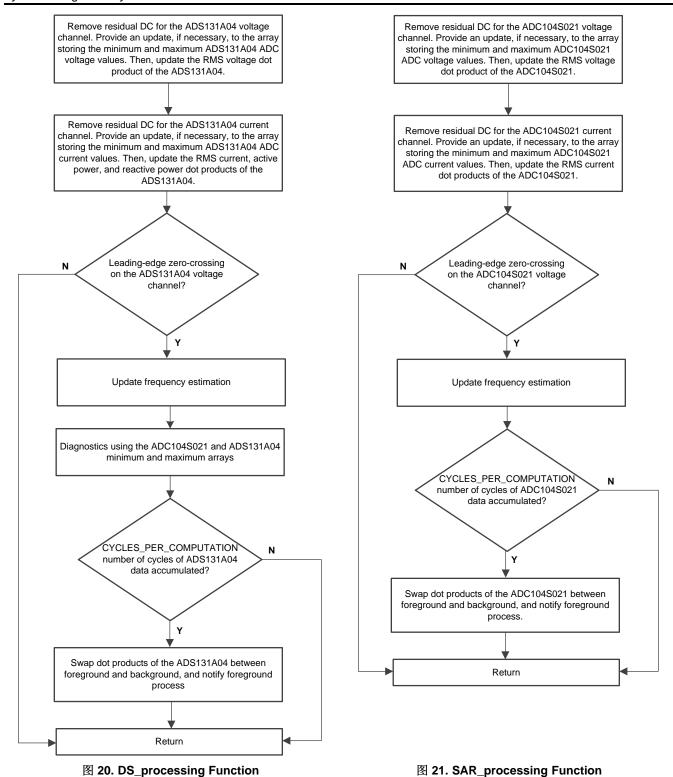

This section discusses the software implementation. The first subsection discusses the software used to setup the MSP432 peripherals, ADS131A04 ADC, and ADC104S021 ADC. Subsequently, the metrology software is described as two major processes: the foreground process and background process.

#### 2.6.1 Setup Software

#### 2.6.1.1 MSP432 Setup

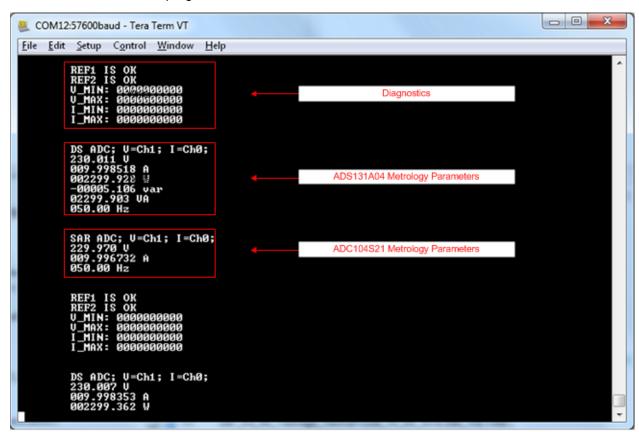

The MSP432 is used to set up the ADS131A04 and ADC104S021, calculate metrology parameters, and communicate these parameters through the RS-232 to a terminal program.

#### 2.6.1.1.1 GPIO, SPI, and UART Setup

For communication of the metrology parameters, a UART port is used on the MSP432. The UART communication is set to a baud rate of 57600 with 8 data bits, no parity, and 1 stop bit. By connecting the UART port pins to an isolated UART, then to the RS-232 board (such as TIDA-00163), the metrology parameters calculated by the MSP432 can be displayed by a PC using a terminal program.

To communicate with the ADS131A04 and ADC104S021, two different SPI ports are used. The SPI clock for both of these ports is set to 3 MHz with the most significant bit shifted out first. These different SPI ports are independent of each other but are used to communicate to the two devices of a particular ADC. For example, the ADS131A04 uses the same UCB0 port for the two ADS131A04 devices on this board. Similarly, the ADC104S021 uses the same UCB2 port for the two ADC104S021 devices.

In addition to the normal SPI lines used to communicate to the A04, the A04 devices also use additional GPIO lines for communication. One of these additional GPIO pins is used to provide a reset signal to the ADS131A04 to get it to a known state before sending commands to it. The second extra GPIO pin is connected to the DRDY pin of the ADS131A04. This pin is used to alert the MSP432 of a new set of ADS131A04 ADC samples now ready so that the MSP432 can query the ADS131A04 devices for these new ADC samples. To immediately alert the MSP432 of the new ADC samples, the MSP432 GPIO pin connected to DRDY is configured as an interruptible input.

As a method to determine when there is an issue with the ADC reference of the A04 devices, the board also has comparators which compare the ADS131A04 references to a set voltage threshold. By connecting the output of these comparators to the corresponding interruptible GPIO pins on the MSP432, the state of the two ADC references can be logged.

表 14 lists the GPIO associations in the application.

#### 表 14. GPIO Associations

| PORT PIN FUNCTION         |                                                                   |

|---------------------------|-------------------------------------------------------------------|

| RS-232 GPIO CONFIGURATION |                                                                   |

| P3.2(UCA2 UART port)      | UART receive for RS-232 communication                             |

| P3.3 (UCA2 UART port)     | UART transmit for sending metrology parameters through the RS-232 |

# 表 14. GPIO Associations (continued)

| PORT PIN                                | FUNCTION                                     |  |

|-----------------------------------------|----------------------------------------------|--|

| ADS131A04 GPIO CONFIGURATION            |                                              |  |

| P5.2                                    | ADS131A04 chip select                        |  |

| P1.5 (UCB0 SPI port)                    | ADS131A04 SPI clock                          |  |

| P1.6 (UCB0 SPI port)                    | ADS131A04 SPI input (SIMO)                   |  |

| P1.7 (UCB0 SPI port)                    | ADS131A04 SPI output (MISO)                  |  |

| P3.0                                    | ADS131A04 DRDY                               |  |

| P4.5                                    | ADS131A04 RESET                              |  |

| ADS131A04 REFERENCE CHECK GPIO CONFIGUR | ATION                                        |  |

| P2.7                                    | ADCREF1 OK (for status of U2 reference)      |  |

| P2.6                                    | ADCREF2 OK (for status of U4 reference)      |  |

| ADC104S021 GPIO CONFIGURATION           |                                              |  |

| P5.0                                    | Chip select 1 for the U1 device on the board |  |

| P5.1                                    | Chip select 2 for the U3 device on the board |  |

| P3.5 (UCB2 SPI port)                    | ADC104S021SPI clock                          |  |

| P3.6 (UCB2 SPI port)                    | ADC104S021SPI input (SIMO)                   |  |

| P3.7(UCB2 SPI port)                     | ADC104S021SPI output (MISO)                  |  |

### 2.6.1.1.2 Clocks

The MSP432 uses multiple clocks in this application.  $\frac{15}{2}$  lists the different clock settings used in this application.

# 表 15. Application Clock Settings

| PORT PIN                                 | FUNCTION                                         |  |

|------------------------------------------|--------------------------------------------------|--|

| MASTER CLOCK (MCLK, CPU CLOCK)           |                                                  |  |

| Clock frequency                          | 48 MHz (clock divider = 1)                       |  |

| Number of flash wait states              | 2                                                |  |

| Clock source                             | Internal DCO of the MSP432                       |  |

| SUBSYSTEM MASTER CLOCK (SMCLK)           |                                                  |  |

| Clock frequency                          | 24 MHz (clock divider = 2)                       |  |

| Clock source                             | Internal DCO of the MSP432                       |  |

| AUXILIARY CLOCK (ACLK)                   |                                                  |  |

| Clock frequency                          | 32768 Hz                                         |  |

| Clock source                             | 32768-kHz crystal                                |  |

| RS-232                                   |                                                  |  |

| Speed                                    | 57600 baud                                       |  |

| Clock source                             | SMCLK                                            |  |

| TIMER FOR UPDATE OF METROLOGY PARAMETERS |                                                  |  |

| Timer used                               | Timer A0                                         |  |

| Clock source                             | ACLK                                             |  |

| Generated interval                       | 1 second (32768 counts)                          |  |

| Timer mode                               | Up mode                                          |  |

| ADC104S021 SPI CLOCK                     |                                                  |  |

| Clock frequency                          | 3 MHz (clock divider = 8)                        |  |

| Clock source                             | SMCLK                                            |  |

| Clock polarity                           | Inactive state is high (UCCKPL = 1)              |  |

| Clock phase                              | Data is valid on clock leading edge (UCCKPH = 0) |  |

### 表 15. Application Clock Settings (continued)

| PORT PIN FUNCTION   |                                                  |

|---------------------|--------------------------------------------------|

| ADS131A04 SPI CLOCK |                                                  |

| Clock frequency     | 3 MHz (clock divider = 8)                        |

| Clock source        | SMCLK                                            |

| Clock polarity      | Inactive state is low (UCCKPL = 0)               |

| Clock phase         | Data is valid on clock leading edge (UCCKPH = 0) |

#### 2.6.1.1.3 Direct Memory Access (DMA)

The direct memory access (DMA) module is used to transfer all of the ADS131A04 and ADC104S021 ADC samples from these devices to the memory of the MSP432 with minimal bandwidth requirements from the CPU. To get the ADC sample data from the ADC devices, the MSP432 requires writing data to the SPI transmit buffers to activate the SPI clocks. The DMA module is used to not only transfer the received SPI data to memory, but also is used to write the dummy data to the SPI transmit buffers of the MSP432 so that the receive operations can be triggered. As a result, there are two DMA channels used for each of the SPI ports used for communication to an ADC. One channel is for sending the dummy data from the MSP432 memory to the SPI transmit buffers. The other channel is used for moving the received SPI data to the memory of the MSP432. Once the transfer is complete, an interrupt is generated to complete any necessary post-transfer processing.

表 16 lists the DMA channel associations.

表 16. DMA Channel Associations

| DMA CHANNEL NUMBER | FUNCTION                                         |

|--------------------|--------------------------------------------------|

| 0                  | ADS131A04 SPI transmit (for triggering receive)  |

| 1                  | ADS131A04 SPI receive                            |

| 2                  | Not used                                         |

| 3                  | Not used                                         |

| 4                  | ADC104S021 SPI transmit (for triggering receive) |

| 5                  | ADC104S021 SPI receive                           |

| 6                  | Not used                                         |

| 7                  | Not used                                         |

#### 2.6.1.1.4 Interrupt Priorities

The software has five interrupts that are prioritized. 表 17 lists these interrupt priorities.

表 17. Interrupt Priorities

| INTERRUPT | SIGNIFICANCE                                                                                                            | PRIORITY CODE |

|-----------|-------------------------------------------------------------------------------------------------------------------------|---------------|

| DMA1      | Transfer of ADS131A04 ADC samples to the MSP432 memory has completed.                                                   | 0x20          |

| PORT3     | New ADS131A04 ADC samples have been generated so the MSP432 can now query the ADS131A04 device for the new ADC samples. | 0x40          |

| DMA2      | Transfer of ADC104S021 ADC samples to the MSP432 memory has completed.                                                  | 0x60          |

| TA0_0     | Time to send a new metrology parameter for RS-232 communication.                                                        | 0x80          |

| EUSCIA2   | Transmit buffer for RS-232 communication is empty so a new byte of the RS-232 communication packet can be sent.         | 0x80          |

www.ti.com.cn System Design Theory

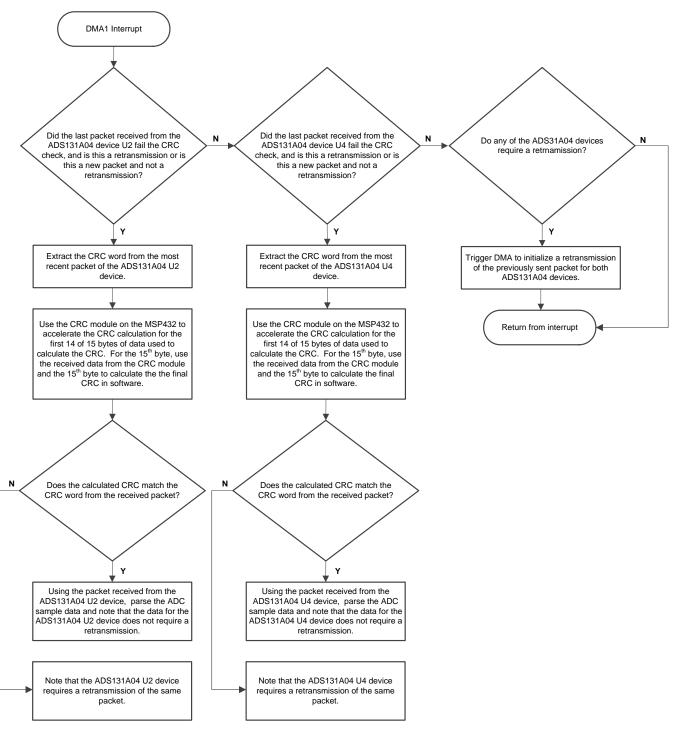

In 表 17, the interrupts with the lower priority code value have higher interrupt priority. In the software, communication to the terminal is a relatively low priority so the TAO\_0 and EUSCIA2 priorities have the highest priority code. The DMA2 interrupt has the next lowest priority since no time critical processing is required to be done in this interrupt. For the Port3 interrupt, a high priority interrupt is selected because this interrupt is where the majority of the sample processing is done. The DMA1 interrupt has the highest priority since a CRC check is performed on the sample data received from the ADS131A04 in this interrupt and if there are any CRC errors are present it should be detected as soon as possible so that the MSP432 can request and receive the sample data again before the next ADC sample is ready.

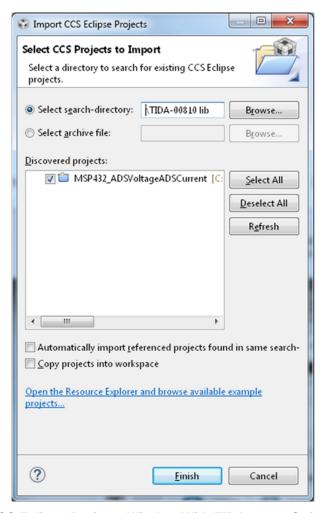

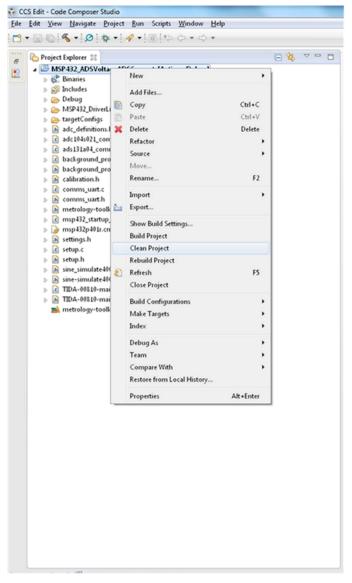

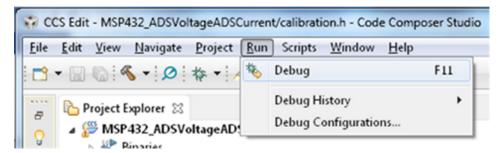

# 2.6.1.2 ADS131A04 Setup

For communication to the ADS131A04 devices, the device chaining feature of these devices is enabled so that communication to the two ADS131A04 devices can be done transparently, by concatenating the packets to be sent to the two A04 devices into one merged packet and sending it out through the shared SPI lines. This method of chaining does not use two different chip select lines from the MSP432 like what is done for the ADC104S021 devices.

After reset, the MSP432 device first sends a reset signal to the ADS131A04 device to get it to a known state. After resetting the ADS131A04 devices, commands are sent to these devices to initialize them. These setup commands are sent out manually to the software so a DMA is not used for transferring this command data to the ADS131A04. The order of commands sent is as follows:

- Send an UNLOCK command to the ADS131A04 until an UNLOCK ACK is received from both ADS131A04 devices.

- Send a WAKEUP command to the ADS131A04 until a WAKEUP ACK is received from both ADS131A04 devices.

- 3. Send a command to set the ICLK divider of the A04 devices to 2. Keep sending this command until the appropriate ACK is received.

- 4. Send a command to set the OSR to 256 and the Modclk divider either to 8 (for a 50-Hz nominal line frequency) or 6 (for a 60-Hz nominal line frequency). This step results in a sample rate of 4000 samples per seconds whenever the software is configured for a line frequency of 50 Hz and a sample rate of 5333.3 whenever the software is configured for a line frequency of 60 Hz. Keep sending this command until the appropriate ACK is received.

- 5. Send a command to the A04 devices to use the following configuration:

- High resolution mode

- Negative charge pump disabled

- Internal reference enabled

Keep sending the command until the appropriate ACK is received.

- 6. Send a command to the A04 devices to use a fixed frame size of six words. In the hardware configuration of the board, each word is set to be 24-bits long resulting in a communication frame size of 18 bytes per ADS131A04 device. Keep sending this command until the appropriate ACK is received.

- 7. Send a command to enable all of the ADS131A04 ADCs. Keep sending this command until the appropriate ACK is received.

- 8. Send a command to the A04 devices to use the following configuration:

- · CRC is enabled on all bits received and transmitted.

- The time before the device asserts the done signal after the LSB is shifted out is set to 12 ns.

- The time before the device asserts Hi-Z on Dout after the LSB of the data frame is shifted out is 12 ns.

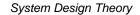

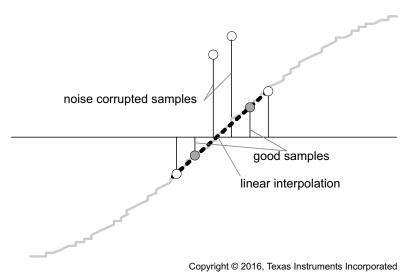

After the ADS131A04 devices are set up, it alerts the MSP432 of new sample data being available. This alert is done through providing GPIO interrupts from the DRDY pin of the ADS131A04. After receiving one of these interrupts, the MSP432 only needs to write dummy data into the SPI transmit buffers so that it can receive the ADC sample data from the ADS131A04 devices. The ADS131A04 automatically sends this data out through the SPI port so no command data must be sent to the ADS131A04 once it is set up. Due to the chaining of the two ADS131A04 devices, the received data frame consists of the data frames of each of the A04 devices which means that a total of twelve 24-bit words (36 bytes) are sent from the ADS131A04 devices. The first six words sent correspond to the first ADS131A04 device (designated as U2 on the PCB) and the last six words correspond to the second ADS131A04 device (designated as U4 on the PCB). 15 shows the order of words in a data frame that is received from each individual ADS131A04 device by the MSP432.

| Status Channel 0 Channel 1 Channel 2 Sample Sample Sample | Channel 3<br>Sample | CRC |

|-----------------------------------------------------------|---------------------|-----|

|-----------------------------------------------------------|---------------------|-----|

图 15. Words Received From Each ADS131A04 Device

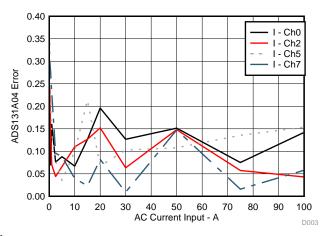

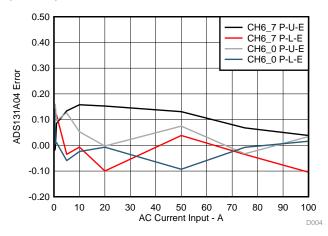

In the data received from an A04 device, the first word provides a status update of the ADC internal system monitor, the next four words represent the ADC samples, and the last word is the CRC word calculated by the ADS131A04. Once this packet is received by the MSP432, it extracts the CRC word, calculates its own CRC based on the values of the other words in the packet, and compares the two CRCs to ensure that no data transmissions have occurred. To accelerate the CRC calculation, the CRC module of the MSP432 is used for performing the CRC calculations of the first 14 bytes of the 15 byte data used in the calculation. If the two CRCs match, the received sample words are parsed into the corresponding ADC sample data for use for metrology calculations. If the two CRCs do not match, the MSP432 initializes the resending of the sample data.