# TI Designs: TIDA-060001 SunSpec® 快速关断发送和接收参考设计

# TEXAS INSTRUMENTS

# 说明

该参考设计将 AFE031 电力线通信模拟前端和 C2000™MCU 连接起来,使用移频键控 (FSK) 通过有 线耦合接口发送和接收数据。本设计演示了 SunSpec<sup>®</sup> 标准协议使用 FSK (f<sub>M</sub>: 131.25kHz 和 f<sub>s</sub>: 143.75kHz) 传输特定的 33 位文字包。目的是为始

终保持活动状态的信号提供一套集成的系统解决方案, 实现光伏逆变器到光伏 (PV) 模块的通信。

# 资源

| TIDA-060001                 |  |

|-----------------------------|--|

| AFE031                      |  |

| TMS320F28379D<br>LaunchPad™ |  |

| TPS62177                    |  |

| SN74LVC2G07                 |  |

设计文件夹 产品文件夹 产品文件夹 产品文件夹 产品文件夹 产品文件夹

# 特性

- 集成电力线驱动器

- 可编程 Rx-Tx 滤波器和 Tx/Rx 增益控制

- 适用于 SunSpec 协议的预编程开源示例代码

- 高分辨率 PWM

- 支持 EN50065 CENELEC 频带 A、B、C、D

- 支持 FSK、S-FSK 和 OFDM

# 应用

- 适用于光伏逆变器的快速关断 PLC

- 适用于 PV 模块的快速关断 PLC

- 直流线路上的 PLC FSK

### System Description

ゐ

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

# 1 System Description

This reference design interfaces an AFE031 with a C2000 MCU to send and receive data over a wired coupled interface using frequency shift keying (FSK). The design demonstrates the SunSpec standard protocol transmitting the specific 33-bit word packet using FSK ( $f_M$ : 131.25 kHz and  $f_S$ : 143.75 kHz). The purpose is to provide a keepalive signal with an integrated system solution that communicates from the string inverter to a photovoltaic (PV) module. This design guide addresses component selection, design theory, and test results of the TIDA-060001 reference design. The following subsections describe the various devices within this reference design system and highlight the characteristics most critical in implementing the corresponding functions.

# 1.1 Key System Specifications

$\frac{1}{2}$  describes the parameters around the FSK signal that is generated in the software example. The end goal is to send the complete packet, wait the designated wait period, and repeat.

| SYMBOL   | TX<br>SPECIFICATION | MIN         | NOM                    | МАХ         | UNIT                     | COMMENT                  |

|----------|---------------------|-------------|------------------------|-------------|--------------------------|--------------------------|

| W1       | Logic 1 code word   | {{-1,-1,    | -1,+1,+1,+1,-1,+1,+1   |             | +1 = Mark, -1<br>= Space |                          |

| WO       | Logic 0 code word   | {{+1,+*     | 1,+1,-1,-1,-1,+1,-1,-1 | ,+1,-1}}    |                          | +1 = Mark, -1<br>= Space |

| packet_1 | Complete packet     |             | ABC = [W1,W1,W1]       |             |                          |                          |

| packet_0 | Complete packet     |             | ABC = [W0, W0, W0]     |             |                          |                          |

| Fm       | Mark frequency      | 131.236875  | 131.25                 | 131.263125  | kHz                      |                          |

| Fs       | Space frequency     | 143.735625  | 143.75                 | 143.764375  | kHz                      |                          |

| Ts       | Bit period          | 5.119488    | 5.12                   | 5.120512    | ms                       |                          |

| Tt       | Tx period           | 168.943104  | 168.96                 | 168.976896  | ms                       | 3 words                  |

| Tq       | Quiet period        | 901.029888  | 901.12                 | 901.210112  | ms                       | 16 words                 |

| Тс       | Cycle period        | 1069.972992 | 1070.08                | 1070.187008 | ms                       | 19 words                 |

### 表 1. SunSpec® FSK Specifications

# 2 System Overview

# 2.1 Block Diagram

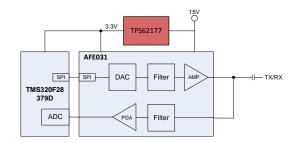

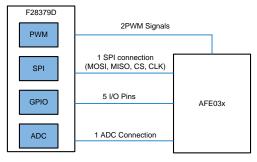

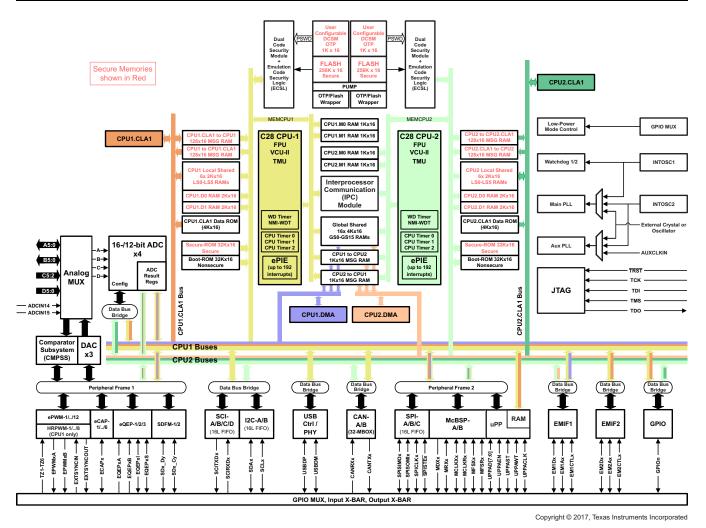

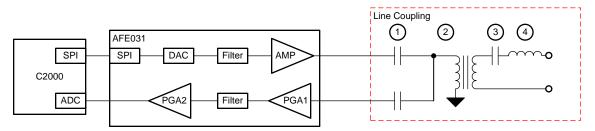

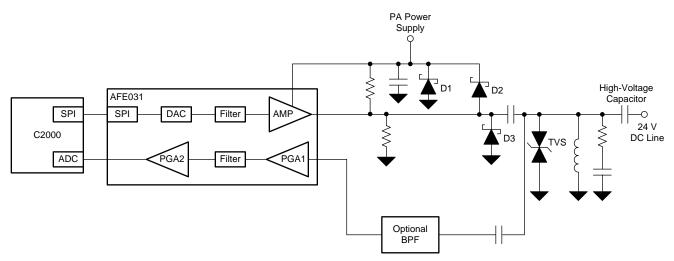

I shows a block diagram of the system. In this example, not all of the connections are used, but all are present on the BoosterPack<sup>™</sup> plug-in module for future development.

图 1. C2000<sup>™</sup> and AFE031 Block Diagram

The AFE has multiple internal registers that allow configuration of the internal components of the AFE chip, including filter selection, gain selection, and mode selections. These registers can be accessed using the SPI peripheral.

The AFE also has various GPIOs that allow the MCU to set the AFE into certain modes, as well as receive interrupts for critical events on the AFE. The ADC connection allows the MCU to receive or sample an input signal. The PWM signals provide a way to create an output for the AFE. Currently, the AFE031 supports two modes of data transmission: PWM mode and DAC mode.

# 2.2 Highlighted Products

This reference design features the following devices:

- AFE031: Powerline Communication Analog Front-End

- LAUNCHXL-F28379D: C2000 Delfino MCUs F28379D LaunchPad Development Kit

- TPS62177: 28-V, 0.5-A, Step-Down Converter With Sleep Mode

- SN74LVC2G07: Dual Buffer and Driver With Open-Drain Outputs

For more information on each of these devices, see their respective product folders at TI.com.

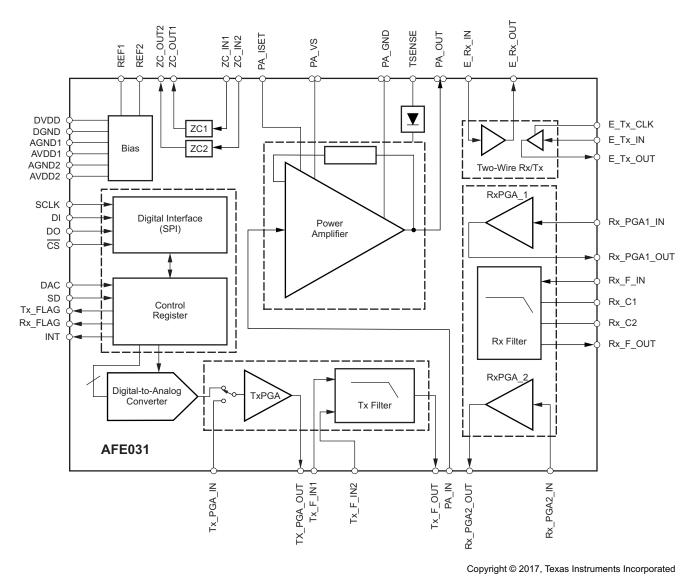

# 2.2.1 AFE031

The AFE031 is a low-cost, integrated, powerline communication (PLC) analog front-end (AFE) device that is capable of capacitive or transformer coupled connections to the powerline while under control of a DSP or microcontroller (MCU). This device is ideal for driving low-impedance lines that require up to 1.5 A into reactive loads. The integrated receiver is able to detect signals down to 20  $\mu V_{RMS}$  and is capable of a wide range of gain options to adapt to varying input signal conditions. This monolithic integrated circuit provides high reliability in demanding PLC applications.

The AFE031 transmit power amplifier operates from a single supply in the range of 7 V to 24 V. At maximum output current, a wide output swing provides a 12-V  $_{PP}$  (I<sub>OUT</sub> = 1.5 A) capability with a nominal 15-V supply. The analog and digital signal processing circuitry operates from a single 3.3-V power supply.

图 2. Functional Block Diagram of AFE031

# 2.2.2 LAUNCHXL-F28379D

The TMS320F2837xD MCU family, referred to as the F2837xD in this design guide, is a dual-core MCU design based on the TI 32-bit C28x CPU architecture. Each core is identical with access to its own local RAM and flash memory, as well as globally shared RAM. Sharing information between the two CPU cores is accomplished with an inter-processor communications (IPC) module. Additionally, each core shares access to a common set of highly integrated analog and control peripherals, providing a complete solution for demanding real-time high-performance signal processing applications, such as digital power, industrial drives, inverters, and motor control.

In addition to the high-performance CPUs, each core has a control law accelerator (CLA), which is an independent 32-bit floating-point processor designed to execute math-intensive calculations. The CLA runs concurrently and at the same speed of the main CPU, thereby effectively doubling the computational performance of each core. With each CPU running at 200 MHz, the CLAs can then effectively boost the total performance of the device to 800 MIPS.

System Overview

图 3. Functional Block Diagram of LAUNCHXL-F28379D

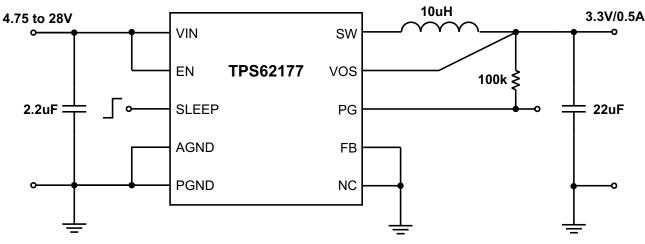

# 2.2.3 TPS62177

The TPS6217x is a high efficiency synchronous step-down DC/DC converter, based on the DCS-Control<sup>™</sup> topology. With a wide operating input voltage range of 4.75 V to 28 V, the device is ideally suited for systems powered from multi-cell Li-Ion as well as 12 V and even higher intermediate supply rails, providing up to 500-mA output current.

The device features a typical quiescent current of 22  $\mu$ A in normal mode and 4.8  $\mu$ A in sleep mode. In sleep mode, the efficiency at very low load currents can be increased by as much as 20%. In shutdown mode, the shutdown current is less than 2  $\mu$ A and the output is actively discharged.

图 4. Typical Application Schematic of TPS62177

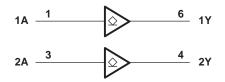

### 2.2.4 SN74LVC2G07

System Overview

This dual buffer and driver is designed for 1.65-V to 5.5-V VCC operation. The output of the SN74LVC2G07 device is open drain and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions. The maximum sink current is 32 mA.

图 5. Functional Block Diagram of SN74LVC2G07

# 2.3 System Design Theory

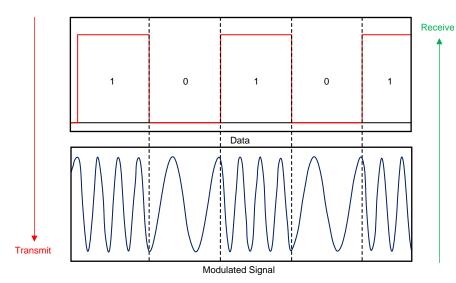

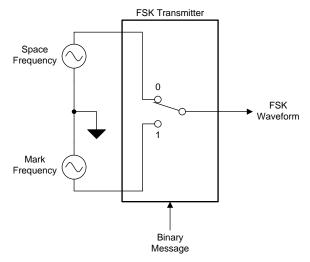

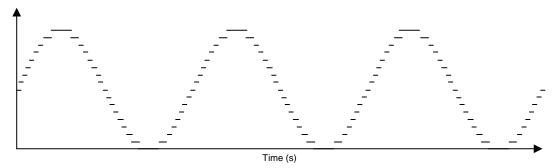

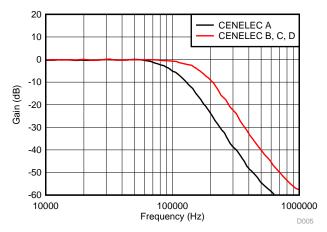

FSK is a modulation scheme that utilizes discrete changes of frequency to transmit and receive digital data. One of the simplest subsections of this modulation scheme, as well as the modulation used in this demo, is called binary frequency shift keying (BFSK).

In this scheme, the system is switching between two discrete frequencies: the mark frequency ("1") and the space frequency ("0"). These frequencies correlate directly to the bit value of the transmitted data.

8 6 shows what this looks like in the time domain.

图 6. BFSK in Time Domain

图 7. Transmitter Example

The two oscillators produce a higher (space) and a lower (mark) frequency signals. These oscillators are connected to a switch along with an internal clock. A clock is applied internally to both oscillators to avoid phase discontinuities of the output waveform during the transmission of the message. The binary input sequence is applied to choose the frequencies according to the binary input. In this case, binary "0" corresponds to the output of the space frequency and binary "1" corresponds to the output of the mark frequency.

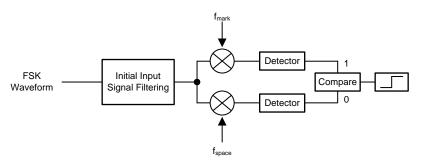

8 shows an example of a simplified FSK receiver to convert a received signal back into the desired digital information.

System Overview

图 8. Receiver Example

An FSK waveform is initially filtered and then mixed with signals of the desired mark (f  $_{mark}$ ) and space (f  $_{space}$ ) frequencies. The output is run through a detector algorithm and the results are compared to decipher if the signal being received pertains to a mark, binary "1", or space, binary "0". Additional functionality is included to decipher received bits, based on the duration of the received mark or space signal, and handle the boundaries between consecutive bits.

This is a simple overview on how FSK works. The following sections discuss how this is implemented on a C2000 device.

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

### 3.1.1 Hardware

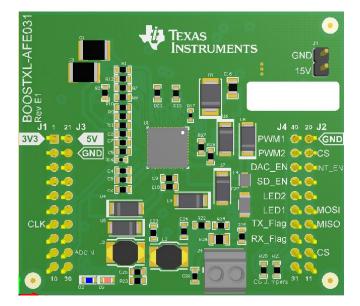

The system created for the SunSpec FSK transmitter or receiver is a combination of the following boards:

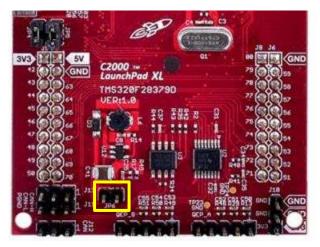

图 9. TMDS28379D LaunchPad

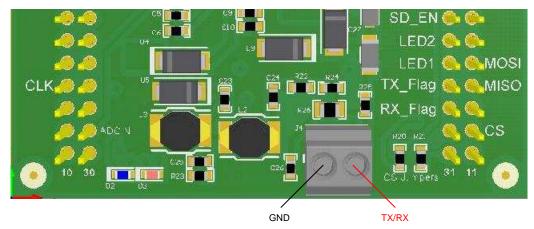

图 10. BoosterPack Test Board

Find the BoosterPack test board design files in C2000Ware.

### 3.1.1.1 Hardware Setup

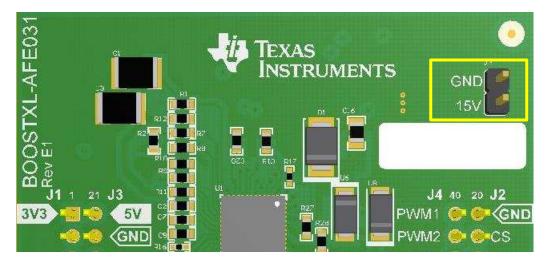

There are a few things that must be done so that the hardware can be debugged correctly. Power is supplied to the BOOSTXL-AFE031 test board through the 15-V jumper. The BoosterPack has a regulator that supplies power to the LaunchPad connected. [8] 11 shows a close up of the 15-V headers.

图 11. BOOSTXL-AFE031 Power Pins

The wire connected to the right input of the terminal block shown in 🕅 12 is the line that the transmitted output or received input FSK signal resides on, depending on whether the system is set up as a transmitter or receiver. The wire connected to the left input of the terminal block is the ground line. These lines can then be connected to some coupling circuitry or directly to another BOOSTXL-AFE031 terminal block for controlled testing, TX/RX to TX/RX and GND to GND.

图 12. BOOSTXL-AFE031 Terminal Block Connections

Because the BoosterPack is supplying power to the LaunchPad, the PC USB interface must be isolated. Header jumpers JP1, JP2, and JP3 on the LaunchPad must be removed to enable electrical isolation. 13 is a close up of the location of the headers.

图 13. F28379D Jumper Configuration

When using the system as a FSK receiver, the LaunchPad needs 5 V to power the C2000 ADC. With the LaunchPad being isolated from the PC USB interface, the 5-V power rail must be generated by stepping up the supplied 3.3 V. Header JP6 on the LaunchPad must be added to enable the step-up regulator. 14 is a close up of the location of the header.

图 14. F28379D JP6 Location

When using the system as a receiver, make sure that the F28379D LaunchPad is version 2.0 or greater. Earlier versions (Ver 1.1 and 1.2) have an issue with the ADCIN pin that is connected to the BOOSTXL-AFE031. For more information, see the revision history of the LAUNCHXL-F28379D Overview User's *Guide*.

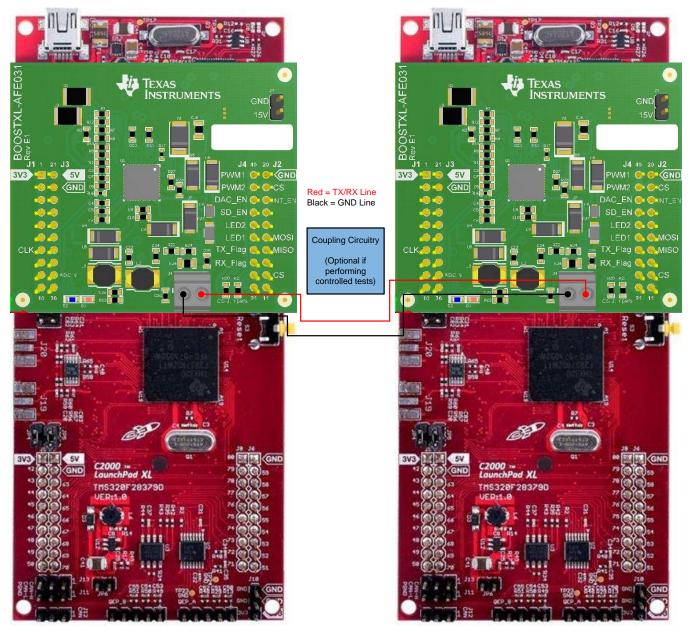

When using the transmitter solution in conjunction with the receiver solution, the complete system connection should look similar to what is shown in  $\boxtimes$  15.

图 15. TX-RX Solution System

# 3.1.1.2 Interfacing With a Power Line

PLC is used with Texas Instruments' C2000 paired with the AFE031 device, which enables data to be sent over existing power cables. This pairing means that one can both power and control or retrieve data at the same time with just power cables running though these devices. This setup minimizes the overall cost that would be needed otherwise to create a communications path with extra cabling.

# 3.1.1.2.1 Line Coupling

Line coupling is one of the most crucial segments of the PLC system, having two primary functions. The first function is to couple the signal from the AFE031 to and from the AC mains and DC bus. The second is to prevent the low frequency and high voltage of 50 or 60 Hz from the mains from damaging the PLC circuitry.

# 3.1.1.2.2 Coupling to an AC Line

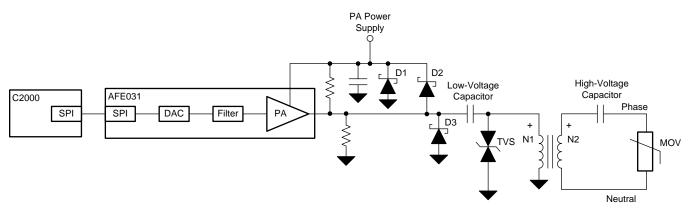

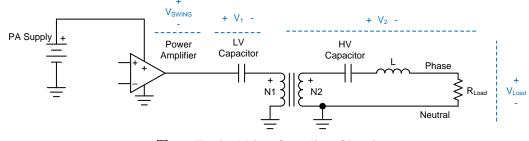

For coupling to the AC main, the following components are needed: a low-voltage capacitor, transformer, high-voltage capacitor, and an inductor. This section does not show the necessary protection circuitry; that information is discussed in  $\ddagger$  3.1.1.2.4.  $\boxtimes$  16 shows a simplified diagram.

图 16. Simplified Line Coupling Circuit for AC Main

This section addresses the components from the left side (that connects to the TX and RX of the AFE031 device) to the right side (that connects to the power line). Consider the following key points during hardware design.

# 3.1.1.2.2.1 LV Capacitor

The low-voltage (LV) capacitor couples the time-varying components of the PA output signal into the line coupling transformer. The LV capacitor should have a large enough capacitance to appear as a low-impedance throughout the signal band of interest. A value of 10  $\mu$ F is a common value for signals ranging from 35 kHz to 150 kHz. The BoosterPack LV capacitor value is 10  $\mu$ F because the space and mark frequencies (131.25 kHz and 141.75 kHz) lie within the range. The voltage rating of the LV capacitor must be sufficient to withstand the clamping voltage of the TVS diode (discussed in  $\ddagger$  3.1.1.2.4) operating under surge conditions. Generally, this limit is equal or slightly higher to the PA supply voltage.

# 3.1.1.2.2.2 Ratio of Transformer

Most PLC transformers are compact, with turns ratios between 1:1 and 4:1, low leakage inductance, and approximately 1 mH of winding inductance. This inductance in series with the high-voltage capacitor results in a voltage divider attenuating the ac mains voltage down to negligible levels at the module output.

To determine the optimal turns ratio for the transformer, it must be based on the PA's capabilities of maximum output swing and maximum output current to achieve maximum power transfer into the load.

$$\frac{N_{1}}{N_{2}} = \sqrt{\frac{PA, V_{OUT}_{Peak}}{PA, I_{OUT}_{Peak} \times R_{Load}}}$$

(1)

There are three cases where a one limitation is dominant than the others.

- Case 1: If the turns ratio of the transformer is greater than the ideal calculated value, the TX output of the AFE031 is limited by the voltage swing of the PA.

- Case 2: If the turns ratio of the transformer is less than the ideal calculated value, the TX output of the

AFE031 is limited by the maximum output current from the PA.

• Case 3: If the turns ratio of the transformer is equal to the ideal calculated value, the TX maximum output occurs as the amplifier approaches both its maximum output voltage and maximum output current, resulting in maximum power transfer to the load.

The transformer affects the coupling emission performance of the EN50065-1 when under a 2-MHz frequency. To compensate, TI recommends using products from Würth Electronik.

### 3.1.1.2.2.3 HV Capacitor

The high-voltage (HV) capacitor blocks the low-frequency mains voltage by forming a voltage divider with the winding inductance of the line-coupling transformer. While using high-voltage CBB capacitors, the maximum voltage range must exceed the amplitude of the power grid AC voltage. Operating the capacitor at approximately 80% of its AC-rated voltage ensures a long component operating life. The next important requirement is a standard setting maximum reactive power (VA limit). For example, the European product standards for attaching a device to the power grid must have a reactive power of less than 10 VAR, resulting in a capacitor values less than 0.55  $\mu$ F.  $\Delta$ 2 shows how the value 0.55  $\mu$ F is used to determine the HV capacitor value.

$$HVCap = \frac{VA_{\text{LIMIT}}}{VAC^2 (2\pi \times f)}$$

(2)

For a 240-V AC, 50-Hz application with a 10-VA limit,

$$HVCap \le \frac{10}{240^2 (2\pi \times 50)} \cong 550 \text{ nF}$$

(3)

A metallized polypropylene electromagnetic interference and radio frequency interference (EMI/RFI) suppression capacitor is recommended because of the low loss factor associated with the dielectric, which results in minimal internal self-heating.

# 3.1.1.2.2.4 HV Side Inductor

The inductor connected in series with the HV capacitor is required when driving low line impedances, and the HV capacitor is restricted to approximately 470 nF. In applications that operate in the CENELEC A band, the impedance of the 470-nF capacitance at 40 kHz is approximately 8.5  $\Omega$ . If the application requires the ability to drive a 2- $\Omega$  load, for example, this series impedance is restrictive. Adding the series inductor can mitigate this effect. To properly select the value of the inductance, the operating frequency range of the system must be known. A common example would be the PRIME frequency band, which is approximately 40 kHz to 90 kHz. Selecting the HV capacitor and inductor to have a resonant frequency in the center of the frequency band is recommended, and results in a series inductor value of 12.8  $\mu$ H and HV capacitor value of 470 nF.

$$L = \frac{1}{HVCap \times (2\pi \times f)^2}$$

(4)

The inductor must be sized to be capable of withstanding the maximum load current without saturation.

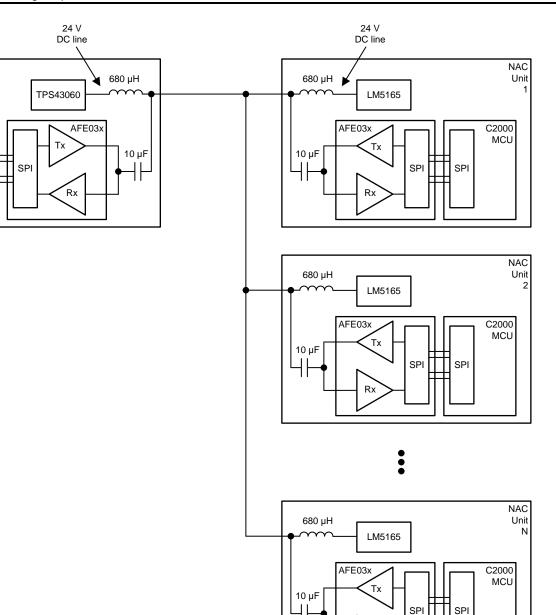

### 3.1.1.2.3 Coupling to DC Line

Coupling to a DC line has similar components for protection with the lack of components, such as an HV inductor, metal-oxide varistor (MOV), and transformer. [8] 17 shows what is needed for a coupling circuit and transient protection.

<sup>14</sup> SunSpec®快速关断发送和接收参考设计

图 17. Coupling Circuit for a DC Line

A 10- $\mu$ F capacitor is used to couple to the DC line. When coupling to a DC line, remember that the line is generally low impedance and can affect the output swing of the PA in the AFE031. Connecting an inductor in series with the line provides enough impedance to the PLC signal such that the power supply (possibly very low impedance) does not interfere with the PLC signal modulation. [8] 18 shows PLC modules coupled to a low-impedance DC line.

Head

End

Unit

C2000

SPI

MCU

图 18. Example of Multiple PLC Modules Coupled to a DC Line

Rx

For detailed test data on this circuit, see the DC Power-Line Communication Reference Design .

#### 3.1.1.2.4 **Protection Circuit**

PLC are often located in operating environments that are harsh for electrical components connected to the AC line. Noise or surges from electrical anomalies such as lightning, capacitor bank switching, inductive switching, or other grid fault conditions can damage high-performance integrated circuits if they are not properly protected. The AFE031 can survive even the harshest conditions if several recommendations are followed: MOVs, transient voltage suppression diodes (TVSs), Schottky diodes, and a Zener diode.

图 19. Recommended Transient Protection

# 3.1.1.2.4.1 Metal Oxide Varistors

There are several factors to consider when selecting an MOV:

- Working voltage

- · Required amount of transient energy to be absorbed by the MOV

- Peak transient current

- Power dissipation

图 20. Metal Oxide Varistor (MOV)

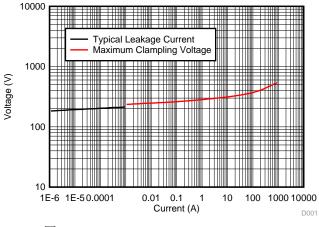

An MOV is a device that has high resistance until its triggering voltage is exceeded. Once this voltage level has been exceeded, the MOV reduces its resistance and absorbs the energy from the pulse. 🛽 21 shows the I/V characteristic of a typical MOV.

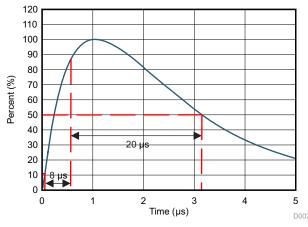

By the nature of the materials and techniques used in the construction of these components, MOVs respond quickly to a fast transient pulse, have high instantaneous power ratings, and are well-suited for protection on the AC line. The maximum clamping voltages are typically specified in response to a high-speed transient similar to that shown in 🕅 22. The 8/20-µs waveform is commonly associated as a waveform that represents the spectral content of lightning strikes.

图 22. Typical 8/20-µs Pulse for MOV and TVS Performance Specification

# 3.1.1.2.4.2 Transient Voltage Suppressors

A TVS is a very fast-acting clamping device that turns on in the case of an overvoltage condition, shunting the surge of current into ground. TVSs are rated primarily by the power handling capability and the clamping voltage. TVSs are available in either unidirectional or bidirectional configurations.

图 23. Bidirectional TVS Diode

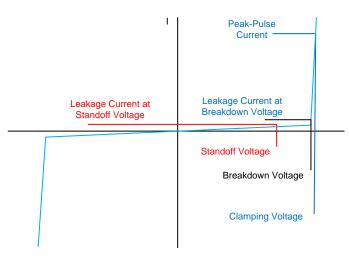

For PLC applications, a bidirectional TVS is recommended; the component is placed next to the line coupling transformer. 🛛 24 shows the I/V characteristics for a typical bidirectional TVS.

图 24. Typical Bidirectional TVS I/V Characteristics

As a surge or pulse on the AC line occurs, the voltage rises across the TVS. If the voltage rises higher than the TVS breakdown voltage, the TVS turns on and rapidly changes from high impedance to low impedance, shunting current into ground. The low-voltage capacitor between the PA output and the TVS blocks any DC voltage at the TVS. As a result, the normal FSK or OFDM signal from the PA appears to be centered around ground at the TVS. This condition requires the TVS to be bidirectional.

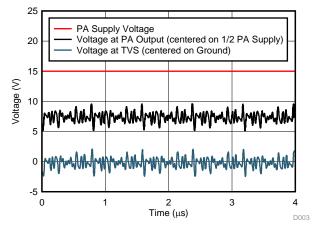

25 illustrates this concept.

图 25. Typical Signal at TVS

Because the signal is symmetric around ground at the TVS, the TVS breakdown voltage must be equal to approximately one-half of the PA power-supply voltage. It is important for the TVS to remain off during normal operation to avoid clipping and introducing distortions to the output signal. It is also important that the TVS turn on and clamp at the lowest possible voltage beyond normal operation to provide maximum protection.

This BoosterPack is designed with surge protection parts. A bidirectional TVS diode with a shunt connection to attach on the LV side of the transformer is used to clamp the voltage of a surge. The stable voltage of the TVS must be exactly half of the PA supply voltage of the AFE, meaning a 15-V AFE must use a 7.5-V TVS. This ½ ratio is based on the fact that:

• The PA of the AFE is a type AB, which uses a single power rail. Thus, the 12-V powered PA TX output

is at a 6-V bias with a ±6-V amplitude, meaning that the signal has a ±6-V range. While on transmission, the TVS must not be allowed to saturate the signal, so the stable voltage must be kept to  $\geq \frac{1}{2}$  of the PA power rail.

If a 12-V PA uses a 7.5-V TVS, during the arrival of a surge pulse, the LV side bias is locked-on at 7.5 V, but if the surge occurs at the exact moment of a TX maximum amplitude (which is 6 V), then the signal on the TX route is 7.5 V + 6 V = 13.5 V, which is higher than the power rail and causes damage to the PA of the AFE. So, the TVS voltage must be ≤ ½ of the PA power rail.

# 3.1.1.2.4.3 Current Steering Diodes

图 26. Current Steering Diodes

While the MOV and TVS components clamp the pulse and either dissipate or re-direct most of the energy to ground, TI also recommends placing current-steering (Schottky) diodes at the output of the PA section of the AFE031. In the unlikely event a transient surge increases the PA output pin beyond its power-supply rail, low-drop Schottky diodes can steer the current around the AFE031 safely to ground. Maintaining a low (less than 0.8 V) forward voltage drop on the Schottky diode is recommended for maximum protection. If the Schottky diode that connects the output of the PA to the power-supply rail turns on and becomes forward-biased, it is important to steer the current to ground without significantly disturbing the PA power-supply voltage. Placing a Zener diode at the PA power-supply pins to ground provides a low-impedance path for surges that attempt to raise the power-supply voltage beyond the absolute maximum rated voltage for the AFE031.

# 3.1.1.2.5 Determining PA Power Supply Requirements

Calculating the minimum power-supply requirements for the PA, the desired load voltage, load impedance, and available power-supply voltage or desired transformer ratio are all the parameters that must be known. For this FSK PLC example, similar to PRIME, the goal is to drive a  $1-V_{RMS}$  signal into a  $2-\Omega$  load. The minimum power-supply voltage required is calculated by adding the peak-to-peak load voltage; the voltage dropped across the HV capacitor and inductor, V2; the voltage dropped across the LV Cap, V1; and twice the output swing to rail limit of the PA, VSWING. For FSK and SFSK systems, the peak-to-average ratio is  $\sqrt{2}$ , while this ratio is approximately 3:1 for OFDM systems.

图 27. Typical Line Coupling Circuit

Consider these ratios when performing calculations that relate the RMS voltages and peak voltages during an analysis. Choosing a large value for the LV capacitor results in the voltage drop (V1) becoming negligible in most circumstances. The losses in the transformer are also negligible, even at high load currents, if the proper transformer with a low DCR is used. For FSK and SFSK systems, the voltage drop across the HV capacitor and inductor, V2, is also usually negligible.

For the AFE031 BoosterPack, an FSK signal with a 2- $\Omega$  load and 1-V<sub>RMS</sub> load voltage:

$PA_{Supply} = V_{Load} \times Turns Ratio \times (2 \times V_{Swing})$   $PA_{Supply} = 2.878 V \times 1.5 + (2 \times 2 V) = 8.25 V$ (6)

For more information on power dissipation of the AFE031, see *Analog Front-End Design for a Narrowband Power-Line Communications Modem Using the AFE031*.

# 3.1.2 Software

The target processor for the software is the TMDS320F28379D, but the software can be ported to other devices. For the project collateral and example code discussed in this guide, refer to the latest C2000Ware release within the directory:

C:\ti\c2000\C2000Ware\_x\_xx\_xx\device\_support\f2837xd\examples\cpu1

The available example projects are:

- boostxl\_afe031\_f28379d\_pwmmode

- boostxl\_afe031\_f28379d\_dacmode

- boostxl\_afe031\_f28379d\_rx

# 3.1.2.1 Interfacing With AFE03x for Transmitting SunSpec® Protocol

When interfacing with the AFE03x as a transmitter, first decide which mode of operation to use for the AFE03x: DAC mode or PWM mode.

In DAC mode, the C2000 MCU sends SPI data to update an internal DAC on the AFE031; the DAC value output is filtered and amplified. In this mode, a sine table is cycled through, and each point is sent to the AFE031 over SPI.

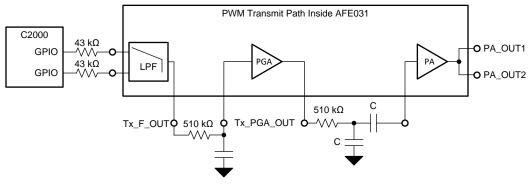

In PWM mode, the SPI connection is only used to configure the registers for the AFE. Two PWM signals are generated and supplied to the AFE031 at the desired frequency for FSK transmission. The AFE adds these signals together to create a waveform that creates less harmonics than a single PWM signal.

These two modes require different hardware configurations, so be sure to choose one or the other. If using the BOOSTXL-AFE031 test board as a reference, the hardware has been designed so that both modes can be used by simply adding or removing components.

When interfacing with the AFE03x as a receiver, the SPI connection is only used to set the registers of the AFE, much like the PWM transmit mode. The receive path of the AFE is enabled to allow the input signal to reach the ADC input of the C2000 MCU. Along this path lies some filters and two programmable-gain amplifiers (PGA) to step up or step down the input signal before entering the C2000 ADC.

### 3.1.2.1.1 Configuring the AFE031

There are two main steps to configure the AFE device. First, ensure that the GPIOs are configured correctly. On the AFE device, two main GPIOs are set up: DAC Mode Select and System Shutdown. Both of these pins are pulled low. All other GPIOs connected can also be pulled low.

The next step is to configure the device over SPI. In the software example, the *HAL\_afe031Init()* function configures the AFE031 and is defined within AFE03x\_Config.c.

The following steps show the sequence the function follows to correctly configure the device:

- 1. Configure GPIOs.

- a. Set up SD and DAC pins on the AFE device. Both of these pins must be brought low.

- Software example function: HAL\_afe031\_cfgGpio();

- 2. Configure SPI.

- a. Configure SPI module for 16-bit characters. For more information regarding SPI requirements, see *AFE031 Powerline Communications Analog Front-End*.

- Software example function: HAL\_spi\_cfg();

- 3. Perform a soft reset on the AFE device:

- a. Write 0x14 to the reset register.

- Software example function: HAL\_afe031\_softReset();

- 4. Enable the bias:

- a. Write 0x03 to the enable2 register.

- Software example function: HAL\_afe031\_biasEnable();

- 5. Select a frequency band:

- a. Write either 1 or 0 to the CA\_CBCD bit inside the control1 register. If a 1 is written, the frequency response of the TX and RX filters will be configured to CENELEC B, C, and D. If a 0 is written, then CENELEC A will be configured.

- Software example function: HAL\_afe031\_bandSelect(1);

- 6. Clear all interrupts:

- a. Write 0x00 to the control2 register.

- b. Software example function: HAL\_afe031\_clrAllInt();

- 7. Configure all interrupts:

- Interrupts can be configured by writing to the control2 register. The software example function currently only enables the T\_flag that indicates thermal overload.

- Software example function: HAL\_afe031\_cfgInt();

- 8. Enable ZC:

- a. Write a 1 to the ZC bit in the enable2 register.

- b. Software example function: HAL\_afe031\_zcEnable();

- 9. Write the TX gain if transmitting:

- a. Write either a 0, 1, 2, or 3 to the TXG bits in the gain select register. The gains are as follows:

- 0 = 0.25 V/V

- 1 = 0.5 V/V

- 2 = 0.707 V/V

- 3 = 1 V/V

- b. Software example function: HAL\_afe031\_writeTxGain(UINT16 gain);

- Note that the software example function uses an array to write the 0 to 3. Thus when using the function, the input parameter corresponds to the index of the desired HAL\_afe031\_txGainLut array element. For example, passing 0 to the function corresponds to a gain of 0.25 V/V.

- 10. Write the RX gain if receiving:

- a. Write 0 to 15 to the RXG bits in the gain select register. The gains range from 0.25 V/V when RXG is set to 0x0, to 128 V/V when RXG is set to 0xF.

- For specific gains, see 表 4.

- b. Software example function: HAL\_afe031\_writeRxGain(UINT16 gain);

- Note that the software example function uses an array to write 0 to 15. Thus, when using the function, the input parameter corresponds to the index of the desired *HAL\_afe031\_rxGainLut* array element. The included array does not have values for all RX gain configurations.

When these steps are completed, begin the final few configurations needed based on the transmit or receive implementation being used.

# 3.2 Transmit Path

When the AFE is initialized correctly, enable the system to transmit based on which transmit method is chosen: PWM mode or DAC mode.

### 3.2.1 PWM Mode

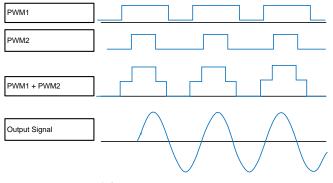

In PWM mode, the C2000 F28379D generates two symmetric PWM signals that go directly into the AFE device. The two symmetric PWM signals are 66% and 33% duty cycle. These signals are added together inside the AFE device and create a waveform that has the least amount of noise. 🛽 28 shows how this addition works.

图 28. PWM Addition

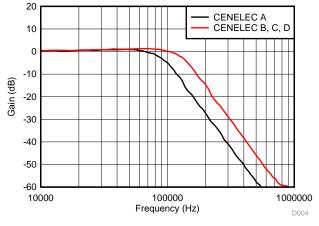

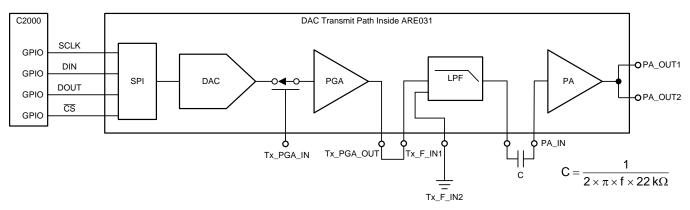

图 29 shows the path of the PWM signals. The PWM signals go into the low-pass filter internal to the AFE030/AFE031 device, and are added together to create the above PWM1+PWM2 waveform. 图 30 shows the gains witnessed at certain frequencies at the output of the internal TX low-pass filter.

图 30. TX Filter Gain vs Frequency

Next, the signal goes through a low-pass filter, PGA, another low-pass filter, and finally out of the PA. The external low-pass filters can be tuned to filter the desired frequencies, as shown in  $\frac{1}{2}$  2.

| FREQUENCY BAND       | R (Ω) | C (nF) |

|----------------------|-------|--------|

| SFSK: 63 kHz, 74 kHz | 510   | 2.7    |

| CENELEC A            | 510   | 1.5    |

| CENELEC B, C, D      | 510   | 1      |

### 表 2. External R and C Values to Increase Filter Response in PWM Applications

### 3.2.2 HRPWM vs EPWM

Unique to the C2000 device is the ability to use high-resolution PWM (HRPWM). HRPWM enables increased resolution for both the duty cycle and period of the PWM signals. In this example, HRPWM is used to generate both the mark and the space frequencies.

The HRPWM is based on micro edge positioner (MEP) technology. MEP logic is capable of positioning an edge very finely by sub-dividing one coarse system clock of a conventional PWM generator. The time step accuracy is on the order of 150 ps.

$\pm$  3 shows the resolutions possible with and without HRPWM.

|                        | REGULAR RES | AR RESOLUTION (PWM) |      | UTION (HRPWM) |  |

|------------------------|-------------|---------------------|------|---------------|--|

| PWM FREQUENCY<br>(kHz) | 100-MHz     | EPWM CLK            |      |               |  |

| ()                     | BITS        | %                   | BITS | %             |  |

| 20                     | 12.3        | 0.02                | 18.1 | 0.000         |  |

| 50                     | 11          | 0.05                | 16.8 | 0.001         |  |

| 100                    | 10          | 0.1                 | 15.8 | 0.002         |  |

| 150                    | 9.4         | 0.15                | 15.2 | 0.003         |  |

| 200                    | 9           | 0.2                 | 14.8 | 0.004         |  |

| 250                    | 8.6         | 0.25                | 14.4 | 0.005         |  |

| 500                    | 7.6         | 0.5                 | 13.4 | 0.009         |  |

| 1000                   | 6.6         | 1                   | 12.4 | 0.018         |  |

| 1500                   | 6.1         | 1.5                 | 11.9 | 0.027         |  |

| 2000                   | 5.6         | 2                   | 11.4 | 0.036         |  |

表 3. Resolution for PWM and HRPWM

For example, the mark frequency is generated at a 131.25-kHz signal. Using PWM, only a 131.2-kHz or a 131.3-kHz signal can be generated. This limitation is due to the resolution that is available for the PWM module. If HRPWM is added, a 131.250-kHz signal can be effectively generated.

If this amount of accuracy is not necessary or the desired frequency can be reached with a normal PWM, HRPWM is not required. HRPWM is an add-on to PWM. To disable this add-on in the software example, remove the code associated with it inside the main.c file.

# 3.2.3 PWM Mode Software Implementation

The example program referenced is: boostxl\_afe031\_f28379d\_pwmmode.

To enable PWM mode in software, complete the following flow:

- 1. Enable PWM transmit mode:

- To enable the PWM transmit mode, set the TX and PA bits in the enable register to 1, and set the DAC bit to 0.

- Software example function: HAL\_afe031\_txPWMEnable();

- 2. Disable the DAC transmit mode.

Two PWM sources create the two PWM signals: one PWM source is used to set the frequency of the two outputted signals and the other controls the bit rate for the sent data. In the software example, PWM2 is used to control the bit rate and generate an interrupt to determine the frequency that must be outputted.

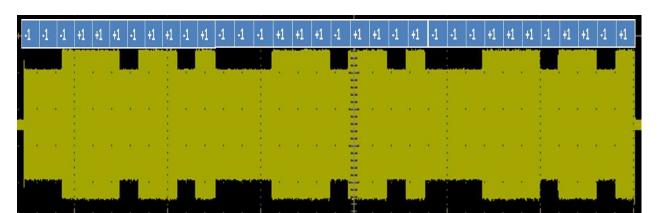

In the software example, the PWM2 interrupt handles all of the FSK protocol requirements. The implemented protocol is a repeatable pattern, which allows the software to be based on a cycle count. One cycle count is the time period for one bit. In this implementation, 33 bits (11 bits per word, three words) are sent. During each cycle, it checks the value of the next bit and the PWM frequency changes to either the mark or space frequencies. After 33 cycles, the system stops sending PWM signals and enters the quiet mode. After 209 cycles, the cycle count is reset and the software starts sending the packet again. With the FSK transmission being handled by the PWM2 interrupt, the CPU's main function is free to be used for other applications. By default, the software example transmits a packet\_1 referenced in 表 1, but this can be changed to a packet\_0 by setting the packet\_to\_send variable to a zero.

#### 3.3 Testing and Results

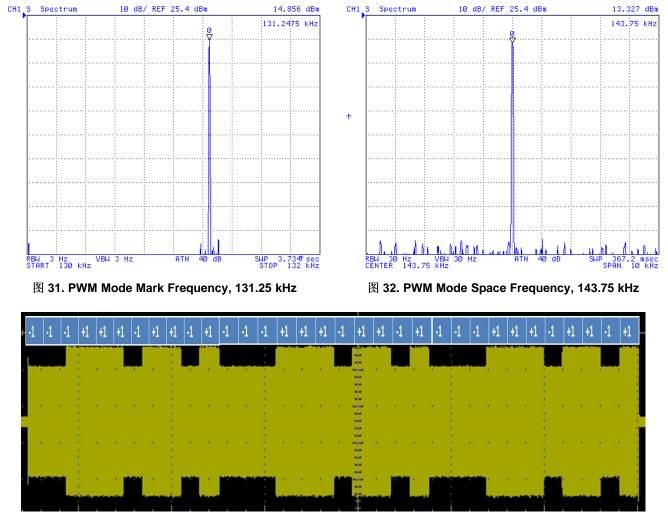

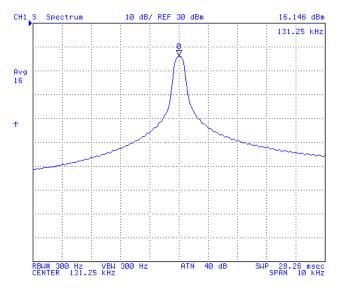

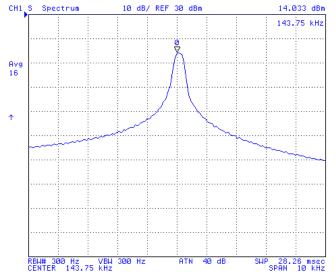

图 31 and 🛽 32 show that the system created both the mark and space frequencies. 🖉 33 shows the complete packet being sent out of the system.

图 33. Full Packet Transmission Waveform

#### DAC Mode 3.4

This section describes one way to create a DAC mode FSK transmitter. DAC mode is very similar to the PWM mode, in that PWM interrupts are used to accomplish FSK transmission. 🛽 34 shows the transmit path used when using DAC mode.

In DAC mode, the software sends data over SPI to the internal DAC to set the output value. To accomplish sending a single tone or sine wave, a ramp of DAC values at a given frequency are sent. Using a PWM interrupt occurring every period, send the updated DAC value at a frequency determined by the PWM period. The number of points in the sine table and desired frequency determine the frequency of the PWM signal. For example, if given a 100-kHz sine wave that has ten points, all ten points must be sent within 100 kHz. This means that the PWM must generate an interrupt that follows 公式 7: PWM Frequency = Points of Sine Table × Desired Frequency (7)

图 35 shows what this looks like in the time domain.

图 35. DAC Sine Wave Ramp

# 3.4.1 DAC Mode Software Implementation

The example program referenced is: boostxl\_afe031\_f28379d\_dacmode.

To enable DAC mode in software, complete the following flow:

- 1. Enable DAC transmit mode internal to AFE:

- To enable the PWM transmit mode, set the TX and PA bits in the enable register to 1, and set the DAC bit to 0.

- Software example function: HAL\_afe031\_txDACEnable();

- 2. Enable the DAC transmit mode with GPIO toggle and Configure word length for SPI:

- Set the GPIO connected the the DAC pin to 1.

- Set the word length to 10 bytes for SPI communication.

- Software example function: HAL\_afe031\_dacEnable();

(8)

(9)

Sending information in DAC mode can be accomplished similarly to how the PWM mode operates. One PWM source is used to set the DAC mode value to the correct value of the sine ramp that gets sent out. The second PWM is used for bit rate to generate an interrupt and determine what frequency must be outputted.

A problem can occur if attempting to reach vary precise frequencies with this implementation. The problem can be looked at with  $\Delta$  $<math> \pm$  8.

Number of steps in Sine Table =  $\frac{\text{Frequency of Interrupt}}{\text{Frequency of Desired Signals}}$

If trying to generate 131.25 kHz, then only two variables can change. One approach is to set the number of steps in the sine table. For example, if there are 10 steps in the sine table the frequency of interrupt is:

Frequency of Interrupt = (Number of Steps in Sine Table) × (Frequency of Desired Signal) Frequency of Interrupt = 1.3125 MHz

With a 200-MHz clock, even if an interrupt occurs at either 152 or 153 CPU cycles, the interrupt frequencies would be 1.31579 MHz and 1.30719 MHz, respectively. These frequencies do not fall within spec for the frequency tolerances in  $\gtrsim$  1. This result means setting the step size cannot be the correct implementation for precise frequency generation.

The other way to think of this is to set the frequency of interrupt. For example, set the interrupt for 1 MHz, which is possible to generate. The number of steps in the sine wave would then be:

Number of Steps in Sine Table = (1 MHz) / (131.25 kHz) = 7.61905

Using the floating-point capability of the F28379D, the processor can keep track of that remainder, and now the accuracy depends on the sine table, not the 1-MHz clock. The step size can be found using  $\Delta \mathfrak{A}$  9:

Step Size = (Points in Sine Table)/ (Number of Steps in Sine Table)

Continuing with the previous example, a 4096 sine table gives a step size of 537.6. This result means in every interrupt, the sine table steps another 537.6. Because the program is sorting through an array, this number is rounded off to 537. However, as this number gets added and the program shifts through the sine table, the next step will vary off the decimal step size. An example interrupt routine is as follows:

- //Transmit next data point in sine wave. Also convert float SinePosition to unsigned int:

- Uint16 temp = sinePosition;

- HAL\_spi\_xmt((sineTable[temp]));

- //Calculate next step:

- sinePosition += sineStep; }

- //Check for overflow:

- if(sinePosition > 4095)

- { sinePosition -= 4095; }

In this implementation, a 1-MHz Interrupt is created, which only moves data from one memory address to another. A way to make this less CPU intensive is to use the C2000's direct memory access (DMA). The DMA peripheral moves data from one memory address to another based on a trigger event. Pre-fill two buffers with the correct data that is chosen to send out over SPI, and use the DMA to switch between the two. When switching from one buffer to the other, the older buffer refills with the values.

In the DAC mode software, a 1-MHz PWM signal is used to generate a DMA event that moves data from one of these buffers to the SPI TX buffer. Because the older buffer must be refilled after each use, the DMA triggers an event each time it finishes reading an entire buffer. During this interrupt, the buffers are switched, and the old one is refilled. By following this implementation, CPU utilization versus memory trade-offs can be weighed and the buffers can be sized accordingly. If extra memory is available, using a bigger buffer reduces the CPU overhead. If not a lot of memory is available, then the smaller buffer size increases the CPU overhead.

Exactly like the PWM mode software implementation, the PWM2 interrupt handles all of the FSK protocol needs. The protocol being implemented is a repeatable pattern, which allows the software to be based on a cycle count. One cycle count is the time period for one bit. In this implementation, 33 bits (11 bits per word, three words) are being sent. During each cycle, check to see the value of the next bit and the step size changes to allow the sine table to be sent out at the mark or space frequencies. After 33 cycles, the system stops sending DAC values and enters the quiet mode. After 209 cycles, the cycle count is reset and the software starts sending the packet again. With the FSK transmission being handled by the PWM2 interrupt, the CPU's main function is free to be used for other applications. By default, the software example transmits a packet\_1 referenced in 表 1, but this can be changed to a packet\_0 by setting the packet\_to\_send variable to a zero.

# 3.5 Test Results

图 36 and 图 37 show that the system created both the mark and space frequencies. 图 38 shows the complete packet being sent out of the system.

图 36. DAC Mode Mark Frequency Spectrum Analyzer

图 37. DAC Mode Space Frequency Spectrum Analyzer

图 38. Full Packet Transmission Waveform

# 3.6 Receive Path

The C2000 AFE031 interface can also be used as a FSK receiver to translate the transmitted frequency shifted signal into digital data. This section describes one way to create an FSK receiver using the C2000 AFE031 interface.

# 3.6.1 Receive Path Overview

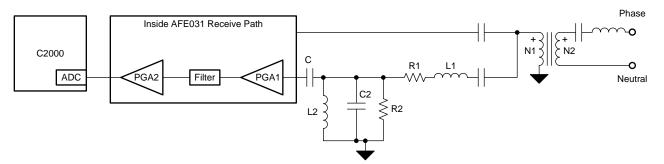

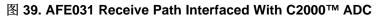

Image 39 shows the C2000 AFE031 system receive path. There is a significant amount of filtering the input signal must traverse along the path from the transformer on the right to the input of the C2000 ADC on the left. On the AFE side, the AFE031 has vast filtering abilities for these signals.

The AFE031 RX path consists of the Rx PGA1, the Rx low-pass filter, and Rx PGA2. Both Rx PGA1 and Rx PGA2 are high-performance PGAs that can be configured through SPI. Rx PGA1 can operate as either an attenuator, providing loss, or an amplifier, providing gain. The gain steps of the Rx PGA1 are 0.25 V/V, 0.5 V/V, 1 V/V, and 2 V/V. The gain steps of the Rx PGA2 are 1 V/V, 4 V/V, 16 V/V, and 64 V/V. For specific Rx PGA gain select register values, see  $\frac{1}{5}$  4. Configuring the Rx PGA1 as an attenuator (at gains less than 1 V/V) is useful for applications where the presence of large interference signals are present within the signal band. Attenuating the large interference allows these signals to pass through the analog Rx signal chain without causing an overload; the interference signal can then be processed and removed within the MCU, as necessary.

Hardware, Software, Testing Requirements, and Test Results

| BIT NAME       | LOCATION (0 = LSB) | DEFAULT | R/W | FUNCTION                                                                                                         |

|----------------|--------------------|---------|-----|------------------------------------------------------------------------------------------------------------------|

| RX1G-0, RX1G-1 | 0, 1               | 0, 1    | R/W | This bit is used to set the gain of the RX<br>PGA1.<br>00 = 0.25 V/V<br>01 = 0.5 V/V<br>10 = 1 V/V<br>11 = 2 V/V |

| RX2G-0, RX2G-1 | 2, 3               | 0, 0    | R/W | This bit is used to set the gain of the RX<br>PGA2.<br>00 = 1  V/V $01 = 4  V/V$ $10 = 16  V/V$ $11 = 64  V/V$   |

表 4. AFE031 RX PGA Gain Settings

The Rx filter is a very low noise, unity-gain, fourth-order low-pass filter. The Rx filter cutoff frequency is selectable between CENELEC A or CENELEC B, C, and D modes that is set within the control register. Because the Rx filter is a very low-noise analog filter, two external capacitors, shown in 图 40, are required to properly configure the Rx filter. 表 5 shows the proper capacitance values for CENELEC A and CENELEC B, C, and D bands.

图 40. External Filtering for the AFE031 Receive Path

| FREQUENCY BAND  | Rx C1, PIN 24 (pF) | Rx C2, PIN 23 (pF) | CUTOFF FREQUENCY (kHz) |

|-----------------|--------------------|--------------------|------------------------|

| CENELEC A       | 680                | 680                | 90                     |

| CENELEC B, C, D | 270                | 560                | 145                    |

Capacitor Rx C1 is connected between pin 24 and ground, and Rx C2 is connected between pin 23 and ground. For the capacitors shown, TI recommends that these components be rated to withstand the full AVDD power-supply voltage.

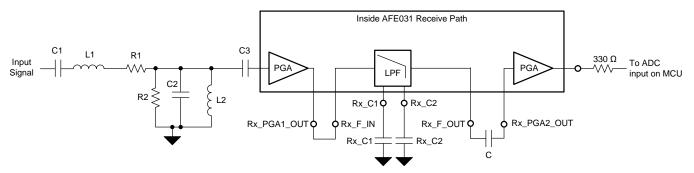

图 41. RX Filter Gain vs Frequency

$\boxtimes$  41 shows the gains witnessed at certain frequencies at the output of the RX low-pass filter. This response displayed is under normal AFE03x operating conditions. Attenuation begins at frequencies slightly before the actual cutoff frequencies in  $\ge$  5.

An external fourth-order passive passband filter is optional, but recommended for applications where high performance is required. The external passive pass-band filter removes any unwanted, out-of-band signals from the signal path, and prevents them from reaching the active internal filters within the AFE031. 表 6 shows the values needed for CENELEC A or CENELEC B, C, D with a 0-dB passband. The component values used on the BoosterPack are for a CENELEC B, C, D with a 0-dB passband.

Hardware, Software, Testing Requirements, and Test Results

# ${\it ${\bar $\pi$}$}$ 6. Recommended Component Values for Fourth-Order Passive Bandpass Filter (0-dB Passband Attenuation)

| FREQUENCY<br>BAND | FREQUENCY<br>RANGE (kHz) | CHARACTERISTIC<br>IMPEDANCE (Ω) | R1 (Ω) | R2 (Ω) | C1 (nF) | C2 (nF) | L1 (µH) | L2 (µH) |

|-------------------|--------------------------|---------------------------------|--------|--------|---------|---------|---------|---------|

| CENELEC A         | 35 to 95                 | 1k                              | 1k     | 10k    | 4.7     | 1.5     | 1500    | 4700    |

| CENELEC<br>B,C,D  | 95 to 150                | 1k                              | 1k     | 10k    | 1.7     | 1       | 1200    | 1500    |

| SFSK              | 63 to 74                 | 1k                              | 1      | 10k    | 2.7     | 2.2     | 2200    | 2200    |

For other band-pass filter component values with a different passband attenuation, see the *Powerline Communications Analog Front-End*.

# 3.6.2 Receiver Software Implementation

The example program referenced is: boostxl\_afe031\_f28379d\_rx \.

The software example is designed to do the following:

- · Continuously sample the received FSK signal after it has traveled through the AFE031 receive path

- Execute a correlation based algorithm on the sampled values to detect if a mark or space frequency is being received

- Decipher mark and space bits based on the frequency detected and its duration

- Store the received bits and packetize them into a desired and usable format

To enable the system to receive in software, complete the following:

- 1. Set the RX bit in the enable register to 1 to open the AFE031 receive path.

- Software example function: HAL\_afe031\_rxEnable();

- 2. Include the fsk\_corr\_detect library and related header files in the project:

- fsk\_corr\_detect.lib

- fsk\_corr\_detector.h

- fsk\_packetization.h

### 3.6.2.1 Initial Setup and Parameters

The FSK signals being received follow a set of communication parameters that must be designed around within software. 🔀 42 shows the communication parameters of interest.

The labeled parameters represent the following:

- T<sub>bit</sub>: Bit period

- F<sub>bit</sub>: Bit frequency

- F<sub>mark</sub>: Mark frequency

- F<sub>space</sub>: Space frequency

- T<sub>s</sub>: Sampling period

- F<sub>s</sub>: Sampling frequency

For the example program, the communication parameters being followed by default are stated in  $\gtrsim 1$ . Create a *FSK\_CORR\_DETECTOR* structure, declared in fsk\_corr\_detector.h, to hold the parameters necessary for accurate receiving.

volatile FSK\_CORR\_DETECTOR FSK\_struct1; // FSK structure

The example software and fsk\_corr\_detect library are designed to detect a set of user-specified frequencies, one mark frequency and one space frequency. These frequencies must be within the frequency band ranges of the AFE031's CENELEC A or CENELEC B, C, D configurations. The example program uses a mark frequency of 131.25 kHz and a space frequency of 143.75 kHz and is meant to be used with the CENELEC B, C, D configuration. Set the *mark\_freq* and *space\_freq* members of the *FSK\_CORR\_DETECTOR* structure with these frequencies.

```

FSK_struct1.mark_freq = 131250; // Mark Frequency Detected

FSK_struct1.space_freq = 143750; // Space Frequency Detected

```

The C2000's ADC is used to sample the FSK input signal. The sampling frequency,  $f_s$ , must follow the Nyquist theorem. The input signal must be sampled at a rate of at least 2× the highest signal frequency trying to be detected. That is, if the highest signal frequency to be detected is 100 kHz,  $f_s$  must be at least 200 kHz. In the example program, the highest frequency being detected is a 143.75-kHz space frequency and the sampling rate is set to 300 kHz, which is more than the required rate. Set the *isr\_freq* member of the *FSK\_CORR\_DETECTOR* structure to the acceptable  $f_s$ .

```

FSK_struct1.isr_freq = 300000; // ADC Sampling frequency

```

A bit decision algorithm is intended to be run at three times the bit frequency. For example, if each bit period is 1 ms long, the bit frequency is 1 kHz, making the desired bit decision frequency 3 kHz. The example program is detecting bits with a period of 5.12 ms making the bit frequency 195.3125 Hz and the desired bit decision frequency 585.9375 Hz. The bit decision frequency in software should be as close as possible to the desired frequency to prevent bit boundary issues. Set the *bit\_freq* member of the *FSK\_CORR\_DETECTOR* structure with this bit decision frequency.

FSK\_struct1.bit\_freq = 586; // Bit decision frequency, 3x bit frequency

In summary, 表 7 lists the frequency parameters set for the example program.

| PARAMETER                        | FREQUENCY           |

|----------------------------------|---------------------|

| Detected mark frequency          | 131.25 kHz          |

| Detected space frequency         | 143.75 kHz          |

| Input signal sampling frequency  | 300 kHz             |

| Bit decision algorithm frequency | 586 Hz (rounded up) |

### 表 7. Software Frequency Parameters

Set the *detection\_threshold* member of the *FSK\_CORR\_DETECTOR* structure. This value plays a role in tuning the bit detection sensitivity.

#define FSK\_BIT\_DETECTION\_THRESHOLD 0.1 // Bit detection threshold value

FSK\_struct1.detection\_threshold = FSK\_BIT\_DETECTION\_THRESHOLD; // Set threshold

Complete the fsk\_corr\_detect library's initialization based on the member values inputted by calling the corresponding init function.

FSK\_CORR\_DETECTOR\_INIT(&FSK\_struct1); // Initialize FSK structure

Additionally, the format of received information is taken into account by setting the following parameters within software.

- The number of bits that make up a word, #define within fsk\_packetization.h:

- #define NUMBER\_OF\_BITS\_PER\_WORD 11

- The number of words that make up a packet, #define within fsk\_packetization.h:

- #define NUMBER\_OF\_WORDS 3

- The number of total bits within a packet, #define within fsk\_corr\_detector.h:

- #define RX\_MESSAGE\_SIZE 33

### 3.6.2.2 Interrupt Service Routines

ISRs running at these predetermined frequencies carry out the main functions of the receiver solution. The example program makes use of the C2000's EPWMs and CPU timer to trigger necessary interrupts.

An ADC sampling ISR, configured using EPWM1, is set to trigger at the 300-kHz input signal sampling frequency. The ISR function samples the ADC, scales the sampled value, and passes the scaled value to a library function for signal processing.

A bit-decision ISR, configured using EPWM2, is set to trigger at 585.92 Hz. This frequency is as close to the desired 585.9375 Hz the EPWM module could achieve. The ISR function takes the signal processing work of the previous ADC sampling ISR and checks if a mark or space bit has been detected. If a mark or space bit is detected, then the detected bit is placed into a received message buffer. When the message buffer is full, a flag is set to signify that a full packet has been received.

A message timeout ISR, configured using CPU timer 2, is set to trigger if the user-specified time limit is reached while receiving. By default, this time limit is set to 3 seconds by the RX\_MESSAGE\_TIMEOUT #define. The timer begins right before the system starts receiving and resets if a packet is received. If a packet is not received within the specified time limit, the ISR triggers and causes the system to stop receiving.

### 3.6.2.3 Run Time Operation

During the run time, the receiver operates in the following way:

- 1. The system begins to continuously receive incoming data by starting the EPWMs and CPU timer to trigger interrupts.

- Example program function: Start\_Receiving();

- 2. The ISRs run until the full packet of data is received or the specified timeout is reached.

- The *rxMessage[]* buffer is filled with the received bits while the ISRs are running.

- 3. When the packet of data is received or the specified timeout is reached, the system stops receiving data to reduce CPU usage during quiet periods.

### Hardware, Software, Testing Requirements, and Test Results

www.ti.com.cn

- Example program function: Stop\_Receiving();

- The function stops the EPWMs and stops and resets the CPU timer.

- 4. The received data is then packetized into the desired format.

- Example program function: Packetize(int message[], int packet[]);

- The function takes the *rxMessage[]* buffer containing 33 received bits and fills the *packet[]* buffer with three 11-bit words by summing up the received bits for each word. The *rxMessage[]* buffer contents are then set to zero.

- +1 equates to a W1 following the specifications in arcadet 1

- -1 equates to a W0 following the specifications in atural 1

- The function sums up the values of the *packet[]* and saves the sum to the *packet\_sum* variable.

- +3 equates to a packet\_1 following the specifications in  $\frac{1}{8}$  1

- -3 equates to a packet\_0 following the specifications in  $\frac{1}{2}$  1

- 5. The packetized data is used before the receive process restarts.

- Example program function: Visual\_Indication();

- The function causes the LEDs on the BOOSTXL-AFE031 to blink accordingly:

- Blue LED blinks if a packet\_1 is received.

- Red LED blinks if a packet\_0 is received.

- Red and blue LEDs blink if neither a packet\_1 or packet\_0 are received, or if a timeout occurs.

### 3.7 Testing Results

The performance of the FSK receiver solution is tested in a controlled lab environment using either the PWM or DAC mode transmitter solution to provide the input FSK signal. The established setup is similar to what is shown in 🕅 15 without any coupling circuitry. The purpose of the tests were to confirm that the receiver solution could effectively translate a received FSK signal into the original digital information.

When the guidelines discussed in  $\ddagger$  3.6.2 are appropriately followed, a C2000 MCU can take an FSK input signal and accurately decode each bit of data it contains. 🕅 43 shows the results, where a packet of thirty-three unique bits are successfully captured.

| 🗸 🥭 rxMessage | int[33] | [-1,-1,-1,1,1] |

|---------------|---------|----------------|

| 00- [0]       | int     | -1             |

| 09= [1]       | int     | -1             |

| 69= [2]       | int     | -1             |

| (v)= [3]      | int     | 1              |

| 00-[4]        | int     | 1              |

| 00= [5]       | int     | 1              |

| 00= [6]       | int     | -1             |

| (×)= [7]      | int     | 1              |

| 69= [8]       | int     | 1              |

| (c)= [9]      | int     | -1             |

### 图 43. Packet of Received Bits of Data

This captured data is in the form of an 11-bit code word transmitted three consecutive times. Each code word having a sum of one is then packetized in the format shown in 🛽 44.

| ✓ (= packet      | int[3] | [1,1,1] |

|------------------|--------|---------|

| <b>(×)</b> = [0] | int    | 1       |

| (x)= [1]         | int    | 1       |

| (x)= [2]         | int    | 1       |

# 图 44. Packetized Data

### 3.8 System Utilization

| RESOURCE NAME | TYPE      | PURPOSE                                                                                                  | USAGE AND RESTRICTIONS                                           |

|---------------|-----------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| ADCINA        | Module/IO | ADC input for sampling input signal                                                                      | Restricted to ADC inputs that are available an accessible        |

| EPWM1         | Module    | Triggers the interrupt for the signal sampling routine                                                   | Can be configured a number of ways to meet desired ISR frequency |

| EPWM2         | Module    | Triggers the interrupt for running the bit decision routine                                              | Can be configured a number of ways to meet desired ISR frequency |

| SPI           | Module/IO | For accessing the AFE03x's registers during initialization                                               | Only needed for initialization for the RX solution               |

| CPU Timer 2   | Module    | Can be used to create a timeout when no<br>information has been received for a certain<br>amount of time | ISR may have lower priority than other set ISRs                  |

# 表 8. C2000™ Resources Used

表 9 lists the number of CPU cycles consumed by each fsk\_corr\_detect library function.

| FUNCTION NAME                       | DESCRIPTION                                                                                                                          | CPU CYCLES | TYPE           |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|

| FSK_CORR_DETECTOR_INI<br>T          | Initializes variables used by the FSK library, based off the frequency parameters the user sets within a fsk_corr_detector structure | 60         | Initialization |

| FSK_CORR_DETECTOR_RU<br>N           | Performs necessary calculations on the sampled ADC values to demodulate the input signal                                             | 59         | Run time       |

| FSK_CORR_DETECTOR_Ove<br>rSampl_RUN | Performs the logic to decipher if a bit has been received                                                                            | 134        | Run time       |

| Packetize                           | Takes a received message data buffer and builds usable code words and packets                                                        | 1381       | Run time       |

### 表 9. Library Function CPU Cycles

The run-time CPU utilization of the software solution, when being used in its default state and receiving information specified in  $\frac{1}{5}$  1, can be calculated using the information in  $\frac{1}{5}$  10.

### 表 10. Software ISR and Function Usage

| ISR OR FUNCTION        | AVERAGE CYCLES | FREQUENCY OF EXECUTION |

|------------------------|----------------|------------------------|

| ADC Sampling ISR       | 74             | 300 kHz                |

| Bit-decision ISR       | 175            | Approximately 586 Hz   |

| Packetization Function | 1381           | Approximately 1 Hz     |

CPU utilization equation:

CPU Utilization = ((74 ×  $f_s$  + 175 × 3 ×  $f_{bit}$  + 1381 ×  $f_{Packetization}$ ) /  $f_{CPU}$ ) × 100% (10)

CPU utilization at F28379D's 200-MHz clocking frequency: CPU Utilization = ((74 × 300 kHz + 175 × 586 Hz + 1381 × 1 Hz) / 200 MHz) × 100% = 11.15% (11)

# 3.9 Device Dependency and Porting

While the FSK receiver solution is built for and tested on the F2837xD, the solution should directly port to devices that have floating point unit (FPU) and trigonometric math unit (TMU) support. The fsk\_corr\_detect library's functionality is dependent on the FPU and TMU being present. Devices with both FPU and TMU support include the F2837xD, F2837xS, F2807x, and F28004x.

# 3.10 Tuning and Calibration

The C2000's AFE031 system can be tuned and calibrated for receiving within software and hardware. These concepts are discussed in the following subsections.

# 3.11 Setting the AFE03x's PGAs

The AFE031's PGAs along the RX path are used to amplify or attenuate the input signal to be within the desired voltage range before entering the C2000's ADC. It is desired for the signal at the ADC pin to be within the range defined by the ADC's reference voltage. For example, the F28379D LaunchPad's reference voltage is 3 V; therefore, the signal should be within a range of 0 V to 3 V to prevent clipping.

For best results, this signal should be close to this voltage range, without going over or under, to use the full resolution of the ADC. Use the AFE031's PGAs to tune the signal to meet this criteria using the gain value settings in  $\overline{x}$  4. For how to set the RX PGA values within software, see Step 10 of  $\ddagger$  3.1.2.1.1.

# 3.12 Automatic Gain Control (AGC)

If the receiver system is to be used within an application that has an input signal with inconsistent amplitudes, it may be necessary to implement some form of automatic gain control (AGC) to manage the signal before it reaches the C2000's ADC input. The AGC would be a closed-loop feedback system that measures the amplitude of the input signal, or a related response, and based on what is observed amplify or attenuate the signal.

The AFE031's internal PGAs could be leveraged to dynamically amplify or attenuate the signal to be within the desired amplitude range. For gain select times of the two PGAs along the RX path, see *Powerline Communications Analog Front-End*.

Another approach would be to perform the AGC externally before the signal enters the C2000 AFE031 system. However, this requires additional circuitry involving a variable gain amplifier (VGA) to be added.

# 3.13 Setting the Bit Detection Threshold

The *detection\_threshold* member of the FSK\_CORR\_DETECTOR structure is in direct relation to the accuracy of bit detections. The threshold must be set to a value between 0 and 1. If set to a value too high, then bits will not be detected at all, but if set too low then there could be confusion as to what constitutes a mark or space bit and cause bit errors. It may take some trial and error to find a value that consistently detects bits without errors.

# 3.14 Setting the Bit Detection Threshold (Filtered)

The detection\_threshold member of the FSK\_CORR\_DETECTOR structure is directly related to the accuracy of bit detections. The threshold must be set to a value between 0 and 1. If set to a value too high, then bits will not be detected at all; however, if set to a value too low, then there could be confusion as to what constitutes a mark or space bit resulting in bit errors.

In the software example, the *bit\_detect\_strength* variable that is assigned a value by the FSK\_CORR\_DETECT\_STRENGTH library function provides some insight into what the detection\_threshold member should be set to. The bit\_detect\_strength variable is set to a value after each execution of the library function. The detection\_threshold member needs to be given a value at or below the bit\_detect\_strength calculated while receiving a mark or space signal. Compare the bit\_detect\_strength value witnessed when receiving a mark signal to the value witnessed when receiving a space signal. The detection\_threshold be set to a value at or below the lower of the two values witnessed. It may take some trial and error to find a value that consistently detects bits without errors.

# 3.15 FSK Correlation Detector Library

For inquiries related to the FSK correlation detector library used in the software example, email the following address:

# C2000-fsk\_rx\_source\_access@list.ti.com

To request access to the library's source code (contingent on end application review and export control approval from Texas Instruments, Inc), follow the instructions at: https://www.ti.com/licreg/docs/swlicexportcontrol.tsp?form\_id=268791&prod\_no=C2000-AFE031\_FSK\_RX\_SOURCE&ref\_url=c2000.

Design Files

### 4 Design Files

### 4.1 Schematics

To download the schematics, see the design files at TIDA-060001.

### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-060001.

### 4.3 PCB Layout Recommendations

For thermal considerations for PCB layout, see Powerline Communications Analog Front-End.

### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-060001.

### 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-060001.

### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-060001.

### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-060001.

### 5 Software Files

To download the software files, see the design files at C2000Ware.

### 6 Related Documentation

- 1. Texas Instruments, Spread-Frequency Shift Keying Power Line Modem Software Architecture Application Report

- 2. SunSpec Alliance, SunSpec Homepage

- 3. Texas Instruments, Analog Front-End Design for a Narrowband Power-Line Communications Modem Using the AFE031 Application Report

- 4. Texas Instruments, AFE031 Powerline Communications Analog Front-End Data Sheet

- 5. Texas Instruments, *DC Power-Line Communication Reference Design*

### 6.1 商标

C2000, LaunchPad, E2E, BoosterPack, DCS-Control, SimpleLink are trademarks of Texas Instruments. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. SunSpec is a registered trademark of SunSpec Alliance, Inc. Wi-Fi is a registered trademark of Wi-Fi Alliance. All other trademarks are the property of their respective owners.

### 7 Terminology

- PLC— Powerline communications

- FSK— Frequency shift keying

HRPWM— High-resolution pulse width modulation

AFE— Analog front end

# 8 About the Authors

VINCENT RODRIQUEZ is an applications engineer within the SimpleLink<sup>™</sup> Wi-Fi<sup>®</sup> group, where he works on hardware and software development, creating collateral and reference designs showcasing the CC31xx/CC32xx Wi-Fi devices. Vince graduated from Texas A&M University with a bachelor's of science in electronic systems engineering technology in 2016.

**ERROL LEON** is an applications engineer that specializes in analog signal chain design at Texas Instruments, where he is responsible for developing application notes, evaluation modules, and reference design solutions. Errol earned his master of science in electrical engineering (MSEE) and bachelor (BSEE) from California Polytechic University San Luis Obispo. Errol is also a member of the Institute of Electrical and Electronics Engineers (IEEE).

**KEVIN ALLEN** is an applications engineer within the C2000 Group, where he works on creating collateral and supporting C2000 devices. Kevin graduated from the University of Texas Dallas with a bachelor's of science in electrical engineering.

### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试 外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司