Design Guide: TIDM-1011

# 适用于 C2000 MCU 的 Tamagawa T-Format 绝对编码器主接

## 口参考设计

## 说明

C2000™ 微控制器 (MCU) Position Manager 技术可提供集成式解决方案来连接最常用的数字和模拟位置传感器,而无需外部现场可编程门阵列 (FPGA) 或应用特定集成电路 (ASIC)。Position manager 的评估套件BoosterPack™ 是一种用于评估各种编码器接口的灵活且具有成本效益的平台,旨在与多个 C2000 LaunchPad™ 开发套件一起工作。该参考设计的软件专门用于实施 T-Format(位置编码器的数字双向接口)。此参考设计包括高度优化且易于使用的软件参考例程,支持使用 Position Manager BoosterPack 来运行 T-Format 位置编码器。

## 资源

TIDM-1011 设计文件夹

LAUNCHXL-F28P65X LAUNCHXL-F28379D LAUNCHXL-F280039C LAUNCHXL-F280049C 工具文件夹

LAUNCHXL-F280025C

SN65HVD78、TLV702、TPS22918-Q1 产品文件夹

C2000WARE-MOTORCONTROL-SDK 工具文件夹

咨询我们的 TI E2E™ 支持专家

## 特性

- 用于位置编码器接口的灵活、低压 BoosterPack 评估平台

- 用于 T-Format 编码器接口的集成 MCU 解决方案, 无需额外的 FPGA

- 可通过驱动程序函数和接口函数提供的数据结构轻 松执行连接 T-Format 的命令

- 支持 2.5MBPS 的时钟频率, 经验证运行电缆长度 最大为 100m

- 包括展示 T-Format 实现的评估软件示例

## 应用

- 工业

- 电机驱动器

## 1 系统说明

工业驱动器(如伺服驱动器)需要精确、高度可靠且低延迟的位置反馈。Tamagawa 的 T-Format 协议旨在实现传感器和控制器之间的数字数据串行传输。传感器可以是编码器(线性、旋转或角度)、接触式探头或加速计。后续电子器件或控制器包括数控装置、伺服放大器和可编程逻辑控制器。

TIDM-1011 设计实现了连接到 C2000 LaunchPad 的 T-Format 编码器接口。T-Format 是基于 RS-485 标准的纯串行数字接口。T-Format 能够传输位置值以及其他物理量,并支持对编码器的内部存储器进行读取和写入。传输的数据类型包括绝对位置、转数、温度、参数、诊断等。从接口发送到编码器的命令选择响应数据类型。

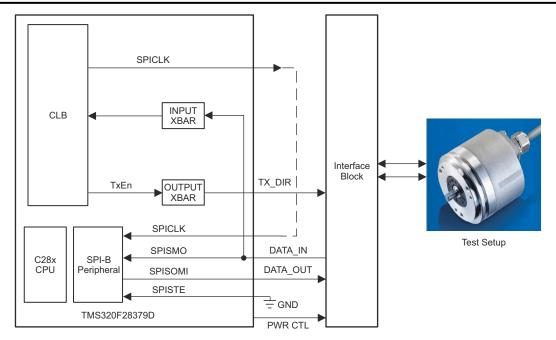

图 1-1 展示了连接到 BOOSTXL POSMGR 和 F28379D LaunchPad 编码器接口的 T-format 编码器。

图 1-1. 具有 T-Format 位置编码器接口的工业伺服驱动器

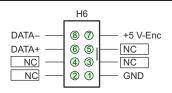

支持 T-Format 的位置编码器通过单根 4 线屏蔽电缆连接到 TIDM-1011 器件。RS-485 用作 T-Format 编码器的物理层。使用的四根线为:

- DATA+和 DATA-:用于通信数据的差分信号

- 电源和接地:编码器电源和接地

德州仪器 (TI) 的 C2000 T-Format (PM\_tformat) 编码器接口实现无需 FPGA 或 CPLD 等外部硬件,即可将 T-Format 编码器连接到 C2000 器件。此参考设计具有以下特性:

- T-Format 协议所需的 2.5Mbps 时钟频率

- 集成电缆传播延迟补偿功能,可实现可变电缆长度,经验证最长可达 100m

- 软件驱动程序功能:

- 执行与编码器的事务。这包括发送请求和接收响应。

- 计算 CRC

- 将接收到的 CRC 与计算得出的 CRC 进行比较

- 打包和解压缩数据

此参考设计包括所有源代码。用户可以根据其应用的需要进行实现所需的任何更改。

#### 备注

该参考设计仅提供 T-Format 规范中定义的命令的基本接口驱动程序。用户必须使用该设计提供的基本接口来开发所有更高级别的应用软件。

www.ti.com.cn 系统说明

## 1.1 关键系统规格

表 1-1. 关键系统规格

| 参数        | 规格                       | 详细信息     |

|-----------|--------------------------|----------|

| 输入电压      | 5V <sup>(1)</sup>        | 节 3.3.1  |

| 输出电压(编码器) | 5V                       | 节 3.3.1  |

| 支持的协议     | T-Format                 | Tamagawa |

| 频率(编码器接口) | 约 2.5MBPS                | Tamagawa |

| 编码器位数     | T-Format 协议标准            | Tamagawa |

| CPU 周期数   | C2000 T-Format 编码器接口基准测试 | 节 3.3.5  |

(1) 编码器连接到 TIDM-1011 器件的时间决定了该电源的电流限制。TI 建议使用具有可调电流限制的通用台式可调电源。

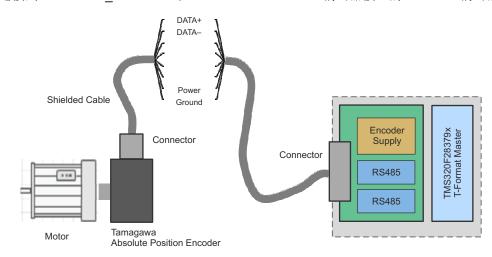

## 2 系统概述

C2000 T-Format TIDM-1011 参考设计是硬件和软件的组合。核心硬件组件是 C2000 实时微控制器 (MCU) 和 RS-485 收发器。C2000 LaunchPad 和包含 RS-485 收发器的 TIDM-1011 BoosterPack 是此实现中使用的电路 板。C2000 电机控制 SDK 软件包包含必要的软件。该软件包括一个用于实现主要 T-format 接口功能的库和一个用于演示 T-Format 通信的系统级示例。

T-Format 编码器接口采用 C2000 CLB (可配置逻辑块)和 SPI (串行外设接口)模块。CLB 控制 SPI 时钟并补偿电缆传播延迟。CLB 还控制 RS-485 收发器发送使能。SPI 模块充当 RS-485 物理层的发送/接收接口。固件用 C 语言编写,并在 C2000 MCU 的 C28x 上运行。

C2000 LaunchPad 可为 TIDM-1011 RS-485 收发器供电并为编码器提供 5V 电压。如果编码器规范要求的电流高于 LaunchPad 可提供的电流,也可以单独提供 5V 电压。

在启动期间,C28x 上运行的应用程序会初始化 MCU 时钟并配置引脚多路复用器。MCU 的 SPI 和 CLB 也根据需要配置用于发送和接收数据。

## 2.1 方框图

图 2-1. TIDM-1011 系统方框图

## 2.2 重点产品

TIDM-1011 参考设计硬件包含一个 C2000 LaunchPad 和一个 BOOSTXL-POSMGR BoosterPack。本节介绍使用 的主要器件。有关这些每个器件的更多信息,请参阅 Tl.com 上相应的产品文件夹。

#### 2.2.1 C2000 实时 MCU LaunchPad

多个 LaunchPad 套件都支持 TIDM-1011 参考设计(请参阅表 2-1)。表 2-1 中列出的每个 C2000 实时微控制器 都具有可配置逻辑块 (CLB)。编码器接口广泛使用 CLB。CLB 外设是 C2000 器件独有的,允许用户在无需外部 FPGA 或 CLPD 的情况下整合自定义逻辑。CLB 由组合在一起以启用自定义数字逻辑的子模块组成。子模块包 括:有限状态机(FSM)、查找表(LUT)和计数器。CLB还与现有片上控制外设连接,以增强功能并提供设计选

如需详细了解 CLB,请访问 "C2000 Academy 可配置逻辑块"模块。

具有 CLB 的器件包括:

#### TMS320F28379D MCU :

在两个 200MHz C28x CPU 和两个 200MHz 实时控制协处理器 (CLA) 之间提供 800MIPS 的总体系统性能。这 款强大的 MCU 包含 1MB 的板载闪存以及独特性能的外设,例如 16 位或 12 位模数转换器 (ADC)、比较器、 12 位数模转换器 (DAC)、△-∑ 同步滤波器、HRPWM、eCAP、eQEP 和 CAN 等。请在 TMS320F28379D 器件产品文件夹中查找完整的器件特性和规格。

TMS320F280039C MCU:

在 120MHz C28x CPU 和 120MHz CLA 之间提供 240MIPS。此 MCU 包含高达 384kB 的片上闪存,并包含 3 个 12 位 ADC 和增强型可配置逻辑块 (CLB) 等。请在 TMS320F280039C 器件产品文件夹中查找完整的器件

• 表 2-1 列出了其他受支持的器件、对应的产品文件夹和 LaunchPad 开发套件。

| 表 2-1. | 支持的器件和 | LaunchPad |

|--------|--------|-----------|

|--------|--------|-----------|

| MCU 器件产品文件夹 <sup>(2)</sup> |

|----------------------------|

| TMS320F28379D              |

| TMS320F280049C             |

| TMS320F280025C             |

| TMS320F280039C             |

| TMS320F28388D              |

| TMDS320F28P650DK9          |

|                            |

<sup>(1)</sup> TMS320F28388D 器件系列没有 LaunchPad 开发套件。您必须通过其他方式提供与 RS-485 物理接口的连接。选项包括 (1) 您自己的硬 件, (2) 与 BOOSTXL POSMGR 连线的 controlCard, 或 (3) TMXIDDK379D。

#### 2.2.2 SN65HVD78

SN65HVD78 器件将一个差分驱动器和一个差分接收器组合在一起,这两个器件由一个 3.3V 单电源供电。驱动器 差分输出和接收器差分输入通过内部连接,构成一个适用于半双工(两线制总线)通信的总线端口。这些器件都 具有宽共模电压范围,因而适用于长线缆上的多点应用。

请在 SN65HVD78 产品文件夹中查找完整的器件特性和规格。

## 2.2.3 TLV702

TLV702 系列低压降 (LDO) 线性稳压器是具有出色线路和负载瞬态性能的低静态电流器件。所有器件版本具有热 关断和电流限值以保证安全。这些器件在不产生输出负载的情况下可调节至特定的精度。

请在 TLV702 产品文件夹中查找完整的器件特性和规格。

TIDM-1011 参考设计需要一个具有可配置逻辑块 (CLB) 类型 1 或更高版本 MCU 的 C2000 LaunchPad。所示为此版本发布时支持的器 件。可能存在其他适用器件。

www.ti.com.cn 系统概述

#### 2.2.4 TPS22918-Q1

TPS22918-Q1 是一款单通道负载开关,可对上升时间和快速输出放电进行配置。该器件包含一个可支持 2A 最大连续电流的 N 沟道 MOSFET。开关由一个开关输入控制,能够直接连接低电压控制信号。

请在 TPS22918-Q1 产品文件夹中查找完整的器件特性和规格。

#### 2.3 设计注意事项

本节提供以下方面的内容:

- 1. Tamagawa T-Format 协议概述。

- 2. C2000 T-Format 编码器接口概述。

- 3. TIDM-1011 硬件 (BOOSTXL-POSMGR BoosterPack) 实现。

- 4. C2000 MCU 实现,包括所需的输入/输出、CRC 计算和 CLB 设计。

- 5. C2000 T-Format 编码器接口软件库概述。

#### 备注

本节仅提供实现细节。有关以下方面的信息:

- 硬件要求、设置和测试:请参考节3。

- 软件:安装和运行软件:参阅:《C2000 T-Format 编码器接口软件指南》(html, pdf)。该软件指 南包括以下文档:

- 通信演示

- T-Format 应用程序编程接口 (API)

- 将库整合到您自己的解决方案中

- 从以前的版本迁移

## 2.3.1 Tamagawa T-Format 协议

Tamagawa 是一家编码器技术制造商,该项技术在机床、机器人、电机驱动等领域用于获取高精度位置信息。 Tamagawa 旋转编码器主要分为两种类型:增量编码器或绝对编码器。增量编码器提供脉冲序列,而绝对编码器 提供绝对数字值。绝对编码器包括单圈和多圈两种类型。

TIDM-1011 参考设计主要针对通过 RS-485 线路驱动器提供数字输出的绝对编码器。TIDM-1011 支持的事务协议格式称为 T-Format。

#### 备注

本节概述了 T-Format 协议。有关具体信息,请参阅 Tamagawa 提供的 T-Format 规范。

#### 备注

并非 Tamagawa 生产的所有编码器都使用 T-Format 协议。请检查编码器的规格。

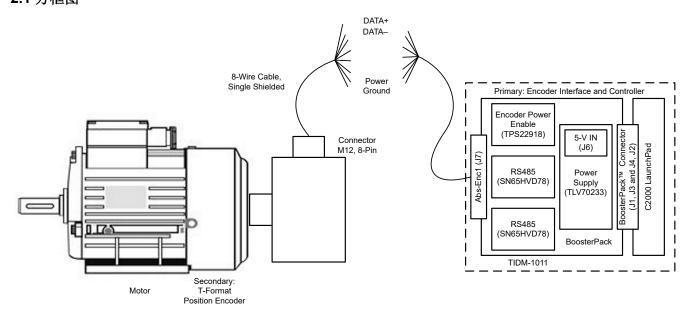

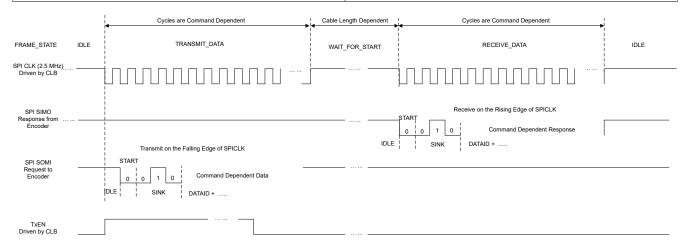

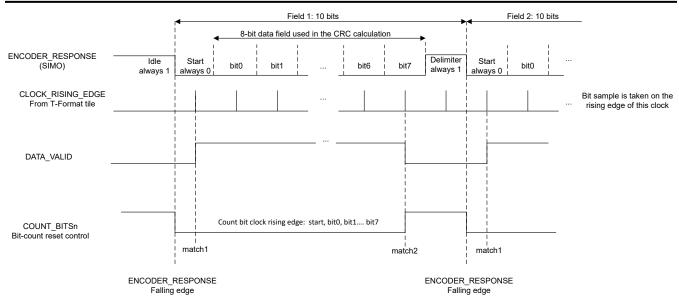

C2000 T-Format 编码器接口提供了控制器与编码器通信所需的物理层。此编码器接口提供 RS-485 驱动控制,以便通过编码器发送和接收数字信息。在这种情况下,T-Format 事务是从控制器发送的请求以及来自编码器的响应。从编码器接口的角度来看,一个事务可以分为 FRAME\_STATES,如图 2-2 所示:

- 1. 空闲: 无 RS-485 活动

- 2. TRANSMIT DATA:控制器向编码器发送请求

- 3. WAIT\_FOR\_START:等待编码器的响应

- 4. RECEIVE\_DATA:控制器收到编码器的响应

- 5. 返回到 IDLE。

与编码器的每个事务都会重复此模式。

图 2-2. T-Format 帧

#### 备注

图 2-2 包括与 C2000 编码器接口实现相关的信息。例如, CLB 驱动 SPI CLOCK 和 TxEN 信号。

T-Format 通信协议大致分为三种类型的事务:数据读取、复位和 EEPROM 访问。每个事务都有一个由协议定义的唯一数据 ID。数据 ID 用于标识控制器通过编码器接口发出的特定请求。

| ベ Z-Z. I-i Offiliat 争力 |       |                 |  |

|------------------------|-------|-----------------|--|

| 事务类型                   | 数据 ID | 传输              |  |

| 读取                     | ID 0  | 旋转一圈的绝对数据       |  |

|                        | ID 1  | 多圈数据            |  |

|                        | ID 2  | 编码器 ID          |  |

|                        | ID 3  | 以上所有内容加上编码器错误状态 |  |

| 复位                     | ID 7  | 复位旋转一圈的绝对数据     |  |

|                        | ID 8  | 复位多圈数据          |  |

|                        | ID C  | 复位错误            |  |

| EEPROM                 | ID D  | 读取编码器的 EEPROM   |  |

|                        | ID 6  | 写入编码器 EEPROM    |  |

|                        |       |                 |  |

表 2-2 T-Format 事务

每个事务由 10 位字段组成。每个字段具有表 2-3 中所示的格式。第一个位是起始位(始终为 0),最后一个位是定界位(始终为 1)。起始位和定界位之间 8 位数据的内容取决于字段的具体类型。

#### 表 2-3. T-Format 字段格式

|    | 位 1          | 位 2 | 位 3 | 位 4 | 位 5                       | 位 6 | 位 7             | 位 8 | 位 9 | 位 10         |

|----|--------------|-----|-----|-----|---------------------------|-----|-----------------|-----|-----|--------------|

| 内容 | 起始位<br>始终为 0 |     | 内   |     | 个数据位:最<br>字段。这 <b>8</b> 6 |     | E.<br>E CRC 计算中 | ١.  |     | 定界位<br>始终为 1 |

T-Format 协议定义的字段为:

ControlField (CF) 每个请求和每个响应中的第一个字段。ControlField 包含事务的唯一数据 ID。

StatusField (SF) 来自编码器的状态信息。

**DataFields (DFx)** 来自编码器的信息。DataFields 的内容和数量取决于事务。DataFields 的示例包括编码器

的 ID、位置信息和错误代码。最多可以有 8 个 DataFields。

**CRCField** 数据的 8 位循环冗余校验 (CRC)。CRCField 是 EEPROM 读取或写入请求的最后一个字

段。CRCField 始终是编码器响应中的最后一个字段。

www.ti.com.cn 系统概述

**EEPROM** AddressField (ADF)

要在 EEPROM 事务中读取或写入的地址。

**EEPROM DataField** 包含在 EEPROM 事务中读取的数据或要写入的数据。 (EDF)

备注

有关每个字段的具体内容,请参阅 Tamagawa 中提供的 T-Format 规范。

请求中使用的字段如表 2-4 所示。控制器会通过编码器接口发送请求来开始事务。请求会以包含数据 ID 的 ControlField 开始。编码器使用数据 ID 来识别所请求的确切事务。对于读取或复位请求,只需要 ControlField。 在 EEPROM 读取或写入的情况下,控制器还会发送一个 EEPROM AddressField 和 EEPROM DataField (用于 写入),后跟一个 CRCField。

#### 表 2-4. T-Format 请求字段

| 请求类型      | 传输的字段        |                     |                  |                         |  |

|-----------|--------------|---------------------|------------------|-------------------------|--|

| 读取        | ControlField |                     |                  |                         |  |

| 复位        | ControlField |                     |                  |                         |  |

| EEPROM 写入 | ControlField | EEPROM AddressField | EEPROM DataField | CRCField <sup>(1)</sup> |  |

| EEPROM 读取 | ControlField | EEPROM AddressField | CRCField         |                         |  |

(1) CRC 计算包括控制、EEPROM 地址和 EEPROM 数据字段中的 8 位数据。不包括起始位和定界位。

编码器响应中使用的字段取决于特定的请求。对于读数和复位事务(表 2-5),编码器会以 ControlField 的回波进 行响应,之后是 StatusField 和一个或多个 DataFields。最后,编码器会始终发送一个 CRCField。CRCField 可用 作已接收数据的完整性检查。

#### 表 2-5. 用于读取和复位的 T-Format 响应字段

| 数据 ID | 类型 | 控制<br>字段 <sup>(1)</sup> | 状态<br>字段 |                     | DataField (DF0:DF1:DF7) + CRC (2) (3) |      |      |      |      |      |                     |     |

|-------|----|-------------------------|----------|---------------------|---------------------------------------|------|------|------|------|------|---------------------|-----|

| ID 0  | 读取 | CF                      | SF       | ABS0 <sup>(4)</sup> | ABS1                                  | ABS2 | CRC  |      |      |      |                     |     |

| ID 1  | 读取 | CF                      | SF       | ABM0 <sup>(5)</sup> | ABM1                                  | ABM2 | CRC  |      |      |      |                     |     |

| ID 2  | 读取 | CF                      | SF       | ENID(6)             | CRC                                   |      |      | •    |      |      |                     |     |

| ID 3  | 读取 | CF                      | SF       | ABS0                | ABS1                                  | ABS2 | ENID | ABM0 | ABM1 | ABM2 | ALMC <sup>(7)</sup> | CRC |

| ID 7  | 复位 | CF                      | SF       | ABS0                | ABS1                                  | ABS2 | CRC  |      | '    |      |                     |     |

| ID 8  | 复位 | CF                      | SF       | ABS0                | ABS1                                  | ABS2 | CRC  |      |      |      |                     |     |

| ID C  | 复位 | CF                      | SF       | ABS0                | ABS1                                  | ABS2 | CRC  |      |      |      |                     |     |

- (1) CF: ControlField。与请求中发送的 ControlField 匹配。

- (2) DF: DataField。最多8个字段,具体取决于事务。

- (3) CRCField 始终在最后使用的 DataField 之后立即传输。CRC 包括所用 CF + SF + DataFields 中的 8 位数据。不包括每个字段的起始位 和定界位。

- ABS:旋转一圈的绝对数据。使用 3 个字段。

- (5) ABM:多圈数据。使用3个字段。

- ENID:编码器 ID。一个字段。

- ALMC:编码器错误。一个字段

在以下数据读取示例中,控制器请求多圈数据(数据 ID 1)。参考表 2-5,响应 DataFields 对应于多圈数据 (ABM0:ABM1:ABM2).

#### 表 2-6. 数据读取示例

| 请求: | 数据 ID 1 的<br>ControlField |             |            |            |            |     |

|-----|---------------------------|-------------|------------|------------|------------|-----|

| 响应: | 数据 ID 1 的<br>ControlField | StatusField | DataField0 | DataField1 | DataField2 | CRC |

对于 EEPROM 事务,编码器会以 ControlField + EEPROM AddressField + EEPROM DataField + CRCField 进行响应,如表 2-7 所示。

#### 表 2-7. EEPROM 读取/写入响应字段

| 数据 ID | 申请 | 字段 0         | 字段 1                   | 字段 2                               | 字段 3                    |

|-------|----|--------------|------------------------|------------------------------------|-------------------------|

| ID 6  | 写入 | ControlField | EEPROM<br>AddressField | EEPROM<br>DataField <sup>(1)</sup> | CRCField <sup>(3)</sup> |

| ID D  | 读取 | ControlField | EEPROM<br>AddressField | EEPROM<br>DataField <sup>(2)</sup> | CRCField                |

- (1) 从编码器 EEPROM 读取的数据。

- (2) 写入 EEPROM 的数据。这是请求中 DataField 的回声。

- (3) CRC 计算包括控制、EEPROM 地址和 EEPROM 数据字段中的 8 位数据。不包括每个字段的起始位和定界位。

#### 2.3.2 C2000 T-Format 编码器接口概述

通过 T-Format 编码器接口进行的通信主要由以下组件实现:

- CPU (C28x)

- 配置器件、CLB和SPI

- 打包和解包数据

- 计算 EEPROM 命令的发送 CRC

- 仅限 F2837xD: 计算接收数据的 CRC

- 将计算出的 CRC 与接收到的 CRC 进行比较

- 可配置逻辑块 (CLB)

- 控制 SPI 时钟

- 控制到 RS-485 收发器的发送使能信号

- 根据接口的要求,测量和补偿电缆传播延迟

- 计算接收数据的 CRC (F2837xD 上不提供该功能)

- 串行外设接口 (SPI)

- 执行编码器数据发送和接收

- 器件互连 (XBAR 或 CLB XBAR )

- 路由进出 CLB 和器件的信号

- 外部接口块

- 带有 RS-485 差分线路驱动器的 TIDM-1011 板

## 备注

根据器件特性,会使用不同的方法来计算 CRC。请参阅节 2.3.5 以了解相关信息。

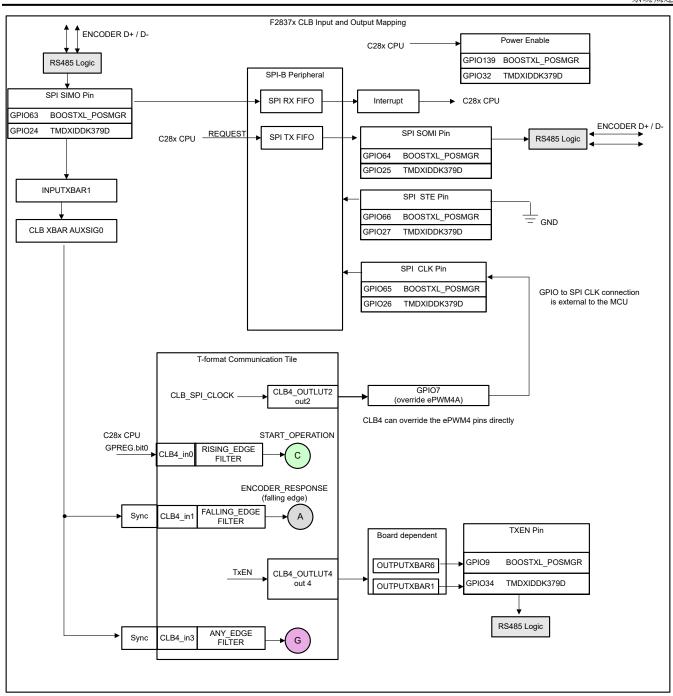

图 2-3 展示了 T-Format 编码器接口连接。

www.ti.com.cn 系统概述

图 2-3. TMS320F28379D 内的 T-Format 实现图

本节的其余部分介绍了设计的以下方面:

- TIDM-1011 硬件 (BOOSTXL-POSMGR)

- 包括 CLB 设计的 C2000 MCU 资源

- 编码器接口使用的 C2000 软件

#### 2.3.3 TIDM-1011 板实现

TIDM-1011 板提供以下功能:

- 用于 C2000 MCU 和编码器之间 RS-485 通信的差分线路驱动器和接收器。

- 从 MCU 路由到 RS-485 驱动器/接收器方向控制的 TxEN 信号。

- 路由到 GPIO 的 SPICLK 信号,在其中可由 CLB 外设控制。对于除 F2837x 系列之外的所有受支持器件,此连接是可选的。

#### 备注

TIDM-1011 子卡与 Position Manager BoosterPack 插件模块 (BOOSTXL-POSMGR) 相同,这意味着 TIDM-1011 可以与其他几种类型的位置编码器相连接。默认情况下,该板兼容所有功能。该参考设计主 要针对 T-Format 绝对编码器协议,可以忽略未提及的硬件模块。

表 2-8 列出了 TIDM-1011 T-Format 实现所使用的连接器及其功能。

表 2-8. TIDM-1011 板和 BOOSTXL-POSMGR 连接器

| 连接器                 | 说明                           | 由 TIDM-1011 使用   |

|---------------------|------------------------------|------------------|

| Abs-Enc-1 (J7)      | T-Format 和其他绝对编码器            | 是,LaunchPad 站点 2 |

| Abs-Enc-2 (J8)      | T-Format 和其他绝对编码器            | 否                |

| Abs-Enc-2 破孔 (J10)  | 允许在站点 2 使用两个绝对编码器 (使用跳<br>线) | 否                |

| SinCos (J14)        | SinCos 编码器                   | 否                |

| 旋转变压器 ( J14 和 J15 ) | 具有 15V 激励电路的旋转变压器接口          | 否                |

| PTO (J17)           | 脉冲序列输出                       | 否                |

| J1、J3 和 J4、J2       | BoosterPack 连接器              | 是                |

| J6                  | 5V 直流电源输入                    | 是                |

#### 表 2-8. TIDM-1011 板和 BOOSTXL-POSMGR 连接器 (continued)

|     |                | , — — , — , — , — , — , — , — , — , — , |

|-----|----------------|-----------------------------------------|

| 连接器 | 说明             | 由 TIDM-1011 使用                          |

| J16 | 15V 直流旋转变压器激励结 | 输入 否                                    |

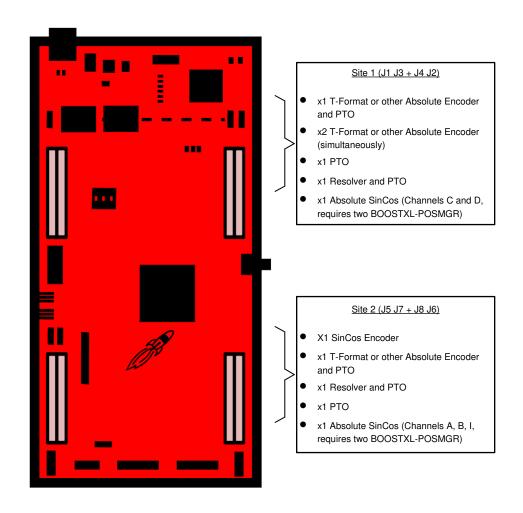

图 2-4 展示了 LaunchPad 每个站点上的编码器支持。

图 2-4. TIDM-1011 板和 BOOSTXL-POSMGR 编码器支持

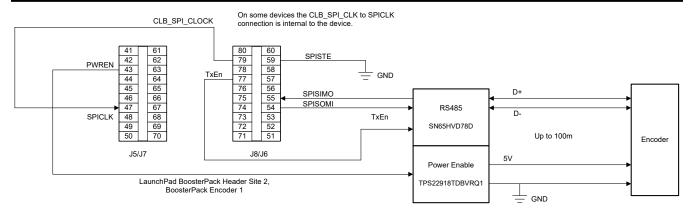

根据提供的信息,TIDM-1011 使用 LaunchPad 站点 2 和 BOOSTXL-POSMGR 的编码器 1 连接。图 2-5 显示了相关连接。TIDM-1011 BoosterPack 的完整原理图可从 BOOSTXL-POSMGR 产品页面下载。

#### 备注

F2837xD 器件需要在 CLB 生成的时钟 (CLB\_SPI\_CLK) 和 SPICLK 引脚之间建立外部连接。在所有其他器件上,CLB 可以直接驱动 SPICLK,无需外部连接。

www.ti.com.cn 系统概述

图 2-5. 具有 BOOSTXL-POSMGR 编码器 1 引脚排列的 LaunchPad Site2

## 2.3.4 MCU 资源要求

表 2-9 列出了 TIDM-1011 参考设计使用的 C2000 实时 MCU 资源。节 2.3.5 中介绍了每个器件的具体信息。

| 资源名称和数量                         | 类型              | 用途                                                    |

|---------------------------------|-----------------|-------------------------------------------------------|

| CLB x 2                         | 1 个逻辑块          | 提供 SPI 时钟、延迟补偿和 TxEn 控制。如果逻辑块已更改,则还必须更新 CLB 的输入/输出路由。 |

|                                 | 1 个逻辑块(可选)      | 在收到消息时计算响应 CRC。此选项仅在具有 CLB 类型 2 或更高版本的器件上可用。          |

| GPIO x 2                        | I/O             | • CLB 输出,RS-485 方向控制 (TxEN)                           |

|                                 |                 | • CPU 编码器功率控制 (PwrCtl)                                |

| GPIO x 1                        | I/O(仅限 F2837xD) | • CLB_SPI_CLK 的 CLB 输出                                |

|                                 |                 | • CLB 类型 1:将此引脚从外部路由到 SPICLK 输                        |

|                                 |                 | $\lambda$ .                                           |

|                                 |                 | • CLB 类型 2 或更高版本:直接从 CLB 为 SPI 模                      |

|                                 |                 | 块提供时钟。无需外部连接,但可用于测试和调                                 |

|                                 |                 | 试。                                                    |

| INPUTXBAR 或 CLB_INPUTXBAR x 1   | 模块、I/O          | 将 SPI SIMO 引脚连接到 CLB。                                 |

| OUTPUTXBAR 或 CLB_OUTPUTXBAR x 1 | 模块、I/O          | 将 CLB 连接到 TxEN (方向控制)。                                |

| SPI x 1                         | 模块和 I/O         | 一个用于在 RS-485 物理层上发送和接收的 SPI 实                         |

表 2-9. TIDM-1011 资源使用情况

#### 2.3.5 特定于器件的资源使用情况

TIDM-1011 使用的特定于器件的资源包括:

CPU 和内存

- 执行 CRC 计算所需的资源。

- 输入和输出信号以及使用的特定 CLB 逻辑块实例。

#### 2.3.5.1 CRC 计算

循环冗余校验 (CRC) 是一种用于通信网络和数据存储的错误检测机制。C2000 MCU 上用于计算 CRC 的器件资源会随着时间的推移而增加。根据器件特性以及是发送还是接收数据,TIDM-1011 会使用不同的资源。表 2-10 中总结了资源使用情况。

模块

表 2-10. 用于 CRC 计算的资源 接件 接收数据 CRC

| 器件      | 接收数据 CRC  | 发送数据 CRC  |

|---------|-----------|-----------|

| F2837xD | C28x+ 查找表 | C28x+ 查找表 |

| F28004x | 可配置逻辑块    | C28x 查找表  |

例。SPI 时钟由 CLB 控制。

各种功能的 CPU 和内存使用情况。

#### 表 2-10. 用于 CRC 计算的资源 (continued)

| 器件     | 接收数据 CRC | 发送数据 CRC       |

|--------|----------|----------------|

| 所有其它内容 | 可配置逻辑块   | C28x 的 VCRC 扩展 |

- 所有 C28x 器件上都提供 C28x 查找表。然而,这种方法是最慢的,并且需要 RAM 内存来存储查找表。 TIDM-1011 仅在没有其他功能的器件上使用查找表。

- 具有 CLB 类型 2 或更高版本的器件上提供**可配置逻辑块 (CRC)**。CLB 使用配置为线性反馈移位寄存器 (LFSR) 的计数器来计算 CRC。该方法一直用于计算接收数据时编码器响应的 CRC。因为无需额外计算,所以 这会释放 C28x 带宽。C28x 直接从计数器寄存器读取 CRC 结果。此方法的成本是用于配置逻辑块的 CLB 逻辑块资源和代码。节 2.3.7 中记录了 CLB CRC 的实现。

- VCRC 是专门用于 CRC 计算的 C28x 指令集扩展。对于较长的信息,该实现比 C28x 查找表更快。此外, VCRC 不需要 RAM 空间来存储查找表。对于具有 VCRC 模块的器件,此方法一直用于计算 EEPROM 读取/ 写入事务中使用的发送数据 CRC。

备注

CRC 方法可在 T-Format 库头文件中选择。

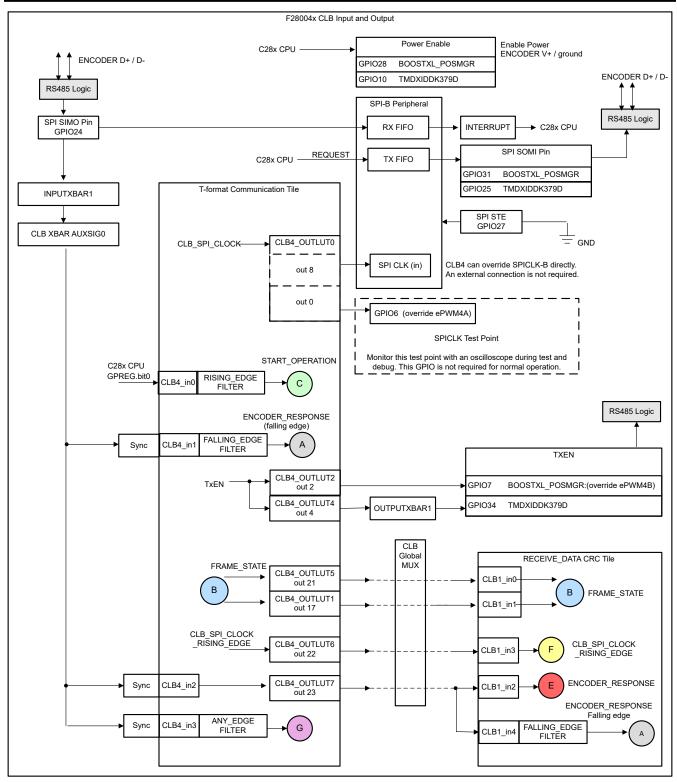

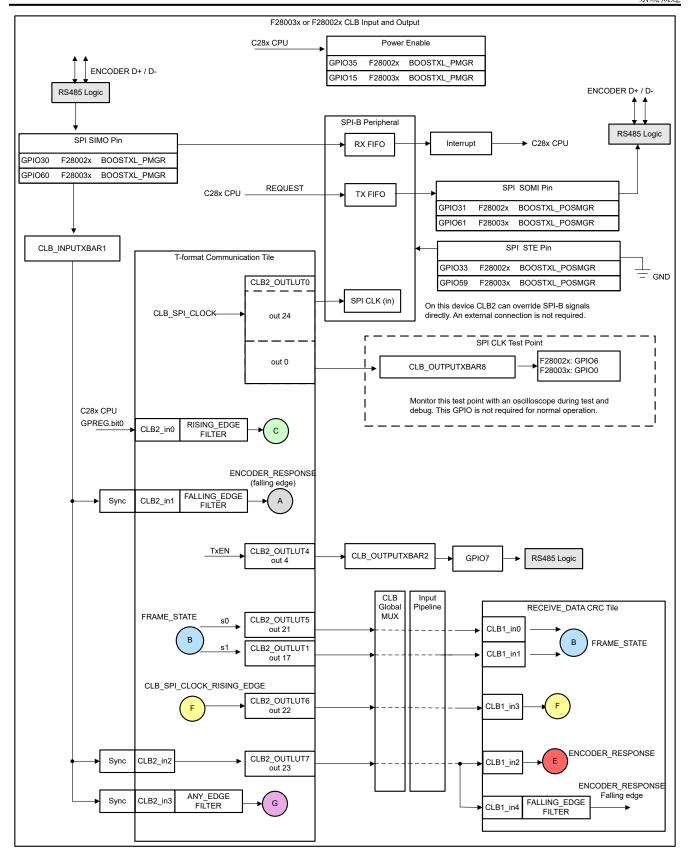

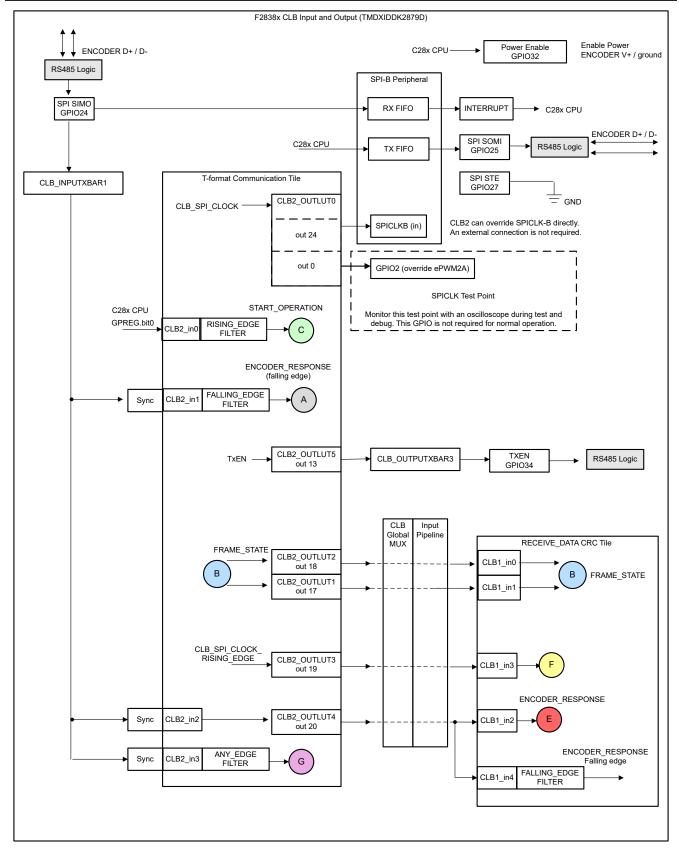

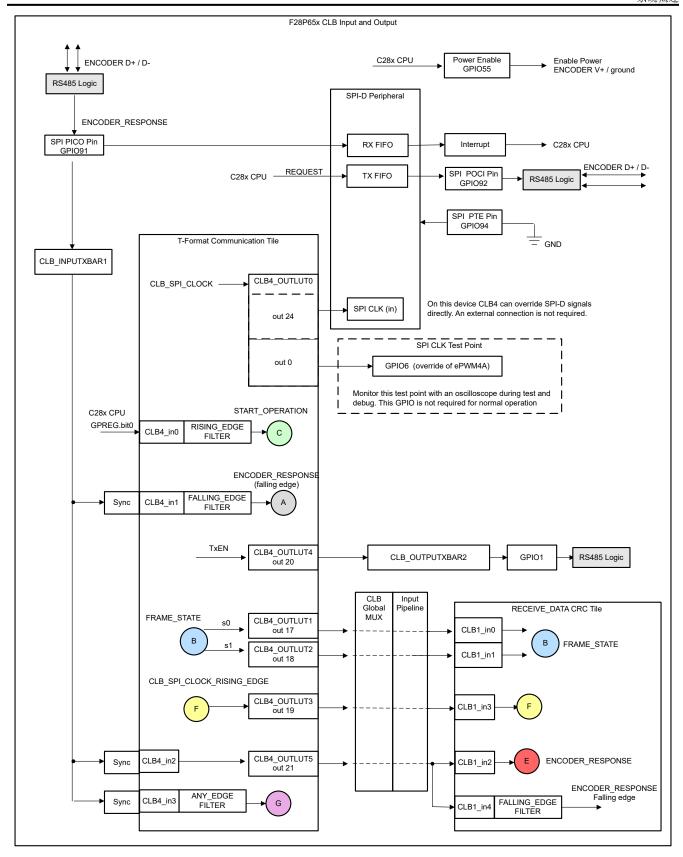

#### 2.3.5.2 输入、输出信号和 CLB 逻辑块

本节介绍了每个器件上使用的输入/输出和 CLB 逻辑块连接。

#### 备注

在输入/输出图中,彩色圆圈中的字母表示端口连接。

• 通信逻辑块:节 2.3.6 中介绍了连接器 A、B、C 和 G。

• CRC 逻辑块: 节 2.3.7 中介绍了连接器 B、F、E 和 A。

使用的 GPIO 引脚和 SPI 模块取决于特定于器件的 LaunchPad 和 BOOSTXL-POSMGR BoosterPack 引脚排列。 CLB 的输入和输出连接取决于该器件的特性。使用的具体逻辑块实例取决于逻辑块覆盖 SPICLK 等其他信号的能力。表 2-11 总结了每个器件系列使用的输入/输出资源。每个器件的 I/O 图详细说明了使用了哪些 GPIO 和 CLB 逻辑块。

#### 表 2-11. 每个器件的输入/输出和逻辑块摘要

| 器件                 | I/O 图                | CLB RX CRC 逻辑块 | SPI 模块 | CLB 至 SPICLK | 其他 I/O                                                              |

|--------------------|----------------------|----------------|--------|--------------|---------------------------------------------------------------------|

| F2837xD            | 图 2-6                | 否              | SPI-B  | 外部连接         | EPWM4B 的逻辑块 4<br>覆盖。 <sup>(1)</sup><br>器件 INPUTXBAR 和<br>OUTPUTXBAR |

| F28004x            | 图 2-7                | 是              | SPI-B  | 直接由 CLB 驱动   | 器件 INPUTXBAR 和<br>OUTPUTXBAR                                        |

| F28003x<br>F28002x | 图 2-8                | 是              | SPI-B  | 直接由 CLB 驱动   | CLB_INPUTXBAR 和<br>CLB_OUTPUTXBAR                                   |

| F2838x             | 图 2-9 <sup>(2)</sup> | 是              | SPI-B  | 直接由 CLB 驱动   | CLB_INPUTXBAR 和<br>CLB_OUTPUTXBAR                                   |

| F28P65x            | 图 2-10               | 是              | SPI-D  | 直接由 CLB 驱动   | CLB_INPUTXBAR 和<br>CLB_OUTPUTXBAR                                   |

- (1) CLB 逻辑块 4 会覆盖 EPWM4B 输出信号以控制 GPIO7。不使用其他 ePWM 功能。

- (2) LaunchPad 开发平台不支持 F2838x 系列。I/O 图中展示了 TMDXIDDKF273XD 硬件平台使用的引脚。

- (3) 对于具有 CRC 逻辑块的器件, I/O 图中展示了通信逻辑块和 CRC 逻辑块之间的连接。

#### 备注

在本文档发布时,TMDXIDDKF273XD 开发套件项目支持 F2837xD 和 F28004x。为方便起见,I/O 图中提供了 BOOSTXL POSMGR 和 TMDXIDDKF273XD 平台的 GPIO。

www.ti.com.cn 系统概述

图 2-6. BOOSTXL\_POSMGR 和 TMDXIDDKF273XD 的 F2837xD 输入、输出和 CLB 用法

系统概述 www.ti.com.cn

图 2-7. BOOSTXL\_POSMGR 和 TMDXIDDKF273XD 的 F28004x 输入、输出和 CLB 用法

www.ti.com.cn 系统概述

图 2-8. BOOSTXL\_POSMGR 的 F28002x 和 F28003x 输入、输出和 CLB 用法

系统概述 www.ti.com.cn

图 2-9. TMDXIDDKF273XD 的 F2838x 输入和输出

www.ti.com.cn 系统概述

图 2-10. BOOSTXL\_POSMGR 的 F28P65x 输入、输出和 CLB 用法

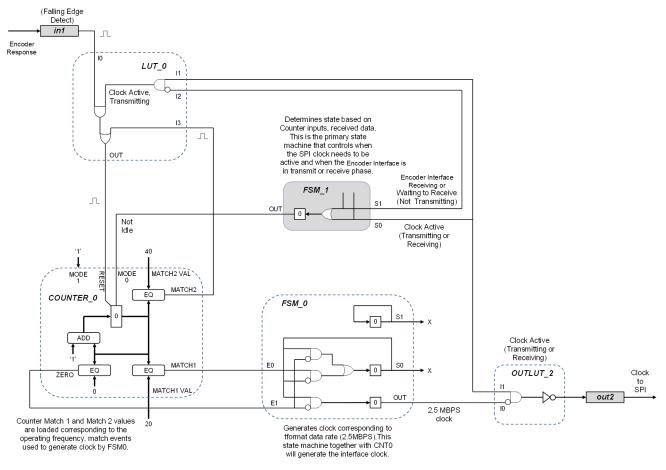

## 2.3.6 CLB T-Format 实现详细信息

CLB 通信逻辑块负责以下工作:

- 为 SPI 提供时钟以发送请求。

- · 监视 SPI SIMO 引脚有没有收到编码器的响应。

- 将 SPICLK 与传入响应对齐。

- 为 SPI 提供时钟以接收响应。

本节介绍了使用三种不同方法设计的通信逻辑块:

- 1. 使用波形显示事务在每个阶段的 CLB 行为。

- 2. 包括子模块互连的 CLB 逻辑块设计。

- 3. 使用逻辑框图。

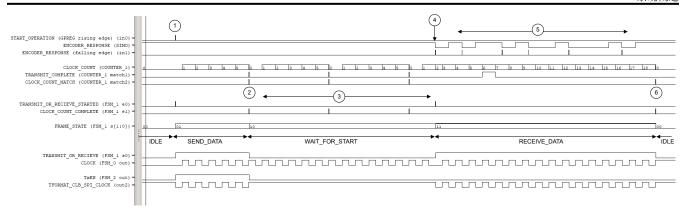

## 2.3.6.1 事务波形

在实现 CLB 设计时,首先使用波形直观地显示所需的 CLB 行为可能会有所帮助。为此,首先考虑一个示例事务。回想一下 T-Format 事务包含请求传输和编码器的响应。传输可以拆分成 FRAME\_STATE,如图 2-11 所示。第一步是将事务的每个元素映射到 CLB 子模块。表 2-12 展示了一个示例映射。

| 表 2-12. T-Forma | :事务到 | <b>CLB</b> | 映射 |

|-----------------|------|------------|----|

|-----------------|------|------------|----|

| 事务行为                  | CLB 映射                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 跟踪 FRAME_STATE        | 有限状态机 (FSM):在给定先前状态和当前输入的情况下转换到新状态。                                                                                                                      |

| 对生成的时钟进行计数            | 计数器:配置为在 TRANSMIT_DATA 和 RECEIVE_DATA 状态期间根据时钟边沿递增。mode0 输入控制计数器何时处于活动状态以及计数器何时停止。利用计数器的匹配值来驱动状态转换(TRANSMIT_DATA 到 WAIT_FOR_START, RECEIVE_DATA 到 IDLE)。 |

| 生成特定宽度的时钟信号           | 此要求会映射到第二个计数器。利用匹配值来生成上升/下降沿的时序。然后,LUT(查找表)会根据该时序生成实际的边沿。                                                                                                |

| 将时钟与编码器的响应对齐          | 生成时钟的计数器可以进行配置,使得边沿转换与编码器的响应正确对齐。                                                                                                                        |

| 仅允许在发送和接收期间为 SPI 提供时钟 | LUT 会在不需要时阻止时钟。                                                                                                                                          |

| 控制 TxEN               | LUT 利用当前的 FRAME_STATE 来控制该信号。                                                                                                                            |

| 指示 CLB 开始事务           | C28x 配置用于事务的计数器和 SPI。CLB GPREG 允许 C28x CPU 直接更改 CLB 输入以开始事务。                                                                                             |

图 2-11. T-Format 事务示例

下一步是实现特定子模块行为的可视化。从快速草图开始,然后在设计开发过程中添加其他详细信息。图 2-12 展示了一个示例波形。

www.ti.com.cn 系统概述

图 2-12. CLB 通信波形

#### 备注

图 2-12 是使用 CLB SystemC 仿真模型生成的,该模型使用自定义输入作为编码器的响应。所发送的请求未在图 2-12 中具体显示。SPI 模块根据 CLB\_SPI\_CLK 在 TRANSMIT\_DATA(或 SEND\_DATA)阶段发送请求。

以下部分中使用了图 2-12中的标记1至6来描述设计中与该标记相对应的特定行为。标记为:

- 1. 从 IDLE 转换到 TRANSMIT DATA (或 SEND DATA)

- 2. 转换到 WAIT FOR START

- 3. 在 WAIT FOR START 期间

- 4. 转换到 RECEIVE DATA

- 5. 在 RECEIVE\_DATA 期间

- 6. 转换回 IDLE

在对每个 FRAME\_STATE 进行说明之后,节 2.3.6.2 给出了完整的逻辑块设计。在查看每种状态的描述期间,请 参阅节 2.3.6.2 和图 2-12。

#### 2.3.6.1.1 IDLE 状态

在 IDLE 状态期间,接口上没有任何活动。C28x 必须首先设置一个请求。T-Format API 提供了设置每种请求类型的函数:

- PM tformat setupCommandReadEEPROM()

- PM tformat setupCommandWriteEEPROM()

- PM tformat setupCommandReadoutOrReset()

\_setupCommand 函数会创建请求数据包,将数据加载到 SPI TX FIFO,并将 CLB 配置为生成发送请求和接收响应所需的 SPI 时钟数。设置完成后,C28x 会通过调用 PM startOperation() 函数启动事务。

#### 参阅:图 2-2,标记(1)。

事务开始时,START\_OPERATION 信号会通过 GPREG 被拉高。GPREG 是 CLB 的通用寄存器,允许 C28x 直接控制逻辑块的输入。START\_OPERATION 会在一个 CLB 时钟周期内保持高电平,因为针对输入启用了 CLB 的上升沿滤波器。此时,主状态机 (FSM\_1) 会通过将 FRAME\_STATE 从 IDLE 移到 TRANSMIT\_DATA 状态进行响应。

## 2.3.6.1.2 TRANSMIT\_DATA 状态

在 TRANSMIT\_DATA (或 SEND\_DATA) 状态期间,编码器接口将请求发送到编码器。该请求会在 SPICLK 的下降沿从 SPI TX FIFO 发出。在 TRANSMIT DATA 期间,CLB 会进行以下操作:

- 通过将 TxEN 信号拉高来启用通过 RS-485 驱动器进行传输。

- 开始生成 CLOCK 信号。CLOCK 成为 CLB SPI CLOCK。

- CLB SPI CLOCK 驱动 SPI 模块时钟。

- CLOCK\_COUNT (COUNTER\_1) 跟踪生成的 CLB\_SPI\_CLOCK 的数量。

在命令设置期间,C28x 将发送传输所需的 CLB\_SPI\_Clock 数量加载到 CLOCK\_COUNT 的 match1 和 match2 中。

#### 参阅:图 2-2,标记(2)。

当达到所需的时钟数量时,CLOCK\_COUNT\_COMPLETE (match2) 和 TRANSMIT\_COMPLETE (match1) 信号会被拉高。影响如下:

- 主状态机转换到 WAIT\_FOR\_START

- CLOCK 信号从 CLB SPI CLOCK 断开

- TxEN 被驱动为低电平,以便为传感器或编码器提供对 RS-485 的控制。

## 2.3.6.1.3 WAIT\_FOR\_START 状态

参阅:图 2-2,标记(3)。

在 WAIT\_FOR\_START 状态期间,CLB 会监视 ENCODER\_RESPONSE 的下降沿。下降沿对应于编码器响应中的第一个起始位。所需的时间可以是任意数量的时钟周期,具体取决于编码器的状态和电缆长度。

在 WAIT\_FOR\_START 期间,CLOCK\_COUNT 匹配和 CLOCK\_COUNT\_COMPLETE 信号会被忽略,生成的 CLOCK 会与 CLB\_SPI\_CLOCK 断开连接。

#### 2.3.6.1.4 RECEIVE\_DATA 状态

参阅:图 2-2,标记(4)。

在 ENCODER RESPONSE 的下降沿, FRAME STATE 从 WAIT FOR START 转换为 RECEIVE DATA。

参阅:图 2-2,标记(5)。

在 RECEIVE\_DATA 期间, SPI 接收来自编码器的响应。响应的大小(时钟数)取决于 TRANSMIT\_DATA 期间发送的特定请求。在命令设置期间, C28x 配置了所需时钟的数量。要接收响应,请按照以下步骤操作:

- CLB 会将 CLB\_SPI\_CLK 与响应对齐。在时钟的上升沿对响应进行采样。通过复位控制时钟边沿位置的计数器,在响应的每个边沿上重复对齐。

- CLOCK 信号会重新连接到 CLB SPI CLK。

- 时钟计数 (COUNTER\_1) match2 由 HLC 调整。读取当前计数,增加接收响应所需的时钟数,然后写回。

- 在 RX FIFO 已满后,SPI 会中断 C28x 以指示已接收到响应。C28x 会调用特定的 receiveData 函数来解压缩数据。

#### 参阅:图 2-2,标记(6)。

当达到接收响应所需的时钟数时,CLOCK\_COUNT\_COMPLETE 信号会被拉高。CLB 会将 FRAME\_STATE 返回到 IDLE。

与编码器的每个事务都会重复此模式。

www.ti.com.cn 系统概述

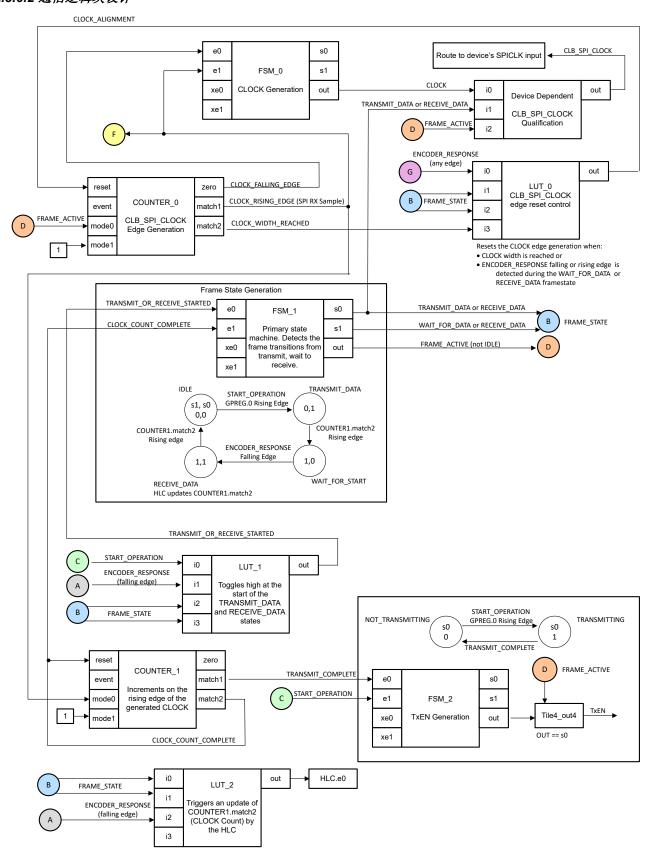

## 2.3.6.2 通信逻辑块设计

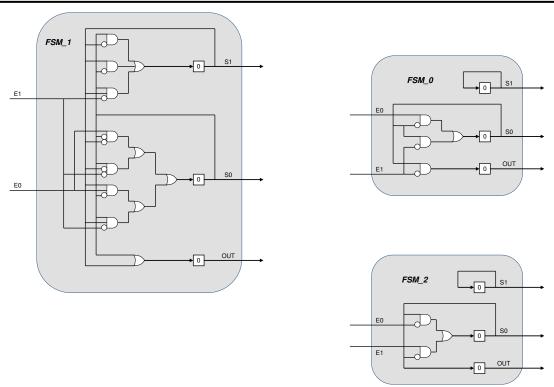

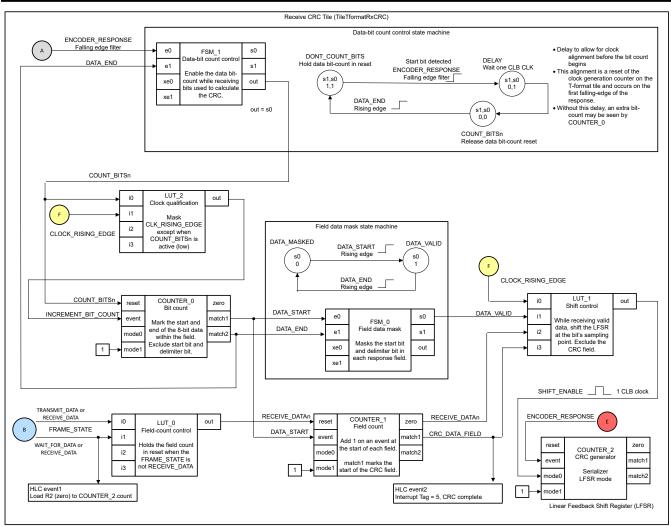

图 2-13. T-Format 通信逻辑块

图 2-13 展示了通信逻辑块设计。本节深入讨论了该设计的三个关键组成部分:

- 1. FRAME\_STATE 生成 (FSM\_1)

- 2. ENCODER\_RESPONSE 检测 (LUT\_1)

- 3. SPI CLK 对齐 (LUT\_0)

#### 备注

在图 2-13 中,彩色圆圈中的字母表示输入/输出图(节 2.3.5.2)中所述的端口连接。

通过在 CLB 工具中查看逻辑块的配置,可以找到其他子模块的公式。节 2.3.6.3 以原理图的形式包含每个模块的 更多信息。

FRAME\_STATE (FSM\_1 s1, s0) 转换如图 2-13 中所示。为了推导相应的公式,这里使用了卡诺图 (表 2-13 和表 2-14)。生成的公式由 OR 运算符连接,并输入到 CLB 工具中。这些公式不需要简化为最简单的形式。

|        |      |                  | CLOCK            | 当前输入<br>(e1, e0)<br>_COMPLETE, TX_OR_F | RX   |

|--------|------|------------------|------------------|----------------------------------------|------|

|        |      | 0,0              | 0 , 1            | 1,1                                    | 1,0  |

|        | 0,0  | 0                | 1 <sup>(1)</sup> | 1 <sup>(1)</sup>                       | 0    |

|        | IDLE | IDLE             | TX               | TX                                     | IDLE |

| 上一状态   | 0,1  | 1 <sup>(2)</sup> | 1 <sup>(2)</sup> | 0                                      | 0    |

|        | TX   | TX               | TX               | WAIT                                   | WAIT |

| s1, s0 | 1,1  | 1 <sup>(3)</sup> | 1 <sup>(3)</sup> | 0                                      | 0    |

|        | RX   | RX               | RX               | IDLE                                   | IDLE |

|        | 1,0  | 0                | 1 <sup>(4)</sup> | 1 <sup>(4)</sup>                       | 0    |

|        | WAIT | WAIT             | RX               | RX                                     | WAIT |

表 2-13. FRAME STATE FSM 1 卡诺图, 状态 s0

- (1) s0 = (!s1 & !s0 & e0)

- (2) s0 = (!s1 & s0 & !e1)

- (3) s0 = (s1 & s0 & !e1)

- (4) s0 = (s1 & !s0 & e0)

表 2-14. FRAME STATE FSM 1 卡诺图, 状态 s1

|        |      |                  | 当前输入<br>(e1, e0)<br>CLOCK_COMPLETE, TX_OR_RX |                  |                  |

|--------|------|------------------|----------------------------------------------|------------------|------------------|

|        |      | 0,0              | 0,1                                          | 1,1              | 1,0              |

|        | 0,0  | 0                | 0                                            | 0                | 0                |

|        | IDLE | IDLE             | TX                                           | TX               | IDLE             |

| 上一状态   | 0,1  | 0                | 0                                            | 1 <sup>(1)</sup> | 1 <sup>(1)</sup> |

|        | TX   | TX               | TX                                           | WAIT             | WAIT             |

| 上一状态   | 1,1  | 1 <sup>(2)</sup> | 1 <sup>(2)</sup>                             | 0                | 0                |

| s1, s0 | RX   | RX               | RX                                           | IDLE             | IDLE             |

|        | 1,0  | 1 <sup>(3)</sup> | 1 <sup>(3)</sup>                             | 1 <sup>(3)</sup> | 1 <sup>(3)</sup> |

|        | WAIT | WAIT             | RX                                           | RX               | WAIT             |

- (1) s1 = (!s1 & s0 & e1)

- (2) s1 = (s1 & s0 & !e1)

- (3) s1 = (s1 & !s0)

来自 FSM\_1 的 OUT 信号只是当前状态的或运算:s1|s2。这对应于帧的任何活动部分(非 IDLE)。

检测编码器的响应是该设计的另一个关键组成部分。LUT\_1 负责检测事务的开始和编码器响应的开始。为了简化设计,我们做出了以下假设:

- ENCODER RESPONSE 下降沿永远不会与 START OPERATION 上升沿同时发生。

- START OPERATION 的上升沿仅在 IDLE 状态期间发生。

鉴于编码器仅响应从 C28x 发起的传输并且 C28x 控制 START\_OPERATION,这些假设是合理的。这些假设会得 到以下公式:out = (i3 & i2) & i1 | i0: www.ti.com.cn 系统概述

如果 FRAME\_STATE == WAIT\_FOR\_START (i3 & i2) 和 ENCODER\_RESPONSE 下降沿 (i1),则输出会变为 高电平。

- 如果 START\_OPERATION 上升沿 (i0),则输出会变为高电平

- 否则,输出为低电平。

由于电缆延迟,编码器的响应可能随时出现。要正确读取响应,必须正确对齐 CLB\_SPI\_CLK。LUT\_0 负责时钟对齐和时钟宽度。LUT\_0 会在适当的时候复位 COUNTER\_0 来实现对齐和时钟宽度。COUNTER\_0 匹配值控制 CLB SPI CLOCK 边沿时序。

- 时钟宽度: 当 CLOCK WIDTH REACHED (i3) 为高电平时,复位 COUNTER 0。

- 对齐时钟:如果 FRAME\_STATE 为 WAIT\_FOR\_START (i2 & !i1) 或 RECEIVE\_DATA (i2 & i1),则会在 ENCODER RESPONSE 的任意边沿 (i0) 上复位 COUNTER 0。

这样会等到以下公式: LUT\_0 out = i3 | (((i2 & !i1) | (i2 & i1)) & i0)。

通过在 CLB 工具中查看逻辑块的配置,可以检查其他子模块的公式。节 2.3.6.3 以原理图的形式包含每个模块的更多信息。

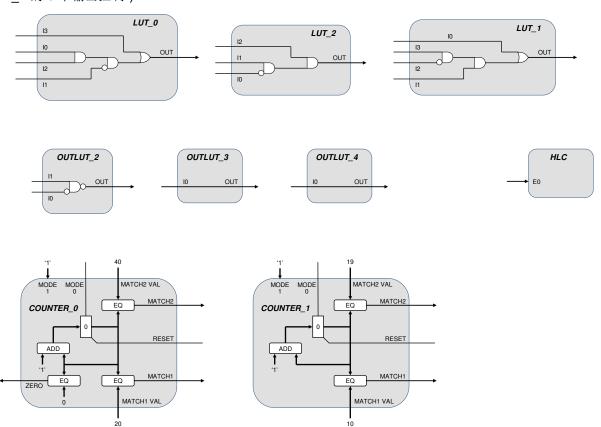

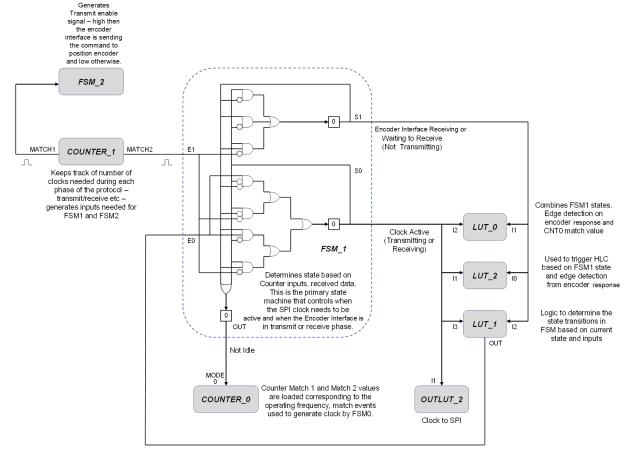

#### 2.3.6.3 逻辑视图

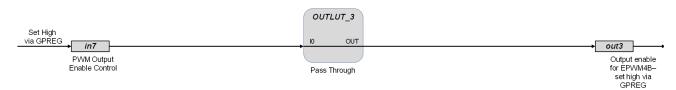

以下几个图展示了与节 2.3.6.2 相同的信息,不过是通过逻辑框图显示的。特别是:

- 图 2-14 和图 2-15 展示了使用逻辑门的 CLB 块的内容。

- 图 2-16 使用该逻辑来显示主状态机如何控制其他块。

- 图 2-17 跟踪几个从其输入开始并经过一些相关逻辑的简单 CLB 输出信号。

- 图 2-18 跟踪时钟到 SPI 输出,从 Input1 开始,经过 LUT\_0、FSM\_0、Counter\_0,一直到 Ouput\_LUT\_0 (受 FSM 1 的 3 个输出控制)。

- 图 2-19 跟踪发送使能输出,从 Input0 和 Input1 开始,经过 LUT\_0、Counter\_0、Counter1 和 FSM\_2(受 FSM\_1 的 3 个输出控制)。

图 2-14. LUT、OUTLUT 和计数器

系统概述 www.ti.com.cn

图 2-15. 有限状态机

图 2-16. 主状态机

www.ti.com.cn 系统概述

图 2-17. CLB 输出 - HLC Event0 和 EPWM 输出使能

备注

只有 F2837xD 设计会覆盖 ePWM 输出。

系统概述 www.ti.com.cn

图 2-18. CLB 输出 - 时钟到 SPI

www.ti.com.cn 系统概述

图 2-19. CLB 输出 - RS485 使能

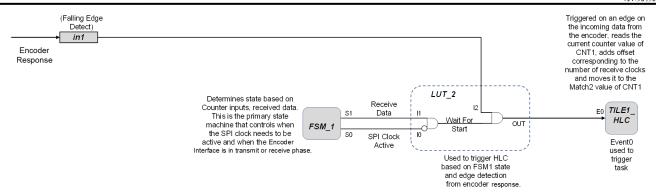

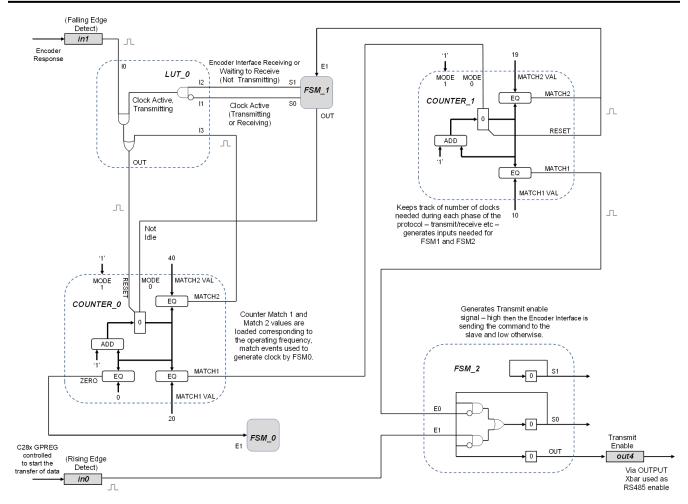

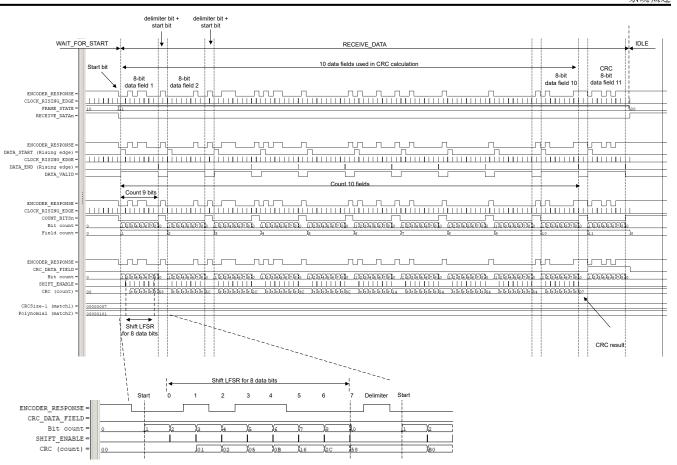

#### 2.3.7 CLB 接收数据 CRC 实现

如节 2.3.5.1 中所述, CLB 类型 2 或更高版本能够在收到响应时或动态计算响应数据 CRC。在这种情况下,所需的信号连接到第二个逻辑块以执行 CRC 计算。逻辑块之间的连接如节 2.3.5.2 中所述。

为了生成 CRC, 计数器配置为线性反馈移位寄存器 (LFSR)。接收到的数据会馈送到 LFSR 的事件输入。当数据有效时,通过 LFSR 的事件输入应用移位。此设计需要知道数据何时有效,以便正确应用移位。回顾节 2.3.1 中的协议概述,有效数据的标准如下:

- FRAME STATE 为 RECEIVE DATA

- 当前位是字段中的 8 位数据之一。也就是说,会跳过开始位和定界位。图 2-21 展示了这种情况。

- 该字段不是 CRCField。CRC 始终是编码器响应中的最后一个字段。

系统概述 www.ti.com.cn

图 2-20. CRC 字段数据有效

表 2-15 展示了映射到 CLB 功能的具体要求。

表 2-15. CRC 生成到 CLB 映射

| ************************************** |                                                                                                   |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| CRC 功能                                 | CLB 映射                                                                                            |  |  |

| 仅包含8位数据(跳过开始位和定界位)                     | COUNTER 模块用于对 T-Format 字段中的位进行计数。匹配值表示第一个有效位和最后一个有效位,如图 2-20 所示。然后,FSM 根据计数器匹配输出来确定是否向 LFSR 应用移位。 |  |  |

| 仅包含有效字段(跳过 CRC)。                       | COUNTER 模块在 RECEIVE_DATA 状态期间每个字段开始时递增。<br>达到 CRCField 后,匹配输出被置位。                                 |  |  |

| 控制 LFSR 的移位 (mode0)                    | 使用 LUT 来根据位计数和字段计数确定数据是否有效。如果有效,<br>LUT 会向 LFSR 施加一个移位脉冲。                                         |  |  |

图 2-21 展示了数据 ID3 CRC 生成的示例波形。图 2-22 展示了 CRC 逻辑块实现。可以使用 CLB 工具来查看子模块的公式。

www.ti.com.cn 系统概述

图 2-21. CRC 波形数据 ID3

系统概述 www.ti.com.cn

图 2-22. CLB 接收数据 CRC 生成逻辑块

#### 2.3.8 PM T-Format 编码器接口库

PM T-Format 编码器接口库提供以下内容:

- 节 2.3.6 和节 2.3.7 中所述的 CLB 逻辑实现。

- 定义明确的应用程序编程接口 (API), 使 C2000 器件能够与 T-Format 位置编码器通信

本节简要概述了 API 提供的函数。

www.ti.com.cn 系统概述

## 2.3.8.1 PM T-Format 参考设计命令

T-Format 参考设计支持节 2.3.1 中所述的命令。该示例提供了一些错误检查。其他功能供系统开发人员使用。T-Format 协议的详细信息可从 Tamagawa 获得。

## 2.3.8.2 PM T-Format 参考设计中支持的函数

PM T-Format 应用程序编程接口 (API) 使 C28x 能够与 T-Format 编码器进行通信。有关 API 的详细说明,请参阅: 《C2000 T-Format 编码器接口软件指南》 (html, pdf)。

该软件指南包含以下方面的内容:

- 通信演示项目

- T-Format 应用程序编程接口 (API)

- 将库整合到您自己的解决方案中

- 从以前的版本迁移

表 2-16 简要概述了 API。

#### 表 2-16. T-Format 参考设计中的函数

| 农 Z-10. 1-Format 多考议 / 中的函数 |                                                                                               |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------|--|--|

| API 函数类型                    | 说明                                                                                            |  |  |

|                             | 运行时函数                                                                                         |  |  |

| 命令设置                        | 为要发送的给定请求和接收的响应设置 SPI 和 CLB。支持所有 T-Format 命令:读取、复位和 EEPROM 命令                                 |  |  |

| 启动操作                        | 此函数启动 CLB 状态机向 TRANSMIT_DATA 的转换。这将启动请求的传输。                                                   |  |  |

| 接收数据                        | 用于解析 T-Format 数据结构并使用从编码器接收的数据对其进行填充的请求专用函数。                                                  |  |  |

| 更新编码器参数                     | 用于根据从编码器接收到的数据更新位置、匝数或编码器 ID 的函数。                                                             |  |  |

|                             | 初始化函数                                                                                         |  |  |

| 设置外设                        | 在系统初始化期间使用该函数设置针对 T-Format 的 SPI、CLB 和互相连接的 XBAR。每次系统复位后都必须调用该函数。在调用设置外设函数之前,不执行 T-Format 事务。 |  |  |

| 生成 CRC 表                    | 仅当 C28x 使用查找表计算 CRC 时才需要。对于给定的具有指定位数 (nBits) 的 CRC 多项式 (polynomial),生成一个包含 256 个条目的表。         |  |  |

| 设置频率                        | 调整 CLB_SPI_CLK 以与 T-Format 频率相匹配。具体调整取决于 CLB 时钟。                                              |  |  |

## 3 硬件、软件、测试要求和测试结果

## 3.1 硬件

要对 TIDM-1011 进行实验,需要使用以下硬件组件:

- TIDM-1011 BoosterPack (也称为 BOOSTXL-POSMGR)

- 外部 5V 直流电源 (请参阅表 1-1)

- 受支持的 LaunchPad, 具有带可配置逻辑块 (CLB) 的 C28x 器件。有关列表,请参阅表 2-1。

- USB B 至 A 电缆

- Tamagawa 的 T-Format 绝对编码器 (例如, TS5700N8501)

- Tamagawa 的 4 引脚电缆 长度需满足应用的要求 (最大 100m)

- 定制适配器,用于将 Tamagawa 的 4 位母端接电缆连接到引线适配器

- 装有 Code Composer Studio (CCS) v12.0.0 或更高版本的 PC

## 备注

并非所有 Tamagawa 绝对编码器都使用 T-Format 进行通信。要按原样使用提供的软件,格式必须为 T-Format。

## 3.1.1 TIDM-1011 跳线配置

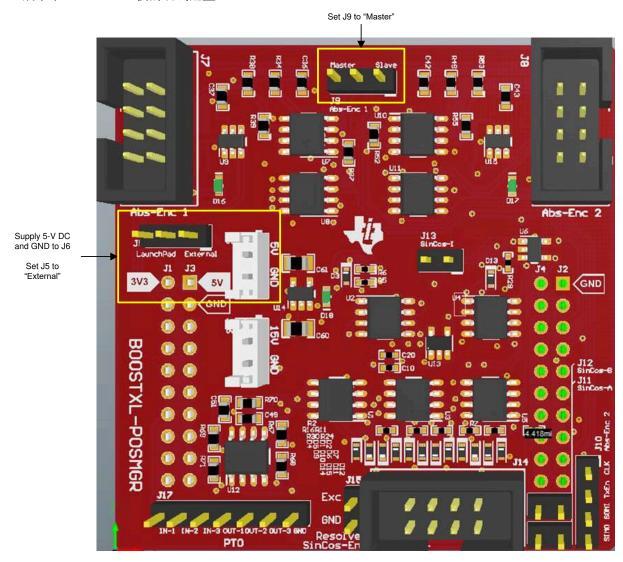

需要将 Position Manager BoosterPack 插入到 LaunchPad 站点 2,如图 3-4 中所示。

图 3-1 展示了 TIDM-1011 板的跳线配置。

图 3-1. TIDM-1011/Position Manager BoosterPack 跳线配置

#### 表 3-1 列出了 TIDM-1011 板的跳线配置。

#### 表 3-1. TIDM-1011 板跳线详细信息

| *** |                      |                   |  |  |

|-----|----------------------|-------------------|--|--|

| 跳线  | 功能                   | 位置                |  |  |

| J5  | TIDM-1011,5V,电源平面源选择 | 外部 <sup>(1)</sup> |  |  |

| J9  | Abs-Enc-1,主/从模式选择    | 主器件(2)            |  |  |

| J11 | 正弦/余弦,编码器 A 信号使能     | 开路                |  |  |

| J12 | 正弦/余弦,编码器 B 信号使能     | 开路                |  |  |

| J13 | 正弦/余弦,编码器指引信号使能      | 开路                |  |  |

- (1) 该配置需要为 J6 提供外部电源,如图 3-1 中所示。

- (2) 请勿使用从模式选项。此模式的 bootsterPack 逻辑中存在错误。

## 3.2 软件

本节概述了 TIDM-1011 使用的软件。有关完整的文档,请参阅 C2000 T-Format 编码器接口软件指南 (HTML、PDF)。

#### 该软件指南包括:

- 系统演示代码的文档

- T-Format 应用程序编程接口 (API) 的文档

- 将库整合到您自己的解决方案中

- 将解决方案移植到 C28x CPU2 的指南

- 更改历史记录

- 从以前版本的库迁移

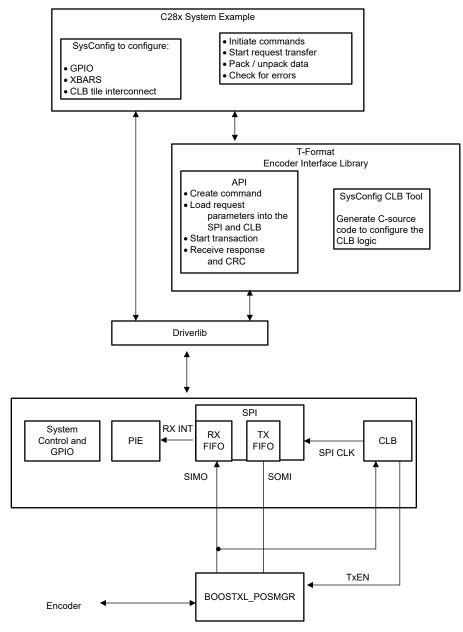

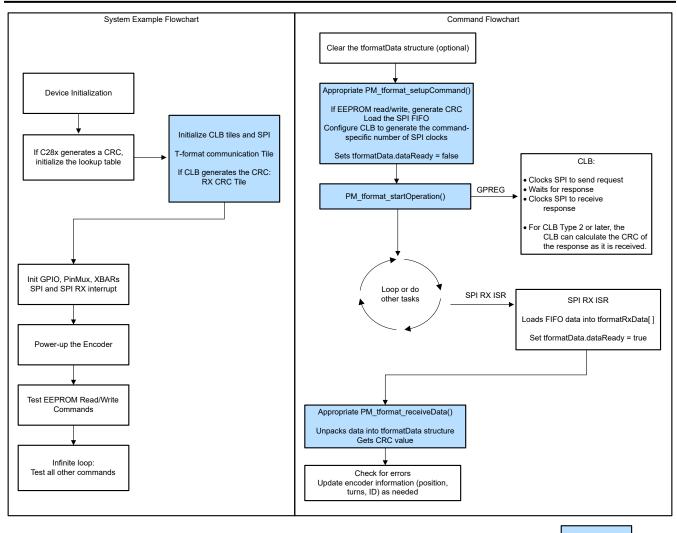

图 3-2 显示了本参考设计中实现的软件架构。采用模块化与可移植方式来实现软件。主要组件包括 C2000 驱动程序库、T-Format 编码器接口库、SysConfig GUI 器件配置工具和 CLB 工具。

图 3-2. T-Format 参考软件架构

图 3-3 展示了 C2000 T-Format 通信演示的流程图。示例应用会配置 C2000 器件,创建命令请求数据包,启动命令,解压缩响应并检查 CRC。

Blue boxes are library functions

图 3-3. T-Format 参考软件流程图

## 3.2.1 C2000 驱动程序库 (DriverLib)

C2000 驱动程序库 (Driverlib) 是一组适用于 C2000 器件系列的低级 API。Driverlib 提供了易于使用的函数调用来 配置存储器映射的外设寄存器。C2000Ware 和 C2000Ware 电机控制 SDK 中提供了 Driverlib 的完整源代码。有 关更多信息,请参阅 C2000 软件指南的"DriverLib"部分。

#### 3.2.2 C2000 SysConfig

C2000 SysConfig 是用于配置 C2000 实时控制 MCU 的图形用户界面工具。SysConfig 会自动生成与 Driverlib 连 接的嵌入式软件。在此参考设计中, SysConfig 工具用于生成代码来配置 SPI、GPIO、INPUTXBAR/ OUTPUTXBAR 和 CLB MUX。有关更多信息,请参阅 C2000 Academy: SysConfig 模块。

#### 3.2.3 C2000 可配置逻辑块工具

C2000 CLB 工具支持通过图形界面配置 CLB 逻辑。CLB 工具是一款易于使用的 GUI,内置于 Code Composer Studio 中, 并可利用 C2000 SysConfig 插件。此参考设计中使用 CLB 工具为 T-Format 编码器接口配置逻辑块, 如设计说明中所述。有关更多信息,请参阅 C2000 Academy: 可配置逻辑块。

#### 3.2.4 安装 Code Composer Studio™ 和 C2000WARE-MOTORCONTROL-SDK

- 1. 安装 CCS v12.0.0 或更高版本 (如果尚未在 PC 上安装)。

- 2. 安装 C2000WARE-MOTORCONTROL-SDK v4.01.00.00 或更高版本(如果尚未在 PC 上安装)

3. 安装后,请参阅 C2000 T-Format 编码器接口软件指南(html,pdf)以获取进一步说明。

#### 各注

只需要上述软件即可构建这些示例。若要重新构建基于 CLB 的库,还需要 CLB 工具。此工具包含在 Code Composer Studio (sysconfig) 和 SDK 的 C2000Ware 子组件(支持实用程序)中。若要运行基于 CLB 的仿真,需要安装其他工具(请参阅 *CLB 工具用户指南* 中关于这些工具的说明)。

#### 3.2.5 查找参考软件

此参考设计中包含的软件由两部分组成:

- 说明 T-Format 编码器接口用法的系统示例。示例项目源文件的位置如表 3-2 所示。

- T-Format 编码器接口库。表 3-3 展示了库源文件的位置。

有关完整的文档,请参阅《C2000 T-Format 编码器接口软件指南》(html, pdf)。

## 表 3-2. 系统示例的位置

| C:\ti\c2000\C2000Ware_MotorControl_SDK_[version]\ | SDK 的默认安装位置。([SDK])                                |

|---------------------------------------------------|----------------------------------------------------|

| [SDK]\solutions\boostxl_posmgr\                   | 特定于器件的基础安装目录 ([pm_base])                           |

|                                                   | Code Composer Studio (CCS) projectspec 文件。用于将工程导入您 |

|                                                   | 的 CCS 工作区。                                         |

## 表 3-3. T-Format 编码器接口库的位置

| C:\ti\c2000\C2000ware_MotorControl_SDK_[version] | SDK 的默认安装位置。([SDK])                                  |

|--------------------------------------------------|------------------------------------------------------|

| [SDK]\libraries\position_sensing\tformat         | 库基础安装目录 ([lib_base])                                 |

| [lib_base]\ccs\[device]                          | 参考库的 Code Composer projectspec 文件。使用这些工程可为每个器件重新构建库。 |

## 3.3 测试和结果

本节详细介绍了测试程序、结果和基准测试。另外还提供了故障排除指南。

#### 3.3.1 硬件配置

- 1. 确保按照表 3-1 中所述对 TIDM-1011 板的跳线进行配置。

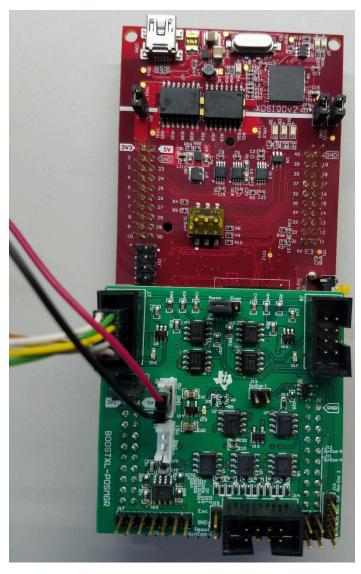

- 2. 使用 BoosterPack 连接器(J5 至 J7 和 J8 至 J6)将 TIDM-1011 板连接到 LaunchPad。确保将 TIDM-1011 器件连接到 LaunchPad 的站点 2,如图 3-4 中所示。

图 3-4. 连接到 LaunchPad™ 的站点 2 的 Position Manager BoosterPack

- 3. 将 USB 电缆连接到 LaunchPad。

- 4. 设置到编码器的连接。

- a. 准备一个适配器,使用 8 位母型转引线适配器将 Tamagawa 电缆连接到 T-Format 接口(有关用于编码器连接器 J7 的接头,请参阅 BOM)。

- b. 插入在上一步中创建的适配器的接头,以连接到 Abs-Enc-1 (J7)。Tamagawa 电缆的母端连接到编码器。 图 3-5 展示了 J7 的引脚排列。

## 图 3-5. TIDM-1011 板上的 Abs-Enc-1 (J7) 引脚排列

5. 5V 直流电源和 GND 连接到 J6,如图 3-1 中所示。板现在应该看起来像图 3-6。LED D18 应该点亮,表明板已通电。

## 备注

对于某些编码器,BoosterPack 可能无法在上电时提供足够的电流。如果编码器未做出响应,请尝试将 BoosterPack 外部的电源连接到编码器。如果这样做,请将公共接地连接到 BoosterPack。

图 3-6. Position Manager BoosterPack 已通电并连接到 Tamagawa 编码器

## 3.3.2 构建和加载项目

按照 *C2000 T-Format 编码器接口软件指南*(html, pdf)中的说明来加载和运行系统解决方案。请参阅软件指南的"T-Format 系统解决方案"部分。

这些说明包括:

- 将项目导入到适用于器件的 Code Composer Studio (CCS) 中

- 配置库和系统示例

- 选择构建配置

- 填充 watch window

- 运行代码

#### 3.3.3 运行代码

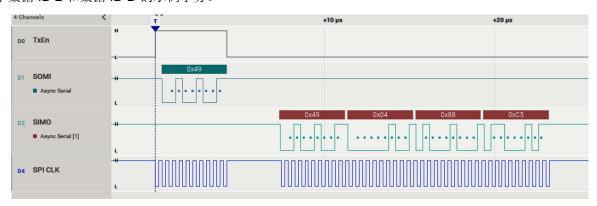

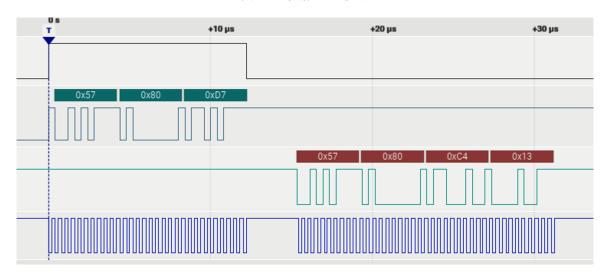

T-Format 系统解决方案是仅用于通信的演示。该演示会发送命令,接收响应并检查错误。对于每个 T-Format 命令,都会重复此模式。在运行演示时,您可以使用逻辑分析仪或示波器来监控 MCU 的输出信号。图 3-7 和图 3-8 展示了数据 ID 2 和数据 ID D 的示例事务。

图 3-7. 数据 ID 2 波形

图 3-8. 数据 ID D 波形

#### 备注

只有 F2837xD 需要在 CLB 生成的 SPI 时钟和 SPICLK 引脚之间进行外部连接。其他器件在 CLB 和 SPICLK 之间具有内部连接。对于具有内部连接的器件,SPICLK 也可引出至一个引脚进行监控。节 2.3.5.2 中的器件输入/输出图展示了 SPI CLK 的测试连接。

检查波形:

www.ti.com.cn

- 1. 根据 T-Format 规范的要求, SPI CLK 频率为 2.5MHz。

- 2. 请求中的 ControlField 与响应中的 ControlField 相匹配。例如,在数据 ID2 中,ControlField 为 0x49。示例 软件会检查此匹配情况,如果出现错误,则会停止。

- 3. 响应中的字段数会根据请求而预期的。

- 4. 响应中的 CRCField (最后一个字段)对于接收到的数据是正确的。示例软件会检查这一点,如果出现错误,则会停止。

- 5. 根据编码器的规格验证编码器 ID。

- 6. 尝试不同的电缆长度(最长 100m),并观察波形的变化。只有请求和响应之间的时间应该改变。

手动转动电机或编码器的轴:

- 1. 沿一个方向转动轴。请注意 watch window 中的位置和匝数变化。

- 2. 向相反方向转动轴。观察位置并向相反方向转动。

## 3.3.4 电缆长度验证

表 3-4 列出了使用各种类型的编码器进行的测试;执行了电缆长度测试。测试包括基本的命令集运行和读取位置值以及其他数据(如果适用)。

表 3-4. 电缆长度测试报告

| 编码器名称       | 类型 | 分辨率 (位) | 电缆长度 <sup>(1)</sup> (m) | 最大 T-FORMAT 时钟 | 测试结果 |

|-------------|----|---------|-------------------------|----------------|------|

| TS5702N40   | 旋转 | 17 位    | 70m                     | 2.5MBPS        | 通过   |

| TS5700N8501 | 旋转 | 24 位    | 70m                     | 2.5MBPS        | 通过   |

(1) 对于某些编码器,还就最大为 100m 的电缆长度进行了测试。

#### 3.3.5 基准测试

表 3-5 列出了从 RAM 执行 T-Format 库函数所需的 C28x CPU 周期。此数据使用以下方法收集:

- C2000 Codegen Tools V22.6.0.LTS

- float\_support: fpu32tmu\_support: tmu0fp\_mode: relaxed

- · abi: eabi

表 3-5. 周期数基准测试

|                            |                       | 周期:-O2 -mf2                                                           |                                               |  |

|----------------------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------|--|

| 功能                         | CRC 计算 <sup>(1)</sup> | TX CRC 由 VCRC 计算得出 <sup>(2)</sup><br>RX CRC 由 CLB 计算得出 <sup>(3)</sup> | TX 和 RX CRC 都由<br>C28x 查找表计算得出 <sup>(4)</sup> |  |

| setupCommandReadEEPROM     | 发送                    | 266                                                                   | 264                                           |  |

| setupCommandWriteEEPROM    | 发送                    | 280                                                                   | 291                                           |  |

| setupCommandReadoutOrReset | 不适用                   | 231                                                                   | 222                                           |  |

| spiRxISR                   | 不适用                   | 418                                                                   | 418                                           |  |

| startOperation             | 不适用                   | 19                                                                    | 14                                            |  |

| receiveDataID0_1_7_8_C     | 接收                    | 41                                                                    | 118                                           |  |

| receiveDataID2             | 接收                    | 35                                                                    | 81                                            |  |

| receiveDataID3             | 接收                    | 64                                                                    | 218                                           |  |

| receiveDataID6             | 接收                    | 57                                                                    | 101                                           |  |

| receiveDataIDC             | 接收                    | 53                                                                    | 97                                            |  |

| updateEncoderID            | 不适用                   | 1                                                                     | 1                                             |  |

| updatePositionsOrTurns     | 不适用                   | 18                                                                    | 18                                            |  |

- (1) 所示函数计算发送数据 CRC 或接收数据 CRC。"不适用"表示该函数不需要 CRC 计算。

- (2) C28x CPU 的 VCRC 扩展计算发送数据 CRC。

- (3) CLB 在响应传入时计算接收到的数据 CRC。此方法使用额外的 CLB 逻辑块并需要 CLB 类型 2 或更高版本。

- (4) 发送和接收 CRC 均由 C28x 使用查找表进行计算。

表 3-6 列出了与每个库源文件相对应的 16 位字代码大小。C28x 查找表占用 256 个字的 RAM 或闪存,此表中并未反映。

#### 表 3-6. 16 位字的代码大小

|                     | 代码大小:-O2 -mf2 |                          |  |

|---------------------|---------------|--------------------------|--|

| 源文件                 |               | TX 和 RX CRC:<br>C28x 查找表 |  |

| pm_tformat_source   | 936           | 923                      |  |

| clb_config          | 480           | 246                      |  |

| pm_tformat_crc      | 26            | 148                      |  |

| pm_tformat_crc_vcrc | 14            | 不适用                      |  |

#### 3.3.6 疑难解答

检查以下波形有助于进行故障排除。请参考设计说明中的 I/O 图:

- CLB 生成的 SPI 时钟。

- SPI 的输出数据。这是发送到编码器的请求。

- SPI 的输入数据。这是响应。

- TxEN 信号。在请求传输期间,该信号必须为高电平。

- RS485 线路驱动器和编码器之间的编码器数据信号 (D+/D-)。注意:数据是差分信号。因此,需要使用特殊的探头来观察。

- 1. 如果 SPI 不发送请求:

- 检查 SPICLK 和 CLB 之间的连接。CLB 驱动 SPI CLK。除了 F2837xD 外,所有器件上的 MCU 都可以在内部进行此连接。在 F2837xD 上,必须在外部进行此连接。

- 在命令设置后观察 SPI 寄存器,并在启动操作后再次观察。如果 SPI 收到时钟,TX FIFO 级别会降低,而 RX FIFO 级别会增加。

- 2. 编码器没有响应:

- 确认在请求传输期间 TxEN 为高电平。

- 检查 SPI 时钟频率。时钟频率必须为 2.5MHz,编码器才会响应。如果时钟不是 2.5MHz,请检查系统示例 头文件中的频率配置 (TFORMAT FREQ DIVIDER)。

- 检查编码器是否正确通电。在某些情况下,LaunchPad 无法提供编码器所需的电流。尝试单独为编码器供电,确保所有接地都连接在一起。

- 3. 在发送期间观察到 SPI CLK, 但在响应时间内观察不到:

- 检查编码器与测试硬件的连接。

- 如果修改了该设计:

- 检查响应引脚是否已路由到正确的 CLB 逻辑块和该逻辑块的正确输入。CLB 必须检测到编码器的响应。只有这样,CLB 才会生成 CLB\_SPI\_CLK。

- 如果 CLB 在内部驱动 SPI CLK,请检查该逻辑块和逻辑块输出使能是否正确。只有特定的逻辑块才能 访问特定的 SPI 模块。这可能会在不同的器件上发生变化。

## 4设计文件

要下载设计文件,请参阅位于 TIDM-1011 的产品页面。

## 5 相关文档

#### 入门:

- 1. 德州仪器 (TI), C2000 T-Format 编码器接口软件指南 (html, pdf)。

- 2. 德州仪器 (TI), C2000 Academy 可提供易于使用的培训模块,涵盖有关所有 C2000 器件的各类主题。

- 3. 德州仪器 (TI), C2000 Academy: CLB 模块

- 4. 德州仪器 (TI), C2000 软件指南包括 C2000 软件、软件开发套件和开发工具的概述。

- 5. 德州仪器 (TI), C2000 实时控制 MCU 外设参考指南 CLB 类型 表示在特定实现上找到的功能集。特定 C2000 MCU 的 CLB 类型信息在器件数据表和本参考指南中进行了说明。

- 6. 德州仪器 (TI), C2000 器件的 CRC 引擎

## 参考设计:

- 1. 德州仪器 (TI), 《DesignDRIVE 开发套件 IDDK v2.2.1 用户指南》

- 2. 德州仪器 (TI),《DesignDRIVE 开发套件 IDDK v2.2.1 硬件参考指南》

- 3. 德州仪器 (TI),《适用于工业驱动和电机控制的 C2000 DesignDRIVE 软件》

- 4. 德州仪器 (TI), 《C2000 Position Manager SinCos 库用户指南》

#### 5.1 商标

C2000<sup>™</sup>, BoosterPack<sup>™</sup>, and TI E2E<sup>™</sup> are trademarks of Texas Instruments. LaunchPad<sup>™</sup> is a trademark of Texas Instruments Incorporated.

所有商标均为其各自所有者的财产。

#### 6 术语

ABSx 来自 T-Format 规范。ABS0:ABS1:ABS2 为旋转 1 圈的绝对位置数据

ABMx 来自 T-Format 规范。ABM0:ABM1:ABM2 是多圈数据。

**ADF** 来自 T-Format 规范。EEPROM 读取/写入中使用的地址数据字段。

ALMC来自 T-Format 规范。编码器错误字段。BOOSTXL-POSMGR请参阅 Position Manager BoosterPack

**C28x** 指具有 C28x CPU 内核的器件

**CF** 来自 T-Format 规范。ControlField。任何请求和任何响应中的第一个字段。

**CLB** 可配置逻辑块

命令(或请求) 从编码器接口发送到编码器。该命令用于确定从编码器发回哪些信息。

**CPLD** 复杂可编程逻辑器件

**CRC** 循环冗余校验。T-Format 使用多项式 X^8 + 1。

**数据 ID 代码** 来自 T-Format 规范。识别特定 T-Format 请求的 4 位代码 + 奇偶校验。

分界符 来自 T-Format 规范。每个字段末尾的 1 位,始终为 1。

**DFx** 来自 T-Format 规范。响应中的 DataField。使用的字段及其内容取决于请求。

来自 T-Format 规范。EEPROM 数据字段。用于 EEPROM 读取/写入。 编码器接口 为 C2000 实时 MCU 等控制器提供连接绝对编码器通信协议接口的逻辑。

**ENID** 来自 T-Format 规范。编码器 ID。

字段 来自 T-Format 规范。任何请求或响应都由一个或多个 10 位字段组成。

FPGA 现场可编程门阵列

PM\_tformat 用于所有编码器接口参考设计函数的前缀。PM 代表位置管理器。

Position Manager TIDM-1011 板与 C2000 Position Manager BoosterPack 插件模块相同(请参阅节

BoosterPack (BOOSTXL-

2.3.3)

POSMGR)

申请 请参阅命令

**Sink 代码** 来自 T-Format 规范。ControlField (CF) 中的起始位之后紧接着是 0,1,0 固定模式

**SF** 来自 T-Format 规范。StatusField。

**SPI** 串行外设接口。

**起始位** 来自 T-Format 规范。任何 T-Format 字段开头的 1 位,始终为 0。

后续电子器件 T-Format 编码器接口 + 控制器实现

**T-Format** Tamagawa 提供的绝对编码器所使用的通信协议规范

## 7 关于作者

**LORI HEUSTESS** 多年来一直是 C2000 团队的一员。她感兴趣的领域包括 CPU 和外设验证、软件开发和工业应用。Lori 目前在 C2000 工业应用团队工作。

SUBRAHMANYA BHARATHI AKONDY 从事过几种 C2000 MCU 产品和控制外设的架构定义和设计。擅长 MCU 架构、应用和设计方面。

SHEENA PATEL 在 C2000 MCU 组的工业驱动器团队中担任产品营销工程师。

## 8 修订历史记录

| Changes from Revision D (October 2022) to Revision E (July 2023)          | Page                |

|---------------------------------------------------------------------------|---------------------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式                                                 |                     |

| ,添加了 <i>TMS320F28P65x 的 LaunchPad</i>                                     |                     |

| • 向"支持的器件和 LaunchPad"表中添加了 <i>TMS320F28P65x</i> 支持                        | 4                   |

| • 更新了图像以进行阐释并保持一致性                                                        |                     |

| ● 更新了 <i>每个器件的输入/输出和逻辑块摘要</i> 表,以包含 TMS320F28P65x                         | 12                  |

| <ul> <li>更新了 TMDXIDDKF273XD 的 F2838x 输入和输出 图像,以包含 TMS320F28P65</li> </ul> | 5x12                |

| • 添加到软件指南内容列表中                                                            | 34                  |

| • 向故障排除列表中添加了数据                                                           | 42                  |

| Changes from Revision C (September 2020) to Revision D (October 2022)     | Page                |

| • 添加了 LaunchPad <i>资源和软件开发套件</i> (SDK)                                    |                     |

| • 将 <i>高达 xxx 的时钟频率</i> 更新为 xxx 的时钟频率                                     | 1                   |

| • 添加了 LaunchPad 平台和有关可配置逻辑块的信息。                                           | 4                   |

| • 将事务详细信息的位置更新到"实现详细信息"部分                                                 |                     |

| • 将标题从 PM T-Format 主器件详细信息 更改为 C2000 T-Format 编码器接口概述 .                   | 8                   |

| • 从图中删除了 GPIO 编号和 SPI 实例信息                                                | 8                   |

| • 更新了 SPI 的旧术语                                                            |                     |

| • 更新了"TIDM-1011 板和 BOOSTXL-POSMGR 连接器"表格中的最后一列                            |                     |

| • 添加了 LaunchPad 接头使用信息                                                    | 9                   |

| • 更新了"MCU资源要求"中的信息                                                        | 11                  |

| • 移到了"MCU资源要求"部分                                                          | 11                  |

| • 进行了更新以指示使用了 SysConfig。                                                  | 11                  |

| • 向"CLB逻辑块用法"表添加了详细信息并添加了表格标题                                             | 18                  |

| • 将状态转换说明段落的格式更改为有序的步骤列表,并添加了其他详细信息                                       | 18                  |

| • 向表 2-2 ( MCU 资源要求 ) 中添加了详细信息                                            | 18                  |

| • 将目录信息更新为表格(采用段落列表格式)                                                    | 18                  |

| • 更新了图以阐明输入源,删除了过时术语,并添加了其他说明。更正了"CLB输出                                   | ¦ - SPI 时钟"图中的 LUT0 |

| 输入。                                                                       |                     |

| • 将一些详细信息整合到硬件和软件章节中                                                      | 30                  |

| • 更新了受支持的 LaunchPad 和所需的 CCS 版本。                                          |                     |

| • 添加了软件架构图和说明。                                                            | 34                  |

| • 添加了内容                                                                   |                     |

| • 添加了新内容                                                                  | 36                  |

| • 添加了新内容                                                                  |                     |

| • 更新了工具版本和关于构建基于 CLB 的项目的注释。                                              | 36                  |

| • 将目录信息更新到单个位置                                                            |                     |

| • 更新了步骤 2,以更正 LaunchPad 站点 2 的连接器名称                                       |                     |

| • 添加了一条注意事项,指出可能需要为编码器提供外部电源                                              |                     |

| • 添加了一个包含示例项目位置的表格,并在说明中添加了详细信息                                           | 40                  |

| • 添加了 C2000 Academy                                                       |                     |

| • 更新了术语列表                                                                 | 43                  |

| Changes from Revision B (January 2020) to Revision C (September 2020)     | Page                |

| • 更新了整个文档中的表格、图和交叉参考的编号格式                                                 | 2<br>               |

| Changes from Revision A (2019 年 11 月) to Revision B (2020 年 1 月)          | Page                |

| • 增加了说明图 6-11 的段落                                                         | 18                  |

| • 添加了图 6-11 以显示逻辑框图。                                             | 18   |

|------------------------------------------------------------------|------|

| Changes from Revision * (2018 年 4 月) to Revision A (2019 年 11 月) | Page |

| • 添加了 <i>CLB 的输入配置</i> 部分                                        | 11   |

| • 添加了                                                            | 18   |

| • 更改了 <i>软件</i> 部分中的信息                                           | 34   |

| • 更改了 电缆长度测试报告 表中的编码器编号                                          |      |

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司