TI Designs: TIDA-01587

效率大于 95% 且适用于无刷式直流伺服驱动器的 10.8V/30W

4.3cm² 功率级参考设计

#### 说明

此 15W 16mm x 27mm 功率级参考设计用于驱动和控制依靠三至四芯锂离子电池供电运行的无刷式直流 (BLDC) 电机的位置。此解决方案经过优化,具有较高的效率和极小的外形尺寸,可轻松安装到电机中并实现精确的电机位置控制。另外,此设计还能高速驱动电机并提供位置反馈。此参考设计可提供过流和短路保护,且板载 MCU 提供 UART 连接功能,从容允许通过任何外部控制器进行控制。

### 资源

TIDA-01587 设计文件夹 DRV8304 产品文件夹 CSD87502Q2 产品文件夹 MSP430FR5949 产品文件夹 TPS709 产品文件夹 TVS3300 产品文件夹

咨询我们的 E2E™ 专家

### 特性

- BLDC 伺服驱动器的工作电压范围为 6V 至 16.8V (3 至 4 节锂离子电池)

- 支持 2.5A<sub>RMS</sub> 连续和 5A 峰值电机绕组电流

- 支持对永磁电机进行梯形正弦控制

- 采用数字霍尔传感器反馈来实现 BLDC 电机的闭环 60° 电气位置控制

- 支持通过正弦激励和模拟霍尔传感器反馈进行位置 控制

- 16mm x 27mm 的极小型 PCB 外形尺寸

- 功率级效率超过 95%, 无需散热器

- 借助高效率的功率级、低功耗 MCU 和低静态电流 LDO 提高了电池寿命

- 过流、击穿和欠压保护

- 提供 UART 有线通信

- 工作环境温度: -20°C 至 +55°C

#### 应用

- 类人机器人

- 扫地机器人

- 割草机器人

A

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

## 1 System Description

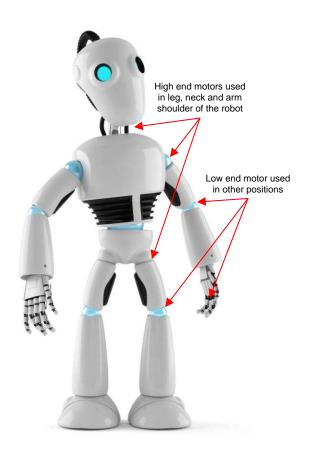

A humanoid robot is a type of service robot used in wide-end applications such as research applications where human access is risky, high-end toys used for teaching, dancing, and speaking, and more. Multiple motors are present in a typical humanoid depending upon the features and application requirement. The commonly used motors are brushed DC (BDC), brushless DC (BLDC), and sometimes stepper types.

1 shows the examples of motor drive locations in a typical humanoid. The high-end or high-power motors are typically present in the neck, legs, shoulders, and so on. Low-end or low-power motors are used in other locations such as elbows, knees, fingers, and so on. The electronic drive used in these motors has the following requirements:

- Must be small enough to fit with the motor

- Must support accurate position and torque control

- Must have the sufficient holding torque capability

图 1. Typical Humanoid—Motor Drive Locations

Vacuum robots are another service robot widely used in consumer applications for cleaning. The motors used in vacuum robots have different requirements like high-speed rotation, high torque-slow speed operation, or position control depending on the functionality these motors support (for example, suction, wheel, side brush, position control of the robotic vision control motor, and so on). BDC, BLDC, or stepper motors are typically used. The electronic drives have similar requirements as said in the case of humanoids.

www.ti.com.cn System Description

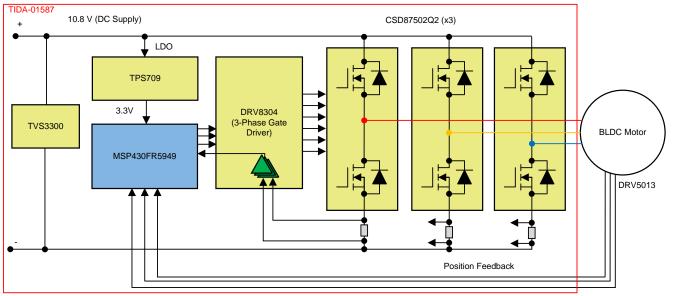

This three-phase BLDC power stage reference design can support the position control in a humanoid or the motor control in a vacuum robot. The design demonstrates the BLDC motor servo drive power stage in a very small form factor using the highly-integrated three-phase gate driver DRV8304 featuring a high level of integration and protection, reducing the overall BOM to a large extend.

System Description www.ti.com.cn

The very small form factor and higher efficiency is also achieved by using the CSD87502Q2 offering two independent 30-V N-channel MOSFET in a SON 2x2 mm plastic package, having a low drain-to-source on-resistance ( $R_{DS(on)}$ ) of 27 m $\Omega$ . The TPS709 LDO features a low-quiescent current (< 1  $\mu$ A) and generates the low-noise, stable, 3.3-V power supply for the MCU. The MSP430FR5949 runs the position control algorithm by taking the position feedback signals from the motor, and offers trapezoidal and sinusoidal motor control. The TVS3300 provide surge voltage protection on input voltage supply.

The test report evaluates the board power capability, efficiency, overcurrent protection, peak current capability, and the position control with sufficient hold-up torque.

# 1.1 Key System Specifications

### 表 1. Key System Specifications

| PARAMETERS                   | SPECIFICATIONS                                                                     |  |

|------------------------------|------------------------------------------------------------------------------------|--|

| Input voltage                | 10.8-V DC (6-V minimum to 16.8-V maximum)                                          |  |

| Rated output power           | 30 W                                                                               |  |

| RMS winding current          | 2.5 A                                                                              |  |

| Peak winding current         | 5 A                                                                                |  |

| Inverter switching frequency | 20 kHz (adjustable from 5 kHz to 100 kHz)                                          |  |

| Feedback signals             | DC bus voltage, analog or digital position feedback, low-sid inverter leg currents |  |

| Protections                  | Overcurrent, input undervoltage, over temperature, shoot-through                   |  |

| Cooling                      | Natural cooling only, no heat sink                                                 |  |

| Operating ambient            | -20°C to +55°C                                                                     |  |

| Board specification          | 16 mm x 27 mm, 2-layer, 1-oz copper, 1.6-mm board thickness                        |  |

| Efficiency                   | > 95%                                                                              |  |

www.ti.com.cn System Overview

## 2 System Overview

### 2.1 Block Diagram

Copyright © 2018, Texas Instruments Incorporated

图 2. TIDA-01587 Block Diagram

# 2.2 Highlighted Products

### 2.2.1 DRV8304

The key requirements in selecting the gate driver are:

- Small form factor, three-phase gate driver with high level of integration and protection

- Support the operating voltage range with sufficient gate current

- Support the required minimum DC input voltage, still provides sufficient gate voltage for the external FET to operate at the minimum R<sub>DS(on)</sub>

- · Low power consumption

The reference design uses the three-phase gate driver DRV8304, which is specified for 6 V to 38 V, providing a maximum gate current of 150-mA source and 300-mA sink. The DRV8304 can support applications including field-oriented control (FOC), sinusoidal current control, and trapezoidal current control of BLDC motors. The DRV8304 device integrates three current-sense amplifiers (CSA) for sensing the phase currents of BLDC motors for optimum FOC and current-control system implementation. An AUTOCAL feature automatically calibrates the CSA offset error for accurate current sensing.

The DRV8304 device is based on smart gate-drive (SGD) architecture to eliminate the need of any external gate components (resistors and Zener diodes) while fully protecting the external FETs. The SGD architecture optimizes dead time to avoid any shoot-through conditions, provides flexibility in reducing electromagnetic interference (EMI) by gate slew-rate control and protects against any gate-short conditions. Strong pulldown current also prevent any dv/dt gate turnon. The gate driver provide overcurrent and short-circuit protection by MOSFET V<sub>DS</sub> monitoring.

System Overview www.ti.com.cn

#### 2.2.2 CSD87502Q2

The key requirements in selecting the power stage MOSFETs are:

- Low R<sub>DS(on)</sub> and gate charge for high efficiency operation

- Small form factor

- Low thermal resistance and provision for heat dissipation to PCB

The reference design uses the CSD87502Q2, which is a 30-V, 27-m $\Omega$  N-channel device with dual independent MOSFETs in a SON 2×2-mm plastic package. The dual FETs feature a low R<sub>DS(on)</sub> that minimizes losses and offers low component count for space-constrained applications. The low junction-to-ambient thermal resistance with the help of thermal pads on the package allows easy heat dissipation.

#### 2.2.3 MSP430FR5949

The MSP430™ ultra-low-power (ULP) FRAM platform combines uniquely embedded FRAM and a holistic ultra-low-power system architecture, allowing innovators to increase performance at lowered energy budgets. FRAM technology combines the speed, flexibility, and endurance of SRAM with the stability and reliability of flash at much lower power.

The MSP430 ULP FRAM portfolio consists of a diverse set of devices featuring FRAM, the ULP 16-bit MSP430 CPU, and intelligent peripherals targeted for various applications. The ULP architecture showcases seven low-power modes, optimized to achieve extended battery life in energy-challenged applications.

The device has a 16-bit RISC architecture supporting up to a 16-MHz clock. The device has five 16-bit timers with up to seven capture/compare registers each. The seven capture/compare registers helps to realize six PWM signals for three-phase sine control with a single time base. The device has 32-bit hardware multiplier and a 12-bit analog-to-digital converter (ADC) with internal reference and sample-and-hold and up to 16 external input channels. The enhanced serial communication allows easy communication with master controller in different service robots.

#### 2.2.4 TPS709

The TPS70933 linear regulator is an ultra-low, quiescent current device designed for power-sensitive applications. The LDO can work up to a 30-V input voltage, which makes it ideal for up to six-cell Li-ion battery supply application. A precision band-gap and error amplifier provides 2% accuracy over temperature. A quiescent current of only 1  $\mu$ A makes this LDO ideal for battery-powered, always-on systems that require very little idle-state power dissipation. This device has thermal-shutdown, current limit, and reverse-current protections for added safety. The TPS70933 linear regulator is available in WSON-6 and SOT-23-5 packages.

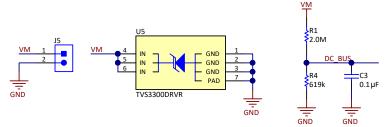

### 2.2.5 TVS3300

The TVS3300 is a transient voltage suppressor that provides robust protection for electronic circuits exposed to high transient voltage events. Unlike a traditional TVS diode, the TVS3300 precision clamp triggers at a lower breakdown voltage and regulates to maintain a flat clamping voltage throughout a transient overvoltage event. The lower clamping voltage combined with a low dynamic resistance enables a unique TVS protection solution that can lower the voltage a system is exposed during a surge event by up to 30% in unidirectional configuration and up to 20% in bidirectional configuration when compared to traditional TVS diodes.

www.ti.com.cn System Overview

The TVS3300 is a unidirectional precision surge protection clamp with a 33-V working voltage designed specifically to protect systems with mid-voltage rails in industrial, communication, and factory automation applications. The TVS3300 has a fast response time when surge current is applied so there is no overshoot voltage during clamping, making it ideal to replace traditional TVS and Zener diodes.

The TVS3300 is available in two small footprint packages which, when used in place of an industry standard SMB package, can reduce footprint by 94% (WCSP package) and 79% (SON package) for space constrained applications. Both package options robustly dissipate the surge power and provide up to 58% lower leakage current compared to traditional TVS diodes in SMA and SMB package.

# 2.3 System Design Theory

### 2.3.1 DC Voltage Input to the Board

The board gets the DC input voltage through the jumper J5 as shown in 🛭 3. The TVS3300 is a surge protection clamp provided at the input to protect the circuit from input voltage surges. The design is optimized for a three-cell Li-ion battery and can support up to four-cell applications, having a maximum voltage of 16.8 V.

Copyright © 2018, Texas Instruments Incorporated

# 图 3. Schematic of Battery Power Input Section

The input supply voltage PVDD is scaled using the resistive divider network, which consists of R1, R4, and C3, and fed to the MCU. Considering the maximum voltage for the MCU ADC input as 3.3 V, the maximum DC input voltage measurable by the MCU is calculated as in 公式 1.

$$V_{DC}^{max} = V_{ADC\_DC}^{max} \times \frac{(619 \text{ k}\Omega + 2000 \text{ k}\Omega)}{619 \text{ k}\Omega} = 3.3 \times \frac{(619 \text{ k}\Omega + 2000 \text{ k}\Omega)}{619 \text{ k}\Omega} = 13.96 \text{ V}$$

(1)

Considering a 10% headroom for this value, the maximum recommended voltage input to the system is  $13.96 \times 0.9 = 12.56 \text{ V}$ . So for a power stage operating from three-cell Li-ion, having a maximum operating voltage of 12.6 V, this voltage feedback resistor divider is ideal. Also, this choice gives optimal ADC resolution for a system operating from 6 V to 12.6 V.

### 2.3.2 Power Stage Design: Three-Phase Inverter

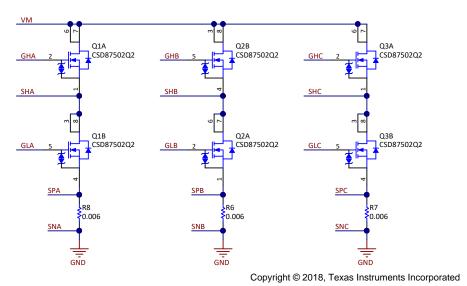

The three-phase inverter is realized using three dual MOSFET blocks CSD87502Q2, as shown in  $\[ \]$  4. Each CSD87502Q2 block consists of two independent 30-V, 27-m $\Omega$  N-channel MOSFETs in a SON 2×2-mm plastic package.

System Overview www.ti.com.cn

图 4. Schematic of Three-Phase Inverter

The resistors R6, R7, and R8 are used for inverter leg current sensing. The voltage across the sense resistor is fed to the MCU through the current shunt amplifiers in the DRV8304.

### 2.3.3 Selecting the Sense Resistor

The selection of sense resistor depends on different factors as follows:

- Power dissipation in the sense resistor

- Offset error voltage and gain of the current sense amplifier

- Peak current to be sensed

The sense resistors are designed to carry a continuous nominal RMS current of 2.5 A and a peak current of 5 A. A high sense resistance value increases the power loss in the resistors. A low sense resistor value increases the error due to input offset voltage of the current sense amplifier at high gain. If the current-sense amplifier is used without offset calibration, select the sense resistor value such that the sense voltage across the resistor is sufficiently higher than the op-amp input offset voltage to reduce the effect of the offset error. The TLV9061 has a maximum input offset error voltage of 1.5 mV. The reference design uses a  $0.006-\Omega$  sense resistor, and the power loss in sense resistor can be calculated using  $\triangle \vec{x}$  2:

Power loss in the resistor =

$$I_{RMS}^2 \times R_{SENSE} = 2.5^2 \times 0.006 = 0.0375 \text{ W}$$

(2)

At a 5-A peak current, using  $\triangle \exists$  2, the power loss in the resistor = 0.15 W.

# 2.3.4 Power Stage Design: Three-Phase Gate Driver

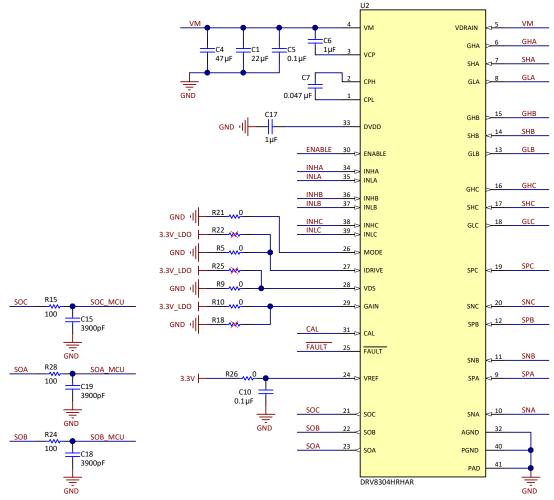

§ 5 shows the schematic of the DRV8304 gate driver. C17 is the DVDD decoupling capacitor that must be placed close to DRV8304. C6 and C7 are the charge pump capacitors. These capacitors are selected to provide a stable charge pump voltage with minimum ripple. VM is the DC supply input; in this case, it is the battery voltage of 10.8 V. C1 and C4 are the bulk ceramic capacitor placed near the inverter bridge.

The gate drive circuit is designed, and the different resistors are selected to meet the specification as per 表 2.

www.ti.com.cn System Overview

# 表 2. Design Specification of DRV8304 Gate Driver

| PARAMETER                                         | DEFAULT VALUE            | CIRCUIT DESCRIPTION                   |

|---------------------------------------------------|--------------------------|---------------------------------------|

| MODE (PWM mode)                                   | 6x PWM control mode      | MODE pin tied to AGND                 |

| I <sub>DRIVE</sub> (gate source and sink current) | 15-mA source, 30-mA sink | IDRIVE pin tied to AGND               |

| V <sub>DS</sub> (monitor reference voltage)       | 0.15 V                   | VDS pin tied to AGND                  |

| GAIN (current sense amplifier gain)               | 40 V/V                   | GAIN pin tied to 3.3 V (DVDD)         |

| $V_{REF}$                                         | 3.3 V                    | Support bidirectional current sensing |

| CAL                                               | Controllable through MCU | Amplifier calibration through MCU     |

Copyright © 2018, Texas Instruments Incorporated

图 5. Schematic of DRV8304 Gate Driver

System Overview www.ti.com.cn

### 2.3.5 Current Sense Amplifier

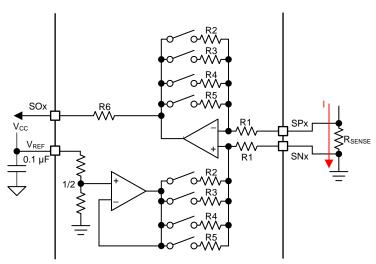

The SOx pin on the DRV8304 outputs an analog voltage equal to the voltage seen across the SPx and SNx pin multiplied by the gain setting (CSA\_GAIN). The gain setting is adjustable between four different levels (5, 10, 20, and 40 V/V). The amplifier as shown in 图 6 can be used to monitor the current through the half-bridges and the current is approximately calculated using 公式 3.

$$I_{SENSE} = \frac{\frac{V_{REF}}{2} - SO_{X}}{CSA\_GAIN \times R_{SENSE}}$$

(3)

图 6. DRV8304 Current Sense Amplifier

The sense amplifier gains on the DRV8304 and sense resistor value are selected based on the target current range,  $V_{REF}$ , sense resistor power rating, and temperature. In bidirectional operation of the sense amplifier, the dynamic range at the output is approximately:

$$V_O = \left(V_{REF} - 0.25 \text{ V}\right) - \frac{V_{REF}}{2}$$

where

$$V_{REF} = 3.3 \text{ V} \tag{4}$$

The required current sense range for the reference design is from –5 A to +5 A. The DRV8304 has an SOx output linear range of 0.25 V to  $V_{REF}$  – 0.25 V (from the  $V_{LINEAR}$  specification). The differential range of the sense amplifier input is –0.3 V to +0.3 V ( $V_{SPDIF}$ ).

$$R_{SENSE} = \frac{1.4 \text{ V}}{A_{V} \times I_{SENSE}}$$

$$V_{O} = (3.3 \text{ V} - 0.25 \text{ V}) - \left(\frac{3.3 \text{ V}}{2}\right) = 1.4 \text{ V}$$

(5)

With  $R_{SENSE}$  = 0.006  $\Omega$  and an amplifier gain of 40 V/V, using  $\Delta \pm 5$ , the design allows a current sensing from –5.8 A to +5.8 A, which means 15% over rated from the required rated peak current of 5 A.

www.ti.com.cn System Overview

#### 2.3.6 MSP430FR5949 MCU

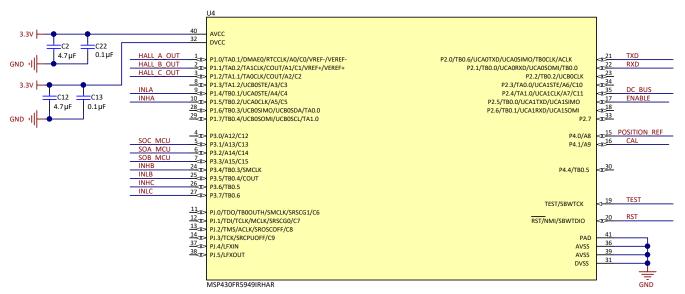

⊠ 7 shows the configuration of MSP430FR5949 MCU. The reference design uses 4.7-μF decoupling capacitors (C2, C12) at AVCC and DVCC pins. A 0.1-μF capacitor has been added to obtain the best performance at a high frequency. The Timer B module of the MCU is used for PWM generation. The seven capture/compare registers helps to realize six PWM signals for three-phase sine control, with a single time base. The six PWM signals are generated at TB0.1 to TB0.6 pins. The digital Hall signals are connected to port 1 of the MCU. For an analog position signal interface, configure the pins as analog pins. The MCU is configured for sensing different analog signals like the inverter leg currents, DC bus voltage, position reference signals, and so on. The provision for UART communication is also provided.

Copyright © 2018, Texas Instruments Incorporated

图 7. Schematic of MSP430FR5949

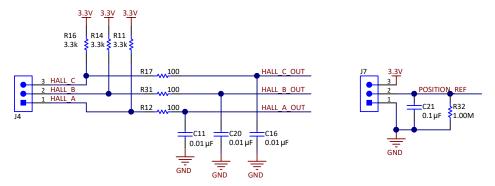

#### 2.3.7 Motor Position Feedback

⊗ 8 shows the position feedback interface from the motor to the reference design board. By default, the reference design is configured to sense digital Hall sensor output, which is connected to port 1 of MCU. The reference design can support analog position feedback also; in that case, connect the sensor output to same port pins and configure the pins as an analog input pin of the MCU ADC.

The position reference signal can be connected to J7 by connecting an external potentiometer (POT).

Copyright © 2018, Texas Instruments Incorporated

图 8. Schematic of Position Feedback

System Overview www.ti.com.cn

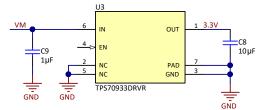

#### 2.3.8 LDO

The reference design uses the ultra-low quiescent current, LDO linear regulator TPS70933 to generate the 3.3-V power supply for the MCU from the input voltage of 10.8 V. № 9 shows the schematic of the LDO circuit.

Copyright © 2018, Texas Instruments Incorporated

### 图 9. Schematic of 3.3-V LDO

The selection of LDO depends on the wide input voltage support (in this design, from 6 V to 16.8 V), the load current, and power dissipation. Power dissipation depends on input voltage and load conditions. Power dissipation ( $P_{DISS}$ ) is equal to the product of the output current and the voltage drop across the output pass element, as given in  $\triangle \pi$  6.

$$P_{DISS} = (V_{IN} - V_{OUT}) \times I_{OUT}$$

(6)

Assuming a nominal LDO load current of 20 mA, the power dissipation at  $V_{IN}$  = 16.8 V can be calculated as:

$$P_{DISS} = (16.8 - 3.3) \times 0.02 = 0.27 \text{ W}$$

表 3 shows the specifications of the LDOs used in this reference design. At lower input voltage, the power dissipation in the LDO reduces. This reference design assumes a maximum LDO output current of 30 mA when operating from a three-cell Li-ion battery.

表 3. Specification of Buck Converter

| PARAMETER              | DESIGN SPECIFICATION            |  |  |

|------------------------|---------------------------------|--|--|

| Input voltage          | 6 V to 16.8 V (10.8-V nominal)  |  |  |

| Output voltage         | 3.3 V                           |  |  |

| Maximum output current | 30 mA (at 10.8-V input voltage) |  |  |

# 3 Hardware, Software, Testing Requirements, and Test Results

### 3.1 Required Hardware and Software

#### 3.1.1 Hardware

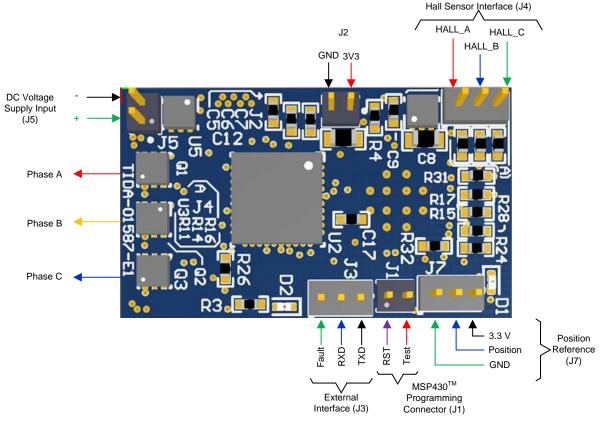

## 3.1.1.1 Connector Configuration of TIDA-01587

10 shows the connector configuration of this reference design, which features:

- Two-terminal input for power supply (J5): This pin is used to connect the input DC supply from the battery. The positive and negative terminals can be identified as shown in

10.

- Three-terminal output for motor winding connection: The phase output connections for connecting to the BLDC motor winding marked as Phase A, Phase B, and Phase C as shown in

10.

- Three-pin connector J3: This connector is used for external UART communication interface. The RX and TX pins enable the communication with external master controller. The FAULT pin of this connector gives indication on FAULT signal from gate driver DRV8304.

- Two-pin connector J1: This is the programming connector for the MSP430FR5949 MCU, along with the 3.3-V lines at connector J2. The two-wire Spy-Bi-Wire protocol is used to program the MSP430FR5949. See the MSP430FR5949 development tools for programming options with an external JTAG interface.

- Three-pin connector J7: This connector interfaces the position reference from external potentiometer. A 20k POT can be used.

- Three-pin connector J4: This connector interfaces hall senor position signal from the motor.

Copyright © 2018, Texas Instruments Incorporated

图 10. PCB Connectors

#### 3.1.1.2 Procedure for Board Bring-up and Testing

Follow this procedure for board bring-up and testing:

- 1. Remove the motor connections from the board and power on the input DC supply. Make sure that a minimum of a 8-V DC input is applied and the 3.3 V is generated in the board.

- 2. Program the MCU. Make sure that the configuration in the program is done as per † 3.1.2.

- 3. Remove the programmer, and switch off the DC input supply.

- 4. Connect the phase outputs from the board to the motor winding terminals.

- 5. Use a DC power supply with current limit protection and apply 8-V DC to the board. The motor starts rotating and stops at the position mentioned by the position reference.

- 6. To change direction, switch off the DC input, and correct the logic in the program and re-load the same in to the MCU.

#### 3.1.2 Software

# 3.1.2.1 High-Level Description of Application Firmware

The reference design firmware offers the following features and user controllable parameters:

- 60° electrical position control using digital hall sensor position feedback

- · BLDC motor speed control using trapezoidal control

表 4 lists the firmware system components.

### 表 4. TIDA-01587 Firmware System Components

| SYSTEM COMPONENT                            | DESCRIPTION                                                                                                                                                                      |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development and emulation                   | Code Composer Studio™ (CCS) version 7                                                                                                                                            |

| Target controller                           | MSP430FR5949                                                                                                                                                                     |

| PWM frequency                               | 20-kHz PWM (default), programmable for higher and lower frequencies                                                                                                              |

| Interrupts                                  | Port 1 Interrupts enabled on P1.0, P1.1, and P1.2 corresponds to digital hall sensor interface                                                                                   |

| PWM generation—Timer configuration          | PWMs: TB0.1–TB0.6; CLOCK = 16 MHz, PWM frequency set for 20 kHz                                                                                                                  |

| Position feedback—Hall sensor signals       | P1.0 → HALL A<br>P1.1 → HALL B<br>P1.2 → HALL C                                                                                                                                  |

| ADC channel assignment                      | A7 → DC bus voltage feedback A8 → Position reference from potentiometer A13 → Phase C inverter leg current A14 → Phase A inverter leg current A15 → Phase B inverter leg current |

| MCU digital inputs/output and communication | P2.5 → ENABLE signal for DRV8304 P2.0 → UART TXD P2.1 → UART RXD P4.1 → CAL pin of DRV8304                                                                                       |

## 3.1.2.2 Customizing the Reference Code

Select the main.c file. Parameters exist at the top of the file that can be optimized and are included as the configuration variables. The following section of code shows these parameters:

```

#define PWM_PERIOD 400 // PWM Frequency (Hz) = 16MHz / ((2*PWM_PERIOD) - 1)

#define DUTY_CYCLE 70 // Input Duty Cycle inversely relative to PWM_PERIOD

#define POLES 8 // Number of poles in motor

#define Gear_Ratio 1 // Gear ratio in the Motor

```

#### 3.1.2.2.1 **PWM\_PERIOD**

The PWM\_PERIOD parameter sets the value in capture and compare register 0 of Timer\_B0. The Timer\_B0 is initialized to operate at a 16-MHz clock. Use 公式 7 to calculate the PWM frequency. The TIMER\_A0 PWM is configured in up-down mode.

PWM Frequency (Hz) =

$$\frac{16 \text{ MHz}}{((2 \times \text{PWM}_{PERIOD}) - 1)}$$

(7)

For example, with PWM\_PERIOD = 400, PWM frequency ≈ 20 kHz.

## 3.1.2.2.2 **DUTY\_CYCLE**

Adjust this parameter to control the speed of the motor. This parameter is inversely related to PWM\_PERIOD.

### 3.1.2.2.3 POLES

This parameter is the number of magnetic poles in the rotor of motor. The algorithm sets the 60° electrical position control using BLDC trapezoidal control, which means the resolution accuracy is 60° electrical.

The equivalent mechanical position resolution accuracy can be calculated from the number of magnetic poles in the rotor (p).

Mechanical Angle

$$(\theta_m) = \frac{\text{Electrical Angle}(\theta_e)}{\left(\frac{p}{2}\right)}$$

(8)

For example, with p = 8, Mechanical resolution angle from motor =  $15^{\circ}$ . If the motor has a gear with 10:1 gear ratio, then:

Equivalent mechanical position resolution =  $\frac{\text{Mechanical resolution angle from motor}}{\text{Gear ratio}} = 1.5^{\circ}$

# 3.2 Testing and Results

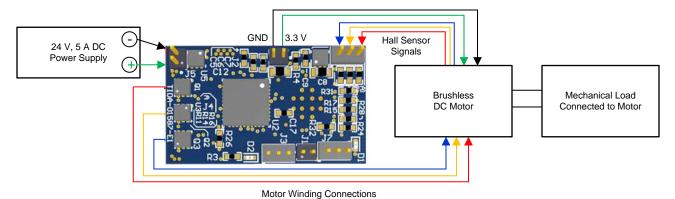

## 3.2.1 Test Setup

The test is performed with a BLDC motor at 10.8-V DC with trapezoidal and sinusoidal control. 图 11 shows the test setup.

Copyright © 2018, Texas Instruments Incorporated

图 11. Load Test Setup

#### 3.2.2 Test Results

# 3.2.2.1 3.3-V Power Supply Generated by the LDO

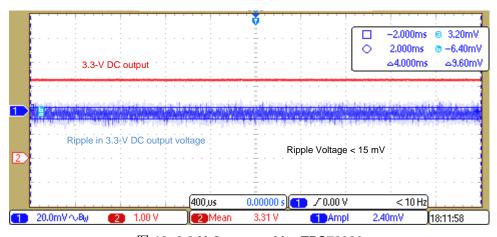

图 12 shows the 3.3 V generated from the LDO. The ripple in the 3.3-V rail is less than 15 mV.

图 12. 3.3 V Generated by TPS70933

### 3.2.2.2 DRV8304 Gate Driver Output Voltage

17

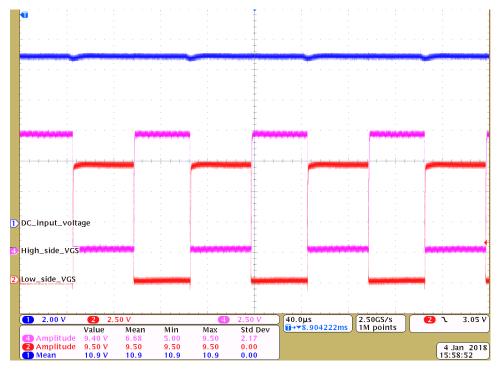

图 13. Low-Side and High-Side Gate Drive Voltage at 10.8-V DC

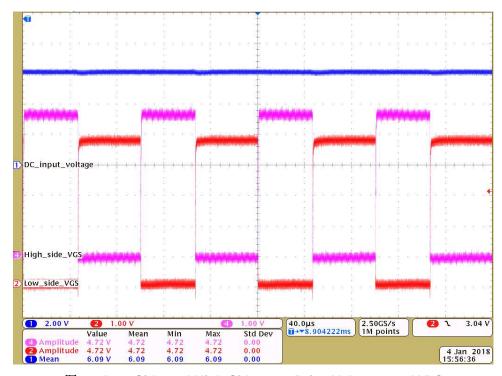

图 14. Low-Side and High-Side Gate Drive Voltage at 6-V DC

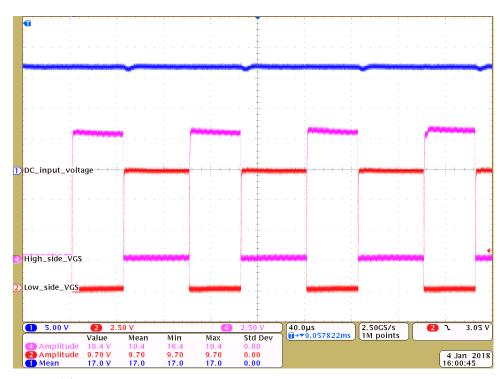

图 15. Low-Side and High-Side Gate Drive Voltage at 17-V DC

### 3.2.2.3 Dead Time From DRV8304

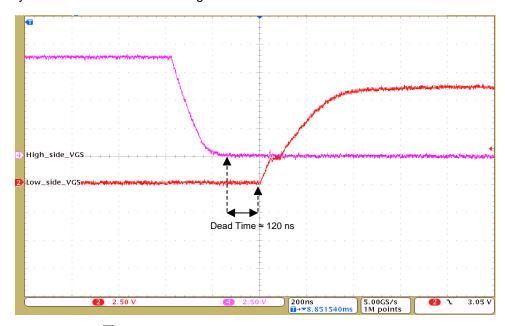

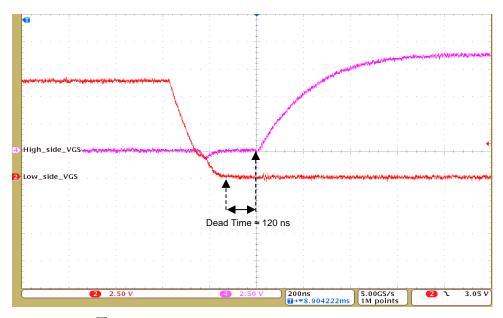

The dead time (t<sub>DEAD</sub>) is measured as the time between turning off one of the half bridge MOSFETs and turning on the other. The hardware version of DRV8304 inserts a fixed dead time of 120 ns.

17 shows the high-side and low-side gate source voltage from the DRV8304, which shows the dead time inserted by the DRV8304 at both the edges of the PWM.

图 16. Dead Time at Rising Edge of Low-Side V<sub>es</sub>

图 17. Dead Time at Trailing Edge of Low-Side V<sub>GS</sub>

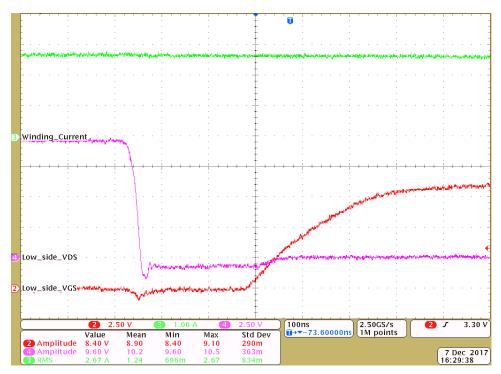

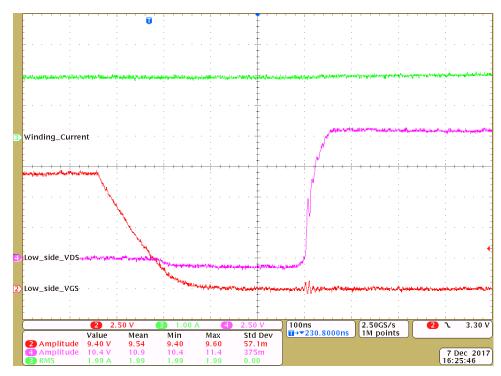

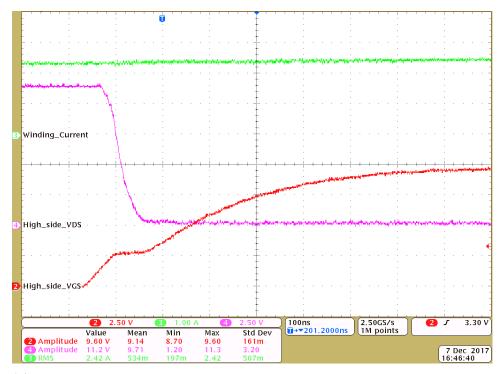

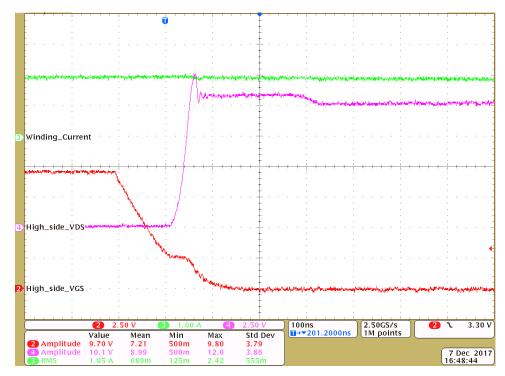

### 3.2.2.4 MOSFET Switching Waveforms

$\boxtimes$  18 to  $\boxtimes$  21 show the V<sub>DS</sub> and V<sub>GS</sub> waveforms of the low-side and high-side MOSFETs at a gate current of the DRV8304 (I<sub>DRIVE</sub>) is set at a 15-mA source (the low gate charge of the CSD87502Q2 allows low source current) and a 30-mA sink current. Switching waveforms are clean without much overvoltage ringing due to the following:

- Small size CSD87502Q2 with two FETs in same package allows reduced PCB parasitic and hence reduces the phase node voltage ringing.

- The current controlled gate driver with slew rate control helps to optimize the switching.

- The I<sub>DRIVE</sub> and T<sub>DRIVE</sub> features of the gate driver helps to shape the gate current to optimize the switching.

$\ \, \boxtimes \,$  18. Low-Side FET Turnon: Low-Side  $V_{GS}$  and  $V_{DS}$  at 2-A Winding Current

$\underline{\hbox{\bf 8}}$  19. Low-Side FET Turnoff: Low-Side  $V_{gs}$  and  $V_{Ds}$  at 2-A Winding Current

${\ensuremath{\mathbb R}}$  20. High-Side FET Turnon: High-Side  ${\ensuremath{V}}_{\text{GS}}$  and  ${\ensuremath{V}}_{\text{DS}}$  at 2-A Winding Current

$\ensuremath{\mathbb{E}}$  21. High-Side FET Turnoff: High-Side  $V_{\text{GS}}$  and  $V_{\text{DS}}$  at 2-A Winding Current

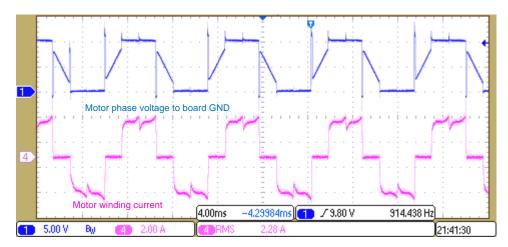

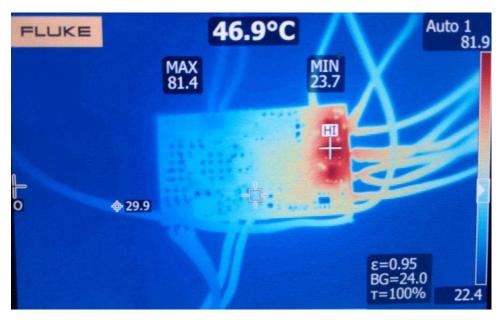

### 3.2.2.5 Load Test

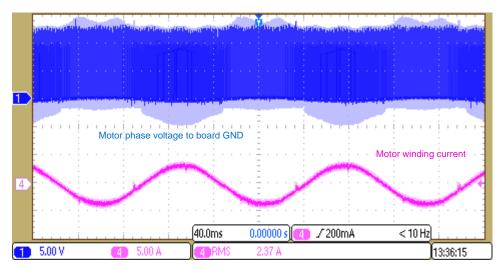

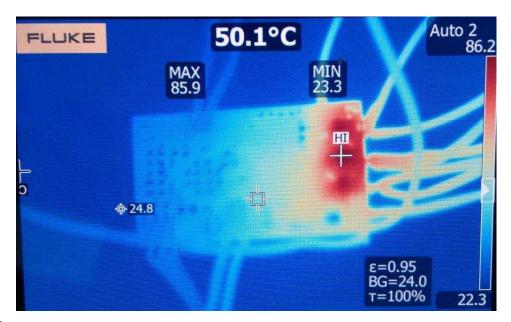

The load test is done with test setup as shown in  $\boxtimes 11$ .  $\not\equiv 5$  lists the load test results.  $\boxtimes 22$  shows the test results with trapezoidal control at 2.28-A<sub>RMS</sub> winding current and 100% duty cycle, and  $\boxtimes 23$  shows the results thermal image of the board after 10 minutes of continuous running. The maximum temperature observed on the MOSFET is 81.4°C.  $\boxtimes 24$  shows the test results with sinusoidal control at a 2.37-A<sub>RMS</sub> winding current, and  $\boxtimes 25$  shows the thermal image of the board after 10 minutes of continuous running. The maximum temperature observed on the MOSFET is 85.9°C.

图 24 shows the test results with sinusoidal control at 2.5-A winding current.

表 5. Load Test Results at 10.8-V DC

| CONTROL<br>METHOD   | VDC (V) | IDC (A) | WINDING<br>CURRENT (RMS)<br>(A) | INPUT POWER (W) | MAXIMUM IC<br>TEMPERATURE<br>(°C) |

|---------------------|---------|---------|---------------------------------|-----------------|-----------------------------------|

| Trapezoidal control | 10.8    | 2.70    | 2.28                            | 29.16           | 81.4                              |

| Sinusoidal control  | 10.8    | 2.72    | 2.37                            | 29.4            | 85.9                              |

图 22. Load Test Results With Trapezoidal Control at 2.28-A<sub>RMS</sub> Winding Current, 100% Duty Cycle

图 24. Load Test Results With Sinusoidal Control at 2.37-A<sub>RMS</sub> Winding Current

图 25. Thermal Image of Board With Sinusoidal Control at 2.37-A<sub>RMS</sub> Winding Current

## 3.2.2.6 Power Stage Efficiency Test

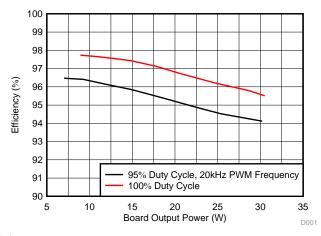

The reference design board power stage efficiency is experimentally tested with a test setup as shown in 图 11. 表 6 lists the test results without heat sink at a 100% duty cycle. 表 7 lists the test results without heat sink at a 95% duty cycle.

表 6. Inverter Efficiency Test Results at 100% Duty Cycle Without Heat Sink and Without Airflow

| INPUT DC<br>VOLTAGE (V) | INPUT DC<br>CURRENT (A) | INPUT DC POWER (W) | MOTOR WINDING<br>RMS CURRENT (A) | BOARD OUTPUT<br>POWER (W) | EFFICIENCY (%) |

|-------------------------|-------------------------|--------------------|----------------------------------|---------------------------|----------------|

| 10.63                   | 0.859                   | 9.13               | 0.792                            | 8.93                      | 97.73          |

| 10.81                   | 1.031                   | 11.15              | 0.932                            | 10.89                     | 97.66          |

| 10.78                   | 1.207                   | 13.02              | 1.074                            | 12.70                     | 97.56          |

| 10.75                   | 1.411                   | 15.17              | 1.239                            | 14.78                     | 97.44          |

| 10.91                   | 1.678                   | 18.31              | 1.460                            | 17.79                     | 97.13          |

| 10.87                   | 1.965                   | 21.35              | 1.698                            | 20.65                     | 96.73          |

| 10.80                   | 2.378                   | 25.67              | 2.039                            | 24.70                     | 96.21          |

| 10.73                   | 2.785                   | 29.87              | 2.362                            | 28.62                     | 95.80          |

| 10.69                   | 2.989                   | 31.95              | 2.507                            | 30.51                     | 95.51          |

# 表 7. Inverter Efficiency Test Results at 95% Duty Cycle Without Heat Sink and Without Airflow

| INPUT DC<br>VOLTAGE (V) | INPUT DC<br>CURRENT (A) | INPUT DC POWER (W) | MOTOR WINDING RMS CURRENT (A) | BOARD OUTPUT<br>POWER (W) | EFFICIENCY (%) |

|-------------------------|-------------------------|--------------------|-------------------------------|---------------------------|----------------|

| 10.91                   | 0.667                   | 7.27               | 0.661                         | 7.02                      | 96.47          |

| 10.87                   | 0.886                   | 9.63               | 0.845                         | 9.28                      | 96.41          |

| 10.83                   | 1.156                   | 12.52              | 1.070                         | 12.03                     | 96.13          |

| 10.78                   | 1.448                   | 15.61              | 1.325                         | 14.96                     | 95.85          |

| 10.90                   | 1.813                   | 19.76              | 1.634                         | 18.85                     | 95.36          |

| 10.81                   | 2.191                   | 23.69              | 1.959                         | 22.48                     | 94.88          |

| 10.77                   | 2.490                   | 26.81              | 2.215                         | 25.35                     | 94.53          |

| 10.69                   | 3.002                   | 32.10              | 2.657                         | 30.21                     | 94.12          |

26 shows the efficiency curve of these test conditions.

图 26. Power Stage Efficiency versus Output Power

The low  $R_{DS(on)}$  of the CSD87502Q2 MOSFET power blocks along with clean MOSFET switching by the DRV8304 smart gate driver enable maximum three-phase inverter efficiency. The thermal pads on the MOSFET power blocks help to extract the heat to the PCB.

### 3.2.2.7 Overcurrent Limit Results

The gate driver DRV8304 implement adjustable  $V_{DS}$  monitors to detect overcurrent or short conditions on the external MOSFETs. The high-side  $V_{DS}$  monitors measure the voltage between the VDRAIN and SHX pins. In configuration with three current shunt amplifiers, the low-side  $V_{DS}$  monitors measure the voltage between the SHX and SPX pins.

When the voltage monitored is greater than the  $V_{DS}$  trip point ( $V_{DS,OCP}$ ) after the  $V_{DS}$  deglitch time ( $t_{DS,OCP}$ ) has expired, the DRV8304 detects an OCP condition and takes action according to the fault setting. In the hardware version of the DRV8304, the  $V_{DS}$  monitor acts in automatic retry mode with a 4-ms retry time.

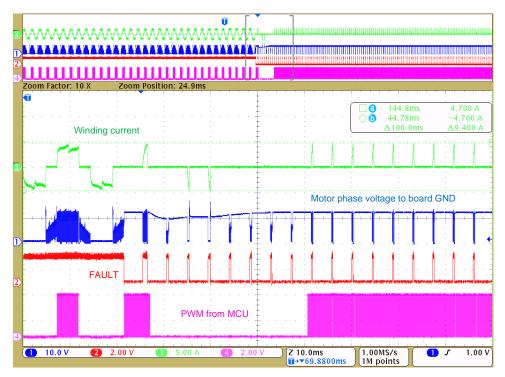

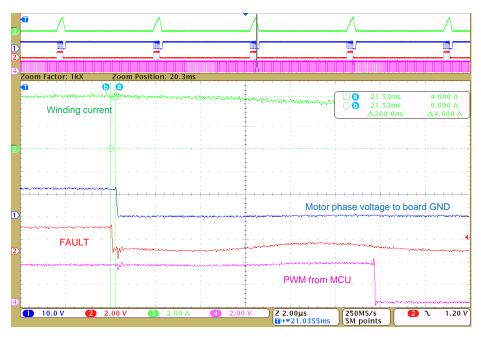

827 shows the  $V_{DS}$  overcurrent action with the  $V_{DS}$  reference voltage set to 0.15 V.

Assuming the junction temperature of 75°C, the  $R_{DS(on)}$  at 75°C ≈ 34 m $\Omega$  (approximately 1.26 times the  $R_{DS(on)}$  at 25°C, from the CSD87502Q2 data sheet).

#### where:

- $V_{DS}$  deglitch time  $(t_{DS,OCP}) = 4.5 \mu s$

- Current limit threshold = V<sub>DS</sub> threshold / R<sub>DS(on)</sub> = 4.41 A

图 27. Overcurrent Protection With MOSFET V<sub>DS</sub> Monitoring

图 28. Zoomed View of Overcurrent Protection With MOSFET V<sub>DS</sub> Monitoring

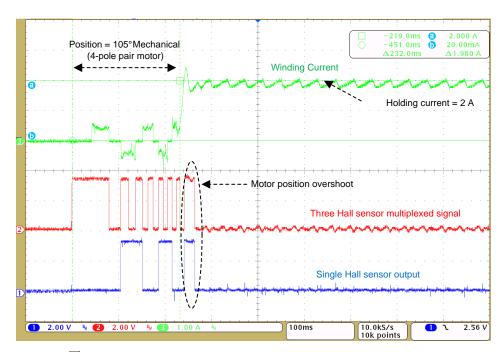

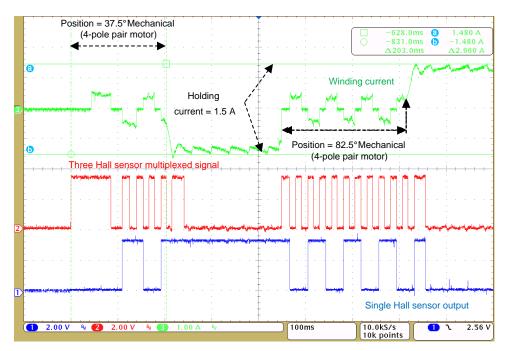

## 3.2.2.8 BLDC Motor 60° Electrical Position Control With Trapezoidal Excitation

Position control algorithm on the MSP430FR5949 is implemented using port interrupts capability of the MSP430 MCU. The testing is done on the BLDC motor that has three digital Hall position sensors.

⊠ 30 shows the test result with step change in mechanical position reference from 37.5° mechanical to 82.5° mechanical with a 1.5-A holding current.

图 29. Test Results for Position Control at 105° Mechanical

图 30. Test Results for Position Control With a Step Change in Position Reference

Design Files www.ti.com.cn

## 4 Design Files

# 4.1 Schematics

To download the schematics, see the design files at TIDA-01587.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01587.

# 4.3 PCB Layout Recommendations

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01587.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01587.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01587.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01587.

#### 5 Software Files

To download the software files, see the design files at TIDA-01587.

## 6 Related Documentation

- 1. Texas Instruments, Field Oriented Control (FOC) Made Easy for Brushless DC (BLDC) Motors Using TI Smart Gate Drivers Application Brief

- 2. Texas Instruments, DRV8304 38-V 3-Phase Smart Gate Driver Data Sheet

### 6.1 商标

E2E, MSP430, Code Composer Studio are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

### 7 Terminology

**BLDC**— Brushless DC

**ESD**— Electrostatic discharge

**MCU**— Microcontroller unit

**PWM**— Pulse width modulation

www.ti.com.cn About the Authors

### 8 About the Authors

**MANU BALAKRISHNAN** is a systems engineer at Texas Instruments, where he is responsible for developing subsystem design solutions for the Industrial Motor Drive systems. Manu brings to this role his experience in power electronics and analog and mixed signal designs. He has system level product design experience in permanent magnet motor drives. Manu earned his bachelor of technology in electrical and electronics engineering from the University of Kerala and his master of technology in power electronics from National Institute of Technology Calicut, India.

**VARAD JOSHI** is a project trainee in the Industrial Systems team at Texas Instruments, where he is learning and developing reference design solutions with a focus on motor drive systems. Varad is a final-year student pursuing a bachelor of engineering (B.E. hons) in electrical and electronics engineering from Birla Institute of Technology & Sciences (BITS), Pilani, Goa.

**JASRAJ DALVI** is an end equipment lead with Industrial Systems team at Texas Instruments, where he is responsible for defining reference design solutions and control algorithms for motor control systems. He completed his bachelors of engineering degree in electrical engineering from University of Pune, India and his post-graduate diploma in marketing management at S.I.B.M. in Pune, India.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司