# TI Designs: TIDA-01426

利用低压直流电源生成线路交流电压且可用于传感器励磁的参考设计

## 说明

此参考设计展示了如何让设计人员使用分立式组件获得可用于检测火焰的高压信号。低 BOM 成本和小型解决方案尺寸是此参考设计的重要目标。通过采用推挽转换器拓扑,可以实现宽输入范围和短启动时间。

### 资源

TIDA-01426设计文件夹TL494产品文件夹TL431产品文件夹CSD19538Q3A产品文件夹TLV171产品文件夹

咨询我们的 E2E 专家

## 特性

- 通用输入范围为 10V 到 36V

- 120V、60Hz 输出, THD 最高 4%

- 10V 时的启动时间为 56ms

- 5% 输出精度

- 高达 1W 的输出功率

- 小尺寸和低 BOM 成本

## 应用

- HVAC 阀门和致动器控制

- HVAC 传感器发送器

- HVAC 系统控制器

A

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

## 1 System Description

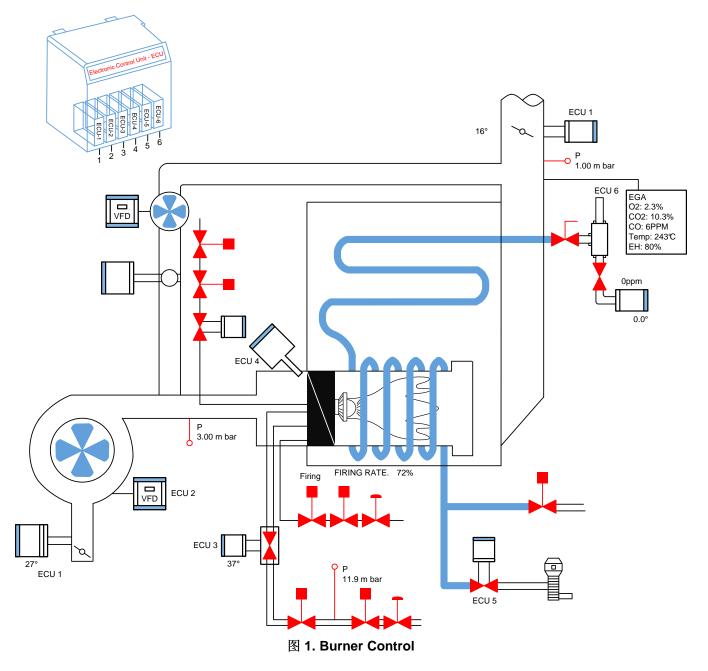

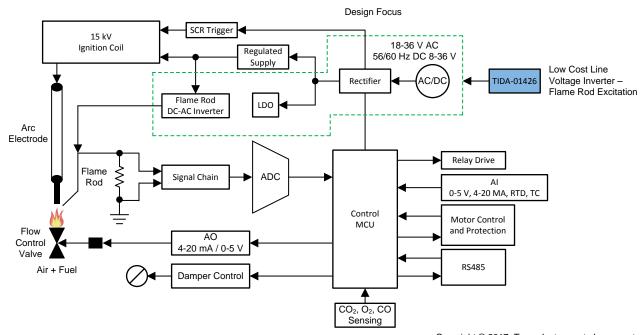

A burner system is an integral part of a heating, ventilation, and air conditioning (HVAC) system. A burner system helps generate hot water or steam for heating purposes. The hot water is circulated either for utility purposes or for temperature control. The burner system has control electronics as shown in \$\mathbb{B}\$ 1 to operate in optimum conditions and prevent any failure with a predictive diagnosis alarm. The electronics unit has actuator control and field sensing cards for the motor drive, damper control, flow control, temperature and pressure sensing, and so on. The unit also ignites and senses flame inside the burner as shown by ECU4 (see \$\mathbb{B}\$ 1). This reference design focuses on the excitation power supply for the flame rod.

www.ti.com.cn System Description

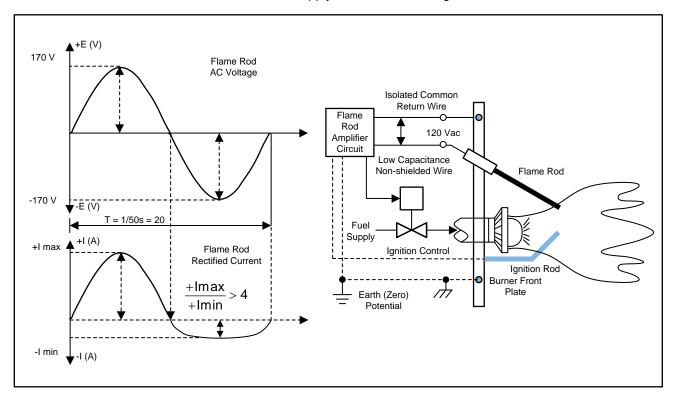

The flame rod sensor is a high impedance sensor. Under the presence of flame, an ionization effect takes place due to which current flows from the flame rod to earth. This current is proportional to flame intensity. As shown in  $\[mathbb{R}\]$  2, a high-voltage excitation is required for ionization effect. To prevent carbonization effect, AC excitation is applied. This excitation is usually a line supply 50- or 60-Hz signal. A low-frequency AC signal is used to prevent losses due to cable capacitance and skin effect. The geometric ratio of flame rod and earth plate decides the conduction in positive and negative polarity. Usually the ratio is lower to make the flame rod conduct more in positive half cycles and negligible in negative half cycles. This ratio results in output similar to a half wave rectifier. Thus, the flame rod is equivalent to a forward bias diode with a high series impedance, which is the function of flame intensity as shown in  $\[mathbb{R}\]$  2. A signal chain amplifies the lower AC current and controls the fuel supply for the burner firing rate.

图 2. Flame Sensing Using Flame Rod

## 1.1 Key System Specifications

表 1. Key System Specifications

|                                                                                                                     | PARAMETER                        |     |     | SPECIFICATIONS |    |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|-----|----------------|----|--|--|--|--|

|                                                                                                                     | MIN                              | TYP | MAX | UNIT           |    |  |  |  |  |

| Input oupply voltage (\/ \)                                                                                         | DC                               | 10  | 24  | 33             | V  |  |  |  |  |

| Input supply voltage (V <sub>IN</sub> )                                                                             | AC at 50 or 60                   | 18  | 24  | 33             | V  |  |  |  |  |

| Quiescent current (I <sub>Q</sub> )                                                                                 |                                  | _   | _   | 0.3            | Α  |  |  |  |  |

| Output voltage (V <sub>O</sub> )                                                                                    | Output voltage (V <sub>o</sub> ) |     | 120 | 140            | V  |  |  |  |  |

| Output current (I <sub>O</sub> )                                                                                    |                                  | _   | _   | 0.0015         | Α  |  |  |  |  |

| Output load (R <sub>L</sub> ) Max cable capacitance 720 pF, assuming 22 AWG, 60 feet, 1 pair twisted cable 12 pF/ft |                                  | 1   | 40  | 100            | ΜΩ |  |  |  |  |

System Description www.ti.com.cn

# 表 1. Key System Specifications (continued)

| PARAMETER   |                      |   | SPECIFICATIONS |     |      |  |  |  |

|-------------|----------------------|---|----------------|-----|------|--|--|--|

|             |                      |   | TYP            | MAX | UNIT |  |  |  |

|             | Initial accuracy     | _ | 5              | _   | %    |  |  |  |

| Performance | THD                  | _ | 4              |     | %    |  |  |  |

|             | Startup time at 10 V | _ |                | 100 | ms   |  |  |  |

## 2 System Overview

## 2.1 Block Diagram

图 3. System Block Diagram

## 2.2 Highlighted Products

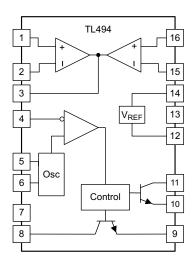

#### 2.2.1 TL494

The TL494 device incorporates all the functions required in the construction of a control circuit for pulse width modulation (PWM) on a single chip. The TL494 device contains two error amplifiers, an on-chip adjustable oscillator, a dead-time control (DTC) comparator, a pulse-steering control flip-flop, a 5-V, 5%-precision regulator, and output control circuits. The error amplifiers exhibit a common-mode voltage ranging from -0.3 V to VCC -2 V. The DTC comparator has a fixed offset that provides approximately 5% dead time. The uncommitted output transistors provide either common-emitter or emitter-follower output capability. The TL494 device provides for push-pull or single-ended output operation, which can be selected through the output-control function. The architecture of this device prohibits the possibility of either output being pulsed twice during push-pull operation. The TL494C device is characterized for operation from 0°C to 70°C. The TL494I device is characterized for operation from -40°C to 85°C.

图 4. TL494 Block Diagram

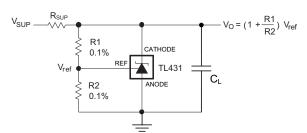

## 2.2.2 TL431

The TL431 device is a three-terminal adjustable shunt regulator. The output voltage can be set to any value between  $V_{REF}$  (approximately 2.5 V) and 36 V with two external resistors. These devices have a typical output impedance of 0.2  $\Omega$ . Active output circuitry provides a very sharp turnon characteristic, making these devices excellent replacements for Zener diodes in onboard regulation, adjustable power supplies, and switching power supplies.

图 5. TL431 Shunt Regulator

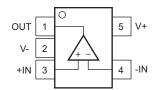

### 2.2.3 TLV171

The 36-V TLV171 device provides a low-power option for cost-conscious industrial systems requiring an electromagnetic interference (EMI)-hardened, low-noise, single-supply operational amplifier (op amp) that operates on supplies ranging from 2.7 V (±1.35 V) to 36 V (±18 V). The TLV171 provides low offset, drift, and quiescent current balanced with high bandwidth for the power. Input signals beyond the supply rails do not cause phase reversal. The TLV171 is stable with capacitive loads up to 200 pF. The input can operate 100 mV below the negative rail and within 2 V of the top rail during normal operation.

图 6. TLV171 Block Diagram

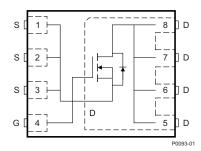

### 2.2.4 CSD19538Q3A

The CSD19538Q3A is NexFET<sup>TM</sup> power MOSFET with a drain-to-source voltage of 100 V, a low R<sub>DSon</sub> of 49 m $\Omega$ , and small footprint SON of 3.3 mm × 3.3 mm to achieve very low conduction losses and reduce board space.

图 7. MOSFET CSD19538Q3A

## 2.3 System Design Theory

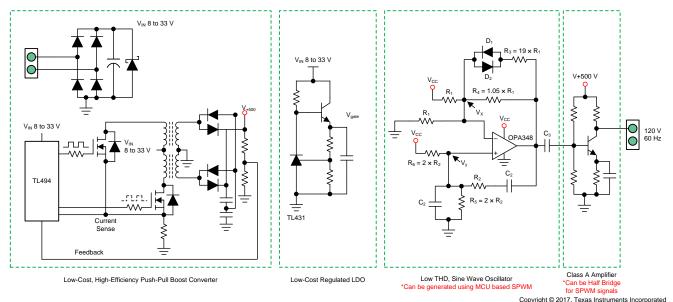

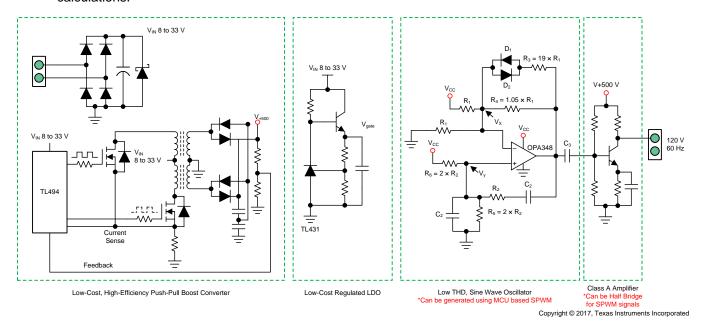

The TIDA-01426 design focuses on the design of a power supply targeted for flame rod excitation in burner control, as shown in 88. The supply needs to generate a low-voltage regulated supply for low-power peripherals and line supply voltage for flame rod excitation. Using the TL494 and TL431 devices generates the required low- and high-voltage supplies.

Copyright © 2017, Texas Instruments Incorporated

图 8. Typical Electronics Control Board

## 2.3.1 Designing Push-Pull Converter

#### 2.3.1.1 TL494 Calculations

To generate high DC bus voltage, push-pull topology is implemented in this reference design. Using flux swing in both polarities and high switching frequency makes it easy to design the small size magnetic transformer. TL494 integrated peripherals like an oscillator, dead-time controller, error amplifier, and PWM generator make it possible to design a low-cost, regulated output, push-pull converter.

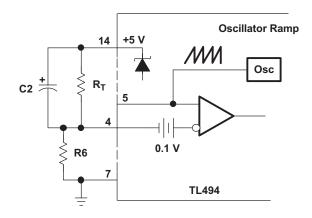

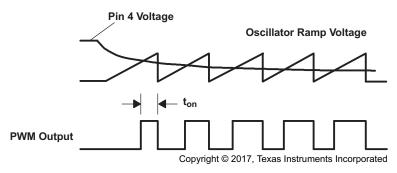

#### 2.3.1.1.1 Oscillator Calculations

The oscillator of the TL494 is set by  $R_t$  and  $C_t$ . To design a smaller magnetic transformer, a 100-kHz oscillating frequency is selected. For push-pull configuration with a  $C_t$  of 1 nF, the computed  $R_t$  value is 5k as shown in  $\triangle \not\equiv 1$ . The closest standard value is 4.99k. In the schematic,  $R_6$  and  $R_6$  denotes  $R_t$  and  $R_6$ . For stable oscillations, a low-ppm resistor and C0G capacitor are recommended.

$$R_{T} = \frac{1}{2 \times f_{OSC} \times C_{T}} = \frac{10^{9}}{2 \times 100000 \times 1} = 5 \text{ k}$$

(1)

### 2.3.1.1.2 Soft-Start and Dead-Time Calculations

$$C_2 = \frac{100 \times \frac{1}{f_{SW}}}{R_6} = \frac{100 \times \frac{1}{100000}}{1000} = 1 \,\mu\text{F}$$

(2)

As the soft-start slope slowly decays, the potential due resistor divider  $R_6$  and  $R_7$  with an internal 0.1-V offset result into a tailored dead time. After soft-start, the voltage at the pin is a ratio of  $R_6$ : $R_7$  multiplied by  $V_{REF}$ . The value for dead time is computed based on the turnon and turnoff time of the MOSFET so that enough blanking is provided to prevent cross conduction. For this reference design, a blanking time of 500 ns is provided with resistor  $R_7$  of 5k.

图 9. Soft-Start Circuit

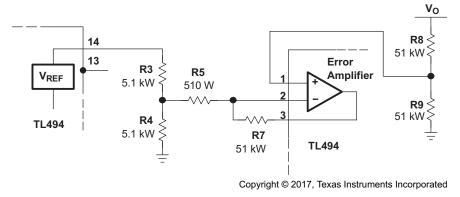

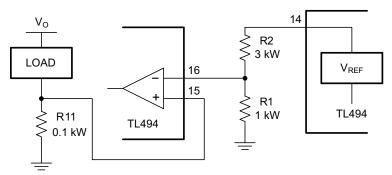

## 2.3.1.1.3 Voltage Error Amplifier

A simple non-inverting error amplifier is implemented with one of the TL494 internal op amps. An internal reference of 5 V is divided to 2.5 using resistors  $R_{11}$  and  $R_{14}$  in board. 20 10 is shown with resistors 20 and 20 10 is shown with resistors 20 and 20 11 is shown with resistors 20 and 20 12 is shown with resistors 20 and 20 13 is shown with resistors 20 and 20 14 is shown with resistors 20 and 20 15 is shown with resistors 20 and 20 16 is shown with resistors 20 and 20 26 is shown with resistors 20 27 is shown with resistors 20 28 and 20 29 in the desired closed loop gain.

图 10. Feedback Error Amplifier

#### 2.3.1.1.4 Overcurrent Protection

Overcurrent protection is implemented using one of the internal op amps of the TL494. A stable 1 V is applied to the negative terminal of the op amp using resistors  $R_{13}$  and  $R_{15}$  in the actual circuit. A current sense resistor  $R_{12}$  of 1  $\Omega$  is connected to the source pin of the MOSFET  $Q_1$  and  $Q_2$ . The circuit is limited to a peak current of 1 A once the voltage across sense resistor  $R_{12}$  increases to a 1-V reference.

Copyright © 2017, Texas Instruments Incorporated

图 11. Current-Limiting Circuit

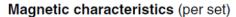

## 2.3.1.2 Magnetic Design

The objective for this application is to have a smaller footprint transformer. To achieve the same, this reference design has a 100-kHz switching frequency and a max duty cycle of 40%. In this application, Wurth E13 core transformer is used. For a custom transformer design, the proper core material needs to be selected. N87, N88, N95, N96, and N97 are some standard core materials available from TDK Epcos for a switching frequency up to 500 kHz. N87 core can be selected which has saturation flux of 0.39 T at 100°C with core loss of 3.75 mW / mm³ at 100 kHz switching. This application uses a custom Wurth Transformer. The design equations shown in  $\frac{1}{8}$  3 can be used for a custom transformer design. For a cost-sensitive application, a Toroid core can also be used. For ease of design, the maximum flux swing (Bm) can be limited to 0.2 T with current density (J) of 3 A/mm². The E13 core is selected to show design calculations.

| SR NO | PARAMETER                              | VALUE                                                                                                              | UNIT            |

|-------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| 1     | Cross sectional area (A <sub>c</sub> ) | 12.4                                                                                                               | mm <sup>2</sup> |

| 2     | Window area (A <sub>w</sub> )          | $\left(\frac{\left(8.9-3.7\right)}{2}-0.3\right)\times\left(4.5-0.3\right)=9.66$ where 0.3 is for bobbin clearance | mm²             |

| 3     | Area product (A <sub>p</sub> )         | $A_c \times A_w = 82.58$                                                                                           | mm⁴             |

| 4     | Nominal inductance (A <sub>i</sub> )   | 850                                                                                                                | nH              |

表 2. E13 Core Calculations

## E 13/7/4 (EF 12.6)

Core B66305

- To IEC 61246

- For miniature transformers

- Available with SMD coil former

- E cores with high permeability for common-mode chokes and broadband applications

- Delivery mode: single units

$\Sigma$ I/A = 2.39 mm<sup>-1</sup> I<sub>e</sub> = 29.6 mm A<sub>e</sub> = 12.4 mm<sup>2</sup> A<sub>min</sub> = 12.2 mm<sup>2</sup> V<sub>e</sub> = 367 mm<sup>3</sup>

## Approx. weight 2 g/set

## Ungapped

| Material | A <sub>L</sub> value<br>nH | μ <sub>e</sub> | P <sub>V</sub><br>W/set          | Ordering code   |

|----------|----------------------------|----------------|----------------------------------|-----------------|

| N30      | 1000 +30/–20%              | 1900           |                                  | B66305G0000X130 |

| T46      | 3600 ±30%                  | 6839           |                                  | B66305F0000X146 |

| N27      | 800 +30/–20%               | 1510           | < 0.40 (200 mT, 100 kHz, 100 °C) | B66305G0000X127 |

| N87      | 850 +30/–20%               | 1620           | < 0.20 (200 mT, 100 kHz, 100 °C) | B66305G0000X187 |

图 12. E13 Core Specification

## 表 3. Transformer Calculations

| SR<br>NO | PARAMETER                              | EQUATION                                                                                                                                                                                                                                | COMPUTED<br>VALUE      | SELECTED<br>VALUE                                |

|----------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------|

| 1        | Required area product                  | $A_{p} = \frac{\left(\sqrt{2} \times V_{DC} \times I_{DC}\right) \times \left(1 + \frac{1}{\eta}\right)}{4 \times k_{w} \times B_{m} \times f_{s} \times J}$ where $k_{w} = 0.4$ , $\eta = 0.8$ , $V_{DC} = 500$ V, and $I_{DC} = 2$ mA | 33.14 mm <sup>4</sup>  | Area product computed as shown in 表 2 is greater |

| 2        | Primary turns                          | $N_1 = \frac{V_{MIN}}{4 \times B_m \times f_s \times A_c}$ where $A_c$ is the cross section of the core                                                                                                                                 | 10                     | 10                                               |

| 3        | Turns ratio                            | $n = \frac{V_{DC}}{2 \times D_{MAX} \times V_{MIN}}$ where $D_{MAX} = 0.4$                                                                                                                                                              | 62.5                   | 63                                               |

| 4        | Secondary turns                        | $N_2 = n \times N_1$                                                                                                                                                                                                                    | 630                    | 630                                              |

| 5        | Secondary RMS current                  | $I_2 = \sqrt{D_{MAX}} \times I_{DC}$                                                                                                                                                                                                    | 1.43 mA                | _                                                |

| 6        | Primary RMS current                    | $I_1 = n \times I_2$                                                                                                                                                                                                                    | 90.5 mA                | _                                                |

| 7        | Cross section area of primary wire     | $a_1 = \frac{I_1}{J}$                                                                                                                                                                                                                   | 0.026 mm <sub>2</sub>  | 36 SWG<br>0.02927 mm <sub>2</sub>                |

| 8        | Cross sectional area of secondary wire | $a_2 = \frac{I_2}{J}$                                                                                                                                                                                                                   | 0.0004 mm <sub>2</sub> | 45 SWG<br>0.003973<br>mm <sub>2</sub>            |

| 9        | Total winding area                     | $\sum_{i=1}^{2} a_{i} N_{i} = (2 \times N_{1} \times a_{1}) + (N_{2} \times a_{2})$                                                                                                                                                     | 3.08 mm <sub>2</sub>   | _                                                |

| 10       | Utilization factor                     | $\left(\frac{\text{Total Winding Area}}{\text{Window Area A}_{\text{w}}}\right) \times 100$                                                                                                                                             | 31.88 %                | Value < 40 %                                     |

Inductors can be added in series with output diodes and capacitors to limit ripple current.

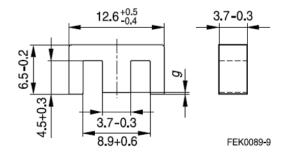

### 2.3.1.3 MOSFET Drive and Losses

The fast switching speed, low drop voltage, and high input impedance of MOSFETs make them suitable for push-pull switching. The TI NexFET CSD19538Q3A with low drain-to-source channel resistance is selected for push-pull drive. The MOSFET is driven using an external totem pole transistor for a better drive capability.

#### 2.3.1.3.1 Conduction Losses

The MOSFET gate drive is driven through the totem pole circuit as shown in 🗵 13.

图 13. MOSFET Totem Pole Drive

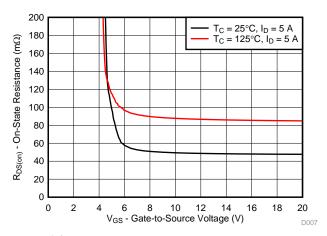

During high pulse, the NPN transistor conducts resulting in a gate drive voltage of 8.5 V due to a 0.5-V drop across the collector emitter. From the MOSFET datasheet, the typical  $R_{DSon}$  for a 8-V gate-to-source voltage is 50 m $\Omega$ .

图 14. MOSFET On-State Resistance

Power loss during conduction phase is computed as shown in 公式 3.

$$P_{cond} = \frac{1}{T} \int_{0}^{ton} (n \times I_0)^2 \times R_{DSon} dt = \frac{1}{T} (n \times I_0)^2 \times R_{DSon} \times ton = (n \times I_0)^2 \times R_{DSon} dt \times D = 317 \ \mu W \tag{3}$$

## 2.3.1.3.2 Gate Drive Power Loss

During turnon, the gate-to-source capacitance ( $C_{gs}$ ) charges through resistor R + R $_g$ . The current waveform is exponential decay. During this period there is power loss across the N-channel transistor.  $Q_{gs}$  is obtained from the MOSFET datasheet as shown in  $\frac{1}{8}$  4.

表 4. Electrical Characteristics<sup>(1)</sup>

|                     | PARAMETER                        | TEST CONDITIONS                                                  | MIN   | TYP   | MAX   | UNIT  |  |  |

|---------------------|----------------------------------|------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| STATIC              | CHARACTERISTICS                  |                                                                  |       |       | '     |       |  |  |

| BV <sub>DSS</sub>   | Drain-to-source voltage          | $V_{GS} = 0 \text{ V}, I_{D} = 250 \mu\text{A}$                  | 100.0 | _     | _     | V     |  |  |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 80 V                    | _     | _     | 1.0   | μΑ    |  |  |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = 20 V                    | _     | _     | 100.0 | nA    |  |  |

| $V_{GS(th)}$        | Gate-to-source threshold voltage | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$                             | 2.8   | 3.2   | 3.8   | V     |  |  |

| В                   | Drain-to-source on resistance    | $V_{GS} = 6 \text{ V}, I_{D} = 5 \text{ A}$                      | _     | 58.0  | 72.0  | mΩ    |  |  |

| R <sub>DS(on)</sub> | Diam-to-source on resistance     | $V_{GS} = 10 \text{ V}, I_{D} = 5 \text{ A}$                     | _     | 49.0  | 59.0  | 11122 |  |  |

| g <sub>fs</sub>     | Transconductance                 | V <sub>DS</sub> = 10 V, I <sub>D</sub> = 5 A                     | _     | 6.1   | _     | S     |  |  |

| DYNAM               | IIC CHARACTERISTICS              |                                                                  | ,     |       | '     |       |  |  |

| C <sub>iss</sub>    | Input capacitance                |                                                                  | _     | 349.0 | 454.0 | pF    |  |  |

| C <sub>oss</sub>    | Output capacitance               | $V_{GS} = 0 \text{ V}, V_{DS} = 50 \text{ V}, f = 1 \text{ MHz}$ | _     | 69.0  | 90.0  | pF    |  |  |

| C <sub>rss</sub>    | Reverse transfer capacitance     |                                                                  | _     | 12.6  | 16.4  | pF    |  |  |

| $R_{G}$             | Series gate resistance           | _                                                                | _     | 4.6   | 9.2   | Ω     |  |  |

| $Q_g$               | Gate charge total (10 V)         |                                                                  | _     | 4.3   | _     | nC    |  |  |

| $Q_{gd}$            | Gate charge gate-to-drain        | V 50 V I 5 A                                                     | _     | 0.8   | _     | nC    |  |  |

| $Q_{gs}$            | Gate charge gate-to-source       | $V_{DS} = 50 \text{ V}, I_{D} = 5 \text{ A}$                     | _     | 1.6   | _     | nC    |  |  |

| $Q_{g(th)}$         | Gate charge at V <sub>th</sub>   |                                                                  | _     | 1.0   | _     | nC    |  |  |

| Q <sub>oss</sub>    | Output charge                    | V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0 V                    | _     | 12.3  | _     | nC    |  |  |

| t <sub>d(on)</sub>  | Turnon delay time                |                                                                  | _     | 5.0   | _     | ns    |  |  |

| t <sub>r</sub>      | Rise time                        | $V_{DS} = 50 \text{ V}, V_{GS} = 10 \text{ V},$                  | _     | 3.0   | _     | ns    |  |  |

| t <sub>d(off)</sub> | Turnoff delay time               | $I_{DS} = 5 \text{ A}, R_G = 0 \Omega$                           | _     | 7.0   | _     | ns    |  |  |

| t <sub>f</sub>      | Fall time                        |                                                                  | _     | 2.0   | _     | ns    |  |  |

| DIODE               | DIODE CHARACTERISTICS            |                                                                  |       |       |       |       |  |  |

| $V_{SD}$            | Diode forward voltage            | I <sub>SD</sub> = 5 A, V <sub>GS</sub> = 0 V                     | _     | 0.85  | 1     | V     |  |  |

| Q <sub>rr</sub>     | Reverse recovery charge          | V <sub>DS</sub> = 50 V, I <sub>F</sub> = 5 A,                    | _     | 94.00 | _     | nC    |  |  |

| t <sub>rr</sub>     | Reverse recovery time            | di/dt = 300 A/μs                                                 | _     | 32.00 | _     | ns    |  |  |

|                     |                                  |                                                                  |       |       |       |       |  |  |

<sup>(1)</sup>  $T_A = 25^{\circ}C$

Power lost due to gate switching is computed as shown in 公式 4.

$$P_{GATE} = V_{GS} \times Q_{GS} \times f_{SW} = 8.5 \times 1.6 \times 10^{-9} \times 100000 = 1.36 \text{ mW}$$

(4)

## 2.3.1.3.3 MOSFET Switching Losses

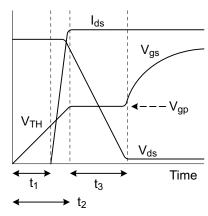

During turnon and turnoff, the gate voltage rises slowly as the input capacitance charges, this results in switching loss across MOSFET. These losses can be computed independently for turn on and turn off by computing timing of each phase. As shown in [8] 15 and [8] 16, during turnon initially the input capacitance charges until the gate potential reaches the gate threshold voltage. After reaching the threshold, the drain current starts to increase until the gate voltage reaches Miller voltage. After reaching Miller voltage, the drain-to-source voltage falls as the gate-to-drain capacitance charges. Switching losses are in the region between the threshold voltage to Miller voltage and from the Miller voltage to the fall of the drain-to-source voltage.

$V_{gs}$   $V_{ds}$   $V_{ds}$   $V_{ds}$   $V_{ds}$   $V_{ds}$

图 15. MOSFET Turnon Characteristics

图 16. MOSFET Turnoff Characteristics

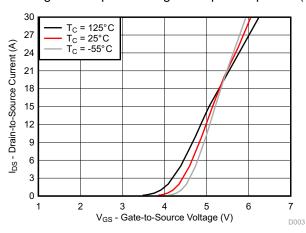

To compute the timings, the gate threshold voltage and plateau voltage need to be computed. From the MOSFET datasheet, gate voltage is computed using a two-point equation (see 图 17 and 公式 5).

图 17. MOSFET Transfer Characteristics

$$V_{TH} = \frac{V_{GS1} \times \sqrt{I_{D2}} - V_{GS2} \times \sqrt{I_{D1}}}{\sqrt{I_{D2}} - \sqrt{I_{D1}}} = \frac{4.5 \times \sqrt{28} - 6 \times \sqrt{3}}{\sqrt{28} - \sqrt{3}} = 3.77 \text{ V}$$

(5)

The Miller voltage is computed as shown in 公式 6.

$$V_{P} = V_{TH} + \sqrt{\frac{I_{1}}{K}} = 3.77 + \sqrt{\frac{\frac{0.07968}{I_{D1}}}{\left(V_{GS1} - V_{TH}\right)^{2}}} = 3.77 + \sqrt{\frac{\frac{0.0905}{3}}{\left(8 - 3.77\right)^{2}}} = 4 \text{ V}$$

(6)

With the gate threshold and Miller voltage computed, turnon timings  $t_1$ ,  $t_2$ , and  $t_3$  are shown in 公式 7, 公式 8, and 公式 9, respectively.

$$t_{1} = \left(R_{g} + R_{ext}\right) \times C_{iss} \times In \left(\frac{1}{1 - \left(\frac{V_{TH}}{V_{GS}}\right)}\right) = \left(4.6 + 4.7\right) \times 349 \text{ pF} \times In \left(\frac{1}{1 - \left(\frac{1}{1 - \left(\frac{3.77}{8.5}\right)}\right)}\right) = 1.9 \text{ ns}$$

(7)

$$t_{2} = \left(R_{g} + R_{ext}\right) \times C_{iss} \times In \left(\frac{1}{1 - \left(\frac{V_{P}}{V_{GS}}\right)}\right) = \left(4.6 + 4.7\right) \times 349 \text{ pF} \times In \left(\frac{1}{1 - \left(\frac{4}{8.5}\right)}\right) = 1.98 \text{ ns}$$

(8)

$$t_3 = \left(R_g + R_{ext}\right) \times C_{GD} \times \frac{V_{MIN}}{\left(V_{GS} - V_{GP}\right)} = \left(4.6 + 4.7\right) \times 12.6 \text{ pF} \times \frac{12}{\left(8.5 - 3.89\right)} = 305 \text{ ps}$$

(9)

With timings  $t_1$ ,  $t_2$ , and  $t_3$  computed, power loss during turnon time is calculated using  $\triangle \vec{\pi}$  10.

$$P_{ton} = \left(V_{IN} \times \frac{(n \times I_0)}{2} \times (t_2 - t_1) \times f_{SW}\right) + \left(n \times I_0 \times \frac{(V_{IN})}{2} \times t_3 \times f_{SW}\right) = 18.4 \ \mu W \tag{10}$$

Similarly, the turnoff timings  $t_4$ ,  $t_5$ ,  $t_6$ , and turnoff loss is computed as shown in  $\triangle \vec{x}$  11,  $\triangle \vec{x}$  12, and  $\triangle \vec{x}$  13.

$$t_{4} = \left(R_{g} + R_{ext}\right) \times C_{iss} \times In\left(\frac{V_{GS}}{V_{P}}\right) = \left(4.6 + 4.7\right) \times 349 \, pF \times In\left(\frac{12}{4}\right) = 3.65 \, ns \tag{11}$$

$$t_5 = \left(R_g + R_{ext}\right) \times C_{GD} \times \frac{V_{DS}}{V_P} = \left(4.6 + 4.7\right) \times 12.6 \text{ pF} \times \frac{12}{4} = 361 \text{ ps}$$

(12)

$$t_{6} = \left(R_{g} + R_{ext}\right) \times C_{iss} \times In\left(\frac{V_{p}}{V_{TH}}\right) = \left(4.6 + 4.7\right) \times 349 \text{ pF} \times In\left(\frac{4}{3.77}\right) = 1001 \text{ ps}$$

(13)

With timings t<sub>4</sub>, t<sub>5</sub>, and t<sub>6</sub> computed, power loss during turnoff time is calculated using 公式 14.

$$P_{toff} = \left(n \times I_0 \times \frac{(V_{IN})}{2} \times t_5 \times f_{SW}\right) + \left(V_{IN} \times \frac{(n \times I_0)}{2} \times t_6 \times f_{SW}\right) = 22.1 \,\mu\text{W}$$

(14)

The total power loss in MOSFET is calculated using 公式 15:

$$P_{T} = P_{cond} + P_{GATE} + P_{ton} + P_{toff} = 1.7 \text{ mW}$$

$$(15)$$

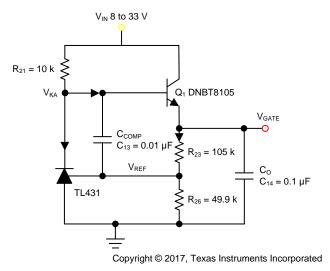

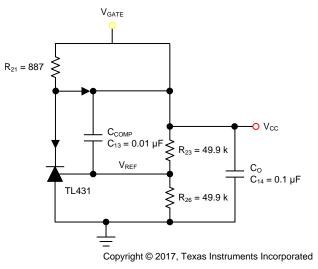

### 2.3.1.4 LDO Using TL431

The regulated gate drive supply and peripheral supply are generated using a discrete LDO designed with the TL431. This peripheral supply can be used to power up the MCU, op amp, and other peripherals in a burner control system. In this reference design, the LDO powers up the sine wave oscillator. The components in the gate drive supply as shown in 818 is computed as per Section 2.2.2.1 of the TIDA-01065 design guide with a feedback current of 50  $\mu$ A. The capacitor  $C_{13}$  is introduced for stability by adding zero in the feedback loop. This capacitor improves the phase margin and reduces oscillation in output.

图 18. Gate Voltage Supply

The peripheral LDO is designed with an output current of 1 mA and 5 V. The values of discrete components as shown in  $\boxtimes$  19 are computed as per Section 2.2.2.1 of the TIDA-01065 design guide with a feedback current of 50  $\mu$ A. The capacitor  $C_{13}$  is introduced for stability by adding zero in the feedback loop. This capacitor improves the phase margin and reduces oscillation in output.

图 19. Peripheral Supply

### 2.3.1.5 Sine Wave Oscillator

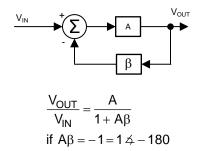

In this reference design, a sine wave oscillator is used to generate a 50-Hz line signal by using a low THD+noise op amp. With this approach, it is possible to produce very low distorted output. As show in 20, the oscillator must satisfy the criteria for a closed loop positive feedback for the circuit to oscillate. Due to positive feedback, the denominator value becomes zero, resulting in instability known as Barkhausen Criterion. In unstable mode, the output of circuit tends to infinity due to the limitation of the power rail in circuit output will saturate to rail supply. For active devices, the gain of the circuit changes as output approaches the supply rail. This results in a change of value A and forces  $4\beta$  away from the singularity. Due to this change, trajectory towards power rail slows and eventually halts.

图 20. Oscillator Control Loop

At this point, any one of these three possible conditions can occur:

- Nonlinearity in saturation or a cutoff region may result to become stable and latch at a particular output

- Initial change may cause the active device to be saturated or cut off for a long period before becoming linear and then moving to an opposite rail

- The circuit stays linear and reverses polarity to an opposite rail

The second condition results in a distorted output and is usually preferred for generating quasi square wave signals, while the third conditions produces sine wave output. The gain and phase of the circuit play a critical role for designing a sine way oscillator. For an op-amp based circuit, the phase margin of the op amp must be negligible so that the closed loop positive feedback archives ∡-180 phase shift at oscillating frequency. Considering these conditions, the closed loop gain, phase shift, THD distortion, and slew rate are some key parameters for selecting an op amp to design sine wave oscillators.

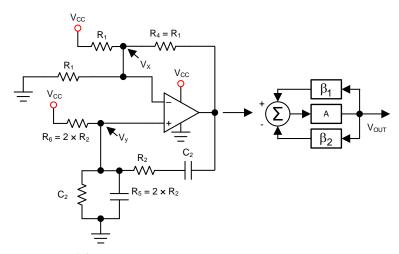

This reference design uses a single-supply Wein bridge oscillator. The classic Wein bridge oscillator has both positive and negative feedback. This helps in getting a very low distorted output. For analysis, consider the circuit as shown in § 21. The circuit operating can be modeled as a non-inverting amplifier.

18

图 21. Sine Wave Oscillator for Op Amp

Voltage at the positive terminal of the op amp is given using 公式 16.

$$V_{y} = V_{O} \times \left( \frac{sR_{2}C_{2}}{1 + 3sR_{2}C_{2} - (sR_{2}C_{2})^{2}} \right)$$

(16)

A simple form of 公式 16 in a frequency parameter is given using 公式 17.

$$\beta = \frac{V_y}{V_0} = \begin{pmatrix} & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$$

From a classic non-inverting amplifier, the closed loop gain equation ignoring the dominant pole effect at a low frequency is given using 公式 18.

$$V_{O} = V_{y} \times \left(1 + \frac{R_{4}}{R_{1}}\right) \tag{18}$$

As a result, the forward gain is found using 公式 19.

$$A = \frac{V_O}{V_y} = \left(1 + \frac{R_4}{R_1}\right) \tag{19}$$

The total loop gain is given using 公式 20.

$$T(jf) = A\beta = \frac{\left(1 + \frac{R_4}{R_1}\right)}{\left(3 + j\left(\frac{f}{f_{R_2C_2}} - \frac{f_{R_2C_2}}{f}\right)\right)}$$

(20)

These equations imply system response of bandpass filter, at higher and lower frequency it approaches to zero and at peak frequency of  $f = f_{R2C2}$ , the total loop gain reduces to:

$$t_{(jf_{R_2C_2})} = \frac{\left(1 + \frac{R_4}{R_1}\right)}{3} \tag{21}$$

The magnitude of the total loop gain has three possibilities:

- $T(jf_{R_2}c_2)<1$ : The pole pair lies in the left half of the complex plane, resulting in an exponentially decaying signal.

- T(jf<sub>R2</sub>C<sub>2</sub>)>1: This condition results in unstable operation, resulting in oscillation of growing amplitude. The pole pair lies on the right half of a complex plane. The oscillation builds up until the op amp saturates to the power rail. This condition results in a distorted output.

- T(jf<sub>R2</sub>C<sub>2</sub>)=1: This condition results in neutral stability. The pole pair lies exactly on an imaginary axis of the complex plane. It satisfies the Barkhausen criterion of the loop gain of unity and a phase shift of 360°. The output is sinusoidal with very low distortion. For this condition, the R<sub>4</sub>/R<sub>1</sub> ratio needs to satisfy a magnitude of 2.

Due to the drift of active and passive devices, the total loop gain does not maintain a magnitude of value 1, so modify the circuit as shown in  $\boxtimes$  22 to achieve automatic gain control (AGC). At initial startup condition, diodes D<sub>1</sub>, D<sub>2</sub>, and R<sub>3</sub> result into condition T(jf<sub>R2C2</sub>) > 1, resulting into oscillations quickly building up. After the oscillation has built up, the gain stabilizes to match the Barkhausen criteria due to effective resistors R3 and R4, which are in parallel to achieve a ratio close to a magnitude of 2.

图 22. Practical Op Amp Oscillator

Select an op amp that has very low distortion for oscillating frequency, low noise, and enough of a slew rate to achieve sustain oscillation. The closed loop bandwidth needs to be greater than 270  $f_{OSC}$ . Therefore, for a 50-Hz  $f_{OSC}$  signal, the sine wave oscillator needs a closed-loop bandwidth greater than 13.5 kHz and a slew rate of >  $2\pi f_{OSC}V_O$ . Selecting TLV171 from the device datasheet gets a unity gain bandwidth of 3 MHz and a typical open loop gain of 130 dB.

#### 表 5. TLV171 Electrical Characteristic

|                      | PARAMETER                            | TEST CONDITIONS                                                | MIN        | TYP      | MAX      | UNIT                        |

|----------------------|--------------------------------------|----------------------------------------------------------------|------------|----------|----------|-----------------------------|

| OFFSET '             | VOLTAGE                              |                                                                |            |          |          |                             |

| V <sub>OS</sub>      | Input offset voltage                 | T <sub>A</sub> = 25°C                                          | _          | 0.75     | ±2.7     | mV                          |

| VOS                  | input onset voltage                  | $T_A = -40$ °C to +125°C                                       | _          | _        | ±3.0     | IIIV                        |

| dV <sub>OS</sub> /dT | Input offset voltage drift           | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                 | _          | 1        | _        | μV/°C                       |

| PSRR                 | Input offset voltage vs power supply | V <sub>S</sub> = 4 V to 36 V, T <sub>A</sub> = -40°C to +125°C | 90         | 105      | _        | dB                          |

| INPUT BI             | AS CURRENT                           |                                                                |            |          | <u>.</u> |                             |

| I <sub>B</sub>       | Input bias current                   | _                                                              | _          | ±10      | _        | pА                          |

| Ios                  | Input offset current                 | _                                                              | _          | ±4       | _        | pA                          |

| NOISE                |                                      |                                                                |            |          | <u>.</u> |                             |

|                      | Input voltage noise                  | f = 0.1 Hz to 10 Hz                                            | _          | 3        | _        | $\mu V_{PP}$                |

| •                    | Input voltage noise density          | f = 100 Hz                                                     | _          | 27       | _        | nV/√ <del>Hz</del>          |

| e <sub>n</sub>       | input voltage noise density          | f = 1 kHz                                                      | _          | 16       | _        | IIV/ VIIZ                   |

| INPUT VO             | DLTAGE                               |                                                                |            |          |          |                             |

| V <sub>CM</sub>      | Common-mode voltage range            | _                                                              | (V-) - 0.1 | _        | (V+) - 2 | V                           |

| CMRR                 | Common-mode rejection ratio          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$          | 94         | 105      | _        | dB                          |

| INPUT IM             | PEDANCE                              |                                                                | +          |          | Ų.       |                             |

|                      | Differential                         | _                                                              | _          | 100    3 | _        | $MΩ \parallel pF$           |

|                      | Common-mode                          | _                                                              | _          | 6    3   | _        | 10 <sup>12</sup> Ω   <br>pF |

## 表 5. TLV171 Electrical Characteristic (continued)

| PARAMETER       |                                   | TEST CONDITIONS                                                                                                                         | MIN | TYP     | MAX | UNIT |

|-----------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| OPEN-L          | OOP GAIN                          |                                                                                                                                         |     |         |     |      |

| A <sub>OL</sub> | Open-loop voltage gain            | $V_S = 36 \text{ V},$<br>$(V-) + 0.35 \text{ V} < V_O < (V+) - 0.35 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 94  | 130     | _   | dB   |

| FREQUE          | ENCY RESPONSE                     |                                                                                                                                         |     |         |     |      |

| GBP             | Gain bandwidth product            | _                                                                                                                                       | _   | 3.0     | _   | MHz  |

| SR              | Slew rate                         | G = +1                                                                                                                                  | _   | 1.5     | _   | V/µs |

|                 |                                   | To 0.1%, V <sub>S</sub> = ±18 V, G = +1, 10-V step                                                                                      | _   | 6       | _   |      |

| t <sub>S</sub>  | Settling time                     | To 0.01% (12 bits), $V_S = \pm 18 \text{ V}$ , $G = +1$ , 10-V step                                                                     | _   | 10      | _   | μs   |

|                 | Overload recovery time            | V <sub>IN</sub> × gain > V <sub>S</sub>                                                                                                 | _   | 2       | _   | μs   |

| THD+N           | Total harmonic distortion + noise | G = +1, f = 1 kHz, V <sub>O</sub> = 3 V <sub>RMS</sub>                                                                                  | _   | 0.0002% | _   | _    |

As a result, the dominant pole frequency of the TLV171 is given using 公式 22.

$$f_{dom} = \frac{f_{unity}}{\frac{130}{20}} = 0.948 \text{ Hz}$$

(22)

The closed loop AC gain for a non-inverting topology with a feedback factor of 1/3 at a frequency of 15 kHz is given using  $2 \stackrel{<}{\lesssim} 23$ .

$$A_{cl} = \frac{\frac{A_{DC\_OPEN}}{1 + \beta \times A_{DC\_OPEN}}}{\sqrt{1 + \frac{f^2}{f_{dom}^2} \frac{1}{\left(1 + \beta A_{DC\_OPEN}\right)^2}}} = \frac{\frac{3162277}{1 + 0.33 \times 3162277}}{\sqrt{1 + \left(\frac{15000^2}{0.948^2}\right) \times \left(\frac{1}{\left(1 + 0.33 \times 3162277\right)^2}\right)}} = 3.029$$

(23)

So the TLV171 meets approximately a closed loop gain of 3. Calculate the phase margin error using 公式 24 to get a phase error of 0.003°.

$$\phi = 90^{\circ} - \left( \tan^{-1} \frac{f}{f_{dom}} \right) = 0.003^{\circ}$$

(24)

From the slew rate requirement, considering an output voltage of 4 V and a 50-Hz f<sub>OSC</sub> slew rate needs to be greater than 1.25 mV/µs (ignoring asymmetric slew rate error in non-inverting mode due to a common-mode parasitic).

$$SR > 2\pi \times f_{OSC} \times V_{O} \times 10^{-6} = 2\pi \times f_{OSC} \times V_{O} \times 10^{-6} > 1.25 \frac{mV}{\mu s}$$

(25)

By cross verifying with the TLV171 FPB, check that the slew rate satisfies the closed loop bandwidth requirement by using  $\triangle \exists$  26.

$$FPB = \frac{SR \text{ in } \frac{V}{\mu s}}{2\pi \times V_O} = \frac{1.5 \times 10^6}{8\pi} = 59.7 \text{ kHz}$$

(26)

22

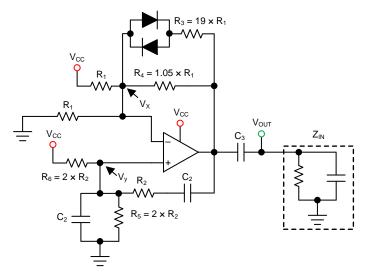

## 2.3.1.6 High Gain Amplifier

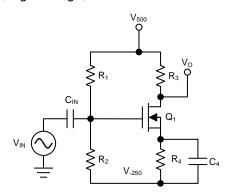

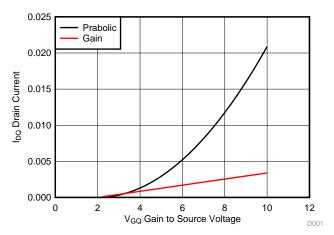

To achieve a 120-V sine wave output, there needs to be an amplifier; this amplifier can be a topology like Class A, Class AB, and so on. To achieve the cost target, a Class A amplifier has been implemented in this reference design. Class AB can be implemented to achieve high efficiency and low distortion with a filter circuit. A Class A amplifier as shown in 323 operates in the linear operating region, due to which output distortion are low. In a Class A amplifier, additional quiescent current is required to bias the transistor in the operating region. Calculate the bias point to achieve linear output. This reference design uses the BSS127-S N-channel, high-voltage, low-cost MOSFET to design this Class A amplifier.

图 23. Class A Amplifier

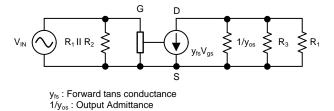

Resistors  $R_1$  and  $R_2$  provide bias voltage to Q1. To calculate  $R_1$  and  $R_2$ , first calculate the Q point of Q1 for the required gain. The AC equivalent of a circuit is as shown in  $\boxed{8}$  24.

图 24. AC Equivalent Circuit

$A_v: y_{fs} \times (R_1 II R_3 II 1/y_{os})$

The drain current of the MOSFET is parabolic in nature, so the drain current is given using 公式 27.

$$I_{ds} = K \times (V_{GSON} - V_{GSOFF})^{2}$$

(27)

Solving  $\triangle$ 式 27 for  $V_{GSOFF}$  = 10 V,  $V_{GSOFF}$  = 3 V, and  $I_{ds}$  = 16 mA from the datasheet, compute K as shown in  $\triangle$ 式 28.

### Electrical Characteristics (@TA = +25°C, unless otherwise specified.)

| Characteristic                                         | Symbol              | Min | Тур  | Max  | Unit | Test Condition                                    |

|--------------------------------------------------------|---------------------|-----|------|------|------|---------------------------------------------------|

| OFF CHARACTERISTICS (Note 8)                           |                     |     |      |      |      |                                                   |

| Drain-Source Breakdown Voltage                         | BV <sub>DSS</sub>   | 600 | _    | _    | V    | $V_{GS} = 0V, I_D = 250\mu A$                     |

| Zero Gate Voltage Drain Current T <sub>J</sub> = +25°C | IDSS                | _   | _    | 0.1  | μA   | V <sub>DS</sub> = 600V, V <sub>GS</sub> = 0V      |

| Gate-Body Leakage                                      | I <sub>GSS</sub>    | -   | _    | ±100 | nA   | $V_{GS} = \pm 20V, V_{DS} = 0V$                   |

| ON CHARACTERISTICS (Note 8)                            |                     |     |      |      |      |                                                   |

| Gate Threshold Voltage                                 | V <sub>GS(TH)</sub> | 3   | _    | 4.5  | V    | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$              |

| Static Drain-Source On-Resistance                      | D                   | I   | 80   | 160  | Ω    | V <sub>GS</sub> = 10V, I <sub>D</sub> = 16mA      |

| Static Drain-Source Off-Resistance                     | R <sub>DS(ON)</sub> | 1   | 95   | 190  | 12   | $V_{GS} = 5.0V$ , $I_D = 16mA$                    |

| Forward Transfer Admittance                            | Y <sub>fs</sub>     | -   | 76   | _    | mS   | V <sub>DS</sub> = 10V, I <sub>D</sub> = 16mA      |

| Diode Forward Voltage                                  | V <sub>SD</sub>     | _   | _    | 1.5  | V    | $V_{GS} = 0V, I_S = 16mA$                         |

| DYNAMIC CHARACTERISTICS (Note 9)                       |                     |     |      |      |      |                                                   |

| Input Capacitance                                      | Ciss                | _   | 21.8 | _    |      |                                                   |

| Output Capacitance                                     | Coss                | 1   | 2.2  | _    | pF   | $V_{DS} = 25V$ , $V_{GS} = 0V$ , $f = 1.0MHz$     |

| Reverse Transfer Capacitance                           | Crss                | ı   | 0.3  | _    |      |                                                   |

| Total Gate Charge                                      | $Q_{g}$             | _   | 1.08 | _    |      | V - 40V V - 200V                                  |

| Gate-Source Charge                                     | Qgs                 | _   | 0.08 | _    | nC   | $V_{GS} = 10V, V_{DD} = 300V,$<br>$I_{D} = 0.01A$ |

| Gate-Drain Charge                                      | $Q_{qd}$            | _   | 0.50 | _    | 1    | ID = 0.0 IA                                       |

| Turn-On Delay Time                                     | t <sub>D(ON)</sub>  | _   | 5.0  | _    | ns   | V - 000V V - 40V                                  |

| Turn-On Rise Time                                      | t <sub>R</sub>      | _   | 7.2  | _    | ns   | $V_{DD} = 300V, V_{GS} = 10V,$                    |

| Turn-Off Delay Time                                    | t <sub>D(OFF)</sub> | _   | 28.7 | _    | ns   | $R_{GEN} = 6\Omega$ ,<br>$I_D = 10mA$             |

| Turn-Off Fall Time                                     | t <sub>F</sub>      | ı   | 168  | _    | ns   | ID - TOTIA                                        |

| Reverse Recovery Time                                  | t <sub>RR</sub>     | 1   | 131  | _    | ns   | V <sub>R</sub> =300V, I <sub>F</sub> =0.016A,     |

| Reverse Recovery Charge                                | Q <sub>RR</sub>     | _   | 32   | _    | nC   | di/dt = 100A/μs                                   |

Notes:

- 5. Device mounted on FR-4 PCB with minimum recommended pad layout, single sided.

- Device mounted on 1" x 1" FR-4 PCB with high coverage 2 oz. Copper, single sided.

Repetitive rating, pulse width limited by junction temperature, 10µs pulse, duty cycle = 1%.

- 8. Short duration pulse test used to minimize self-heating effect.

- Guaranteed by design. Not subject to production testing.

#### 图 25. MOSFET Electrical Characteristics

$$k = \frac{dI_{dsq}}{dV_{GSq}} = 2 \times K \times (V_{GSq} - V_{GSOFF})$$

(28)

The transconductance of the MOSFET is found by taking the derivative of the transfer function for the drain current at a bias point of the amplifier.

$$y_{fq} = \frac{dI_{dsq}}{d_{V_{GSq}}} = 2 \times K \times (V_{GSq} - V_{GSOFF})$$

(29)

Assuming the high load resistance and output admittance is sufficiently high, the impedance seen by the MOSFET is almost equal to R3. For a good biasing point, it is good to bias the output at half of the supply rails. As a result, the drain resistance is given using 公式 30.

$$R_3 = 0.5 \times \frac{\left(V_{DD} + V_{SS}\right)}{I_{DQ}} \tag{30}$$

By substituting  $R_3$  and  $y_{fq}$  for the total gain in  $\triangle \sharp 31$ :

$$A_{vq} = y_{fq} \times R_3 = 2 \times K \times \left(V_{GSq} - V_{GSOFF}\right) \times 0.5 \frac{\left(V_{DD} - V_{SS}\right)}{I_{DQ}}$$

(31)

Rearranging the terms for  $I_{DQ}$  leads to  $\triangle \stackrel{<}{\precsim}$  32:

$$I_{DQ} = \frac{2 \times K \times \left(V_{GSq} - V_{GSOFF}\right) \times 0.5 \times \left(V_{DD} - V_{SS}\right)}{A_{vq}}$$

(32)

Solving  $\triangle \sharp$  27 and  $\triangle \sharp$  32 graphically with V<sub>dd</sub> of 500 V, V<sub>GSOFF</sub> = 3 V and a gain of 330, bias points V<sub>GSQ</sub> and I<sub>GSQ</sub> can be computed using interpret of two curves (see  $\boxtimes$  26).

图 26. Bias Point Calculations

$\boxtimes$  26 shows that the curve intercepts the x-axis at 3.3 V and the y-axis at 551  $\mu$ A. So the bias point for BSS127-S is  $V_{GSQ} = 3.3$  V and  $I_{DQ} = 551$   $\mu$ A.

Solving the equation with  $I_{DQ}$  = 551  $\mu$ A results in  $R_3$  = 442 k. Selecting a closed standard value of 442 kV at the source can be set close to 0.09 times the supply rail. Computing for a  $V_{dd}$  of 500 V and  $I_{DQ}$  = 551  $\mu$ A results in  $R_4$  = 82 k. Selecting the next standard resistor with a 5% tolerance we select 88.7k. With 88.7k and  $I_{DQ}$  = 551  $\mu$ A, the source voltage is 48.8 V. Adding the gate-to-source bias voltage, the gate voltage needs to be 52.1 V. Using voltage divider logic, R1 and R2 can be easily computed for a low-bias current. Assuming an  $R_2$  of 2.2 M $\Omega$  and a supply rail  $V_{dd}$  of 500 V, the required resistance  $R_1$  is 18 M $\Omega$ . The nearest standard value to select is 18 M $\Omega$ . Capacitance  $C_4$  is a bypass capacitor for a higher AC gain value. To calculate C4, assume impedance by capacitance for a 50-Hz frequency as 0.1 times of R4.  $X_C = 0.1 \times R_4 = 8.8$  k

By knowing the impedance of a capacitor at a specific frequency, it is easy to calculate capacitance using 公式 34.

$$C_4 = \frac{1}{2\pi f X_C} = 361 \,\text{nF}$$

(34)

The next standard value selected is a 470-nF capacitor. Capacitance  $C_{in}$  is a high-pass-filter capacitor that blocks DC level from the oscillator output. The parallel resistance value of resistors R1 and R2 with  $C_{in}$  together form the high pass filter. By selecting a cutoff frequency of 5 Hz, compute  $C_{in}$  as per  $\triangle \pm 35$ .

$$C_{in} = \frac{1}{2\pi f_{C} \times 0.1 \times (R_{1} || R_{2})} = 162 \text{ nF}$$

(35)

The next standard value of 220 nF is selected for the input filter capacitor.

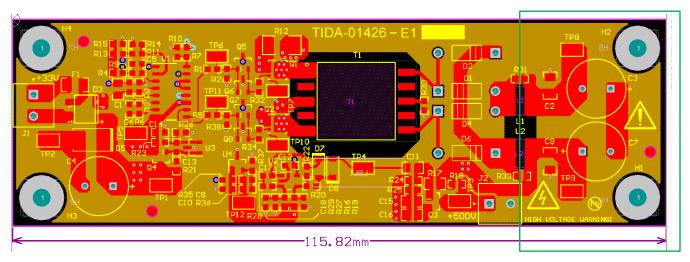

## 3 Hardware, Testing Requirements, and Test Results

## 3.1 Hardware

Before powering up the TIDA-01426 board, verify for any components not populated as per the schematic. Check for power nodes and shock hazard symbols to avoid electric shocks as shown in 🖺 27.

图 27. High-Voltage Section

## 3.1.1 Connectors

The interface board has two connectors as described in  $\frac{1}{2}$  6.

### 表 6. Input Output Connectors

| CONNECTOR | DESCRIPTION    | VOLTAGE                      |

|-----------|----------------|------------------------------|

| J1        | Input voltage  | 12 to 36 V                   |

| J2        | Output voltage | 120 V <sub>RMS</sub> , 60 Hz |

### 3.1.2 Test Points

The required test points have been populated on the interface board to measure signals. See 表 7 for more details.

表 7. Test Points

| TEST POINT NO | DESCRIPTION              | VOLTAGE VALUE                |

|---------------|--------------------------|------------------------------|

| TP1           | Supply voltage           | 12 to 36 V                   |

| TP2, TP9      | GND                      | 0 V                          |

| TP5           | Gate supply              | 8 V                          |

| TP12          | Op amp supply            | 5 V                          |

| TP4           | Sine wave oscillator     | 1.5 V <sub>RMS</sub> , 60 Hz |

| TP3           | Class A amplifier output | 120 V <sub>RMS</sub> , 60 Hz |

| TP6           | Emitter 1 output         | 7-V, 100-kHz PWM             |

| TP11          | Emitter 2 output         | 7-V, 100-kHz PWM             |

| TP7           | Totem Pole 1 output      | 8-V ,100-kHz PWM             |

| TP10          | Totem Pole 2 output      | 8-V, 100-kHz PWM             |

| TP8           | Positive high voltage    | 500 V                        |

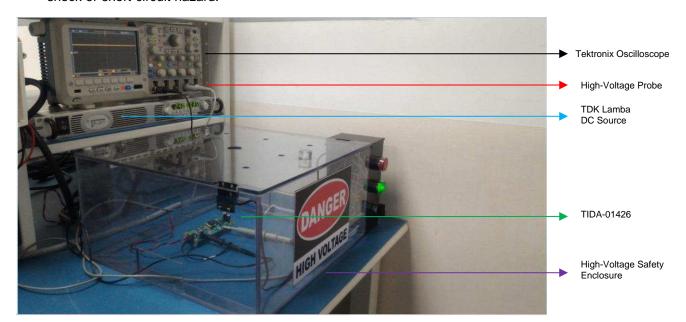

The test setup is as shown in 🛭 28. Ensure the board is placed inside a safety enclosure to prevent any shock or short-circuit hazard.

图 28. Test Setup

## 3.2 Testing and Results

## 3.2.1 Gate Supply

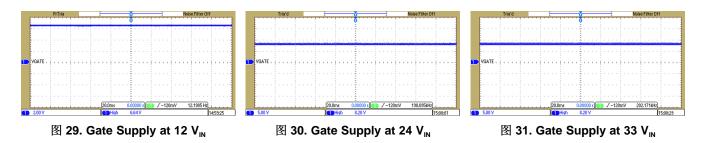

The following figures show the gate output voltage changes as the line voltage changes from the minimum supply to the maximum supply.

## 3.2.2 LDO Supply

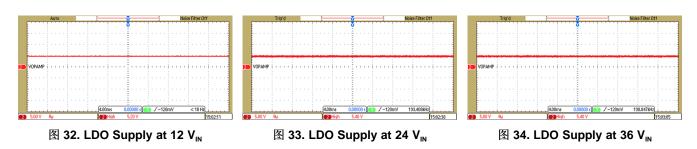

The following figures show the LDO output voltage as the line voltage changes from the minimum supply to the maximum supply.

## 3.2.3 Push-Pull Output

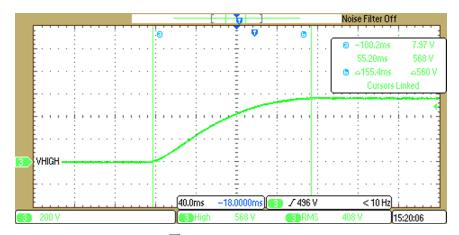

The start-up time for 500 V is tested at the lowest input supply. Yar gets a start-up time of 100 ms to achieve 55 ms as shown in

■ 35.

图 35. Start-up Time

## 3.2.4 Sensor Output

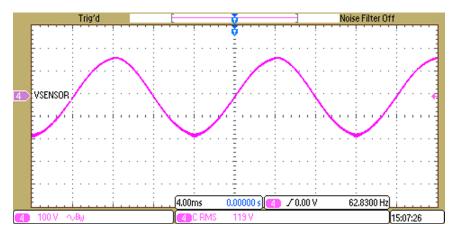

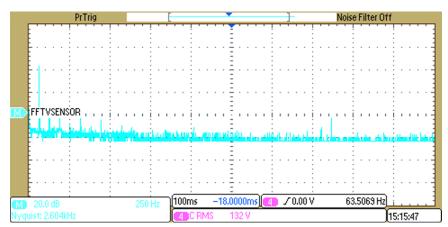

Sensor output is measured at a 24-V input, and the FFT plot is taken to verify harmonic content (see \bigseparty 36).

图 36. Sensor Output

As seen from \$\textit{\textit{8}}\$ 37, the peak is at 63 Hz with a 42-dB magnitude and harmonics with magnitudes of 7 dB, -18 dB, -12 dB, and -5 dB. The THD computed for an observed output is 1.8%.

图 37. FFT Plot Sensor Output

Design Files www.ti.com.cn

## 4 Design Files

### 4.1 Schematics

To download the schematics, see the design files at TIDA-01426.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01426.

## 4.3 PCB Layout Recommendations

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01426.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01426.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01426.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01426.

#### 5 Software Files

To download the software files, see the design files at TIDA-01426.

## 6 Related Documentation

1. Texas Instruments, *Designing Switching Voltage Regulators With the TL494*, TL494 Application Report (SLVA001)

### 6.1 商标

NexFET is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 7 About the Authors

**SRINIVASAN IYER** is a systems engineer at Texas Instruments India, where he is responsible for developing reference design solutions for the industrial segment. Srinivasan has six years of experience in power supply and analog circuit designs for field transmitter and signal chain. Srinivasan received his BE from the University of Pune, India.

**MIROSLAV OLJACA** is the end equipment manager for Building Automation applications and system solutions. Miro has nearly 30 years of engineering experience and has been granted at least a dozen patents, several related to high-performance signal processing, and he has written many articles on the subject. Miro received his BSEE and MSEE from the University of Belgrade, Serbia.

## 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司