# TI Designs: TIDA-01371

用于超声波系统的可编程 **±100V**、高电流、浮点线性稳压器参考设计

# TEXAS INSTRUMENTS

#### 说明

超声波发送器需要稳定的可编程直流电源,以便在传输期间将高电流驱动到压电传感器中。该参考设计展示了一款能够提供 ±2.5 至 ±100V 输出电压的正负线性稳压器。使用外部控制电压实现可编程性(应来自 DAC)。低噪声性能可帮助使用现成的低噪声正负 LDO 稳压器以及用于浮动稳压器接地的电路替代无源和有源噪声滤波器。此外,它使用外部功率 MOSFET 调节稳压器的电流容量,以支持特殊的成像模式(如横波或弹性成像模式)。为了向传感器提供极高的电流,大输入电容器能够以 1ms 的持续时间提供高能量,从而使从该电源消耗的平均电流保持在极低的值。该设计可与 TIDA-01352 设计(高电压直流/直流升压级)结合使用。

#### 资源

| TIDA-01371  | 设计文件夹 |

|-------------|-------|

| TIDA-01352  | 设计文件夹 |

| TPS7A47     | 产品文件夹 |

| TPS7A33     | 产品文件夹 |

| TLV171      | 产品文件夹 |

| TLV2171     | 产品文件夹 |

| CSD19533KCS | 产品文件夹 |

#### 特性

- 浮动和跟踪稳压器,使用具有优于±1.5%负载调节 性能的现成 LDO 稳压器替换无源和有源噪声滤波器

- 创新的电流共享方案使用 TI 的一流低 R<sub>DS(ON)</sub> CSD 系列功率 MOSFET 和低阻抗驱动器电路来改善瞬态响应

- 使用来自 DAC 的控制信号实现 ±2.5 至 ±100V 的可编程输出电压

- 可针对 1ms 脉冲调节输入电流(经测试高达 ± 20A),以支持特殊成像模式

- 独立的正负电压电源能够灵活地为超声波发射电路 供电

#### 应用

- 医用超声波扫描仪

- 声纳成像设备

- 无损评价设备

咨询我们的 E2E 专家

M

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

## 1 System Description

Medical ultrasound imaging is a widely-used diagnostic technique that enables visualization of internal organs, their size, structure, and blood flow estimation. An ultrasound system uses a focal imaging technique that involves time shifting, scaling, and intelligently summing the echo energy using an array of transducers to achieve high imaging performance. When initiating an imaging, a pulse is generated and transmitted from multiple transducer elements. The pulse, now in the form of mechanical energy, propagates through the body as sound waves, typically in the frequency range of 1 to 15 MHz.

## 1.1 Key System Specifications

${\it \pm}$  1 shows the key specifications for this TI Design.

#### 表 1. Key System Specifications

|                    | PARAMETER                         | SPECIFICATIONS                                                     | DETAILS |

|--------------------|-----------------------------------|--------------------------------------------------------------------|---------|

| Positive regulator | Off-the-shelf regulator TPS7A4701 | 36 V, 1 A                                                          | 节 2.5.1 |

|                    | Voltage scaling                   | Test up to V <sub>IN</sub> = 120 V                                 | 节 2.5.1 |

|                    | Current scaling                   | Test up to I <sub>OUT</sub> = 20 A pulsed for 1 ms every 1 second  | 节 2.5.1 |

| Negative regulator | Off-the-shelf regulator TPS7A3301 | −36 V, −1 A                                                        | 节 2.5.2 |

|                    | Voltage scaling                   | Test up to $V_{IN} = -120 \text{ V}$                               | 节 2.5.2 |

|                    | Current scaling                   | Test up to I <sub>OUT</sub> = -20 A pulsed for 1 ms every 1 second | 节 2.5.2 |

#### 2 System Overview

A medical ultrasound application requires high-voltage pulses to be transmitted inside a human body to get information about blood, organs, tissues, and so on. These pulses are bipolar in nature and are transmitted by pulsers.

There are two modes in general:

- 1. Pulse (Brightness or B) mode where high-voltage pulses (-100 and 100 V) are transmitted for a particular short time only.

- 2. Continuous (CW) mode where low-voltage (±2.5 to ±10 V) pulses are continuously transmitted.

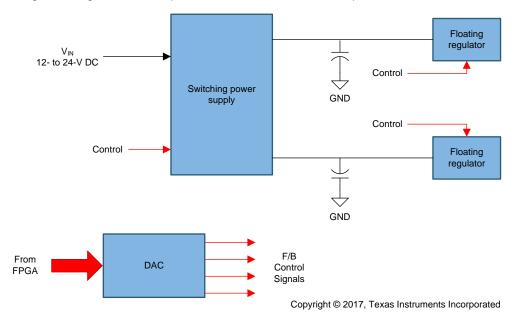

Note that the same power supply is used for both the modes meaning the output of power supply is ranging from ±2.5 to ±100 V. Such a powering scheme is typically implemented using a switched mode power supply (SMPS) followed by regulators as shown in 🗵 1. The voltage noise on the output signal is very important when CW mode is used because the signal amplitudes are low. Within Pulse mode, there is a special mode called Elastography (or Shear wave) mode. The current requirements are huge (sometimes more than 100 A) for a short period of time (may be tens of microseconds). Delivering such a high current at high voltages without dropping the output voltage is a challenge. To cover for the droop in output voltage, the high value of capacitors is also used at the output of SMPS.

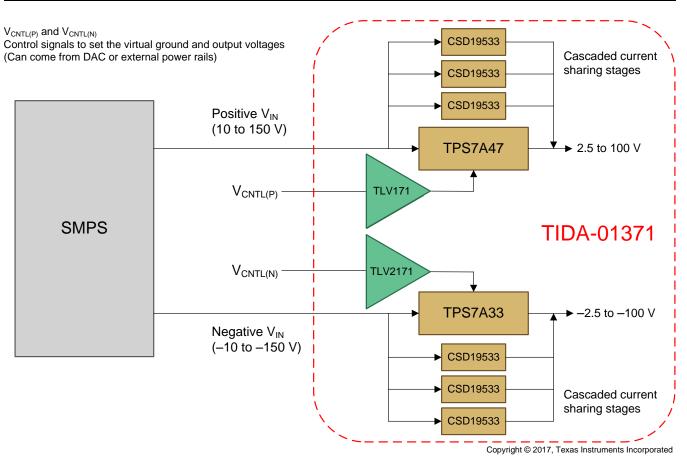

图 1. Typical Power Supply Scheme in Medical Ultrasound Application

#### 2.1 Example of Power Calculations—Standard Imaging Mode

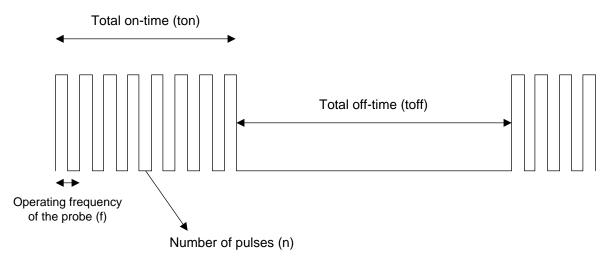

The following is an example of pulse mode for medical imaging. The standard mode has a driving waveform as shown in  $\boxtimes$  2.

Assume the following nomenclatures:

- ton = total on-time

- toff = total off-time

- f = operating frequency of the probe

- n = number of pulses

- c = capacitance of the probe at operating frequency f

• N = number of transducers

图 2. Standard Driving Waveform for Ultrasound Transducers

For a 128-channel transducer ultrasound system, N = 128.

For the next example, consider a probe with the following specifications:

- C = 470 pF

- f = 7.5 MHz

- Total number of pulses n = 10

- toff = 300 μs

- ton = 1.3 μs (calculated using n = 10 and f = 7.5 MHz)

- Voltage for transition is from –100 to 0 V or 0 to 100 V

Peak power consumption =

$$4 \times 128 \times 470 p \times 100^2 \times 7.5 M = 18 kW$$

(1)

Peak output current =

$$\frac{18 \text{ kW}}{100}$$

= 180 A (2)

Average power consumption =

$$\frac{18 \text{ kW}}{300} \times 1.3 = 78 \text{ W}$$

(3)

For a 20-V dip on the output capacitor of SMPS (that is, input capacitor of floating regulators):

$$C_{OUT} > \frac{I_{OUT} \times ton}{20} > \frac{180 \times 1.3 \ \mu}{20} > 11.7 \ \mu F$$

(4)

This means that with an output capacitor of SMPS =  $470 \, \mu F$ , the dip on the output voltage (of the SMPS) is 0.49 V. In such a case, there is no need to use the floating regulator. The output capacitor of the SMPS is enough to provide the required ability to drive the transducers.

However, there are some special imaging modes like Elastography where the requirements are different.

## 2.2 Example of Power Calculations—Special Imaging Mode (Elastography)

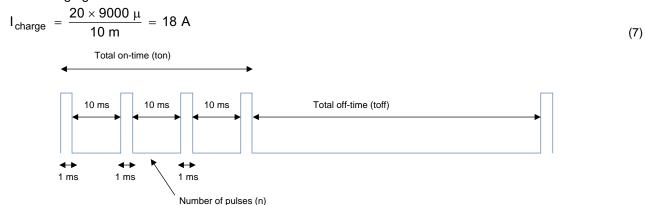

The special imaging mode Elastography has a driving waveform as shown in 图 3. Considering the same nomenclature as explained in 2.1 节:

- n = 5 pulses

- ton = 55 ms

- toff = 2 seconds

$$P_{AVG} = P_C \times \frac{1}{11} \times \frac{55}{2055} = 43.7 \text{ W}$$

(5)

公式 6 shows that average power needed for Elastography is less than the standard imaging mode.

Assuming the same voltage dip of 20 V:

$$C_{OUT} > \frac{I_{OUT} \times ton}{V_{dip}} > \frac{180 \times 1 \, m}{20} > 9000 \, \mu F$$

(6)

However, this needs to be replenished in time periods of 10 ms between the two 1-ms pulses as shown in

3.

If the SMPS is a 80-W rated power supply, the system would be current limited to 80/100 = 0.8 A only. The charging current needed in such case is:

图 3. Elastography—Driving Waveform for Ultrasound Transducers

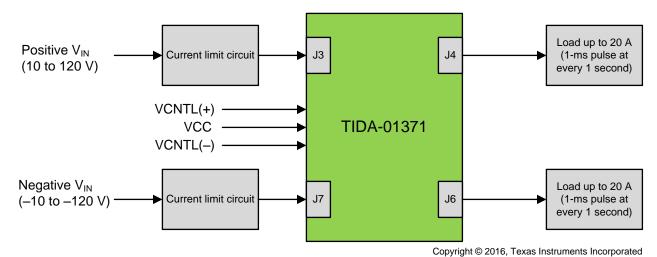

## 2.3 Block Diagram

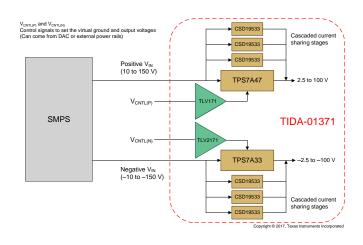

The positive floating regulator uses an off-the-shelf linear regulator TPS7A4701 from Texas Instruments. It is a 36-V ultra-low noise  $(4-\mu V_{RMS})$  low-dropout linear regulator capable of sourcing a 1-A load. The ground of this regulator is floated using a DC amplifier made using the TLV171. The voltage scaling is achieved using a BJT at the input and current scaling is achieved using external N-channel MOSFETs CSD19533 from Texas Instruments. The design has three stages connected in parallel for the current scaling feature. More stages can be used for higher current requirements.

The negative floating regulator uses an off-the-shelf linear regulator TPS7A3301 from Texas Instruments. It is a -36-V ultra-low noise ( $16\text{-}\mu\text{V}_{\text{RMS}}$ ) low-dropout linear regulator capable of sinking a 1-A load. The ground of this regulator is floated using a DC amplifier made using the TLV2171. The voltage scaling is achieved using a BJT at the input and current scaling is achieved using external N-channel MOSFETs CSD19533 from Texas Instruments. The design has three stages connected in parallel for the current scaling feature. More stages can be used for higher current requirements.

The DC amplifiers for setting the floating (or virtual) grounds are controlled using control voltages  $V_{\text{CNTL(P)}}$  and  $V_{\text{CNTL(N)}}$ . These signals can come from DACs or external power supplies. Because the transient response is important for medical ultrasound applications, low-impedance drive circuits using diodes and NPN-PNP transistors are used for driving the current scaling MOSFETs.

图 4. System Block Diagram

#### 2.4 Highlighted Products

This design has two sections: one is a positive regulator and other is a negative regulator. Both the sections use off-the-shelf low dropout (LDO) regulators from Texas Instruments along with N-channel MOSFETs and op amps.

#### 2.4.1 TPS7A47

The TPS7A47 device is a 36-V ultra-low noise  $(4-\mu V_{RMS})$  LDO linear regulator capable of sourcing a 1-A load and providing a positive output voltage. The output voltage for the TPS7A47 can be configured with external feedback resistors. The device is designed with bipolar technology primarily for high-accuracy, high-precision applications where clean voltage rails are critical to maximize system performance. This feature makes it ideal for powering high-performance analog circuitry in critical applications such as medical. The device is also ideal for post DC-DC converter regulation.

#### 2.4.2 TPS7A33

The TPS7A33 device is a -36-V ultra-low noise (16- $\mu$ V<sub>RMS</sub>, 72-dB PSRR) LDO linear regulator capable of sinking a 1-A load and providing a negative output voltage. The output voltage for the TPS7A33 can be configured with external feedback resistors. The device is designed with bipolar technology primarily for high-accuracy, high-precision applications where clean voltage rails are critical to maximize system performance. This feature makes it ideal for powering high-performance analog circuitry in critical applications such as medical. The device is also ideal for post DC-DC converter regulation.

#### 2.4.3 CSD19533KCS

The CSD19533KCS device is a 100-V, 8.7-m $\Omega$ , TO-220 NexFET<sup>TM</sup> power MOSFET. With a pulsed drain current limit of 207 A (at 25°C) at pulse durations  $\leq$  100  $\mu$ s and duty cycle  $\leq$ 1%, it makes it ideal for the pulsed current output applications like medical ultrasound.

#### 2.4.4 TLVx171

The 36-V TLVx171 family provides a low-power option for cost-conscious industrial systems requiring an electromagnetic interference (EMI)-hardened, low-noise, single-supply operational amplifier (op amp) that operates on supplies ranging from 2.7 V (±1.35 V) to 36 V (±18 V). The single-channel TLV171, dual-channel TLV2171, and quad-channel TLV4171 provide low offset, drift, quiescent current balanced with high bandwidth for the power. This series of op amps are rail-to-rail input as well as output.

#### 2.5 System Design Theory

This section explains the theory, component selection, and design details for both the positive and negative regulator sections.

#### 2.5.1 Positive Floating Regulator

The positive regulator section uses a 36-V off-the-shelf positive LDO regulator and floats the ground of regulator with a DC amplifier (using low-voltage op amp and transistor).

#### 2.5.1.1 Floating or Virtual Ground for Positive Regulator

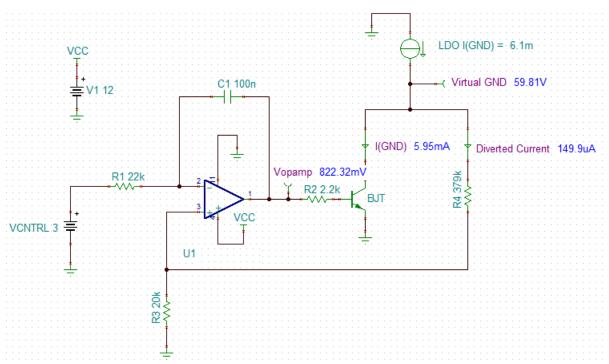

The ground of a regulator can be floated using multiple methods and tricks. For this application, the ground of regulator is floated using a DC amplifier. Any positive regulator has some current flowing into the GND pin, which is termed as I(GND) in its datasheet. For the TPS7A4701, it is specified as 6.1 mA typical when the output current is 1 A.

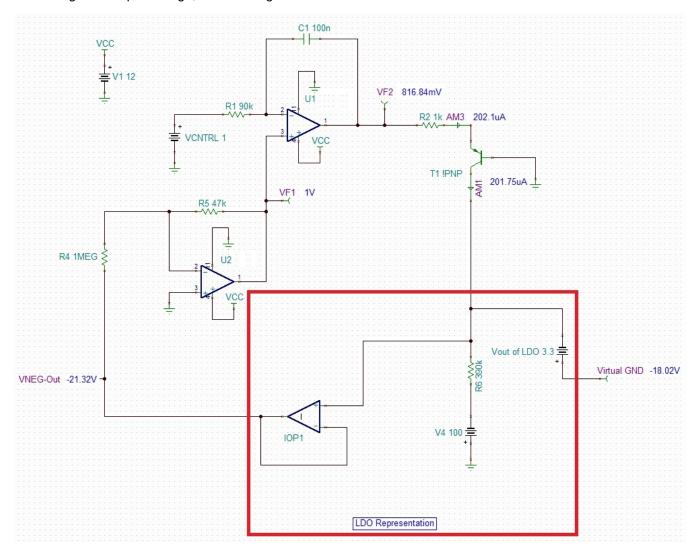

Taking this current as a worst case, the user can put is as current source in the TINA simulation shown in  $\S$  5. Regulator I(GND) is the current from the GND pin. This current is divided into two paths: one through an NPN BJT and other through a resistor voltage divider. Op amp U1 is operated as an integrator in open-loop configuration and drives the BJT through a series resistance of 2.2 kΩ. The op-amp is supplied with a 12-V supply VCC. The  $V_{CNTRL}$  input decides the value of virtual ground voltage by using 2 % 8.

Virtual GND =

$$\left(\frac{379k + 20k}{20k} \times V_{CNTL}\right) \approx 20 \times V_{CNTL}$$

(8)

图 5. TINA Simulation for DC Amplifier for Floating Regulator Ground (Positive Regulator)

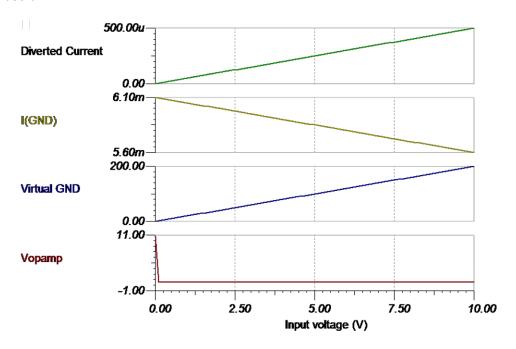

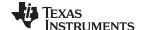

To understand the relationship between the control voltage and virtual ground signal, the graph shown in § 6 is useful.

图 6. DC Transfer Characteristics: Control Voltage versus Virtual Ground

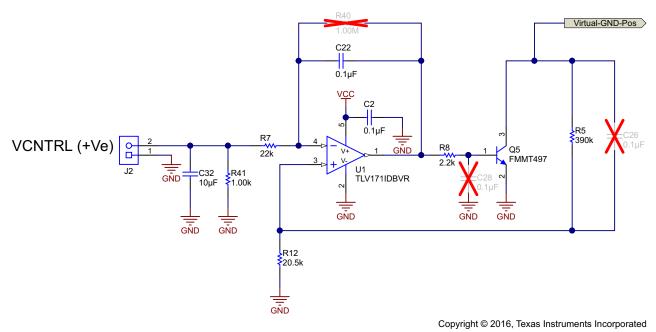

Based on the TINA circuit simulation, the TLV171 is used as an op amp for generating virtual ground using control voltage. The schematic for this section is shown in  $\boxed{8}$  7.

图 7. DC Amplifier to Generate Virtual Ground (Positive Regulator)

#### 2.5.1.2 Voltage Scaling Circuit

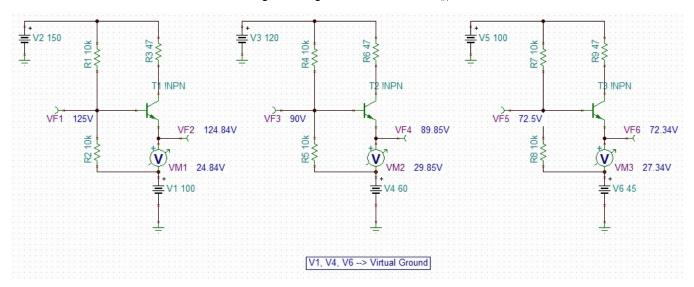

The scalability in terms of voltage is implemented using voltage sharing circuit at the input of the regulator. Referring to № 9, the resistors R13 and R14 along with BJT Q6 are used for implementing voltage sharing circuit.

Assuming the input voltage  $V_{IN}$  is 120-V DC and virtual ground (say  $V_{VG}$ ) is set at 90 V, the R13 and R14 resistors generate a mid-point voltage =  $(V_{IN} + V_{VG}) / 2 = (120 + 90) / 2 = 105$  V. This signal at the base of the BJT (= 105 V) keeps the emitter of BJT at 104.3 V approximately (depending on the BJT used; this can vary). This means the voltage going to the regulator is  $V_{EMITTER} - V_{VG} = 104.5 - 90 = 14.5$  V. This is true for any value of  $V_{IN}$  and  $V_{VG}$  (for example,  $V_{IN} = 100$  V,  $V_{VG} = 60$  V,  $V_{BASE} = 80$  V,  $V_{EMITTER} = 79.3$  V, and regulator input voltage = 19.3 V).

This functionality helps in keeping a safe voltage at the input of the regulator by setting  $V_{IN}$  and  $V_{VG}$ .  $\boxtimes$  8 shows the TINA simulation for voltage scaling circuit at different  $V_{IN}$  and VVG values.

$\underline{\mathbb{R}}$  8. Voltage Scaling Circuit Simulation at Different  $V_{IN}$  and  $V_{VG}$  Values

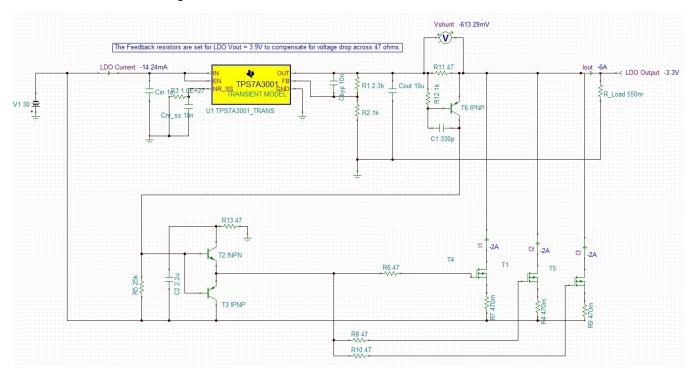

#### 2.5.1.3 Positive Regulator Circuit Using Virtual Ground

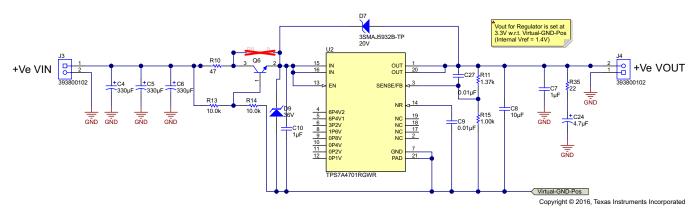

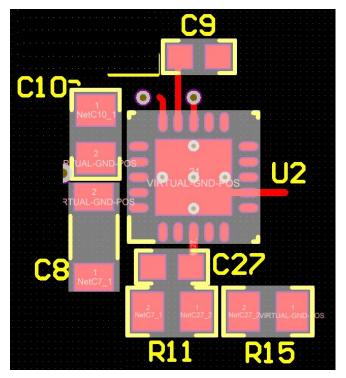

§ 9 shows the positive regulator circuit using the TPS7A4701. The input capacitor C10 and output capacitor C8 are recommended values from the datasheet of the TPS7A4701. The output of the regulator with respect to virtual ground is 3.3 V set using feedback resistors R11 and R15.

D9 (36-V TVS) and D7 (20-V Zener diode) are used as protection devices for the regulator. The Zobel network (R35 and C24) are used to reduce the effect of inductive wires connected at the output.

图 9. Positive Regulator Using TPS7A4701 and Virtual Ground

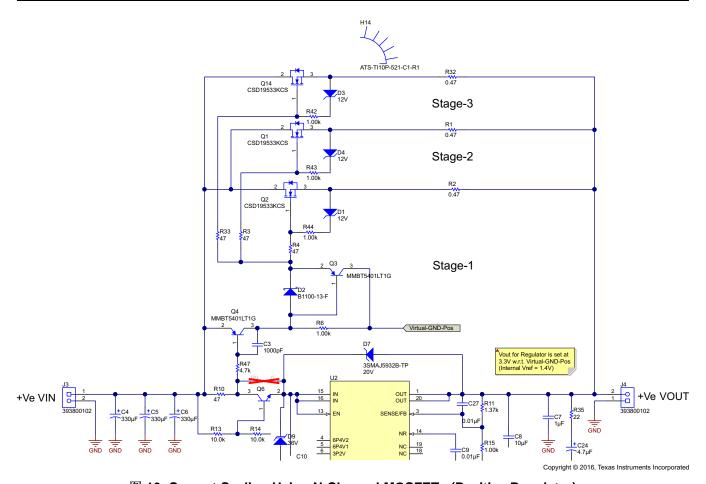

## 2.5.1.4 Current Scaling Using External MOSFETs

The current scalability is implemented using N-channel MOSFETs as shown in  $\boxtimes$  10. Once current starts flowing through the input path of the regulator, it generates a voltage drop across 47  $\Omega$ , which is in series with the BJT Q6. Because it is placed across the base and emitter of PNP transistor Q4, the voltage drop across this resistor always remains 0.6 to 0.7 V (depending upon the BJT), limiting the current flowing through the regulator at 0.7 V/47  $\Omega$  = 15 mA approximately. Any load current higher than 15 mA passes through the parallel MOSFET paths. Because the transient response is important for the application, a low-impedance drive circuit using a diode and PNP transistor is used for driving the MOSFET. The currents flowing through each MOSFET is also equalized by series resistors of 0.47  $\Omega$ .

图 10. Current Scaling Using N-Channel MOSFETs (Positive Regulator)

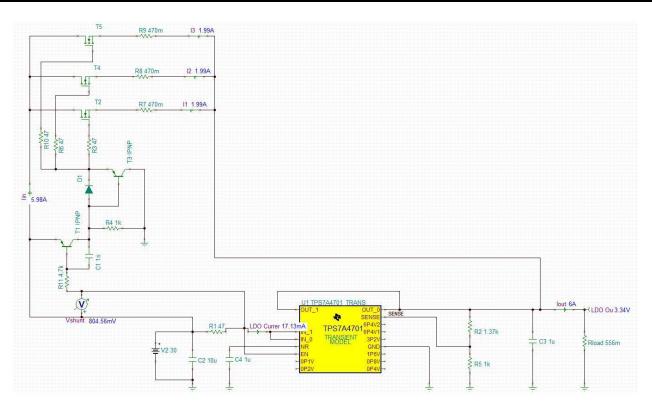

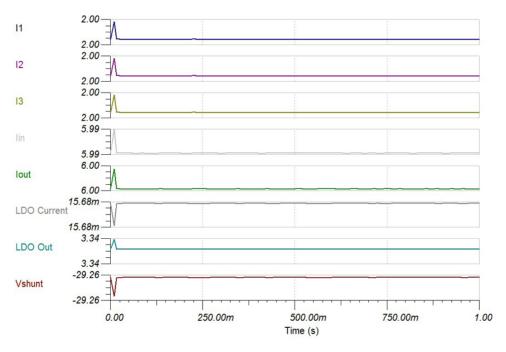

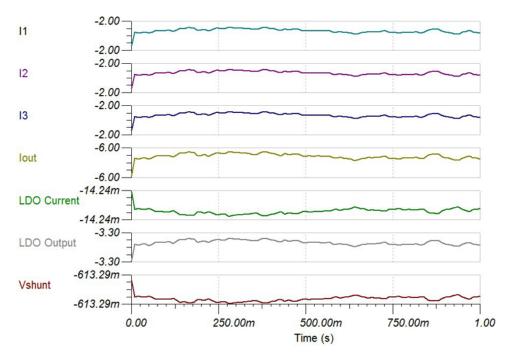

The TINA simulation for the current sharing is shown in 211. The output current is set at 6-A DC and each of the N-channel MOSFETs shares 2 A. The current flowing through the 47- $\Omega$  resistor is only 15.68 mA, which is governed by voltage set by PNP transistor. The transient waveforms for the current sharing are shown in 212.

图 11. TINA Simulation for Current Sharing

图 12. Transient Current Sharing (Positive Regulator)

## 2.5.2 Negative Floating Regulator

The negative regulator section uses a -36-V off-the-shelf positive LDO regulator and floats the ground of regulator with a DC amplifier (using two low-voltage op-amps and transistor).

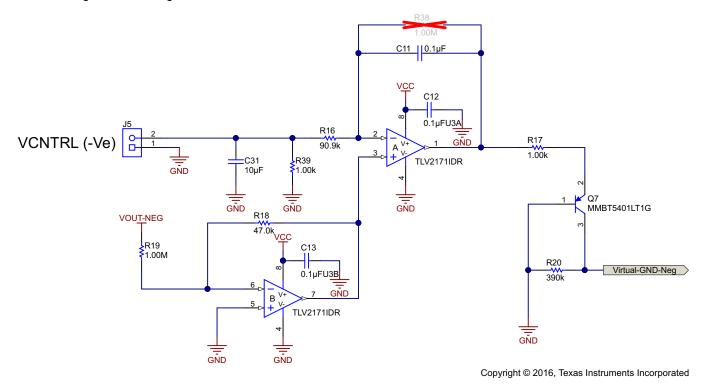

#### 2.5.2.1 Floating or Virtual Ground for Negative Regulator

For this section, the ground of regulator is floated using a DC amplifier as shown in  $\boxtimes$  13. Any negative regulator has a specification termed as I(GND) in the LDO datasheet. For the TPS7A3301, it is specified as 5 mA typical when the output current is 500 mA. This current is diverted using a PNP BJT. Two op amps form a DC amplifier. The first stage converts the negative output voltage to a positive value. The second op amp is an error amplifier and the system has a stable point where the negative Input becomes equal to the positive input of this second op amp. If the output goes too negative the PNP transistor (at the output of second op amp) is driven and this shifts the virtual ground towards zero. The  $V_{CNTL}$  input decides the value of the output voltage by using  $\triangle \vec{x}$  9:

$$VNEG(out) \approx 21 \times V_{CNTL}$$

(9)

As shown in 🗵 13, the output of the first op amp locks at V<sub>CNTL</sub> voltage (= 1 V) and sets the negative output voltage at −21.32 V and virtual ground at −18.02 V. The relationship between the control voltage, negative output voltage, and virtual ground is shown in 🗵 14.

图 13. TINA Simulation for DC Amplifier for Floating Regulator Ground (Negative Regulator)

${\ensuremath{\mathbb R}}$  14. DC Transfer Characteristics: Control Voltage versus Negative  ${

m V}_{

m out}$  and Virtual Ground

Based on the TINA circuit simulation, the TLV2171 is used as an op amp for generating virtual ground using control voltage. The schematic of this section is shown in 🖺 15.

图 15. DC Amplifier to Generate Virtual Ground (Negative Regulator)

#### 2.5.2.2 Voltage Scaling Circuit

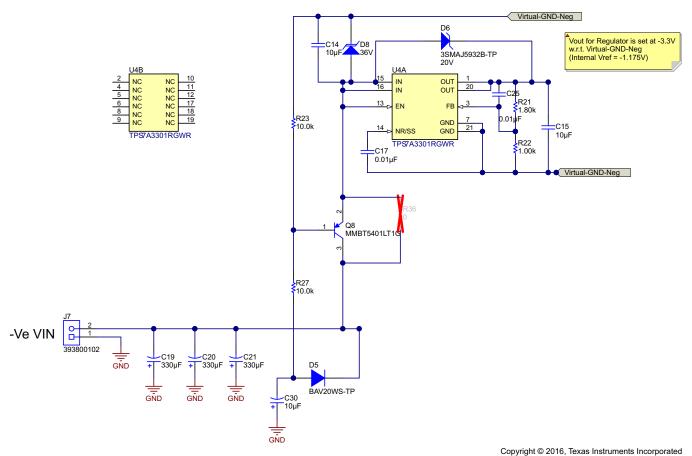

Referring to [8] 16, the scalability in terms of voltage is implemented using a voltage sharing circuit at the input of the regulator. Resistors R27 and R23 along with BJT Q8 are used for implementing voltage sharing circuit. The operation is similar to the circuit explained in † 2.5.1.2 for positive regulator input voltage scaling.

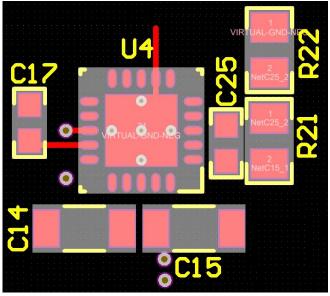

#### 2.5.2.3 Negative Regulator Circuit Using Virtual Ground

☑ 16 shows the negative regulator circuit using the TPS7A3301. Input capacitor C14 and output capacitor C15 are recommended values from the TPS7A3301 datasheet. The output of the regulator with respect to virtual ground is 3.3 V set using feedback resistors R21 and R22.

D8 (36-V TVS) and D6 (20-V Zener diode) are used as protection devices for the regulator.

Note that the peak detector circuit is used before feeding the input to the regulator. Capacitor C30 and diode D5 along with R27 (=  $10 \text{ k}\Omega$ ) are used as the peak detector circuit. This helps in improving the output voltage because during the loaded condition, the input voltage across the bulk capacitors (C19, C20, and C21) will start drooping. The peak detector circuit holds the charge until the time constant value of  $10 \text{ \mu s} \times 10 \text{k} = 0.1$  seconds.

图 16. Negative Regulator Using TPS7A3301 and Virtual Ground

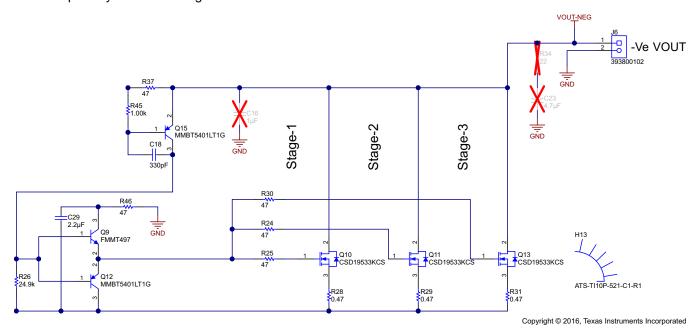

## 2.5.2.4 Current Scaling Using External MOSFETs

The current scalability is implemented using N-channel MOSFETs as shown in  $\[mathbb{N}\]$  17. Once current starts flowing through the regulator, it generates a voltage drop across 47  $\Omega$ , which is in series with the regulator output. The voltage drop across this resistor always remains 0.6 to 0.7 V (depending upon the BJT), limiting the current flowing through the regulator at 0.7 V/47  $\Omega$  = 15 mA approximately. Any load current higher than 15 mA passes through the parallel MOSFET paths. Because the transient response is important for the application, a low-impedance drive circuit using a buffer (made using NPN and PNP transistors) is used to drive the MOSFET. The current buffer is decoupled using a 47– $\Omega$  resistor (R46) and a 2.2- $\mu$ F capacitor (C29). The sense signal across R37 generates a current to be flown through R26. The voltage drop across R26 is used for generating Vgs to drive the MOSFETs. The currents flowing through each MOSFET is also equalized by series resistors of 0.47  $\Omega$ .

Note that the output is always affected by the voltage drop across R37, which can be in the range of 0.6 to 0.7 V (depending on the BJT used). This should be considered while setting up the output voltage, especially in lower voltage conditions.

图 17. Current Scaling Using N-Channel MOSFETs (Negative Regulator)

The TINA simulation for the current sharing is shown in  $\boxtimes$  18. The output current is set at –6-A DC and each of the N-channel MOSFETs shares –2 A. The current flowing through the 47- $\Omega$  resistor is only –14.24 mA, which is governed by voltage set by the PNP transistor across 47  $\Omega$ . The transient waveforms for the current sharing are shown in  $\boxtimes$  19.

图 18. TINA Simulation for Current Sharing

图 19. Transient Current Sharing (Negative Regulator)

#### 2.5.3 Selecting Power MOSFETs

The output current delivering ability of the regulator depends on a few parameters.

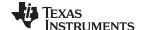

图 20. Current Delivering Ability of Input Capacitor

As shown in 图 20, the deliverable current is calculated as 公式 10:

$$I_{DELIVER} = \frac{V_{DIP} \times C_{IN}}{t}$$

(10)

$V_{\text{dip}}$  is dependent on the regulator's maximum input to output difference allowable (as mentioned in the regulator's datasheet). For the TIDA-01371, both regulators have the maximum allowable input to output difference of 36 V. Also, due to input voltage scaling circuit, that maximum can be doubled. In summary, the TIDA-01371 can support a voltage dip on input capacitor of 72 V approximately.

Using the example shown in № 20, assume the voltage across input capacitor is dropping from 100 V to 70 V in a time period of 1 ms. Because it is dropping in a linear fashion, the actual voltage seen by the MOSFETs is an average of the same, which is 15 V.

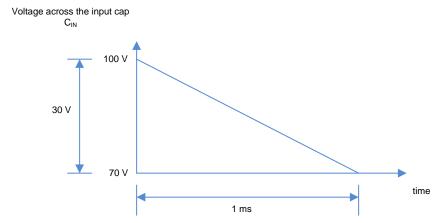

Now look at the MOSFET datasheet for the SOA graph. This graph defines the instantaneous V-I product of the MOSFET. The SOA graph for CSD19533KCS is shown in

図 21.

At VDS = 15 V and a pulse of 1 ms, the maximum drain to source current supported by CSD19533KCS is  $\approx$  15 A.

As the voltage dip across input capacitor goes bigger, the current capability of the MOSFET (based on the SOA graph) will reduce.

The MOSFETs are selected based on the following parameters:

- 1. Current to be delivered

- 2. Voltage dip on the input capacitor

- 3. Pulse duration for which MOSFET is turned on

- 4. Package of MOSFET

图 21. SOA Graph for CSD19533KCS

#### 3 Hardware, Testing Requirements, and Test Results

This section explains the test setup required to test the TIDA-01371 design.

## 3.1 Test Setup

The board has a total of seven connectors:

- J1 = VCC for virtual ground generation circuit

- J2 = Control voltage for positive regulator

- J3 = Positive input connector (10 to 120 V)

- J4 = Positive output connector (2.5 to 100 V)

- J5 = Control voltage for negative regulator

- J6 = Negative output connector (–2.5 to –100 V)

- J7 = Negative input connector (10 to 120 V)

## **WARNING**

The user must have experience in handling high-voltage circuits while testing this board.

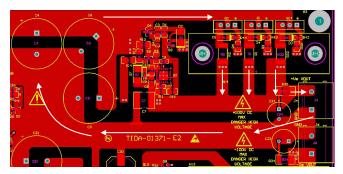

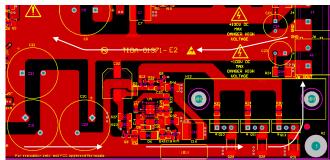

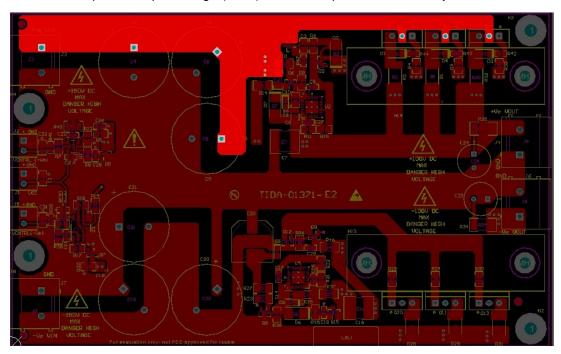

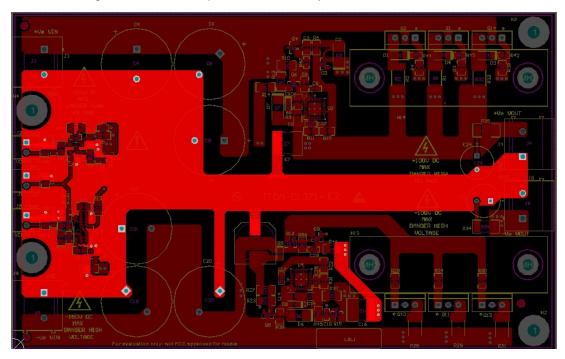

图 22. Top View of TIDA-01371 Board

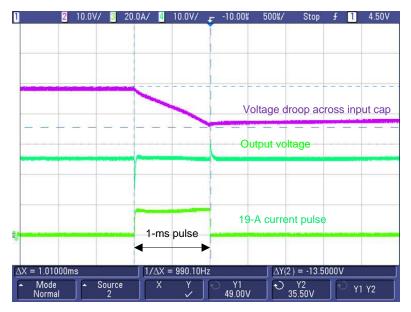

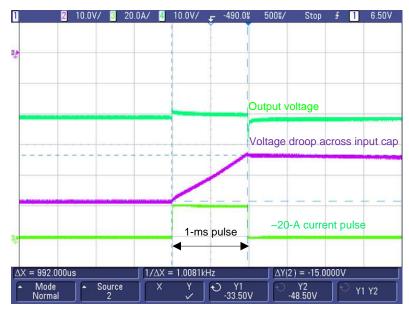

The block diagram shown in <a>8</a> 23 highlights the test setup required to test the TIDA-01371 board for load regulation tests. The load regulation is required to have 1-ms pulses generated for very high currents (±20 A) to be connected at J4 and J6. Also, the current limits typically set by the SMPS circuits is the average current limit. To see the actual droop across the input bulk capacitors of the TIDA-01371, special current limit circuits are built and used for testing purposes.

图 23. Test Setup

23

## 3.2 Testing and Results

This section shows the test results for the TIDA-01371 design.

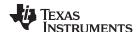

#### 3.2.1 Transfer Characteristics

The positive regulator section is operating with respect to a virtual ground. This virtual ground is set using an external control voltage  $V_{CNTL(P)}$ .  $\boxtimes$  24 shows the transfer characteristics for a positive regulator with respect to the control voltage.

图 24. Transfer Characteristics for Positive Regulator (at Input Voltage of 110 V)

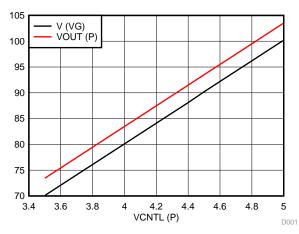

The negative regulator section is operating with respect to a virtual ground. This virtual ground and ultimately the negative output voltage is set using an external control voltage  $V_{CNTL(N)}$ .  $\boxtimes$  25 shows the transfer characteristics for a negative regulator with respect to the control voltage.

图 25. Transfer Characteristics for Negative Regulator (at Input Voltage of -110 V)

#### 3.2.2 Load Regulation with Pulsed Load

图 26. Load Regulation for Positive Regulator

图 27. Load Regulation for Negative Regulator

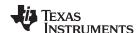

## 3.2.3 Load Regulation with Constant Load

Shows the load regulation for the positive and negative regulator together.

图 28. Load Regulation With Constant Load

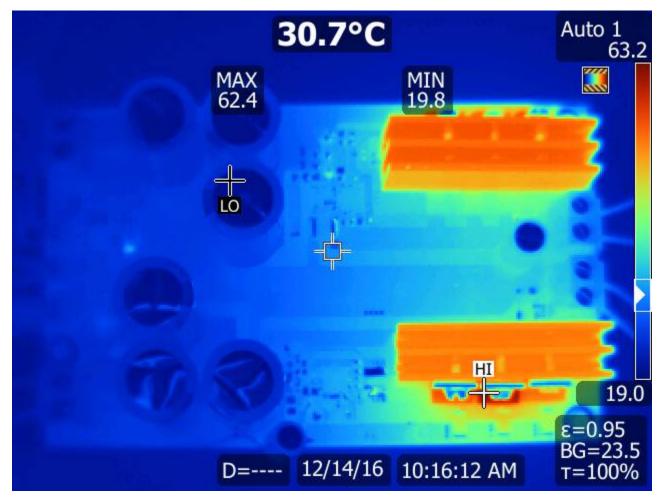

#### 3.2.4 Thermal Performance

The CW mode needs a continuous current flow through both the regulator sections at the same time. The TIDA-01371 board is tested for thermal performance with the following conditions:

- +V<sub>IN</sub> = 15 V

- +V<sub>OUT</sub> = 10 V at 500 mA

- −V<sub>IN</sub> = −15 V

- $-V_{OUT} = -10 \text{ V at } 500 \text{ mA}$

- Ambient temperature = 22°C

- Forced cooling = No

- Time after which thermal image is taken (using thermal camera) = 30 minutes

The thermal image for the TIDA-01371 is shown in

■ 29.

图 29. Thermal Image for TIDA-01371

Design Files www.ti.com.cn

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01371.

## 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01371.

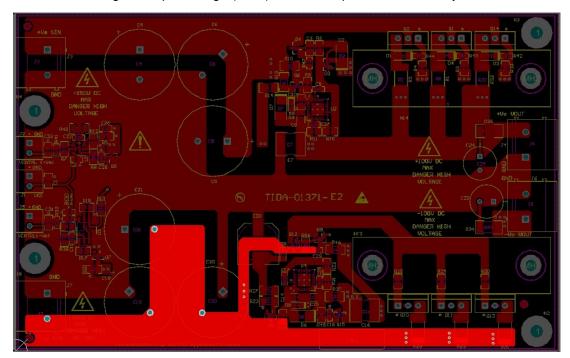

## 4.3 PCB Layout Recommendations

Because the design supports high current and high voltage conditions, it is required to have a proper layout. The TIDA-01371 board has four layers: Top, GND, PWR, and bottom.

图 30. Placements for TPS7A4701 and Adjacent Components

图 31. Placements for TPS7A3301 and Adjacent Components

www.ti.com.cn Design Files

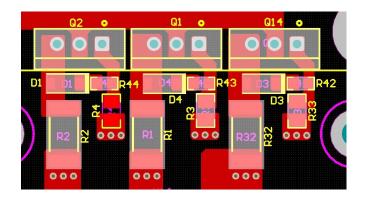

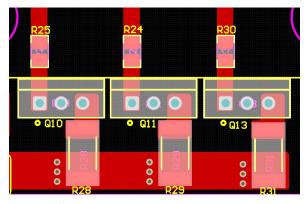

§ 32 and § 33 show the placement of power MOSFETs and corresponding components like gate resistor, current equalization resistors, and clamping Zener diodes.

图 32. Placements for MOSFETs and Adjacent Circuits for Positive Regulator

图 33. Placements for MOSFETs and Adjacent Circuits for Negative Regulator

图 34 and 图 35 show the direction of current flow and the layout done according to these directions.

图 34. Current Path for Positive Regulator

图 35. Current Path for Negative Regulator

Design Files www.ti.com.cn

图 36. Layout Showing +VIN Plane

🛚 37 shows how ground is laid as a plane on all four layers.

图 37. Layout Showing GND Plane

www.ti.com.cn Design Files

图 38 shows how negative input voltage (-VIN) is laid as a plane on all four layers.

图 38. Layout Showing -VIN Plane

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01371.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01371.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01371.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01371.

## 5 Related Documentation

1. Texas Instruments, TINA TI Simulation Software (http://www.ti.com/tina-ti)

#### **5.1** 商标

NexFET is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

Terminology www.ti.com.cn

## 6 Terminology

**DAC**— Digital-to-analog converter

LDO— Low dropout

SOA— Safe operating area

## 7 About the Authors

**SANJAY PITHADIA** is a systems engineer at Texas Instruments, where he is responsible for developing subsystem design solutions for the Medical Healthcare and Fitness sector. Sanjay has been with TI since 2008 and has been involved in designing products related to Energy, Smart Grid, Industrial Motor Drives, and Medical Imaging. Sanjay brings to this role his experience in analog design, mixed signal design, industrial interfaces, and power supplies. Sanjay earned his bachelor of technology in electronics engineering at VJTI, Mumbai.

**SANJAY DIXIT** is a system architect in the Industrial Systems-Medical Healthcare and Fitness Sector at Texas Instruments, where he is responsible for specifying reference designs.

www.ti.com.cn 修订历史记录

# 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Changes from Original (February 2017) to A Revision                      |    |

|--------------------------------------------------------------------------|----|

| • 已更改 布局以适应当前设计指南模板                                                      | 1  |

| • 己添加 在资源 中添加了 TIDA-01352                                                |    |

| • 已更改 denominator in the C <sub>OUT</sub> equation from "300" to "20"    | 4  |

| • 已更改 title from Circuit Design to System Design Theory                  |    |

| • 已更改 BJT in <i>Current Scaling Using External MOSFETs</i> from Q5 to Q6 | 12 |

| • 已更改 TINA Simulation for Current Sharing figure                         |    |

| • 己删除 Software Files section                                             |    |

|                                                                          |    |

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司