# TEXAS INSTRUMENTS

## 说明

汽车电池电源线路在运行系统时容易出现瞬变。所需的典型保护包括过压、过载、反极性和跨接启动。在汽车的生命周期中,交流发电机可能会被更换为非 OEM 部件。售后市场上的交流发电机可能具有不同的负载突降保护或没有负载突降保护,这可能导致损坏电子控制单元 (ECU)。此 TI 参考设计借助硬件控制提供保护,可处理这些潜在未抑制的负载突降脉冲(12V 和 24V)。在未抑制负载突降脉冲期间,可能会实现 A 类运行。

#### 资源

| TIDA-01167 | 设计文件夹 |

|------------|-------|

| LM5060-Q1  | 产品文件夹 |

| TPS7A1650  | 产品文件夹 |

| LM2903-Q1  | 产品文件夹 |

咨询我们的 E2E 专家

Copyright © 2016, Texas Instruments Incorporated

#### 特性

- 过压保护

- 过载保护

- 瞬态抑制

- 反极性保护

- 可配置选项支持在未抑制负载突降脉冲期间实现 A 类运行

- 可扩展至多电池拓扑 (12V、24V、48V)

- 通过极低静态电流提高系统效率

- 符合 ISO 7637-2、ISO 16750-2 的要求

## 应用

- 电子控制单元

- 车身控制模块

- 电池 ORing 应用

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

### 1 System Description

Automotive 12-, 24-, and 48-V battery power supply lines are prone to transients while running the system. Typical protections required for such a system are overvoltage, overload, reverse polarity, and jump start. Electronic circuits powered by direct battery lines need to be protected from such transients. An improper protection circuit could lead to damaging the components. Typically, DC-DC converters and system basis chips are directly operated on battery supply lines. Robust components and controllers are required to place on the battery power supply lines to suppress the transients. Typical protection requirements for 12- and 24-V batteries are considered for the TIDA-01167 reference design.

## 1.1 Key System Specifications

| 表 1. Key System | <b>Specifications</b> |

|-----------------|-----------------------|

|-----------------|-----------------------|

| PARAMETER                        | SPECIFICATION          | MIN | TYP    | MAX               | UNIT |

|----------------------------------|------------------------|-----|--------|-------------------|------|

| V <sub>INPUT</sub>               | DC input voltage       | 0   | _      | 70 <sup>(1)</sup> | V    |

| Output current                   | Q1, Q2 configurable    | _   | 2.50   | _                 | А    |

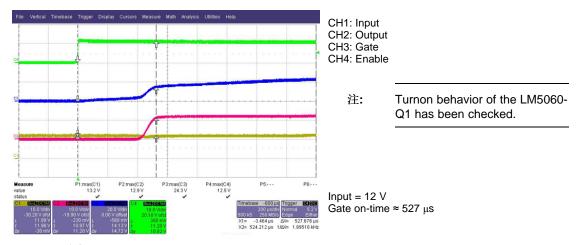

| Cata valtage (turnen time)       | 12 V                   | _   | 527.00 | _                 | μs   |

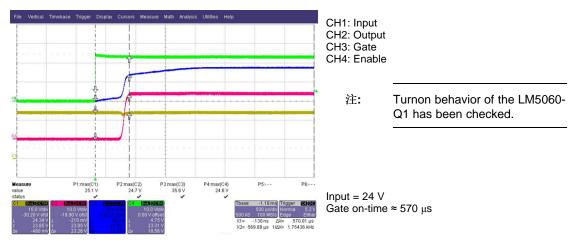

| Gate voltage (turnon time)       | 24 V                   | _   | 570.00 | _                 | μs   |

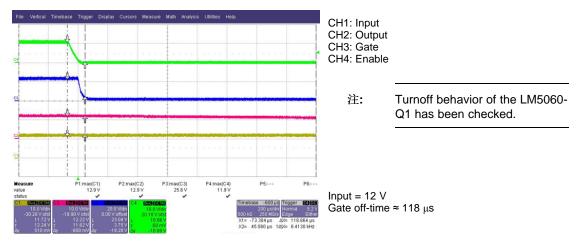

| Cata valtage (turnoff time)      | 12 V                   | _   | 118.00 | _                 | μs   |

| Gate voltage (turnoff time) 24 V | 24 V                   | _   | 233.00 | _                 | μs   |

| Operating aurent                 | 12 V, Jumper J5 closed | _   | 3.18   | _                 | mA   |

| Operating current                | 24 V, Jumper J5 closed | _   | 3.40   | _                 | mA   |

| 12 V, Jumper J5 o                | 12 V, Jumper J5 open   | _   | 53.00  | _                 | μΑ   |

| Quiescent current                | 24 V, Jumper J5 open   | _   | 102.00 |                   | μA   |

<sup>(1)</sup> Based on requirement specification maximum operating voltage of the design can be changed.

www.ti.com.cn System Overview

### 2 System Overview

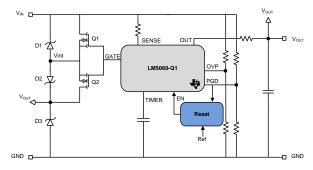

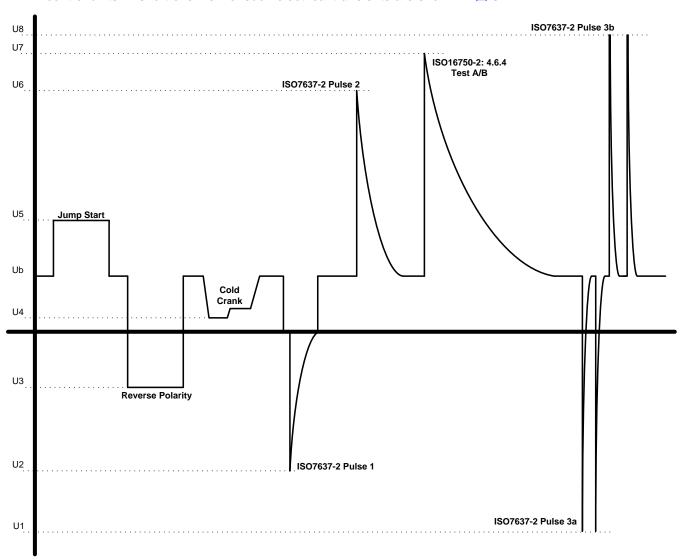

## 2.1 Block Diagram

Copyright © 2016, Texas Instruments Incorporated

图 1. Block Diagram

## 2.2 Highlighted Products

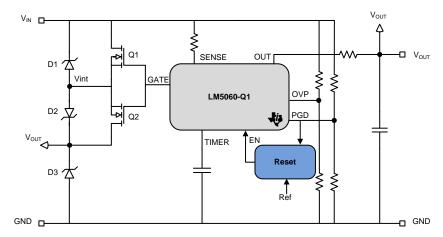

#### 2.2.1 LM5060-Q1

The LM5060 high-side protection controller provides intelligent control of a high-side N-channel MOSFET during normal on/off transitions and fault conditions. In-rush current is controlled by the nearly constant rise time of the output voltage. A Power Good output indicates when the output voltage reaches the input voltage and the MOSFET is fully on. Input UVLO (with hysteresis) is provided as well as programmable input overvoltage protection (OVP). An enable input provides remote on or off control. The programmable UVLO input can be used as second enable input for safety redundancy. A single capacitor programs the initial start-up  $V_{GS}$  fault detection delay time, the transition  $V_{DS}$  fault detection delay time, and the continuous overcurrent  $V_{DS}$  fault detection delay time. When a detected fault condition persists longer than the allowed fault delay time, the MOSFET is latched off until either the enable input or the UVLO input is toggled low and then high.

System Overview www.ti.com.cn

Copyright © 2016, Texas Instruments Incorporated

图 2. LM5060-Q1 Functional Block Diagram

#### Key features include:

- Available in automotive grade, AEC Q-100

- Wide operating input voltage range: 5.5 to 65 V

- Less than 15-μA quiescent current in disabled mode

- Controlled output rise time for safe connection of capacitive loads

- Charge pump gate driver for external N-channel MOSFET

- Adjustable undervoltage lockout (UVLO) with hysteresis

- · Programmable fault detection delay time

www.ti.com.cn System Overview

- Adjustable input OVP

- Immediate restart after overvoltage shutdown

System Overview www.ti.com.cn

## 2.3 System Design Theory

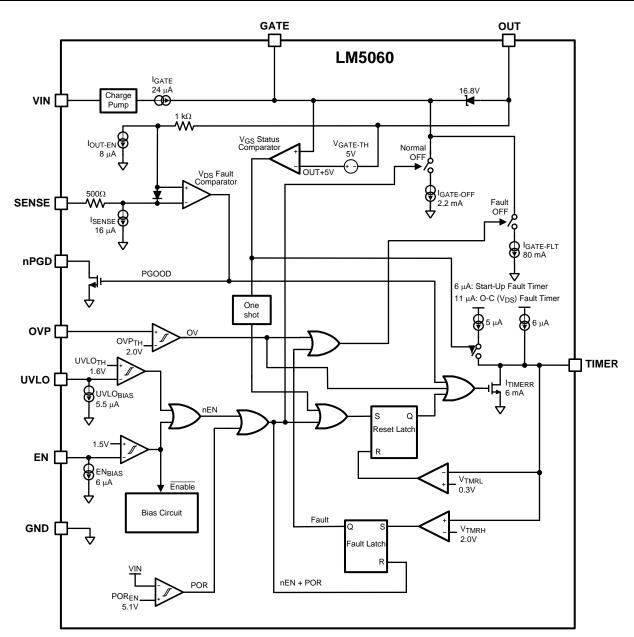

#### 2.3.1 Automotive Conducted Transients

In automotive environment batteries are connected to various electronic control units, loads, and sensor and load systems. Due to several parameters, conducted transients are seen on power lines for electronic control units. A short overview of such electrical transients are shown in 8.3.

图 3. Overview of Transients

表 2 provides the description, behavior, and impact of automotive power line electrical transients.

表 2. List of Automotive Electrical Transients Standards

| STANDARD OR SPECIFICATION | INSTITUTE OR COMPANY                                                                            |

|---------------------------|-------------------------------------------------------------------------------------------------|

| ISO 7637-2                | Road vehicles: Electrical disturbances from conduction and coupling                             |

| ISO 16750-2               | Road vehicles: Environmental conditions and testing for electrical and electronic equipment     |

| LV124                     | Group of original equipment manufacturers (OEMS, such as Audi®, BMW®, Porsche®, VW®, and so on) |

| SAEJ1113-11               | USA Standard by the Society of Auto Engineers                                                   |

www.ti.com.cn System Overview

#### 表 2. List of Automotive Electrical Transients Standards (continued)

| STANDARD OR SPECIFICATION | INSTITUTE OR COMPANY         |  |

|---------------------------|------------------------------|--|

| JASO A-1                  | Japanese automobile standard |  |

Specification of these standards are not limited to this list; auto manufacturers have their own internal standards. Although changes are typically only in a few parameters of different tests or limits, the essence of the requirements are the same.

ISO 7637 is titled *Road vehicles – Electrical disturbances from conduction and coupling*, and part 2 is specifically "Electrical transient conduction along supply lines only". The standard defines a test procedure, including the description of test pulses, to test the susceptibility of an electrical subsystem to transients, which could potentially be harmful to its operation. Each pulse is modeled to simulate a transient that could be created by a real event in the car. This design mainly focus for reverse polarity protection and ORing applications, which is predominantly placed next to battery.

ISO 16750 is titled *Road vehicles – Environmental conditions and testing for electrical and electronic equipment*, and part 2 is specifically "Electrical loads." An easy way to think of this standard is that it essentially defines a series of "supply voltage quality" events—variations of the battery supply voltage under various conditions. For the most part, these conditions are not harmful to the electrical subsystem, but can affect its state of operation. The tests in this standard are designed to see how the subsystem behaves before, during, and after these events.

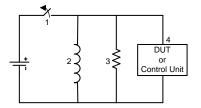

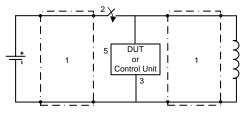

#### 2.3.1.1 ISO 7637-2 Pulse 1

This test is a simulation of transients due to supply disconnection from inductive loads. It is applicable to DUTs which, as used in the vehicle, remain connected directly in parallel with an inductive load.

Copyright © 2016, Texas Instruments Incorporated

图 4. ISO 7637-2 Pulse 1

#### Key features include:

- · Ignition switch and main relay or relevant

- Inductive load (relays, solenoids or motors, and so on)

- Load resistance (effective load on the power supply)

- Control unit or DUT (exposed to transients)

- Battery

System Overview www.ti.com.cn

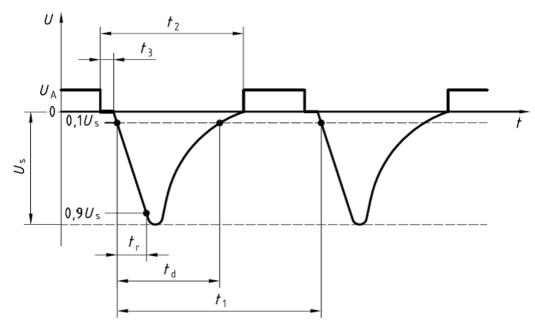

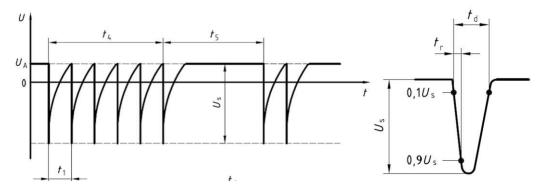

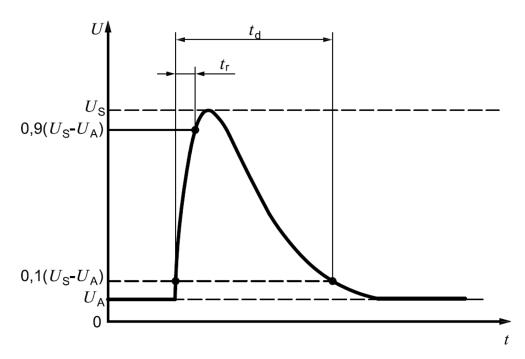

Pulse 1 occurs when switch(1) is open. The pulse itself, simulating an inductive kick in a parallel system, is a high voltage, negative-going transient. The waveform and its parameters are given in 85 and 55 and 5

图 5. ISO 7637-2 Pulse 1 Waveform

表 3. ISO 7637-2 Pulse 1 Parameters

| PARAMETER                     | 12-V SYSTEM            | 24-V SYSTEM                            |

|-------------------------------|------------------------|----------------------------------------|

| U <sub>s</sub>                | −75 to −100 V          | -450 to -600 V                         |

| R <sub>i</sub>                | 10 Ω                   | 50 Ω                                   |

| t <sub>d</sub>                | 2 ms                   | 1 ms                                   |

| t,                            | (1 <sub>-0.5</sub> )μs | <b>(</b> 3 <sub>-1.5</sub> <b>)</b> μs |

| t <sub>1</sub> <sup>(1)</sup> | 0.5 to 5 s             |                                        |

| t <sub>2</sub>                | 200 ms                 |                                        |

| t <sub>3</sub> (2)            | < 100 μs               |                                        |

<sup>(1)</sup> t1 must be chosen such that the DUT is correctly initialized before the application of the next pulse.

Pulse specification and parameters might vary based on OEM and vehicle configuration.

<sup>(2)</sup> t3 is the smallest possible time necessary between the disconnection of the supply source and the application of the pulse.

www.ti.com.cn System Overview

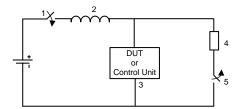

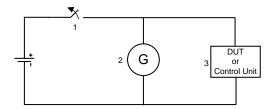

#### 2.3.1.2 ISO 7637-2 Pulse 2a

Pulse 2a simulates transients due to sudden interruption of currents in a device connected in parallel with DUT due to inductance of the wiring harness.

Copyright © 2016, Texas Instruments Incorporated

图 6. ISO 7637-2 Pulse 2a Simulation Picture

#### Key features include:

- · Ignition switch and main relay or relevant

- Inductance (wiring harness)

- Control Unit or DUT (exposed to transients)

- Load resistance (effective load on the power supply)

- · Load switch

- Battery

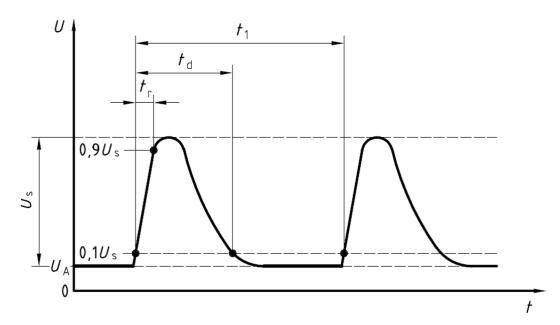

图 7. ISO 7637-2 Pulse 2a Waveform

System Overview www.ti.com.cn

| 表 4. Pulse 2a Paramete |

|------------------------|

|------------------------|

| PARAMETER                     | 12-V SYSTEM                            | 24-V SYSTEM |

|-------------------------------|----------------------------------------|-------------|

| U <sub>s</sub>                | 37 to 50 V                             | ,           |

| $R_i$                         | 2 Ω                                    |             |

| $t_d$                         | 0.05 ms                                |             |

| t <sub>r</sub>                | <b>(</b> 1 <sub>-0.5</sub> <b>)</b> μs |             |

| t <sub>1</sub> <sup>(1)</sup> | 0.2 to 5 s                             |             |

<sup>(1)</sup> The repetition time t<sub>1</sub> can be short, depending on the switching. The use of a short repetition time reduces the test time.

Pulse specification and parameters might vary based on OEM and vehicle configuration.

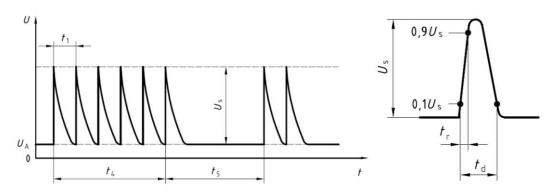

#### 2.3.1.3 ISO 7637-2 Pulses 3a and 3b

These test pulses are a simulation of transients, which occur as a result of the switching processes. The characteristics of these transients are influenced by distributed capacitance and inductance of the wiring harness.

Copyright © 2016, Texas Instruments Incorporated

图 8. ISO 7637-2 Pulse 3a and 3b Simulation Picture

Key features include:

- · Wiring harness with distributed inductance and capacitance

- Ignition switch and main relay or relevant

- Control Unit or DUT (exposed to transients)

- Inductive load (relays, solenoids or motors, and so on)

- Battery

Pulse 3a is seen in control unit or DUT when supply is turned ON or load is switched before the control unit. A burst of negative arching transients are seen due to relay on and off.

图 9. ISO 7637-2 Pulse 3a Waveform

www.ti.com.cn System Overview

#### 表 5. ISO 7637-2 Pulse 3a Parameters

| PARAMETER      | 12-V SYSTEM                           | 24-V SYSTEM  |

|----------------|---------------------------------------|--------------|

| U <sub>s</sub> | 112 to 150 V                          | 150 to 200 V |

| R <sub>i</sub> |                                       | 50 Ω         |

| t <sub>d</sub> | (0.1 <sup>+0.1</sup> <sub>0</sub> )μs |              |

| t <sub>r</sub> | 5 ns ± 1.5 ns                         |              |

| t <sub>1</sub> | 100 μs                                |              |

| t <sub>4</sub> | 10 ms                                 |              |

| t <sub>5</sub> | 90 ms                                 |              |

Pulse 3a is seen in control unit or DUT when load is switched after the control unit. A burst of positive arching transients are seen due to relay on and off.

图 10. ISO 7637-2 Pulse 3b Waveform

## 表 6. ISO 7637-2 Pulse 3b Parameters

| PARAMETER      | 12-V SYSTEM                        | 24-V SYSTEM  |

|----------------|------------------------------------|--------------|

| U <sub>s</sub> | 75 to 100 V                        | 150 to 200 V |

| $R_{i}$        | 50                                 | Ω            |

| t <sub>d</sub> | $\left(0.1^{+0.1}_{0}\right)\mu s$ |              |

| t <sub>r</sub> | 5 ns ±                             | 1.5 ns       |

| t <sub>1</sub> | 100 μs                             |              |

| t <sub>4</sub> | 10 ms                              |              |

| t <sub>5</sub> | 90 ו                               | ms           |

Pulse specification and parameters might vary based on OEM and vehicle configuration.

System Overview www.ti.com.cn

## 2.3.1.4 ISO 16750-2 4.6.4 Load Dump

This test is a simulation of load dump transient, occurring in the event of a discharged battery being disconnected while the alternator is generating charging current and with other loads remaining on the alternator circuit at this moment. Load dump may occur on account of a battery being disconnected as a result of cable corrosion, poor connection or of intentional disconnection with the engine running. This pulse was actually moved from ISO 7637 to ISO 16750.

The actual load dump event is extremely high energy and high voltage, which would be very difficult (and expensive) to protect against on every subsystem in the vehicle. Instead, every OEM installs a clamping circuit to the alternator, which limits the voltage to a more manageable level for the subsystem. This clamped voltage varies from OEM to OEM, but is typically in the range of 30 to 40 V.

Copyright © 2016, Texas Instruments Incorporated

图 11. ISO 16750-2 Test A Simulation Picture

Key features include:

- Battery connection (loose contact or disconnection)

- Alternator with internal clamping

- Control unit or DUT (exposed to transients)

- Battery

图 12. ISO16750-2 Test A Waveform (Without Centralized Load Dump)

www.ti.com.cn System Overview

#### 表 7. ISO16750-2 4.6.4.2.1 Test A Parameters

| PARAMETER           | TYPE OF SYS               | TEM                        |

|---------------------|---------------------------|----------------------------|

| FARAIVIETER         | U <sub>N</sub> = 12 V     | U <sub>N</sub> = 24 V      |

| U <sub>s</sub> (V)  | 79 ≤ U <sub>S</sub> ≤ 101 | 151 ≤ U <sub>S</sub> ≤ 202 |

| $R_{i}(\Omega)$     | 0.5 ≤ R <sub>i</sub> ≤ 4  | 1 ≤ R <sub>i</sub> ≤ 8     |

| t <sub>d</sub> (ms) | $40 \le t_d \le 400$      | 100 ≤ t <sub>d</sub> ≤ 350 |

| t <sub>r</sub> (ms) | 10 (0)                    |                            |

Pulse specification and parameters might vary based on OEM and vehicle configuration.

## 2.3.1.5 ISO 16750-2 4.7 Reverse Voltage

This test checks the ability of a control unit to withstand against the connection of a reversed battery when using an auxiliary starting device. During the service or while repairing the car, there is a possible risk of mis wire or wrong connections of system wiring harness to battery. In such case electronic control units needs to have protection for reverse battery voltage.

In automotive systems, the alternator is directly connected to battery without any fuse. Rectifier diodes in the alternator can withstand the reverse voltage for 60 s. If the diodes in alternator are damaged, then there is a scope for damage of wires and possible fire inside the system. Once the fuses or alternator are replaced, the rest of the devices are expected to run with class A. So the control units are expected to withstand the reverse voltage for at least  $60 \text{ s} \pm 6 \text{ s}$ .

表 8. ISO16750-2 Reverse Voltage Parameters

| NOMINAL VOLTAGE U <sub>N</sub> (V) | TEST VOLTAGE  U <sub>A</sub> (V) |

|------------------------------------|----------------------------------|

| 12                                 | 14                               |

| 24                                 | 28                               |

Pulse specification and parameters might vary based on OEM and vehicle configuration.

### 3 Hardware, Testing Requirements, and Test Results

#### 3.1 Required Hardware

## 3.1.1 Undervoltage $(V_{IN} < 5 V)$

When the battery voltage is less than 5 V, the LM5060-Q1 is in undervoltage mode, and the gate voltage will be pulled to ground. Q1 and Q2 will remain in OFF state. In an automotive environment, the UVLO state is not widely used as it is not included as feature of this design. The UVLO pin connects directly to the input of LM5060-Q1, so the device is independent of the UVLO threshold. The LM5060-Q1 starts or stops functioning based on the  $V_{IN}$  parameters defined in the datasheet of the device.

In an automotive environment, typical batteries used for supply are 12 V, 24 V, and 48 V. In normal operation, the LM5060-Q1 will always remains in an ON state. Methods and mechanism to support cold crank conditions will be explained in  $\ddagger$  3.1.4.

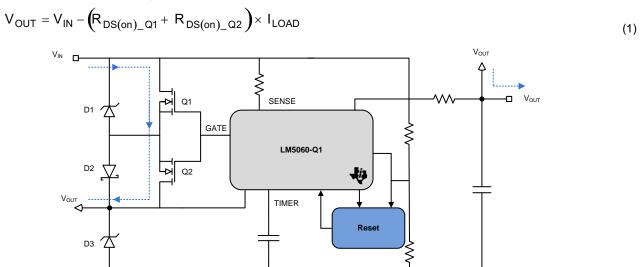

## 3.1.2 Normal Operation (5 V $\leq$ V<sub>IN</sub> $\leq$ 75 V)

If the enable pin is high and input voltage is less than the overvoltage threshold, then the gate of the LM5060-Q1 will turn on Q1 and Q2. Output voltage follows the input voltage with a voltage drop across Q1 and Q2 as shown in  $\boxed{8}$  13.

Copyright © 2016, Texas Instruments Incorporated

图 13. Normal Behavior

#### 3.1.3 Transient Suppression

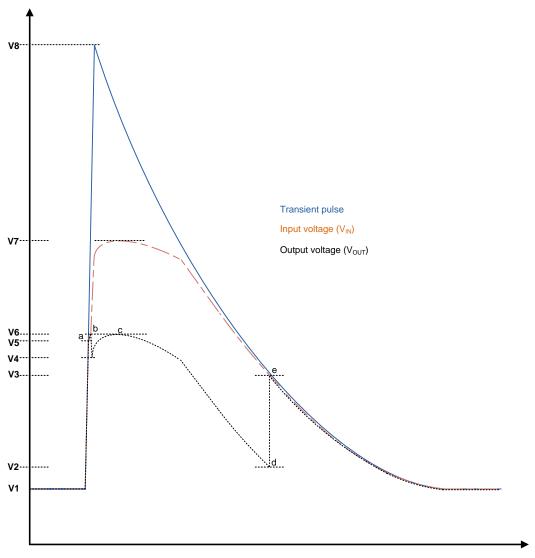

Transient suppression is a critical part for automotive input protection. As mentioned in † 2.3.1, there are different types of transients that need to be handled at the battery input. There is a need to have a common topology to support various automotive input protection requirements. Load dump typically describes input protection. In most automotive cases, the load dump pulse is handled in the alternator. During the service or repairs, there is a scope and chance to replace the current alternator with a low-cost solution. Low-cost alternators might have different specification or no load dump protection, which might leads to damage of electronics.

图 14. Input Protection Characteristics

If the represents the behavior of an input protection module during load dump pulses. Output voltage can be reduced to the voltage levels based on requirements and system design. V1 is the nominal battery input voltage applied to the system. During normal state, voltage at the output will be constant based on state of input voltage. As discussed in this case, circuit behavior is same as shown in If 13 (output voltage following the input voltage with Q1 and Q2). Since Q1 and Q2 are turned on, D3 is the TVS diode that will suppress the transients from input and output. Due to transients as shown in If 14, if the input voltage starts rising, output voltage will follow the input voltage until V5. V5 is the minimum break down voltage of D3.

$$V5 = V_{BV_D3\_Min}$$

(2)

When D3 breaks down, input current will start rising and leading D3 to clamp the voltage. As per 🖺 14, the transition between a to b represents the clamping behavior of D3.

$$I_{INPUT} = I_{LOAD} + \frac{(V_{IN} - V_{CV_D3})}{(R_{DS(on)_Q1} + R_{DS(on)_Q2})}$$

(3)

As the input voltage rises, the input current ( $I_{INPUT}$ ) will further increase. The LM5060-Q1 has overload detection, which will turn off Q1 and Q2 (and so on). If the input current is above the overcurrent threshold limit ( $I_{OCP\_LM5060}$ ), gate voltage will be pulled down with an 80-mA sink current. When the gate voltage is pulled down, Q1 and Q2 will be turned off. As shown in  $\boxtimes$  15, when Q1 and Q2 are turned off current will be flowing through D1, D2. Output voltage ( $V_{OUT}$ ) will vary based on input voltage ( $V_{IN}$ ),  $V_{BV\_D1}$ ,  $V_{BV\_D3}$  (break down voltages), and load current ( $I_{LOAD}$ ).

图 15. LM5060-Q1 OCP Latch During Transient

When OCP error is latched at the initial stage when  $V_{IN} < (V_{BV\_D1\_min} + V_{BV\_D3\_min} + V_{FD\_D2})$ :  $V_{OUT} = V4 = V_{IN} - V_{FD\_D2} - V_{BV\_D1\_min}$  (4)

During the load dump, voltage will further rise, which leads to clamping of both D1 and D3.

When  $V_{TRANS} \ge (V_{BV D1 min} + V_{BV D3 min} + V_{FD D2})$ :

$$V_{IN\_max} = V7 = (V_{CV\_D1\_max} + V_{CV\_D3\_max} + V_{FD\_D2})$$

(5)

$$V_{OUT\_max} = V6 = V_{CV\_D1\_max}$$

(6)

The load current of the system during the transients plays an important role for power dissipation and component selection. Peak power dissipation in the TVS diodes depends on the clamping voltage, peak transient voltage, and resistance of alternator. Selecting TVS diodes must be done based on energy dissipated in them during the peaks of transient.

Q1 and Q2 are turned off due to over current error. If the circuit design is not done properly, the LM5060-Q1 will turn OFF output voltage upon the completion of transient pulse. Input protection circuit must be implemented with appropriate circuit to remove the over current error. Take care when designing this circuit so that it will not clear all overcurrent errors. An overcurrent error that is produced due to transient (overvoltage) must be reset with an appropriate circuit. Selecting a reset voltage must be chosen appropriately to handle voltage drops and breakdown voltage of D1 (V<sub>BV D1 min</sub>).

If:

- V<sub>OUT min</sub> is the maximum voltage drop allowed

- V<sub>IN\_RESET</sub> is the LM5060-Q1 transient reset voltage

- R<sub>i</sub> is the alternator input resistance

Then:

$$V_{IN\_RESET} > V_{OUT\_min} + V_{CV\_D1\_max}$$

(7)

$$V_{IN\_RESET} < V_{BV\_D3} + (I_{OCP\_LM5060}) \times (R_i)$$

(8)

If  $V_{IN\_RESET}$  was set at very high voltages, there could be a chance of repeating the overcurrent error along with D3 breakdown voltage, which leads to output voltage latched off. So to avoid this incidence, reset voltage has to be set in such a way that overcurrent error will not be repeated.

If  $V_{\text{IN\_RESET}}$  is set at low input voltage, then output voltage might fall too low. If the output voltage falls low, it could be inconvenient to the DC-DC converter and affect the selection of components. In such a case, place a better filter circuit at input to avoid the damage or overstress to DC-DC converter or relevant components.

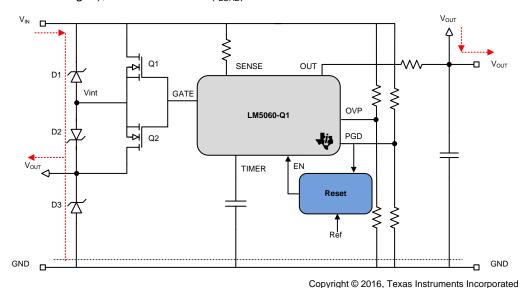

#### 3.1.4 Circuit Behavior

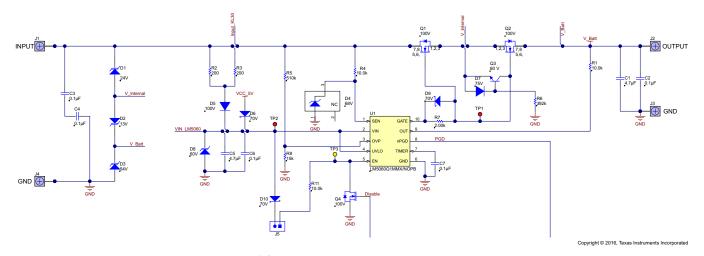

图 16. Input Protection Circuit

- R2, R3, D5, and D8 are used to protect the VIN pin of the LM5060 during the transients. R1, R2, and D8 can be changed accordingly to support transient peak voltages.

- Q1 is the main switch for overload and overvoltage errors for U1, whereas Q2 is to support the reverse polarity protection.

- There is no internal protection or detection of reverse polarity in the LM5060. Q3, D7, R6, and R7 are

used to protect the design from reverse polarity. Q3 will turn on and reduce the gate to source voltages

of Q1 and Q2. D7 is used to protect the Q3 whereas R6 to reduce the current consumption.

- R7 is used to control the turnon time of Q1 and Q2. It will also support in reducing the leakage current during the reverse polarity. During error state it is required to turn off the supply lines faster, so D9 is used to bypass R7 to turn off the Q1 and Q2.

- The undervoltage function is rarely used in automotive environment. It is not common for 12-V or 24-V systems. Design can be adapted for a 48-V system to set a defined voltage at the UVLO pin to save or reduce complexities of DC-DC converters.

- During cold crank conditions, input voltage will fall less than 5 V. The 5-V output of DC-DC converter can be connected through D6 to keep the LM5060 in active mode.

- D10 is used in the design to support external trigger input at test point along with J5 jumper pin. In end applications, D10 and J5 can be removed, and the external trigger input can be connected directly to R11.

- R1 and R4 are used to set the threshold for overload protection in the design. D4 will protect the sense pin during the peak transients. If unsuppressed load dump pulse is applied at input pin. Sense pin can withstand maximum 75V, D4 is used to protect the sense pin during high voltage transients.

- Due to inrush currents, high- or low-voltage transients, and noise, there could be OVP and overload errors set in the LM5060. An external timer capacitor C7 will be used to allow blanking period for these errors to differentiate noise and actual errors. Based on system requirement C7 is configurable. A fault will be latched when a 6-µA current flowing the C7 builds a voltage at timer, typically 2 V. When a fault is latched, Q1 and Q2 are turned off.

R5, R8 potential divider to support OVP for LM5060. During an overvoltage, Q1 and Q2 are turned off

when the input voltage falls less than the OVP threshold voltage; then output voltage resumes as Q1

and Q2 are turned ON.

Copyright © 2016, Texas Instruments Incorporated

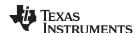

图 17. Comparator Reset Mechanism

- Comparator circuit is used to reset the LM5060. As discussed in † 3.1.3, it is required to reset the LM5060 if the overload error is latched due to transient voltage. Do not reset overload errors if the input voltage is in normal range.

- In a normal state, if the nPGD pin of the LM5060 is pulled low, voltage at non-inverting pin of U2A also remains low. As a result, voltage in the disable net is pulled to low by a comparator as 2.5 V is present at the inverting pin due to R9 and R12.

- The nPGD pin of the LM5060 is floating when overvoltage or overload errors are detected. Voltage at R15 gives a fraction of battery voltage across potential dividers of R10, R13, and R15. R16 can be populated with a appropriate value to give the hysteresis for the module.

- R14 is the pullup resistance for the open drain connection of the comparator.

- As specified in 公式 8, V<sub>IN\_RESET</sub> must be less than sum of the breakdown voltage and overload current with internal resistance. OVP for the LM5060 must be chosen to support the application appropriately.

## 3.2 Testing and Results

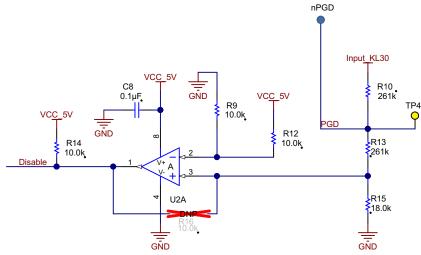

Test setup for automotive polarity protection has been done as shown in 🛚 18.

图 18. Test Setup

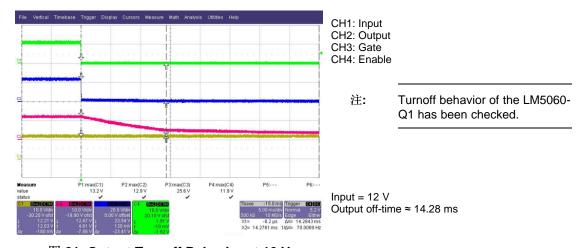

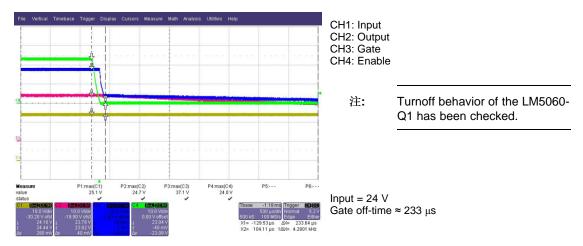

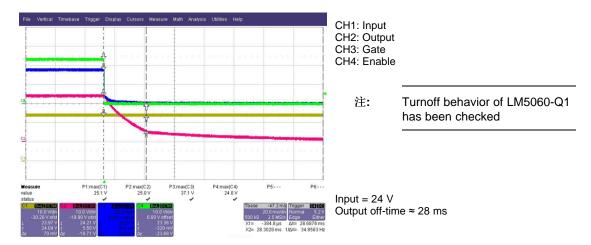

To check the performance of the LM5060-Q1, This TI Design has been tested for 12-V and 24-V applications.

## 3.2.1 Operational Tests

图 19. Turnon Behavior at 12 V

图 20. Gate Turnoff Behavior at 12 V

图 21. Output Turnoff Behavior at 12 V

图 22. Gate Turnon Behavior at 24 V

图 23. Gate Turnoff Behavior at 24 V

图 24. Output Turnoff Behavior at 24 V

#### 3.2.2 **Transient Tests**

图 25 shows the setup for transient testing.

图 25. Setup for Transient Tests

The transient tests used the following equipment:

- Teseq PA5840 Power Amplifier and Battery Simulator

- Teseq NSG 5500 Automotive Transient Immunity Tests

- Agilent Technologies Oscilloscope

23

### 3.2.2.1 12-V Battery

图 26. ISO7637-2 Pulse 1

图 27. TIDA-01167 Pulse 1 Behavior at 12 V

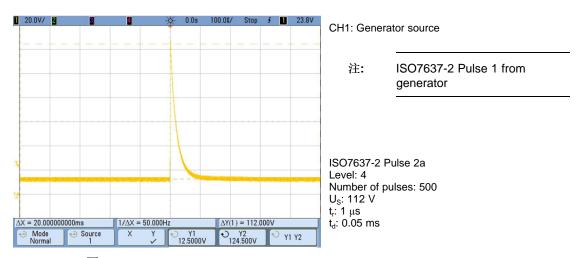

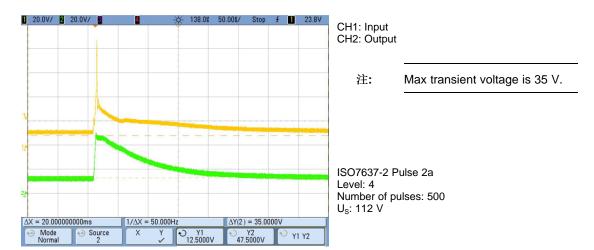

图 28. ISO7637-2 Pulse 2a

图 29. TIDA-01167 Pulse 2a Behavior at 12 V

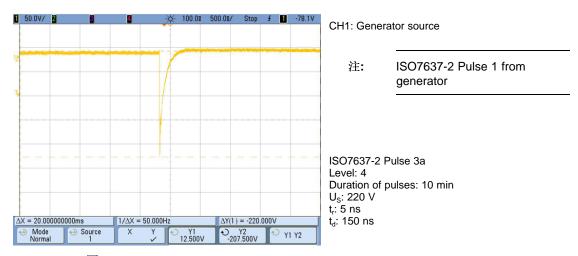

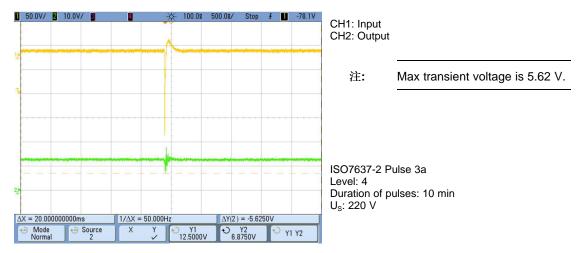

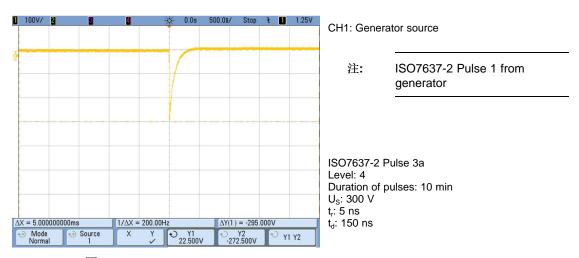

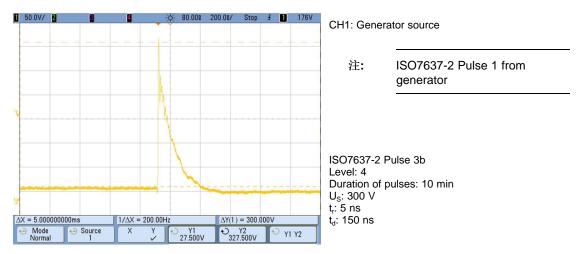

图 30. ISO7637-2 Pulse 3a

图 31. TIDA-01167 Pulse 3a Behavior at 12 V

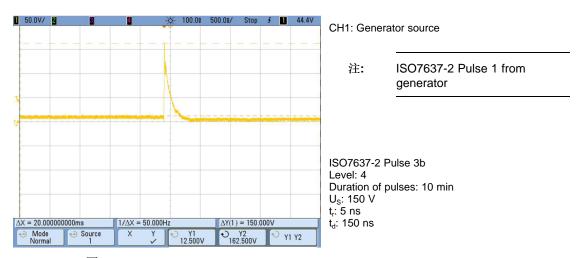

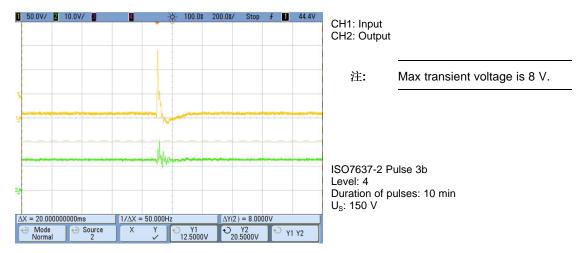

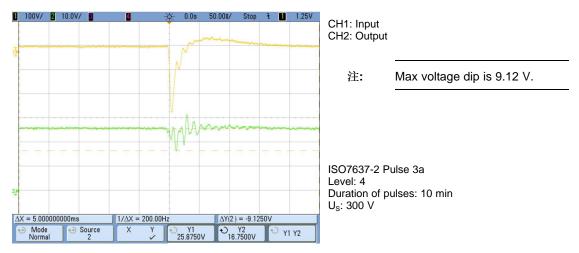

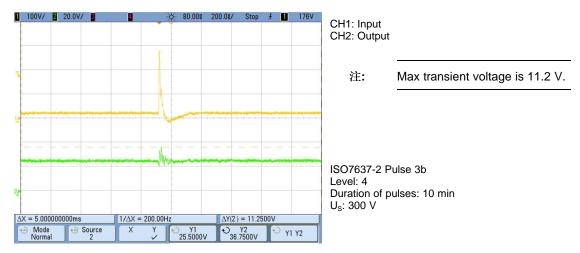

图 32. ISO7637-2 Pulse 3b

图 33. TIDA-01167 Pulse 3b Behavior at 12 V

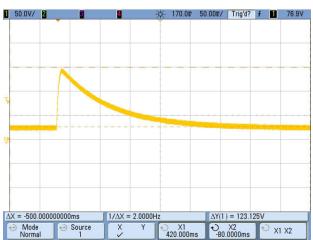

CH1: Generator source

ISO16750-2 unsuppressed load

dump from generator

ISO16750-2 unsuppressed load dump

图 34. ISO16750-2 Pulse 3b

CH1: Input CH2: Output

注:

Output max voltage is 41.75 V and min voltage is 7.5 V. Class A operation is possible as output voltage is in operating range for the 12-V system.

ISO16750-2 unsuppressed load dump U<sub>s</sub>: 101 V (87+14) R<sub>i</sub>: 0.5 Ω

图 35. TIDA-01167 Behavior 12-V Unsuppressed **Load Dump**

## 3.2.2.2 24-V Battery

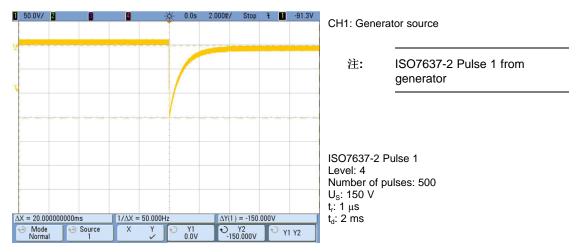

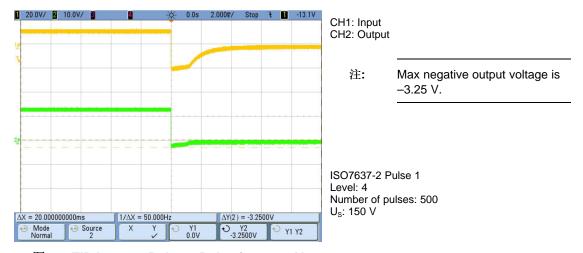

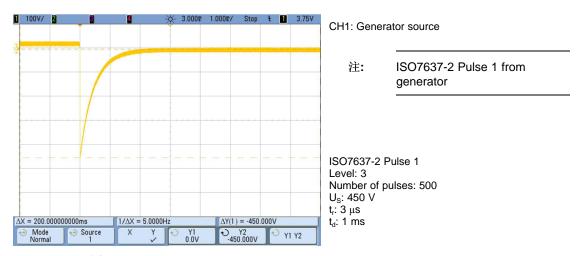

图 36. ISO7637-2 Pulse 1

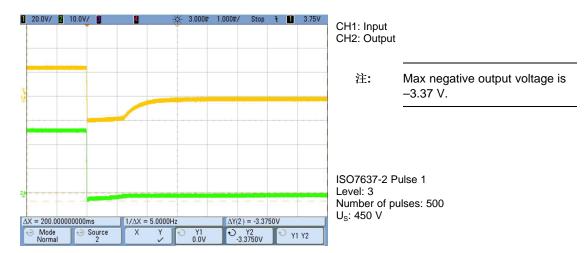

图 37. TIDA-01167 Pulse 1 Behavior at 24 V

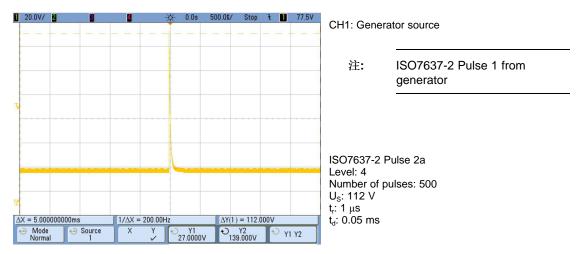

图 38. ISO7637-2 Pulse 2a

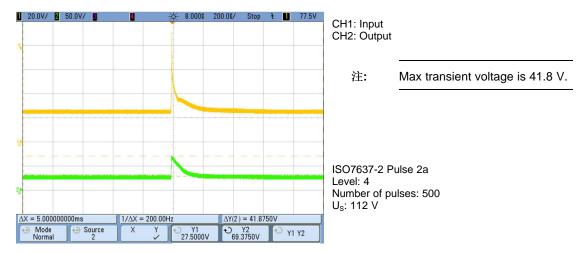

图 39. TIDA-01167 Pulse 2a Behavior at 24 V

图 40. ISO7637-2 Pulse 3a

图 41. TIDA-01167 Pulse 3a Behavior at 24 V

图 42. ISO7637-2 Pulse 3b

图 43. TIDA-01167 Pulse 3b Behavior at 24 V

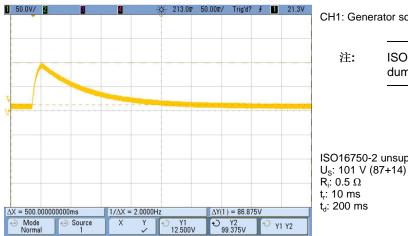

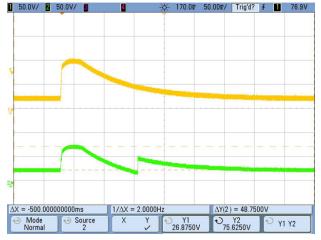

CH1: Generator source

注: ISO16750-2 unsuppressed load dump from generator

ISO16750-2 unsuppressed load dump

U<sub>s</sub>: 150 V (123.1+27)

$R_i$ : 4  $\Omega$   $t_r$ : 10 ms  $t_d$ : 200 ms

图 44. ISO16750-2 Unsuppressed Load Dump 24

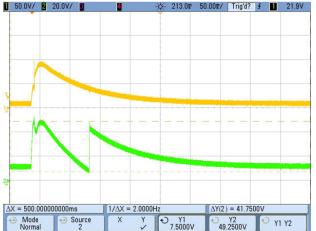

图 45. TIDA-01167 Unsuppressed Load Dump Behavior for 24 V

CH1: Input CH2: Output

注: Output max voltage is 75 V and min voltage is 26.8 V. Class A operation is possible as output voltage is in operating range for

the 24-V system.

Take care in the design for maximum operating voltage of

devices.

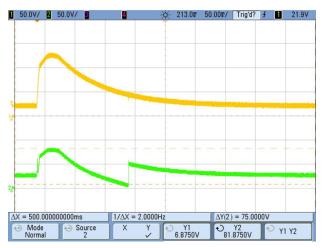

ISO16750-2 unsuppressed load dump

U<sub>s</sub>: 150 V (123.1+27)

$R_i$ : 4  $\Omega$   $t_d$ : 200 ms

图 46. TIDA-01167 Unsuppressed Load Dump Behavior for 24 V

CH1: Input CH2: Output

注:

Output max voltage is 81 V and min voltage is 6.8 V. Class B operation is possible.

Take care in the design for maximum operating voltage of devices.

ISO16750-2 unsuppressed load dump

$U_{s}$ : 175 V (148+27)  $R_{i}$ : 4  $\Omega$  $t_{d}$ : 200 ms

汽车 12V 和 24V 电池输入保护参考设计

www.ti.com.cn Design Files

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01167.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01167.

## 4.3 PCB Layout Recommendations

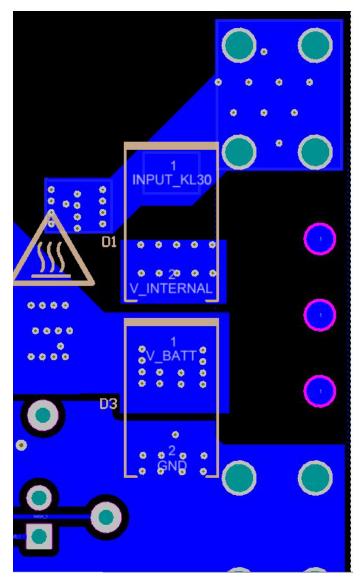

PCB layout has to be done with appropriate measures to ensure the smooth operation of functionality for input protection:

- 1. Check the series path tracks for power dissipation, set the layer thickness and area appropriately

- 2. Place vias appropriately to handle the conduction currents.

- 3. Place C3 and C4 very close to the connector.

- 4. Place D1, D2, D3 very closely and appropriately near to the connector.

Design Files www.ti.com.cn

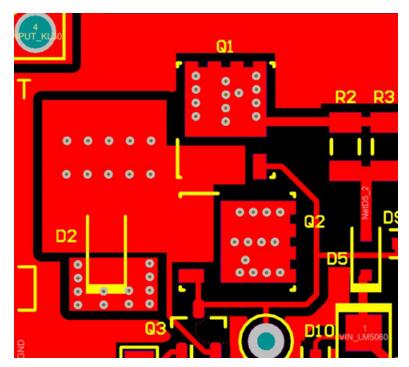

图 47. TVS Diodes Placement

- 5. Place decoupling capacitors near to the devices.

- 6. Place Q1 and Q2 close together.

www.ti.com.cn Design Files

图 48. Q1,Q2 Placement

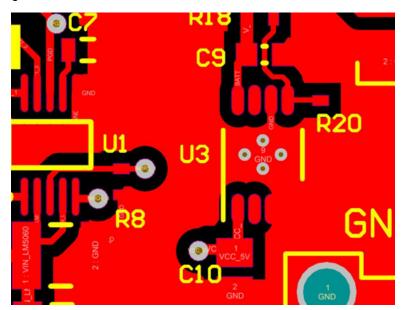

- 7. Connections from sense pin and output pins should be short and noise free.

- 8. Timer capacitor C7 should be near to U1 with low resistance to ground.

- 9. Place C5 and C6 near to U1, C9 and C10 near to U3, C8 near to U2.

- 10. C1 and C2 should be placed close to the output pins.

- 11. Place the current sensing device and shunt on the same side of the PCB.

- 12. Follow layout guidelines for U1 and U3.

图 49. U1 and U3 Layout

Design Files www.ti.com.cn

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01167.

#### 4.4 Gerber Files

To download the Gerber files, see the design files at TIDA-01167.

## 4.5 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01167.

#### 5 Related Documentation

- Texas Instruments, LM5060-Q1 Hotswap Design Calculator (SLVC667)

- 2. Texas Instruments, *Hot Swap Calculator Tutorial: Steps 1 & 2 Operating Conditions, Current Limit, & Circuit Breaker* (http://www.ti.com/general/docs/video/watch.tsp?entryid=4607940999001)

- 3. Texas Instruments, *Circuit protection overview*, TI Training (https://training.ti.com/circuit-protection-overview)

#### 5.1 商标

Audi is a registered trademark of AUDI AG. BMW is a registered trademark of BMW AG. Porsche is a registered trademark of Porsche AG. VW is a registered trademark of Volkswagen of America, Inc. All other trademarks are the property of their respective owners.

#### 6 About the Author

**RAMA KAMBHAM** (Rama Chandra Reddy) is an automotive system engineer working in Texas Instruments Deutschland. Rama brings to this role his extensive experience in Battery Management Systems and Engine Management Systems in the automotive domain. Rama earned his bachelor of engineering degree from Osmania University Hyderabad, India.

www.ti.com.cn 修订历史记录

## 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Cł | nanges from Original (November 2016) to A Revision | Page |

|----|----------------------------------------------------|------|

| •  | 已更改 布局以适应当前设计指南模板                                  |      |

| •  | 已更改 电路板图像                                          | ′    |

|    |                                                    |      |

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司