# TI 参考设计: TIDA-00976 高速高侧电流感应参考设计

# TEXAS INSTRUMENTS

# 说明

TIDA-00976 TI 设计是一种高速电流到电压电路。此设计针对需要在 5V 到 30V 电压的正电源轨中进行高速电流测量的电流感应 应用 进行了优化。此设计将降低 30V 电压中的共模电压,并产生集中在 2.5V 的输出电压,以利用模数转换器 (ADC) 进行采样。通过使用不同的精度参考,可以轻松更改输出共模。

#### 资源

THS4131产品文件夹TINA-TITM工具文件夹

咨询我们的 E2E 专家

# 特性

- 带宽 > 15MHz

- 转换电流到电压

- 高侧电压范围: 5V 至 30V

- 灵活的输出共模电压

# 应用

- 电能质量监测仪

- 射频 (RF) 功率放大器 (PA) 控制和包络跟踪

- 电机控制

- 功率因数校正和测量

该TI参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

# 1 System Description

The TIDA-00976 TI Design is a fixed-gain, high-bandwidth, and fully-differential, current-to-voltage conversion circuit designed for high-speed applications. With a supply voltage range of 5 to 30 V, this amplifier provides exceptional flexibility in high-side current-sense applications. With an input voltage of 30 V and typical ADC input voltage ranges of 5 V or less, the TIDA-00976 uses a two-stage configuration to reduce the input voltage range to a safe range for a typical ADC. The TIDA-00976 has been optimized for high-input voltage and large currents. The TIDA-00976 uses two THS4131 high-speed, fully-differential amplifiers (FDAs) to convert an input current to output voltage.

Design options for higher supply voltage and additional filtering are provided to cover additional applications.

# 1.1 Key System Specifications

2

#### 表 1. Key System Specifications

| PARAMETER                               | SPECIFICATIONS                    |  |

|-----------------------------------------|-----------------------------------|--|

| Supply voltage                          | 5- to 30-V external supply        |  |

| Current-to-voltage gain                 | 100 to 400 mV <sub>PP</sub> / Amp |  |

| Differential-output common-mode voltage | 2.5 V (adjustable)                |  |

| Target bandwidth                        | > 15 MHz                          |  |

| Onboard active load                     | Vin = 5 to 30 V; Gain = 500 mV/A  |  |

| Onboard circuit breaker                 | 12 A                              |  |

www.ti.com.cn System Overview

# 2 System Overview

# 2.1 Block Diagram

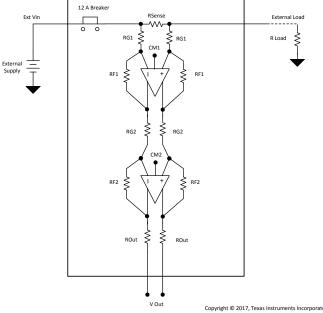

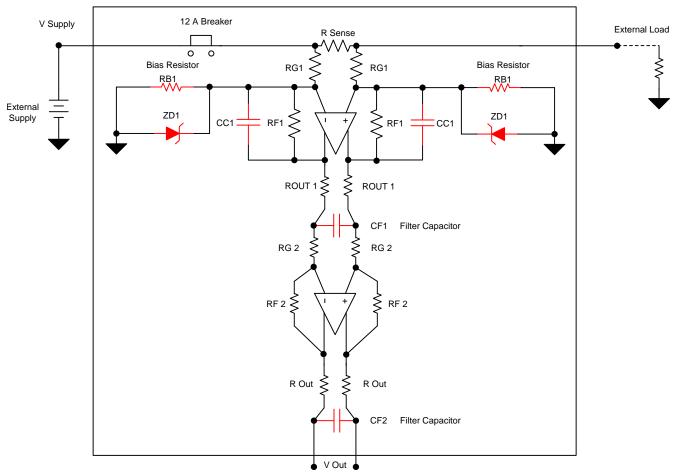

A block diagram of the system is shown in 🖺 1. The main portion of the design is two fully-differential amplifiers (FDAs). A circuit breaker and a precision reference are included on the reference design board. There is also a connector for an external load.

图 1. System Block Diagram

System Overview www.ti.com.cn

# 2.2 Design Considerations

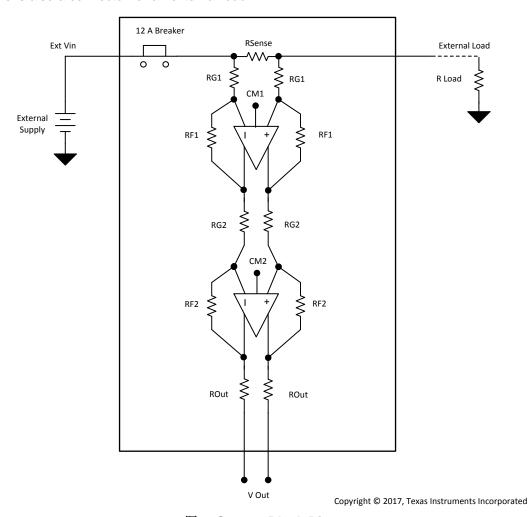

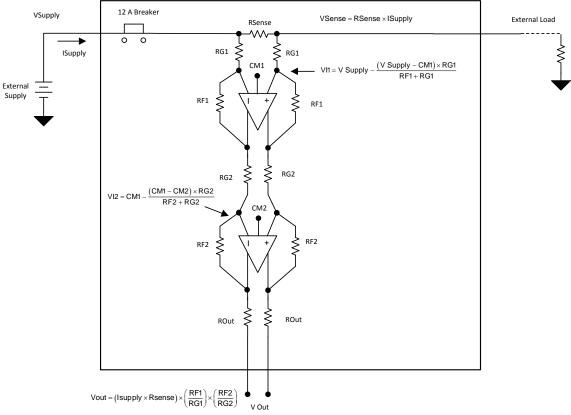

Voltage calculations at key points in the signal path are annotated in 🗵 2.

Copyright © 2017, Texas Instruments Incorporated

图 2. Detail of Common-Mode Voltages and Design Equations

www.ti.com.cn System Overview

#### 2.3 Highlighted Products

#### 2.3.1 THS4131

This TI Design features the THS4131 FDA. The THS4131 provides an excellent combination of wide supply range, high speed, and low noise, which makes it ideally suited for high-side, current-sense applications. The THS4131 has externally set gain with four resistors.

In addition to a wide supply-voltage range, the THS4131 also has a very wide input common-mode range. The input common-mode voltage can range from (V- + 1.0 V) to (V+ - 0.5 V). This wide input common-mode range allows flexibility for current sensing from the positive supply rail.

The common-mode rejection ratio (CMRR) provided by the fully-differential signal chain reduces any feed-through from the power supply regulator voltage fluctuations, which increases the power-supply rejection ratio (PSRR) of the current-sense circuit.

#### 2.3.2 REF5025AID

The REF5025 is a 2.5-V, low-noise, precision voltage reference. This reference is used to set the output common-mode voltage. The REF50xx series offers several voltage options if required for different ADC common modes.

#### 2.4 System Design Theory

The design of TIDA-00976 is a high-side, current-sensing circuit. In a high-side, current-sense system the sense resistor is between the power supply and the circuit. The primary advantage of a high-side, current-sense circuit is that the ground path is undisturbed. Many systems use ground connections to suppress noise and power-supply voltage transients, so the high-side, current-sense option is desirable. The primary drawback of high-side, current-sense circuits is that the supply voltage is now the common-mode voltage of the sense voltage generated on the sense resistor. This reference design uses a THS4131 FDA with an input common mode that can support supply voltages up to 30 V.

An FDA with wide bandwidth is the core of the signal path as shown in 2. In order to support the full supply range of 30 V while also driving a low-voltage ADC, there is a second FDA on the reference design board. If the external VSupply voltage is less than 7 V, the second amplifier may not be necessary. A detail of the common-mode voltages is shown in 2.

In addition to a wide supply-voltage range, the TIDA -00976 also offers a very high frequency response. Without filtering, the core design supports bandwidths up to 15 MHz. This frequency response can be tailored for the specific application with additional components.

System Overview www.ti.com.cn

# 2.4.1 Design Options

There are several options built into the TIDA-00976 reference design. These options are shown in 🗵 3, which help extend the voltage range and ensure stability of the final circuit.

The first option is the addition of pull-down resistors, which are labeled RB1. These resistors will reduce the amplifier input common-mode pin voltages and allow for an input voltage higher than 30 V to be applied to the external supply port.

To protect the amplifier inputs from voltage transients in a high-noise environment, placeholders for Zener diodes are provided as shown in 3. The reverse-bias rating on the diodes should be rated for at least the maximum supply voltage or 30 V. The addition of the reverse-biased Zener diode might present significant input capacitance that causes frequency-response peaking or instability. As a result, the capacitors CC1 can be used to reduce peaking of the frequency response. A good starting value for this component is 1 pF to 5 pF. A detailed description of stabilizing an amplifier by the addition of an input capacitance can be found in the *Op amp stability and input capacitance*[2].

In order to reduce sampled noise when using an ADC to measure the system output, the system bandwidth should not be significantly larger than the signal bandwidth. The TIDA-00976 has over 15 MHz of bandwidth. If the sampled signal has lower bandwidth, capacitors CF1 and CF2 can be used to reduce broadband noise.

Copyright © 2017, Texas Instruments Incorporated

图 3. Design Options Shown in Red

# 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Hardware

#### **CAUTION**

Caution hot surface. The PCB surface can get very hot while passing high currents. Contact may cause burns. Do not touch

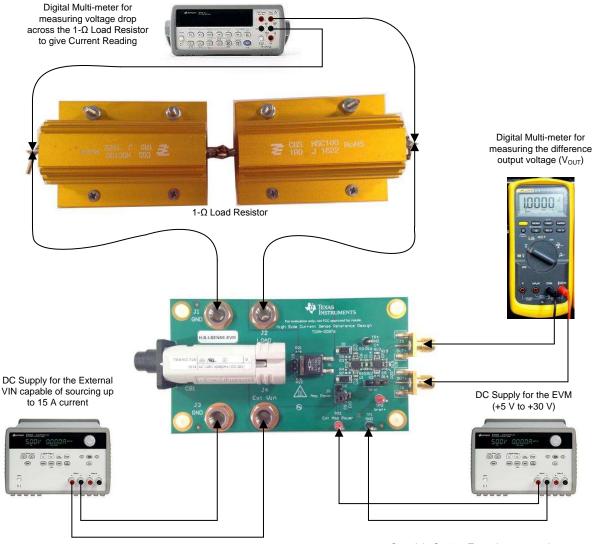

The performance of the TIDA-00976 was evaluated by simulation in TINA-TI as well as in the lab using an external load.

4 shows the hardware setup diagram for evaluating the reference design for converting a high-side input current to an output voltage.

Copyright © 2017, Texas Instruments Incorporated

图 4. Hardware Setup Diagram

# 3.1.1 Applying Power and Basic Setup

The TIDA-00976 has a supply voltage range of 5 to 30 V. The following steps detail the TIDA-00976 setup procedure for high-side input current to output voltage testing, as shown in

≰ 4.

#### 3.1.1.1 Board Power Supply Setup

The TIDA-00976 reference design supports a supply voltage range of 5 to 30 V.

- 1. With the supplies disconnected, set the voltage on the DC power supply (capable of souring 1-A current) between 5 to 30V. Also, set the current compliance limit to approximately 100 mA on the DC power supply.

- 2. Keeping the supplies turned OFF, connect the DC power supply to the EXT amp power connection (TP2) and GND (TP1) as shown in

4. Reference the 7 for test-point (TP) and jumper connections. Make sure the shorting block on jumper J8 is connected across pins 1 and 2.

- 3. Turn on the DC power supply connected to the external amp power connector. The supply current recorded on the power supply should be around 27 mA.

#### 3.1.1.2 Connecting the Digital Multimeter to Measure the Output Voltage

- 1. Connect the digital multimeter voltage port to OUT+ (J6) and COM port to OUT- (J5), as shown in 图 4.

- 2. Set the dial on the multimeter to DC voltage measurement mode. The multimeter measures the voltage difference across the outputs OUT+ and OUT-.

#### 3.1.1.3 Connecting the External High-Current Load and High-Current Testing

- 1. Connect a high-current,  $1-\Omega$  load resistor bank across the connectors J1 (GND) and J2 (LOAD). Ensure that the connector cable is rated for 15 A (14 gauge or larger). The voltage measurement across the  $1-\Omega$  load resistor bank is equivalent to the load current being measured.

- 2. Connect another digital multimeter voltage port across the 1- $\Omega$  load resistor bank to measure the voltage across it, as shown in  $\boxed{8}$  4.

- 3. With the supplies turned OFF, connect a high-current bench supply capable of sourcing 15-A current across connectors J4 (external Vin) and J3 (GND). Ensure that the connecting cable is rated for at least 15 A.

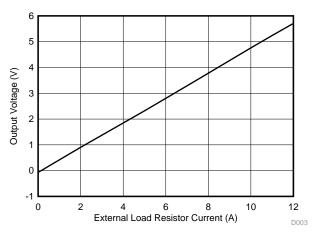

- 4. Turn on the DC power supply connected to the external Vin responsible for providing the input load current. 图 5 gives the relationship between the input load current and the output voltage measured across the outputs OUT+ and OUT-.

#### 3.1.2 Output Common-Mode Voltage Option

In order to support direct interfacing with an ADC, the TIDA-00976 reference design uses a precision reference (REF5025AID) to set the common-mode voltage of U2. This precision reference allows direct DC coupling with ADCs that require a 2.5-V input common-mode voltage. Options ranging from 2 to 10 V are available in the REF50xx family of precision voltage references.

In the event that another common-mode voltage is desired, move the shorting block on jumper J7 across pins 1 and 2. Connect the Vref+ test point to a bench supply and set the voltage to the desired common-mode voltage. The valid common-mode voltages range from 1 V to (Vs+ - 1 V) for the THS4131.

# 3.2 Testing and Results

# 3.2.1 High-Side Current Testing

$\ddagger$  3.1.1 details the setup procedure for high-side current testing.  $\boxtimes$  5 shows the linear relationship between the measured input load current and the output voltage across OUT+ and OUT- or  $V_{OUT} = (OUT+)$  - (OUT-).

图 5. Output Voltage Versus Load Current

#### 3.2.2 Frequency Response Testing

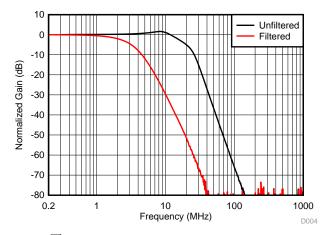

In order to measure the frequency response without having to source and sink a large current, a differential signal input can be inserted at jumper J9. Replace resistor R1 with a  $100-\Omega$  resistor and connect a differential voltage source across J9. The frequency response of the reference design can now be measured with standard  $100-\Omega$  differential test equipment. 8 6 shows the frequency responses of the two-stage current-sense circuit.

The filtered frequency response in the below graph includes the diode protection circuit at the input (ZD1) along with CC1 of 5pF (see 3). The protection diode used in the circuit is the SMAZ30-13-F with approximately 60 pF of reverse bias capacitance. Also, the CF1 and CF2 are set to 10 pF and 30 pF, respectively. The unfiltered frequency response test is performed by removing all the above mentioned components used for the filtered frequency response.

图 6. Measured Frequency Response

# 3.2.3 Common-Mode Voltage Versus Error Current

Due to the high voltages involved, it is important to calculate the power dissipated in the first stage feedback and gain-set resistors. Power dissipation for typical configurations is shown in  $\frac{1}{8}$  2. It is important to note that for a given voltage the resistor power will increase as the resistor value decreases. For this reason, there is a trade-off between selecting low resistor values to reduce noise compared with increased power dissipation. When using surface mount resistors, some typical resistor power ratings are shown in  $\frac{1}{8}$  3.

丰 2 Common Mode Voltage Versus Error Current

| 10 2. 0   |        | de Voltage | versus Error v | Current |

|-----------|--------|------------|----------------|---------|

| ADC INPUT | 014 00 | 0140 (10   | DC4 (O)        | :D04 (- |

| SUPPLY<br>VOLTAGE (V) | ADC INPUT<br>COMMON MODE (V) | CM1 (V) | CM2 (V) | RG1 (Ω) | iRG1 (mA) | pRG1 (mW) /<br>pRF1 (mW) |

|-----------------------|------------------------------|---------|---------|---------|-----------|--------------------------|

| 5                     | 2.5                          | 2.5     | 2.5     | 5k      | 0.17      | 0.14 / 0.29              |

| 7                     | 2.5                          | 3.5     | 2.5     | 5k      | 0.3       | 0.45 / 0.9               |

| 10                    | 2.5                          | 5       | 2.5     | 5k      | 0.33      | 0.54 / 1.1               |

| 15                    | 2.5                          | 7.5     | 2.5     | 5k      | 0.5       | 1.25 / 2.5               |

| 20                    | 2.5                          | 10      | 2.5     | 5k      | 0.67      | 2.24 / 4.49              |

| 30                    | 2.5                          | 15      | 2.5     | 5k      | 1         | 5 / 10                   |

# 表 3. Surface Mount Resistor Power Ratings (1)

| PACKAGE SIZE | POWER RATING (mW) |

|--------------|-------------------|

| 0603         | 125               |

| 0402         | 63                |

| 0201         | 50                |

<sup>(1)</sup> Vishay®

#### 3.2.4 Signal Gain Calculation

The current-to-voltage signal gain calculation as well as the common-mode voltage at various nodes in the circuit are shown in  $\ 2$ . The individual stage gain is mainly set by the ratio of feedback resistor (RF) and gain-setting resistor (RG). In actual application, the second FDA output interfaces to a low-voltage ADC. As a result, the maximum input voltage swing of the ADC usually sets the maximum signal current that is measured for a given sense resistor and overall gain configuration.  $\ 2$  shows the maximum signal current that can be measured for 3  $V_{PP}$  maximum input at the ADC for the different sense resistor and gain configurations.

表 4. Signal Gain (V/A)

| SENSE RESISTOR ( $\Omega$ ) | STAGE 1<br>GAIN (V/V) | STAGE 2<br>GAIN (V/V) | OVERALL GAIN<br>(mV/A) | SUPPLY DROOP<br>(mV/A) | MAX. CURRENT (A)<br>at 3 V <sub>PP</sub> |

|-----------------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------------------------|

| 0.100                       | 2                     | 2                     | 400                    | 100                    | 7.5                                      |

| 0.050                       | 2                     | 5                     | 500                    | 50                     | 6                                        |

| 0.010                       | 2                     | 5                     | 100                    | 10                     | 30                                       |

| 0.010                       | 4                     | 4                     | 160                    | 10                     | 19                                       |

#### 3.2.5 Noise and Offset Errors

The primary offset error and noise terms are shown in  $\frac{1}{8}$  5 and  $\frac{1}{8}$  6, respectively. While the offset voltage and offset currents are the largest terms, they are also systematic and can be calibrated out from the final measurements. It is the noise terms that cannot be calibrated out due to the randomness associated with the noise. For high-side current-sense applications, the input gain-setting resistor (RG) must be high in order to minimize error currents while applying high-input voltages as discussed in  $\frac{1}{12}$  3.2.3. As a result, the large gain (RG) and feedback resistors (RF) have noise that is significantly more than the amplifier noise. An RG of 5 k $\Omega$  has a thermal noise of 9 nV/ $\sqrt{Hz}$ , while the amplifier input-noise voltage is 1.3 nV/ $\sqrt{Hz}$ . A detailed description of calculating noise in a fully-differential amplifier can be found in the *Analysis of fully differential amplifiers*[3].

#### 表 5. Input Referred Offset Error Terms

| PARAMETER                                                                  | V <sub>os</sub> | I <sub>os</sub> |

|----------------------------------------------------------------------------|-----------------|-----------------|

| Value                                                                      | 0.2 mV          | 100 nA          |

| Error magnitude with Rg = $5k\Omega$ , A <sub>V</sub> = 2 V/V BW = $20MHz$ | 0.4 mV          | 0.33 mV         |

#### 表 6. Input Referred Noise Error Terms

| PARAMETER                                                                                      | V <sub>N</sub> | I <sub>N</sub> | RG_Noise (1) |

|------------------------------------------------------------------------------------------------|----------------|----------------|--------------|

| Value                                                                                          | 1.3 nV/√Hz     | 1 pA/√Hz       | 5 kΩ         |

| Error magnitude with Rg = $5k\Omega$ , A <sub>V</sub> = $2 \text{ V/V}$<br>BW = $20\text{MHz}$ | 5.8 uV RMS     | 22 uV RMS      | 40.5 uV RMS  |

<sup>(1)</sup> Thermal Noise = √4kTRG

Copyright © 2017, Texas Instruments Incorporated

Design Files www.ti.com.cn

# 4 Design Files

# 4.1 Schematics

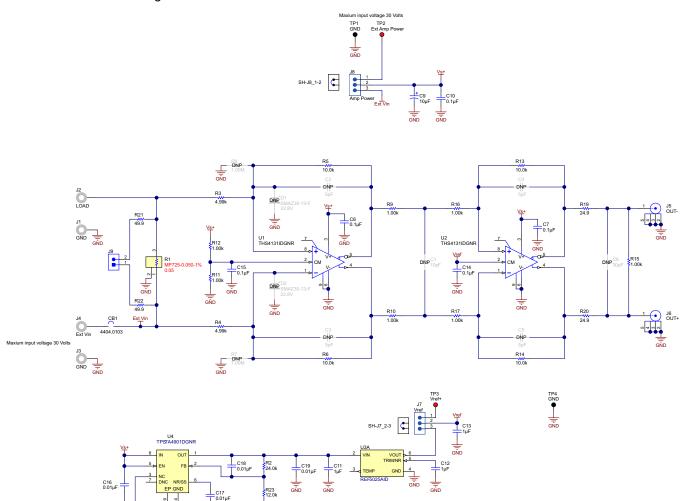

To download the schematics, see the design files at TIDA-00976. ☒ 7 shows the schematic diagram for the reference design.

图 7. Schematic Diagram

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00976.

# 4.3 PCB Layout Recommendations

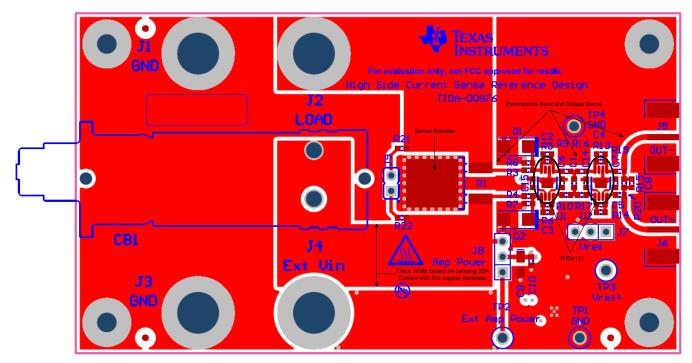

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-00976.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-00976.

www.ti.com.cn Design Files

# 4.5 Layout Guidelines

For layout guidelines related to the THS4131, refer the layout section in the THS413x High-Speed, Low-Noise, Fully-Differential I/O Amplifiers[1].

图 8. Example Layout (Top Layer)

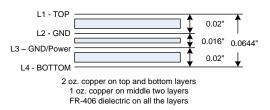

图 9. Layer Stackup

#### 4.6 Gerber Files

To download the Gerber files, see the design files at TIDA-00976.

# 4.7 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00976.

Related Documentation www.ti.com.cn

#### 5 **Related Documentation**

- 1. Texas Instruments, THS413x High-Speed, Low-Noise, Fully-Differential I/O Amplifiers, THS4130 and THS4131 Datasheet (SLOS318)

- 2. Texas Instruments, Op amp stability and input capacitance, Technical Brief (SLYT087)

- 3. Texas Instruments, Analysis of fully differential amplifiers, Technical Brief (SLYT157)

- 4. Vishay Corporation, Vishay Resistors

#### 5.1 商标

TINA-TI is a trademark of Texas Instruments, Inc.. Vishay is a registered trademark of Vishay Intertechnology, Inc.. All other trademarks are the property of their respective owners.

#### 6 **About the Author**

LOREN SIEBERT is an applications engineer with TI in the High-Speed Amplifier division in Fort Collins, Colorado. He supports applications ranging from 4G and 5G radio base stations to precision, highaccuracy ADC drivers.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司