# TI Designs

# 采用 PRU-ICSS 的简单开放实时以太网 (SORTE) 主系统参考设计

# TEXAS INSTRUMENTS

#### 说明

TIDEP-0085 设计实现了包含可编程实时单元和工业通信子系统 (PRU-ICSS) 的简单开放实时以太网 (SORTE) 主系统。借助 SORTE 协议,客户 应用 能够在 4μs 周期时间内在主系统和器件之间交换处理数据。客户可以通过源代码中的 PRU 固件提供差异化的产品。

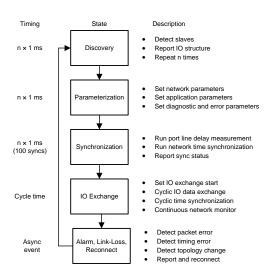

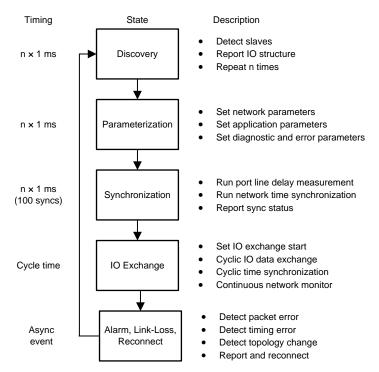

SORTE 协议包括器件发现、参数化、PHY 和电缆延迟测量、同步和处理数据交换。

#### 资源

TIDEP-0085设计文件夹AM3359产品文件夹TLK110产品文件夹DP83822I产品文件夹TMDSICE359工具文件夹

咨询我们的 E2E 专家

#### 特性

- SORTE 主系统参考实现

- 在一个网络中支持多达 254 个器件

- 支持在 4μs 周期时间内交换处理数据

- 在源代码中提供 PRU 固件

- 可完全自定义的 PRU 固件

#### 应用

- 工业以太网

- 伺服驱动器和运动控制

- 可编程逻辑控制器 (PLC)

- 工业通信模块

- 工业输入/输出 (IO) 模块

- 工业传感器和执行器

- 步进驱动器

- 芯片间通信接口

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

## 1 System Description

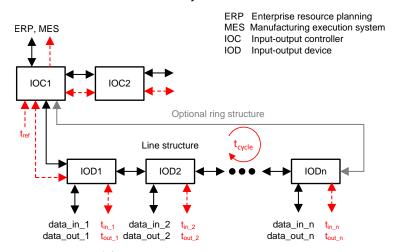

Production systems are organized in various levels to manage the production process. Optimization of the production process is only possible with a fully transparent and timely accurate view of the IO functions. Compared to consumer and office equipment, industrial communication must be deterministic and safe. There is cyclic exchange of IO data between devices on the field level of a manufacturing floor and the controller, which manages multiple IO devices organized in line or ring structure. Multiple IO controller (IOC) can be connected at the control level to exchange data between various machines or between machines and automation components, such as robots, conveyor belts, and tool magazines. Communication to office level bridges between the operational technology and the information technology (IT). This bridge function requires security for authentication and data while still maintaining the timing context of IO operation.

§ 1 shows an overview of an industrial control system.

图 1. Industrial Control System

IO communication over industrial Ethernet is repeated with a preconfigured cycle time. There are different classes of cycle times in a production system ranging from 31.25  $\mu$ s for motion control applications to more than 10 ms for a complete manufacturing site. Based on the communication cycle time ( $t_{cycle}$ ), the IOC sends new data packets to IO devices (IOD). The IOC serves as a timing master with a local time reference (tref). The IOD synchronizes to the master time reference and all IODs in the network have same understanding of time. The time synchronization inside an IO communication network allows giving all input and output data at each node a reference time. For example IOD2 data\_in2 is captured at a preconfigured time  $t_{in_2}$ . Same behavior for the output data, which is triggered with time  $t_{out_2}$ . The time synchronized control of input and output data over a network of many IO devices serves as a basis for PLCs and multi-axis motion controllers, which are used in machine tools and robotics applications.

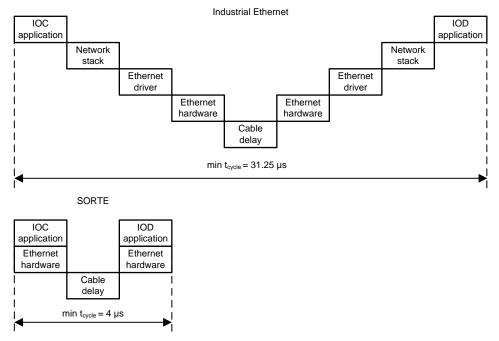

There are more than 30 known industrial Ethernet standards driven from leading companies of the industrial automation market. The scope of these standards covers not just the physical layer and data link layer but also higher network layers and the interface to the application which programs the IO data over the network. Overall cycle time of the control loop is the sum of various hardware and software processing steps. For networks with more than one device the forwarding delay up to the last device must be considered.

www.ti.com.cn System Description

Some the comparison of industrial Ethernet with processing steps in software on a host controller compared to SORTE using PRU-ICSS.

图 2. Cycle Time Optimization Through Processing Enhancements

PRU-ICSS is the programmable real-time core with real-time Ethernet peripheral, which allows combining application, networking, and Ethernet processing into a single-processing step. There are no additional variations in the signal chain to transfer data over interconnects, cache memories, and application CPU. The timing model in \( \begin{aligned} \text{2} is a simplified view for a single device connection. When calculating the minimum cycle time, the number of IODs connected in the network must be considered. For each device there is an additional adder for cable delay and bridge delay in the Ethernet hardware.

Ethernet packets according to IEEE802.3 standard follow a defined frame structure and packet timing, which works for the internet at a worldwide level. Addressing scheme with 6 bytes for source address, 6 bytes of destination address, and additional network separation through virtual local area networks (VLANs) connect trillions of Internet protocol (IP) devices to a single network. In the case of controlling IODs with a single controller, the number of devices in the network can be scoped to 16 bit for a manufacturing site and 8 bit (256 devices) for a single control unit.

The scope of the SORTE protocol is to address single control unit networks, which spans no more than 8 bits of address. Another limit of standard Ethernet is the minimum frame length of 64 bytes. In many cases the size of IO data per control cycle is much smaller than 64 bytes. The minimum frame size of the SORTE protocol is 4 bytes.

System Description www.ti.com.cn

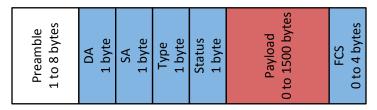

3 shows the size-optimized frame structure. First optimization is before a packets starts with a shortened pre-amble. The pre-amble can be shortened to 1 byte as the physical layer no longer requires a long pre-amble for synchronization

图 3. SORTE Frame Structure

DA: Destination address, 0 = master, 1..254 slaves, 255 = broadcast

SA: Source address, 0 = master, 1..254 slaves

Type: DISCOV\_MC, PARAM\_MC, SYNC\_MC, LD\_REQ\_P2P, LD RESP\_P2P,

OUT\_MC, IN\_UC, ALARM\_UC, DIAG\_UC, RECON\_UC

Status: Bit 0: 0 = continuous, 1 = last

Bit 1: 0 = pending, 1 = done

Bit 2: 0 = no\_error, 1 = error

Bit 3: 0 = no state change, 1 = state change in next cycle

Bit 4-7: master and slave states

M\_DISC (0)

M\_PARAM (1)

M\_SYNC (2)

M IO EXCHANGE (3)

S\_ALARM (4)

**S\_DIAG** (5)

S\_RECON (6)

S\_RESET (7)

The gap between two packets is defined to 12 bytes by IEEE standard. Ethernet PHY can support less than 3 bytes of gap between two packets. The frame check sum (FCS) at the end of the packet is fixed to CRC32 (4 bytes) by the reference. SORTE allows for dynamic selection of error detection or even error correction codes. For the first implementation, a CRC8 polynomial is selected. Standard Ethernet expects the frame size within the range of 64 to 1518 bytes. SORTE protocol and Ethernet PHY support minimum-sized packets and have no upper bounds.

表 1 shows the comparison of frame parameters between IEEE802.3 Ethernet, SORTE protocol, and industrial Ethernet physical layer device DP83822I.

#### 表 1. Ethernet Frame Parameter

| PARAMETER      | IEEE802.3 100Mb | SORTE        | DP83822I PHY |

|----------------|-----------------|--------------|--------------|

| InterPacketGap | 960 ns          | 260 ns       | <200 ns      |

| Preamble + SFD | 8 bytes         | 1 to 8 bytes | 1 byte       |

| FCS            | CRC32 (4 bytes) | 0 to 4 bytes | _            |

| SA, DA         | 6 + 6 bytes     | 1 + 1 bytes  | _            |

| MinFrameSize   | 64 bytes        | 4 bytes      | 1 byte       |

| MaxFrameSize   | 1518 bytes      | Endless      | Endless      |

www.ti.com.cn System Description

The SORTE protocol enhancements compared to standard Ethernet are grouped into:

- Optimization of processing steps between application layer and Ethernet hardware

- Optimization of frame format, frame pre-amble, and interframe gap

- Optimization of frame processing for two-port Ethernet hardware

- · Dynamic change of frame parameters and processing based on protocol states

1.1 节 describes the key features of PRU-ICSS hardware, which supports all four optimizations previously listed.

## 1.1 Key System Specifications

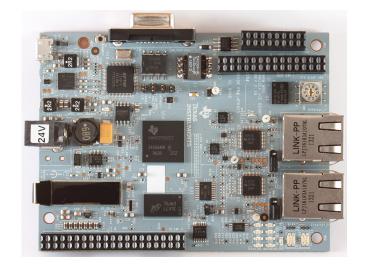

Texas Instruments has a family of ARM®-based processor with integrated industrial communication peripheral also referred as PRU-ICSS. The entry level device is AM335x processor with one instance of PRU-ICSS. Processor families like AM437x and AM57xx have two instances of the flexible real-time Ethernet peripheral. This design describes the implementation of SORTE protocol based on AM3359 device on the industrial communication engine (ICE).

Complete documentation of the processor, ICE board, and PRU\_ICSS can be found with following links:

- AM3359 Technical Documents Product Folder

- AM335x Sitara™ Processors Datasheet[3]

- AM335x and AMIC110 Sitara Processors Technical Reference Manual[4]

- AM3359 ICE Tool Folder

- PRU-ICSS Wiki Page

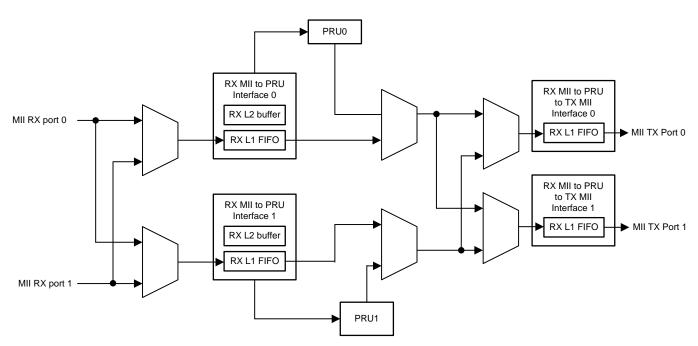

The PRU register file serves different operating modes, which are configured through CPCFG0[PRU0\_GPI\_MODE] register. Setting this bit field to three configures MII\_RT mode. Other modes are direct input, 16-bit parallel capture, and 28-bit shift mode. In Ethernet mode the MII RX ports can go to either PRU or directly from RX L1 FIFO to one or both MII TX ports. This flexible configuration of port assignment, PRU assignment, and RX FIFO modes supports many real-time Ethernet functions.

System Description www.ti.com.cn

图 4. Ethernet Port Configuration

A shows the multiplexing options in MII\_RT mode. MII RX port 0 can feed its data into either interface, which is dedicated to PRU0 and PRU1. Only one RX port can be mapped to one interface at a time. In auto-forwarding mode the data from RX port goes to RX L1 FIFO and then directly to the configured MII TX port. In addition, PRU can receive Ethernet frame through RX L1 FIFO, which is typically used for *on-the-fly* processing, or RX L2 FIFO, which is used for cut-through processing.

For Ethernet MAC mode with one PRU same, RX and TX port numbers are mapped. The various Ethernet packet processing modes are described in Section 4.4.6 MII\_RT of the *AM335x and AMIC110 Sitara Processors Technical Reference Manual*[4].

For real-time Ethernet the time to transfer packets and process packets are key performance parameter. With the programmable approach there is still the requirement of minimum latency and low jitter. The RX\_L1 interface is used for on-the-fly processing of Ethernet packets. In this mode PRU reads the data and status through register R31 and writes data through register R30 and R31. The frame data does not leave the PRU core which enables minimum latency. To remove any PRU firmware jitter between MII receive time and MII transmit time, the forwarding time is controlled using a hardware timer. TX\_START\_DELAY bit field in TXCFG0 and TXCFG1 registers configures this forwarding time in the range of 0 to 5 µs in 40-ns increments.

Real-time Ethernet, which is switch-based, that is conditional forwarding of packets based on address information, requires a more complex data flow model, which includes memory transfer to and from data memory. There are two different modes for switch-based packet processing. For industrial field bus type of applications, the benefit of low latency supports a larger network (> 7 hops) in ring or line structure. Low latency can only be accomplished with cut-through processing of Ethernet packets. The switching decision time for cut-through is always after the address information at the beginning of the packet and, therefore, constant – typically  $< 3 \mu s$ . In store and forward mode, the switching time varies a lot as large packets cause a delay of 120  $\mu s$  per switch, whereas small packets can be forwarded in less than 7  $\mu s$ .

www.ti.com.cn System Description

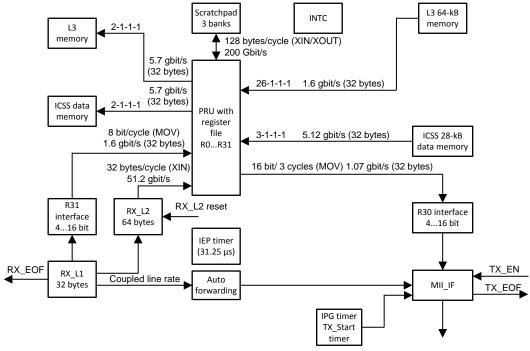

§ 5 shows the data flow model with respective timing parameters to transfer Ethernet frames in PRU-ICSS system. PRU can use three different instructions to move data:

- Broadside move instructions XIN and XOUT (51.2 Gbit/s for 32 bytes)

- Burst data commands LBCO and SBCO (5.12 Gbit/s read and 5.7 Gbit/s write for 32 bytes)

- MOV instruction for RX\_L1 and TX\_L1 (1.6 Gbit/s rad and 1.07 Gbit/s write for 32 bytes)

Switch-based processing without 100% time division multiplexing of packets, that is engineered traffic, can run into port collision situations. For example, the local interface starts to transmit a large packet on port 1. Shortly after the start of transmission on port 1, another frame is received on port 0, which must get send out to port 1 as well. This is a collision case that requires the PRU to buffer incoming frames from port 0 for up to 1500 bytes and 24 small-sized packets. This buffer or collision queue no longer fits into PRU register bank or additional scratch pad register banks, which can be reached through broadside instructions XIN and XOUT with highest throughput. The local data memory inside PRU-ICSS can be used for collision packets. For more complex switching architectures (IEEE 802.1Q learning bridge) with up to eight queues per physical port, the memory model can be extended using L3 memory of the Sitara processor. The read latency of the first 32-bit word from L3 memory especially comes at a high cost. The 32-byte block read from L3 memory runs with 1.6 Gbit/s data rate.

Another timing parameter of switched Ethernet transfers is the gap between two packets also called interpacket gap (IPG). To ensure minimum IPG time on a transmit port a hardware timer enforces the gap time based on previous packets. This hardware timer can be programmed to support different setting of IPG. In addition PRU shall support minimum gap time between packets and for this PRU requires real-time view of packet start and end time. Start of frame (SOF) and end of frame (EOF) for both receive and transmit port are important real-time triggers, which PRU can react on using event mapping in interrupt controller (INTC).

图 5. PRU Ethernet Switch Data Flow - One Slice

System Description www.ti.com.cn

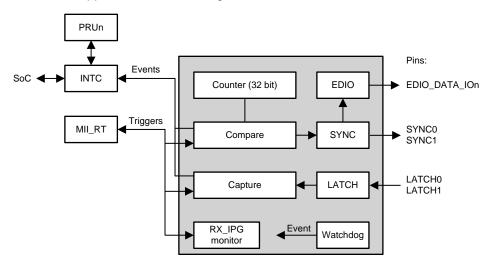

Real-time control of Ethernet packets requires the connection of a timer module with MII\_RT interface triggers.

5 shows the integration of a tunable counter with multiple capture and compare units, external hardware synchronization pins (SYNC, LATCH), low-latency IO (EDIO) pins, watchdog, and monitor of IPG time.

## 2 System Overview

## 2.1 Block Diagram

图 6. Block Diagram

## 2.2 Design Considerations

## 2.2.1 Industrial Ethernet Peripheral

The industrial Ethernet peripheral (IEP) hardware is clocked with either a dedicated iep\_clk or same clock as PRU. Switching from iep\_clk to ocp\_clk is done by writing 1 to the IEPCLK.OCP\_EN bit. IEP clock can also be stopped through CGR.IEP\_CLK\_EN bit. The asynchronous clock option of IEP timer comes at an overhead of additional wait states to read from IEP register space. PRU read commands with LBCO instructions take 12 PRU cycles versus three cycles reading other PRU-ICSS register and memory.

For real-time Ethernet, incoming and outgoing packets generate capture events to take time stamps with reference to MII\_RT. These time stamps can be used to synchronize time in a network through line delay measurement and bridge delay measurement of Synchronization packets. The compare units generate events to time trigger outgoing packets, send interrupt to PRU through INTC, and send event to SYNC hardware for external signaling. EDIO function is typically not time triggered but PRU firmware triggered. The watchdog timer module can be used to make sure PRU is operational or ARM is operational. The event is than either mapped to PRU event register or ARM INTC.

图 7. Industrial Ethernet Peripheral (IEP)

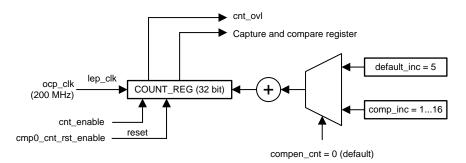

The counter in IEP block, also referred as IEP timer, can be rate compensated and offset adjusted. Default increment of the counter is with every IEP hardware clock. 8 shows the IEP timer. The 32-bit COUNTER\_REG is clocked with 200 MHz when cnt\_enable bit is set in IEP\_TMR\_GLB\_CFG register. A wrap-around of the 32-bit counter at 200 MHz occurs every 4.2 seconds also indicated by cnt\_ovl status bit. Alternative mode for wrap-around is using compare 0 register through cmp0\_cnt\_rst\_enable bit. For rate compensation the increment of the counter is varied from the default value of five. The alternative increment can be pre-programmed between 1 and 16 ns. The number of IEP updates with alternative increment is set by compen\_cnt bit field in IEP\_TMR\_COMPEN register. The compare unit and capture unit use the COUNTER\_REG for event generation.

图 8. IEP Timer With Rate Compensation

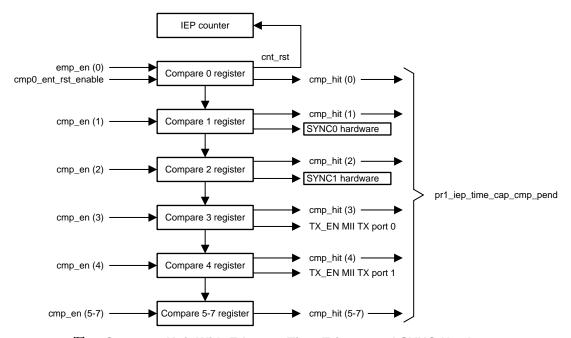

№ 9 shows the IEP compare unit with eight compare registers. Each compare register has separate a enable bit. Compare 0 register can be used to reset the IEP counter. For real-time Ethernet application, the compare 0 value can be set to the communication cycle time, for example 250-µs cycle time. In comparison to the IEP counter, the compare register is greater or equal. For example, if counter value is at 200 and IEP compare register is programmed to 150, there will be an immediate hit. A compare register can also be reprogrammed within the same cycle. For example if the counter is at 200, the compare register triggered before at 150 and is re-programmed to 250. Before a new compare hit event is generated, the new hit must be cleared from the previous hit.

图 9. Compare Unit With Ethernet Time Trigger and SYNC Hardware

Compare registers 1 to 4 have additional hardware triggers for:

- External SYNC0 signal (compare 1)

- External SYNC1 signal (compare 2)

- Enable packet transfer on MII TX port 0 (compare 3)

- Enable packet transfer on MII TX port 1 (compare 4)

Compare 3 and compare 4 register can be used to schedule packets on MII TX ports 0 and 1 with 5-ns resolution. Additional jitter between internal MII\_RT hardware and external Ethernet PHY can be removed by running both devices from the same clock source. Compare register 5 through 7 are general purpose with no direct hardware function. These registers generate a compare hit (cmp\_hit) event, which can be read and cleared through CMP\_STATUS\_REG register. All events out of compare registers are combined to a single event into the INTC. The interrupts controller supports event generation to both PRU cores or other masters in the system like ARM CPU and enhanced direct memory access (EDMA). The PRU first must find out which compare or capture event occurred. The read latency to access IEP register takes 12 cycles. IEP timer event driven EDMA transfer of IEP register space into PRU-ICSS data memory can reduce this latency to three cycles. The chaining capability of EDMA would also allow to clear the flags after they are transferred into memory.

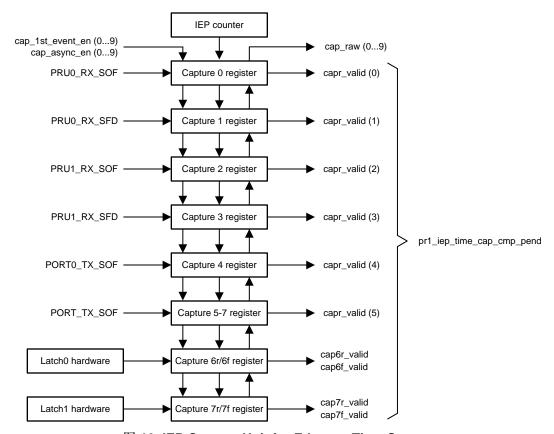

The IEP capture unit takes time stamps when packets are transferred over MII interface or external signal connected to LATCH 0 and LATCH1 pin have a positive or negative edge.

10 shows the block diagram of the capture unit. The value captured through external events is taken from CONTER\_REG at the time the event occurs. As external events may not be synchronized with internals iep\_clk a double flop synchronization with the iep\_clk is enabled by default configuration of cap\_async\_en[0..9] configuration bits. The capture mechanism supports two modes controlled with cap\_1st\_event\_en[0..9] bits. When this control bit is set for a certain capture register, the captured time value will be kept even if there are more events happening. Only by reading the capture register will enable a new time capture. In continuous mode the time is captured with every event.

CAPTURE0-5 registers are dedicated to packet boundaries on receive and transmit over MII\_RT interface. Receiving a packet on one port has two options for time stamps. One is start of frame (RX\_SOF) indicated by RX\_DV signal going active on MII\_RT interface. The second option is after the MII\_RT interface detected sync frame delimiter (RX\_SFD) data pattern, which is typically the last data nibble of the preamble. For transmit the time stamp is taken when MII\_RT interface starts sending a packet indicated through TX\_EN signal.

图 10. IEP Capture Unit for Ethernet Time Stamps

Detailed information about LATCH, SYNC, watchdog, and EDIO can be find in the *AM335x and AMIC110* Sitara Processors Technical Reference Manual [4].

## 2.2.2 MII\_RT Interface

MII\_RT interface has additional features to support real-time Ethernet compared to standard MII interface and Ethernet media access layer (MAC). The full documentation of the interface can be found in Section 4.4.6 of the *AM335x and AMIC110 Sitara Processors Technical Reference Manual*[4]. This chapter summarizes the key features of MII\_RT for real-time processing of Ethernet packets.

The interface has 16 memory mapped configuration registers.

Registers RXCFG0 and RXCFG1 configure the receive port functions:

- · Enable or disable receive traffic

- Cut pre-amble or provide all data to PRU register

- Select MII RX data from port 0 or 1

- Enable RX\_L2 buffer (broadside) instead of RX\_L1 (16-bit register)

- · Define the byte order into receive fifos

- Enable or disable auto-forward of received pre-amble

Register TXCFG0 and TXCFG1 configures the transmit port functions:

- Enable or disable TX port

- Automatically insert pre-amble by TX FIFO and not by PRU

- Enable transmit self-clear on TX\_EOF event

- Byte order in R30 register interface to TX L1 FIFO

- Set MII TX port for PRU

- One PRU can send same packet to both ports

- Select transmit auto sequence which takes the data directly from RX L1 FIFO

- Set delay between received packet and transmit in the range of 80 ns up to 5 μs. Configure TX\_EN and TX\_DV setup time signal from TX\_CLK.

Registers TXCRC0 and TXCRC1 allow PRU to read back CRC32 for diagnostics.

Registers TXIPG0 and TXIPG1 configure the minimum time for IPG

Registers PRS0 and PRS1 provide current state of MII CRS and COL signals. If not used for half duplex, these pins could be used as digital inputs with low-read latency compared to system GPIOs.

Registers RXFRMS0 and RXFRMS1 configure minimum and maximum frame size to trigger RX\_MIN or MAX\_FRM\_ERR. These are 16-bit values, which support frame length outside IEEE 802.3 definitions.

Registers RXPCNT0 and RXPCNT1 configure minimum and maximum number of nibbles before SFD to trigger RX\_MIN or MAX\_PRE\_COUNT\_ERR.

Registers RXERR0 and RXERR1 indicate errors for frame size and pre-amble size.

PRU\_ICSS can reprogram the MII\_RT interface for every packet. Some of the configurations are only allowed with disabled receive or transmit mode or only during IPG time. In order to simplify MII\_RT interface configuration, 表 2 summarizes the settings for different packet processing mode.

# 表 2. MII\_RT Configurations

|        | MII CONFIGURATION | CUT-THROUGH<br>(CT) | AUTO-FORWARD<br>(AF) | DELAY MASTER<br>(DM) | DELAY SLAVE<br>(DS) | HOST RECEIVE<br>(HR) | HOST SEND<br>(HS) | TIME<br>TRIGGERED<br>SEND<br>(TSS) | PEER TO PEER<br>(P2P) |

|--------|-------------------|---------------------|----------------------|----------------------|---------------------|----------------------|-------------------|------------------------------------|-----------------------|

|        | RX_ENABLE         | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

|        | Reserved          | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

|        | RX_CUT_PREAMBLE   | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

| RXCFG0 | RX_MUX_SELECT     | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

| KACFGU | RX_L2_ENABLE      | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

|        | RX_BYTE_SWAP      | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

|        | RX_AUT_FWD_PRE    | 1                   | 1                    | 0                    | 1                   | 0                    | _                 | _                                  | 1                     |

|        | Bit 731 Reserved  | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

|        | RX_ENABLE         | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

|        | Reserved          | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

|        | RX_CUT_PREAMBLE   | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

| RXCFG1 | RX_MUX_SELECT     | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

| KACFGI | RX_L2_ENABLE      | 1                   | 1                    | 1                    | 1                   | 1                    | _                 | _                                  | 1                     |

|        | RX_BYTE_SWAP      | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

|        | RX_AUT_FWD_PRE    | 1                   | 1                    | 0                    | 1                   | 0                    | _                 | _                                  | 1                     |

|        | Bit 731 Reserved  | 0                   | 0                    | 0                    | 0                   | 0                    | _                 | _                                  | 0                     |

|        | TX_ENABLE         | 1                   | 1                    | 1                    | 1                   | _                    | 1                 | 1                                  | 1                     |

|        | TX_AUTO_PREAMBLE  | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

|        | TX_EN_MODE        | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 1                                  | 0                     |

|        | TX_BYTE_SWAP      | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

| TXCFG0 | Reserved bit 74   | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

| IXCFG0 | TX_MUX_SEL        | 1                   | 1                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

|        | TX_AUTO_SEQUENCE  | 0                   | 1                    | 0                    | 1                   | _                    | 0                 | 0                                  | 0                     |

|        | Reserved          | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

|        | TX_START_DELAY    | 0x40 (320 ns)       | 0x40 (320 ns)        | 0x40 (320 ns)        | 0x40 (320 ns)       | _                    | Default           | Default                            | 0x40 (320 ns)         |

|        | TX_CLOCK_DELAY    | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

# 表 2. MII\_RT Configurations (continued)

|        | MII CONFIGURATION | CUT-THROUGH<br>(CT) | AUTO-FORWARD<br>(AF) | DELAY MASTER<br>(DM) | DELAY SLAVE<br>(DS) | HOST RECEIVE<br>(HR) | HOST SEND<br>(HS) | TIME<br>TRIGGERED<br>SEND<br>(TSS) | PEER TO PEER<br>(P2P) |

|--------|-------------------|---------------------|----------------------|----------------------|---------------------|----------------------|-------------------|------------------------------------|-----------------------|

|        | TX_ENABLE         | 1                   | 1                    | 1                    | 1                   | _                    | 1                 | 1                                  | 1                     |

|        | TX_AUTO_PREAMBLE  | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

|        | TX_EN_MODE        | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 1                                  | 0                     |

|        | TX_BYTE_SWAP      | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

| TXCFG1 | Reserved bit 74   | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

| IXCFGI | TX_MUX_SEL        | 0                   | 0                    | 1                    | 1                   | _                    | 1                 | 1                                  | 1                     |

|        | TX_AUTO_SEQUENCE  | 0                   | 1                    | 0                    | 1                   | _                    | 0                 | 0                                  | 0                     |

|        | Reserved          | 0                   | 0                    | 0                    | 0                   | _                    | 0                 | 0                                  | 0                     |

|        | TX_START_DELAY    | 0x40 (320 ns)       | 0x40 (320 ns)        | 0x40 (320 ns)        | 0x40 (320 ns)       | _                    | Default           | Default                            | 0x40 (320 ns)         |

|        | TX_CLOCK_DELAY    | 6                   | 6                    | 6                    | 6                   | 6                    | 6                 | 6                                  | 6                     |

|        |                   |                     |                      |                      |                     |                      |                   |                                    |                       |

|        | RXCFG0            | 0x55                | 0x55                 | 0x15                 | 0x55                | 0x15                 | _                 | _                                  | 0x55                  |

|        | RXCFG1            | 0x5d                | 0x5d                 | 0x1d                 | 0x5d                | 0x1d                 | _                 | _                                  | 0x5d                  |

|        | TXCFG0            | 0x60400101          | 0x60400301           | 0x60400001           | 0x60400201          | _                    | 0x60400001        | 0x60400005                         | 0x60400001            |

|        | TXCFG1            | 0x60400001          | 0x60400201           | 0x60400101           | 0x60400301          | _                    | 0x60400101        | 0x60400105                         | 0x60400101            |

## 2.2.3 System Design

The SORTE protocol uses programmable approach to real-time communication for IO networks with a maximum of 254 devices. This protocol is fully documented and released in source code. The protocol is open to customers to learn, adapt, and enhance the protocol for their application requirements. SORTE is not bound to a given communication standard and breaks some of the limits of existing standards, such as minimum Ethernet frame size, addressing, and error detection. The primary use case of the protocol is to connect different end-equipment using Ethernet physical layer devices and 100-Mbit Ethernet cable.

In applications such as PLC backplane and modular drives, the protocol can be used to communicate inside the end-equipment using serial communication interfaces at different speeds. The protocol can be enhanced in future to support:

- · Different data rates up to Gb

- LVDS physical layer with additional error correction code

- · Non real-time channel for standard Ethernet traffic

- Chip-to-chip interface with external master port

The version 1.0 of the protocol describes the 100-Mbit Ethernet physical layer configuration supported by TI Sitara processor families – AM335x, AM437x, AM57xx, and 66AK2G. These processors have PRU-ICSS peripheral integrated. The PRU-ICSS firmware handles the networking layers of the protocol to maximize bandwidth of the host CPU to generate and consume IO data.

#### 2.2.3.1 Packet Format

SORTE uses an optimized packet format to minimize processing delay and forwarding delay in the network. There are two different modes a received packet is forwarded. Packets which are not modified by a device are forwarded using auto-forward hardware in PRU-ICSS. In this mode the PRU can still read the content of the packet and extract input data or verify content of a packet. In the second mode, incoming packet is stored in receive FIFO; PRU modifies the packet and sends it to the transmit FIFO. The time when content of transmit FIFO is sent to the wire is determined by either PRU or auto-forward timer. The auto-forward timer can be programmed in a wide range from few ns up to 5 µs in steps of 5 ns.

☒ 3 shows the common format for all packet types. Addressing of source and destination is limited to one byte, that is 254 device network with one master. Value 255 in DA is reserved for broadcast message. Type field describes the packet type, which is unique for various states of the protocol. There are in total nine different packet types defined. Status field gives status information of current operation and state in which the master and device are currently operating in.

Payload field can be empty for some packet types or go for maximum length of 1500 bytes. The hardware supports packets larger than 1500 bytes and extending the maximum size to larger packets can be defined. There is the standard FCS from Ethernet, which uses 32-bit CRC code. For shorter packets this checksum can be configured to be CRC8 or CRC16. For minimum packet size and more granular error detection, the RX\_ERR signal from Ethernet interface can be used instead of FCS. The IPG for 100-Mbit Ethernet is 960 ns. ICSS hardware has a programmable timer to enforce the IPG for back-to-back packets. For smaller networks, this parameter can be set to a shorter period like 640 ns.

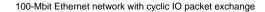

#### 2.2.3.2 **Topology**

The protocol supports one master and up to 254 devices. There are two modes supported. Mode one is line topology in which one master port sends and receives all the packets connected to the line. Mode two is a ring topology in which the master sends redundant packets on two ports to allow for one ring break without disturbing cyclic IO communication. Ring mode also allows shortening cycle time for the same amount of IO devices compared to line mode. During start-up phase the master explores the topology and mode of the devices. Operating mode can be redundant or normal if ring mode is discovered. With line topology only normal mode is supported. There are no multiple masters allowed in the network. The last device in a line topology has only one port connected. The other port of last device in a line remains open and cannot be used as an edge port for other Ethernet traffic.

图 11. Topology

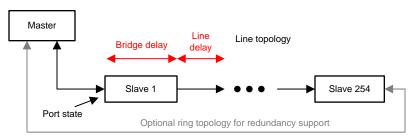

#### 2.2.3.3 Start-up Phase

After power-up the master starts sending a Discovery packet to the network. Each device increments the node counter and inserts the number of input bytes and the number of output bytes in the payload field. There is a 16-bit wide field that contains the number of input data and another 16-bit field for the number of output data bytes per device. As long as there is another device connected on the other port of a device the packet is forwarded with STATUS byte set to *continuous*. Only last device in the line changes the STATUS to *last* and returns the packet back to the master.

The Discovery packet repeats n times at start-up until a stable network configuration is reached. At this time all input and output parameters of the network are known by the master. The length of a Discovery packet is 1030 bytes for a system, which supports 254 devices. Assuming a maximum line delay of 500 ns (100-m cable  $\times$  5 ns) + physical layer delay of 300 ns + bridge delay of 320 ns, there is a total delay of 1120 ns per device or 285.6  $\mu$ s for a complete line in one direction. The total round trip time with 255 devices is 571.2  $\mu$ s. With additional margin for the master to store and compare the results of the Discovery packet a cycle time of 1 ms is configured. Typical repeat count is in the range of 10 to 100.

图 12. State Machine

#### 2.2.3.4 Discovery

Discovery of the network is completed only once during start-up or in the case the topology changes. The network devices report a topology change in case a connection to one port is lost. In this case the start-up phase is initiated by the master, a link-loss message from the device to the master triggers the restart of the network.

12 shows the state machine of the real-time Ethernet protocol. IO data exchange can be as fast as 3 ms after power up of the master. For a more reliable start-up sequence supporting networks with more than ten devices, 50 to 100 ms can be chosen for start-up timing. For example, ten repeats for Discovery, ten repeats for Parameterization, and 50 repeats for Synchronization states.

# 表 3. Discovery Packet Format LENGTH R/W DEFAULT

| FIELD  | LENGTH | R/W                        | DEFAULT | DESCRIPTION                                                                                                                                         |

|--------|--------|----------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| DA     | 1 byte | w (master)<br>r (device)   | 0xff    | Broadcast message to all devices                                                                                                                    |

| SA     | 1 byte | w (master)                 | 0x00    | Master is source of packet. Not required to check address by devices                                                                                |

| Туре   | 1 byte | w (master)<br>r (device)   | 0x01    | 0x01 = DISCOV. Discovery packet type. Devices check the type on receives.                                                                           |

| Status | 1 byte | w (master)<br>r/w (device) | 0x00    | 0 = continuous, 1 = last On continuous the device inserts the IO parameter. On last state the device only forwards the packet without modification. |

## 表 3. Discovery Packet Format (continued)

| FIELD   | LENGTH            | R/W                          | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------------|------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Payload | 6 + 254 × 4 bytes | r/w (master)<br>r/w (device) | 0×00    | Word 0: CNT – counter incremented +1 by each device also used as 32 bit pointer into data field Word 1: read position offset used in output data exchange, updated by each device Word 2: 16 bit number of input data for device 1 Word 3: 16 bit number of output data for device 1 Word 509: number of inputs bytes for device 254 Word 510: number of output bytes for device 254 Each device inserts its own number of input and output date using byte 0 as a 32 bit pointer to the position. |

| FCS     | 4 bytes           | w (master)<br>r (device)     | CRC32   | Default Ethernet FCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

For advanced diagnostics the Ethernet PHYs may report line quality parameter and line break parameter. The line break parameter is typically the length of the broken wire, which is included in the LINK\_LOSS packet. Line quality parameter is part of diagnostic data, which can be integrated into payload input data field or reported through separate diagnostic packet. Diagnostic packets can be sent by each device in the corresponding cycle number, which matches the device number. This ensures that there is only one diagnostic packet per cycle. Maximum latency to report diagnostic data back to the master is 254 IO cycles.

#### 2.2.3.5 Parameterization

After Discovery phase the master distributes network parameters to the network. The Parameterization packet includes the following information:

- IO communication cycle time in ns (32 bit)

- Cycle time of time synchronization in ns (32 bit)

- Period of line delay measurements in ms (16 bit)

- Burst count of line delay measurement (8 bit)

- Gap time for line delay burst in ms (8 bit)

- Delay forward time in ns (16 bit)

- Application input time to relative to cycle start time in ns (32 bit)

- Application output time to relative to cycle start time in ns (32 bit)

- Topology mode: 0 = normal, 1 = ring, 2 ring redundant (8 bit)

- Diagnostic mode: 0 = part of payload, 1 = separate diagnostic packet per device

- Alarm mode: 0 = no immediate network reset on alarms, 1 = network reset on alarms

- CRC mode to choose from no, 8-, 16-, or 32- bit CRC code word

Parameterization packet is sent to all devices and returned by last device in network to the master. The status *LAST* is set by the device which returns the packet. Like with Discovery packet the Parameterization packet can be sent multiple times to ensure all devices are ready to take the parameters. Only if all devices are returning the packet with status LAST the parameters configured by the master are accepted. If a device does not accept the parameters, the device sets the status to *FAIL*. A typical repeat value for Parameterization packets is 1 to 10 with a cycle time of 1 ms.

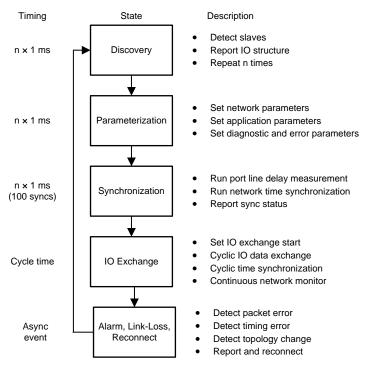

#### 2.2.3.6 Time Synchronization

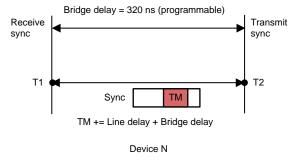

There are two types of operation with respect to time synchronization of the network. First, each device runs line delay measurement to the neighbor ports and repeats it according to parameter provided by master. 13 shows the principal of line delay measurement. LD\_REQ packet does not contain any payload bytes. The device that sends out the LD\_REQ packet saves the transmit time stamp of the packet as time T1. The device that receives the request packet takes a receive time stamp T3 and prepares a LD\_RESP packet in which the payload contains the local delay between receiving LD\_REQ and transmitting LD\_RESP packet. Time to T4 is taken when the LD\_RESP is sent to the wire. While the packet starts transmission, the local delay (T4-T3) is inserted into the payload field. Using PRU-ICSS with programmable delay between packet receive and packet transmit, the line delay measurement can be simplified. In this case the local delay (T4-T3) is already known by the delay master. The device, which receives LD\_REQ, does a loopback on same port with a preprogrammed local delay. The LD\_REQ and LD RESP packets are identical. On the last LD REQ packet the status bit indicates a state transition.

图 13. Line Delay Measurement

The sequence of line delay measurements is triggered from the master port. First the master sends LD\_REQ to the first device, which triggers a line delay measurement on the other port of the device and so on.

The time synchronization function, as shown in [8] 14, starts after line delay is measured. The master sends out a SYNC packet with the master time (TM), which represents the time at MII interface when the packet leaves the master device. The first device receives the SYNC packet and updates the master time with line delay towards the master port and local bridge delay. With preprogrammed bridge delay of 320 ns the TM field can updated without reading time stamp T1 and T2. Subsequent devices perform the same update to TM field. Last device in the line does not update and forward the SYNC packet.

After the SYNC packet is processed, the device adjusts the local time to be equal with the master time. As the hardware of master and devices run from different oscillators, the local time adjustment can be split into drift compensation, —for example long term variation over temperature— and offset compensation coming from frequency offsets of the oscillators. Using a filtered adaptation of local timer will compensate short time jitter induced from interface clock or external influence like shock and vibration. The timer adjustment is performed right after SYNC packet is received by the forwarding PRU.

图 14. Time Synchronization

During IO Exchange state the master sends output packet at a known time. The devices use this time reference to adjust local time. In case there is a long time drift of line delay, the master time field can be appended to the output packet and updated by the devices in the same way as the sync packet.

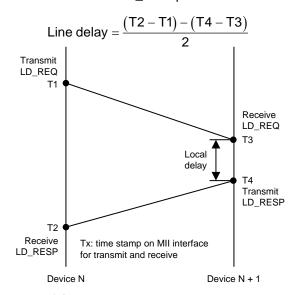

## 2.2.3.7 IO Exchange

After start-up phase with Discovery, Parameterization, and time synchronization, the master and devices transition to cyclic IO Exchange state. The state change is indicated in last sync packet. Last sync packet is sent out 10 µs before state change to IO state.

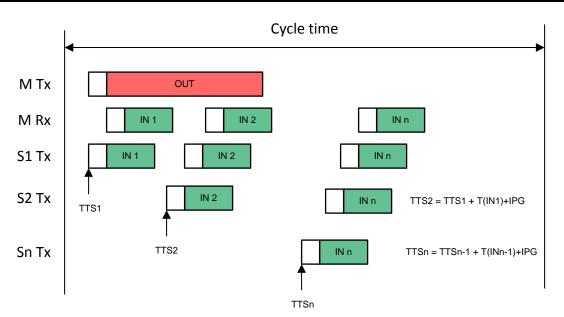

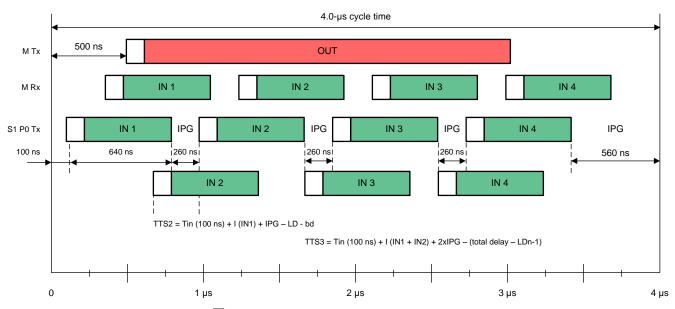

In IO state, the device and master operate in full duplex mode. The first device starts sending its data towards the master after 100 ns. The master begins sending the multicast packet, which contains all output data after 500 ns. This out packet is also used for time synchronization at each device. The difference to sync packet is that cycle time is not 10 µs but cycle time of IO Exchange state. The minimum cycle time of IO Exchange is 4 µs when up to four devices are connected to the master.

The master always sends the multicast out packet at the beginning of a cycle. The devices have variable start time for sending the in packet towards the master. This time depends on the line delay, bridge delay and in packet size of other devices which are between the master and the current device.

Is shows the principle operation of the IO Exchange. The master sends single packet, which contains all output data of each device. The location inside the out packet for each device was provided during Discovery phase. Input data is sent by each device in a separate packet. To allow for maximum bandwidth in short cycle times, each device calculates the optimum time triggered send value (TTSx). An error condition occurs when transmission of local in packet is not finished before sending packet from other devices.

图 15. IO Cycle Principle

图 16. IO Distribution in 4-µs Cycle Time

The input packet format is identical for each device in this example. Source address (SA) is redundant information as the time when a packet received at the master provides the same information.

表 4. Input Packet Format

| BYTE<br>1 | BYTE 2 | BYTE<br>3 | BYTE 4 | BYTE 5 | BYTE 6 | BYTE 7 | BYTE 8 |

|-----------|--------|-----------|--------|--------|--------|--------|--------|

| 0x55      | 0xd5   | SA        | STATUS | DATA 1 | DATA 2 | DATA 3 | CRC8   |

The output packet format contains 16 data bytes, which are evenly distributed over four devices. Additional 2 bytes of tx time stamp (TX\_TS1 and TX\_TS2) are added to use for time synchronization during IO Exchange. CRC8 polynomial spans over bytes 3 through 20. Transmit time stamp (TX\_TS) is 16 bit with MSB in byte 21 and LSB in byte 22.

## 表 5. Output Packet Format

| BYTE<br>1 | BYTE 2 | BYTE<br>3 | BYTE 4 | BYTE 5 | <br>BYTE 20 | BYTE 21 | BYTE 22 | BYTE 23 |

|-----------|--------|-----------|--------|--------|-------------|---------|---------|---------|

| 0x55      | 0xd5   | SA        | STATUS | DATA 1 | <br>DATA 16 | TX_TS1  | TX_TS2  | CRC8    |

#### 2.2.3.8 Error and Diagnostic

There are several ways to detect and handle error conditions in the network. In order to exchange packets a physical link must be available. PRU-ICSS has two options to detect whether link is available. The MDIO interface can be used to read Ethernet physical layer status. A faster way to detect a link loss provides RX\_ERR counter in MII\_RT interface. In case there are 32 or more continuous RX\_ERR events within a 10-µs sliding window, an RX\_ERR32 event is sent to the INTC.

During protocol start-up a certain device may report an error through STATUS bit field. Bit 2 indicates an error condition from a slave towards the master, such as the Parameterization parameters are not accepted by certain devices. Frame errors are indicated by FCS at the end of the packet. SORTE protocol provides options of various FCS code words. During start-up phase with larger packets for Discovery and Parameterization, a 32-bit CRC code word is used and verified by MII\_RT hardware. During IO Exchange phase with smaller packets, CRC8 polynomial is generated and verified by PRU firmware.

More error identification can be completed through timing analysis of received packets and IPG time. In case time synchronization is lost in the network, the timing of packets sent and received will start to drift. This drift can be measured by each network node using RX and TX time stamps of received and sent packets during IO Exchange phase.

There are three packet types defined to report back to the master. If a certain device in the network must enforce a reset condition and tell the master which device has issued, the request a RESET packet is defined.

Application on the devices may see error conditions, which are relevant for the application on the master device. ALARM packet provides the possibility to report alarm coder word with associated alarm data. Engineering of the network must reserve extra space for ALARM packets after IN packets are sent.

Application and network interface can provide additional diagnostic data to the master. The DIAG packet has additional time stamp field to report when diagnostic data was captured. As with ALARM packets the DIAG packets required extra bandwidth during IO Exchange.

Bandwidth allocation can be for single packet per cycle or all packets per cycle. In single cycle packet mode each device in the network maintains a cycle counter in IO Exchange state and takes the slot of the cycle counter modulo device number.

The master may not immediately retrain the network on a failing condition reported by the devices in the network. The interface described in † 2.2.3.10 provides the option to not retrain, retrain after first error, or retrain after a number of errors.

The interface also defines a functional error test. When set, the PRU will force a predefined number of CRC errors in the packets. In addition a timing error can be enforced through this interface.

## 2.2.3.9 Packet Format Summary

# 表 6. Packet Format Summary<sup>(1)</sup>

| PACKET | DA  | SA | TYPE       | STATUS                | PAYLOAD                                                                                                                                                                                     | SIZE [BYTES] |

|--------|-----|----|------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| DISC   | FF  | 0  | DISK (1)   | CONT DONE             | count + reserved +<br>(2 bytes) in_ptr +<br>out_ptr (4) + 254 x<br>4                                                                                                                        | 1026         |

| PARAM  | FF  | 0  | PARAM (2)  | CONT DONE             | LD_PERIOD (8), LD_BURST (8) SYNC_CNT (16), CYC_TIME (32) T_IN (32), T_OUT (32) SYNC_MODE (8), LD_MODE (8) ERROR_MODE (8), DIAG_LEVEL(8), IPG(16), BD(16), TTS_IN (N*32) RESERVED (16 bytes) | 1062         |

| LD_REQ | N-1 | N  | LD_REQ (3) | LD_PENDING<br>LD_DONE | -                                                                                                                                                                                           | 8            |

| SYNC   | FF  | 0  | SYNC (5)   | _                     | 32-bit master time<br>TM, 1 ns field                                                                                                                                                        | 12           |

| OUT    | FF  | 0  | OUT        | CONT                  | Dynamic, 2 bytes<br>of TX_TS before<br>CRC                                                                                                                                                  | 8+ variable  |

| IN     | 0   | N  | IN         | _                     | Dynamic                                                                                                                                                                                     | 8+ variable  |

| RESET  | 0   | N  | RES        | RESET                 | N - device number which reports error                                                                                                                                                       | 9            |

| ALARM  | 0   | N  | ALARM      | ALARM                 | ALARM_CODE<br>(8), ALARM_DATA<br>(32)                                                                                                                                                       | 13           |

| DIAG   | 0   | N  | DIAG       | _                     | DIAG_CODE (8),<br>DIAG_TS (32),<br>DIAG_DATA (64)                                                                                                                                           | 21           |

<sup>(1)</sup> Abbreviation definitions available in 7 节.

## 2.2.3.10 Memory Map

PRU-ICSS has three internal memory blocks, which are low latency for PRU to read in 3-1-1-1 cycle bursts. First 32 bit takes three cycles and consecutive reads of single burst command (LBBO or LBCO) take one PRU cycle per 32 bits. The memory blocks are PRU0 data memory, PRU 1 data memory, and ICSS shared memory. PRU0 detects PRU0 data memory at offset 0 and PRU1 data memory at offset 0x2000. PRU1 detect PRU0 data memory at offset 0x2000 and PRU1 data memory at offset 0. Both PRUs see ICSS shared RAM at offset 0x10000.

The SORTE master protocol example runs on PRU0 and uses PRU0 data memory for control interface between ARM and PRU\_ICSS, look-up tables, packet storage, and IO data. 表 7 lists all the entries of PRU0 data memory.

## 表 7. Memory Map PRU0 Data Memory

| PRU0 DATA<br>MEMORY     | OFFSET | LENGTH   | DATA                               | COMMENT                      |

|-------------------------|--------|----------|------------------------------------|------------------------------|

| SORTE_REG_<br>INTERFACE | 0x000  | 256      | See 表 8                            | _                            |

| CRC8_TABLE              | 0x100  | 256      | Look-up table for CRC8             | _                            |

| DISCOVERY_<br>RX        | 0x200  | 1033     | Received Discovery packet          | Used for engineering         |

| OUT_DATA                | 0x700  | Variable | Data field of OUT packet           | 16 bytes for 4-μs cycle time |

| IN_DATA                 | 0x800  | Variable | All in packets from IO<br>Exchange | _                            |

#### 表 8. Memory Map SORTE Register Interface

| PRU0 DATA<br>MEMORY  | OFFSET | LENGTH  | DATA                                                                                                                 | COMMENT                                                                                                                                                                    |

|----------------------|--------|---------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control register     | 0x000  | 32 bits | Bit field set by host                                                                                                | _                                                                                                                                                                          |

| Enable               | _      | _       | Bit 0: 0 =disable<br>1 enable                                                                                        | Global start of protocol                                                                                                                                                   |

| Engineering          | _      |         | Bit 1: 0 = offline (host)<br>1 = online (PRU)                                                                        | Engineering of cycle time and scheduling of packets Offline uses additional register settings.                                                                             |

| Debug                | _      | _       | Bit 2: 0 = off<br>1 = on                                                                                             | Debug trace buffer active,<br>must be configured when<br>enabled                                                                                                           |

| Diagnostic           | _      | _       | Bit 3: 0 = off<br>1 = on                                                                                             | Diagnostic trace buffer, must be configured when enabled                                                                                                                   |

| CRC error<br>mode    | _      | _       | Bit 4 and 5: 00: no retrain on error 01: retrain on single crc 10: retrain on n crc 11: not defined                  | Error handling when master receives CRC error during IO Exchange.  Must specify number of CRC errors with setting 10.                                                      |

| Timing error<br>mode | _      | _       | Bit 6 and 7: 00: no retrain on<br>error<br>01: retrain on single error<br>10: retrain on n errors<br>11: not defined | Error handling when master receives timing error of IN packets during exchange. Must specify number of errors with setting 10.                                             |

| Diagnostic<br>mode   | _      | _       | Bit 8: 00 : disabled<br>01: enable_single<br>10: enable_all<br>11: enable_shared                                     | When enabled, the engineering leaves space in a cycle to send and receive a separate diagnostic packet.  Mode 01 allows one diagnostic packet of specified size per cycle. |

# 表 8. Memory Map SORTE Register Interface (continued)

| PRU0 DATA<br>MEMORY        | OFFSET | LENGTH   | DATA                                                                                                                                                                                                                                                             | COMMENT                                                              |

|----------------------------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Functional<br>error test   | _      | _        | Bit 9 to 11: 000 – no error test, test competed  001 – force crc error with one packet  010 – force timing error with one packet  011 – force 3 crc errors  100 – force 3 timing errors  101 – force 10 crc errors  110 – force 10 timing errors  111 - reserved | Host sets the error tests. PRU clears the test when completed.       |

| Status register            | 0x0004 | 32 bits  | Bit field set by host                                                                                                                                                                                                                                            | Status of SORTE protocol                                             |

| Protocol state             | _      | _        | Bit 0 to 2: 000: idle 001: discovery 010: parameterization 011: line delay 100: sync 101: IO exchange 110: error 111:                                                                                                                                            | PRU indicates which state it is currently in.                        |

| Port 0 state               | _      | _        | Bit 3: 0=no link<br>1 = link                                                                                                                                                                                                                                     | PRU indicates whether port is active.                                |

| Port 1 state               | _      | _        | Bit 4: 0 = no link<br>1 = link                                                                                                                                                                                                                                   | PRU indicates whether port is active.                                |

| SYNC state                 | _      | _        | Bit 5: 0 = no sync<br>1 = sync                                                                                                                                                                                                                                   | Device is not in sync state if the monitored jitter is out of range. |

| Communicatio n state       | 0x0008 | 32 bits  | _                                                                                                                                                                                                                                                                | _                                                                    |

| CRC error count            |        | _        | Bit 0 to 7: number of CRC errors                                                                                                                                                                                                                                 | CRC error threshold for retrain                                      |

| Timing violation count     | _      | _        | Bit 8 to 15: number timing error count                                                                                                                                                                                                                           | Timing error threshold for retrain                                   |

| Size of diagnostic Packets | _      | _        | Bit 16 to 23: number of bytes in extra diagnostic packet                                                                                                                                                                                                         | Diagnostic packet sent                                               |

| Reserved                   |        |          | Bit 23 to 31                                                                                                                                                                                                                                                     |                                                                      |

| Firmware revision 1        | 0x000C | 32 bits  | Bit 0 to 7: interim version<br>Bit 8 to 15: minor version<br>Bit 16 to 23: major version<br>Bit 24: 0 = master, 1 = slave<br>Bit 25 to 31: reserved                                                                                                              | PRU firmware revision of SORTE protocol written by PRU               |

| Interrupt<br>control       | 0x0010 | 32 bits  | Bit 0 to 7: timing interrupts<br>Bit 8 to 15: packet interrupts<br>Bit 16 to 23: state interrupts<br>Bit 24 to 31: reserved                                                                                                                                      | Host can select interrupt sources.                                   |

| Interrupt status           | 0x0014 | 32 bits  | Bit 0 to 7: timing interrupts<br>Bit 8 to 15: packet interrupts<br>Bit 16 to 23: state interrupts<br>Bit 24 to 31: reserved                                                                                                                                      | Interrupt status set by PRU.                                         |

| Interrupt clear            | 0x0018 | 32 bits  | Bit 0 to 7: timing interrupts<br>Bit 8 to 15: packet interrupts<br>Bit 16 to 23: state interrupts<br>Bit 24 to 31: reserved                                                                                                                                      | Host must clear interrupt to receive new one.                        |

| Reserved                   | 0x001C | 32 bits  | _                                                                                                                                                                                                                                                                | _                                                                    |

| PARAM DATA                 | 0x0020 | 32 bytes | 32 bytes of parameters sent by the master                                                                                                                                                                                                                        | _                                                                    |

| Cycle_time                 | _      | 32 bits  | Cycle time in ns                                                                                                                                                                                                                                                 | Minimum cycle time is 4 μs<br>Maximum cycle time 100 ms              |

# 表 8. Memory Map SORTE Register Interface (continued)

| PRU0 DATA<br>MEMORY       | OFFSET | LENGTH   | DATA                                                                                                      | COMMENT                                                                                                                                                           |

|---------------------------|--------|----------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sync_time                 | -      | 32 bits  | Cycle time of sync packets in ns                                                                          | If none is defined the master out packet is used as timing reference which has time stamp appended                                                                |

| Delay_period              | _      | 32 bits  | Period of line delay<br>measurements in ms<br>0: no additional line delay<br>1-n: add line delay to cycle | Line delay is measured during start-up sequence. For period >0 a window of 2 µs is appended to IO Exchange to run line delay with period specified in this field. |

| Delay_burst               | _      | 8 bits   | Number of back to back delay measurements. Default = 16.                                                  | _                                                                                                                                                                 |

| Delay_gap                 | _      | 8 bits   | Delay gap time in ms                                                                                      | Gap time for line delay bursts in ms                                                                                                                              |

| Delay_forward<br>_time    | _      | 16 bits  | Local forward time in ns                                                                                  | Delay forwards time of device,<br>which responds after given<br>time on same port                                                                                 |

| Inter_packet_g<br>ap      | _      | 16 bits  | Inter packet gap in ns                                                                                    | Minimum delay for back to back packets enforced by MII interface. Must respect Ethernet PHY min IPG.                                                              |

| T_in                      | _      | 16 bits  | Offset time in ns                                                                                         | Input time relative to cycle start time                                                                                                                           |

| T_out                     | _      | 16 bits  | Offset time in ns                                                                                         | Output time relative to cycle start time                                                                                                                          |

| Topology                  | _      | 8 bits   | 0: line<br>1: ring<br>2: ring redundant<br>3 to 255: reserved                                             | Topology mode                                                                                                                                                     |

| Diagnistics               | _      | 8 bits   | 0 = part of payload<br>1 = separate diagnostic packet<br>per device                                       | Diagnostic mode during IO<br>Exchange state                                                                                                                       |

| Alarm                     | _      | 8 bits   | 0: no immediate reset on alarm 1: immediate reset on alarm                                                | Master indicates to device how to behave in error conditions.                                                                                                     |

| Crc_mode                  | -      | 8 bits   | 0: NO_CRC<br>1: CRC32<br>2: CRC16<br>3: CRC8<br>4: CASTAGNOLI<br>5 to 255: reserved                       | Crc code used during<br>exchange state for IN and<br>OUT packet                                                                                                   |

| Reserved                  | 0x0040 | 16 bytes | _                                                                                                         | _                                                                                                                                                                 |

| Statistic register port 0 | 0x0050 | 16 bytes | Port specific statistic                                                                                   | _                                                                                                                                                                 |

| Cycle count               | _      | 32 bits  | IO cycle counter                                                                                          | Min 4 μs                                                                                                                                                          |

| CRC errors                | _      | 32 bits  | CRC error counter                                                                                         | _                                                                                                                                                                 |

| Timing errors             | _      | 32 bits  | Timing error counter                                                                                      | _                                                                                                                                                                 |

| Format errors             | _      | 32 bits  | Format error counter                                                                                      | Can be length or data structure<br>For example, unknown<br>command or address                                                                                     |

| Protocol retrain          | 0x0070 | 32 bits  | Retrain counter                                                                                           | Number of retrains since power up                                                                                                                                 |

| Reserved                  | 0x0074 | 12 bytes | _                                                                                                         | _                                                                                                                                                                 |

| Network timing            | 0x0080 | 16 bytes | Packet timing for cyclic IO<br>Exchange                                                                   | Used to monitor any drift in network                                                                                                                              |

## 2.3 Highlighted Products

#### 2.3.1 AM3359

- Up to 1-GHz Sitara ARM Cortex-A8 32-bit RISC processor

- NEON™ SIMD coprocessor

- 32KB of L1 Instruction and 32KB of data cache with single-error detection (parity)

- 256KB of L2 cache with error correcting code (ECC)

- 176KB of on-chip boot ROM

- 64KB of dedicated RAM

- · Emulation and debug JTAG

- Interrupt controller (up to 128 interrupt requests)

#### PRU-ICSS:

- Supports protocols such as EtherCAT®, PROFIBUS®, PROFINET®, EtherNet/IP™, and more

- Two PRUs 32-bit load and store RISC processor capable of running at 200 MHz

- 8KB of instruction RAM with single-error detection (parity)

- 8KB of data RAM with single-error detection (parity)

- Single-cycle, 32-bit multiplier with 64-bit accumulator

- · Enhanced GPIO module provides shift-in or shift-out support and parallel latch on external signal

- 12KB of shared RAM with single-error detection (parity)

- Three 120-byte register banks accessible by each PRU INTC for handling system input events

- Local interconnect bus for connecting internal and external masters to the resources inside the PRU-ICSS

- Peripherals inside the PRU-ICSS:

- One universal asynchronous receiver and transmitter (UART) port with flow control pins that supports up to 12 Mbps