## Errata

# 适用于 DLPR410 和 DLPR910 器件的 DLP® 产品公告

### 摘要

AMD Xilinx 已停止生产 XCF16P 配置 PROM,它用作以下 TI 器件的基底器件:2510442-0005、 DLPR410YVA、DLPR410AYVA、DLPR410BYVA、DLPR910YVA、DLPR910AYVA。本文档详细介绍了德州仪器 (TI) 产品设计更新和支持。

### 内容

| 1 受影响的产品                 | 2 |

|--------------------------|---|

| 2 主串行外设接口闪存配置方法          | 2 |

| 3 SPI 闪存配置方法             | 2 |

| 3.1 配置指南                 |   |

| 3.2 FPGA 引脚排列信息          |   |

| 3.3 支持 SPI 闪存配置方法的设计详细信息 |   |

| 3.4 SPI 闪存布局连接           |   |

| 3.5 己批准 SPI PROM         |   |

| 4 常见问题与解答                |   |

| 5 修订历史记录                 |   |

### 1 受影响的产品

AMD Xilinx 已停止生产 XCF16P 配置 PROM,它用作以下 TI 器件的基底器件:

- 2510442-0005

- DLPR410YVA

- DLPR410AYVA

- DLPR410BYVA

- DLPR910YVA

- DLPR910AYVA

### 2 主串行外设接口闪存配置方法

使用 DLPC910 或 DLPC410 控制器的产品设计需要进行更新,以实现 Xilinx 主串行外设接口 (SPI) 闪存配置方法。

## 3 SPI 闪存配置方法

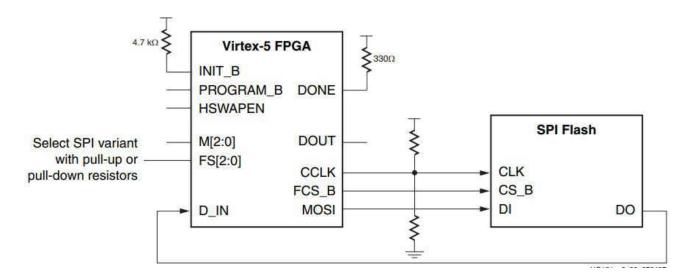

请参阅以下 AMD Xilinx 信息,了解如何将 DLPC910 和 DLPC410 (Virtex-5 FPGA) 连接到 SPI 闪存以进行配置。

### 3.1 配置指南

Xilinx Virtex-5 配置指南:

https://docs.xilinx.com/v/u/en-US/ug191

### 3.2 FPGA 引脚排列信息

Xilinx Virtex-5 XC5VLX30FF676 FPGA 引脚排列信息:

http://www.xilinx.com/content/dam/xilinx/support/packagefiles/v5packages/5vlx30ff676.pkg.txt

# 3.3 支持 SPI 闪存配置方法的设计详细信息

通过 DLPC910 和 DLPC410 支持主串行外设接口 (SPI) 闪存配置的设计详细信息如下:

- 1. FPGA 控制器上的主串行外设接口闪存配置模式 M[2..0] 引脚必须更改为 M[2:0] = 001。

- 有关更多信息,请参阅 Xilinx Virtex-5 配置指南 UG191 的第62页:

- 2. 必须正确连接 FS[2:0] 引脚,以确定所选 SPI 闪存用于连接 FPGA 控制器的读取命令类型。下表(<u>UG191</u> Xilinx Virtex-5 配置指南中的表 2-8)描述了可用的选择:

Table 2-8: Virtex-5 Device SPI Read Command Variant Select Table

| FS[2:0] | SPI Read Command | Comments                                                                                                                                                                                                                                              |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000     | 0xFF             |                                                                                                                                                                                                                                                       |

| 001     | RCMD[7:0]        | RCMD[7:0] on ADDR[7:0] are sampled by the INIT_B rising edge, along with M[2:0] and FS[2:0]. RCMD[7:0] can be used to support any SPI read commands not supported here. The timing requirements for FS[2:0] and RCMD[7:0] are the same as for M[2:0]. |

| 010     | 0x52             |                                                                                                                                                                                                                                                       |

| 011     | Reserved         |                                                                                                                                                                                                                                                       |

| 100     | 0x55             |                                                                                                                                                                                                                                                       |

| 101     | 0x03             |                                                                                                                                                                                                                                                       |

| 110     | 0xE8             |                                                                                                                                                                                                                                                       |

| 111     | 0x0B             |                                                                                                                                                                                                                                                       |

FS2 = DLPC910 控制器和 DLPC410 控制器的引脚 AB11

FS1 = DLPC910 控制器和 DLPC410 控制器的引脚 AA13

FS0 = DLPC910 控制器和 DLPC410 控制器的引脚 AA14

### 3.4 SPI 闪存布局连接

DLPC910 和 DLPC410 控制器必须使用下图所述的连接方式连接至 SPI 闪存

SPI 闪存写保护 (WP#) 应该被拉高以允许通过 Virtex 5 JTAG 接口进行编程。应将 SPI 闪存复位 (RESET#) 或保持 (HOLD#) 拉至高电平,以防止 SPI 闪存暂停与 DLPC410 和 DLPC910 控制器的串行通信。

有关 SPI 配置闪存如何连接到 DLPC410 控制器和 DLPC910 控制器的更多详细信息,请参阅 DLPLCRC910EVM 和 DLPLCRC410EVM 的原理图。

FCS\_B = DLPC910 控制器和 DLPC410 控制器的引脚 AA10

MOSI = DLPC910 控制器和 DLPC410 控制器的引脚 AA9

CCLK = DLPC910 控制器和 DLPC410 控制器的引脚 J10

D IN = DLPC910 控制器和 DLPC410 控制器的引脚 K11

### 3.5 已批准 SPI PROM

用于 Virtex-5 且通过 Xilinx 批准的 SPI PROM 列表可在 Xilinx ISE Impact Tool 版本 14.1 的器件列表中找到。

### 备注

在 PCB 重新设计期间,请确保在设计中保留现有的安全 PROM ( DLPR410、DLPR910 ) ,并直接添加对配置 SPI 闪存的布局支持。

### 3.5.1 适用于 Virtex-5 且通过 AMD Xilinx 批准的 SPI 闪存的当前列表

| 制造商                 | 器件型号              |

|---------------------|-------------------|

| Adesto Technologies | AT45DB321E        |

| ISSI                | IS25LP128         |

| Infineon            | S25FL064P         |

| Infineon            | S25FL128          |

| Infineon            | S25FL128LAGMFM010 |

| Infineon            | S25FL129P         |

### 3.5.2 Xilinx 支持论坛

如需进一步的支持,请联系 AMD Xilinx 支持论坛 http://support.xilinx.com/。

### 4 常见问题与解答

1. 我们是否可以使用 AMD Xilinx 批准的 SPI PROM 中的任何一种?

是,该列表由 AMD Xilinx 提供,其中包含由 Virtex-5 支持的 SPI 闪存。如果您有具体问题,请联系 AMD Xilinx。

2. 我们是通过 TI 还是通过分销商进行购买?

TI 不会销售适用于 DLPC410、DLPC910 的 SPI 闪存。

3. 如何对 SPI 闪存进行编程?

终端客户将在 PCB 组装之前或组装后通过 Xilinx 工具对 SPI 闪存进行编程。TI 将在 TI.com 上发布固件配置 文件: https://www.ti.com.cn/product/cn/DLPR410 和 https://www.ti.com.cn/product/cn/DLPR910。

4. 我们应何时开始重新设计 DLPC410 和 DLPC910 PCB。

TI 建议您在 2023 年第 2 季度之前完成 PCB 的重新设计并进行测试。请注意,在 PCB 重新设计期间,请确保在设计中保留现有的安全 PROM(DLPR410、DLPR910),并直接添加对配置 SPI 闪存的布局支持。

### 5 修订历史记录

| 日期            | 修订版本 | 说明    |

|---------------|------|-------|

| February 2023 | *    | 初始发行版 |

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司