**DAC8771**

ZHCSHP3 - FEBRUARY 2018

# 具有自适应电源管理功能的 **DAC8771** 单通道 **16** 位电压或电流输出数模转换器

### 1 特性

- 输出电流:

- OmA 24mA; 3.5mA 23.5mA;OmA 20mA; 4mA 20mA; ±24mA

- 输出电压(可配置或不配置 20% 的超量程):

- 0V 5V; 0V 10V; ±5V; ±10V

- 0V 6V; 0V 12V; ±6V; ±12V

- 自适应电源管理

- 单宽电源引脚

- 12V 36V (使用降压/升压转换器)

- 12V 33V (不使用降压/升压转换器)

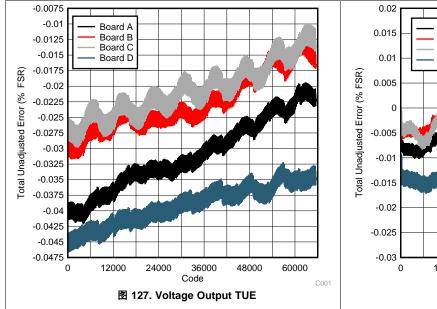

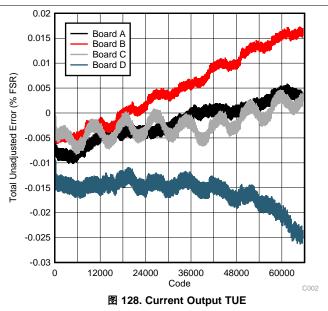

- ±0.1% 满量程范围 (FSR) 总未调节误差 (TUE)

- 微分非线性 (DNL): ±1 最低有效位 (LSB) 最大值

- 5V 内部基准(10ppm/°C 最大值)

- 5V 内部数字电源输出

- CRC/帧错误检查,看门狗定时器

- 过热报警、开路/短路

- 报警条件下的安全操作

- 自动学习功能

- 宽温度范围: -40°C 至 +125°C

#### 2 应用

- 4mA 至 20mA 电流环路

- 模拟输出模块

- 可编程逻辑控制器 (PLC)

- 楼宇自动化

# 3 说明

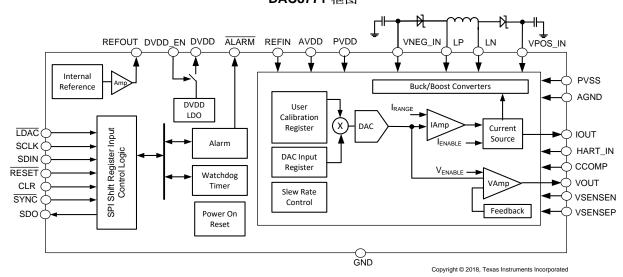

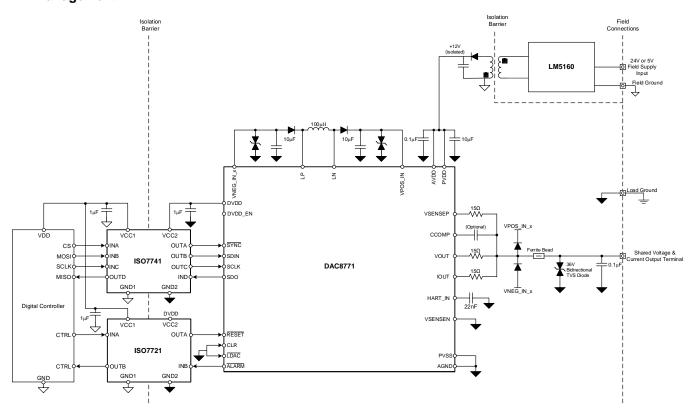

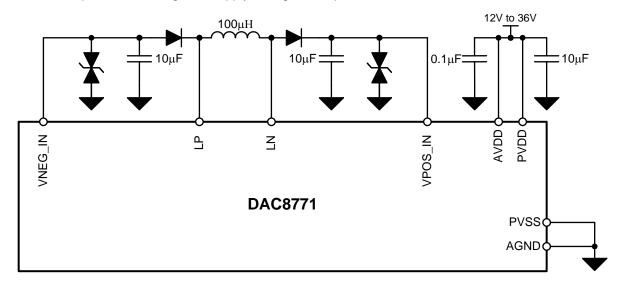

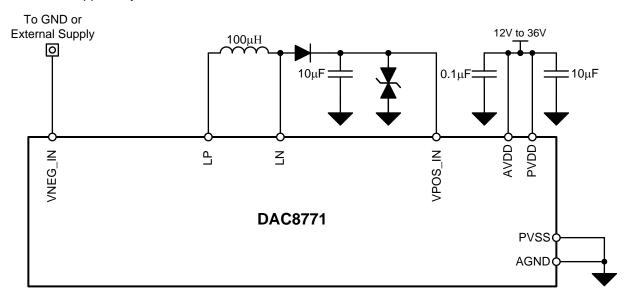

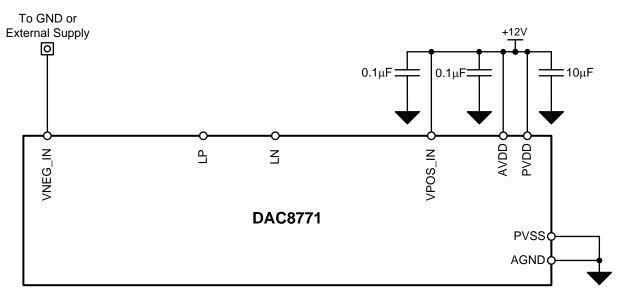

DAC8771 是一款单通道的精密全集成 16 位数模转换器 (DAC),具有自适应电源管理功能,适用于工业控制应用中,低功耗是一个关键问题。自适应电源管理电路在使能后能够最大程度降低芯片功耗。通过编程设定为电流输出后,电流输出驱动器上的电源电压根据电流输出引脚处电压的连续反馈,通过降压/升压转换器在 4V 至 32V 范围内进行调节。通过编程设定为电压输出后,该电路为电压输出级 (±15V) 生成可编程电源电压。DAC8771 包含一个 LDO,用于从单电源引脚生成数字电源 (5V),特别适合用于支持隔离式应用中,低功耗是一个关键问题。

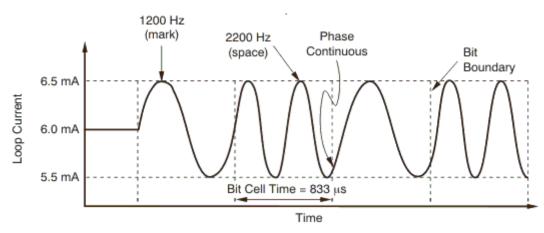

DAC8771 还采用一种 HART 信号接口,支持在电流输出中叠加外部 HART 信号。电流输出 DAC 压摆率由寄存器通过编程设定。该器件可在使用集成降压/升压转换器的情况下由 +12V 至 +36V 的单个外部电源供电,或在禁用降压/升压转换器的情况下由多个外部电源供电。

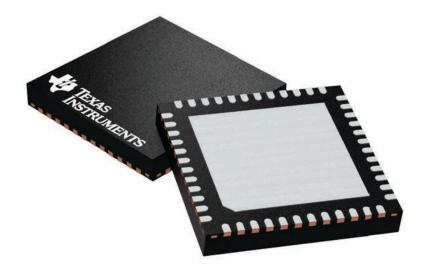

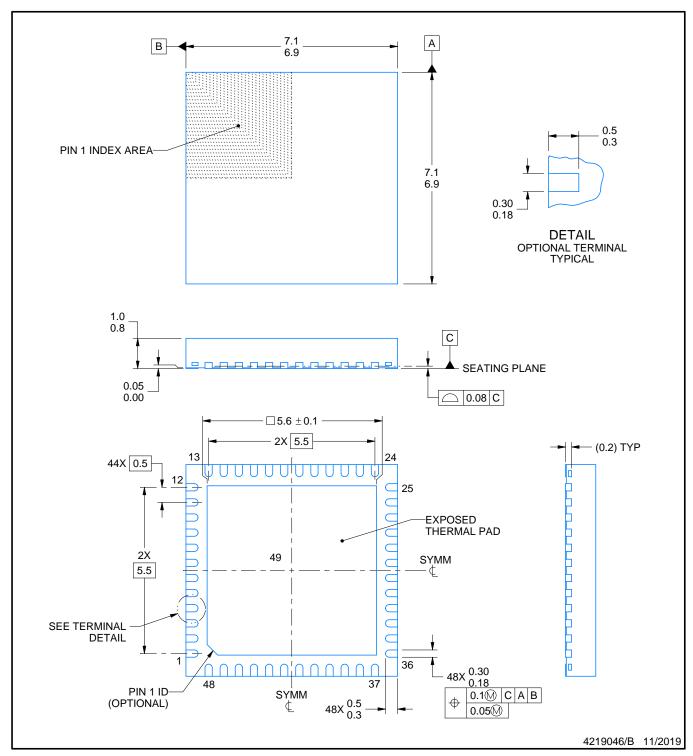

### 器件信息(1)

| 器件型号    | 封装        | 封装尺寸 (标称值)      |

|---------|-----------|-----------------|

| DAC8771 | VQFN (48) | 7.00mm x 7.00mm |

(1) 要了解所有可用封装,请参阅数据表末尾的可订购产品附录。

### DAC8771 框图

# 目录

| 1 | 特性1                                                  |    | 8.4 Device Functional Modes    |    |

|---|------------------------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                                 |    | 8.5 Register Maps              | 45 |

| 3 | 说明 1                                                 | 9  | Application and Implementation | 60 |

| 4 | 修订历史记录 2                                             |    | 9.1 Application Information    | 60 |

| 5 | Device Comparison Table                              |    | 9.2 Typical Application        | 63 |

| 6 | Pin Configuration and Functions 3                    | 10 | Power Supply Recommendations   | 66 |

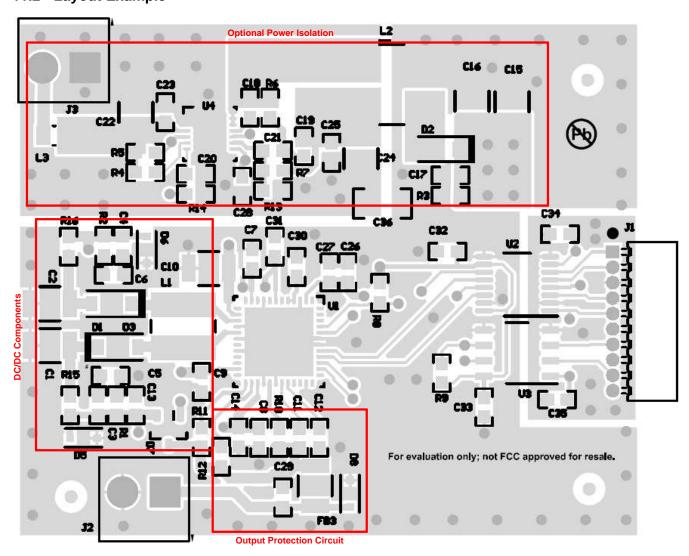

| 7 | Specifications5                                      | 11 | Layout                         | 68 |

| • | 7.1 Absolute Maximum Ratings 5                       |    | 11.1 Layout Guidelines         | 68 |

|   | 7.2 ESD Ratings                                      |    | 11.2 Layout Example            | 69 |

|   | 7.3 Recommended Operating Conditions                 | 12 | 器件和文档支持                        | 72 |

|   | 7.4 Thermal Information                              |    | 12.1 器件支持                      | 72 |

|   | 7.5 Electrical Characteristics                       |    | 12.2 文档支持                      | 72 |

|   | 7.6 Timing Requirements: Write and Readback Mode. 13 |    | 12.3 接收文档更新通知                  | 72 |

|   | 7.7 Typical Characteristics                          |    | 12.4 社区资源                      | 72 |

| 8 | Detailed Description 31                              |    | 12.5 商标                        |    |

| - | 8.1 Overview                                         |    | 12.6 静电放电警告                    | 72 |

|   | 8.2 Functional Block Diagram31                       |    | 12.7 Glossary                  | 72 |

|   | 8.3 Feature Description                              | 13 | 机械、封装和可订购信息                    | 72 |

# 4 修订历史记录

| 日期         | 修订版本 | 说明   |

|------------|------|------|

| 2017年 2018 | *    | 第一版. |

# 5 Device Comparison Table

| PRODUCT | RESOLUTION DIFFERENTIAL NONLINEARITY (LSB) |    | SPECIFIED<br>TEMPERATURE<br>RANGE |  |  |

|---------|--------------------------------------------|----|-----------------------------------|--|--|

| DAC8771 | 16                                         | ±1 | -40°C to +125°C                   |  |  |

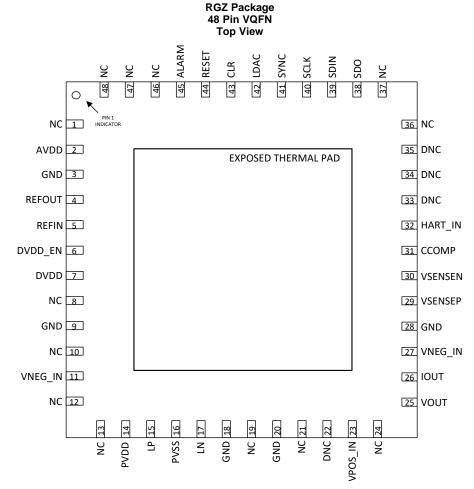

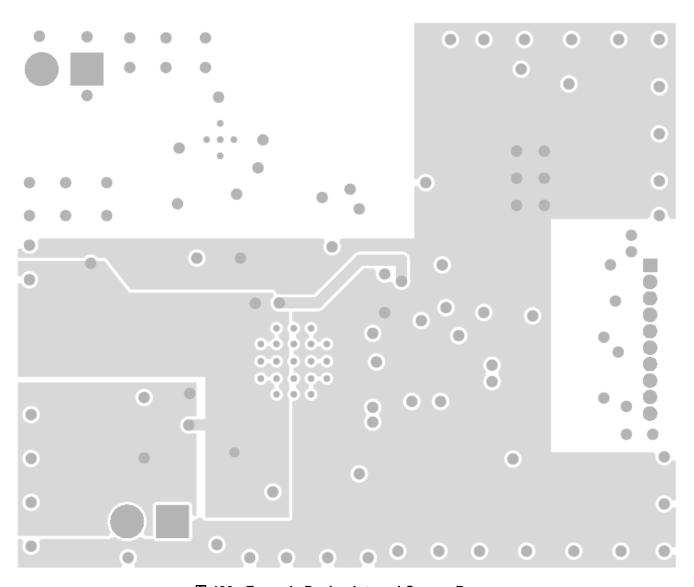

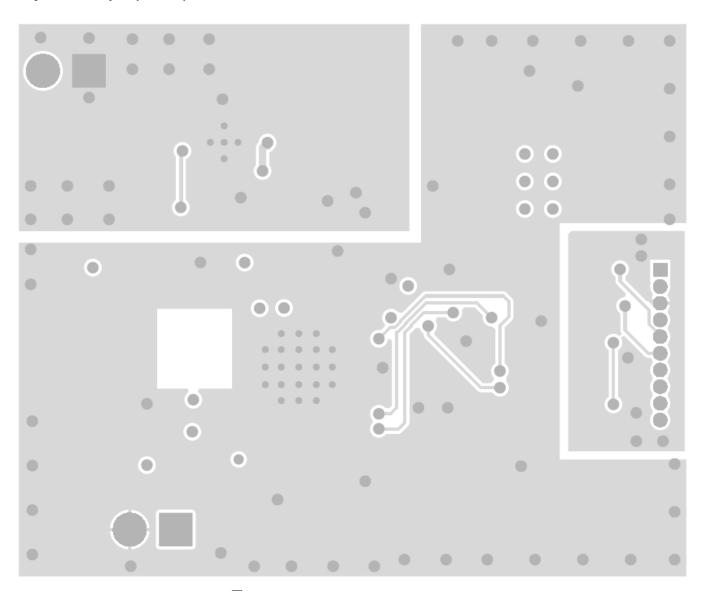

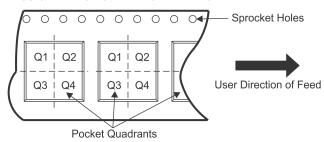

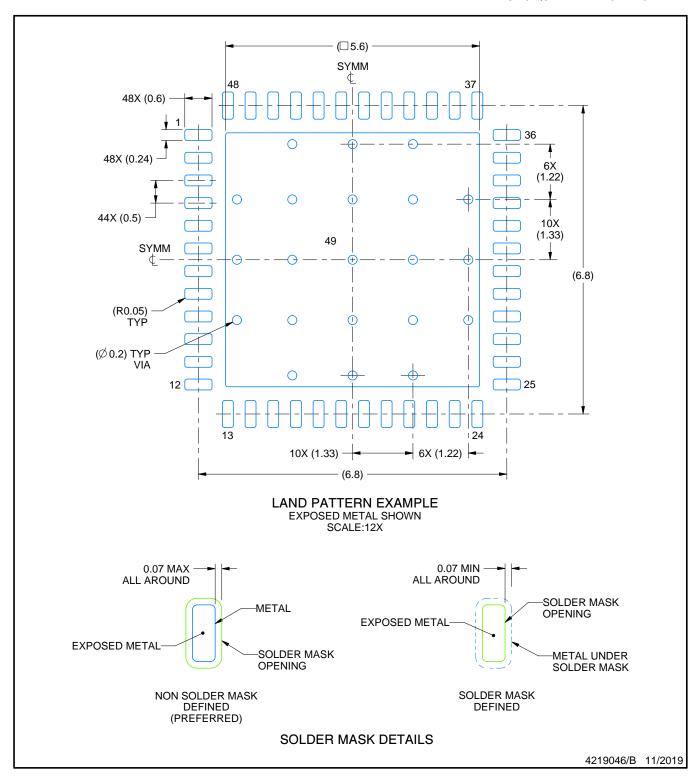

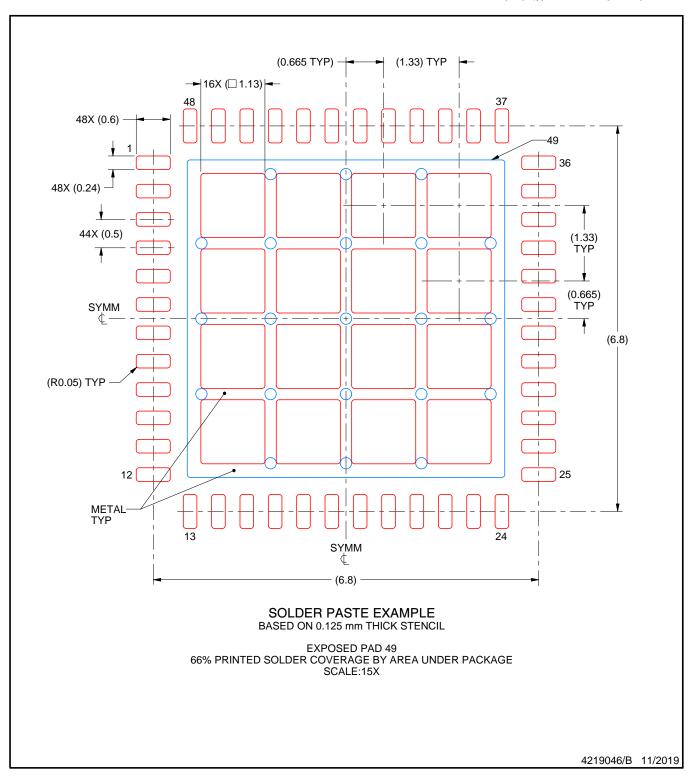

# 6 Pin Configuration and Functions

Thermal pad connected to ground.

### **Pin Functions**

| NAME                                                                    | NUMBER                                                                                      | TYPE          | DESCRIPTION                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVDD                                                                    | 2                                                                                           | Supply        | Power supply for all analog circuitry of the device except buck-boost converter and output amplifiers.                                                                                                                                     |

| GND 3, 9, 18, 20, 28 Supply Ground.                                     |                                                                                             | Ground.       |                                                                                                                                                                                                                                            |

| REFOUT                                                                  | 4 Analog Output Internal reference output. Connects to REFIN when using internal reference. |               | Internal reference output. Connects to REFIN when using internal reference.                                                                                                                                                                |

| REFIN                                                                   | 5                                                                                           | Analog Input  | Reference input. Connects to REFOUT when using internal reference.                                                                                                                                                                         |

| DVDD_EN 6 Digital Input leave this pin unconnected to enable the interr |                                                                                             | Digital Input | Internal power-supply enable pin. Connect this pin to GND to disable the internal DVDD, or leave this pin unconnected to enable the internal DVDD. When this pin is connected to GND an external supply must be connected to the DVDD pin. |

# Pin Functions (continued)

| NAME                                                      | NUMBER                                                    | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------|-----------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVDD                                                      | 7                                                         | Supply           | Digital supply pin (Input/Output). Internal DVDD enabled when DVDD_EN is floating, External DVDD must be supplied when DVDD_EN is connected to GND.                                                                                                              |

| VNEG_IN                                                   | 11, 27                                                    | Supply           | Negative power supply for output stage. Connected internally, however both external connections are required.                                                                                                                                                    |

| PVDD                                                      | 14                                                        | Supply           | Buck-Boost converter power supply.                                                                                                                                                                                                                               |

| LP                                                        | 15                                                        | Analog<br>Output | External inductor positive terminal.                                                                                                                                                                                                                             |

| PVSS                                                      | 16                                                        | Supply           | Switch ground for Buck-Boost converter.                                                                                                                                                                                                                          |

| LN                                                        | 17                                                        | Analog<br>Output | External inductor negative terminal.                                                                                                                                                                                                                             |

| VPOS_IN                                                   | 23                                                        | Supply           | Positive power supply for output stage.                                                                                                                                                                                                                          |

| VOUT                                                      | 25                                                        | Analog<br>Output | Voltage output pin.                                                                                                                                                                                                                                              |

| IOUT                                                      | 26                                                        | Analog<br>Output | Current output pin.                                                                                                                                                                                                                                              |

| VSENSEP                                                   | 29                                                        | Analog Input     | Positive sense pin for voltage output.                                                                                                                                                                                                                           |

| VSENSEN                                                   | 30                                                        | Analog Input     | Negative sense pin for voltage output.                                                                                                                                                                                                                           |

| CCOMP 31 Analog capacitor improves stability for high cap |                                                           |                  | External compensation capacitor connection pin for voltage output. Addition of the external capacitor improves stability for high capacitive loads at the VOUT pin by reducing the bandwidth of the output amplifier at the expense of settling time.            |

| HART_IN                                                   | 32                                                        | Analog Input     | Input pin for HART modulation. If this pin is used it must be AC coupled to the HART input sinusoidal waveforms via a capacitor. If this feature is not used TI recommends to AC couple this pin to ground via a capacitor, though it may also be left floating. |

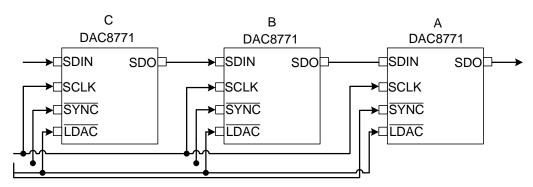

| SDO                                                       | 38                                                        | Digital Output   | Serial data output. Data is valid on the falling edge of SCLK.                                                                                                                                                                                                   |

| SDIN                                                      | 39                                                        | Digital Input    | Serial data input. Data is clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schmitt-Trigger logic input.                                                                                                              |

| SCLK                                                      | 40                                                        | Digital Input    | Serial clock input of serial peripheral interface (SPI™). Data can be transferred at rates up to 25 MHz. Schmitt-Trigger logic input.                                                                                                                            |

| SYNC                                                      | 41                                                        | Digital Input    | SPI™ bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is low. When SYNC is high SDO is in a high-impedance state.                                                                                        |

| LDAC                                                      | 42                                                        | Digital Input    | Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC output.                                                                                                                      |

| CLR                                                       | 43                                                        | Digital Input    | Level triggered clear pin (active high). Clears DAC output to zero code or mid code (see DAC Clear section).                                                                                                                                                     |

| RESET                                                     | 44                                                        | Digital Input    | Reset input (active low). Logic low on this pin causes the device to perform a reset.                                                                                                                                                                            |

| ALARM                                                     | 45                                                        | Digital Output   | $\overline{\text{ALARM}}$ pin. Open drain output. External pull-up resistor required (10 k $\Omega$ ). The pin goes low (active) when any ALARM condition is detected (open-circuit, over-temperature, watchdog timeout, and others).                            |

| NC                                                        | 1, 8, 10, 12,<br>13, 19, 21,<br>24, 36, 37,<br>46, 47, 48 | N/A              | No connection is required on these pins.                                                                                                                                                                                                                         |

| DNC                                                       | 22,33, 34,<br>35                                          | N/A              | Do not connect these pins.                                                                                                                                                                                                                                       |

# 7 Specifications

www.ti.com.cn

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| -                                              | -                                   | MIN     | MAX                     | UNIT |

|------------------------------------------------|-------------------------------------|---------|-------------------------|------|

|                                                | PVDD/AVDD to PBKG                   | -0.3    | 40                      |      |

|                                                | PVSS to GND                         | -0.3    | 0.3                     |      |

|                                                | VPOS_IN to VNEG_IN                  | -0.3    | 40                      |      |

|                                                | VPOS_IN to GND                      | -0.3    | 33                      |      |

|                                                | VNEG_IN to GND                      | -20     | 0.3                     |      |

| Input voltage                                  | VSENSEN to GND                      | VNEG_IN | VPOS_IN                 | V    |

|                                                | VSENSEP to GND                      | VNEG_IN | VPOS_IN                 |      |

|                                                | CCOMP to VNEG_IN                    | -0.3    | 6                       |      |

|                                                | DVDD to GND                         | -0.3    | 6                       |      |

|                                                | REFOUT/REFIN to GND                 | -0.3    | 6                       |      |

|                                                | Digital input voltage to GND        | -0.3    | DVDD+0.3                |      |

|                                                | VOUT to GND                         | VNEG_IN | VPOS_IN                 |      |

| Output voltage                                 | IOUT to GND                         | VNEG_IN | VPOS_IN                 | V    |

|                                                | SDO, ALARM to GND                   | -0.3    | DVDD+0.3                |      |

| Input Current                                  | Current into any pin                | -10     | 10                      | mA   |

| Power dissipation                              | ו                                   |         | (TJmax –<br>TA)/ThetaJA | W    |

| Operating junction temperature, T <sub>J</sub> |                                     | -40     | 150                     |      |

| Junction tempera                               | Junction temperature range (TJ max) |         | 150                     | °C   |

| Storage tempera                                | ture, T <sub>stg</sub>              | -65     | 150                     |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)(1)

|                         |                                                                | MIN  | NOM MAX | UNIT |

|-------------------------|----------------------------------------------------------------|------|---------|------|

| POWER SUPPL             | Y                                                              |      |         |      |

| PVDD/AVDD/ to GND       | Positive supply voltage to ground                              | 12   | 36      | ٧    |

| VPOS_IN to GND          | Positive supply voltage to ground for all modes                | -0.3 | 33      |      |

| VNEG_IN to              | Negative supply voltage to substrate for current output mode   | -18  | 0       | ٧    |

| GND                     | Negative supply voltage to substrate for voltage output mode   | -18  | -5      | ٧    |

| VPOS_IN to VNEG_IN      |                                                                | 12   | 36      | ٧    |

| VSENSEN to<br>GND       | The minimum headroom spec for voltage output stage must be met | -7   | 7       | V    |

| DVDD to GND             | Digital supply voltage to substrate                            | 2.7  | 5.5     | ٧    |

| DIGITAL INPUTS          | 3                                                              |      |         |      |

| VIH, input high voltage |                                                                | 2    |         | V    |

| VIL, input low          | 3.6 V < DVDD < 5.5 V                                           |      | 0.8     | V    |

| voltage                 | 2.7 V < DVDD < 3.6 V                                           |      | 0.6     | V    |

| REFERENCE INPUT         |                                                                |      |         |      |

| REFIN to GND            | Reference input to substrate                                   | 4.95 | 5.05    | V    |

| TEMPERATURE             | RANGE                                                          |      |         |      |

| TA                      | Operating temperature                                          | -40  | 125     | °C   |

<sup>(1)</sup> The minimum headroom spec for voltage output stage and the compliance voltage for current output stage should be met. When Buck-Boost converter is enabled VPOS\_IN\_x/VNEG\_IN\_x are generated internally to meet headroom and compliance specs. When Buck-Boost converter is disabled VPOS\_IN\_x, AVDD, and PVDD must be tied together.

### 7.4 Thermal Information

|                               |                                              | DAC8771 |      |

|-------------------------------|----------------------------------------------|---------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | RGZ     | UNIT |

|                               |                                              | 48 PINS |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 21.8    | °C/W |

| $R_{\theta JC(top)}$          | Junction-to-case (top) thermal resistance    | 9.2     | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 5.6     | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.1     | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 5.5     | °C/W |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance | 0.3     | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953

#### 7.5 Electrical Characteristics

|           | PARAMETER                                     | TEST CONDITIONS                                             | MIN    | TYP | MAX   | UNIT            |

|-----------|-----------------------------------------------|-------------------------------------------------------------|--------|-----|-------|-----------------|

| CURRENT ( | DUTPUT                                        |                                                             |        |     |       |                 |

|           |                                               |                                                             | 0      |     | 24    | mA              |

|           |                                               |                                                             | 0      |     | 20    | mA              |

| IOUT      | Output Current Ranges                         |                                                             | 3.5    |     | 23.5  | mA              |

|           |                                               |                                                             | -24    |     | 24    | mA              |

|           |                                               |                                                             | 4      |     | 20    | mA              |

| ACCURACY  | ,                                             |                                                             |        |     |       |                 |

|           | Resolution                                    |                                                             | 16     |     |       | Bits            |

| 18.11     | Dalatina (1)                                  | All ranges except bipolar range                             | -10    |     | 10    | LSB             |

| INL       | Relative accuracy <sup>(1)</sup>              | Bipolar range only                                          | -12    |     | 12    | LSB             |

| DNL       | Differential Nonlinearity <sup>(1)</sup>      | Ensured monotonic                                           | -1     |     | 1     | LSB             |

| -         |                                               | -40°C to 125°C                                              | -0.1   |     | 0.1   |                 |

| T         | Tatal Hard Posts of Fores (1)                 | TA = +25°C                                                  | -0.08  |     | 0.08  | 0/ 500          |

| TUE       | Total Unadjusted Error <sup>(1)</sup>         | -40°C to 125°C (4-20mA)                                     | -0.130 |     | 0.130 | %FSR            |

|           |                                               | TA = +25°C (4-20mA)                                         | -0.08  |     | 0.08  |                 |

|           |                                               | -40°C to 125°C                                              | -0.06  |     | 0.06  |                 |

| 05        | Offset Error <sup>(1)</sup>                   | TA = +25°C                                                  | -0.05  |     | 0.05  | %FSR            |

| OE        | Offset Error(1)                               | -40°C to -125°C (4-20mA)                                    | -0.085 |     | 0.085 |                 |

|           |                                               | TA = +25°C (4-20mA)                                         | -0.04  |     | 0.04  |                 |

| OE-TC     | Offset Error Temperature Coefficient          | -40°C to -125°C                                             |        | 1.5 |       | ppm FSR /<br>°C |

| 705       | Zana Onda Farra                               | DAC data set to 0x0000                                      | -13    |     | 13    | uA              |

| ZCE       | Zero Code Error                               | DAC data set to 0x0000 (4-20mA)                             | -13    |     | 13    | uA              |

| ZCE-TC    | Zero Code Error Temperature<br>Coefficient    | DAC data set to 0x0000, -40°C to -125°C                     |        | 1.5 |       | ppm/ °C         |

|           |                                               | -40°C to -125°C                                             | -0.1   |     | 0.1   |                 |

|           | 0 (1)                                         | TA = +25°C                                                  | -0.075 |     | 0.075 |                 |

| GE        | Gain Error <sup>(1)</sup>                     | -40°C to -125°C (4-20mA)                                    | -0.110 |     | 0.110 | %FSR            |

|           |                                               | TA = +25°C (4-20mA)                                         | -0.08  |     | 0.08  |                 |

| GE-TC     | Gain Error Temperature Coefficient            | -40C to -125C                                               |        | 3   |       | ppm FSR /<br>°C |

|           |                                               | DAC data set to 0xFFFF, -40°C to -125°C                     | -0.1   |     | 0.1   | %FSR            |

| FSE       | Full Scale Error                              | DAC data set to 0xFFFF, -40°C to -125°C (4-20mA)            | -0.130 |     | 0.130 | %FSR            |

| NFSE      | Negative Full Scale Error                     | DAC data set to 0x0000, bipolar range only, -40°C to -125°C | -0.05  |     | 0.05  | %FSR            |

| FSE-TC    | Full Scale Error Temperature<br>Coefficient   |                                                             |        | 3   |       | ppm FSR /<br>°C |

| DD75      | Picalas Zara Erra                             | bipolar range only, DAC data set to 0x8000, -40°C to -125°C | -0.05  |     | 0.05  | 0/505           |

| BPZE      | Bipolar Zero Error                            | bipolar range only, DAC data set to 0x8000, TA = +25°C      | -0.02  |     | 0.02  | %FSR            |

| BPZE-TC   | Bipolar Zero Error Temperature<br>Coefficient | 0x8000h into DAC,-40°C to -125°C                            |        | 4   |       | ppm/ °C         |

|           |                                               | 1                                                           |        |     |       |                 |

<sup>(1)</sup> For current output all ranges except ±24 mA, low code of 256d and a high code of 65280d are used, for ±24 mA range low code of 0d and a high code of 65280d. For voltage output, low code of 256d and a high code of 65280d are used

|            | PARAMETER                                     | TEST CONDITIONS                                                             | MIN            | TYP   | MAX           | UNIT            |

|------------|-----------------------------------------------|-----------------------------------------------------------------------------|----------------|-------|---------------|-----------------|

| \/O        | Loon Commission on Valteur                    | Output=24mA                                                                 |                |       | VPOS_I<br>N-3 |                 |

| VCL        | Loop Compliance Voltage                       | Output=±24mA                                                                | VNEG<br>_IN -3 |       | VPOS_I<br>N-3 | V               |

| RL         | Resistive Load                                | All except ±24 mA range                                                     |                |       | 1.2K          | Ω               |

| KL         | Resistive Load                                | ±24 mA range                                                                |                |       | 0.625K        | 22              |

| DC-PSRR    | DC Power Supply Rejection Ratio               | DAC data set to 0x8000, 20mA range                                          |                | 0.1   |               | μA/V            |

| Zo         | Output Impedance                              | DAC data set to 0x8000                                                      |                | 10    |               | $M\Omega$       |

| IOLEAK     | Output Current Leakage                        | lout is disabled or in power-down                                           |                | 1     |               | nA              |

| HART INTER | FACE                                          |                                                                             |                |       |               |                 |

| VHART-IN   | HART Input                                    |                                                                             | 400            | 500   | 600           | mVpp            |

|            | Corresponding Output                          | HART In = 500mVpp 1.2KHz                                                    |                | 1     |               | mApp            |

| VOLTAGE O  | UTPUT                                         |                                                                             |                |       |               |                 |

|            |                                               |                                                                             | 0              |       | 5             |                 |

|            | Voltage Output Ranges (normal mode)           |                                                                             | 0              |       | 10            |                 |

|            | Voltage Output Ranges (Overrange mode)        |                                                                             | -5             |       | 5             |                 |

| VOUT       |                                               |                                                                             | -10            |       | 10            |                 |

| VO01       |                                               |                                                                             | 0              |       | 6             |                 |

|            |                                               |                                                                             | 0              |       | 12            |                 |

|            |                                               |                                                                             | -6             |       | 6             |                 |

|            |                                               |                                                                             | -12            |       | 12            |                 |

| ACCURACY   |                                               |                                                                             |                |       |               |                 |

|            | Resolution                                    |                                                                             | 16             |       |               | Bits            |

| INL        | Relative Accuracy, INL <sup>(1)</sup>         |                                                                             | -12            |       | 12            | LSB             |

| DNL        | Differential Nonlinearity, DNL <sup>(1)</sup> | Ensured monotonic                                                           | -1             |       | 1             | LSB             |

| TUE        | Total Unadjusted Error, TUE <sup>(1)</sup>    | -40°C to 125°C, VOUT unloaded                                               | -0.1           | ±0.05 | 0.1           | %FSR            |

| TUE        | Total Olladjusted Ellor, TOE                  | TA = +25°C, VOUT unloaded                                                   | -0.75          |       | 0.75          | 70F3K           |

| BPZE       | Bipolar Zero Error                            | bipolar range only, DAC data set to 0x8000, -40°C to 125°C, VOUT unloaded   | -0.05          |       | 0.05          | %FSR            |

|            |                                               | bipolar range only, DAC data set to 0x8000, TA = +25°C, VOUT unloaded       | -0.03          |       | 0.03          |                 |

| BPZE-TC    | Bipolar Zero Error Temperature<br>Coefficient | bipolar range only, DAC data set to 0x8000, -40°C to 125°C, (VOUT unloaded) |                | 1     |               | ppm FSR /<br>°C |

| OE         | Offset Error                                  | Unipolar ranges only, (Vout unloaded), -40°C to 125°C                       | -5             |       | 5             | mV              |

| OE         | Offset Error                                  | Unipolar ranges only, (Vout unloaded), TA = 25°C                            |                | 0.65  |               | mV              |

| OE-TC      | Offset Error Temperature Coefficient          | Unipolar ranges only, -40°C to 125°C                                        |                | 1.5   |               | ppm FSR/ °C     |

| OF.        | Gain Error <sup>(1)</sup>                     | -40°C to 125°C, VOUT unloaded                                               | -0.1           |       | 0.1           | 0/ EQD          |

| GE         | Gain Ellory                                   | TA = +25°C, VOUT unloaded                                                   | -0.07          |       | 0.07          | %FSR            |

| GE-TC      | Gain Error Temperature Coefficient            |                                                                             |                | 3     |               | ppm FSR /<br>°C |

| FSE        | Full Scale Error                              | DAC data set to 0xFFFF, -40° to 125°C, (Vout unloaded)                      | -0.1           |       | 0.1           | %FSR            |

| ı OL       | Full Scale Error                              | DAC data set to 0xFFFF, 25°C, (Vout unloaded)                               |                | 0.03  |               | %FSR            |

|          | PARAMETER                                                | TEST CONDITIONS                                                                                 | MIN   | TYP   | MAX  | UNIT            |

|----------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|-------|------|-----------------|

| NFSE     | Negative Full Scale Error                                | Bipolar ranges only, DAC data set to 0x0000, -40°C to 125°C, (Vout unloaded)                    | -0.07 |       | 0.07 | %FSR            |

| INI OL   | negative Full Scale Effor                                | Bipolar ranges only, DAC data set to 0x0000, -40°C to 125°C, (Vout unloaded)                    |       | 0.002 |      | %FSR            |

| FSE-TC   | Full Scale Error Temperature<br>Coefficient              | (Vout unloaded)                                                                                 |       | 2     |      | ppm FSR /<br>°C |

|          | Headroom                                                 | Output unloaded, VPOS_IN with respect to VOUT, DAC data set to 0xFFFF, specified by design      | 0.5   |       |      | V               |

|          |                                                          | 1kΩ output load, VPOS_IN with respect to VOUT, DAC data set to 0xFFFF, specified by design      | 3     |       |      | V               |

|          |                                                          | Bipolar, ranges only, VNEG_IN with respect to VOUT, DAC data set to 0x0000, specified by design | -3    |       |      | V               |

|          | Footroom                                                 | Unipolar ranges only, VNEG_IN with respect to VOUT, DAC data set to 0x0000, specified by design | -5    |       |      | V               |

|          | Short-Circuit Current                                    | SCLIM[1:0] = "00" (see register map)                                                            | 17    |       | 27   | mA              |

|          |                                                          | SCLIM[1:0] = "01" (see register map)                                                            | 8     |       | 12   | mA              |

|          |                                                          | SCLIM[1:0] = "10" (see register map)                                                            | 22    |       | 30   | mA              |

|          |                                                          | SCLIM[1:0] = "11" (see register map)                                                            | 26    |       | 36   | mA              |

| RL       | Load                                                     |                                                                                                 | 1     |       |      | kΩ              |

|          | Capacitive Load Stability                                | RL = Open                                                                                       |       |       | 20   | nF              |

| CL       |                                                          | $RL = 1 k\Omega$                                                                                |       |       | 20   | nF              |

|          |                                                          | RL = 1 k $\Omega$ with External compensation capacitor (150pF) connected.                       |       |       | 1    | μF              |

| 70       | DC Output Impedance                                      | Voltage output enabled, Vout = Mid-Scale, 0-10V range                                           |       | 0.01  |      | Ω               |

| ZO       |                                                          | Voltage output disabled                                                                         |       | 50    |      | $M\Omega$       |

|          |                                                          | Voltage output disabled (POC = '0')                                                             |       | 30    |      | kΩ              |

| DC-PSRR  | DC Power Supply Rejection Ratio                          | No Output Load                                                                                  |       | 10    |      | μV/V            |

|          | VSENSEP Impedance                                        | VOUT Enabled, Vout = Mid-Scale, 0-<br>10V Range, specified by design                            |       | 120   |      | kΩ              |

|          | VSENSEN Impedance                                        | VOUT Enabled, Vout = Mid-Scale, 0-<br>10V Range, specified by design                            |       | 240   |      | kΩ              |

| EXTERNAL | REFERENCE INPUT                                          |                                                                                                 |       |       |      |                 |

| IREF     | External reference current                               | Vout = Negative Full-Scale, ±12V range                                                          |       | 350   |      | μΑ              |

|          | Reference Input Capacitance                              |                                                                                                 |       | 100   |      | pF              |

|          | REFERENCE OUTPUT                                         |                                                                                                 |       |       | 1    |                 |

| VREF     | Reference Output                                         | TA = 25°C                                                                                       | 4.99  |       | 5.01 | V               |

| VREF-TC  | Reference TC                                             | TA = -40°C to 125°C                                                                             | -10   |       | 10   | ppm/°C          |

| TUE      | DAC Voltage Output Total unadjusted error <sup>(1)</sup> | -40°C to 125°C, VOUT unloaded,<br>Internal reference enabled                                    |       | 0.2   |      | %FSR            |

|          | DAC Current Output Total unadjusted error <sup>(1)</sup> | -40°C to +125°C, Internal reference enabled                                                     |       | 0.2   |      | %FSR            |

|          | Output Noise (0.1 Hz to 10 Hz)                           | TA = 25°C                                                                                       |       | 13    |      | µV р-р          |

|          | Noise Spectral Density                                   | At 10 kHz, 25°C                                                                                 |       | 200   |      | nV/sqrtHz       |

|            | PARAMETER                         | TEST CONDITIONS                                                           | MIN          | TYP  | MAX | UNIT  |

|------------|-----------------------------------|---------------------------------------------------------------------------|--------------|------|-----|-------|

| CL         | Capacitive Load                   |                                                                           |              |      | 600 | nF    |

| IL         | Load Current                      |                                                                           |              | ±5   |     | mA    |

|            | Short Circuit Current             | Reference output shorted to GND                                           |              | 20   |     | mA    |

|            | Load Regulation                   | Sourcing and Sinking, TA = +25°C                                          |              | 5    |     | μV/mA |

|            | Line regulation                   | TA = +25°C                                                                |              | 1    |     | uV/V  |

| виск вос   | ST CONVERTER                      |                                                                           |              |      |     |       |

| RON        | Switch On Resistanvce             | TA = +25°C                                                                |              | 3    |     | Ω     |

| ILEAK      | Switch Leakage Current            | TA = +25°C                                                                |              | 20   |     | nA    |

| L          | Inductor                          | between LP and LN                                                         |              | 100  |     | μH    |

| ILMAX      | Peak Inductor Current             | TA = +25°C, maximum specified by design                                   |              | 0.35 | 0.5 | Α     |

|            | 0                                 | VPOS_IN                                                                   | 4            |      | 32  | V     |

| VO         | Output Voltage                    | VNEG_IN                                                                   | -18          |      | -5  | V     |

| CL         | Load Capacitor                    | VPOS_IN and VNEG_IN                                                       | 10           |      |     | μF    |

|            | Start up time                     | After enabling VPOS_IN and VNEG_IN with 10µF load capacitor on these pins |              | 3    |     | ms    |

| DVDD LDO   |                                   |                                                                           |              |      | ·   |       |

| VO         | Output Voltage                    |                                                                           |              | 5    |     | V     |

| ILOAD      | Load Current                      |                                                                           |              |      | 10  | mA    |

| CL         | Load Capacitor                    |                                                                           |              |      | 0.2 | μF    |

| THERMAL    | ALARM                             |                                                                           |              |      |     |       |

|            | Trip point                        |                                                                           |              | 150  |     | °C    |

|            | Hysteresis                        |                                                                           |              | 15   |     | °C    |

| DIGITAL IN | PUTS                              |                                                                           |              |      | ·   |       |

|            | Hysteresis voltage                |                                                                           |              | 0.4  |     | V     |

|            | Input Current                     |                                                                           | -5           |      | 5   | μΑ    |

|            | Pin Capacitance                   | Per pin                                                                   |              | 10   |     | pF    |

| DIGITAL O  | JTPUTS                            |                                                                           |              |      | ·   |       |

| SDO        |                                   |                                                                           |              |      |     |       |

| VOL        | Output Low Voltage                | Sinking 200 μA                                                            |              |      | 0.4 | V     |

| VOH        | Output High Voltage               | Sourcing 200 µA                                                           | DVDD-<br>0.5 |      |     | V     |

| ILEAK      | High Impedance Leakage            |                                                                           | -5           |      | 5   | μΑ    |

|            | High Impedance Output Capacitance |                                                                           |              | 10   |     | pF    |

| ALARM      |                                   |                                                                           |              |      |     |       |

| VOL        | Output Low Voltage                | At 10 mA                                                                  |              | 0.4  |     | V     |

| ILEAK      | High Impedance Leakage            |                                                                           |              | 50   |     | μA    |

|            | High Impedance Output Capacitance |                                                                           |              | 10   |     | pF    |

| POWER RE   | QUIREMENTS                        |                                                                           |              |      |     |       |

| IVANDD     | Current Flowing into AVDD         | Buck-Boost converter enabled, All IOUT Active, 0mA, 0-20mA range          |              | 3    |     | mA    |

| IAVDD      |                                   | IOUT Active, 0 mA, 0-20mA range, VNEG_IN = 0V                             |              | 1.3  |     | mA    |

| IPVDD      | Current Flowing into PVDD         | Buck-Boost converter enabled, Peak<br>Current, specified by design        |              |      | 0.5 | А     |

|            |                                   | Buck-Boost converter disabled                                             |              | 0.1  |     | mA    |

## **Electrical Characteristics (continued)**

|                   | PARAMETER                                | TEST CONDITIONS                                                                                                                             | MIN TY | P MAX    | UNIT      |

|-------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----------|

| IDVDD             | Current Flowing into DVDD                | All digital pins at DVDD, DVDD 2.7V to 5.5V                                                                                                 | 1      | .8       | mA        |

|                   |                                          | IOUT Active, 0mA, 0-20mA range                                                                                                              |        | 1.2      | mA        |

| IVPOS_IN          | Current Flowing into VPOS_IN             | VOUT Active, no load, 0-10V range, mid scale code                                                                                           |        | 3        | mA        |

|                   |                                          | IOUT Active, 0mA, ±24mA range                                                                                                               |        | 1.2      | mA        |

| IVNEG_IN          | Current Flowing into VNEG_IN             | VOUT Active, no load, 0-10V range, mid scale code                                                                                           |        | 3        | mA        |

| PDISS             | Power dissipation (PVDD+AVDD)            | Buck-Boost converter positive output enabled, IOUT mode operation, All IOUT channels enabled, Rload = $1\Omega$ , 24mA, PVDD = AVDD = $12V$ | 0.22   | 26 0.275 | W         |

| IVSENSEP          | Current Flowing into VSENSEP             | VOUT Disabled, specified by design                                                                                                          |        | 40       | nA        |

| IVSENSEN          | Current Flowing into VSENSEN             | VOUT Disabled, specified by design                                                                                                          |        | 20       | nA        |

| DYNAMIC P         | ERFORMANCE                               |                                                                                                                                             |        |          |           |

| VOLTAGE O         | DUTPUT                                   |                                                                                                                                             |        |          |           |

|                   | Output Voltage Settling Time             | 0 to 10V, to ±0.03% FSR RL = 1k $\Omega$    CL = 200pF                                                                                      | 1      | 5        | μs        |

| т.                |                                          | 0 to 5V, to ±0.03% FSR RL = 1k $\Omega$    CL = 200pF                                                                                       | 1      | 0        | μs        |

| T <sub>sett</sub> |                                          | -5 to 5V, to ±0.03% FSR RL = 1k $\Omega$    CL = 200pF                                                                                      | 2      | 20       | μs        |

|                   |                                          | -10 to 10V, to ±0.03% FSR RL = $1k\Omega$    CL = 200pF                                                                                     | 3      | 30       | μs        |

|                   | Output voltage ripple                    | Buck-Boost converter enabled, 50 KHz<br>20dB/decade low-pass filter on<br>VPOS_IN                                                           |        | 2        | mVpp      |

| SR                | Slew Rate                                | RL = 1kΩ    CL = 200pF                                                                                                                      |        | 1        | V/µs      |

|                   | Power-On Glitch Energy <sup>(2)</sup>    | Specified by design                                                                                                                         |        | 0.1      | V         |

|                   | Power-off Glitch Energy <sup>(3)</sup>   | Specified by design                                                                                                                         |        | 0.8      | V         |

|                   | Code-Code Glitch                         |                                                                                                                                             | 0.1    | 5        | μV-sec    |

|                   | Digital Feedthrough                      |                                                                                                                                             |        | 1        | nV-sec    |

|                   | Output Noise (0.1 Hz to 10 Hz Bandwidth) | 0-10V range, Mid-Scale                                                                                                                      | 0      | .1       | LSB p-p   |

|                   | Output Noise (100 kHz Bandwidth)         | 0-10V range, Mid-Scale                                                                                                                      | 20     | 00       | μVrms     |

|                   | Output Noise Spectral Density            | ±10V Measured at 10 kHz, Mid-Scale                                                                                                          | 20     | 00       | nV/sqrtHz |

| AC-PSRR           | AC Power Supply Rejection Ratio          | 200mV 50/60Hz sinusoid superimposed on power supply voltage (AC analysis).                                                                  | -7     | '5       | dB        |

| CURRENT C         | DUTPUT                                   |                                                                                                                                             |        |          |           |

|                   |                                          | 24 mA Step, to 0.1% FSR, no L                                                                                                               | 1      | 0        | μs        |

| Tsett             | Output Current Settling Time             | 24 mA Step, to 0.1% FSR , L = 1mH, CL = 22nF                                                                                                | 5      | 60       | μs        |

|                   | Output current ripple                    | Buck-boost converter enabled, 50 KHz 20dB/decade low-pass filter on VPOS_IN                                                                 |        | 2        | μΑрр      |

| L                 | Inductive Load <sup>(4)</sup>            |                                                                                                                                             |        | 50       | mH        |

<sup>(2)</sup> No load, DVDD supply ramps up before VPOS\_IN, and VNEG\_IN, ramp rate of VPOS\_IN, and VNEG\_IN limited to 18V/msec (3) Vout disabled, no load, ramp rate of VPOS\_IN, and VNEG\_IN limited to 18V/msec

<sup>680</sup>nF is required at IOUT pin for 50mH pure inductor load

| PARAMETER                               | TEST CONDITIONS                                                    | MIN | TYP | MAX | UNIT |

|-----------------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| AC-PSRR AC Power Supply Rejection Ratio | 200mV 50/60Hz Sine wave<br>superimposed on power supply<br>voltage |     | -75 |     | dB   |

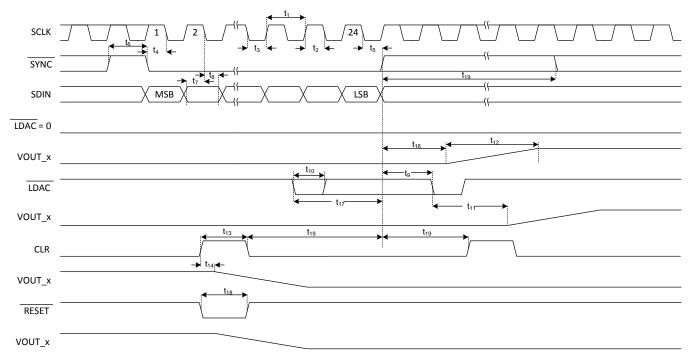

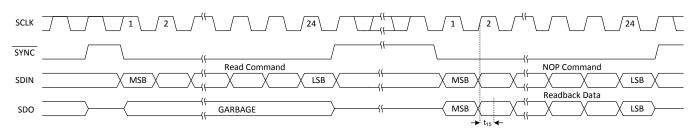

# 7.6 Timing Requirements: Write and Readback Mode

At  $T_A = -40^{\circ}\text{C}$  to +125°C and DVDD = +2.7 V to +5.5 V, unless otherwise noted.

|                   | PARAMETER                                                                | TEST CONDITIONS                    | MIN         | MAX   | UNIT |

|-------------------|--------------------------------------------------------------------------|------------------------------------|-------------|-------|------|

| f <sub>SCLK</sub> | Max clock frequency                                                      |                                    |             | 25    | MHz  |

| t <sub>1</sub>    | SCLK cycle time                                                          |                                    | 40          |       | ns   |

| t <sub>2</sub>    | SCLK high time                                                           |                                    | 18          |       | ns   |

| t <sub>3</sub>    | SCLK low time                                                            |                                    | 18          |       | ns   |

| t <sub>4</sub>    | SYNC falling edge to SCLK falling edge setup time                        |                                    | 15          |       | ns   |

| t <sub>5</sub>    | 24 <sup>th</sup> /32 <sup>nd</sup> SCLK falling edge to SYNC rising edge |                                    | 13          |       | ns   |

| t <sub>6</sub>    | SYNC high time                                                           | Digital slew rate control disabled | 40          |       | ns   |

| t <sub>7</sub>    | Data setup time                                                          |                                    | 8           |       | ns   |

| t <sub>8</sub>    | Data hold time                                                           |                                    | 5           |       | ns   |

| t <sub>9</sub>    | SYNC rising edge to LDAC falling edge                                    |                                    | 33          |       | ns   |

| t <sub>10</sub>   | LDAC pulse width low                                                     |                                    | 10          |       | ns   |

| t <sub>11</sub>   | LDAC falling edge to DAC output response time                            |                                    |             | 50    | ns   |

| t <sub>12</sub>   | DAC output settling time                                                 |                                    | See section | n 5.3 | μs   |

| t <sub>13</sub>   | CLR high time                                                            |                                    | 10          |       | ns   |

| t <sub>14</sub>   | CLR activation time                                                      |                                    |             | 50    | ns   |

| t <sub>15</sub>   | SCLK rising edge to SDO valid                                            |                                    |             | 14    | ns   |

| t <sub>16</sub>   | SYNC rising edge to DAC output response time                             |                                    |             | 50    | ns   |

| t <sub>17</sub>   | LDAC falling edge to SYNC rising edge                                    |                                    | 100         |       | ns   |

| t <sub>18</sub>   | RESET pulse width                                                        |                                    | 10          |       | ns   |

| t <sub>19</sub>   | SYNC rising edge to CLR falling/rising edge                              |                                    | 60          |       | ns   |

图 1. Write Mode Timing

图 2. Readback Mode Timing

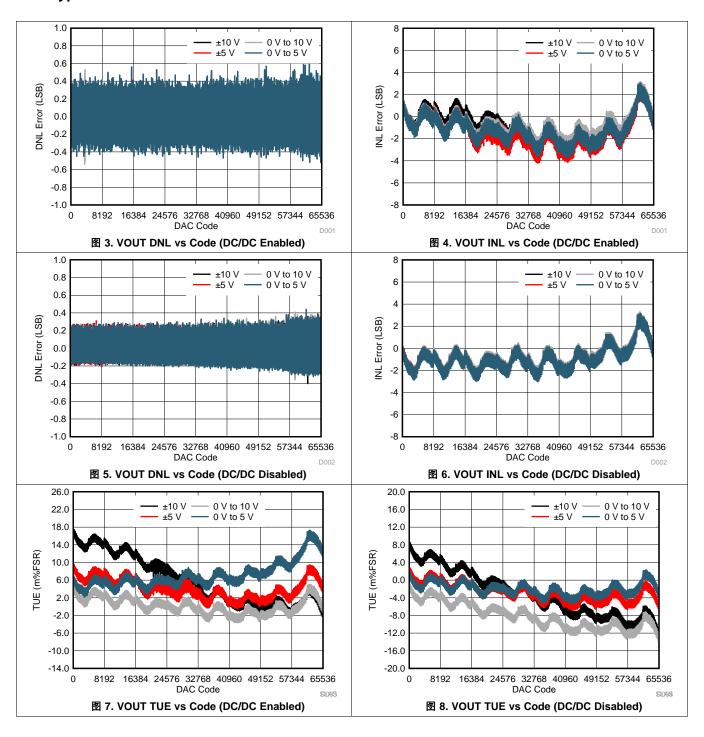

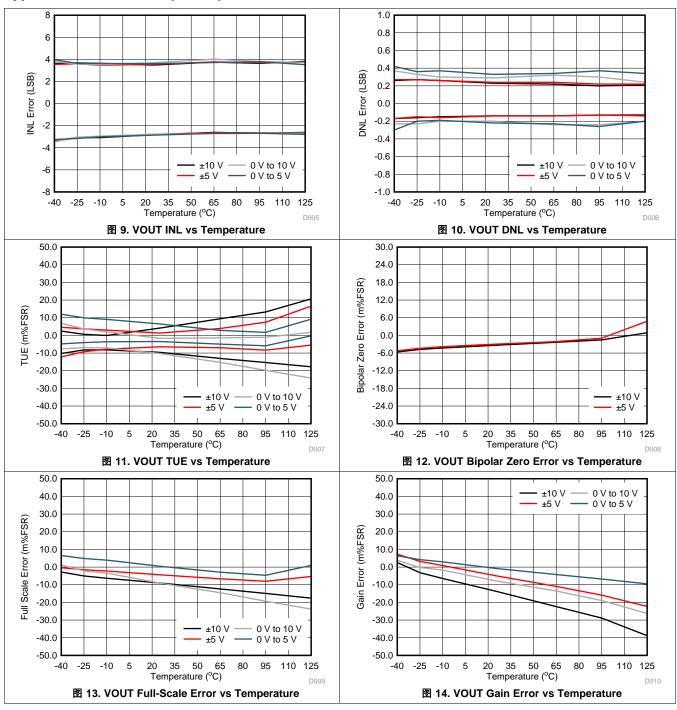

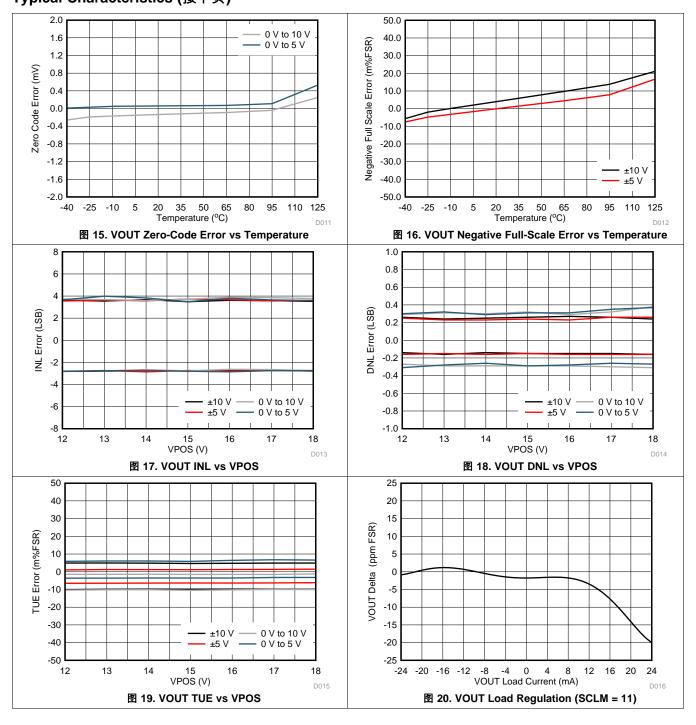

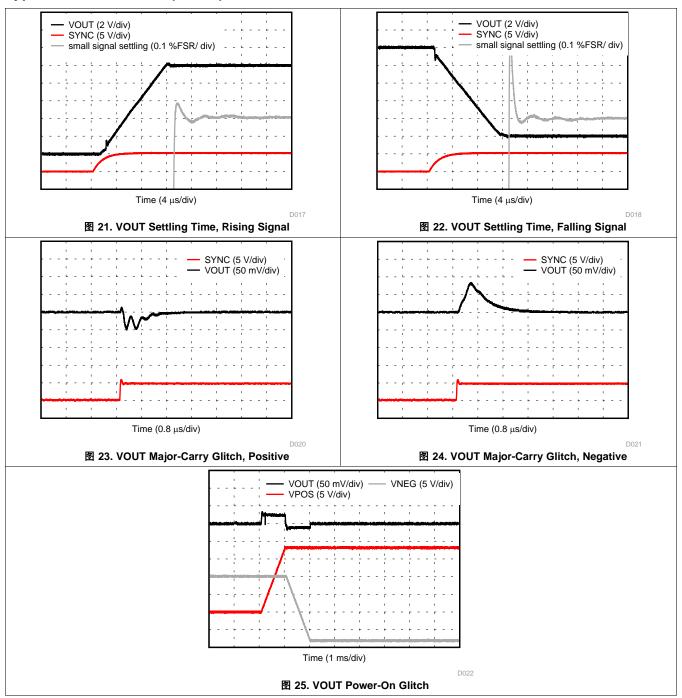

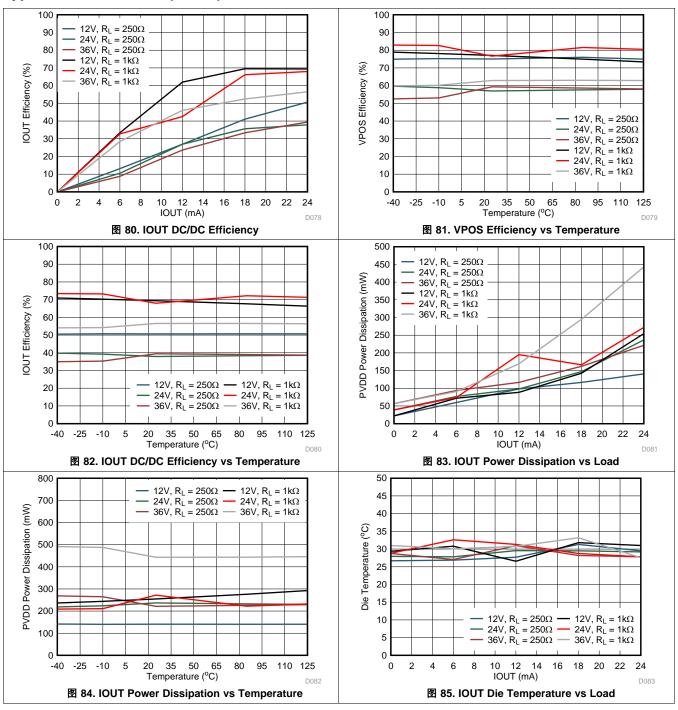

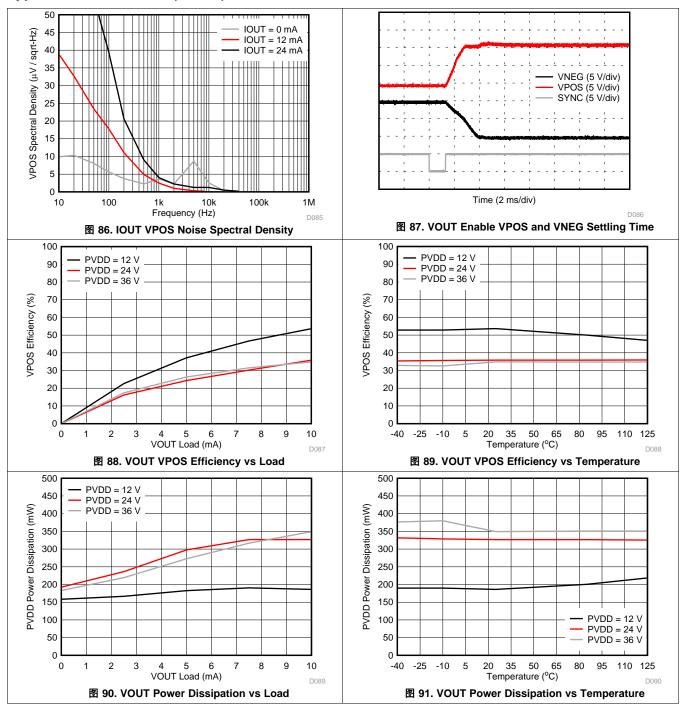

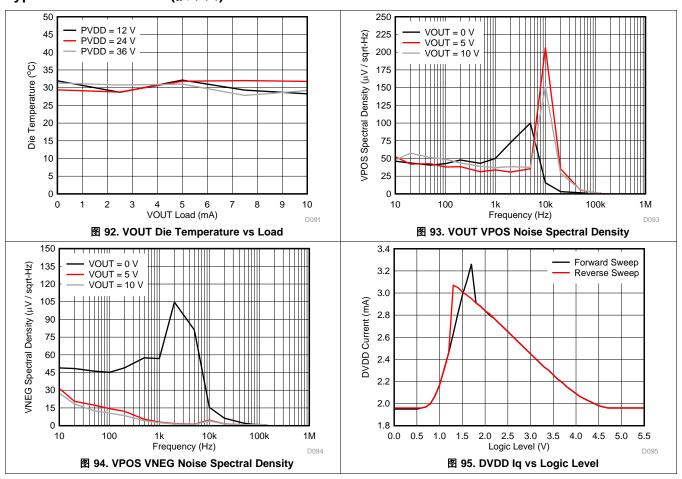

### 7.7 Typical Characteristics

Typical Characteristics (接下页)

#### 40 ±24 mA 3.5 mA to 23.5 mA 3.5 mA to 23.5 mA 30 6 0 mA to 20 mA -- 4 mA to 20 mA 0 mA to 20 mA - 4 mA to 20 mA 0 mA to 24 mA 0 mA to 24 mA 20 Error (LSB) (m%FSR) 2 10 0 0 TUE ( -2 -10 -20 -6 -30 -8 -40 8192 16384 24576 32768 40960 49152 57344 65536 8192 16384 24576 32768 40960 49152 57344 65536 0 0 DAC Code DAC Code 图 38. IOUT INL vs Code (DC/DC Disabled) 图 39. IOUT TUE vs Code (DC/DC Enabled) 40 8 30 6 20 TUE (m%FSR) 10 INL (LSB) -10 -20 3.5 mA to 23.5 mA 3.5 mA to 23.5 mA 0 mA to 20 mA 4 mA to 20 mA 0 mA to 20 mA 4 mA to 20 mA -30 -6 0 mA to 24 mA 0 mA to 24 mA -40 -8 8192 16384 24576 32768 40960 49152 57344 65536 -25 -10 0 -40 5 20 35 50 65 80 95 110 125 DAC Code Temperature (°C) D037 图 40. IOUT TUE vs Code (DC/DC Enabled) 图 41. IOUT INL vs Temperature 1.0 50 0.8 40 0.6 30 0.4 20 TUE (m%FSR) 10 0.2 0.0 0 -0.2 -10 -20 -0.4 3.5 mA to 23.5 mA ±24 mA 3.5 mA to 23.5 mA -0.6 -30 0 mA to 20 mA $\,$ 0 mA to 20 mA - 4 mA to 20 mA 4 mA to 20 mA -0.8 -40 0 mA to 24 mA 0 mA to 24 mA -50 35 50 65 20 35 50 -40 -25 -10 20 80 95 110 125 -40 -25 -10 65 80 95 110 125 Temperature (°C) Temperature (°C) 图 42. IOUT DNL vs Temperature 图 43. IOUT TUE vs Temperature

# 8 Detailed Description

#### 8.1 Overview

www.ti.com.cn

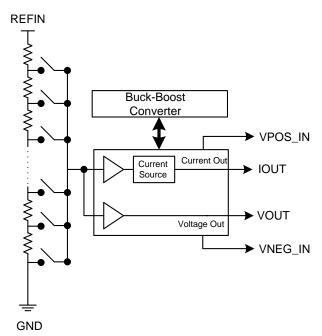

The DAC8771 consists of a resistor-string digital-to-analog converter (DAC) followed by buffer amplifiers. The output of the buffer drives the current output stage and the voltage output amplifier. The resistor-string section is simply a string of resistors, each of value R, from REFIN to GND, as Functional Block Diagram illustrates. This type of architecture ensures DAC monotonicity. The 16-bit binary digital code loaded to the DAC register determines at which node on the string the voltage is tapped off before being fed into the output amplifier. The current output stage converts the output from the string to current using a precision current source. The voltage output provides a voltage output to the external load. When the current output stage is disabled the IOUT pin is Hi-Z. When the voltage output stage is disabled, the output impedance is controlled by the POC bit, by default set to 30 k $\Omega$ . After power-on, both output stages are disabled. The DAC8771 also contains a Buck-Boost converter which can be used to generate the power supply for the current output stage and voltage output amplifier.

#### 8.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

图 96. General Architecture

#### 8.3 Feature Description

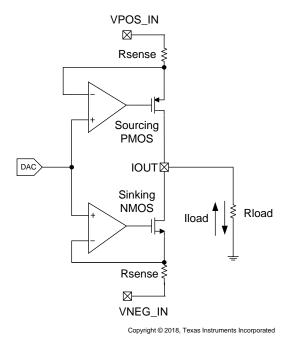

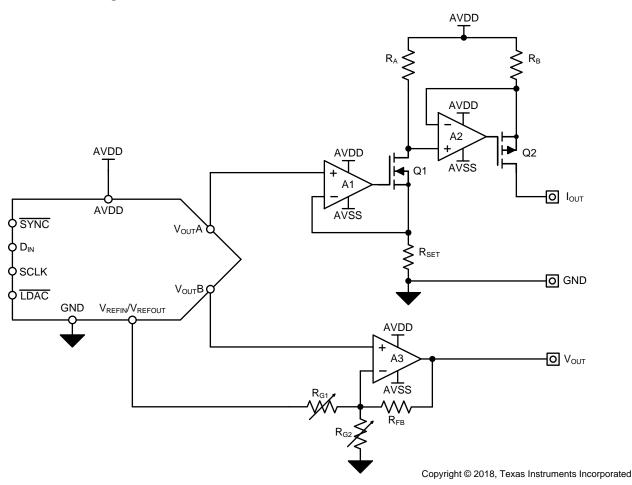

#### 8.3.1 Current Output Stage

The current output stage consists of a pre-conditioner and a precision current source as shown in  $\ 20$  97. This stage provides a current output according to the DAC code. The output range can be programmed as 0 mA - 20 mA, 0 mA - 24 mA, 4 mA - 20 mA, 3.5 mA - 23.5 mA, or  $\pm 24$  mA. In the current output mode, the maximum compliance voltage on pin IOUT is between (-|VNEG\_IN| + 3 V)  $\leq$  |V<sub>IOUT</sub>|  $\leq$  (VPOS\_IN - 3 V). When in unipolar current output modes the low-side of the compliance voltage limit is replaced by GND. This compliance voltage is automatically maintained when the Buck-Boost converter is used to generate these supplies (see Buck-Boost Converter section). However, when using an external supply for VPOS\_IN pin (Buck-Boost converter disabled), the VPOS\_IN and VNEG\_IN supplies should be chosen such that this compliance voltage is maintained.

# Feature Description (接下页)

图 97. Current Output

The 16 bit data can be written to DAC8771 using address 0x05 (DAC data register, 表 4 and 表 5).

For a 0-mA to 20-mA output range:

$$IOUT = 20mA \ x \left[ \frac{CODE}{2^N} \right] \tag{1}$$

For a 0-mA to 24-mA output range:

$$IOUT = 24mA \ x \left[ \frac{CODE}{2^N} \right] \tag{2}$$

For a 3.5-mA to 23.5-mA output range:

$$IOUT = 20mA x \left[ \frac{CODE}{2^N} \right] + 3.5mA \tag{3}$$

For a 4-mA to 20-mA output range:

$$IOUT = 16mA x \left[ \frac{CODE}{2^N} \right] + 4mA \tag{4}$$

For a -24-mA to 24-mA output range:

$$IOUT = 40mA \ x \left[ \frac{CODE}{2^N} \right] - 20mA \tag{5}$$

Where:

- CODE is the decimal equivalent of the code loaded to the DAC.

- N is the bits of resolution; 16

# Feature Description (接下页)

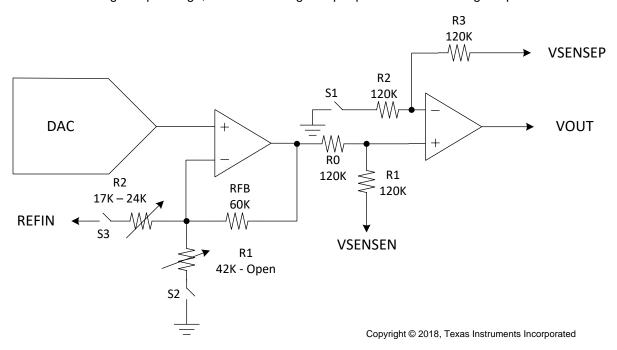

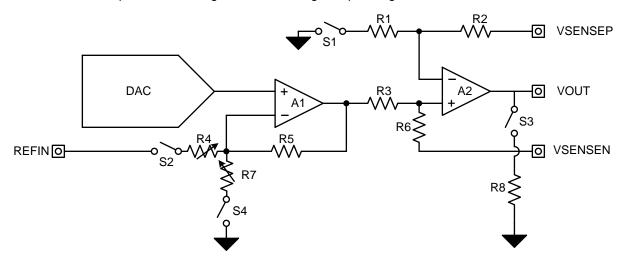

#### 8.3.2 Voltage Output Stage

The voltage output stage as conceptualized in

8 98 provides the voltage output according to the DAC code and the output range setting. The output range can be programmed as 0 V to +5 V or 0 V to +10 V for unipolar output mode, and ±5 V or ±10V for bipolar output mode. In addition, an option is available to increase the output voltage range by 20%. The output current drive can be up to 34 mA. The output stage has short-circuit current protection that limits the output current to 16 mA, this limit can be changed to 8 mA, 20 mA or 24 mA via writing bits 15 and 14 of address 0x04. The minimum headroom and foot-room for the voltage output stage is automatically maintained when the Buck-Boost converter is used to generate these supplies. However, when using an external supply for VPOS\_IN and VNEG\_IN pin (Buck-Boost converter disabled) the minimum headroom and foot-room as per must be maintained. In this case, the *Recommended Operating Conditions* shows the maximum allowable difference between VPOS\_IN and VNEG\_IN.

The voltage output is designed to drive capacitive loads of up to 1  $\mu$ F. For loads greater than 20 nF, an external compensation capacitor must be connected between CCOMP and VOUT to keep the output voltage stable at the expense of reduced bandwidth and increased settling time. Note that, a step response (due to input code change) on the voltage output pin loaded with large capacitive load (> 20 nF) triggers the short circuit limit circuit of the output stage. This results in setting the short circuit alarm status bits. Therefore, it is recommended to use slew rate control for large step change, when the voltage output pin is loaded with high capacitive loads.

图 98. Voltage Output

The VSENSEP pin is provided to enable sensing of the load. Ideally, it is connected to VOUT at the terminals. Additionally, it can also be used to connect remotely to points electrically "nearer" to the load. This allows the internal output amplifier to ensure that the correct voltage is applied across the load as long as headroom is available on the power supply. However, if this line is cut, the amplifier loop would be broken. Therefore, an optional resistor can be used between VOUT and VSENSEP to prevent this.

The VSENSEN pin can be used to sense the remote ground and offset the VOUT pin accordingly. The VSENSEN pin can sense a maximum of ±7 V difference from the GND pin of the DAC8771.

The 16 bit data can be written to DAC8771 as shown in DAC data registers,表 4 and 表 5.

For unipolar output mode:

$$VOUT = VREFIN \ x \ GAIN \ x \ \left[\frac{CODE}{2^N}\right]$$

(6)

### Feature Description (接下页)

For bipolar output mode:

$$VOUT = VREFIN \times GAIN \times \left[\frac{CODE}{2^N}\right] - \frac{GAIN \times VREFIN}{2}$$

(7)

#### Where:

- CODE is the decimal equivalent of the code loaded to the DAC.

- N is the bits of resolution; 16

- VREFIN is the reference voltage; for internal reference, VREFIN = +5 V.

- GAIN is automatically selected for a desired voltage output range as shown in

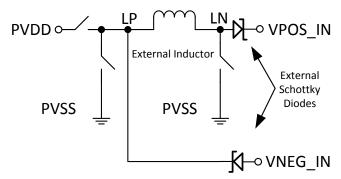

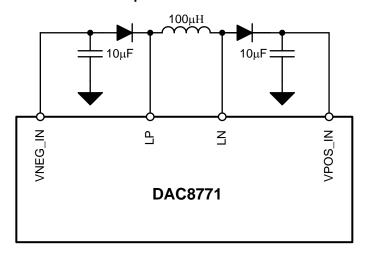

#### 8.3.3 Buck-Boost Converter

The DAC8771 includes a Buck-Boost Converter to minimize the power dissipation of the chip and provides significant system integration. This Buck-Boost converter is based on a Single Inductor Multiple Output (SIMO) architecture and requires a single inductor to simultaneously generate all the analog power supplies required by the chip. The Buck-Boost converter uses three on-chip switches (shown in 99) which are synchronously controlled via current mode control logic. The DC/DC converter is designed to work in discontinuous conduction mode (DCM) with an external inductor of value 100 μH connected between LN and LP pins (see *Buck-Boost Converter External Component Selection* section). The peak inductor current inductor is limited to a value of 0.5 A internally.

图 99. Buck-Boost Converter

The Buck-Boost converter employs a variable switching frequency technique. This technique increases the converter efficiency at all loads by automatically reducing the switching frequency at light loads and increasing it at heavy loads. At no load condition, the converter stops switching completely until the load capacitor discharges by a preset voltage. At this point, the converter automatically starts switching and recharges the load capacitor(s). In addition to saving power at all loads, this technique ensures low switching noise on the converter outputs at light loads. The minimum load capacitor for the Buck-Boost converter is 10  $\mu$ F. This capacitor must be connected between the Schottky diode(s) and ground (0 V) for each arm of the Buck-Boost converter. The Buck-Boost converter, when enabled, generates ripples on the supply pins (VPOS\_IN and VNEG\_IN). This ripple is typically attenuated by the power supply rejection ratio of the output amplifiers (IOUT or VOUT) and appears as noise on the output pin of the amplifiers (IOUT and VOUT). A larger load capacitor in combination with additional filter (see application section) reduces the output ripple at the expense of increasing settling time of the converter output.

The input voltage to the Buck-Boost converter (pin PVDD) can vary from +12 V to +36 V. These outputs can be individually enabled or disabled via the user SPI interface (See Commands in  $\frac{1}{5}$  4 and  $\frac{1}{5}$  5).

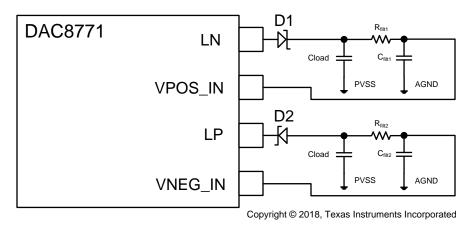

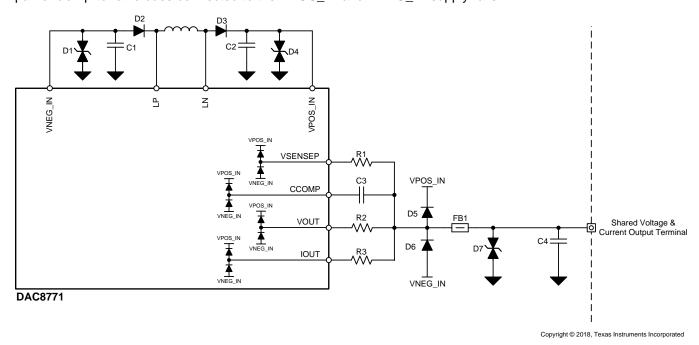

### 8.3.3.1 Buck-Boost Converter Outputs

The Buck-Boost converter can be used to provide power to the current output stage or the voltage output stage by enabling the Buck-Boost converter and connecting the power supplies as shown in ₹ 100. Additional passive filters can optionally be added between the Schottky diode and input supply pins (VPOS\_IN and VNEG\_IN) to attenuate the ripple feeding into the VPOS\_IN and VNEG\_IN pin.

### Feature Description (接下页)

图 100. Buck-Boost Converter Positive and Negative Outputs

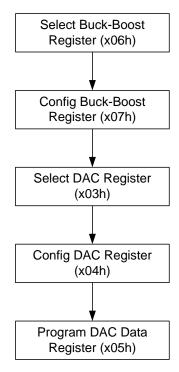

#### 8.3.3.2 Selecting and Enabling Buck-Boost Converter

The analog outputs of the Buck-Boost converter can be enabled in two different ways: Current Output Mode or Voltage Output Mode. The positive/negative arm of the selected Buck-Boost converter can be enabled via writing to address 0x07 (*Configuration Buck-Boost Register (address = 0x07) [reset = 0x0000]*). Note that, VNEG\_IN is internally shorted to GND when the negative arm of Buck-Boost converter is not enabled.

When used in voltage output mode, the Buck-Boost converter generates a constant ±15.0 V for the positive and negative power supplies.

When used in current output mode the Buck-Boost converter generates the positive and negative power supply based on the RANGE setting, for example the negative power supply is only generated for ±24 mA range.

The minimum voltage that the Buck-Boost converter can generate on the VPOS\_IN pin in 4.96 V with a typical efficiency of 75% at PVDD = 12 V and a load current of 24 mA, thus significantly minimizing power dissipation on chip. The maximum voltage that the Buck-Boost converter can generate on the VPOS\_IN pin is 32 V. Similarly, the minimum voltage that the Buck-Boost converter can generate on the VNEG\_IN pin in -15.0 V. The maximum voltage that the Buck-Boost converter can generate on the VNEG\_IN pin in -5.0 V

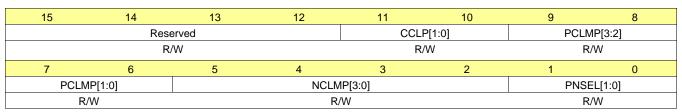

#### 8.3.3.3 Configurable Clamp Feature and Current Output Settling Time

A large signal step on the output pin IOUT (for example 0 mA to 24 mA) with a load of 1 K $\Omega$  would require that the respective Buck-Boost converter change the output voltage on the VPOS\_IN pin from 4.0 V to 27 V. Thus, the current output settling time will be dominated by the settling time of the VPOS\_IN voltage. A trade off can be made to reduce the settling time at the expense of power saving by increasing the minimum voltage that the respective Buck-Boost converter generates on the positive output.

The DAC8771 implements a configurable clamp feature. This feature allows multiple modes of operation based on CCLP[1:0] and HSCLMP bits (*Configuration Buck-Boost Register (address = 0x07) [reset = 0x0000]*).

### 8.3.3.3.1 Default Mode - CCLP[1:0] = "00"

This is the default mode of operation, CCLP[1:0] = "00" for Buck-Boost converter is to be in full tracking mode. The minimum voltage generated on VPOS\_IN in this case is 4 V. The Buck-Boost converter varies the positive and negative outputs adaptively such that the voltage across these outputs and IOUT pins is  $\leq$  3 V. This is accomplished by internally feeding back the voltage across the current output PMOS and NMOS to the respective Buck-Boost converter control circuit. For example, for a load current of 24 mA flowing through a load resistance of 1 K $\Omega$ , the generated voltage at the VPOS\_IN pin will be around 27V.

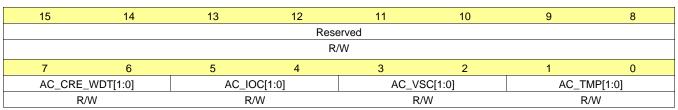

#### 8.3.3.3.2 Fixed Clamp Mode - CCLP[1:0] = "01"